# Ģ ita 8 2 2 8 8 ilta ig

DZS11-EA OPTION DESCRIPTION

# digital Computer Special Systems

AUSTRALIA

# digital **Computer Special Systems**

OPTION DESCRIPTION

DZS11-EA

AUGUST, 1981

DATE

YA-CØ6LC-ØØ A (X006)

DOCUMENT NUMBER REVISION

N/A

创

**PROGRAM NUMBER**

YA-CØ6LB-ØØ

DRAWING SET NUMBER

DZS11-EA

**OPTION NUMBER**

3.1

NOTEBOOK SECTION

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | 1 |  |

|-------|--|--|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|--|

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |

|       |  |  |          | and the second se |       |   |  |

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |

|       |  |  |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |

| di ta |  |  | <b>.</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.1.1 |   |  |

Copyright 1981 by Digital Equipment Corporation.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in the document.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC    | VT           | IAS     |

|--------|--------------|---------|

| DECUS  | DECsystem-10 | MASSBUS |

| DECnet | DECsystem-20 | PDT     |

| PDP    | DECwriter    | RSTS    |

| UNIBUS | DIBOL        | RSX     |

| VAX    | EduSystem    | VMS     |

#### CONTENTS

Page

## CHAPTER 1 INTRODUCTION

| 1.1     | CODE                                                |  |

|---------|-----------------------------------------------------|--|

|         | SCOPE1-1<br>ENGINEERING DRAWINGS1-2                 |  |

| 1.2     |                                                     |  |

| 1.3     | DZ11 STATISTICAL MULTIPLEXER GENERAL DESCRIPTION1-3 |  |

| 1.3.1   | DZS11-EA General Description1-6                     |  |

| 1.3.2   | VT1XX-EA General Description                        |  |

| 1.3.3   | VT1XX-EB General Description1-6                     |  |

| 1.3.4   | VT1XX-EC General Description1-6                     |  |

| 1.4     | PHYSICAL DESCRIPTION1-9                             |  |

| 1.4.1   | DZS11-EA Physical Description1-9                    |  |

| 1.4.2   | VT1XX-EA Physical DEscription1-10                   |  |

| 1.4.3   | VT1XX-EB Physical Descriptionl-10                   |  |

| 1.4.4   | VT1XX-EC Physical Description1-10                   |  |

| 1.5     | SPECIFICATIONS1-15                                  |  |

| 1.5.1   | Electrical 1-15                                     |  |

| 1.5.2   | Environmental                                       |  |

| 1.5.3   | Physical1-16                                        |  |

| 1.5.4   | Operational                                         |  |

| 1.5.5   | Composite Port1-21                                  |  |

| 1.5.5.1 | Composite Port Interface1-21                        |  |

| 1.5.5.2 | Composite Port Interface Signals1-24                |  |

| 1.6     | DZ STAT MUX OPTIONS1-26                             |  |

| 1.7     | DZ STAT MUX CABLES1-27                              |  |

| 1.7.1   | DZS11-EA Cables1-27                                 |  |

| 1.7.2   | VT1XX-EA/EB Composite Port Cables1-27               |  |

| 1.7.3   | VT1XX-EA/EB Asynchronous Port Cables1-28            |  |

|         | 이 가슴 물건에 있는 것 같은 것 같  |  |

## CHAPTER 2 INSTALLATION

| 2.1     | SCOPE                             | 2-1 |

|---------|-----------------------------------|-----|

| 2.2     | UNPACKING AND INSPECTION          |     |

| 2.3     | INSTALLATION CONSIDERATIONS       | 2-1 |

| 2.4     | PRE INSTALLATION CONSIDERATIONS   | 2-2 |

| 2.4.1   | Device Placement                  | 2-2 |

| 2.4.2   | System Requirements               | 2-2 |

| 2.4.2.1 | UNIBUS Loading                    |     |

| 2.4.2.2 | Power Requirements                |     |

| 2.4.2.3 | Interrupt Priority                |     |

| 2.4.2.4 | Device Address Assignment         |     |

| 2.4.2.5 | Device Vector Address Assignment  | 2-4 |

| 2.4.3   | Composite Port Requirements       | 2-4 |

| 2.4.3.1 | Composite Port Cable Requirements |     |

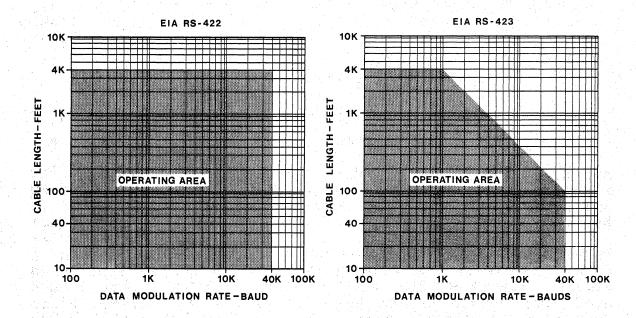

| 2.4.3.2 | EIA RS-232C and EIA RS-423        |     |

| 2.4.3.3 | EIA RS-423, RS-232C Slew Rates    |     |

| 2.4.3.4 | EIA RS-422 Long Line Driver       | 2-9 |

| 2.4.4   | Composite Port Clock Source       | -12 |

iii

| 2.4.5 | Composite Port Baud Rate2-12                |

|-------|---------------------------------------------|

| 2.4.6 | Microdiagnostic Controls                    |

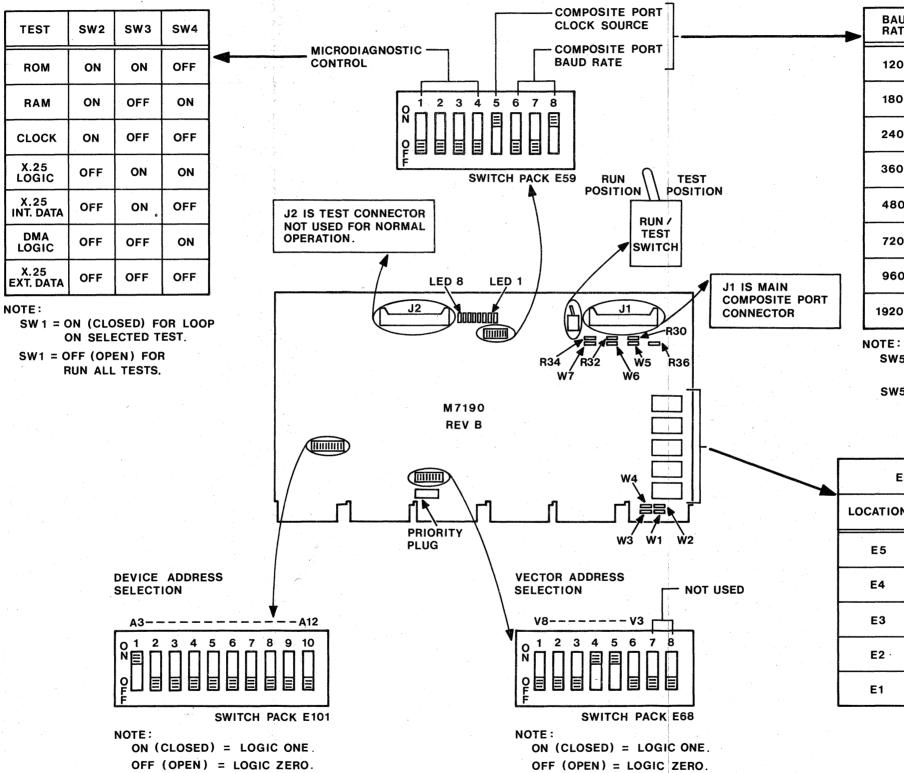

| 2.5   | M7190 CONFIGURATION                         |

| 2.5.1 | Check Factory Configured Components2-13     |

| 2.5.2 | Check Socketed Devices2-13                  |

| 2.5.3 | Set Device UNIBUS Address                   |

| 2.5.4 | Set Device Vector Address2-13               |

| 2.5.5 | Check Priority Plug2-13                     |

| 2.5.6 | Check Composite Port Signal Conditioning    |

|       | Components                                  |

| 2.5.7 | Set Composite Port Baud Rate                |

| 2.5.8 | Set RUN/TEST Switch2-14                     |

| 2.6   | DZS11-EA MODULE INSTALLATION                |

| 2.6.1 | Backplane Considerations2-19                |

| 2.6.2 | M719Ø Insertion2-19                         |

| 2.7   | DZS11-EA M719Ø TEST2-2Ø                     |

| 2.7.1 | Initialise DZS11-EA2-20                     |

| 2.7.2 | Run the On Board Microdiagnostic            |

| 2.7.3 | Load and Run the UNIBUS Diagnostic2-20      |

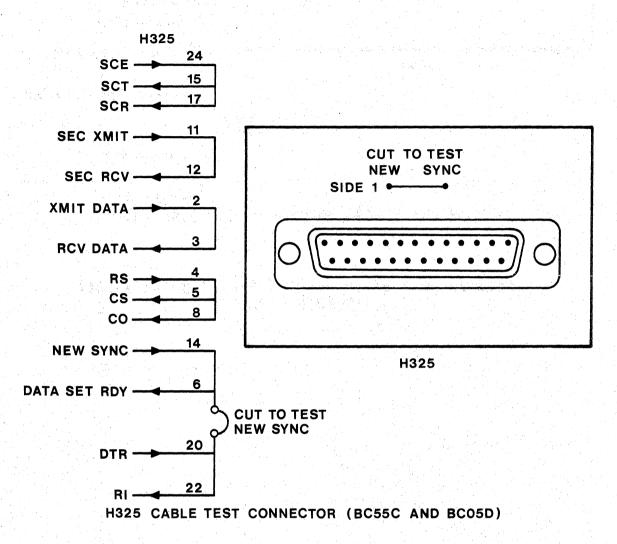

| 2.7.4 | Test the BCØ5C-25 Cable2-21                 |

| 2.8   | VT1XX-EA/VT1XX-EB INSTALLATION2-24          |

| 2.9   | DZ STAT MUX NETWORK TESTING2-25             |

| 2.9.1 | Set DZS11-EA into Run Mode2-25              |

| 2.9.2 | Connect DZS11-EA to DZ STAT MUX Network2-25 |

| 2.9.3 | Test DZ STAT MUX Composite Link             |

| 2.10  | CUSTOMER ACCEPTANCE                         |

# CHAPTER 3 PROGRAMMING AND OPERATION

| 3.1     | INTRODUCTION                           |

|---------|----------------------------------------|

| 3.2     | DZS11-EA CONTROLS AND INDICATORS       |

| 3.2.1   | DZS11-EA Manual Controls               |

| 3.2.1.1 | RUN/TEST Switch                        |

| 3.2.2   | DZS11-EA LED Indicators                |

| 3.2.2.1 | Run Mode LED Status                    |

| 3.2.2.2 | Test Mode LED Status                   |

| 3.2.3   | DZS11-EA Initialisation (Device Reset) |

| 3.3     | REGISTER BIT ASSIGNMENTS               |

| 3.3.1   | Control and Status Register (CSR)      |

| 3.3.2   | Receive Buffer (RBUF)                  |

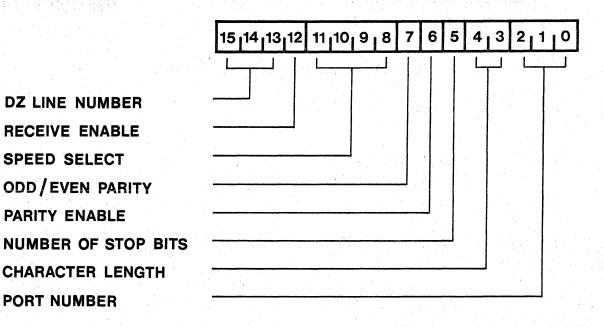

| 3.3.3   | Line Parameter Register (LPR)          |

| 3.3.4   | Transmit Control Register (TCR)        |

| 3.3.5   | Modem Status Register (MSR)            |

| 3.3.6   | Transmit Data Register (TDR)           |

| 3.4     | PROGRAMMING FEATURES                   |

| 3.4.1   | Baud Rate                              |

| 3.4.2   | Character Length                       |

| 3.4.3   | Stop Bits                              |

| 3.4.4   | Parity                                 |

| 3.4.5   | Interrupts                             |

|         |                                        |

ati.

| 3.4.6   | Emptying the Silo                                     |

|---------|-------------------------------------------------------|

| 3.4.7   | Transmitting a Character                              |

| 3.5     | PROGRAMMING EXAMPLES                                  |

| 3.6     | NETWORK DESCRIPTION                                   |

| 3.7     | NETWORK INITIALISATION                                |

| 3.7.1   | DZS11-EA Role in Network Initialisation               |

| 3.7.2   | Reset Message                                         |

| 3.7.3   | The RIM Message                                       |

| 3.7.4   | The SIM Message                                       |

| 3.8     | SYNCHRONISATION                                       |

| 3.8.1   | General                                               |

| 3.8.2   | Data Flow from Host Computer to Terminals             |

| 3.8.2.1 | Synchronisation Using DTR Signal from Terminals3-37   |

| 3.8.2.2 | Synchronisation Using XON/XOFF                        |

| 3.8.2.3 | Control Mechanism to Prevent Buffer Overflow3-38      |

| 3.8.3   | Data Flow from Terminals to Host Computer             |

| 3.8.3.1 | XON/XOFF from Host Computer                           |

| 3.8.3.2 | XON/XOFF from VT1XX-EA/EB                             |

| 3.9     | NETWORK RECONFIGURATION FOR OPTIMUM RESPONSE AND      |

|         | THROUGHPUT                                            |

| 3.10    | NETWORK ERROR DETECTION AND RECOVERY                  |

| 3.11    | NETWORK STATUS AND STATISTICS DISPLAY                 |

| 3.11.1  | DZS11-EA Status Display                               |

| 3.11.2  | VT1XX-EA/EB Status Display                            |

| 3.12    | ASYNCHRONOUS DATA LOCAL ECHO                          |

| 3.12.1  | Setting the VT1XX-EA/EB for Local Echo Operation.3-44 |

| 3.12.2  | Programming Considerations for Local Echo             |

|         | Operation                                             |

| 3.12.3  | Local Echo in RSTS/E                                  |

| 3.12.4  | Local Echo in RSX11/M and VMS                         |

## CHAPTER 4 DETAILED DESCRIPTION

| 4.1     | SCOPE                            | 4-1 |

|---------|----------------------------------|-----|

| 4.2     | ENGINEERING DRAWINGS             | 4-1 |

| 4.3     | GENERAL DESCRIPTION              | 4-2 |

| 4.4     | FUNCTIONAL BLOCK DESCRIPTION     | 4-2 |

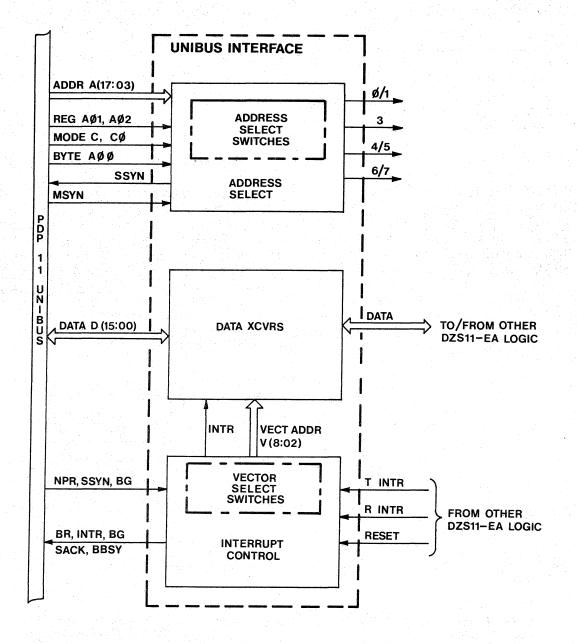

| 4.4.1   | UNIBUS Interface                 |     |

| 4.4.1.1 | Address Selection                |     |

| 4.4.1.2 | Interrupt Control                | 4-3 |

| 4.4.1.3 | Data Transceivers                |     |

| 4.4.2   | UNIBUS Microcontroller Interface |     |

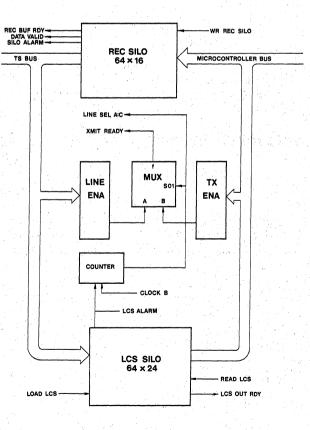

| 4.4.2.1 | Received Data Silo               |     |

| 4.4.2.2 | Transmit Control Logic           |     |

| 4.4.2.3 | Line Control and Status Silo     |     |

| 4.4.2.4 | UNIBUS Registers                 |     |

1

| 4.4.3    | Microcontroller4-8                                                                         |

|----------|--------------------------------------------------------------------------------------------|

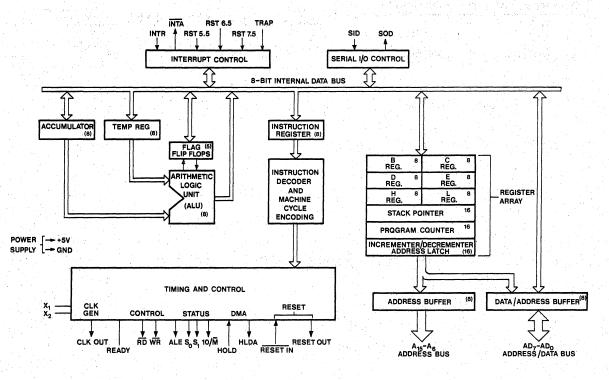

| 4.4.3.1  | Microprocessor                                                                             |

| 4.4.3.2  | Programe PROM                                                                              |

| 4.4.3.3  | Scratch RAM4-9                                                                             |

| 4.4.3.4  | Programmable Clock                                                                         |

| 4.4.3.5  | UNIBUS Interface                                                                           |

| 4.4.3.6  | Composite Port Controller                                                                  |

| 4.5      | UNIBUS INTERFACE DETAILED DESCRIPTION4-13                                                  |

| 4.5.1    | Address Selection Logic                                                                    |

| 4.5.2    | Receiver Interrupt Control                                                                 |

| 4.5.3    | Transmitter Interrupt Control                                                              |

| 4.5.4    | Data Transceivers4-14                                                                      |

| 4.5.5    | Receiver Control Logic                                                                     |

| 4.5.6    | Transmit Control Logic                                                                     |

| 4.5.7    | UNIBUS Registers4-16                                                                       |

| 4.5.7.1  | UNIBUS Control and Status Register                                                         |

| 4.5.7.2  | UNIBUS Receiver Buffer4-17                                                                 |

| 4.5.7.3  | UNIBUS Line Parameter Register                                                             |

| 4.5.7.4  | UNIBUS Transmit Control Register                                                           |

| 4.5.7.5  | UNIBUS Modem Status Register4-19                                                           |

| 4.5.7.6  | UNIBUS Transmit Data Register                                                              |

| 4.6      | MICROCONTROLLER DETAILED DESCRIPTION                                                       |

| 4.6.1    | 8085 Microprocessor                                                                        |

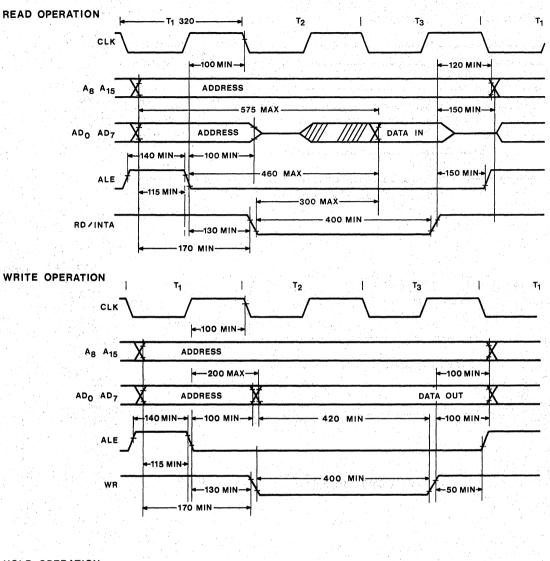

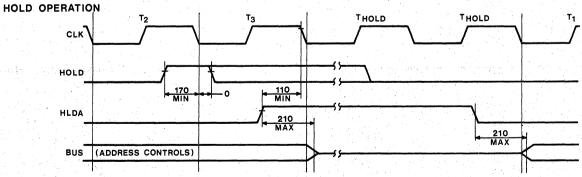

| 4.6.2    | Bus Timing                                                                                 |

| 4.6.3    | Microprocessor Memory4-28                                                                  |

| 4.6.3.1  | Memory Decoding                                                                            |

| 4.6.4    | Microprocessor Memory I/O Map4-28                                                          |

| 4.6.5    | I/O Decoding                                                                               |

| 4.6.6    | Interrupt Vectors4-30                                                                      |

| 4.6.7    | Microcontroller Clock                                                                      |

| 4.6.7.1  | Clock Operational Description4-32                                                          |

| 4.7      | COMPOSITE PORT COMMUNICATION CONTROLLER4-35                                                |

| 4.7.1    | DMA Controller4-35                                                                         |

| 4.7.1.1  | DMA Operation4-38                                                                          |

| 4.7.1.2  | IDLE Cycle                                                                                 |

| 4.7.1.3  | ACTIVE Cycle                                                                               |

| 4.7.1.4  | Address Generation                                                                         |

| 4.7.1.5  | Current Address Register4-40                                                               |

| 4.7.1.6  | Current Word Register4-40                                                                  |

| 4.7.1.7  | Base Address and Base Word Count Registers4-41                                             |

| 4.7.1.8  | Command Register4-41                                                                       |

| 4.7.1.9  | Mode Register4-41                                                                          |

| 4.7.1.10 | Request Register4-41                                                                       |

| 4.7.1.11 |                                                                                            |

| 4.7.1.12 | Status Register                                                                            |

| 4.7.1.13 |                                                                                            |

| 4.7.1.14 | 人名英格兰姓氏 网络拉拉斯拉拉 法法律的 化合物 化合物 化合物 化合物 法法律的 法法律的 化合物 化合物 化合物 化合物 化合物 化合物 化合物 化合物 化分析 化合物 化合物 |

| 4.7.2    | HDLC Controller                                                                            |

| 4.7.2.1  | CPU Interface                                                                              |

| 4.7.2.2  | Register Description4-50                                                                   |

ø

0

| 4.7.2.3 | DMA Transfers                                                                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------|

| 4.7.2.4 | Serial Data Logic4-51                                                                                                              |

| 4.7.2.5 | Principals of Operation4-52                                                                                                        |

| 4.8     | UNIBUS MICROCONTROLLER INTERFACE                                                                                                   |

|         | 사업 수업에서 가지 전자에 대해 주 것이 있는 것이 있는 것이 있는 것이 같다. 것이 같은 것이 같은 것이 같다. 것이 같은 것이 같은 것이 같이 않는 것이 같이 많이 많이 없다. |

| 4.8.2   | Transmit Enable Register                                                                                                           |

| 4.8.3   | Receiver Buffer4-60                                                                                                                |

| 4.8.4   | UNIBUS Status Register (USR)                                                                                                       |

| 4.8.5   | Switch Register                                                                                                                    |

| 4.8.6   | LED Display Register4-64                                                                                                           |

| 4.8.7   | Modem Status Register (MSR)4-66                                                                                                    |

CHAPTER 5 MAINTENANCE

| 5.1   | SCOPE                                           |

|-------|-------------------------------------------------|

| 5.2   | MAINTENANCE PHILOSOPHY                          |

| 5.3   | PREVENTATIVE MAINTENANCE                        |

| 5.4   | TEST EQUIPMENT REQUIRED                         |

|       | ON BOARD MAINTENANCE FEATURES                   |

|       | CORRECTIVE MAINTENANCE ON A PDP/11 PROCESSOR5-3 |

| 5.6.1 | Loading PDP/11 Diagnostic DZDZA                 |

|       | Starting PDP/11 Diagnostic DZDZA                |

| 5.7   | CORRECTIVE MAINTENANCE ON A VAX PROCESSOR       |

APPENDIX A DZS11-EA SHIPPING LIST

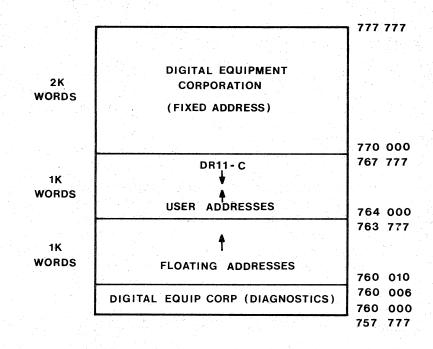

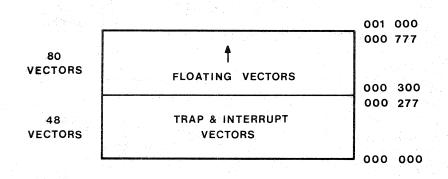

APPENDIX B FLOATING DEVICE ADDRESSES AND VECTORS

| B.1 | FLOATING | DEVICE  | ADDRESS | SES    |         |          | B-1     |

|-----|----------|---------|---------|--------|---------|----------|---------|

| B.2 | FLOATING | VECTOR  | ADDRESS | SES    |         |          | B-3     |

| B.3 | EXAMPLES | OF DEVI | ICE AND | VECTOR | ADDRESS | ASSIGNME | NTS.B-5 |

## APPENDIX C DZS11-EA MICRODIAGNOSTIC

| C.1   | INTRODUCTIONC-1             |

|-------|-----------------------------|

| C.1.1 | GO/NOGO TestC-1             |

| C.1.2 | OFF LINE MicrodiagnosticC-2 |

| C.1.3 | UNIBUS MicrodiagnosticC-2   |

|       | REQUIREMENTS                |

| C.2.1 | Equipment                   |

| C.2.2 | Storage                     |

vii

| C.2.3   | Microdiagnostic Status DisplayC-3    |

|---------|--------------------------------------|

| C.3     | STARTING PROCEDUREC-6                |

| C.3.1   | Starting GO/NOGO TestC-6             |

| C.3.2   | Starting OFF LINE MicrodiagnosticC-6 |

| C.3.3   | Starting UNIBUS Microdiagnostic      |

| C.3.4   | DZS11-EA Control Switch Settings     |

| C.4     | OPERATING PROCEDURES                 |

| C.4.1   | GO/NOGO TestC-8                      |

| C.4.2   | OFF LINE DiagnosticC-8               |

| C.4.3   | UNIBUS Microdiagnostic               |

| C.5     | MICRODIAGNOSTIC ERRORS               |

| C.5.1   | GO/NOGO Errors                       |

| C.5.2   | OFF LINE Microdiagnostic ErrorsC-10  |

| C.6     | MISCELLANEOUS                        |

| C.6.1   | Execution Times                      |

| C.7     | TEST DESCRIPTION                     |

| C.7.1   | General                              |

| C.7.2   | GO/NOGO Test                         |

| C.7.3   | OFF LINE Diagnostic                  |

| C.7.3.1 | Test 1                               |

| C.7.3.2 | Test 2                               |

| C.7.3.3 | Test 3                               |

| C.7.3.4 | Test 4                               |

| C.7.3.5 | Test 5                               |

| C.7.3.6 | Test 6                               |

| C.7.3.7 |                                      |

|         | Test 7C-18                           |

| C.7.4   | DZS11-EA UNIBUS DiagnosticC-18       |

## APPENDIX D DZ STAT MUX PROTOCOL

| D.1     | GENERAL                                          |

|---------|--------------------------------------------------|

| D.1.1   | Functions of the ProtocolD-1                     |

| D.1.2   | TerminologyD-1                                   |

| D.1.2.1 | Use of X.25 TerminologyD-1                       |

| D.1.2.2 | Route-through TerminologyD-1                     |

| D.2     | MAIN CHARACTERISTICS OF THE PROTOCOLD-2          |

| D.2.1   | Multiplexed Link ProtocolD-2                     |

| D.2.2   | Communication ModeD-2                            |

| D.2.3   | Route-Through Addressing AlgorithmD-2            |

| D.3     | ELEMENTS OF PROTOCOLD-4                          |

| D.4     | LINK SETUP AND INITIALISATIOND-4                 |

| D.4.1   | RIM (Request Initialisation Mode) FrameD-4       |

| D.4.1.1 | RIM Information Field FormatD-5                  |

| D.4.1.2 | Expected Response from Local MuxD-5              |

| D.4.2   | SIM (Set Initialisation Mode) FrameD-6           |

| D.4.2.1 | SIM Information Field FormatD-7                  |

| D.4.3   | RSET (RESET) FrameD-9                            |

| D.4.4   | LPBK (Loopback) FrameD-9                         |

| D.5     | INFORMATION TRANSFER, LINK SUPERVISORY AND ERROR |

|         | CONTROL FUNCTIONSD-9                             |

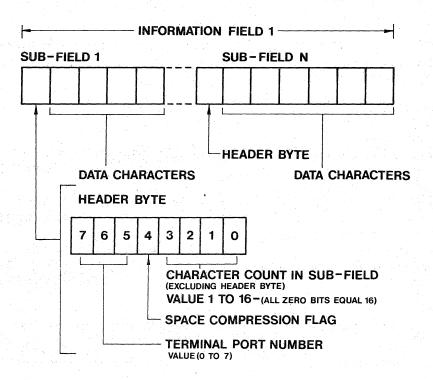

| D.5.1 | I Frame Information Field Terminal Port Encoding<br>SchemeD-10 |

|-------|----------------------------------------------------------------|

| D.6   | TRANSFER OF DZ SPECIFIC INFORMATIOND-11                        |

| D.6.1 | Line ParametersD-11                                            |

| D.6.2 | BreakD-12                                                      |

| D.6.3 | Transmit DisableD-12                                           |

| D.6.4 | Transmit EnableD-12                                            |

| D.6.5 | Route-through DisableD-12                                      |

| D.6.6 | Route-through EnableD-13                                       |

| D.6.7 | DTR, CAR, RING                                                 |

a

## ILLUSTRATIONS

| Figure No: <u>Title</u>                                    |                                         | Page     |

|------------------------------------------------------------|-----------------------------------------|----------|

| 1.1 Typical DZ STAT MUX Net<br>1.2 Typical PDP/11 Applicat |                                         |          |

| 1.3 Typical VAX-11/780 Appl                                |                                         |          |

| 1.4 $DZS11-EA Option (M7190)$                              |                                         |          |

| 1.5 VT1XX-EA Module Set                                    |                                         |          |

| 1.6 VT100 Rear View with VT                                | 1XX-EA/EB Installed                     | 1-12     |

| 1.7 VT1XX-EB Module Set                                    |                                         |          |

| 1.8 VT1XX-EC Option                                        |                                         |          |

| 1.9 BCØ5C-25 RS-232C Cable.                                |                                         |          |

| 1.10 BC05Z-25 Long Line Driv                               |                                         |          |

| 1.12 VT1XX-EA/EB Asynchronou                               | s Port Cables                           | 1-28     |

| 2.1 DZS11-EA Component and<br>Summary                      | Jumper Configuration                    |          |

| 2.2 Baud Rate vs Cable Leng                                |                                         |          |

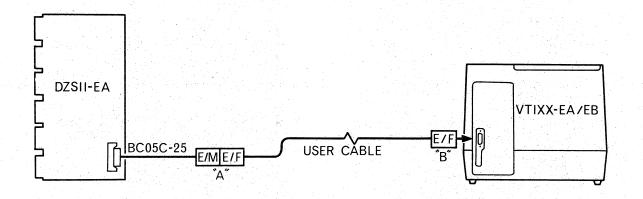

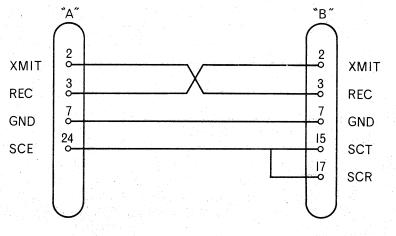

| 2.3 DZ STAT MUX EIA RS-423                                 | Direct Cable Connectio                  | n2-6     |

| 2.4 DZ STAT MUX EIA RS-232C                                |                                         |          |

| 2.5 DZS11-EA Long Line Driv                                |                                         | ····2-1Ø |

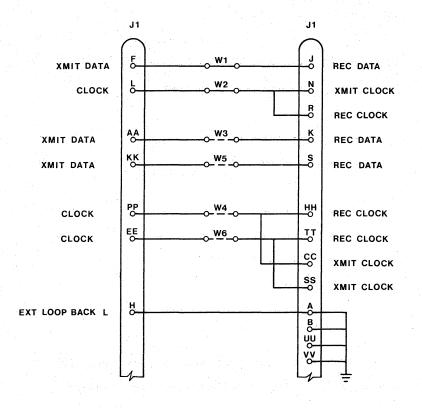

| 2.6 DZS11-EA Turnaround Tes<br>(Sheet 1 of 3)              | • • • • • • • • • • • • • • • • • • • • | 2-28     |

| 2.6 DZS11-EA Turnaround Tes<br>(Sheet 2 of 3)              | t Connectors                            | 2-29     |

| 2.6 DZS11-EA Turnaround Tes<br>(Sheet 3 of 3)              | t Connectors                            |          |

|                                                            |                                         | ••••2 50 |

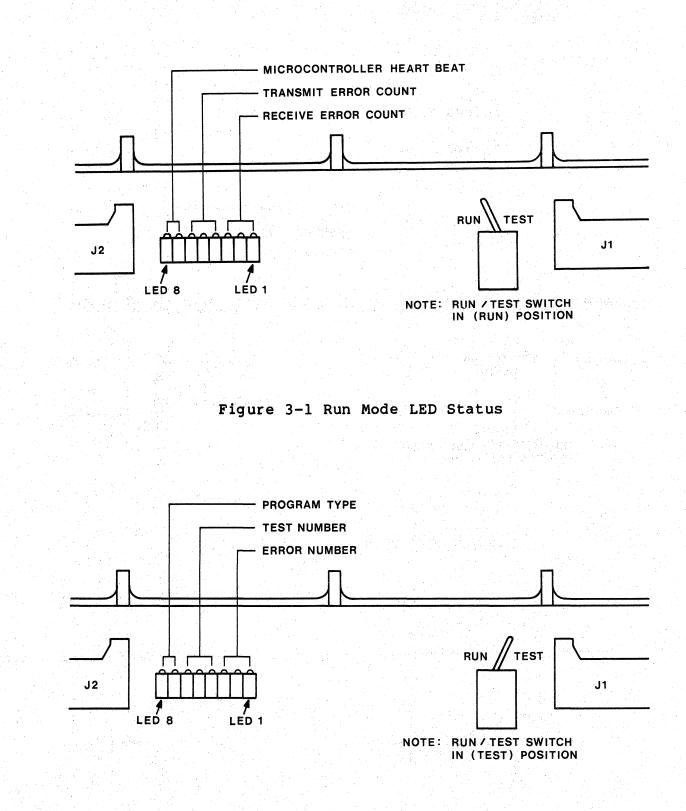

| 3.1 RUN Mode LED Status                                    |                                         | 3-5      |

| 3.2 TEST Mode LED Status                                   |                                         |          |

| 3.3 DZS11-EA Register Bit A                                |                                         |          |

| 3.4 VT1XX-EA/EB Network Sta                                | tistics Display                         | 3-43     |

| 3.5 VT100 Setup B Display                                  | • • • • • • • • • • • • • • • • • • • • | ••••3-45 |

| 4.1 UNIBUS Interface Block                                 | Diagram                                 |          |

| 4.2 UNIBUS Microcontroller                                 |                                         |          |

| 4.3 Microprocessor Block Di                                |                                         |          |

| 4.4 8085 Block Diagram                                     |                                         |          |

| 4.5 8085 Bus Timing                                        |                                         |          |

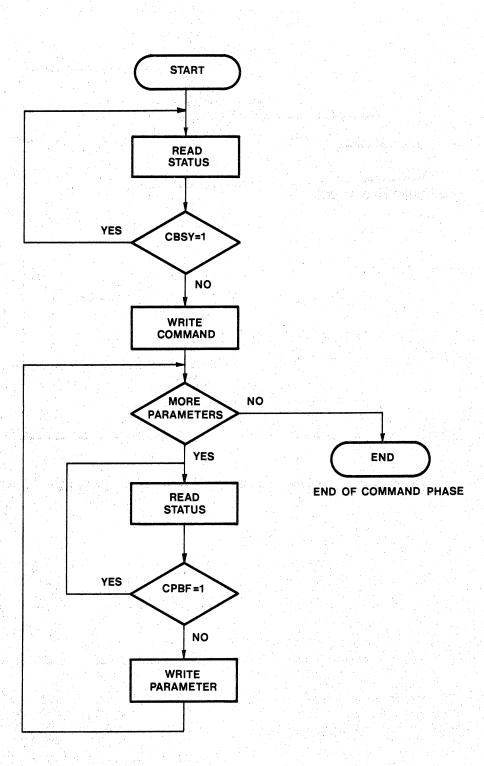

| 4.6 8273 Command Phase Flow                                | Chart                                   | 4-53     |

| B.1 UNIBUS Address Map                                     | • • • • • • • • • • • • • • • • • • • • | ••••B-2  |

| C.1 Microdiagnostic Flag Ch                                |                                         |          |

| C.2 UNIBUS Microdiagnostic                                 | State Diagram                           | ••••C-19 |

| D.1 RIM Message Format                                     |                                         | ••••D-5  |

| D.2 SIM Message Format                                     |                                         |          |

| D.3 Terminal Port Encoding                                 |                                         |          |

|                                                            |                                         |          |

2

| -          | - | - | - | -  | $\sim$   |  |  |

|------------|---|---|---|----|----------|--|--|

| Т          | Δ | ы |   | н. | 5        |  |  |

| - <b>L</b> | - | ~ | _ | -  | <b>u</b> |  |  |

|            |   |   |   |    |          |  |  |

| <u>Table No:</u>                                                                                                                                                                                                                                                                                                                                                                                               | <u>Title</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2DZ STAT MUX Multipl1.3Asynchronous Ports1.4DZS11-EA Composite                                                                                                                                                                                                                                                                                                                                               | erational Specifications<br>exing Specification<br>Specifications<br>Port Connector Pinning<br>Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-18<br>1-19<br>1-22                                                                                                                                                        |

| <ul> <li>2.2 EIA RS-423 AND RS-2<br/>Values</li></ul>                                                                                                                                                                                                                                                                                                                                                          | hart<br>232C Wave Shaping Resistor<br>ation Summary<br>ection (E1Ø1)<br>ction (E68)<br>tch Pack (E59)<br>ameter Switch Pack (E59)                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-8<br>2-15<br>2-17<br>2-18<br>2-22                                                                                                                                         |

| <ul> <li>3.2 LED Dispaly Status</li> <li>3.3 CSR Bit Functions.</li> <li>3.4 RBUF Bit Functions.</li> <li>3.5 LPR Bit Functions.</li> </ul>                                                                                                                                                                                                                                                                    | (Run Mode)<br>(Test Mode)<br>h Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-4<br>3-9<br>3-12<br>3-14                                                                                                                                                  |

| 4.28085A Machine Cycle4.3Microcontroller Add4.4Microcontroller Ved4.5Clock A and B Frequ4.68253 Control Word I4.78237 Internal Regis4.88327 Command Register4.98237 Mode Register4.108237 Request Register4.118237 Status Register4.128237 Software Commat4.138237 Software Commat4.14Rx Interrupt Result4.15Tx Interrupt Result4.16LCS 3 Bit Definitions4.18Switch Register Definitions4.19LED Display Format | ons.<br>Chart.<br>Iress Assignments<br>Stor Addresses<br>Tormat<br>Format<br>Sters<br>Sters<br>Bit Definitions<br>Bit Definition<br>Bit Definition | $\begin{array}{c} 4-26 \\ 4-29 \\ 4-30 \\ 4-32 \\ 4-33 \\ 4-35 \\ 4-43 \\ 4-44 \\ 4-44 \\ 4-45 \\ 4-45 \\ 4-45 \\ 4-56 \\ 4-56 \\ 4-59 \\ 4-61 \\ 4-63 \\ 4-64 \end{array}$ |

| 5.1 Test Equipment Requ                                                                                                                                                                                                                                                                                                                                                                                        | uired                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-2                                                                                                                                                                         |

xi

| A.1                      | DZS11-EA Shipping ListA-1                                 |

|--------------------------|-----------------------------------------------------------|

| C.1<br>C.2<br>C.3<br>C.4 | LED Display Format                                        |

| D.1<br>D.2               | Commands and ResponsesD-3<br>SIM Frame Bit DefinitionsD-8 |

Ř.

ø

#### PREFACE

This manual describes in detail the installation requirements, programming and operational considerations, and maintenance procedures including diagnostic support, for the DZS11-EA Statistical Multiplexer (M7190). A variety of appendices are provided to supplement the above.

Complete understanding of the documents contents requires that the reader have a general knowledge of statistical multiplexing techniques, digital circuitry and a basic understanding of PDP-11 computers.

Other publications which support this document are:-

- DZS11-EA Print Set

- VT1XX-EA/EB Technical Manual

- PDP-11 Processor Handbook

- PDP-11 Peripherals Handbook

- PDP-11 Paper Tape Software Handbook

- Appropriate System User's Manual

### CHAPTER 1

1-1

#### INTRODUCTION

### 1.1 SCOPE

Sections 1.1 through 1.3 of this chapter contains an introduction to the DZ Statistical Multiplexer network; including DZS11-EA, VT1XX-EA, VT1XX-EB, and VT1XX-EC. Section 1.4 of this chapter contains DZS11-EA specifications.

#### **1.2 ENGINEERING DRAWINGS**

A complete set of engineering drawings and circuit schematics is provided in a companion volume to this manual entitled DZS11-EA Field Maintenance Print Set. The general logic symbols used on these drawings are described in the DIGITAL Logic Handbook. Specific symbols and conventions are also included in certain PDP-11 systems manuals. The following paragraphs describe the signal nomenclature convention used on the drawing set.

Signal names in the DZS11-EA print set are given in the following basic form:

#### SOURCE SIGNAL NAME POLARITY

SOURCE indicates the drawing number of the print set where the signal originates. The drawing number of a print is located in the lower right corner of the print title block (S1, S2, S3 etc). SIGNAL NAME is the proper name of the signal. The names used in the print set are also used in this manual. POLARITY is either H or L to indicate the voltage level of the signal. H means +3 V; L means ground. As an example, the signal:

(S2) SELECT L

originates on sheet 2 of the M7190 module drawing and is read, when SELECT is true, this signal is at ground. UNIBUS signal lines do not carry a SOURCE indicator. These signal names represent a bidirectional wire-ORed bus; as a result, multiple sources for a particular bus signal exist. Each UNIBUS signal name is prefixed with the word BUS.

#### 1.3 DZ11 STATISTICAL MULTIPLEXER GENERAL DESCRIPTION

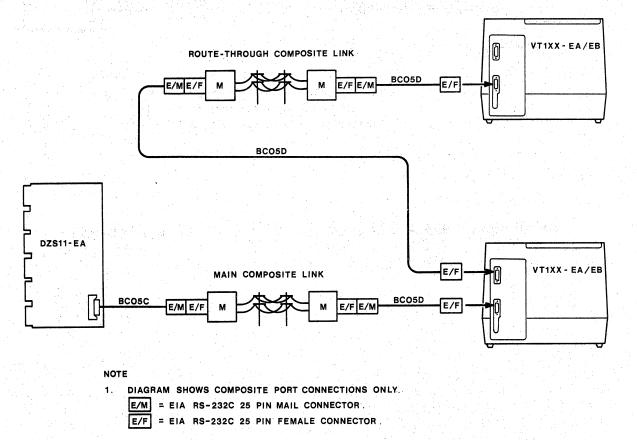

The DZ Statistical Multiplexer (DZ STAT MUX) is a term used to describe a statistical multiplexer network consisting of one DZS11-EA as described by this manual and any combination of one or two VT1XX-EA or VT1XX-EB remote statistical multiplexers enabling a max of 8 remotely located asynchronous terminals to share a common composite communications link.

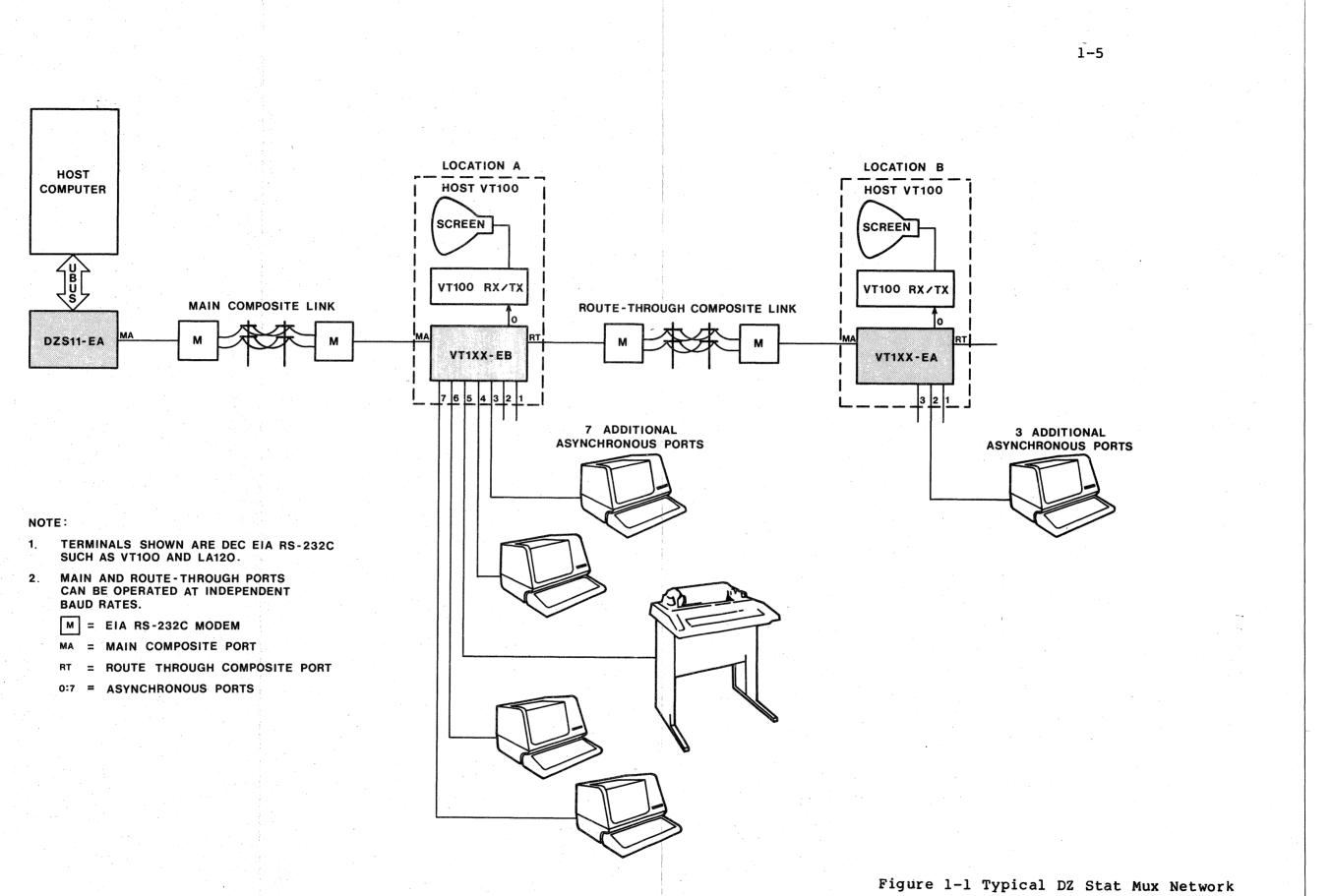

Figure 1-1 shows a typical DZ STAT MUX network consisting of eight asynchronous terminals connected to a computer system via a serial composite communication link.

The network consists of a DZS11-EA statistical multiplexer mounted in the computer system, a VT1XX-EB eight channel statistical multiplexer at location "A" and a VT1XX-EA four channel statistical multiplexer at location "B".

The DZS11-EA and VT1XX-EB are interconnected by the Main composite link, the VT1XX-EB and VT1XX-EA are interconnected by the Route-Through composite link. Both VT1XX-EA and VT1XX-EB options have route through ports and can therefore be interchanged in Figure 1.1.

Both composite links conform to the X.25 level 2 communication protocol, thereby offering a high degree of data integrity through automatic re-transmission upon detection of transmission errors.

Integral long line drive devices on all components of the network enable direct interconnection of the composite links with cable lengths in excess of one km., where modem connections are not required. This feature uses RS-422 full differential transceivers and is selectable at installation time by means of quick connect straps.

Both VT1XX-EA and VT1XX-EB mount within a standard VT100 enclosure, and so when installed, the first asynchronous terminal and statistical multiplexer become an integral unit. Any combination of the maximum eight asynchronous terminals, can be located across locations "A" and "B", e.g six may be connected at location A and two may be connected at location The host VT100 housing the VT1XX-EA/EB option need not be Β. of one these terminals. Asynchronous ports are enabled/disabled at installation.

Features of the DZ11 Statistical Multiplexer include:-

- Integral DZ11-A asynchronous communications multiplexer and statistical multiplexer on one hex module

- DZ11-A, DZ11-C asynchronous multiplexer software compatibility.

- Integral VT1ØØ and VT1XX-EA/EB statistical multiplexer at terminal location

- Connection of up to 8 asynchronous terminals (including host VT100s) located at one or two remote locations via one composite communication link and route through composite link in the case where two VT1XX-EA/EBs are used.

- High communication efficiency of the composite link through dynamic bandwidth allocation.

- Data integrity between asynchronous terminal port and computer, through composite port high level protocol which handles message sequencing and error correction by automatic re-transmissions.

- Comprehensive micro diagnostic tools for network and option diagnosis.

- Echoplex or local echo operation for asynchronous ports.

- Ability to format asynchronous ports through system software SET commands.

#### 1.3.1 DZS11-EA General Description

The DZS11-EA is a single module containing DZ11-A asynchronous multiplexer emulator and statistical multiplexer. The option is program compatible to the DZ11-A and therefore interfaces to the operating system via standard device drivers. To the operating system, a DZ STAT MUX network consisting of DZS11-EA, and one or two VT1XX-EA/EB stat muxes appears as eight asynchronous terminals connected via a standard DZ11-A multiplexer.

#### 1.3.2 VT1XX-EA General Description

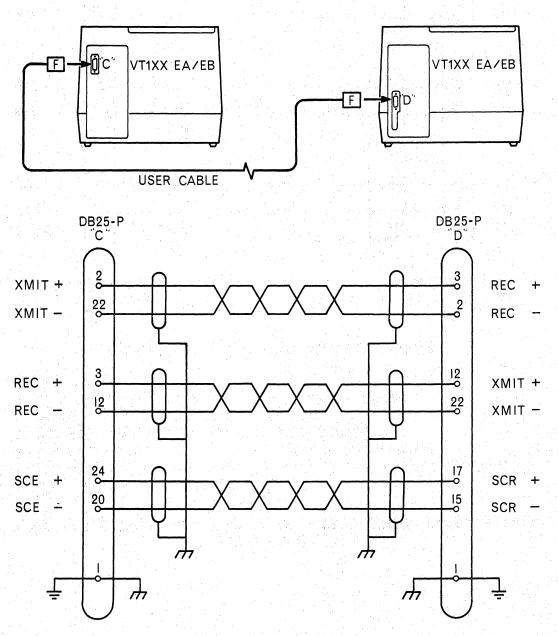

The VT1XX-EA statistical multiplexer is a component of the DZ STAT MUX network. The option is a four channel stat mux enabling four asynchronous terminals to be statistically multiplexed to a DZS11-EA via the composite communication link. The VT1XX-EA has two composite communication ports, the Main and the Route-through.

The Main composite communication port interfaces to a primary device, (a DZS11-EA or another VT1XX-EA/EB when the VT1XX-EA is the second cluster controller) via the Main composite link while the Route-through port interfaces to the secondary device in the case where Route-through is implemented. Both composite ports operate independently at baud rates from 1200 to 19200 bits/second from an internal or external timing source.

Asynchronous port parameters are down line loaded via the DZS11-EA at network initialization time or following operating system SET commands. This feature enables asynchronous ports to be re-formatted at the terminal keyboard by issuing the appropriate operating system SET command.

#### 1.3.3 VT1XX-EB General Description

The VT1XX-EB statistical multiplexer is a component of the DZ STAT MUX network and is shown in Figure 1.1 at location "A". The option is identical in operation to the VT1XX-EA with the exception of an additional four asynchronous ports, thus enabling a maximum of up to eight asynchronous terminals to be statistically multiplexed to a DZS11-EA.

#### 1.3.4 VT1XX-EC General Description

The VT1XX-EC is an option for the VT1XX-EA four channel statistical multiplexer. The option is field installable, and modifies a VT1XX-EA (4 channel stat. mux) to a VT1XX-EB (8 channel stat. mux).

#### . 11. – Alexandro Alexandro and Alexandro and Alexandro and Alexandro and Alexandro and Alexandro and Alexandro a

가 있는 것을 하는 것을 가지 않는 것 이 같은 것을 하는 것을 가지 않는 것을 하는 것을 가지 않는 것을 가지 않는 것을 가지 않는 것을 하는 것을 하는 것을 하는 것을 가 이 같은 것을 하는 것을 수 있다. 것을 하는 것을 것을 하는 것을 것을 것을 수 있다. 것을 것을 것을 것을 수 하는 것을 하는 것을 하는 것을 하는 것을 하는 것을 하는 것을 수 있다. 것을 것을 하는 것을 것을 것을 수 있다. 것을 것을 것을 수 있다. 것을 것

0

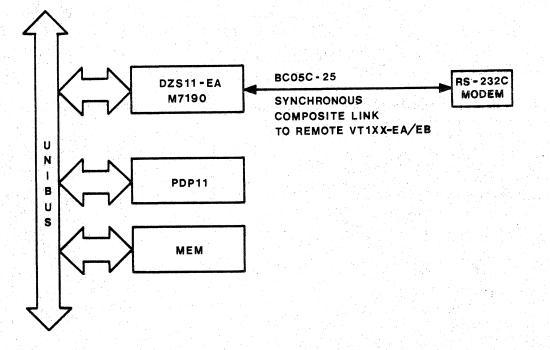

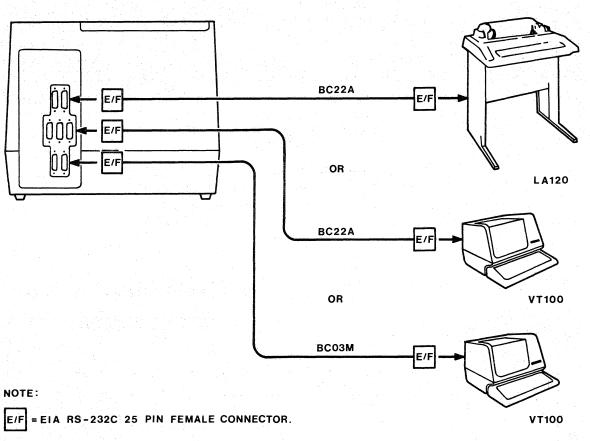

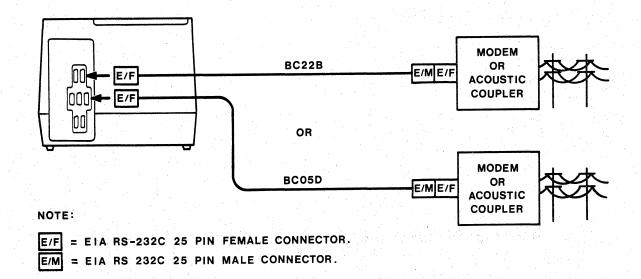

Figure 1-2 Typical PDP11 Application

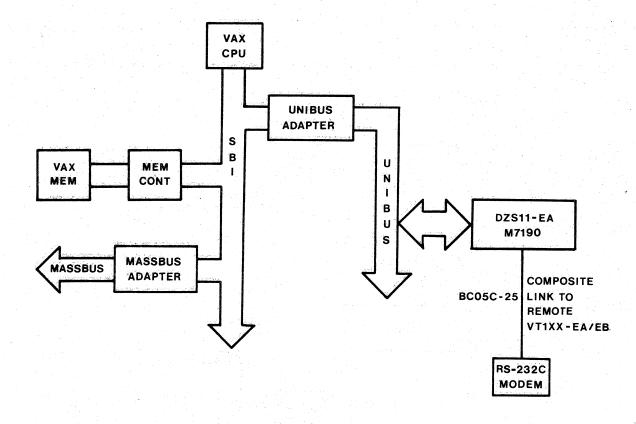

# Figure 1-3 Typical VAX-11/780 Application

Ċ

畿

\$x

ĸ

#### 1.4 PHYSICAL DESCRIPTION

#### 1.4.1 DZS11-EA Physical Description

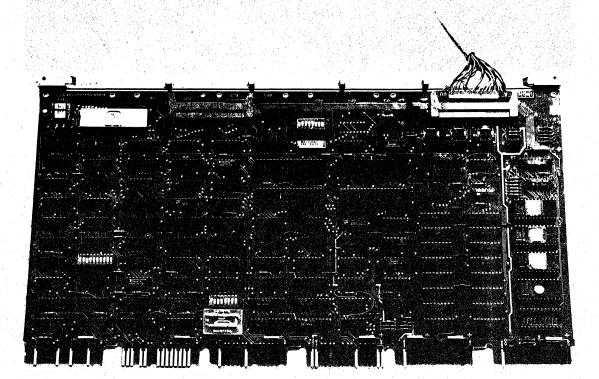

The DZS11-EA consists of one hex size printed circuit board and composite port interconnect cable as shown in Figure 1-4. The option replaces the functionality of a DZ11-A, distribution panel, eight interconnect cables and the traditional stand alone statistical multiplexer.

The option interfaces to the UNIBUS via a standard small peripheral controller slot (SPC), and to the DZ STAT MUX network via a standard RS-232C interrconnect cable (BCØ5C-25).

An on board 8 bit microcontroller performs the DZ11-A emulation and statistical multiplexing functions. Microdiagnostics can be evoked by maintenance personnel, enabling diagnosis of both the DZS11-EA option and DZ STAT MUX network.

Figure 1-4 DZS11-EA Option (M7190)

#### VT1XX-EA Physical Description 1.4.2

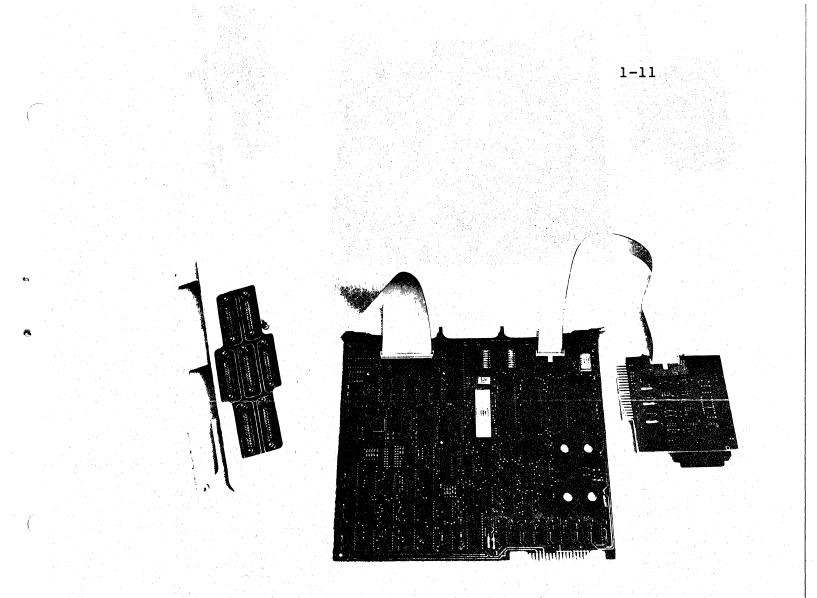

The VT1XX-EA four channel statistical multiplexer is a printed circuit board set, plus mounting hardware, specifically designed to mount into a VT100 mounting When installed, the VT1XX-EA and host VT100 enclosure. integral option, with the host VT100's become an communication port connected to the first asynchronous port (port  $\emptyset$ ) of the VT1XX-EA.

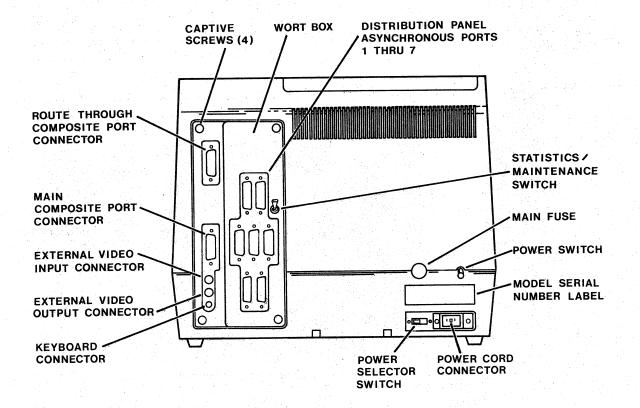

Figure 1-5 shows the components of the VT1XX-EA. Figure 1-6 shows a rear view of the host VT100 following installation of the VT1XX-EA. Note, that the VT100's communications port has become the Main composite port for the VT1XX-EA with the Route-Through composite port directly Of the seven additional asynchronous ports shown on above. the distribution panel, only the first 3 (ports 1, 2, and 3) are operational in the case of the VT1XX-EA.

#### VT1XX-EB Physical Description 1.4.3

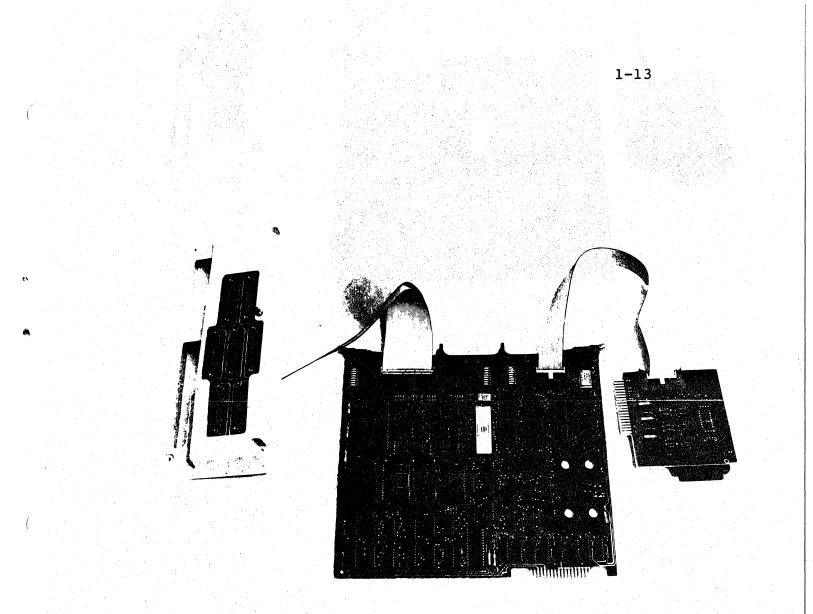

The VT1XX-EB eight channel statistical multiplexer consists of one VT1XX-EA plus one VT1XX-EC four channel expansion option. (Refer Section 1.4.4). Figure 1-7 shows the VT1XX-EB, consisting of VT1XX-EA with VT1XX-EC installed.

#### VT1XX-EC Physical Description 1.4.4

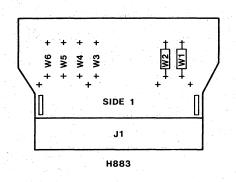

The VT1XX-EC is an expansion option for the VT1XX-EA statistical multiplexer. The option connects a VT1XX-EA to a VT1XX-EB by the addition of four asynchronous ports. The VT1XX-EC option consists of one printed circuit board and cable as shown in Figure 1-8. The printed circuit board clips to the VT1XX-EA/EB control module. The BC05Z-01 cable connects the four additional UARTS to the distribution board.

2

ð,

14

£7

Figure 1-5 VT1XX-EA Module Set

Figure 1-6 VT100 Rear View with VT1XX-EA/EB Installed.

69

ø

-

£.

Figure 1-7 VT1XX-EB Module SET

Figure 1-8 VT1XX-EC Option

Ô

Ö

#### 1.5 SPECIFICATIONS

The following paragraph contains electrical, environmental and performance specifications for the DZS11-EA. Performance specifications are listed in two separate categories, composite and asynchronous ports. Table 1-2 lists the composite port parameters, Table 1-3 lists the VT1XX-EA/EB asynchronous port parameter supported by the DZS11-EA.

1.5.1 Electrical

M7190 Module Power Requirements

| +5V + 5%             | 3.35  | ampers | typical | (3.5   | ampers | max) |

|----------------------|-------|--------|---------|--------|--------|------|

| +15V <del>T</del> 3% | Ø.Ø13 | ampers | typical | (0.069 | ampers | max) |

| -15V + 3%            | 0.020 | ampers | typical | (0.080 | ampers | max) |

UNIBUS loading

ac loading = 1 unit load dc loading = 1 unit load

1.5.2 Environmental

**Operating:**  $5^{\circ}C$  to  $50^{\circ}C$  ( $40^{\circ}F$  to  $122^{\circ}F$ ) with a relative humidity of 5% to 95% (noncondensing), with adequate airflow across the module. When operating at the maximum temperature ( $50^{\circ}C$  or  $122^{\circ}F$ ), air flow must maintain the inlet to outlet air temperature rise across the module at no more than  $5^{\circ}C$  ( $9^{\circ}F$ ).

Storage:  $-40^{\circ}$ C to  $80^{\circ}$ C ( $-40^{\circ}$ F to  $176^{\circ}$ F) with a relative humidity of 5% to 95% noncondensing.

NOTE

Before operating a module that has been stored in an environment outside the specified operating environment, the module must be allowed to stabilize at the operating environment for at least 5 minutes minimum.

# 1-16

A

0

### 1.5.3 Physical

| Height | 40 cm   | (15.7 | in) | typical |

|--------|---------|-------|-----|---------|

| Width  | 1.27 cm | ( Ø.5 | in) | typical |

| Length | 22.8 cm | ( 8.9 | in) | typical |

#### 1.5.4 Operational

Operational specification for the DZS11-EA statistical multiplexer are listed below in tables 1-1, 1-2, and 1-3.

Table 1-1 lists DZS11-EA UNIBUS operational specification Table 1-2 lists DZ STAT. MUX, multiplexing specifications Table 1-3 lists VT1XX-EA/EB asynchronous port specifications. Table 1-1 DZS11-EA UNIBUS Operational Specifications

| PARAMETER                     | DESCRIPTION                                                                                                                                                                                                                                                                      |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers                     | Control and Status Register (CSR)<br>Receive Buffer Register (RBUF)<br>Line Parameter Register (LPR)<br>Transmit Control Register (TCR)<br>Modem Status Register (MSR)<br>Transmit Data Register (TDR)                                                                           |

| Register<br>Addresses         | CSR 760010 Read/Write<br>RBUF 760012 Read Only<br>LPR 760012 Write Only<br>TCR 760014 Read/Write<br>MSR 760016 Read Only<br>TDR 760016 Write Only                                                                                                                                |

|                               | NOTE: Address specified is first address<br>of the floating address space. Refer to<br>Appendix B Floating Device Addresses and<br>Vectors.                                                                                                                                      |

| Interrupt Vector<br>Addresses | 300 Receiver Interrupt<br>304 Transmitter interrupt.<br>See floating Vectors Appendix B.                                                                                                                                                                                         |

| Priority Level                | Normally, a level 5 priority plug is<br>supplied. The interface level can be<br>modified to level 4, 6, or 7 by using the<br>proper priority plug.                                                                                                                               |

| Interrupt Types               | 가슴에서 이미지 않는 것이 있는 것이 있는 것이 있는 것이 있는 것이 있다.<br>같은 것이 같은 것이 같은 것이 같은 것은 것은 것은 것이 있는 것이 같은 것이 같은 것이 같은 것이 같은 것이 없다. 것이 같은 것이 같은 것이 없는 것이 없는 것이 없다. 것이 있는 것이 있는 것<br>같은 것이 같은 것이 같은 것이 같은 것이 같은 것이 없다. 것이 있는 것이 없는 것이 없는 것이 같은 것이 없다. 같은 것이 없는 것이 없는 것이 없다. 것이 없는 것이 없는 것이 없는 것이 없다. |

|                               | RDONE<br>Occurs each time a character appears at<br>the silo output.                                                                                                                                                                                                             |

|                               | SA<br>Silo Alarm. Occurs after 16 characters<br>enter the silo. Rearmed by reading the<br>silo. This interrupt disables the RDONE<br>interrupt.                                                                                                                                  |

|                               | TRDY<br>Occurs when the scanner finds a line<br>ready to transmit on.                                                                                                                                                                                                            |

|                               | NOTE                                                                                                                                                                                                                                                                             |

|                               | There are no modem interrupts.                                                                                                                                                                                                                                                   |

Table 1-2 DZ STAT MUX Multiplexing Specification

| PARAMETER                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Apparent<br>Efficiency   | Up to 400% depending on application.<br>Defined as aggregate asynchronous<br>terminal port Bandwidth divided by<br>Composite port Bandwidth.                                                                                                                                                                                                                                                                                                           |

| Real<br>Efficiency       | <pre>% Baud Rate  xx 1200 xx 2400 xx 4800 xx 9600 xx 19200</pre>                                                                                                                                                                                                                                                                                                                                                                                       |

|                          | Note: Real efficiency is a measure of<br>the net composite port bandwidth<br>available for information transfer. The<br>percentage quoted does not include<br>character compression from asynchronous<br>to synchronous, e.g. removal of start,<br>parity and stop bits. In a typical<br>system where 8 data bits, 1 start and 1<br>stop bit are compressed into 8 data bits,<br>the net bandwidths listed above are<br>increased by a factor of 120%. |

| Transit Delay            | MinMaxBaud Ratexxxmsxxxms1200 b/sxxxmsxxxms2400 b/sxxxmsxxxms4800 b/sxxxmsxxxms9600 b/sxxxmsxxxms19200 b/s                                                                                                                                                                                                                                                                                                                                             |

|                          | NOTE: Transit delays specified above are<br>approx. and are defined as the echoplex<br>time, i.e. the time taken for a full<br>round trip journey from asynchronous port<br>through network not including operating<br>system and back to asynchronous port.                                                                                                                                                                                           |

| Character<br>Compression | Up to 16 space characters $(40_8)$ are transmitted as one 8 bit character.                                                                                                                                                                                                                                                                                                                                                                             |

| Buffer Space             | DZS11-EA 3K characters<br>VT1XX-EA/EB 12K characters                                                                                                                                                                                                                                                                                                                                                                                                   |

# 1-18

U

ð

漭

| PARAMETER      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Mode | Full Duplex                                                                                                                                                                                                                                                                                                                                                                                          |

| Data Format    | Asynchronous, serial by bit, 1 start and<br>1, 1-1/2 (5-level codes only) or 2 stop<br>bits supplied by the hardware under<br>program control.                                                                                                                                                                                                                                                       |

| Character Size | 5,6,7 or 8 bits; program-selectable.<br>(Does not include parity bit).                                                                                                                                                                                                                                                                                                                               |

| Parity         | Parity is program-selectable. There may<br>be none, or it may be odd or even.                                                                                                                                                                                                                                                                                                                        |

| Order of Bit   | Transmission/reception low-order bit first.                                                                                                                                                                                                                                                                                                                                                          |

| Baud Rates     | 50, 75, 110, 135.5, 150, 300, 600, 1200, 1800, 2000, 2400, 3600, 4800, 7200 and 9600.                                                                                                                                                                                                                                                                                                                |

| Breaks         | Can be generated and detected on each line.                                                                                                                                                                                                                                                                                                                                                          |

| Throughput     | Up to 115% (Real Efficiency) of DZS11-EA composite baud rate                                                                                                                                                                                                                                                                                                                                         |

| Asynchronous   | Pin 1 Protective Ground<br>Pin 7 Signal Ground<br>Pin 2 Transmitted Data<br>Pin 3 Received Data<br>Pin 20 Data Terminal Ready<br>Pin 22 Ring Indicator<br>Pin 8 Carrier                                                                                                                                                                                                                              |

| Distortion     | The maximum "space to mark" and "mark to<br>space" distortion allowed in a received<br>character is 40 percent.<br>The maximum speed distortion allowed in a<br>received character for 2000 baud is 3.8<br>percent. All other baud rates allow 4<br>percent. The maximum speed distortion<br>from the transmitter for 2000 baud is 2.2<br>percent. All other baud rates have less<br>than 2 percent. |

Table 1-3 Asynchronous Port Specifications

Table 1-3 Asynchronous Port Specifications cont.

| PARAMETER                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asyn. Port<br>Enable/Mapping | Individual ports can be enabled or<br>disabled at VT1XX-EA/EB installation by<br>appropriate setting of dual in line (DIL)<br>switches.<br>This feature enables the maximum<br>configuration of 16 physical ports to be<br>logically connected to the 8 DZS11-EA<br>ports. At network initialisation,<br>enabled ports are logically mapped to the<br>eight DZS11-EA ports, e.g. in a network<br>consisting of two VT1XX-EB's with six<br>enabled ports at the primary VT1XX-EB and<br>two enabled ports at the secondary<br>VT1XX-EB, the six enabled ports at the<br>VT1XX-EB will be mapped to DZS11-EA ports<br>Ø thru 5 inclusive, while the remaining 2<br>enabled port at the secondary VT1XX-EB<br>will be mapped to ports 6 and 7.<br>Only the first 8 of the enabled ports in<br>the network are mapped. |

| Port Flow<br>Synchronisation | Data synchronisation is necessary on each<br>asynchronous port to control the flow of<br>data. Two methods are available to the<br>user, they are:-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                              | <pre>o Software XON/XOFF control characters</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                              | o Hardware DTR/DSR signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                              | The user has the choice of one of the<br>above procedures on a per line basis.<br>This is enabled at installation time by<br>setting DIL switches.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Local Echo/<br>Echoplex      | Asynchronous ports can be operated in<br>either echoplex mode or local echo mode.<br>The modes can be operator configured by<br>modifying SET UP B field 5 of the host<br>VT100. Field 5 contains four bits, each<br>bit controls two ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### 1.5.5 Composite Port

This section contains an introduction to and specification of the DZ STAT MUX network composite links. The term "Main composite link" as used throughout this manual, denotes the logical data link between DZS11-EA and primary VT1XX-EA/EB. The term "Route-through composite link" as used through-out this manual denotes the logical data link between primary VT1XX-EA/B and secondary VT1XX-EA/EB. Both Main and Route-through composite links are shown in Figure 1-1.

The composite links are used for link control between the DZ STAT MUX components, and for the transfer of data between DZS11-EA UNIBUS interface and the VT1XX-EA/EB asynchronous ports.

Link control tasks include; Network initialisation, following system initialisation and or power up. Down line loading of asynchronous port parameters e.g baud rate, and character format from DZS11-EA to VT1XX-EA/EB, and control of data flow, in the form of frame sequencing and re-transmission control.

#### 1.5.5.1 Composite Port Interface

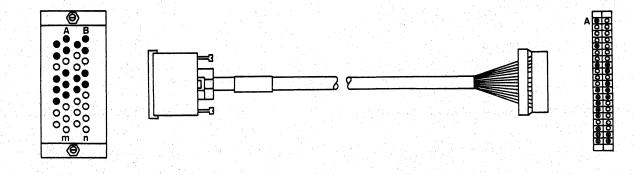

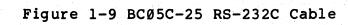

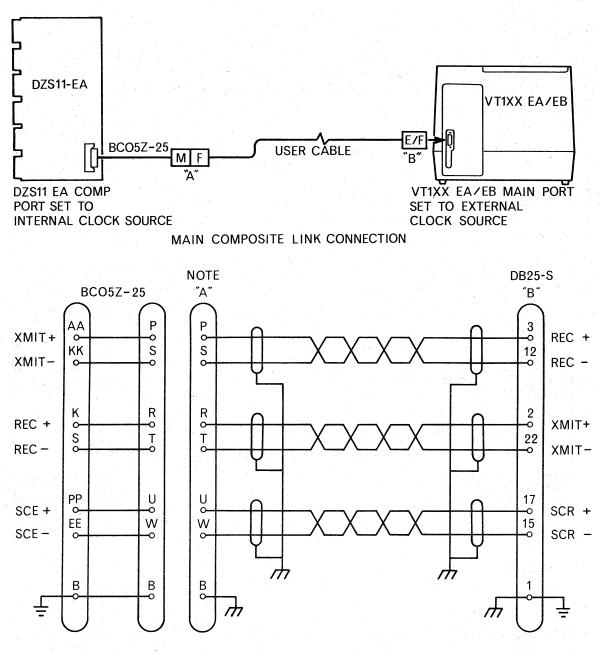

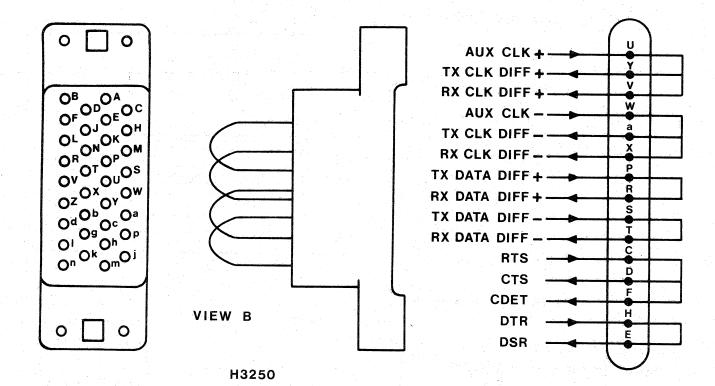

The DZS11-EA composite port conforms to EIA RS-232C and EIA RS-423 interface standards simultaneously. Interconnection to the Main composite link is via a BCØ5C-25 cable, (Figure Table 1-4 lists the correlation between connector pins 1-9). and signal functions for this cable. Although the DZS11-EA is shipped with the composite port conforming to EIA RS-232C for modem connection, the port can be re-configured for long line driver capability at installation time utilising RS-422 full differential transceivers. The modification requires component changes on the DZS11-EA module plus the addition of an option cable to replace the standard BCØ5C-25. The exact cable type is dependent upon the network configuration, however, cable type BCØ5Z-25 is such a cable and is therefore included in Table 1-4 as an example. Figure 1-10 shows the BCØ5Z-25.

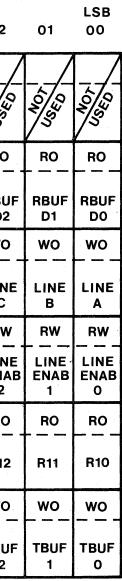

# Table 1-4 DZS11-EA Composite Port Connector Pinning