# microcomputer handbook series

÷3

# digital

# memories and peripherals

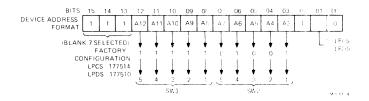

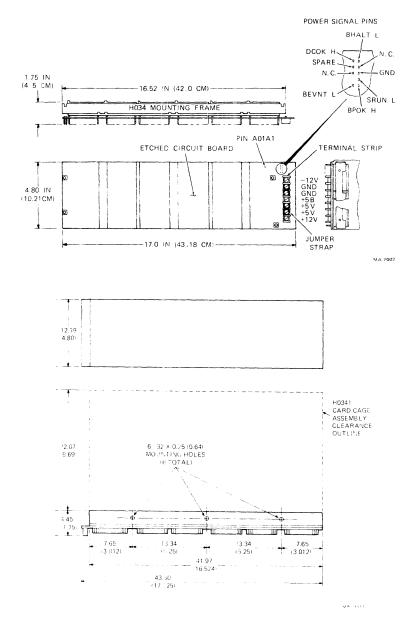

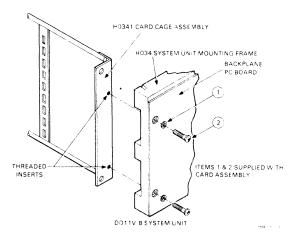

digital equipment corporation

Copyright <sup>©</sup> 1976, 1977, 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this handbook.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

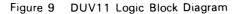

DEC PDP FLIP CHIP FOCAL DIGITAL DECUS

# CONTENTS

#### CHAPTER 1 INTRODUCTION

| 1.1 | SCOPE                         | 1-1 |

|-----|-------------------------------|-----|

| 1.2 | PERIPHERAL EQUIPMENT          | 1-1 |

| 1.3 | LSI-11 FAMILY CHARACTERISTICS | 1-1 |

| 1.4 | PROCESSORS                    | 1-2 |

| 1.5 | LSI-11 BUS                    | 1-2 |

| 1.6 | DEVICE REGISTERS              | 1-3 |

| 1.7 | INTERRUPTS                    | 1-3 |

| 1.8 | MEMORY ADDRESSES              | 1-3 |

#### CHAPTER 2 LSI-11 BUS PERIPHERALS AND OPTIONS

| GENERAL                                 | 2-1   |

|-----------------------------------------|-------|

| GENERAL SPECIFICATIONS                  | 2-2   |

| DETAILED SPECIFICATIONS                 | 2-2   |

| CONFIGURATION                           | 2-10  |

| Addresses                               | 2-10  |

| Control and Status Registers            | 2-12  |

| Data Buffer Registers                   | 2-13  |

| Interrupts                              | 2-13  |

| Interrupt Vectors                       |       |

| FUNCTIONAL DESCRIPTION                  | 2-14  |

| CATEGORIES                              | 2-14  |

| Interface Options                       | 2-14  |

| Communications Options                  |       |

| Expansion Memories                      | 2-17  |

| Peripherals                             |       |

| Miscellaneous Options                   | 2-19  |

| OPTION DESCRIPTIONS                     |       |

| AAV11-A 4-Channel 12-Bit D/A Converter  | 2-21  |

| ADV11-A Analog to Digital Converter     | 2-31  |

| BDV11 Diagnostic, Bootstrap, Terminator | 2-51  |

| DLV11 Serial Line Unit                  | 2-81  |

| DLV11-E Asynchronous Line Interface     | 2-103 |

| DLV11-F Asynchronous Line Interface     | 2-125 |

| DLV11-J Four Asynchronous Serial        |       |

| Interfaces                              |       |

| DRV11 Parallel Line Unit                | 2-173 |

| DRV11-B DMA Interface                   | 2-193 |

| DRV11-P LSI-11 Bus Foundation Module    | 2-217 |

| DUV11 Line Interface                    | 2-245 |

| DZV11 Asynchronous Multiplexer        | 2-269 |

|---------------------------------------|-------|

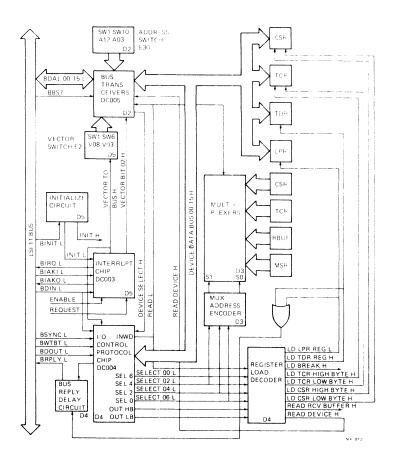

| IBV11-A Instrument Bus Interface      | 2-295 |

| KPV11-A,-B,-C Power-Fail/Line-Time    |       |

| Clock/Terminator                      | 2-317 |

| KWV11-A Programmable Real-Time Clock. | 2-339 |

| LAV11 Printer Option                  | 2-361 |

| LPV11 Printer Option                  | 2-375 |

| MMV11-A 4K by 16-Bit Core Memory      | 2-395 |

| MRV11-AA 4K by 16-Bit Read-Only       |       |

| Memory                                | 2-413 |

| MRV11-BA LSI-11 UV PROM/RAM           | 2-425 |

| MSV11-B 4K by 16-Bit Read/Write       |       |

| Memory                                | 2-441 |

| MSV11-CD 16K by 16-Bit Read-Write     |       |

| Memory                                | 2-447 |

| MSV11-D,-E Memory                     |       |

| REV11-A DMA Refresh, Bootstrap/       |       |

| Terminator                            |       |

| REV11-C DMA Refresh, Bootstrap        | 2-491 |

| RKV11-D RK05 Disk Drive Controller    |       |

| RLV11 RL01 Disk Drive Controller      | 2-545 |

| RXV11 Floppy Disk Option              |       |

| TEV11 Terminator                      |       |

|                                       |       |

## CHAPTER 3 USING PROMs

| 3.1 | GENER  | ۹L                                | 3-1  |

|-----|--------|-----------------------------------|------|

| 3.2 | PROGR  | AMMING NOTES                      | 3-1  |

| 3.3 | LOADIN | IG AND INSTALLING PROMs           | 3-3  |

|     | 3.3.1  | General                           | 3-3  |

|     | 3.3.2  | MRV11-AA Procedures               | 3-3  |

|     | 3.3.3  | MRV11-BA Procedures               |      |

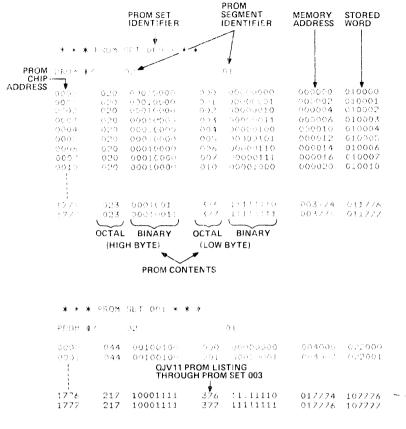

| 3.4 | PROM F | ORMATTING USING THE QJV11 PROGRAM | 3-7  |

|     | 3.4.1  | General                           | 3-7  |

|     | 3.4.2  | Loading QJV11                     | 3-7  |

|     | 3.4.3  | Entering Parameters               | 3-9  |

|     | 3.4.4  | QJV11 Operation                   | 3-12 |

|     |        |                                   |      |

#### CHAPTER 4 HARDWARE OPTIONS

| 4.1 | INTRO | DUCTION           |      |

|-----|-------|-------------------|------|

| 4.2 | васкр | LANE OPTIONS      |      |

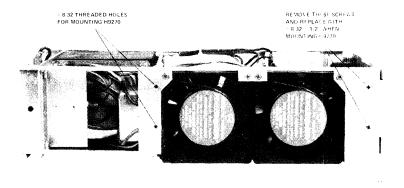

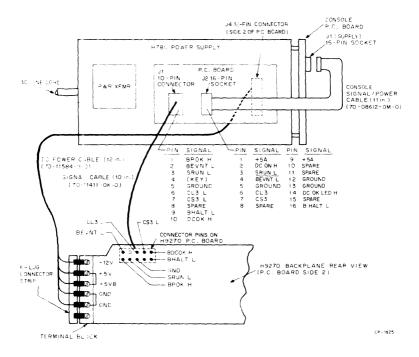

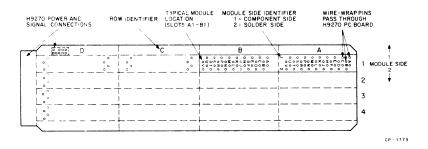

|     | 4.2.1 | H9270 Backplane   | 4-4  |

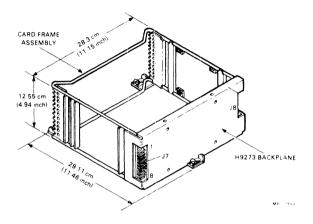

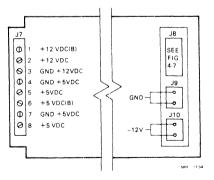

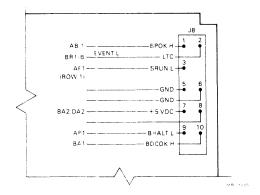

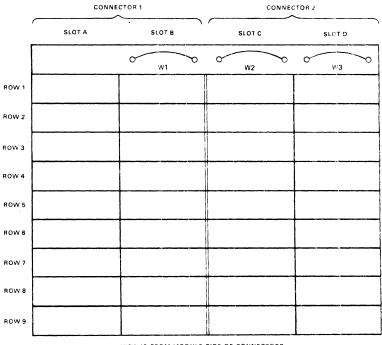

|     | 4.2.2 | H9273-A Backplane |      |

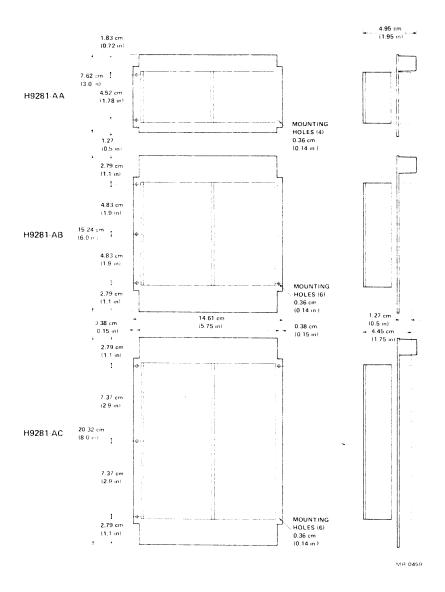

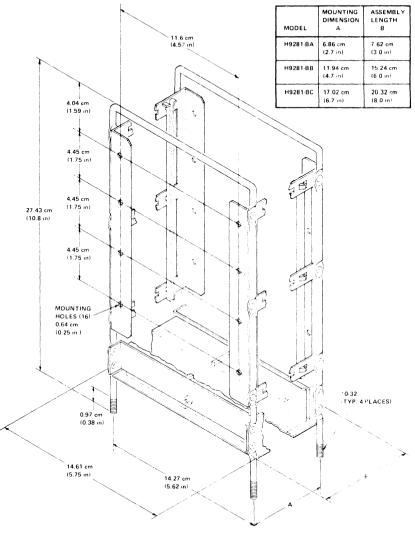

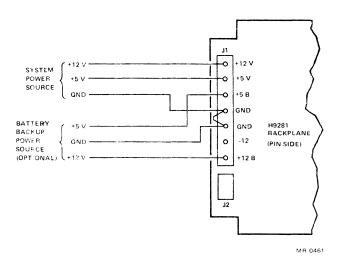

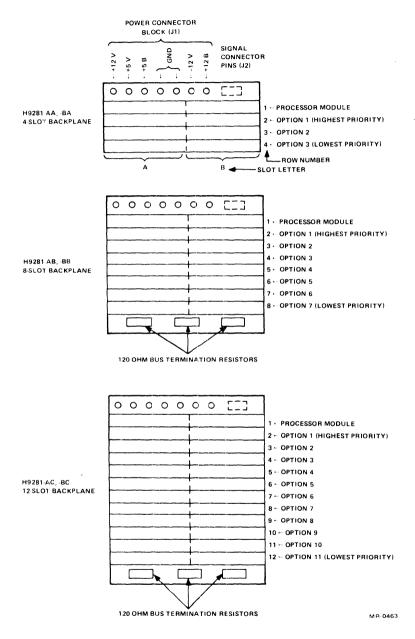

|     | 4.2.3 | H9281 Backplane   | 4-12 |

|     | 4.2.4 | DDV11-B Backplane | 4-18 |

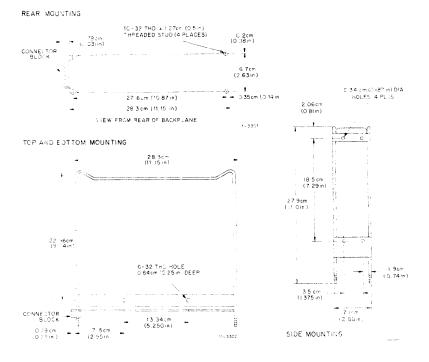

| 4.3   | ENCLO         | SURES                                            |       |

|-------|---------------|--------------------------------------------------|-------|

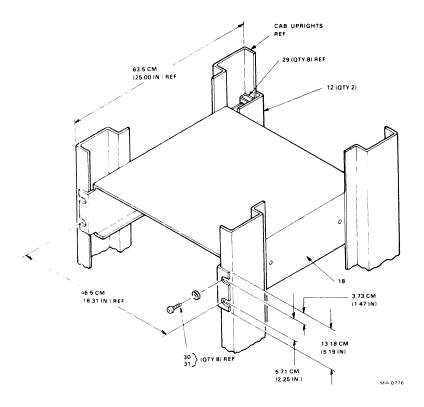

|       | 4.3.1         | H909-C General Purpose Logic Enclosure           | 4-24  |

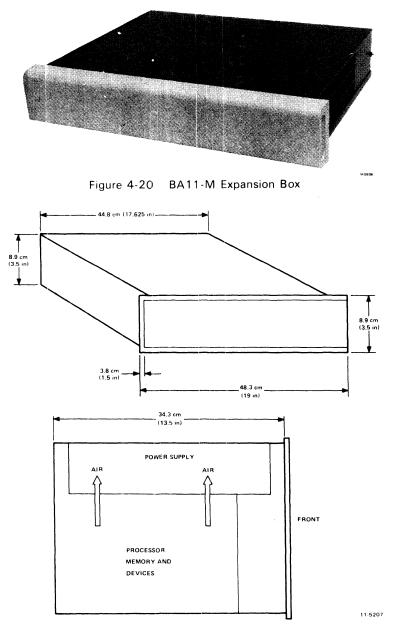

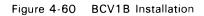

|       | 4.3.2         | BA11-M Expansion Boxes                           | 4-26  |

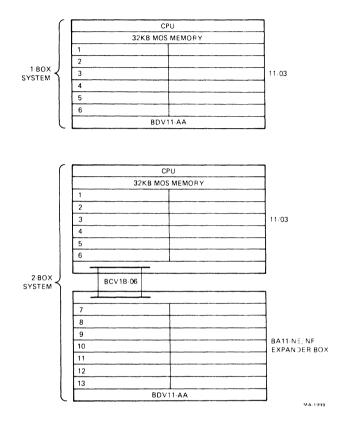

|       | 4.3.3         | BA11-N Mounting Box                              | 4-31  |

|       | 4.3.4         | Backplane and Module Configuration               | 4-39  |

| 4.4   | CABIN         | ETS                                              | 4-41  |

|       | 4.4.1         | H984 Series Cabinets                             |       |

|       | 4.4.2         | H9800-A Cabinets                                 | 4-44  |

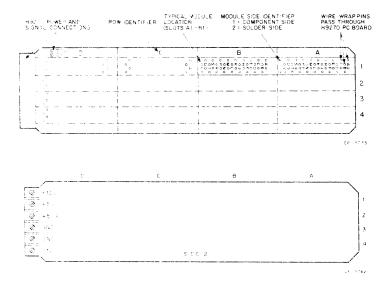

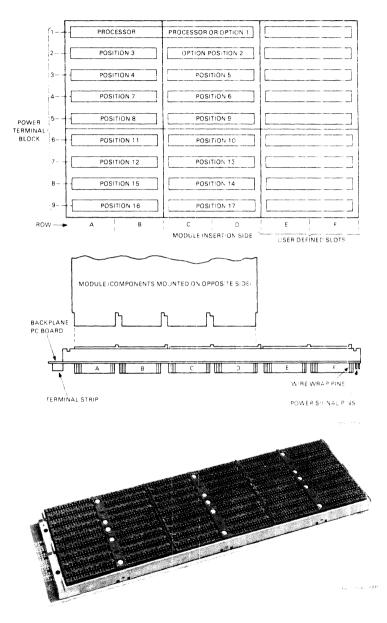

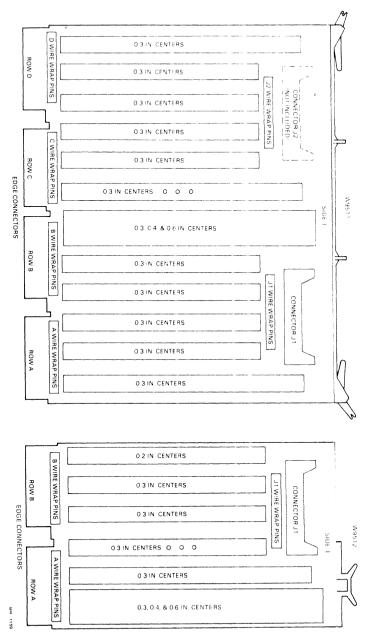

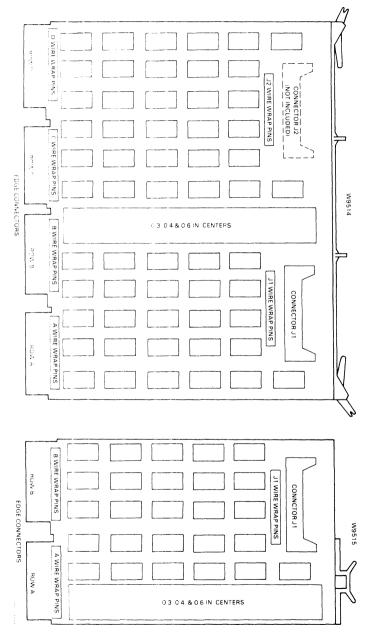

| 4.5   | LSI-11        | BUS-COMPATIBLE, WIRE-WRAPPABLE                   |       |

|       |               | LES (W9511, W9512, W9514 and W9515)              |       |

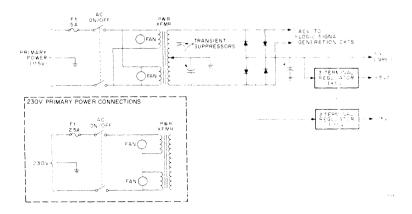

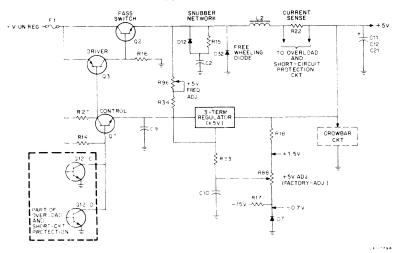

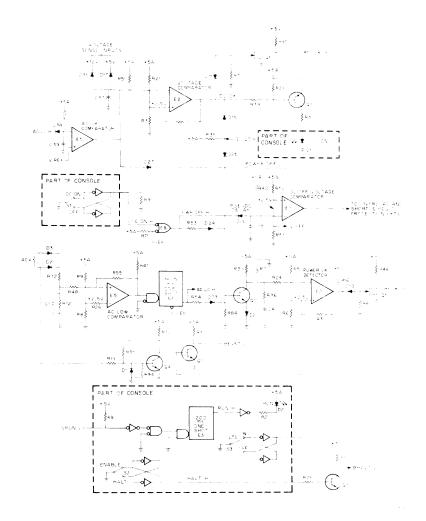

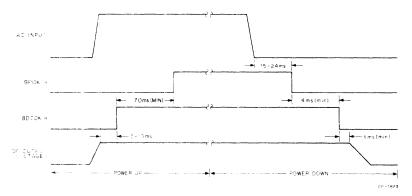

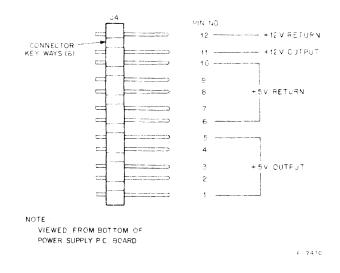

| 4.6   | H780 I        | POWER SUPPLY OPTIONS                             | 4-50  |

|       | 4.6.1         | General                                          |       |

|       | 4.6.2         | Specifications                                   | 4-52  |

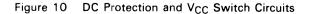

|       | 4.6.3         | Functional Description                           |       |

|       | 4.6.4         | H780-C,-D,-H,-J,-K,-L Installation               | 4-65  |

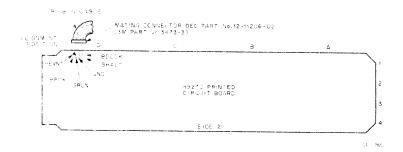

| 4.7   | CABLE         | S AND CONNECTORS                                 | 4-84  |

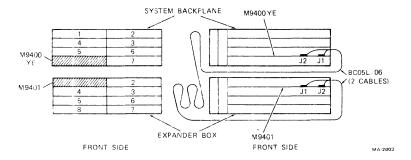

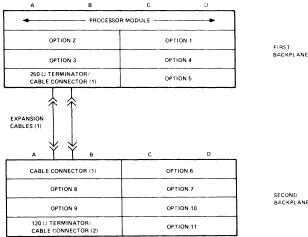

|       | 4.7.1         | Using the BCV1B                                  | 4-86  |

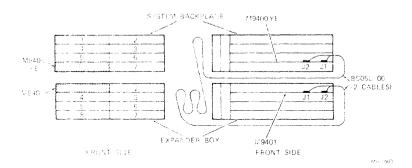

|       | 4.7.2         | Using the BCV1A                                  | 4-88  |

|       |               |                                                  |       |

| CHAPT | ER5 I         | NTEGRATED CIRCUITS                               |       |

| 5.1   | INTEG         | RATED CIRCUITS                                   | 5-1   |

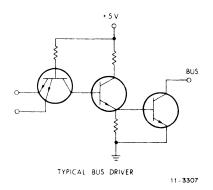

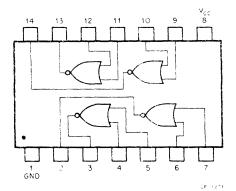

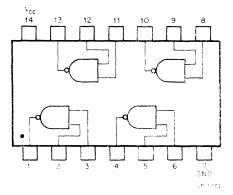

|       | 5.1.1         | Bus Receivers and Bus Drivers                    |       |

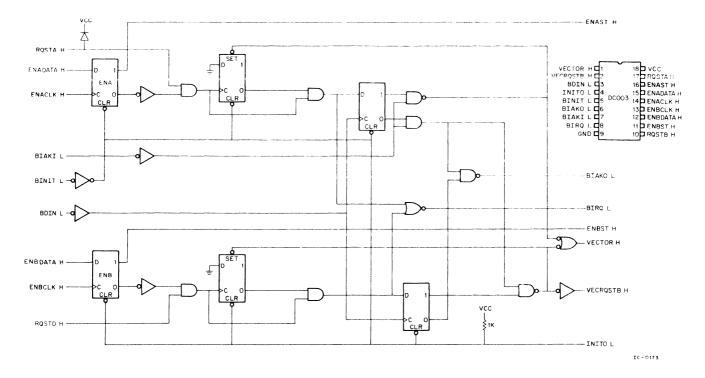

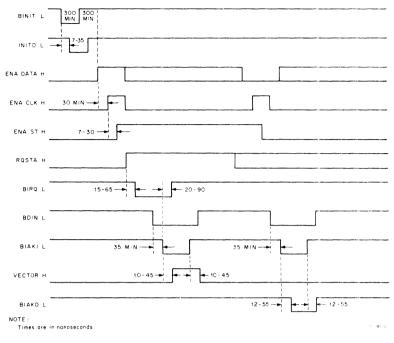

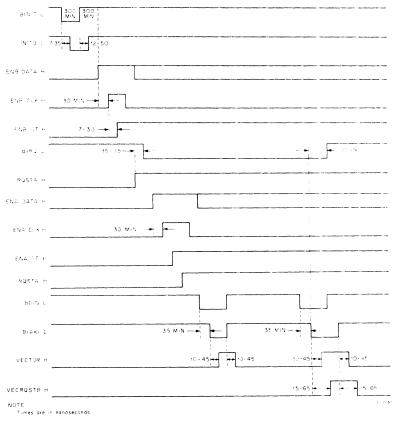

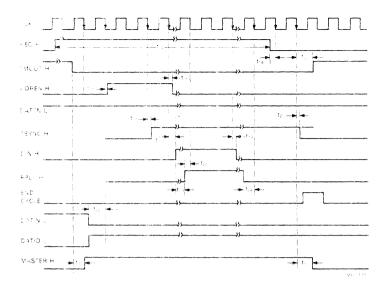

|       | 5.1.2         | DC003 Interrupt Logic                            |       |

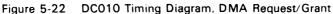

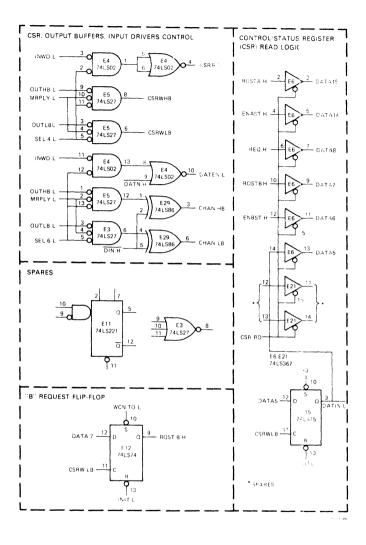

|       | 5.1.3         | DC004 Protocol Logic                             |       |

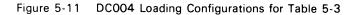

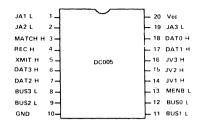

|       | 5.1.4         | DC005 Transceiver Logic                          |       |

|       | 5.1.5         | DC006 Word Count/Bus Address Logic               |       |

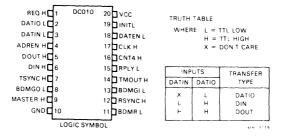

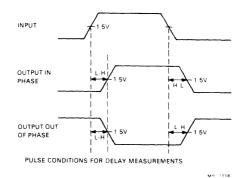

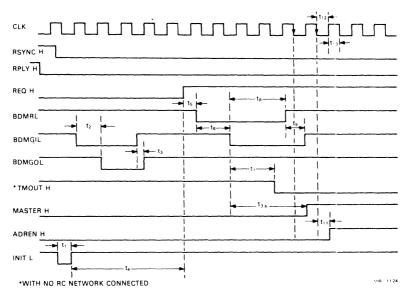

|       | 5.1.6         | DC010 Direct Memory Access Logic                 |       |

|       | 5.1.7         | Specifications                                   |       |

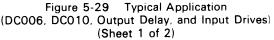

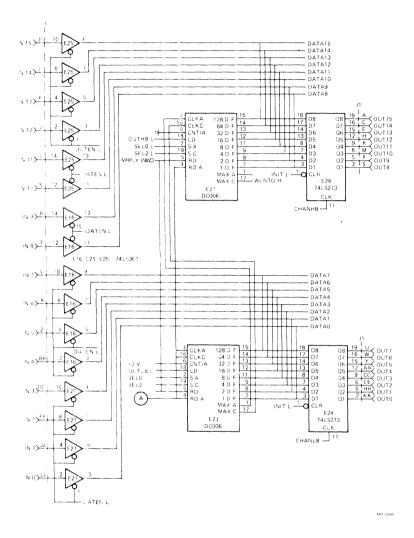

| 5.2   | TYPIC         | AL APPLICATION                                   |       |

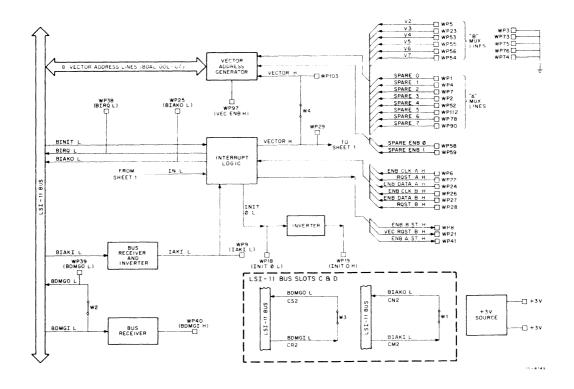

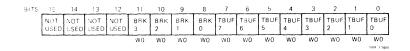

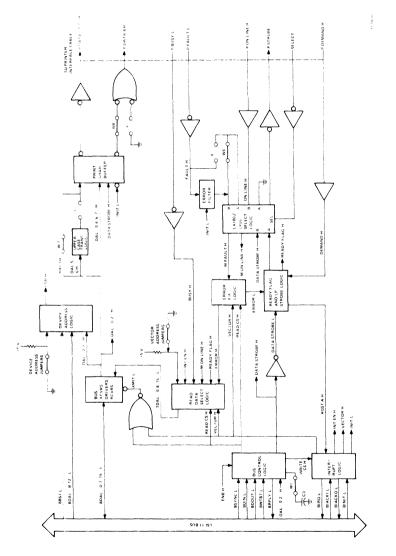

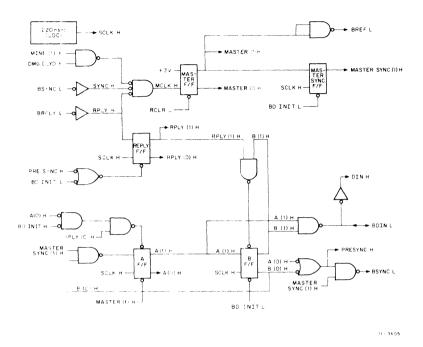

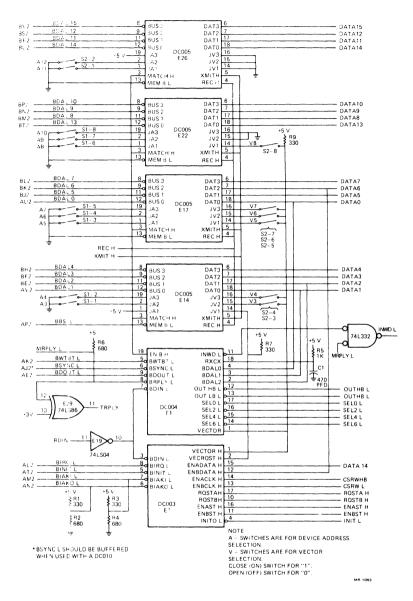

|       | 5.2.1         | DC003, DC004, DC005 Application                  | 5-44  |

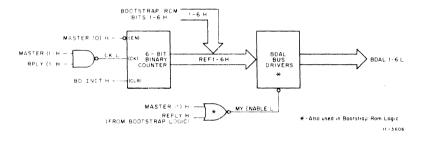

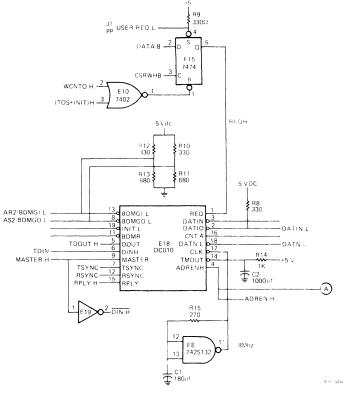

|       | 5.2.2         | DMA Application                                  | 5-48  |

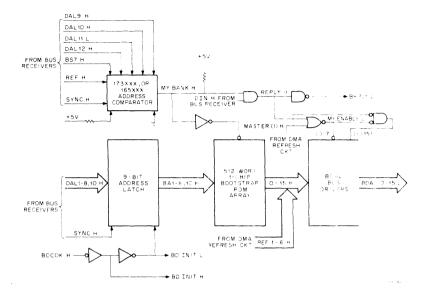

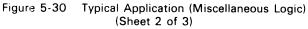

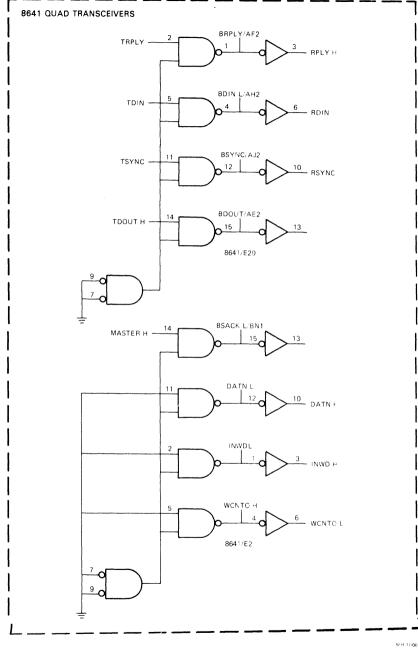

|       | 5. <b>2.3</b> | Miscellaneous Logic                              | 5-51  |

|       |               |                                                  |       |

| APPEN | DIXA          | ASSIGNMENT OF ADDRESSES AND VEC                  | TORS  |

| APPEN | DIX B         | LSI-11 BUS SIGNALS                               |       |

| APPEN | DIX C         | PERIPHERAL AND OPTION DATA                       |       |

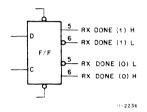

| APPEN | DIX D         | NOMENCLATURE FOR CIRCUIT SCHEMA                  | ATICS |

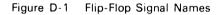

| APPEN | DIX E         | ASYNCHRONOUS SERIAL LINE UNIT (SL<br>COMPARISONS | U)    |

| APPEN | DIX F         | COMPARISON OF DATA TRANSMI<br>TECHNIQUES         | SSION |

v

# CHAPTER 1

# INTRODUCTION

#### 1.1 SCOPE

This handbook is a reference guide for the memory and peripheral hardware options that can be installed on the LSI-11 bus. It includes descriptions, specifications, configuration information, programming information as applicable to the options, and functional theory. The hardware options described in this handbook are designed to interface with a processor via the LSI-11 bus. Therefore, the user should be familiar with the contents of the appropriate processor handbook.

#### 1.2 PERIPHERAL EQUIPMENT

Digital Equipment Corporation designs and manufactures the memory and peripheral options described in this handbook. The general design criterion was to provide maximum system throughput for peripherals when installed on the LSI-11 bus. LSI-11 bus-compatible processors and peripherals are designed to work together, providing a broad spectrum of system-compatible hardware options. The memory and peripheral devices can be used with any LSI-11 bus configuration; the system can later be expanded or modified to meet new system requirements. This hardware flexibility, when coupled with DIGITAL software and support, provides a single source for all present and future microcomputer processing needs.

#### 1.3 LSI-11 FAMILY CHARACTERISTICS

LSI-11 bus systems include various processors, memory and peripheral device options, and software. Some of the characteristics of the LSI-11 bus systems are as follows:

- Low-cost, powerful processors for integration into any small- or medium-sized computer system.

- Direct addressing of all memory locations and peripheral device registers.

- Efficient processing of 8-bit bytes (characters) without the need to rotate, swap, or mask.

- Asynchronous bus operation that allows system components to run at their highest possible speed; replacement with faster devices means faster operation without other hardware or software changes.

- A module component design that provides ease and flexibility in configuring systems.

- Inherent direct memory access capabilities for high data rate devices.

- A bus structure that provides position-dependent priority for peripheral device interfaces connected to the I/O bus.

- Vectored interrupts that allow service routine entry without device polling.

#### 1.4 PROCESSORS

The processor is connected to the LSI-11 bus (backplane) as a subsystem that executes programs and arbitrates usage of the LSI-11 bus for peripherals. It contains multiple, high-speed, general-purpose registers that can be used as accumulators, address pointers, index registers, and other specialized functions. The processor can perform data transfers directly between peripheral input/output (I/O) devices and memory without disturbing the processor registers. Data transfers include both 16-bit word and 8-bit byte data.

#### 1.5 LSI-11 BUS

System components, including the processor, memory, and peripherals, are interconnected and communicate with each other via the LSI-11 bus. The form of communication is the same for all devices on the bus; instructions that communicate with memory can communicate with peripheral devices. Each device, including memory locations and peripheral device registers, is assigned an individual byte or word address on the LSI-11 bus.

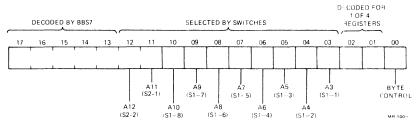

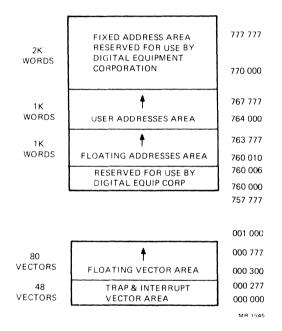

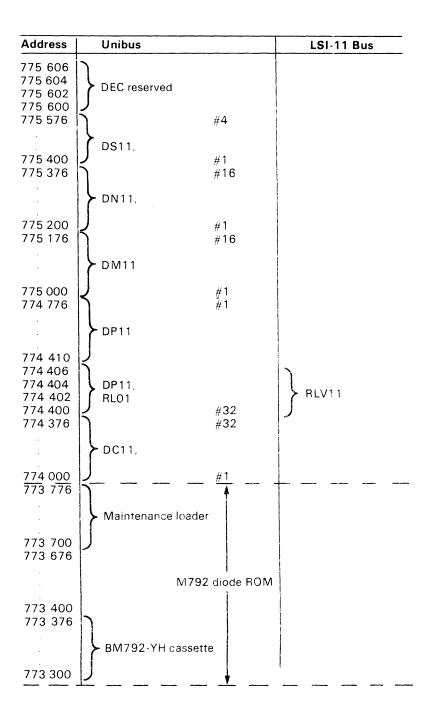

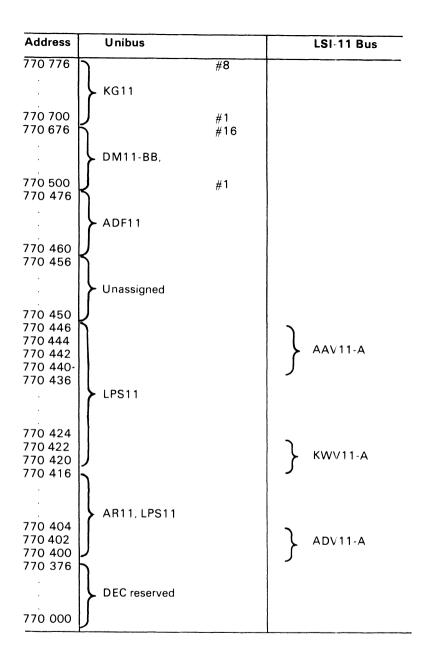

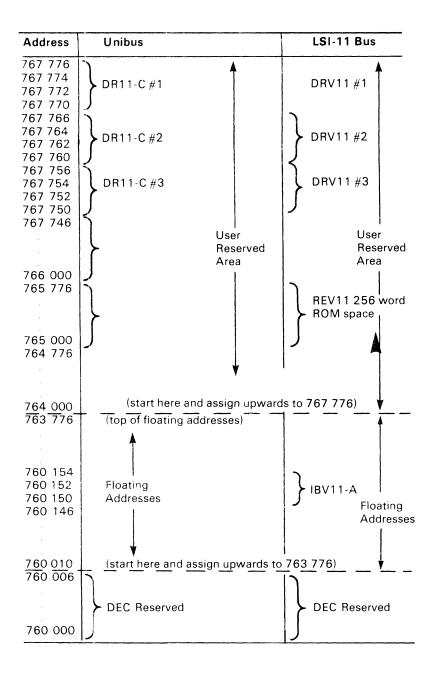

The LSI-11 bus supports 18-bit addresses. However, processors and peripherals having a 16-bit addressing capability are completely PDP-11 hardware- and software-compatible within the 16-bit limitation. By PDP-11 convention, all peripheral device addresses are located within the upper 4K address space in the system, whether 16-bit or 18-bit addresses are used. This 4K address space is called the I/O page or "bank 7."

Whenever the I/O page is addressed, the processor must assert the BBS7 L bus signal. All peripheral devices use this signal line during addressing rather than decoding address bits (15:13) or (17:13). An active (asserted) BBS7 L signal will always indicate an address in the I/O page, enabling peripheral device addressing.

Peripheral device addresses within the I/O page are decoded by each peripheral device. Each peripheral device will include one or more "device register(s)." These registers can be accessed under program control in exactly the same manner as memory locations. Unique addresses within the I/O page are encoded on address bits (15:00).

#### NOTE

Address bits, for the purpose of this discussion, are logical states present on LSI-11 bus signal lines BDAL (17:00) L during the addressing portion of a bus cycle.

Refer to the appropriate processor handbook for a complete description of bus transactions, including bus cycles, addressing, etc.

#### 1.6 DEVICE REGISTERS

All peripheral devices are defined by one or more device registers that are addressed as part of the main memory. These registers are generally designated control and status register(s).

Control and status registers (CSRs) contain all the necessary information to establish communications with the device. Some devices will require fewer than 16 status bits, while other devices could require more than 16 bits and, therefore, will require additional registers. The bits of the CSR have predetermined assigned functions. Typical bit functions include interrupt enable, error, done or ready, and enable.

Data buffer registers (DBRs) are for temporarily storing data to be transferred into and out of the processor. The number and type of data registers is a function of the individual peripheral device requirements.

#### 1.7 INTERRUPTS

Interrupts allow devices to obtain processor service when they are "ready" for service, or "done" with a specific operation. The interrupt structure allows the processor to execute other programs while one or more peripherals are "busy." When a peripheral requires service, it requests an interrupt. The processor completes execution of the present instruction, saves PC and PS words on the stack, and acknowledges the interrupt. The highest priority peripheral device currently requesting interrupt service responds by inputting its interrupt vector address to the processor. The processor uses this vector address as a pointer to two memory locations containing the PC (starting address) and PS for the peripheral device interrupt service routine. Program control is transferred from the interrupted program to the routine associated with the requesting peripheral device. Note that no device polling is required since the interrupt vector is unique for that device. Once the device service routine execution has been completed, control is returned either to the previously interrupted program or to another peripheral device requesting interrupt service.

#### 1.8 MEMORY ADDRESSES

Memory addresses are generally limited to the address space other than the I/O page. However, the I/O page can contain read-only memory (ROM) for disk bootstraps, paper tape loaders, diagnostics, etc. and/or read/write memory for DMA buffers. The system designer must use care in assigning memory addresses within the I/O page to avoid conflicts with peripheral device addresses used for actual system hardware, or addresses that system software may attempt to access for peripheral devices not actually installed in the system. See Appendix A for the standard assignments of the addresses in the I/O page.

# LSI-11 BUS PERIPHERALS AND OPTIONS

#### GENERAL

This chapter contains descriptions, features, specifications, configuration, and functional information for the LSI-11 bus peripherals and options. The data is arranged alphanumerically by option designation and is summarized by categories in Table 2-1. The option designation is printed on the top of each page to assist in locating any specific option. All the peripherals and options interface with the LSI-11 bus.

All the options include a module that connects to the bus backplane and provides the interface connections between the bus and the peripheral device. Some options provide only the interface module and will provide direct connections from the user's device to the bus. Other options include the device, such as line printers and disk drives. Some options have the capability to interface more than a single device, such as disk drives or terminals.

| Option      | Name                                   | Page  |

|-------------|----------------------------------------|-------|

| INTERFACE O | PTIONS                                 |       |

| AAV11-A     | 4-Channel, 12-Bit D/A Converter        | 2-21  |

| ADV11-A     | Analog-to-Digital Converter            | 2-31  |

| DRV11       | Parallel Line Interface                | 2-173 |

| DRV11-B     | DMA Interface                          | 2-193 |

| DRV11-P     | LSI-11 Bus Interface Foundation Module | 2-217 |

| IBV11-A     | Instrument Bus Interface               | 2-295 |

| KWV11-A     | Programmable Real-Time Clock           | 2-339 |

| DLV11       | Asynchronous Serial Line Interface     | 2-81  |

| DLV11-E     | Asynchronous Line Interface            | 2-103 |

| DLV11-F     | Asynchronous Line Interface            | 2-125 |

| DLV11-J     | Four Asynchronous Serial Interfaces    | 2-147 |

| DUV11       | Synchronous Line Interface             | 2-245 |

| DZV11       | Asynchronous Multiplexer               | 2-269 |

#### Table 2-1 Peripherals and Option Designations

| Table 2-1 Peripherals | s and Option | <b>Designations</b> | (Cont) |

|-----------------------|--------------|---------------------|--------|

|-----------------------|--------------|---------------------|--------|

| Option | Name | Page  |

|--------|------|-------|

| Option | Name | i age |

#### **EXPANSION MEMORIES**

| MMV11-A     | 4K by 16-Bit Core Memory             | 2-395 |

|-------------|--------------------------------------|-------|

| MRV11-AA    | 4K by 16-Bit Read-Only Memory        | 2-413 |

| MRV11-BA    | UV PROM/RAM Memory                   | 2-425 |

| MSV11-B     | 4K by 16-Bit MOS Read/Write Memory   | 2-441 |

| MSV11-CD    | 16K by 16-Bit MOS Read/Write Memory  | 2-447 |

| MSV11-D, -E | 8K, 16K, or 32K Random Access Memory | 2-471 |

#### PERIPHERALS

| LAV11   | LA180 Printer Option          | 2-361 |

|---------|-------------------------------|-------|

| LPV11   | LA180/LP05 Printer Option     | 2-375 |

| RKV11-D | RK05 Disk Drive Option        | 2-509 |

| RLV11   | RL01 Disk Drive Option        | 2-545 |

| RXV11   | RX01 Floppy Disk Drive Option | 2-575 |

#### **MISCELLANEOUS OPTIONS**

| BDV11           | Diagnostic, Bootstrap, Terminator       | 2-51  |

|-----------------|-----------------------------------------|-------|

| KPV11-A, -B, -C | Power-Fail, Line-Time Clock, Terminator | 2-317 |

| REV11-A, -C     | DMA Refresh, Bootstrap, Terminator      | 2-491 |

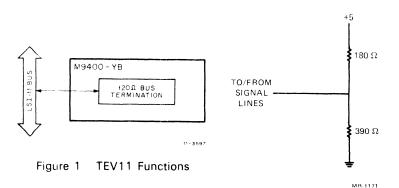

| TEV11           | Terminator                              | 2-605 |

#### GENERAL SPECIFICATIONS

All the LSI-11 bus modules will operate under the following conditions:

| Temperature | 5° to 60° C (41° to 140° F) |

|-------------|-----------------------------|

| Humidity    | 10 to 95% (no condensation) |

When operating at the maximum outlet temperature ( $60^{\circ}$  C or  $140^{\circ}$  F), adequate air flow must be maintained to control the inlet to outlet temperature rise across the modules to  $5^{\circ}$  C ( $9^{\circ}$  F) maximum. The air flow should be directed to flow across the modules.

#### DETAILED SPECIFICATIONS

All the individual module specifications are included in the detailed description of the peripheral or option. A summary of the module characteristics is provided in Table 2-2; these characteristics are defined as follows.

1. The option designation is the alphanumerical code assigned to the option.

| Option<br>Desig. | Module<br>No(s). | Description                           | Power Requ<br>+5 V ± 5% | uirements<br>+12 V ± 3 % | Bus Loads*<br>AC (Max) | DC | Size   | Page |

|------------------|------------------|---------------------------------------|-------------------------|--------------------------|------------------------|----|--------|------|

| AAV11-A          | A6001            | 4-channel, 12-bit<br>D/A converter    | 1.5 A                   | 0.4 A                    | 1.9                    | 1  | Quad   | 2-21 |

| ADV11-A          | A012             | 16-channel, 12-bit<br>A/D converter   | 2.0 A                   | 0.45 A                   | 3.25                   | 1  | Quad   | 2-31 |

| BDV11            | M8012            | Boot, term,<br>diagnostic             | 1.6 A                   | 0.07 A                   | 2.0                    | 1  | Quad   | 2.51 |

| DLV11            | M7940            | Asynchronous serial<br>line interface | 1.0 A                   | 0.18A                    | 2.5                    | 1  | Double | 2-81 |

| DLV11-E          | M8017            | Asynchronous line interface           | 1.0 A                   | 0.18 A                   | 1.6                    | 1  | Double | 2-10 |

| DLV11-F          | M8028            | Asynchronous line<br>interface        | 1.0 A                   | 0.18 A                   | 2.2                    | 1  | Double | 2-12 |

| DLV11-J          | M8043            | 4 asynchronous serial interfaces      | 1.0 A                   | 0.25 A                   | 1                      | 1  | Double | 2-14 |

Table 2-2 Module Specifications

\*These ac loads figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

| <br>Option<br>Desig. | Module<br>No(s). | Description                          | Power Req<br>+5 V ± 5% | uirements<br>+12 V ± 3 % | Bus Loads*<br>AC (Max) | DC | Size   | Page  |

|----------------------|------------------|--------------------------------------|------------------------|--------------------------|------------------------|----|--------|-------|

| DRV11                | M7941            | Parallel line unit interface         | 0.9 A                  | -                        | 1.4                    | 1  | Double | 2-173 |

| DRV11-B              | M7950            | DMA interface                        | 1.9A                   | -                        | 3.3                    | 1  | Quad   | 2-193 |

| DRV11-P              | M7948            | Foundation<br>module                 | 1.0A<br>+ user logic   | -                        | 2.1                    | 1  | Quad   | 2-217 |

| DUV11                | M7951            | Synchronous serial<br>line interface | 0.86 A                 | 0.32                     | 1.00                   | 1  | Quad   | 2-245 |

| DZV11-A              | M7957            | Asynchronous<br>line interface       | 1 15 A                 | 0.39 A                   | 3.95                   | 1  | Quad   | 2 269 |

| IBV11-A              | M7954            | Instrument bus<br>interface          | 0.8 A                  |                          | 1.8                    | 1  | Double | 2-295 |

| KPV11-A              | M8016            | Power-fail/line-<br>time clock       | 0.56 A                 | -                        | 1.63                   | 1  | Double | 2-317 |

Table 2-2 Module Specifications (Cont)

\*These ac loads figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

| Option<br>Desig | Module<br>No(s). | Description                                                   | Power Requ<br>+5 V ± 5% | uirements<br>+12 V ± 3 % | Bus Loads*<br>AC (Max) | DC | Size    | Page  |

|-----------------|------------------|---------------------------------------------------------------|-------------------------|--------------------------|------------------------|----|---------|-------|

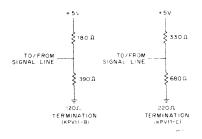

| KPV11-B         | M8016-YB         | Power-fail/line-<br>time clock/120 $\Omega$<br>bus terminator | 0.56 A                  | -                        | 1.63                   | 1  | Double  | 2-317 |

| KPV11-C         | M8016-YC         | Power-fail/line-<br>time clock/220 $\Omega$<br>bus terminator | 0.56 A                  | -                        | 1.63                   | 1  | Double  | 2-317 |

| KWV11-A         | M7952            | Programmable<br>real-time clock                               | 1.75 A                  | 0.01 A                   | 3.4                    | 1  | Quad    | 2-339 |

| LAV11           | M7949            | LA180 line printer<br>interface                               | 0.8 A                   | -                        | 1.8                    | 1  | Double  | 2-361 |

| LPV11           | M8027            | LA180/LP05<br>printer interface                               | 0.8 A                   | -                        | 1.4                    | 1  | Double  | 2-375 |

| MMV11-A         | H223<br>G653     | 4K × 16 core<br>memory                                        |                         |                          | 1.91                   | 1  | 2 quads | 2-395 |

|                 |                  | (standby current)<br>(operating current)                      | 3.0 A<br>7.0 A          | 0.2 A<br>0.6A            |                        |    |         |       |

Table 2-2 Module Specifications (Cont)

\* These ac loads figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

| <br>Option<br>Desig. | Module<br>No(s). | Description                                                      | Power Requ<br>+5 V ± 5% | uirements<br>+12 V ± 3 % | Bus Loads<br>AC (Max) | DC | Size   | Page  |

|----------------------|------------------|------------------------------------------------------------------|-------------------------|--------------------------|-----------------------|----|--------|-------|

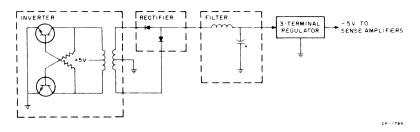

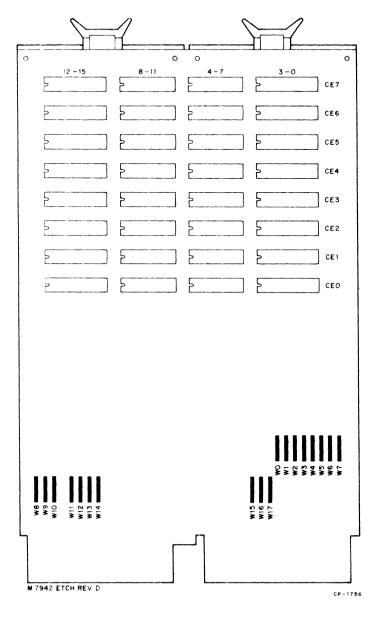

| <br>MRV11-AA         | M7942            | 4K X 16 read-only<br>memory (less<br>PROM integrated<br>circuits | 0.4 A                   | -                        | 1.8                   | 1  | Double | 2-413 |

|                      |                  | (with 32 512 X 4<br>PROM integrated<br>circuits)<br>(MRV11-AC)   | 2.8 A                   |                          |                       |    |        |       |

| MRV11-BA             | M8021            | UV PROM-<br>RAM (less PROM<br>integrated circuits)               | 0.58 A                  | 0.34 A                   | 2.8                   | 1  | Double | 2-425 |

|                      |                  | (with 8 1K X 8<br>PROM integrated<br>circuits)<br>(MRV11-BC)     | 0.62 A                  | 0.5 A                    |                       |    |        |       |

Table 2-2 Module Specifications

\*These ac loads figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

| Option<br>Desig. | Module<br>No(s). | Description                                        | Power Req<br>+5 V ± 5% | uirements<br>+12 V ± 3 % | Bus Loads*<br>AC (Max) |   | Size   | Page  |

|------------------|------------------|----------------------------------------------------|------------------------|--------------------------|------------------------|---|--------|-------|

| <br>MSV11-B      | M7944            | 4K X 16 read/write<br>MOS memory                   | 0.6 A                  | 0.54 A                   | 1.9                    | 1 | Double | 2-441 |

| MSV11-CD         | M7955-YD         | 16K X 16 read/write<br>MOS memory                  | 1.1 A                  | 0.54 A                   | 2.3                    | 1 | Quad   | 2-447 |

| MSV11-D          | M8044            | 4K/16K/32K<br>MOS memory                           | 1.7 A                  | 0. <b>34</b> A           | 2.0                    | 1 | Double | 2-471 |

| MSV11-E          | M8045            | 4K/16K/32K<br>MOS memory                           | 2.0 A                  | 0.41 A                   | 2.0                    | 1 | Double | 2-471 |

| REV11-A          | M9400-YA         | 120 Ω terminator,<br>DMA refresh,<br>bootstrap ROM | 1.6 A                  | -                        | 2.2                    | 1 | Double | 2.491 |

| REV11-C          | M9400-YC         | DMA refresh,<br>bootstrap ROM                      | 1.6 A                  | -                        | 2.2                    | 1 | Double | 2-491 |

Table 2-2 Module Specifications (Cont)

\*These ac loads figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 pF/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

| Option<br>Desig. | Module<br>No(s). | Description                       | Power Requ<br>+5 V ± 5% | uirements<br>+12 V ± 3 % | Bus Loads<br>AC (Max) | DC | Size    | Page  |

|------------------|------------------|-----------------------------------|-------------------------|--------------------------|-----------------------|----|---------|-------|

| RKV11-D          | M7269            | LSI-11 bus control<br>for RKV11-D | 1.8 A                   | -                        | 1.9                   | 1  | Double  | 2-509 |

| RLV11            | M8013<br>M8014   | RLO1 disk<br>drive                | 6.5 A                   | 1.0 A                    | 3.2                   | 1  | 2 quads | 2-545 |

| RXV11-A          | M7946            | RX01 interface                    | 1.5 A                   |                          | 1.8                   | 1  | Double  | 2-575 |

| TEV11            | M9400-YB         | 120 $\Omega$ terminator           | 0.5 A                   |                          | 0                     | 0  | Double  | 2-605 |

Table 2-2 Module Specifications (Cont)

\*These ac loads figures were measured using standard TDR (time domain reflectometry) techniques. The conversion factor is 9.35 p.F/ac load. These numbers are nominal values which will tend to vary from module to module due to normal tolerances of components used in the manufacturing of the product.

2. The module number is the number assigned to the interface modules that are connected to the LSI-11 bus. This number is printed on the module handle and can be used as a quick reference to determine what specific options are installed in any system. The module numbers are listed numerically in Table 2-3 so that the user can identify the options installed by using the module numbers.

| Module   | Option   | Description                                       |

|----------|----------|---------------------------------------------------|

| A012     | ADV11-A  | 16-Channel, 12-Bit A/D Converter                  |

| A6001    | AAV11-A  | 4-Channel, 12-Bit D/A Converter                   |

| G653     | MMV11-A  | 4K X 16-Bit Core Memory                           |

| H223     | MMV11-A  | 4K X 16-Bit Core Memory                           |

| M7269    | RKV11-D  | RK05 Disk Drive Option                            |

| M7940    | DLV11    | Serial Line Unit Interface                        |

| M7941    | DRV11    | Parallel Line Unit Interface                      |

| M7942    | MRV11-AA | 4K X 16-Bit Read-Only Memory<br>(Less PROMs)      |

| M7944    | MSV11-B  | $4K \times 16$ -Bit Read/Write MOS<br>Memory      |

| M7946    | RXV11-A  | Floppy Disk Drive Option                          |

| M7948    | DRV11-P  | Foundation Module                                 |

| M7949    | LAV11    | LA180 Line Printer Option                         |

| M7950    | DRV11-B  | DMA Interface                                     |

| M7951    | DUV11-DA | Synchronous Serial Line Interface                 |

| M7952    | KWV11-A  | Programmable Real-Time Clock                      |

| M7954    | IBV11-A  | Instrument Bus Interface                          |

| M7955-YD | MSV11-CD | 16K × 16-Bit Read/Write MOS<br>Memory             |

| M7957    | DZV11-A  | Asynchronous Line Interface                       |

| M8012    | BDV11    | Bootstrap, Diagnostic, and<br>Terminator          |

| M8013    | RLV11    | RL01 Disk Drive Option                            |

| M8014    | RLV11    | RL01 Disk Drive Option                            |

| M8016    | KPV11-A  | Power-Fail/Line-Time Clock                        |

| M8016-YB | KPV11-B  | Power-Fail/Line-Time Clock/120-<br>Ohm Terminator |

| M8016-YC | KPV11-C  | Power-Fail/Line-Time Clock/220-<br>Ohm Terminator |

| M8017    | DLV11-E  | Asynchronous Line Interface                       |

| M8021    | MRV11-BA | UV PROM/RAM (Less<br>PROMs)                       |

| M8027    | LPV11    | LA180/LP05 Printer Option                         |

| M8028    | DLV11-F  | Asynchronous Line Interface                       |

| M8043    | DLV11-J  | Four Asynchronous Line Interfaces                 |

Table 2-3 Module Identification Numbers

| Module   | Option  | Description                          |

|----------|---------|--------------------------------------|

| M8044    | MSV11-D | 4K, 8K, 16K, 32K MOS Memory          |

| M8045    | MSV11-E | 4K, 8K, 16K, 32K MOS Memory          |

| M9400-YA | REV11-A | DMA Refresh/Bootstrap ROM/120-       |

| M9400-YB | TEV11   | Ohm Terminator<br>120-Ohm Terminator |

| M9400-YC | REV11-C | DMA Refresh/Bootstrap ROM            |

Table 2-3 Module Identification Numbers (Cont)

- 3. The module description identifies the category of the option.

- 4. The power requirements specify the power used by the option when connected to the bus backplane. These requirements are used to determine the total power supply loading within a single system as described in Chapter 4.

- 5. The bus loads for ac and dc loading are provided so that the user can calculate the total ac and dc loading for any system. Complete details for the backplane requirements are contained in Chapter 4.

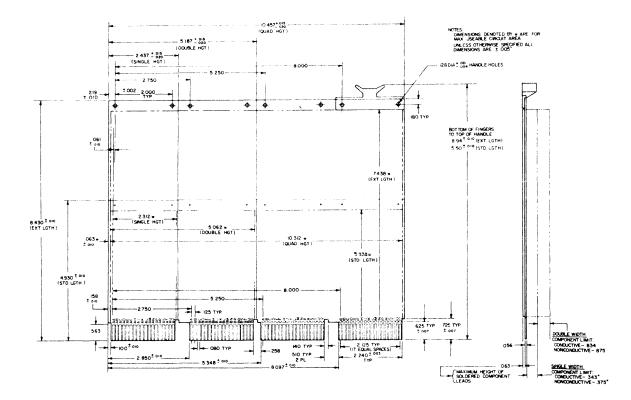

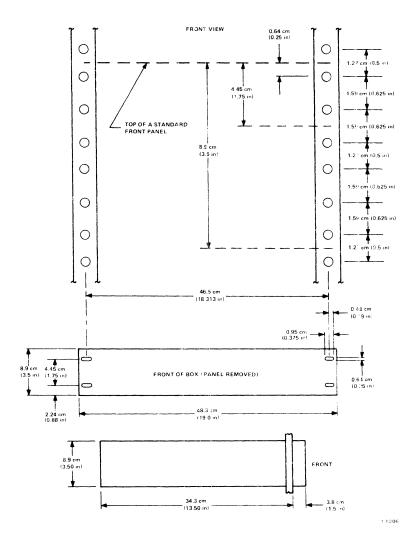

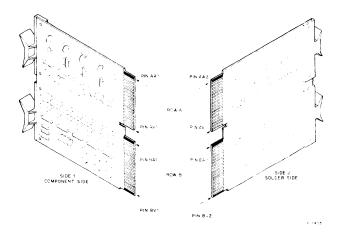

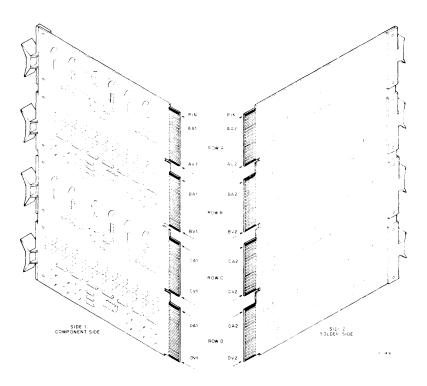

- 6. The interface modules are standardized as either a double or a quad and all are extended length. The double size module is 13.2 cm (5.2 in) high, 22.8 cm (8.9 in) long, and 1.27 cm (0.5 in) wide. The quad size module is 26.5 cm (10.5 in) high, 22.8 cm (8.9 in) long, and 1.27 cm (0.5 in) wide (Figure 2-1).

#### CONFIGURATION

The LSI-11 bus permits a unified addressing structure in which control/status and data registers for peripheral devices are directly addressed as memory locations. All operations on these registers, such as transferring information to or from them or manipulating data within them, are performed by normal memory address instructions. The use of memory address instructions on peripheral device registers greatly increases the flexibility of input/output communications.

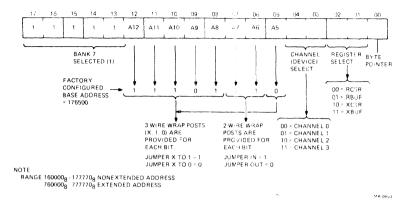

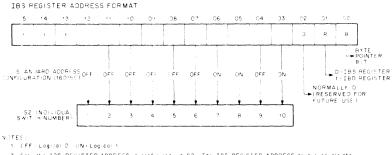

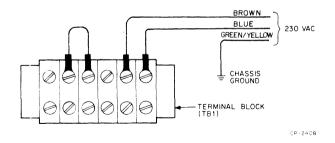

#### Addresses

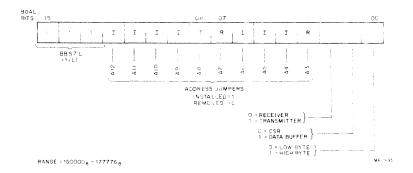

All the options except memories have at least one control and status register and may have several data registers. Each register is assigned an address through which the option can communicate with the processor. The upper 4K of memory address space is reserved for the processor and external input/output (I/O) registers. The user can select any address (Appendix A) in the range of 160000 through 177776 and assign it to the option interface module. The modules are configured to the desired address by selecting dip switches, connecting or disconnecting wirewrap pins, or installing or removing wired jumpers on the module.

Figure 2-1 Module Dimensions

2-11

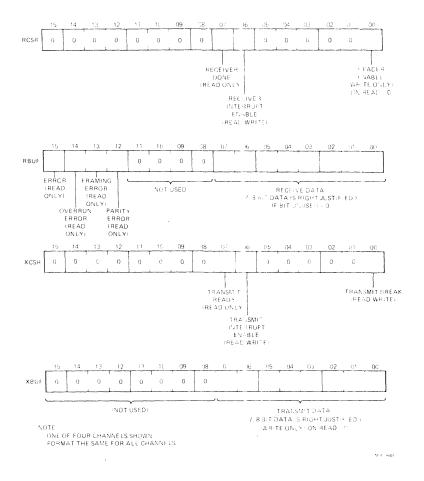

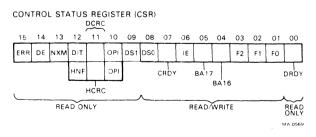

#### **Control and Status Registers**

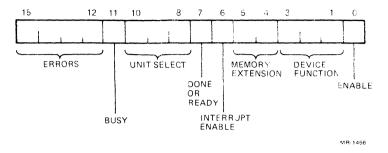

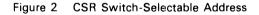

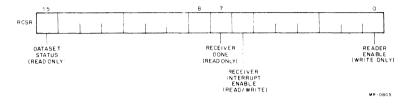

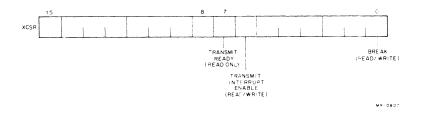

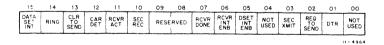

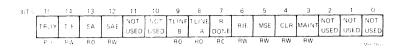

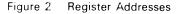

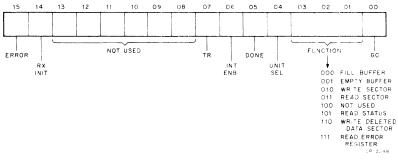

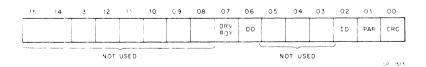

The general form for the control and status registers, shown in Figure 2-2, does not necessarily apply to every device, but is presented as a guide

Figure 2-2 Controls and Status Register

Many devices require less than 16 status bits. Other devices will require more than 16 bits and therefore will require additional status and control registers.

The bits in the control and status registers are generally assigned as described in Table 2-4.

| Bit   | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Errors | Generally there is an individual bit<br>associated with a specific error.<br>When more bits are required for<br>errors, they can be obtained by ex-<br>panding the error section in the<br>word or by using another status<br>word. Generally bit 15 is the in-<br>clusive-OR of all other error bits (if<br>there is more than cne). Most de-<br>vices will have "hard" error condi-<br>tions which will cause an interrupt if<br>bit 6 is set. Some may also have<br>"soft" errors (warning types) which<br>do not cause immediate interrupts. |

| Table | 2-4 | Typical  | Control | and | Status | Register |

|-------|-----|----------|---------|-----|--------|----------|

| 10010 |     | , ypioai | 0011101 | and | otatao | negiotoi |

| Bit  | Name                 | Function                                                                                                                                                                                                                                                                |

|------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | Busy                 | Set to indicate that a device oper-<br>ation is being performed.                                                                                                                                                                                                        |

| 10-8 | Unit Select          | Some peripheral systems have more<br>than one device per control. For<br>example, a disk system can have<br>multiple surfaces per control and an<br>analog-to-digital converter can have<br>multiple channels. The unit bits se-<br>lect the proper surface or channel. |

| 7    | Done or Ready        | The register can contain a done bit,<br>a ready bit or a done-busy pair of<br>bits, depending on the device. These<br>bits are set and cleared by the pe-<br>ripheral device, but may be queried<br>by the program to determine the<br>availability of the device.      |

| 6    | Interrupt Enable     | Set by the program to allow an interrupt to occur as a result of a function done or error condition.                                                                                                                                                                    |

| 5–4  | Memory Extension     | Allows devices to use a full 18 bits to specify addresses on the bus.                                                                                                                                                                                                   |

| 3–1  | Device Function Bits | Specifies the operation that a device is to perform.                                                                                                                                                                                                                    |

| 0    | Enable               | Set to enable the device to perform an operation.                                                                                                                                                                                                                       |

Table 2-4 Typical Control and Status Register (Cont)

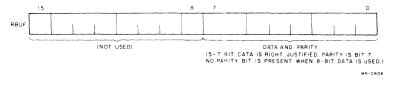

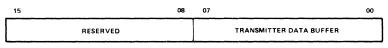

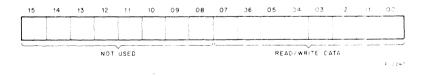

#### **Data Buffer Registers**

The data buffer register is used for temporarily storing data to be transferred into or out of the computer. The number and type of data registers is a function of the device.

#### Interrupts

Interrupts are requests, made by peripheral devices, which cause the processor to temporarily suspend its present (background) program execution to service the requesting device. Each device that is capable of requesting an interrupt must have a user-supplied service routine that is automatically entered when the processor acknowledges the interrupt

request. After completing the service routine execution, program control is returned to the interrupted program. This type of operation is especially useful for the slower peripheral devices.

A device can interrupt the processor only when interrupts are enabled and services interrupts only when the appropriate PSW bits are cleared. Device priority is highest for devices electrically closest to the processor along the bus. Any device that can interrupt the processor can also interrupt the service routine execution of a lower priority device if the processor's priority is set during that execution; hence, interrupt nesting to any level is possible with this interrupt structure. Each device normally contains a control/status register (CSR), which includes an interrupt enable bit. A program must set this bit before an interrupt can be generated by the device.

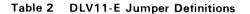

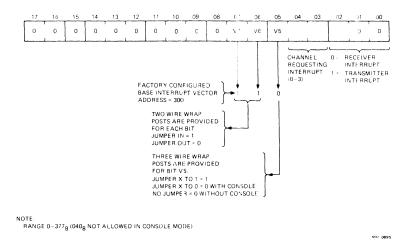

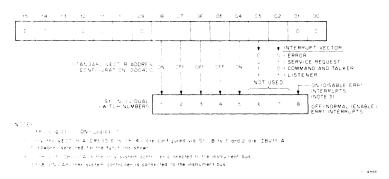

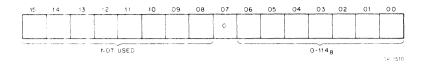

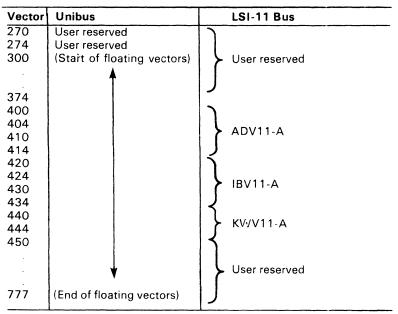

#### Interrupt Vectors

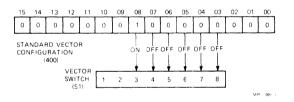

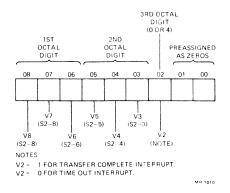

An interrupt vector associated with each device is hard-wired into the device's interface/control logic. This vector is an address pointer that is transmitted to the processor during the interrupt acknowledge sequence, allowing automatic entry into the service routine without device polling. The user can select an interrupt vector from within the range of 000 to 777 for any interrupting options. The module can be configured to the desired interrupt vector by either selecting dip switches, connecting or disconnecting wire-wrap pins, or installing or removing wired jumpers on the module.

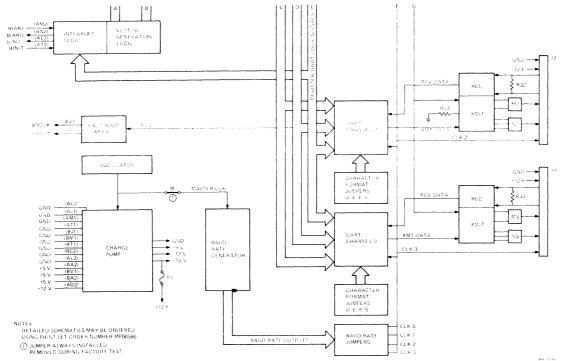

#### FUNCTIONAL DESCRIPTION

The functional description is provided for all the options in order to assist the user in understanding the theory of operation.

#### CATEGORIES

The LSI-11 bus peripherals and options are classified into general categories that pertain to their performance and function. This listing indicates the wide span of equipment capability available to the user.

#### **Interface Options**

AAV11-A The AAV11-A is a 4-channel, 12-bit digital-to-analog converter module that includes control and interfacing circuits. It has four D/A converters, a dc-dc converter that provides power to the analog circuits, and a precision voltage reference. Each channel has its own holding register that can be addressed separately and provides 12 bits of resolution. Bits 0, 1, 2, and 3 of the fourth holding register are brought out to the I/O connector so that they can be used as a 4-bit digital output register.

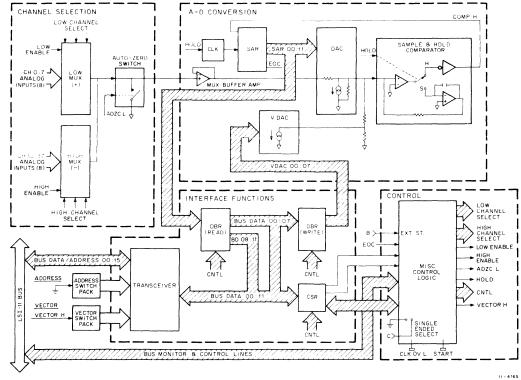

ADV11-A The ADV11-A is a 12-bit successive approximation analog-to-digital converter that samples analog data at specified rates and stores the digital equivalent value for processing. The multiplexer can accommodate up to 16 single-ended or 8 quasi-differential inputs. The converter uses a patented auto-zeroing design that measures the sampled data with respect to its own offset and therefore cancels out its own offset error.

> External event inputs can originate at the user's equipment or from the Schmitt trigger output of the KWV11-A clock. Three reference signals are provided for self-testing any channel input. These signals consist of two dc levels and one bipolar triangular waveform. This output can be used with DIGITAL diagnostic software to produce a data base for extremely precise analog linearity testing.

- DRV11 The DRV11 is a parallel interface module that is used to interconnect the LSI-11 bus with general-purpose, parallel line, TTL or DTL devices. It allows program-controlled data transfers at rates up to 40K words per second and uses LSI-11 bus interface and control logic to generate interrupts and process vector handling. The data is handled by 16 diode-clamped input lines and 16 latched output lines. There are two 40-pin connectors on the module for user interface applications.

- DRV11-B The DRV11-B is an interface module that uses direct memory access (DMA) to transfer data directly between the system memory and an I/O device. The interface is programmed by the processor to move variable length blocks of 8- or 16-bit data words to or from specified locations in the system memory. Once programmed, there is no processor intervention required. The module can transfer up to 250K 16-bit words per second in the single-cycle mode and up to 500K 16-bit words per second in the burst mode. It also allows read-modify-restore operations.

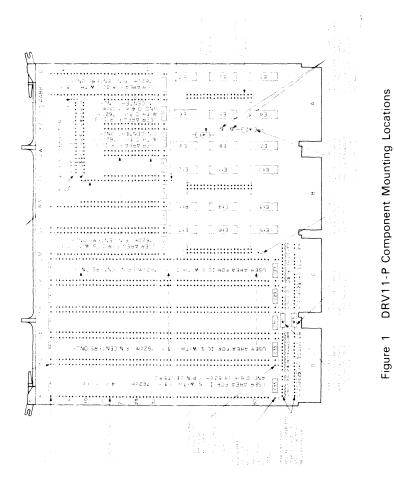

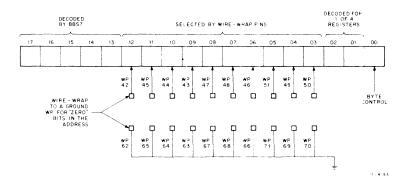

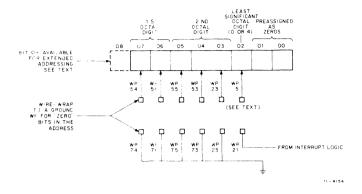

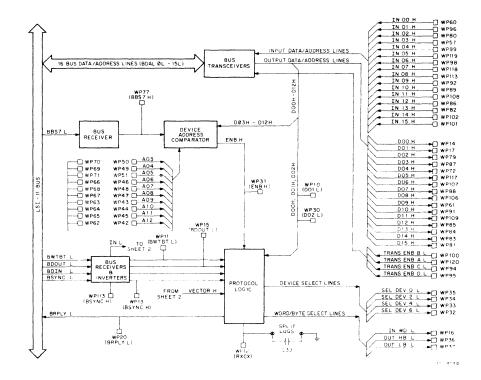

- DRV11-P The DRV11-P is a foundation wire-wrap interface module with a 40-pin I/O connector. Approximately 25 percent of the module is occupied by bus transceivers, interrupt vector generation logic, device comparator logic, protocol logic, and interrupt logic. The remaining 75 percent is for user applications; this portion has plated-through holes for securing ICs and wire-wrap pins for interconnecting the user's circuits. The plated-through holes can accept 6-, 8-, 14-, 16-, 18-, 20-, 22-, 24-, and 40-pin dual-inline integrated circuits or discrete components.

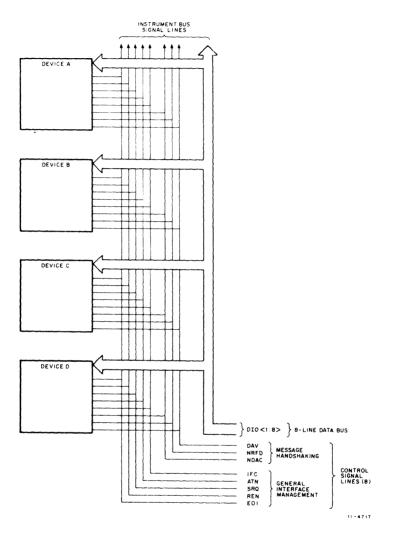

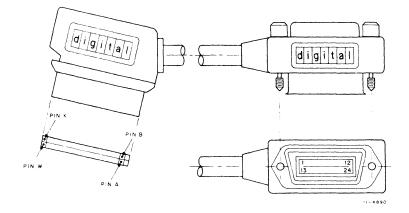

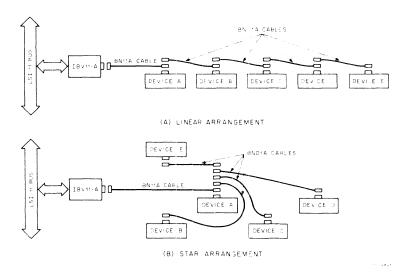

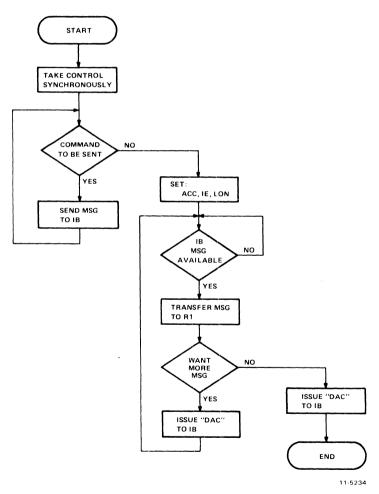

- IBV11-A The IBV11-A is an interface module that interconnects the LSI-11 bus with the instrument bus described in IEEE standard 488-1975, "Digital Interface for Programmable Instrumentation." The IBV11-A makes a processor-controlled programmable instrument system possible. The module can accommodate up to 15 IEEE-488 devices and is PDP-11 software-compatible.

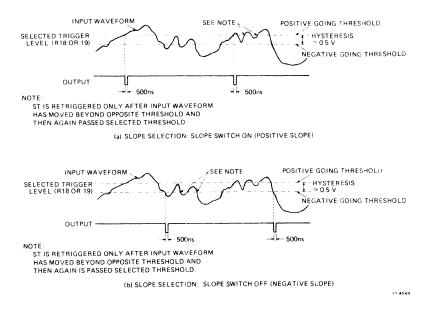

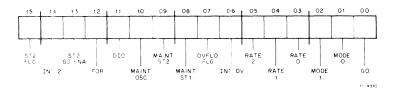

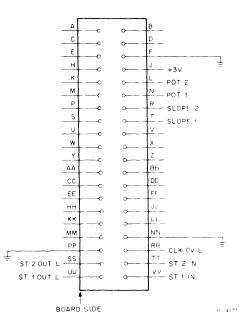

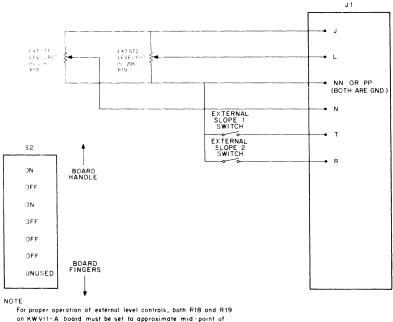

- KWV11-A The KWV11-A is a programmable real-time clock/ counter that provides a means of determining time intervals or counting events. It can be used to generate interrupts to the processor at predetermined intervals or establish timing between input and output events. It can also initialize the ADV11-A analog-to-digital converter by a clock counter overflow or by firing a Schmitt trigger. The clock counter has a resolution of 16 bits and can be driven by any one of five crystal-controlled frequencies (100 Hz to 1 MHz), from a line frequency input, or from a Schmitt trigger fired by an external input. The module can operate in any of four programmable modes: single interval, repeated interval, external event timing, and external event timing from zero base.

#### **Communications Options**

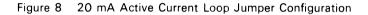

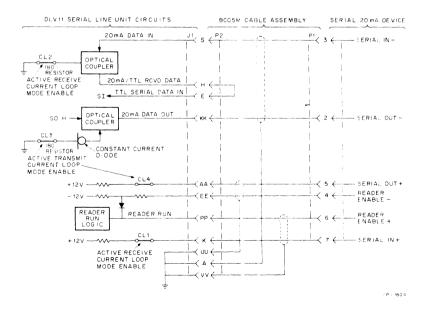

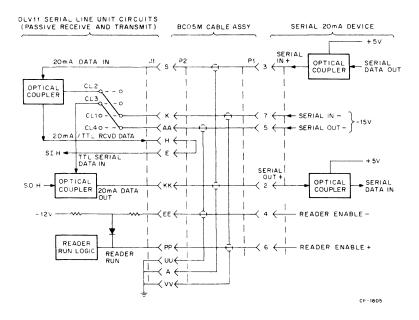

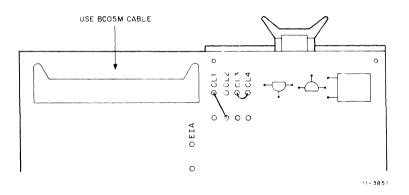

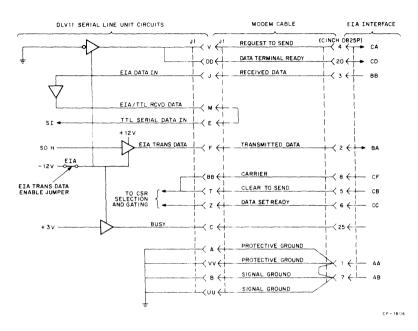

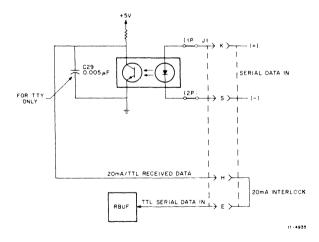

- DLV11 The DLV11 is a serial line unit (SLU) that interfaces with asynchronous serial I/O devices. The module has jumperselectable baud rates (50–9600) and serial word format that includes the number of stop bits, number of data bits, and even, odd, or no parity bit. The DLV11 can support 20 mA current loop interfaces or EIA "data leads only" interfaces.

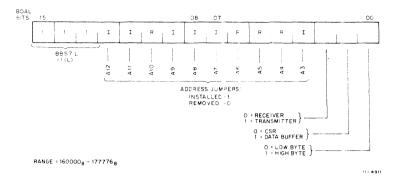

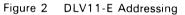

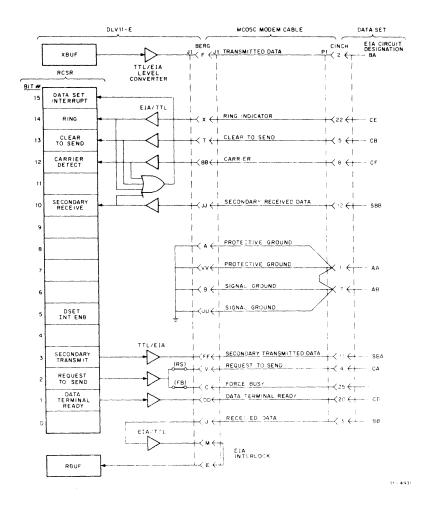

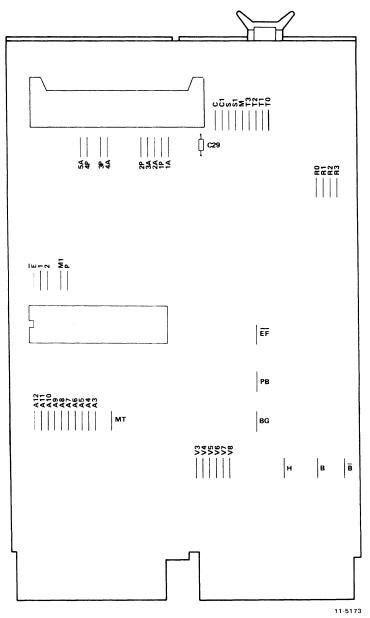

- DLV11-E The DLV11-E is an asynchronous line interface module that interconnects the LSI-11 bus to standard serial communications lines. The module receives serial data, converts it to parallel data, and transfers it to the LSI-11 bus. Also, it accepts parallel data from the LSI-11 bus, converts it to serial data, and transmits it to the peripheral device. The module has jumper-selectable or softwareselectable baud rates (50–19200), and jumper-selectable stop bit and data bit formats. The DLV11-E offers full modem control for EIA/CCITT interfaces.

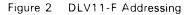

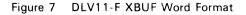

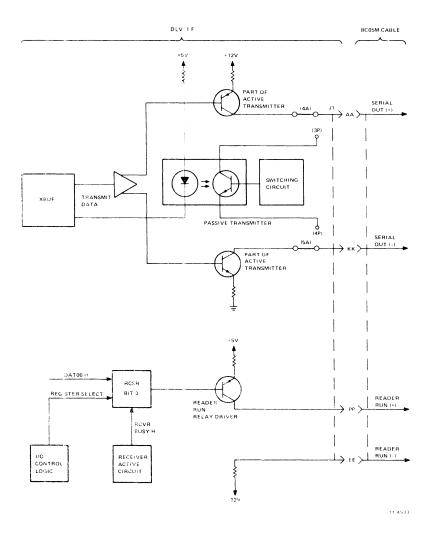

- DLV11-F The DLV11-F is an asynchronous line interface module that interconnects the LSI-11 bus to several types of standard serial communications lines. The module receives serial data, converts it to parallel data, and transfers it to the LSI-11 bus. It also accepts parallel data from the LSI-11 bus, converts it to serial data, and transmits it

to the peripheral device. The module has jumper-selectable or software-selectable baud rates (50–19200) and jumper-selectable stop bits and data bits. The DLV11-F supports either 20 mA current loop or EIA standard lines, but does not include modem control.

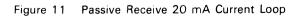

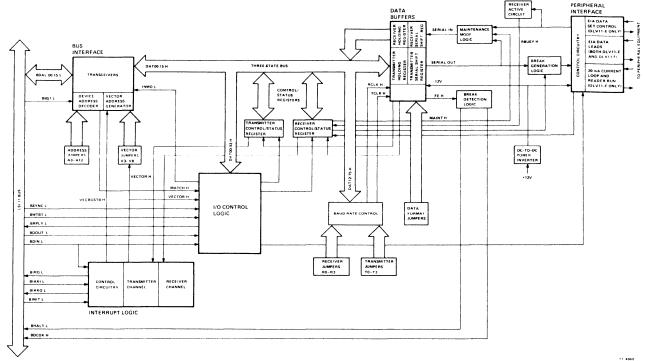

- DLV11-J The DLV11-J contains four independent asynchronous serial line channels used to interface peripheral devices to the LSI-11 bus. Each channel transmits and receives data from the peripheral device over EIA data leads (lines that do not use a control line). The module can be used with 20 mA current loop devices if a DUV11-KA adpater is used. The DLV11-J has jumper-selectable baud rates from 150 to 38.4K baud.

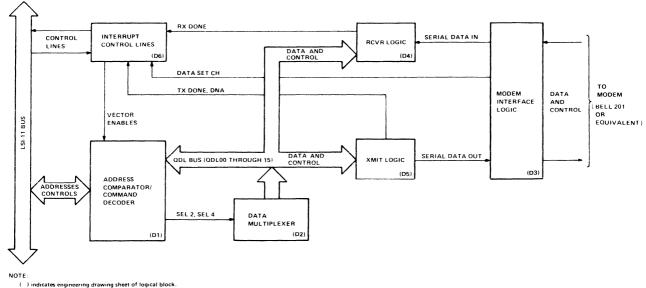

- DUV11 The DUV11 synchronous line interface module establishes a data communication line between the LSI-11 bus and a Bell 201 synchronous modem or equivalent. The module is fully programmable with respect to sync characters, character length (5 to 8 bits), and parity selection. The receiver logic accepts serial data from the modem and converts it to parallel data for the LSI-11 bus. The transmitter logic converts the parallel LSI-11 bus data into serial data for the transmission line. The interface logic converts the TTL logic levels to the EIA voltage levels required by the Bell 201 modems and also controls the modem for half-duplex or full-duplex.

- DZV11 The DZV11 is an asynchronous multiplexer interface module that interconnects the LSI-11 bus with up to four asynchronous serial data communications channels. The module provides EIA interface voltage levels and data set control to permit dial-up (auto-answer) operations with full-duplex modems such as Bell models 103, 113, 212, or equivalent. The DZV11 does not support half-duplex operations or the secondary transmit and receive operations available in some modems such as Bell 202. The DZV11 has applications in data concentration and collection systems where front-end systems interface to a host computer and for use in a cluster controller for terminal applications.

#### **Expansion Memories**

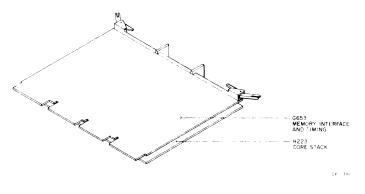

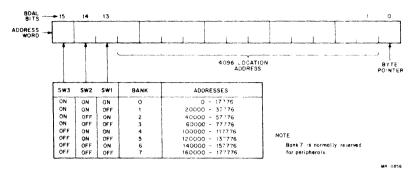

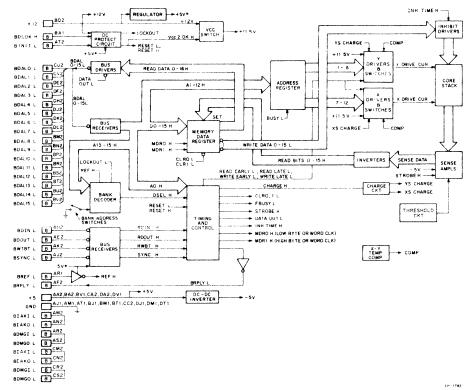

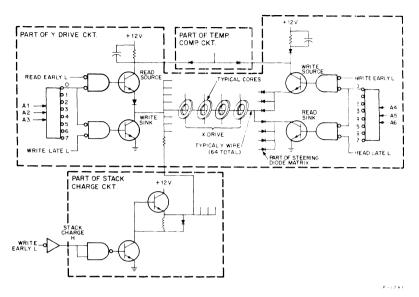

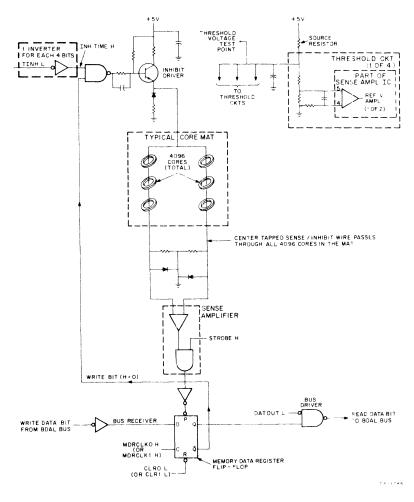

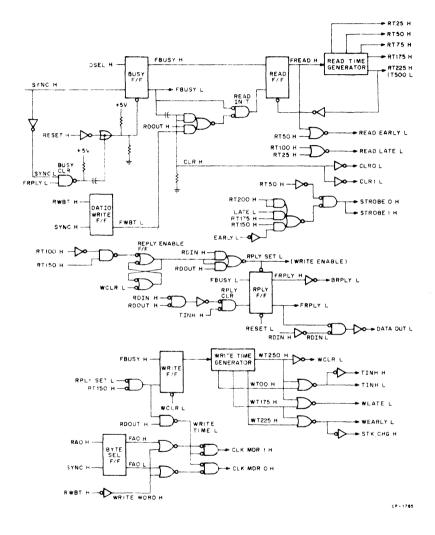

MMV11-A The MMV11-A is a 4K by 16-bit core memory option that provides nonvolatile read/write storage. The memory can be configured by bank addressing switches. The module is limited to LSI-11 bus backplanes that contain the LSI-11 bus in both the A/B and the C/D slots.

- MRV11-AA The MRV11-AA is a read-only memory module on which the user can install fusible link, programmable, read-only memory (PROM) chips or masked read-only memory (ROM) chips. The user selects the address space of the memory by configuring removable jumper wires.

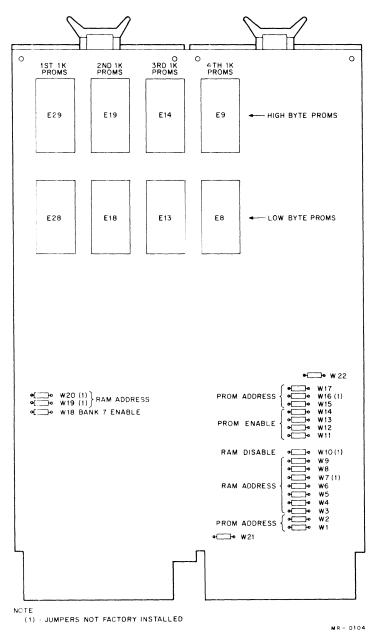

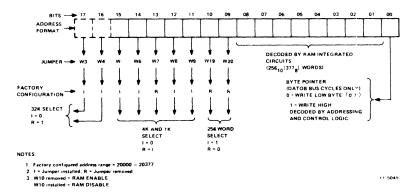

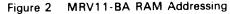

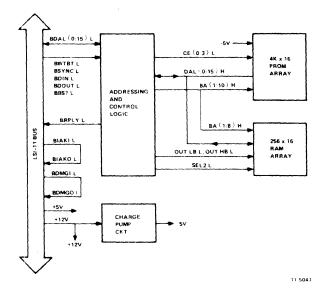

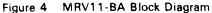

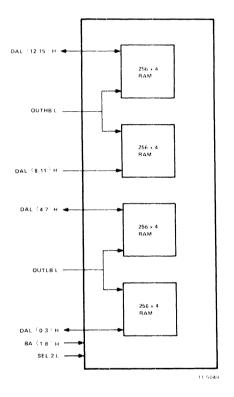

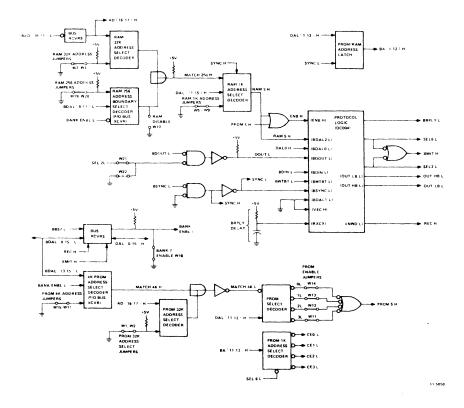

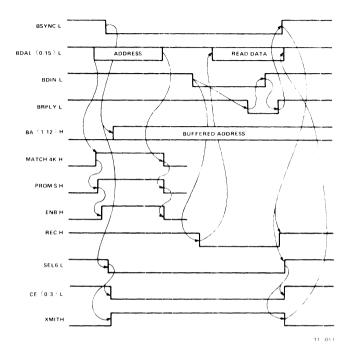

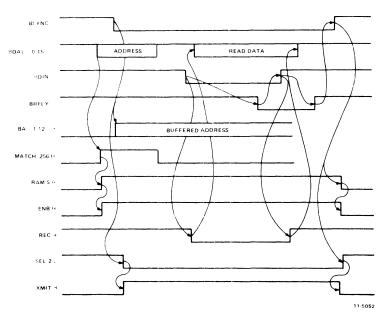

- MRV11-BA The MRV11-BA is a read-only memory module that uses ultraviolet (UV) erasable, programmable, read-only memory (PROM) integrated circuits. The module also contains a 256 by 16-bit random access memory (RAM) that can be used as a "scratchpad" or "stack" by the system software.

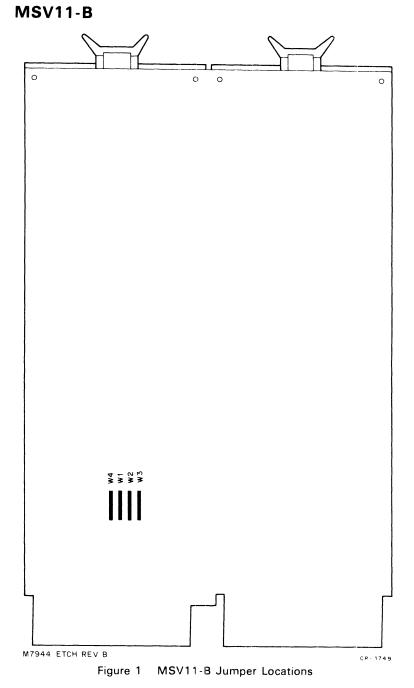

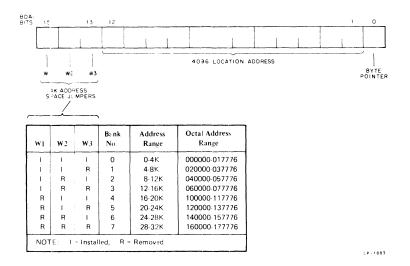

- MSV11-B The MSV11-B is a 4K by 16-bit dynamic MOS read/write memory module. The user can select the memory addresses of the module by configuring removable jumpers. The memory refresh must be controlled by external bus signals.

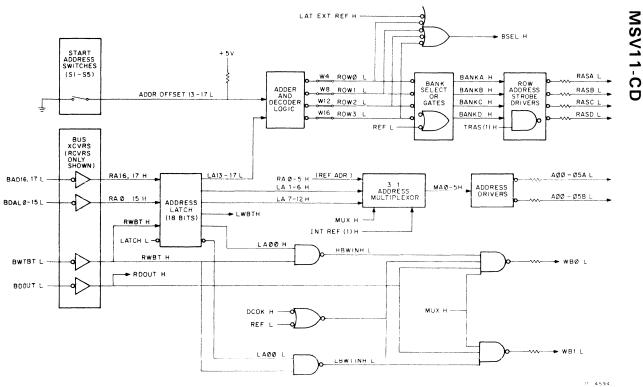

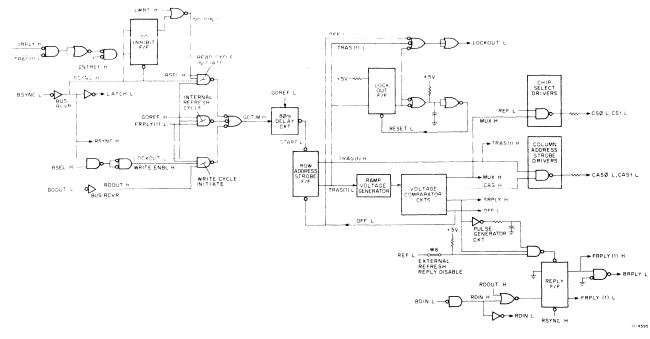

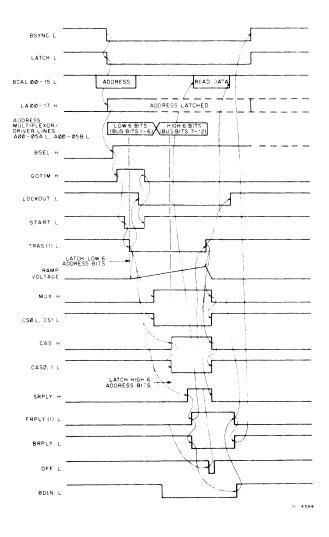

- MSV11-CD The MSV11-CD is a 16K by 16-bit dynamic MOS read/write memory module. Refresh is automatically performed by the module but it can be disabled if the user wishes to use the LSI-11 bus refresh signals. This memory module can be configured to operate in the battery backup mode. The user can configure the memory addresses by selecting switch settings.

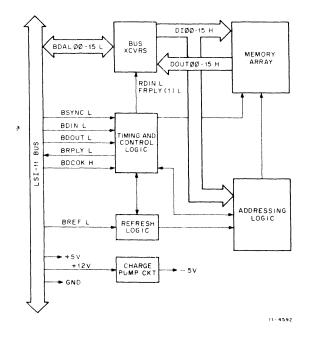

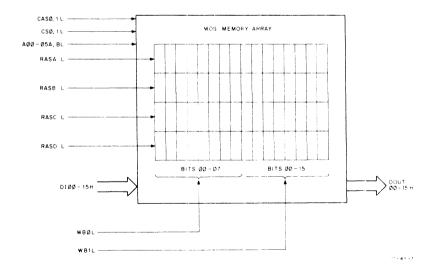

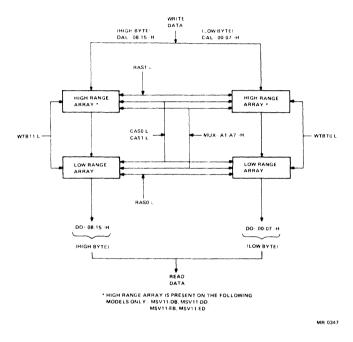

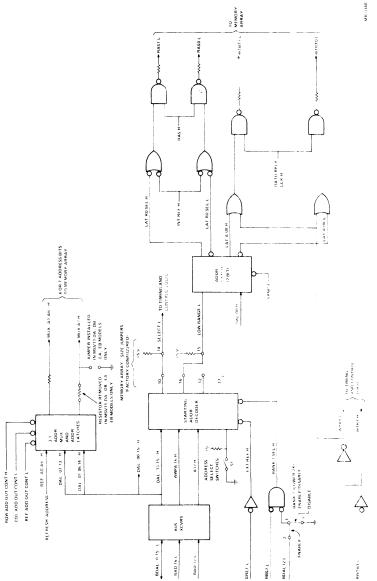

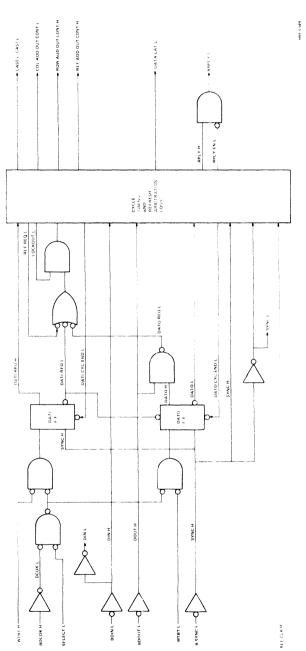

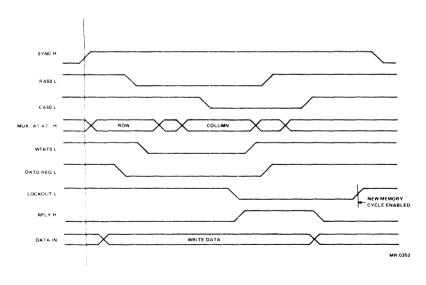

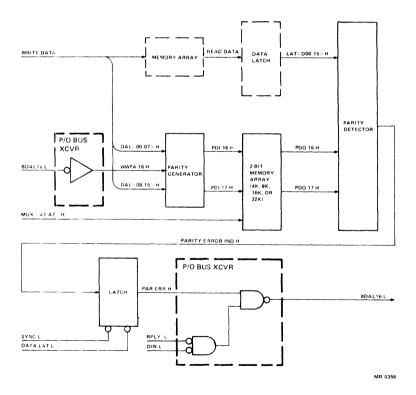

- MSV11-D, -E The MSV11-D module has either 8K, 16K, or 32K by 16 bits of MOS memory. The MSV11-E is the same as the MSV11-D except that it has an 18-bit word that generates and detects byte parity for each word. The modules have an on-board memory refresh and perform the necessary LSI-11 bus cycles. The memory addressing is selectable by the user by configuring switch settings. The module can use a battery backup system to preserve data when primary power is lost.

#### Peripherals

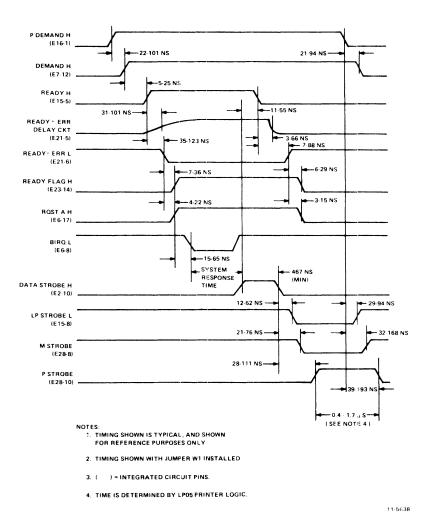

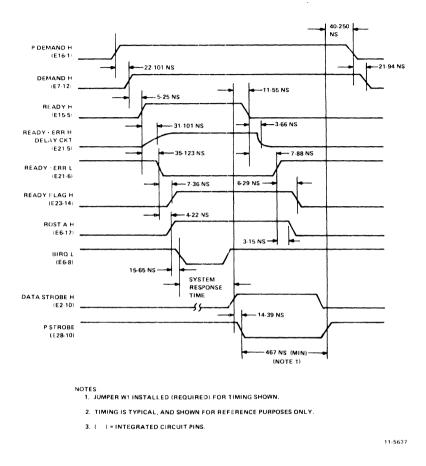

- LAV11 The LAV11 option consists of an LA180 DECprinter, an interface module, and a BC11S-25 interface cable. The interface module provides interconnection between the LA180 DECprinter and the LSI-11 bus. The module outputs ASCII characters to the printer and monitors various printer operations that require operator control.

- LPV11 The LPV11 printer option consists of an interface module, an interface cable, and either an LP05 or LA180 line printer. The interface module provides programmed control of data transfers and provides printer strobe signals

appropriate for either printer. The LA180 DECprinter is a high-speed printer that prints 180 characters per second and the LP05 printer can print 240 or 300 lines per minute, depending on which model is selected.

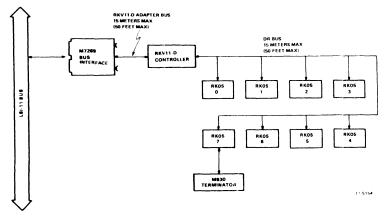

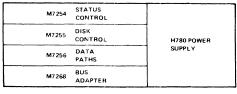

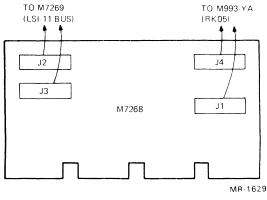

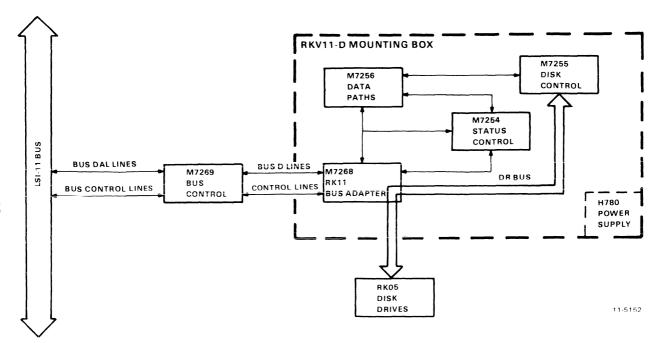

- RKV11-D The RKV11-D option consists of an RK05 disk drive controller, an LSI-11 bus interface module, and an RK05J disk drive. The RK05 disk drive controller can be used with up to eight RK05J disk drive units to form a mass memory storage system that contains up to 21M bytes of storage. The RKV11-D system is block-oriented but is capable of transferring from 1 to 2<sup>16</sup> consecutive data words without reinitiation or processor intervention. The data transfers occur from the RKV11-D to the system memory by direct memory access (DMA) and operate at maximum bus bandwidth. The system can use either RK05J or RK05F disk drives and the controller can be mounted in a standard 48.3 cm (19 in) cabinet.

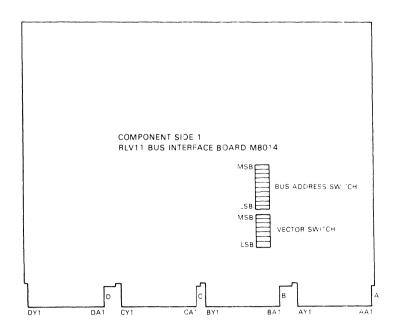

- RLV11 The RLV11 option interfaces the LSI-11 bus with an RLO1 disk drive controller and an RLO1 disk drive assembly. The controller can only be used in an H9273-A type backplane which incorporates on LSI-11 bus in slots A and B, with an interboard bus in slots C and D. The controller can interface up to four RLO1 disk drives for a complete system of 21M bytes of storage. The RLO1 disk drive is a random access, mass storage system that stores data in fixed length blocks on a preformatted disk cartridge. Each drive can store up to 5.24 million bytes. The RLV11 transfers data using direct memory access (DMA) techniques; this allows data transfers without processor intervention and at bus bandwidth speed.

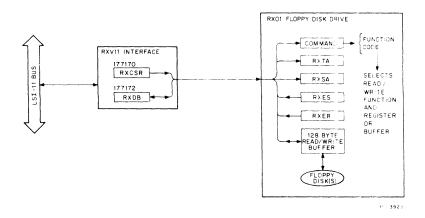

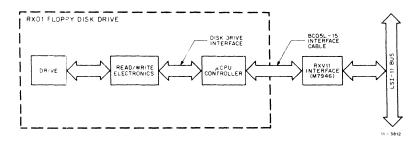

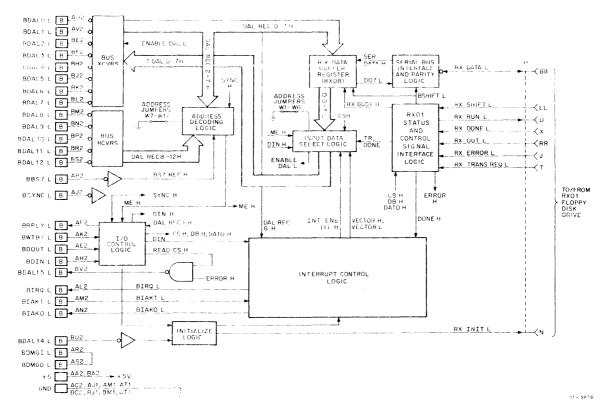

- RXV11 The RXV11 option consists of an interface module, cable assembly, and either a single or dual drive RX01 floppy disk. This option is a random access mass storage device that stores data in fixed-length blocks on a preformatted flexible diskette. Each diskette can store and retrieve up to 256K, 8-bit bytes of data. The RXV11 system is rackmountable in the standard 48.3 cm (19 in) cabinet.

#### **Miscellaneous Options**

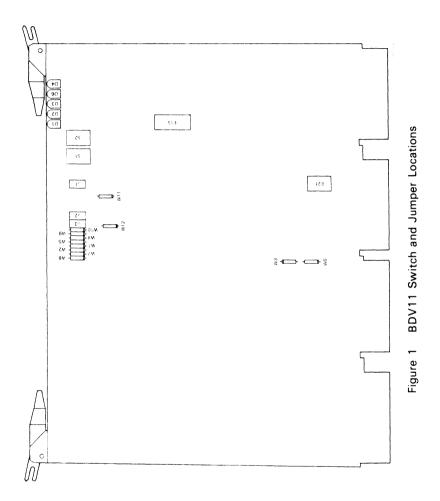

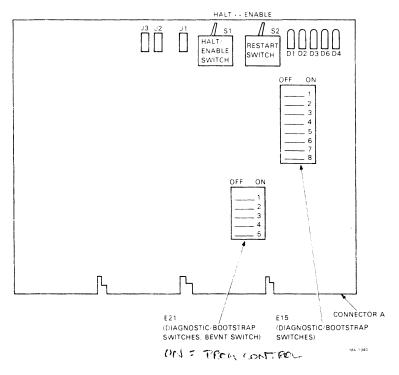

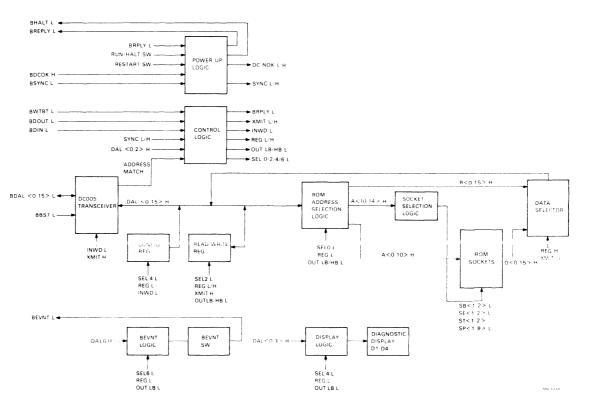

BDV11 The BDV11 module has 2K words of read-only memory (ROM) that contains diagnostic and bootstrap programs. These programs are user-selectable by setting dip switches. The diagnostic programs will test the processor, the memory, and the user's console. The bootstrap programs can boot LSI-11 peripheral devices. The module also has 120-ohm bus termination circuits. The user can add up to 16K words of read-only memory (ROM) and up to 2K words of erasable programmable ROM (EPROM) on the module. This 18K words of additional memory can be used with no increase in the amount of I/O address space.

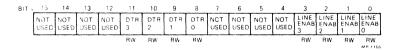

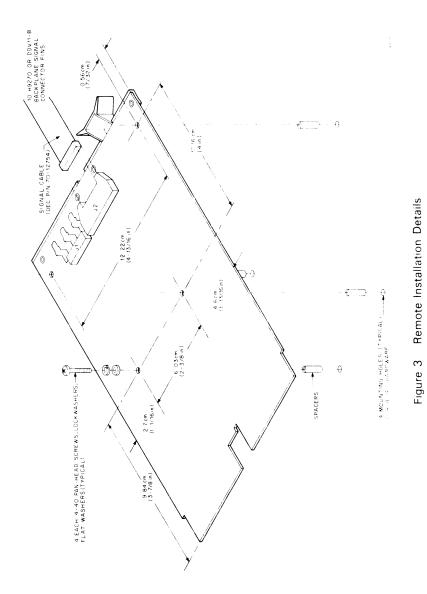

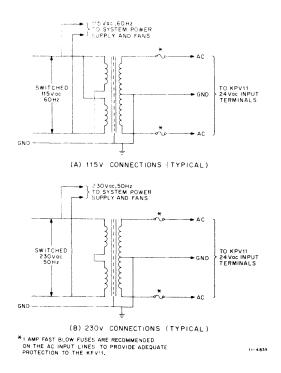

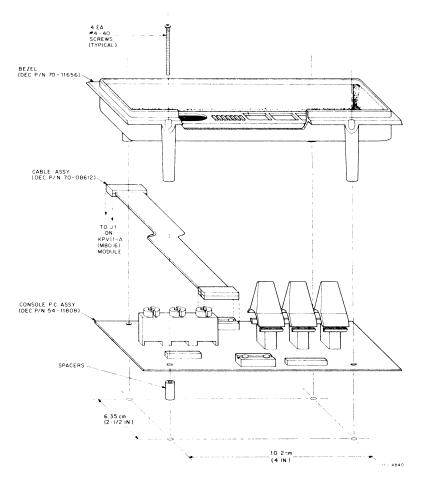

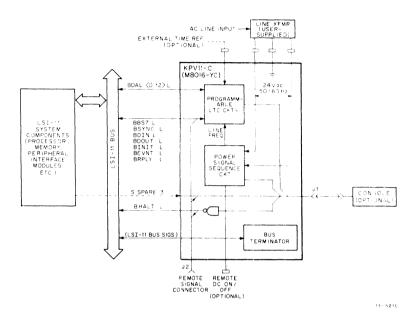

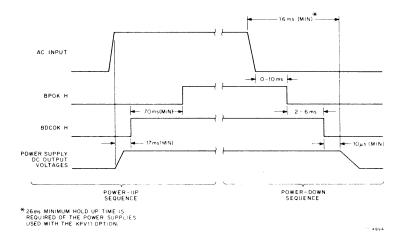

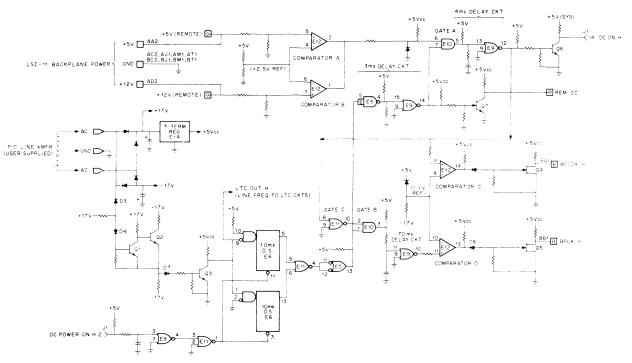

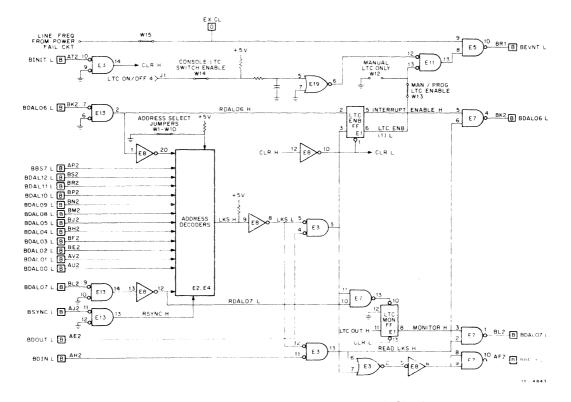

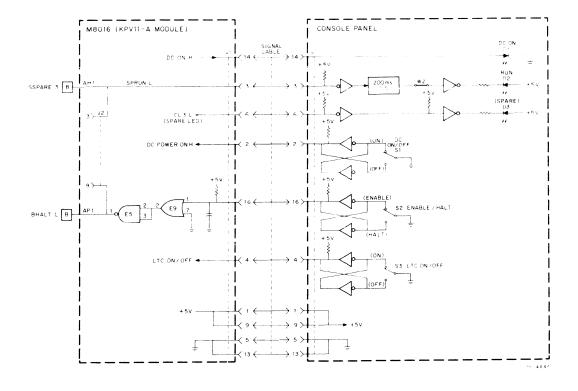

- KPV11-A, -B, The KPV11-A module generates power-up and powerdown sequences, monitors for a power-fail condition, and generates the line-time clock (LTC) function. The KPV11-B is the same as the "A" except that it provides 120-ohm termination circuits. The KPV11-C is the same as the "A" except that it provides 220-ohm termination circuits. The module can be installed on any backplane or remotely installed via an optional cable.

- REV11-A, -C The REV11-C module has a bootstrap ROM and direct memory access (DMA) refresh circuits. The REV11-A is identical to the REV11-C except it has additional 120ohm termination circuits.

- TEV11 The TEV11 is a bus terminator module that provides 120-ohm bus termination circuits.

## AAV11-A 4-CHANNEL 12-BIT D/A CONVERTER

#### GENERAL

The AAV11-A is a 4-channel, digital-to-analog converter module that includes control and interfacing circuits. It has four D/A converters, a dcdc converter that provides power to the analog circuits, and a precision voltage reference. Each channel has its own holding register that can be addressed separately and provides 12 bits of resolution. These registers can be written and read, using either word or byte format. In addition, bits 0, 1, 2 and 3 of the fourth holding register are brought out to the I/Oconnector so they can be used as a 4-bit digital output register.

#### FEATURES

- Four 12-bit digital input channels, binary encoded for either unipolar mode or bipolar mode

- Jumper-selected output ranges and modes: Bipolar mode ±2.56 V, ±5.12 V, ±10.24 V Unipolar mode 0 to +5.12 V, 0 to +10.24 V

- One part in 4096 resolution

- 5 V/μs slew rate

- ±5 mA drive capability per converter

#### SPECIFICATIONS

| Identification           | A6001                                                                                    |

|--------------------------|------------------------------------------------------------------------------------------|

| Size                     | Quad                                                                                     |

| Power                    | +5.0 Vdc ± 5% at 1.5 A<br>+12.0 Vdc ± 3% at 0.4 A                                        |

| Bus Loads<br>AC<br>DC    | 1.9<br>1.0                                                                               |

| Resolution               | 12-bits (1 part in 4096)                                                                 |

| Number of D/A converters | 4                                                                                        |

| Digital input            | 12-bits (binary encoded for unipolar<br>mode; offset binary encoded for bipolar<br>mode) |

# AAV11-A

| Digital storage                                    | Read-write, word or byte operable, single buffered                                                    |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Output voltage range<br>(jumper selected)          | $\pm 2.56$ V, $\pm 5.12$ V, $\pm 10.24$ V bipolar, 0 V to $\pm 5.12$ V, 0 V to $\pm 10.24$ V unipolar |

| Gain accuracy                                      | Adjustable (factory set for bipolar $\pm 5.12$ V)                                                     |

| Gain temperature<br>coefficient                    | 10 PPM per °C, max.                                                                                   |

| Offset temperature coefficient                     | 20 PPM of full scale range per °C, max.                                                               |

| Linearity                                          | $\pm$ 1/2 LSB max. non-linearity                                                                      |

| Differential linearity                             | $\pm$ 1/2 LSB, monotonic                                                                              |

| Output impedance                                   | 1 ohm max.                                                                                            |

| Drive capability                                   | $\pm 6$ mA max. per converter                                                                         |

| Slewing speed                                      | 5 V/µs                                                                                                |

| Rise and settling time (to<br>0.1% of final value) | 4 $\mu s$ (8 $\mu s$ with 5000 pF load in parallel with 1 $k\Omega)$                                  |

#### CONFIGURATION

#### General

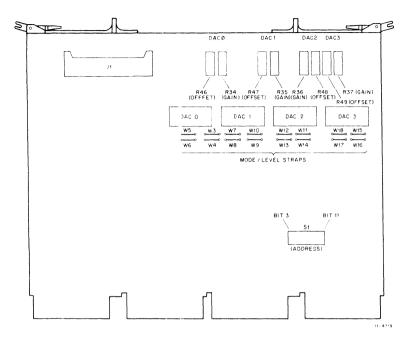

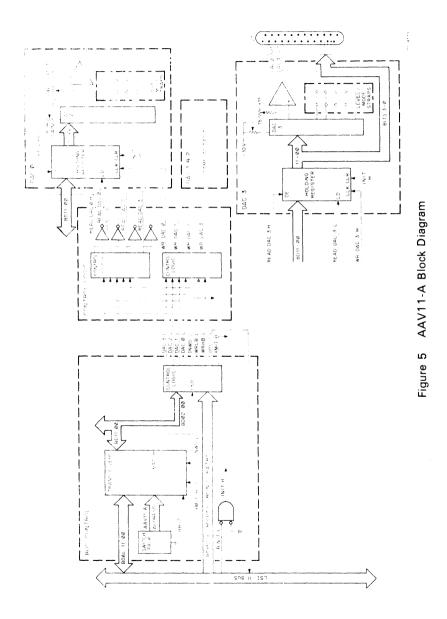

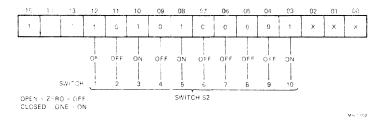

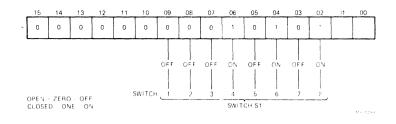

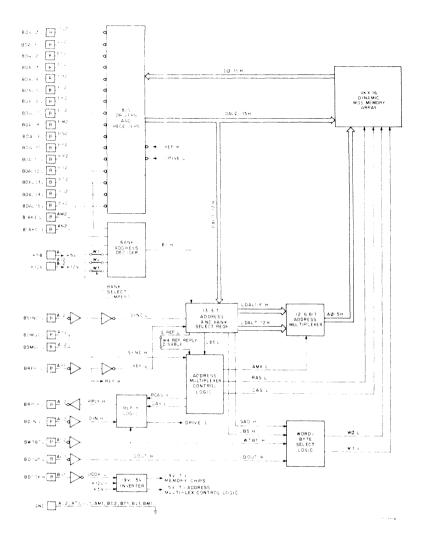

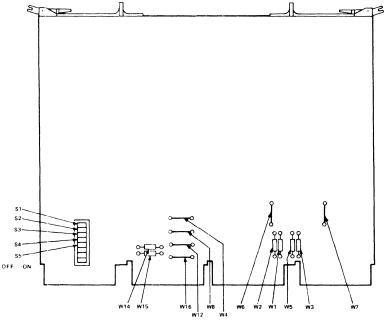

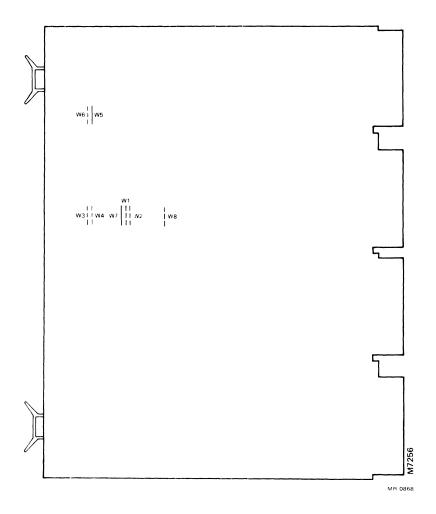

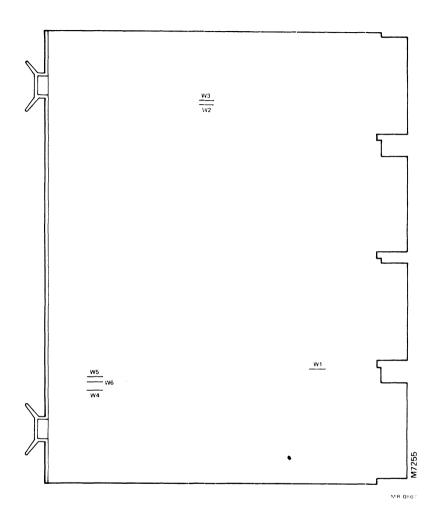

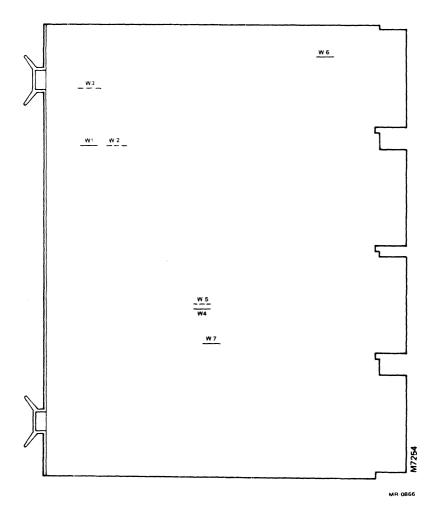

The following paragraphs describe how the user can configure the module so that it will function within his system by setting dip switches (Figure 1) to obtain the desired device address. The voltage range for each D/A converter (DAC 0 – DAC 3) can be independently configured by installing or removing the designated jumpers (Figure 1) associated with a specific D/A converter. Also described in this section is the method of connecting external devices to the module. The standard factory addresses for the registers are listed in Table 1.

| Register  | Mnemonic | Address |  |

|-----------|----------|---------|--|

| Holding 0 | DAC 0    | 170440  |  |

| Holding 1 | DAC 1    | 170442  |  |

| Holding 2 | DAC 2    | 170444  |  |

| Holding 3 | DAC 3    | 170446  |  |

| Table 1 | Standard | Addresses |

|---------|----------|-----------|

|---------|----------|-----------|

# AAV11-A

Figure 1 AAV11-A Connectors, Switches, and Jumpers

#### **Device Registers**

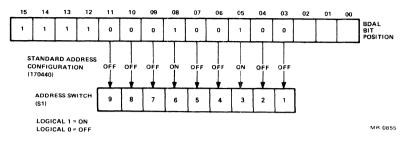

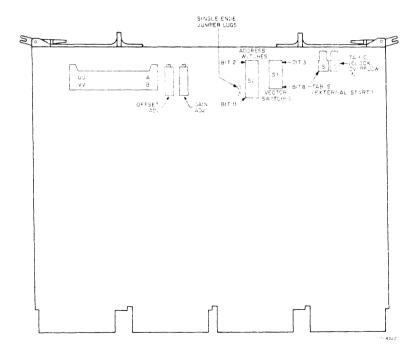

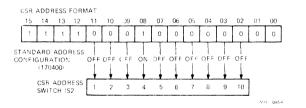

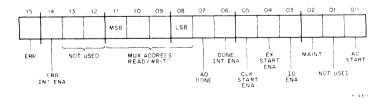

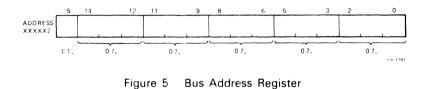

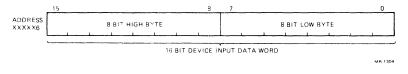

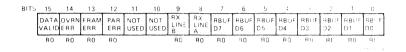

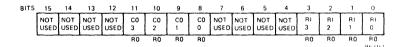

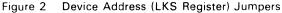

The device registers can be configured to respond to any address within the range 170000 to 177777. Each register address does not have to be individually set. The DAC 0 register address is selectable and the last digit will be zero. The remaining registers will use addresses 17XXX2, 17XXX4, and 17XXX6 for the DAC 1, DAC 2 and DAC 3 registers, respectively. The factory-configured device address is 170440 as shown in Figure 2. The word formats for the DAC registers are described in Table 2. Note that all device registers are always a sequence of four consecutive even locations. There is no vector used for this module.

#### D/A Converter Range and Mode

The range and mode (bipolar or unipolar) voltages can be selected by the user inserting or removing jumpers as shown in Figure 1. Four jumpers are associated with each D/A converter. The module is factory-configured for -5.12 to +5.12 V bipolar operation. The jumper configurations for the bipolar mode ranges are shown in Table 3; the unipolar ranges are shown in Table 4.

# **AAV11-A**

| Bit   | DAC 0, DAC 1, DAC 2 | DAC 3              |

|-------|---------------------|--------------------|

| 15-12 | Not used            | Not used           |

| 11    | Binary 11           | Binary 11          |

| 10    | Binary 10           | Binary 10          |

| 9     | Binary 9            | Binary 9           |

| 8     | Binary 8            | Binary 8           |

| 7     | Binary 7            | Binary 7           |

| 6     | Binary 6            | Binary 6           |

| 5     | Binary 5            | Binary 5           |

| 4     | Binary 4            | Binary 4           |

| 3     | Binary 3            | Binary 3/Control 3 |

| 2     | Binary 2            | Binary 2/Control 2 |

| 1     | Binary 1            | Binary 1/Control 1 |

| 0     | Binary O            | Binary 0/Control 0 |

Table 2 DAC Word Formats

Table 3 Jumper Configurations for Bipolar Operation

|       | ±2.56 V | $\pm 5.12$ V | $\pm 10.24$ V |

|-------|---------|--------------|---------------|

| DAC 1 |         |              |               |

| W3    | IN      | IN           | OUT           |

| W4    | OUT     | OUT          | IN            |

| W5    | IN      | OUT          | OUT           |

| W6    | IN      | IN           | IN            |

| DAC 2 |         |              |               |

| W7    | IN .    | IN           | OUT           |

| W8    | OUT     | OUT          | IN            |

| W9    | IN      | OUT          | OUT           |

| W10   | IN      | IN           | IN            |

|       | ±2.56 V | $\pm$ 5.12 V | ±10.24 V |

|-------|---------|--------------|----------|

| DAC 3 |         |              |          |

| W11   | IN      | IN           | OUT      |

| W12   | OUT     | OUT          | 1N       |

| W13   | IN      | OUT          | OUT      |

| W14   | IN      | IN           | IN       |

| DAC 4 |         |              |          |

| W15   | IN      | IN           | OUT      |

| W16   | OUT     | OUT          | IN       |

| W17   | IN      | OUT          | OUT      |

| W18   | IN      | IN           | IN       |

Table 3 Jumper Configurations for Bipolar Operation (Cont)

Table 4 Jumper Configurations for Unipolar Operation

|             | 0 V — +5.12 V                                                                     | 0 V — +10.24 V |

|-------------|-----------------------------------------------------------------------------------|----------------|

| DAC 1       |                                                                                   |                |

| W3          | IN                                                                                | IN             |

| W4          | OUT                                                                               | OUT            |

| W5          | IN                                                                                | OUT            |

| W6          | OUT                                                                               | OUT            |

| DAC 2       |                                                                                   |                |

| W7          | IN                                                                                | IN             |

| W8          | OUT                                                                               | OUT            |

| W9          | IN                                                                                | OUT            |

| <b>W1</b> 0 | OUT                                                                               | OUT            |

| DAC 3       |                                                                                   |                |

| W11         | IN                                                                                | IN             |

| W12         | OUT                                                                               | OUT            |

| <b>W1</b> 3 | IN                                                                                | OUT            |

| W14         | OUT                                                                               | OUT            |

| DAC 4       |                                                                                   |                |

| W15         | IN                                                                                | IN             |

| W16         | OUT                                                                               | OUT            |

| W17         | IN                                                                                | OUT            |

| W18         | OUT                                                                               | OUT            |

|             | المتحادث والمحادث والمحادث المتالة بمحكمة ومحتكم واليواحد بالباري محاد الماري وعج |                |

#### **J1 Output Connections**

Analog output devices such as oscilloscopes may be either grounded or floating. If the oscilloscope is grounded, either through its power plug or through contact between its chassis and a grounded cabinet, the oscilloscope ground should not be connected to any of the AAV11-A ground pins. Doing so may result in a ground loop which will adversely affect oscilloscope control results as well as ADV11-A operation (if used). If the oscilloscope is floating, its ground should be connected to the AAV11-A logic ground, J1 pins L, N, R, or T. Note that the foregoing assumes that the LSI-11 power supply ground is connected to power line (earth) ground. If continuity checks reveal no such connection, attach a length of 12-gauge wire between the power supply ground and a convenient point associated with earth ground.

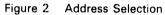

Oscilloscope X and Y inputs may be either differential or single-ended. Differential inputs should be driven as in Figure 3.

Figure 3 Connection to Oscilloscope with Differential Input

When oscilloscopes with single-ended inputs are involved, the AAV11-A analog grounds (pins UU and HH) are not used. Return path for X and Y signal currents is through ground for a grounded oscilloscope or through

logic ground (pins L, N, R, or T) for a floating oscilloscope. Since the grounded, single-ended oscilloscope receives an input voltage which is the sum of the AAV11-A output and the ground difference voltage between the oscilloscope and the AAV11-A, noise and line frequency errors may be minimized by plugging the oscilloscope into an ac socket as close as possible to the LSi-11 system. Running single-ended oscilloscopes in a floating configuration will eliminate noise and line frequency errors which are due to ground voltage differences.

The effect of magnetic coupling into the oscilloscope input lines can be minimized for a differential-input oscilloscope by running the AAV11-A output and its return line in a twisted pair. No benefit is derived from a twisted pair with a single-ended oscilloscope input.

The effect of electrostatic coupling into the oscilloscope input lines can be minimized by shielding the input lines from AAV11-A to the oscilloscope. The shield should be connected to ground at one end only. Grounding the shield at both ends may result in a ground loop which will adversely affect oscilloscope control results and any ADV11-A A/D operations (if used).

Careful selection of cabling is essential. The D/A outputs are capable of driving a maximum of 5000 pF. Output impedance is 1 ohm. Output current limit is 5 mA.

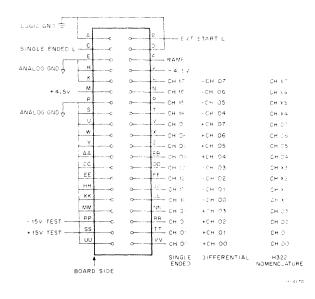

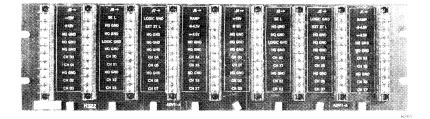

### **Optional Equipment**

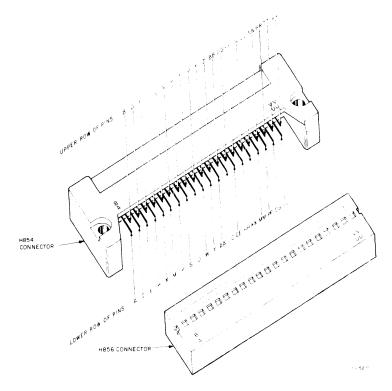

Figure 4 illustrates the H854 40-pin connector pin assignments for user outputs. These pins may be connected to the optional H322 distribution panel for convenient user access via an optional BC08R cable. The optional BC04Z is available for applications which require an unterminated cable. One end is terminated with an H856 connector that mates with the H854 connector on the AAV11-A module. The other end is an unterminated ribbon cable. The BC04Z cable is available in lengths of 3.05 m (10 ft), 4.5 m (15 ft), and 7.6 m (25 ft).

### PROGRAMMING

All four DAC holding registers are automatically set to zero on system initialization. This produces -5.12 V at the DAC outputs when the mode/level jumpers are connected as delivered from the factory. Any holding register value remains in effect until changed by the processor in response to a program instruction. Coding to the D/A converters is offset binary for bipolar operation and straight binary for unipolar operation. Offset binary defines 0 as maximum negative voltage, mid-point (i.e.,  $4000_8$  for the 12-bit AAV11-A) as 0 V, and all 1s (7777<sub>8</sub>) as maximum positive voltage. These relationships are illustrated in Table 5.

## **AAV11-A**

Figure 4 J1 Connector Pin Assignments

| Table 5 | AAV11-A | Digital-to-Analog | Conversions* |

|---------|---------|-------------------|--------------|

|---------|---------|-------------------|--------------|

|                                               | Bipolar                                                                                     |                                                                                         | Unipolar                                                  |                                                               |                                                           |

|-----------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------|

| Input<br>Code<br>(octal)                      | ±2.56 V<br>(volts)                                                                          | ±5.12 V<br>(volts)                                                                      | ±10.24 V<br>(volts)                                       | 0 V to<br>+5.12 V<br>(volts)                                  | 0 V to<br>+10.24 V<br>(volts)                             |

| 0000<br>0001<br>3777†<br>4000<br>4001<br>7777 | $\begin{array}{r} -2.56 \\ -2.55875 \\ -0.00125 \\ 0.0 \\ +0.00125 \\ +2.55875 \end{array}$ | $\begin{array}{r} -5.12 \\ -5.1175 \\ -0.0025 \\ 0.0 \\ +0.0025 \\ +5.1175 \end{array}$ | $-10.24 \\ -10.235 \\ -0.005 \\ 0.0 \\ +0.005 \\ +10.235$ | +0.0<br>+0.00125<br>+2.55875<br>+2.56<br>+2.56125<br>+5.11875 | +0.0<br>+0.025<br>+5.1175<br>+5.12<br>+5.1225<br>+10.2375 |

\* Offset binary for bipolar, straight binary for unipolar operating modes. Conversions may be made between 2's complement signed binary and offset binary numbers by subtracting  $4000_8$  from the 2's complement number (or adding  $4000_8$  to the offset binary number) and using only the low order 12 bits of the result.

† Note that in all ranges, actual maximum positive voltage output is 1 LSB less than nominal maximum positive output.

### FUNCTIONAL DESCRIPTION

#### General

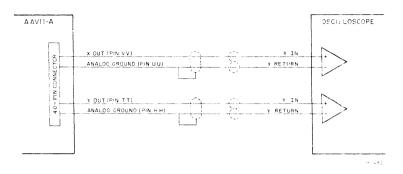

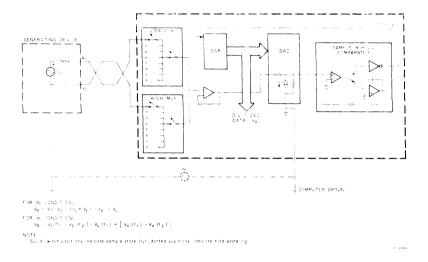

The function of the AAV11-A module is to convert digital data input to an analog dc voltage output that is representative of the input. This is accomplished by the bus interface, the control logic, and the D/A converter functions as shown in Figure 5.

# AAV11-A

## AAV11-A

### **Bus Interface**

The logic associated with the bus interface section maintains proper communications protocol between the processor LSI-11 bus and the AAV11-A. This logic generates and monitors the bus signals involved during data transfers between the processor and the AAV11-A, permitting the AAV11-A to recognize when it is being addressed by the processor (address defined by setting on the address switch pack), to accept input data from the processor, and to output data to the processor.

### **Control Logic**

The AAV11-A has no control/status register. The four digital-to-analog converters continually generate voltages at their outputs that reflect whatever digital values have most recently been written into their respective holding registers. The role of the control logic is to make the necessary discriminations between requests to change the state of the holding registers (i.e., to *write* into the holding registers), and requests to put the holding register contents onto the BD lines where they can be picked up through the transceivers by the processor.

### DACs 0, 1, and 2

Digital-to-analog conversion functions are performed in each of the four AAV11-A channels by identical circuits:

- A holding register which stores the digital value output by the processor

- A digital-to-analog converter (DAC) proper which generates a current that is a function of the holding register value and of the mode/level jumper conditions

- An amplifier that translates the current into a proportional voltage, provides a low output impedance for the channel, and permits adjustment of signal offset.

## DAC 3

DAC 3 is identical to DACs 0, 1, and 2 except that holding register bits 0–3 are routed to the I/O connector as well as to the DAC. This arrangement permits these bits to be routed to external equipment that requires binary control signals at programmable intervals. Control data in these bit positions affects any 12-bit D/A conversion that they coincide with, but since they involve the least significant bits of the word, the worst-case error is less than 0.5 percent. Consequently, DAC 3 can be used as a 12-bit DAC or as an 8-bit DAC plus four output bits for CRT Intensify, Store, Non-Store, Erase, etc.

## ADV11-A ANALOG TO DIGITAL CONVERTER

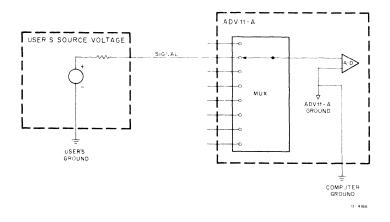

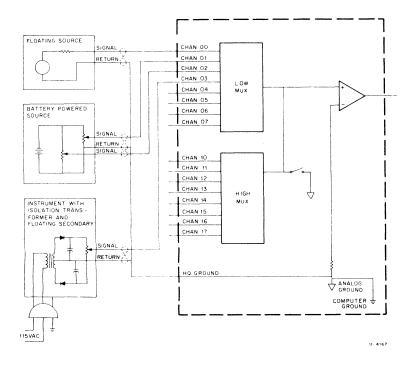

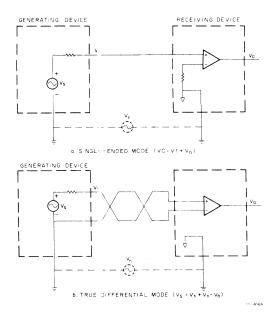

### GENERAL