digital

EK-VT100-TM-002

digital equipment corporation • maynard, massachusetts

1st Edition, August 1979 2nd Edition, September 1980

Copyright © 1979, 1980 by Digital Equipment Corporation All rights reserved.

The material in this manual is for informational purposes and is \_ subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS      |

|---------|--------------|--------------|

| DEC     | DECSYSTEM-20 | OMNIBUS      |

| PDP     | DIBOL        | <b>OS</b> /8 |

| DECUS   | EDUSYSTEM    | RSTS         |

| UNIBUS  | VAX          | RSX          |

|         | VMS          | IAS          |

# CONTENTS

## CHAPTER 1 INTRODUCTION AND SPECIFICATIONS

| VT100 Specifications            | 1-2 |

|---------------------------------|-----|

| Ordering Hardware Documentation |     |

| Related Documentation           | 1-4 |

# **CHAPTER 2** OPERATOR INFORMATION

| Part 1 – Keyboard Controls and Indicators | . 2-1  |

|-------------------------------------------|--------|

| Numeric Keypad                            |        |

| Monitor Control                           | 2-5    |

| Audible Indicators (Tones)                | . 2-5  |

| Part 2 - SET-UP Mode                      | 2-6    |

| SET-UP Features                           | 2-7    |

| SET-UP A                                  |        |

| SET-UP B                                  | 2-8    |

| Determining What a SET-UP Feature Does    | . 2-8  |

| How to Change a SET-UP Feature            | . 2-10 |

| Setting the Answerback Message            | . 2-11 |

| Saving SET-UP Features                    | . 2-12 |

| Recalling SET-UP Features                 |        |

| Resetting the Terminal                    |        |

| Part 3 – Definitions of SET-UP Features   | . 2-13 |

| ANSI/VT52 Mode                            | . 2-13 |

| Answerback Message                        | . 2-13 |

| Auto Repeat                               | 2-13   |

| Auto XON/XOFF                             | . 2-14 |

| Bits per Character                        | . 2-14 |

| Characters per Line                       | . 2-14 |

| Cursor                                    | 2-14   |

| Interlace                                 | 2-14   |

| Keyclick Tone                             | 2-15   |

| LINE/LOCAL                                | 2-15   |

| Margin Bell                               |        |

| New Line                                  | 2-15   |

| Parity                                    | 2-15   |

| Parity Sense                              | . 2-15 |

| Power                                     |        |

| Receive Speed                             | . 2-16 |

| Screen Background                         |        |

| Screen Brightness                             | 2-16 |

|-----------------------------------------------|------|

| Scroll                                        | 2-16 |

| Tabs                                          | 2-16 |

| Transmit Speed                                | 2-16 |

| Wraparound                                    |      |

| Part 4 – Self-Testing the VT100               | 2-17 |

| Self-Test Error Codes                         | 2-17 |

| Part 5 – What To Do in the Event of a Problem | 2-19 |

# CHAPTER 3 INSTALLATION AND INTERFACE INFORMATION

| Site Considerations                   | 3-1   |

|---------------------------------------|-------|

| Unpacking and Installation            | 3-1   |

| User Maintenance                      | 3-3   |

| Interface Information                 | 3-4   |

| EIA Interface                         | 3-4   |

| Electrical Characteristics            | . 3-5 |

| VT100 Output Voltages                 | . 3-5 |

| VT100 Input Voltages                  |       |

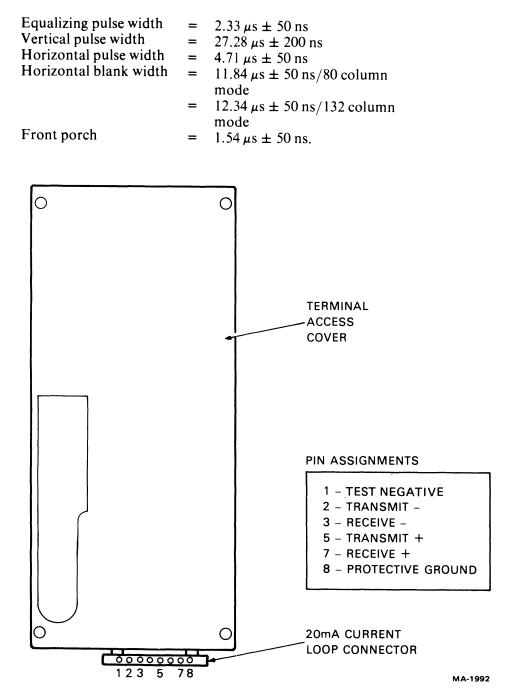

| Optional 20 mA Current Loop Interface |       |

| External Video Connectons             |       |

| Composite Video Output (J9)           | . 3-6 |

| Video Input (J8)                      |       |

# CHAPTER 4 TECHNICAL DESCRIPTION

| 4.1      | Introduction to VT100 Technical Description | 4-1 |

|----------|---------------------------------------------|-----|

| 4.1.1    | Scope of Chapter                            | 4-1 |

| 4.1.2    | Order of Presentation                       | 4-1 |

| 4.1.3    | Definition of Terms and Abbreviations       | 4-1 |

| 4.1.4    | Hardware Introduction                       | 4-1 |

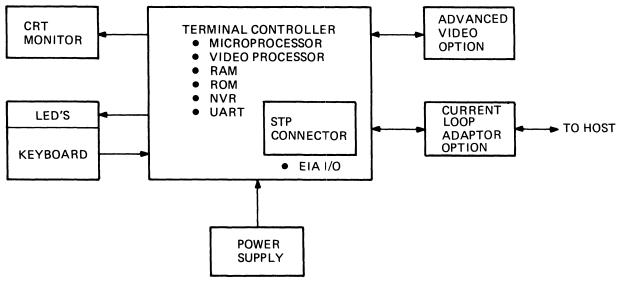

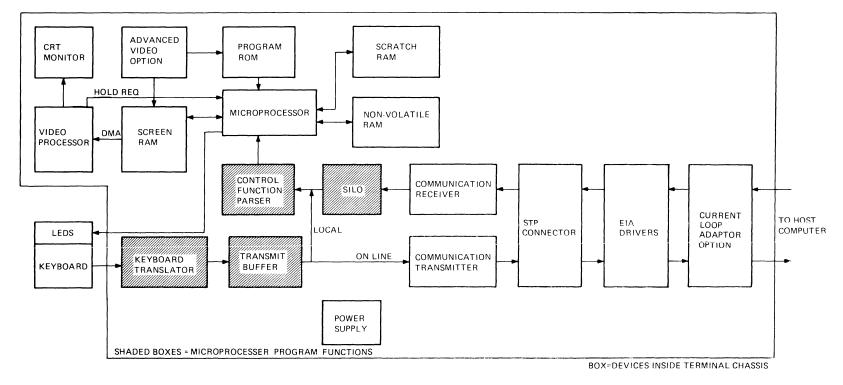

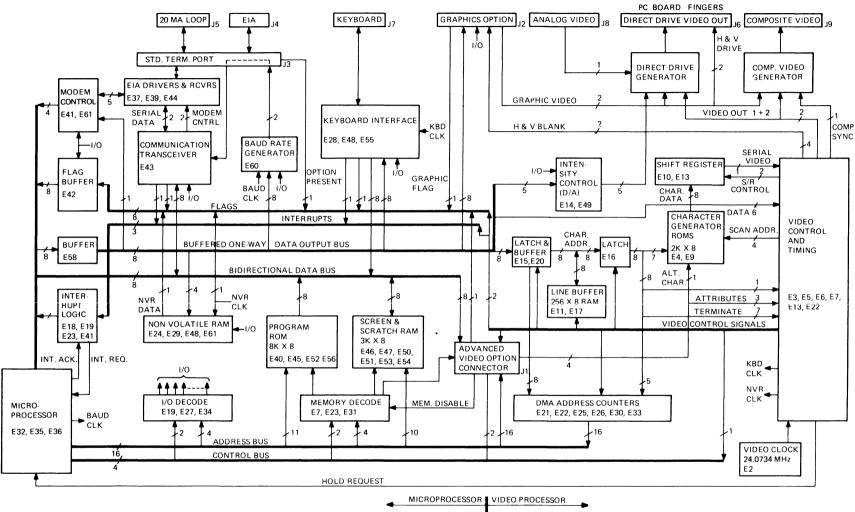

| 4.1.5    | Block Diagram Description                   | 4-3 |

| 4.1.5.1  | Microprocessor                              | 4-3 |

| 4.1.5.2  | Program ROM                                 | 4-3 |

| 4.1.5.3  | Scratch RAM                                 | 4-3 |

| 4.1.5.4  | Nonvolatile RAM                             | 4-3 |

| 4.1.5.5  | Advanced Video Option                       | 4-3 |

| 4.1.5.6  | Keyboard                                    | 4-5 |

| 4.1.5.7  | LEDs                                        | 4-5 |

| 4.1.5.8  | Keyboard Translator                         | 4-5 |

| 4.1.5.9  | Transmit Buffer                             | 4-5 |

| 4.1.5.10 | Communication Transmitter                   | 4-5 |

| 4.1.5.11 | Communication Receiver                      | 4-5 |

| 4.1.5.12 | SILO                                        | 4-5 |

| 4.1.5.13 | Control Function Parser                     | 4-5 |

| 4.1.5.14 | Screen RAM                                  | 4-6 |

| 4.1.5.15 | Video Processor                             | 4-6 |

| 4.1.5.16 | CRT Monitor                                 | 4-6 |

| 4.1.5.17 | Power Supply                                | 4-7 |

| 4.1.5.18 | Standard Terminal Port                      | 4-7 |

| 4.1.5.19 | EIA Interface                               |     |

| 4.1.5.20 | Current Loop Interface Adapter              |     |

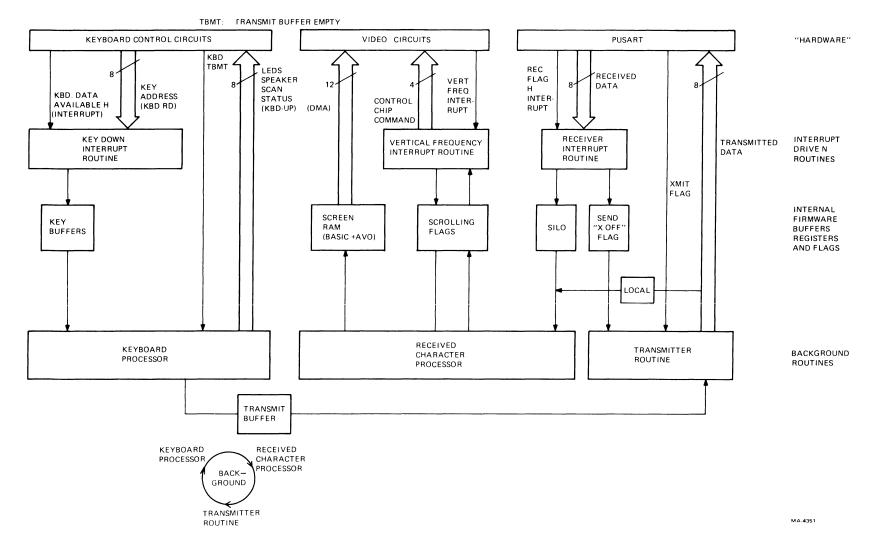

| 4.1.6    | Firmware Introduction                       | 4-7 |

|          |                                             |     |

| 4.2     | Microprocessor                     | 4-9  |

|---------|------------------------------------|------|

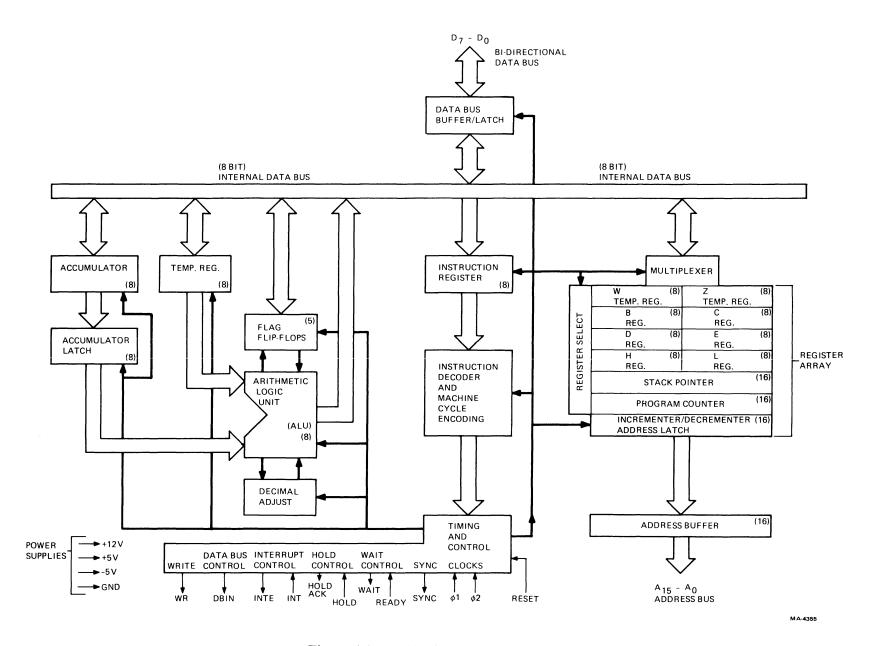

| 4.2.1   | 8080 Microprocessor                | 4-9  |

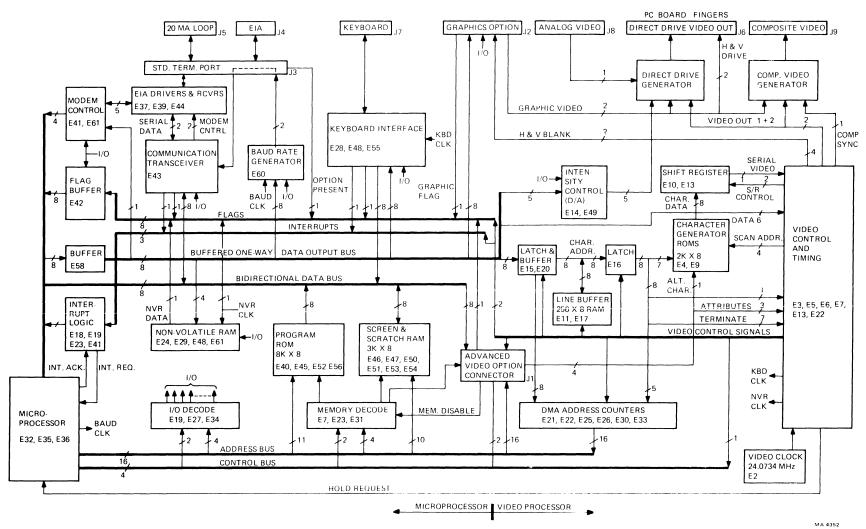

| 4.2.2   | Data Bus and System Controller     | 4-11 |

| 4.2.3   | Clock Generator                    |      |

| 4.2.4   | Bus Timing                         |      |

| 4.2.5   | Microprocessor Memory              |      |

| 4.2.5.1 | Memory Map                         |      |

| 4.2.5.2 | Memory Devices                     |      |

| 4.2.5.3 | ROM Decoding                       |      |

| 4.2.5.4 | RAM Decoding                       |      |

| 4.2.5.5 | Memory Disable                     |      |

| 4.2.6   | I/O Decoding                       |      |

| 4.2.6.1 | PUSART Read and Write              |      |

| 4.2.6.2 | I/O Read and Write                 |      |

|         | Interrupt Vector                   |      |

| 4.2.7   | Power-Up and Self-Test             |      |

| 4.2.8   | Communication Transceiver          |      |

| 4.3     |                                    |      |

| 4.3.1   | PUSART Principles                  |      |

| 4.3.2   | PUSART Operation                   |      |

| 4.3.3   | PUSART Addressing                  |      |

| 4.3.4   | PUSART Programming                 |      |

| 4.3.5   | Data Transmission                  |      |

| 4.3.6   | Data Reception                     |      |

| 4.3.7   | Baud Rate Generator                |      |

| 4.3.8   | Serial Interface                   |      |

| 4.3.9   | Modem Control                      |      |

| 4.3.10  | Data Types                         |      |

| 4.3.11  | SILO                               |      |

| 4.3.12  | XON/XOFF                           | 4-29 |

| 4.3.13  | Control Function Parser            |      |

| 4.3.14  | Local                              |      |

| 4.3.15  | Standard Terminal Port             | 4-29 |

| 4.3.16  | Communication Self-Test            |      |

| 4.4     | Keyboard                           | 4-30 |

| 4.4.1   | Keyboard Block Diagram             | 4-30 |

| 4.4.2   | Keyboard UARTs                     | 4-31 |

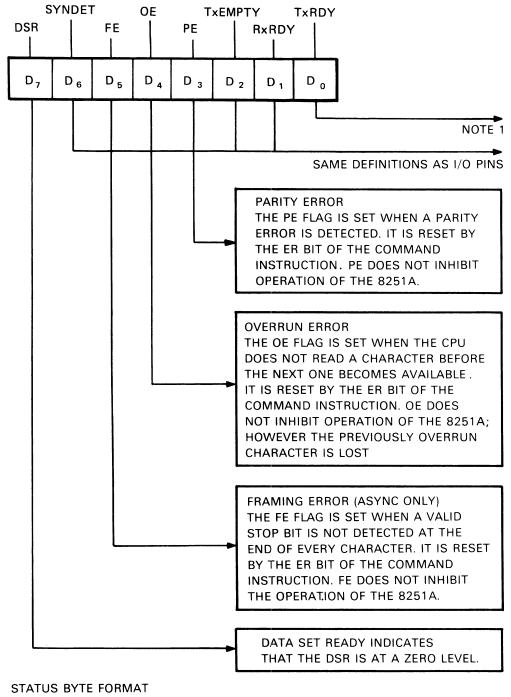

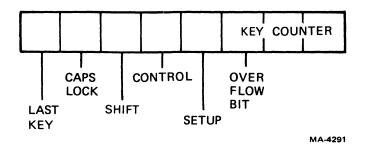

| 4.4.3   | Keyboard Status Byte               | 4-31 |

| 4.4.4   | Key Address Counter                |      |

| 4.4.5   | Key Scanning and Address Formation | 4-34 |

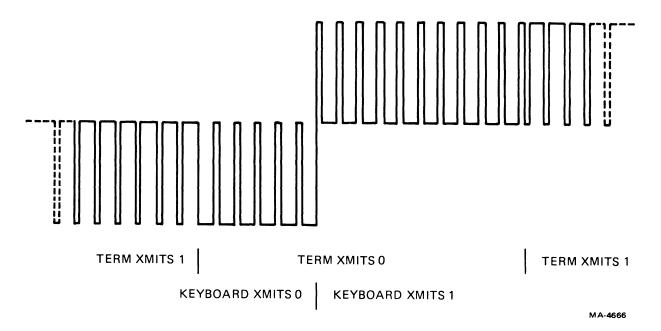

| 4.4.6   | Bidirectional Interface Operation  |      |

| 4.4.6.1 | Interface Line                     |      |

| 4.4.6.2 | Receiving Side                     |      |

| 4.4.6.3 | Terminal Data Encoding             |      |

| 4.4.6.4 | Combined Interface Signal          | 4-38 |

| 4.4.6.5 | Decoding of Data from Terminal     | 4-38 |

| 4.4.6.6 | Keyboard Output                    |      |

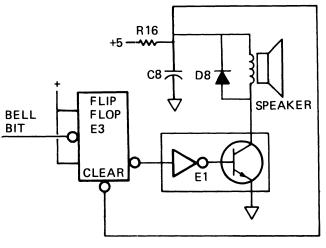

| 4.4.7   | Bell                               |      |

| 4.4.8   | Keyboard Interrupt Routine         |      |

| 4.4.9   | Logical Keyboard Processor         |      |

| 4.4.9.1 | Key Recognition                    |      |

| 4.4.9.2 | Key Rollover                       |      |

| 4.4.9.2 | Generation of Codes                |      |

|         | Keyboard Transmit Buffer           |      |

| 4.4.9.4 | Reyouard Transmit Duilei           |      |

| 4.4.9.5  | Auto Repeat 4                              | 1-44          |

|----------|--------------------------------------------|---------------|

| 4.5      | Nonvolatile RAM                            |               |

| 4.5.1    | Principles 4                               |               |

| 4.5.2    | NVR Device                                 |               |

| 4.5.3    | NVR Control                                |               |

| 4.5.4    | NVR Support Circuits                       |               |

| 4.5.5    | Microprocessor Management                  | 1_17          |

| 4.5.6    | NVR Timing                                 | 1- <i>1</i> 7 |

| 4.6      | Video Processor                            |               |

| 4.6.1    | Introduction                               |               |

| 4.6.1.1  | The Raster                                 |               |

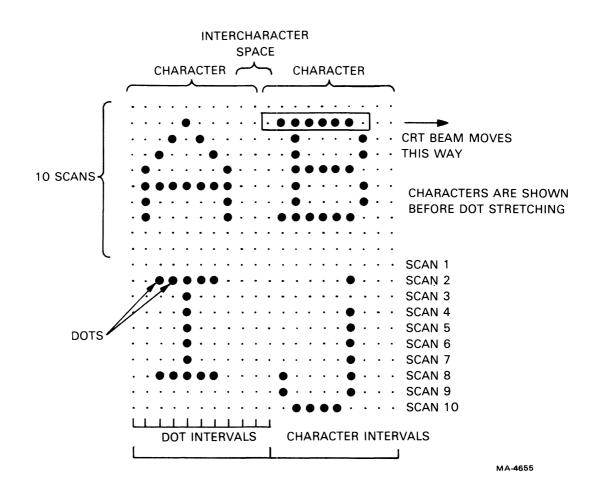

| 4.6.1.2  | Character Formation                        | +-JI<br>4 51  |

| 4.6.1.3  | Video Processor Data                       | 4-51          |

| 4.6.1.4  | Video Processor Character Generation       | +-32          |

| 4.6.1.5  | Attributes                                 | +-32          |

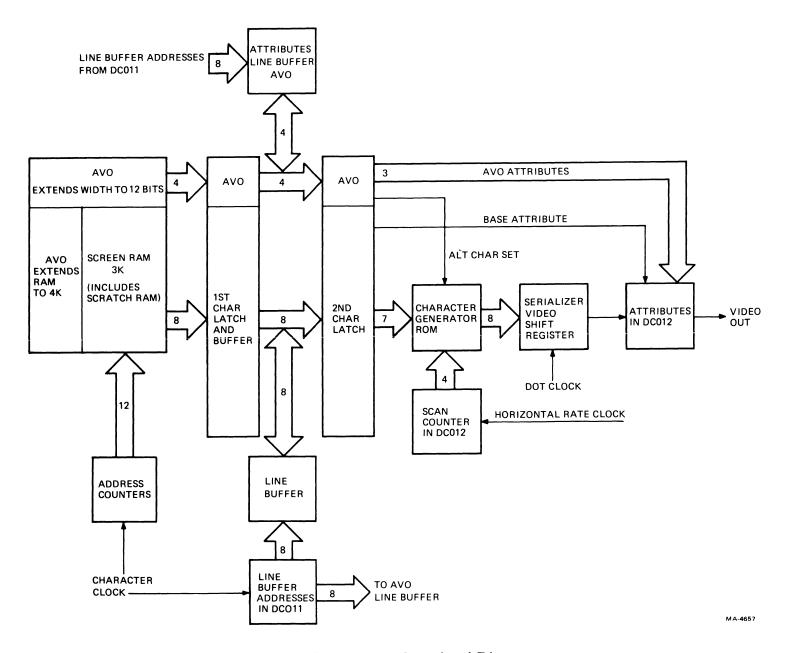

| 4.6.1.6  | Advanced Video Option (AVO)                | +-32          |

| 4.6.2    |                                            |               |

| 4.6.2.1  | Timing Chip Description                    |               |

|          | Input Decoder                              |               |

| 4.6.2.2  | 80/132 Column Selection                    | 4-57          |

| 4.6.2.3  | Dot Counter 4                              |               |

| 4.6.2.4  | Double-Width Multiplexer 4                 |               |

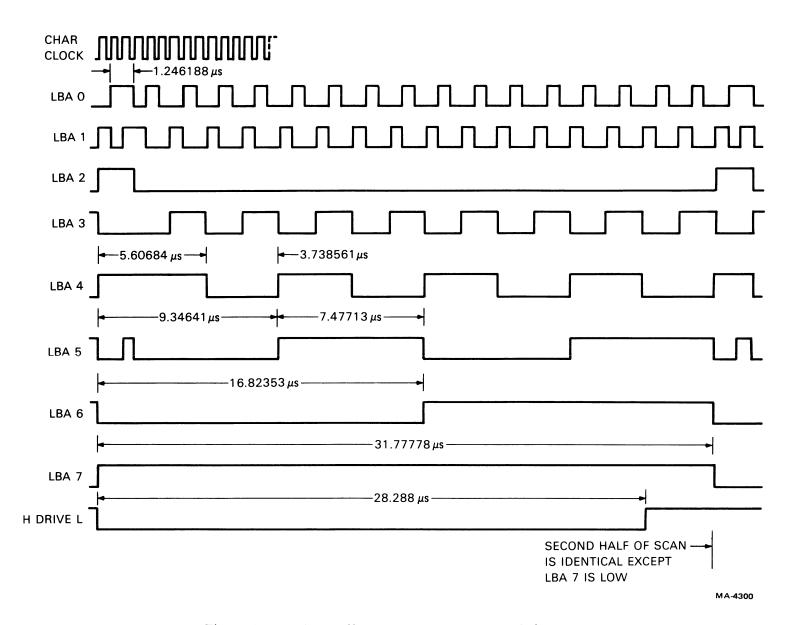

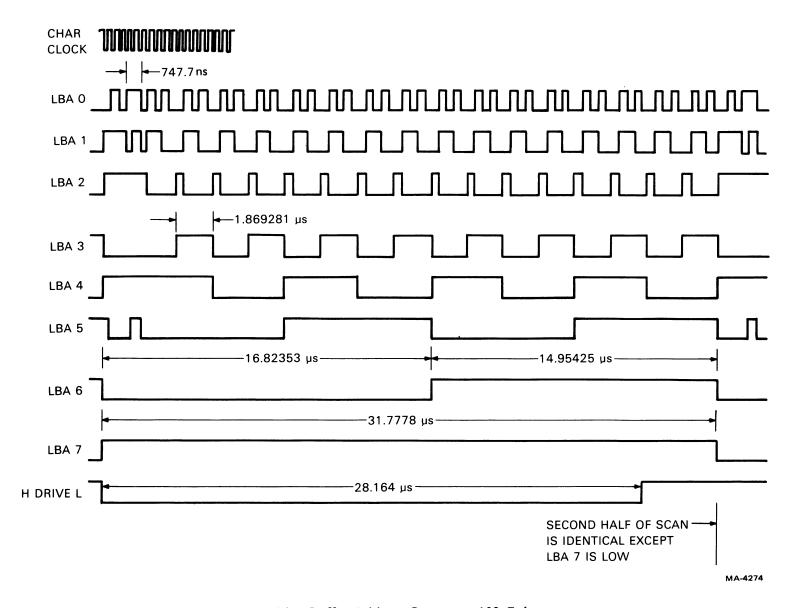

| 4.6.2.5  | Horizontal Counter                         |               |

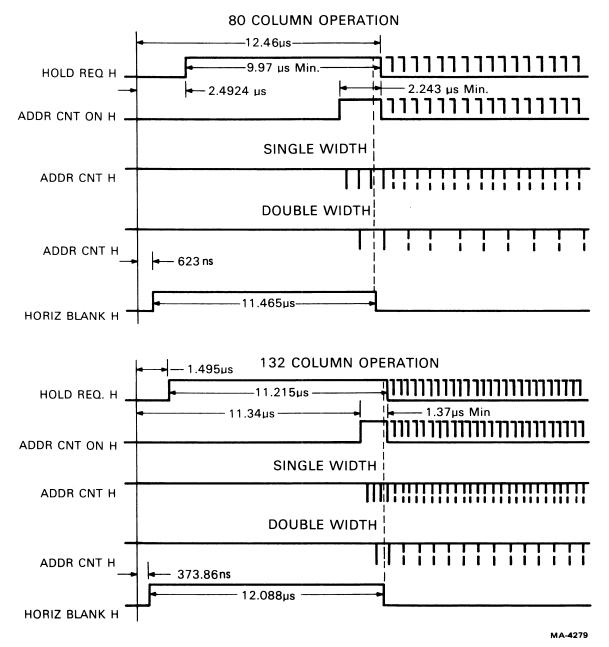

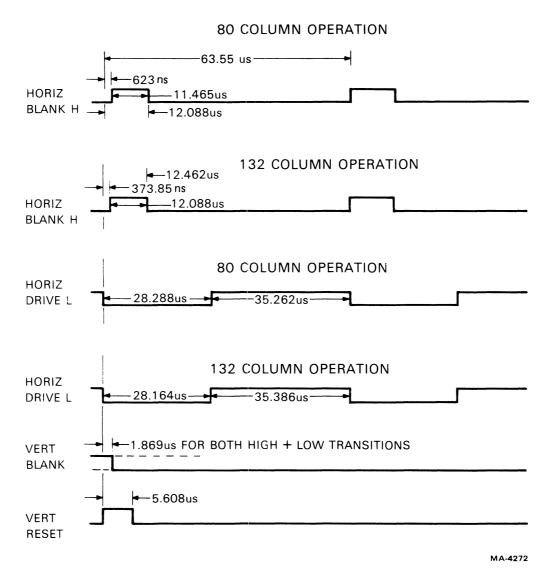

| 4.6.2.6  | Horizontal Drive and Horizontal Blank 4    |               |

| 4.6.2.7  | Line Buffer Addressing 4                   |               |

| 4.6.2.8  | Vertical Operation 4                       |               |

| 4.6.2.9  | Vertical Counter 4                         | 4-64          |

| 4.6.2.10 | Vertical Outputs 4                         |               |

| 4.6.2.11 | Composite Sync 4                           | 4-67          |

| 4.6.2.12 | Hold Request, Address Load, and            |               |

|          | Double-Width 4                             | 4-67          |

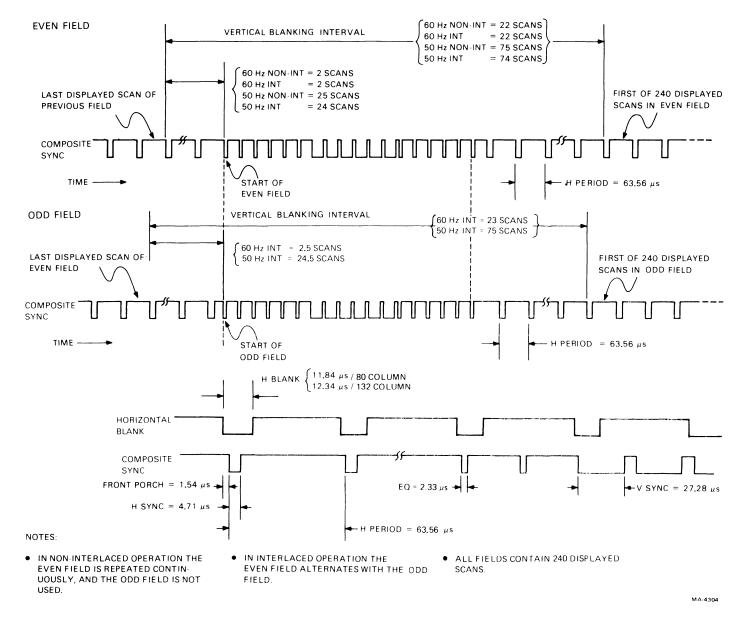

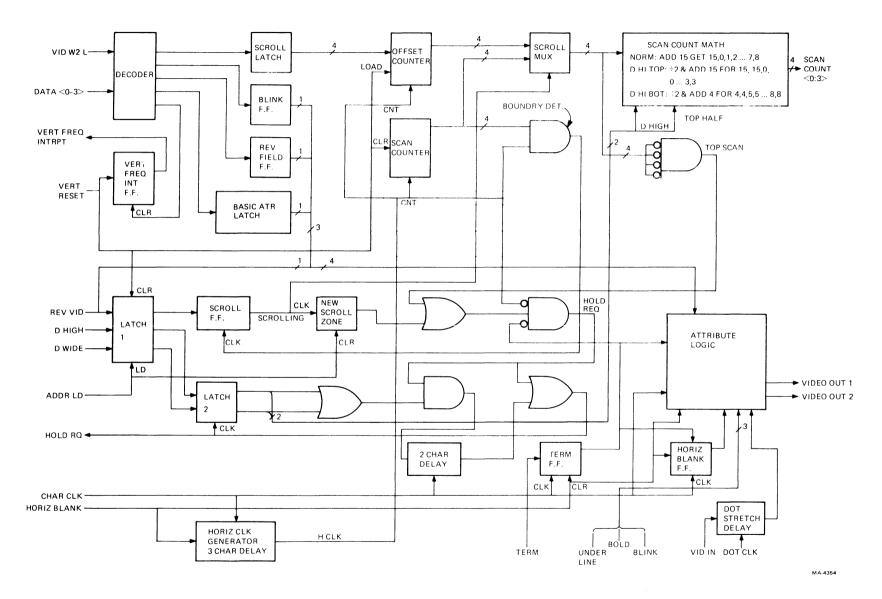

| 4.6.3    | Control Chip Description 4                 | 4-67          |

| 4.6.3.1  | Input Decoder Functions 4                  |               |

| 4.6.3.2  | Attribute Latches 4                        | 4-71          |

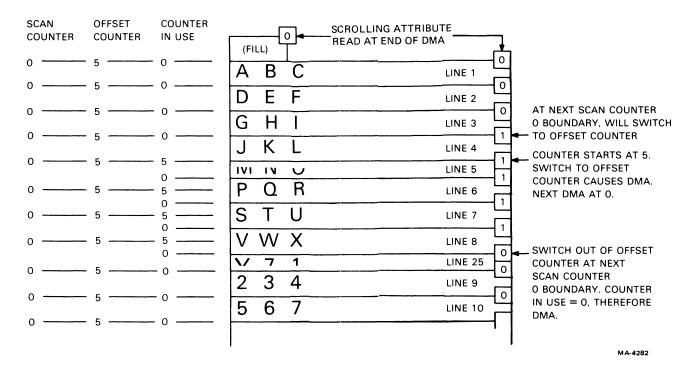

| 4.6.3.3  | Scroll Counter                             | 4-71          |

| 4.6.3.4  | Scan Count Math 4                          | 4-72          |

| 4.6.3.5  | Generation of HOLD REQUEST                 | 4-72          |

| 4.6.3.6  | Horizontal Blank and Terminate             | 4-73          |

| 4.6.3.7  | Double Width and Hold Request              |               |

| 4.6.3.8  | Attributes                                 |               |

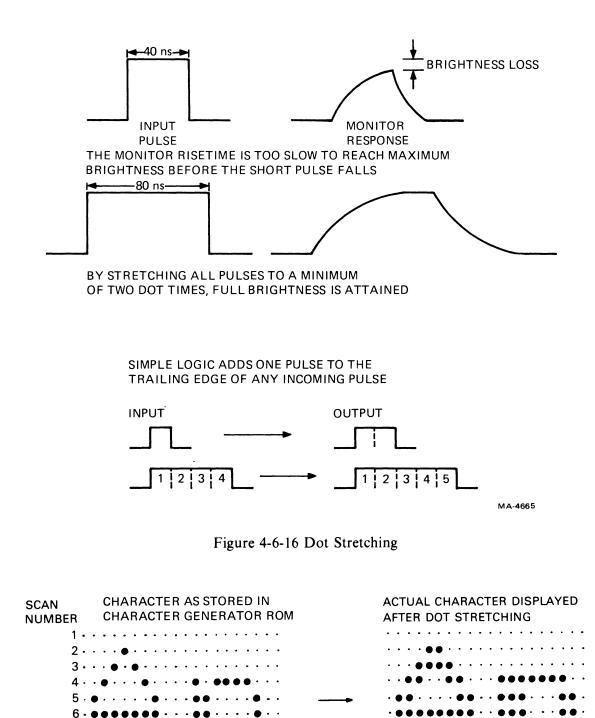

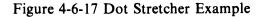

| 4.6.3.9  | Dot Stretcher                              |               |

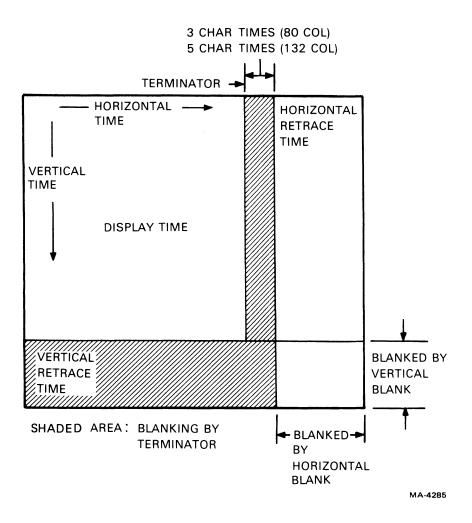

| 4.6.4    | Address Counter and Data Structure in RAM  |               |

| 4.6.5    | Address Latch Buffer                       |               |

| 4.6.6    | Line Buffer                                |               |

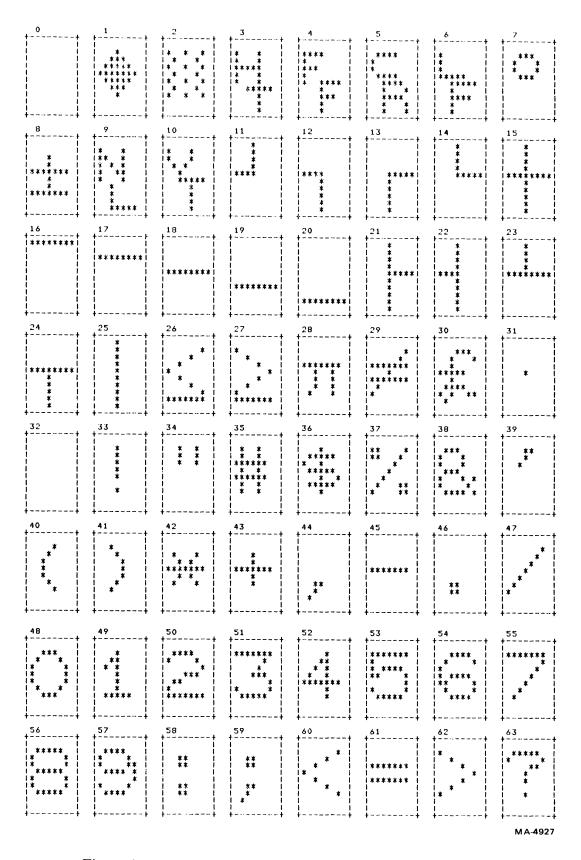

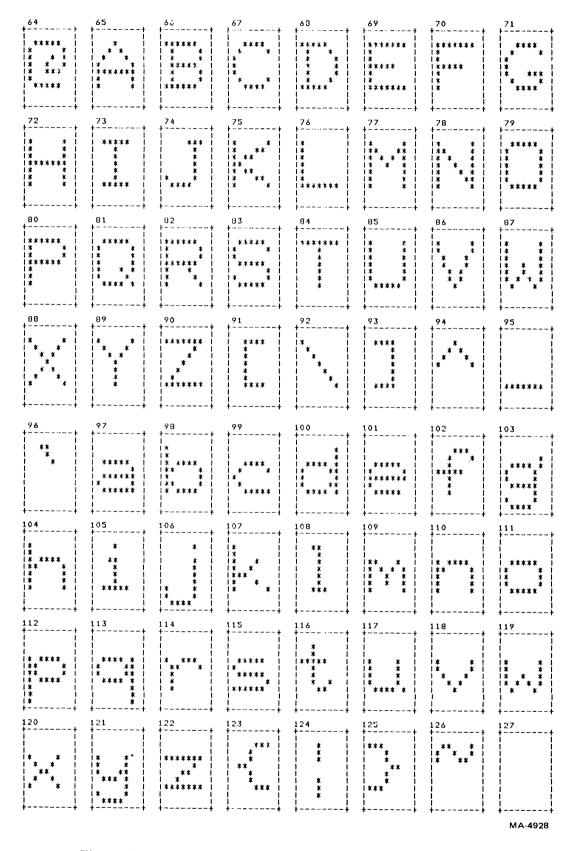

| 4.6.7    | Character Generator                        |               |

| 4.6.8    | Video Shift Register                       |               |

| 4.6.9    | Terminator                                 |               |

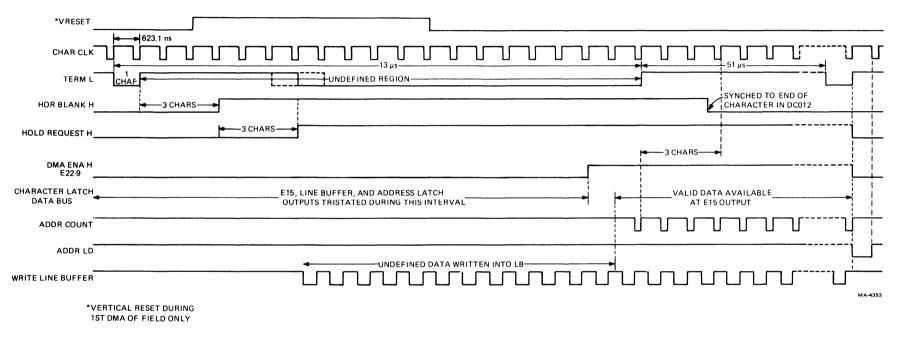

| 4.6.10   | DMA Cycle Timing Diagram                   | 4_80          |

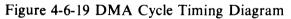

| 4.6.11   | Video Blanking                             |               |

| 4.6.12   | Video Input and Output                     | 4_82          |

| 4.6.12.1 | Direct Drive Video                         |               |

| 4.6.12.2 | Composite Video Out                        |               |

| 4.6.12.2 | Video In                                   |               |

|          |                                            |               |

| 4.6.13   | Intensity Control                          |               |

| 4.7      | Microprocessor – Video Processor Interface | 4-03          |

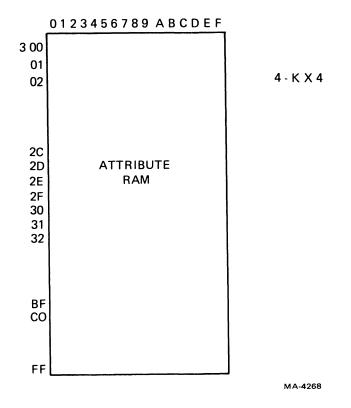

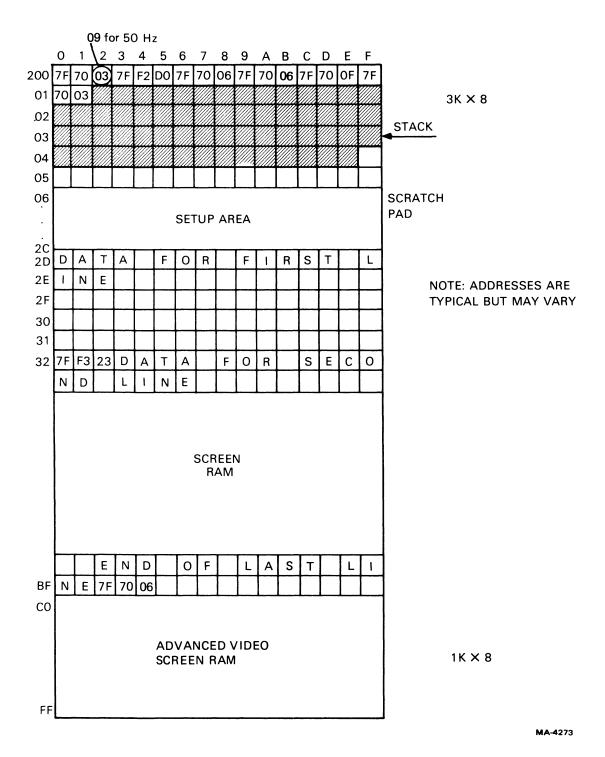

| 4.7.1    | Screen Memory Organization             | 4-86  |

|----------|----------------------------------------|-------|

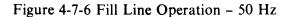

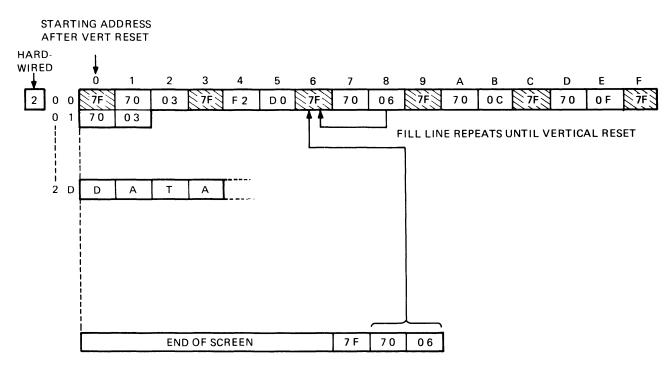

| 4.7.2    | Fill Line Operation                    | 4-87  |

| 4.7.3    | Line Organization                      | 4-88  |

| 4.7.3.1  | Physical Screen                        |       |

| 4.7.3.2  | Logical Screen                         | 4-92  |

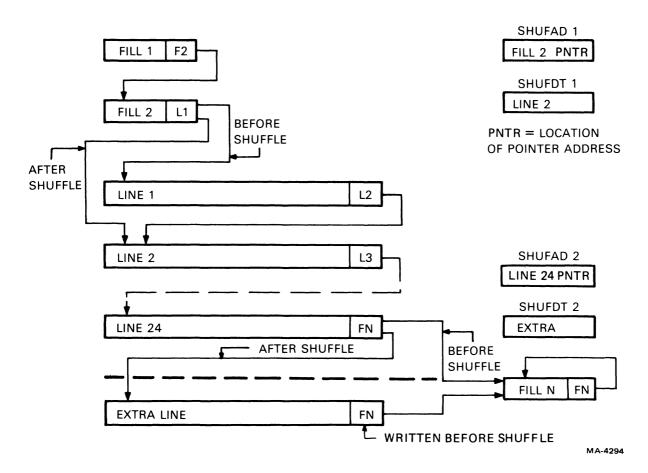

| 4.7.4    | Address Shuffling                      | 4-92  |

| 4.7.5    | Shuffle Timing                         | 4-94  |

| 4.7.6    | Scrolling Region                       | 4-95  |

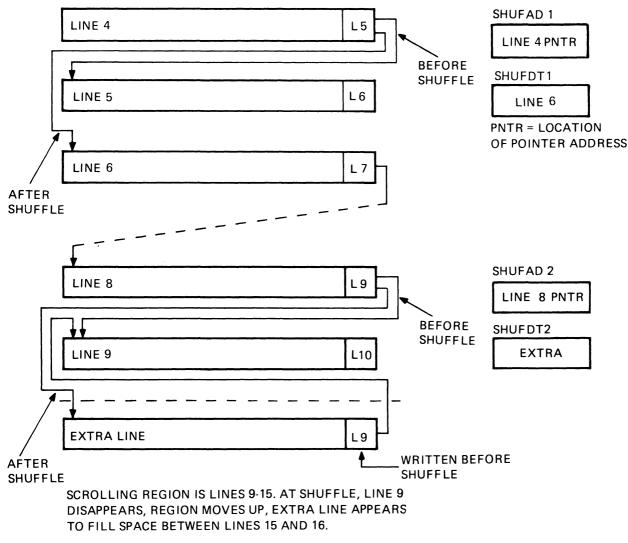

| 4.7.7    | Split Screen Jump Scrolling            |       |

| 4.7.8    | Smooth Scroll                          | 4-95  |

| 4.7.9    | Split Screen Smooth Scrolling          | 4-97  |

| 4.7.10   | Cursor                                 |       |

| 4.7.11   | SET-UP                                 |       |

| 4.8      | Monitor                                |       |

| 4.8.1    | Monitor Description: 30-16080 (Elston) |       |

| 4.8.1.1  | Video Driver                           |       |

| 4.8.1.2  | Brightness                             |       |

| 4.8.1.3  | Vertical Oscillator                    |       |

| 4.8.1.4  | Self-Oscillation                       |       |

| 4.8.1.5  | Vertical Output                        | 4-100 |

| 4.8.1.6  | Linearization                          |       |

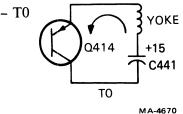

| 4.8.1.7  | Horizontal Driver                      | 4-101 |

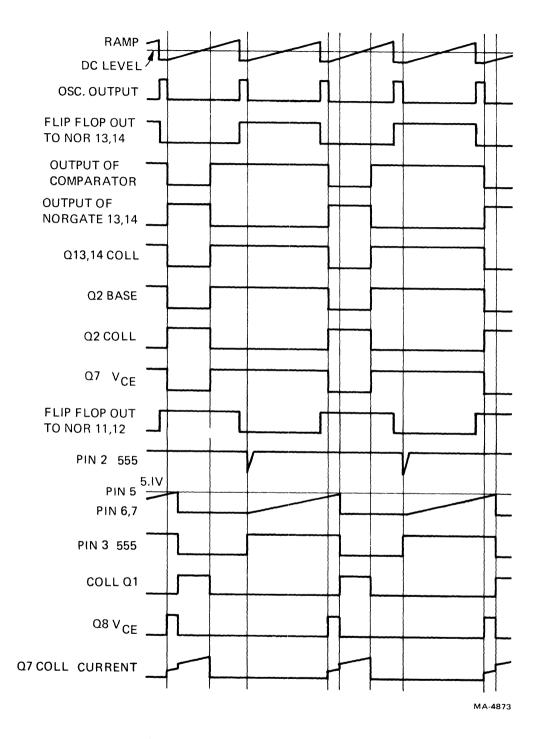

| 4.8.1.8  | Horizontal Deflection Operation        |       |

| 4.8.1.9  | Horizontal Output Circuit              |       |

| 4.8.1.10 | High Voltage and Focus                 |       |

| 4.8.2    | Monitor Description: 30-14590 (Ball)   | 4-104 |

| 4.8.2.1  | Video Amplifier                        |       |

| 4.8.2.2  | Vertical Deflection                    | 4-104 |

| 4.8.2.3  | Horizontal Deflection                  | 4-105 |

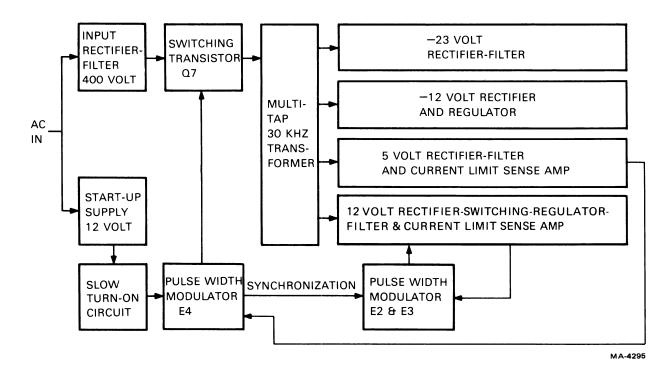

| 4.9      | Power Supply                           |       |

| 4.9.1    | Power Input                            | 4-107 |

| 4.9.2    | Start-Up Circuit                       |       |

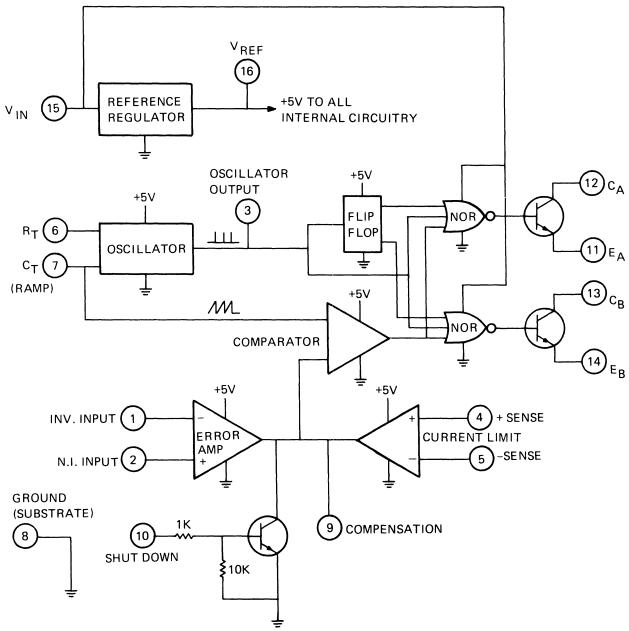

| 4.9.3    | Control Circuit                        | 4-108 |

| 4.9.4    | Outputs                                |       |

| 4.9.5    | Power Supply Specifications            |       |

| 4.9.5.1  | Input Specifications                   |       |

| 4.9.5.2  | Cooling                                |       |

| 4.9.5.3  | Base Product Power Requirements        |       |

# CHAPTER 5 VT100 SERIES SERVICE

| 5.1     | Introduction                             | 5-1  |

|---------|------------------------------------------|------|

| 5.2     | Troubleshooting                          | 5-1  |

| 5.2.1   | Troubleshooting the VT100 with Self Test |      |

| 5.2.2   | Troubleshooting Basic VT100 Variations   |      |

|         | Without Self Test                        | 5-3  |

| 5.2.3   | Troubleshooting the VT105                | 5-3  |

| 5.2.4   | Troubleshooting the VT132                |      |

| 5.2.5   | Troubleshooting Options                  |      |

| 5.2.6   | VT100 Internal Self Tests                |      |

| 5.2.6.1 | Power-Up Test                            |      |

| 5.2.6.2 | Data Loopback Test                       |      |

| 5.2.6.3 | EIA Test                                 |      |

| 5.2.6.4 | Video Adjust Test                        | 5-11 |

| 5.2.6.5 | SET-UP Screen Test                      | 5-12  |

|---------|-----------------------------------------|-------|

| 5.2.7   | Error Codes                             |       |

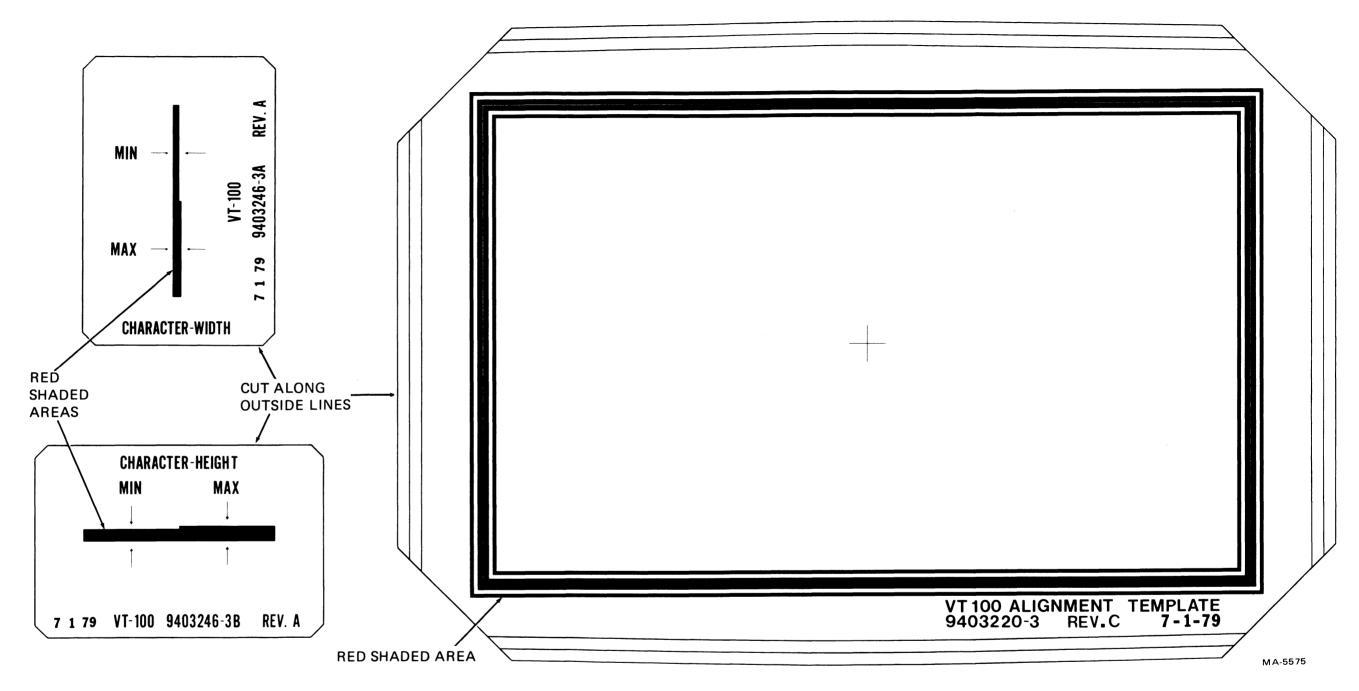

| 5.3     | Video Alignment                         |       |

| 5.3.1   | General                                 |       |

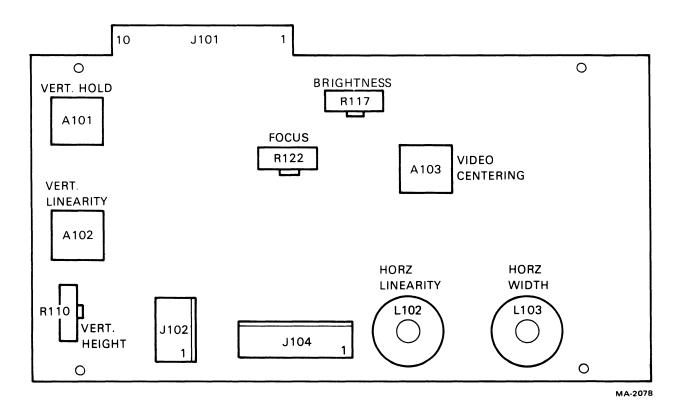

| 5.3.2   | Monitor Adjustments (Ball Brothers)     | 5 1 5 |

| 5.3.2.1 | Brightness                              |       |

| 5.3.2.2 | Focus                                   |       |

| 5.3.2.3 |                                         |       |

| 5.3.2.4 | Yoke Rotation                           |       |

|         | Vertical Height                         |       |

| 5.3.2.5 | Horizontal Width                        |       |

| 5.3.2.6 | Centering                               |       |

| 5.3.2.7 | Vertical Linearity                      |       |

| 5.3.2.8 | Horizontal Linearity                    |       |

| 5.3.2.9 | Vertical Hold                           |       |

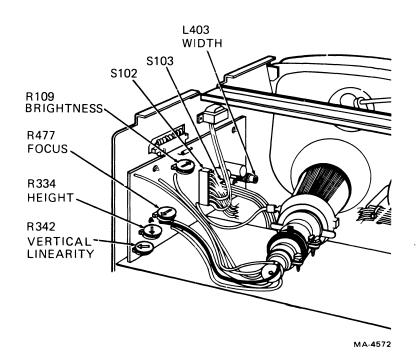

| 5.3.3   | Monitor Adjustments (Elston)            |       |

| 5.3.3.1 | Brightness                              | 5-21  |

| 5.3.3.2 | Focus                                   | 5-22  |

| 5.3.3.3 | Yoke Rotation                           | 5-23  |

| 5.3.3.4 | Vertical Height                         |       |

| 5.3.3.5 | Horizontal Width                        |       |

| 5.3.3.6 | Centering                               |       |

| 5.3.3.7 | Vertical Linearity                      |       |

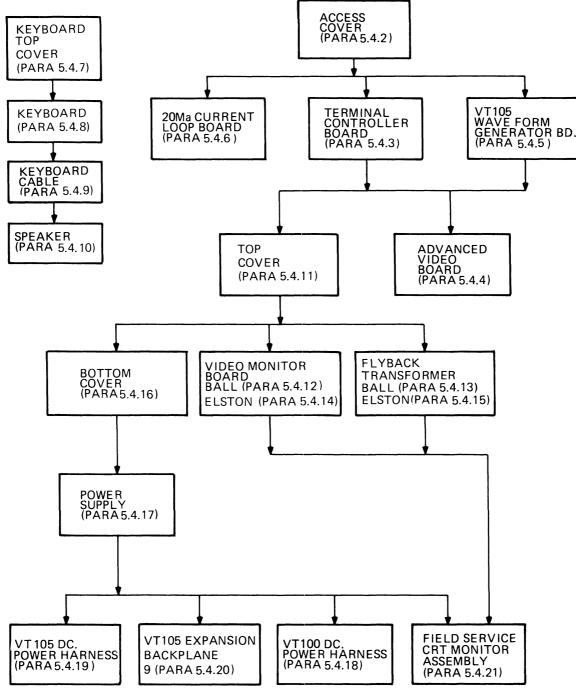

| 5.4     | Module Removal and Replacement.         |       |

| 5.4.1   | General                                 |       |

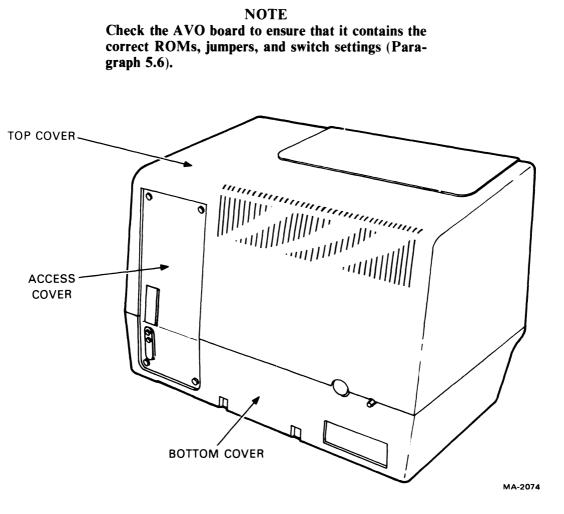

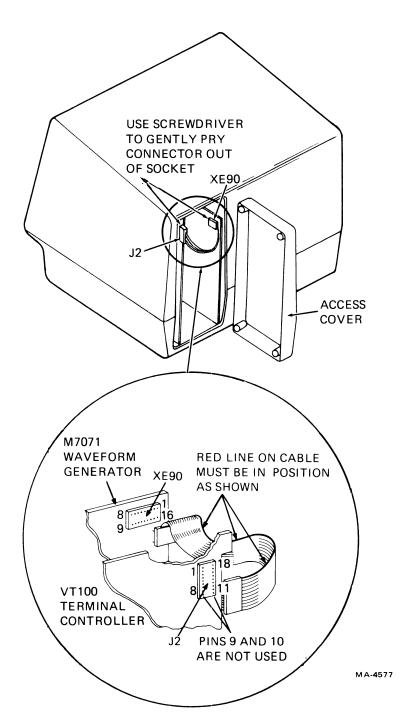

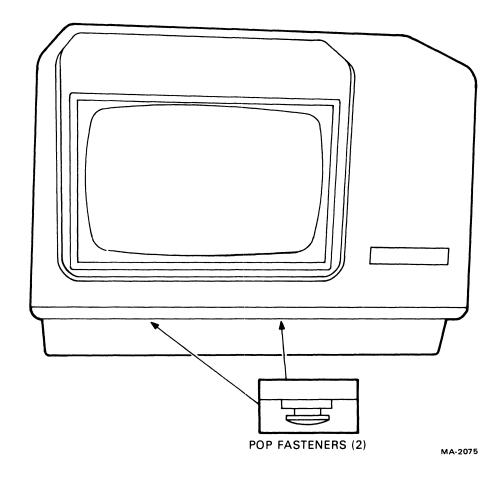

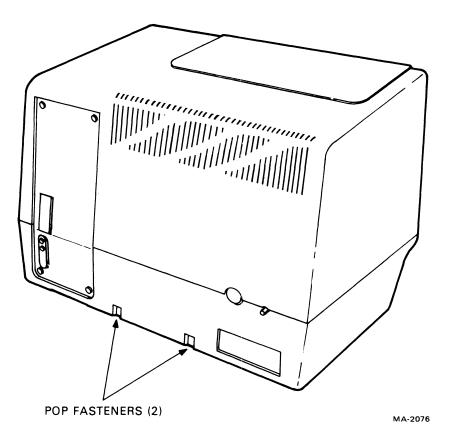

| 5.4.2   | Access Cover                            |       |

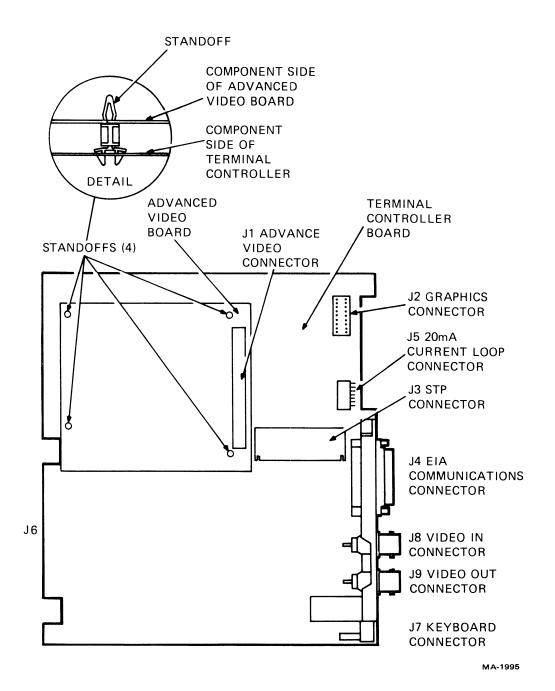

| 5.4.3   | Terminal Controller Board               |       |

| 5.4.4   | Advanced Video Board                    |       |

|         |                                         |       |

| 5.4.5   | VT105 Waveform Generator Board          |       |

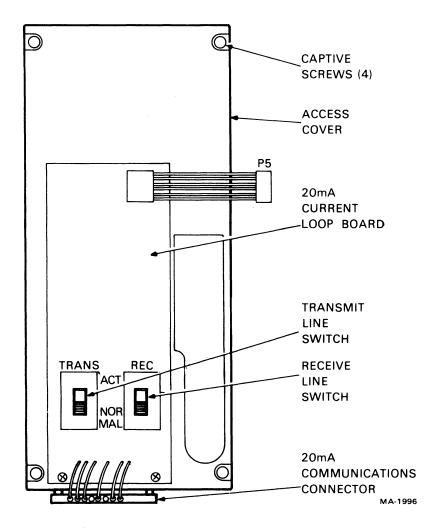

| 5.4.6   | 20 mA Current Loop Board                |       |

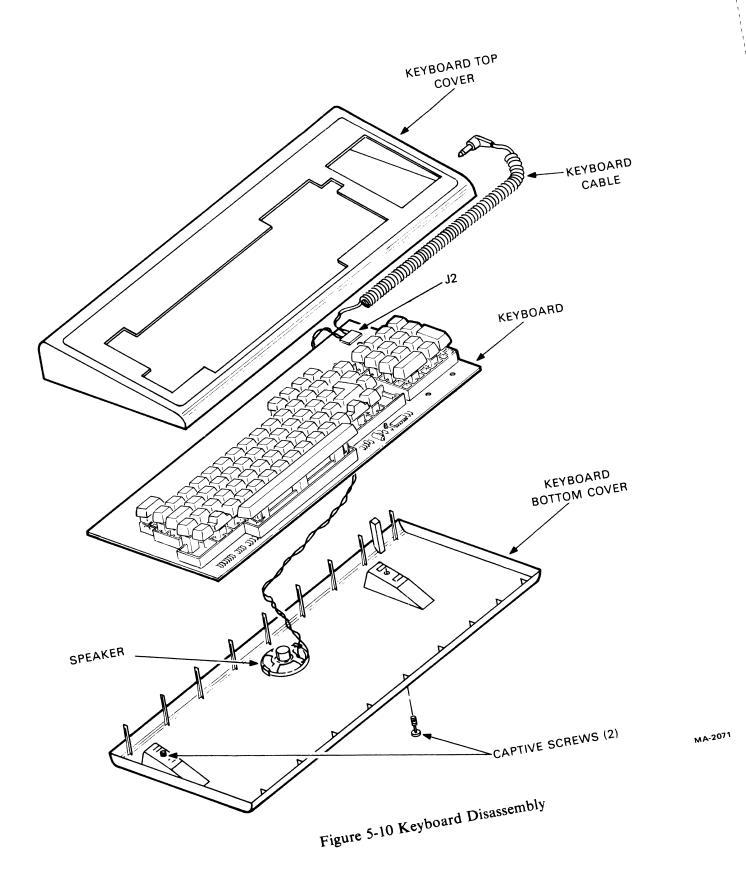

| 5.4.7   | Keyboard Top Cover                      |       |

| 5.4.8   | Keyboard                                |       |

| 5.4.9   | Keyboard Cable                          |       |

| 5.4.10  | Keyboard Speaker                        |       |

| 5.4.11  | Terminal Top Cover                      |       |

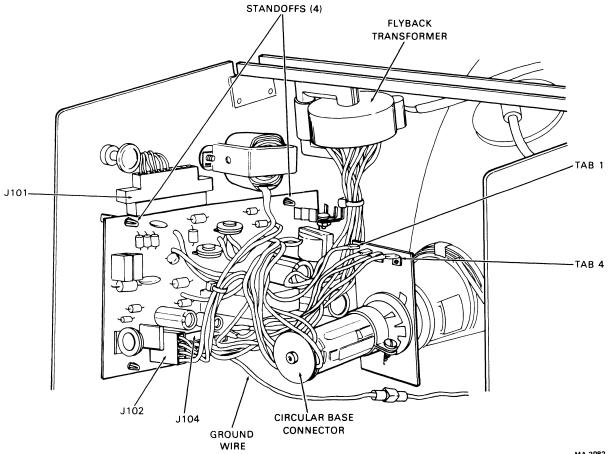

| 5.4.12  | Video Monitor Board (Ball Monitor)      |       |

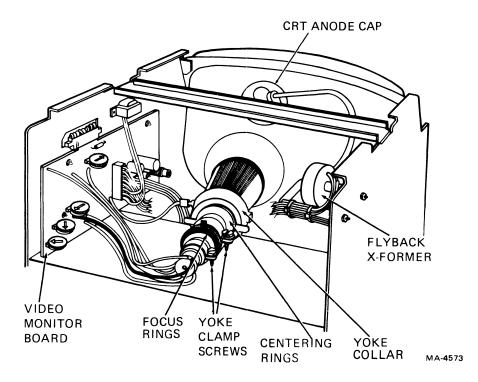

| 5.4.13  | Flyback Transformer (Ball Monitor)      |       |

| 5.4.14  | Video Monitor Board (Elston)            |       |

| 5.4.15  | Flyback Transformer (Elston)            | 5-38  |

| 5.4.16  | Terminal Bottom Cover                   | 5-39  |

| 5.4.17  | Power Supply                            | 5-39  |

| 5.4.18  | VT100 DC Power Harness                  |       |

| 5.4.19  | VT105 DC Power Harness                  | 5-42  |

| 5.4.20  | VT105 Expansion Backplane Removal and   |       |

|         | Installation                            | 5-44  |

| 5.4.21  | Field Service CRT Monitor Assembly      | 5-44  |

| 5.4.22  | CRT Storage and Disposal                |       |

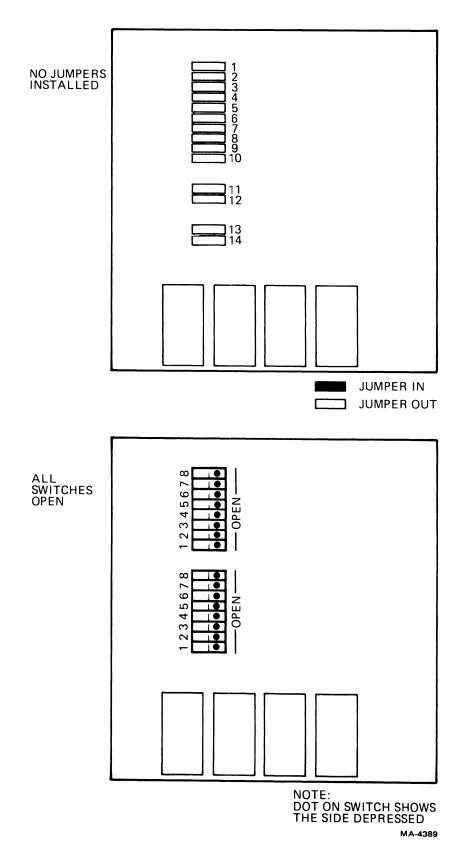

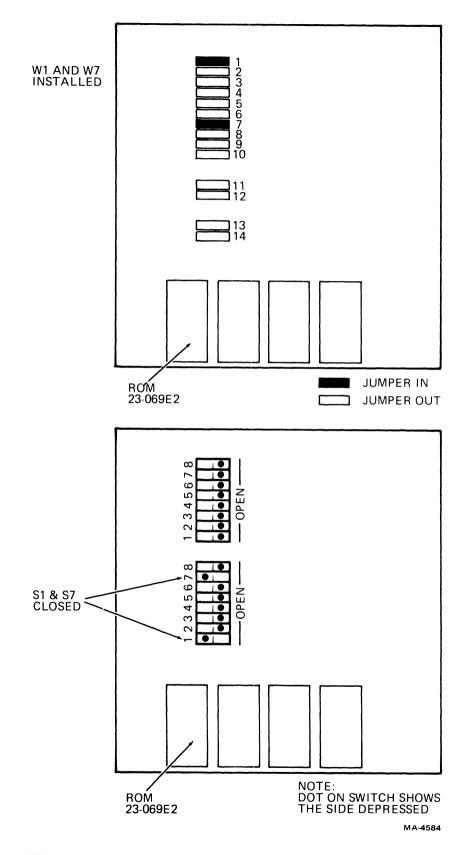

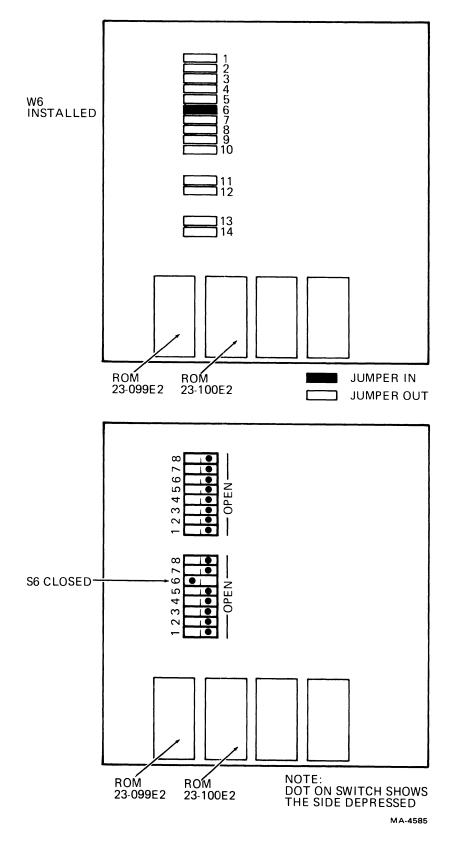

| 5.5     | Board Configurations                    |       |

| 5.5.1   | Terminal Controller Board               |       |

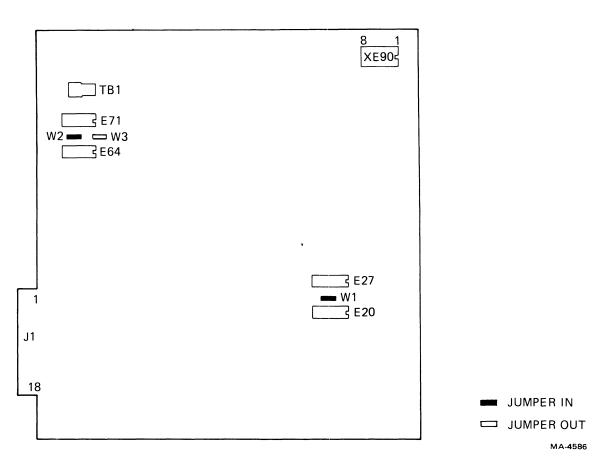

| 5.5.2   | Advanced Video Board                    |       |

|         | VT105 Waveform Generator Board          |       |

| 5.5.3   |                                         |       |

| 5.6     | Component Level Troubleshooting         |       |

| 5.6.1   | Troubleshooting the Terminal Controller |       |

| 5.6.1.1 | Microprocessor                          | 2-20  |

| Video Processor              | 5-52                                                                                                                                     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Communications               |                                                                                                                                          |

| Nonvolatile RAM              | 5-54                                                                                                                                     |

| Troubleshooting the Keyboard | 5-54                                                                                                                                     |

|                              |                                                                                                                                          |

|                              |                                                                                                                                          |

| Troubleshooting the Options  |                                                                                                                                          |

|                              | Communications<br>Nonvolatile RAM<br>Troubleshooting the Keyboard<br>Troubleshooting the Power Supply<br>Troubleshooting the CRT Monitor |

# **CHAPTER 6 OPTIONS**

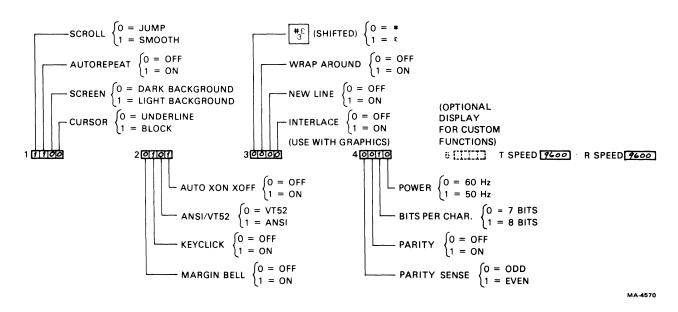

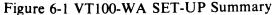

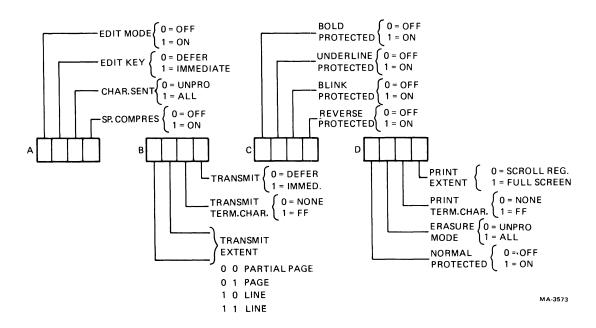

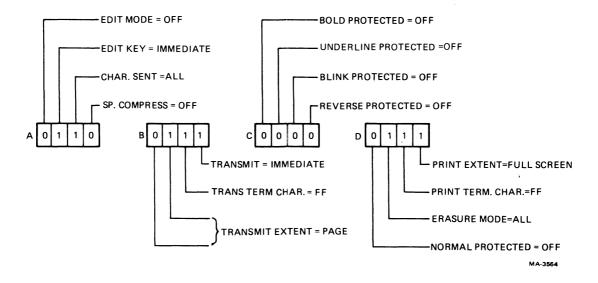

| 6.1      | SET-UP Procedures for VT100 Series Options | 6-1  |

|----------|--------------------------------------------|------|

| 6.1.1    | VT100-WA and VT100-WB SET-UP               |      |

| 6.1.2    |                                            | 6-2  |

| 6.1.3    | VT132 SET-UP                               | 6-2  |

| 6.1.3.1  | VT132 SET-UP A                             | 6-2  |

| 6.1.3.2  | VT132 SET-UP B                             | 6-2  |

| 6.1.3.3  | VT132 SET-UP C                             | 6-2  |

| 6.1.3.4  | Changing a VT132 SET-UP Feature            | 6-2  |

| 6.1.3.5  | Setting the VT132 Answerback Message       |      |

| 6.1.3.6  | Setting the VT132 Transmit Parity          | 6-6  |

| 6.1.3.7  | Saving VT132 SET-UP Features               | 6-6  |

| 6.1.3.8  | Recalling VT132 SET-UP Features            | 6-6  |

| 6.1.3.9  | VT132 Default Feature Settings             | 6-6  |

| 6.1.3.10 | VT132 Tab Default                          |      |

| 6.1.3.11 | VT132 General Default                      | 6-6  |

| 6.1.3.12 | Resetting the VT132                        | 6-6  |

| 6.2      | Advanced Video Option                      |      |

| 6.2.1    | Advanced Video Option Installation         |      |

| 6.2.2    | Advanced Video Option Checkout             |      |

| 6.2.3    | Program Memory Expansion                   | 6-10 |

| 6.2.4    | Alternate Character Set                    |      |

| 6.2.4.1  | Alternate ROM Description                  | 6-11 |

| 6.2.4.2  | Character ROM Programming                  |      |

|          | Instructions                               | 6-12 |

| 6.2.5    | AVO Technical Description                  | 6-12 |

| 6.2.5.1  | Extended Character and Attribute           |      |

|          | Memory                                     |      |

| 6.2.5.2  | Character Attribute Latches                |      |

| 6.2.5.3  | Program ROM Decoding                       |      |

| 6.2.6    | Troubleshooting the AVO                    |      |

| 6.3      | 20 mA Current Loop Adapter                 |      |

| 6.3.1    | 20 mA Current Loop Option Installation     |      |

| 6.3.2    | Configurations                             | 6-14 |

| 6.3.3    | 20 mA Current Loop Option Checkout         |      |

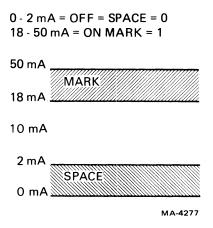

| 6.3.4    | Current Loop Principles                    | 6-15 |

| 6.3.4.1  | Current Loop Adapter Description           |      |

| 6.3.5    | Interface Signals                          |      |

| 6.3.6    | Interface Specifications                   | 6-17 |

| 6.3.7    | Troubleshooting the Current Loop Adapter   |      |

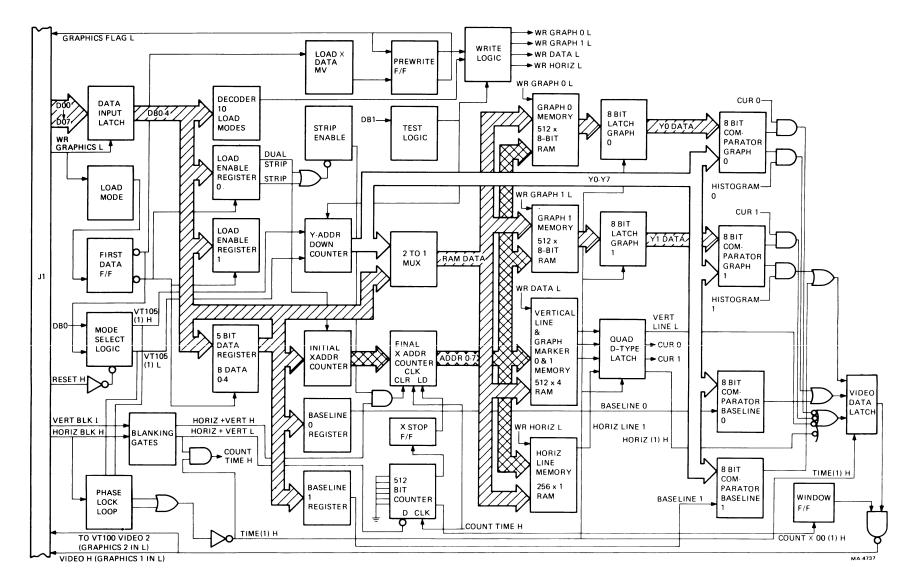

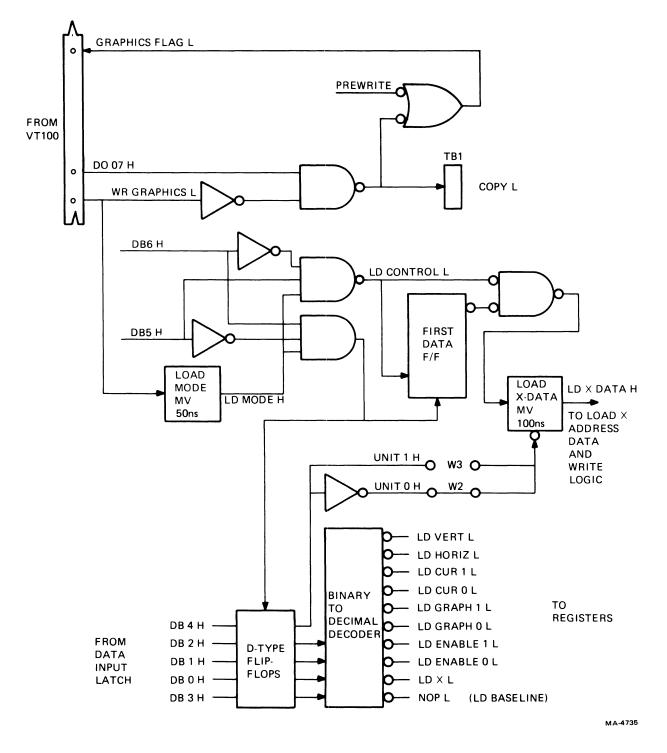

| 6.4      | VT105 Graphics Processor                   | 6-18 |

| 6.4.1    | Enabling Graphic Information               | 6-18 |

| 6.4.1.1  | Writing Data to the Waveform               |      |

|          | Generator                                  | 6-19 |

| 6.4.1.2  | Reading Data from the Waveform         |      |

|----------|----------------------------------------|------|

|          | Generator                              |      |

| 6.4.1.3  | Decoding the Input                     | 6-21 |

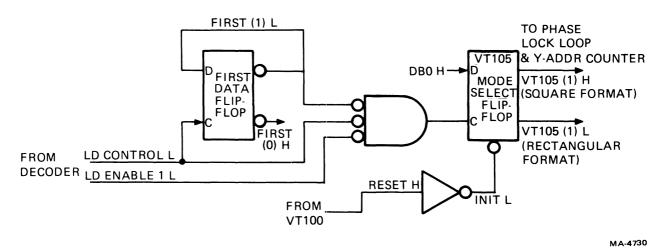

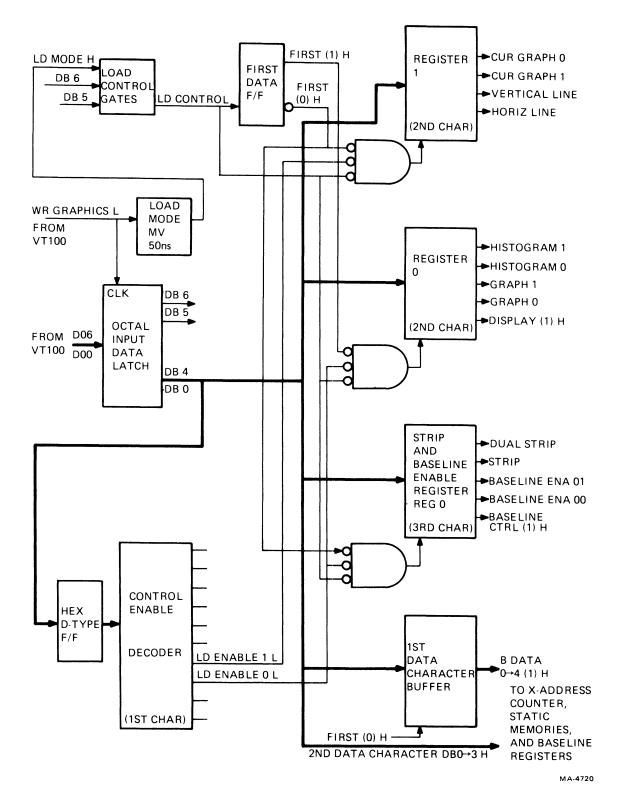

| 6.4.1.4  | Selecting Mode of Operation            |      |

| 6.4.1.5  | Decoding Field Selection               |      |

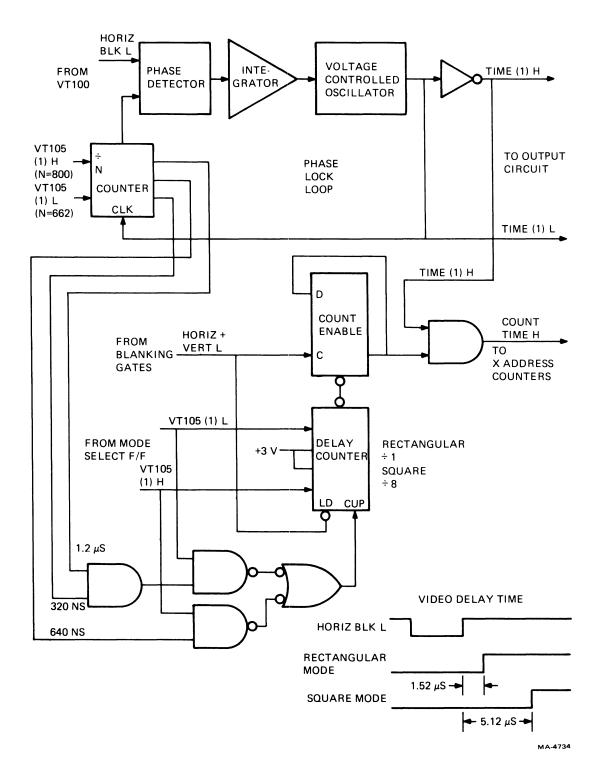

| 6.4.1.6  | Phase Lock Loop Timing                 |      |

| 6.4.1.7  | Establishing Desired Display           |      |

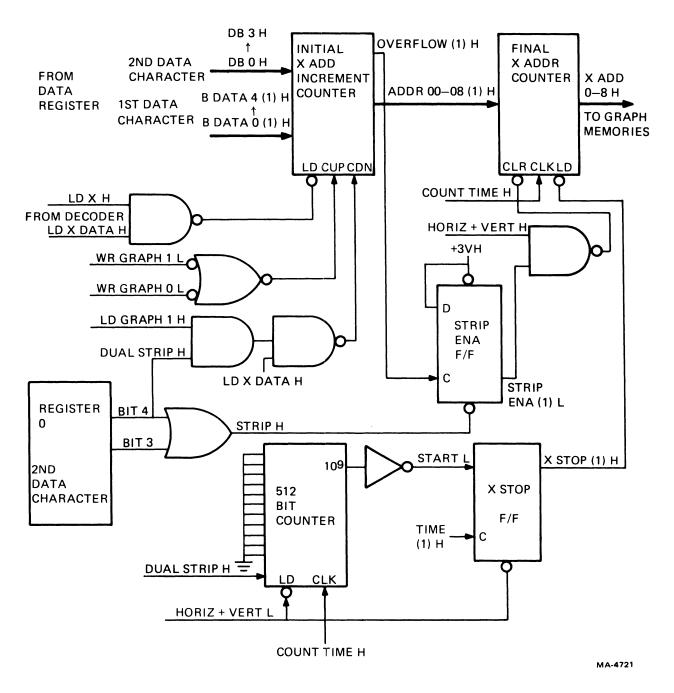

| 6.4.1.8  | Loading X-Address Information          |      |

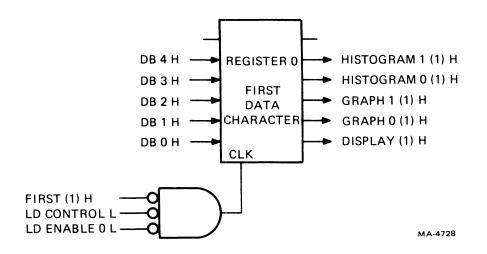

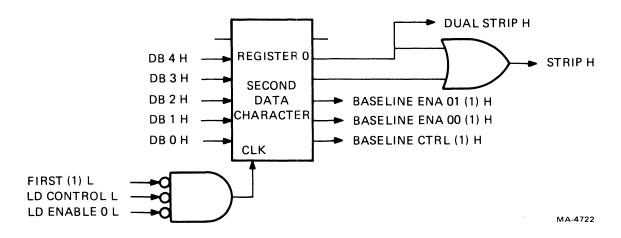

| 6.4.1.9  | Loading Graph Memories                 | 6-30 |

| 6.4.1.10 | Generating Baselines (Shade Lines)     |      |

| 6.4.1.11 | Enabling a Histogram (Shading a        |      |

|          | Graph)                                 | 6-32 |

| 6.4.1.12 | Loading Vertical Lines                 | 6-32 |

| 6.4.1.13 | Adding Graph Marker                    | 6-36 |

| 6.4.1.14 | Generating Horizontal Lines            | 6-36 |

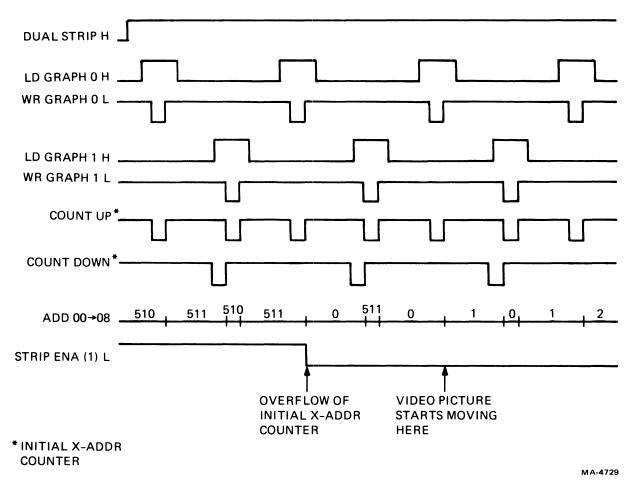

| 6.4.1.15 | Generating Strip Charts                | 6-36 |

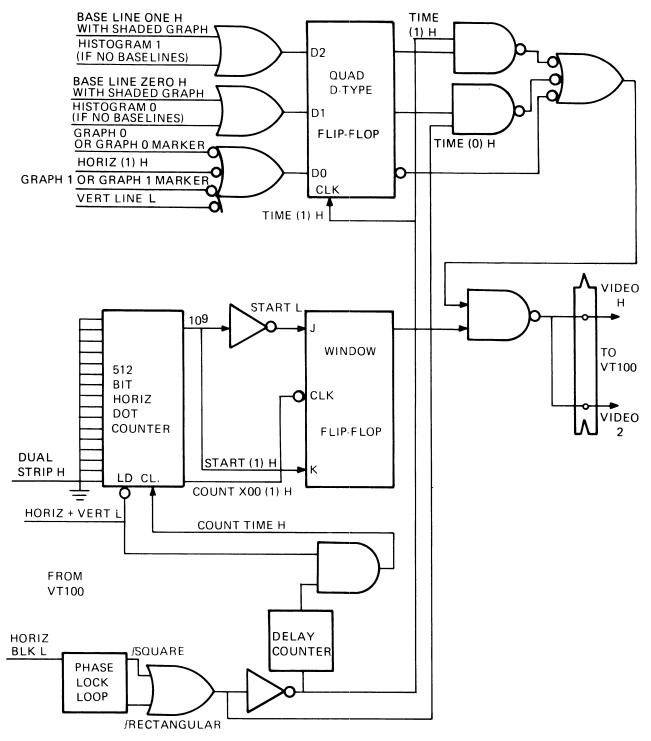

| 6.4.1.16 | Combining Video Out and Timing         | 6-41 |

| 6.4.2    | VT105 Graphic Test Procedure           | 6-43 |

| 6.4.2.1  | Test Set-Up                            | 6-43 |

| 6.4.2.2  | Test Graph 0, Histogram 0, and Graph 0 |      |

|          | Markers                                | 6-44 |

| 6.4.2.3  | Test Graph 1, Histogram 1, and Graph 1 |      |

|          | Markers                                | 6-46 |

| 6.4.2.4  | Test the Horizontal Lines              | 6-46 |

| 6.4.2.5  | Test the Vertical Lines                | 6-46 |

| 6.4.2.6  | Test Shade Line 0 (Baseline 0)         | 6-48 |

| 6.4.2.7  | Test Shade Line 1 (Baseline 1)         | 6-49 |

| 6.4.2.8  | Test Strip Chart 0                     | 6-50 |

| 6.4.2.9  | Test Strip Chart 1                     |      |

| 6.4.2.10 | Exit the Graphic Test Mode             | 6-51 |

# CHAPTER 7 STANDARD TERMINAL PORT

| 7.1     | Introduction                      | 7-1  |

|---------|-----------------------------------|------|

| 7.2     | Definitions                       | 7-1  |

| 7.3     | Overview                          | 7-2  |

| 7.4     | Functional Specifications         | 7-3  |

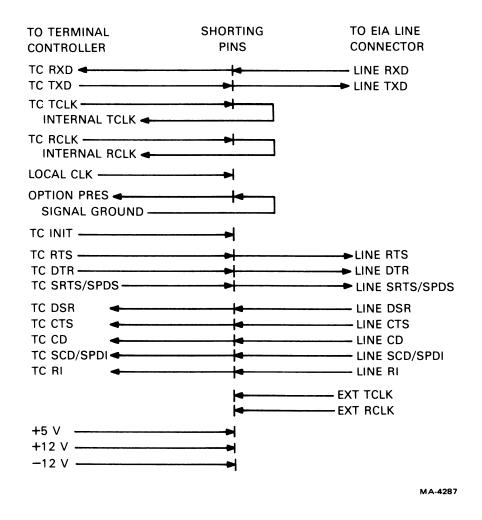

| 7.4.1   | Interface Signal Lines            | 7-3  |

| 7.4.2   | Protocol Specifications           | 7-6  |

| 7.4.2.1 | Terminal Operation With No Option |      |

|         | Present                           | 7-6  |

| 7.4.2.2 | Standard Set-Up For Local Link    | 7-6  |

| 7.4.2.3 | Control Sequences For Terminal    |      |

|         | Parameters                        | 7-7  |

| 7.4.2.4 | Initialization                    | 7-9  |

| 7.4.2.5 | BREAK                             | 7-9  |

| 7.5     | Electrical Specifications         | 7-9  |

| 7.5.1   | Signal Lines                      | 7-9  |

| 7.5.1.1 | Signal Levels                     |      |

| 7.5.1.2 | Signal Timing                     |      |

| 7.5.2   | Power Supply Lines                |      |

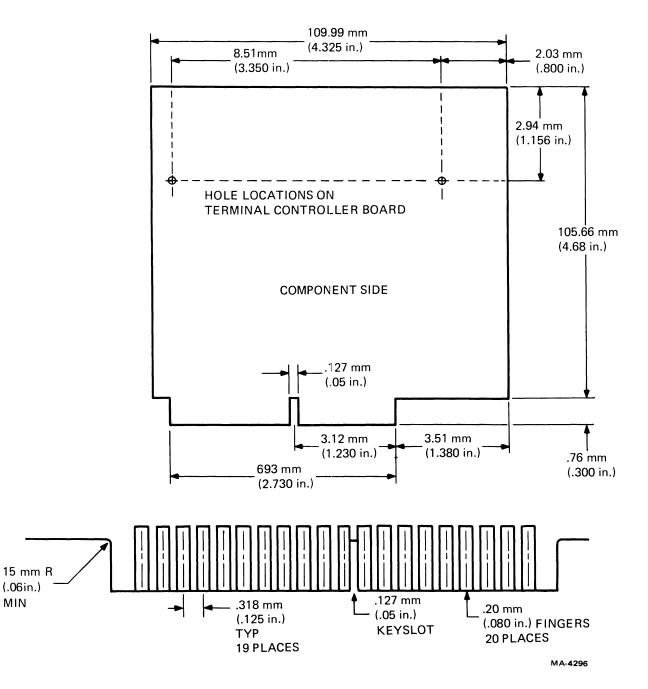

| 7.5.3   | Connector Pinout                  | 7-10 |

| 7.6     | Mechanical Specifications         |      |

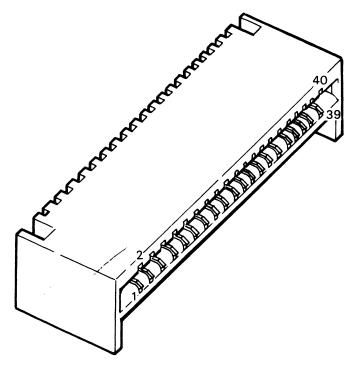

| 7.6.1   | Shorting Connector                   | 7-10 |

|---------|--------------------------------------|------|

| 7.6.2   | STP Connector Card                   | 7-10 |

| 7.7     | Guidelines for the Designer          |      |

| 7.7.1   | Use with Receive Only Device         |      |

| 7.7.1.1 | Single UART Method                   |      |

| 7.7.1.2 | Two UART Method                      | 7-13 |

| 7.7.2   | Use With Passive Device              |      |

| 7.7.3   | Use With Active Device               | 7-13 |

| 7.7.3.1 | Terminal Processor as Standalone CPU |      |

| 7.7.3.2 | Terminal Processor Augmenting Basic  |      |

|         | Terminal Operation                   | 7-14 |

| 7.7.4   | Use With Communications Option       |      |

| 7.7.5   | Use With An External Processor       | 7-14 |

| 7.7.6   | Use With More Than One Option        | 7-14 |

## CHAPTER 8 GRAPHICS CONNECTOR

| 8.1 | Introduction    | 8-1 |

|-----|-----------------|-----|

|     | Hardcopy Enable |     |

## APPENDIX A PROGRAMMING INFORMATION

## APPENDIX B RECOMMENDED SPARES LIST (RSL)

## APPENDIX C GLOSSARY OF TERMS AND ABBREVIATIONS

## **FIGURES**

| 2-1   | VT100 Keyboard                  |      |

|-------|---------------------------------|------|

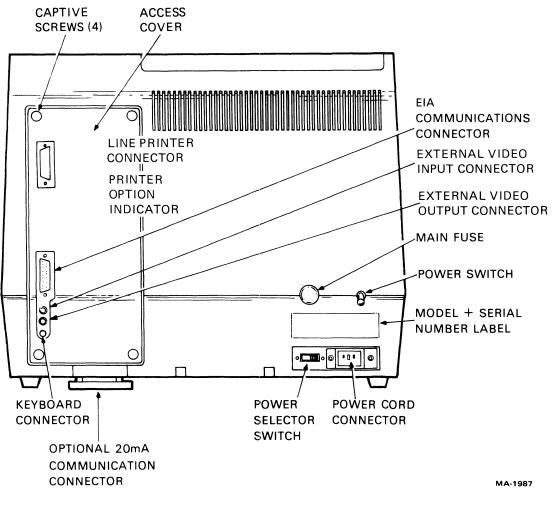

| 2-2   | VT100 Terminal (Rear View)      | 2-6  |

| 2-3   | SET-UP A Mode Presentation      | 2-7  |

| 2-4   | SET-UP B Mode Presentation      | 2-8  |

| 2-5   | SET-UP B Mode Summary           | 2-9  |

| 3-1   | VT100 Terminal Dimensions       | 3-2  |

| 3-2   | VT100 Rear View                 | 3-3  |

| 3-3   | 20 mA Current Loop Interface    | 3-7  |

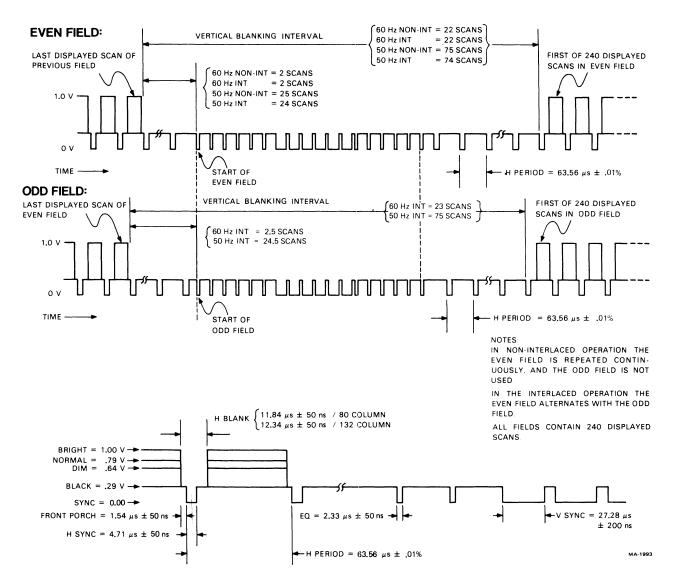

| 3-4   | Composite Video Output          |      |

| 4-1-1 | VT100 Components                |      |

| 4-1-2 | Functional Block Diagram        |      |

| 4-1-3 | VT100 Firmware Block Diagram    | 4-8  |

| 4-2-1 | 8080 Block Diagram              | 4-10 |

| 4-2-2 | Microprocessor Block Diagram    | 4-12 |

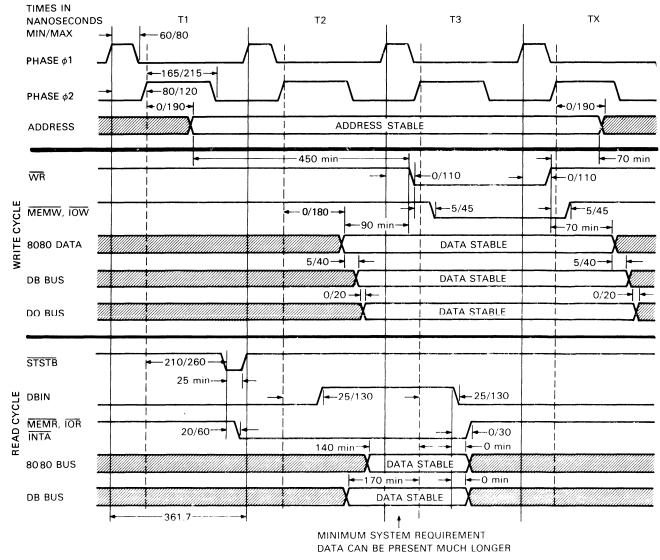

| 4-2-3 | Microprocessor Bus Timing       | 4-14 |

| 4-2-4 | Memory Map                      |      |

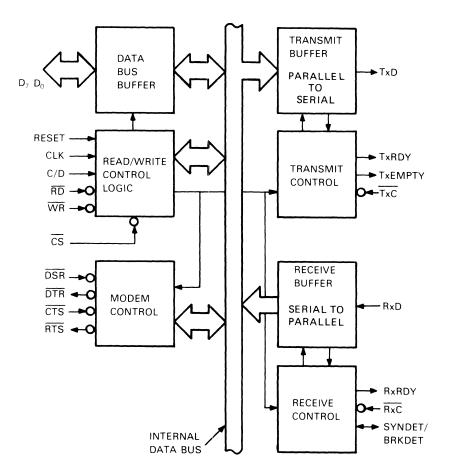

| 4-3-1 | 8251A PUSART Block Diagram      | 4-21 |

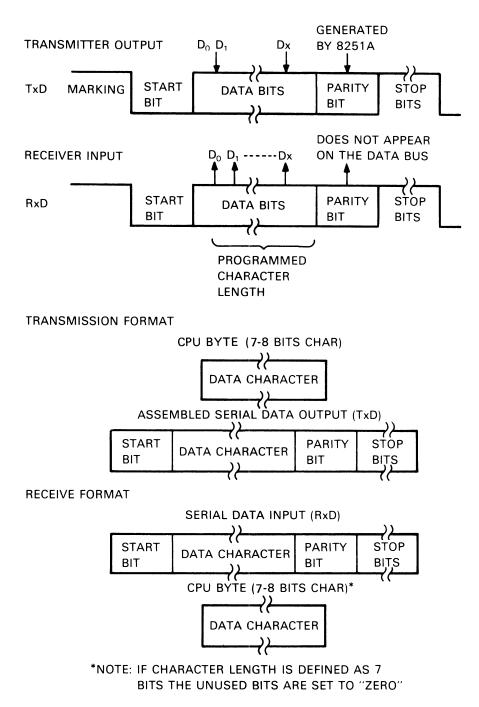

| 4-3-2 | Asynchronous Data Format        |      |

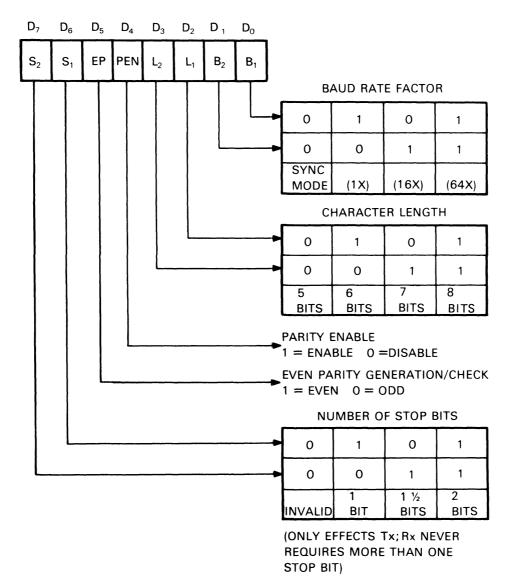

| 4-3-3 | Mode Instruction                | 4-24 |

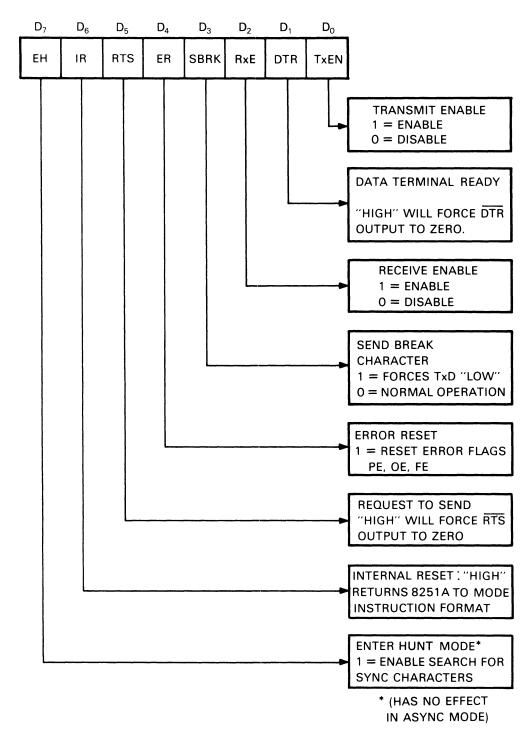

| 4-3-4 | Command Instruction             | 4-25 |

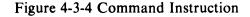

| 4-3-5 | Status Byte Format              | 4-26 |

| 4-4-1 | Keyboard Block Diagram          | 4-31 |

| 4-4-2 | Keyboard Status Byte            |      |

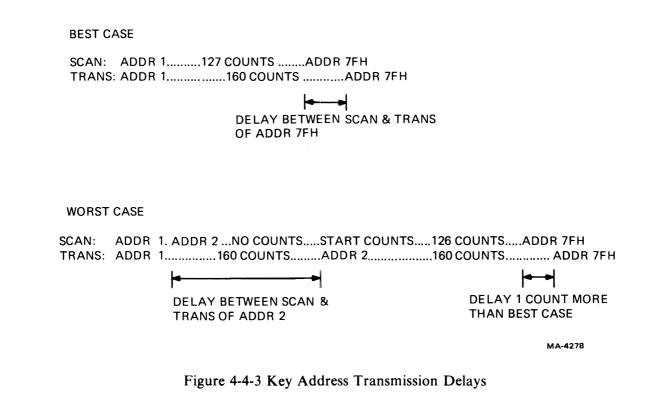

| 4-4-3 | Key Address Transmission Delays | 4-33 |

|       |                                 |      |

| 4-4-4          | Keyboard Switch Array                       | 4-35   |

|----------------|---------------------------------------------|--------|

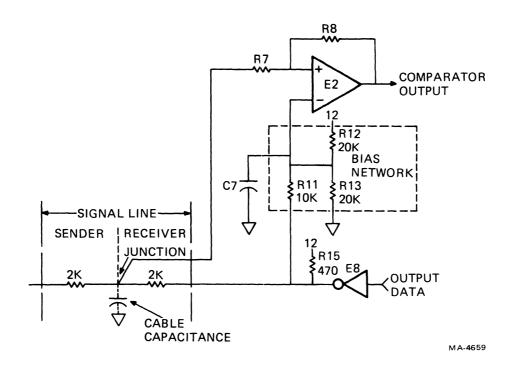

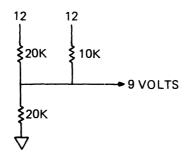

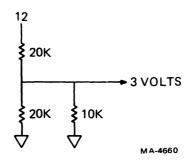

| 4-4-5A         | Keyboard Interface Circuit                  | 4-36   |

| 4-4-5B         | Bias Network – E8 High                      |        |

| 4-4-5C         | Bias Network – E8 Low                       | 4-36   |

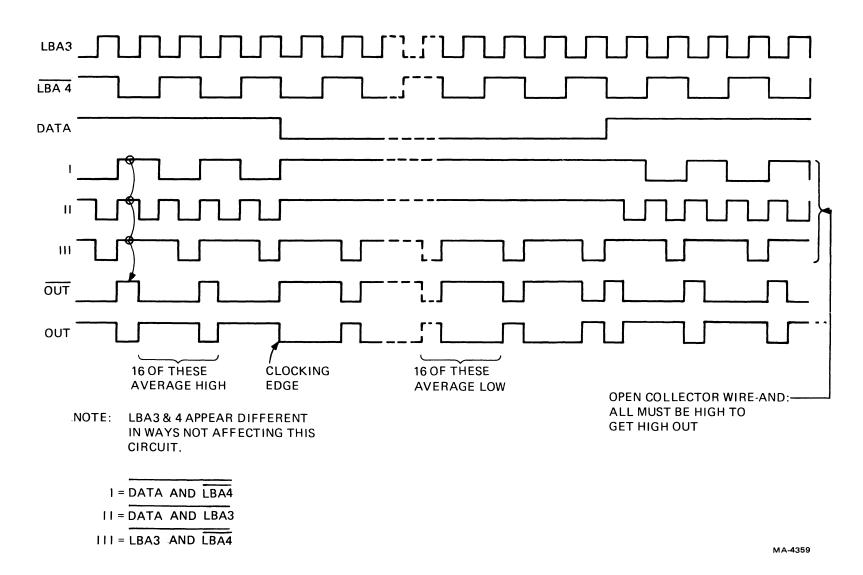

| 4-4-6          | Encoding of Terminal Data and Clock         | 4-30   |

| 4-4-7          | Four Keyboard Interface States              |        |

| 4-4-8          | Keyboard Interface Signal                   | A-40   |

| 4-4-9          | Bell Circuit                                | A A1   |

| 4-4-10         | Keys Flag Byte                              |        |

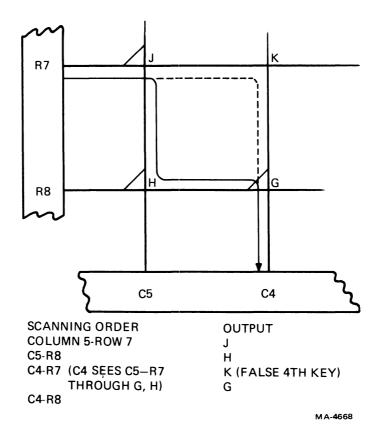

| 4-4-11         | Sneak Path                                  |        |

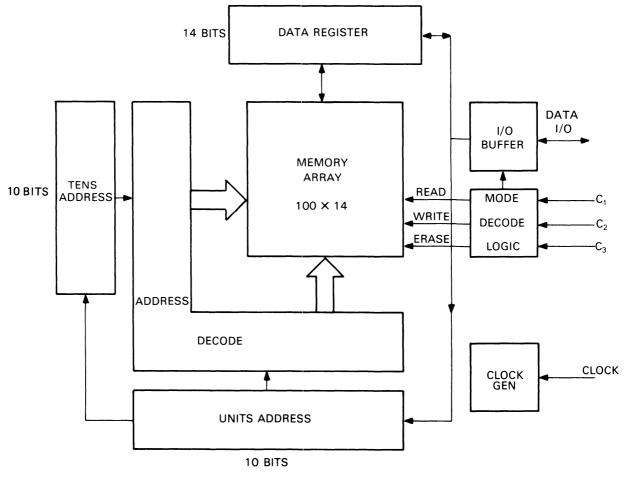

| 4-5-1          | ER1400 NVR Block Diagram                    |        |

| 4-5-2          | NVR Signals                                 |        |

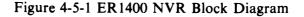

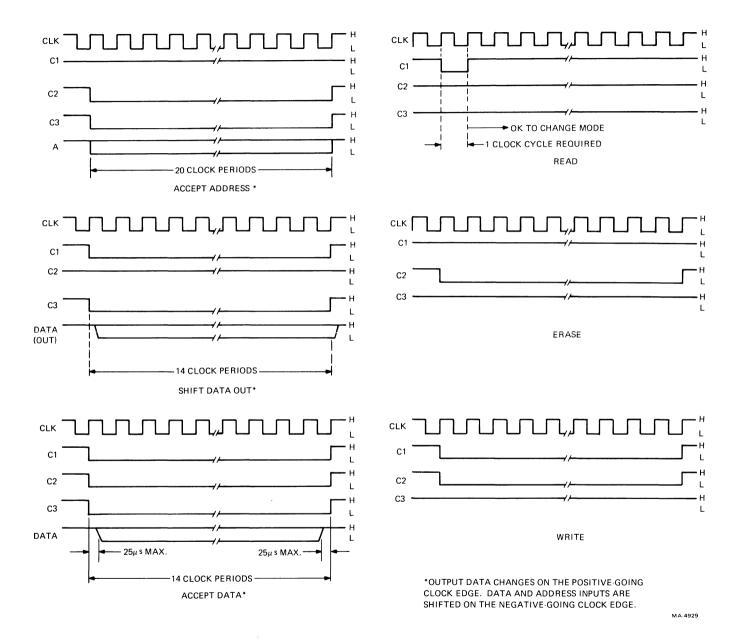

| 4-5-3          | NVR Timing Diagrams                         | 4-40   |

| <b>4-6-</b> 1  | Video Processor Block Diagram.              |        |

| 4-6-2          | Dots, Scans, and Characters                 |        |

| 4-6-3          | Video Processor Functional Diagram.         |        |

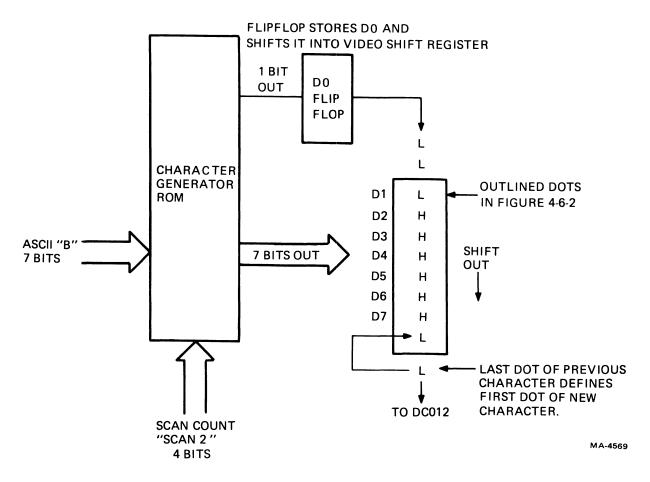

| 4-6-4          | Character Generator Example                 |        |

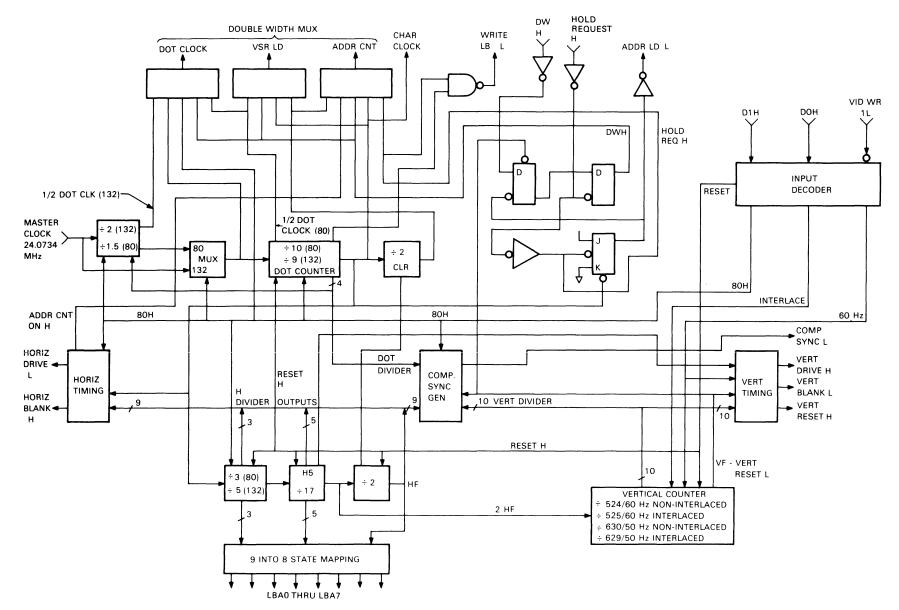

| 4-6-5          | DC011 Block Diagram                         |        |

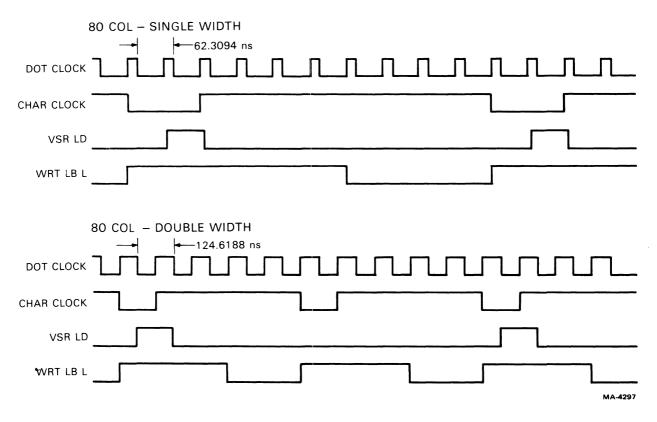

| 4-6-6          | Video Latch Timing – 80 Column              |        |

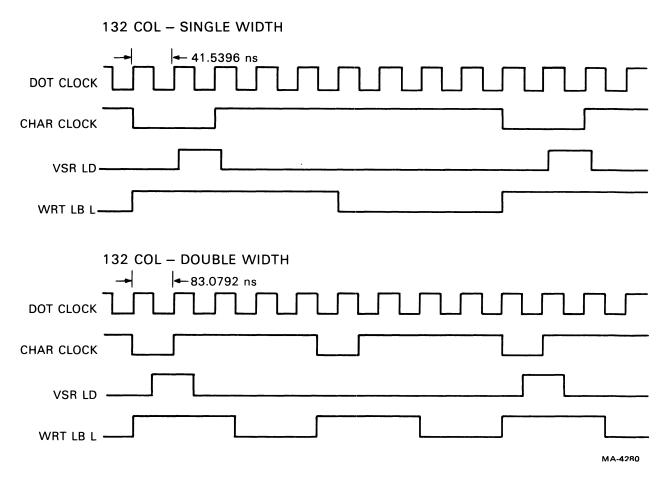

| 4-6-7          | Video Latch Timing – 30 Column              | . 4-57 |

| 4-6-8          | Address Count Timing – 152 Column           | . 4-30 |

| 4-0-8<br>4-6-9 | Address Count Timing                        |        |

| 4-6-10         | Horizontal Timing.                          | 4-01   |

|                | Line Buffer Address Outputs – 80 Column     |        |

| 4-6-11         | Line Buffer Address Outputs – 132 Column    |        |

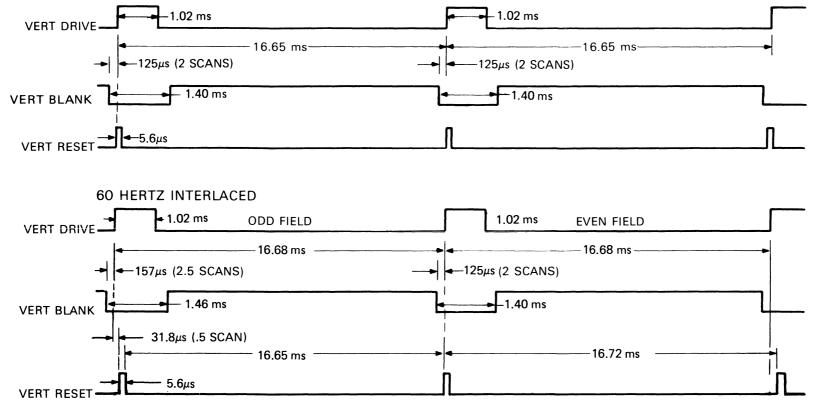

| 4-6-12         | Vertical Signals – 60 Hz                    | . 4-05 |

| 4-6-13         | Vertical Signals – 50 Hz                    |        |

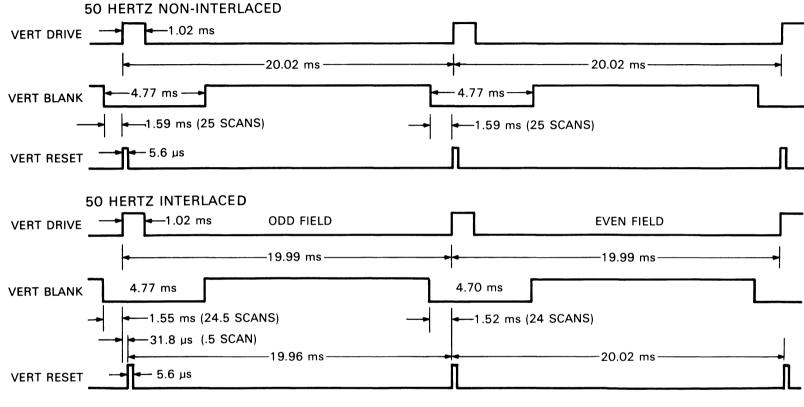

| 4-6-14         | Composite Sync Output                       | . 4-08 |

| 4-6-15         | DC012 Block Diagram.                        |        |

| 4-6-16         | Dot Stretching.                             |        |

| 4-6-17         | Dot Stretcher Example                       |        |

| 4-6-18         | Character Generator ROM Patterns            |        |

| 4-6-19         | DMA Cycle Timing Diagram                    | . 4-81 |

| 4-6-20         | Character Latch Timing                      |        |

| 4-6-21         | Video Blanking                              |        |

| 4-7-1          | Line Organization                           |        |

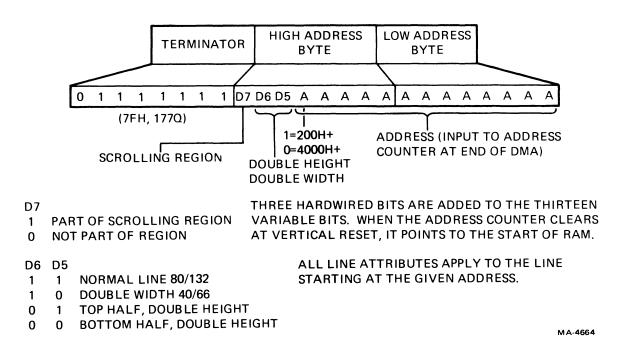

| 4-7-2          | Terminator and Address Bytes                |        |

| 4-7-3          | Screen RAM Organization – 80 Column, 60 Hz. |        |

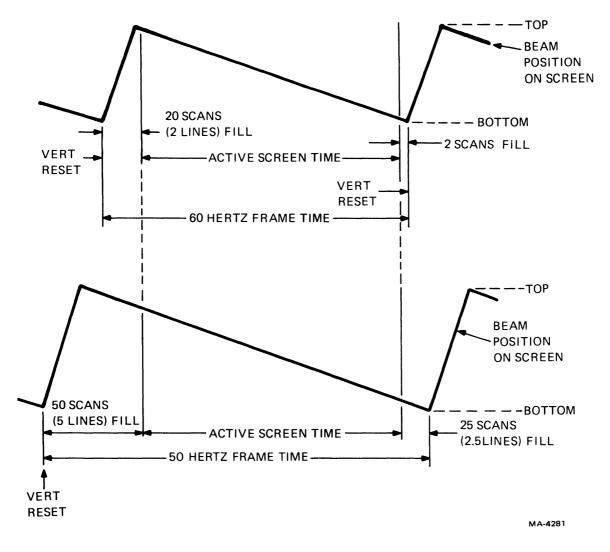

| 4-7-4          | Need for Fill Lines                         |        |

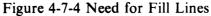

| 4-7-5          | Fill Line Operation – 60 Hz.                |        |

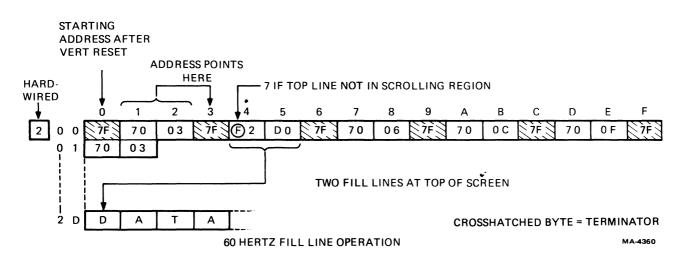

| 4-7-6          | Fill Line Operation – 50 Hz.                |        |

| 4-7-7          | End Of Screen Fill Line Operation           |        |

| 4-7-8          | Line Address Offset Table                   |        |

| 4-7-9          | Full Screen Address Shuffling               |        |

| 4-7-10         | Split Screen Address Shuffle                | . 4-90 |

| 4-7-11         | Split Screen Smooth Scroll at Midpoint      | 4-9/   |

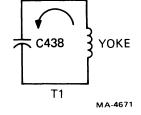

| 4-8-1          | Horizontal Deflection Current – T0          |        |

| 4-8-2          | Horizontal Deflection Current – T1          |        |

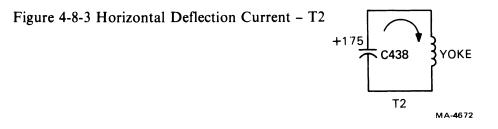

| 4-8-3          | Horizontal Deflection Current – T2          |        |

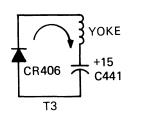

| 4-8-4          | Horizontal Deflection Current – T3          |        |

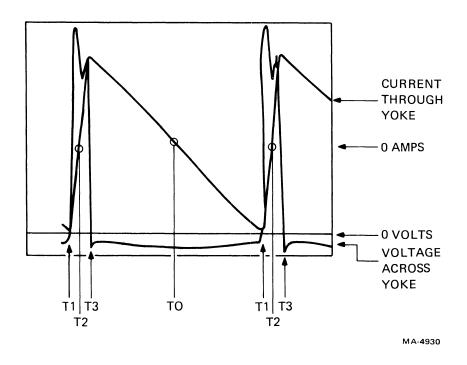

| 4-8-5          | Horizontal Deflection Waveforms             |        |

| 4-9-1          | VT100 Power Supply Block Diagram            |        |

| 4-9-2          | 3524 Regulator Block Diagram                |        |

| 4-9-3          | Power Supply Timing Diagram                 | 4-109  |

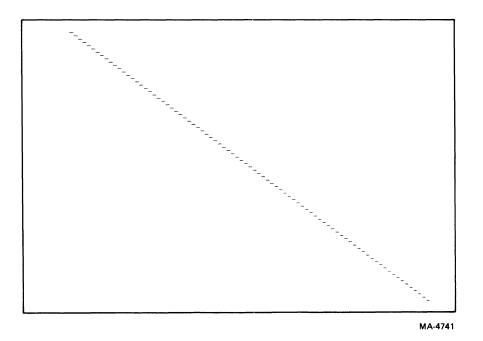

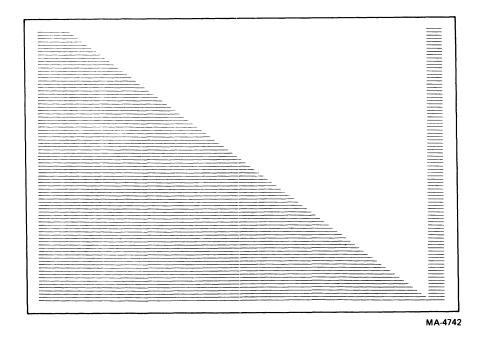

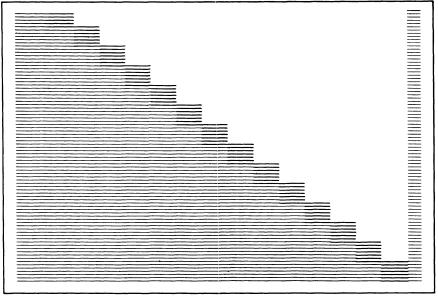

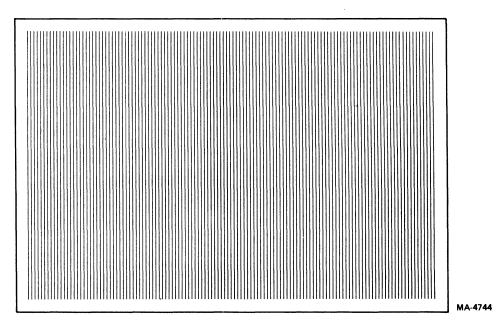

| 5-1   | Video Alignment Templates                    | 5-13 |

|-------|----------------------------------------------|------|

| 5-2   | Ball Video Monitor Board Adjustments         |      |

| 5-3   | Ball Monitor CRT Adjustments                 |      |

| 5-4   | Elston Video Monitor Board Adjustments       |      |

| 5-5   | Elston Monitor CRT Adjustments               |      |

| 5-6   | Removal Procedures Flowchart                 |      |

| 5-7   | VT100 Terminal (Rear View)                   |      |

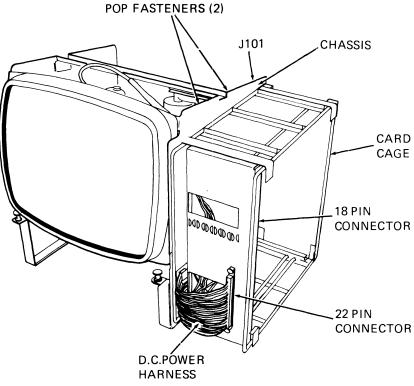

| 5-8   | VT105 Interconnections                       |      |

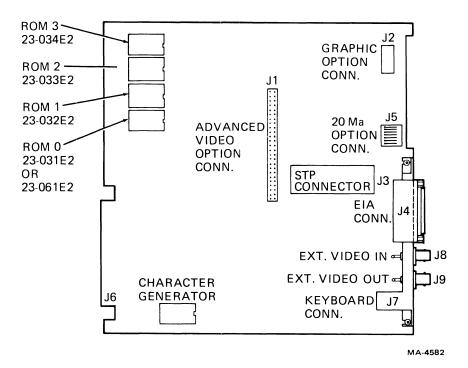

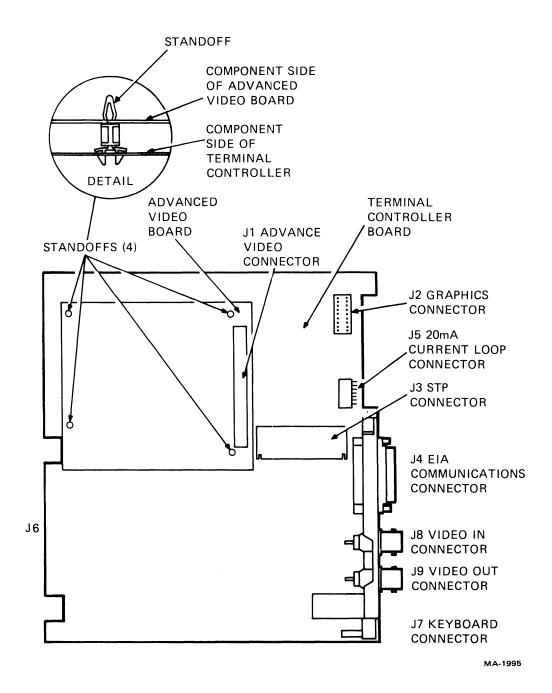

| 5-9   | Terminal Controller with AVO                 |      |

| 5-10  | Keyboard Disassembly                         |      |

| 5-11a | Top Cover Removal (Front View)               |      |

| 5-11b | Top Cover Removal (Rear View)                | 5-34 |

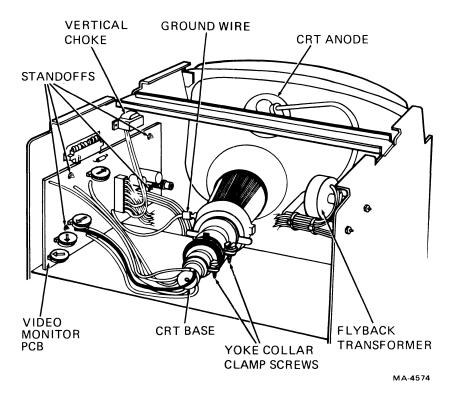

| 5-12  | Ball Video Monitor Board Removal.            | 5-35 |

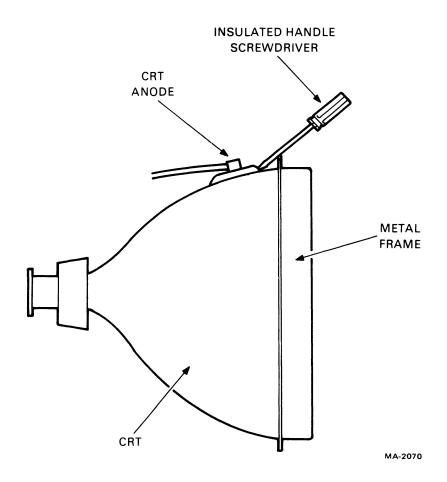

| 5-13  | CRT Anode Discharging.                       |      |

| 5-14  | Elston Video Monitor Board Removal           |      |

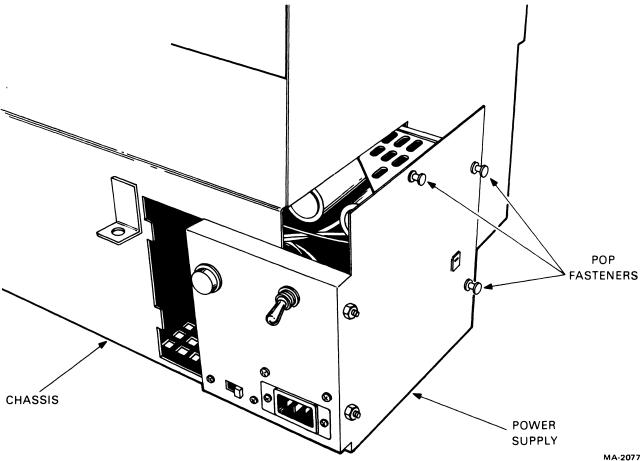

| 5-15  | Power Supply Removal                         |      |

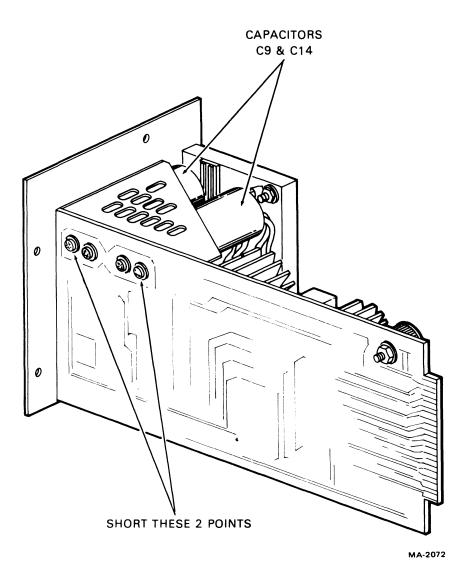

| 5-16  | Power Supply Capacitor Discharging           |      |

| 5-17  | VT100 DC Power Harness Removal               | 5_42 |

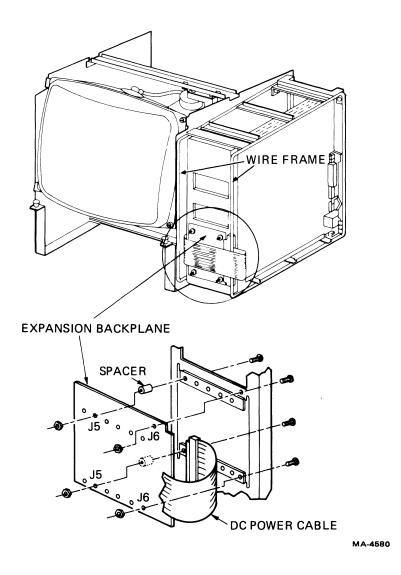

| 5-18  | VT105 Expansion Backplane Removal            |      |

| 5-19  | Terminal Controller Board, VT100             | 5-45 |

| 5-19  | Configuration                                | 5-45 |

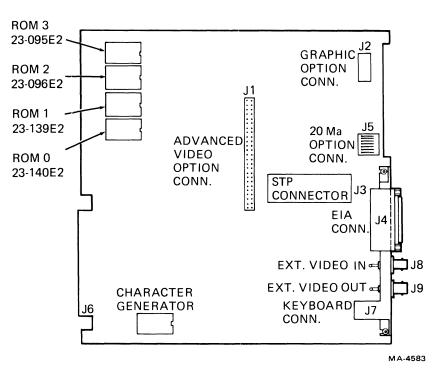

| 5-20  | Terminal Controller Board, VT132             | 5-45 |

| 5-20  | Configuration                                | 5 16 |

| 5-21  | Advanced Video Board, VT100 Configuration    |      |

| 5-22  |                                              | 5-47 |

| 3-22  | Advanced Video Board, VT100-WA/WB            | E 40 |

| 5.00  | Configuration                                |      |

| 5-23  | Advanced Video Board, VT132 Configuration    |      |

| 5-24  | VT105 Waveform Generator Board Configuration |      |

| 6-1   | VT100-WA SET-UP Summary                      |      |

| 6-2   | VT100-WB SET-UP Summary.                     |      |

| 6-3   | VT132 SET-UP B Presentation                  |      |

| 6-4   | VT132 SET-UP B Summary                       |      |

| 6-5   | VT132 SET-UP C Presentation                  |      |

| 6-6   | VT132 SET-UP C Summary                       |      |

| 6-7   | VT132 SET-UP B Default Summary               |      |

| 6-8   | VT132 SET-UP C Default Summary               |      |

| 6-9   | Advanced Video Option Installation           |      |

| 6-10  | 20 mA Current Loop Option                    |      |

| 6-11  | Interface States                             |      |

| 6-12  | M7071 Waveform Generator Block Diagram       |      |

| 6-13  | Decoding the Control Character               |      |

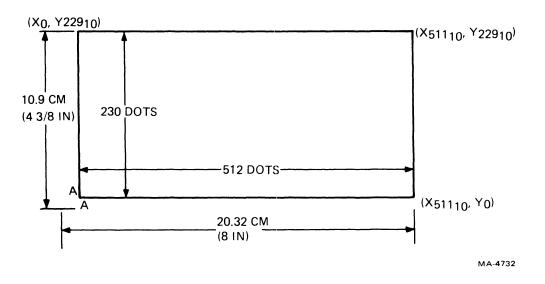

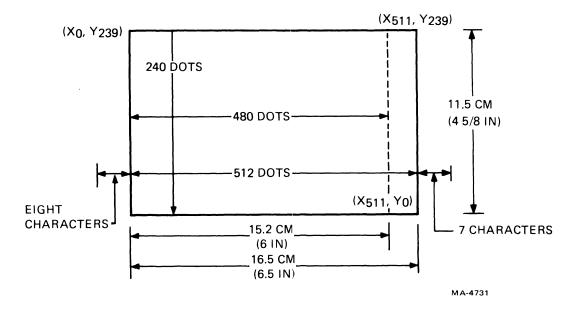

| 6-14  | Rectangular Aspect Ratio Graph Drawing Field |      |

| 6-15  | Square Aspect Ratio Graph Drawing Field      |      |

| 6-16  | Selecting Mode of Operation                  |      |

| 6-17  | Phase Lock Loop Timing                       |      |

| 6-18  | Loading the Registers                        |      |

| 6-19  | Register 0 (1st Data Character).             |      |

| 6-20  | Register 0 (2nd Data Character)              |      |

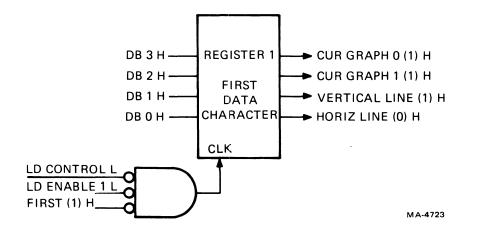

| 6-21  | Register 1 (1st Data Character).             |      |

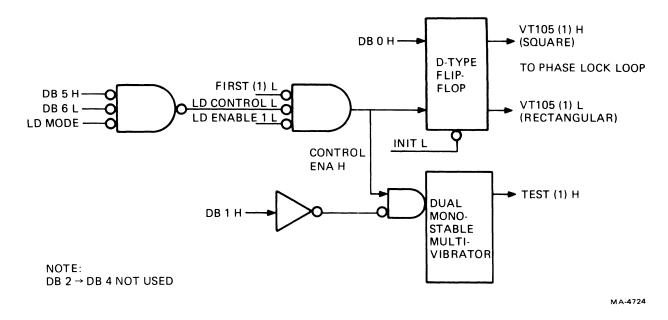

| 6-22  | Register 1 (2nd Data Character)              |      |

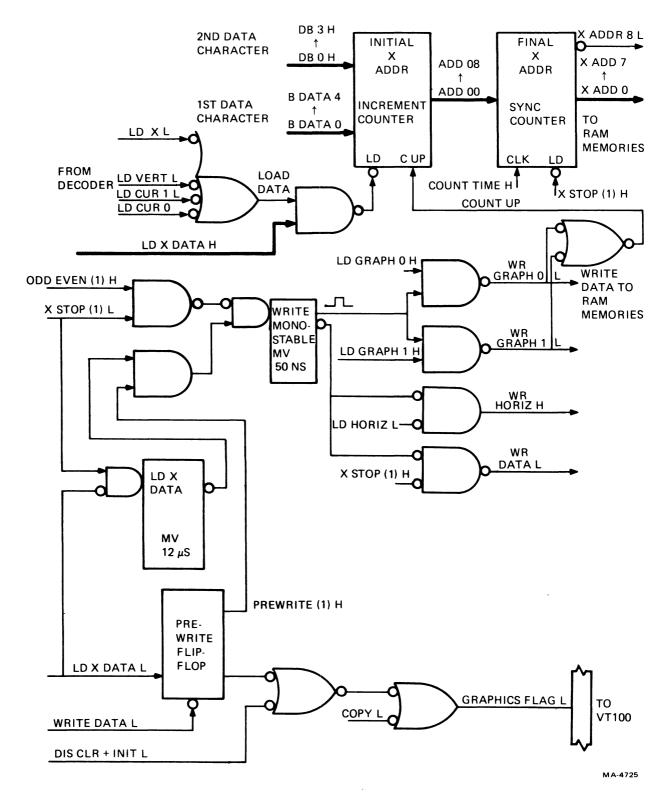

| 6-23  | Loading Address Data                         |      |

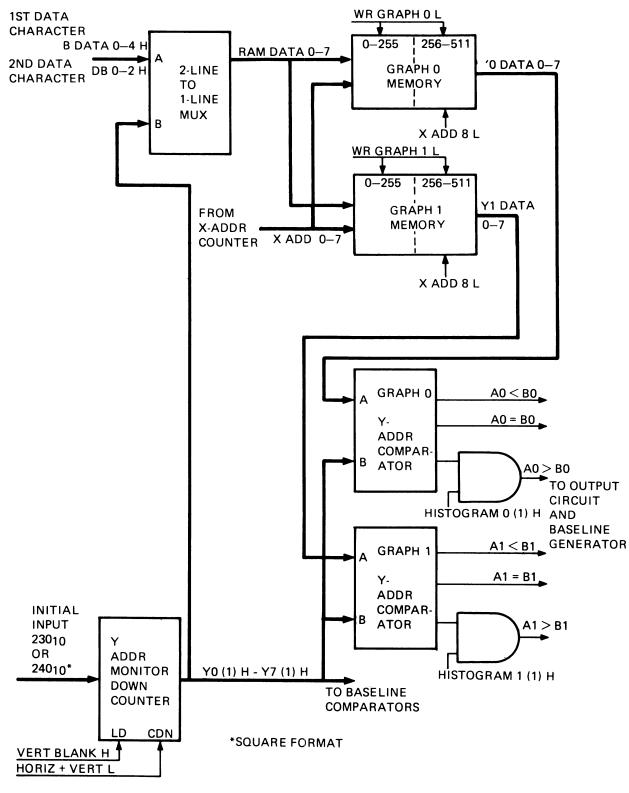

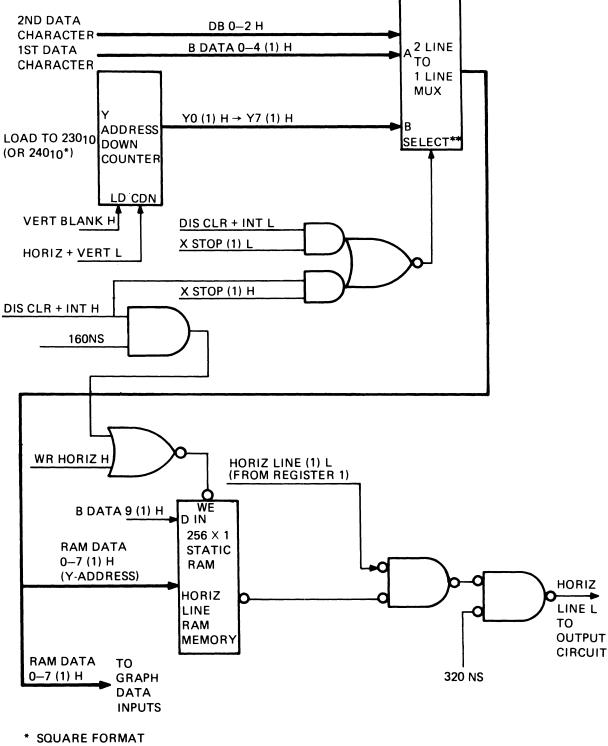

| 6-24  | Graph Memory and Y-Address Monitor           | 6-33 |

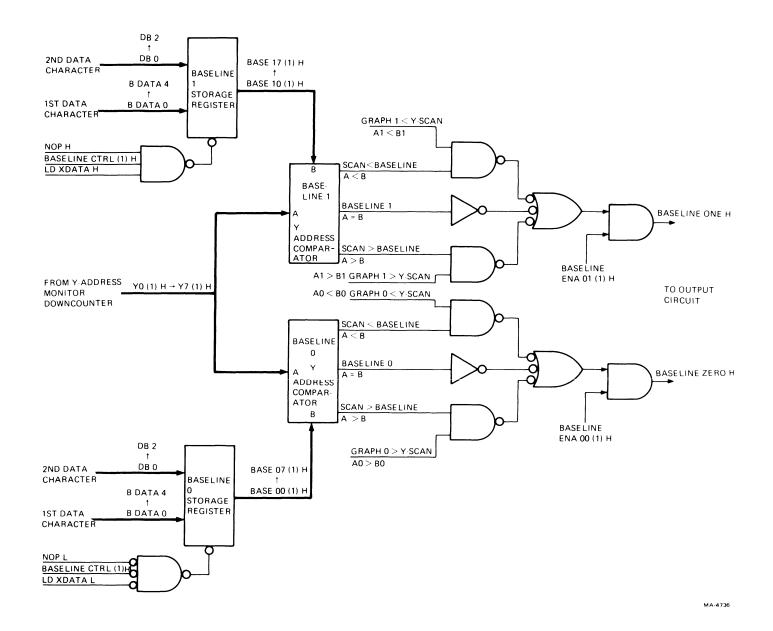

| 6-25  | Baseline (Shade Line) Registers and          |      |

|       | Comparators                                  | 6-34 |

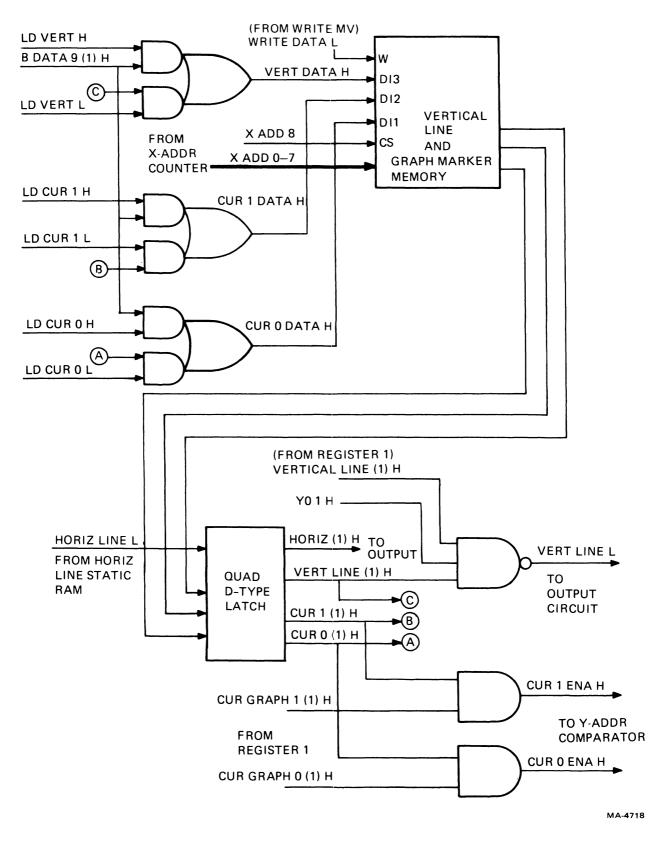

| 6-26 | Vertical Line and Graph Marker Memory | 6-35 |

|------|---------------------------------------|------|

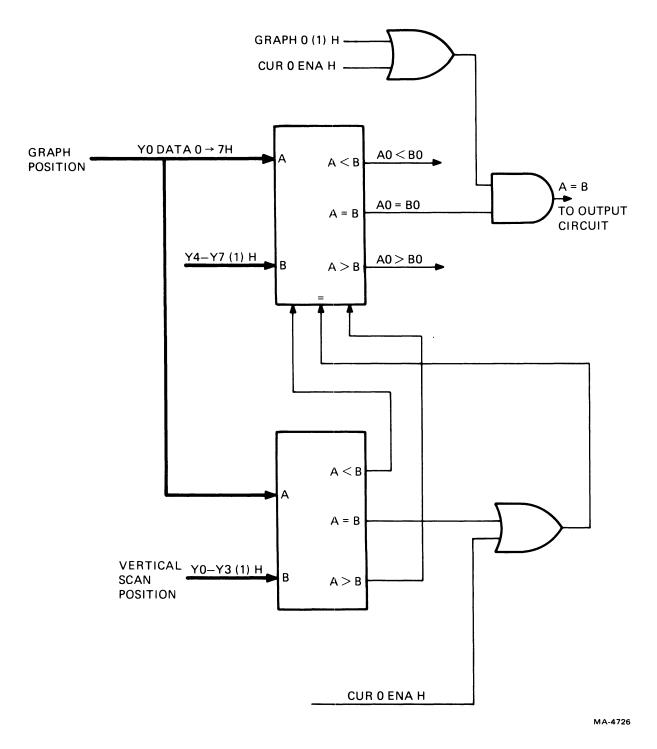

| 6-27 | Graph Marker Y-Address Comparator     |      |

| 6-28 | Horizontal Line Memory                | 6-38 |

| 6-29 | Generating Strip Charts               | 6-39 |

| 6-30 | Dual Strip Chart Timing Diagram       | 6-41 |

| 6-31 | Combining Video Out                   | 6-42 |

| 6-32 | Graph Test Pattern                    |      |

| 6-33 | Histogram Test Pattern                | 6-45 |

| 6-34 | Graph Marker Test Pattern             |      |

| 6-35 | Horizontal Lines Test Pattern         |      |

| 6-36 | Vertical Lines Test Pattern           |      |

| 6-37 | Shade Line (Baseline) Test Pattern    | 6-48 |

| 6-38 | Strip Chart Test Pattern              |      |

| 7-1a | Serial Line Splice Connection         | 7-2  |

| 7-1b | STP With No Option Present            |      |

| 7-1c | STP With Option Present               |      |

| 7-2  | STP Signal Lines                      |      |

| 7-3  | Local Clock                           |      |

| 7-4  | STP Connector                         |      |

| 7-5  | STP Option Card                       | 7-12 |

| A-1  | Terminal Data Flow                    | A-1  |

| A-2  | VT100 Keyboard                        | A-3  |

## TABLES

| 2-1   | Categories of SET-UP Features               | 2-9         |

|-------|---------------------------------------------|-------------|

| 2-2   | SET-UP Feature Change Summary               | 2-10        |

| 2-3   | Fatal Displayed Error Codes                 | 2-18        |

| 2-4   | Nonfatal Displayed Error Codes              |             |

| 2-5   | Problem Checklist                           |             |

| 3-1   | EIA Connector Signals                       | 3-5         |

| 4-2-1 | ROM Ship Select Addressing                  | 4-17        |

| 4-2-2 | List of Hex I/O Addresses                   | 4-17        |

| 4-2-3 | Interrupt Addresses                         |             |

| 4-3-1 | Baud Rate Generator Divisors                | 4-27        |

| 4-3-2 | Loopback Test Connectors                    | 4-30        |

| 4-4-1 | Keyboard Receiver Signals                   | 4-37        |

| 4-6-1 | Video Mode Selection (Write Address = C2H)  |             |

| 4-6-2 | Control Chip Commands (Write Address = A2H) | 4-70        |

| 4-6-3 | Scan Count Sequence                         |             |

| 4-6-4 | Character Attribute Combinations            | 4-75        |

| 5-1   | Keyboard LED Error Codes                    | 5-1         |

| 5-2   | VT100 Display Error Codes                   | 5-2         |

| 5-3   | Basic VT100 Troubleshooting Procedure       | 5-4         |

| 5-4   | LED Error Codes                             | 5-9         |

| 5-5   | Displayed Error Codes                       | 5-10        |

| 6-1   | VT132 SET-UP Feature Change Summary         | 6-5         |

| 6-2   | Control Characters                          | 6-22        |

| A-1   | SET-UP Features and Machine States          | A-4         |

| A-2   | Alphabetic Key Codes (Octal)                | A-5         |

| A-3   | NonAlphabetic Key Codes (Octal)             | A-6         |

| A-4   | Function Key Codes                          | <b>A-</b> 7 |

| A-5                                      | Control Codes Generated                           | A-8                                |

|------------------------------------------|---------------------------------------------------|------------------------------------|

| A-6                                      | Cursor Control Key Codes                          | A-9                                |

| A-7                                      | VT52 Mode Auxiliary Keypad Codes                  |                                    |

| A-8                                      | ANSI Mode Auxiliary Keypad Codes                  |                                    |

| A-9                                      |                                                   |                                    |

| A-10                                     | Control Characters                                |                                    |

| A-11                                     | VT100 Escape Sequences Summary                    | A-16                               |

| <b>B-</b> 1                              |                                                   |                                    |

| <b>B-2</b>                               |                                                   |                                    |

| B-3                                      |                                                   |                                    |

| B-4                                      | VT132 Recommended Spares                          |                                    |

| A-9<br>A-10<br>A-11<br>B-1<br>B-2<br>B-3 | Special Graphics Characters<br>Control Characters | A-<br>A-<br>A-<br>B<br>B<br>B<br>B |

# CHAPTER 1 INTRODUCTION AND SPECIFICATIONS

This is the technical manual for the VT100 series video terminals. It contains information a service technician or engineer needs to operate, test, and repair the VT100 series to a component level.

| Chapter 1  | Contains VT100 specifications and documentation ordering information.                                                                                                                                                                  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2  | Contains basic operator information, including use of the keyboard, use of SET-<br>UP modes for setting terminal characteristics, and simple trouble checking.                                                                         |

| Chapter 3  | Contains installation procedures and interface information.                                                                                                                                                                            |

| Chapter 4  | Contains a technical description of the basic VT100 video terminal. This chapter assumes that the reader has the Field Engineering Print Set, MP00633.                                                                                 |

| Chapter 5  | Contains servicing information for the basic VT100 video terminal.                                                                                                                                                                     |

| Chapter 6  | Contains SET-UP information for the various VT100 series options, installation information, a technical description, and service information for the Advanced Video option, the Current Loop option, and the VT105 Graphics Processor. |

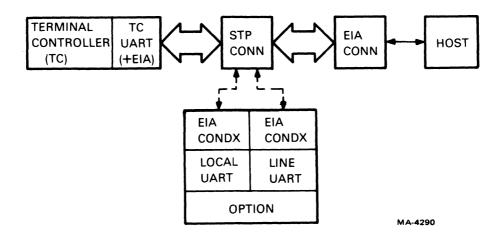

| Chapter 7  | Contains a technical description and interfacing information for the standard terminal port (STP).                                                                                                                                     |

| Chapter 8  | Contains interfacing information for the graphics connector.                                                                                                                                                                           |

| Appendix A | Contains programming information for the VT100 series, including interface timing considerations and descriptions of control functions the VT100 responds to, both in ANSI mode and in DEC VT52-compatible mode.                       |

| Appendix B | Contains a Recommended Spares List.                                                                                                                                                                                                    |

Appendix C Contains a glossary of terms and abbreviations used in this manual.

## **VT100 SPECIFICATIONS**

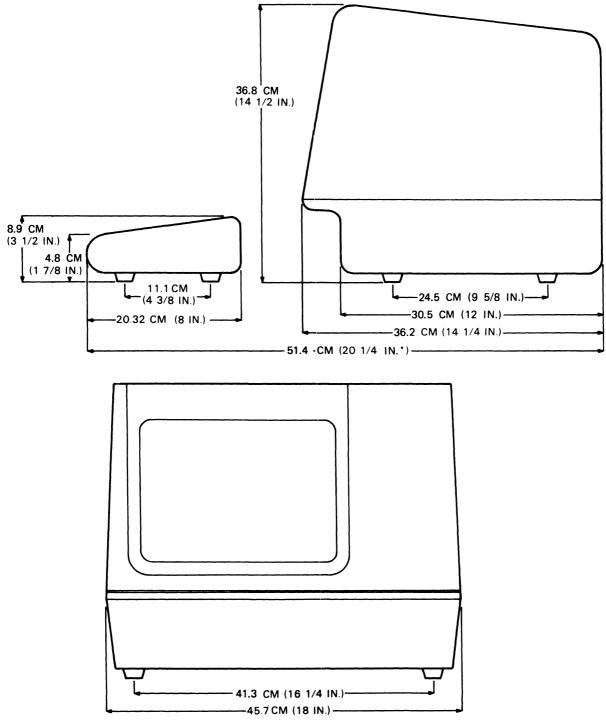

## DIMENSIONS

| Monitor |                       |

|---------|-----------------------|

| Height  | 36.83 cm (14.5 inch)  |

| Width   | 45.72 cm (18 inch)    |

| Depth   | 36.20 cm (14.25 inch) |

| -       |                       |

## Keyboard

| Height              | 8.89 cm (3.5 inch)   |

|---------------------|----------------------|

| Width               | 45.72 cm (18 inch)   |

| Depth               | 20.32 cm (8 inch)    |

| Minimum table depth | 51.4 cm (20.25 inch) |

## Weight

| Monitor         | 13.6 kg (30 lb) |

|-----------------|-----------------|

| Keyboard        | 2.0 kg (4.5 lb) |

| Shipping weight | 18.6 kg (41 lb) |

## ENVIRONMENTAL

## Nonoperating

Temperature Relative humidity Altitude

$-40^{\circ}$  to 66° C (-40° to 151° F) 0 to 95% 9.1 km (30,000 ft)

### Power

| Line voltage | 90–128 V rms single phase, 2 wire                      |

|--------------|--------------------------------------------------------|

| -            | 180–256 V rms single phase, 2 wire (switch-selectable) |

Line frequency

Current

Input power Current limiting Power cord

igle phase, 2 wire (s

47–63 Hz

3.0 A rms maximum at 115 V rms 1.5 A rms maximum at 230 V rms

250 VA apparent 150 W max. 3 A normal blow fuse Detachable, 3 prong, 1.9 m (6 ft)

| <b>Display</b><br>CRT                                                                                    | 30 cm (12 inch) diagonal measure, P4 phosphor                                                                                                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Format                                                                                                   | 24 lines $\times$ 80 characters or 14 lines $\times$ 132 characters (selectable)                                                                                                                                                                                                                             |

| Character<br>Character size<br>80 column mode<br>132 column mode<br>Active display size<br>Character set | $7 \times 9$ dot matrix with descenders<br>3.35 mm $\times$ 2.0 mm (0.132 inch $\times$ 0.078 inch)<br>3.35 mm $\times$ 1.3 mm (0.132 inch $\times$ 0.051 inch)<br>203 mm $\times$ 127 mm (8 inch $\times$ 5 inch)<br>96-character displayable ASCII subset (upper- and lowercase, numeric, and punctuation) |

| Cursor type                                                                                              | Keyboard-selectable, blinking block character or blinking underline                                                                                                                                                                                                                                          |

| <b>Keyboard</b><br>General                                                                               | 83-key detachable unit with 1.9 m (6 ft) coiled cord attached                                                                                                                                                                                                                                                |

| Key layout                                                                                               | 65-key arrangement and sculpturing similar to standard typewriter, with 18-key numeric keypad.                                                                                                                                                                                                               |

| Numeric keypad                                                                                           | 18-key with period, comma, minus, enter, and four general purpose function keys.                                                                                                                                                                                                                             |

| Visual indicators                                                                                        | 7 LEDs; 3 dedicated to ON LINE, LOCAL, and KBD LOCKED; 4 are user-programmable.                                                                                                                                                                                                                              |

| Audible signals<br>Keyclick<br>Bell                                                                      | Sound simulates typewriter.<br>1) sounds upon receipt of BEL code; 2) sounds 8 characters from right<br>margin (keyboard-selectable).                                                                                                                                                                        |

| Multiple bell                                                                                            | Sounds upon detection of error in SET-UP save or recall operation.                                                                                                                                                                                                                                           |

| Communication<br>Type<br>Speeds                                                                          | EIA<br>Full duplex: 50, 75, 110 (two stop bits), 134.5, 150, 200, 300, 600, 1200,<br>1800, 2000, 2400, 3600, 4800, 9600, 19,200                                                                                                                                                                              |

| Code<br>Character format                                                                                 | ASCII<br>Asynchronous                                                                                                                                                                                                                                                                                        |

| Character size                                                                                           | 7 or 8 bits; keyboard-selectable. (Note: if 8-bit character is selected, 8th bit is always space.)                                                                                                                                                                                                           |

| Parity                                                                                                   | Even, odd, or none (keyboard-selectable)                                                                                                                                                                                                                                                                     |

| Synchronization                                                                                          | Keyboard-selectable via automatic generation of XON and XOFF control codes.                                                                                                                                                                                                                                  |

## **ORDERING HARDWARE DOCUMENTATION**

The following VT100 DECscope video terminal hardware manuals can be purchased from DIGITAL's Accessories and Supplies Group.

| Part No.    | Title                                   |

|-------------|-----------------------------------------|

| EK-VT100-UG | VT100 User Guide                        |

| EK-VT100-J1 | VT100 Pocket Service Guide              |

| EK-VT100-IP | VT100 Illustrated Parts Breakdown (IPB) |

| EK-VT105-TM | VT105 Technical Manual                  |

| MP 00633    | VT100 Print Set                         |

| MP 00642    | VT105 Print Set                         |

| EK-VT105-IP | VT105 Illustrated Parts Breakdown (IPB) |

Purchase orders for accessories and supplies should be forwarded to:

Digital Equipment Corporation Accessories and Supplies Group Cotton Road Nashua, N.H. 03060

Contact your local sales office or call DIGITAL Direct Catalog Sales toll-free 800-258-1710 from 8:30 a.m. to 5:00 p.m. eastern standard time (U.S. customers only). New Hampshire customers should dial (603)-884-6660. Terms and conditions include net 30 days and F.O.B. DIGITAL plant. Freight charges are prepaid by DIGITAL and added to the invoice. Minimum order is \$35.00. Minimum does not apply when full payment is submitted with an order. Checks and money orders should be made out to Digital Equipment Corporation.

### **Related Documentation**

Intel 8080 Microcomputer Systems User's Manual From: Intel Corporation 3065 Bowers Avenue Santa Clara, California 95051

EIA Specifications RS-232-C and RS-170 From: Electronic Industry Association EIA Engineering Department 2001 Eye Street, N.W. Washington, DC 20006

ANSI Standards X3.41-1974, X3.64-1977, 3.4-1977 From: Sales Department American National Standards Institute 1430 Broadway New York, NY 10018

# CHAPTER 2 OPERATOR INFORMATION

### PART 1 KEYBOARD CONTROLS AND INDICATORS

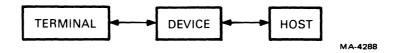

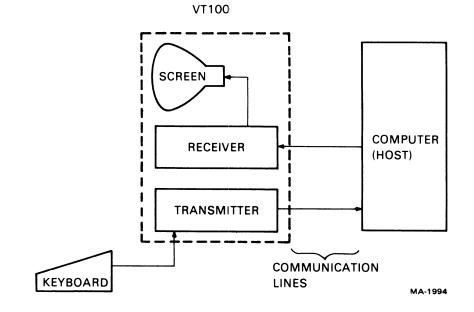

The VT100 terminal normally performs a two-part function. It is an input device to a computer – information entered through the keyboard is sent to the computer. It is simultaneously an output device for the computer – that is, data coming in from the computer is displayed on the video screen. The following controls and indicators on the VT100 keyboard are illustrated in Figure 2-1.

SET-UP

# SET-UP Key

Used in conjunction with other keys to perform specific functions such as setting tabs, scrolling, and altering terminal characteristics.

### **ON LINE Indicator**

Lights to show that the VT100 is on-line and ready to transmit or receive messages.

### **LOCAL Indicator**

Lights to show that the terminal is off-line and cannot communicate with the host device. In local mode the keyboard remains active and all characters typed are placed on the screen.

### **KBD LOCKED Indicator**

Lights to show the keyboard has been turned off. The VT100 is still able to receive data from the host. This condition can be cleared by entering and exiting SET-UP mode.

### L1-L4 Indicators

These indicators are turned on and off by the host. Consult your local operating procedures for the meaning of each indicator. L1-L4 also show self-test errors.

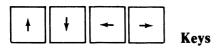

Each of these keys causes the VT100 to transmit a code that has a special meaning to your system. Consult your local operating procedures for the meaning of these keys. In SET-UP mode the  $\uparrow$  and  $\downarrow$  keys increase or decrease display brightness. The  $\leftarrow$  and  $\rightarrow$  keys move the cursor left and right.

## **BACKSPACE Key**

Transmits a backspace code.

Figure 2-1 VT100 Keyboard

2-2

MA-1998

Transmits a break signal.

Each of these keys causes the VT100 to transmit a code that has a special meaning to your system. Consult your local operating procedures for the meanings of these keys.

### Numeric Keypad

The numeric keypad enables numbers to be entered in calculator fashion. Each key in the numeric keypad generates the same character as the corresponding numeric key on the main keyboard. The **ENTER** key corresponds to the **RETURN** key. These keys may also be interpreted by the host computer as special function keys. Consult your local operating procedures for the meanings of these keys.

| ſ |   |    |   |    |

|---|---|----|---|----|

|   | D | ΕL | E | TE |

## **DELETE Key**

Causes the VT100 to transmit a delete character code to the host system. The deleted character may or may not be erased from the screen.

### **RETURN Key**

Transmits either a carriage return (CR) code or a carriage return and line feed (LF) code. This is a SET-UP selectable feature.

# LINEFEED Key

This key transmits a line feed code.

## SHIFT Key

When pressed, this key enables the uppercase function of all keys. If a key does not have an uppercase function the SHIFT key is disregarded.

# **RESET Key**

In SET-UP mode this key starts the reset sequence. This has the same result as turning the terminal power off and then on.

# 80/132 COLUMNS Key

In SET-UP A mode this key switches the display line size from 80 to 132 characters per line or from 132 to 80 characters per line.

# **RECEIVE SPEED Key**

In SET-UP B mode this key steps the terminal through the receive baud rate settings in ascending order.

# **TRANSMIT SPEED Key**

In SET-UP B mode this key steps the terminal through the transmit baud rate settings in ascending order.

| _ |

|---|

| ٨ |

| 6 |

# **TOGGLE 1/0 Key**

In SET-UP B mode this key turns the selected operational feature on or off.

# **BELL Key**

When pressed in combination with the CTRL key this key causes a bell code to be sent to the host.

# SET-UP A/B Key

In SET-UP mode this key switches the terminal from SET-UP A to SET-UP B or from SET-UP B to SET-UP A.

# LINE/LOCAL Key

In SET-UP mode this key switches the VT100 to communicate with your system (ON LINE) or stops the VT100 from communicating with your system (LOCAL).

# CLEAR ALL TABS Key

In SET-UP A this key clears all horizontal tabs set in the VT100.

# SET/CLEAR TAB Key

In SET-UP A this key sets or clears individual horizontal tabs.

# \_\_\_\_ CAPS LOCK Kev

This key enables the transmission of uppercase alphabetic characters only. All numeric and special symbol keys remain in lowercase.

#### NO SCROLL

CAPS LOCK

## NO SCROLL Key

When first pressed, this key stops the transmission of data from the computer to the VT100. When pressed a second time, transmission resumes from where it was stopped. Check your local operating procedures to ensure that your system recognizes this key.

# **CTRL Key**

When pressed in combination with another key, **CTRL** causes the VT100 to transmit a code that has a special meaning to your system.

## TAB Key

This key transmits a tab code.

# ESC Key

This key transmits a code that normally has a special meaning to your system. In many applications, it tells your system to treat the next keys pressed as a command.

### **MONITOR CONTROL**

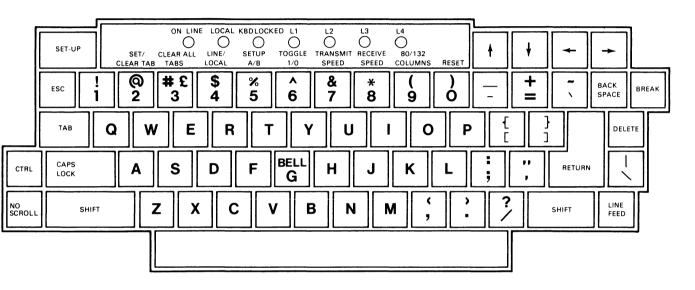

The VT100 monitor contains only one control, the power switch, shown in Figure 2-2.

### AUDIBLE INDICATORS (TONES)

There are three audible indicators associated with the VT100: a short tone (click), a long tone (beep), and a series of long tones.

### Short Tone (click)

The short tone sounds whenever a key is pressed, with the following exceptions:

- SHIFT or CTRL keys do not generate any keyclick because these keys do not transmit any codes but only modify the codes transmitted by other keys.

- When the KBD LOCKED indicator is turned on; in which case, the characters typed are lost.

- The keyclick feature has been turned off in SET-UP mode.

### Long Tone (beep)

The long tone sounds to indicate one of the following conditions:

- A bell code was received from the computer.

- The cursor is eight characters away from the right margin and the margin bell feature is enabled.

### **Series of Long Tones**

The terminal sounds the long tone several times in rapid succession to indicate that the nonvolatile memory (NVR) had difficulty reading or writing SET-UP features. (When this occurs, check the SET-UP features and then perform the recall or save operation again.)

Figure 2-2 VT100 Terminal (Rear View)

### PART 2 SET-UP MODE

Unlike most terminals, the VT100 does not use switches or jumpers to individually turn the built-in terminal features on or off. Instead, the VT100 uses a nonvolatile memory (NVR) that always remembers what features have been selected, as if a switch had been set.

Selection and storage of built-in terminal features is performed in a special mode of operation called SET-UP mode. When you enter SET-UP mode, the status of features stored in temporary memory shows on the screen. You can then change the features and store any new feature selections either temporarily, by leaving SET-UP mode; or on a fixed basis, by performing a Save operation. In either case, terminal operation reflects the new feature selection. If a recall operation is performed, or the terminal is reset, or terminal power is turned off, all temporary feature settings are replaced by features that have been stored on a fixed basis.

### **SET-UP Features**

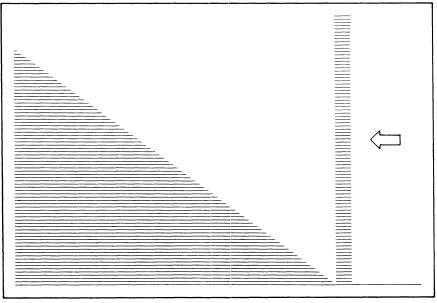

SET-UP mode provides two brief summaries of the current feature status. The first presentation – SET-UP A – displays the location of tab stops set and a visual ruler that numbers each character position on the line. The second presentation – SET-UP B – summarizes the status of the other terminal features.

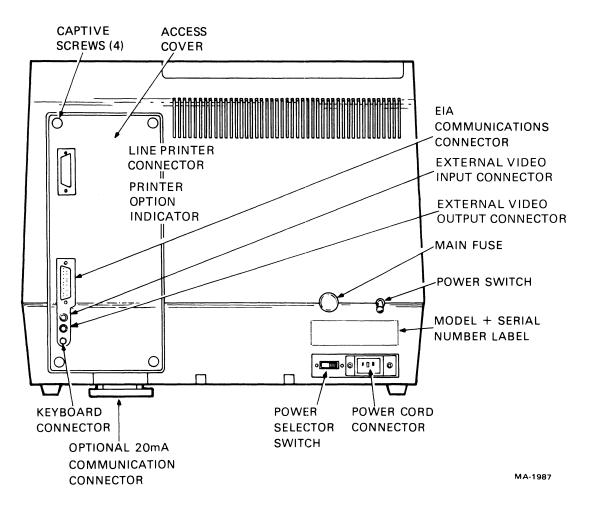

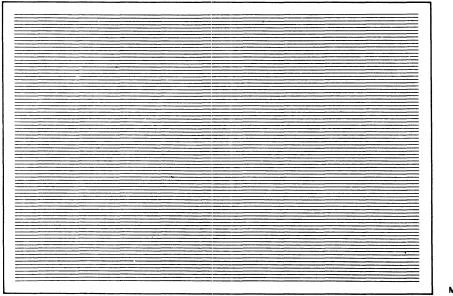

**SET-UP A** – To enter SET-UP A, press the **SET-UP** key. The display has a presentation similar to Figure 2-3. The bottom line of the display consists of a "ruler" that numbers each character position available on a line. Each tab stop is shown by a "T" above the ruler. If the tab stop(s) set are those desired, you may exit **SET-UP** mode by pressing the SET-UP key again or you may now change the tabs to meet your requirements.

Figure 2-3 SET-UP A Mode Presentation

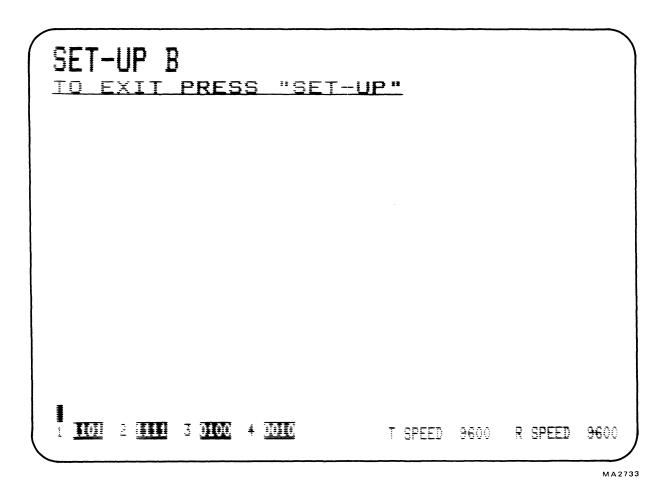

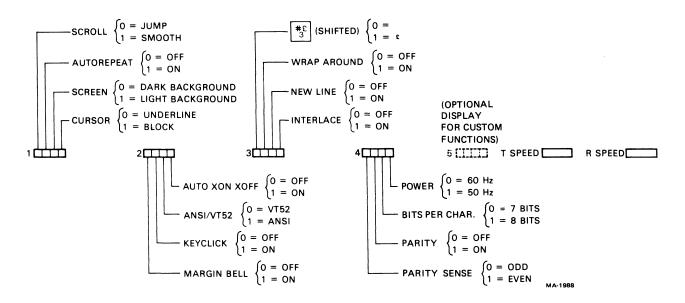

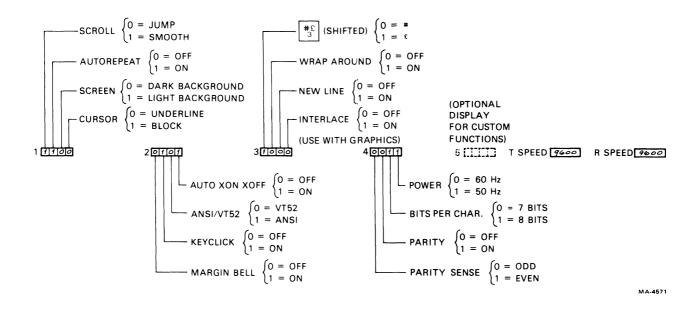

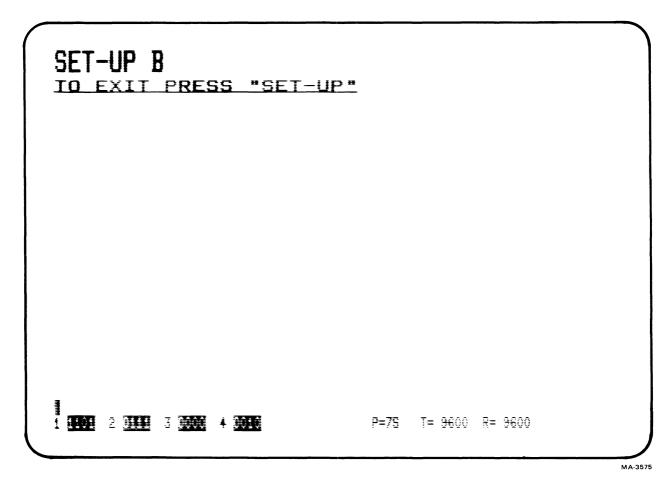

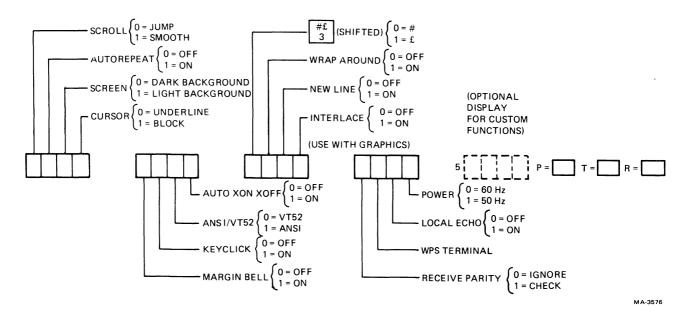

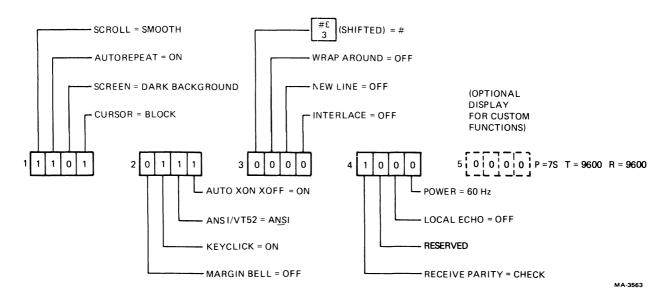

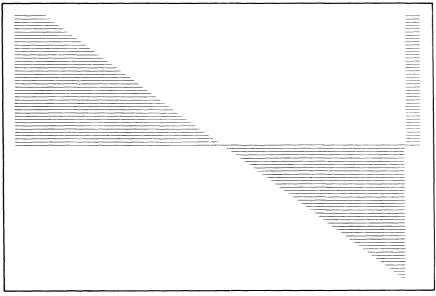

**SET-UP B** – SET-UP B mode may only be entered from SET-UP A mode. To enter SET-UP B from SET-UP A press the 5 key on the main keyboard. The display looks like Figure 2-4. Figure 2-5 summarizes the SET-UP B presentation. This summary allows you to quickly determine what features are enabled. For additional information on a feature refer to in Part 3, SET-UP Feature Definitions.

To exit SET-UP B press the SET-UP key.

Figure 2-4 SET-UP B Mode Presentation

### **Determining What a SET-UP Feature Does**

SET-UP features are basically a series of options in the VT100 that allow the terminal to be tailored to its operating environment. Table 2-1 lists each feature and shows one of the following general categories.

Installation Computer compatibility Operator comfort

The installation category includes the initial installation of the terminal and any special options that may be attached to the terminal. If any options are added or removed, or the physical location of the terminal is changed, verify the settings of these SET-UP features.

Figure 2-5 SET-UP B Mode Summary

| Feature                | Installation | Computer<br>Compatibility | Operator<br>Comfort |

|------------------------|--------------|---------------------------|---------------------|

| Ansi/VT52 mode         |              | X                         |                     |

| Answerback message     |              | X                         |                     |

| Auto Repeat            |              | А                         | Х                   |

| Auto XON/XOFF          |              | Х                         | A                   |

| Bits per Character     |              | X                         |                     |

| Characters per Line    |              | X                         |                     |

| Cursor                 |              | X                         | Х                   |

| Interlace              | X            |                           | A                   |

| Keyclick               | Λ            |                           | Х                   |

| Line/Local             |              | х                         | ~                   |

| Margin Bell            |              | A                         | Х                   |

| New Line               |              | X                         | Λ                   |

|                        |              | X                         |                     |

| Parity<br>Parity Sanca |              | X                         |                     |

| Parity Sense           | V            | А                         |                     |

| Power                  | X            | v                         |                     |

| Receive Speed          |              | X                         |                     |

| Screen Background      |              |                           | X                   |

| Screen Brightness      |              | ••                        | X                   |

| Scroll                 |              | X                         | Х                   |

| Tabs                   |              | X                         |                     |

| Transmit Speed         |              | X                         |                     |

| Wraparound             |              | X                         |                     |

| <b>#£</b>              |              | X                         |                     |

| 3 (shifted)            |              |                           |                     |

**Table 2-1 Categories of SET-UP Features**

Computer compatibility contains the features that must be set correctly so that the VT100 can communicate with the host computer. An error in these settings may cause incorrect data to be sent to or received from the computer; or an error may prevent the VT100 from communicating with the computer. The settings for these features must be obtained from the host computer programmer, operator, or system manager since there are many combinations of settings designed to work with particular computers and special software. These feature settings normally change only when you need to communicate with a different computer or a unique software package.

The operator comfort category contains SET-UP features designed exclusively for the operator. These features allow the operator to tailor the VT100 to fit individual preference. These features do not affect any operations that occur between the terminal and the computer.

Part 3, SET-UP Feature Definitions, describes the specific function of each feature.

### How to Change a SET-UP Feature

Changing any or all SET-UP features is a simple operation and is generally performed by following the same basic steps.

- 1. Enter SET-UP mode by pressing the SET-UP key.

- 2. Select the appropriate SET-UP mode by pressing the 5 key on the main keyboard each time you want to switch from SET-UP A to SET-UP B or from SET-UP B to SET-UP A.

- 3. Position the cursor above the feature switch or tab stop to be changed. To position the cursor, the SPACE bar, ←, →, TAB, and RETURN keys may be used. Some features do not use this step since a specific key is dedicated to changing the feature.

- 4. Change the feature setting by pressing either the 6 key on the main keyboard or the appropriate dedicated key. Each time the key is pressed the feature changes, generally to the opposite state.

Table 2-2 briefly summarizes SET-UP features, the SET-UP mode you must be in to change a feature, and the key used to change the feature setting.

| Feature            | Changed In<br>SET-UP Mode | Key to<br>Change<br>Feature |

|--------------------|---------------------------|-----------------------------|

| Answerback message | В                         | *                           |

| ANSI/VT52 mode     | В                         | G                           |

| Auto Repeat        | В                         | ^<br>6                      |

| Auto XON/XOFF      | В                         | ^<br>6                      |

| Bits per Character | B                         | ^<br>6                      |

| Brightness         | Ā                         | + +                         |

### Table 2-2 SET-UP Feature Change Summary

\* A special sequence is required for this feature. See the detailed features description.

| Feature                         | Changed In<br>SET-UP Mode | Key to<br>Change<br>Feature                                                                |

|---------------------------------|---------------------------|--------------------------------------------------------------------------------------------|

| Characters per Line             | А                         | (9)                                                                                        |

| Cursor                          | В                         | ^<br>6                                                                                     |

| Interlace                       | В                         | ^<br>6                                                                                     |

| Keyclick                        | В                         | ^<br>6                                                                                     |

| Line/Local                      | А                         | \$<br>4                                                                                    |

| Margin Bell                     | В                         | Â<br>6                                                                                     |

| New Line                        | В                         | Â<br>6                                                                                     |

| Parity                          | В                         | G                                                                                          |

| Parity Sense                    | В                         | ^<br>6                                                                                     |

| Power                           | В                         | <b>6</b>                                                                                   |

| Receive Speed                   | В                         | * 8                                                                                        |

| Screen                          | В                         | <b>6</b>                                                                                   |

| Scroll                          | В                         | <b>6</b>                                                                                   |

| Tabs                            | А                         | $\begin{bmatrix} 0 \\ 2 \\ and \end{bmatrix} = \begin{bmatrix} \# \\ 3 \\ 3 \end{bmatrix}$ |

| Transmit Speed                  | В                         | &<br>7                                                                                     |

| Wraparound                      | В                         | <b>6</b>                                                                                   |

| <b>#£</b><br><b>3</b> (shifted) | В                         | <b>6</b>                                                                                   |

Table 2-2 SET-UP Feature Change Summary (Cont)

## Setting the Answerback Message

Setting the answerback message differs from setting any other terminal feature. An answerback message can be typed into the VT100, using the following steps.

- 1. Place the terminal in SET-UP B mode.

- 2. Press the SHIFT and A keys at the same time. The terminal responds by placing A = on the screen. (The SHIFT key is required. The CAPS LOCK key does not work here.)

- 3. Type the message delimiter character which may be any character not used in the actual answerback message. The message delimiter character is not part of the answerback message. If a mistake is made when typing the answerback message, type the message delimiter character again and go back to step 2. This is the *only* way to correct errors in the answerback message.

- 4. Type the answerback message. The message may be up to 20 characters, including space and control characters. Control characters are displayed as a character to indicate their presence in the message.

- 5. Type the message delimiter character. Once the message delimiter character is typed the answerback message disappears from the screen.

Once the above steps have been completed the answerback message is temporarily stored in the VT100 and can be saved with the save operation.

### Saving SET-UP Features