RK11-D and RK11-E moving head disk drive controller manual

1st Edition, August 1973 2nd Printing, January 1974 3rd Printing, August 1974 4th Printing, February 1975

#### Copyright © 1974, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

**COMPUTER LAB**

**UNIBUS**

### CONTENTS

|                | P                                       | Page       |

|----------------|-----------------------------------------|------------|

| CHAPTER 1      | GENERAL DESCRIPTION                     |            |

| 1.1            |                                         | 1-1        |

| 1.2            | OPTIONS                                 | 1-1        |

| 1.3            | FUNCTIONAL DESCRIPTION                  | 1-1        |

| 1.3.1          |                                         | 1-1        |

| 1.3.2          |                                         | 1-2        |

| 1.3.2.1        |                                         | 1-2        |

|                |                                         | 1-3        |

| 1.3.2.2        |                                         | _          |

| 1.3.2.3        | Drive Reset Function                    | 1-3        |

| 1.3.2.4        | Write Lock Function                     | 1-4        |

| 1.3.2.5        | Write Function                          | 1-4        |

| 1.3.2.6        | Read Function                           | 1-4        |

| 1.3.2.7        | Write Check Function                    | 1-4        |

| 1.3.2.8        | Read Check Function                     | 1-4        |

| 1.3.2.9        |                                         | 1-5        |

| 1.4            |                                         | 1-5        |

| 1.5            | SPECIFICATIONS                          | 1-5        |

| 1.6            | RELATED DOCUMENTS                       | 1-5        |

| CHAPTER 2      | INSTALLATION                            |            |

| 2.1            | INTRODUCTION                            | 2-1        |

| 2.2            | POWER REQUIREMENTS                      | 2-1        |

| 2.3            | CABLING REQUIREMENTS                    | 2-1        |

| 2.4            | RK11-D and RK11-E OPTION CONFIGURATIONS | 2-1        |

| 2.5            | INSTALLATION PROCEDURE                  | 2-3        |

| 2.6            | INSTALLATION TESTING                    | 2-3        |

| 2.0            | INDIALLATION ILUTINO                    | 2-3        |

| CHAPTER 3      | PROGRAMMING CONSIDERATIONS              |            |

| 3.1            | INTRODUCTION                            | 3-1        |

| 3.2            | DEVICE REGISTERS AND ADDRESSES          | 3-1        |

| 3.3            | DATA FORMAT                             | 3-9        |

| 3.4            | PROGRAM INTERRUPTS                      | 3-9        |

| 3.5            | TIMING CONSIDERATIONS                   | 3-10       |

| 3.6            | POWER FAIL                              | 3-10       |

| CHAPTER 4      | DETAILED DESCRIPTION                    |            |

| 4.1            | INTRODUCTION                            | 4-1        |

| 4.2            | STATUS CONTROL                          | 4-1        |

| 4.2.1          | RKCS, Function, and Control Logic       | 4-1        |

| 4.2.2          | RKWC Logic                              | 4-2        |

| 4.2.3          | Internal Word Count Logic               | 4-2        |

| 4.2.3<br>4.2.4 | RKER and Error Detection Logic          | 4-2<br>4-3 |

| 4.2.5          | Internal Bus A Multiplexers             | 4-3<br>4-5 |

|                | •                                       |            |

| 4.3            | DISK CONTROL                            | 4-5        |

| 4.3.1          | Head Movement                           | 4-5        |

| 4.3.2          | RD GATE and WT GATE                     | 4-6        |

| 4.3.3          | Adder Register                          | 4-6        |

## **CONTENTS (Cont)**

|            | rage                                                       |

|------------|------------------------------------------------------------|

| 4.3.4      | Drive Selection and Hardware Poll                          |

| 4.3.5      | Drive Error and Drive Power Low                            |

| 4.3.6      | Drivers and Receivers                                      |

| 4.3.7      | Crystal Oscillator                                         |

| 4.4        | DATA PATHS                                                 |

| 4.4.1      | In Buffer                                                  |

| 4.4.2      | 4-Word File                                                |

| 4.4.3      |                                                            |

| 4.4.4      |                                                            |

| 4.4.5      |                                                            |

|            |                                                            |

| 4.4.6      | Data Paths Control Logic                                   |

| 4.4.6.1    | In Buffer Control                                          |

| 4.4.6.2    | Out Buffer Control                                         |

| 4.4.6.3    | RKER 09 (DLT) Control                                      |

| 4.4.6.4    | 4-Word File Control                                        |

| 4.4.6.5    | NPR Initiation                                             |

| 4.4.6.6    | RKDA Control                                               |

| 4.4.7      | Internal Bus D Multiplexers                                |

| 4.5        | BUS CONTROL                                                |

| 4.5.1      | Address Selection Logic                                    |

| 4.5.2      | NPR Logic                                                  |

| 4.5.3      | Interrupt Control Logic                                    |

| 4.5.4      | Unibus Drivers and Receivers                               |

| CHAPTER 5  | MAINTENANCE                                                |

| 5.1        | INTRODUCTION                                               |

| 5.2        | INSPECTION                                                 |

| 5.3        | DIAGNOSTICS                                                |

| 5.4        | KM11-A MAINTENANCE PANEL 5-2                               |

| APPENDIX A | RK11-D AND RK11-E INTEGRATED CIRCUITS (ICs) A-1            |

|            | ILLUSTRATIONS                                              |

| Figure No. | Title Page                                                 |

| 1-1        | RK11-D and RK11-E Disk Drive System                        |

| 1-2        | RK11 Controller, Functional Block Diagram                  |

| 2-1        | RK11 Cable Connections                                     |

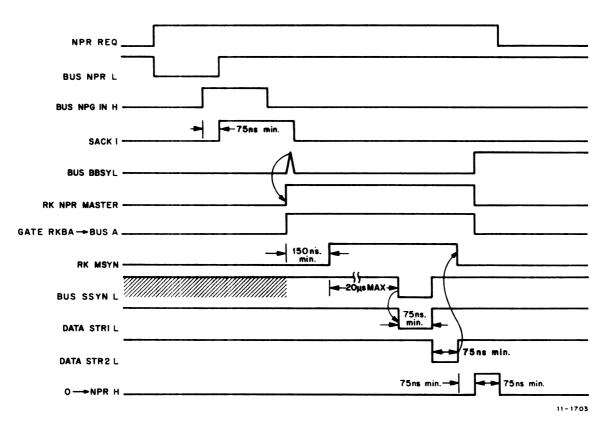

| 4-1        | Non-Processor Request (NPR) Timing Diagram for RK11        |

|            | (Write or Write Check Function)                            |

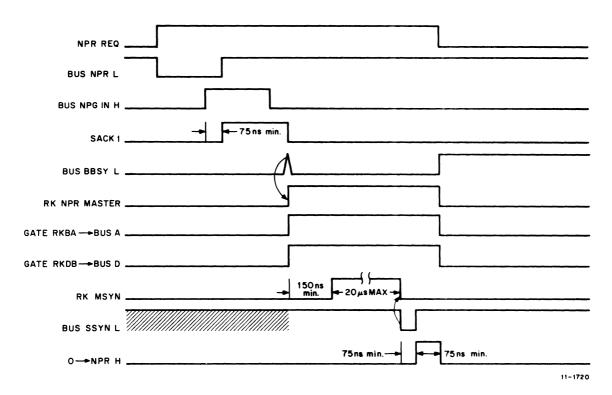

| 4-2        | Non-Processor Request (NPR) Timing Diagram for RK11        |

|            | (Read Function)                                            |

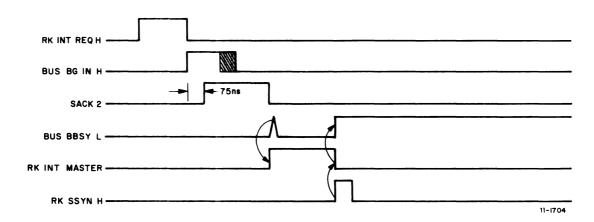

| 4-3        | RK11 Bus Request Interrupt Timing Sequence                 |

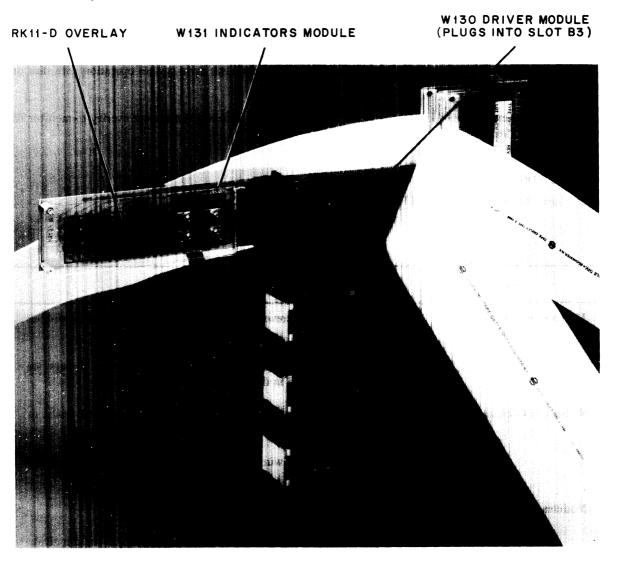

| 5-1        | KM11-A Maintenance Panel Installed in RK11 Controller Unit |

| 5-1<br>5-2 | RK11-D Overlay for KM11-A Maintenance Panel                |

|            | • • • • • • • • • • • • • • • • • • •                      |

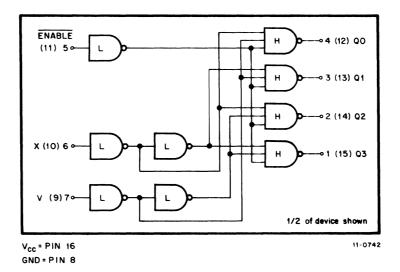

| A-1        | MC4007 Dual/Binary-to-One-of-Four Line Decoder             |

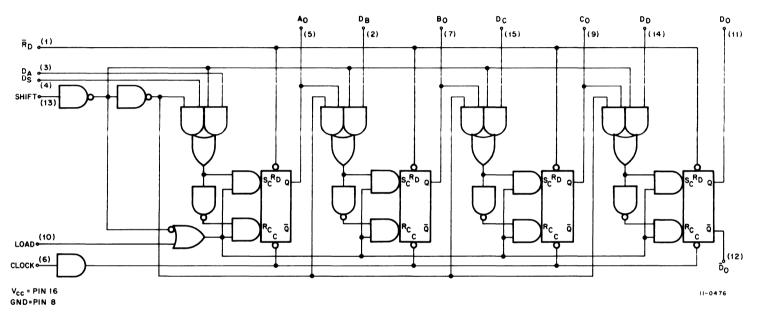

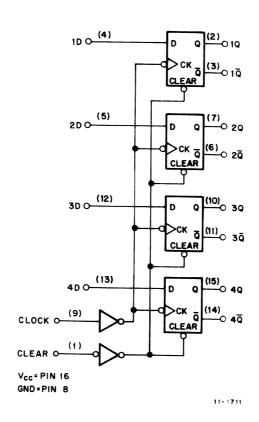

| A-2        | 8271 4-Bit Shift Register                                  |

## ILLUSTRATIONS (Cont)

|             |                                                          | Page  |

|-------------|----------------------------------------------------------|-------|

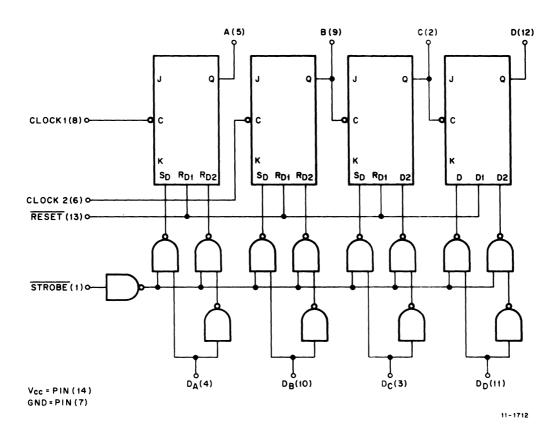

| A-3         | 8281 DC 4-Bit Binary Counter/Storage Element             | . A-4 |

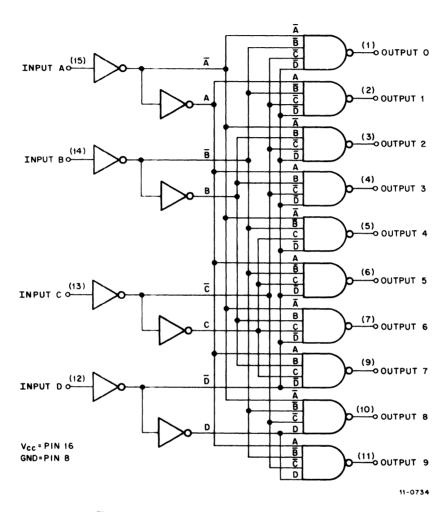

| A-4         | 7442 4-Line-to-10-Line Decoder                           |       |

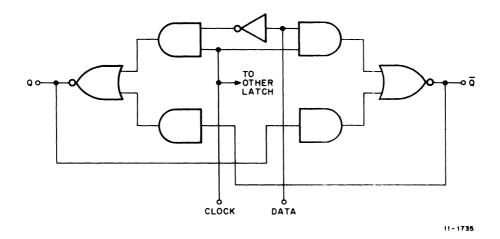

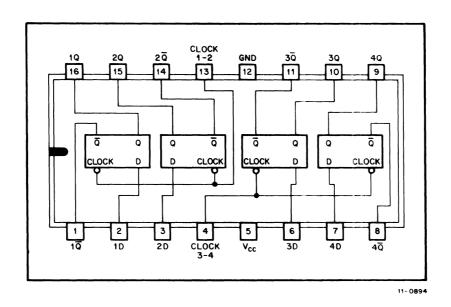

| <b>A-</b> 5 | 7475 Quad Bistable Latches                               |       |

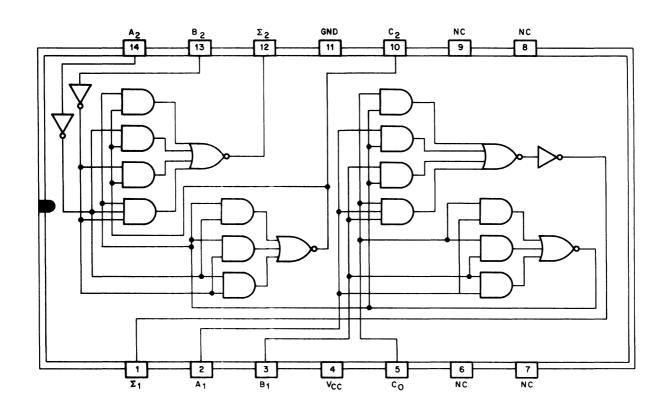

| A-6         | 7482 2-Bit Binary Full Adder                             |       |

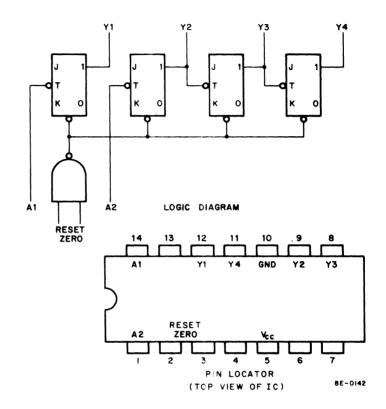

| A-7         | 7493 4-Bit Binary Counter                                |       |

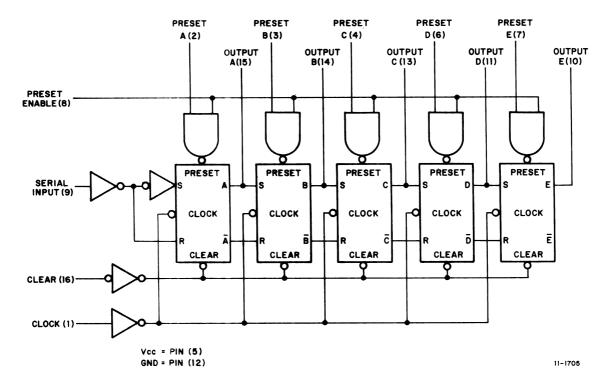

| A-8         | 7495 5-Bit Shift Register                                |       |

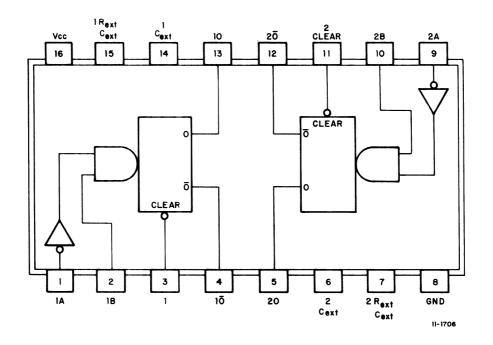

| <b>A-9</b>  | 74123 Dual Retriggerable Monostable Multivibrator        |       |

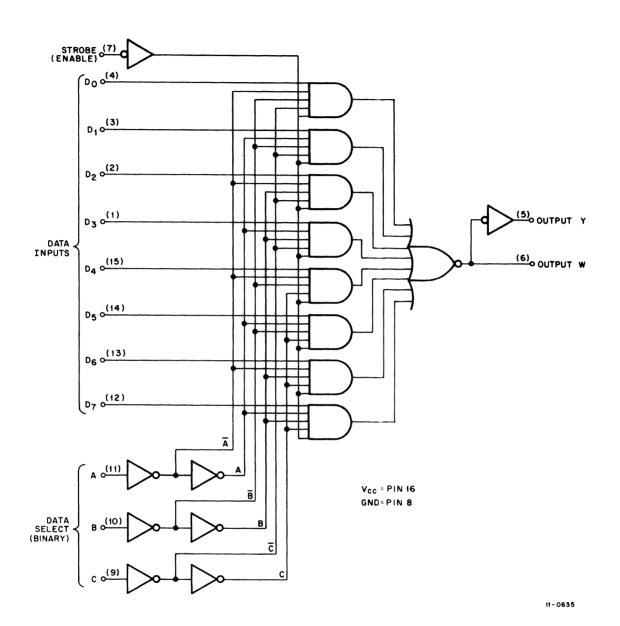

| A-10        | 74151 8-Line-to-1-Line Data Selector/Multiplexer         |       |

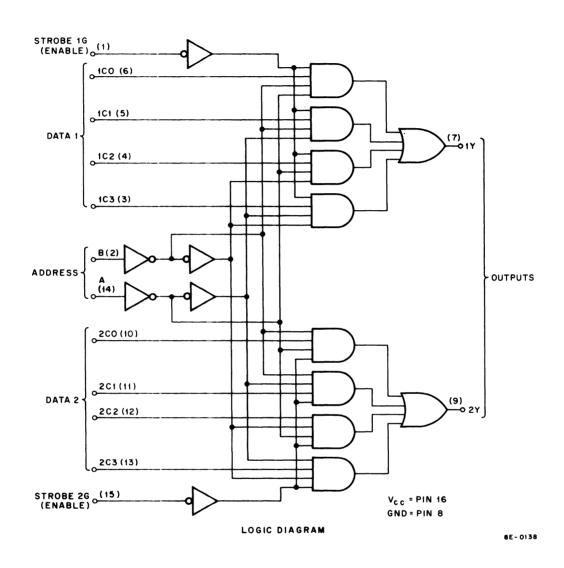

| A-11        | 74153 Dual 4-Line-to-1-Line Data Selector/Multiplexer    |       |

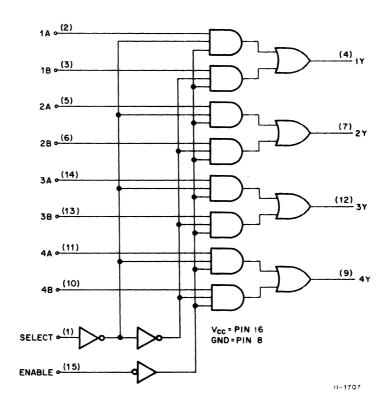

| A-12        | 74157 Quadruple 2-Line-to-1-Line Multiplexer             |       |

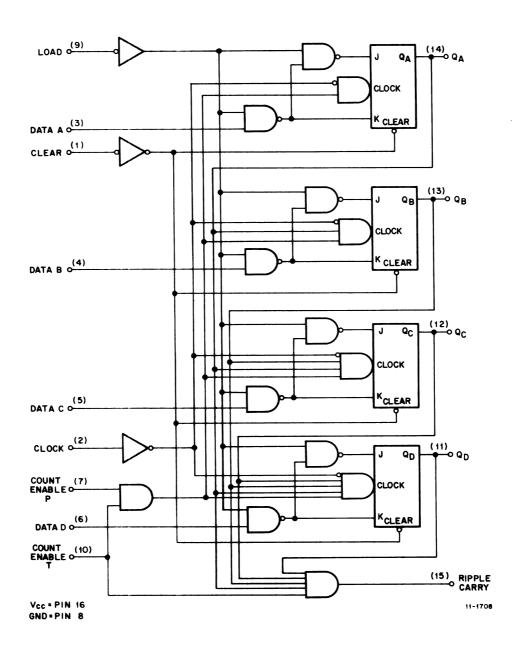

| A-13        | 74161 Synchronous 4-Bit Binary Counter                   |       |

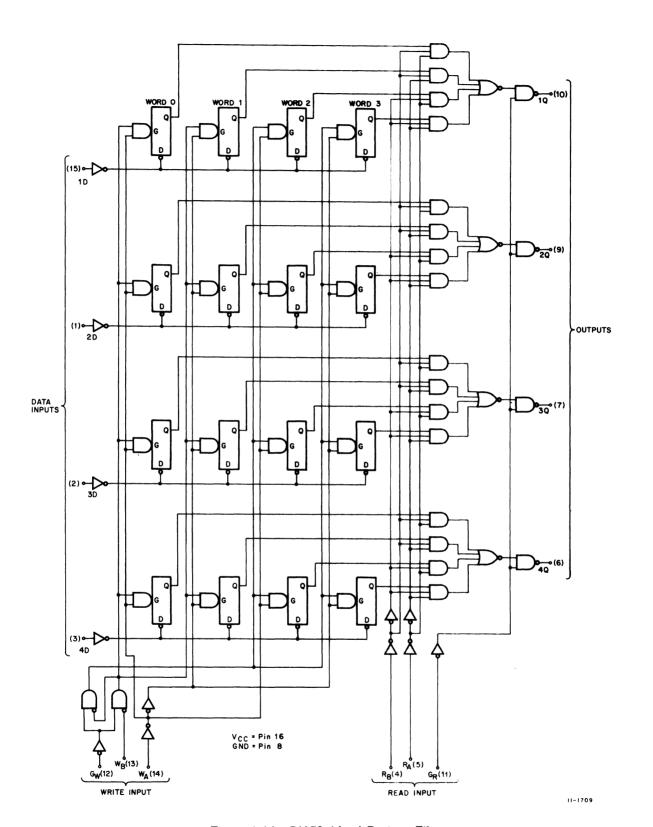

| A-14        | 74170 4-by-4 Register File                               |       |

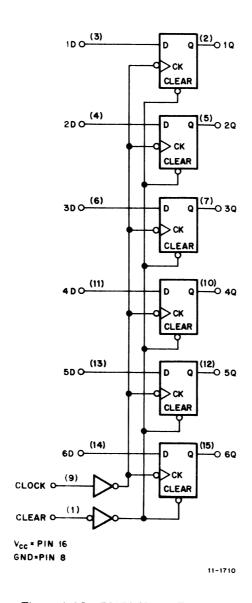

| A-15        | 74174 Hex D-Type Flip-Flop                               |       |

| A-16        | 74175 Quad D-Type Flip-Flop                              |       |

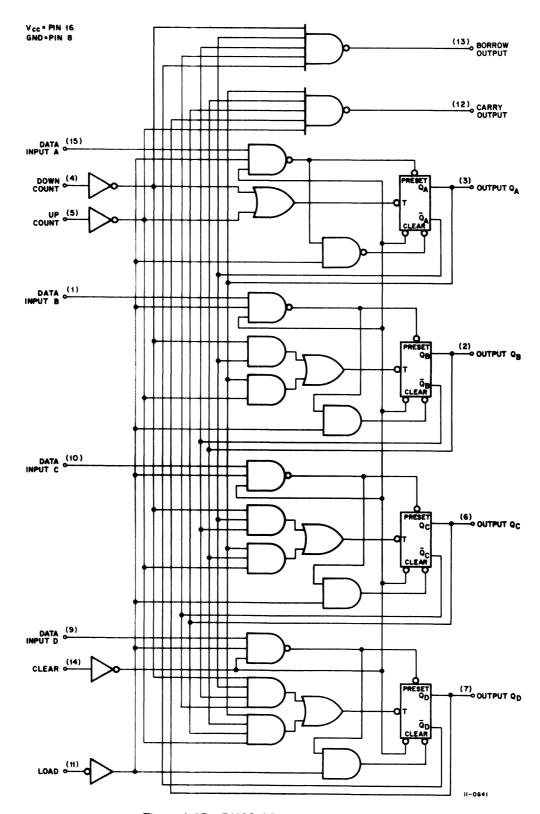

| A-17        | 74193 4-Bit Binary Counter                               |       |

|             | TABLES                                                   |       |

| Table No.   | Title                                                    | Page  |

| 1-1         | RK11 Registers                                           | . 1-3 |

| 1-2         | Specifications                                           |       |

| 1-3         | Related Documents                                        |       |

| 4-1         | Multiplexer Register Selection                           |       |

| 5-1         | Visual Inspection Checklist                              |       |

| A-1         | RK11-D and RK11-E Medium Scale Integrated Circuits (MSI) |       |

|   |  | • |

|---|--|---|

|   |  |   |

|   |  |   |

|   |  |   |

| , |  |   |

|   |  |   |

# INTRODUCTION

This manual provides the user with the theory of operation of the RK11 Moving Head Disk Drive Controller, and with the logic descriptions necessary to understand and maintain it effectively. Discussions in the manual deal with general and detailed descriptions of the RK11-D and RK11-E Controllers. For detailed coverage of the RK05 itself, refer to the RK05 Disk Drive Maintenance Manual, DEC-00-HRK05-C-D.

Although control signals and data are transferred between the RK11 Controller and the Unibus, it is beyond the scope of this manual to cover the operation of the bus itself. Detailed information regarding the Unibus may be found in the PDP-11 Peripherals Handbook.

Reference is occasionally made within this manual to engineering drawings, not contained herein. These drawings are in the RK11 Moving Head Disk Drive Controller Engineering Drawings Manual, a copy of which is supplied with each RK11 Controller. That manual contains current RK11 prints, updated to the time when the equipment is shipped.

|  |  | • |

|--|--|---|

|  |  | J |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

# CHAPTER 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

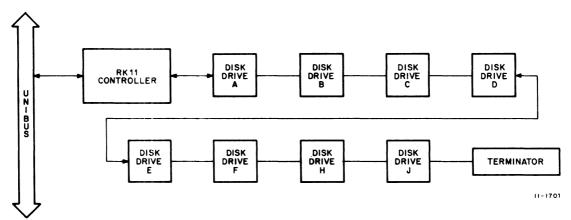

The RK11-D and RK11-E are controllers for rotating mass memories capable of communicating with up to eight daisy-chained disk drives (Figure 1-1). The system is block-oriented, but is capable of transferring from 1 to  $2^{16}$  consecutive data words without reinitiation or processor intervention. These data transfers occur on the Unibus at the Non-Processor Request (NPR) level of communication.

Figure 1-1 RK11-D and RK11-E Disk Drive System

#### 1.2 OPTIONS

The RK11 Controller has two options, RK11-D and RK11-E, both of which are used with the RK05 Disk Drive. The RK11-D transfers 16-bit data, and the RK11-E transfers 18-bit data. Option selection is made by adjusting the jumper configuration as described in Paragraph 2.4.

#### 1.3 FUNCTIONAL DESCRIPTION

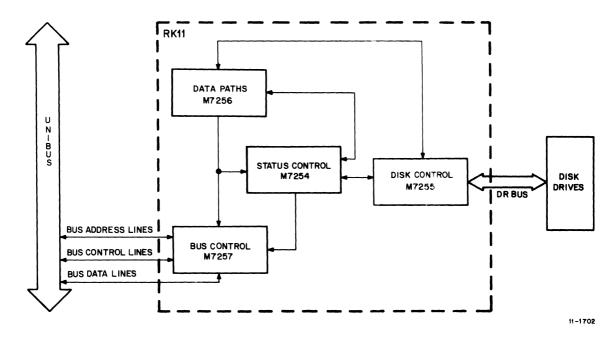

The RK11 Controller and the RK05 Disk Drive form the disk drive system, which interfaces with a PDP-11 processor via the Unibus. The RK11 is implemented on four functional modules (M7254, M7255, M7256, and M7257), and interfaces with the RK05 Disk Drive via a drive bus (DR BUS) as shown in Figure 1-2.

Figure 1-2 RK11 Controller, Functional Block Diagram

#### 1.3.1 Disk Drives

The RK05 is a moving-head disk drive that uses RK03-KA disk cartridges for data storage. Data is stored on both sides of the disk by a pair of movable heads, which are always positioned over opposing surfaces of the same cylinder simultaneously. Each side of the disk contains 203<sub>10</sub> tracks, each of which contains 12<sub>10</sub> sectors capable of storing 400<sub>8</sub> or 256<sub>10</sub> data words.

The sector format consists of 15<sub>8</sub> words of preamble terminating in a sync bit, followed by a one-word header, 400<sub>8</sub> data words, a one-word checksum, and one word of postamble. Sector pulses signal the beginning of each sector, and an index pulse indicates the last sector, signifying that the sector following is Sector 0.

The DR BUS consists of eight disk drives connected in daisy-chain fashion, each of which can be write protected either by an RK11 Controller Write Lock function or by manual intervention.

On a disk cartridge, the upper surface is defined as surface 0, and is active when RKDA 04 (SUR) is clear. If a data transfer requires an overflow from surface 0, SUR is set automatically, and surface 1 (the lower surface of the cartridge) is activated at sector 0. If a data transfer requires an overflow from surface 1, the RK11 automatically moves the disk drive heads to the next cylinder, checks the header word to verify head positioning, and resumes the data transfer at sector 0 of surface 0 again, but this time on a new cylinder. Attempting this cross-cylinder operation from surface 1 of the last cylinder will result in an error condition (RKER 14 - OVR).

For more detailed information on the disk drive operation and the related power supply, refer to the *RK05 Disk Drive Maintenance Manual* (DEC-00-HRK05-C-D), which is shipped with the disk drives. That manual also contains a complete description of the DR BUS lines.

#### 1.3.2 RK11 Controller

The RK11 is divided into four major functional units, as shown in Figure 1-2. The Status Control initiates the programmable RK11 functions and monitors logic status conditions. The Disk Control monitors disk drive status conditions and controls all disk drive functions. The Data Paths transfer parallel data to and from the Unibus, and serial data to and from the disk drives. The Bus Control interfaces the RK11 with the Unibus for address selection, NPR data transfers, and interrupt sequences.

The RK11 contains seven 16-bit programmable hardware registers, addressed from the Unibus, that provide the software interface between the RK11 and the Unibus. Table 1-1 lists these registers and their addresses.

Table 1-1

RK11 Registers

| Name                         | Abbreviation | Address |

|------------------------------|--------------|---------|

| RK11 Drive Status Register   | RKDS         | 777400  |

| RK11 Error Register          | RKER         | 777402  |

| RK11 Control Status Register | RKCS         | 777404  |

| RK11 Word Count Register     | RKWC         | 777406  |

| RK11 Bus Address Register    |              |         |

| (Current Memory Address)     | RKBA         | 777410  |

| RK11 Disk Address Register   | RKDA         | 777412  |

| RK11 Data Buffer Register    | RKDB         | 777416  |

Through software control, the RK11 can perform four control functions (Control Reset, Seek, Drive Reset, and Write Lock) and four data transfer functions (Write, Read, Write Check, and Read Check). The hardware poll feature enables more than one disk drive to perform multiple Seek or Drive Reset functions simultaneously. The RK11 also initiates an interrupt sequence on the Unibus in response to any of six interrupt conditions described in Paragraph 3.4.

1.3.2.1 Control Reset – The Control Reset function initializes all internal registers and flip-flops, and clears all of the bits of the seven programmable registers except RKCS 07 (READY), which it sets, and RKDS 01 through 11, which are not affected. Disk drive operation is only affected indirectly, as a result of RK11 logic being cleared.

Control Reset serves as an effective "abort," because it terminates all controller action; however, care should be taken during a Write operation as the abort does not occur until completion of the current sector. If a Control Reset function is used to abort a function in process to allow a high-priority user access to a disk drive, that drive must first be checked for head motion (indicated by RKDS 06 — Read/Write/Seek Ready). If the function is initiated before the heads have stopped, a hard error results, after which a Drive Reset function must be performed on that drive before it can be used again.

1.3.2.2 Seek Function – For a Seek function, the RK11 directs the selected disk drive to move its head mechanism to the cylinder address specified by RKDA 05 through 12. When this portion of a Seek has been initiated, the controller returns to the Ready state (RKCS 07). But if the specified cylinder address is greater than 312<sub>8</sub>, the function is aborted and bit 06 (nonexistent Cylinder) of the RKER is set. RKCS 06 (Interrupt Done Enable) then determines the program reaction.

The selected disk drive completes the Seek function by moving its head mechanism to the desired cylinder, whereupon RKDS 06 (R/W/S RDY) is set. The time required to initiate a Seek function is normally 1  $\mu$ s, but may range up to 3.3 ms if an attempt is made to abort a Write function. Head movement may take up to a maximum of 80 ms.

1.3.2.3 Drive Reset Function — For a Drive Reset function, the controller directs the selected disk drive to move its head mechanism to cylinder address 000 and reset all active error status lines. To the controller, the Drive Reset function is the same as a Seek function, even to the manner in which the hardware poll logic is used; however, a Drive Reset function can take much longer than a Seek function to execute. The time required to complete a Drive Reset function depends on the physical position of the head mechanism at the time the function is initiated, and therefore may take up to a maximum of two seconds.

- 1.3.2.4 Write Lock Function The Write Lock function write-protects a selected disk drive until the condition is overridden by operation of the corresponding WT PROT (Write Protect) switch on the disk drive (refer to RK05 Disk Drive Maintenance Manual, DEC-00-HRK05-C-D). The disk drive is automatically write-enabled when power is first applied, or when the disk drive RUN/LOAD switch is set to RUN.

- 1.3.2.5 Write Function For a Write function, the controller first performs a normal Seek function. When that is completed, the next Header word is read and checked for correct cylinder identification (cylinder address). If the header is correct, the controller begins the Write operation when the Sector Counter (RKDA 00 through 03) equals the sector address (RKDS 00 through 03), hereafter referred to as SC = SA.

A preamble consisting of 15 words of zeroes is written, followed by a sync pulse. Then the header word is rewritten automatically, followed immediately by the data words for the sector. As the data words pass through the controller, a one-word checksum word is calculated and automatically written after the last sector data word, followed by one word of zeroes for the postamble. If the cylinder address is incorrect, the controller makes 16 attempts to establish the correct cylinder address before the function is aborted, setting RKER 12 (Seek Error). (Compatibility with the RK11-C, which makes only one attempt, may be achieved by cutting a jumper on the Status Control module.)

An RKWC overflow at any time from the start of the Write function stops the NPR data transfers and sets RKCS 07 (Ready, RDY) at the end of the current sector. If the RKWC has not overflowed at the end of a given sector, the function is continued at the next contiguous sector; however, if the last sector of the disk cartridge is transferred without RKWC having overflowed, then RKER 14 (OVR, Overrun) is set.

- 1.3.2.6 Read Function For a Read function, the controller first performs a normal Seek function. When that is completed, the controller waits for SC = SA, then reads and checks the header word. If the cylinder address is correct, the controller continues reading the sector and NPR-transfers the data words onto the Unibus. If the cylinder address is initially incorrect, the controller makes 16 attempts (jumper selectable to one, as previously noted) to establish the correct cylinder address before the function is aborted, setting RKER 12. As the data words of a sector pass through the controller, a one-word checksum word is calculated and compared with the checksum read from the disk drive. If there is a discrepancy between the two checksums, RKER 01 (Checksum Error) is set, and the controller reaction is determined by RKCS 06 (IDE) and RKCS 08 (SSE, Stop on Soft Error). An RKWC overflow at any time from the start of the Read function stops the NPR data transfers and sets RKCS 07 (RDY) at the end of the current sector. If the RKWC has not overflowed at the end of a given sector, the function is continued at the next contiguous sector.

- 1.3.2.7 Write Check Function The Write Check function is used to compare the contents of memory to the contents of a continuous block of data on a disk cartridge. The controller first performs a Seek function, just as for a Write function, and then reads and checks the next header word. If the cylinder address is correct, the controller waits for SC = SA, then begins reading the rest of the sector (Data and Checksum) while performing BUS NPR transfers for each data word. Each data word from the disk drive is compared, bit by bit, with memory data from the Unibus. The disk drive checksum, in turn, is compared with the checksum calculated by the controller. If any bit is found to be in error, RKER 00 (Write Check Error) is set. Controller reaction is then determined by RKCS 06 (IDE) and RKCS 08 (SSE). The Write Check function may be performed on a short sector (less than 256 data words) as long as the number of words write checked is equal to the number of words previously written into the sector.

- 1.3.2.8 Read Check Function The Read Check function is identical to a normal Read function, except that no NPRs occur. Only the checksum is calculated and compared with the checksum read from the disk drive. This function enables the program to know beforehand if a given block of data is readable and error free. Because the Read Check is essentially a parity check, it must be performed on a whole-sector basis only.

1.3.2.9 Hardware Poll — The controller is capable of permitting any or all disk drives to perform a Seek or Drive Reset function simultaneously. The hardware poll feature in the Disk Control identifies the logical disk drive in RKDS 13—15 (DRIVE IDENT) for any disk drive that has completed a Seek or Drive Reset function. This poll causes an interrupt if RKCS 06 (IDE) is set, the controller is in the Ready state (RKCS 07 set), and the controller is not already attempting to initiate an interrupt from some other function. If two or more disk drives complete a Seek or Drive Reset function simultaneously, the controller interrupts once for each disk drive and identifies each in turn to the RKDS. In this situation, the processor interrupt status must be raised to a level equal to or greater than that of the RK11, or else a second interrupt will occur immediately after the first, causing the interrupt service routine to be interrupted. Similarly, back-to-back interrupts will also result from directing the heads to a cylinder at which they are already positioned, with the first interrupt coming from the initiation of a Seek function and the second coming from notification from the hardware poll that the heads are already at the desired address. In this case, also, care should be taken in the assigning of processor priorities to handle this situation.

#### 1.4 PHYSICAL DESCRIPTION

The RK11 Controller consists of the four RK11 modules (M7254, M7255, M7256, and M7257) and one system unit. The system unit containing the modules can be mounted in any PDP-11/15, 11/20, 11/35, 11/40, or 11/45 mounting box when used in conjunction with the proper power harness. The modules utilize many MSI integrated circuits (ICs). (Refer to Appendix A.)

The RK11 Disk Drive System consists of the Controller, disk drives, and the necessary cabling. Disk drives A through D (Figure 1-1) are contained in a standard 19-in. PDP-11 cabinet, which can be configured as part of a system or made to stand alone. Disk drives E through J are mounted in a second 19-in. cabinet, which is always bolted to the left side of the first cabinet. An 860 C/D Power Control Unit located at the top of the first cabinet supplies ac power for disk drives A through D. Power for disk drives E through J is supplied in a similar manner in the second cabinet. Drives A through D make up a daisy-chained bus of four disk drives connected directly to the controller. Drives E through J make up a second daisy-chained bus of four disk drives connected directly to disk drive D in the first cabinet. The M7700 card of each disk drive contains a rotary switch that defines the physical disk drive bus (DR BUS) position. The first disk drive on the DR BUS is switched to position 1 and is designated disk drive A, and so on through disk drive J. This configuration may be varied as DR BUS length allows. The maximum length of DR BUS is 50 ft. The disk drives on the DR BUS terminate in an M930 Terminator module connected to the last drive on the bus. For more disk drive system and disk drive information, refer to the RK05 Disk Drive Maintenance Manual, DEC-00-RK05-DA.

Both the RK11-D and the RK11-E require an M7700, Rev J or later. The RK11-E also requires a G180, Rev K or later, but the RK11-D is capable of operating with any revision of the G180.

#### 1.5 SPECIFICATIONS

Table 1-2 specifies the RK11 parameters in the areas of environmental limits, logic format, timing format, and power requirements, and sets forth model designations.

#### 1.6 RELATED DOCUMENTS

Table 1-3 lists software and hardware documents that pertain to the RK11 Controller.

Table 1-2 Specifications

| Category                                               | Parameters                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Environmental Limits                                   |                                                                                                                                                                                                                                                                                                          |

| Temperature:<br>Relative Humidity:<br>Vibration/Shock: | 60° to 110° F ambient (Operating) 20 to 80% without condensation (Operating) To prevent data errors, extreme vibrations should be avoided while the disk drives are transferring data. (Operating)                                                                                                       |

| Format                                                 |                                                                                                                                                                                                                                                                                                          |

| Drive Format:                                          | 1 Disk Cartridge/Disk Drive<br>203 Cylinders/Disk Drive<br>2 Disk Surfaces/Disk Drive<br>2 Tracks/Cylinder                                                                                                                                                                                               |

| Data Word Format:                                      | 12 Sectors/Track 16-bit (RK11-D) or 18-bit (RK11-E) data word 256 <sub>10</sub> = 400 <sub>8</sub> Data Words/Sector 3072 <sub>10</sub> = 6000 <sub>8</sub> Data Words/Track 614,400 <sub>10</sub> Data Words/Surface 1,247,232 <sub>10</sub> Data Words/Disk Drive Bit Density — Approximately 2200 bpi |

| Recording Method:                                      | Double Frequency                                                                                                                                                                                                                                                                                         |

| Data Transfer Path:                                    | Unibus NPR                                                                                                                                                                                                                                                                                               |

Table 1-3

Related Documents

| Title                                                         | Number           |

|---------------------------------------------------------------|------------------|

| Software: Disk Operating System Monitor Programmer's Handbook | DEC-11-SERA-D    |

| Hardware:                                                     |                  |

| PDP-11 Peripherals<br>Handbook                                | None             |

| RK05 Disk Drive Maintenance Manual                            | DEC-00-HRK05-C-D |

(Also the related PDP-11 System and Processor manuals used with the RK11 Controller.)

# CHAPTER 2 INSTALLATION

#### 2.1 INTRODUCTION

The RK11 Controller system configuration depends on the number of disk drives used in a particular disk drive system. Each RK11 can interface up to eight disk drives. The first four disk drives are housed in one cabinet; the additional disk drives are housed in a second cabinet. Each cabinet contains the power controls for the associated disk drives and all necessary cabling. The RK11 Controller options (RK11-D and RK11-E) are jumper selectable on the RK11 modules (Paragraph 2.4). For details regarding disk drive installation, refer to the RK05 Disk Drive Maintenance Manual, DEC-00-HRK05-C-D.

#### 2.2 POWER REQUIREMENTS

Power is supplied to the RK11 Controller by the +5 V power supply for the mounting box in which it is positioned. For an RK11 mounted in a BA11 Mounting Box (PDP-11/20), power is supplied via a PDP-11 system power cable, which plugs into slot A3 of the system unit. For PDP-11/35, PDP-11/40, and PDP-11/45 use, a special power cable is supplied with the equipment.

#### 2.3 CABLING REQUIREMENTS

Cabling requirements for the RK11 Controller include the Unibus cable connections and the disk drive cable (DR BUS) connections (Figure 2-1), as well as power cabling in certain systems. Both the Unibus and the DR BUS use BC11A cables.

The Unibus In cable plugs into slots A1 and B1 of the system unit, and the Unibus Out cable plugs into slots A4 and B4. If the system unit is mounted in a mounting box adjacent to other operating units utilizing the Unibus, Unibus In and Out connections between the units are made with an M920 Unibus Connector module. If the RK11 is the last unit on the Unibus, an M930 Unibus Terminator module is plugged into slots A4 and B4. The DR BUS cable plugs into system unit slots A2 and B2.

#### 2.4 RK11-D AND RK11-E OPTION CONFIGURATIONS

The RK11 Controller is normally configured as the RK11-D option, but may be configured to the RK11-E option by altering the jumpers. Details concerning these optional jumper configurations are available on the cover sheets for circuit schematics of modules M7254, M7255, M7256, and M7257. The jumpered connections are also shown in the module engineering drawings, which show the jumper function in the logic (refer to Chapter 4). The crystal on the M7255 module must also be changed for the RK11-E option. The 2.88 MHz crystal should be replaced with a 3.09 MHz crystal (see DISK 4).

# UNIBUS IN CONNECTION (SLOTS A1 AND B1)

DR BUS CABLE (SLOTS A2 AND B2)

UNIBUS OUT CABLE (SLOTS A4 AND B4)

Figure 2-1 RK11 Cable Connections

#### 2.5 INSTALLATION PROCEDURE

The jumpers on the modules should be in the desired configuration before the RK11 is installed. After the jumpers for option selection have been configured, the seven interrupt vector address jumpers and eight address selection jumpers of the M7257 should be configured to the proper values. Those values are, typically, 220 for the vector address and 777400 through 777416 for the address selection (refer to engineering drawing D-CS-M7257-0-1). There are also seven inhibit strobe jumpers on the M7257 module which, when cut, inhibit the loading of a particular programmable register (Paragraph 4.5.1).

When the jumpers have been properly configured, the desired interrupt level jumper, typically BR5, should be installed on the M7254 Status Control module (see the cover sheet for that module). The RK11 crystal clock switch on the M7255 Disk Control module (see cover sheet) should be positioned to AUTO for the RK11 internal crystal clock.

The RK11 Controller unit is installed in the following manner:

- 1. Check that wiring is not damaged, that module holddown clips are in place, and that no modules are loose.

- 2. Install the Unibus cabling or modules according to the RK11 configuration in the PDP-11 system (Paragraph 3.3).

- 3. Install the disk drive cable (DR BUS) in slots A2 and B2.

- 4. Connect the power wiring from the system.

Power is applied to the RK11 as the system power is turned on. The disk drives are powered independently, as described in the RK05 Disk Drive Maintenance Manual. When power is applied to the RK11, a processor initialize (BUS INIT) signal from the Unibus initializes the logic.

#### 2.6 INSTALLATION TESTING

To ensure that the RK11 system is properly installed and operational, installation testing is performed by running RK11 diagnostic programs, including one pass of the RK11 disk data test (MAINDEC-11-D5HA-PB2), 15 minutes of the RK11 static test (MAINDEC-11-D5HA-PB1), and random exerciser (MAINDEC-11-DZRKG-A-PB). If performance of these tests fails to reveal any errors, it may be assumed that the RK11 is operational, and that it has been correctly installed. These diagnostics are supplied with the RK11, together with instructions and descriptions regarding their use.

|  |  | -     |

|--|--|-------|

|  |  |       |

|  |  | *<br> |

|  |  |       |

|  |  | -     |

|  |  |       |

# CHAPTER 3 PROGRAMMING CONSIDERATIONS

#### 3.1 INTRODUCTION

This chapter discusses the software interface for the RK11 Controller, including device registers and their addresses, the interrupt process, timing considerations, and data format.

#### 3.2 DEVICE REGISTERS AND ADDRESSES

All RK11 software control is accomplished by seven device registers. These registers are assigned memory addresses and can be read or written into (except as noted) using instructions that refer to the respective register addresses. The seven device registers, their bit assignments, and their memory addresses are listed below. Unassigned and write-only bits are always read as zeroes. Any attempt to manipulate unassigned or read-only bits has no effect on the bit. The INIT signal refers to the initialization signal issued by the processor.

#### DRIVE STATUS REGISTER (RKDS) Address = 777400

NOTE

This register is a read-only register, and contains the selected drive status and current sector address.

| DRIVE IDENT | DPL | RK05 | DRU | SIN | SOK | DRY | R/W/S | WPS | SC= | SEC | TOR | COU | NTER |

|-------------|-----|------|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|------|

| 2 1 0       |     |      |     |     |     |     | RDY   |     | SA  | 3   | 2   | 1   | 0    |

| 15 14 13    | 12  | 11   | 10  | 9   | 8   | 7   | 6     | 5   | 4   | 3   | 2   | 1   | 0    |

| Bit   | Designation                                          | Description and Operation                                                                                                                                         |

|-------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00-03 | Sector Counter (SC)                                  | These 4 bits are the current sector address of the selected drive. Sector address 00 is defined as the sector following the sector that contains the index pulse. |

| 04    | Sector Counter<br>Equals Sector<br>Address (SC = SA) | Indicates that the disk heads are positioned over the disk address currently held in the sector address.                                                          |

| 05    | Write Protect Status (WPS)                           | Sets when the selected disk is in the write-protected mode.                                                                                                       |

| Bit   | Designation                          | Description and Operation                                                                                                                                                                                                                                                                                                                                                     |

|-------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06    | Read/Write/Seek<br>Ready (R/W/S RDY) | Indicates that the selected drive head mechanism is not in motion, and that the drive is ready to accept a new function.                                                                                                                                                                                                                                                      |

| 07    | Drive Ready (DRY)                    | Indicates that the selected disk drive complies with the following conditions:                                                                                                                                                                                                                                                                                                |

|       |                                      | a. The drive is properly supplied with power.                                                                                                                                                                                                                                                                                                                                 |

|       |                                      | b. The drive is loaded with a disk cartridge.                                                                                                                                                                                                                                                                                                                                 |

|       |                                      | c. The disk drive door is closed.                                                                                                                                                                                                                                                                                                                                             |

|       |                                      | d. The LOAD/RUN switch is set to RUN.                                                                                                                                                                                                                                                                                                                                         |

|       |                                      | e. The disk is rotating at a proper speed.                                                                                                                                                                                                                                                                                                                                    |

|       |                                      | f. The heads are properly loaded.                                                                                                                                                                                                                                                                                                                                             |

|       |                                      | g. The disk is not in a DRU (bit 10 of RKDS) condition.                                                                                                                                                                                                                                                                                                                       |

| 08    | Sector Counter-OK (SOK)              | Indicates that the Sector Counter operating on the selected drive is not in the process of changing, and is ready for examination. If this bit is not set, the Sector Counter is not ready for examination, and a second attempt should be made.                                                                                                                              |

| 09    | Seek Incomplete (SIN)                | Indicates that due to some unusual condition a Seek function cannot be completed. Can be accompanied by RKER 15 (Drive Error). Cleared by a Drive Reset function.                                                                                                                                                                                                             |

| 10    | Drive Unsafe<br>(DRU)                | Indicates that an unusual condition has occurred in the disk drive, and it is unable to properly perform any operations. Reset by setting the RUN/LOAD switch to LOAD. If, when the switch is returned to RUN, the condition recurs, an inoperative drive can be assumed, and corrective maintenance procedures should be begun. Can be accompanied by RKER 15 (Drive Error). |

| 11    | RK05 Disk on Line (RK05)             | Always set, to identify the selected disk drive as RK05.                                                                                                                                                                                                                                                                                                                      |

| 12    | Drive Power Low<br>(DPL)             | Sets when an attempt is made to initiate a new function, or if a function is actively in process when the control senses a loss of power to one of the disk drives. Can be accompanied by RKER 15 (Drive Error). Reset by a BUS INIT or a Control Reset function.                                                                                                             |

| 13–15 | Identification of Drive (ID)         | If an interrupt occurs, these bits will contain the binary representation of the logical drive number that caused the interrupt.                                                                                                                                                                                                                                              |

## ERROR REGISTER (RKER) Address = 777402

NOTE

This is a read-only register.

| DRE | OVR | WLO | SKE | PGE | NXM | DLT | TE | NXD | NXC | NXS | U | NUSI | ED | CSE | WCE |

|-----|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|---|------|----|-----|-----|

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8  | 7   | 6   | 5   | 4 | 3    | 2  | 1   | 0   |

| Bit      | Designation                   | Description and Operation                                                                                                                                                                                                                           |

|----------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Write Check<br>Error (WCE)    | Indicates that an error was encountered during a Write Check function as a result of a faulty bit comparison between disk data and memory data. Clears upon the initiation of a new function. This is a soft error condition.                       |

| 01       | Checksum Error<br>(CSE)       | Sets while performing a Read Check or a Read function as a result of a faulty recalculation of the checksum. Cleared upon the initiation of any new function. This is a soft error condition.                                                       |

| 02-04    | Unused                        |                                                                                                                                                                                                                                                     |

| The rema | <del>-</del>                  | e all hard errors, and are cleared only by a BUS INIT or a Control                                                                                                                                                                                  |

| 05       | Nonexistent<br>Sector (NXS)   | Indicates that an attempt was made to initiate a transfer to a sector larger than 13 <sub>8</sub> .                                                                                                                                                 |

| 06       | Nonexistent<br>Cylinder (NXC) | Indicates that an attempt was made to initiate a transfer to a cylinder larger than 3128.                                                                                                                                                           |

| 07       | Nonexistent Disk (NXD)        | Indicates that an attempt was made to initiate a function on a nonexistent drive.                                                                                                                                                                   |

| 08       | Timing Error<br>(TE)          | Indicates that a loss of timing pulses for at least 5 $\mu$ s has been detected.                                                                                                                                                                    |

| 09       | Data Late<br>(DLT)            | Sets during a Write or Write Check function when the multibuffer file is empty and the operation is not yet complete. Sets during a Read function when the multibuffer file is filled and the operation is not yet complete.                        |

| 10       | Nonexistent Memory (NXM)      | Sets if memory does not respond with a SSYN within 20 $\mu$ s of the time when the RK11 becomes bus master during an NPR sequence. Because of the speed of the RK05 Disk Drive, it is possible that NXM will be accompanied by RKER 09 (Data Late). |

| Bit | Designation                   | Description and Operation                                                                                                                                                                                                                                                            |

|-----|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | Programming<br>Error (PGE)    | Indicates that RKCS 10 (Format) was set while initiating a function other than Read or Write.                                                                                                                                                                                        |

| 12  | Seek Error<br>(SKE)           | Sets if the disk head mechanism is not properly positioned while executing a normal Read, Write, Read Check, or Write Check function. The control checks 16 times before flagging this error. A simple jumper change will force the control to check just once.                      |

| 13  | Write Lockout Violation (WLO) | Sets if an attempt is made to write on a disk that is currently write-protected.                                                                                                                                                                                                     |

| 14  | Overrun<br>(OVR)              | Indicates that, during a Read, Write, Read Check, or Write Check function, operations on sector 13 <sub>8</sub> , surface 1 of cylinder address 312 <sub>8</sub> were finished, and the RKWC has not yet overflowed. This is essentially an attempt to overflow out of a disk drive. |

| 15  | Drive Error<br>(DRE)          | Sets if one of the drives in the system senses a loss of either ac or dc power and a function is either initiated or in process while the selected drive is not ready or in some error condition.                                                                                    |

### CONTROL STATUS REGISTER (RKCS) Address = 777404

|   | ERR | HE | SCP | V             | IBA | FMT | EXB | SSE | RDY | IDE | EX. | ИЕМ. | FU | NCTI | ON | GO |

|---|-----|----|-----|---------------|-----|-----|-----|-----|-----|-----|-----|------|----|------|----|----|

| l |     |    |     | $/\backslash$ |     |     |     |     |     |     | 1   | 0    | 2  | 1    | 0  |    |

|   | 15  | 14 | 13  | 12            | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4    | 3  | 2    | 1  | 0  |

| Bit | Designation        | Description and Operation                                                                                                                                                                                                                                                                                                                            |

|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00  | GO<br>(Write Only) | Loaded by the operator. Causes the control to carry out the function contained in bits 01 through 03 of the RKCS (Function). Remains set until the control actually begins to respond to GO, which may take from 1 $\mu$ s to 3.3 ms, depending on the current operation of the selected disk drive (to protect the format structure of the sector). |

# Bit Designation

#### **Description and Operation**

01-03 Function (Read/Write)

The Function register, or function bits, are loaded with the binary representation of the function to be performed by the control when a GO command is initiated. These bits are loaded by the program and cleared by BUS INIT. They retain the function until altered by the program or cleared, enabling the user to continue from a soft error condition with GO. A description of each of the eight functions is given in Paragraph 1.3.2. The binary codings are as follows:

| Bit 2 | Bit 1 | Bit 0 | Operation     |

|-------|-------|-------|---------------|

| 0     | 0     | 0     | Control Reset |

| 0     | 0     | 1     | Write         |

| 0     | 1     | 0     | Read          |

| 0     | 1     | 1     | Write Check   |

| 1     | 0     | 0     | Seek          |

| 1     | 0     | 1     | Read Check    |

| 1     | 1     | 0     | Drive Reset   |

| 1     | 1     | 1     | Write Lock    |

04,05 Memory Extension

(MEX)

(Read/Write)

Reserved for extended bus addresses used in conjunction with the RKBA. This 2-bit counter increments each time the RKBA overflows. A bus DATO to these bits overrides any RKBA overflow. Loaded by the program and cleared by BUS INIT. Use of these bits is intended for systems equipped with a memory larger than 32K words.

O6 Interrupt on Done

Enable (IDE)

(Read/Write)

When set causes the control to issue a bus request and interrupt to vector address 220 if:

- a. A function has completed activity.

- b. A hard error is encountered.

- c. A soft error is encountered and bit 08 of the RKCS (SSE) is set.

- d. RKCS 07 (RDY) is set and GO is not set.

| Bit | Designation                                      | Description and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07  | Control Ready<br>(RDY)<br>(Read Only)            | Indicates that the control is ready to perform a function. Set by INIT, a hard error condition, or by the termination of a function. Cleared by GO being set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 08  | Stop on Soft Error (SSE)                         | If a soft error is encountered when this bit is set:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | (Read/Write)                                     | a. All control action will stop at the end of the current sector if RKCS 06 (IDE) is reset, or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |                                                  | b. All control action will stop and a bus request will occur at the end of the current sector if RKCS 06 (IDE) is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 09  | Extra Bit (EXB)                                  | For the RK11-D and RK11-E, EXB is unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10  | Format (FMT)<br>(Read/Write)                     | FMT is under program control, and must be used only in conjunction with normal Read and Write functions. Used to format a new disk pack or to reformat any sector erased due to control or drive failure. Alters the normal Write operation, under which the header is rewritten each time the associated sector is rewritten, in that the head positioner is not checked for proper positioning before the Write. Alters the normal Read operation in that only one word, the header word, is transferred to memory per sector. For example, a 3-word Read function in Format mode will transfer header words from three consecutive sectors to three consecutive memory locations for software checking. |

| 11  | Inhibit Incrementing the RKBA (IBA) (Read/Write) | Inhibits the RKBA from incrementing during a normal transfer function. This allows data transfers to occur to or from the same memory location throughout the entire transfer operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12  | Unused                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13  | Search Complete<br>(SCP)<br>(Read Only)          | Indicates that the previous interrupt was the result of some previous Seek or Drive Reset function. Cleared at the initiation of any new function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14  | Hard Error<br>(HE)<br>(Read Only)                | Sets when any of RKER $05-15$ are set. Stops all control action, and processor reaction is dictated by RKCS 06 (IDE), until cleared, along with RKER $05-15$ , by INIT or a Control Reset function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15  | Error<br>(ERR)<br>(Read Only)                    | Sets when any bit of the RKER sets. Processor reaction is dictated by RKCS 06 and RKCS 08 (IDE and SSE). Cleared if all bits in the RKER are cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

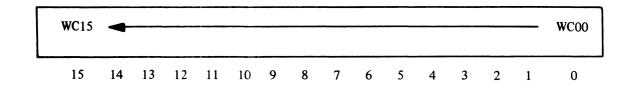

#### WORD COUNT REGISTER (RKWC) Address = 777406

Bit Designation

00-15 WC00-WC15

(Read/Write)

### **Description and Operation**

The bits in this register contain the 2's complement of the total number of words to be affected or transferred by a given function. The register increments by one after each word transfer. When the register overflows (all WC bits go to zero), the transfer is complete and RK11 operation is terminated at the end of the present disk sector. However, only the number of words specified in the RKWC are transferred.

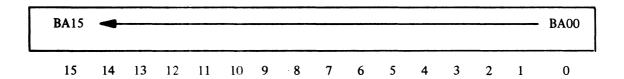

#### CURRENT BUS ADDRESS REGISTER (RKBA) Address = 777410

Designation

00-15 BA00-BA15 (Read/Write)

Bit

#### **Description and Operation**

The bits in this register contain the bus address to or from which data will be transferred. The register is incremented by two at the end of each transfer. If the system has extended memory, the RKBA will overflow to the EX MEM (bits 04 and 05 of the RKCS) to reflect the extended bus addresses.

#### **DISK ADDRESS REGISTER (RKDA)**

**Address = 777412**

| DRIV | /E SE | LECT |    | (  | CYLIN | NDER | ADD | RESS |   |   | SUR | SEC1 | OR A | ADDR | ESS |

|------|-------|------|----|----|-------|------|-----|------|---|---|-----|------|------|------|-----|

| 2    | 1     | 0    | 7  | 6  | 5     | 4    | 3   | 2    | 1 | 0 |     | 3    | 2    | 1    | 0   |

| 15   | 14    | 13   | 12 | 11 | 10    | 9    | 8   | 7    | 6 | 5 | 4   | 3    | 2    | 1    | 0   |

#### NOTE

This register will not respond to commands while the controller is busy. Therefore, RKDA bits are loaded from the bus data lines only in the Control Ready (RDY — bit 07 of the RKCS) state, and are cleared by BUS INIT and Control Reset. The RKDA is incremented automatically at the end of each disk sector.

| Bit   | Designation                    | <b>Description</b> and <b>Operation</b>                                                                                                                    |

|-------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00-03 | Sector Address<br>(SA)         | Binary representation of the disk sector to be addressed for the next function.                                                                            |

| 04    | Surface<br>(SUR)               | When active, enables the lower disk head so that operation is performed on the lower surface; when inactive, enables the upper disk head.                  |

| 05-12 | Cylinder Address<br>(CYL ADDR) | Binary representation of the cylinder address currently being selected. The largest valid address or number for the cylinder address is 312 <sub>8</sub> . |

| 13–15 | Drive Select<br>(DR SEL)       | Binary representation of the logical drive number currently being selected.                                                                                |

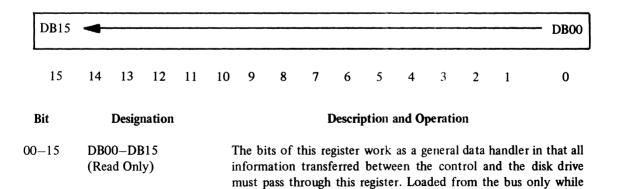

#### DATA BUFFER REGISTER (RKDB) Address = 777416

# NOTE Address 777414 is unused.

the RK11 is bus master during an NPR sequence.

#### 3.3 DATA FORMAT

Data is stored on the disk cartridge in groups of 12 sectors per track for both 16-bit (RK11-D) and 18-bit (RK11-E) options. Each of the twelve disk sectors contains 256 words and is defined by physical sector marks. These sector marks generate a sector pulse from the disk drive to the controller. Another similar physical disk mark, called an index mark, defines the starting point for the sequence of sectors. All of the sectors are formatted identically in five parts; preamble (terminated with a sync bit), header, data, checksum, and postamble (Figure 3-1).

**SYNC BIT**

| PREAMBLE                           | HEADER                          | DATA                                                              | CHECKSUM                       | POSTAMBLE           |

|------------------------------------|---------------------------------|-------------------------------------------------------------------|--------------------------------|---------------------|

| 15 <sub>8</sub> Words<br>of Zeroes | Cylinder<br>Address<br>(1 Word) | 256 <sub>10</sub> (400 <sub>8</sub> ) Words<br>(16-Bit or 18-Bit) | Sector<br>Checksum<br>(1 Word) | 1 Word<br>of Zeroes |

The preamble and postamble areas of a sector serve as boundaries before and after the information major states (header, data, and checksum) to ensure compatibility between disk drives at the cartridge level despite variations in sector pulse positioning (refer to the RK05 Disk Drive Maintenance Manual, DEC-00-HRK05-C-D).

The preamble consists of 15<sub>8</sub> words of zeroes, adequate to guarantee that RD GATE will turn on during a known zero data field. The disk drive head then waits for the first one to occur (sync bit), and begins to read with the header word. For a Write function, the sync bit is automatically written by hardware following 15<sub>8</sub> words of zeroes.

The header area of a sector consists of a single word containing the cylinder address from RKDA 05 - 12. Before a data transfer function is performed, the header word is read and checked against the cylinder address portion of the RKDA to ensure that the disk drive heads are positioned above the proper cylinder. The Write function always rewrites the header on the disk, using the cylinder address portion of the RKDA. The sector format for a raw (unformatted) cartridge is written under program control in conjunction with RKCS 10 (Format, FMT) (Paragraph 3.2).

The data area consists of 256<sub>10</sub> data words. These words, like all of the words in each area of the sector, are 16 bits long in the RK11-D and 18 bits long in the RK11-E.

The checksum area of a sector consists of a single word that is the checksum of all 256 data words. This checksum is compared by the controller to the checksum that it calculates itself whenever a Write Check, Read, or Read Check function is performed within a given sector. For a Write function, the controller calculates a checksum and writes it on the disk cartridge following the last data word.

Short portions (less than 256 data words) of a sector may be read or written as long as this short sector is the last sector of the data transfer. When a short sector is written, the remainder of the sector is automatically written with zeroes. The Write Check function may be performed on a short sector as long as the number of words write checked is equal to the number of words previously written into the sector. Because the Read Check function is essentially a parity check, it must be performed on a whole-sector basis only.

#### 3.4 PROGRAM INTERRUPTS

A program interrupt is initiated by an interrupt request, which can only occur if RKCS 06 (IDE, Interrupt Done Enable) is set. Six hardware conditions can generate an interrupt request to the processor:

- a. The occurrence of a hard error condition (RKCS 14 HE).

- b. The presence of a soft error condition (RKER 00 WCE) or RKER 01 (CSE) if RKCS 08 (SSE) is set.

- c. Completion of transfer of the designated number of words.

- d. The acceptance (Address Acknowledge) of a Seek or Drive Reset function by the selected disk drive, freeing the controller for hardware polling or a new function.

- e. The initiation of a Write Lock function on a disk drive, indicating that the controller is free to perform a new function.

- f. The completion of hardware polling (RKCS 13 SCP), indicating that the disk drive in the DR SEL bits of the RKDA has completed a Seek or Drive Reset function (RKDS 06 R/W/S RDY).

The interrupt request of the RK11 Controller can be configured at BR levels 4, 5, 6, or 7. The RK11 is typically set at level BR5.

Because of the format structure of the RK11, any interruption of the Write function cannot be tolerated until the end of the current sector, as it would result in what would be essentially an unformatted disk cartridge. As a result, outside intervention is inhibited until the current sector is completed, including Control Reset functions and processor initialize (BUS INIT) signals. This means that such functions as Control Reset, Seek, and Write Lock, which take only a few microseconds to initiate, can take as long as 3.3 ms if initiated during a Write function. For this reason, Seek, Drive Reset, and Write Lock functions cause an interrupt as soon as the function is initiated, provided that RKCS 06 (IDE) is set.

#### 3.5 TIMING CONSIDERATIONS

RK11 timing is a consideration in the performance of overlapping Seek or Drive Reset functions, because these functions can be initiated on free disk drives while previous Seek or Drive Reset functions are in process on other disk drives. Thus, up to eight disk drives can be performing a Seek or Drive Reset function simultaneously. The hardware poll logic of the Disk Control generates an interrupt when a disk drive has completed the Seek or Drive Reset function (RKDS 06 - R/W/S RDY set). When a Seek or Drive Reset function has been initiated on the disk drive (Address Acknowledge), an interrupt request occurs if RKCS 06 (IDE) is set. This process normally requires 1  $\mu$ s, but may range up to 3.3 ms if an attempt is made to abort a Write function. Head movement, however, may take as long as 80 ms, after which a second interrupt (RKCS 13 - Search Complete) occurs (if Interrupt Done Enable is set). In the interval between these two events, the selected disk drive is busy moving its heads, but the controller is free to perform any RK11 function on any other available disk drive. Once a disk drive has begun moving its head mechanism, only a Drive Reset function can stop it. An attempt to perform any other function on a disk drive whose heads are in motion results in a hard error condition.

The data transfer (Read, Write, Read Check, and Write Check) functions all begin with an automatic Seek function. This allows the user of a single disk drive system to forget about the Seek function completely and initiate data transfer functions directly. The hardware poll logic is initiated only for Seek and Drive Reset functions and not for the Seek portion of data transfer functions.

#### 3.6 POWER FAIL

If any of the disk drive power supplies senses a loss of either ac or dc power, no new functions can be initiated. If only an ac power loss is sensed and a function is in process, the current disk sector is completed. If, at the beginning of the next sector, an ac power loss is still sensed but dc power is satisfactory (e.g., momentary line power fluctuations), the controller waits for ac power to return before starting operation on the next sector, as long as the next sector is in the same cylinder. However, if the heads must be moved to reach the next sector, an error condition is generated (RKER 155 – Drive Error, and RKDS 12 – Drive Power Low) and the function is aborted. If, at the beginning of the next sector, a loss of dc power is sensed, the same error condition is generated. That condition (DRE and DPL) is also set if a dc power loss occurs while the controller is actively transferring data to or from a disk drive.

# CHAPTER 4 DETAILED DESCRIPTION

#### 4.1 INTRODUCTION

This chapter provides a detailed logic level description of each of the four RK11 modules (Figure 1-2): Status Control, Disk Control, Data Paths, and Bus Control. Much of the logic is implemented by means of MSI integrated circuits (ICs). Appendix A to this manual provides logic diagrams containing pin designations for such ICs.

#### 4.2 STATUS CONTROL

The Status Control logic of the M7254 module initiates the programmable functions of the RK11 Controller and monitors logic status conditions by means of the programmable Control Status register (RKCS) and Word Count register (RKWC) and the Error register (RKER).

The RKCS receives function and control information from the Unibus and implements it by initiating and directing RK11 functions, generating interrupt requests, and monitoring RK11 status information, which it transmits to the Data Paths via the Internal Bus A Multiplexers.

The RKWC receives data transfer word count information from the Unibus, is incremented for each word of data that is transferred, and overflows (WC OVF) to indicate the end of NPR transfers.

The RKER provides error status information to the RKCS control logic and to the programmer via the Internal Bus A Multiplexers.

The Status Control also contains the bus request level selection jumper for the Unibus interrupt level lines. The RK11 Controller is normally set at bus request level 5 (BR5). Status Control logic is contained in engineering drawing D-CS-M7254-0-1, sheets 1 through 6.

#### 4.2.1 RKCS, Function, and Control Logic

The function logic of the RKCS determines the function to be performed and provides control signals for each function. The control logic directs RK11 logic operations, supplies status information to the RKCS, and generates interrupt requests to the Bus Control.