KD11-E central processor maintenance manual

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

## CONTENTS

|           |                                     | Page   |

|-----------|-------------------------------------|--------|

| CHAPTER 1 | OVERALL DESCRIPTION                 |        |

| CHAPTER 2 | INSTRUCTION SET                     |        |

| 2.1       | INTRODUCTION                        | . 2-1  |

| 2.2       | ADDRESSING MODES                    |        |

| 2.3       | PDP-11/34 INSTRUCTIONS              |        |

| 2.4       | INSTRUCTION EXECUTION TIME          |        |

| 2.4.1     | Basic Instruction Set Timing        |        |

| 2.4.2     | Bus Latency Times                   |        |

| 2.5       | EXTENDED INSTRUCTION SET            |        |

| 2.6       | INSTRUCTION SET DIFFERENCES         |        |

| CHAPTER 3 | CPU OPERATING SPECIFICATIONS        |        |

| CHAPTER 4 | DETAILED HARDWARE DESCRIPTION       |        |

| 4.1       | INTRODUCTION                        | . 4-1  |

| 4.2       | DATA PATH                           |        |

| 4.2.1     | General Description                 |        |

| 4.2.2     | Arithmetic Logic Unit (ALU)         |        |

| 4.2.3     | Scratchpad                          |        |

| 4.2.4     | B Leg                               |        |

| 4.2.5     | ALU Multiplexer (AMUX)              |        |

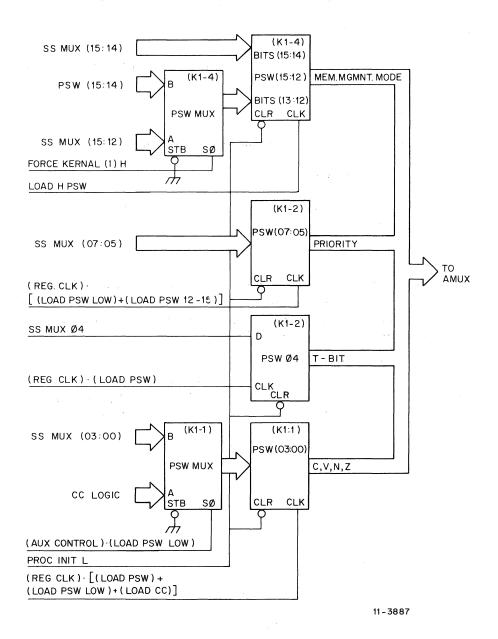

| 4.2.6     | Processor Status Word               |        |

| 4.3       | CONDITION CODES                     |        |

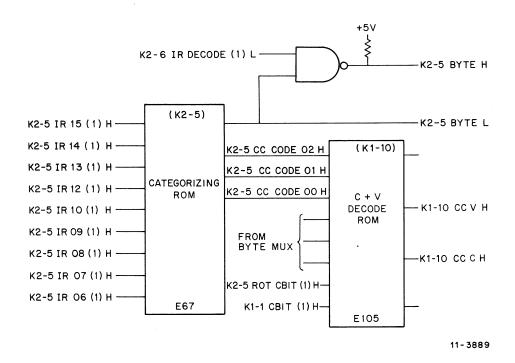

| 4.3.1     | Instruction Categorizing ROM        |        |

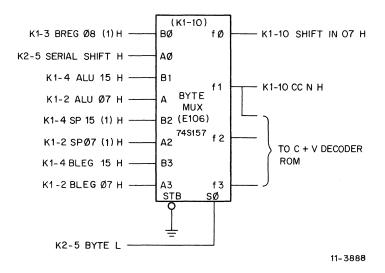

| 4.3.2     | Byte Multiplexer (BYTE MUX)         |        |

| 4.3.3     | C and V Decode ROM                  |        |

| 4.3.4     | Condition Code Signal CC Z H        | . 4-25 |

| 4.4       | UNIBUS ADDRESS AND DATA INTERFACE   |        |

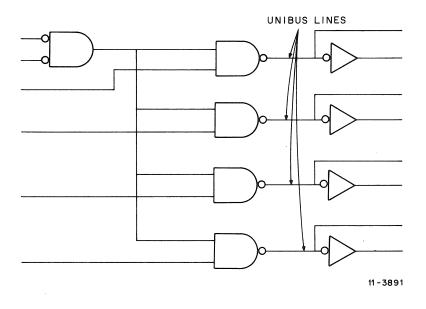

| 4.4.1     | Unibus Drivers and Receivers        | . 4-25 |

| 4.4.2     | Unibus Address Generating Circuitry | . 4-25 |

| 4.4.3     | Internal Address Decoder            |        |

| 4.5       | INSTRUCTION DECODING                | . 4-29 |

| 4.5.1     | General Description                 | . 4-29 |

| 4.5.2     | Instruction Register                | . 4-30 |

| 4.5.3     | Instruction Decoder                 | . 4-30 |

| 4.5.3.1   | Instruction Decoder Circuitry       | . 4-30 |

| 4.5.3.2   | Double-Operand Instructions         | . 4-31 |

| 4.5.3.3   | Single-Operand Instructions         |        |

| 4.5.3.4   | Branch Instructions                 |        |

| 4.5.3.5   | Operate Instructions                | . 4-34 |

| 4.6       | AUXILIARY ALU CONTROL               | . 4-35 |

| 4.7       | DATA TRANSFER CIRCUITRY             | . 4-39 |

## CONTENTS (Cont)

|          | Page                                       |

|----------|--------------------------------------------|

| 4.7.1    | General Description                        |

| 4.7.2    | Control Circuitry                          |

| 4.7.2.1  | Processor Clock Inhibit                    |

| 4.7.2.2  | Unibus Synchronization                     |

| 4.7.2.3  | Bus Control                                |

| 4.7.2.4  | M8264 NO-SACK Timeout Module               |

| 4.7.2.5  | MSYN/SSYN Time-Out Circuitry               |

| 4.7.2.6  | Bus Errors                                 |

| 4.7.2.7  | Parity Errors                              |

| 4.7.2.8  | End of Transfer Circuitry                  |

| 4.7.2.9  | Data-in-Pause Transfer                     |

| 4.7.2.10 | Odd Address Detection                      |

| 4.8      | POWER FAIL/AUTO RESTART                    |

| 4.9      | PROCESSOR CLOCK                            |

| 4.10     | PRIORITY ARBITRATION                       |

| 4.10.1   | Bus Requests                               |

| 4.10.2   | Nonprocessor Requests (NPRs)               |

| 4.10.3   | Halt Grant Requests                        |

| 4.11     | SERVICE TRAPS                              |

| 4.11.1   | General Description                        |

| 4.11.2   | Circuit Operation                          |

| 4.11.2   | MEMORY MANAGEMENT                          |

| 4.12.1   | General                                    |

| 4.12.1.1 | Introduction                               |

| 4.12.1.2 | Programming                                |

| 4.12.1.2 | Basic Addressing                           |

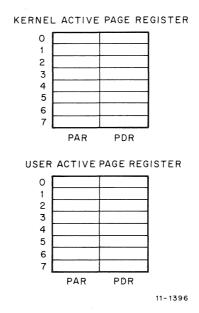

| 4.12.1.3 | Active Page Registers                      |

| 4.12.1.4 | Capabilities Provided by Memory Management |

|          | Relocation                                 |

| 4.12.2   | Virtual Addressing                         |

| 4.12.2.1 | Program Polocotion                         |

| 4.12.2.2 | Program Relocation                         |

| 4.12.2.3 | Memory Units                               |

| 4.12.3   | Protection                                 |

| 4.12.3.1 | Inaccessible Memory                        |

| 4.12.3.2 | Read-Only Memory                           |

| 4.12.3.3 | Multiple Address Space                     |

| 4.12.4   | Active Page Registers                      |

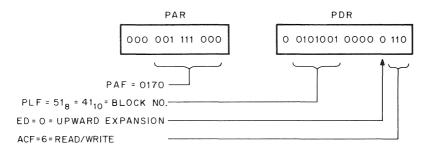

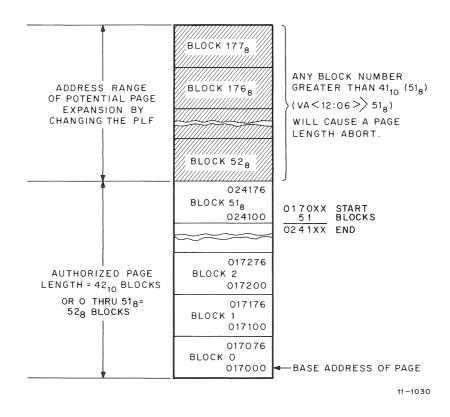

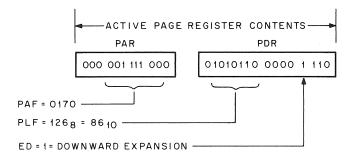

| 4.12.4.1 | Page Address Registers (PAR)               |

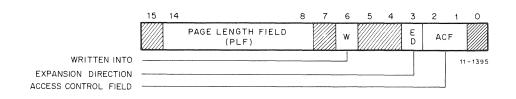

| 4.12.4.2 | Page Descriptor Registers                  |

| 4.12.5   | Virtual and Physical Addresses             |

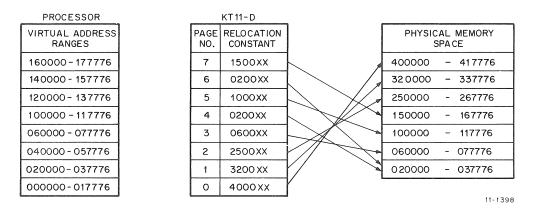

| 4.12.5.1 | Construction of a Physical Address         |

| 4.12.5.2 | Determining the Program Physical Address   |

| 4.12.6   | Status Registers                           |

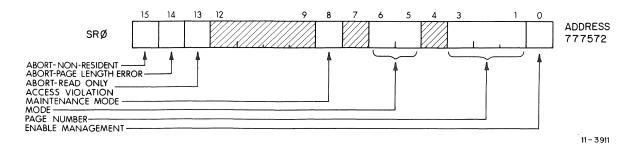

| 4.12.6.1 | Status Register 0 (SR0)                    |

| 4.12.6.2 | Status Register 2 (SR2)                    |

| 4.12.7   | Mode Description                           |

## CONTENTS (Cont)

|                                              |                                                                                                                | Page                       |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------|

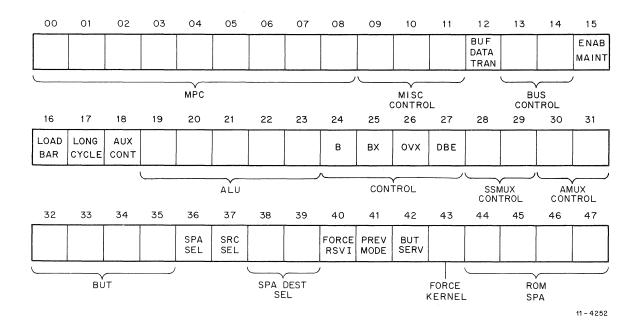

| 4.12.8<br>4.13<br>4.13.1<br>4.13.2<br>4.13.3 | Interrupt Conditions  CONTROL STORE  General Description  Branching Within Microroutines  Control Store Fields | . 4-74<br>. 4-74<br>. 4-74 |

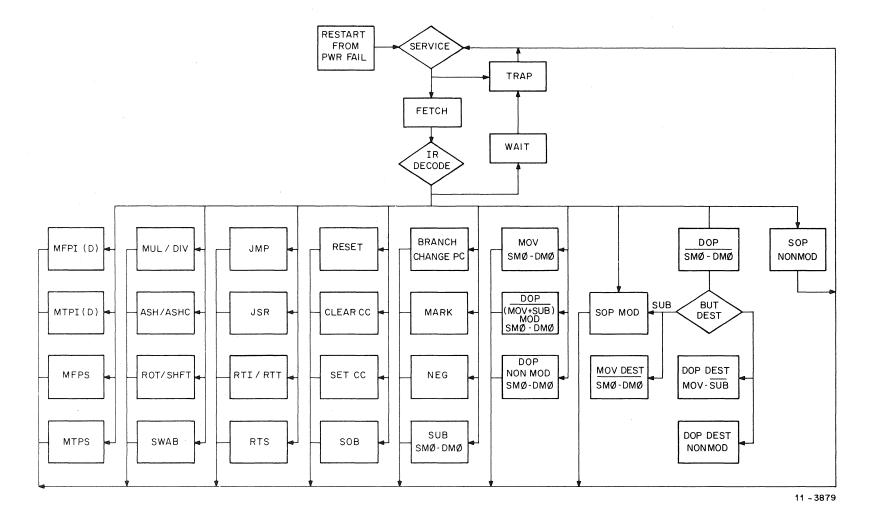

| CHAPTER 5                                    | MICROCODE                                                                                                      |                            |

| 5.1<br>5.2                                   | MICROPROGRAM FLOWS                                                                                             |                            |

|                                              | ILLUSTRATIONS                                                                                                  |                            |

| Figure No.                                   | Title                                                                                                          | Page                       |

| 2-1                                          | Addressing Mode Instruction Formats                                                                            | . 2-2                      |

| 2-2                                          | PDP-11 Instruction Formats                                                                                     |                            |

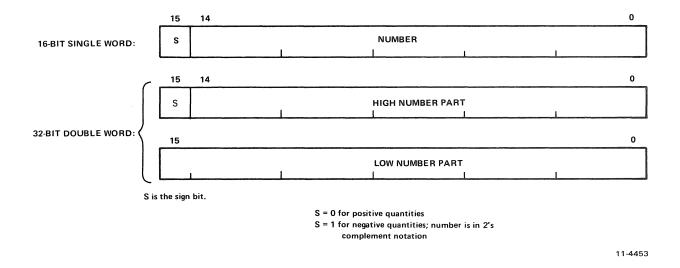

| 2-3                                          | Extended Instruction Set Number Formats                                                                        | . 2-30                     |

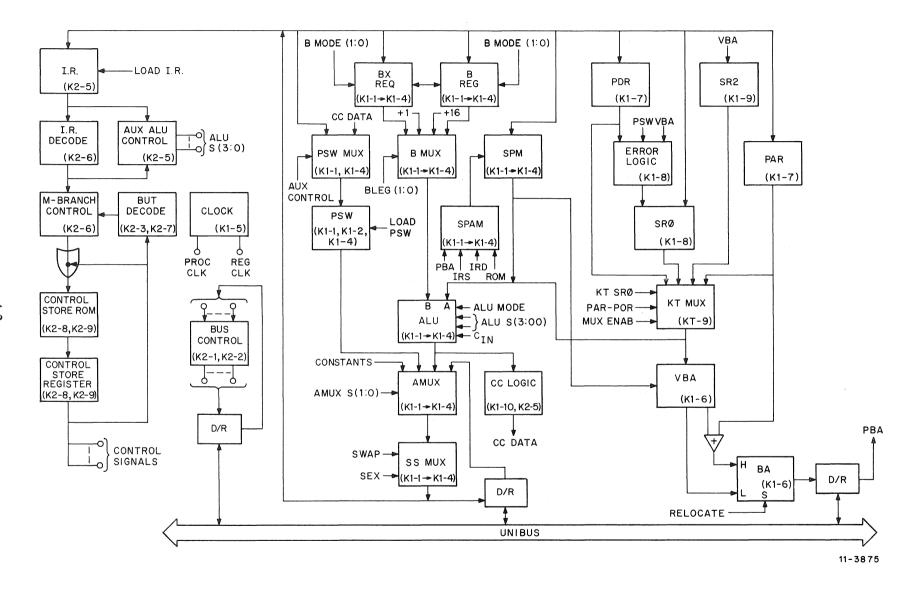

| 4-1                                          | KD11-E Block Diagram                                                                                           | . 4-2                      |

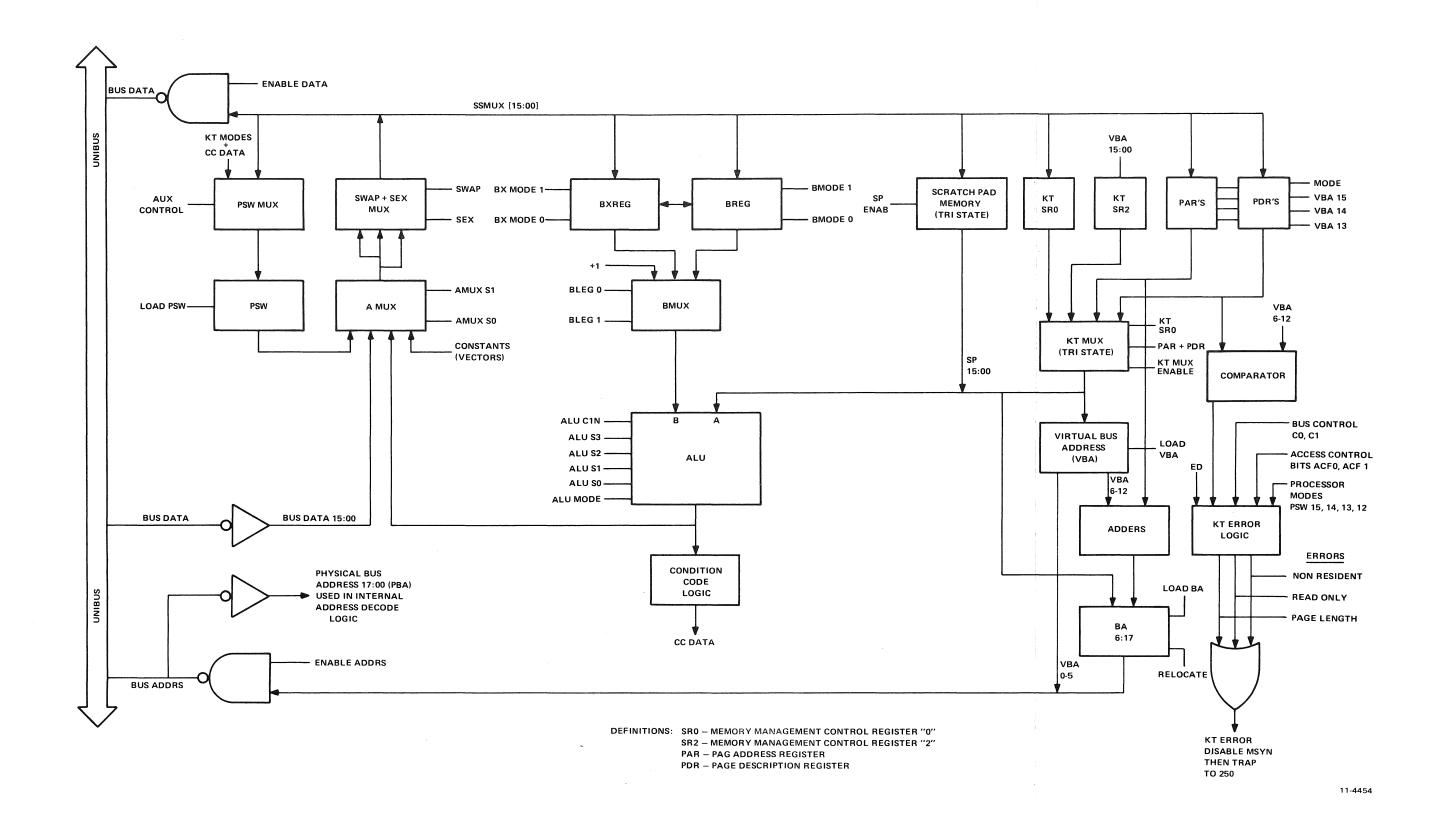

| 4-2                                          | Simplified KD11-E Data Path                                                                                    | . 4-3                      |

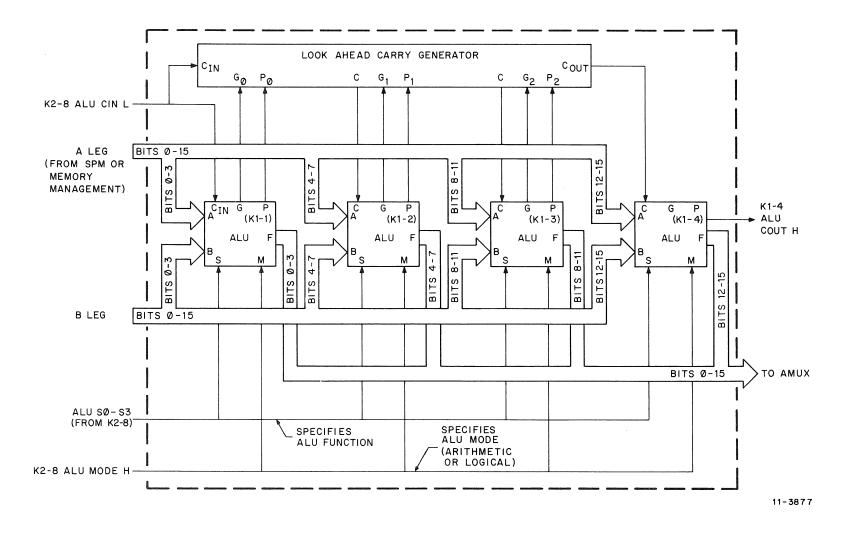

| 4-3                                          | ALU Block Diagram                                                                                              |                            |

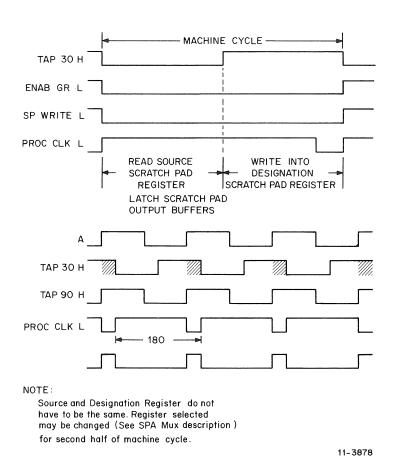

| 4-4                                          | Scratchpad Timing                                                                                              | . 4-8                      |

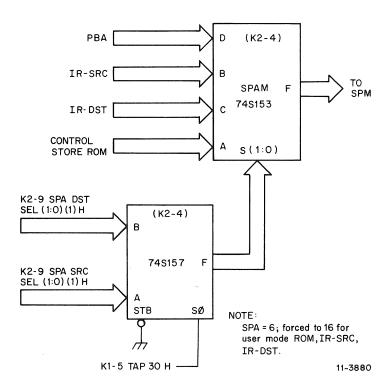

| 4-5                                          | Scratchpad Address Multiplexer (SPAM)                                                                          | . 4-9                      |

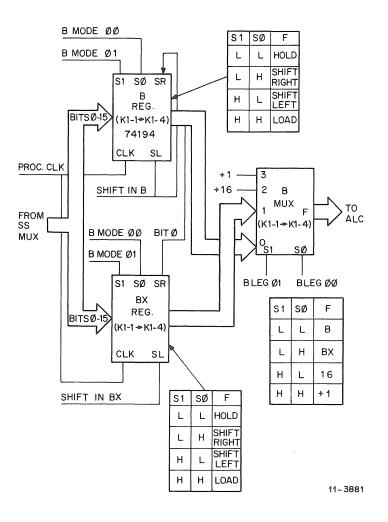

| 4-6                                          | B Leg Block Diagram                                                                                            | . 4-11                     |

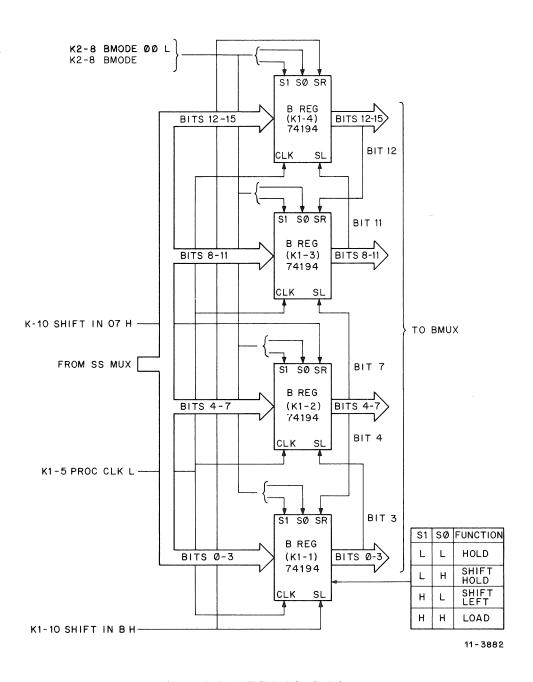

| 4-7                                          | BREG Block Diagram                                                                                             | . 4-12                     |

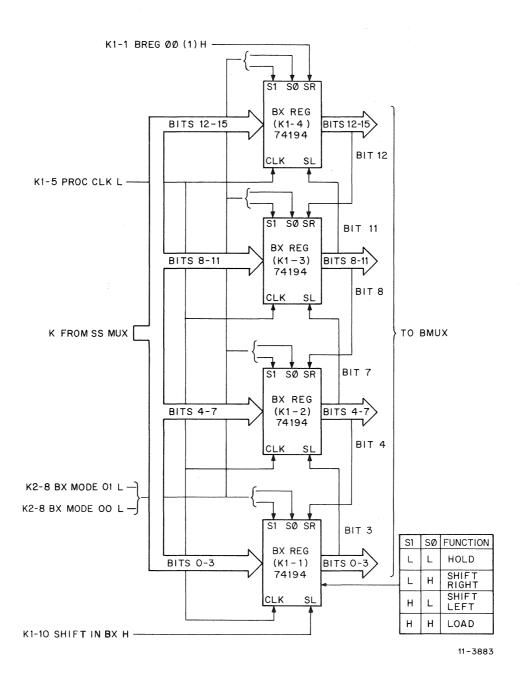

| 4-8                                          | BX REG Block Diagram                                                                                           | . 4-14                     |

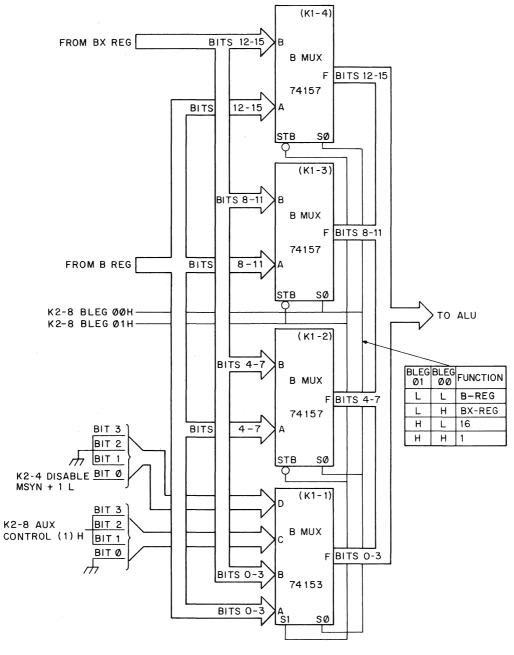

| 4-9                                          | BMUX Block Diagram                                                                                             |                            |

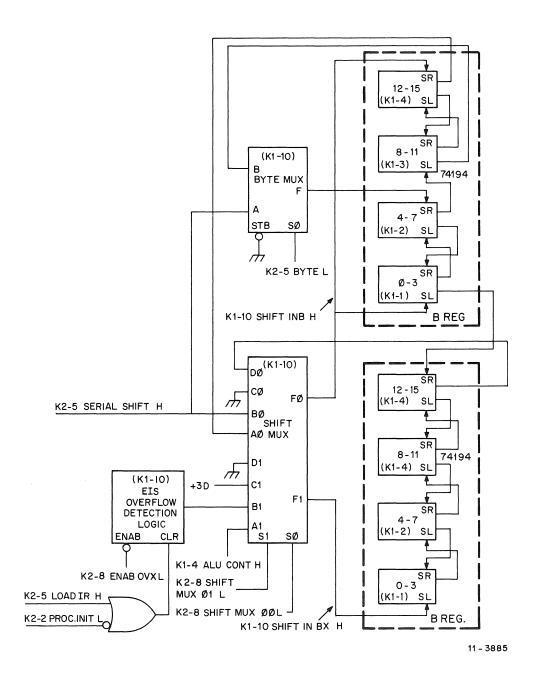

| 4-10                                         | B Leg Shift Logic                                                                                              |                            |

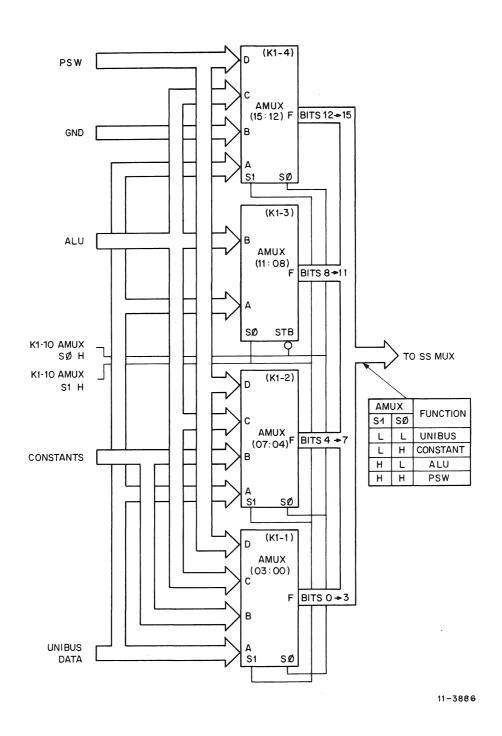

| 4-11                                         | AMUX Block Diagram                                                                                             |                            |

| 4-12                                         | Processor Status Word                                                                                          |                            |

| 4-13                                         | Byte Multiplexer                                                                                               | . 4-24                     |

| 4-14                                         | Rotate Instructions                                                                                            | . 4-26                     |

| 4-15                                         | C and R Decode ROM                                                                                             | . 4-27                     |

| 4-16                                         | Unibus Transceiver                                                                                             | . 4-27                     |

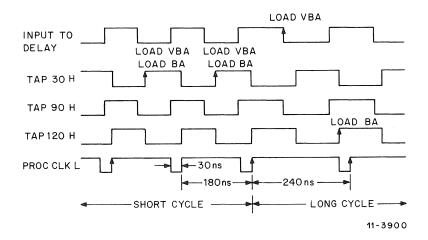

| 4-17                                         | Processor Clock Cycle Timing                                                                                   | . 4-28                     |

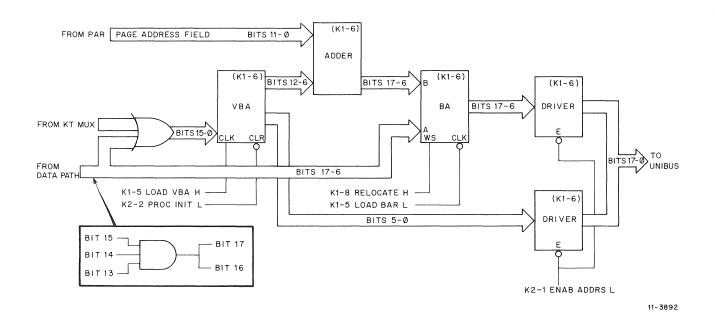

| 4-18                                         | Unibus Address Logic Block Diagram                                                                             | . 4-28                     |

| 4-19                                         | Unibus Synchronizer                                                                                            | . 4-39                     |

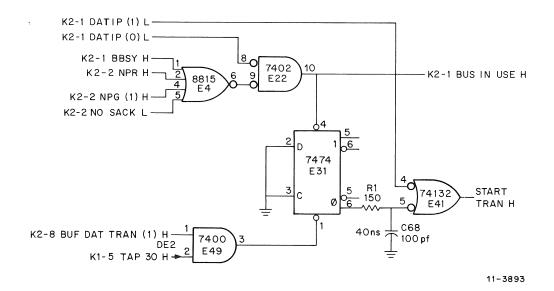

| 4-20                                         | NO-SACK Timeout Module                                                                                         | . 4-42                     |

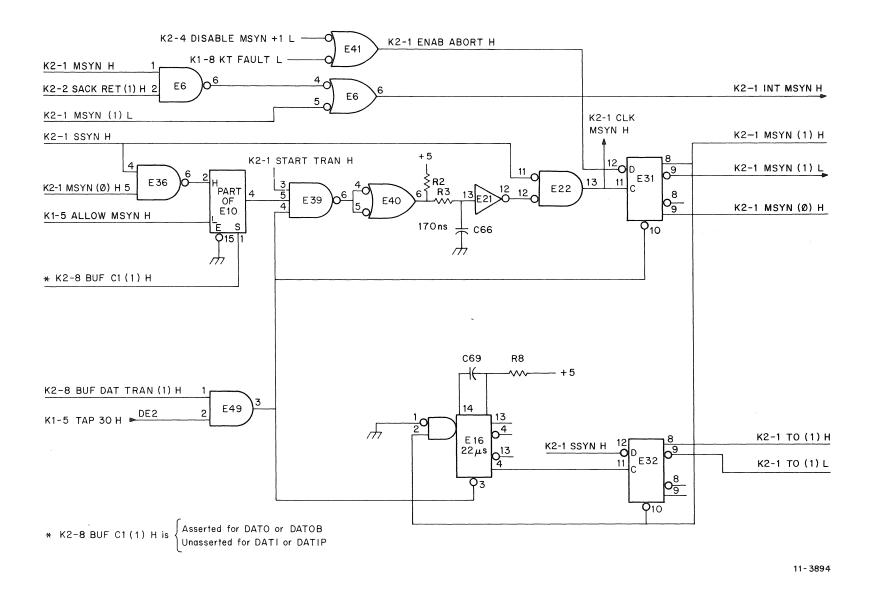

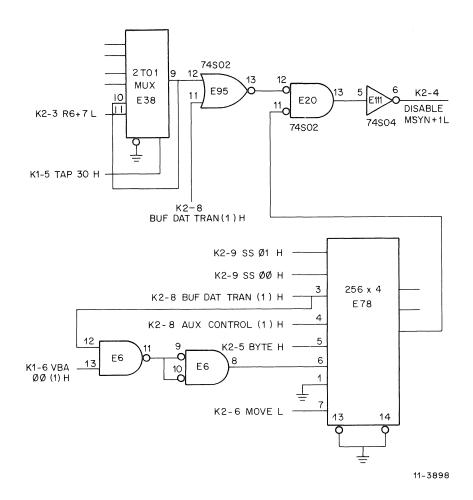

| 4-21                                         | SSYN/MSYN Control                                                                                              | . 4-43                     |

| 4-22                                         | Data Transfer Multiplexer                                                                                      |                            |

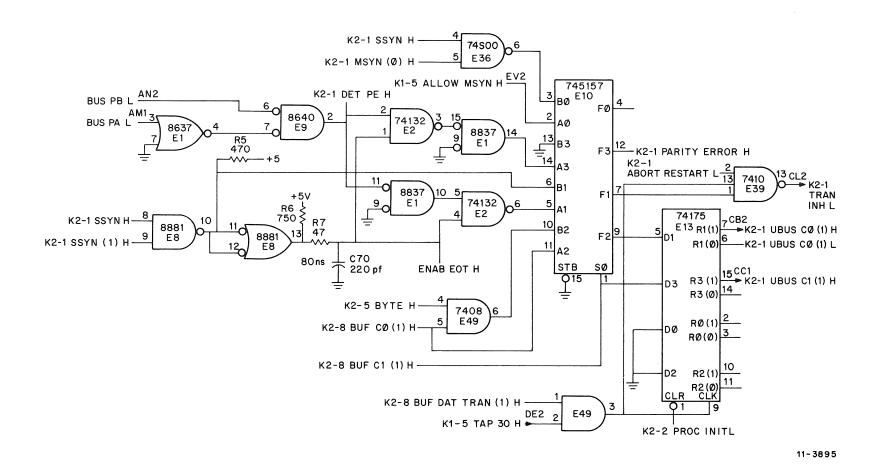

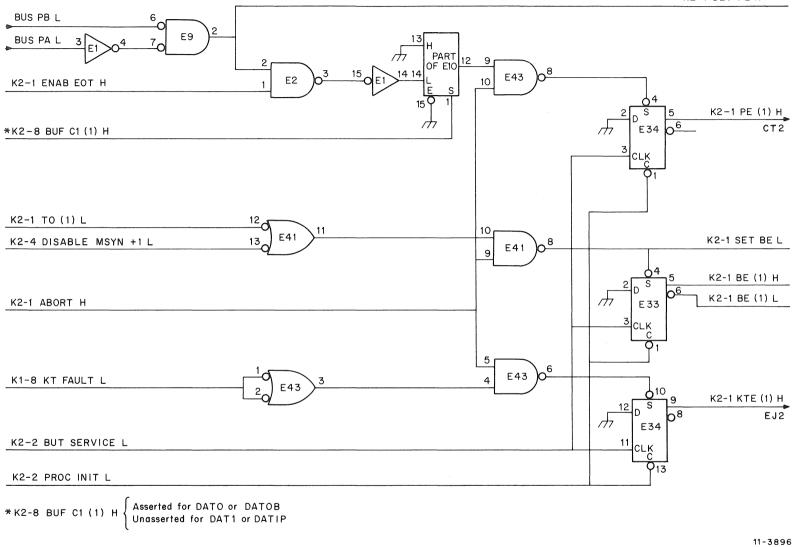

| 4-23                                         | Error Logic                                                                                                    |                            |

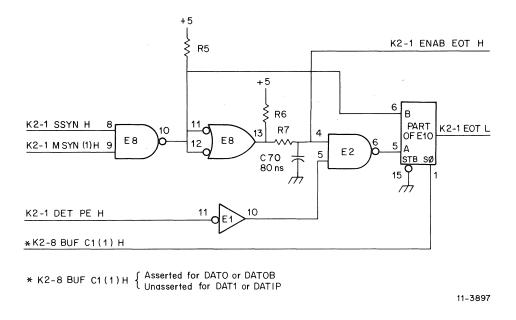

| 4-24                                         | End-of-Transfer Logic                                                                                          |                            |

| 4-25                                         | Odd Address Detection                                                                                          |                            |

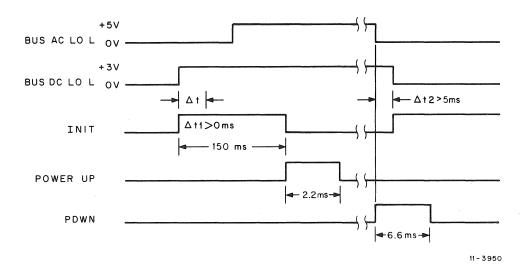

| 4-26                                         | BUS AC LO and BUS DC LO Timing Diagram                                                                         | . 4-49                     |

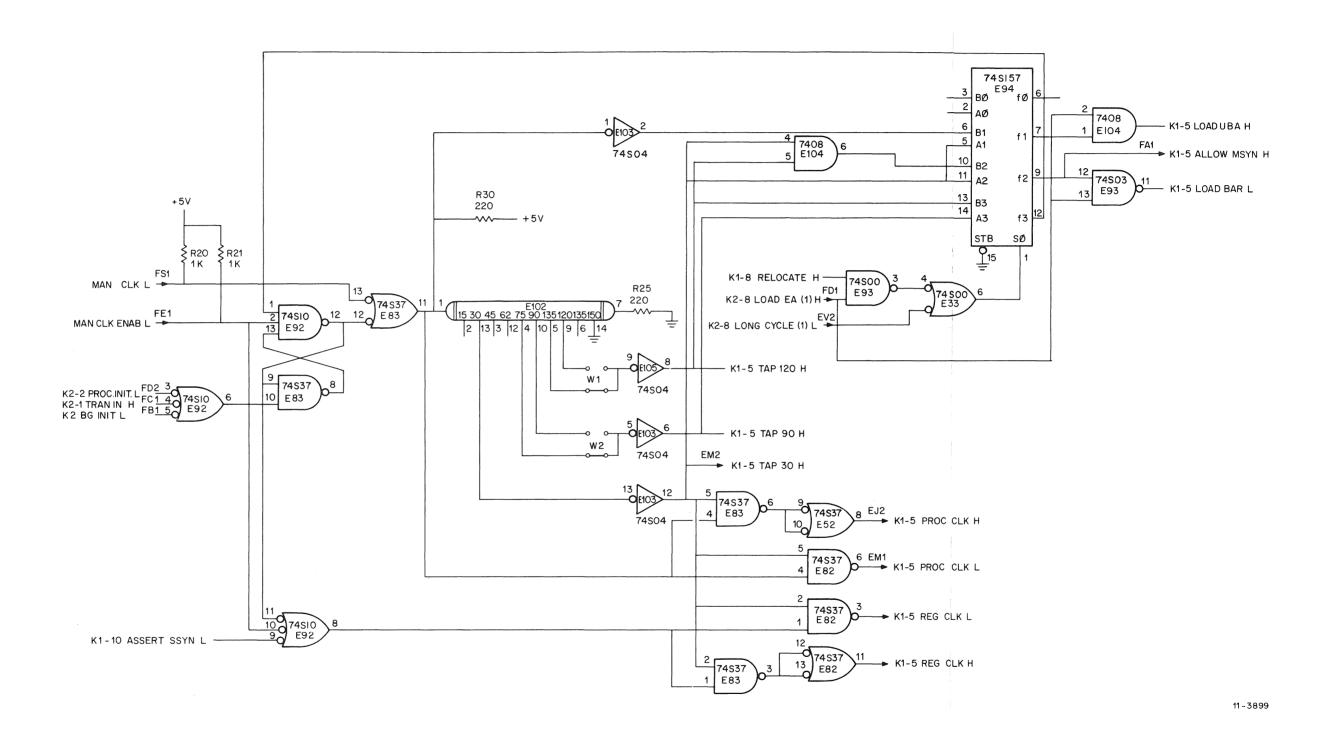

| 4-27                                         | Processor Clock Circuit                                                                                        | 4-51                       |

## ILLUSTRATIONS (Cont)

|             |                                                                 | Page   |

|-------------|-----------------------------------------------------------------|--------|

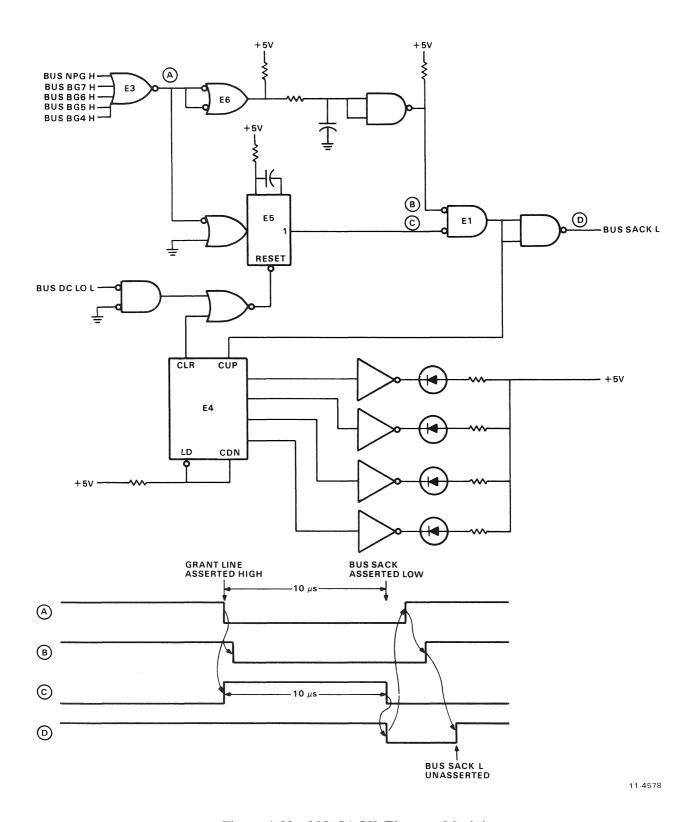

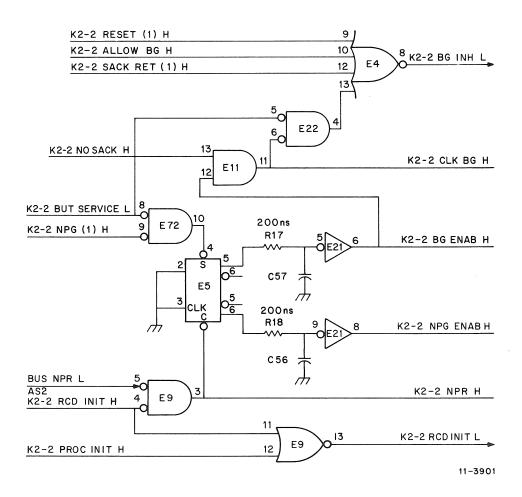

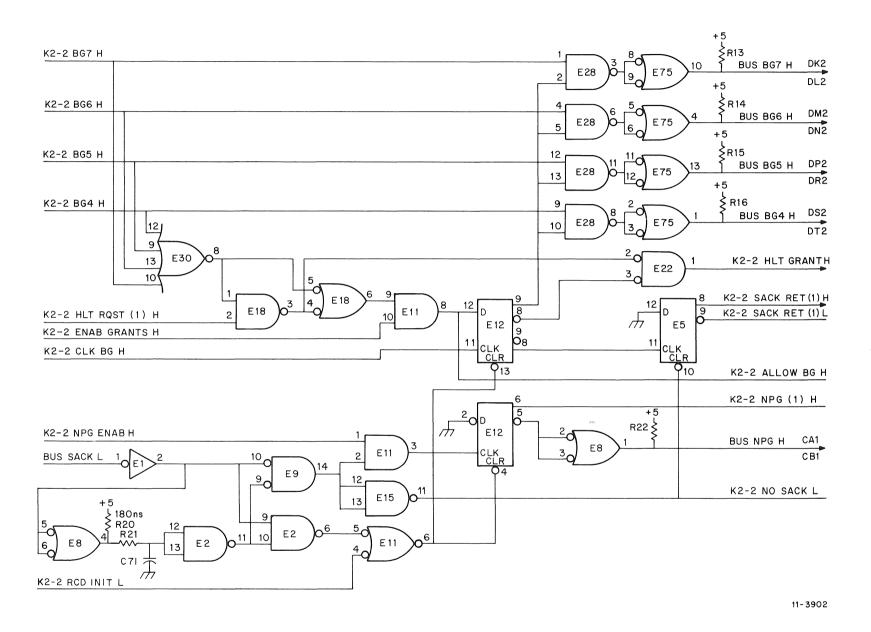

| 4-28        | Priority Arbitration Synchronizer                               | 4-53   |

| 4-29        | Priority Bus Control                                            |        |

| 4-30        | Active Page Registers                                           | 4-59   |

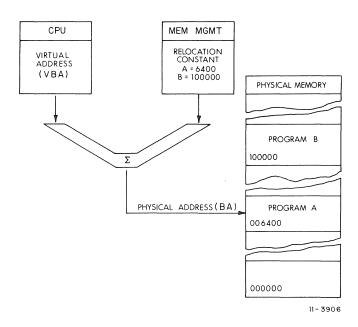

| 4-31        | Simplified Memory Relocation Example                            |        |

| 4-32        | Relocation of a 32K Word Program into 124K-Word Physical Memory |        |

| 4-33        | Page Address Register                                           |        |

| 4-34        | Page Descriptor Register                                        |        |

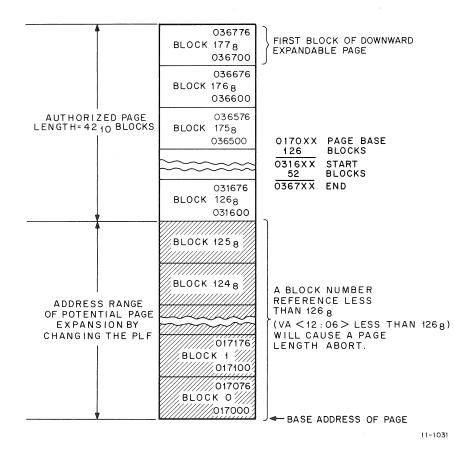

| 4-35        | Example of an Upward-Expandable Page                            |        |

| 4-36        | Example of a Downward-Expandable Page                           |        |

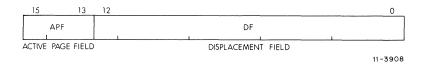

| 4-37        | Interpretation of a Virtual Address                             |        |

| 4-38        | Displacement Field of Virtual Address                           |        |

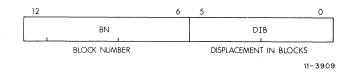

| 4-39        | Construction of a Physical Address                              |        |

| 4-40        | Format of Status Register 0 (SR0)                               |        |

| 4-41        | Format of Status Register 2 (SR2)                               |        |

| 4-42        | Control Store Fields                                            |        |

| 5-1         | KD11-E Simplified Flow Diagram                                  |        |

|             | TABLES                                                          |        |

|             | IADLES                                                          |        |

| Table No.   | Title                                                           | Page   |

| 2-1         | Addressing Modes                                                | . 2-3  |

| 2-2         | Single Operand Instructions                                     | . 2-5  |

| 2-3         | Double Operand Instructions                                     | . 2-10 |

| 2-4         | Program Control Instructions                                    | . 2-14 |

| 2-5         | Miscellaneous Instructions                                      |        |

| 2-6         | Condition Code Operators                                        |        |

| 2-7         | PDP-11/34 Instruction Set                                       |        |

| 2-8         | Programming Differences                                         |        |

| 3-1         | Standard and Modified Unibus Pin Assignments                    |        |

| 4-1         | Function Units of the KD11-E Data Path                          |        |

| 4-2         | ALU Functions and Control Signals                               |        |

| 4-3         | Scratchpad Enabling Configurations and Modes                    |        |

| 4-4         | SPAM Input Data Sources                                         |        |

| 4-5         | SPM Register Utilization                                        |        |

| 4-6         | B and BX Register Enabling Configurations and Modes             |        |

| 4-7         | BMUX Enabling Configurations and Modes                          |        |

| 4-8         | Processor Status Word Register Bit Assignments                  |        |

| <b>4-</b> 9 | Auxiliary Control for Binary and Unary Instructions             |        |

| 4-10        | Priority Service Order                                          |        |

| 4-11        | Vector Addresses                                                |        |

| 4-12        | PAR/PDR Address Assignments                                     |        |

| 4-13        | Access Control Field Keys                                       |        |

| 4-14        | Relating Virtual Address to PAR/PDR Set                         |        |

| -           |                                                                 | / 1    |

### **PREFACE**

This manual describes the KD11-E Central Processing Unit (M7265 and M7266). The user must have a general knowledge of digital circuitry and a basic understanding of PDP-11 computers to completely understand the contents of this manual.

The following related documents may be valuable as references:

PDP-11 Peripherals Handbook PDP-11/34 Processor Handbook PDP-11/34 System User's Guide (EK-11034-OP-001) KD11-E Print Set (MP00043)

# CHAPTER 1 OVERALL DESCRIPTION

The KD11-E is a 2-board central processing unit (CPU) that is combined with a memory system, Unibus terminators, and optional peripherals in a DD11-P backpanel to build a basic PDP-11/34 computer. The unit connects directly to the Unibus as a subsystem, and is capable of controlling the time allocation of the Unibus for peripherals, performing arithmetic and logic operations, and decoding instructions. It can perform data transfers directly between I/O devices and memory, do both single- and double-operand addressing, handle both 16-bit word and 8-bit byte data, and address up to 128K of Unibus address space via a memory management system.

The KD11-E is program-compatible with both the KD11-A (PDP-11/35 and PDP-11/40 computer systems) and the LSI-11 (with the inclusion of the two special LSI-11 instructions). It contains the KT11-D Memory Management System (optional with the KD11-A, not offered with the LSI-11) and executes the Extended Instruction Set (EIS) instructions, which were optional with the KD11-A and standard with the LSI-11. The KD11-E does not execute the Floating Instruction Set (FIS).

# CHAPTER 2 INSTRUCTION SET

#### 2.1 INTRODUCTION

The KD11-E is defined by its instruction set. The sequences of processor operations are selected according to the instruction decoding. The following describes the PDP-11/34 instructions and instruction set addressing modes along with instruction set differences from those of the KD11-A, KD11-B, and KD11-D.

#### 2.2 ADDRESSING MODES

Data stored in memory must be accessed and manipulated. Data handling is specified by a PDP-11/34 instruction (MOV, ADD, etc.), which usually indicates:

- 1. The function (operation code)

- 2. A general-purpose register to be used when locating the source operand and/or locating the destination operand

- 3. An addressing mode (to specify how the selected register(s) is to be used)

Because a large portion of the data handled by a computer is usually structured (in character strings, in arrays, in lists, etc.), the PDP-11/34 has been designed to handle structured data efficiently and flexibly. The general registers may be used with an instruction in any of the following ways:

- 1. As accumulators. The data to be manipulated resides within the register.

- 2. As pointers. The contents of the register are the address of the operand, rather than the operand itself.

- 3. As pointers, which automatically step through core locations. Automatically stepping forward through consecutive core locations is known as autoincrement addressing; automatically stepping backward is known as autodecrement addressing. These modes are particularly useful for processing tabular data.

- 4. As index registers. In this instance the contents of the register and the word following the instruction are summed to produce the address of the operand. This allows easy access to variable entries in a list.

PDP-11/34s also have instruction addressing mode combinations that facilitate temporary data storage structures for convenient handling of data which must be frequently accessed. This is known as the "stack."

In the PDP-11/34, any register can be used as a "stack pointer" under program control; however, certain instructions associated with subroutine linkage and interrupt service automatically use Register 6 as a "hardware stack pointer." For this reason, R6 is frequently referred to as the "SP."

R7 is used by the processor as its program counter (PC).

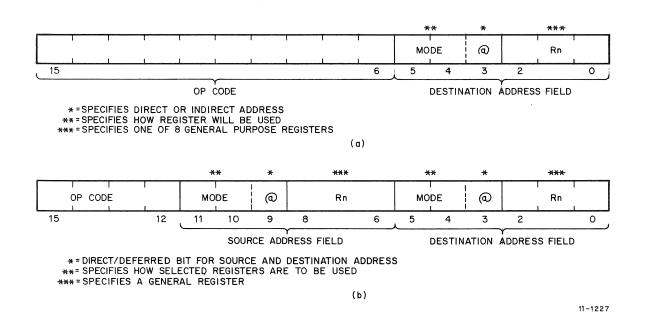

Two types of instructions utilize the addressing modes: single-operand and double-operand. Figure 2-1 shows the formats of these two types of instructions. The addressing modes are listed in Table 2-1.

Figure 2-1 Addressing Mode Instruction Formats

Table 2-1 Addressing Modes

| Mode                                              | Binary<br>Code | Name                      | Assembler<br>Syntax* | Function                                                                                                                                                                                           |

|---------------------------------------------------|----------------|---------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   |                |                           | Direct Modes         |                                                                                                                                                                                                    |

| 0                                                 | 000            | Register                  | Rn                   | Register contains operand.                                                                                                                                                                         |

| 2                                                 | 010            | Autoincrement             | (Rn)+                | Register contains address of operand. Register contents incremented after reference.                                                                                                               |

| 4                                                 | 100            | Autodecrement             | <b>–</b> (Rn)        | Register contents decremented before reference register contains address of operand.                                                                                                               |

| 6                                                 | 110            | Index                     | X(Rn)                | Value X (stored in a word following the instruction) is added to (Rn) to produce address of operand. Neither X nor (Rn) is modified.                                                               |

| American state of 100 to 100 to programs accommon |                |                           | Deferred Modes       |                                                                                                                                                                                                    |

| 1                                                 | 001            | Register<br>Deferred      | @Rn or (Rn)          | Register contains the address of the operand.                                                                                                                                                      |

| 3                                                 | 011            | Autoincrement<br>Deferred | @(Rn)+               | Register is first used as a pointer to a word containing the address of the operand, then incremented (always by two, even for byte instructions).                                                 |

| 5                                                 | 101            | Autodecrement<br>Deferred | @-(Rn)               | Register is decremented (always by two, even for byte instructions) and then used as a pointer to a word containing the address of the operand.                                                    |

| 7                                                 | 111            | Index Deferred            | @X(Rn)               | Value X (stored in the memory word following the instruction) and (Rn) are added and the sum is used as a pointer to a word containing the address of the operand. Neither X nor (Rn) is modified. |

Table 2-1 Addressing Modes (cont)

| Mode | Binary<br>Code | Name              | Assembler<br>Syntax* | Function                                                                                           |

|------|----------------|-------------------|----------------------|----------------------------------------------------------------------------------------------------|

|      |                |                   | PC Addressing        |                                                                                                    |

| 2    | 010            | Immediate         | #n                   | Operand follows instruction.                                                                       |

| 3    | 011            | Absolute          | @#A                  | Absolute address follows instruction.                                                              |

| 6    | 110            | Relative          | A                    | Address of A, relative to the instruction, follows the instruction.                                |

| 7    | 111            | Relative Deferred | @A                   | Address of location containing address of A, relative to the instruction, follows the instruction. |

<sup>\*</sup> Rn = Register

### 2.3 PDP-11/34 INSTRUCTIONS

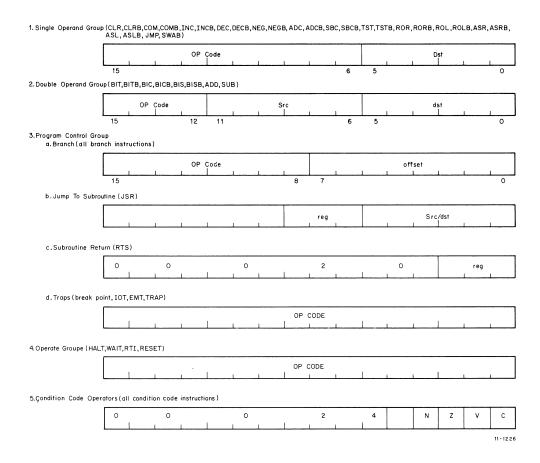

The PDP-11/34 instructions can be divided into five groups:

- 1. Single-Operand Instructions (shifts, multiple precision instructions, rotations)

- 2. Double-Operand Instructions (arithmetic and logical instructions)

- 3. Program Control Instructions (branches, subroutines, traps)

- 4. Operate Group Instructions (processor control operations)

- 5. Condition Code Operators (processor status word bit instructions)

Tables 2-2 through 2-6 list each instruction, including byte instructions for the respective instruction groups. Figure 2-2 shows the six different instruction formats of the instruction set, and the individual instructions in each format.

X, n, A = next program counter (PC) word (constant)

**Table 2-2 Single Operand Instructions**

| Mnemonic                  | OP Code           | Operation                      | Condition Codes                                                                                                                 | Description                                                                                                                                                           |

|---------------------------|-------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR<br>CLRB<br>Clear      | 0050DD*<br>1050DD | $(dst)^{\dagger} \leftarrow 0$ | N: cleared<br>Z: set<br>V: cleared<br>C: cleared                                                                                | Contents of specified destination are replaced with zeroes.                                                                                                           |

| COM<br>COMB<br>Complement | 0051DD<br>1051DD  | (dst) ← n (dst)                | <ul><li>N: set if most significant bit of result is 0</li><li>Z: set if result is 0</li><li>V: cleared</li><li>C: set</li></ul> | Replaces the contents of the destination address by their logical complement (each bit equal to 0 set and each bit equal to 1 cleared).                               |

| INC<br>INCB<br>Increment  | 0052DD<br>1052DD  | $(dst) \leftarrow (dst) + 1$   | N: set if result is less than 0 Z: set if result is 0 V: set if (dst) was 077777 C: not affected                                | Add 1 to the contents of the destination.                                                                                                                             |

| DEC<br>DECB<br>Decrement  | 0053DD<br>1053DD  | $(dst) \leftarrow (dst) - 1$   | N: set if result is less than 0 Z: set if result is 0 V: set if (dst) was 100000 C: not affected                                | Subtract 1 from the contents of the destination.                                                                                                                      |

| NEG<br>NEGB<br>Negate     | 0054DD<br>1054DD  | $(dst) \leftarrow -(dst)$      | N: set if result is less than 0 Z: set if result is 0 V: set if result is 100000 C: cleared if result is 0                      | Replaces the contents of the destination address by its 2's complement. Note that 100000 is replaced by itself.                                                       |

| ADC<br>ADCB<br>Add Carry  | 0055DD<br>1055DD  | (dst) ← (dst) + C              | N: set if result is less than 0 Z: set if result is 0 V: set if (dst) is 077777 and C is 1 C: set if (dst) is 177777 and C is 1 | Adds the contents of the C-bit into the destination. This permits the carry from the addition of the low-order words/bytes to be carried into the high-order results. |

Table 2-2 Single Operand Instructions (Cont)

| Mnemonic                      | OP Code          | Operation                                   | Condition Codes                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                                                    |

|-------------------------------|------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBC<br>SBCB<br>Subtract Carry | 0056DD<br>1056DD | (dst) ← (dst) -C                            | N: set if result is less than 0 Z: set if result is 0 V: set if (dst) was 100000 C: cleared if (dst) is 0 and C is 1                                                                                                                                                                                                | Subtracts the contents of the C-bit from the destination. This permits the carry from the subtraction of the low order words/bytes to be subtracted from the high-order part of the result.                    |

| TST<br>TSTB<br>Test           | 0057DD<br>1057DD | $(dst) \leftarrow (dst)$                    | N: set if result is less than 0 Z: set if result is 0 V: cleared C: cleared                                                                                                                                                                                                                                         | Sets the condition codes N and Z according to the contents of the destination address.                                                                                                                         |

| ROR<br>RORB<br>Rotate Right   | 0060DD           | (dst) ← (dst)<br>rotate right<br>one place. | N: set if high-order bit of the result is set Z: set if all bits of result are 0 V: loaded with the exclusive- OR of the N-bit and the C-bit as set by ROR                                                                                                                                                          | Rotates all bits of the destination right one place. The low-<br>order bit is loaded into the C-bit and the previous contents of<br>the C-bit are loaded into the high-order bit of the destination.           |

| ROL<br>ROLB<br>Rotate Left    | 0061DD<br>1061DD | (dst) ← (dst) rotate left one place.        | N: set if the high order bit of the result word is set (result < 0); cleared otherwise Z: set if all bits of the result word = 0; cleared otherwise V: loaded with the exclusive- OR of the N-bit and C-bit (as set by the completion of the rotate operation) C: loaded with the high order bit of the destination | Rotate all bits of the destination left one place. The high-order bit is loaded into the C-bit of the status word and the previous contents of the C-bit are loaded into the low-order bit of the destination. |

Table 2-2 Single Operand Instructions (Cont)

| Mnemonic                                 | OP Code          | Operation                                     | Condition Codes                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASR<br>ASRB<br>Arithmetic<br>Shift Right | 0062DD<br>1062DD | (dst) ← (dst) shifted one place to the right. | N: set if the high order bit of the result is set (result < 0); cleared otherwise  Z: set if the result = 0; cleared otherwise  V: loaded from the exclusive- OR of the N-bit and C-bit (as set by the completion of the shift operation).  C: loaded from low order bit of the destination                                           | Shifts all bits of the destination right one place. The high-order bit is replicated. The C-bit is loaded from the low-order bit of the destination. ASR performs signed division of the destination by two.                                                       |

| ASLB Arithmetic Shift Left               | 0063DD<br>1063DD | (dst) ← (dst) shifted one place to the left.  | <ul> <li>N: set if high-order bit of the (result &lt; 0); cleared otherwise</li> <li>Z: set if the result = 0; cleared otherwise</li> <li>V: loaded with the exclusive-OR of the N-bit and C-bit and C-bit (as set by the completion of the shift operation)</li> <li>C: loaded with the high-order bit of the destination</li> </ul> | Shifts all bits of the destination left one place. The low-order bit is loaded with a 0. The C-bit of the status word is loaded from the high-order bit of the destination. ASL performs a signed multiplication of the destination by 2 with overflow indication. |

Table 2-2

Single Operand Instructions (Cont)

| Mnemonic                             | OP Code | Operation                                                                                   | Condition Codes                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|---------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASH<br>Arithmetic<br>Shift           | 072RSS  | R ← R Shifted Arithmetically NN places to right or left Where NN = (src)                    | N: set if result <0; cleared otherwise. Z: set if result = 0; cleared otherwise. V: set if sign of register changed during shift; cleared otherwise. C: loaded from last bit shift out of register.                                                           | The contents of the register are shifted right or left the number of times specified by the source operand. The shift count is taken as the low-order 6 bits of the source operand. This number ranges from -32 to +31. Negative is a right shift and positive is a left shift. See Paragraph 2.5 for example.                                                                                                                                                                                                                                                                                                                                        |

| ASHC<br>Arithmetic<br>Shift Combined | 073RSS  | R, Rvl ← R, Rvl The double word is shifted NN places to the right or left, where NN = (src) | N: set if result <0; cleared otherwise. Z: set if result = 0; cleared otherwise. V: set if sign bit changes during the shift; cleared otherwise. C: loaded with high-order bit when right shift (loaded with the last bit shifted out of the 32-bit operand). | The contents of the register and the register ORed with one are treated as one 32-bit word. Rvl (bits 0-15) and R (bits 16-31) are shifted right or left the number of times specified by the shift count. The shift count is taken as the low-order 6 bits of the source operand. This number ranges from -32 to +31. Negative is a right shift and positive is a left shift.  When the register chosen is an odd number, the register and the register ORed with one are the same. In this case, the right shift becomes a rotate. The 16-bit word is rotated right the number of bits specified by the shift count. See Paragraph 2.5 for example. |

| SXT<br>Sign Extend                   | 0067DD  | $(dst) \leftarrow 0$ if N bit<br>is clear<br>$(dst) \leftarrow -1$ N bit<br>is set          | N: unaffected Z: set if N bit clear V: cleared C: unaffected                                                                                                                                                                                                  | If the condition code bit N is set then a -1 is placed in the destination operand: if N bit is clear, then a 0 is placed in the destination operand. This instruction is particularly useful in multiple precision arithmetic because it permits the sign to be extended through multiple words.                                                                                                                                                                                                                                                                                                                                                      |

Table 2-2 Single Operand Instructions (Cont)

| Mnemonic          | OP Code | Operation                      | Condition Codes                                                                                                                                                            | Description                                                                                                |

|-------------------|---------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| SWAB<br>Swap Byte | 0003DD  | Byte 1/Byte 0<br>Byte 0/Byte 1 | N: set if high-order bit of low-order byte (bit 7) of result is set; cleared otherwise.  Z: set if low-order byte of result = 0; cleared otherwise.  V: cleared C: cleared | Exchanges high-order byte and low-order byte of the destination word (destination must be a word address). |

Table 2-3 Double Operand Instructions

| Mnemonic               | OP Code           | Operation                                      | Condition Codes                                                                                                                                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV<br>MOVB<br>Move    | 01SSDD*<br>11SSDD | (dst) ← (src) <sup>†</sup>                     | N: set if (src) < 0; cleared otherwise Z: set if (src) = 0; cleared otherwise V: cleared C: not affected                                                                                                                                                                                                                                                 | Word: Moves the source operand to the destination location. The previous contents of the destination are lost. The source operand is not affected.  Byte: Same as MOV. The MOVB to a resistor (unique among byte instructions) extends the most significant bit of the low order byte (sign extension). Otherwise, MOVB operates on bytes exactly as MOV operates on words.                                   |

| CMP<br>DMPB<br>Compare | 02SSDD<br>12SSDD  | (src) - (dst) [in detail, (src) + ~ (dst) + 1] | N: set if result < 0, cleared otherwise  Z: set if result = 0; cleared otherwise  V: set if there was arithmetic overflow (i.e., operands were of opposite signs and the sign of the destination was the same as the sign of the result); cleared otherwise.  C: cleared if there was a carry from the most significant bit of the result; set otherwise | Compares the source and destination operands and sets the condition codes which may then be used for arithmetic and logical conditional branches. Both operands are unaffected. The only action is to set the condition codes. The compare is customarily followed by a conditional branch instruction. Note that unlike the subtract instruction the order of operation is (src) - (dst), not (dst) - (src). |

Table 2-3

Double Operand Instructions (Cont)

| Mnemonic                 | OP Code          | Operation                                  | Condition Codes                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                       |

|--------------------------|------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT<br>BITB<br>Bit Test  | 03SSDD<br>13SSDD | (src)∧(dst)                                | N: set if high order bit of result set; cleared other- wise Z: set if result = 0; cleared otherwise V: cleared C: not affected                                              | Performs logical AND comparison of the source and destination operands and modifies condition codes accordingly. Neither the source nor destination operands are affected. The BIT instruction may be used to test whether any of the corresponding bits that are set in the destination are clear in the source. |

| BIC<br>BICB<br>Bit Clear | 04SSDD<br>14SSDD | (dst) ← ~ (src)<br>∧ (dst)                 | <ul> <li>N: set if high order bit of result set; cleared otherwise</li> <li>Z: set if result = 0; cleared otherwise</li> <li>V: cleared</li> <li>C: not affected</li> </ul> | Clears each bit in the destination that corresponds to a set bit in the source. The original contents of the destination are lost. The contents of the source are unaffected.                                                                                                                                     |

| BIS<br>BISB<br>Bit Set   | 05SSDD<br>15SSDD | $(dst) \leftarrow (src)$ $\bigwedge (dst)$ | N: set if high order bit of result set; cleared other- wise Z: set if result = 0; cleared otherwise V: cleared C: not affected                                              | Performs inclusive-OR operation between the source and destination operands and leaves the result at the destination address; i.e., corresponding bits set in the destination. The contents of the destination are lost.                                                                                          |

| ADD<br>Add               | 06SSDD           | (dst) ← (src)<br>+ (dst)                   | N: set if result 0; cleared otherwise Z: set if result = 0; cleared otherwise                                                                                               | Adds the source operand to the destination operand and stores the result at the destination address. The original contents of the destination are lost. The contents of the source are not affected. Two's complement addition is performed.                                                                      |

Table 2-3 Double Operand Instruction (Cont)

| Mnemonic        | OP Code | Operation                                                           | Condition Codes                                                                                                                                                                                                                                                                                                                                                                    | Description                                                                                                                                                                                                                                                                          |

|-----------------|---------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADD (Cont)      |         |                                                                     | V: set if there was arithmetic overflow as a result of the operation (that is, both operands were of the same sign and the result was of the opposite sign); cleared otherwise.  C: set if there was a carry from the most significant bit of the result; cleared otherwise.                                                                                                       |                                                                                                                                                                                                                                                                                      |

| SUB<br>Subtract | 16SSDD  | (dst) ← (dst) −<br>(src) in detail,<br>(dst) + ~ (src)<br>+ 1 (dst) | N: set if result < 0; cleared otherwise  Z: set if result = 0; cleared otherwise  V: set if there was arithmetic overflow as a result of the operation (i.e., if operands were of opposite signs and the sign of the source was the same as the sign of the result); cleared otherwise  C: cleared if there was a carry from the most significant bit of the result; set otherwise | Subtracts the source operand from the destination operand and leaves the result at the destination address. The original contents of the destination are lost. The contents of the source are not affected. In double precision arithmetic, the C-bit, when set, indicates a borrow. |

<sup>\*</sup> SS = source (address mode and register) † (src) = source contents

Table 2-3 Double Operand Instructions (Cont)

| Mnemonic        | OP Code | Operation                | Condition Codes                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MUL<br>Multiply | 070RSS  | R, Rvl ← Rx(src)         | N: set if product is <0; cleared otherwise.  Z: set if product is 0; cleared otherwise.  V: cleared  C: set if the result is less than -2 <sup>15</sup> or greater than or equal to 2 <sup>15</sup> -1.                                                                                                                                   | The contents of the destination register and source taken as two's complement integers are multiplied and stored in the destination register and the succeeding register (if R is even). If R is odd, only the low-order product is stored. Assembler syntax is: MUL S,R.  (Note that the actual destination is R, Rvl which reduces to just R when R is odd.)  (See Paragraph 2.5.1 for example). |

| DIV<br>Divide   | 071RSS  | R, Rvl ← R, Rvl<br>(src) | N: set if quotient <0; cleared otherwise. Z: set if quotient = 0; cleared otherwise. V: set if source = 0 or if the absolute value of the register is larger than the absolute value of the source. (In this case the instruction is aborted because the quotient would exceed 15 bits.) C: set if divide 0 attempted; cleared otherwise. | The 32-bit two's complement integer in R and Rvl is divided by the source operand. The quotient is left in R; the remainder is of the same sign as the dividend. R must be even.  (See Paragraph 2.5.2 for example.)                                                                                                                                                                               |

| XOR             | 074RDD  | (dst) ← Rv (dst)         | N: set if the result <0; cleared otherwise. Z: set if result = 0; cleared otherwise. V: cleared C: unaffected                                                                                                                                                                                                                             | The exclusive OR of the register and destination operand is stored in the destination address. Contents of register are unaffected. Assembler format is XOR R,D.                                                                                                                                                                                                                                   |

**Table 2-4 Program Control Instructions**

| Mnemonic                                  | OP Code        | Operation                                                             | Condition Codes | Description                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|----------------|-----------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR<br>Branch                              | 000400<br>xxx† | $PC \leftarrow PC + (2 \times \text{offset})$                         | Unaffected      | Provides a way of transferring program control within a range of -128 to +127 words with a one word instruction. It is an unconditional branch.                                                                                                                                                                                          |

| BNE<br>Branch if not<br>equal             | 001000<br>xxx  | $PC \leftarrow PC + $ $(2 \times \text{offset})$ if $Z = 0$           | Unaffected      | Tests the state of the Z-bit and causes a branch if the Z-bit is is clear. BNE is the complementary operation to BEQ. It is used to test inequality following a CMP, to test that some bits set in the destination were also in the source, following a BIT, and generally, to test that the result of the previous operation was not 0. |

| BEQ<br>Branch if equal                    | 001400<br>xxx  | $PC \leftarrow PC + $ $(2 \times offset) \text{ if } $ $Z = 1$        | Unaffected      | Tests the state of the Z-bit and causes a branch if Z is set. As an example, it is used to test equality following a CMP operation, to test that no bits set in the destination were also set in the source following a BIT operation, and generally, to test that the result of the previous operation was 0.                           |

| BGE<br>Branch if greater<br>than or equal | 002000<br>xxx  | $PC \leftarrow PC + $ $(2 \times offset) \text{ if } $ $N \vee V = 0$ | Unaffected      | Causes a branch if N and V are either both clear or both set. BGE is the complementary operation to BLT. Thus, BGE always causes a branch when it follows an operation that caused addition to two positive numbers. BGE also causes a branch on a 0 result.                                                                             |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic                                  | OP Code       | Operation                                                                                   | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------|---------------|---------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLT<br>Branch if less<br>than             | 002400<br>xxx | $PC \leftarrow PC +$ $(2 \times \text{ offset}) \text{ if}$ $N V = 1$                       | Unaffected      | Causes a branch if the exclusive-OR of the N- and V-bits are 1. Thus, BLT always branches following an operation that added two negative numbers, even if overflow occurred. In particular, BLT always causes a branch if it follows a CMP instruction operating on a negative source and a positive destination (even if overflow occurred). Further, BLT never causes a branch when it follows a CMP instruction operating on a positive source and negative destination. BLT does not cause a branch if the result of the previous operation was 0 (without overflow). |

| BGT<br>Branch if greater<br>than          | 003000<br>xxx | $PC \leftarrow PC + $ $(2 \times \text{ offset})$ if Z v (N \(\forall \text{V}\) = 0        | Unaffected      | Operation of BGT is similar to BGE, except BGT does not cause a branch on a 0 result.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BLE<br>Branch if less than<br>or equal to | 003400<br>xxx | $PC \leftarrow PC + $ $(2 \times \text{ offset}) \text{ if} $ $Z \vee (N \forall V) $ $= 1$ | Unaffected      | Operation is similar to BLT, but in addition will cause a branch if the result of the previous operation was 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BPL<br>Branch if plus                     | 100000<br>xxx | $PC \leftarrow PC + $ (2 × offset) if $N = 0$                                               | Unaffected      | Tests the state of the N-bit and causes a branch if N is clear. BPL is the complementary operation of BMI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BMI<br>Branch if minus                    | 100400<br>xxx | $PC \leftarrow PC + (2 \times \text{ offset}) \text{ if } N = 1$                            | Unaffected      | Tests the state of the N-bit and causes a branch if N is set. It is used to test the sign (most significant bit) of the result of the previous operation.                                                                                                                                                                                                                                                                                                                                                                                                                 |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic                                                      | OP Code       | Operation                                                              | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------|---------------|------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BHI<br>Branch if higher                                       | 101000<br>xxx | $PC \leftarrow PC +$ $(2 \times offset)$ if $C = 0$                    | Unaffected      | Causes a branch if the previous operation causes neither a carry nor a 0 result. This will happen in comparison (CMP) operations as long as the source has a higher unsigned value than the destination.                                                                                                                                                                                         |

| BLOS<br>Branch if lower<br>or same                            | 101400<br>xxx | $PC \leftarrow PC +$ $(2 \times offset)$ if $C \vee Z = 1$             | Unaffected      | Causes a branch if the previous operation caused either a carry or a 0 result. BLOS is the complementary operation to BHI. The branch occurs in comparison operations as long as the source is equal to or has a lower unsigned value than the destination. Comparison of unsigned values with the CMP instruction to be tested for "higher or same" and "higher" by a simple test of the C-bit. |

| BVC<br>Branch if V-bit<br>clear                               | 102000<br>xxx | $PC \leftarrow PC + $ $(2 \times \text{ offset}) \text{ if } $ $V = 0$ | Unaffected      | Tests the state of the V-bit and causes a branch if the V-bit is clear. BVC is complementary operation to BVS.                                                                                                                                                                                                                                                                                   |

| BVS<br>Branch if V-bit set                                    | 102400<br>xxx | PC ← PC +<br>(2 × offset) if<br>V = 1                                  | Unaffected      | Tests the state of V-bit (overflow) and causes a branch if the V-bit is set. BVS is used to detect arithmetic overflow in the previous operation.                                                                                                                                                                                                                                                |

| BCC BHIS Branch if carry clear Branch if higher than the same | 103000<br>xxx | PC ← PC +<br>(2 × offset) if<br>C = 0                                  | Unaffected      | Tests the state of the C-bit and causes a branch if C is clear. BCC is the complementary operation to BCS.                                                                                                                                                                                                                                                                                       |

| BCS BLO Branch if carry set Branch if lower                   | 103400<br>xxx | $PC \leftarrow PC + $ $(2 \times \text{ offset}) \text{ if } $ $C = 1$ | Unaffected      | Tests the state of the C-bit and causes a branch if C is set. It is used to test for a carry in the result of a previous operation.                                                                                                                                                                                                                                                              |

Table 2-4 Program Control Instructions (Cont)

| Mnemonic    | OP Code | Operation  | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|---------|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JMP<br>Jump | 0001DD  | PC ← (dst) | Unaffected      | JMP provides more flexible program branching than provided with the branch instruction. Control may be transferred to any location in memory (no range limitation) and can be accomplished with the full flexibility of the addressing modes, with the exception of register mode 0. Execution of a jump with mode 0 will cause an illegal instruction condition. (Program control cannot be transferred to a register.) Register deferred mode is legal and will cause program control to be transferred to the address held in the specified register. Note that instructions are word data and must therefore be fetched from an even numbered address. A boundary error trap condition will result when the processor attempts to fetch an instruction from an odd address. |

2-18

Table 2-4

Program Control Instructions (Cont)

| Mnemonic               | OP Code | Operation                                                                                                                                                                                       | Condition Codes | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JRS Jump to subroutine | 004RDD  | (tmp) ← (dst) (tmp is an internal processor register) ↓ (SP) ← reg (push reg contents onto processor stack) reg ← PC PC holds location following JSR; this address PC ← (tmp), now put in (reg) | Unaffected      | In execution of the JSR, the old contents of the specified register (the linkage pointer) are automatically pushed onto the processor stack and new linkage information placed in the register. Thus, subroutines nested within subroutines to any depth may all be called with the same linkage register. There is no need either to plan the maximum depth at which any particular subroutine will be called or to include instructions in each routine to save and restore the linkage pointer. Further since all linkages are saved in a re-entrant manner on the processor stack, execution of a subroutine may be interrupted, and the same subroutine re-entered and executed by an interrupt service routine. Execution of the initial subroutine can then be resumed when other requests are satisfied. This process (called nesting) can proceed to any level. |

|                        |         |                                                                                                                                                                                                 |                 | JSR PC, dst is a special case of the PDP-11 subroutine call suitable for subroutine calls that transmit parameters.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RTS<br>Return from     | 00020R  | $PC \leftarrow (reg) \\ (reg) \leftarrow SP \uparrow$                                                                                                                                           | Unaffected      | Loads contents of register into PC and pops the top element of the processor stack into the specified register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |