Tillhör KD11-A processor LPA (5) maintenance manual

1st Edition, September 1973 2nd Printing, October 1973 3rd Printing, February 1974 4th Printing, August 1974 5th Printing, December 1974 6th Printing, March 1975

Copyright © 1973, 1974, 1975 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

**DIGITAL**

COMPUTER LAB

UNIBUS

# CONTENTS

|           |                                        | Pag                                   |

|-----------|----------------------------------------|---------------------------------------|

| CHAPTER 1 | INTRODUCTION                           |                                       |

|           |                                        |                                       |

| 1.1       | SCOPE                                  | · · · · · · · · · · · · · · · · · · · |

| 1.2       | ORGANIZATION                           | 1-                                    |

|           |                                        |                                       |

| CHAPTER 2 | MICROPROGRAMMING                       |                                       |

| 2.1       | SCOPE                                  |                                       |

| 2.2       | BASIC PROCESSOR                        |                                       |

| 2.3       | CONVENTIONAL IMPLEMENTATION            |                                       |

| 2.4       | MICROPROGRAMMED IMPLEMENTATION         |                                       |

| 2.5       | BASIC READ-ONLY MEMORY (ROM)           |                                       |

|           | DLOCV DIACDAM DESCRIPTION              |                                       |

| CHAPTER 3 | BLUCK DIAGRAM DESCRIPTION              |                                       |

| 3.1       | SCOPE                                  | 3-                                    |

| 3.2       | INTERFACE                              |                                       |

| 3.2.1     | KY11-D Programmer's Console            | 3-                                    |

| 3.2.2     | Unibus Timing and Control              | 3-                                    |

| 3.3       | DATA PATHS                             |                                       |

| 3.3.1     | Data Paths, Multiplexers and Registers |                                       |

| 3.3.2     | Decoding                               |                                       |

| 3.3.3     | Arithmetic Logic Unit                  |                                       |

| 3.3.4     | PS Register                            |                                       |

| 3.3.5     | Register (REG)                         |                                       |

| 3.4       | MICROCONTROL                           |                                       |

| 3.4.1     | Condition Codes Input                  |                                       |

| 3.4.2     | ALU Control                            |                                       |

| 3.4.3     | Flag Control                           |                                       |

| 3.4.4     | U Branch Control                       |                                       |

| 3.4.5     | BUT MUX                                |                                       |

| 3.4.6     | U WORD Control ROM and U WORD Reg      |                                       |

| 3.4.7     | Microaddress Alteration                |                                       |

| 3.4.8     | JAMUPP Logic                           |                                       |

| 3.4.9     |                                        |                                       |

| 3.4.10    | BUPP & SR MATCH                        |                                       |

| 3.4.11    |                                        |                                       |

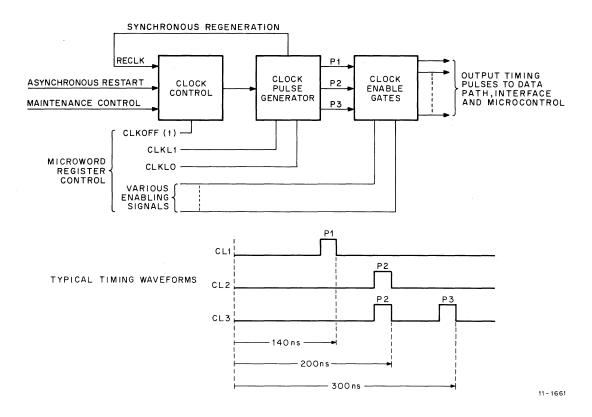

| 3.4.11.1  | Clock Pulse Generator                  |                                       |

| 3.4.11.2  | Clock Control                          |                                       |

| 3.4.11.3  | Clock Enable Gates                     |                                       |

|           |                                        |                                       |

| CHAPTER 4 | MICROPROGRAM FLOW DIAGRAMS             |                                       |

| 4.1       | SCOPE                                  | 4-1                                   |

| 4.2       | HOW TO READ FLOW DIAGRAMS              |                                       |

| 4.2.1     | Entry Point                            |                                       |

| 4.2.2     | Microprogram Word                      |                                       |

| 4.2.3     | Exit Points                            |                                       |

| 4.2.4     | Branch Microprogram Test (BUT)         |                                       |

| 4.2.5     | Operation Symbols                      |                                       |

| 4.3       | FLOW DIAGRAM EXAMPLES                  |                                       |

|           |                                        |                                       |

# CONTENTS (Cont)

|                | Page                             |

|----------------|----------------------------------|

| CHAPTER 5      | LOGIC DIAGRAM DESCRIPTION        |

| 5.1            | INTRODUCTION                     |

| 5.2            | PRINT FORMAT 5-1                 |

| 5.2.1          | Circuit Schematic Format         |

| 5.2.1.1        | Logic Flow                       |

| 5.2.1.2        | Module Pins                      |

| 5.2.1.3        | Print Prefixes                   |

| 5.2.1.4        | Signal Level Indicators          |

| 5.2.1.5        | Flip-Flop Outputs                |

| 5.2.1.6        | Inhibit Situations               |

| 5.2.1.7        | Parentheses and Colons           |

| 5.2.1.8        | Parentheses and Commas           |

| 5.2.1.9        |                                  |

|                | 1 0                              |

| 5.2.1.10       |                                  |

| 5.2.1.11       | System Information               |

| 5.2.1.12       | Jumper Information               |

| 5.2.1.13       | Cable Connection                 |

| 5.2.2          | Wire List Format                 |

| 5.2.2.1        | Alphabetical Searches            |

| 5.2.2.2        | Print References                 |

| 5.2.2.3        | Etch Backpanel                   |

| 5.2.2.4        | Forward Searching                |

| 5.3            | M7231, DATA PATHS, K1 MODULE 5-3 |

| 5.4            | M7232, U WORD, K2 MODULE         |

| 5.5            | M7233, IR DECODE, K3 MODULE      |

| 5.6            | M7234, TIMING, K4 MODULE         |

| 5.7            | M7235, STATUS, K5 MODULE         |

| CHAPTER 6      | KY11-D PROGRAMMER'S CONSOLE      |

| 6.1            | KY11-D CONSOLE                   |

| 6.2            | KY11-D CONSOLE BOARD             |

| 6.2.1          | Print KYD-2, Display             |

| 6.2.2          | Print KYD-3, Switches            |

| 6.3            | CABLES                           |

| CHAPTER 7      | PROCESSOR OPTIONS                |

| 7.1            | SCOPE                            |

| 7.2            | KJ11-A STACK LIMIT REGISTER      |

| 7.2.1          | Functional Description           |

| 7.2.2          | Detailed Description             |

| 7.3            | KM11-A MAINTENANCE CONSOLE       |

| 7.3.1          | Functional Description           |

| 7.3.1<br>7.3.2 | T                                |

|                |                                  |

| 7.3.3          | Configurations                   |

| 7.3.4          | Power                            |

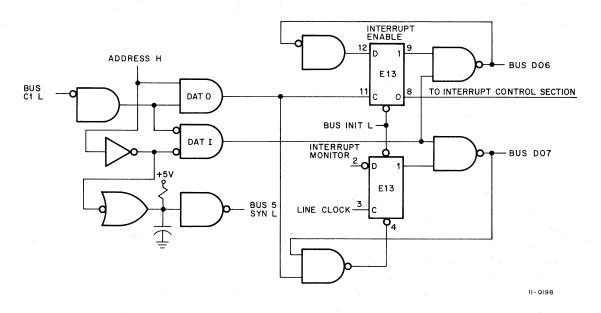

| 7.4            | KW11-L LINE FREQUENCY CLOCK      |

| 7.4.1          | General Description              |

| 7.4.2          | Address Selector                 |

| 7.4.3          | Interrupt Control                |

| 7.4.4          | Status Register                  |

# **ILLUSTRATIONS**

| Figure No. | Title                                                     | Page |

|------------|-----------------------------------------------------------|------|

| 2-1        | Conventional Control Section, Simplified Block Diagram    | 2-3  |

| 2-2        | Microprogrammed Control Section, Simplified Block Diagram |      |

| 2-3        | Basic ROM Structure                                       |      |

| 2-4        | Microword Format                                          | 2-7  |

| 3-1        | KD11-A Priority Transfer Timing and Control for NPRs      |      |

| 3-2        | KD11-A Priority Transfer Timing and Control for BRs       |      |

| 3-3        | NPR Priority Transfer Timing Sequence                     |      |

| 3-4        | BR Priority Transfer Timing Sequence                      |      |

| 3-5        | KD11-A Bus Data XFER Timing and Control                   |      |

| 3-6        | KD11-A DATI(P) Bus Transaction Timing Diagram             |      |

| 3-7        | KD11-A DATO(B) Bus Transaction Timing Diagram             |      |

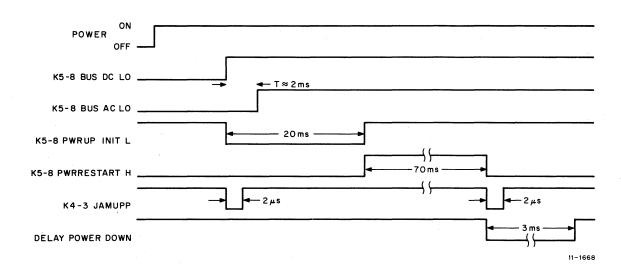

| 3-8        | KD11-A Power Up Timing Sequence                           |      |

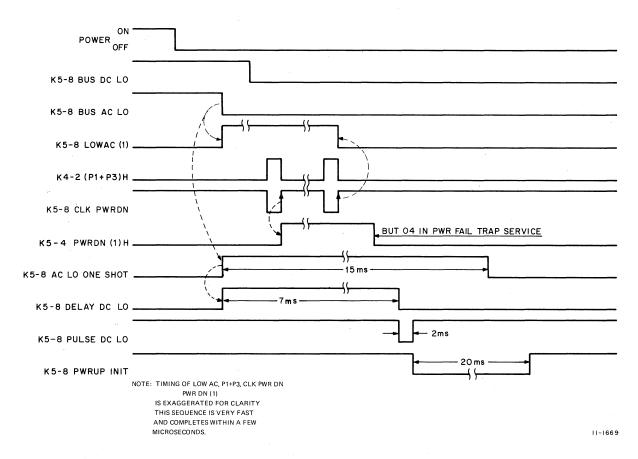

| 3-9        | KD11-A Power Down Timing Sequence                         |      |

| 3-10       | U Branch Control Sequence, Simplified Branching Operation |      |

| 3-11       | KD11-A Processor Clock, Block Diagram                     |      |

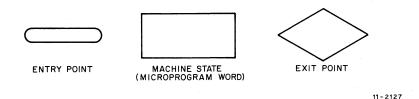

| 4-1        | Basic Flow Diagram Symbols                                |      |

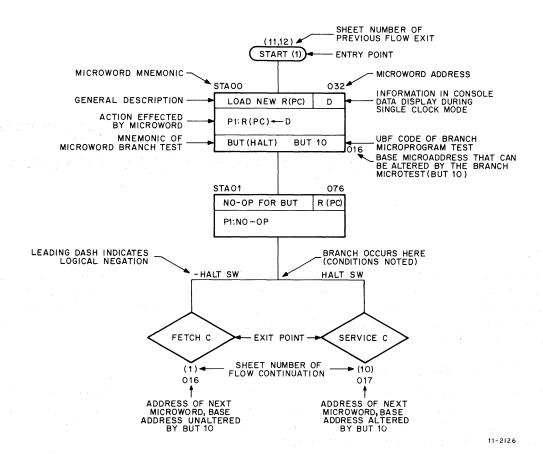

| 4-2        | Flow Diagram Example                                      |      |

| 7-1        | KD11-A Maintenance Console Overlay                        |      |

| 7-2        | KT11-D, KE11-E,F Maintenance Console Overlay              |      |

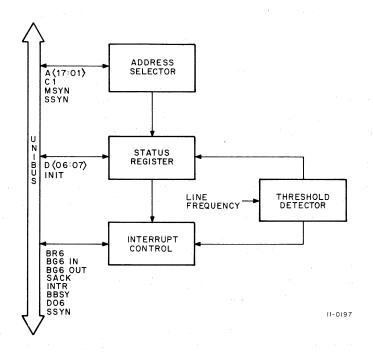

| 7-3        | KW11-L Block Diagram                                      |      |

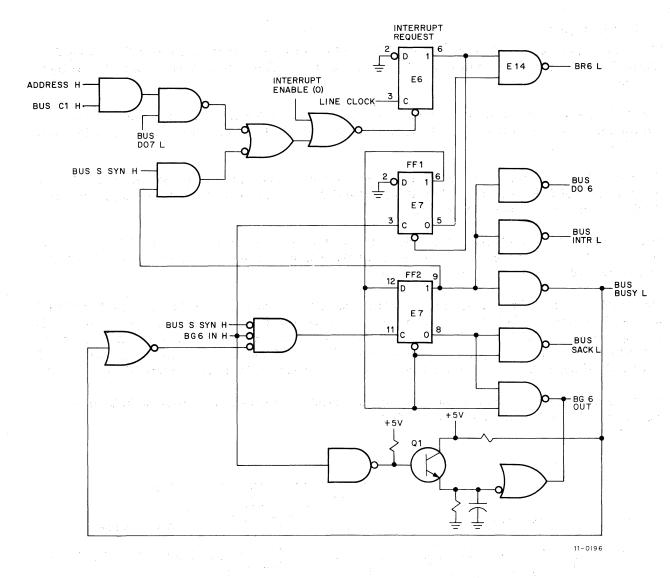

| 7-4        | Interrupt Request Section, Simplified Diagram             | 7-13 |

| 7-5        | Status Register, Simplified Logic Diagram                 | 7-14 |

|            | TABLES                                                    |      |

| Table No.  | Title                                                     | Page |

| 1 1        | P.L. I.D.                                                 |      |

| 1-1<br>2-1 | Related Documents                                         |      |

| 3-1        | Function of Microword Bits (U WORD)                       |      |

| 3-2        | PDP-11/40 Data Path Multiplexer Control                   |      |

| 3-3        | KD11-A Functional Components                              |      |

| 4-1        | BUT CHART                                                 |      |

| 4-2        | Flow Diagram Example 1                                    |      |

| 4-3        | Flow Diagram Example 2                                    |      |

| 4-4        | Microwords (Numerical Order)                              |      |

| 4-5        | Microwords (Alphabetical Order)                           |      |

| 7-1        | Comparison of Address and SLR                             |      |

| 7-2        | Detecting Type of Violation                               |      |

| 7-3        | KM11-A Controls and Indicators for KD11-A Overlay         | 7-4  |

| 7-4        | KM11-A Indicators for KT11-D and KE11-E,F Overlay         |      |

| 7-5        | KM11-A Configurations                                     |      |

| 7-6        | Interrupt Control Flip-Flops                              |      |

|            | A A A                                                     |      |

# CHAPTER 1 INTRODUCTION

# 1.1 SCOPE

This manual describes the KD11-A Processor which is the basic component of the PDP-11/35 and PDP-11/40 computer systems. The processor is connected to the Unibus as a subsystem and controls time allocation of the Unibus for peripherals, and performs arithmetic and logic operations through instruction decoding and execution. The information contained in this manual pertains primarily to the processor itself, however, certain processor options are also described (KY11-D, KJ11-A, KM11-A, and KW11-L).

Table 1-1 lists the other manuals that are necessary for a complete understanding of the basic PDP-11/35 or PDP-11/40 system.

Table 1-1

Related Documents

| Title                                                            | Document<br>Number | Remarks                                                                                               |

|------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------|

| PDP-11/35 (BA11-DA,<br>DB 10-1/2" Mounting<br>Box) System Manual | EK-11035-TM-001    | Describes overall PDP-11/35 system and includes sections on installation, operation, and programming. |

| PDP-11/40, PDP-11/35<br>System Manual (21"<br>Chassis)           | EK-11040-TM-002    | Describes overall PDP-11/40 system and includes sections on installation, operation, and programming. |

| KE11-E & KE11-F<br>Instruction Set<br>Options Manual             | EK-KE11E-TM-002    | Covers the KE11-E Extended Instruction Set and KE11-F Floating Instruction Set processor options.     |

| KT11-D Memory<br>Management Option<br>Manual                     | EK-KT11D-TM-002    | Covers the KT11-D Memory Management Option.                                                           |

#### 1.2 ORGANIZATION

The description of the KD11-A Processor is divided into four major sections: microprogramming (Chapter 2), block diagram (Chapter 3), flow diagrams (Chapter 4), and logic diagrams (Chapter 5).

Chapter 2 first discusses the processor and briefly covers the conventional method of implementing the instruction set. The remainder of the chapter is devoted to a discussion of microprogrammed implementation, the basic microprogram memory, and the structure of the microprogram word.

Chapter 3 describes the processor at a block diagram level and introduces the processor architecture by describing the basic block diagram which illustrates all of the major logic elements and interconnections within the processor. The narrative in this chapter is summarized by a table that lists each functional block on the diagram, describes the block, and lists inputs and outputs to and from that block.

Most of the information required to follow a sequence of machine states on a flow diagram is contained in the flow diagram itself. Chapter 4 is, therefore, divided into two major parts: The first part explains the format of the flow diagram, and the second part provides examples of tracing instruction operations through the flow diagrams.

Chapter 5 is the last section covering the KD11-A Processor. It provides a description of the processor logic and includes an explanation of print set conventions.

Chapter 6 of this manual provides a complete description of the KY11-D Programmer's Console, with the exception of operating procedures which are covered in the PDP-11/40, PDP-11/35 System Manual (21" Chassis), EK-11040-TM-002.

Chapter 7 describes three of the internal processor options that may be used with the KD11-A. These options are: the KW11-L Line Frequency Clock, the KJ11-A Stack Limit Register, and KM11-A Maintenance Console. The other available processor options (KE11-E, KE11-F, and KT11-D) are included in the manuals listed in Table 1-1.

A complete drawing set is supplied with this manual in a companion volume entitled *PDP-11/40 System Engineering Drawings*. The drawing set includes the basic block diagram, microword format, function tables, flow diagrams, and logic diagrams. Familiarity with the ISP notation (Paragraph 4.2 of the *PDP-11/40 System Manual*) as well as the print format (Paragraph 5.2 of this manual) will aid in understanding the prints.

# CHAPTER 2 MICROPROGRAMMING

#### 2.1 SCOPE

This chapter provides a general introduction to the microprogramming techniques used in the KD11-A Processor. Because microprogramming is the key to KD11-A Processor operation, it is essential to understand the basic techniques before attempting to use the block diagram, flow diagrams, and logic diagrams. This chapter first describes the basic processor and briefly covers the conventional method of implementing the instruction set. An introduction into microprogrammed implementation is then covered. The remainder of the chapter is devoted to a discussion of the basic microprogrammed memory and the structure of the microprogrammed word.

# 2.2 BASIC PROCESSOR

A computer system must be capable of manipulating, storing, and routing data. The component of a computer that operates on the data is the processor. Although the processor is designed to effect complicated changes to the data that it receives, it actually consists of elements making only simple changes. The complex data manipulations are achieved by combining a large number of these simple changes in a variety of ways.

The processor consists of logical elements, each element designed to perform a specific function. For example, some elements store data, some read data from another part of the computer, and others perform simple modifying functions such as complementing the data or combining two operands by either addition or by logical ANDing. These simple basic operations can be combined into functional groups known as *instructions*. An instruction can include a number of operations so that data can be combined, changed, moved, or deleted. The instructions can be further combined into *programs* which use a number of instructions to construct even more complex operations.

The basic logical elements of a processor can perform only a small number of operations at one time. Therefore, to combine a number of these operations into an instruction, the instruction must be divided into either a series of sequential steps or into groups of functions that can be performed simultaneously. One method of describing the procedure the processor uses to execute an instruction is to call each operation (or group of operations) a *machine state*. An instruction then becomes a sequence of machine states which the processor always enters in a specific, predetermined order, depending on the individual instruction.

The processor can be divided into three general functional parts: the INTERFACE section, which exchanges data with devices external to the processor; the DATA PATHS section, which performs data handling functions; and the MICROCONTROL section, which includes the logic that determines which operations are to be performed during a particular state and what the next machine state should be. (These sections of the processor and their component elements are shown on the KD11-A Processor Block Diagram, drawing B-BD-KD11-A-BD.) The INTERFACE section consists basically of logic necessary for transferring data between the processor, the Unibus, and the programmer's console. The DATA PATH and MICROCONTROL sections interact to perform the three main processor functions of data storage, modification, and routing.

In order for the processor to combine data operands, it must be capable of storing data internally while simultaneously reading additional data. The processor often stores information about the instruction being executed, about the program from which the instruction was taken, and about the location of the data being handled, in addition to storing a number of data operands. When the processor must select some of this internally stored data, or store new data, the MICROCONTROL section provides the required control signals to initiate appropriate actions within the data storage section.

Data manipulation is performed both on data that remains within the processor and on data being transferred between the processor and the rest of the system. In some instances, the data remaining within the processor is used to control the processor by providing inputs to the sensing logic in the MICROCONTROL section. The various logic elements that actually modify data are controlled by signals from the MICROCONTROL section which selects the particular operation to be performed.

Interconnections between the logic elements that store data and the logic elements that manipulate data are not fixed; they are established as required by the specific machine state. The MICROCONTROL section generates signals that cause data routing logic elements to form appropriate interconnections within the processor and between the INTERFACE and DATA PATHS sections of the logic.

#### 2.3 CONVENTIONAL IMPLEMENTATION

Before attempting to understand the microprogramming implementation of the MICROCONTROL section, which is the key to the KD11-A Processor, it is advantageous to reveiw the conventional method of implementation which uses combinational logic networks to produce the necessary control outputs.

In a conventional processor, each control signal is the output of a combinational network that detects all of the machine states, as well as other conditions, for which the signal should be asserted. The machine state is represented by the contents of a number of storage elements (such as flip-flops) which are loaded from signals that are, in turn, outputs of combinational networks. The inputs to these networks include: the current machine state, sensed conditions within the processor, and sensed external conditions.

The number of logical elements in a conventional processor is often reduced by using logic networks to generate intermediate signals that can be used to produce a variety of control signals and/or machine states. Unfortunately, while this sharing of logic reduces processor size, it increases the complexity and makes it more difficult to understand the processor logic because it is no longer obvious what conditions cause each signal. In addition, the distinction between sequence control and function control is often lost, making it more difficult to determine whether improper operation is caused by a faulty machine state sequence or by erroneous control signals within an otherwise correct machine state.

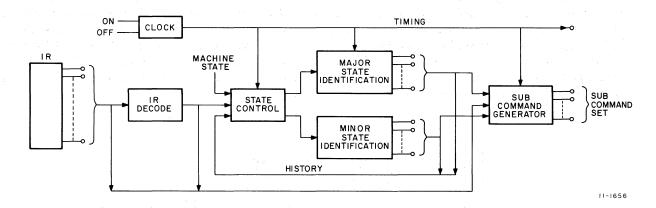

A simplified block diagram of a conventional control section of a processor is shown in Figure 2-1. The Instruction Register (IR) and associated decoding logic determine the logic function (instruction) that is to be performed. The major and minor state identification logic serves as a sequence control to determine the order of functions to be performed. The major state logic selects the major operation to be performed, such as Fetch (obtain an instruction), Source (obtain the source operand), Destination (obtain the destination operand), Execute (perform the action specified by the instruction), or Service (handle required interrupts, traps, etc.).

Within each major state, the processor MICROCONTROL section must perform several minor operations. For example, the Fetch major state obtains an instruction from core memory. Minor states during Fetch include: retrieve the instruction from memory, update the Program Counter, load the Instruction Register, and decode the instruction.

Finally, a set of subcommands must be generated to perform the elemental operations required by a minor state. The subcommand set that is selected is dependent on which major and minor states have been selected by the state control logic.

The sequence control of the processor (major state, minor state, and subcommand set logic) is practical only if a well-defined set of elementary operations is generated. This is the function of the state control logic shown in Figure 2-1. The state control consists of a complex array of combinational logic that monitors the output of the IR decoder which defines the instruction, the current machine states (major and minor), and external sources (state of Processor Status Register, console switches, Unibus signals, etc.) to set the required major and minor machine states at the occurrence of each system clock pulse. It should be noted that the state control logic selects the next elementary operation as a function of the current operation and external conditions.

Although the KD11-A Processor does not employ the type of MICROCONTROL section discussed in this paragraph, the concepts presented serve as a review of conventional control and are a desirable starting point from which to discuss the principles of microprogramming. In both cases, the prime function of the MICROCONTROL section is the same; only the hardware implementation differs.

Figure 2-1 Conventional Control Section, Simplified Block Diagram

#### 2.4 MICROPROGRAMMED IMPLEMENTATION

When the control system is implemented by microprogramming techniques, each control signal is completely defined for every machine state. The section of the processor that selects the control signals can thus be implemented as a storage device (read-only memory). This memory is divided into words; there is a separate word for each machine state. Each word, in turn, contains a bit for every control signal associated with the related machine state. During each machine state, the contents of the corresponding word in the read-only memory is transmitted on the control lines. For most control signals, the output of the memory is the control signal and no additional logic is required.

The heart of the microprogrammed processor is the read-only memory (ROM) which stores a copy of the required control signals for each machine state and a list of the machine states to follow the current state. Each word in the ROM defines an elementary operation and the bit pattern within the word corresponds to subcommands. All that is required to generate a unique set of subcommands is to read out the contents of a location in the ROM. To generate a sequence of elementary operations, the address input to the ROM is changed with each system clock pulse. Some of the bits in the ROM are used to define the next location to be read, often depending on conditions sensed by the processor.

Each microprogram word that defines an elementary operation or machine state is referred to as a *microword* (sometimes referred to as a microinstruction). Sequences of microwords are referred to as *microroutines*. The register that defines which microword is to be read is referred to as the *microprogram pointer*.

An instruction fetched from core memory is loaded into the Instruction Register, decoded, and used in generating a microprogram address that points to the starting location of a group of microroutines stored in the ROM. When the microroutines are executed, the required subcommand sets are produced to activate other elements within the processor, such as DATA PATHS or Unibus control in the INTERFACE section.

The microprogram may be viewed as a group of hardware subroutines carefully designed to implement the PDP-11/40 instruction set and permanently stored in the ROM.

In order to maintain proper sequencing of a microroutine, each microword contains an address field for the *next* microword. However, provisions are made to modify this address when it is required to branch to other microwords or microroutines because of conditions sensed within the processor (e.g., instruction, address mode, interrupt flag, etc.).

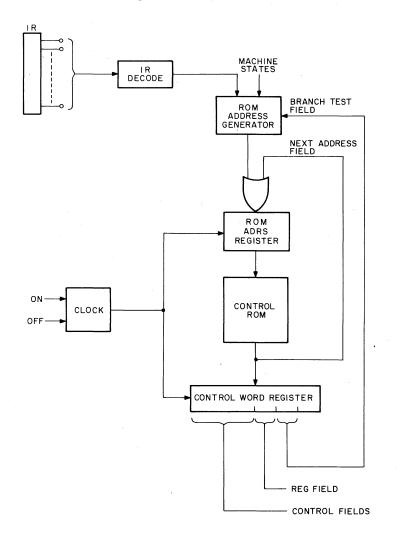

A simplified block diagram of the microprogrammed control logic is shown in Figure 2-2. As can be seen on the diagram, the instruction loaded into the Instruction Register (IR) from core memory is decoded to provide a ROM address. This address causes a specified control word (microword) to be retrieved from the ROM and loaded into a Buffer Register. This microword contains the control fields used by the processor to perform the selected function. The microword also contains a next address field and a branch test field which are fed back to the ROM Address Generator to select the next microword in the sequence. The microword present in the Buffer Register operates on the machine while the next microword in the sequence is being fetched.

Figure 2-2 Microprogrammed Control Section, Simplified Block Diagram

The combination of the next address field and the branch test field controls the sequence of microroutines. The next address field provides a base address which selects the next microword to be used in the normal sequence. However, this base address can be modified prior to being loaded into the microprogram Address Register.

Before discussing the address modification, it is important to understand that modification occurs prior to storage in the ROM ADRS Register and, therefore, is performed on the subsequent next address (the *next*, next address). For example, microword 1 in the sequence contains an address pointing to microword 2, and microword 2 contains an address pointing to microword 3. When microword 1 is being operated on, the next address field (microword 2) is already present in the ROM ADRS Register and, therefore, cannot be modified. However, when word 1 is being used and the address for word 2 is in the ROM ADRS Register, the address for word 3 can be modified between the ROM output and the ROM ADRS Register.

The branch test field of the microword specifies conditions to be tested and controls when the test is to occur; the conditions determine to what location the microprogram is to branch. Logic within the processor permits testing of the Instruction Register, flags, and other internal and external conditions to determine if branching is required. If a branch is necessary, processor logic modifies the address of the next ROM microword. After the modified address has been loaded into the ROM ADRS Register, a branch occurs to the new location and the specified microword is retrieved from the ROM.

# 2.5 BASIC READ-ONLY MEMORY (ROM)

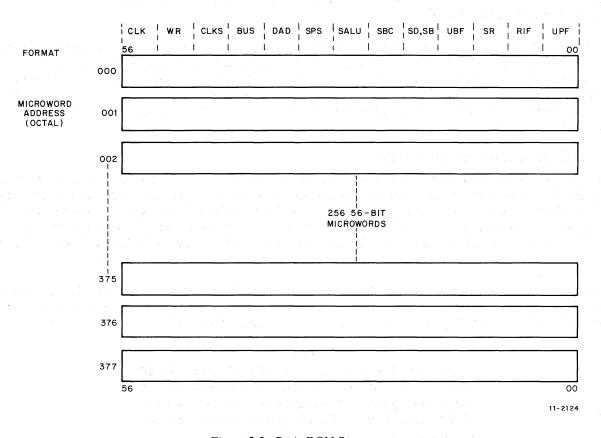

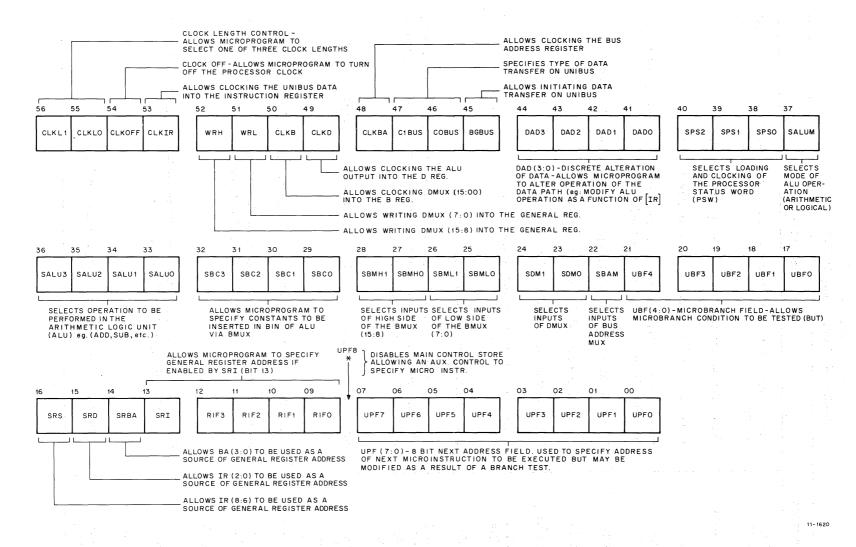

The microprogram read-only memory (ROM) contains 256 56-bit words. During each processor cycle, one word is fetched from this ROM and stored in a Buffer Register. The outputs of the Buffer Register are transmitted to other sections of the processor to act as control signals or to be used as the address of the next microword. The first eight bits of every microword (07:00) are used to hold the address of the next microword to be used. The remaining bits (56:09) are control bits. (Bit 08 is reserved for use with extended ROM addresses for Extended Instruction Set options.)

Figure 2-3 illustrates the basic structure of the microwords in the ROM. The detailed format of the microword is shown in print D-BD-KD11-A-BD and in Figure 2-4. Note that this format is identical for all 256 microwords in the ROM. The function of each bit position in the microword is described in Table 2-1.

# NOTE

In the KD11-A Processor documentation, the prefix *MICRO* (from the Greek Mu) is abbreviated as U (similar to  $\mu$ ). The U abbreviation appears in the names for the microword buffer (U WORD), in the ROM ADRS (Microprogram Pointer, UPP), and in other logic block names and signal names.

#### DETAILED FORMAT OF THE 56-BIT MICROWORD IS SHOWN IN FIGURE 2-4

Figure 2-3 Basic ROM Structure

Figure 2-4 Microword Format

Table 2-1 Function of Microword Bits (U WORD)

| U Bit                | Mnemonic                         | Meaning and Function                                                                                                                                                                                  |

|----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56<br>55             | CLKL1<br>CLKL0                   | Clock length control. Permits the microprogram to select one of three clock lengths.                                                                                                                  |

| 54                   | CLKOFF                           | Permits the microprogram to turn off the processor clock.                                                                                                                                             |

| 53                   | CLKIR                            | Permits clocking Unibus data into the Instruction Register (IR).                                                                                                                                      |

| 52<br>51             | WRH<br>WRL                       | Permit writing the Data Multiplexer data into the general registers. WRH writes the high-order byte; WRL writes the low-order byte.                                                                   |

| 50                   | CLKB                             | Permits clocking the entire Data Multiplexer (full word) into the B Register.                                                                                                                         |

| 49                   | CLKD                             | Permits clocking the ALU output into the D Register.                                                                                                                                                  |

| 48                   | CLKBA                            | Permits clocking the Bus Address Register.                                                                                                                                                            |

| 47<br>46             | C1BUS<br>C0BUS                   | Specify the type of data transfer on the Unibus.                                                                                                                                                      |

| 45                   | BGBUS                            | Initiates data transfer on the Unibus.                                                                                                                                                                |

| 44<br>43<br>42<br>41 | DAD3<br>DAD2<br>DAD1<br>DAD0     | Discrete alteration of data. Permit the microprogram to alter operation of the data path. For example, modifying the Arithmetic Logic Unit (ALU) operation as a function of the Instruction Register. |

| 40<br>39<br>38       | SPS2<br>SPS1<br>SPS0             | Select loading and clocking situations on the Processor Status (PS) word.                                                                                                                             |

| 37                   | SALUM                            | Selects the mode of ALU operation (mode can be either arithmetic or logical).                                                                                                                         |

| 36<br>35<br>34<br>33 | SALU3<br>SALU2<br>SALU1<br>SALU0 | Select the operation to be performed by the ALU, such as add, subtract, etc. This selection can be modified by the DAD code noted above.                                                              |

| 32<br>31<br>30<br>29 | SBC3<br>SBC2<br>SBC1<br>SBC0     | Permit the microprogram to specify the constants to be inserted into the B input of the ALU by way of the B Multiplexer.                                                                              |

| 28<br>27             | SBMH1<br>SBMH0                   | Select the inputs of the high-order byte of the B Multiplexer.                                                                                                                                        |

Table 2-1 (Cont)

Function of Microword Bits (U WORD)

| U Bit                                  | Mnemonic                                | Meaning and Function                                                                                                                                                                                                                      |

|----------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26<br>25                               | SBML1<br>SBML0                          | Select the inputs of the low-order byte of the B Multiplexer.                                                                                                                                                                             |

| 24<br>23                               | SDM1<br>SDM0                            | Select the inputs of the D Multiplexer.                                                                                                                                                                                                   |

| 22                                     | SBAM                                    | Selects the inputs of the Bus Address Multiplexer.                                                                                                                                                                                        |

| 21<br>20<br>19<br>18<br>17             | UBF4<br>UBF3<br>UBF2<br>UBF1<br>UBF0    | Represent microbranch field. Select the microbranch condition to be tested. This test is referred to as the Branch Microprogram Test (BUT).                                                                                               |

| 16                                     | SRS                                     | Permits bits (8:6) of the Instruction Register to be used as the source of the general register address.                                                                                                                                  |

| 15                                     | SRD                                     | Permits bits (2:0) of the Instruction Register to be used as the source of the general register address.                                                                                                                                  |

| 14                                     | SRBA                                    | Permits bits (3:0) of the Bus Address Register to be used as the source of the general register address.                                                                                                                                  |

| 13                                     | SRI                                     | Enables RIF (3:0) of the microword for general register address.                                                                                                                                                                          |

| 12<br>11<br>10<br>09                   | RIF3<br>RIF2<br>RIF1<br>RIF0            | Permit microprogram to specify general register address, provided these bits are enabled by SRI (bit 13).                                                                                                                                 |

| 07<br>06<br>05<br>04<br>03<br>02<br>01 | UPF7 UPF6 UPF5 UPF4 UPF3 UPF2 UPF1 UPF0 | Represent an 8-bit next address field that is used to specify the address of the next microinstruction to be executed. However, it may be modified as the result of a BUT. The U08 bit is for UPF8 and is provided for the KE11-E option. |

# CHAPTER 3 BLOCK DIAGRAM DESCRIPTION

# 3.1 SCOPE

This chapter introduces the KD11-A Processor architecture by describing the basic block diagram which illustrates all of the major logic elements and interconnections within the processor.

The block diagram (drawing D-BD-KD11-A-BD) has been divided into three major functional groupings: INTERFACE, DATA PATHS, and MICROPROGRAM CONTROL. All of the components in each of these segments are covered in detail in succeeding paragraphs. Paragraph 3.5 contains a tabular listing of all components on the block diagram and includes a brief physical description as well as related inputs and outputs. This abbreviated summary can be used as a quick reference once the more detailed description of the block diagram is understood, or it can be used for a quick overview of the KD11-A Processor by those who are already familiar with PDP-11 processors and microprogramming techniques.

The block diagram format provides blocks with major functions titled, and with major data and control interconnections, as well as specific clock and microcontrol signals indicated. In the lower right hand corner of each block is a K- reference which indicates the module schematic or schematics on which the contents of the block can be found. For example, K1-7 indicates sheet 7 of the K1, or M7231 module print; K2 indicates several sheets on the K2, or M7232 module print. The details of logic operation are contained in Chapter 5.

#### 3.2 INTERFACE

The first section of the processor shown on the block diagram is the INTERFACE section which is used to interconnect the KD11-A Processor with other components of the PDP-11/40 system. Each of the functional blocks shown on the INTERFACE portion of the block diagram is covered in the following discussion.

#### 3.2.1 KY11-D Programmer's Console

The KY11-D Programmer's Console is an integral part of the PDP-11/40 system and provides the programmer with a direct system interface. The console allows the user to start, stop, load, modify, or continue a program. Console displays indicate data and address flow for monitoring processor operations. The console control logic is part of the processor INTERFACE section, while the Switch Register, the DATA display, and the ADDRESS display are part of the KY11-D console.

The Switch Register is located on the KY11-D console and consists of the manually-operated switches with resistor pull-ups gated through 8881 drivers to the Unibus. During console operation, the Switch Register is addressed on the Unibus via a microroutine. When the Switch Register address is decoded, the driver gates are enabled, allowing the contents of the Switch Register to appear on the Unibus.

The DATA display indicates the output of the processor Data Multiplexer (DMUX) which selects information from a variety of sources within the processor (e.g., the Unibus, the ALU output, and BUS RD). The display consists of light-emitting diodes (LEDS) and associated current limiting resistors mounted in the programmer's console. The indicators are connected to the processor by cables. The output line of the Data Multiplexer [D MUX (15:00)] always controls the display, but since the multiplexer can select multiple inputs onto its output line, displayed information is varied.

The ADDRESS display indicates the contents of the processor Bus Address Register (BA Register). This display also consists of LEDS and current limiting resistors mounted on the console and connected to the processor by cables. Note that there is no multiplexing involved with the ADDRESS display as there is with the DATA display. Although it is possible to load specific data into the Bus Address Register for display, the display usually indicates the last used Unibus addresses.

Console control logic is associated with the programmer's console operational switches that provide such manual functions as start, halt, load address, examine, deposit, and continue. The console contains the manual switches and associated set-reset flip-flops used for preliminary contact bounce filtering. However, primary console control is handled by the processor either by means of the microprogram, or by combinational logic and flag flip-flops. The microprogram senses switch activation and branches to the specific routine required. The flags accommodate the special needs of the START and CONT switch sequences as well as the incrementation requirements of consecutive EXAM or DEP sequences.

The remaining functional components of the INTERFACE portion of the processor are the Unibus timing and control, the bus terminator and connector module, and the Unibus drivers and receivers.

#### 3.2.2 Unibus Timing and Control

The Unibus timing and control logic provides the required processor control of the Unibus, controls data transfer functions, bus ownership functions, and other miscellaneous functions. The control logic includes drivers and receivers for Unibus signal lines as well as timing and priority logic. Combinational logic, pulse circuits, and discrete flip-flops provide control for data transfers (DATI, DATIP, DATO, DATOB) between the processor and the Unibus with associated error checking (odd address, memory parity, stack overflow) and correction (data timeout).

In addition to the data transfer function, the Unibus timing and control logic provides the necessary control for bus ownership, transfer of bus ownership for non-processor requests (NPRs) and bus requests (BRs), and the timeout function for non-response conditions. The logic also provides power-fail timing related to BUS AC LO, BUS DC LO, and BUS INIT signals. Combinational logic, which includes a number of one-shot timing circuits, sequences these signals for power on and power off conditions.

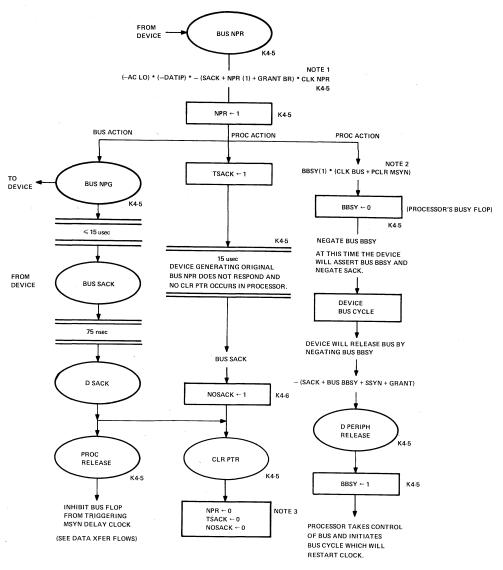

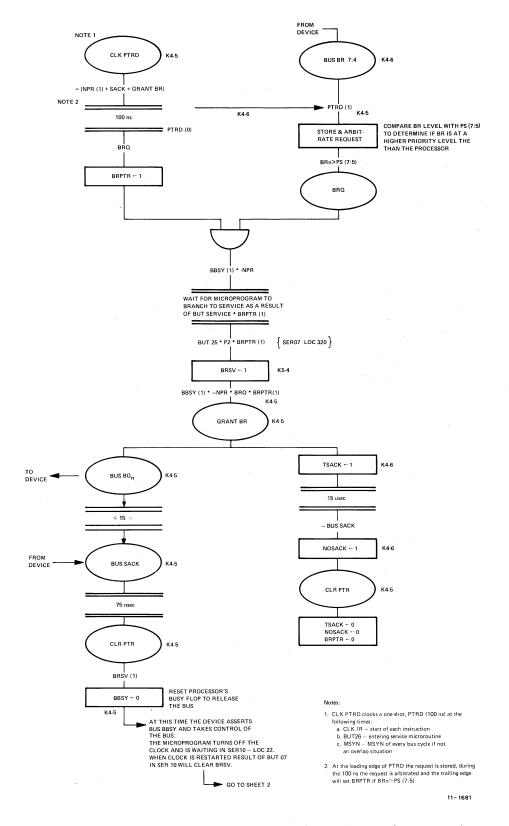

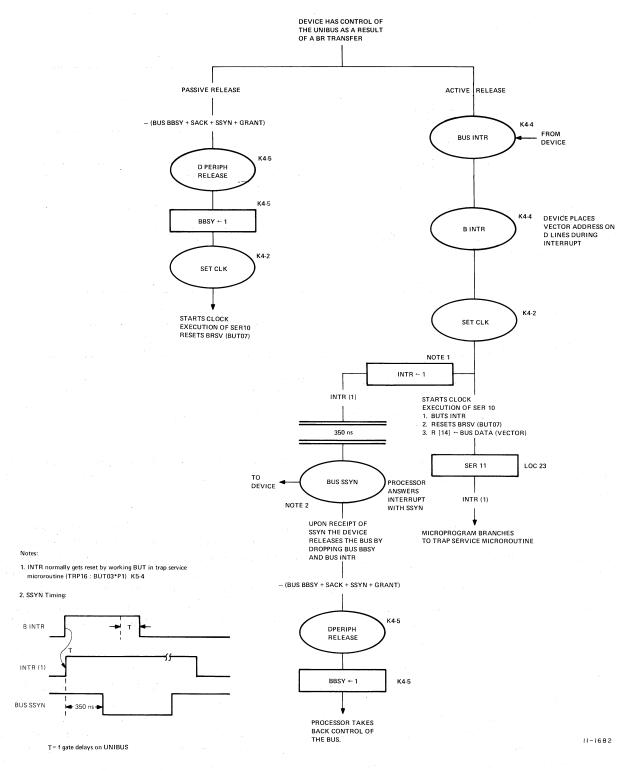

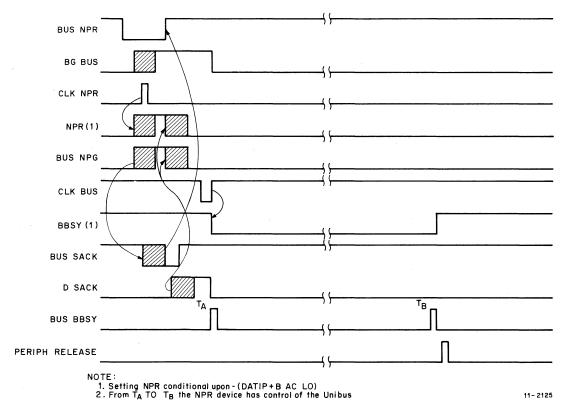

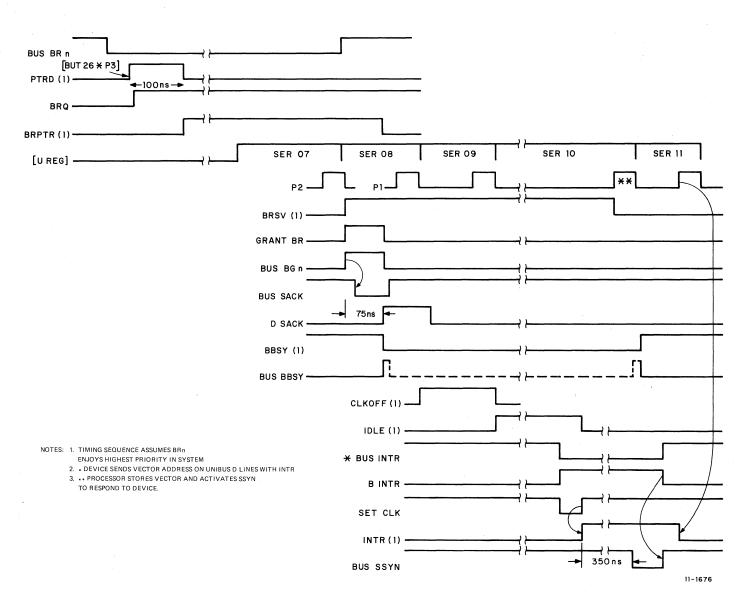

Bus ownership is arbitrated by the processor on a priority basis. The highest priority is the NPR, followed by BR7, BR6, BR5, and BR4. In order for a device to gain bus ownership, its priority must be greater than that of the then current bus master. A flowchart showing the process of arbitrating bus ownership for NPRs is shown in Figure 3-1 and for BRs in Figure 3-2. The timing sequence on the Unibus for NPR transfers is shown in Figure 3-3, and the timing sequence for BRs is shown in Figure 3-4.

A device requests bus ownership by asserting its associated request line, either NPR or BRn. The request is acknowledged when the processor asserts a corresponding bus grant line, NPG or BGn. The bus grant signal causes the requesting device to then assert SACK, which is sent back to the processor. The processor has been asserting the BBSY signal up to this time, and when it receives SACK in response to BGn, it drops BBSY. On an NPR, BBSY is dropped on the next CLK BUS or P CLR MSYN after the NPR flag is set. However, the requesting device reasserts BBSY as soon as the processor drops it, and the requesting device is now the bus master. Several devices may share a common BR priority and request bus ownership simultaneously. In that event, the device closest to the processor has the higher priority since each BG and NPG line is serially wired through every device on the Unibus. When a device asserts a BR or NPR line, it also opens the BG or NPG line to the device next to it, on the side opposite from the processor.

- 1. NPRs are clocked frequently to determine if NPR

- NPRs are clocked frequently to determine if NPR Service needed. NPG occurs.

a. BGBUS (1) microword specifies a data transfer b. ENPR CLK from EIS/FIS option c. CLK IR microprogram in FETCH d. BUT26\*P3 microprogram just entered SERVICE e. —AWBY\*SET CLK clock restarting after bus cycle f. P MSYN A device has asserted BUS MSYN.

- Microprogram either just starting or finishing a data XFER

Bus Cycle or in Service when processor gives up the bus to

the NPR device.

- a. CLK BUS just starting processor Data XFER –

clock will be turned off in this U word or succeeding

- b. PCLR MSYN just finishing a Data XFER Bus Cycle clock is on but will go off when micro-program reaches next Data XFER microroutine.

11-1680

- c. SERVICE give up the bus to do NPRs on BUT26 and on AWBBY.

- SACK timeouts will not cause a trap but will generate CLR PTR which cleans up the NPR Priority XFER control flip-flops, and will restart Processor Clock.

Figure 3-1 KD11-A Priority Transfer Timing and Control for NPRs

Figure 3-2 KD11-A Priority Transfer Timing and Control for BRs (Sheet 1 of 2)

Figure 3-2 KD11-A Priority Transfer Timing and Control for BRs (Sheet 2 of 2)

Figure 3-3 NPR Priority Transfer Timing Sequence

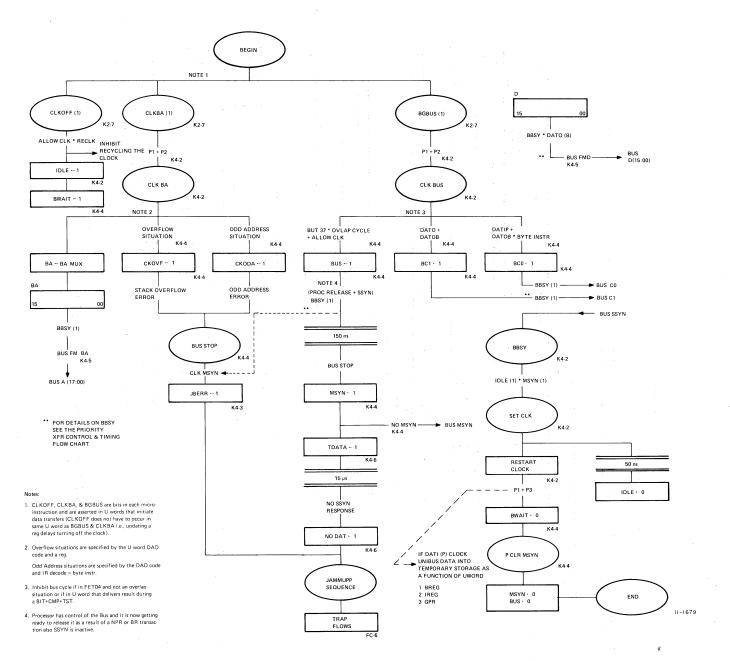

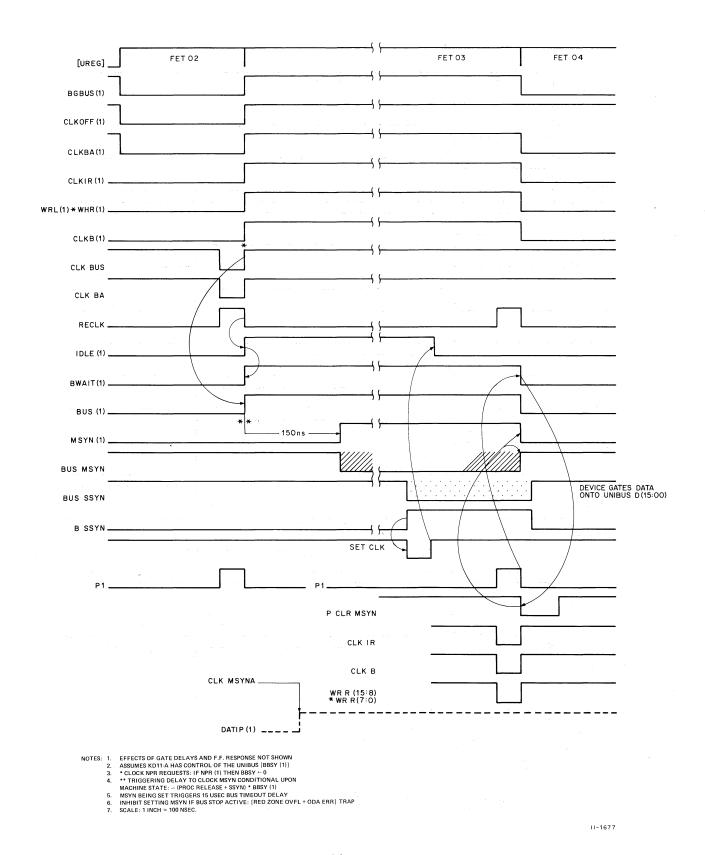

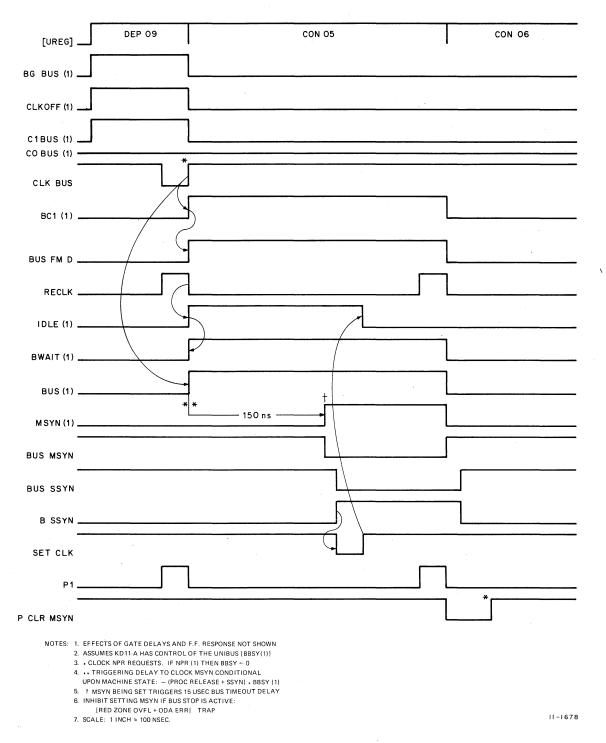

After a device has become bus master, it proceeds to transfer data on the Unibus. The sequence is shown on the flowchart in Figure 3-5. The timing of data transactions are shown in Figures 3-6 and 3-7, for DATI and DATO, respectively.

The power up sequence is shown on the timing diagram in Figure 3-8. BUS AC LO and BUS DC LO are generated by the power supply and indicate the status of the input ac power and the derived dc power. When BUS DC LO goes high, it triggers a 20 ms one-shot, PWRUP INIT. The PWRUP INIT signal initializes all the processor logic and all the Unibus devices. It also causes the microaddress 377 to be generated and set into the UPP Register in order to load it with 0s. The trailing edge of PWRUP INIT triggers the POWER RESTART signal if AC LO is not asserted. The trailing edge of POWER RESTART causes a starting microaddress to be generated and set into the UPP Register, starts the processor clock, and inhibits the initiation of a power down sequence for 3 ms, should BUS AC LO be asserted.

The timing sequence of the power down sequence is shown in Figure 3-9. Powering down causes the power supply to assert BUS AC LO followed by BUS DC LO. The BUS AC LO signal sets the LOWAC flip-flop, assuming the 3 ms PWRDN DELAY signal is not present. With LOWAC (1) set, the next P1 or P3 clock pulse causes CLK PWRDN to be generated, setting the PWRDN flag. The LOWAC flip-flop is reset on the next P1 or P3 clock pulse when PWRDN (1) is asserted. At the completion of the current instruction, the PWRDN flag causes the microprogram to branch to SERVICE and subsequently to the TRAP SERVICE microroutine. The power fail trap routine can call a subroutine from memory that causes all volatile information to be saved and the program to be halted at a known location for restarting. Meanwhile, the BUS AC LO signal causes a 15 ms AC LO signal to be generated, locking up the original AC low condition which may or may not still be present. The BUS AC LO signal inhibits further NPR transactions. Also, a 7 ms DELAY DC LO signal was triggered at the same time. The trailing edge of this signal pulses BUS DC LO, which in turn generates PWRUP INIT, if BUS DC LO is not being asserted by the power supply. At the trailing edge of PWRUP INIT, it is possible to enter the power up sequence if BUS AC LO indicates normal power again on the bus. (Detailed examples of the power down and power up sequences are given in Chapter 5 in the discussion of the logic on Sheet K5-8.)

Figure 3-4 BR Priority Transfer Timing Sequence

Figure 3-5 KD11-A Bus Data XFER Timing and Control

Figure 3-6 KD11-A DATI(P) Bus Transaction Timing Diagram

Figure 3-7 KD11-A DATO(B) Bus Transaction Timing Diagram

Figure 3-8 KD11-A Power Up Timing Sequence

Figure 3-9 KD11-A Power Down Timing Sequence

The microprogram interfaces directly with the Unibus timing and control logic. The start or error checking flip-flops are loaded, either directly or conditionally from the microword. The loading of Unibus data and the deactivation of MSYN occur as a function of the next microword after a DATI or DATIP transfer operation. The processor transmits address and data information to the Unibus under control of the microprogram. Note, however, that bus ownership, the power fail logic, and the Unibus data transfer operate asynchronously and are independent of the microprogram.

The interface portion of the processor contains both bus transmitters (8881 gates) and bus receivers (380 gates) to provide the necessary conversion so that processor and Unibus signals are compatible. The transmitters (drivers) permit the processor to place groups of signals on the bus; the individual signals are noted on the block diagram on the output line of the associated gate. These signals include the outputs of the Bus Address (BA) Register, the D Register, the Processor Status (PS) Register, and the Switch Register. Inputs to the processor from the bus are gated through the bus receiver to the D Multiplexer, which then routes the signals to the proper component within the data paths.

The final functional component in the INTERFACE section of the processor is the bus terminator and connector module, which interconnects system units and also provides the termination required by the Unibus. In the KD11-A Processor, a single set of slots (A09, B09) is provided for the Unibus interface and the processor is single ended. Note that the Unibus Terminator module (M930) is located in, and powered from, the last device on the bus.

# 3.3 DATA PATHS

The DATA PATHS portion of the KD11-A Processor manipulates, stores, and routes data within the processor.

The prime element of the data path logic is the ALU which operates, both logically and arithmetically, upon input data from the interface portion of the processor. To a certain extent, data path logic is ordered upon the ALU because of the requirements to provide data to each of its inputs and to store, or otherwise use, its output. The ALU and all other components in the processor data paths are described in the following paragraphs.

For the purposes of the following discussion, the term "Scratch Pad Register" refers to one of the 16 internal processor registers shown on the block labeled REGISTER (REG). These registers are also referred to as the General Registers.

# 3.3.1 Data Paths, Multiplexers and Registers

The Scratch Pad Register supplies operands for the ALU. These operands either come directly from an instruction source or destination mode operation, or they are stored in the Scratch Pad Register during address calculations. In either case, the ALU receives a direct input from the BUS RD (15:00) line. This input is referred to as the *A input*.

In the Scratch Pad Registers, only one address may be accessed at a time, and simultaneous read and write operations are not permissible. In order to provide the two ALU operands (when both operands come from the Scratch Pad Register), it is necessary to provide temporary storage. This storage is provided by the B Register; the contents of the B Register can be fed through the B Multiplexer (B MUX) into the B input of the ALU.

The ALU A input provides variable operands; the B input provides variable operands, constants, and swapped and sign-extended byte operands. The A input usually comes from the Scratch Pad Register on the wire-ORed BUS RD lines (as shown by the dotted OR gates on the block diagram). The Processor Status Register of the basic machine and certain multiplexers with the KE11-E and KE11-F options are also connected to the A input.

The B input comes from the B MUX which receives its input from either the B constants or the B Register. The B Register, in turn, receives its input from the D Multiplexer (D MUX) which has four possible inputs. Therefore, the B input to the ALU comes from a variety of sources with two levels of multiplexing. These various inputs are discussed in the following paragraphs.

The four inputs to the D MUX are: Unibus data lines BUS D (15:00), which permit the ALU to receive operands from other devices within the system; the buffered BUS RD (15:00) lines, which permit operands from the Scratch Pad Register; the output of the D Register, which is the output of the ALU and can permit the result of a previous arithmetic operation to be used as an operand; and the shifted output of the D Register.

The desired D MUX output can be stored in the B Register, which, in turn, can be fed to the ALU by means of the B MUX. Note that the buffered BUS RD signal can be fed through the D MUX into the B Register. This data path is of special interest in the machine instruction for the register-to-register operations, where both the A and B inputs of the ALU must come from the Scratch Pad Register. For example, the first operand passes through the D MUX into the B Register for storage. The second operand can then be fed to the A input of the ALU, and the first operand fed to the B input by means of the B MUX.

The B constants, which are applied through the B MUX to the ALU, provide elementary values (such as  $1_8$  and  $2_8$ ) for incrementation or decrementation throughout machine operation. They also provide other values such as the Switch Register address, more complex constants such as trap vectors or masks for manipulating instruction offsets, and the conditional constants which are a function of machine status and jumper selection.

The B input to the ALU can be either the B constants value or one of the four possible functions of the B Register. The four B Register functions are:

- a. B Register The contents of the register are applied directly to the ALU. Therefore, BIN (15:00) of the ALU equals B (15:08) and B (07:00).

- b. B Extend The B Register contents are gated so that bit 07 (MSB of the low-order byte) provides an extension for the high-order byte. Note that in this case, the value in the high-order byte is either all 1s or all 0s depending upon bit 07 of the B Register; the low-order byte is the B Register directly.

- c. Byte Duplication Either the low-order byte or the high-order byte may be duplicated. Therefore, BIN (15:00) of the ALU equals either B (15:08) and B (15:08), or B (07:00) and B (07:00).

- d. Byte Swapping The high-order and low-order bytes may be exchanged. Therefore, BIN (15:08) of the ALU equals B (07:00) and BIN (07:00) equals B (15:08) for the high byte and the low byte, respectively.

The ALU provides an altered data output that is used for Unibus addresses and data, and by internal processor registers such as the Scratch Pad Register and the Processor Status Register. The output of the ALU is stored in the D Register and/or the Bus Address Register.

The D Register storage capability permits data which has been operated upon in the ALU to be fed around to the B MUX for further manipulation, thus permitting data to be stored in another register (the B Register). This additional path and storage capability is important because it is necessary for single or double operand register operations and is very often necessary in iterative operations.

Operation of the ALU is also determined by the carry-in (CIN logic) and carry-out (COUT MUX) signals. The carry-in signal does not come directly from the microprogrammed word but is a function of the microprogrammed word and the conditions (usually the Instruction Register) that are enabled at specific locations in the microprogrammed flow.

The Carry-out multiplexer (COUT MUX) provides multiplexing of the specific carry information normally used in the PDP-11. The signals that can be selected are: COUT 15, COUT 07, ALU 15, and PS(C). The COUT 15 signal represents the carry from a word operation; the COUT 07 signal represents the carry from a byte operation. These

signals are used for condition code inputs and rotate/shift operations. The ALU 15 signal is the bit 15 output of the ALU which is used for rotate/shift operations. The PS(C) signal is the carry bit from the Processor Status Register. The signal selected by the COUT MUX is clocked into an extension of the D Register which is called D(C). This storage extension is used in rotate/shift operations and in certain arithmetic operations.

A summary of the functions of the BA MUX, the D MUX and the B MUX, and their associated control signals is given in Table 3-1.

Table 3-1

PDP-11/40 Data Path Multiplexer Control

| Signal                                                                                                                                                                                                                                  | Function                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                         | BA MUX                                                                                                                             |

| Select BA Mux, bits (15:00)<br>SBAM(0)<br>SBAM(1)                                                                                                                                                                                       | Select BUS RD data<br>Select ALU output                                                                                            |

|                                                                                                                                                                                                                                         | D MUX                                                                                                                              |

| Select D Mux, bits (15:00)<br>SDM1(0) * SDM0(0)<br>SDM1(0) * SDM0(1)<br>SDM1(1) * SDM0(0)<br>SDM1(1) * SDM0(1)                                                                                                                          | Select BUS RD data Select Unibus data Select D Register Select D Register shifted right with D(C) shifted into bit position 15.    |

|                                                                                                                                                                                                                                         | B MUX                                                                                                                              |

| Select B Mux Low, bits (07:00)  SBML1(0) * SBML0(0)  SBML1(0) * SBML0(1)  SBML1(1) * SBML0(0)  SBML1(1) * SBML0(1)  Select B Mux High, bits (15:08)  SBMH1(0) * SBMH0(0)  SBMH1(0) * SBMH0(1)  SBMH1(1) * SBMH0(1)  SBMH1(1) * SBMH0(1) | Select B (07:00) Select B (07:00) Select B (15:8) Select BC (07:00)  Select B (07) Select B (07) Select B (07:00) Select BC (15:8) |

| (a + b) * e                                                                                                                                                                                                                             | Selects B Register                                                                                                                 |

| (a + b) * f                                                                                                                                                                                                                             | Selects B Register with sign extension in high byte $[B(15:8) \leftarrow B(7)]$                                                    |

| c * g                                                                                                                                                                                                                                   | Swaps bytes                                                                                                                        |

| c * e                                                                                                                                                                                                                                   | Duplicates high byte in low byte                                                                                                   |

| d * h                                                                                                                                                                                                                                   | Selects constant                                                                                                                   |

| a + b * g                                                                                                                                                                                                                               | Duplicate low byte in high byte                                                                                                    |

# 3.3.2 Decoding

The address and data decoding logic is a combinational logic network that decodes the output of both the D and BA Registers. When the D Register output is decoded, the decoder senses whether or not the output (for both byte and word segments) is 0 [D (15:00) = 0 H]. The Bus Address Register is decoded to determine if a processor address has occurred, or if an address is less than specified values. It should be noted that the decoding logic decodes the BA Register and not the Unibus address. In the first case, the processor addresses, which represent only those internal registers that can be accessed by the processor itself, are used to gate Unibus responses for bus operations. If the decoded address of the Processor Status Register or the console Switch Register, then either PS ADRS H or SR ADRS H is true. Other addresses also exist. If the decoded address is less than the specified value, then a stack overflow violation may occur and the BOVFL signal is true. Stack limit errors are either yellow zone (warning) or red zone (fatal) indications.

# 3.3.3 Arithmetic Logic Unit

The Arithmetic Logic Unit (ALU) is the heart of the data path logic. It performs 16 Boolean operations and 16 arithmetic operations on two 16-bit words. The ALU is controlled by six input signals. One signal, ALUM H, selects either the logic or arithmetic mode of operation. Four signals (ALUS0 through ALUS3) select the desired function. The sixth signal is the output of the carry-in (CIN) logic. Basically, the ALU receives two 16-bit words as inputs (AIN and BIN) and performs the operation selected by the six control signals. The output of the ALU is, therefore, altered data which is used for Unibus addresses and data, and is also used by the internal processor registers such as the Scratch Pad Register or the Processor Status Register. The output of the ALU is stored in the D Register or the BA Register for use.

#### 3.3.4 PS Register

The Processor Status (PS) Register is an 8-bit register that stores information on the current priority of the processor [bits (07:05)], the result of the previous operation (condition codes bits N, Z, V, C), and an indicator for detecting the execution of an instruction to be trapped during program debugging (T bit). The PS Register is located between two basic data paths: D MUX (15:00) and BUS RD (15:00). The register is loaded from the D MUX. In addition, the condition codes control logic provides inputs to the N, Z, V, and C bits. The register output is either gated directly onto the Unibus (in cases where the processor has addressed the Unibus as an absolute address) or is gated onto the BUS RD (15:00) line for use by the processor data paths. This latter case is used, for example, by the condition code instructions which alter the contents of the Processor Status Register.

# 3.3.5 Register (REG)

The 16 internal processor registers comprise the Scratch Pad Register. Eight of these are programmable general registers which include the Program Counter (PC) and Stack Pointer (SP). In the KD11-A Processor, the additional eight registers (not accessible to the program) are used for a variety of functions as shown on the block diagram. Such functions include: intermediate address (TEMP), source and destination data (SOURCE, DEST), a copy of the Instruction Register (IR), the last interrupt vector address (VECT), registers for console operation (TEMPC, ADRSC), and a stack pointer for operation of the KT11-D Memory Management Option (SP USER).

In summation, the data path logic is the fundamental section of the processor; it performs data storage, modification, and routing functions. The other two sections of the processor (interface and control) exist primarily to support the data path logic.

An important aspect of the data path logic is its expandability. The D MUX signals represent an outgoing bus and the BUS RD lines are a wired-OR input bus. Just as the Scratch Pad Register and the Processor Status Register are connected between these two signal buses, other devices can also be connected between them. For example, the KE11-E Extended Instruction Set option and the KE11-F Floating Instruction Set option are connected between these two signal buses for arithmetic expansion of the basic processor.

#### 3.4 MICROCONTROL

The final section of the block diagram is the microcontrol logic which provides the required control signals for the data path logic and the interface logic. The prime element of the control logic is the read-only memory (ROM) which provides the microwords. The bits in each microword (U WORD), in turn, control machine operation as described in Chapter 2. Other elements within the MICROCONTROL section includes microaddress and microaddress modification logic that receives inputs from the ROM, the Instruction Register with associated decoding logic, various processor flags, and basic machine timing and flag control logic.

When an instruction is fetched from an external data storage location, the instruction enters the processor from the Unibus, passes through the D MUX, and is loaded into the Instruction Register under microword control. The output of the Instruction Register is decoded by combinational logic (IR DECODE) to provide the microbranch code (BUBC) for several branch conditions and the discrete auxiliary signals required by the condition code logic and ALU control logic. The last sections of logic are discussed immediately because of their interaction with the DATA PATHS section. The operation of the basic microcontrol follows.

# 3.4.1 Condition Codes Input

The condition codes are used to store information about the results of each instruction so that this information can be used by subsequent instructions. The information recorded in the condition code bits (N, Z, V, C) of the Processor Status Register differ for each instruction type, and often for the part of the instruction being executed. The decoded output of the IR DECODE logic and the select processor status (SPS) code of the microword determine which conditions are to be presented as the data input to the Processor Status Register. In addition, the SPS code determines when the Processor Status Register should be loaded directly from the D MUX.

# 3.4.2 ALU Control

The ALU control combinational logic receives the DAD (discrete alteration of data) code from the microword as a function of the IR decode logic. In general, the SALU and SALUM microword bits directly alter operation of the ALU; however, during the latter part of an instruction, where common instruction flow paths exist for several instructions, the DAD code is combined with the Instruction Register to alter operation of the ALU.

There are 32 possible ALU functions, depending on the state of SALU (03:00), ALUM and CIN. Some of these functions are contained in Table 3-2.

# 3.4.3 Flag Control

The flag control logic is closely related to the IR decode logic because certain instructions require specific flags, such as WAIT and HALT. Other flags exist for service of peripherals and console request, as well as for error conditions. Flip-flops within the flag control logic interact directly with the microbranch logic to provide the required branch conditions in the machine flow to provide flag service.

#### 3.4.4 U Branch Control

In a microprogrammed computer, the next ROM address (next machine state) is dependent on a number of previous conditions. The purpose of the microword branch control (U BRANCH CONTROL) logic and the Branch Microprogram Test (BUT) Multiplexer is to select the next proper machine state. The microbranch control provides some of the inputs to the BUT decoding logic. The microbranch control combines the diverse instruction decoding of the Instruction Register and encodes it into two, three, four, or five bits of a microaddress alteration, called "basic microbranch codes," for specific BUTs [BUBC (BUT XX)]. For most of the complicated branches, such as the first instruction branch or some of the subsequent source or destination instruction branches, these codes are fairly extensive. They may also be fairly simple, consisting of only three bits or, in some cases, three bits of another BUT encoded with another single condition. The latter case is particularly true with the INSTR 2 BUBC and the (BYTE and INSTR 2) BUBC.

Table 3-2

Table of Combinations

74181 — Arithmetic Logic Unit

|        | Selection |                                                |                                                | ALUM=H                                                                                                 | Active High Data ALUM=L Arithmetic Operations                                                                                                                                                                              |                                                                                                                                                                                                                                                                               |  |

|--------|-----------|------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| S3     | S2        | S1                                             | S0                                             | Logic<br>Functions                                                                                     | CIN = 0                                                                                                                                                                                                                    | CIN = 1                                                                                                                                                                                                                                                                       |  |

|        |           | L<br>H<br>H<br>L<br>H<br>H<br>L<br>L<br>H<br>L | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H<br>L<br>H | F=Ā<br>F=A+B<br>F=ĀB<br>F=O<br>F=ĀB<br>F=Ā+B<br>F=Ā+B<br>F=Ā+B<br>F=A+B<br>F=B<br>F=AB<br>F=AB<br>F=AB | F=A F=A+B F=A+B F=minus 1 (2's COMPL) F=A plus $A\overline{B}$ F=(A+B) plus $A\overline{B}$ F=A minus B minus 1 F=A $\overline{B}$ minus 1 F=A plus AB F=A plus B F=(A+ $\overline{B}$ ) plus AB F=AB minus 1 F=AB minus 1 | F=A plus 1 F=(A+B) plus 1 F=(A+B) plus 1 F=0 F=A plus $A\overline{B}$ plus 1 F=(A+B) plus $A\overline{B}$ plus 1 F=A minus B F=A $\overline{B}$ F=A plus AB plus 1 F=A plus B plus 1 F=A plus AB plus 1 F=A plus AB plus 1 F=AB F=A plus A plus 1 F=AB F=A plus A plus 1 F=AB |  |

| H<br>H | H<br>H    | H<br>H                                         | L<br>H                                         | F=A+B<br>F=A                                                                                           | $F=(A+\overline{B})$ plus A<br>F=A minus 1                                                                                                                                                                                 | F=(A+B) plus A plus 1<br>F=A                                                                                                                                                                                                                                                  |  |

<sup>\*</sup>Each bit is shifted to the next more significant position.

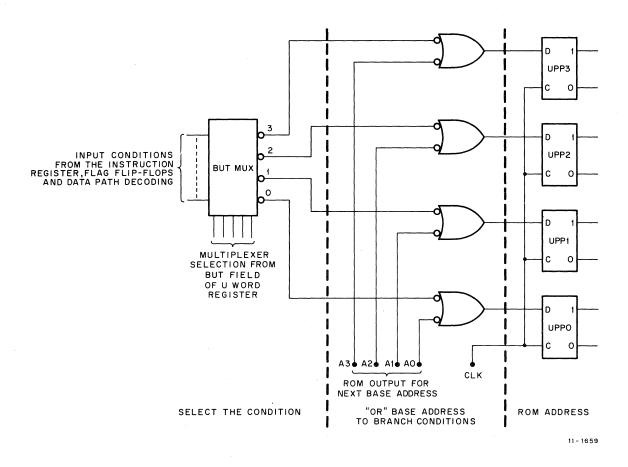

## 3.4.5 BUT MUX

The Branch Microprogram Test Multiplexer (BUT MUX) selects sets of address alterations to alter data into the Microprogram Pointer (UPP) which points to the next ROM address. The BUT MUX provides a 5-bit output with the number of possible inputs on the lowest order bits being greater than the number of inputs that can be selected for the higher order bits. This corresponds to the fact that few of the branches involve all five or six bits of address alteration. There are a number of address alterations that involve only one bit, usually the lowest order bit.