$\times$

KB11-B PROCESSOR MANUAL (PDP-11/70) PETER HOYLE

digital equipment corporation · maynard. massachusetts

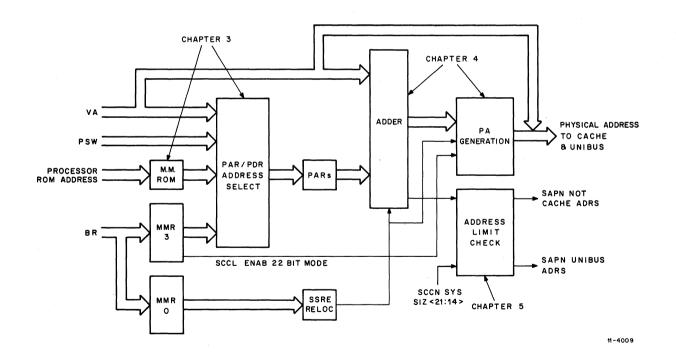

#### Copyright © 1975 by Digital Equipment Corporation

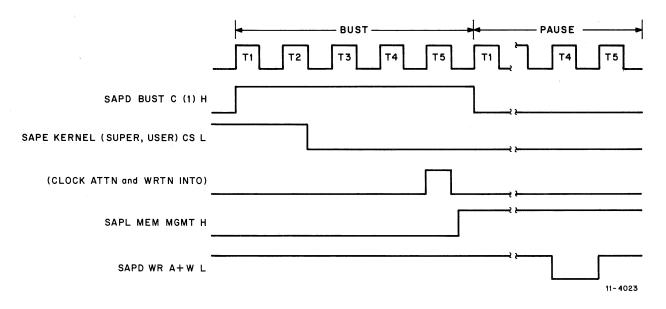

The material in this manual is for informational purposes and is subject to change without notice.

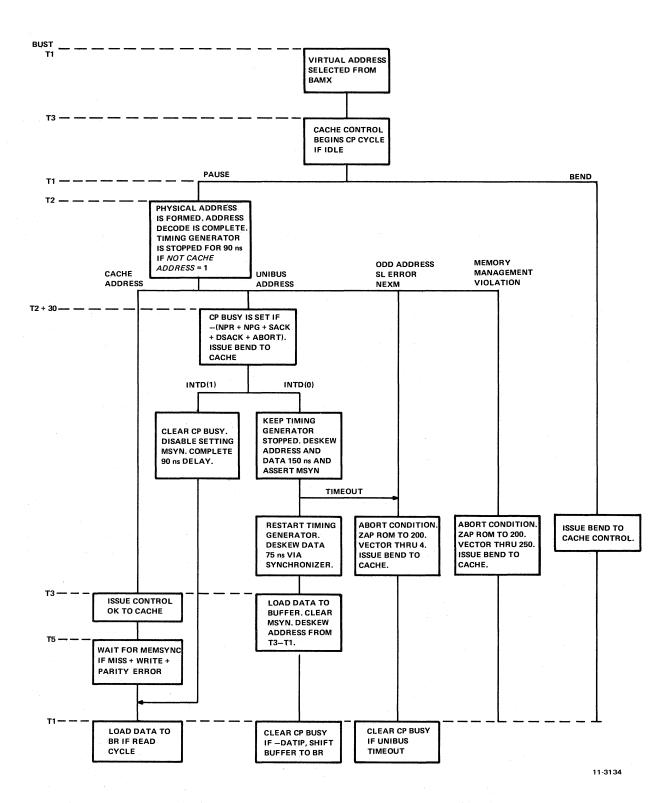

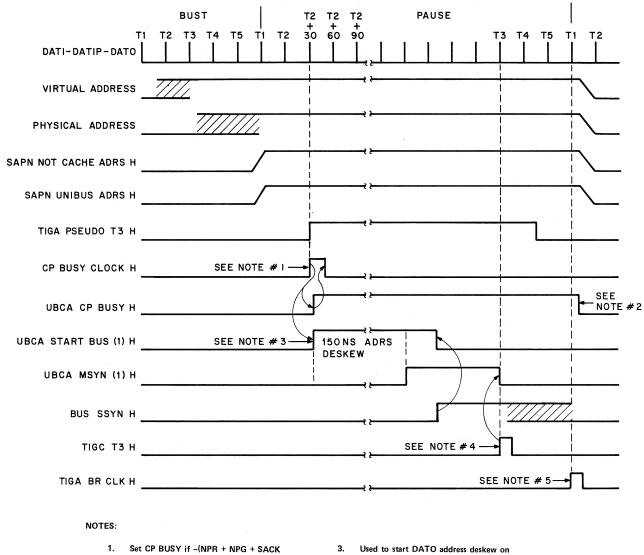

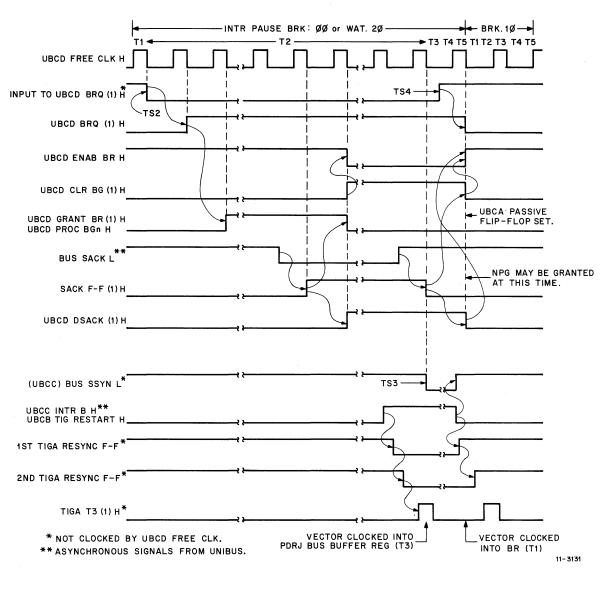

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

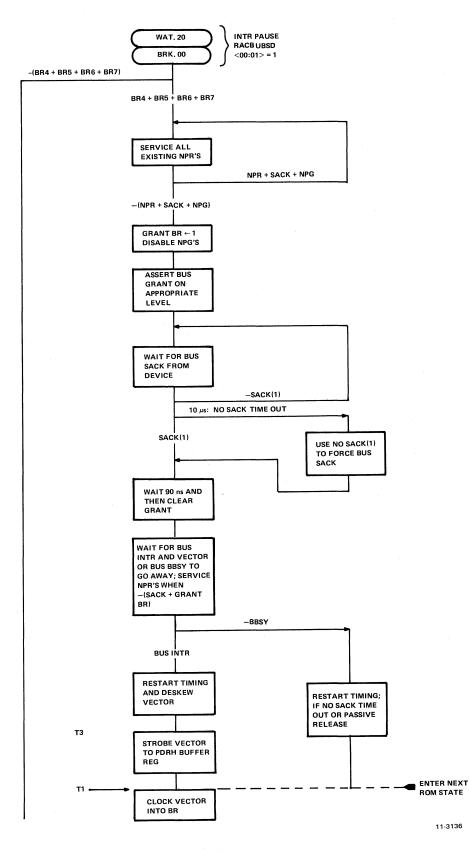

Printed in U.S.A.

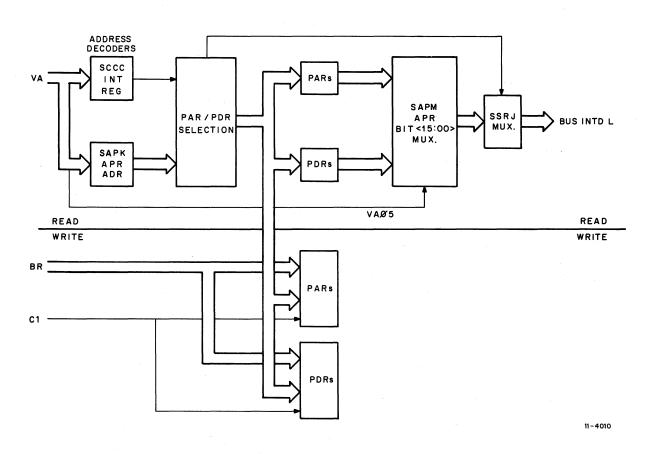

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

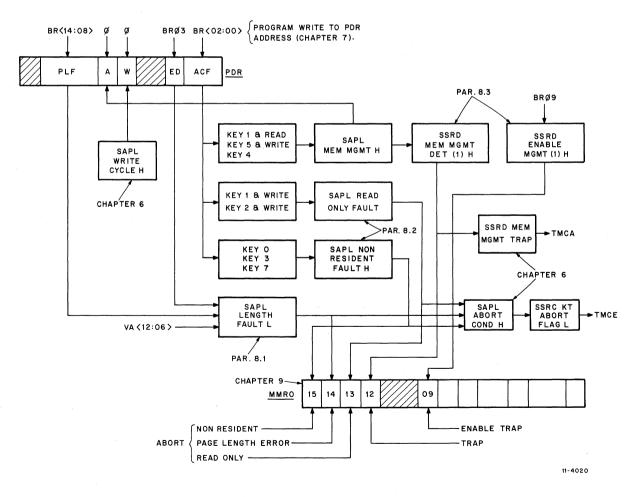

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

> DEC FLIP CHIP DIGITAL UNIBUS DECUS

PDP FOCAL COMPUTER LAB MASSBUS

#### TABLE OF CONTENTS

#### SECTION I

#### SECTION II PROCESSOR

INTRODUCTION

| CHAPTER 1 | INSTRUCTION DECODE AND MICROPROGRAM CONTROL |

|-----------|---------------------------------------------|

| CHAPTER 2 | DATA PATHS                                  |

| CHAPTER 3 | PROCESSOR CONTROL REGISTERS                 |

| CHAPTER 4 | TIMING GENERATOR                            |

| CHAPTER 5 | DATA TRANSFERS                              |

| CHAPTER 6 | ABORTS, TRAPS AND INTERRUPTS                |

**BLOCK DIAGRAM AND CONCEPTS**

#### SECTION III CONSOLE

INTRODUCTION

| CHAPTER 1 | SWITCHES, INDICATORS AND OPERATION |

|-----------|------------------------------------|

| CHAPTER 2 | LOGIC DESCRIPTION                  |

#### SECTION IV MEMORY MANAGEMENT

| INTRODUCTION | PDP-11/70 ADDRESS SPACE                        |

|--------------|------------------------------------------------|

| CHAPTER 1    | GENERAL DESCRIPTION                            |

| CHAPTER 2    | MEMORY MANAGEMENT MAPPING FUNCTION             |

| CHAPTER 3    | PAR AND PDR ADDRESSING DURING RELOCATION       |

| CHAPTER 4    | GENERATION OF THE PHYSICAL ADDRESS             |

| CHAPTER 5    | ADDRESS VALIDITY                               |

| CHAPTER 6    | DESCRIPTION OF PDR                             |

| CHAPTER 7    | READING AND WRITING OF PAR AND PDR REGISTERS   |

| CHAPTER 8    | MEMORY MANAGEMENT ERROR HANDLING               |

| CHAPTER 9    | MEMORY MANAGEMENT REGISTERS (MMR0, 1, 2 and 3) |

|              |                                                |

#### SECTION V UNIBUS MAP

#### INTRODUCTION

| CHAPTER 1 | GENERATION OF THE PHYSICAL ADDRESS        |

|-----------|-------------------------------------------|

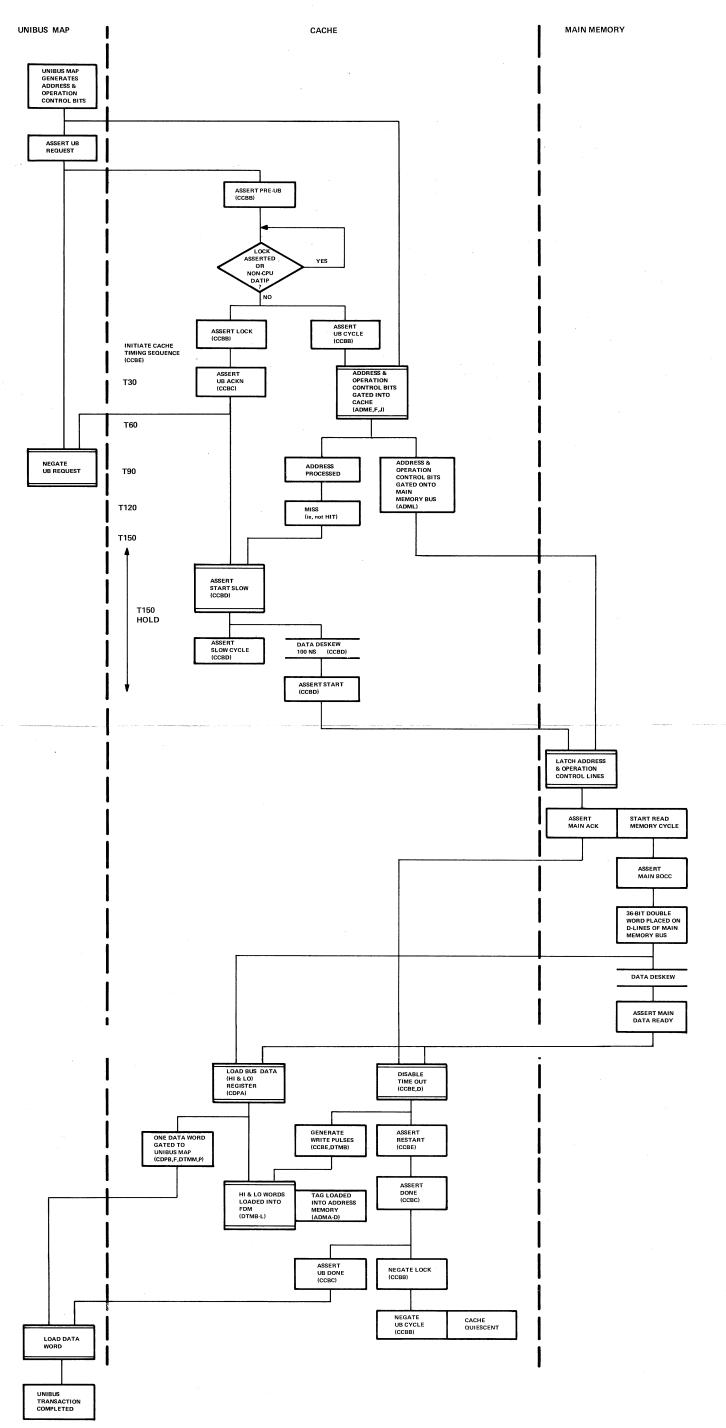

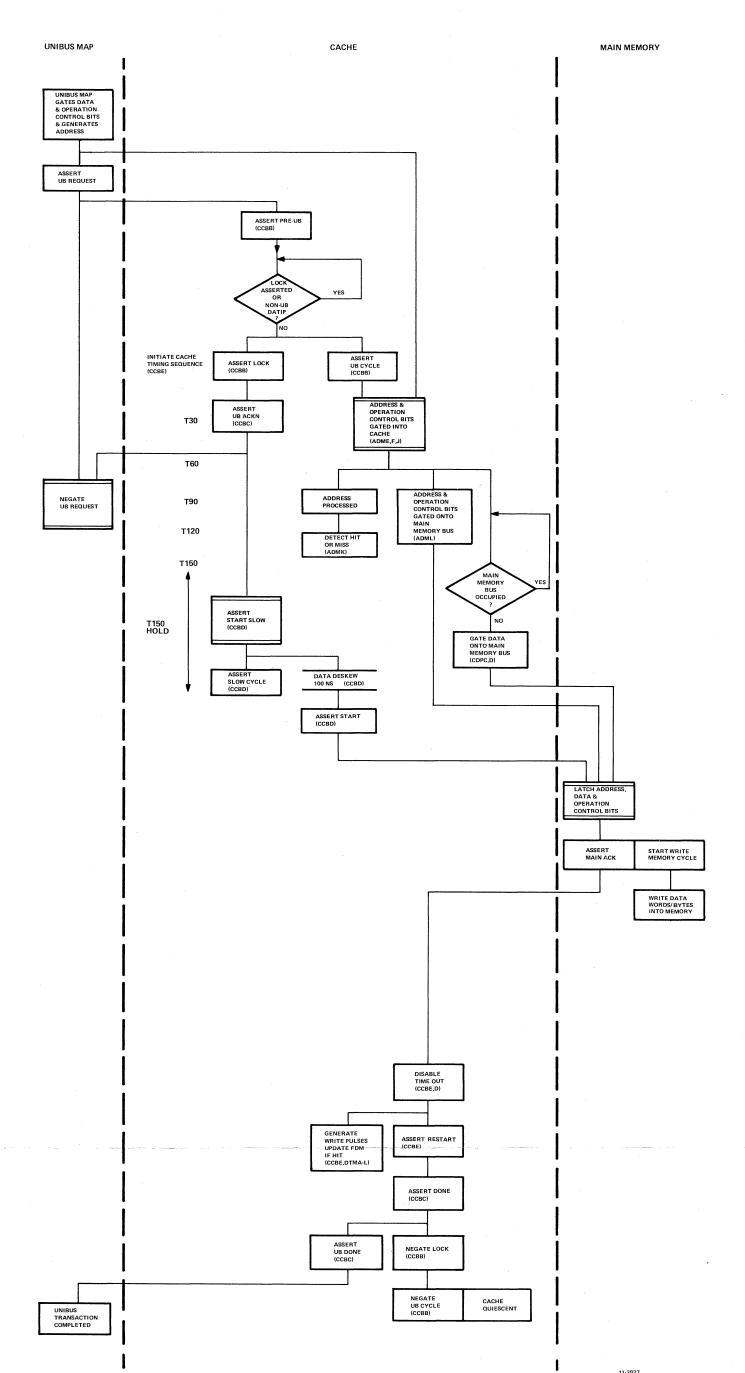

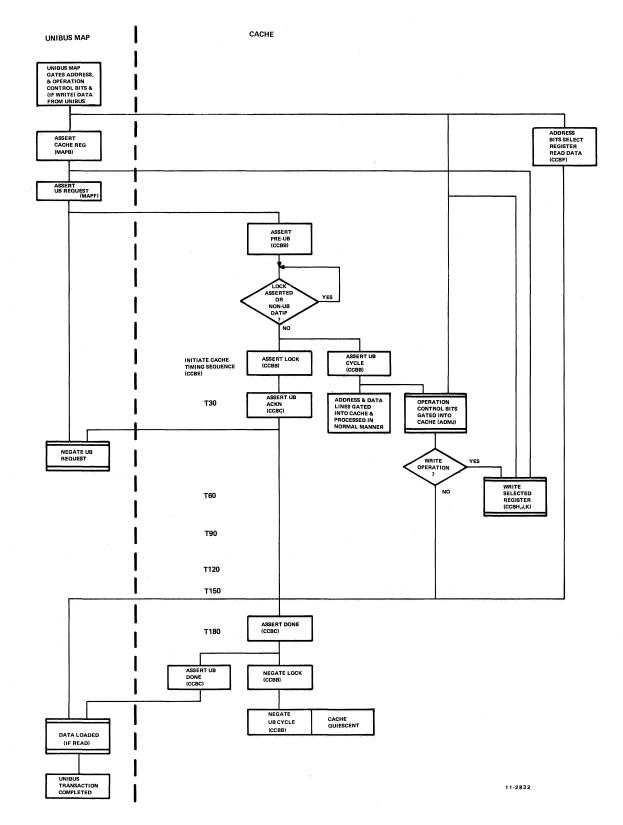

| CHAPTER 2 | UNIBUS/CACHE INTERFACE                    |

| CHAPTER 3 | READING AND WRITING THE MAPPING REGISTERS |

SECTION VI CA

CACHE

## **SECTION I**

# **BLOCK DIAGRAM AND CONCEPTS**

Unless otherwise indicated, references within this section pertain to this section only.

#### SECTION I BLOCK DIAGRAM AND CONCEPTS CONTENTS

**BLOCK DIAGRAM**

BLOCK DIAGRAM

Processor . . . .

Memory Managemen

Unibus Map . . .

**CHAPTER 1**

1.1

1.1.1

1.1.2

1.1.3

| I-1-1 |

|-------|

| I-1-2 |

| I-1-2 |

| I-1-3 |

|       |

Page

| 1.1.4 | Cache                            |

|-------|----------------------------------|

| 1.1.5 | Unibus                           |

| 1.1.6 | Optional Equipment               |

| 1.2   | MEMORY SYSTEM                    |

| 1.2.1 | Representation and Storage I-1-4 |

| 1.2.2 | Address Space                    |

| 1.2.3 | Mapping                          |

| 124   | Parity                           |

| <b>CHAPTER 2</b> | CONCEPTS                            |        |

|------------------|-------------------------------------|--------|

| 2.1              | MICROPROGRAMMING                    | I-2-1  |

| 2.2              | PARALLEL OPERATION (PIPELINING)     | I-2-4  |

| 2.3              | VIRTUAL MACHINES                    | I-2-4  |

| 2.4              | REENTRANT AND RECURSIVE PROGRAMMING | I-2-10 |

#### ILLUSTRATIONS

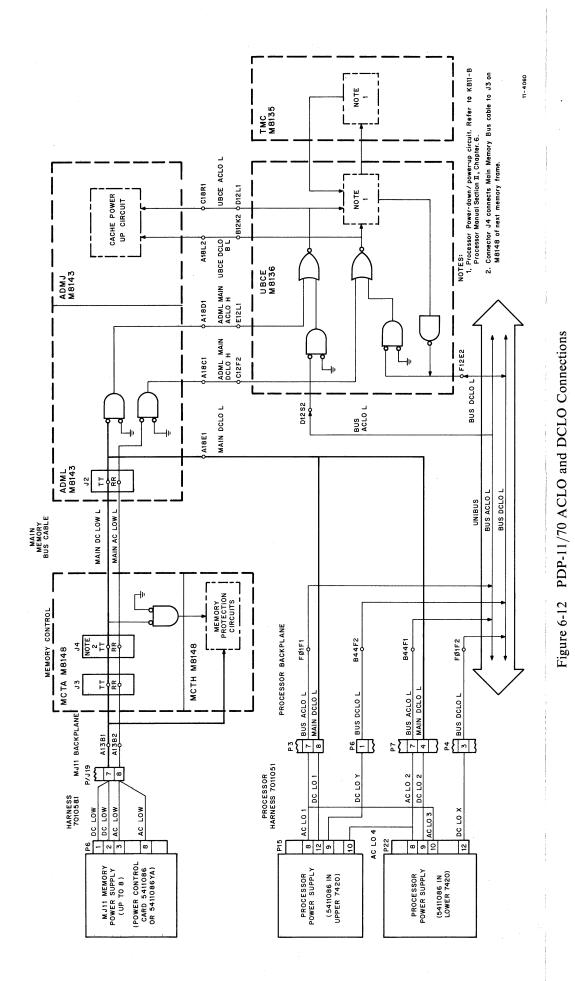

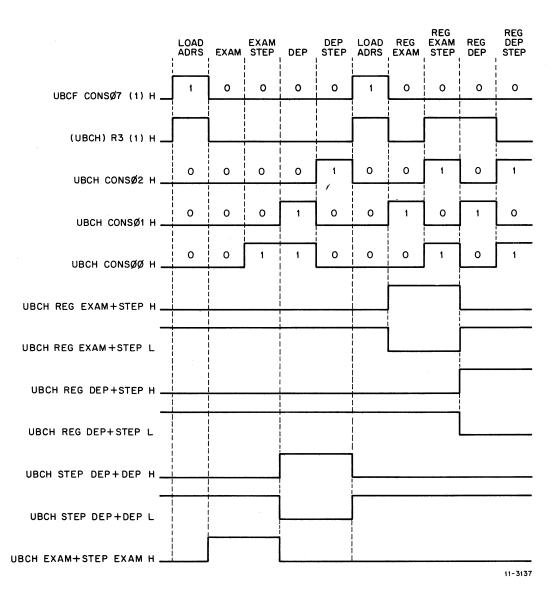

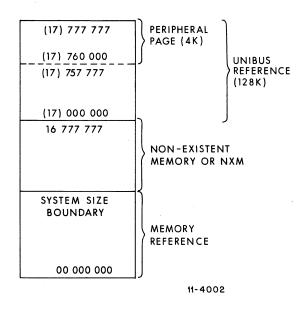

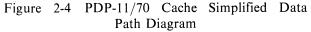

#### Figure No. Title Page I-1-1 1-1 PDP-11/70 Block Diagram ..... I-1-3 PDP-11/70 System Simplified Block Diagram 1-2 I-1-4 1-3 High and Low Byte I-1-5 1-4 Memory Addresses Word and Byte Addresses ..... I-1-5 1-5 I-1-6 Main Memory Addresses 1-6 I-1-6 1-7 Address Paths I-1-7 1-8 Physical Address Space 1-9 I-1-8 I-1-8 1-10 I-1-9 1-11 I-1-9 Parity (P) in the PDP-11/70 System 1-12

#### **INTRODUCTION**

This manual describes the KB11-B Central Processor Unit, which is the basic component of the PDP-11/70 Programmed Data Processor System. The purpose of this manual is to:

- 1. provide an overall understanding of how the KB11-B functions in the PDP-11/70 System.

- 2. describe how the KB11-B logic works in sufficient detail to enable maintenance personnel to perform on-site trouble-shooting and repair.

The format of this manual is functional, i.e., the intent is to explain the various processes that are executed by the KB11-B, as opposed to a module by module logic description. Since this might be a problem for a technician who has a module to repair, an index of logic functions by module is provided.

This manual is divided into six sections:

Section I is an introduction to the PDP-11/70. It describes a block diagram of the system and introduces some system concepts.

Section II describes the processor. Its six chapters explain processor control, data manipulation, Control Registers, timing, data transfers and error handling.

Section III provides both an operating guide to the Console and a detailed description of its logic.

Section IV describes Memory Management and address space.

Section V describes the Unibus Map.

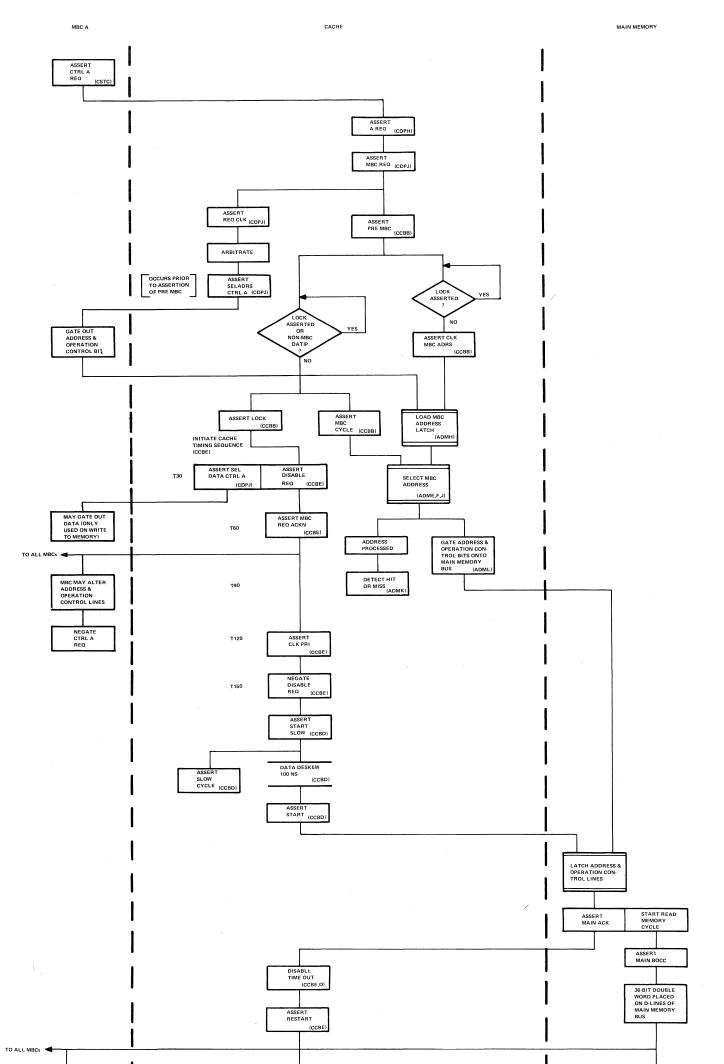

Section VI contains a description of the Cache.

Due to the numerous references to specific logic functions in the text, it is recommended that the reader refer to the *PDP-11/70 Engineering Print Set* while reading this manual.

Comments (both favorable and unfavorable), suggestions, and corrections are welcome. A Reader's Comment sheet is provided for this purpose at the end of this manual.

#### **RELATED DOCUMENTS**

This manual should be used in conjunction with the following related publications:

PDP-11/70 Maintenance and Installation Manual

PDP-11/70 Processor Handbook

MJ11 Memory System Maintenance Manual

FP11 Floating-Point Processor Manual

RWS04/RWS03 Fixed Head Disk Subsystem Maintenance Manual

RWP04 Moving Head Disk Subsystem Maintenance Manual

TWU16 Magnetic Tape Subsystem Maintenance Manual

PDP-11 Peripherals Handbook

## CHAPTER 1 BLOCK DIAGRAM

The PDP-11/70 is the most powerful computer in the PDP-11 family. It is designed to operate in large, sophisticated, high-performance systems. It can by used as a powerful computational tool for high-speed, real-time applications and for large multi-user, multi-task, time-shared applications requiring large amounts of addressable memory space. Although it is a 16-bit machine, it applies the power of a Cache memory and 32-bit memory and I/O structure to demanding, multi-function computing requirements.

The PDP-11/70 contains as an integral part of the Central Processor Unit (CPU), the following hard-ware features and expansion capabilities:

Cache memory organization to provide bipolar memory speed at core memory prices. Memory Management for relocation and protection in multi-user, multi-task environments.

Ability to access up to 4 million bytes of Main Memory.

Optional high-speed mass storage controllers as an integral part of the CPU. These controllers provide dedicated paths to high performance storage devices.

**Optional Floating Point Processor**

#### **1.1 BLOCK DIAGRAM**

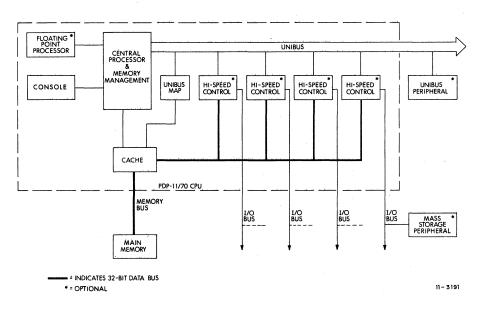

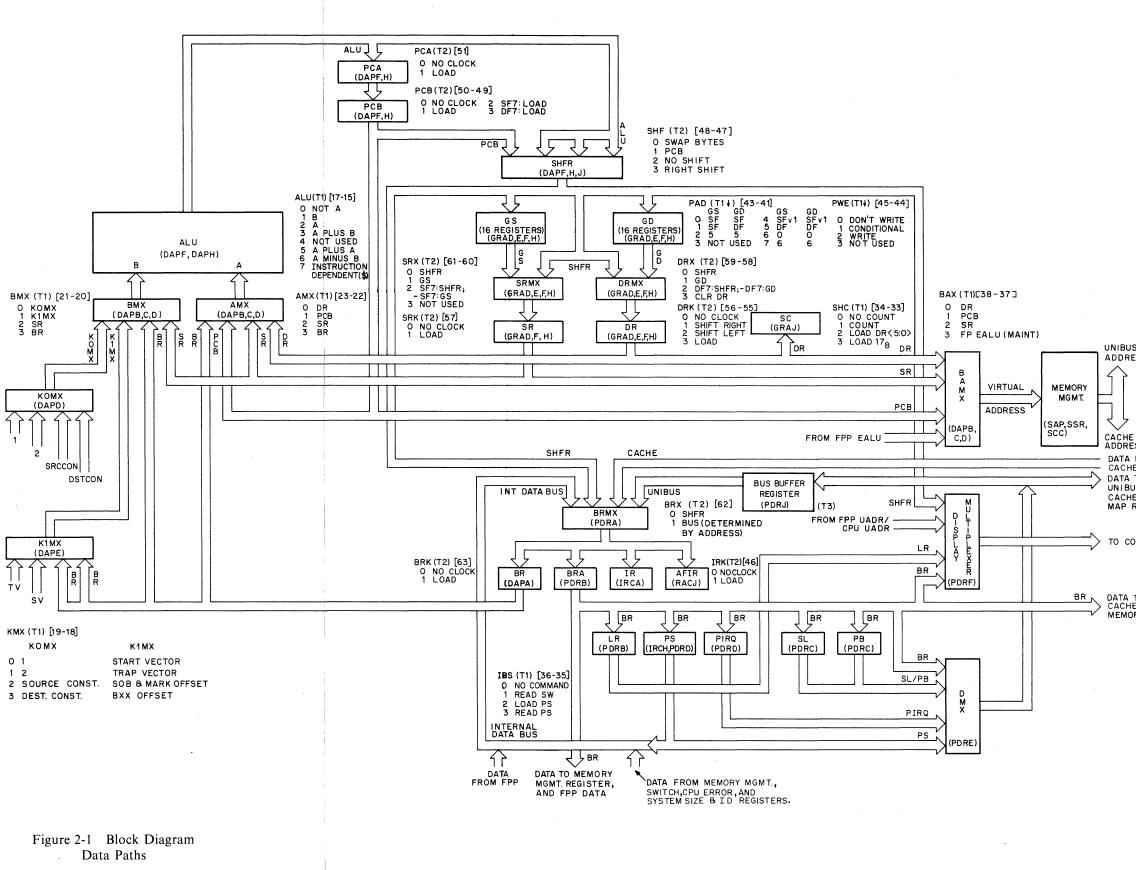

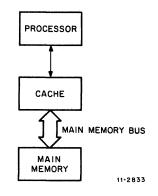

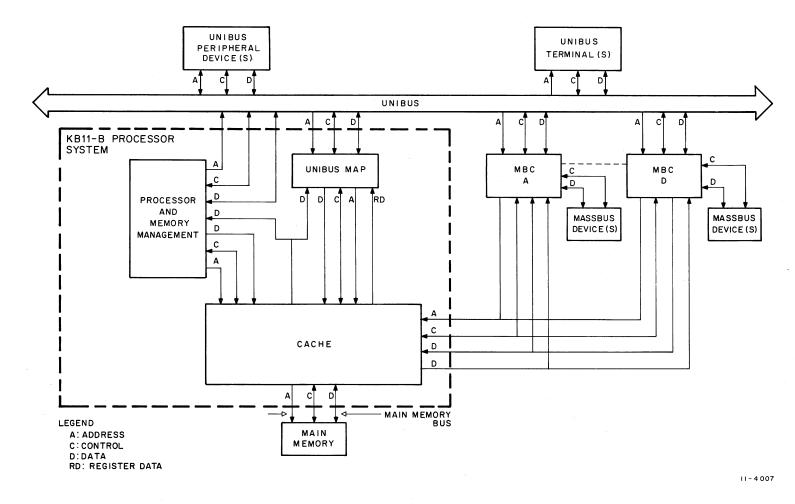

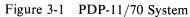

The PDP-11/70 is a medium scale, general-purpose computer. A block diagram of the computer is shown in Figure 1-1.

Figure 1-1 PDP-11/70 Block Diagram

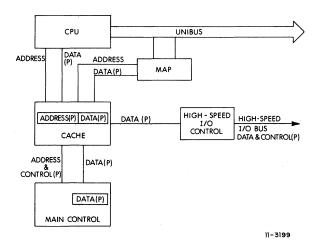

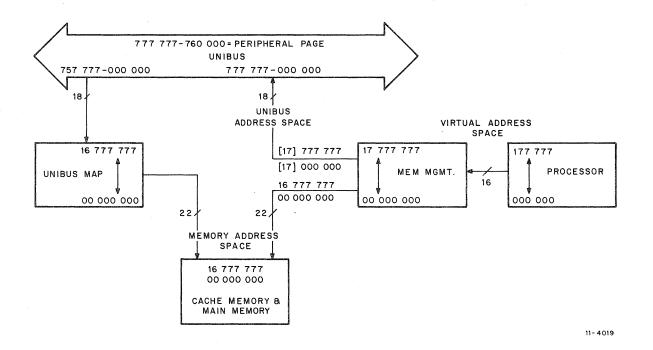

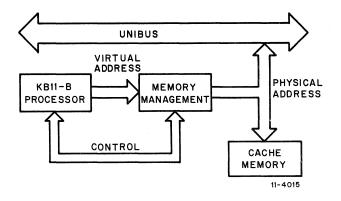

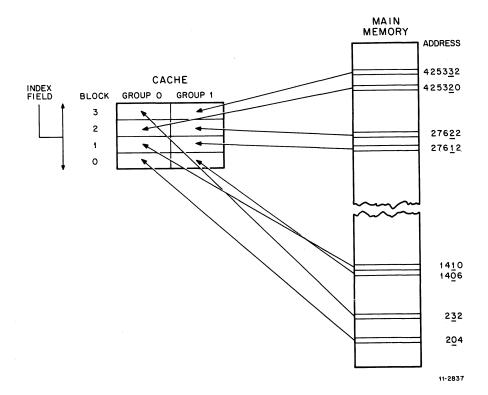

The KB11-B Processor performs all arithmetic and logical operations required in the system. Memory Management is standard with the basic computer, allowing expanded memory addressing, relocation, and protection. Also standard is the Unibus Map, which translates 18-bit Unibus addresses to 22-bit physical memory addresses. The Cache contains 2048 bytes of bipolar memory that buffer the data from Main (core) Memory. Main Memory is on its own high data rate bus. The processor has a direct connection to the Cache/Main Memory system for high-speed access.

The PDP-11/70 Console allows direct control of the computer system. It contains a power switch for the CPU. This switch may also be used as the master switch for the system. The Console is used for starting, stopping, resetting, and debugging. Lights and switches provide the facilities for monitoring operations, system control, and maintenance. Debugging and detailed tracing of operations can be accomplished by having the computer execute single instructions or single bus cycles. Contents of all locations can be examined, and data can be entered manually from the Console switches. Console operation and logic are described in Section III of this manual.

Also within the CPU assembly are pre-wired areas for an optional Floating Point Processor, and for up to four optional high-speed I/O controllers (RH70 Massbus Controllers). These controllers have direct connections through the Cache to Main Memory (using the Cache only for timing purposes).

The Unibus remains the primary control path in the 11/70 system. It is conceptually identical with previous PDP-11 systems; the memory in the system still appears to be on the Unibus to all Unibus devices. Control and status information to and from the high speed I/O controllers is transferred over the Unibus. This expanded internal implementation of the PDP-11 architecture has no effect on programming the PDP-11/70.

Three Unibus devices are standard on the PDP-11/70:

- 1. a KW11-L Line Time Clock

- 2. a DL11 Synchronous Serial Interface (an LA36 DECwriter II is also standard in the PDP-11/70)

3. a Unibus Terminator and Bootstrap Module.

Also standard are 128KB of parity core memory. Memory, in the PDP-11/70, is not on the Unibus, but on its own high-speed bus (refer to Paragraph 1.2).

#### 1.1.1 Processor

The Processor is the instruction execution section of the system. It implements the PDP-11/45 instruction set. It also acts as the arbitration unit for Unibus control by regulating bus requests and transferring control of the bus to the requesting device with the highest priority.

The Processor contains arithmetic and control logic for a wide range of operations. These include highspeed, fixed-point arithmetic with hardware multiply and divide, extensive test and branch operations, and other control operations.

The Processor is described in Section II of this manual.

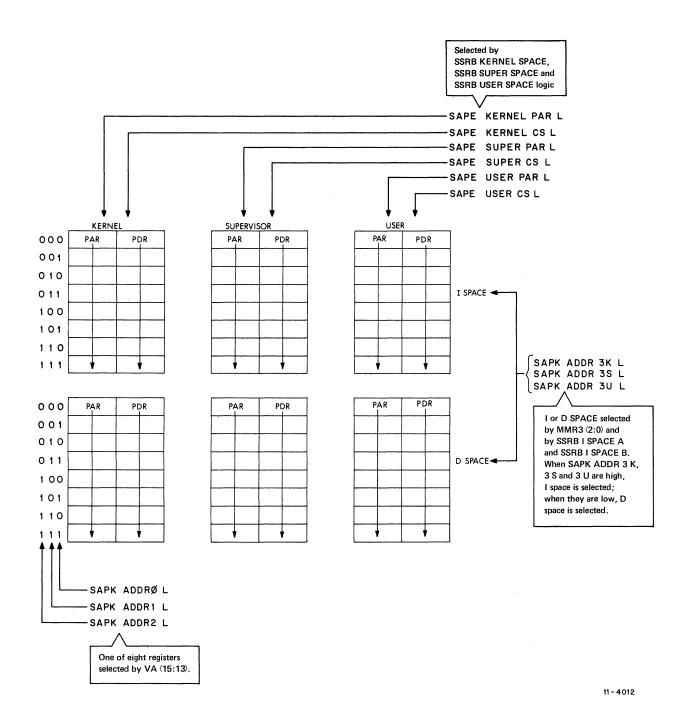

#### 1.1.2 Memory Management

Memory Management provides the hardware facilities necessary for address relocation and protection. It is designed to be a memory management facility for accessing all of physical memory and for multi-user, multi-programming systems where memory protection and relocation facilities are necessary.

In order to most effectively utilize the power and efficiency of the PDP-11/70 in medium and large scale systems, it is necessary to run several programs simultaneously. In such multi-programming environments, several user programs could be resident in memory at any given time. The task of the supervisory program would be to control the execution of the various user programs, to manage the allocation of memory and peripheral device resources, and to safeguard the integrity of the system as a whole by control of each user program.

In a multi-programming system, Memory Management provides the means for assigning memory pages to a user program and preventing that user from making any unauthorized access to these pages. Thus, a user can effectively be prevented from accidental or willful destruction of any other user program or of the system executive program. The basic characteristics of Memory Management are:

16 User mode memory pages

16 Supervisor mode memory pages

16 Kernel mode memory pages

8 pages in each mode for instructions

8 pages in each mode for data

Page lengths from 32 to 4096 words

Each page provided with full protection and relocation

Transparent operation

6 modes of memory access control

Memory access to 2 million words (4 million bytes)

Memory Management is described in Section IV of this manual.

#### 1.1.3 Unibus Map

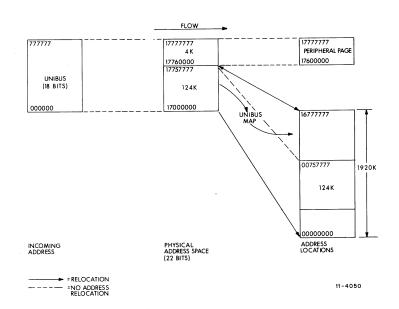

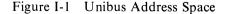

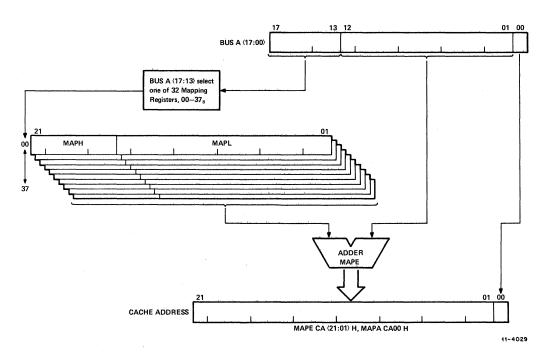

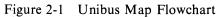

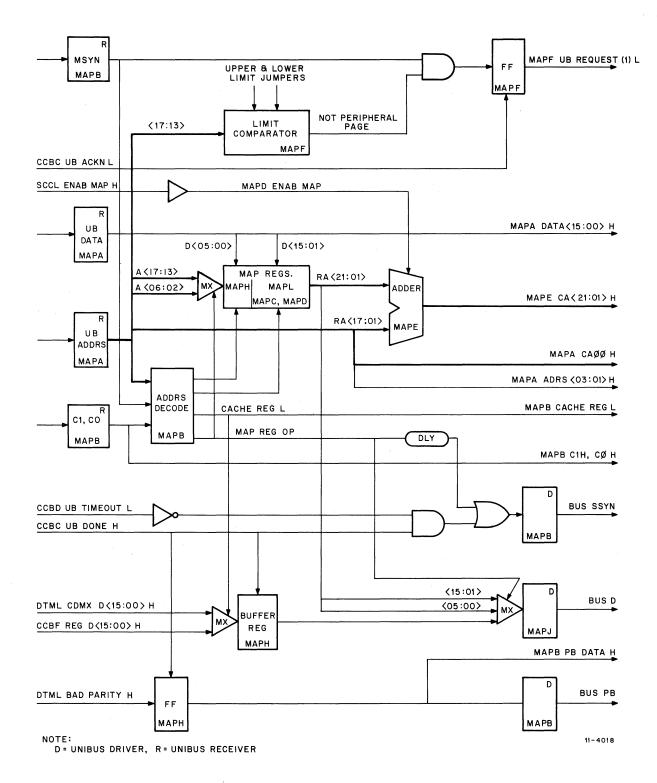

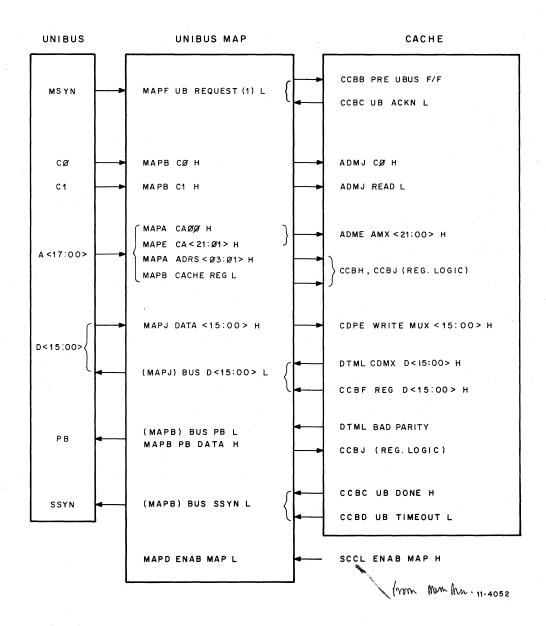

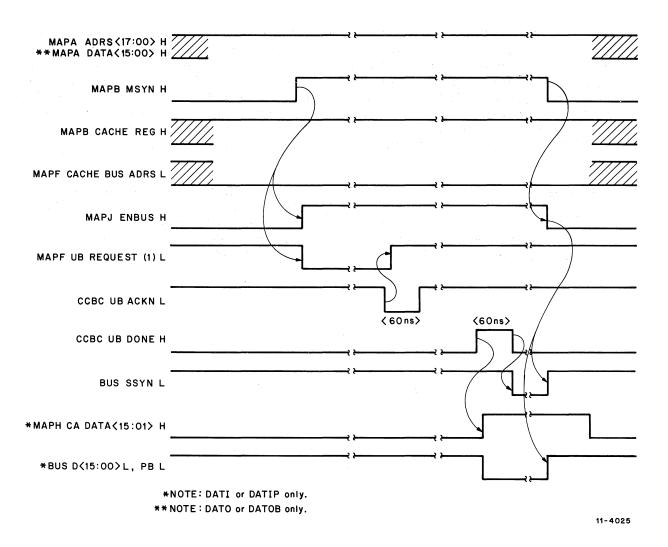

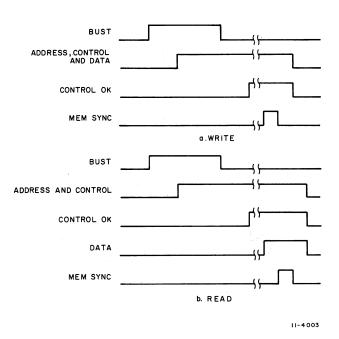

The Unibus Map is the interface to the Memory System (Cache and Main Memory) from the Unibus. It performs the address conversion that allows devices on the Unibus to communicate with physical memory by means of Non-Processor Requests (NPRs). Unibus addresses of 18 bits are converted to 22-bit physical addresses using relocation hardware. This relocation is enabled (or disabled) under program control.

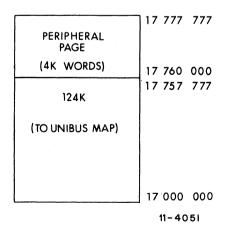

The top 4K word addresses of the 128K Unibus addresses are reserved for CPU and I/O device registers and is called the Peripherals Page. The lower 124K addresses are used by the Unibus Map to reference physical memory.

The Unibus Map is described in Section V of this manual.

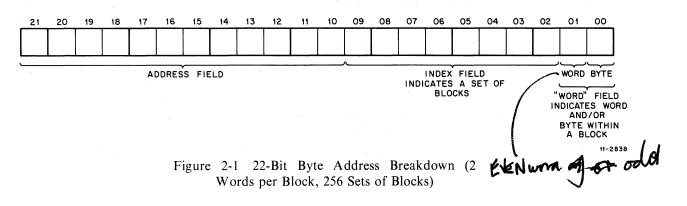

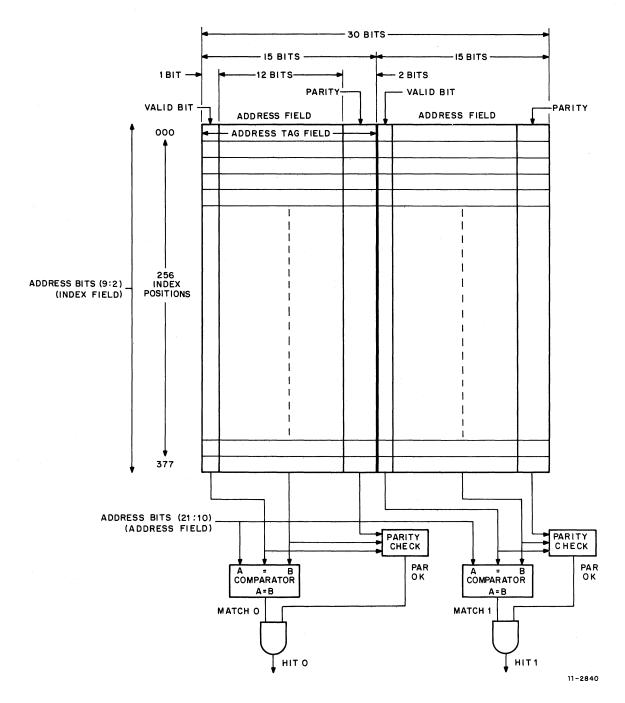

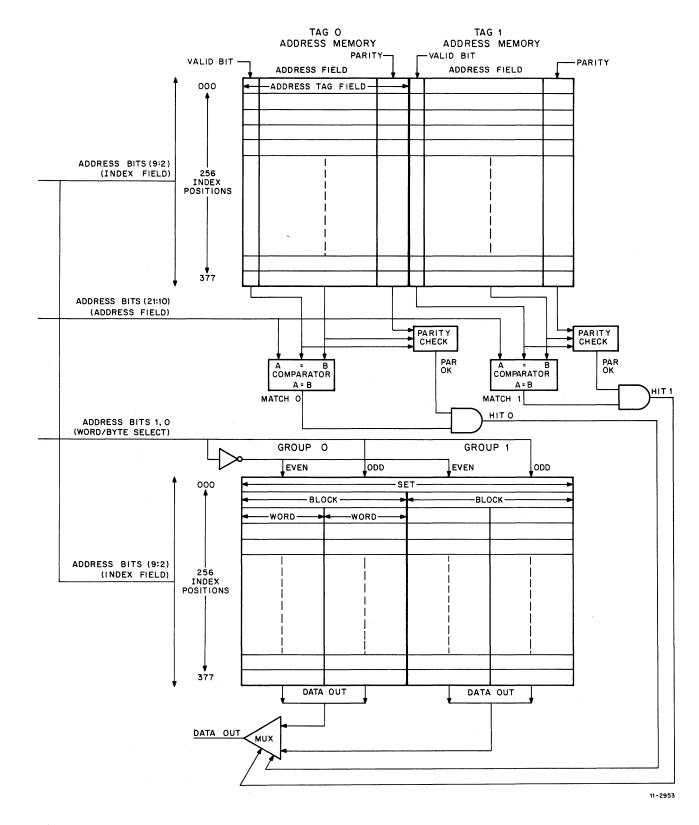

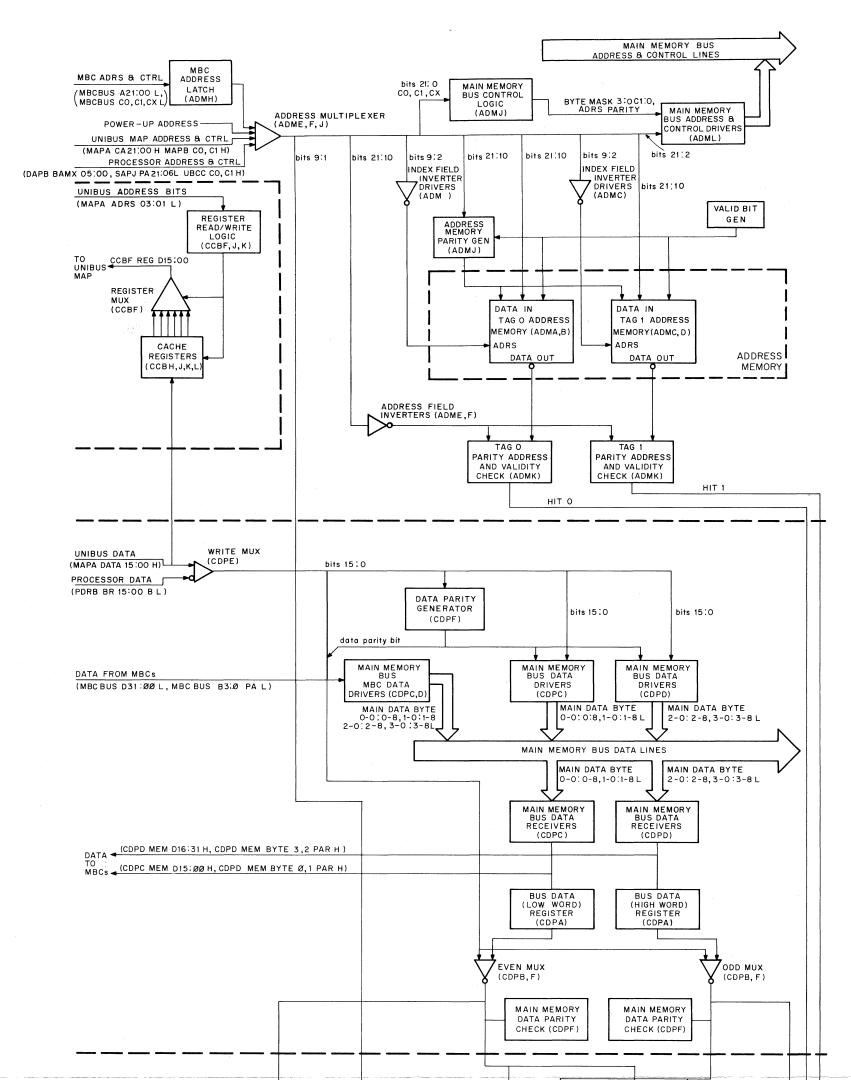

#### 1.1.4 Cache

The Cache is a high-speed memory that buffers words between the processor and Main Memory. The Cache is completely transparent to all programs; programs are treated as if there were one continuous bank of memory. Whenever a request is made from the Processor to fetch data from memory, the Cache does an address compare to see if that data is already in the Cache. If it is, it is fetched from there and no Main Memory read is required. If the data is not already in Cache memory, 4 bytes are fetched from Main Memory and stored in the Cache, with the requested word or byte being passed directly to the processor.

When a request is made from the Processor to write data into memory:

- 1. If it is stored in the Cache, it is written both to the Cache and to Main Memory, thus assuring that Main Memory is always updated immediately.

- 2. If it is not stored in the Cache, it is written only to Main Memory.

Unibus Map references to memory are executed in the same manner as processor references.

Because it stores 1024 words, and because programs tend to use localized sections of code and data, the Cache already contains the next needed word a very high percentage of the time, independently of the program.

The Cache is also the interface between the highspeed I/O controllers and Main Memory.

A detailed description of the Cache is contained in Section VI of this manual.

#### 1.1.5 Unibus

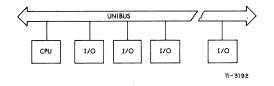

Most of the computer system components and peripherals connect to and communicate with each other on a bus known as the Unibus. Addresses, data, and control information are sent along the 56 lines of the bus. Refer to Figure 1-2.

The form of communication is the same for every device on the Unibus. Peripheral devices use the same set of signals when communicating with the processor, memory, or other peripheral devices. Each device, including memory locations, processor registers, and peripheral device registers, is assigned an address. Peripheral device registers may be manipulated as flexibly as memory by the central processor. All instructions that can be applied to data in core memory can be applied equally well to data in peripheral device registers.

Processor Unibus operations are described in Section II, Chapters 5 and 6 of this manual. Cache Unibus operations are transacted through the Unibus Map (Section V).

#### 1.1.6 Optional Equipment

#### **Floating Point Processor**

The Floating Point Processor fits into prewired slots in the Central Processor backplane. It provides a supplemental instruction set for performing single- and double-precision floating point arithmetic operations and floating-integer conversion in parallel with the CPU. The Floating Point Processor provides both speed and accuracy in arithmetic computations. It provides 7 decimal digit accuracy in single word calculations and 17 decimal digit accuracy in double calculations.

Floating point calculations take place in the FPP's six 64-bit accumulators. The 46 floating point instructions include hardware conversion from singleor double-precision floating point to single- or double-precision integers. Refer to the *Floating Point Processor Manual* for a detailed description.

#### High-Speed Mass Storage

Up to four high-speed I/O controllers can be plugged into the KB11-B backplane. A dedicated interface (wired on the backplane) connects these controllers to the memory. A separate bus (Massbus) connects the controllers to high-speed devices. Present DIGITAL devices that utilize this bus structure are the RP04, RS04, RS03, and TU16. The RP04 is a moving head disk pack drive with capacity for 88 million bytes and a transfer rate of 1.25 microseconds per byte. The RS04 is a fixed head disk with a capacity of 1024K bytes and a transfer rate of 1 microsecond per byte (1.2 microseconds at 50 Hz). The RS03 is a fixed head disk, 512K bytes, 2 microseconds per byte. The TU16 is an industry standard 1600 bpi tape unit. Refer to the following manuals for detailed descriptions of these high-speed devices:

RWS04/RWS03 Fixed Head Disk Subsystem Maintenance Manual

RWP04 Moving Head Disk Subsystem Maintenance Manual

TWU16 Magnetic Tape Subsystem Maintenance Manual

#### **1.2 MEMORY SYSTEM**

#### **1.2.1** Representation and Storage

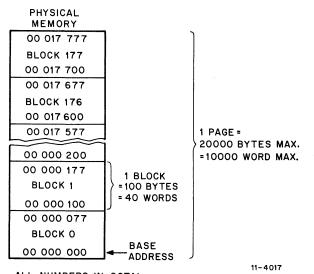

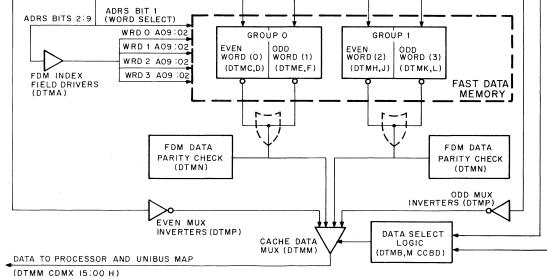

The PDP-11/70 is a 16-bit machine. The data is stored in Main Memory in blocks, each of which consists of two 16-bit words. Thus, the PDP-11 instruction set and the addressing modes are identical to other PDP-11s, but data storage is implemented in a 32-bit configuration. This is transparent to the program and to the processor logic.

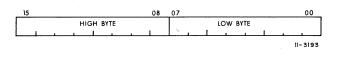

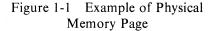

The PDP-11 data word consists of two 8-bit bytes, as shown in Figure 1-3. The program addresses either a single byte, when it uses a byte instruction, or a 16-bit word, when it uses a word instruction.

Figure 1-3 High and Low Byte

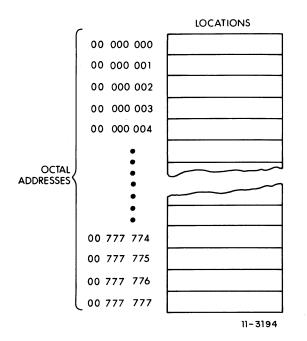

From the point of view of the program, memory can be viewed as a series of locations, with a number (address) assigned to each location. Thus, a 131,072-byte PDP-11 memory could be represented as in Figure 1-4.

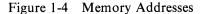

Because PDP-11 memories are designed to accommodate both 16-bit words and 8-bit bytes, the total number of addresses does not correspond to the number of words. A 64K-word memory can contain 128K bytes and consist of 777 777<sub>8</sub> byte locations. Words always start at even-numbered locations.

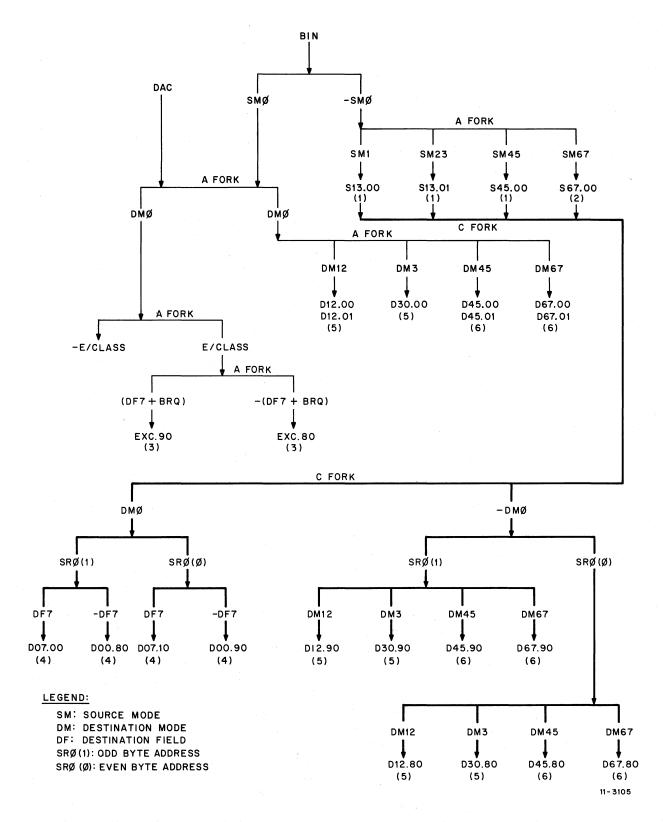

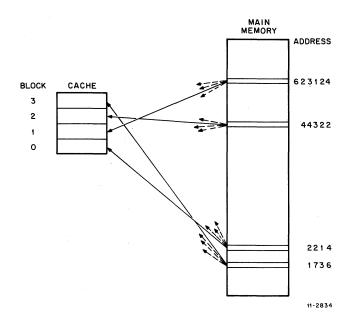

Low bytes are stored at even-numbered memory locations and high bytes at odd-numbered memory locations. Thus it is convenient, from the point of view of the program, to represent the PDP-11 memory as shown in Figure 1-5. Main Memory stores data in blocks. A block consists of two 16-bit words (plus 4 parity bits). Figure 1-6 shows how the data for the same memory shown in Figure 1-5 is stored in Main Memory. Block boundaries are located on program addresses whose low-order octal digit is either 0 or 4.

Main Memory addresses are block addresses. The processor and the Unibus use word addresses and the Cache translates these addresses to block addresses.

The Cache, which is the interface to Main Memory for the processor, the Unibus and the high-speed I/O controllers, reads and writes Main Memory as listed below for each of these units:

#### High-Speed I/O Controllers

- 1. Read: double word only

- 2. Write: double word, single word, or byte.

The controllers listed in Paragraph 1.1.6 do not implement byte writes.

Figure 1-5 Word and Byte Addresses

BLOCK

|           | WORD 0                                   |                                       | WORD 1                                |            |

|-----------|------------------------------------------|---------------------------------------|---------------------------------------|------------|

| 1         | BYTE O                                   | BYTE 1                                | BYTE 2                                | BYTE 3     |

| 00 000 0  | 00 000 000                               | 00 000 001                            | 00 000 002                            | 00 000 003 |

| 00 000 0  | 00 000 004                               | 00 000 005                            | 00 000 006                            | 00 000 007 |

| 00 000 0  |                                          | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |            |

|           | <u> </u>                                 |                                       |                                       |            |

| 7         |                                          |                                       |                                       |            |

| 00 777 7  | n an |                                       |                                       |            |

| 00 777 70 | 00 777 764                               | 00 777 765                            | 00 777 766                            | 00 777 767 |

| 00 777 7  | 00 777 770                               | 00 777 771                            | 00 777 772                            | 00 777 773 |

| 00 777 7  | 00 777 774                               | 00 777 775                            | 00 777 776                            | 00 777 777 |

Figure 1-6 Main Memory Addresses

#### Processor or Unibus

- 1. Read: double word, but only Word 0 or Word 1 are transmitted to processor or Unibus

- 2. Write: single word (Word 0 or Word 1) or single byte (one of bytes 0, 1, 2, or 3).

#### 1.2.2 Address Space

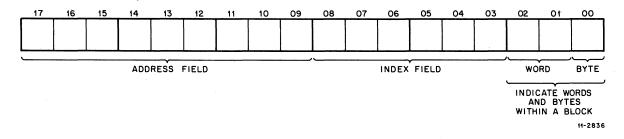

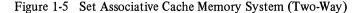

The PDP-11/70 uses 22 bits for addressing physical memory. This represents a total of  $2^{22}$  (over 4 million) byte locations.

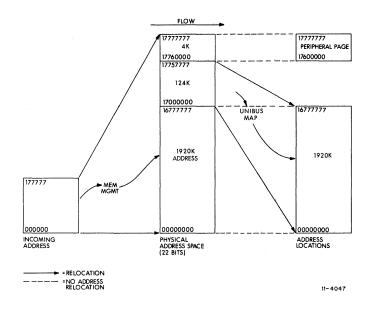

Three separate address spaces are used with the PDP-11/70. Main memory uses 22 bits, the Unibus uses an 18-bit address, and the computer program uses a 16-bit virtual address. This information is summarized below:

| 16 bits | program virtual space | $2^{16} = 64 \text{K}$ bytes  |

|---------|-----------------------|-------------------------------|

| 18 bits | Unibus space          | $2^{18} = 256 \text{K}$ bytes |

| 22 bits | physical memory space | 4 million bytes               |

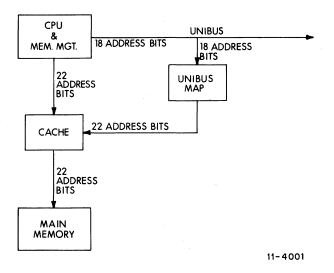

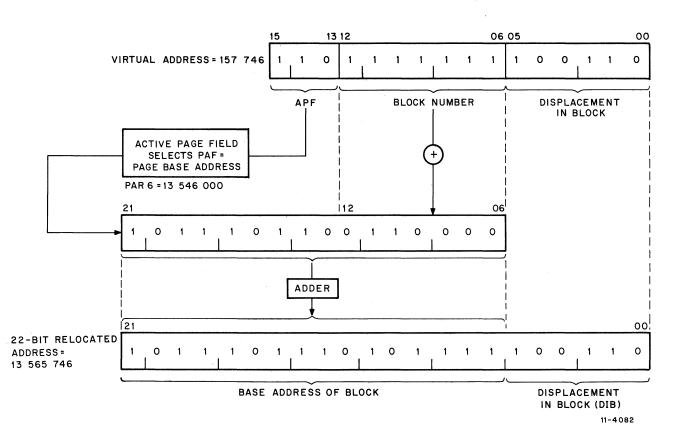

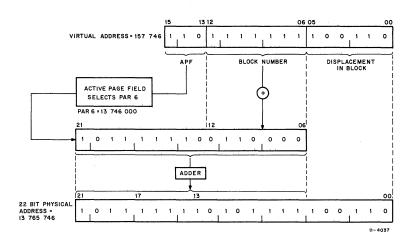

Refer to Figure 1-7. Memory Management generates the physical address output for the processor. This address is an 18-bit address in the case of a Unibus reference and a 22-bit address in the case of a memory reference. The Unibus Map converts 18bit Unibus addresses to 22-bit Cache addresses.

#### Processor Addresses

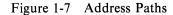

See Figure 1-8. Of the over 2 million 16-bit word locations possible with the 22-bit physical address, the top 128K are used to reference the Unibus rather than physical memory. Maximum physical memory is therefore  $2^{22} - 2^{18}$  bytes, or a total of 1,966,080 words. The system size boundary is the highest address available with the amount of memory included in the system. If the CPU address is between 00 000 000 and the system size boundary, an attempt is made to reference physical memory. Memory addresses between the system size boundary and 16 777 777 are known as Non-Existent Memory (NEXM); any attempt to access these locations is aborted. If the address is in the top 128K, 17 000 000 - 17 777 777, the lower 18 bits of the address are placed on the Unibus.

Figure 1-8 Physical Address Space

#### 1.2.3 Mapping

Mapping is the process of converting the virtual address generated by the program to a physical memory address or to a Unibus address, or the process of converting a Unibus address to a physical memory address.

The virtual address is mapped by Memory Management; the Unibus address is mapped by the Unibus Map. Neither of these increases memory access time.

Memory Management and the Unibus Map are separate units and one may be enabled independently of each other. They are both part of the KB11-B and are included in all PDP-11/70 systems.

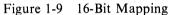

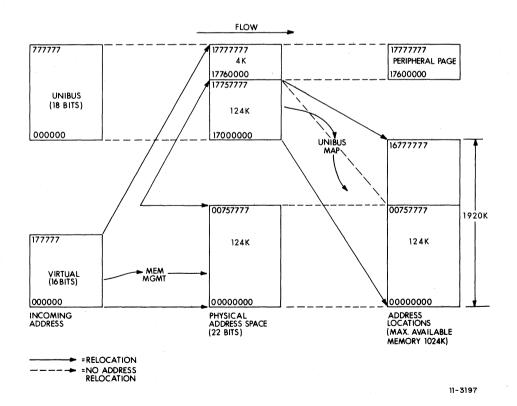

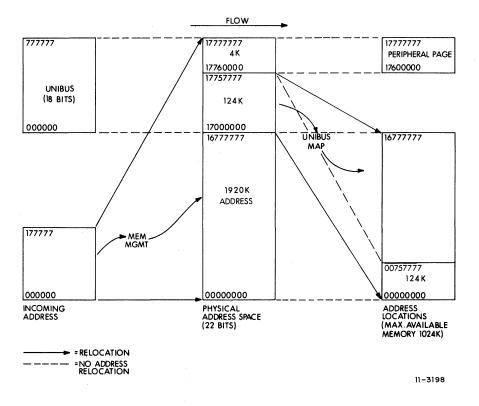

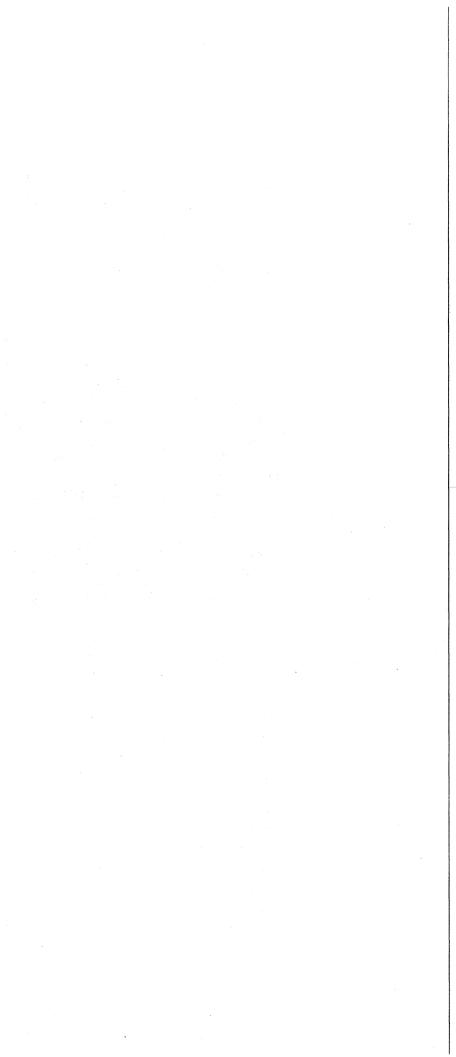

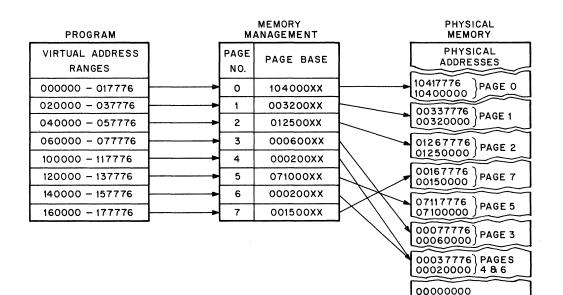

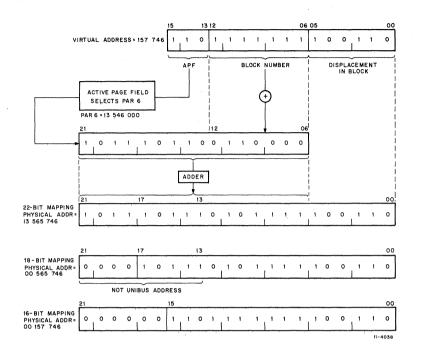

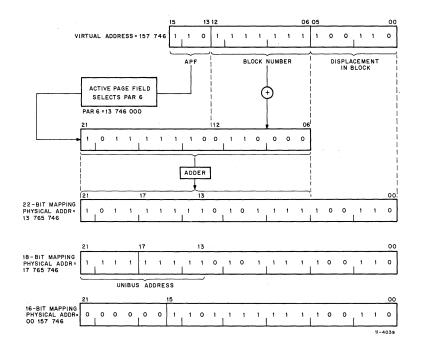

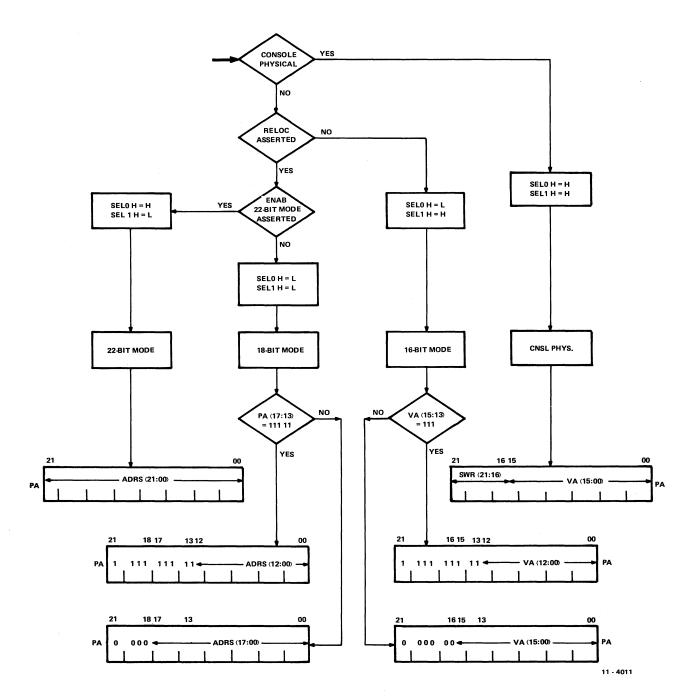

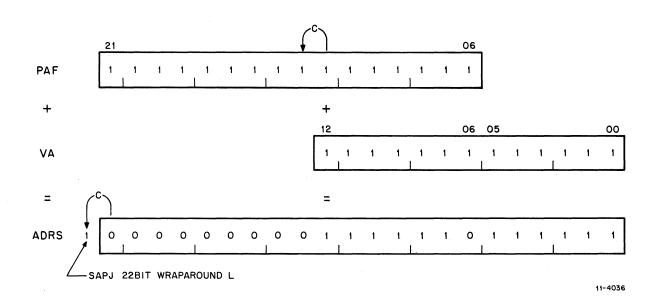

Refer to Figures 1-9 through 1-11.

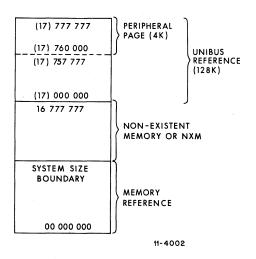

1. Mapping of processor addresses is performed in one of three possible ways by Memory Management:

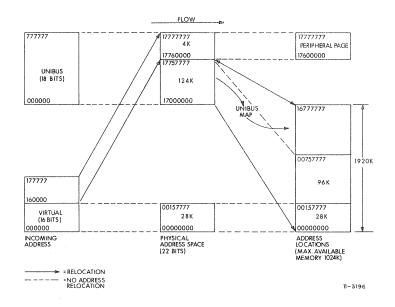

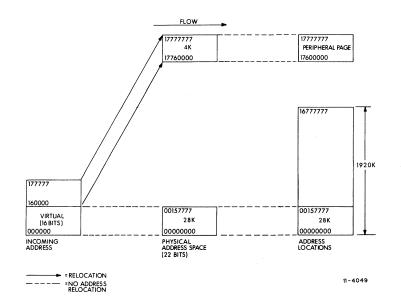

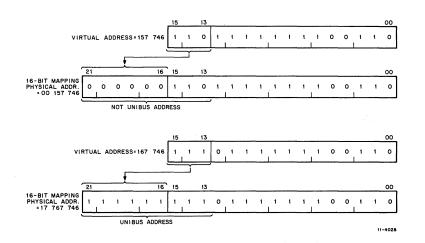

#### 16-BIT MAPPING

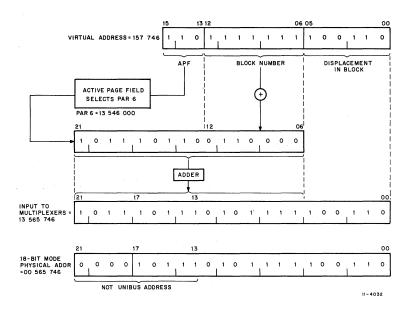

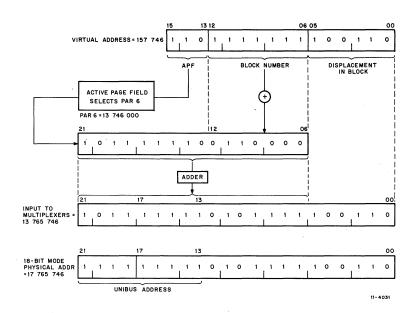

There is fixed mapping from virtual to physical addresses. The lowest 28K virtual addresses are treated as corresponding to the same physical addresses. The top 4K addresses cause Unibus cycles to addresses 17 760 000 – 17 777 777. Refer to Figure 1-9. 16-bit mapping is enabled after. Power Up, Console Start, or the RESET instruction.

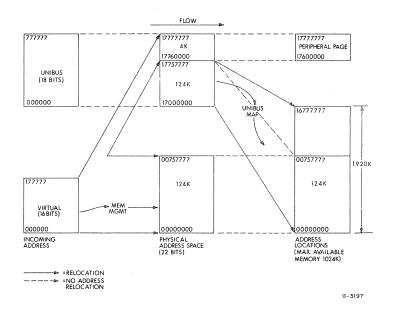

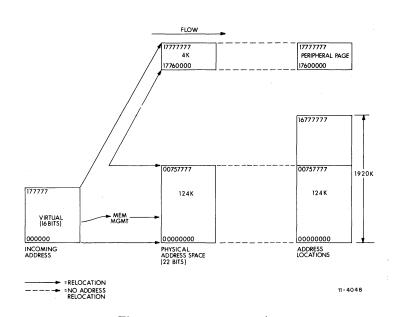

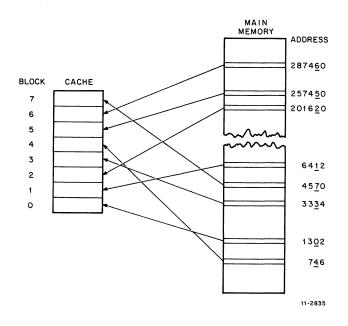

#### 18-BIT MAPPING

32K virtual addresses for each of the three modes (Kernel, Supervisor, User) are mapped into 128K of physical address space. The lowest 124K addresses reference physical memory. The top 4K addresses cause Unibus cycles to addresses 17 760 000 – 17 777 777. Refer to Figure 1-10.

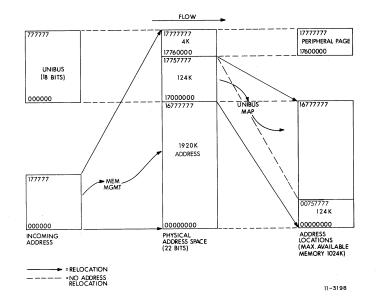

#### 22-BIT MAPPING

This mode produces 22-bit addresses for accessing all of physical memory. The top 128K addresses cause Unibus cycles to addresses 17 000 000 – 17 777 777. Refer to Figure 1-11.

2. Mapping of Unibus addresses is performed by the Unibus Map.

#### UNIBUS MAP NOT ENABLED

When the Unibus Map is not enabled, Unibus addresses  $000\ 000 - 757\ 777$  access memory locations  $00\ 000\ 000 - 00$ 757 777, i.e., they are not modified except for the insertion of leading zeroes.

#### UNIBUS MAP ENABLED

When the Unibus Map is enabled, Unibus addresses 000 000 – 757 777 are relocated and a Unibus device may access any location in physical memory.

Figure 1-10 18-Bit Mapping

Figure 1-11 22-Bit Mapping

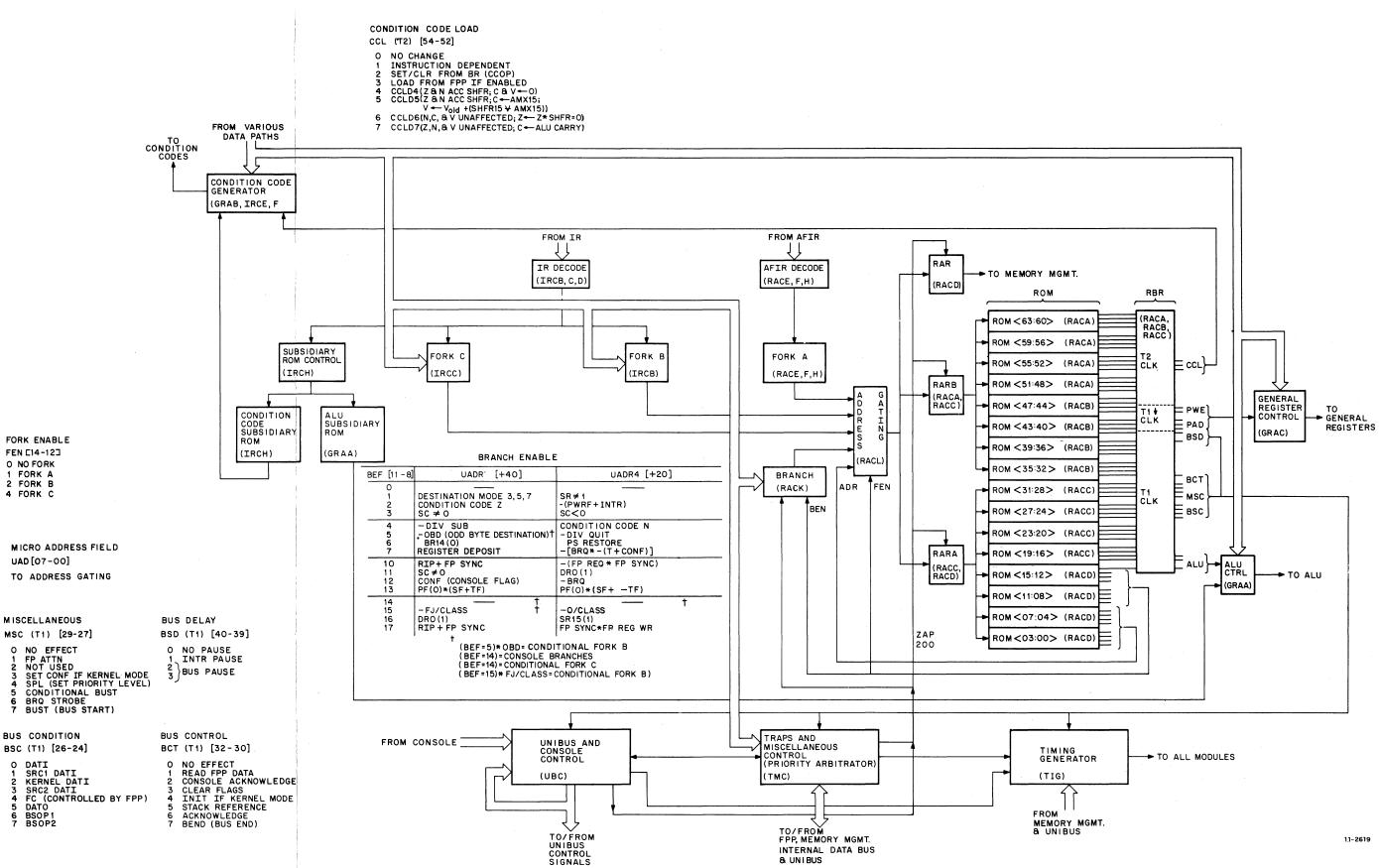

#### 1.2.4 Parity

This paragraph provides general information on parity checking in the PDP-11/70 system. A detailed description of this subject is provided in Section VI of this manual (Cache) and in the Memory Manual.

#### System Reliability

Parity is used extensively in the PDP-11/70 to ensure the integrity of the data and thus to enhance the reliability of the system. All memory (Cache and Main Memory) has byte parity. Parity is generated and checked on all transfers between Main Memory and Cache, and between Cache and the CPU. It is checked between the high-speed mass storage devices and their controllers, and again between the controllers and core memory. A software routine can be used to log the occurrence of parity errors, to handle recovery from errors, and to provide information on system reliability and performance.

#### Parity in the System

Main Memory stores one parity bit for each 8-bit byte, (refer to Figure 1-12). The Cache also stores

byte parity for data, and in addition it stores two parity bits for the address information (tag storage) associated with each two-word block of data.

The bus between Main Memory and the Cache contains parity on the data lines and on the address and control lines. The high-speed I/O controllers check and generate parity for data transfers to Main Memory, and they have the capability of handling address errors that are flagged by the control in the Cache memory. Refer to Section VI, Chapter 3 for a detailed description of the PDP-11/70 parity system.

#### System Handling of Parity Errors

The design of the PDP-11/70 allows recovery from parity errors. It also allows operation in a degraded mode if a section of the memory system is not operating properly. This type of operation is possible under program control by using the control registers.

If part or all of the Cache memory is malfunctioning, it is possible to bypass half or all of the Cache. Misses can be forced within the Cache, such that all read data is brought from Main Memory. Operation will be slower, but the system will yield correct results. If part of Main Memory is not working, Memory Management can be used to map around it. If data found in the Cache does not have correct parity, the memory system automatically tries the copy in Main Memory, to allow program execution to proceed. The correct data from Main Memory automatically replaces the data in the Cache which caused the parity error. Therefore, if the error was caused by transitory conditions, it will not occur again.

#### **Aborts and Traps**

One of two actions can take place after detection of a parity error: (1) The cycle can be aborted. The computer then transfers control through the vector at location 114 to an error handling routine. (2) The instruction is completed, but then the computer traps (also through location 114). In the first case, it was not possible to complete the cycle; in the second case it was. This second type of parity error usually (but not always) causes the trap before the next instruction is fetched.

### CHAPTER 2 CONCEPTS

This chapter introduces several concepts that are useful for the understanding of the KB11-B Processor and the PDP-11/70 system. The first two of these concepts, Microprogramming (2.1) and Parallel Operation or Pipelining (2.2), should be well understood before reading any further. The other two paragraphs, Virtual Machines (2.3) and Reentrant and Recursive Programming (2.4), discuss system concepts that may be easier to understand after a working knowledge of the PDP-11/70 has been acquired.

#### 2.1 MICROPROGRAMMING

The KB11-B Processor uses a microprogram control section which reduces the amount of combinational logic in the processor. This paragraph introduces the concept of microprogramming by first describing a digital computer, then dividing the computer into various parts, and finally, describing how some of these parts differ for a microprogrammed processor.

#### **Digital Computer Description**

Although a computer can effect complicated changes to the data it receives, it must do so by combining a large number of simple changes in different ways. The part of the digital computer that actually operates on the data is the processor. A processor is made up of logical elements; some of these elements can store data, others can do such simple operations as complementing a data operand, combining two operands by addition or by ANDing, or reading a data operand from some other part of the computer. These simple operations can be combined into functional groups; such a group is called an instruction, and it includes operations that read data, operations that combine, change, or simply move the data, and operations that dispose of the data. Instructions can

be further combined into programs, which use the combined instructions to construct even more complex operations.

The logical elements of a processor can only perform a small number of operations at one time. Therefore, to combine operations into an instruction, the instruction is divided into a series of operations (or groups of operations that can be performed simultaneously). The processor does each part of the series in order. One way to describe how the processor executes an instruction is to call each operation (or group of operations) a machine state. An instruction then becomes a sequence of machine states which the processor enters in a specific order.

The processor can be completely described in terms of machine states by listing all the machine states in which the processor can perform (i.e., all the different operations or groups of operations that it can perform) and all the sequences in which these machine states can occur. The sequence of machine states is determined by the current state of the computer; this includes such information as the instruction being executed, the values of the data being operated on, and the results of previous instructions.

In terms of the machine state description, the processor can be divided into two parts. The first part, called the data section, includes the logic elements that perform the operations which make up a machine state. The second part, called the control section, includes all the logic that determines which operations are to be performed and what the next machine state should be. The data section and control section are discussed in the following paragraphs. The data section in the KB11-B is usually referred to as the *Data Paths* and is described in Section II, Chapter 2. The control section is described in Section II, Chapter 1, Instruction Decode and Microprogram Control.

#### The Data Section

During each machine state, the data section performs operations selected by signals from the control section. The data section provides inputs to the control section which help to determine the next machine state; the data section also exchanges data with other devices external to the processor.

The data section can be divided into three functional sections; each section is discussed in one of the following paragraphs.

#### The Data Storage Section

For the processor to combine data operands it must be able to store data internally, while simultaneously reading additional data. Often, a processor stores information about the instruction being executed, about the program from which the instruction was taken, and about the location of the data being operated on, as well as a number of data operands. When the processor must select some of the internally-stored data, or store new data, the control section provides control signals which cause the appropriate action within the data storage section.

#### The Data Manipulation Section

This section includes the various logic elements that actually change data. Many of these elements are controlled by signals from the control section, which select the particular operation to be performed. Data manipulation is performed on data being transferred between the processor and the rest of the system, and on data that remains within the processor. In some cases, the data that remains within the processor is used to control the processor by providing inputs to the sensing section of the processor control.

#### The Data Routing Section

The interconnections between the logic elements in the data storage section and the elements in the data manipulation section are not fixed; they are set up as required in each machine state. The control section generates signals that cause the logic elements in the data routing section to form the appropriate interconnections within the processor, and between the data interface and the data storage and manipulation sections.

#### The Control Section

The control section of a processor receives from the data section, inputs which are used by the sensing logic to help select the next machine state. The control section also generates control signals to all parts of the data section and communicates with other parts of the computer system through control signals. The following paragraphs describe the three parts of the control section.

#### The Sequence Control Section

The primary control of the processor is the selection of the sequence of machine states to be performed. This is done by the sequence control section which selects the next machine state on the basis of:

- 1. the current machine state

- 2. inputs from the data section (such as the instruction type or the data values)

- 3. information about external events.

The sequence control section maintains information about the current machine state, and receives information from the data section and the external environment through the sensing section.

#### The Function Generator

In each machine state, the data section performs operations selected by signals from the control section of the processor. The function generator produces these control signals on the basis of the current machine state and also on the basis of inputs from the sensing section, such as information on the instruction type.

#### The Sensing Logic

In general, the sequence control section requires in puts that select one of a limited number of machine states to follow the current state.

#### The Control Section in the KB11-B

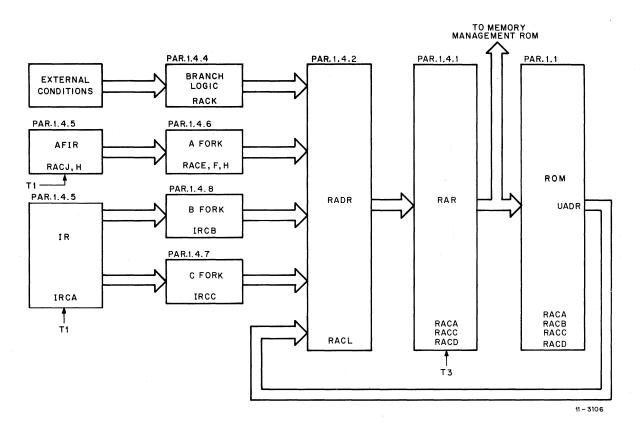

The function generator comprises the microprogram Read Only Memory (ROM), its output buffer, and several logic elements that generate control signals based on sensed inputs (notably through the subsidiary ROMs). The sequence control comprises the microprogram address generation logic. The sensing section includes the various logical elements that receive inputs from the data section, especially the condition-code generator, the subsidiary ROMs, and the branch logic.

#### Microprogramming in the Control Section Implementation

This paragraph describes two methods of implementing the control section of a processor. The first method, which is called the *conventional* method for the purposes of this discussion, uses combinational networks, with many inputs combined in varying ways to produce each output. The second method, which is called *microprogramming*, replaces most of the combinational networks with an array structure. The array requires a small number (approximately 10) of inputs to select the output states for a large number (approximately 100) of signals. Because the array is a regular structure, it is simpler to construct and understand, and less expensive.

#### **Conventional Implementation**

In a conventional processor, each control signal is the output of a combinational network that detects all the machine states (and other conditions) for which the signal should be asserted. The machine state is represented by the contents of a number of storage elements (such as flip-flops), which are loaded from signals that are, in turn, the outputs of combinational networks. The inputs to these networks include:

- 1. the current machine state

- 2. sensed conditions within the Processor

- 3. sensed external conditions.

The number of logical elements in the processor is often reduced by sharing the outputs of networks which generate intermediate signals needed in the generation of several control signals, or even in the generation of control signals and machine states. Unfortunately, while this reduces the size of the processor, it increases the complexity and difficulty of understanding the device because it is no longer obvious what conditions cause each signal. In additon, the distinction between the sequence control and the function generator is blurred, which makes it more difficult to determine whether improper operation is caused by a bad machine state sequence or, more simply, by the wrong control signals within an otherwise correct machine state.

#### Microprogrammed Implementation

The microprogrammed implementation is based on the following observation. Each control signal is completely defined if its value is known for every machine state. The function generator section can therefore be implemented as a storage device: the storage is divided into words, with each word containing a bit for every control signal; there is one word for each machine state. During each machine state, the contents of the corresponding word in the storage element are transmitted on the control lines. For most control signals, the output of the storage unit is the control signal; no additional logic is required.

The two tasks of the sequence control section are to select the next machine state, and to provide information about the current machine state to the function generator. The only information that the function generator in a microprogrammed processor requires is which word to use as control signals. Therefore, the sequence control simply provides an address that selects the correct word. The sequence control must also select the address of the next word to determine the machine state sequence. Because the next machine state is determined in part by the current machine state, information is stored in the microprogram that helps to select the next state; the microprogram word contains the control signal values and the address and sensing control information required by the microprogram address generation logic (i.e., by the sequence control).

In a microprogrammed control like the one described above, the two major portions of the control section have been simplified to regular logical structures. The function generator is entirely separate from the sequence control, so it is easy to isolate malfunctions to the microprogram storage or to the address generator. In addition, the sensing logic is simplified, because each sensed condition is reduced to a single signal and the sensing logic selects the appropriate signals for the current machine state, based on signals output from the microprogram storage. To summarize this discussion, a microprogrammed processor has a simpler, more regular, more easily repaired control structure, based on the generation of control signals from stored information, and the selection of each machine state, based on information stored in the current machine state, and on information from a simplified sensing section.

#### **2.2 PARALLEL OPERATION (PIPELINING)**

In a digital computer system, the processor is usually the fastest part of the system. In order to achieve the maximum speed of operation, all parts of the processor should be used as much as possible. To prevent the processor from wasting time waiting for other parts of the system, the processor must make use of the external data transfer interface as much as possible. Because any one operation that the processor performs uses only part of the processor's available resources, the two considerations above require the processor to perform several operations in parallel.

In general, the sequence of operations required for each instruction uses various parts of the processor at different times. Some parts of the processor, such as the program counter, are used only during the early parts of the instruction; others, like the shift counter, are used only during later parts of the instruction. The processor can be fully utilized only if different parts of the processor can be used for parts of different instructions during the same machine state.

When the processor works on the early part of an instruction at the same time that it completes the previous instruction, this form of parallel operation is called *pipelining*. The processor attempts to make continuous use of the external data interface by fetching each word addressed by the Program Counter (PC) in succession (incrementing the PC during each transfer), on the assumption that the next word required will be the one following the current instruction. In the pipelining analogy, the processor attempts to fill a pipe, corresponding to the different parts of the processor used successively by each instruction, with a series of instructions.

The current instruction often requires some other words from the external storage. At times, the next instruction does not follow the current instruction because the PC has been explicitly changed by the current instruction. When either of these two conditions occurs, the processor must stop the data transfer begun after the instruction fetch and begin a data transfer with a different address. In the pipeline analogy, this is a break in the smooth flow of instructions through the pipe; some time is lost before the pipe drains (the current instruction is completed) and can be refilled (a new instruction fetched and a transfer begun to read the word following that instruction). A second form of parallel operation occurs in the KB11-B to further improve the utilization of the processor. Because the processor includes several types of data storage and data manipulation elements, with different interconnections, several data transfers can take place within the processor simultaneously. As an example, during the same machine state that completes an external data transfer, the processor can read a general register into a temporary storage register, and perform an addition that adds a constant to the program counter.

The use of parallel operations within an instruction reduces the number of machine states (and therefore the total time) required to execute each instruction; the use of pipelining further reduces the number of machine states required to execute a program by effectively eliminating the elapsed time between many external data transfers.

#### 2.3 VIRTUAL MACHINES

The processor executes instructions and operates on data, both of which are stored in memory, and it responds to various asynchronous events.

The response to an interrupt or trap is not entirely designed into the processor. Instead, the response is controlled by a series of instructions (a program) which is selected by a simpler hardware response when the asynchronous event is detected. Often, a number of programs are required to respond to a number of events, and the scheduling, coordination, and interaction of these programs is one of the most important (and difficult) parts of programming a computer system.

In many applications, the user programs that are written for the system are treated as though they are interrupt response programs. This is done to simplify the scheduling, to allow each user program to operate with a terminal (some form of character I/O device), and to allow several user programs to operate at once. By running several programs at once, the processor can be utilized more fully than is generally possible with only one user program, which would often be waiting while devices other than the processor completed data transfer operations. With several programs to be run, the processor can be switched among the programs so that those ready to run have the use of the processor while others are waiting. The use of the processor for several programs at the same time is called multiprogramming.

Running programs in a multiprogrammed system presents several difficulties. Each program can be run at arbitrary times, but all the programs must be capable of running together, without conflict. A failure in one program must not be allowed to affect other programs. Each program must be able to use all features of the system in a simple, easily-learned manner, preferably in such a way that the program does not need to be modified to run in a different hardware configuration.

These difficulties are overcome by providing each program with a virtual machine. The programmer writes his program as though it is to run by itself; the program uses any system resources (such as memory or peripheral devices), and the system provides the services necessary to support the program and coordinate it with other programs in operation. The physical hardware in the system is combined with a control, or executive program, to simulate a more powerful hardware machine; it is for this more powerful, but abstract, machine that the programs are written.

Based on this discussion, the hardware machine and the executive program must combine to fulfill the following four major objectives of the virtual machine:

- 1. Mapping The virtual machine of the program currently in operation must be assigned to some part of the hardware machine.

- 2. Resource management The scheduling of programs, and the allocation of parts of the hardware machine, must be performed by the executive program.

- 3. Communication The virtual machine must be able to request services from the executive program, and the executive program must be able to transfer data back and forth with the user programs.

- 4. Protection The system that supports the virtual machine, and all other virtual machines, must be protected from failures in any one virtual machine.

Each of these subjects is discussed in one of the following paragraphs.

#### Mapping

Each time a program is run (or, if the multiprogramming system is running several programs in a round-robin manner, each time a program resumes operation), it has some of the system dardware allocated to it. This generally includes some part of the memory to contain the instructions and data required by the program, some of the processor's registers, a hardware stack (which is actually an area in the memory and a pointer to that area in a processor register), possibly some peripheral devices, and perhaps a fixed amount of the processor's time. All of thse allocations must be made in such a way that the hardware machine can then execute the user program with a minimum of extra operations; i.e., so that the execution of the user program requires as few additional memory cycles, or additional machine cycles, as possible. Therefore, the allocation is done entirely in the hardware machine; registers in the hardware contain all the allocation (mapping) information, and all references to virtual addresses, virtual stack locations, virtual register contents, or virtual devices converted by hardware to physical references.

In a PDP-11/70 System, mapping is done by two devices. The mapping of virtual registers into processor registers, of the virtual stack, and of the virtual program counter, is done by loading the appropriate values into the processor registers; one of two sets of general registers can be selected for the user, and the processor has a separate stack pointer for user mode, while the program counter is changed by interrupt and trap operations and by the Return from Interrupt (RTI) or Return from Trap (RTT) instructions.

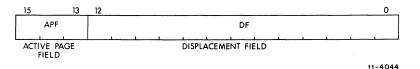

The remaining mapping functions distribute the virtual memory into the physical memory. In the physical memory, many specific addresses are reserved for special functions; the lowest addresses are used for interrupt and trap vectors, while the highest addresses are used for device registers. Because all functions that require reserved addresses in the physical memory are performed either by the physical machine or by the control program, these addresses need not be reserved in the virtual machine. Therefore, the programs written to be run in the virtual machine can use any addresses; specifically, these programs can start at address 000000 and continue through ascending addresses to the highest address needed. In discussions of the virtual memory and the physical memory, it is often necessary to describe the addresses used to select data items within the memory. The range of addresses that it is possible to use is called the *address space*. The maximum range of addresses that can be used in the virtual machine (which in the PDP-11/70 is the maximum number that can be contained in a 16-bit word) is called the virtual address space, while the maximum range of physical addresses that can exist in the hardware system is called the physical address space (in the PDP-11/70 this can be all the addresses expressed by a 22-bit number).

If the user program is to use addresses in the virtual address space that are reserved in the physical address space, the virtual address space must be relocated to some other part of the physical address space. In a multiprogramming system, several user programs, each in its own virtual address space, may be sharing the physical address space. Therefore, the relocation of the virtual address space into the physical address space must be variable; each time a program is run, it may be allocated a different part of the physical address space. Memory Management provides the capability of varying the relocation for each user program by storing a map of the memory allocation in a set of registers.

#### **Resource Management**

In a multiprogramming system, each user program operates in a virtual machine that can utilize any of the possible devices or functions of the physical machine, as well as many functions performed by the executive program. The resources that exist in the system must be allocated to each user program as required, but without allowing conflicts to arise where several user programs require the same resources. The physical machine and the executive program must resolve any protective conflicts by scheduling the resources for use by different programs at different times, and must schedule the user programs to operate when the resources are available.

The management of input/output or peripheral devices is beyond the scope of this discussion, which is primarily concerned with the basic PDP-11/70 System. Within the system, the two most important resources which require the most care and effort to control are the memory and the processor.

#### **Processor Management**

The processor can only execute one instruction at a time. When several programs are sharing the use of the processor, the processor operates on each program in turn; either the processor is shared among the programs, by using periodic interrupts to allow the executive program to transfer the processor to another user program, or each user program runs to completion before the next user program begins. To share the processor on a time basis, the executive program must perform the transfer from one virtual machine to another. Each virtual machine is given control of the physical machine by loading the map of that virtual machine into the physical machine. That is, the executive program changes virtual machines by changing the contents of the processor registers used by the virtual machine, and by changing the contents of the registers in Memory Management which map the virtual address space.

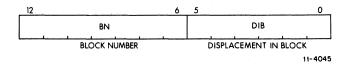

#### Memory Management

The following discussion assumes that Memory Management is enabled. Memory Management is much more complicated than Processor Management. If a program uses a large proportion of the virtual address space, and only a small amount of memory is physically available in the system, the program may be too large to fit into the memory all at once. Fortunately, in most programs only a small part of the program (or possibly several small parts, one for the instruction stream and one or more for blocks of data) is used at any one time. To take advantage of this fact, the virtual address space is divided into pages so that each page can be mapped separately. Only the pages that are in use in the current instruction are required to be in the physical memory during the execution of that instruction.

A system which uses Memory Management to permit each virtual machine to have a larger address space than the available physical memory must also include a mass storage device to hold those parts of each virtual memory that are not in the physical memory. As a program proceeds through a sequence of instructions, it requires different pages of the virtual memory. The memory map in the Memory Management includes relocation information for each page of the virtual address space, and also includes information specifying which pages are currently in the physical memory. If the processor attempts to perform transfers with a virtual address which is on a non-resident page, the instruction is aborted. A part of the executive program which transfers the required page into the physical memory and changes the map in Memory Management to reflect the newly available page is then executed.

#### Memory Use Statistics

If it is necessary for the executive program to bring a page into the physical memory, but all of the physical memory is already in use, the executive program must remove another page (from the same virtual machine or, in a multiprogramming system, from some other virtual machine) from the physical memory. When a page is removed from the physical memory, a copy of that page must be stored in the mass storage device; if a copy of the page is already on the mass storage device, and none of the data (or instructions) stored on the page have been changed, the writing of the page onto the mass storage device can be bypassed. Each time a page must be replaced, the executive program attempts to predict which page is least likely to be used in the future, so that it will not soon need to be moved back into the physical memory.

Memory Management includes hardware to permit choosing the page to be replaced and to determine whether that page must be written onto the mass storage device. Each external data transfer performed by the processor requires that Memory Management convert a virtual address into a physical address and keep track of which virtual pages have been accessed and which virtual pages have been written into. The executive program operates on the assumption that pages which have been recently accessed will also be used soon. To find a page which can be replaced, the executive program looks for a page which has not been used, preferably from the address space of a user other than the current user. If there are no virtual pages currently in the physical memory that have not been accessed, the executive program looks for a page that has not been written into, to avoid having to copy a page to the mass storage device. If all the virtual pages in the physical memory belong to the current user, the executive program looks for a page that has not been used recently, again preferably one that has not been written into. By use of the hardware Memory Management unit and of a variety of scheduling and allocation algorithms in the executive program, the system can provide a number of user programs with virtual machines of great power and flexibility, with a minimum burden on the user program.

#### Communication

A program running in a virtual machine must be able to communicate with the executive program, to request various services performed by the executive program, or to determine the status of the system. The same type of communication can be used for communication between virtual machines, by providing inter-machine communication as a service through the executive program. The same hardware functions that provide a means for the user program to communicate to the executive program are also used by the executive program to determine the status of the user program when a trap or abort condition occurs.

The user program requests services by executing trap instructions (such as EMT, TRAP, or IOT). Abnormal conditions caused by a program failure, such as an odd address for a word data transfer, or an attempt to execute a reserved instruction, cause internal processor traps. In either case, the trap function performed by the processor serves to notify the executive program that an instruction is required.

#### **Context Switching**

The executive program must then begin executing instructions to perform the requested service or to correct the failure condition, if possible. However, in order for the hardware machine to operate on any program other than the user program, the mapping information must be changed to reflect the allocations used by the new program.

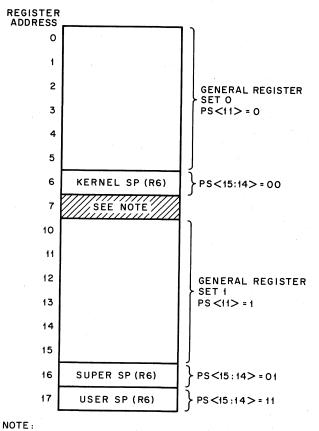

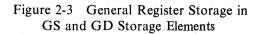

The trapping function performs the change of most of the mapping information. The contents of the Program Counter (PC) and the Processor Status (PS) registers are changed directly; the old contents are stored on a stack in memory, pointed to by a stack pointer, and the new contents are supplied from locations called a trap vector. The address of the trap vector is provided by the processor and depends on the type of trap instruction or trap condition, so that for each trap instruction or condition, a different PC and PS can be supplied. Memory Management stores the maps for the executive program and one user program in separate registers. The processor indicates which map should be used to relocate virtual addresses. During the execution of instructions (as opposed to the interrupt and trap service function), the address space map to use is specified by bits 15 and 14 of the PS. These bits also specify which Stack Pointer (SP) register in the processor to use (there is a separate SP for each virtual machine). Because the trap and interrupt service function loads the PS register with a new value, this function changes almost the entire virtual machine context directly.

The only remaining parts of the virtual machine context that require changes are the general registers in the processor. These can be changed either by saving the contents of the registers from the previous virtual machine on the hardware stack and loading new contents, or by selecting the alternate set of general registers (the processor has two sets of general registers, 0 - 5). Register set selection is controlled by bit 11 of the PS register, so this method can be used in conjunction with the trap service function.

To summarize the change of virtual machines: the mapping in the hardware system includes the selection of a register set, a stack pointer, a program address (in the program counter), an address space, and a processor status. The trap and interrupt service function, which is performed by the processor as an automatic response to trap an instruction or abnormal condition, can change all of these selections as follows:

- 1. The program counter and processor status are changed directly.

- 2. Bits 15 and 14 of the new PS select the new address space and stack pointer.

- 3. Bit 11 of the new PS selects the new register set.

The mapping and selection information for the previous virtual machine is completely saved, either by remaining in unselected portions of the processor and the Memory Management unit, or by being stored on the hardware stack. If the selected register set is shared with other virtual machines, the register contents must be changed by an instruction sequence.

#### **Inter-Program Data Transfers**

When the new virtual machine begins executing a service program for the programmed request (if a trap instruction was executed) or abnormal condition (if a trap condition occurred), the service program must get information from the previous virtual machine. This information may define the status of the previous virtual machine, after an abnormal condition occurred, so that the service program can correct the condition and restore the correct status before returning control to the previous virtual machine. If the service program is performing a service, the information required from the calling program may define the specific type of service to perform, or provide the addresses of data buffers, or specify device and file names.

Most information required by the service program is stored in the calling program's address space. To get this information, and to return information to the calling program, the service program must be able to operate in the present address space and transfer data in the previous address space, at the same time. The KB11-B Processor provides instructions to do this.

The special instructions that transfer data between virtual address space make use of the PS register to specify which address space is being used by the current virtual machine, and which address space was used by the previous machine (this is identified by bits 13 and 12 of the PS). The data is transferred between the hardware stack of the current address space and arbitrary addresses of the previous address space. The calculations of the virtual address in the previous address space; i.e., any index constants or absolute addresses used to generate the virtual address, are taken from the current address space, just as the instructions are.

Each virtual address space is divided into an Instruction (I) space and a Data (D) space. Each I or D space has a full set of 2<sup>16</sup> virtual addresses. Therefore, the communication instructions are available in two versions; one to transfer with the previous I space, and one to transfer with the previous D space. A different instruction is needed for each transfer direction as well, so there are four communication instructions: Move To Previous Instruction (MTPI) space, Move To Previous Data (MTPD) space, and Move From Previous Data (MFPD) space, and Move From Previous Data (MFPD) space.

#### **Returning to the Previous Context**

Because all the mapping and context information for the previous virtual machine is saved when the trap and interrupt service function sets up a new virtual machine, the hardware system can resume the execution of any program at the same point that it was interrupted. This is done with a Return from Interrupt (RTI) or Return from Trap (RTT) instruction, which replaces the PC and PS values of the current virtual machine with the stored values from the previous virtual machine.

The PS selects most of the mapping information, as described previously, so the return instructions completely restore the previous context.

#### Protection

The hardware system and the executive program must be protected from failures in each virtual machine. In addition, most systems provide protection so that no program operating in a virtual machine can take control of the system or affect the operation of the system without authorization. A third form of protection that is useful in a large and complex system is the protection of the executive program against itself. The executive program is divided into a basic, carefully written Kernel, which is allowed to perform any operation, and a broader Supervisor, which cannot perform privileged operations, but which provides various services useful to the executive program and to the user programs.

The forms of protection provided include the different address spaces for different types of programs, a variety of restricted access modes, and restricted processor operations. The address space protection can be used with any type of program, whether operating in User, Kernel, or Supervisor mode. The restricted processor operations are usable only in Kernel mode; Supervisor mode has the same restrictions as User mode.

#### Separate Address Spaces

The most basic protection against modification of the executive program by a User program (or of the Kernel section by the Supervisor section) is the separation of the address spaces. A program operating in User mode operates in the User address space. It cannot access any physical addresses that are not in that address space, regardless of their correspondence to addresses in any other virtual address space. The executive (Kernel) program can prevent a User program from accessing other virtual address spaces through the communication instructions (MTPI, MTPD, MFPI, MFPD) by forcing bits 13 and 12 of the stored processor status word to 1s (to reflect User mode) before executing an RTI or RTT instruction to return control to the user program. This forces the previous mode bits in the PS register to take on User mode, just as the current mode bits are set to User mode, and the communication instructions operate only within the User address space .

#### **Access Modes**

Within one address space, it is often useful to be able to protect certain parts of a program from unintentional modification. This can be done by allowing the data in those addresses to be read, but prohibiting transfers into the addresses. This is known as read-only (or write-protected) access. Areas in a virtual address space that contain alterable data must permit read/write access, but areas that contain unmodified instructions may be readonly.

Another useful form of access protection distinguishes between read accesses that fetch instructions (or address constants) and any accesses that transfer data. If instructions can be accessed by the processor only as instructions, they can be executed but they cannot be read or transferred to any other part of the address space. This prevents the user from determining what the instructions are in order to tamper with the instruction sequence or attempt to modify the program in undesirable ways. This type of access restriction is called execute-only access.

Memory Management provides a read/write, readonly, and execute-only access modes system. The access mode is stored in the mapping registers along with the relocation information; in fact, when a page of the virtual address space is not in memory, a special access code that identifies the page as non-resident is used. The execute-only access mode is not a separate access mode, but is provided by separating the address space into two address spaces that are used for the different kinds of transfers. One address space is used for all transfers that fetch instructions and is called the Instruction (I) space, while a second address space is used for all data transfers and is called the Data (D) space. If the two address spaces are mapped separately, attempts to use the same address for an instruction and for data may address different physical locations. If no addresses in the D space correspond to the physical addresses used in the I space, the instructions cannot be accessed as data and an execute-only access mode has been achieved. This mode must be used with caution: tables that are accessed by indexed address modes must be in D space and MARK instructions, which are stored on the hardware stack as data and then executed, and require the stack to be in the same virtual addresses in I and D space.

#### **Privileged Instructions**

Certain PDP-11 instructions that affect the operation of the hardware machine must be prohibited in the virtual machine. These include the HALT instruction, which stops the physical machine and thus prevents any virtual machine from operation, the RESET instruction, which stops all input/output devices, regardless of which virtual machine they are allocated to, and various PS change instructions. These instructions are allowed only in Kernel mode so that the executive program can control the entire hardware system; they are ineffective in the Supervisor or User mode. The RESET and Set Priority Level (SPL) instructions are allowed to execute in these modes, but have no effect; the HALT instruction activates a trap function so that the executive program may stop all action for the virtual machine that executed the HALT, but not for other virtual machines.

## 2.4 REENTRANT AND RECURSIVE PROGRAMMING

A program can generally be divided into routines, each of which performs a function that is built up from a sequence of instructions. Often, the function performed by a routine is needed in several other routines, so it is desirable to be able to call the routine from many other routines in the program; i.e., the program should be able to transfer the processor to the instructions following the calling instruction. A routine which is called from other routines is said to be subordinate to those routines and is called a subroutine; the special instructions that transfer the processor to the beginning of a subroutine and that return the processor to the calling routine are called subroutine linkage instructions.

#### **Recursive Functions**

Some procedures are most easily implemented as a subroutine that either performs a part of the procedure and then calls itself to perform the rest of the procedure, or completes a computation and returns a partial (and finally, a complete) result. This is called recursive operation. The common example of a recursive procedure is one that calculates the factorial of a number (the factorial is the product resulting from the multiplication of a number, n, by all smaller numbers). The recursive procedure to calculate a factorial of a positive integer is as follows:

- 1. If n is 1 or 0, return 1 as the value of factorial n.

- 2. If n is greater than 1, compute the factorial of n minus 1, multiply that number times n, and return that value.

For example, to compute the value of factorial 3, the procedure is to compute the value of factorial 2 and multiply by 3. However, the value of factorial 2 is the value of factorial 1 times 2. The value of factorial 1 is found by Step 1. to be 1, so the final result is 1 times 2, multiplied by 3, or 6. The same recursion computes the factorial of any positive integer, in n recursions for a number n.

#### Use of a Stack in Recursive Routines

When a subroutine is called recursively, the linkage information for each call (the information required to return to the calling program) must be saved during subsequent calls. Since a recursive subroutine can be called again before it returns from the first call, the linkage information should not be stored in a fixed location; instead, it is stored in a stack, with each linkage in a different location and a pointer that identifies the specific location for each linkage.

Assume that subroutine A calls subroutine B, which then calls subroutine C. Subroutine C must return control to subroutine B before subroutine B can return control to subroutine A. It can be seen that in this case the last linkage which has not been used for a return must be the first one used; i.e., the linkages must be used in a last-in, first-out sequence. A storage area whose locations are used for last-in, first-out storage is called a stack; a pointer is used to point to the last entry placed on the stack, and the subroutine linkage instructions that put information on the stack (a push operation), or remove information from the stack (a pop operation), change the contents of the pointer so that it always points to the correct word for the next linkage operation.

One of the KB11-B processor's general registers is used by the subroutine linkage instructions as a stack pointer. This register is the Kernel Stack Pointer (SP) and it must be initialized to point to the first word in a stack area. This same stack is also used for storage of context or linkage information by the trap and interrupt service function, which is described in Section II, Chapter 6. The traps, interrupts, and subroutine calls are all handled in the same last-in, first-out manner.

A subroutine that can be called recursively should not move data into fixed locations, because later executions of the same subroutine (before the current execution is finished) may also execute the same data transfer instructions. The best way to keep the data storage for each execution of a subroutine separate is to store the data on the stack in the same manner as the linkage information.

#### **Reentrant Functions**

Keeping the data storage separate from the program is particularly important for programs and subroutines that can be called from more than one virtual machine. If several virtual machines are executing the same program, it can be called from more than one virtual machine. If several virtual machines are executing the same program, it is desirable to have only one copy of the program in the physical memory, and to map each virtual address space into the same physical address space. However, in a muliprogramming system, one virtual machine may begin execution of a program and then be interrupted; a second virtual machine may begin execution of the same virtual program and then run out of time; the original virtual machine may resume execution and complete the program; and the second virtual machine may resume executions. The programmer cannot make any assumptions about where each virtual machine may resume execution, nor can he make any assumptions about where each virtual machine stops, so the program must be capable of being reentered at any time, regardless of what other virtual machines have done with the program.

Programs designed to store all their data on a stack, so that each virtual machine that uses the program simply uses a different stack, are called reentrant programs. A different stack pointer is selected each time a different virtual machine is selected. If the executive program changes the context of the user virtual machine, to run a different user, it changes the address mapping of the stack area and the contents of the stack pointer, so that each activation of a program executes the program in complete isolation from other activations by other virtual machines.

#### Indexed Addressing of Parameters

When a program or routine calls a subroutine, the calling routine may send data to the subroutine. The amount of the data to be "passed" to the subroutine may vary, as may the amount of data returned by the subroutine. By placing all the data on the stack, the amount of data becomes unimportant. The subroutine may read different data items on the stack by using the indexed addressing modes with the stack pointer as the base register. Complex subroutines may require that the last word placed on the stack (the word with the lowest virtual address, because the stack expands toward low addresses) contain the number of parameters passed so that the program does not use other data also on the stack but not intended as parameters.

#### Separate Stack and Index Pointers

Using the stack pointer as the base address for indexed addressing presents problems if the subroutine must, in turn, pass data to another subroutine. Each time the first subroutine calculates a parameter for the second subroutine, it pushes the parameter onto the stack. The address in the stack pointer changes to reflect the new data on the stack. As a result, all instructions in the first subroutine which contain index constants are invalid, because the base value that the index constants are supposed to modify has changed. It would be very difficult, if not impossible, to write a subroutine that could use different index constants as the stack pointer changes (because to remain reentrant, the program cannot change any part of the instruction code). A much simpler solution is to separate the base register from the stack pointer by copying the stack pointer value into another general register before using the stack for any other data. This is still reentrant because any change of virtual machine also changes the contents of (or the selection of) all general registers.

The register commonly used as a separate index pointer is register 5. The standard method of calling subroutines in reentrant programs uses register 5 as the index pointer, register 6 as the stack pointer, and a word on the stack (at the address contained in the index pointer) that indicates the number of parameters on the stack. In addition to providing a straightforward and completely reentrant structure, this method is completely compatible with a similar form of non-reentrant subroutine call. The same subroutine can be called both by reentrant programs and by simpler programs that are non-reentrant.

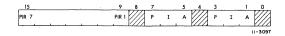

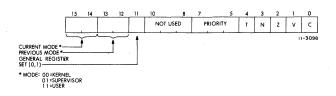

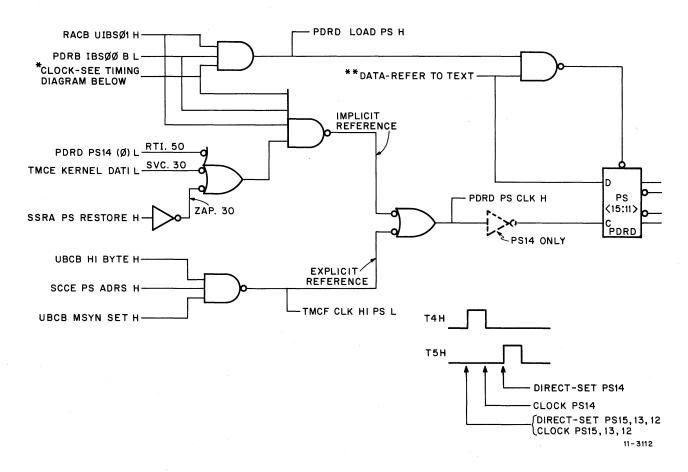

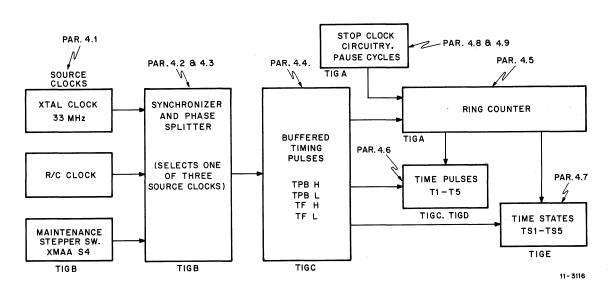

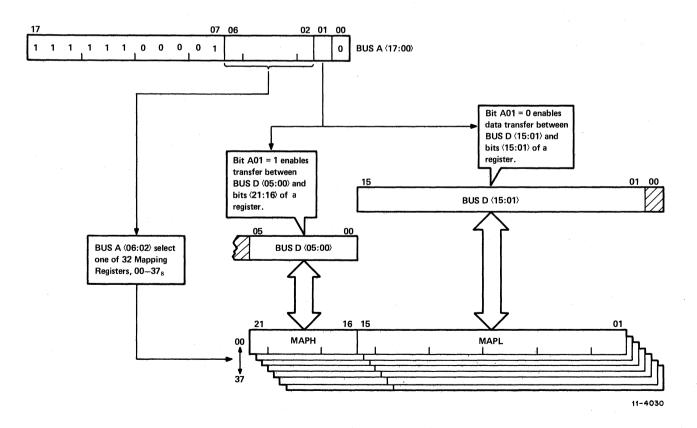

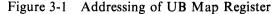

#### Subroutine Call Compatibility