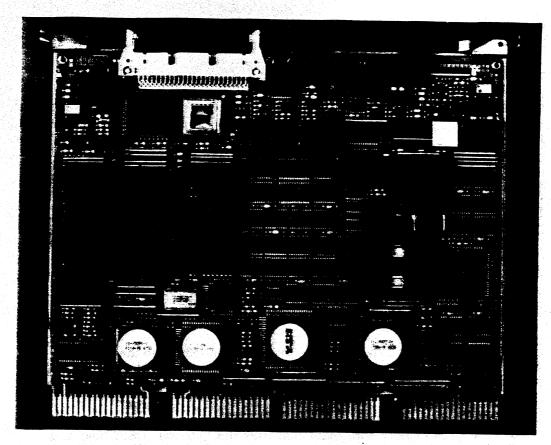

# KA640 CPU Module Technical Manual

Order Number EK-KA640-TM-001

digital equipment corporation maynard, massachusetts

#### First Edition, September 1988

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1988 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| DEC         | MicroVAX 3300 | R   |

|-------------|---------------|-----|

| DECmate     | MicroVAX 3400 | T   |

| DECUS       | MicroVAX 3500 | U   |

| DECwriter   | PDP           | V   |

| DIBOL       | P/OS          | V   |

| LSI-11      | Professional  | · V |

| MASSBUS     | Q-bus         | V   |

| MicroPDP-11 | Q22-bus       | v   |

| MicroVAX    | Rainbow       | W   |

| MicroVAX I  | RSTS          |     |

| MicroVAX II | RSX           |     |

|             |               |     |

RT ThinWire UNIBUS VAX VAXstation VMS VT VT100 Work Processor

FCC NOTICE: The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# Contents

xvii

## **About This Manual**

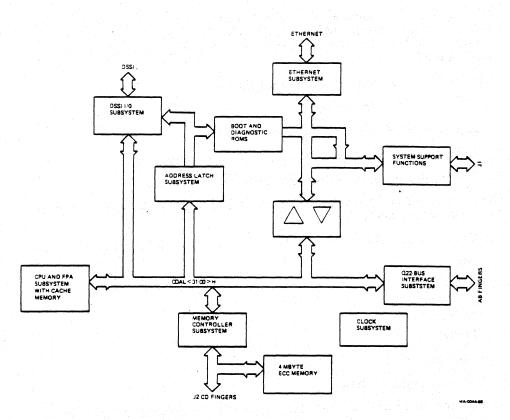

#### 1 Overview

| 1.1  | Introduction                      | 1 |

|------|-----------------------------------|---|

| 1.2  | Central Processing Unit           | 3 |

| 1.3  | Floating Point Accelerator        | 4 |

| 1.4  | Cache Memory                      | 5 |

| 1.5  | Memory Controller                 | 5 |

| 1.6  | MS650-AA Memory Modules           | 5 |

| 1.7  |                                   | 5 |

| 1.8  | Ethernet Interface                | 6 |

| 1.9  | Q22-bus Interface                 | 7 |

| 1.10 | MicroVAX System Support Functions | 7 |

| 1.11 | Firmware                          | 8 |

| 1.12 | Clock Functions                   | 8 |

|      |                                   |   |

# 2 Installation and Configuration

| 2.1   | Introduction                  | 9  |

|-------|-------------------------------|----|

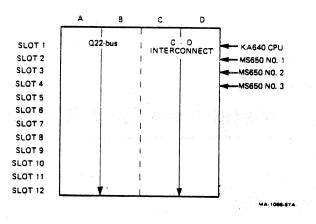

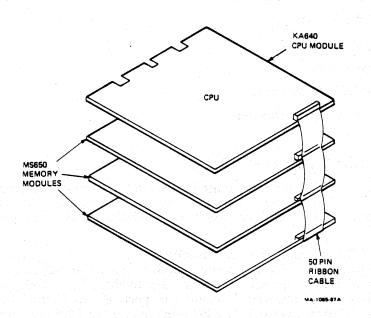

| 2.2   | Installing the KA640          | 9  |

| 2.3   | Configuring the KA640         | 11 |

| 2.4   | KA640 Connectors              | 11 |

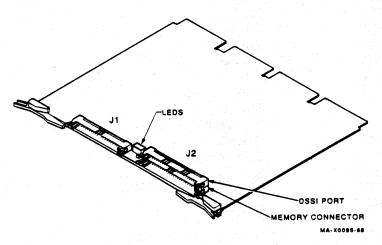

| 2.4.1 | System Support Connector (J1) | 12 |

| 2.4.2 | Memory/DSSI Connector (J2)    | 14 |

| 2.5   | H3602-SA CPU Cover Panel      | 15 |

| 2.6   | Compatible System Enclosures  | 17 |

|       |                               |    |

iv Contents

## 3 Architecture

| 3.1 Central Processor                                  | 18 |

|--------------------------------------------------------|----|

| 3.1.1 Processor State                                  | 19 |

| 3.1.1.1 General Purpose Registers                      | 19 |

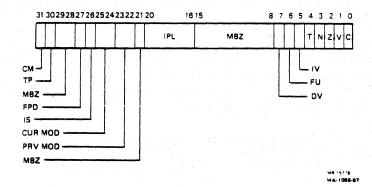

| 3.1.1.2 Processor Status Longword                      | 20 |

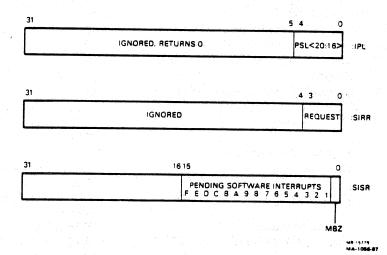

| 3.1.1.3 Internal Processor Registers                   | 21 |

| 3.1.2 Data Types                                       | 25 |

| 3.1.3 Instruction Set                                  | 25 |

| 3.1.4 Memory Management                                | 26 |

| 3.1.4.1 Translation Buffer                             | 26 |

| 3.1.4.2 Memory Management Control Registers            | 27 |

| 3.1.5 Exceptions and Interrupts                        | 28 |

| 3.1.5.1 Interrupts                                     | 28 |

| 3.1.5.2 Exceptions                                     | 30 |

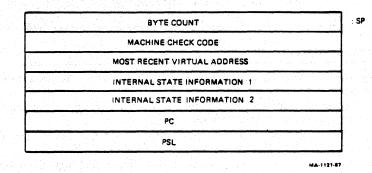

| 3.1.5.3 Information Saved On A Machine Check Exception | 33 |

| 3.1.5.4 System Control Block                           | 39 |

| 3.1.5.5 Hardware Detected Errors                       | 41 |

| 3.1.5.6 Hardware Halt Procedure                        | 42 |

| 3.1.6 System Identification                            | 44 |

| 3.1.7 CPU References                                   | 45 |

| 3.1.7.7 Instruction-Stream Read References             | 45 |

| 3.1.7.8 Data-Stream Read References                    | 46 |

| 3.1.7.9 Write References                               | 46 |

| 3.2 Floating Point Accelerator                         | 46 |

| 3.2.1 Floating Point Accelerator Instructions          | 47 |

| 3.2.2 Floating Point Accelerator Data Types            | 47 |

| 3.3 Cache Memory                                       | 47 |

| 3.3.1 Cacheable References                             | 47 |

| 3.3.2 Cache                                            | 48 |

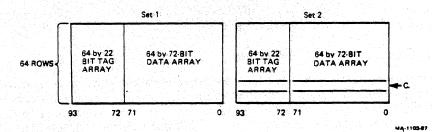

| 3.3.2.1 Cache Organization                             | 48 |

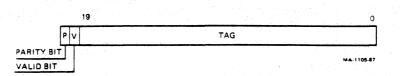

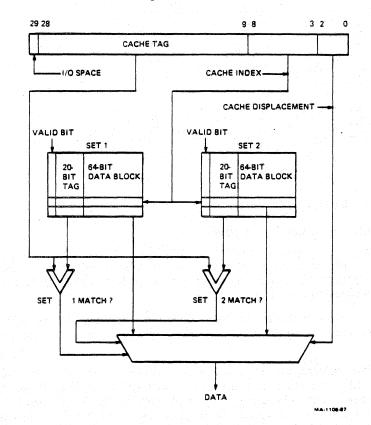

| 3.3.2.2 Cache Address Translation                      | 49 |

| 3.3.2.3 Cache Data Block Allocation                    | 50 |

| 3.3.2.4 Cache Behavior on Writes                       | 51 |

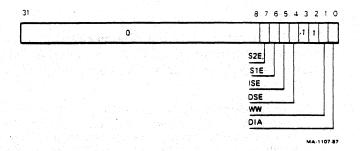

| 3.3.2.5 Cache Disable Register                         | 51 |

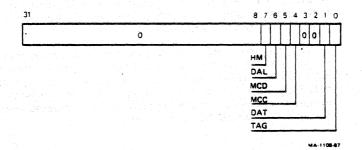

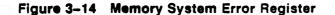

| 3.3.2.6 Memory System Error Register                   | 54 |

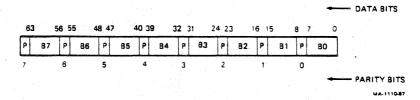

| 3.3.2.7 Cache Error Detection                          | 55 |

| 3.4 Main Memory System                                   | 56 |

|----------------------------------------------------------|----|

| 3.4.1 Main Memory Organization                           | 59 |

| 3.4.2 Main Memory Addressing                             | 59 |

| 3.4.3 Main Memory Behavior on Writes                     | 60 |

| 3.4.4 Main Memory Error Status Register                  | 60 |

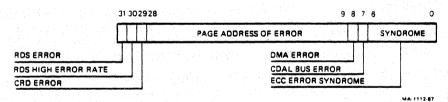

| 3.4.5 Main Memory Control and Diagnostic Status Register | 64 |

| 3.4.6 Main Memory Error Detection and Correction         | 66 |

| 3.5 Console Serial Line                                  | 68 |

| 3.5.1 Console Registers                                  | 68 |

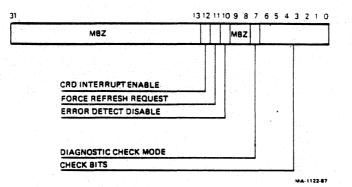

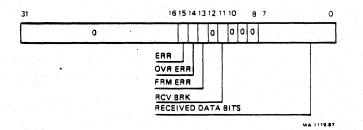

| 3.5.1.1 Console Receiver Control/Status Register         | 68 |

| 3.5.1.2 Console Receiver Data Buffer                     | 69 |

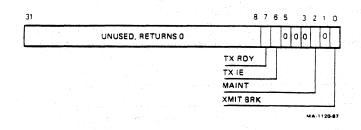

| 3.5.1.3 Console Transmitter Control/Status Register      | 70 |

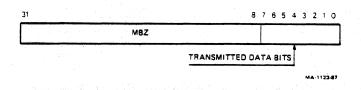

| 3.5.1.4 Console Transmitter Data Buffer                  | 72 |

| 3.5.2 Break Response                                     | 72 |

| 3.5.3 Baud Rate                                          | 72 |

| 3.5.4 Console Interrupt Specifications                   | 73 |

| 3.6 Time of Year Clock and Timers                        | 73 |

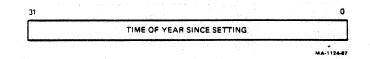

| 3.6.1 Time of Year Clock                                 | 74 |

| 3.6.2 Interval Timer                                     | 74 |

| 3.6.3 Programmable Timers                                | 75 |

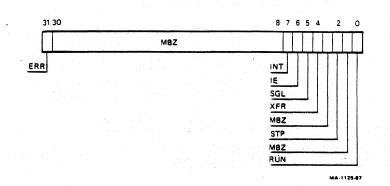

| 3.6.3.1 Timer Control Registers                          | 75 |

| 3.6.3.2 Timer Interval Registers                         | 77 |

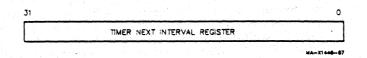

| 3.6.3.3 Timer Next Interval Registers                    | 78 |

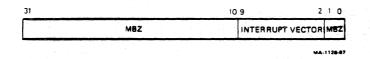

| 3.6.3.4 Timer Interrupt Vector Registers                 | 78 |

| 3.7 Boot and Diagnostic Facility                         | 79 |

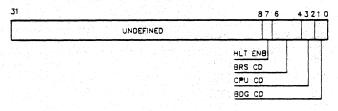

| 3.7.1 Boot and Diagnostic Register                       | 79 |

| 3.7.2 Diagnostic LED Register                            | 81 |

| 3.7.3 ROM Memory                                         | 82 |

| 3.7.3.1 ROM Socket                                       | 82 |

| 3.7.3.2 ROM Address Space                                | 82 |

| 3.7.3.3 KA640 Resident Firmware Operation                | 83 |

| 374 Battery Backed-Un RAM                                | 84 |

vi Contents

| KA640 Initialization                               | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power-Up Initialization                            | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Hardware Reset                                     | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| I/O Bus Initialization                             | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Processor Initialization                           | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 22-bus Interface                                   | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

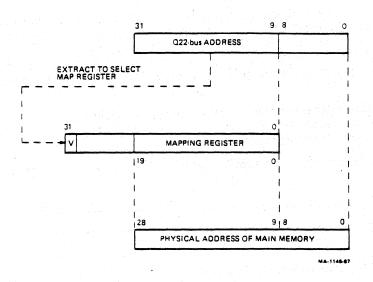

| Q22-bus to Main Memory Address Translation         | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

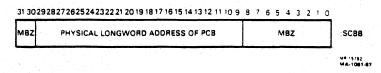

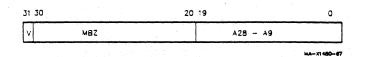

| Q22-bus Map Registers                              | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Accessing the Q22-bus Map Registers                | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Q22-bus Map Cache                                  | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CDAL Bus to Q22-bus Address Translation            | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Interprocessor Communication Register              | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

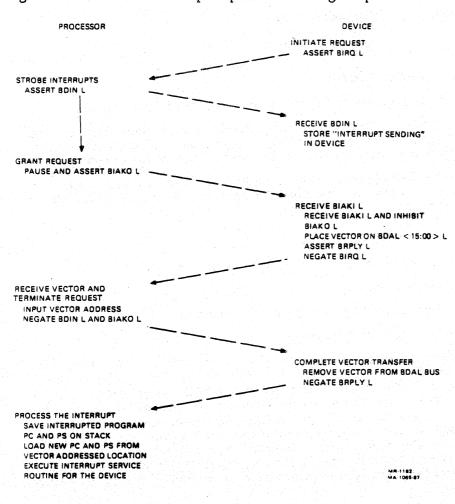

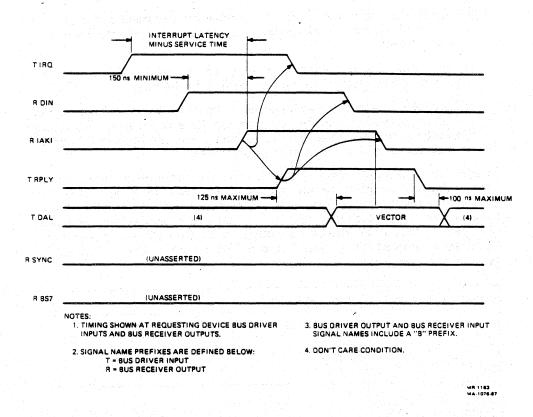

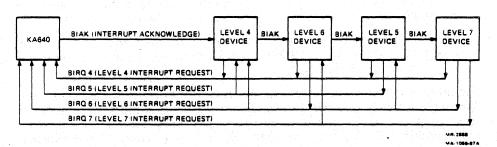

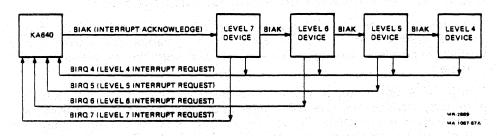

| Q22-bus Interrupt Handling                         | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Configuring the Q22-bus Map                        | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

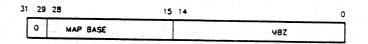

| Q22-bus Map Base Address Register                  | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

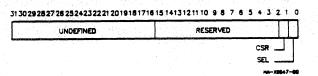

| System Configuration Register                      | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

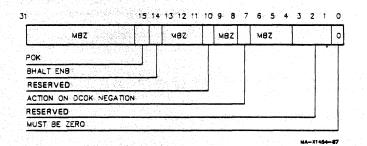

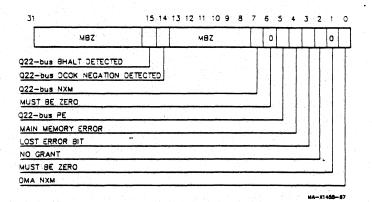

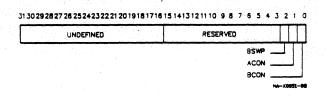

| DMA System Error Register                          | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

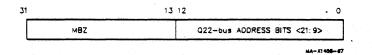

| Q22-bus Error Address Register                     | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

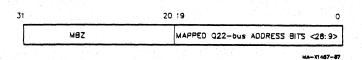

| DMA Error Address Register                         | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Error Handling                                     | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| etwork Interface                                   | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

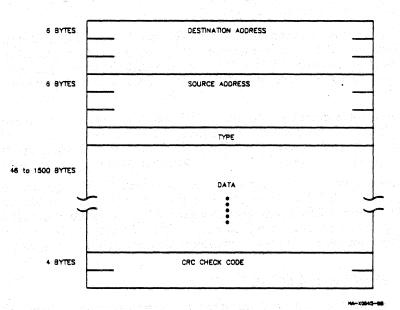

| Ethernet Overview                                  | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

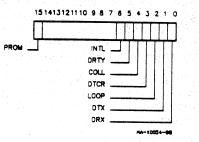

| Network Interface Station Address ROM              | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LANCE Chip Overview                                | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Interface Register Address Port            | 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Interface Register Data Port               | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

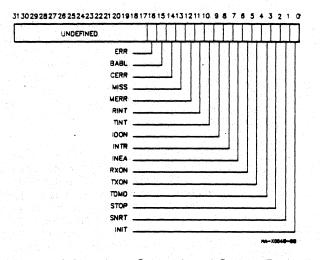

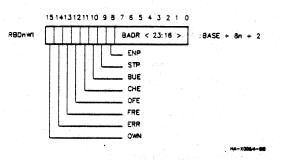

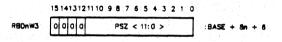

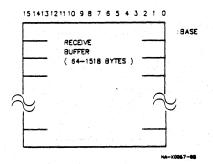

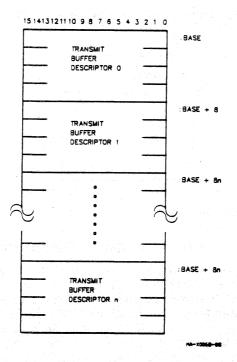

| Network Interface Control and Status Register 0    | 107                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Interface Control and Status Register 1    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Interface Control and Status Register 2    | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Interface Control and Status Register 3    | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

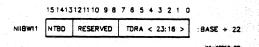

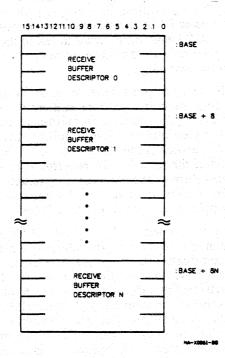

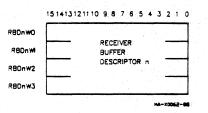

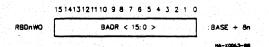

| Network Interface Initialization Block             | 114                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Interface Initialization Block Word 0      | 115                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

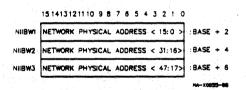

| Network Interface Initialization Block Words 1-3   | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

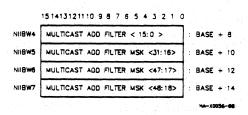

| Network Interface Initialization Block Words 4-7   | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

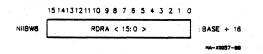

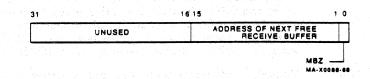

| Network Interface Initialization Block Words 8,9   | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

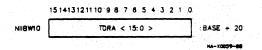

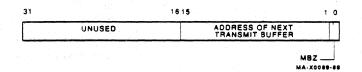

| Network Interface Initialization Block Words 10,11 | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                    | Power-Up InitializationHardware ResetI/O Bus InitializationProcessor Initialization22-bus InterfaceQ22-bus to Main Memory Address TranslationQ22-bus Map RegistersAccessing the Q22-bus Map RegistersQ22-bus Map CacheCDAL Bus to Q22-bus Address TranslationInterprocessor Communication RegisterQ22-bus Interrupt HandlingConfiguring the Q22-bus MapQ22-bus Interrupt HandlingConfiguring the Q22-bus MapQ22-bus Map Base Address RegisterSystem Configuration RegisterDMA System Error RegisterDMA Error Address RegisterDMA Error Address RegisterError Handlingetwork InterfaceEthernet OverviewNetwork Interface Station Address ROMLANCE Chip OverviewNetwork Interface Register Data PortNetwork Interface Control and Status Register 1Network Interface Control and Status Register 2Network Interface Control and Status Register 3Network Interface Initialization BlockNetwork Interface Initialization Block Word 0Network Interface Initialization Block Words 1-3Network Interface Initialization Block Words 4-7Network Interface Initialization Block Words 8,9 |

| 123 |

|-----|

| 124 |

| 124 |

| 128 |

| 129 |

| 130 |

| 134 |

| 135 |

| 136 |

| 136 |

| 137 |

| 137 |

| 137 |

| 138 |

| 138 |

| 139 |

| 139 |

| 139 |

| 140 |

| 142 |

| 143 |

| 145 |

| 146 |

| 146 |

| 148 |

| 148 |

| 149 |

| 149 |

| 151 |

| 152 |

| 152 |

| 152 |

| 162 |

| 163 |

|     |

## 4 KA640 Firmware

| 4.1 KA640 Firmware Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 171         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 4.1.1 Power Up Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 173         |

| 4.1.2 Mode Switch Set to Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 173         |

| 4.1.3 Mode Switch Set to Language Inquiry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 174         |

| 4.1.4 Mode Switch Set to Normal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 174         |

| 4.1.5 KA640 ROM-Based Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 177         |

| 그는 것 같아요. 그는 것 같아요. 이렇게 잘 하는 것 같아요. 이렇게 가지 않는 것 같아요. 이렇게 하는 것 같아요. 이렇 | 182         |

| 4.1.5.2 Console Command Keywords                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 184         |

| 4.1.5.3 Conventions for Tables 4-4 and 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 185         |

| 4.1.5.4 References to Processor Registers and Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 188         |

| 4.1.5.5 BOOT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 <b>89</b> |

| 4.1.5.6 CONFIGURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 191         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 192         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 192         |

| 4.1.5.9 EXAMINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 194         |

| 4.1.5.10 FIND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 196         |

| 4.1.5.11 HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 197         |

| 4.1.5.12 HELP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 198         |

| 4.1.5.13 INITIALIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 200         |

| 4.1.5.14 MOVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 201         |

| 4.1.5.15 NEXT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 203         |

| 4.1.5.16 REPEAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 204         |

| 4.1.5.17 SEARCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 205         |

| 4.1.5.18 SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 208         |

| 4.1.5.19 SHOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 211         |

| 4.1.5.20 START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 214         |

| 4.1.5.21 TEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 215         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 218         |

| 4.1.5.23 X - Binary Load and Unload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 219         |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 221         |

| 4.2 Bootstrapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 221         |

| 그는 것 같은 것 같                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 222         |

| 에는 이번 사람이 있는 것이 같은 것이 있는 것이다. 이번 것이 있는 것                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 223         |

| 4.2.1.2 Boot Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 224         |

| 4.2.2 Primary Bootstrap, VMB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 225         |

| 4.2.3 Device Dependent Bootstrap Procedures                                                                      | 227 |

|------------------------------------------------------------------------------------------------------------------|-----|

| 4.2.3.1 Disk and Tape Bootstrap Procedure                                                                        | 227 |

| 4.2.3.2 PROM Bootstrap Procedure                                                                                 | 228 |

| 4.2.3.3 Network Bootstrap Procedure                                                                              | 229 |

| 4.3 Operating System Restart                                                                                     | 232 |

| 4.3.1 Locating the RPB                                                                                           | 233 |

| 4.4 Machine State When Halted                                                                                    | 233 |

| 4.4.1 Main Memory Layout and State                                                                               | 233 |

| 4.4.1.1 Reserved Main Memory                                                                                     | 234 |

|                                                                                                                  | 234 |

| 4.4.1.3 Bitmap                                                                                                   | 234 |

| 4.4.1.4 Contents of Main Memory                                                                                  | 235 |

| 4.4.2 Cache Memory                                                                                               | 235 |

| 4.4.3 Translation Lookaside Buffer                                                                               | 235 |

| 4.4.4 Halt Protect Space                                                                                         | 236 |

|                                                                                                                  | 236 |

| 4.5.1 Firmware EPROM Layout                                                                                      | 236 |

|                                                                                                                  | 237 |

|                                                                                                                  | 237 |

| 4.5.2.2 CP\$MSG_OUT_NOLF_R4                                                                                      | 238 |

| 4.5.2.3 CP\$READ_WTH_PRMPT_R4                                                                                    | 239 |

| 4.5.3 SSC RAM Layout                                                                                             | 240 |

|                                                                                                                  | 240 |