EK-DZQ11-TM-001

# DZQ11 Asynchronous Multiplexer Technical Manual

EK-DZQ11-TM-001

# DZQ11 Asynchronous Multiplexer Technical Manual

Prepared by Educational Services of Digital Equipment Corporation

First Edition, October 1984

### Copyright © 1984 by Digital Equipment Corporation

All Rights Reserved

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors herein.

#### Printed in U.K.

The following are trademarks of Digital Equipment Corporation.

PDP

P/OS

RSTS

RSX

Rainbow

# digital

DEC DECmate DECUS DECwriter DIBOL MASSBUS

RT UNIBUS Professional VAX VMS VT Work Processor

# CONTENTS

# Page

# CHAPTER 1 GENERAL DESCRIPTION

| 1.1     | INTRODUCTION            | 1-1  |

|---------|-------------------------|------|

| 1.2     | PHYSICAL DESCRIPTION    | 1-3  |

| 1.2.1   | DZQ11 Configurations    | 1-4  |

| 1.2.2   | Interface Cables        | 1-6  |

| 1.2.3   | Test Connectors         | 1-6  |

| 1.3     | SPECIFICATIONS          | 1-8  |

| 1.3.1   | Environmental           | 1-8  |

| 1.3.2   | Electrical              | 1-8  |

| 1.3.3   | Performance             | 1-8  |

| 1.3.3.1 | Interfaces              | 1-8  |

| 1.3.3.2 | Maximum Configurations  | 1-8  |

| 1.3.3.3 | Throughput              | 1-9  |

| 1.3.3.4 | Receivers               | 1-9  |

| 1.3.3.5 | Transmitters            | 1-9  |

| 1.3.3.6 | Baud-Rate Generator     | 1-9  |

| 1.3.3.7 | Performance Summary     | 1-9  |

| 1.3.4   | Interrupts              | 1-10 |

| 1.3.4.1 | Receiver-Done Interrupt | 1-10 |

| 1.3.4.2 | Silo-Alarm Interrupt    | 1-10 |

| 1.3.4.3 | Transmit Interrupt      | 1-10 |

|         |                         |      |

### CHAPTER 2 INSTALLATION

| 2.1   | SCOPE                                | 2-1  |

|-------|--------------------------------------|------|

| 2.2   | UNPACKING AND INSPECTION             | 2-1  |

| 2.3   | INSTALLATION PROCEDURE               | 2-2  |

| 2.3.1 | Modem Control Jumpers                | 2-2  |

| 2.3.2 | Module Installation                  | 2-4  |

| 2.3.3 | Testing DZQ11s in PDP-11 Systems     | 2-8  |

| 2.3.4 | Testing in MicroVAX Systems          |      |

| 2.4   | DEVICE ADDRESS ASSIGNMENTS           |      |

| 2.5   | INTERRUPT VECTOR ADDRESS ASSIGNMENTS | 2-13 |

# CHAPTER 3 DEVICE REGISTERS

| 3.1   | SCOPE                        | 3-1 |

|-------|------------------------------|-----|

| 3.2   | DEVICE REGISTERS             | 3-1 |

| 3.2.1 | Control and Status Register  | 3-1 |

| 3.2.2 | Receiver Buffer              | 3-4 |

| 3.2.3 | Line Parameter Register      | 3-5 |

| 3.2.4 | Transmitter Control Register | 3-7 |

| 3.2.5 | Modem Status Register        | 3-8 |

| 3.2.6 | Transmit Data Register       | 3-8 |

| CHAPTER 4 | PROGRAMMING                                                                                                                                                      |      |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1       | SCOPE                                                                                                                                                            | 4-1  |

| 4.2       | PROGRAMMING FEATURES                                                                                                                                             | 4-1  |

| 4.2.1     | Interrupts                                                                                                                                                       | 4-1  |

| 4.2.2     | Emptying the Silo                                                                                                                                                | 4-2  |

| 4.2.3     | Transmitting a Character                                                                                                                                         | 4-3  |

| 4.2.4     | Data Set Control                                                                                                                                                 | 4-4  |

|           | 수업 방법 그렇게 가지 않는 것은 것은 것이라고 있는 동안이다. 그런 것은 가장 영상에는 것은 것이라는 것이다. 가장 가지 않는 것이다.<br>같은 것은 것은 것은 것이 같은 것은 것은 것이 같은 것이 같은 것이 없는 것은 것은 것이라. 것은 것은 것이 없는 것이다. 것이 같은 것이다. |      |

| CHAPTER 5 | TECHNICAL DESCRIPTION                                                                                                                                            |      |

| 5.1       | SCOPE                                                                                                                                                            | 5-1  |

| 5.2       | CIRCUIT FUNCTIONS                                                                                                                                                | 5-2  |

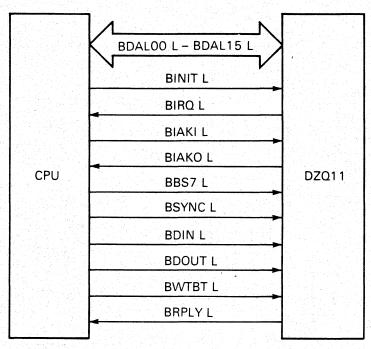

| 5.3       | DZQ11 TO Q-BUS INTERFACE                                                                                                                                         | 5-4  |

| 5.3.1     | Interface Signals                                                                                                                                                | 5-4  |

| 5.3.2     | Circuit Operation                                                                                                                                                | 5-5  |

| 5.3.2.1   | Bus Interface                                                                                                                                                    |      |

| 5.3.2.2   | I/O Control                                                                                                                                                      |      |

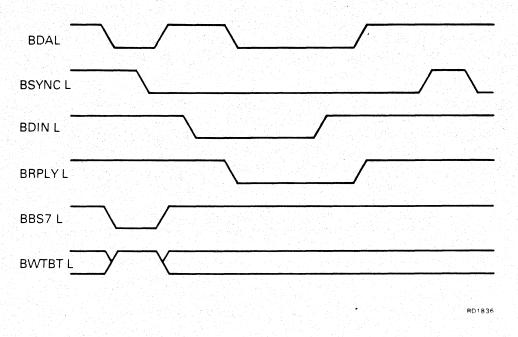

| 5.3.2.3   | Input Operation.                                                                                                                                                 | 5-7  |

| 5.3.2.4   | Output Operation                                                                                                                                                 | 5-8  |

| 5.3.2.5   |                                                                                                                                                                  | 5-8  |

| 5.3.2.6   | Vector Operation.                                                                                                                                                | 5-10 |

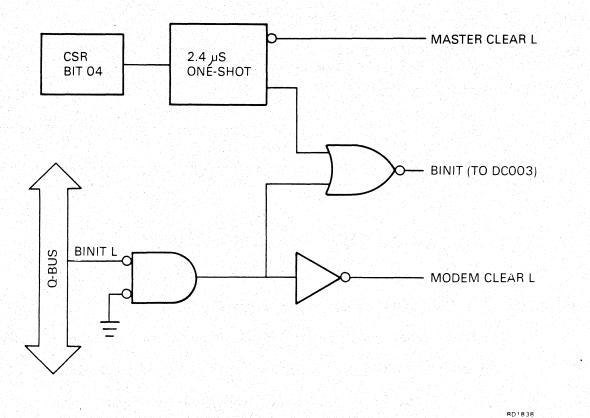

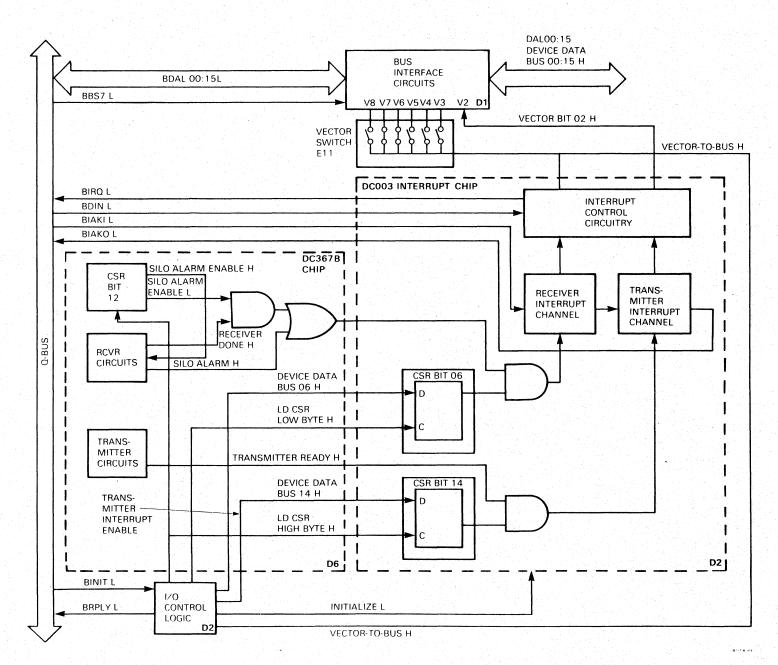

| 5.3.2.7   | Initialize Circuit                                                                                                                                               |      |

| 5.3.2.8   | Interrupt Logic.                                                                                                                                                 | 5-10 |

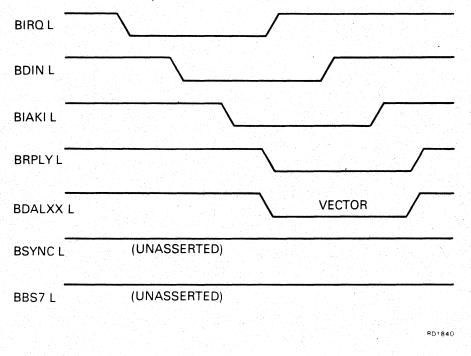

|           | Interrupt Transactions                                                                                                                                           | 5-12 |

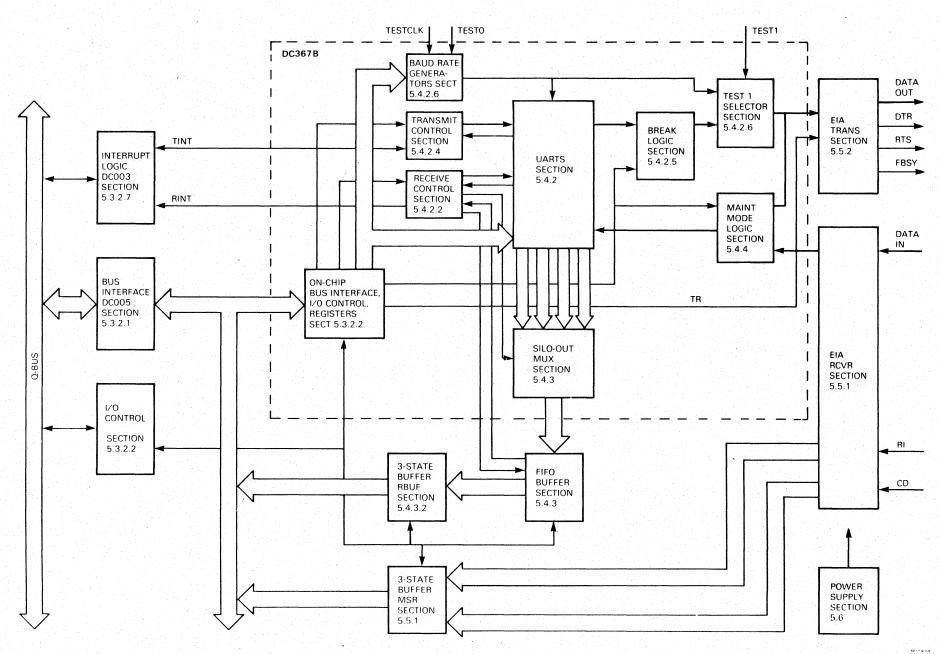

| 5.4       | LINE MULTIPLEXER.                                                                                                                                                | 5-13 |

| 5.4.1     | Hardware Description                                                                                                                                             | 5-13 |

| 5.4.2     | UARTs and Control                                                                                                                                                | 5-13 |

| 5.4.2.1   | Receiver Operation                                                                                                                                               | 5-13 |

| 5.4.2.2   | Receiver Control                                                                                                                                                 | 5-14 |

| 5.4.2.3   | Transmitter Operation                                                                                                                                            | 5-17 |

| 5.4.2.4   | Transmitter Control                                                                                                                                              | 5-17 |

| 5.4.2.5   | Break (BRK) Bits                                                                                                                                                 | 5-19 |

| 5.4.2.6   | Speed and Format Control                                                                                                                                         | 5-20 |

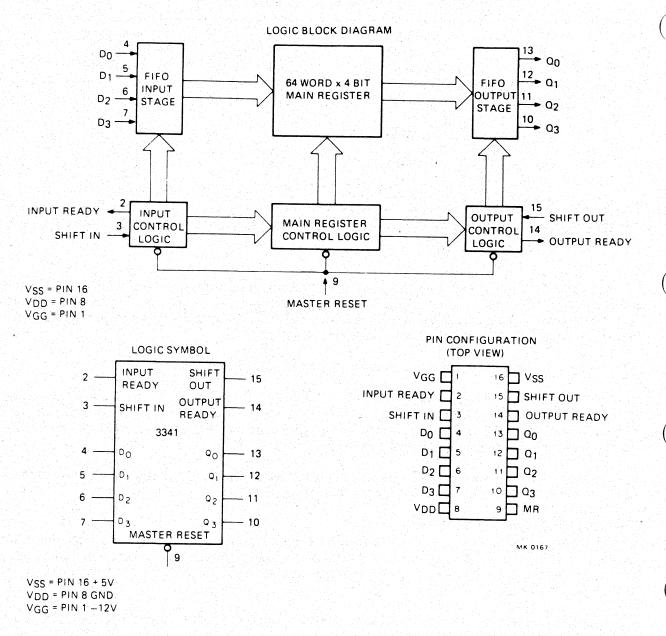

| 5.4.3     | FIFO Buffer                                                                                                                                                      | 5-21 |

| 5.4.3.1   | FIFO Description                                                                                                                                                 | 5-21 |

| 5.4.3.2   | FIFO Operation                                                                                                                                                   | 5-21 |

| 5.4.4     | Maintenance Mode                                                                                                                                                 | 5-22 |

| 5.5       | LINE INTERFACE.                                                                                                                                                  | 5-23 |

| 5.5.1     | Description                                                                                                                                                      | 5-23 |

| 5.5.2     | EIA Receivers                                                                                                                                                    | 5-23 |

| 5.5.3     | EIA Transmitters.                                                                                                                                                | 5-23 |

|           |                                                                                                                                                                  |      |

| 5.6       | POWER SUPPLY                                                                                                                                                     | 5-24 |

| CHAPTER 6 | MAINTENANCE                                                                                                                                                      |      |

| 6.1       | SCOPE                                                                                                                                                            | 6-1  |

| 6.2       | PREVENTIVE MAINTENANCE                                                                                                                                           | 6-1  |

| 6.3       | CORRECTIVE MAINTENANCE                                                                                                                                           | 6-1  |

|           |                                                                                                                                                                  |      |

| 6.3.4   | XXDP+ Diagnostic Programs                 | 6-2  |

|---------|-------------------------------------------|------|

| 6.3.4.1 | General                                   |      |

| 6.3.4.2 | Maintenance Modes                         |      |

| 6.3.4.3 | Setting Up Procedures                     | 6-4  |

| 6.3.4.4 | Software Switch Register                  | 6-4  |

| 6.3.4.5 | Auto-Sizing                               |      |

| 6.3.4.6 | Parameter Inputs and Dialogue             | 6-5  |

| 6.3.4.7 | Functional Description                    | 6-7  |

| 6.3.5   | Interprocessor Test (ITEP)                | 6-10 |

| 6.3.5.1 | Starting ITEP                             |      |

| 6.3.6   | Manual Tests                              | 6-11 |

| 6.4     | CORRECTIVE MAINTENANCE (MicroVAX SYSTEMS) |      |

| 6.4.1   | The Macroverify Diagnostic                |      |

| 6.4.1.1 | Setting-Up Procedures                     |      |

| 6.4.1.2 | Bootstrapping Procedure                   |      |

| 6.4.1.3 | Macroverify Operation                     |      |

| 6.4.2   | DZV11/DZQ11 Diagnostic EHXDZ              |      |

| 6.4.2.1 | Setting-Up Procedures                     |      |

| 6.4.2.2 | Bootstrapping Procedure                   | 6-20 |

| 6.4.2.3 | Running EHXDZ                             |      |

| 6.4.2.4 | Starting-Up                               | 6-22 |

| 6.4.2.5 | Sections                                  |      |

| 6.4.2.6 | Error Messages                            |      |

| 6.4.3   | Test Sequence                             | 6-24 |

|         |                                           |      |

# APPENDIX A IC DESCRIPTIONS

| A.1     | SCOPE                             | A-1  |

|---------|-----------------------------------|------|

| A.2     | DC003 INTERRUPT IC                | A-1  |

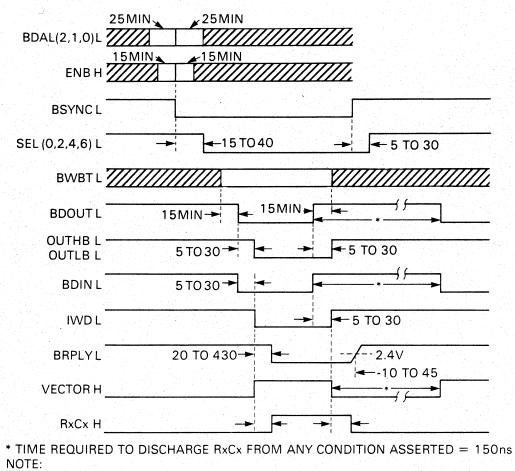

| A.3     | DC004 PROTOCOL IC                 | A-5  |

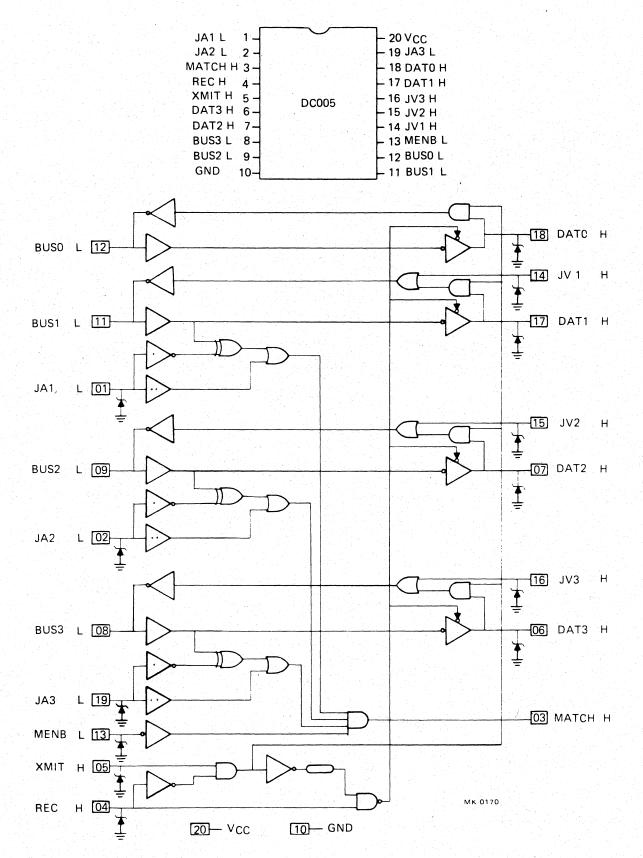

| A.4     | DC005 BUS TRANSCEIVER IC          |      |

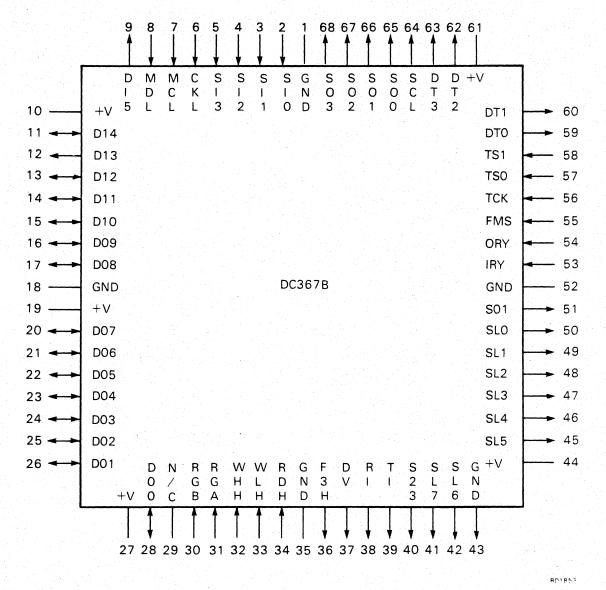

| A.5     | DC367B SEMI-CUSTOM VLSI IC        | A-13 |

| A.5.1   | Description                       | A-13 |

| A.5.2   | Pin Layout                        | A-13 |

| A.5.3   | Specifications of Some Parameters | A-16 |

| A.5.3.1 | Baud-Rate Accuracy                |      |

| A.5.3.2 | Receiver Parameters               | A-17 |

| A.5.3.3 | Read/Write Pulses and Data Delay  |      |

| A.6     | 3341 FIFO SERIAL MEMORY           | A-17 |

## APPENDIX B GLOSSARY OF TERMS

| B.1 | SCOPE    | B-1 |

|-----|----------|-----|

| B.2 | GLOSSARY | B-1 |

# FIGURES

| Figure No.  | Title                               | Page |

|-------------|-------------------------------------|------|

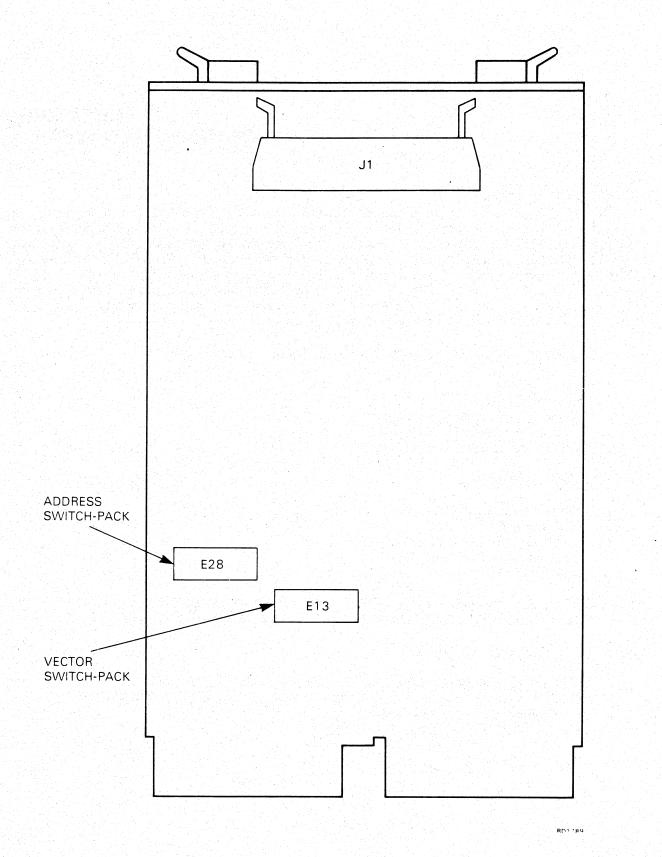

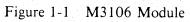

| 1-1         | M3106 Module                        | 1-2  |

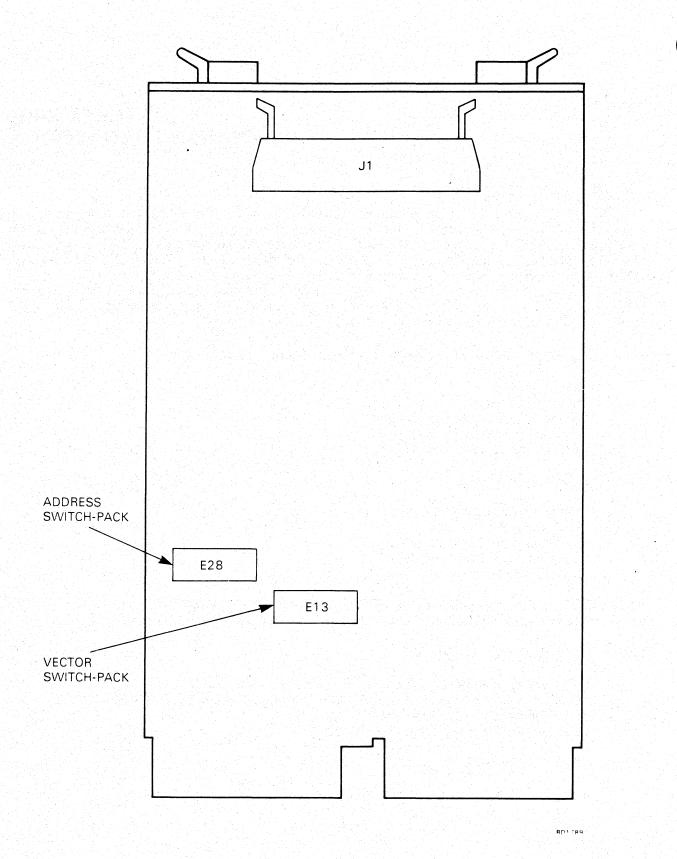

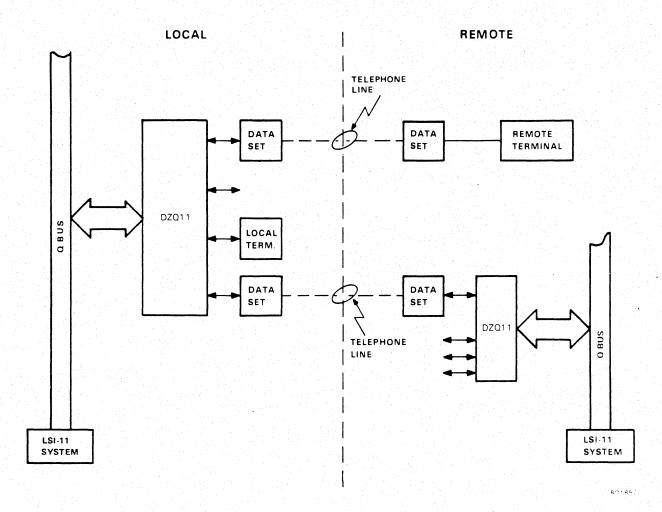

| 1-2         | DZQ11 System Applications           |      |

| 1-3         | Elements of the DZQ11 Option        | 1-5  |

| 1-4         | Test Connectors H325 and H329       | 1-6  |

| 1-5         | Loopback Connection                 | 1-7  |

| 2-1         | Jumper Location on M3106 Module     | 2-3  |

| 2-2         | DZQ11 Installation (BC11U-25)       | 2-5  |

| 2-3         | DZQ11 Installation (70-19964-00)    | 2-8  |

| 3-1         | Register Bit Assignment             |      |

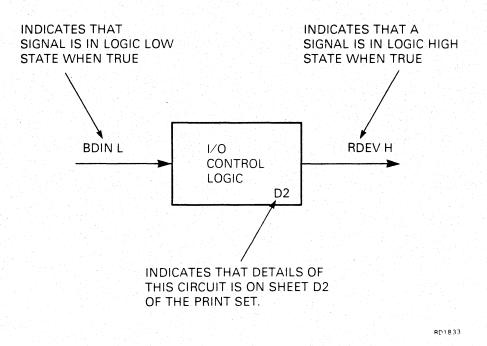

| 5-1         | Labeling Conventions                |      |

| 5-2         | Simplified Functional Block Diagram |      |

| 5-3         | DZQ11/Q-bus Interface               |      |

| 5-4         | Data Input Timing                   |      |

| 5-5         | Data Output Timing                  | 5-9  |

| 5-6         | Initialization Signals              |      |

| 5-7         | Interrupt Logic                     |      |

| 5-8         | Interrupt Timing                    |      |

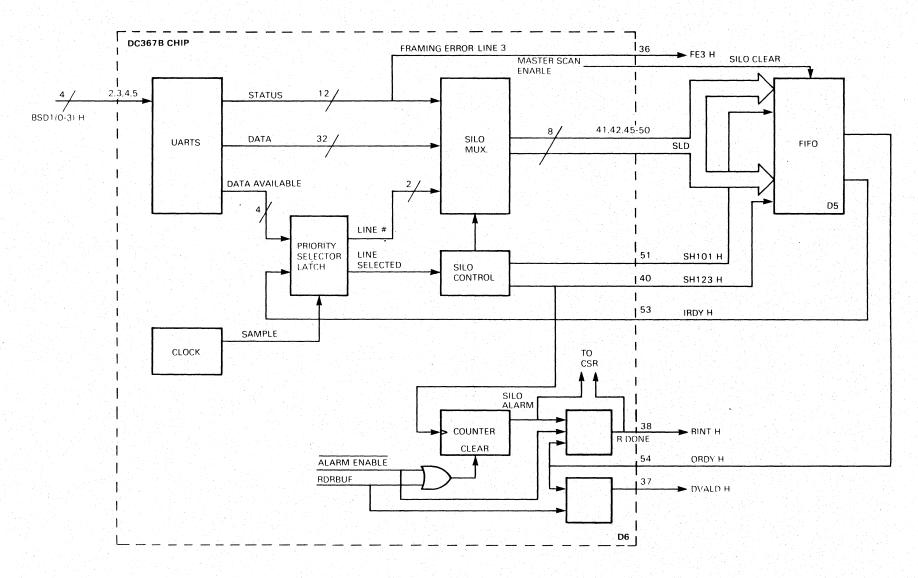

| 5-9         | Receiver Control Block Diagram      |      |

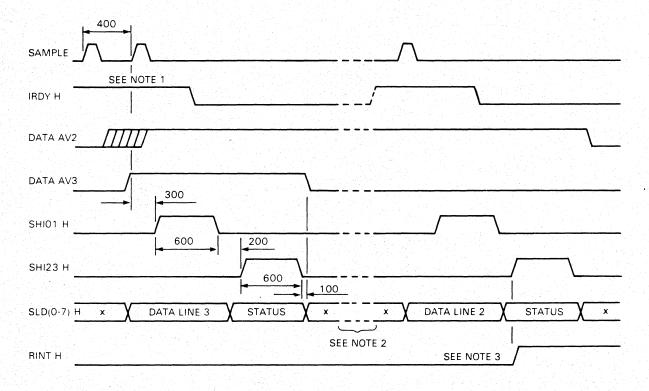

| 5-10        | Receiver Control Timing Diagram     |      |

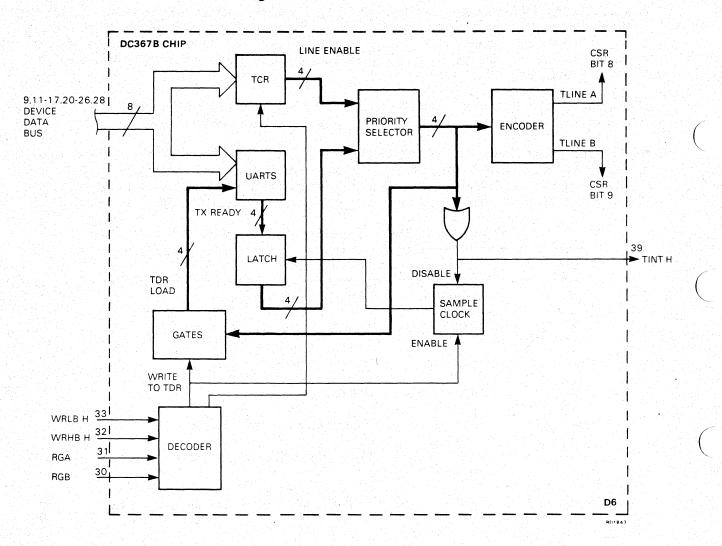

| 5-11        | Transmitter Control Block Diagram   | 5-18 |

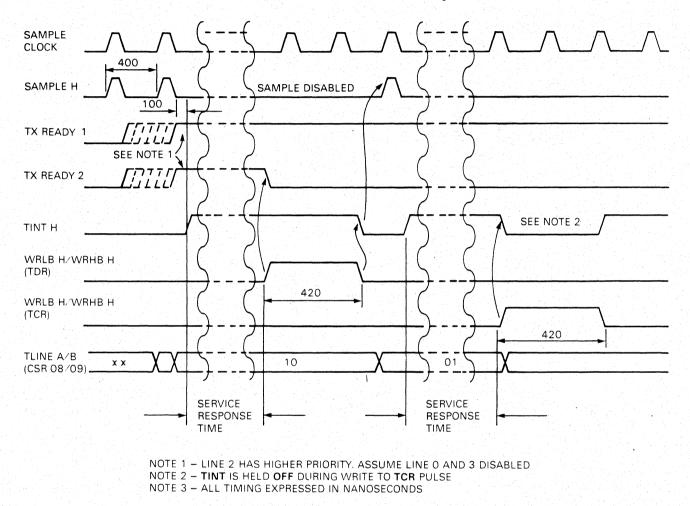

| 5-12        | Transmitter Control Timing Diagram  |      |

| 5-13        | FIFO Output Timing                  |      |

| 5-14        | EIA Receivers                       |      |

| 5-15        | EIA Transmitters                    |      |

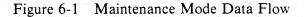

| 6-1         | Maintenance Mode Data Flow          | 6-3  |

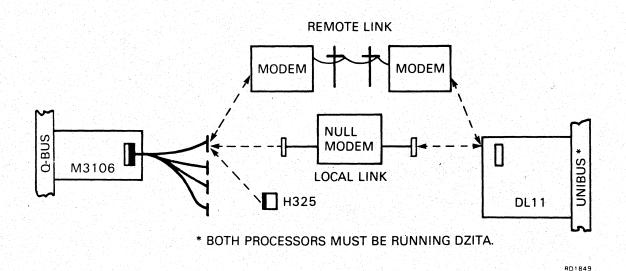

| 6-2         | Interprocessor Test (ITEP)          | 6-4  |

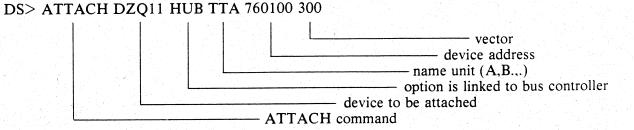

| 6-3         | DZQ11 Test Configurations.          | 6-25 |

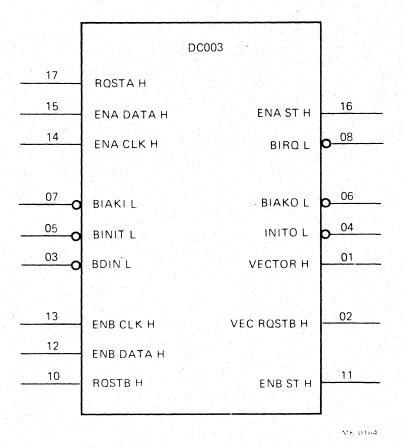

| A-1         | DC003 Logic Symbol                  | A-1  |

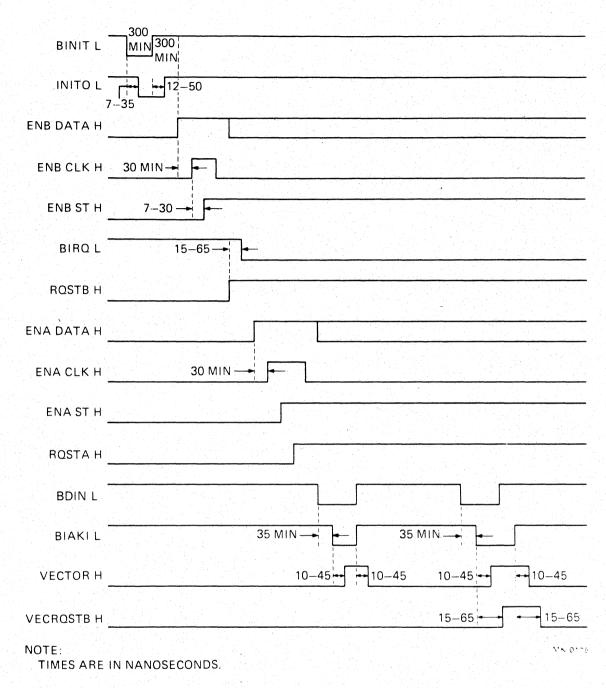

| A-2         | DC003 A Section Timing              | A-2  |

| A-3         | DC003 A and B Section Timing        | A-3  |

| A-4         | DC004 Simplified Logic Diagram      | A-6  |

| A-5         | DC004 Timing Diagram                |      |

| <b>A</b> -6 | DC005 Simplified Logic Diagram      | A-11 |

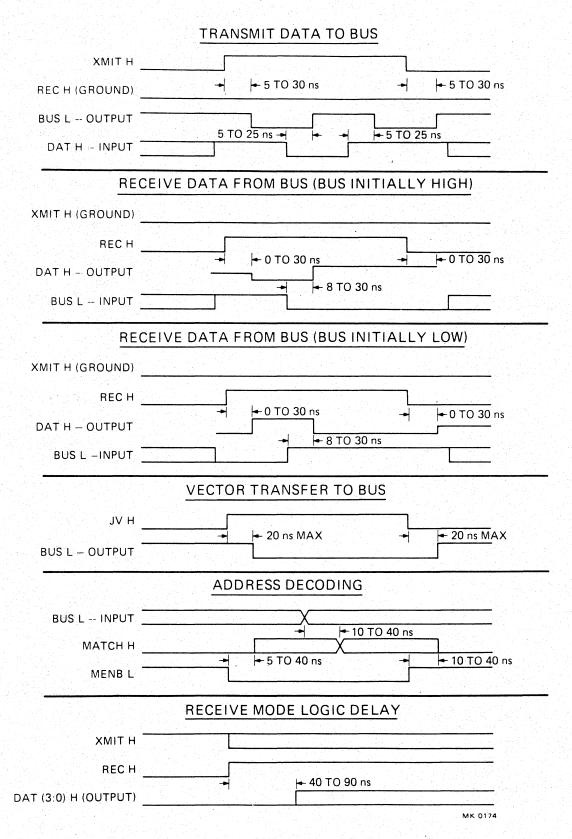

| A-7         | DC005 Timing Diagram                | A-12 |

| A-8         | Pin Layout of the DC367B            | A-13 |

| A-9         | 3341 FIFO Serial Memory             | A-18 |

# TABLES

| Table No. | Title                            | Page |

|-----------|----------------------------------|------|

| 2-1       | Items Supplied per Configuration | 2-2  |

| 2-2       | Jumper Configuration             |      |

| 2-3       | Break Character Response Options |      |

| 2-4       | Address Switch Selection         | 2-6  |

| 2-5       | Vector Switch Selection          | 2-7  |

| 2-6       | Floating Address Assignments     | 2-11 |

| 2-7       | One DUV11 and One DZQ11          |      |

| 2-8       | Two DZQ11s                       |      |

| 2-9 | First Part of Q-bus Vector Address Assignments List                                                             | 2-13 |

|-----|-----------------------------------------------------------------------------------------------------------------|------|

| 3-1 | DZQ11 Register Address Assignments                                                                              | 3-1  |

| 3-2 | CSR Bit Assignments                                                                                             | 3-3  |

| 3-3 | RBUF Bit Assignments                                                                                            | 3-5  |

| 3-4 | LPR Bit Assignments                                                                                             | 3-5  |

| 5-1 | DZQ11/Q-bus Interface Signals                                                                                   | 5-4  |

| 5-2 | Register Selection                                                                                              | 5-6  |

| 5-3 | Transceiver Switching                                                                                           | 5-7  |

| 5-4 | Byte Selection (Output Operation Only)                                                                          | 5-9  |

| 5-5 | DC367B Receiver Control Signals                                                                                 |      |

| 5-6 | DC367B Transmitter Control Signals                                                                              | 5-17 |

| 5-7 | Modem Control and Status Signals                                                                                | 5-30 |

| 6-1 | Diagnostic Programs                                                                                             | 6-1  |

| 6-2 | Multimedia Assignments                                                                                          | 6-2  |

| 6-3 | Typical Map of DZQ11 Status                                                                                     | 6-5  |

| 6-4 | CVDZA Tests                                                                                                     | 6-8  |

| 6-5 | CVDZB Tests                                                                                                     | 6-9  |

| 6-6 | Valid Mode Combinations                                                                                         | 6-11 |

| A-1 | DC003 Signals                                                                                                   | A-4  |

| A-2 | DC004 Pin/Signal Descriptions                                                                                   | A-8  |

| A-3 | DC005 Pin/Signal Descriptions                                                                                   | A-9  |

| A-4 | DC367B Pin/Signal Descriptions                                                                                  | A-14 |

| A-5 | Baud Rate Accuracy                                                                                              | A-16 |

|     | 제품 것은 것은 그들을 것 같아요. 그는 것은 것은 것은 것을 많은 것은 것이 같아요. 그는 것은 것은 것은 것은 것은 것은 것은 것을 못했는 것을 하는 것을 수 있는 것을 했다. 것은 것은 것은 것 |      |

## CHAPTER 1 GENERAL DESCRIPTION

#### **1.1 INTRODUCTION**

The DZQ11 is a Q-bus option. Its outline is shown in Figure 1-1. The DZQ11 is an asynchronous multiplexer that interfaces between a Q-bus processor and four asynchronous serial data communication lines. It can be used in many applications such as data concentration, real-time processing, and cluster controlling. The DZQ11 communications interfaces are compatible with RS-232-C (V.28) and RS-423-A (V.10/X.26). There is enough modem control to permit dial-up (auto-answer) operation with full-duplex modems \*, such as the Bell models 103, 113, 212, or equivalent. Remote full-duplex working, as a control (master) station over private lines, is also possible for point-to-point or multipoint operation. Figure 1-2 shows some possible applications for the DZQ11 in a Q-bus system.

All the DZQ11 parameters can be easily controlled. These parameters are:

- Baud rate

- Character length

- Number of stop bits for each line

- Odd or even parity for each line

- Transmitter receiver interrupts.

Additional features include:

- Limited modem control

- Zero receiver baud rate

- Break generation and detection

- Silo buffering of received data

- Line turnaround.

The DZQ11 is program-compatible with the Q-bus DZV11 and with the UNIBUS option DZ11-A. The only exception is the number of serial lines supported. The DZQ11 does not support 20 mA operation.

Documents describing the DZQ11 are:

- DZQ11 Asynchronous Multiplexer User's Guide EK-DZQ11-UG

- DZQ11 Asynchronous Multiplexer Technical Manual EK-DZQ11-TM

- Field Maintenance Printset MP01795

- DZQ11 Maintenance Card EK-DZQ11-MC

<sup>\*</sup> The DZQ11 modem control does not support half-duplex operation or the secondary transmit-and-receive operation available on some modems (such as the Bell 202).

## CHAPTER 1 GENERAL DESCRIPTION

#### **1.1 INTRODUCTION**

The DZQ11 is a Q-bus option. Its outline is shown in Figure 1-1. The DZQ11 is an asynchronous multiplexer that interfaces between a Q-bus processor and four asynchronous serial data communication lines. It can be used in many applications such as data concentration, real-time processing, and cluster controlling. The DZQ11 communications interfaces are compatible with RS-232-C (V.28) and RS-423-A (V.10/X.26). There is enough modem control to permit dial-up (auto-answer) operation with full-duplex modems \*, such as the Bell models 103, 113, 212, or equivalent. Remote full-duplex working, as a control (master) station over private lines, is also possible for point-to-point or multipoint operation. Figure 1-2 shows some possible applications for the DZQ11 in a Q-bus system.

All the DZQ11 parameters can be easily controlled. These parameters are:

- Baud rate

- Character length

- Number of stop bits for each line

- Odd or even parity for each line

- Transmitter receiver interrupts.

Additional features include:

- Limited modem control

- Zero receiver baud rate

- Break generation and detection

- Silo buffering of received data

- Line turnaround.

The DZQ11 is program-compatible with the Q-bus DZV11 and with the UNIBUS option DZ11-A. The only exception is the number of serial lines supported. The DZQ11 does not support 20 mA operation.

Documents describing the DZQ11 are:

- DZQ11 Asynchronous Multiplexer User's Guide EK-DZQ11-UG

- DZQ11 Asynchronous Multiplexer Technical Manual EK-DZQ11-TM

- Field Maintenance Printset MP01795

- DZQ11 Maintenance Card EK-DZQ11-MC

<sup>\*</sup> The DZQ11 modem control does not support half-duplex operation or the secondary transmit-and-receive operation available on some modems (such as the Bell 202).

ŕ.

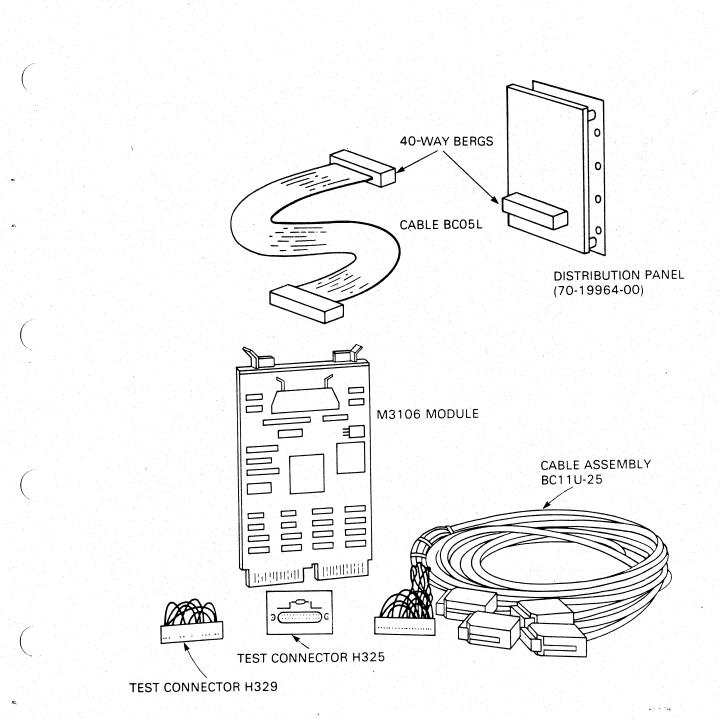

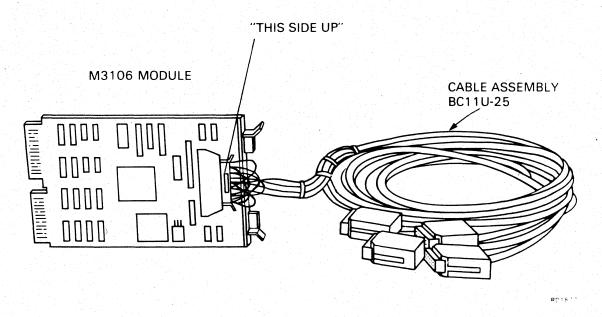

Figure 1-1 M3106 Module

#### **1.2 PHYSICAL DESCRIPTION**

The DZQ11 is made up of two components connected by a ribbon cable. The components are:

- 1. A single dual-height module,  $21.6 \times 13.2$  cm ( $8.51 \times 5.19$  inches), called the M3106 module. All input and output connections are available on a Berg \* header. This module includes all active circuitry as well as the line drivers and receivers.

- 2. A distribution panel  $6.7 \times 8.5$  cm ( $2.6 \times 3.3$  in) which contains four filtered D-type connectors and a Berg header. This header connects to the M3106 by means of a 40-way ribbon connector.

#### NOTE

A G7272 Grant Continuity card may be needed. Refer to Section 2.3.2 for an explanation.

Figure 1-2 DZQ11 System Applications

<sup>\*</sup> Berg is a registered trademark of the Berg Corporation.

#### 1.2.1 DZQ11 Configurations

The basic option supplied is the DZQ11-M and is made up of the following:

| 1. | Logic Module M3106             |  |

|----|--------------------------------|--|

| 2. | User's Guide EK-DZQ11-UG       |  |

| 3. | Maintenance Card EK-DZQ11-MC   |  |

| 4. | Turnaround test connector H329 |  |

The basic option (DZQ11-M) can be supplied with one of five cabinet kits for installation into different systems. These are:

- 1. CK-DZQ11-DA (21-inch cable), example of use PDP-11/23S

- 2. CK-DZQ11-DB (12-inch cable), example of use Micro/PDP-11

- 3. CK-DZQ11-DC (30-inch cable), example of use PDP-11/23+

- 4. CK-DZQ11-DF (36-inch cable), example of use PDP-11/83

- 5. CK-DZQ11-D3 unshielded option (BC11U-25 cable).

The first four cabinet kits are almost identical except for the length of the flat ribbon cables, and the addition of an adapter plate in the CK-DZQ11-DC. They are made up of the following:

- 1. BC05L-xx cable (see NOTE)

- 2. H325 line-loopback connector

- 3. The distribution panel -70-19964-00

- 4. Mounting bolts and washers for the distribution panel.

A system integrated DZQ11 option is a DZQ11-DP.

#### NOTE

The distribution panels provide noise filtering and static discharge protection on the communications lines. The -DC version has an adapter plate which allows the panel to be mounted in the PDP-11/23+.

BC05L-xx cables are supplied in different lengths for each kit as previously specified.

The CK-DZQ11-D3 cabinet kit is a cable assembly made up of four cables, with D-type connectors at one end, and the other end connected to a socket which fits in the module connector. This kit does not provide noise filtering or static discharge protection on the communications lines.

Figure 1-3 Elements of the DZQ11 Option

#### 1.2.2 Interface Cables

The connections from the DZQ11 use 25-pin male subminiature D-type connectors as specified for RS-232-C.

| Circuit AA (CCITT* 101)  | Pin 1  |

|--------------------------|--------|

| Circuit AB (CCITT 102)   | Pin 7  |

| Circuit BA (CCITT 103)   | Pin 2  |

| Circuit BB (CCITT 104)   | Pin 3  |

| Circuit CD (CCITT 108.2) | Pin 20 |

| Circuit CE (CCITT 125)   | Pin 22 |

| Circuit CF (CCITT 109)   | Pin 8  |

Protective Ground Signal Ground Transmitted Data Received Data Data Terminal Ready Ring Indicator Carrier

#### NOTE

# Signal ground and protective ground are connected together, through the chassis, by jumper W1 on the 70-19964-00 distribution panel.

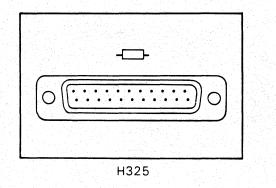

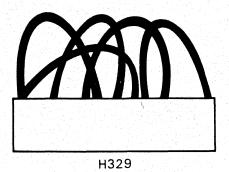

#### 1.2.3 Test Connectors

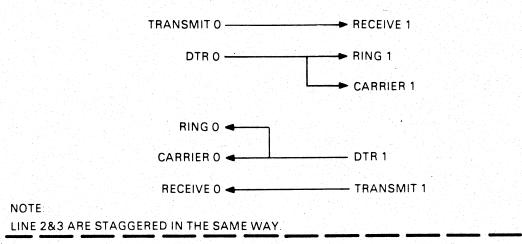

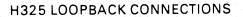

Figure 1-4 shows the two accessory test connectors, H329 and H325.

The H329 plugs into the module I/O connector and connects line 0 to line 1, and line 2 to line 3.

The H325 plugs into an EIA connector on the distribution panel, or BC11U-25 cable assembly, to loopback data and modem signals over a single line. The loopback connections are shown in Figure 1-5.

BD1851

Figure 1-4 Test Connectors H325 and H329

<sup>\*</sup> CCITT – The International Consultative Committee for Telegraphy and Telephony is an advisory committee created under the United Nations to recommend worldwide standards.

BO15 F

#### **1.3 SPECIFICATIONS**

Environmental, electrical, and performance specifications for the DZQ11 are listed in the following paragraphs.

#### 1.3.1 Environmental

| Storage temperature   | 0 degrees C to 66 degrees C<br>(32 degrees F to 151 degrees F)  |

|-----------------------|-----------------------------------------------------------------|

| Operating temperature | 5 degrees C to 60 degrees C<br>(41 degrees F to 140 degrees F)  |

| Relative humidity     | 10% to 95% non-condensing                                       |

| 1.3.2 Electrical      |                                                                 |

| Power consumption     | 1.100 A at $+$ 5 V dc typical<br>0.236 A at $+$ 12 V dc typical |

| Q-bus loading         | Q-bus ac loads – 1.5 ac loads                                   |

#### 1.3.3 Performance

The following paragraphs describe the DZQ11 performance capabilities and restrictions.

O-bus dc loads

**1.3.3.1** Interfaces – The DZQ11 interfaces with the host computer bus and also with the four data communication lines.

1. System Bus Interface

The DZQ11 module interfaces directly to a Q22 or other Q-bus via connectors A and B. The module meets the DIGITAL Q-bus specification.

1.0 dc loads

2. Serial Interfaces

The DZQ11 serial interfaces comply with a subset of EIA/CCITT standards RS-232-C/V.24. The electrical characteristics are compatible with EIA/CCITT standards RS-232-C/V.28 and RS-423/V.10 (unbalanced interface).

**1.3.3.2 Maximum Configurations** – The DZQ11 multiplexer is assigned a device address in the floating address space. The floating address space starts at  $760010_8$  and extends to  $763776_8$ . Maximum configuration of DZQ11s is not limited by floating address space, but is limited by the rules controlling a system configuration of average size.

As the DZQ11 needs one backplane AB slot-pair, it is physically possible to mount:

- Two M3106 modules in a PDP-11/23-S

- Three M3106 modules in a Micro/PDP-11

- Four to five M3106 modules in a PDP-11/23+

These numbers are the absolute maximum, because of the limited number of 70-19964-00 distribution panels that can be installed in the rear panel of the mounting box. These numbers may also be limited by the available capacity of the power supply, if other options are installed in the mounting box.

**1.3.3.3** Throughput – Each DZQ11 is capable of a throughput of 10 970 characters per second (chars/s). This rate is computed as follows.

(Bits/s  $\times$  number of lines  $\times$  directions) divided by bits/char

$(9.600 \times 4 \times 2)/7$  equals 10.970 chars/s, at 5 bits/char with one start and one stop bit and no parity.

The full device throughput can only be maintained when a character service routine takes 100 microseconds or less.

The DZQ11 has a maximum non-standard data rate of 19 800 baud. At this rate the throughput is 22 625 characters per second.

**1.3.3.4** Receivers – The receivers perform serial-to-parallel conversion of 5-, 6-, 7-, or 8-level code with one start bit and at least one stop bit. The character length, number of stop bits, parity generation, and operating speed are programmable parameters for each line. Both the receiver and the transmitter of a corresponding line share the same operating speed, and the receiver line can be enabled or disabled.

Each receiver is double buffered and has an acceptable input distortion of 43.75% on any bit. The sum of the character distortion must also not exceed 43.75%. An exception to this is the stop bit. The stop bit can tolerate an error of 50%, that is, the receiver will accept a stop bit as short as one half of a bit period. Break detection is provided on each receiver via a register bit. In addition, the configuration of switchpack E13-9 and E13-10 can cause the processor to boot or halt when a break is detected on line 3.

**1.3.3.5** Transmitters – The transmitters provide parallel-to-serial conversion of 5-, 6-, 7- or 8-level code with or without parity. The parity sense, when selected, can be either odd or even. The stop code can be either 1 or 2 units except when 5-level code is selected. When 5-level code is selected, the stop code can be set to 1 or 1.5 units. The character length, number of stop units, parity generation and sense, and operating speed are programmable parameters for each line. The operating speed for the transmitter is common with the receiver. Breaks can be transmitted on any line. The maximum start-stop distortion for the output of a transmitter is less than 2.5% for an 8-bit character.

**1.3.3.6** Baud-Rate Generator – The baud-rate generators are completely programmable. Each line has an independent generator which can select 1 of 16 baud rates. Speed tolerance for all rates is better than 0.3%. The baud rates are shown in Section 1.3.3.7.

**1.3.3.7 Performance Summary** – The following list shows the programmable features offered for each line.

| Character length    | 5-, 6-, 7-, or 8-level code                                                                                                                           |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of stop bits | 1 or 2 for 6-, 7-, or 8-level code.<br>1 or 1.5 for 5-level code                                                                                      |

| Parity              | Odd, even, or none                                                                                                                                    |

| Baud rates          | 50, 75, 110, 134.5, 150, 300, 600, 1 200, 1 800, 2 000, 2 400, 3 600, 4 800, 7 200, and 9 600 (and non-standard 19 800)                               |

| Breaks              | Can be generated and detected on each line                                                                                                            |

|                     | Line 3 has a hardware response to detected breaks which, when<br>enabled, may generate a HALT or RESET. This facility can be<br>selected by switches. |

#### 1.3.4 Interrupts

The following interrupts are available on the DZQ11.

**1.3.4.1** Receiver-Done Interrupt – The receiver-done interrupt occurs every time a character appears at the output of the receiver buffer register and the silo alarm is disabled. The receiver-done interrupt can be enabled or disabled from the bus.

**1.3.4.2** Silo-Alarm Interrupt – The silo-alarm interrupt occurs after 16 entries have been made into the receive buffer register by the scanner. This interrupt disables the receiver-done interrupt, and is armed again when the receive buffer register has been read.

**1.3.4.3** Transmit Interrupt – The transmit interrupt occurs every time the scanner finds a bufferempty condition, and the transmitter control register bit is set for that line. It can be enabled or disabled from the bus.

## CHAPTER 2 INSTALLATION

#### 2.1 SCOPE

This chapter contains the procedures for the unpacking, installation, and initial checkout of the DZQ11 asynchronous multiplexer. It contains information on the following:

- Device and vector address selection

- Recommended cables

- Testing after installation

- Floating address and vector assignment.

#### 2.2 UNPACKING AND INSPECTION

The DZQ11 is packed following normal commercial packing practices. To unpack, first remove all packing material and check the equipment against the shipping list. (Table 2-1 contains a list of supplied items per configuration.) Report any damage or shortages to the shipper immediately and inform the local DIGITAL office. Examine all parts and carefully examine the module for damage, loose components, and breaks in the etched paths.

#### CAUTION

The M3106 is supplied in a protective sleeve. Do not remove the sleeve until you are about to install the module. Protect the module from static during installation.

#### WARNING

Procedures which call for the removal of the system covers should be performed by trained personnel only. Information on such procedures is included for user information only.

| Description                                                             | Quantity                     |             |    |    |    |  |  |  |

|-------------------------------------------------------------------------|------------------------------|-------------|----|----|----|--|--|--|

| M3106 module<br>H329 test connector<br>DZQ11 User's Guide (EK-DZQ11-UG) |                              | 1<br>1<br>1 |    |    |    |  |  |  |

| CK-DZQ11-DA/DB/DC/D3/DF Cabinet kits                                    | Qua                          | ntity       |    |    |    |  |  |  |

| Description                                                             | DA                           | DB          | DC | D3 | DF |  |  |  |

| 70-19964-00 distribution panel                                          | 1                            | 1           | 1  | -  | 1  |  |  |  |

| 74-28684-01 adapter plate                                               |                              | -           | 1  | -  |    |  |  |  |

| BC05L-1K 21-inch cable                                                  | 1                            |             |    | -  | -  |  |  |  |

| BC05L-01 12-inch cable                                                  | 가는 가격을 가지.<br>같이 있는 것으로 들었다. | 1           |    | -  | -  |  |  |  |

| BC05L-2F 30-inch cable                                                  |                              |             | 1  |    | -  |  |  |  |

| BC11U-25 cable assembly                                                 |                              | -           |    | 1  | -  |  |  |  |

| BC05L-03 36-inch cable                                                  |                              |             | -  | -  | 1  |  |  |  |

| H325 test connector                                                     | 1                            | 1           | 1  | 1  | 1  |  |  |  |

| 90-06633-00 screws                                                      | 4                            | 4           | 8  | -  | 4  |  |  |  |

| 90-06021-01 washers                                                     | 4                            | 4           | 8  | _  | 4  |  |  |  |

#### Table 2-1 Items Supplied per Configuration

#### 2.3 INSTALLATION PROCEDURE

The following paragraphs describe the installation of the DZQ11 option in a Q-bus system.

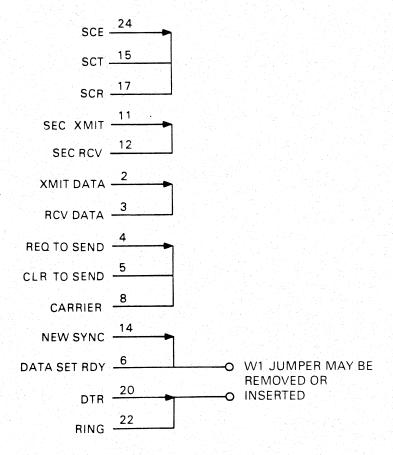

#### 2.3.1 Modem Control Jumpers

There are eight jumpers used for modem control (Figure 2-1). The jumpers labelled W1 to W4 connect the Data Terminal Ready (DTR) circuit to the Request To Send (RTS) circuit. This allows the DZQ11 to assert both DTR and RTS when using modems that need control of RTS. These jumpers must be installed for running the cable and external diagnostic programs. The four jumpers W5 to W8 connect the Forced Busy (FB) circuits to the RTS circuits. When these jumpers are installed, asserting an RTS circuit also places an ON or BUSY level on the corresponding FB circuit. Jumpers W5 to W8 are normally cut out unless they are needed by the modems used. Table 2-2 shows the jumper line assignments.

Figure 2-1 Jumper Location on M3106 Module

| Jumper     | Connection Line |

|------------|-----------------|

| <b>W</b> 1 | DTR to RTS 3    |

| <b>W</b> 2 | DTR to RTS 2    |

| <b>W</b> 3 | DTR to RTS 1    |

| W4         | DTR to RTS 0    |

| <b>W</b> 5 | RTS to FB 3     |

| <b>W</b> 6 | RTS to FB 2     |

| <b>W</b> 7 | RTS to FB 1     |

| <b>W</b> 8 | RTS to FB 0     |

|            |                 |

Table 2-2

Jumper Configuration

#### 2.3.2 Module Installation

To install the M3106 module, perform the following.

#### NOTE

This checkout procedure should be performed by trained maintenance personnel only.

#### CAUTION

Switch off power before inserting or removing modules.

The M3106 is a fine-line-etch PCB. Handle it carefully to avoid damaging the etch.

#### Take anti-static measures to protect the module.

- 1. The Q-bus Interrupt Acknowledge and the DMA Grant signals are daisy-chained through the AB slots of the Q-bus backplane. If a DZQ11 is followed by a quad-size option in an AB/AB (Q/Q) backplane, it may cause an AB slot-pair to be left vacant. In order to maintain the continuity of the daisy-chained signals, a G7272 Grant Continuity card should be installed in the vacant A slot.

- 2. Refer to Section 2.4 for descriptions of the address assignments. Set the switches at E28 so that the module responds to its assigned address. When a switch is closed (ON), a binary 1 is encoded. When a switch is open (OFF), a binary 0 is encoded. The switch numbered 1 is connected to address bit 12, 2 is connected to address bit 11, and so on (Table 2-4).

- 3. The 10-position switch at E13 performs the vector selection. Switch position 7 is not used. Switch position 6 is connected to vector bit 3, 5 is connected to vector bit 4, and so on. When a switch is closed (ON), binary 1 is encoded. When a switch is open (OFF), a binary 0 is encoded (Table 2-5).

- 4. Position 8 of the vector selection switch is a test switch which can disconnect the DZQ11 oscillator from all circuitry. Make sure that this switch is in the ON position before installation.

- 5. Positions 9 and 10 of switch E13 control the DZQ11 response to a Break character received on Line 3. There are three valid options: HALT, BOOT, and no response. Table 2-3 lists the switch selections.

| Swit<br>9 | ich<br>10 | Effect of Break Character | on Line 3              |

|-----------|-----------|---------------------------|------------------------|

| OFF       | OFF       | No effect                 | (normal operation)     |

| ON        | OFF       | Causes Processor to halt  | (specific application) |

| OFF       | ON        | Causes Processor to boot  | (specific application) |

| ON        | ON        | Illegal Condition         |                        |

Table 2-3 Break Character Response Options

- Make sure that +5 volts is present between AA2 and ground and that +12 volts is present between AD2 and ground. Measure at the nearest accessible point, if the backplane cannot be accessed.

- 7. Remove power and insert the module in an AB slot of the backplane.

- 8. Apply power and make sure that the +5 volts and +12 volts is present with the module installed.

#### CAUTION

Insert and remove modules slowly and carefully to prevent damage to the module components on the card guides, and to avoid changing switch selections in error.

Figure 2-2 DZQ11 Installation (BC11U-25)

|         | •  | MSB |       |          |          |     |     |      |      |                   |    |     |           |     |                 |              | LSB |

|---------|----|-----|-------|----------|----------|-----|-----|------|------|-------------------|----|-----|-----------|-----|-----------------|--------------|-----|

| 1. C.V. | 16 | 15  | 14    | 13       | 12       | 11  | 10. | 9    | 8    | 7                 | 6  | 5   | 4         | 3   | 2               | 1            | 0   |

|         | 1  | 1   | 1     | 1        |          |     |     | — sv | итсн | ES —              |    |     | •         | 0   | 0               | 0            | 0   |

|         |    |     |       |          | <b> </b> |     | l   |      |      |                   |    |     | l         |     |                 |              |     |

|         |    |     |       |          | <br>     |     |     |      |      |                   |    |     |           |     |                 |              |     |

|         |    |     | VITCH |          | E28      | E28 | E28 | E28  | E-28 | E28               |    | E28 | E28       | E28 |                 | VICE         |     |

|         |    |     | JMBE  | <u>R</u> |          | 2   | 3   | 4    | 5    | 6                 | 7  | 8   | 9         | 10  |                 | DDRE         |     |

|         |    |     |       |          |          |     |     |      |      |                   |    |     |           |     |                 | 7600         |     |

|         |    |     |       |          |          |     |     |      |      |                   |    |     |           | ON  |                 | 7600         |     |

|         |    |     |       |          |          |     |     |      |      |                   |    |     | ON<br>ON  | ON  |                 | 7600<br>7600 |     |

|         |    |     |       |          |          |     |     |      |      | lata a s<br>Citat |    | ON  |           |     |                 | 7600         |     |

|         |    |     |       |          |          |     |     |      |      |                   |    | ON  |           | ON  |                 | 7600         |     |

|         |    |     |       |          |          |     |     |      |      |                   |    | ON  | ON        |     |                 | 7600         |     |

|         |    |     |       |          |          |     |     |      |      |                   |    | ON  | ON        | ON  | 17              | 7600         | 70  |

|         |    |     |       |          |          |     |     |      |      |                   | ON |     |           |     | 17              | 7601         | 00  |

|         |    |     |       |          |          |     |     |      |      | ON                |    |     |           |     | 17              | 7602         | 00  |

|         |    |     |       |          |          |     |     |      |      | ON                | ON |     |           |     | 17              | 7603         | 00  |

|         |    |     |       |          |          |     |     |      | ON   |                   |    |     |           |     | 17              | 7604         | 00  |

|         |    |     |       |          |          |     |     |      | ON   |                   | ON |     |           |     | 17              | 7605         | 00  |

|         |    |     |       |          |          |     |     |      | ON   | ON                |    |     |           |     | 17              | 7606         | 00  |

|         |    |     |       |          |          |     |     |      | ON   | ON                | ON |     |           |     | 1.1.1.1.1.1.1.1 | 7607         |     |

|         |    |     |       |          |          |     | ON  | ON   | ON   | ON                | ON | ON  | ON        |     | 17              | 7637         | 60  |

|         |    |     |       |          |          |     | ON  | ON   | ON   | ON                | ON | ON  | ON        | ON  | 17              | 7637         | 70  |

|         |    |     |       |          |          |     |     |      |      |                   |    |     | L <u></u> |     |                 |              |     |

### Table 2-4 Address Switch Selection

ON = SWITCH CLOSED TO RESPOND TO A LOGICAL 1 ON THE BUS

RD1818

| Table | 2-5 | Vector | Switch | Selection |  |

|-------|-----|--------|--------|-----------|--|

|       |     |        |        |           |  |

| MSE | 3  |    |    |    |    |   |   |   |      | •    |             |   |     |   | LSB |

|-----|----|----|----|----|----|---|---|---|------|------|-------------|---|-----|---|-----|

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6    | 5    | 4           | 3 | 2   | 1 | 0   |

| 0   | 0  | 0  | 0  | 0  | 0  | 0 |   | • | SWIT | CHES | •<br>•<br>• | > | 1/0 | 0 | 0   |

|     |    | 4  | •  |    |    |   |   | 1 | I    | I    |             | l |     |   |     |

|     |    |    |    |    |    |   |   |   |      |      |             |   |     |   |     |

| 같이 제 같은 물건이 가지요.                                             |                  |                            |                                              | l                                            |                      | l i serie s          |                |                                                                                                |

|--------------------------------------------------------------|------------------|----------------------------|----------------------------------------------|----------------------------------------------|----------------------|----------------------|----------------|------------------------------------------------------------------------------------------------|

|                                                              | SWITCH<br>NUMBER | E13<br>1                   | E13<br>2                                     | E13<br>3                                     | E13<br>4             | E13<br>5             | E13<br>6       | VECTOR<br>ADDRESS                                                                              |

| REFER TO<br>SECTION 2.3.2<br>FOR SETTING<br>OF E13 - 7 TO 10 |                  | ON<br>ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON<br>ON<br>ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON<br>ON<br>ON<br>ON<br>ON<br>ON | ON<br>GN<br>ON<br>ON | ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON | 300<br>310<br>320<br>330<br>340<br>350<br>360<br>370<br>400<br>500<br>600<br>700<br>760<br>770 |

| ONI CIAUT                                                    | CULCLOCED TO     | DDOD                       | LICE                                         | 1100                                         |                      | 1 01                 | TUE            | DUC                                                                                            |

ON = SWITCH CLOSED TO PRODUCE A LOGICAL 1 ON THE BUS

RD1819

RD1852

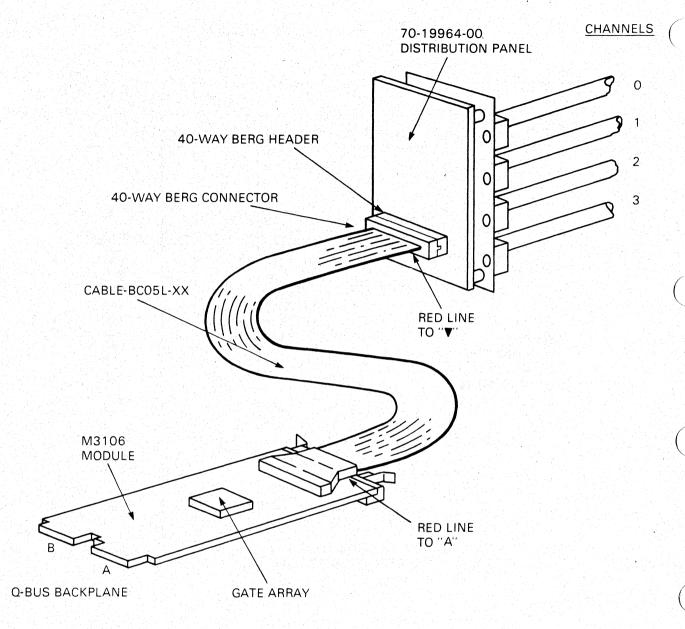

Figure 2-3 DZQ11 Installation (70-19964-00)

#### 2.3.3 Testing DZQ11s in PDP-11 Systems

The following diagnostics are available to test DZQ11s installed in PDP-11 systems. DZITA and DVDZD are only used when a link between two processors is to be tested.

| CVDZA | DZV11/DZQ11 Logic Test – Part 1    |

|-------|------------------------------------|

| CVDZB | DZV11/DZQ11 Logic Test – Part 2    |

| CVDZC | DZV11/DZQ11 Cable/Echo Test        |

| CXDZB | DECX/11 Module                     |

| DZITA | Interprocessor Test Program (ITEP) |

| DVDZD | Overlay for ITEP                   |

Test the option as follows.

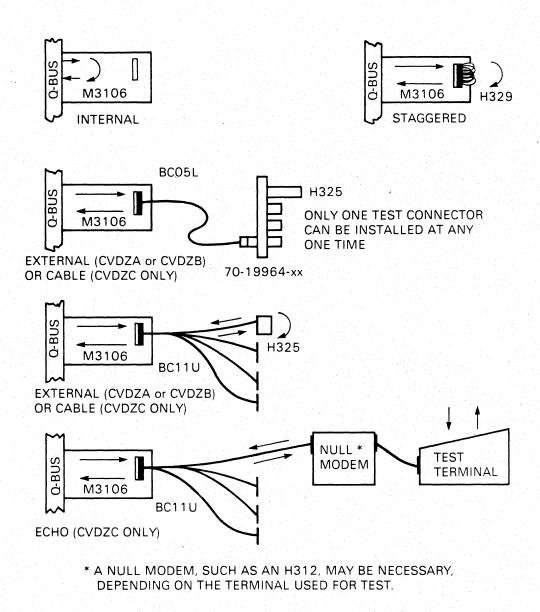

- 1. Run diagnostics CVDZA and CVDZB in internal mode, to verify operation. Refer to the listing for more help. Run at least three passes without error.

- 2. Insert the H329 test connector in J1 with the letter side facing up. J1 is the cable connector at the top of the M3106 module.

Run CVDZA and CVDZB in the staggered mode, to verify module operation. Refer to the diagnostic listing for the correct procedure. Run at least three passes without error.

- 3. If the unshielded cab-kit (D3) version is used, replace the H329 test connector with the Berg end of the BC11U cable assembly. Follow the 'This side up' instruction on the assembly. Refer to Figure 2-2 for assembly and interconnection instructions.

- 4. If the cab-kit versions CK-DZQ11-DA, -DB or -DF are used, feed the cable through the rear of the cabinet and connect the Berg plug to the distribution panel. Mount the distribution panel in the opening at the rear of the cabinet.

The -DC version is provided with an adapter plate to fit the large opening in a PDP-11/23+. Mount the adapter plate on the distribution panel, with four of the eight screws provided. Mount the distribution panel as described above.

- 5. Connect the H325 test connector on the first line and run diagnostic CVDZC. Select the cabletest part of the diagnostic. Three passes are needed without error. Repeat this step for each line.

- 6. Run the DECX/11 system exerciser to verify the absence of Q-bus interference with other system devices.

- 7. The DZQ11 is now ready for connection to external equipment. If the connection is to a local terminal through either of the two options (BC11U-25 or 70-19964-00), a null modem cable assembly must be used. Use the BC22A, BC22D, or BC03P null modem cables for connection between the option and the terminal. The H312-A null modem unit may also be used in place of the null modem cables.

Connections between the option and a modem should be made using a BC22E or BC05D cable.

All of the cables referred to, with the exception of the BC11U-25, must be ordered separately as they are not components of a DZQ11 option.

If a terminal is available, run the diagnostic CVDZC in echo-test mode to verify the cable connections and the terminal equipment.

#### 2.3.4 Testing in MicroVAX Systems

The following diagnostic tests are available for testing DZQ11s in MicroVAX systems.

EHXDZ DZV11/DZQ11 Test EHKMV Macroverify – MicroVAX System Test

Macroverify is a standalone diagnostic which contains a DZV11/DZQ11 test module.

Refer to the appropriate diagnostic listing, or to Chapters 11 and 14 of the MicroVAX Owner's Guide, for details of how to run EHXDZ and EHKMV.

Test the option as follows.

- 1. Boot from the MicroVAX system tests diskette (number 2 of 2). Attach and select the DZQ11 that is to be tested.

- 2. Run EHXDZ for three error-free passes of the internal (default) test.

- 3. Install the H329 staggered loopback connector on the M3106 module. Run EHXDZ for three error-free passes of the staggered test.

- 4. Remove the H329. Install the BC05L cable and the distribution panel.

- 5. If the operation of a terminal link is to be tested, connect the terminal line to the distribution panel. Run the EHXDZ echo test on that line until the link is proven. Depending on the terminal, a null-modem may be needed for this test. Exit echo test by ^Z (CTRL/Z).

- 6. Remove all external cables and connectors from the distribution panel. Boot the CPU tests diskette (number 1 of 2). The Macroverify diagnostic will run automatically when the boot process is complete. When the test completes, the status of all options will be displayed.

- 7. If no device has a TEST FAILED status, the DZQ11 is now ready for connection to external equipment. If the connection is to a local terminal, a null modem cable assembly must be used. Use the BC22A, BC22D, or BC03P null modem cables for connection between the option and the terminal. The H312-A null modem unit may also be used in place of the null modem cables.

Connections between the option and a modem should be made using a BC22E or BC05D cable.

All of the referenced cables must be ordered separately as they are not components of a DZQ11 option.

#### 2.4 DEVICE ADDRESS ASSIGNMENTS

On UNIBUS and Q-bus systems, a range of addresses  $(xxx60010_8 \text{ to } xxx63776_8)$  in the top 4K words is assigned as floating address space (xxx means all top address bits = 1).

The first part of the list of options (sufficient to include the DZQ11) which can be assigned floating device addresses is given in Table 2-6. 'Rank' gives the sequence of address assignment for both Q-bus and UNIBUS options.

If addresses are assigned according to defined rules, configuration programs can check which options are installed in a system. Having a combined list allows us to use one set of configuration rules and one configuration program for both Q-bus and UNIBUS systems.

| Rank | Device                                | Size<br>(decimal) | Modulus<br>(octal) |

|------|---------------------------------------|-------------------|--------------------|

| 1    | DJ11                                  | 4 words           | 10                 |

| 2    | DH11                                  | 8 words           | 20                 |

| 3    | DQ11                                  | 4 words           | 10                 |

| 4    | DU11, DUV11*                          | 4 words           | 10                 |

| 5    | DUP11                                 | 4 words           | 10                 |

| 6    | LK11A                                 | 4 words           | 10                 |

| 7    | DMC11/DMR11                           | 4 words           | 10                 |

| 8    | DZ11, DZS11,<br>DZQ11*/DZV11*<br>DZ32 | 4 words           | 10                 |

#### Table 2-6 Floating Address Assignments

#### \* Q-bus device

For example, the address assignment sequences could be:

| UNIBUS       | Q-bus                        |

|--------------|------------------------------|

| <b>DJ</b> 11 | No Q-bus equivalent of DJ11  |

| DH11         | No Q-bus equivalent of DH11  |

| DQ11         | No Q-bus equivalent of DQ11  |

| DÙ11         | DUV11                        |

| DUP11        | No Q-bus equivalent of DUP11 |

| LK11A        | No Q-bus equivalent of LK11A |

| DMC11        | No Q-bus equivalent of DMC11 |

| DZ11         | DZQ11 and so on.             |

Devices of the same type are given sequential addresses, therefore all DUV11s in a system will have lower addresses than DZQ11s or DZV11s.

For the purpose of address assignment, DZQ11s and DZV11s are considered as devices of the same type.

The column Size(decimal) in Table 2-6, shows how many words of address space are needed for each device. The column Modulus(octal) is the modulus used for starting addresses. For example, devices with an octal modulus of 10 must start at an address which is a multiple of  $10_8$ . The same rule is used to select a gap address (see assignment rules) after an option, or for a nonexistent device.

The assignment rules are as follows.

- 1. Addresses, starting at xxx60010, are assigned according to the sequence of Table 2-6

- 2. Option and gap addresses are assigned according to the octal modulus as follows.

- a. Devices with an octal modulus of 10 are assigned an address on a  $10_8$  boundary (the three lowest-order address bits = 0)

- b. Devices with an octal modulus of 20 are assigned an address on a  $20_8$  boundary (the four lowest-order address bits = 0)

- 3. Address space equal to the device's modulus must be allowed for each device which is connected to the bus

- 4. A one-word gap, assigned according to rule 2, must be allowed after the last device of each type. This gap could be bigger when rule 2 is applied to the following rank

- 5. A one-word gap, assigned according to rule 2, must be allowed for each unused rank on the list if a device with a higher address is used. This gap could be bigger when rule 2 is applied to the following rank

Two examples of address assignment follow. Table 2-7 shows addresses for a system with one DUV11 and one DZQ11. Table 2-8 shows addresses for a system with no DUV11 and two DZQ11s. Note that where there is no Q-bus device at a specific rank, the UNIBUS device parameters must be used to assign the gap. Vector assignments (see Section 2.5) are also shown in these tables.

Table 2-7 is supported by a description of how to apply the assignment rules.

| Rank | Address  | Designation | Vector                                                                                          |

|------|----------|-------------|-------------------------------------------------------------------------------------------------|

| 1    | xxx60010 | DJ11 gap    |                                                                                                 |

| 2    | xxx60020 | DH11 gap    |                                                                                                 |

| 3    | xxx60030 | DQ11 gap    |                                                                                                 |

| 4    | xxx60040 | DÙVII       | 300                                                                                             |

|      | xxx60050 | DUV11 gap   |                                                                                                 |

| 5    | xxx60060 | DUP11 gap   |                                                                                                 |

| 6    | xxx60070 | LK11A gap   | 사망가 가장 같은 것 같은 것 같은 것 같은 것이 같은 것이 있는 것 같은 것이다.<br>같은 것 같은 것이 다시 것은 것 같은 것 같은 것이 가지 않는 것이 같이 있다. |

| 7    | xxx60100 | DMC11 gap   |                                                                                                 |

| 8    | xxx60110 | DZQ11       | 310                                                                                             |

|      | xxx60120 | DZQ11 gap   |                                                                                                 |

| Table | 2-7 | One | DUV | 11 and | One | DZQ11                                                                                                            |

|-------|-----|-----|-----|--------|-----|------------------------------------------------------------------------------------------------------------------|

|       |     |     |     |        |     | and the second |

The first floating address is 760010. As a DJ11 has a modulus of  $10_8$ , its gap can be assigned to 760010. The next available location becomes 760012.

As a DH11 has a modulus of  $20_8$ , it cannot be assigned to 760012. The next modulo 20 boundary is 760020, so the DH11 gap is assigned to this address. The next available location is therefore 760022.

A DQ11 has a modulus of  $10_8$ . It cannot be assigned to 760022. Its gap is therefore assigned to 760030. The next available location is 760032.

The DUV11 has a modulus of  $10_8$ . It cannot be assigned to 760032. It is therefore assigned to 760040. As the size of DUV11 is four words, the next available address is 760050.

There is no second DUV11, so a gap must be left to indicate that there are no more DUV11s. As 760050 is on a 10<sub>8</sub> boundary. The DUV11 gap can be assigned to this. The next available address is 760052.

And so on.

| Rank | Address  | Designation | Vector |  |

|------|----------|-------------|--------|--|

| 1    | xxx60010 | DJ11 gap    |        |  |

| 2    | xxx60020 | DH11 gap    |        |  |

| 3    | xxx60030 | DQ11 gap    |        |  |

| 4    | xxx60040 | DUV11 gap   |        |  |

| 5    | xxx60050 | DUP11 gap   |        |  |

| 6    | xxx60060 | LK11A gap   |        |  |

| 7    | xxx60070 | DMC11 gap   |        |  |

| 8    | xxx60100 | 1 st DZQ11  | 300    |  |

| 8    | xxx60110 | 2nd DZQ11   | 310    |  |

|      | xxx60120 | DZQ11 gap   |        |  |

|      |          |             |        |  |

Table 2-8 Two DZQ11s

# 2.5 INTERRUPT VECTOR ADDRESS ASSIGNMENTS

Addresses between  $300_8$  and  $774_8$  are designated as the floating vector space. These addresses are assigned in sequence as in Table 2-9.

Each Device needs two 16-bit locations for each vector. For example, a device with one receive and one transmit vector needs four words of vector space.

The vector assignment rules are as follows.

- 1. Each device occupies vector address space equal to 'Size' words. For example, the DLV11-J occupies 16 words of vector space. If its vector was  $300_8$ , the next = available vector would be  $340_8$ .

- 2. There are no gaps, except those needed to align an octal modulus.

The vector addresses shown in Tables 2-7 and 2-8 are assigned according to these rules.

Table 2-9 First Part of Q-bus Vector Address Assignments List

| Device        | Size<br>(decimal) | Modulus<br>(octal) |

|---------------|-------------------|--------------------|

| DLV11-J       | 16                | 10                 |

| DLV11,DLV11-F | 4                 | 10                 |

| DRV11-B       | 4                 | 10                 |

| DRV11         | 4                 | 10                 |

| DLV11-E       | 4                 | 10                 |

| VSV11         | 8                 | 10                 |

| KWV11         | 4                 | 10                 |

| DUV11         | 4                 | 10                 |

| DZV11/DZQ11   | 4                 | 10                 |

# CHAPTER 3 DEVICE REGISTERS

### 3.1 SCOPE

This chapter describes the format and bit function of each register in the DZQ11.

## **3.2 DEVICE REGISTERS**

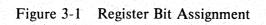

The DZQ11 contains six addressable registers. Figure 3-1 shows the bit assignments of these registers and Table 3-1 lists the registers and related DZQ11 addresses.

| Register Name            | Mnemonic | Address | Program<br>Capability |

|--------------------------|----------|---------|-----------------------|

| Control and Status Reg.  | CSR      | 76XXX0  | Read/Write            |

| Receiver Buffer          | RBUF     | 76XXX2  | Read Only             |

| Line Parameter Register  | LPR      | 76XXX2  | Write Only            |

| Transmitter Control Reg. | TCR      | 76XXX4  | Read/Write            |

| Modem Status Register    | MSR      | 76XXX6  | Read Only             |

| Transmit Data Register   | TDR      | 76XXX6  | Write Only            |

Table 3-1 DZQ11 Register Address Assignments

XXX = Selected in agreement with the floating device address system.

### 3.2.1 Control and Status Register

The control and status register (CSR) can be addressed with a byte or word address. All bits in the CSR are cleared by an occurrence of BINIT, or by setting device Master Clear (CSR < 04 >). The format is shown in Figure 3-1 and the bit assignments are listed in Table 3-2.

|      |                              | MSB<br>15           | 14                | 13                | 12                          | 11                       | 10                       | 09                    | BYT<br>HIGH<br>08        |                    | 06                | 05                 | 04                      | 03                               | 02                       | 01                             | LSB<br>00                |                                                                 |

|------|------------------------------|---------------------|-------------------|-------------------|-----------------------------|--------------------------|--------------------------|-----------------------|--------------------------|--------------------|-------------------|--------------------|-------------------------|----------------------------------|--------------------------|--------------------------------|--------------------------|-----------------------------------------------------------------|

| ۹۰ { | CONTROL<br>& STATUS<br>(CSR) | _RO<br>TRDY         | RW                | RO<br>SA          | RWSAE                       | 101 2357                 | USED -                   | RO<br>TLINE<br>B      | RO<br>TLINE<br>A         | <u>RO</u><br>RDONE | RW<br>RIE         | RW<br>MSE          | RW<br>CLR               | <u>RW</u><br>MAINT               | USED 1                   | USED                           | 100 roy                  |                                                                 |

| 12   | RECEIVER<br>BUFFER<br>(RBUF) | RO<br>DATA<br>VALID | RO<br>OVRN<br>ERR | RO<br>FRAM<br>ERR | RO<br>PAR<br>ERR            | 100                      | 10 in the                | RO<br>RX<br>LINE<br>B | RO<br>RX<br>LINE<br>A    | RO<br>RBUF<br>D7   | RO<br>RBUF<br>D6  | RO<br>RBUF<br>D5   | RO<br>RBUF<br>D4        | <u>RO</u><br>RBUF<br>D3          | RO<br>RBUF<br>D2         | RBUF                           | RO<br>RBUF<br>D0         |                                                                 |

|      | LINE<br>PARAMETER<br>(LPR)   | Nor<br>Vor          | 10350             |                   | WO<br>RX<br>ENAB            | WO<br>SPEED<br>CODE<br>D | WO<br>SPEED<br>CODE<br>C |                       | WO<br>SPEED<br>CODE<br>A | WO<br>ODD<br>PAR   | WO<br>PAR<br>ENAB | WO<br>STOP<br>CODE | WO<br>CHAR<br>LGTH<br>B | WO<br>CHAR<br>LGTH<br>A          | 104                      | WO<br>LINE<br>B                | WO<br>LINE<br>A          | ALL REGIST<br>BITS ARE<br>CLEARED BY<br>MASTER CL<br>EXCEPT FOF |

| 34   | TRANSMIT<br>CONTROL<br>(TCR) | USED I              | USED              | 104 53<br>104 53  | USE02                       | RW<br>DTR3               | RW<br>DTR<br>2           | _RW<br>DTR<br>1       | <u>RW</u><br>DTR<br>0    | USED               | USED              | USED               | USED                    | _ <u>RW</u><br>LINE<br>ENAB<br>3 | _RW<br>LINE<br>ENAB<br>2 | <u>RW</u><br>LINE<br>ENAB<br>1 | _RW<br>LINE<br>ENAB<br>0 | RBUF<14:0<br>TCR<15:08<br>MSR<15:00                             |

|      | MODEM<br>STATUS<br>(MSR)     | 101 NOT             | USED              | -0455             | 10255                       | RO<br>CO<br>3            | <u>RO</u><br>CO<br>2     | RO<br>CO<br>1         | RO<br>CO<br>0            | USED               | 10357<br>10357    | USED T             | 101<br>10250            | RO<br>RI 3                       | RO<br>RI 2               | RO<br>RI 1                     | RO<br>RI 0               |                                                                 |

|      | TRANSMIT<br>DATA<br>(TDR)    | 10250<br>USED       | USED              | 10255             | 101 55<br>102<br>102<br>102 | WO<br>BRK<br>3           | WO<br>BRK<br>2           | WO<br>BRK<br>1        | WO<br>BRK<br>0           | WO<br>TBUF<br>7    | WO<br>TBUF<br>6   | WO<br>TBUF<br>5    | WO<br>TBUF<br>4         | WO<br>TBUF<br>3                  | WO<br>TBUF<br>2          | WO<br>TBUF<br>1                | WO<br>TBUF<br>0          |                                                                 |

3-2

0552

| Bit     | Title                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <02:00> | Not used                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <03>    | Maintenance<br>(MAINT)                                 | This is a READ/WRITE bit. When set it loops the serial output connections of the transmitter to the corresponding serial input connections of the receiver at the UART. (Used for loopback test only.)                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <04>    | Master Clear<br>(CLR)                                  | When written to a 1, this bit generates 'initialize' within the DZQ11.<br>A read-back of the CSR with this bit set indicates initialize in<br>progress within the device. This bit is self-clearing. All registers,<br>silos, and UARTs are cleared with the following exceptions:                                                                                                                                                                                                                                                                                                                                     |

|         |                                                        | 1. Only bit 15 of the receiver buffer register (Data Valid) is cleared; the other bits (<14:00>) are not.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|         |                                                        | 2. The high byte of the transmitter control register is not cleared by Master Clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|         |                                                        | 3. The modem status register is not cleared by Master Clear.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <05>    | Master Scan<br>Enable<br>(MSE)                         | This read/write bit must be set to permit the receiver and transmitter control sections to start scanning. When cleared, Transmitter Ready $(CSR < 15>)$ is inhibited from setting, and the received character buffers (silos) are cleared.                                                                                                                                                                                                                                                                                                                                                                            |

| <06>    | Receiver<br>Interrupt<br>Enable<br>(RIE)               | This bit permits the generation of an interrupt, when $CSR < 07 >$ or $CSR < 13 >$ is set. This bit is read/write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

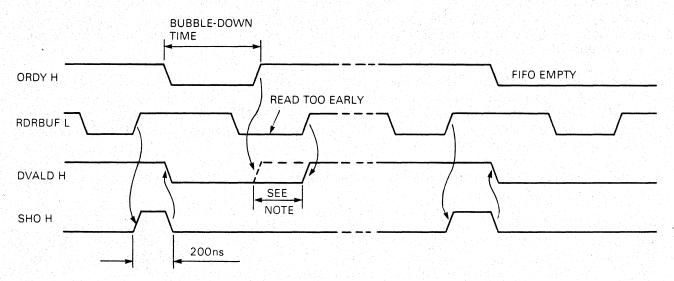

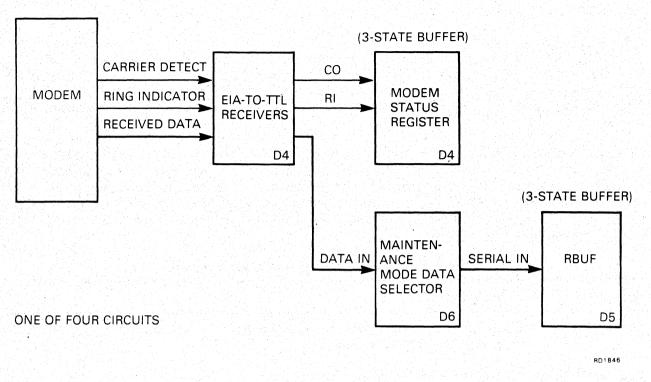

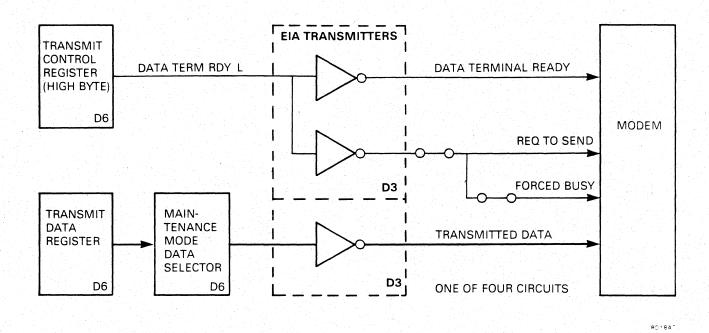

| <07>    | Receiver Done<br>(RDONE)                               | This is a read-only bit that is set when a character appears at the output of the first-in/first-out (FIFO) buffer. For the DZQ11 to run in the interrupt-per-character mode, $CSR<06>$ must be set and $CSR<12>$ must be cleared. With $CSR<06>$ and $CSR<12>$ cleared, character-flag mode is indicated. Receiver Done clears when the receiver buffer register (RBUF) is read or when Master Scan Enable ( $CSR<05>$ ) is cleared. If the FIFO buffer contains an additional character, the Receiver Done flag stays clear for up to 1 microsecond, while that character bubbles through to the bottom of the FIFO. |