DZ11 maintenance manual

PRELIMINARY

digital equipment corporation • maynard, massachusetts

Copyright © 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

## **CONTENTS**

|              | Pag                                  |

|--------------|--------------------------------------|

| CHAPTER 1    | GENERAL DESCRIPTION                  |

| 1.1          | INTRODUCTION                         |

| 1.2          | PHYSICAL DESCRIPTION                 |

| 1.2.1        | DZ11 Configurations                  |

| 1.2.2        | General Specifications               |

| 1.3          | FUNCTIONAL DESCRIPTION               |

| 1.3.1        | PDP-11 Unibus Interface              |

| 1.3.2        | Control Logic                        |

| 1.3.3        | Line Interface                       |

| CILA PETER A |                                      |

| CHAPTER 2    | INSTALLATION                         |

| 2.1          | SCOPE 2-                             |

| 2.2          | CONFIGURATION DIFFERENCES            |

| 2.3          | UNPACKING AND INSPECTION             |

| 2.4          | INSTALLATION PROCEDURE 2-7           |

| CHAPTER 3    | PROGRAMMING                          |

| 3.1          | INTRODUCTION                         |

| 3.2          | REGISTER BIT ASSIGNMENTS             |

| 3.2.1        | Control and Status Register (CSR)    |

| 3.2.2        | Receiver Buffer (RBUF)               |

| 3.2.3        | Line Parameter (LPR)                 |

| 3.2.4        | Transmit Control (TCR)               |

| 3.2.5        | Modem Status (MSR)                   |

| 3.2.6        | Transmit Data (TDR)                  |

| 3.3          | PROGRAMMING FEATURES 3-7             |

| 3.3.1        | Baud Rate                            |

| 3.3.2        | Character Length                     |

| 3.3.3        | Stop Bits                            |

| 3.3.4        | Parity 3-6                           |

| 3.3.5        | Interrupts                           |

| 3.3.6        | Emptying the Silo                    |

| 3.3.7        | Transmitting a Character             |

| 3.3.8        | Data Set Control                     |

| 3.4          | PROGRAMMING EXAMPLES                 |

| CHAPTER 4    | DETAILED DESCRIPTION                 |

| 4.1          | INTRODUCTION 4-                      |

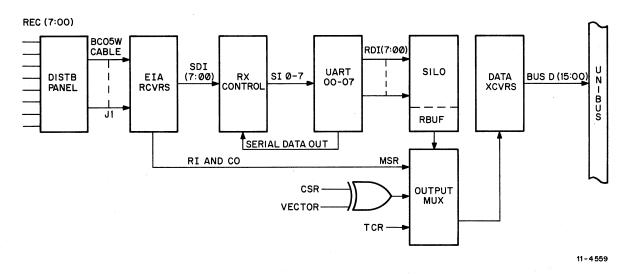

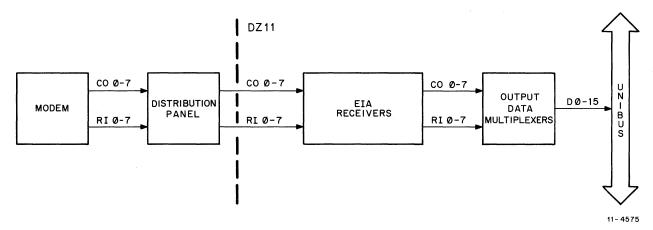

| 4.1.1        | Modem-To-Unibus Data Flow (Receive)  |

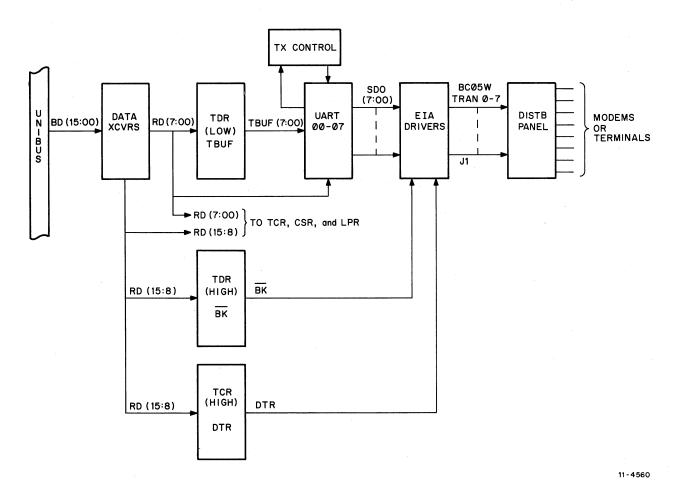

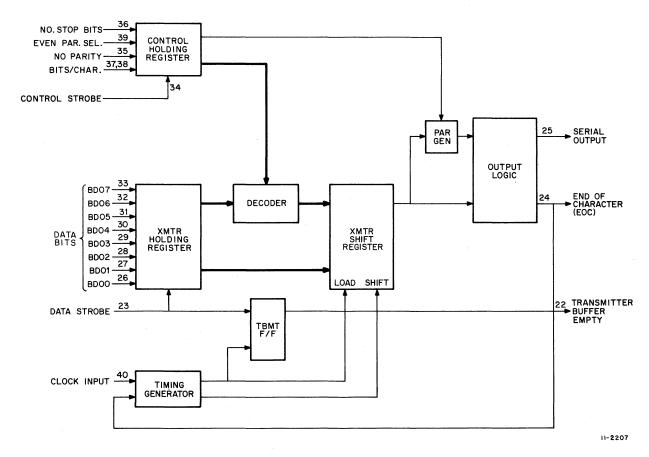

| 4.1.2        | Unibus-To-Modem Data Flow (Transmit) |

| 4.2          | UNIBUS INTERFACE                     |

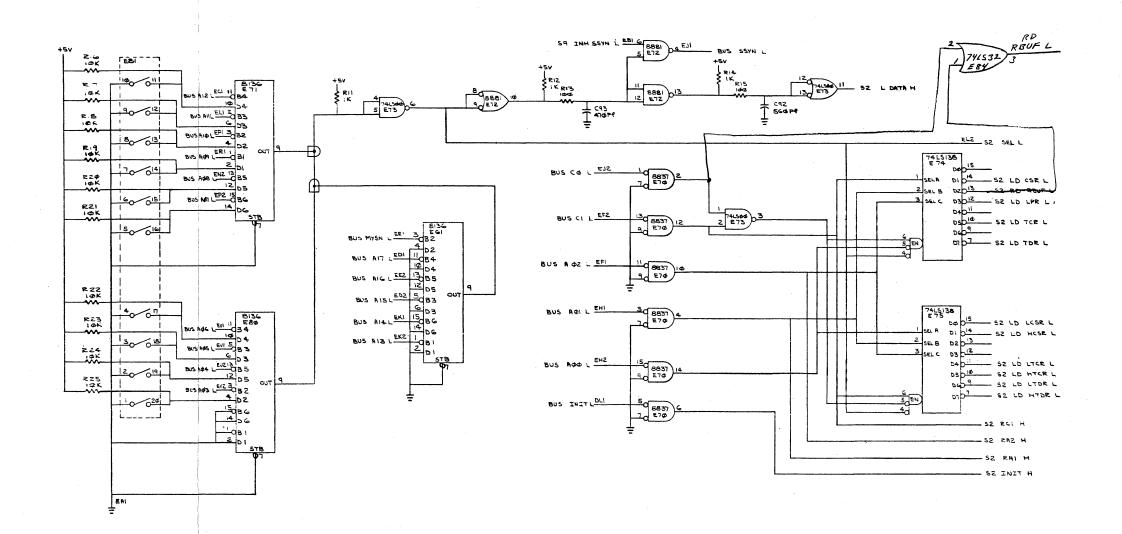

| 4.2.1        | Address Selection                    |

| 4.2.1.1      | Device Address Selection             |

| 4.2.1.2      | Register and Mode Selection          |

## **CONTENTS** (Cont)

|           |                                                      | Page   |

|-----------|------------------------------------------------------|--------|

| 4.2.2     | Interrupt Control                                    | 4-7    |

| 4.2.2.1   | Receiver Interrupt                                   |        |

| 4.2.2.2   | Transmitter Interrupt                                |        |

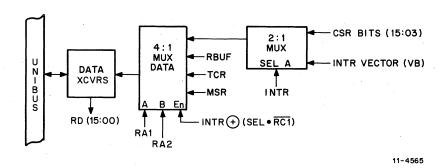

| 4.2.3     | Data Transceivers and Output Multiplexers            |        |

| 4.3       | SCANNER                                              |        |

| 4.3.1     | Receive Control                                      |        |

| 4.3.2     | Transmit Control                                     |        |

| 4.3.3     | Silo and UART Clocks                                 |        |

| 4.4       | REGISTERS                                            |        |

| 4.4.1     | Control and Status Register (CSR)                    |        |

| 4.4.2     | Receiver Buffer (RBUF)                               |        |

| 4.4.3     | Line Parameter Register (LPR)                        |        |

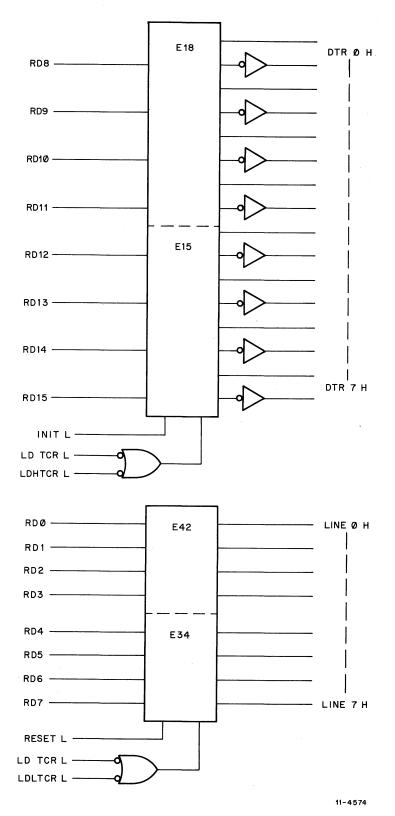

| 4.4.4     | Transmit Control Register (TCR)                      |        |

| 4.4.5     | Modem Status Register (MSR)                          |        |

| 4.4.6     | Transmit Data Register (TDR)                         |        |

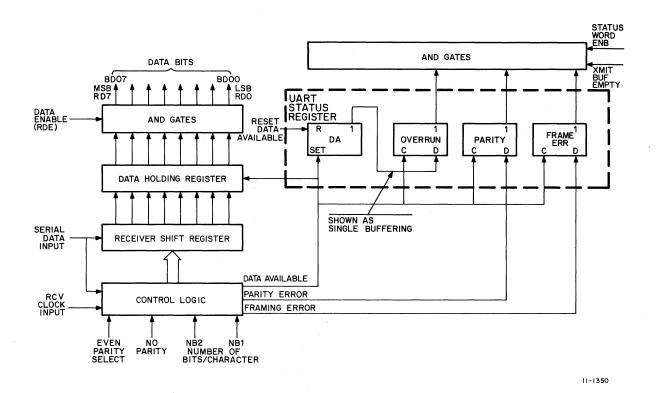

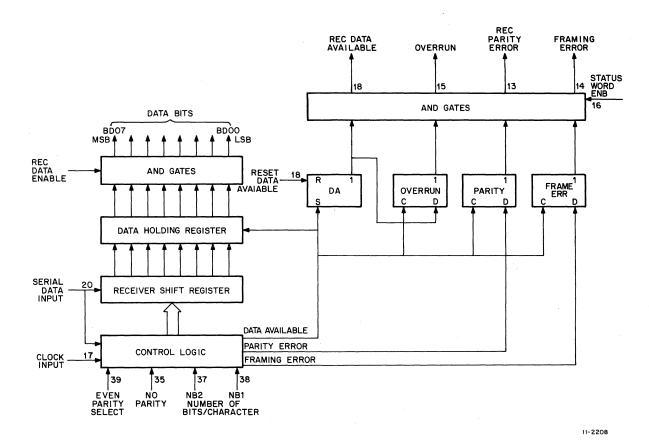

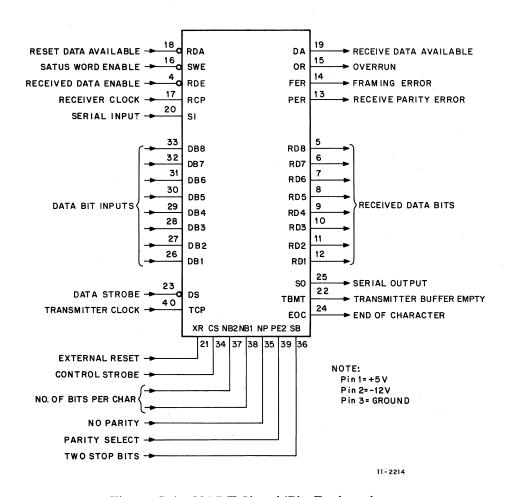

| 4.5       | UNIVERSAL ASYNCHRONOUS RECEIVER-TRANSMITTER (UART) . |        |

| CHAPTER 5 | MAINTENANCE                                          |        |

| 5.1       | INTRODUCTION                                         | 5 1    |

| 5.2       | PREVENTIVE MAINTENANCE                               |        |

| 5.2.1     |                                                      |        |

| 5.2.2     | Mechanical Checks                                    |        |

|           | Test Equipment Required                              |        |

| 5.3       | DZ11 MAINTENANCE SOFTWARE                            |        |

| 5.3.1     | DZ11 Diagnostic                                      |        |

| 5.3.1.1   | Storage                                              |        |

| 5.3.1.2   | Loading                                              |        |

| 5.3.1.3   | Starting                                             |        |

| 5.3.1.4   | Register Restrictions                                |        |

| 5.3.1.5   | SWITCH REGISTER PRIORITIES                           |        |

| 5.3.1.6   | SCOPE SWITCHES                                       |        |

| 5.3.1.7   | STARTING ADDRESS                                     |        |

| 5.3.1.8   | Operations Procedure                                 |        |

| 5.3.1.9   | Program and/or Operator Action                       |        |

| 5.3.2     | DZ11 System Exerciser                                |        |

| 5.3.2.1   | Storage                                              |        |

| 5.3.3     | DZ11 ITEP OVERLAY                                    |        |

| 5.4       | CORRECTIVE MAINTENANCE                               |        |

| 5.4.1     | DZ11 Test Procedures                                 |        |

| 5.4.1.1   | Visual Inspection                                    |        |

| 5.4.1.2   | Internal Loopback                                    |        |

| 5.4.1.3   | Staggered Loopback                                   |        |

| 5.4.1.4   | External                                             |        |

| 5.4.1.5   | On-Line with Terminal                                |        |

| 5.4.2     | DZ11 Option Testing                                  |        |

| 5.4.3     | System Checkout Procedure                            |        |

| 5.4.4     | Diagnostic Tests                                     | . 5-26 |

## **CONTENTS (Cont)**

APPENDIX A INTEGRATED CIRCUITS

4-21

| APPENDIX B | GLOSSARY OF TERMS                                        |      |

|------------|----------------------------------------------------------|------|

| APPENDIX C | UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)       |      |

|            | ILLUSTRATIONS                                            |      |

| Figure No. | Title                                                    | Page |

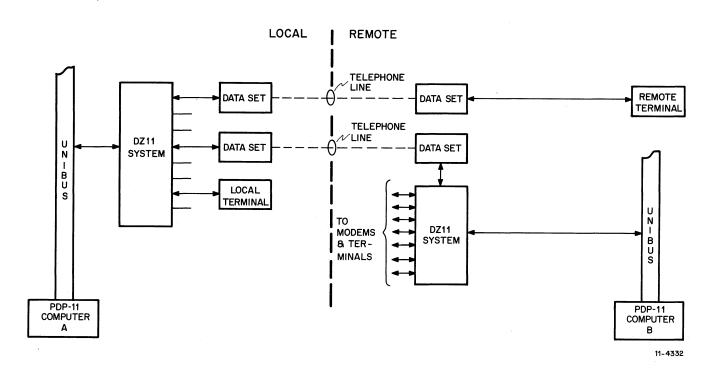

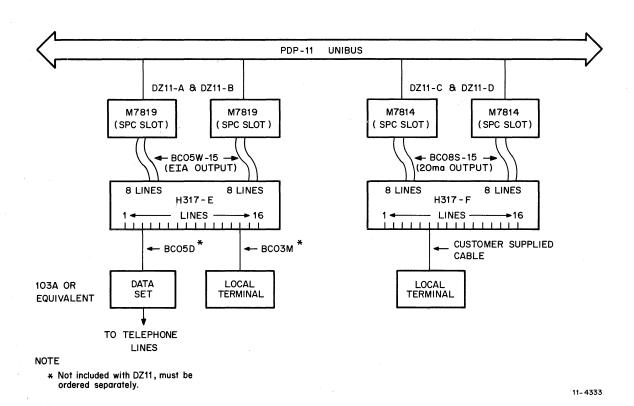

| 1-1        | DZ11 System Applications                                 | 1-2  |

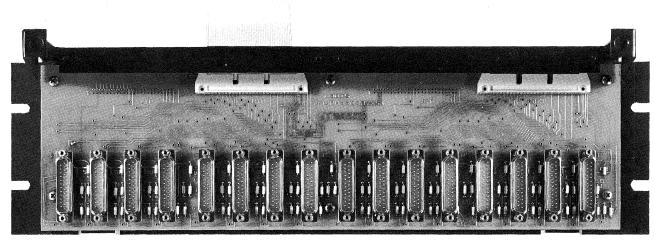

| 1-2        | DZ11 EIA Module (M7819), and Distribution Panel (H317-E) | 1-3  |

| 1-3        | DZ11 20 mA Module (M7814)                                | 1-4  |

| 1-4        | DZ11 Hardware Interconnections                           | 1-6  |

| 1-5        | Line Turnaround                                          | 1-6  |

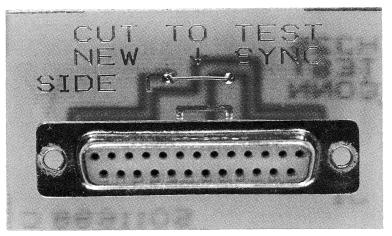

| 1-6        | Test Connectors, H327 and H325                           | 1-7  |

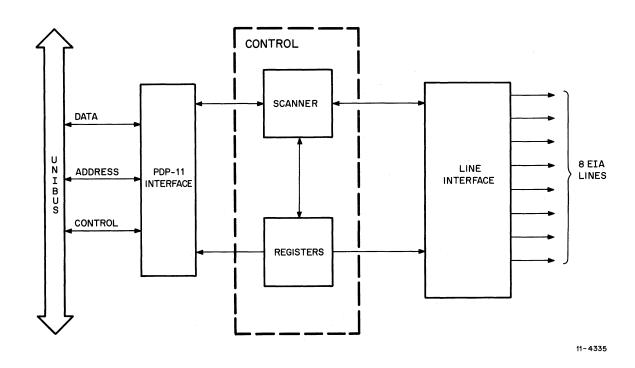

| 1-7        | General Functional Block Diagram                         | 1-11 |

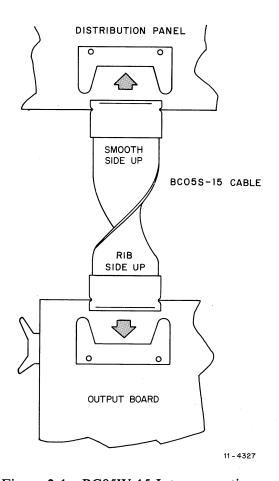

| 2-1        | BC05W-15 Interconnection                                 | 2-4  |

| 3-1        | Register Bit Assignments                                 | 3-3  |

| 4-1        | Modem-to-Unibus Data Flow (Receive)                      | 4-2  |

| 4-2        | Unibus-to-Modem Data Flow (Transmit)                     | 4-2  |

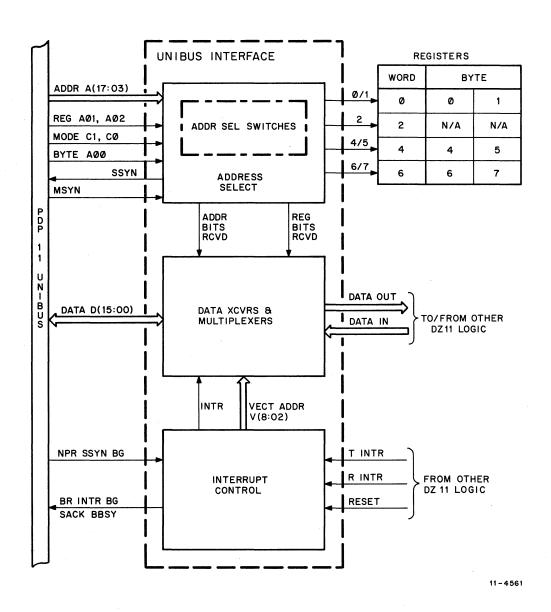

| 4-3        | Unibus Interface Block Diagram                           | 4-4  |

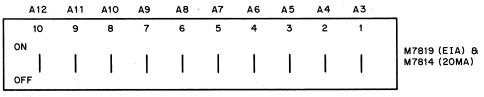

| 4-4        | Address Selection Switches                               | 4-5  |

| 4-5        | Address Word Format                                      | 4-5  |

| 4-6        | Address Selection Logic                                  | 4-6  |

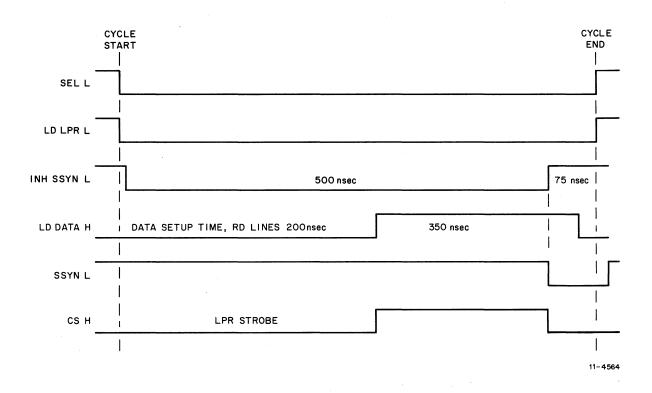

| 4-7        | Line Parameter Loading                                   | 4-8  |

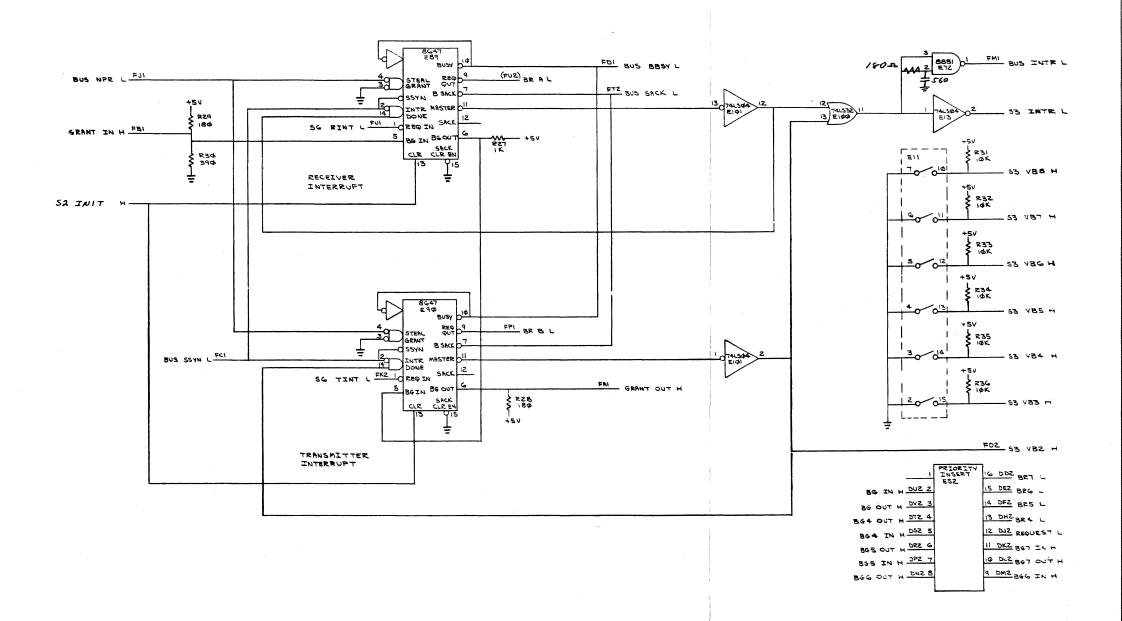

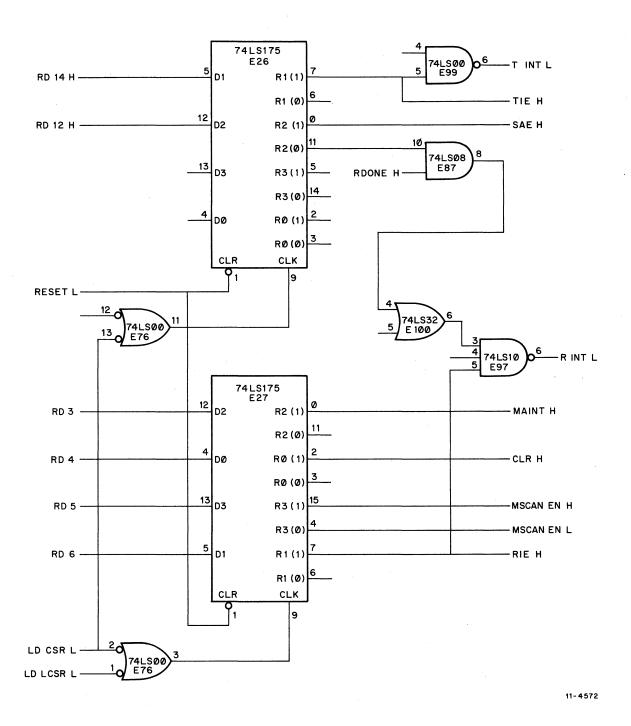

| 4-8        | Interrupt Control Logic                                  | 4-9  |

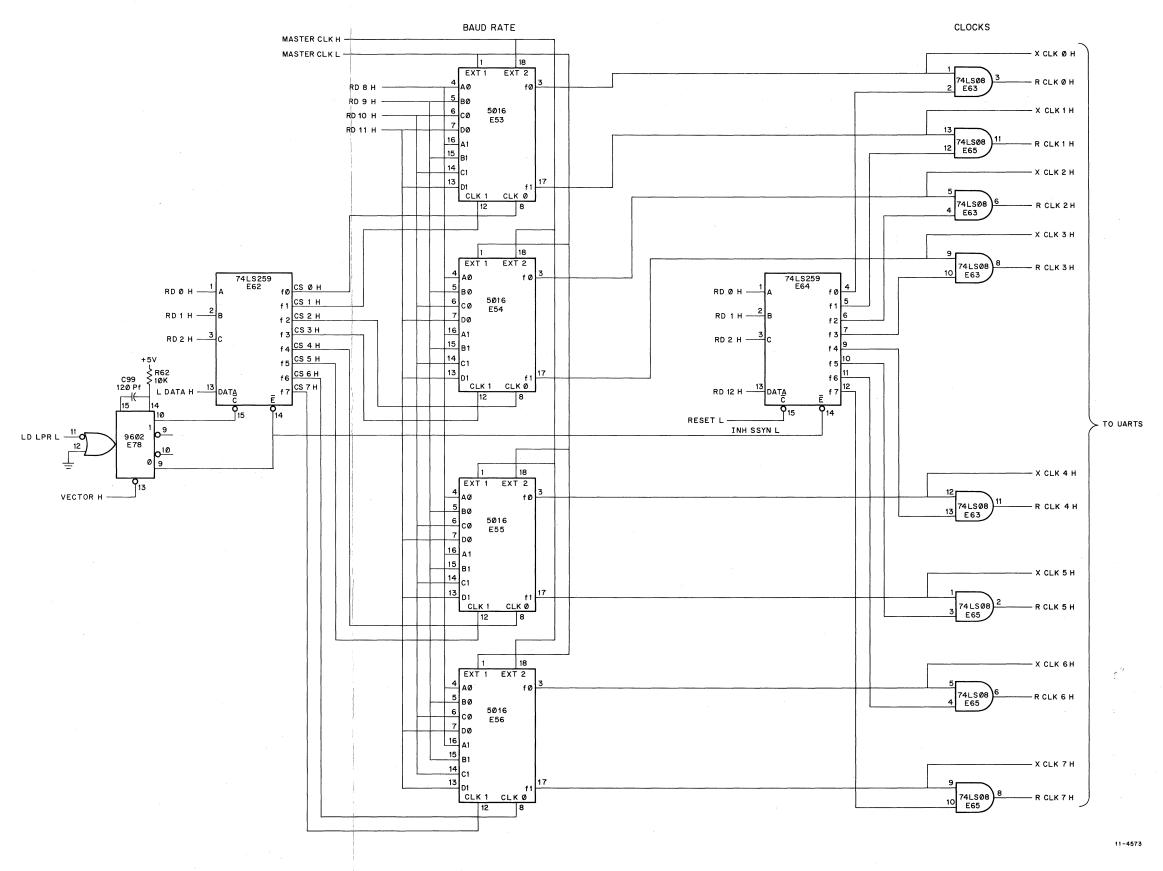

| 4-9        | Unibus Data Flow                                         | 4-10 |

| 4-10       | Output Data Multiplex Bit Correlation                    |      |

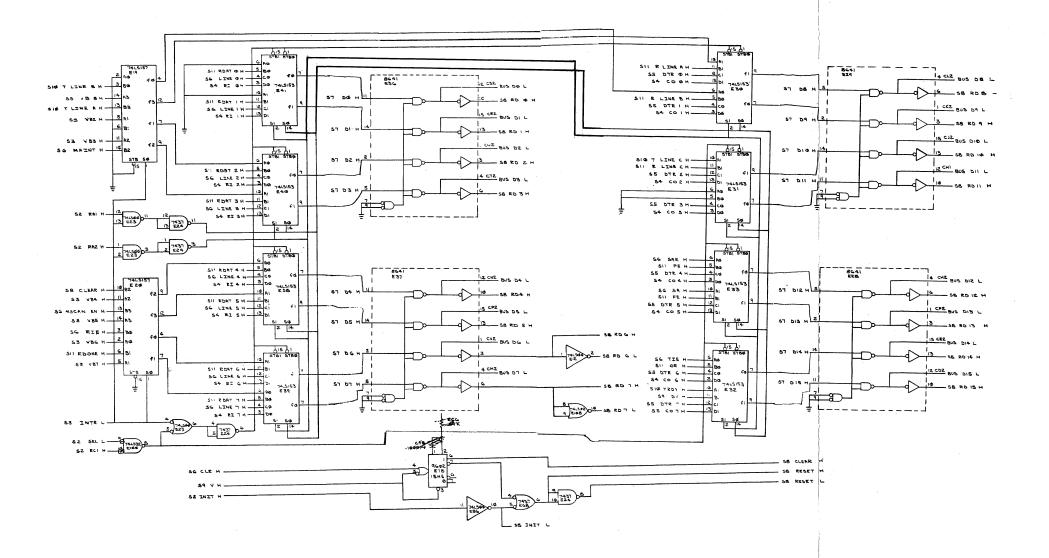

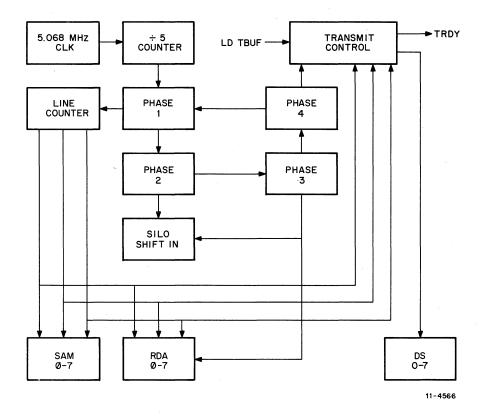

| 4-11       | Scanner Block Diagram                                    | 4-13 |

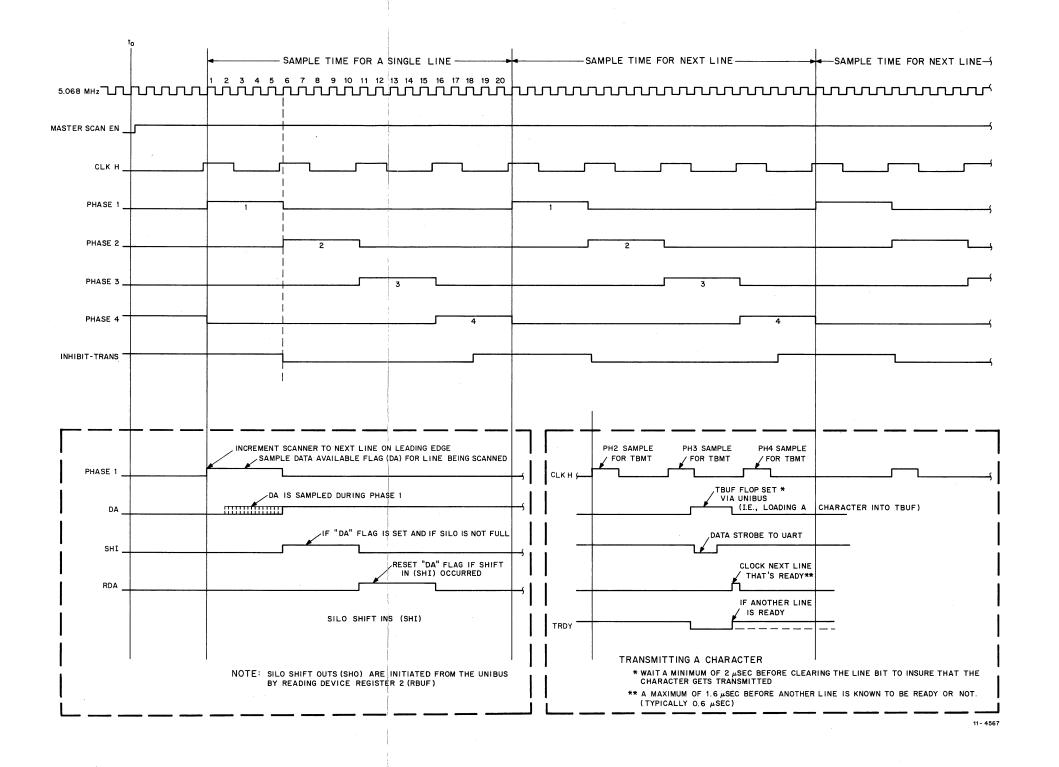

| 4-12       | DZ11-A Scanner Timing                                    |      |

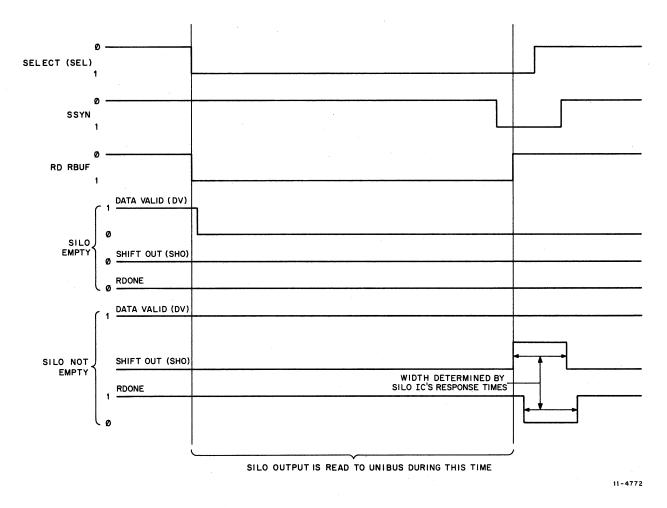

| 4-13       | Silo Character Shift Out Timing Diagram                  |      |

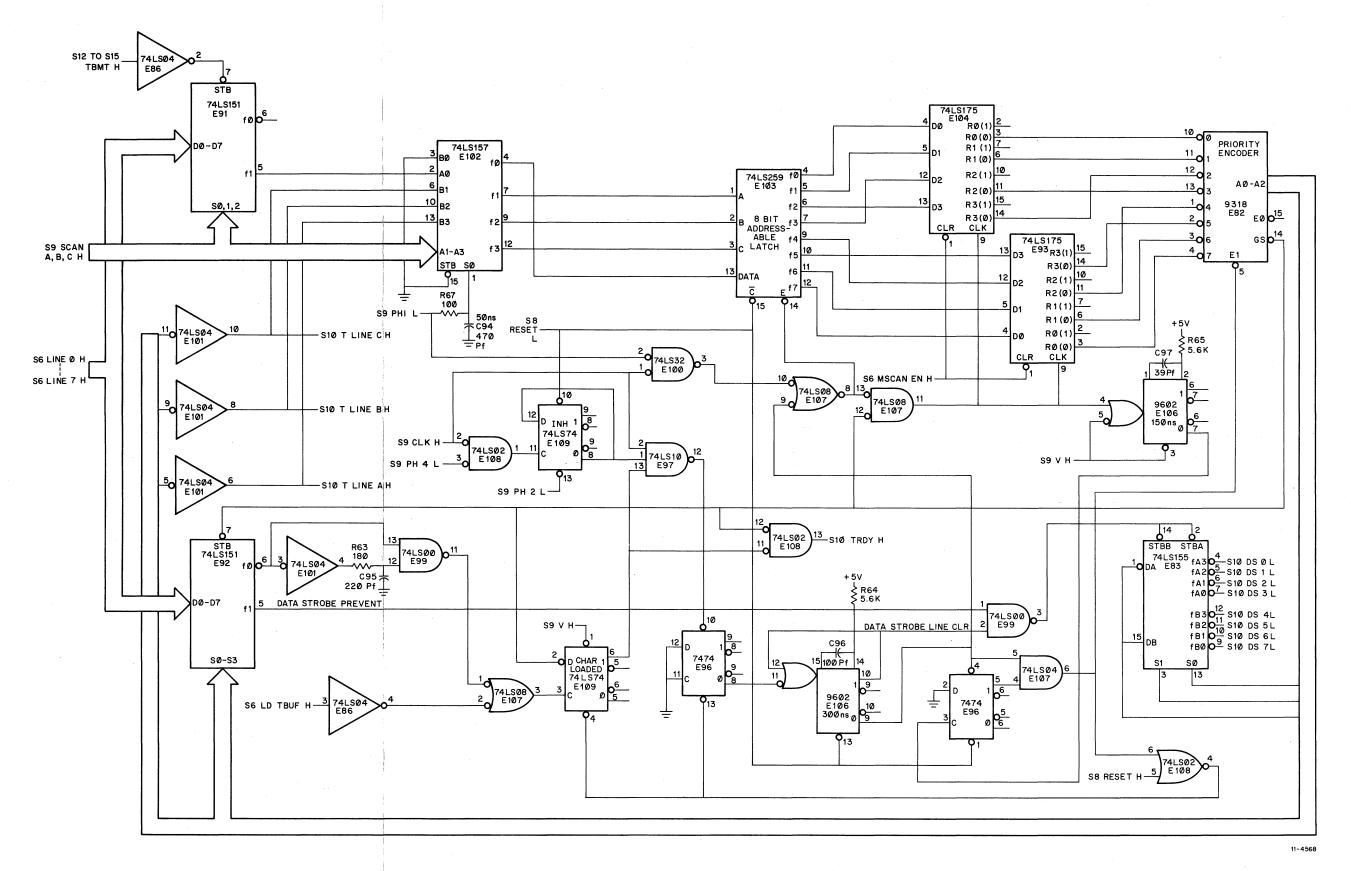

| 4-14       | Transmit Control Logic                                   |      |

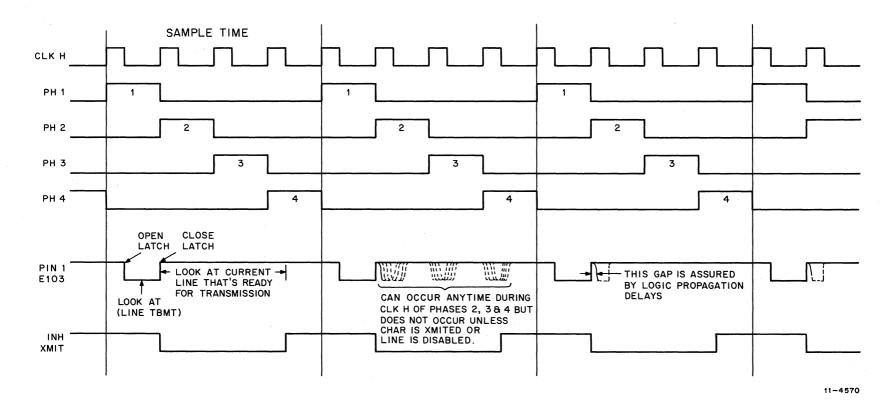

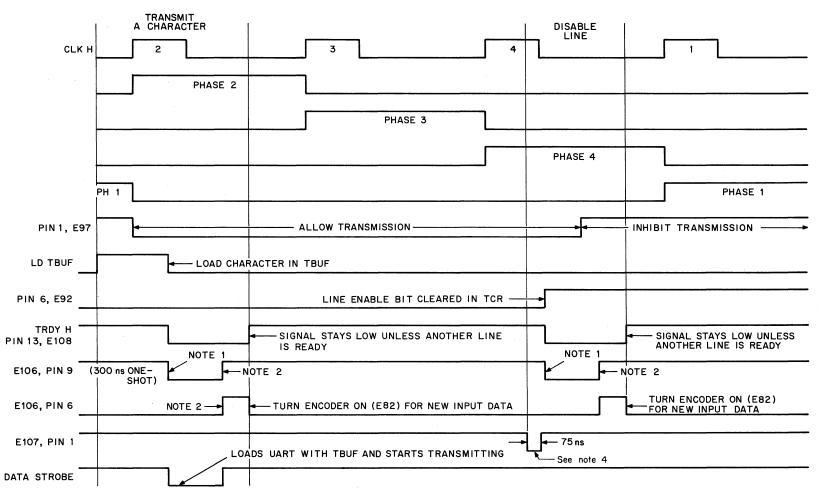

| 4-15       | Transmit Control Timing                                  | 4-17 |

| 4-16       | Character Transfer and Line Disable Timing               |      |

| 4-17       | CSR Diagram                                              | 4-21 |

| 4-18       | LPR Diagram                                              |      |

| 4-19       | TCR Diagram                                              | 4-24 |

| 4-20       | MSR Diagram                                              | 4-25 |

## **TABLES**

| Table No. | Title                       | Page   |

|-----------|-----------------------------|--------|

| 1-1       | DZ11 Model Configurations   | . 1-5  |

| 1-2       | DZ11 Performance Parameters | . 1-10 |

| 3-1       | CSR Bit Functions           | . 3-4  |

| 3-2       | RBUF Bit Functions          | . 3-5  |

| 3-3       | LPR Bit Functions           | . 3-6  |

| 3-4       | Baud Rate Selection Chart   | . 3-8  |

## CHAPTER 1 GENERAL DESCRIPTION

### 1.1 INTRODUCTION

The DZ11 is an asynchronous multiplexer that provides an interface between a PDP-11 processor and eight (8) asynchronous serial lines. It can be used with PDP-11 systems in a variety of applications that include communications processing, time sharing, transaction processing and real time processing. Local operation to terminals or computers is possible at speeds up to 9600 baud using either EIA RS232C interfaces or 20 mA current loop signaling. Remote operation using the public switched telephone network is possible with DZ11 models offering EIA RS232C interfaces. Enough data-set control is provided to permit dial up (auto answer) operation with modems capable of full duplex\* operation such as the Bell models 103 or 113 or equivalent. Remote operation over private lines for full duplex\* point to point or full duplex\* multipoint as 2 control (master) station is also possible. Figure 1-1 depicts several of the possible applications for the DZ11 in a PDP-11 system.

The DZ11 has several features that provide flexible control of communications' parameters such as baud rate, character length, number of stop bits for each line, odd or even parity for each line, and transmitter-receiver interrupts. Additional features include limited data set control, zero receiver baud rate, break generation and detection, silo buffering of received data, module plug-in to hex SPC slots, and line turnaround.

Each DZ11 module provides for operation of eight (8) asynchronous serial lines. Since the module interfaces to these channels with a sixteen (16) line distribution panel, two (2) DZ11 modules can be used with one panel. Also note that the two versions of the DZ11 (EIA or 20 mA output) consists of different module and panel types. This fact allows a system to mix EIA and 20 mA by using multiple DZ11s.

### 1.2 PHYSICAL DESCRIPTION

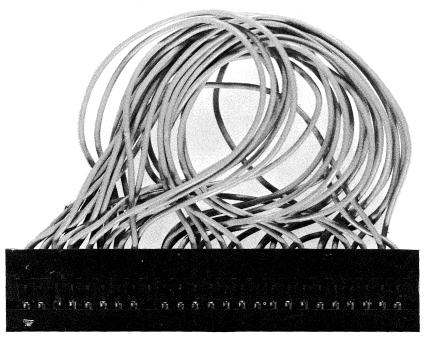

The DZ11 (8-line configuration) comprises a single hex SPC module and a 5.25-inch, unpowered distribution panel, connected by a 15-foot ribbon cable. Several types of interconnecting cables are used between the distribution panel and the modem or terminal, depending on the device. A 16-line configuration uses two modules and a single distribution panel connected by two ribbon cables. The DZ11 modules and distribution panel are shown in Figures 1-2 and 1-3. The subsequent paragraphs present a detailed description of the physical and electrical specifications of the various DZ11 options and configurations.

<sup>\*</sup>The DZ11 data-set control does not support half duplex operations or the secondary transmit and receive operations available with some moderns such as the Bell model 202, etc.

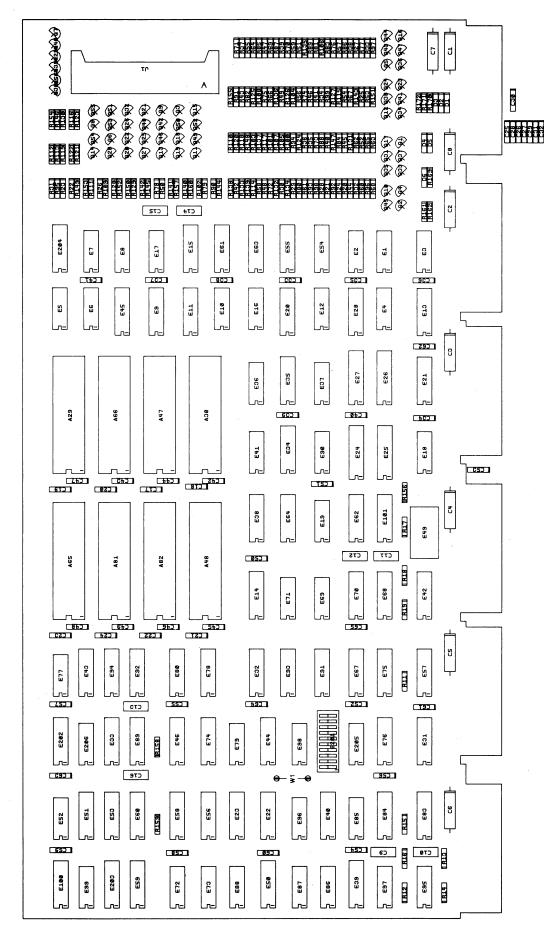

Figure 1-1 DZ11 System Applications

DISTRIBUTION PANEL

M7819

7974-1

Figure 1-2 DZ11 EIA Module (M7819), and Distribution Panel (H317-E)

Figure 1-3 DZ11 20 mA Module (M7814)

### 1.2.1 DZ11 Configurations

The DZ11 can be supplied in six different configurations, each designated by a suffix letter (A, B, C, D, E, or F). The DZ11-A and the DZ11-B options are EIA devices with partial modem control. The DZ11-E is the combination of a DZ11-A and a DZ11-B. The DZ11-C and the DZ11-D are 20-mA loop output versions. The DZ11-F is the combination of a DZ11-C and a DZ11-D. Table 1-1 shows the various option configurations and the required hardware for the various configurations is shown in Figure 1-4.

Table 1-1 DZ11 Model Configurations

| Model                                                    | Output                                       | Module                                               | Panel                                          | Connector                            |

|----------------------------------------------------------|----------------------------------------------|------------------------------------------------------|------------------------------------------------|--------------------------------------|

| DZ11-A<br>DZ11-B<br>DZ11-E<br>DZ11-C<br>DZ11-D<br>DZ11-F | EIA<br>EIA<br>EIA<br>20 mA<br>20 mA<br>20 mA | M7819<br>M7819<br>*M7819<br>M7814<br>M7814<br>*M7814 | H317-E<br>—<br>H317-E<br>H317-F<br>—<br>H317-F | H325/H327<br>H327<br>H325/*H327<br>— |

<sup>\* =</sup> quantity of two

The DZ11-A and DZ11-B each utilize an M7819 module that plugs into slot 2 or 3 of a DD11-B, or any system unit with a hex SPC slot; however, slots in the PDP-11/20 BA11 box cannot be used. The H317-E distribution panel provides 16 communications' lines from two M7819 modules (8 lines per module), and is included with the DZ11-A and DZ11-E configurations. The H317-F distribution panel provides 16 lines for the DZ11-C and DZ11-F configurations, which utilize the M7814 modules (20-mA system). The distribution panels require no power and can be mounted in an H960 19-inch cabinet.

Modems or terminals are connected to the H317-E, the EIA panel, by cables that attach to its 16 cinch DB25P connectors. These cables are not provided by the DZ11, therefore are bought separately by the customer. The BC05D-25 cable is recommended for data set to telephone line interconnections, and the BC03M cable is recommended for local terminal interconnections. A BC05W-15, 50-conductor flat shielded cable connects from the M7819 module to the EIA panel. This conductor carries the data and control signals of all 8 lines. Connections between terminals and the H317-F, the 20 mA panel, are by customer supplied cables to its 16 four screw terminal strips. The data and control signals of all 8 lines are carried to the distribution panel by a BC08S-15 40 conductor, flat shielded ribbon cable.

Two accessory test connectors, H325 and H327, are provided with each DZ11-A, and the H327 is provided with the DZ11-B. The H325 plugs into an EIA connector on the distribution panel to loop back data and modem signals onto a single line. The H327 connector plugs into the M7819 module socket housing and staggers the data and modem lines as shown in Figure 1-5. The connectors are shown in Figure 1-6.

A priority level 5 insert plugs into a socket on the M7819 module to establish interrupts at level 5 on the Unibus.

Figure 1-4 DZ11 Hardware Interconnections

Figure 1-5 Line Turnaround

H327

H325

7974-3

Figure 1-6 Test Connectors, H327 and H325

### 1.2.2 General Specifications

The following are electrical, environmental, and performance specifications for all DZ11 configurations:

### **OUTPUTS**

DZ11-A, -B, and -E

For each line, the DZ11 provides a voltage level interface whose levels and connector pinnings conform to ELECTRONIC INDUSTRIES ASSOCIATION (EIA) standard RS232C and CCITT recommendation V.24. The leads supported by this option are:\*

- Circuit AA (CCITT 101) Pin 1 Protective ground Circuit AB (CCITT 102) - Pin 7 Signal ground b. (CCITT 103) - Pin 2 Transmitted data Circuit BA

- Circuit BB (CCITT 104) - Pin 3 Received data

- Circuit CD (CCITT 108.2) - Pin 20 Data terminal Ready

- Circuit CE (CCITT 125) Pin 22 Ring indicator f.

- Circuit CF (CCITT 109) Pin 8 Carrier

### NOTE

### Signal ground and Protective ground are connected together.

\*Circuit CA (CCITT 105), Request to Send, is connected to circuit CD (DTR) through a jumper on the distribution panel. This allows the H325 connector to turn around DTR into both CO and RI (circuits CF and CE). It also allows control of the Request to Send (RTS) (CA) line for modem data set 202 applications.

DZ11-C, -D, and -F

20 mA loop versions. SPEC will be supplied at a later date.

### **INPUTS**

The PDP-11 Unibus is the input for all DZ11s. The DZ11-A, B, C, and D presents one unit load to the Unibus and the DZ11-E and -F present two unit loads to the Unibus.

### Power Requirements, DZ11-A, -B, and -E\*

| Typical | Maxim | um                         |

|---------|-------|----------------------------|

| 2.2     | 2.5   | amperes at + 5.0 volts, dc |

| 0.13    | 0.15  | amperes at -15.0 volts, dc |

| 0.1     | 0.13  | amperes at +15.0 volts, dc |

<sup>\*</sup>DZ11-E power is twice the above values

### Power Requirements, DZ11-C,-D, and -F

To Be Supplied

### Environmental Requirements, all DZ11s

Class C Environment Operating Temperature: 5° C to 40° C\*

(50° C to 122° F)

Relative Humidity:

10% or less to 95%, with a maximum wet

bulb of 32° C (90° F) and a minimum dew-

point of 2 ° (36° F)

\*Maximum operating temperature is reduced 1.8° C per 1000 meters (1.0° F per 1000 feet) for operation at altitude.

### **Cooling**

DZ11-A, -B, and -E:

Air flow 3 cu. feet/min.

DZ11-C, -D, and -F:

To Be Supplied

### **Heat Dissipation**

DZ11-A, -B, and -E:

57 Btu/hr

DZ11-C, -D, and -F:

To Be Supplied

### **Distortion**

DZ11-A, -B, and -E

The maximum "space to mark" and "mark to space" distortion allowed in a received character is 40%.

The maximum speed distortion allowed in a received character for 2000 baud is 3.8%. All other baud rates allow 4%.

The maximum speed distortion from the transmitter for 2000 band is 2.2%. All other band rates have less than 2%.

Table 1-2 lists the performance parameters of DZ11 operation.

### **Interrupts**

RDONE - Occurs each time a character appears at output of the silo.

SA – Silo Alarm, occurs after 16 characters enter the silo. Rearmed by reading the silo. This interrupt disables the RDONE interrupt.

TRDY - Occurs when the scanner finds a line ready to transmit on.

NOTE: There are no modem interrupts.

### Table 1-2 DZ11 Performance Parameters

Operating Mode:

Full Duplex

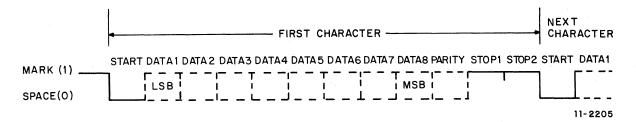

Data Format:

Asynchronous, serial by bit, one start and 1, 1-1/2 (5 level codes only), or 2

stop bits supplied by the hardware under program control.

Character Size:

5, 6, 7, or 8 bits - program selectable. (Does not include parity bit.)

Parity:

Parity is program selectable. There may be none, or it may be odd or even.

| Bit Polarities | Unibus             | Interface                                                             | EIA Out                            |

|----------------|--------------------|-----------------------------------------------------------------------|------------------------------------|

| MODEM DATA     | Low = 1 $High = 0$ | $\begin{aligned} & \text{High} = 1 \\ & \text{Low} = 0 \end{aligned}$ | Low = 1 = MARK<br>High = 0 = SPACE |

| MODEM CONTROL  | Low = 1 $High = 0$ | $\begin{aligned} & \text{High} = 1 \\ & \text{Low} = 0 \end{aligned}$ | Low = OFF<br>High = ON             |

Order of Bit

Transmission/reception Low order bit first

### **Interrupt Level**

Normally Level 5 is supplied. It can be modified by a priority plug.

### **Maximum Configuration**

16 DZ11 modules per Unibus

### Distance

DZ11-A, -B, and -E:

50 feet - up to 9600 baud, if cable is less than 2500 pf.

DZ11-C, -D, and -F:

To Be Supplied

### 1.3 FUNCTIONAL DESCRIPTION

The following paragraphs present a general description of DZ11 operation. A more detailed description is found in Chapter 3 (Programming) and Chapter 4 (Theory of Operation). Figure 1-7 is a general functional block diagram that divides the DZ11 into three basic components: Unibus Interface, Control Logic, and Line Interface.

Figure 1-7 General Functional Block Diagram

### 1.3.1 PDP-11 Unibus Interface

The PDP-11 Unibus Interface component of the DZ11 handles all transactions between the Unibus and the DZ11 Control Logic. The Unibus Interface performs three functions: data handling, address recognition, and interrupt control. In its data handling function, the Interface routes data to and from the various registers in the Control Logic and provides the voltage conditioning necessary to transmit and receive data to and from the PDP-11 Unibus. The address recognition and control logic activates the proper load and read signals when it recognizes its preselected address on the Unibus. These signals are used by the data handling function to route the incoming and outgoing data to the desired locations. The interrupt control function initiates and controls interrupt processing between the DZ11 and the PDP-11 processor.

### 1.3.2 Control Logic

The Control Logic provides the required timing and control signals to handle all transmitter and receiver operations. The Control Logic can be divided into two major sections: the scanner and the registers. The scanner continuously examines each line in succession, and based on information from the Line Interface and the registers, it generates signals that causes data to flow to or from the appropriate line. The scanner comprises a 5.068 MHz oscillator (clock), a 64-word FIFO receiver buffer, a four-phase clocking network, and other control generating logic.

The DZ11 uses four Device Registers in a manner that yields six unique and accessible registers, each having a 16-bit word capacity. The six discrete registers temporarily store input and output data, monitor control signal conditioning, and establish DZ11 operating status. Depending on their functions, some of the registers are accessible in bytes or words; others are restricted to word-only operation. Registers can be read or loaded (written), depending on the operation. The ability to read or write a register allows the use of two of the Device Registers as four independent registers.

### 1.3.3 Line Interface

Two of the most important operations in the DZ11 are the conversions from serial-to-parallel and parallel-to-serial data formats. These conversions are required since the DZ11 is located between the PDP-11 Unibus (a parallel data path) and either local terminals or telephone lines (serial data paths). Conversions for each line in the DZ11 are performed by independent Universal Asynchronous Receiver-Transmitter (UART) integrated circuits. Another component of the Line Interface, the Line Receiver or Driver, converts the TTL voltage levels in the DZ11 so that they correspond to those in the external device input lines (modem or terminal).

## CHAPTER 2 INSTALLATION

### 2.1 SCOPE

This chapter contains the procedures for the unpacking, installation, and initial checkout of the DZ11 Asynchronous Multiplexer. More detailed checkout procedures are outlined in Chapter 5 of this manual.

### 2.2 CONFIGURATION DIFFERENCES

The DZ11 can be supplied with or without a Distribution panel. The DZ11-B and -D do not have Distribution panels. The following list describes the variations:

DZ11-A EIA level conversion with distribution panel

DZ11-B EIA level conversion without distribution panel

DZ11-C 20-mA loop conversion with distribution panel

DZ11-D 20-mA loop conversion with distribution panel

DZ11-E DZ11-A and DZ11-B with distribution panel

DZ11-F DZ11-C and DZ11-D with distribution panel

### 2.3 UNPACKING AND INSPECTION

The DZ11 is packaged in accordance with commercial packaging practices. First, remove all packing material and check the equipment against the shipping list. Damage or shortages should be reported to the shipper immediately, and notification given the DEC representative. Inspect all parts and carefully inspect the module for cracks, loose components, and separations in the etched paths.

### 2.4 INSTALLATION PROCEDURE

The following procedure should be followed to completely check and install the DZ11 module in a PDP-11 system:

1. Check the shipment for a complete agreement with the shipping list. The following items per configuration should be supplied:

| Quantity | Description                        | ABECDF |

|----------|------------------------------------|--------|

| 1        | M7819 Module                       | x x *  |

| 1        | H327 Test Connector                | x x *  |

| 1        | Priority Insert (5)                | x x *  |

| 1        | H317-E Distribution Panel Assembly | x x    |

| 1        | H325 Test Connector                | x x    |

| 1        | BC05W-15 Cable                     | x x *  |

| 1        | Panel Mounting Hardware Set        | x x    |

| 1        | Printset (B-TC-DZ11-0-6)           | хх     |

| 1        | Printset (B-TC-DZ11-0-10)          | X      |

| 1        | Software Kit                       | x x    |

| 1        | DZ11 Maintenance Manual            | X X    |

| 1        | M7814 Module                       | X X *  |

| 1        | BC08S Cable                        | X X *  |

| 1        | Printset (DZ11-C and F)            | XX     |

| 1        | Printset (DZ11-D)                  | X      |

<sup>\*</sup>The DZ11-E shipment contains two of the items listed.

- 2. Check all parts for damage.

- 3. Install the H317 Distribution Panel according to the Unit Assembly Drawing D-UA-DZ11-0-0.

- 4. Check to ensure that all of the machine-insertable jumpers on the Distribution Panel are in place. See Drawing D-CS-5411928-0-1 in the Printset for jumper locations.

- 5. Module Installation

- a. Check the module(s) for obvious damage.

- b. Ensure that the Priority Insert (level 5) is properly seated in socket E52 on the module(s). Refer to drawing D-UA-M7819-0-0.

- c. Refer to Chapter 3, the paragraph describing Address Selection, and set the switches at E81 such that the module will respond to its assigned address. (Refer to Chapter 3 for the address assignment scheme.) When a switch is closed, a binary 1 is decoded, and an open switch decodes as a binary 0. Note that the switch labeled #1 corresponds to bit 3, #2 corresponds to bit 4, etc.

- d. Vector selection is accomplished by the eight-position switch at E11. Switch position #1 and #8 are not used. Switch position #2 corresponds to vector bit 3, #3 corresponds to vector bit 4, etc. An open switch decodes as binary 1, and a closed switch decodes as binary 0.

- e. Ensure that the H327 Test Connector is properly installed at J1 (the cable connector at the top of the module).

- f. Insert the module in its SPC slot and run Diagnostics in the staggered mode to verify module operation. Refer to MAINDEC-11-DZDZA, the diagnostic listing, and to Chapter 5, Programming, of this manual for the correct procedure. Run at least two passes without error.

### **CAUTION**

Insert and remove modules slowly and carefully to avoid snagging module components on the card guides, and possibly changing switch settings inadvertently.

- g. Replace the H327 Test Connector with the BC05W-15 cable (RIB-SIDE UP), and observe the same caution as in Step f above. Insert the other end of the cable (SMOOTH-SIDE UP) at J18 or J20 of the Distribution panel. BE CERTAIN THAT THE CORRECT SIDE OF THE CABLE IS UP IN EACH CASE! See Figure 2-1.

- h. Connect the H325 (or an H315) connector to the first line and run the Diagnostics in External mode. Repeat this step for each line.

- i. Run DEC/X11 System Exerciser to verify the absence of Unibus interference with other system devices.

- j. The DZ11 is now ready for connection to external equipment. If the connection is to be made to a terminal, a null modem cable must be used. The BC03M, H312-A, or BC03P null modem cables will suffice for connection between the Distribution panel and the terminal. However, if the H312-A null modem unit is used, two BC05D EIA cables (one on each side of the null modem unit) are required. If connection is to be made to a Bell 103 or equivalent modem, a BC05D-25 feet cable is required between the Distribution panel and the modem. All of the cables mentioned in this step must be ordered separately as they are NOT components of a standard DZ11 shipment.

Figure 2-1 BC05W-15 Interconnection

# CHAPTER 3 PROGRAMMING

### 3.1 INTRODUCTION

This chapter provides basic information for programming DZ11 system operation. A description of each DZ11 register, its format, programming constraints, and bit functions are presented to aid programming and maintenance efforts. Special programming features are also presented in this chapter.

### 3.2 REGISTER BIT ASSIGNMENTS

A comprehensive pictorial of all register bit assignments is shown in Figure 3-1. The four device registers (DR0, DR2, DR4, and DR6) are subdivided to form six unique registers. This subdivision is accomplished in DR2 and DR6 by assigning read-only (RO) or write-only (WO) status to each register. Since the reading and writing of DR2 and DR6 accesses two registers, PDP-11 processor instructions that perform a read-modify-write (DATIP) bus cycle cannot be used with DR2 or DR6. Also, DR2 permits only word instructions, but either byte or word instructions may be used with DR6. DR0 and DR4 have no programming constraints. In all register operations, the following applies: read-only bits are not affected by an attempt to write, and write-only and "not-used" bits appear as a binary 0 if a read operation is performed. Specific programming constraints for each register are discussed in the subsequent paragraphs. A description of each bit function is presented in Tables 3-1 through 3-3.

The DZ11's device and vector addresses are selected from the floating vector and device address space.

NOTE: The device floating address space is 160010<sub>8</sub> to 163776<sub>8</sub>. The vector floating address space is 300<sub>8</sub> to 776<sub>8</sub>.

Its floating address space follows the DJ11; DH11; DQ11; DU11; DUP11; LK11; and DMC11.

Its floating vector space follows the DC11; KL11/DL11-A, B; DP11; DM11-A; DN11; DM11-BB and other modem control vectors; DR11-A; DR11-C; PA611 reader, PA611 punch; DT11; DX11; DL11-C, D, E; DJ11; DH11; GT40; LPS11; DQ11; KW11-W; DU11; DUP11; DV11; LK11-A; DWUN; and DMC11. If a DZ11 is installed in a system with any of the above listed options, then its assigned vector and device address should follow the vector and device address of the other options.

## Two examples follow:

First, the simplest case where there is only one DZ11:

| Option       | Address | Vector | Comment       |

|--------------|---------|--------|---------------|

| GAP          | 160010  |        | No DJ11s      |

| GAP          | 160020  |        | No DH11s      |

| GAP          | 160030  |        | No DQ11s      |

| GAP          | 160040  |        | No DÙ11s      |

| GAP          | 160050  |        | No DUP11s     |

| GAP          | 160060  |        | No LK11s      |

| GAP          | 160070  |        | No DMC11s     |

| <b>DZ</b> 11 | 160100  | 300    |               |

| GAP          | 160110  |        | No more DZ11s |

Next, a system with one DJ11, one DH11, one GT40, one KW11-W and two DZ11s.

| Option              | Address                    | Vector     | Comment                                                                   |

|---------------------|----------------------------|------------|---------------------------------------------------------------------------|

| DJ11                | 160010                     | 300        |                                                                           |

| GAP                 | 160020                     |            | No more DJ11s                                                             |

| GAP                 | 160030                     |            | DH11 must start on<br>an address boundary<br>that is a multiple<br>of 20. |

| DH11                | 160040                     | 310        |                                                                           |

|                     | 160050                     |            |                                                                           |

| GAP                 | 160060                     |            | No more DH11s                                                             |

| GT40                |                            | 320        | GT40 address is not                                                       |

|                     |                            | 320        | in the floating address space.                                            |

| KW11-W              |                            | 330        | KW11-W address is not in the floating address space.                      |

| GAP                 | 160070                     |            | No DQ11s                                                                  |

| GAP                 | 160100                     |            | No DU11s                                                                  |

| GAP                 | 160110                     |            | No DUP11s                                                                 |

| GAP                 | 160120                     |            | No LK11s                                                                  |

| GAP                 | 160130                     |            | No DMC11s                                                                 |

|                     |                            | 340        | No Divicits                                                               |

|                     |                            |            |                                                                           |

|                     |                            | 330        | No more D711s                                                             |

| DZ11<br>DZ11<br>GAP | 160140<br>160150<br>160160 | 340<br>350 | No more DZ11s                                                             |

|     |                              | MSB<br>15                      | 14                             | 13                             | 12                             | 11                             | 10                             | 09                             | BYTI<br>HIGH<br>08               |                        | 06                       | 05                         | 04                      | 03                       | 02                     | 01                       | LSB<br>00              |

|-----|------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|----------------------------------|------------------------|--------------------------|----------------------------|-------------------------|--------------------------|------------------------|--------------------------|------------------------|

| 6   | CONTROL<br>& STATUS<br>(CSR) | RO<br>TX<br>RDY                | RW<br>TX<br>INTR<br>ENAB       | RO<br>SILO<br>ALARM            | RW<br>SILO<br>ALARM<br>ENAB    | 10NO3                          | RO<br>TX<br>LINE<br>C          | RO<br>TX<br>LINE<br>B          | RO<br>TX<br>LINE<br>A            | RO<br>RX<br>DONE       | RW<br>RX<br>INTR<br>ENAB | RW<br>MAST<br>SCAN<br>ENAB | RW<br>CLEAR             | RW<br>MAINT              | tow Oaso               | 10NO2<br>15ED            | 10M Q1857              |

| 2   | RECEIVER<br>BUFFER<br>(RBUF) | RO<br>DATA<br>VALID            | RO<br>OVRN                     | RO<br>FRAM<br>ERR              | RO<br>PAR<br>ERR               | 10N 2397                       | RO _<br>RX<br>LINE<br>C        | RO<br>RX<br>LINE<br>B          | RO<br>RX<br>LINE<br>A            | RO<br>RBUF<br>D7       | RO<br>RBUF<br>D6         | RO<br>RBUF<br>D5           | RO<br>RBUF<br>D4        | RO<br>RBUF<br>D3         | RO<br>RBUF<br>D2       | RO<br>RBUF<br>D1         | RO<br>RBUF<br>D0       |

| 2   | LINE<br>PARAMETER<br>(LPR)   | 100 GH                         | 1000                           |                                | WO<br>RX<br>ON                 | WO<br>FREQ<br>D                | WO<br>FREQ<br>C                | WO<br>FREQ<br>B                | WO<br>FREQ<br>A                  | WO<br>ODD<br>PAR       | WO<br>PAR<br>ENAB        | WO<br>STOP<br>CODE         | WO<br>CHAR<br>LGTH<br>B | WO<br>CHAR<br>LGTH<br>A  | WO<br>LINE<br>C        | WO<br>LINE<br>B          | WO<br>LINE<br>A        |

| 3-3 | TRANSMIT<br>CONTROL<br>(TCR) | RW<br>DATA<br>TERM<br>RDY<br>7 | RW<br>DATA<br>TERM<br>RDY<br>6 | RW<br>DATA<br>TERM<br>RDY<br>5 | RW<br>DATA<br>TERM<br>RDY<br>4 | RW<br>DATA<br>TERM<br>RDY<br>3 | RW<br>DATA<br>TERM<br>RDY<br>2 | RW<br>DATA<br>TERM<br>RDY<br>1 | RW _<br>DATA<br>TERM<br>RDY<br>0 | RW<br>LINE<br>7        | RW<br>LINE<br>6          | RW<br>LINE<br>5            | RW                      | _ <u>RW</u><br>LINE<br>3 | _RW<br>LINE<br>2       | _R <u>W</u><br>LINE<br>1 | RW                     |

| G   | MODEM<br>STATUS<br>(MSR)     | RO<br>CO<br>7                  | RO<br>CO<br>6                  | RO<br>CO<br>5                  | RO<br>CO<br>4                  | RO<br>CO<br>3                  | RO<br>CO<br>2                  | RO<br>CO<br>1                  | RO<br>CO<br>0                    | RO<br>RING<br>IND<br>7 | RO<br>RING<br>IND<br>6   | RO<br>RING<br>IND<br>5     | RO<br>RING<br>IND<br>4  | RO<br>RING<br>IND<br>3   | RO<br>RING<br>IND<br>2 | RO<br>RING<br>IND<br>1   | RO<br>RING<br>IND<br>0 |

| 6   | TRANSMIT<br>DATA<br>(TDR)    | WO<br>BRK<br>7                 | WO<br>BRK<br>6                 | WO<br>BRK<br>5                 | WO<br>BRK<br>4                 | WO<br>BRK<br>3                 | WO<br>BRK<br>2                 | WO<br>BRK<br>1                 | WO<br>BRK<br>0                   | WO<br>TBUF<br>7        | WO<br>TBUF<br>6          | WO<br>TBUF<br>5            | WO<br>TBUF<br>4         | WO<br>TBUF<br>3          | WO<br>TBUF<br>2        | WO<br>TBUF<br>1          | WO<br>TBUF<br>0        |

Figure 3-1 Register Bit Assignments

**Table 3-1 CSR Bit Functions**

| Bit  | Title                   | Function                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–2  | Not Used                |                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3    | MAINT                   | A read/write bit, when set, causes the serial output data from the transmitter to be fed back as serial input data to the receiver. All lines are turned around. Bit is cleared by BUS INIT and CLR.                                                                                                                                                                                                        |

| 4    | CLR                     | A read/write bit that fires a one-shot to generate a 15-microsecond reset to clear the receiver silo, all UARTs, and the CSR. After a CLR is issued, the CSR and line parameters must be set again. CLR in progress is indicated by CLR = 1. Modem control registers are not affected, nor bits 00 through 14 of RBUF.                                                                                      |

| 5    | Master Scan Enable      | A read/write bit that activates the scanner to enable the Receiver and Transmitter. Cleared by CLR and BUS INIT.                                                                                                                                                                                                                                                                                            |

| 6    | RCV INT Enable          | A read/write bit that enables the receiver interrupt. Cleared by CLR and BUS INIT.                                                                                                                                                                                                                                                                                                                          |

| 7    | RDONE                   | A read only bit (hardware set) that generates a RCV INT if bit $06 = 1$ and bit $12 = 0$ . The bit clears when the RBUF is read and resets when another word reaches the output of the silo (RBUF). If bit $06 = 0$ , RDONE can be used as a flag to indicate that the silo contains a character. If bit $12 = 1$ , RDONE does not cause interrupts but otherwise acts the same.                            |

| 8–10 | Tran Line #             | When bit 15 = 1, these three read-only bits indicate that the line that is ready to transmit a character. Bit 15 clears when the character is loaded into the transmit buffer, but sets again if another line is ready. A new line number appears within a minimum of 1.9 microseconds. The bits 08-10 return to line 0 after a CLR or BUS INIT. These bits are meaningful only when bit 15 (TRDY) is true. |

| 11   | Not Used                | (TRDT) is true.                                                                                                                                                                                                                                                                                                                                                                                             |

| 12   | SAE (Silo Alarm Enable) | A read/write bit that enables the silo alarm and prevents RDONE from interrupting if RIE (bit 06 = 1). If bit 06 = 1, the SAE allows the SA (bit 13) to cause an interrupt after 16 entries in the silo. If bit 06 = 0, the SA can be used as a flag. The bit is cleared by CLR and RESET.                                                                                                                  |

### **Table 3-1 CSR Bit Functions**

| Bit | Title               | Function                                                                                                                                                                                                                                                                                 |

|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | SA (Silo Alarm)     | A read-only bit set by hardware after 16 characters enter the silo that causes an interrupt if bit $06 = 1$ . Cleared by CLR, RESET, and reading the RBUF. When the silo flag occurs (SA = 1), the silo must be emptied to prepare the flag for recognition of 16 additional characters. |

| 14  | TIE (Tran Int Enab) | A read/write bit that allows an interrupt if bit 15 = 1 (TRAN Ready).                                                                                                                                                                                                                    |

| 15  | TRDY (Tran Ready)   | A read-only bit set by hardware when a line number is found whose buffer can be loaded and whose TCR bit has been set by the program. See bits 08-10 functional description                                                                                                              |

### **Table 3-2 RBUF Bit Functions**

| Bit  | Title         | Function                                                                                                                                                                                                                             |

|------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0–7  | RCV Character | These bits contain the received character. If the selected code level is less than 8 bits wide, the high order bits are forced to zero.                                                                                              |

| 8–10 | Line Number   | These bits present the line number on which the character was received.                                                                                                                                                              |

| 11   | Not Used      |                                                                                                                                                                                                                                      |

| 12   | Parity Error  | This bit indicates whether the received bit had a parity error. The parity bit is generated by hardware and does not appear in the RBUF word.                                                                                        |

| 13   | Framing Error | This bit indicates improper framing (stop bit not a mark) of the received character, and can be used for break detection.                                                                                                            |

| 14   | Overrun       | This bit indicates receiver buffer overflow. The result is a received character which is replaced by another received character before storage in the silo. A character is lost but the received character put in the silo is valid. |

| 15   | Data Valid    | This bit indicates that the character read from the silo (RBUF) is valid. The RBUF should read until the DV bit = 0, indicating an invalid character and empty silo. Bit is cleared by CLR and BUS INIT.                             |

Table 3-3 LPR Bit Functions

| Bit   | Title            | Function                                                                                                                                                      |  |  |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0–2   | Line Number      | These bits select the line for parameter loading.                                                                                                             |  |  |

| 3–4   | Character Length | These bits set the character length for the selected line.<br>The parity bit is not part of the character length.                                             |  |  |

|       |                  | 4 3<br>0 0 5 bits<br>0 1 6 bits<br>1 0 7 bits<br>1 1 8 bits                                                                                                   |  |  |

| 5     | Stop Code        | This bit sets the Stop Code length. (0 = One-unit stop, 1 = Two-unit stop or 1.5-unit stop if a 5-level code is employed.)                                    |  |  |

| 6     | Parity           | This bit selects the parity option (0 = No parity check, 1 = Parity enabled on TRAN and RCV.)                                                                 |  |  |

| 7     | Odd Parity       | This bit selects the kind of parity selected (0 = Even Parity Select, 1 = Odd Parity Select.) Bit 06 must be set for this bit to have effect.                 |  |  |

| 8–11  | Speed Select     | These bits select the TRAN and RCV speed for the line selected by bits 0-2. Refer to Table 3-4 for list of available baud rates.                              |  |  |

| 12    | RCVR ON          | This bit must be set when loading parameters to activate the receiver clock. (Transmitter clock is always on.)A CLR or BUS INIT turns the receiver clock off. |  |  |

| 13–15 | Not Used         |                                                                                                                                                               |  |  |

### 3.2.1 Control and Status Register (CSR)

The control and status register (CSR) contains the states of flags and enable bits for scanning, processor interrupts, clearing, and maintenance. The 16-bit CSR has no programming constraints. The CSR format is depicted in Figure 3-1, and bit functions are described in Table 3-1. Write-only and "notused" bits read as zeros to the Unibus, and read-only bits are not affected by write attempts.

### 3.2.2 Receiver Buffer (RBUF)

The receiver buffer (RBUF) register contains the received character bits, with line identification, error status, and data validity flag. As one of two registers in DR2 (RBUF and LPR), RBUF is accessed when a read operation is performed on DR2 (write operation accesses the LPR). The RBUF register has several programming constraints which are:

- 1. Byte instructions cannot be used.

- 2. It is a "Read Only" register.

- 3. TST or BIT instructions cannot be used as they cause the loss of a character.

- 4. Bits 00 through 14 are not affected by CLR or BUS INIT. Bit 15 (Data Valid) is explained in Table 3-2.

The register format of RBUF is depicted in Figure 3-1, and bit functions are described in Table 3-2. Each reading of the RBUF register advances the silo and presents the next character to the program.

### 3.2.3 Line Parameter (LPR)

The line parameter register (LPR) is a 16-bit write only register that sets the parameters (character and stop code lengths, parity, speed, and receiver clock) for each line. Bits 00-02 select the line for parameter loading. Line parameters for each line must be reloaded after a CLR (bit 04 of CSR) or BUS INIT operation. The programming constraints for the LPR are:

- 1. BIS or BIC instructions are not allowed.

- 2. Byte operations have no effect.

The LPR format is depicted in Figure 3-1, and bit functions are described in Table 3-3.

### 3.2.4 Transmit Control (TCR)

The 16-bit (two-byte) transmit control register (TCR) has read and write capability. The TCR low byte corresponds to lines in the multiplexer, and when a line bit is set, it enables the scanner to transmit on the line. Line interrupts are generated by the AND condition of TCRXX • TRDY • TIE.

Clearing a TCR bit prevents the line from transmitting. To transmit to a line, the TBUF Register (DR6, low byte) is loaded with the desired character. The TCR high byte contains a DTR bit for each line. The TCR low byte is cleared by a CLR or BUS INIT; the high byte is cleared by BUS INIT only. To ensure transmission of the last character on a line, the TCR line bit must not be cleared for at least 2.0 microseconds after the character is loaded into the TBUF register.

### 3.2.5 Modem Status (MSR)

The modem status register (MSR) consists of two 8-bit, read-only registers. The low byte provides a ring indicator (RI) for each line, and the high byte reads the state of the carrier (CO) lead for each line. The MSR is the read-only component of DR6. The MSR is not affected by CLR and BUS INIT.

### 3.2.6 Transmit Data (TDR)

The transmit data register (TDR) is the write-only segment of DR6. The TDR constitutes two 8-bit registers, the low byte (TBUF) containing the character to be transmitted, and the high byte containing a BREAK bit for each line. If a BREAK bit is set, the line transmits zeros continuously. Clearing the BRK bit (CLR, BUS INIT, or writing zeros in the bit position) terminates the break condition. The break time interval is program controlled. The break feature cannot be used when the data lines are turned around by bit 03 of the CSR. For character lengths less than 8 bits, the character must be right-justified, as the most significant bits are forced to zero by the DZ11 hardware.

### 3.3 PROGRAMMING FEATURES

The DZ11 has several programming features that allow control of baud rate, character length, stop bits, parity, and interrupts. This section discusses the application of these controls to achieve the desired operating parameters.

### 3.3.1 Baud Rate

The selection of the desired transmission and reception speed is controlled by the conditions of bits 08 through 11 of the LPR. Table 3-4 depicts the required bit configuration for each operating speed. Also, the baud rate for each line is the same for both the transmitter and receiver. Furthermore, the receiver clock is turned on and off by setting and clearing bit 12 in the LPR for the selected line.

Table 3-4 Baud Rate Selection Chart

### **Bits**

| 11 | 10 | 09  | 08 | <b>Baud Rate</b> |

|----|----|-----|----|------------------|

| 0  | 0  | 0   | 0  | 50               |

| 0  | 0  | 0 , | 1  | 75               |

| 0  | 0  | 1   | 0  | 110              |

| 0  | 0  | 1   | 1  | 134.5            |

| 0  | 1  | 0   | 0  | 150              |

| 0  | 1  | 0   | 1  | 300              |

| 0  | 1  | 1   | 0  | 600              |

| 0  | 1  | 1   | 1  | 1200             |

| 1  | 0  | 0   | 0  | 1800             |

| 1  | 0  | 0   | 1  | 2000             |

| 1  | 0  | 1   | 0  | 2400             |

| 1  | 0  | 1   | 1  | 3600             |

| 1  | 1  | 0   | 0  | 4800             |

| 1  | 1  | 0   | 1  | 7200             |

| 1  | 1  | 1   | 0  | 9600             |

| 1  | 1  | 1   | 1  | Not Used         |

### 3.3.2 Character Length

The selection of one of the four available character lengths is controlled by bits 03 and 04 of the LPR. The bit conditions for bits 04 and 03, respectively, are as follows: 00 (5 level), 01 (6 level), 10 (7 level), and 11 (8 level). For character lengths of 5, 6, and 7, the high order bits are forced to zero.

### 3.3.3 Stop Bits

The length of the stop bits in a serial character string is determined by the 05 bit of the LPR. If bit 05 is a zero, the stop length is one unit; bit 05 set to a one selects a two-unit stop, unless the 5-level character length (bits 03 and 04 at zero) is selected, then the stop bit length is 1.5 units.

#### 3.3.4 Parity

The parity option is selected by bit 06 of the LPR. Parity is enabled on transmission and reception by setting bit 06 to one. Bit 07 of the LPR allows selection of even or odd parity, and bit 06 must be set for bit 07 to be significant. The parity bit is generated and checked by hardware, and does not appear in the RBUF or TBUF. The parity error (bit 12, RBUF) flag is set when the received character had a parity error.

### 3.3.5 Interrupts

The Receiver Interrupt Enable (RIE) and Silo Alarm Enable (SAE) bits in the CSR control the circumstances upon which the DZ11 receiver interrupts the PDP-11 processor.

If RIE and SAE are both clear, the DZ11 never interrupts the PDP-11 processor. In this case, the program must periodically check for the availability of data in the SILO and empty the SILO when data is present. If the program operates off a clock it should check for characters in the SILO at least as often as the time it takes for the SILO to fill, allowing a safety factor to cover processor response delays and time to empty the silo. The RDONE bit in the CSR will set when a character is available in the SILO. The program can periodically check this bit with a TSTB or BIT instruction. When RDONE is set the program should empty the SILO.

If RIE is set and SAE is clear, the DZ11 will interrupt the PDP-11 processor to the DZ11 receiver vector address when RDONE is set, indicating the presence of a character at the bottom of the SILO. The interrupt service routine can obtain the character by performing a MOV instruction from the RBUF. If the program then dismisses the interrupt, the DZ11 will interrupt when a subsequent character is available (which may be immediately if additional characters were placed in the SILO while the interrupt was being serviced). Alternately, the interrupt service routine may respond to the interrupt by emptying the SILO before dismissing the interrupt.

If RIE and SAE are both set, the DZ11 will interrupt the PDP-11 processor to the DZ11 receiver vector when the SILO ALARM (SA) bit in the CSR is set. The SA bit will be set when sixteen characters have been placed in the silo since the last time the program has accessed the RBUF. Accessing the RBUF will clear the SA bit and the associated counter. The program should follow the procedure described in Paragraph 3.3.6 to empty the silo completely in response to a silo alarm interrupt. This will ensure that any characters placed in the silo while it is being emptied are processed by the program.

### NOTE

If the program processes only 16 entries in response to each silo alarm interrupt, characters coming in while interrupts are being processed will build up without being counted by the silo alarm circuit and the silo may eventually overflow without the alarm being issued.

If the silo alarm interrupt is used, the program will not be interrupted if fewer than 16 characters are received. In order to respond to short messages during periods of moderate activity the PDP-11 program should periodically empty the silo. The scanning period will depend on the required responsiveness to received characters. While the program is emptying the silo it should ensure that DZ11 receiver interrupts are inhibited. This should be done by raising the PDP-11 processor priority. The silo alarm interrupt feature can significantly reduce the PDP-11 processor overhead required by the DZ11 receiver by eliminating the need to enter and exit an interrupt service routine each time a character is received.

The transmitter interrupt enable bit (TIE) controls transmitter interrupts to the PDP-11 processor. If enabled, the DZ11 will interrupt the PDP-11 processor to the DZ11 transmitter interrupt vector when the Transmitter Ready (TRDY) bit in the CSR is set, indicating that the DZ11 is ready to accept a character to be transmitted.

### 3.3.6 Emptying the Silo

The program can empty the SILO by repeatedly performing MOV instructions from the RBUF to temporary storage. Each MOV instruction will copy the bottom character in the SILO so it won't be lost and will clear out the bottom of the SILO, allowing the next character to move down for access by a subsequent MOV instruction. The program can determine when it has emptied the SILO by testing the DATA VALID bit in each word moved out of the RBUF. A zero value indicates that the SILO has been emptied. The test can be performed conveniently by branching on the condition code following each MOV instruction. A TST or BIT instruction must not access the RBUF because these instructions will cause the next entry in the SILO to move down without saving the current bottom character. Furthermore, following a MOV from the RBUF, the next character in the silo may be available within 1 microsecond. On fast CPUs, the program must use sufficient instructions or NOPs to ensure that successive MOVs from the RBUF are separated by at last 1 microsecond. This will prevent a false indication of an empty silo.

### 3.3.7 Transmitting a Character

The program controls the DZ11 transmitter through five registers on the Unibus: the Control and Status Register (CSR) previously mentioned, the Line Parameter Register (LPR), the Line Register, the Transmitter Buffer (TBUF) and the Break Register (BRK).

Following DZ11 initialization, the program must use the LPR register to specify the speed and character format for each line to be used and must set the Master Scan Enable (MSE) bit in the CSR. The program should set the Transmitter Interrupt Enable (TIE) bit in the CSR if it wants the DZ11 transmitter to operate on a program interrupt basis.

The Line Register is used to enable and disable transmission on each line. One bit in this eight bit register is associated with each line. The program can set and clear bits in this register by using MOV, MOVB, BIS, BISB, BIC and BICB instructions. (If word instructions are used, the Line and DTR registers will be simultaneously accessed.)

The DZ11 transmitter is controlled by a scanner which is constantly looking for an enabled line (Line bit set) which has an empty UART transmitter buffer. When the scanner finds such a line it loads the number of the line into the 3-bit Transmit Line Number (TLINE) field of the CSR and sets the TRDY bit, interrupting the PDP-11 processor if the TIE bit is set. The program can clear the TRDY bit by moving a character for the indicated line into the TBUF or by clearing the Line bit.

Clearing the TRDY bit frees the scanner to resume its search for lines needing service.

To initiate transmission on an idle line, the program should set the TCR bit for that line and wait for the scanner to request service on the line, as indicated by the scanner loading the number of the line into TLINE and setting TRDY. The program should then load the character to be transmitted into the TBUF by using a MOVB instruction. If interrupts are to be used, a convenient way of starting up a line is to set the TCR bit in the main program and let the normal transmitter interrupt routine load the character into the TBUF.

### NOTE

The scanner may find a different line needing service before it finds the line being started up. This will occur if other lines request service before the scanner can find the line being started. The program must always check the TLINE field of the CSR when responding to TRDY to ensure it loads characters for the correct line. Assuming the program services lines as requested by the scanner, the scanner will eventually find the line being started. If several lines require service, the scanner will request service in priority order as determined by line number. Line 7 has the highest priority and line 0 the lowest.

To continue transmission on a line, the program should load the next character to be transmitted into the TBUF each time the scanner requests service for the line as indicated by TLINE and TRDY.

To terminate transmission on a line, the program may use either of two approaches. In the first approach the program clears the Line bit after loading the last character into the TBUF. The program must ensure that a minimum of 2 microseconds elapses between loading the TBUF and clearing the Line bit, otherwise the last character may be lost. In the second approach, the program loads the last character normally and waits for the scanner to request an additional character for the line. The program clears the TCR bit at this time instead of loading the TBUF.

The normal rest condition of the Transmitted Data lead for any line is the marking (1) state. The Break Register (BRK) is used to apply a continuous spacing signal to the line. One bit in this eight bit register is associated with each line. The line will remain in the spacing condition so long as the bit remains set. The program should use a MOVB instruction to access the BRK register. If the program continues to load characters for a line after setting the break bit, transmitter operation will appear normal to the program despite the fact that no characters can be transmitted while the line is in the continuous spacing state. The program may use this facility for sending precisely timed spacing signals by setting the break bit and using Transmit Ready interrupts as a timer.

It should be remembered that each line in the DZ11 is double buffered. The program must not set the BRK bit too soon or the two data characters preceding the spacing may not be transmitted. The program must also ensure that the line returns to the mark state at the end of the spacing period before transmitting any additional data characters. The following procedure will accomplish this. When the scanner requests service the first time after the program has loaded the last data character, the program should load an all-zero character. When the scanner requests service the second time, the program should set the BRK bit for the line. At the end of the spacing period the program should load an all-zero character to be transmitted. When the scanner requests service indicating this character has begun transmission the program should clear the BRK bit and load the next data character.

### 3.3.8 Data Set Control

DZ11 models with EIA interfaces include data set control as a standard feature. The program may sense the state of the Carrier and Ring Indicator signals from each data set and may control the state of the Data Terminal Ready signal to each data set.

The program uses three 8-bit registers to access the DZ11 data set control logic. One bit in each register is associated with each of the 8 lines. There are no hardware interlocks between the data set control logic and the receiver and transmitter logic. Any required coordination should be done under program control.

The Data Terminal Ready (DTR) register is a read/write register. Setting or clearing a bit in this register will turn the appropriate Data Terminal Ready signal on or off. The program may access this register with word or byte instructions. (If word instructions are used the DTR and Line registers will be simultaneously accessed.) The DTR register is cleared by the INIT signal on the Unibus but is not cleared if the program clears the DZ11 by setting the CLR bit of the CSR.

The Carrier Register (CAR) and Ring Register (RING) are read-only registers. The program can determine the current state of the carrier signal for a line by examining the appropriate bit of the CAR register. It can determine the current state of the ring signal by examining the appropriate bit of the RING register. The program can examine these registers separately by using MOVB or BITB instructions or can examine them as a single 16 bit register by using MOV or BIT instructions. The DZ11 data set control logic does not interrupt the PDP-11 processor when a carrier or ring signal changes state. The program should periodically sample these registers to determine the current status. Sampling at a high rate is not necessary.

### 3.4 PROGRAMMING EXAMPLES

The following five examples are sample programs for the DZ11 option. These examples are presented only to indicate how the DZ11 can be used.

Example 1 – Initializing the DZ11

The DZ11 is initialized by: a power-up sequence, a reset instruction, or a device clear instruction.

## Device Clearing the DZ11

| 001000<br>001002<br>001004 | 012737<br>000020 | START: | MOV #20, DZCSR | ;Set bit 4 in the DZ11 ;control and status ;registers.                                            |

|----------------------------|------------------|--------|----------------|---------------------------------------------------------------------------------------------------|

| 001004                     | 160100<br>032737 | 1\$:   | BIT #20, DZCSR | ·T4 h:4 4                                                                                         |

| 001000                     | 000020           | 1Ф.    | BII #20, DZCSK | ;Test bit 4.                                                                                      |

| 001012                     | 160100           |        |                |                                                                                                   |

| 001014                     | 001374           |        | BNE 1\$        | ;If bit 4 is still set, the ;branch condition is true ;and the device clear ;function is still in |

| 001016                     | 000000           |        | HALT           | ;progress. ;The device clear ;function is complete and ;the DZ11 has been ;cleared.               |

DZCSR = 160100 = control and status register address

## Example 2 - Transmit binary count pattern on one line

| 001000<br>001002 | 012737<br>000020 | START: | MOV #20, DZCSR                          | ;Set bit 4 in the DZ11 ;control and status register.                                                        |

|------------------|------------------|--------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 001004           | 160100           |        |                                         |                                                                                                             |

| 001006           | 032737           | 1\$:   | BIT #20, DZCSR                          | ;Test bit 4.                                                                                                |

| 001010           | 000020           |        |                                         |                                                                                                             |

| 001012           | 160100           |        |                                         |                                                                                                             |

| 001014           | 001374           |        | BNE 1\$                                 | ;If bit 4 is still set, the ;branch condition is true ;and the device clear ;function is still in progress. |

| 001016           | 012737           |        | MOV #n, DZLPR                           | ;Load the parameters for                                                                                    |

| 001020           | 001070           |        | Wis v mi, BEET it                       | ;line 0: 8 bit character;                                                                                   |

| 001022           | 160102           |        |                                         | ;2 stop bit; 110 baud.                                                                                      |

| 001024           | 012737           |        | MOV #1, DZTCR                           | ;Enable line 0<br>transmitter.                                                                              |

| 001026           | 000001           |        |                                         |                                                                                                             |

| 001030           | 160104           |        |                                         |                                                                                                             |

| 001032           | 012737           |        | MOV #m, DZCSR                           | ;Set scanner enable bit                                                                                     |

| 001034           | 000040           |        | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | ;5 in the control and                                                                                       |

| 001036           | 160100           |        |                                         | status register.                                                                                            |

| 001040           | 005000           |        | CLR R0                                  | ;Set binary count pattern                                                                                   |

|                  |                  |        | 2_1110                                  | ;to zero.                                                                                                   |

| 001042           | 005737           | 2\$:   | TST DZCSR                               | ;Test the transmitter                                                                                       |

| 001044           | 160100           | 2ψ.    |                                         | ;ready flag (bit 15).                                                                                       |

# Example 2 (Cont)

| 001046 | 100375 | BPL 2\$        | ;If branch condition is ;false, continue; ;otherwise test again.             |

|--------|--------|----------------|------------------------------------------------------------------------------|

| 001050 | 110037 | MOVB RO, DZTDR | Load character to be                                                         |

| 001052 | 160106 | ,              | transmitted.                                                                 |

| 001054 | 105200 | INCB R0        | Increment binary count.                                                      |

| 001056 | 100371 | BPL 2\$        | ;If branch condition is<br>;false, the binary count<br>;pattern is complete. |

| 001060 | 00000  | HALT           | ,F                                                                           |

R0 = Register 0 = Binary Count Pattern

DZCSR = DZ11 Control and Status Register Address = 160100 DZLPR = DZ11 Line Parameter Register Address = 160102 DZTCR = DZ11 Transmit Control Register Address = 160104

DZTDR = DZ11 Transmit Data Register Address = 160106

Example 3 – Transmit a binary count to a terminal in Maintenance Loopback mode, with the receiver "On" in the interrupt mode. Transmit received data to console.

| 001200 | 005000 |      | CLR R0                                | ;Set binary count to zero.  |

|--------|--------|------|---------------------------------------|-----------------------------|

| 001202 | 012701 |      | MOV 1400, R1                          | ;Set R1 to first address of |

| 001204 | 001400 |      | 14017 #CD D C                         | ;data buffer.               |

| 001206 | 012706 |      | MOV #SP, R6                           | ;Initialize stack pointer.  |

| 001210 | 001100 |      |                                       |                             |

| 001212 | 012737 |      | MOV #INT, RVEC                        | ;Set DZ11 vector address    |

| 001214 | 001304 |      |                                       | ;to start of receiver       |

| 001216 | 000300 |      |                                       | ;interrupt routine.         |

| 001220 | 005037 |      | CLR (RVEC+2)                          | ;Set up processor status    |

| 001222 | 000302 |      | ;word for DZ11 receiver               |                             |

|        |        |      |                                       | ;interrupt.                 |

| 001224 | 012737 |      | MOV#20, DZCSR                         | ;Set bit 4 in the DZ11      |

| 001226 | 000020 |      |                                       | control and status;         |

|        |        |      |                                       | register.                   |

| 001230 | 160100 |      |                                       |                             |

| 001232 | 032737 | 1\$: | BIT #20 DZCSR                         | ;Test bit 4.                |

| 001234 | 000020 |      | · · · · · · · · · · · · · · · · · · · |                             |