# DA10 PDP-8/9 INTERFACE

DEC-10-IACA-D

June 1968

DIGITAL EQUIPMENT CORPORATION . MAYNARD, MASSACHUSETTS

Copyright (C) 1968 by Digital Equipment Corporation

#### CONTENTS

## Page

#### CHAPTER 1 INTRODUCTION

| 1.1 | Referenced Publications  | 1-1 |

|-----|--------------------------|-----|

| 1.2 | General Description      | 1-2 |

| 1.3 | Equipment Specifications | 1-2 |

#### CHAPTER 2 OPERATION AND PROGRAMMING

| 2.1   | Indicator Panel         | 2-1 |

|-------|-------------------------|-----|

| 2.2   | Power Control Panel     | 2-2 |

| 2.2.1 | Power Application       | 2-3 |

| 2.3   | Device Selection        | 2-4 |

| 2.3.1 | PDP-10 Device Selection | 2-4 |

| 2.3.2 | PDP-9 Device Selection  | 2-4 |

| 2.3.3 | PDP-8 Device Selection  | 2-4 |

| 2.4   | Programming Notes       | 2-5 |

| 2.4.1 | PDP-10 Instructions     | 2-5 |

| 2.4.2 | PDP-9 Programming       | 2-6 |

| 2.4.3 | PDP-8 Programming       | 2-7 |

#### CHAPTER 3 INSTALLATION

| 3.1   | Power Requirements           | 3-1  |

|-------|------------------------------|------|

| 3.2   | Environmental Conditions     | 3-1  |

| 3.3   | Space Requirements           | 3-1  |

| 3.4   | Device Selection Wiring      | 3-1  |

| 3.4.1 | PDP-8 Device Selection Cards | 3-1  |

| 3.5   | Data Transfer Pulse Mixers   | 3-2  |

| 3.6   | FM10 Buffer Output Mixer     | 3-5  |

| 3.7   | TO10 Buffer Input Mixer      | 3-8  |

| 3.8   | I/O Bus Connections          | 3-10 |

| 3.8.1 | PDP-10 I/O Bus Cables        | 3-10 |

| 3.8.2 | PDP-9 I/O Bus Cables         | 3-11 |

| 3.8.3 | PDP-8 I/O Bus Cables         | 3-12 |

## CONTENTS (Cont)

|       |                                        | Page |

|-------|----------------------------------------|------|

| 3.9   | One-Shot Adjustment                    | 3-12 |

|       | CHAPTER 4<br>THEORY OF OPERATION       |      |

| 4.1   | Functional Description                 | 4-1  |

| 4.2   | Detailed Description                   | 4-3  |

| 4.2.1 | Data Transfer to a PDP-8               | 4-4  |

| 4.2.2 | Data Transfer to a PDP-9               | 4-7  |

| 4.2.3 | Data Transfer From a PDP-8 to a PDP-10 | 4-12 |

| 4.2.4 | Data Transfer From a PDP-9 to a PDP-10 | 4-16 |

| 4.3   | Self-Check Operation                   | 4-19 |

| 4.4   | Power Turn-On and Initialization       | 4-26 |

| 4.5   | Logic Block Diagrams                   | 4-26 |

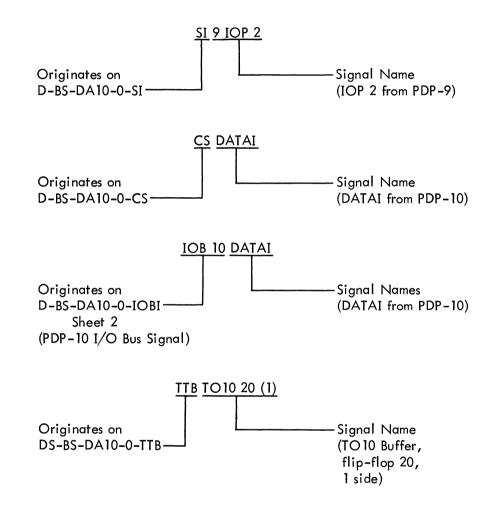

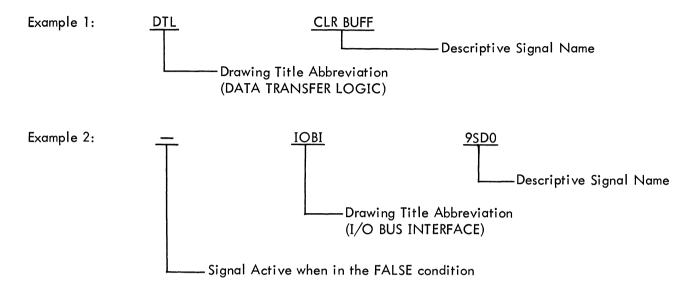

| 4.5.1 | Signals Mnemonics                      | 4-29 |

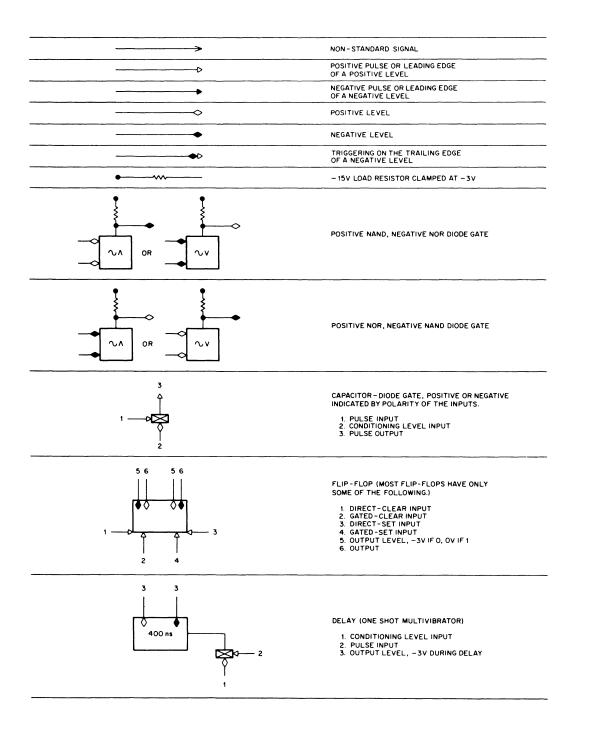

| 4.5.2 | Logic Functions                        | 4-29 |

|       | CHAPTER 5                              |      |

## MAINTENANCE

| 5.1   | Preventive Maintenance       | 5-1 |

|-------|------------------------------|-----|

| 5.1.1 | Mechanical Checks            | 5-1 |

| 5.1.2 | DEC Type 728 Power Supply    | 5-2 |

| 5.1.3 | Margin Checks                | 5-2 |

| 5.2   | Corrective Maintenance       | 5-2 |

| 5.2.1 | Preliminary Investigation    | 5-3 |

| 5.2.2 | System Troubleshooting       | 5-3 |

| 5.2.3 | Module Troubleshooting       | 5-5 |

| 5.3   | Repair                       | 5-5 |

| 5.3.1 | Type R302 Module Replacement | 5-6 |

| 5.4   | Validation Test              | 5–6 |

| 5.5   | Log Entry                    | 5–6 |

| 5.6   | Spare Parts List             | 5–6 |

### CONTENTS (Cont)

## Page

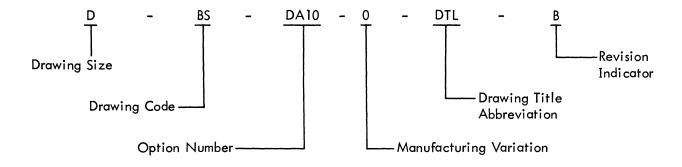

#### CHAPTER 6 ENGINEERING DRAWINGS

# 6-1

6.1 Drawing Terminology 6.2 6-2 Logic Symbols Logic Levels 6-2 6.3 6.4 Flip Chip Pulses 6-4 Engineering Drawing List 6-5 6.5

#### TABLES

| 1-1 | Available Publications                       | 1-1  |

|-----|----------------------------------------------|------|

| 1-2 | DA10 General Specifications                  | 1-4  |

| 2-1 | DA10 Indicator Panel                         | 2-1  |

| 2-2 | Power Control Panel, Switches and Indicators | 2-3  |

| 3-1 | PDP-10 I/O Bus Cables                        | 3-11 |

| 3-2 | PDP-9 I/O Bus Cables                         | 3-11 |

| 3-3 | PDP-8 I/O Bus Cables                         | 3-12 |

| 5-1 | Recommended Spare Parts for DA10             | 5-7  |

| 6-1 | DA10 Engineering Drawings                    | 6-5  |

#### ILLUSTRATIONS

| 1-1 | DA10 Interface, Typical System Diagram     | 1-3 |

|-----|--------------------------------------------|-----|

| 1-2 | DA10 Interface, Assembly Locations         | 1-3 |

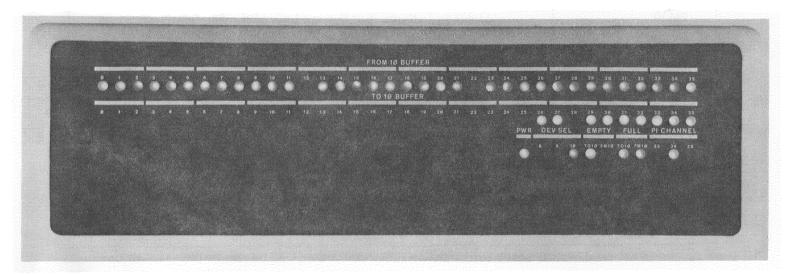

| 2-1 | DA10 Interface, Indicator Panel            | 2-1 |

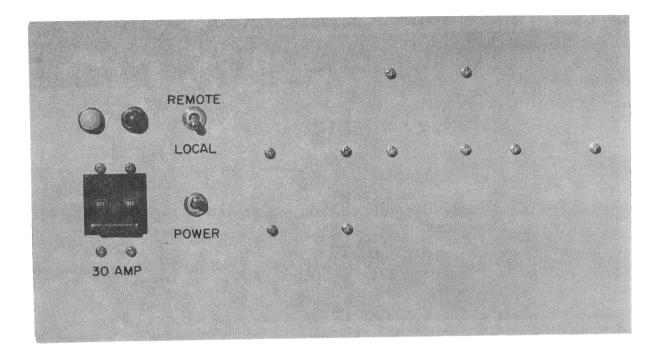

| 2-2 | Type 844 Power Control Panel               | 2-3 |

| 2-3 | CONO Data Word                             | 2-5 |

| 2-4 | CONI Data Word                             | 2-6 |

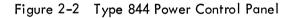

| 3-1 | DA10 Area Requirements                     | 3-2 |

| 3-2 | PDP-8/DA10 Device Selection Cards          | 3-3 |

| 3-3 | FM10 Buffer Output Mixer – PDP–8 Strapping | 3-6 |

| 3-4 | FM10 Buffer Output Mixer – PDP–9 Strapping | 3-7 |

| 3-5 | TO10 Buffer Input Mixer – PDP–8 Strapping  | 3-8 |

| 3-6 | TO10 Buffer Input Mixer – PDP–9 Strapping  | 3-9 |

| 4-1 | DA10 Interface – Simplified Block Diagram  | 4-2 |

## ILLUSTRATIONS (Cont)

|                                                              | Page                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

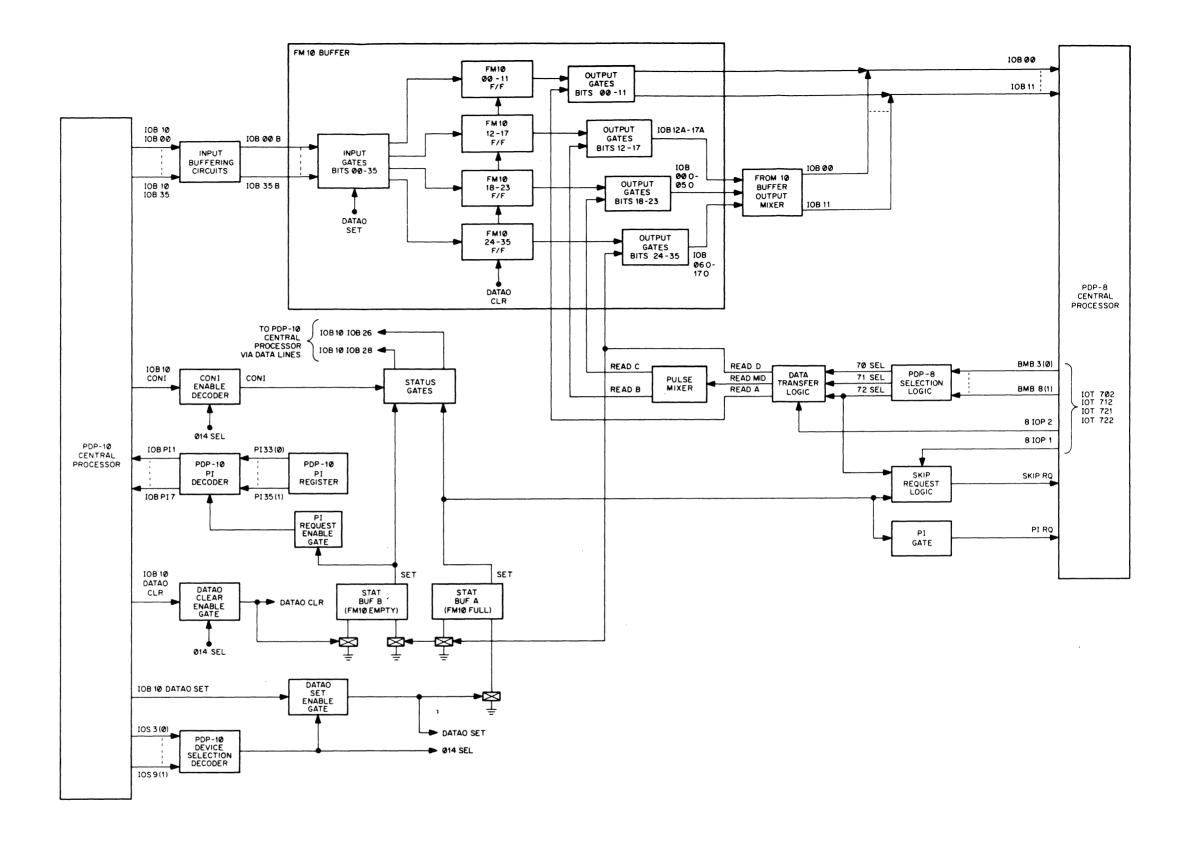

| Data Transfer from PDP-10 to PDP-8, Simplified Block Diagram | 4-5                                                                                                                                                                                                                                                                                                                                                                                                                                       |

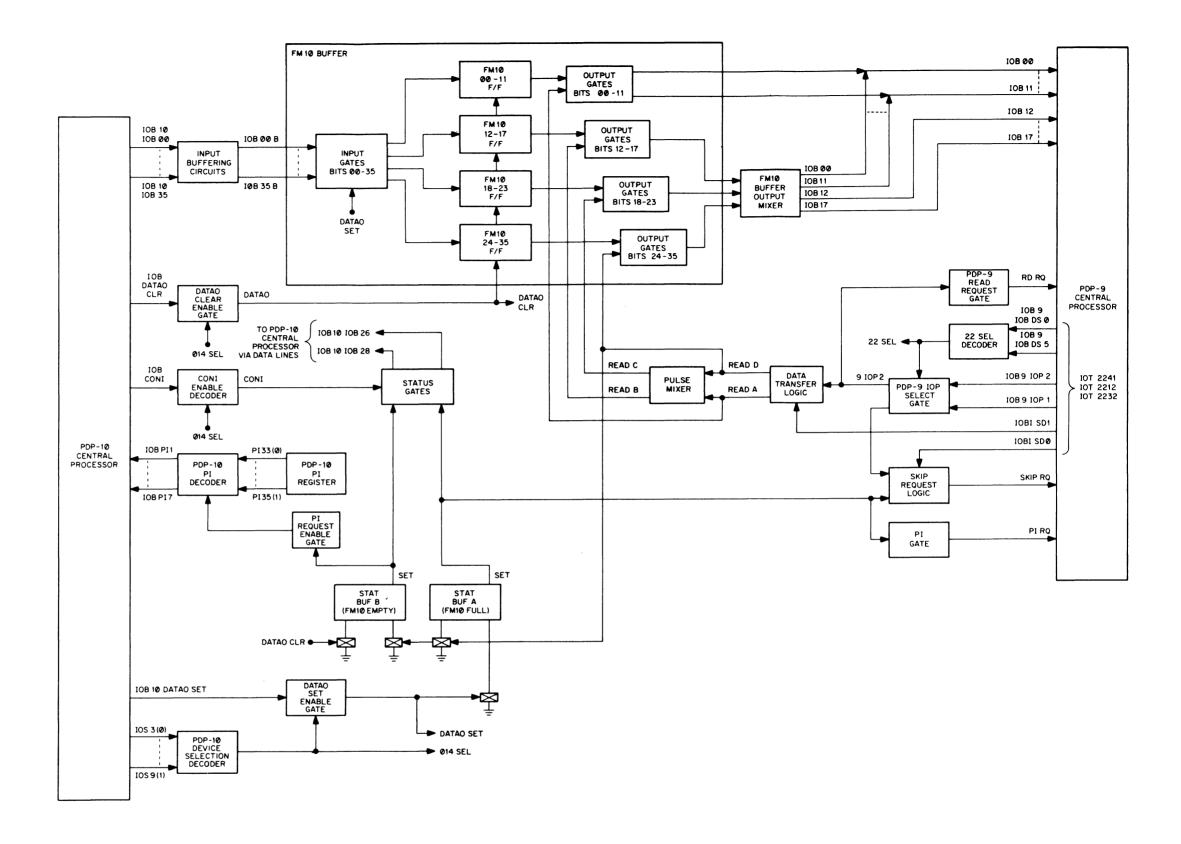

| Data Transfer from PDP-10 to PDP-9, Simplified Block Diagram | 4-9                                                                                                                                                                                                                                                                                                                                                                                                                                       |

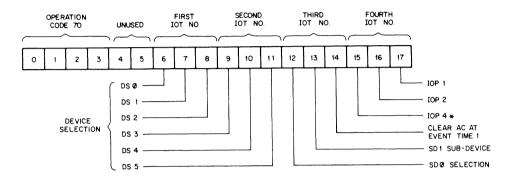

| PDP-9 IOT Instruction Format                                 | 4-11                                                                                                                                                                                                                                                                                                                                                                                                                                      |

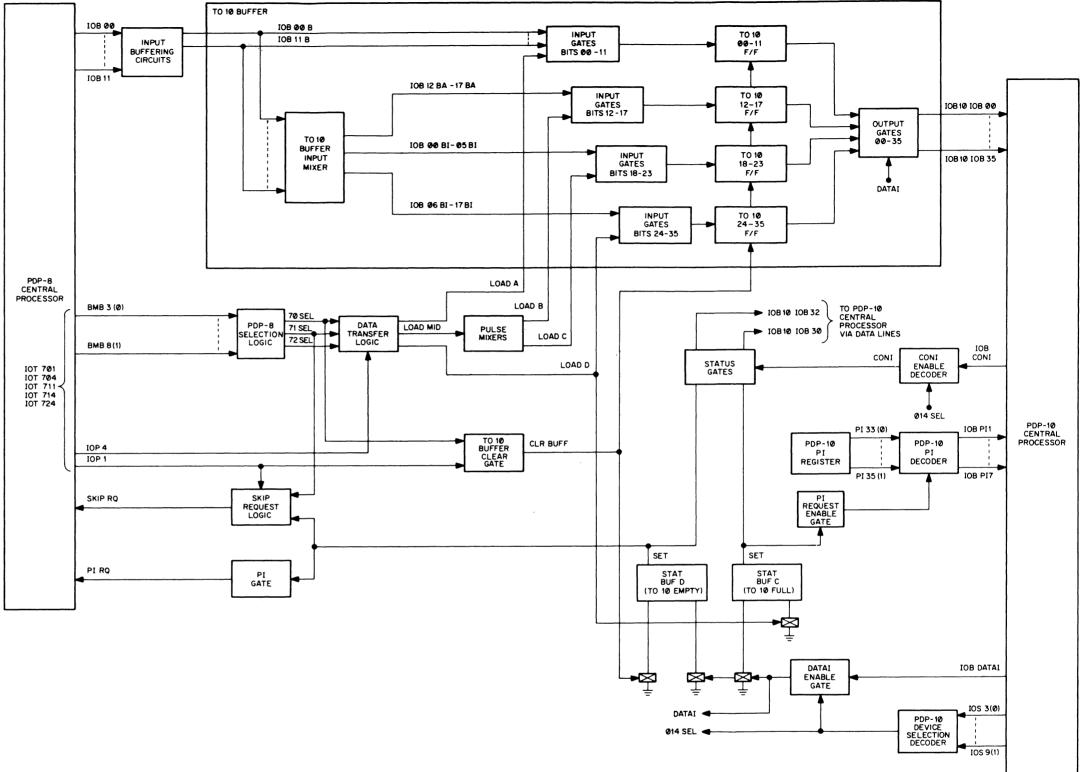

| Data Transfer from PDP-8 to PDP-10, Simplified Block Diagram | 4-13                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Data Transfer from PDP-9 to PDP-10, Simplified Block Diagram | 4-17                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DA10 Self-Check Block Diagram (Part 1)                       | 4-21                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DA10 Self-Check Block Diagram (Part 2)                       | 4-23                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power Up and CONO Instruction, Simplified Block Diagram      | 4-27                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DEC Standard Logic Symbols                                   | 6-3                                                                                                                                                                                                                                                                                                                                                                                                                                       |

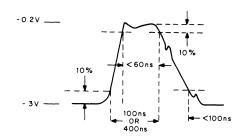

| R-Series and S-Series Pulses                                 | 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                       |

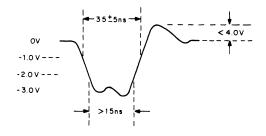

| B-Series Pulse                                               | 6-4                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                              | Data Transfer from PDP-10 to PDP-9, Simplified Block Diagram<br>PDP-9 IOT Instruction Format<br>Data Transfer from PDP-8 to PDP-10, Simplified Block Diagram<br>Data Transfer from PDP-9 to PDP-10, Simplified Block Diagram<br>DA10 Self-Check Block Diagram (Part 1)<br>DA10 Self-Check Block Diagram (Part 2)<br>Power Up and CONO Instruction, Simplified Block Diagram<br>DEC Standard Logic Symbols<br>R-Series and S-Series Pulses |

DA10 PDP-8/9 INTERFACE

DA10 PDP-8/9 Interface

## CHAPTER 1 INTRODUCTION

The DA10 Interface is an optional unit available with the PDP-10 System, manufactured by Digital Equipment Corporation (DEC) Maynard, Massachusetts. The interface allows data and control information to be transferred in both directions between the PDP-10 processor and either a PDP-8 processor or a PDP-9 processor.

This manual and the documents referenced herein provide the necessary information for the installation, operation and mainteance of the DA10 Interface Unit. The level of discussion in this manual assumes the reader is familiar with the logic symbology used by DEC, and the general operations of the PDP-8, PDP-9, and PDP-10 processors.

#### 1.1 REFERENCED PUBLICATIONS

Table 1-1 lists the publications which are available to supplement the information in this manual. These documents can be obtained from the nearest DEC regional office or by writing to:

Digital Equipment Corporation 146 Main Street Maynard, Massachusetts 01754

| Title                         | Document No.  | Description                                                                                                                                 |

|-------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Logic Handbook        | C-105         | Description and specifications of the<br>standard FLIP CHIP modules. Simplified<br>explaination of the selection and use<br>of the modules. |

| PDP-10 Maintenance<br>Manuals |               |                                                                                                                                             |

| Volume 1                      | DEC-10-HMAA-D | Complete information on the internal operation of the KA10 Processor mem-<br>ory, basic I/O, and options.                                   |

| Volume 2                      | DEC-10-HMBA-D | The engineering drawings associated with the KA10 Processor.                                                                                |

| Volume 3                      | DEC-10-HMCA-D | Description, schematics and specifi-<br>cations of the special modules used in<br>the PDP-10 System.                                        |

### Table 1–1 Available Publications

#### Table 1-1 (Cont) Available Publications

| Title                                                             | Document No.      | Description                                                                                            |

|-------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------|

| PDP–10 Peripheral Device<br>Engineering Drawing Set<br>(Volume 4) | DEC-10-I6DA-D     | Logic block diagrams and other pertin–<br>ent engineering drawings for BA10 and<br>DA10 options.       |

| PDP–8 Maintenance<br>Manual                                       | F-87              | Complete information on the PDP–8 processor operation and available                                    |

| PDP–9 Maintenance<br>Manuals                                      |                   | options.                                                                                               |

| Volume 1                                                          | F-97              | Complete information on the PDP-9<br>Processor and available options.                                  |

| Volume 2                                                          | F-97              | Logic block diagrams and other pertin-<br>ent engineering drawings for the PDP-9.                      |

| DA10 Interface Test                                               | MAINDEC-10-D8A0-D | A description and listing of the program<br>used to detect and diagnose malfunc–<br>tions in the DA10. |

| PDP-10 System<br>Reference Manual                                 | DEC-10-HGAA-D     | Programming and operating information on the PDP-10 Processor and options.                             |

#### 1.2 GENERAL DESCRIPTION

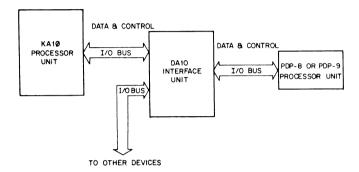

The DA10 Unit allows the interconnecting of the Input/Output (I/O) Bus from the KA10 Processor to the I/O bus of either a PDP-8 or PDP-9 Processor. Because of the differences in word length and I/O signals of the three devices, the DA10 interface assembles 12-bit words from the PDP-8 or 18-bit words from the PDP-9 into a 36-bit word for transfer to the PDP-10 Processor, or divides a 36-bit word from the PDP-10 into the required length for transfer to the associated processor. Figure 1-1 is a typical system diagram using the DA10 Interface. During input and output operations the DA10 receives both data and control information.

#### 1.3 EQUIPMENT SPECIFICATIONS

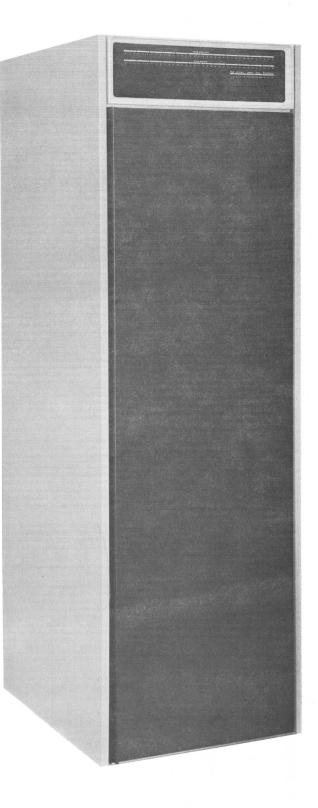

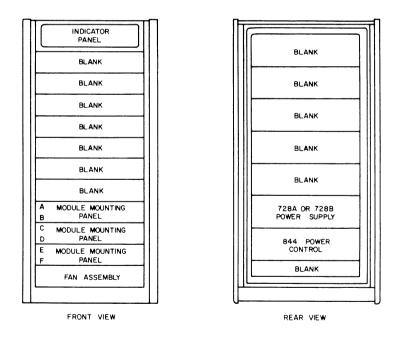

Figure 1-2 shows the assemblies mounted in the front and rear of the DA10 Unit which consists of a standard 19 in. cabinet, Type CAB-9B, which is contructed with welded steel frames and sheet aluminum covering. Access doors are mounted on the front and rear of the cabinet and are held closed by magnetic latches. The power control and dc power supply are mounted inside the rear access door on a plenum door that is latched by a spring-loaded pin at the top. Module mounting panels are mounted behind the front door with the wiring side facing outward. Access to the modules for removal, replacement and/or adjustment is gained through the rear of the cabinet. A fan at the bottom of the cabinet draws cooling air into the cabinet through a dust filter, and a fan assembly mounted in the logic rack passes the cooling air over the modules. The air is exhausted through an opening at the top of the cabinet. Table 1-2 contains the general specifications of the DA10A and DA10B units.

Figure 1-1 DA10 Interface, Typical System Diagram

Figure 1-2 DA10 Interface, Assembly Locations

| Voltage<br>ac              | Current<br>(A)<br>Nominal<br>115V | Power<br>Dissipation<br>(W) | Heat<br>Dissipation<br>(Btu/hr) | Dimensions<br>(in .)                    | Service<br>Clearance<br>(in.) | Weight<br>(lb) | Maximum<br>Cable<br>Lengths<br>(ft)                 |

|----------------------------|-----------------------------------|-----------------------------|---------------------------------|-----------------------------------------|-------------------------------|----------------|-----------------------------------------------------|

| See<br>Notes<br>1 and<br>2 | 2.0                               | 230                         | 800                             | Height: 69<br>Width:21–1/4<br>Depth: 27 | Front 36<br>Rear 36           | 300            | PDP-8: 20<br>PDP-9: 100<br>PDP-10: 150<br>(I/O Bus) |

#### Table 1-2 DA10 General Specifications

Note 1: PDP-10 Systems normally operate from 3-phase (WYE connected),  $115V \pm 10\%$ , 60 Hz  $\pm$  2 Hz, or 230V  $\pm$  10%, 50 Hz  $\pm$  2 Hz phase to neutral. Individual devices have separate power cords using 3-wire 30A (single phase) Hubbel Twistlock connectors. An earth/ground connection must be supplied through the power cord in addition to the ground bus requirements.

Note 2: Equipment for use within North America will have the 3-wire Hubbel #3331 (mates with Hubbel #3330) power cord cap (male plug) supplied on the end of a 25 ft line cord.

Equipment for use outside of North America will have a pressure-type terminal strip suitable for 8 to 18 gage wire enclosed within the equipment's power control.

Two configurations of the DA10 are available. The Type DA10A is a 60 Hz configuration and the Type DA10B is a 50 Hz configuration. With the exception of the power supply and power wiring, both configurations are similar. A 728 power supply is used with the DA10A and a 728A power supply is used with the DA10B. The differences in the power wiring of the two configurations are shown on drawing D-IC-DA10-0-3.

## CHAPTER 2 OPERATION AND PROGRAMMING

The following paragraphs provide the information and programming notes needed to operate the DA10 Interface with either a PDP-8 or PDP-9 Processor. For the detailed programming information refer to the PDP-10 System Reference Manual, DEC-10-HGAA-D.

#### 2.1 INDICATOR PANEL

The indicator panel (Figure 2-1) is mounted on the top front of the DA10 cabinet. It contains the indicators listed in Table 2-1 and displays the contents and status of the registers and flip-flops in this interface unit.

Figure 2-1 DA10 Interface, Indicator Panel

#### Table 2–1 DA10 Indicator Panel

| Indicator                        | Function                                                      |

|----------------------------------|---------------------------------------------------------------|

| FROM 10 BUFFER<br>(0 through 35) | Indicates the contents of the FM10 Buffer, bits 0 through 35. |

| TO 10 BUFFER<br>(0 through 35)   | Indicates the contents of the TO10 Buffer, bits 0 through 35. |

Table 2–1 (Cont) DA10 Indicator Panel

| Indicator                     | Function                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| PWR                           | Lights to indicate that dc power is applied to the logic rack.                                                                                                       |  |  |  |  |  |  |  |  |  |

| DEV SEL                       |                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| 8                             | Lights to indicate that DA10 is selected by the PDP-8 Processor.                                                                                                     |  |  |  |  |  |  |  |  |  |

| 9                             | Lights to indicate that DA10 is selected by the PDP-9 Processor.                                                                                                     |  |  |  |  |  |  |  |  |  |

| 10                            | Lights to indicate that DA10 is selected by the PDP-10 Processor.                                                                                                    |  |  |  |  |  |  |  |  |  |

| EMPTY                         |                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| TO 10<br>(STAT BUFD)          | Lights to indicate that the 36-bits in the TO10 Buffer have been transferred to the PDP-10 or that bit IOB32 is set to a 1 during a CONO instruction.                |  |  |  |  |  |  |  |  |  |

| FM10<br>(STAT BUFB)           | Lights to indicate that the last byte of the FM10 Buffer has been<br>transferred to the PDP-8 or PDP-9 or that IOB28 is set to a 1<br>during a CONO instruction.     |  |  |  |  |  |  |  |  |  |

| FULL                          |                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| TO 10<br>(STAT BUFC)          | Lights to indicate that the last byte from a PDP-8 or PDP-9 which loads the TO10 Buffer has been received or that bit IOB30 is set to a 1 during a CONO instruction. |  |  |  |  |  |  |  |  |  |

| FM 10                         | Lights to indicate that 36-bits from the PDP-10 have been loaded into the FM10 Buffer or that bit IOB26 is set to a 1 during a CONO instruction.                     |  |  |  |  |  |  |  |  |  |

| PI CHANNEL<br>(33 through 35) | Indicates the binary configuration of the PI Channel selected.                                                                                                       |  |  |  |  |  |  |  |  |  |

#### 2.2 POWER CONTROL PANEL

The Type 844 Power Control Panel (Figure 2-2) is mounted on the plenum door at the rear of the cabinet. This panel contains the switches and indicators (listed in Table 2-2) that are used to control the main ac power and select the local and remote modes of operation.

| Tab                  | le 2-2       |            |

|----------------------|--------------|------------|

| Power Control Panel, | Switches and | Indicators |

| Switch/Indicator            | Function                                                                         |  |  |  |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| White indicator             | Lights to indicate that 115 Vac or 230 Vac line power is applied.                |  |  |  |  |  |  |  |

| Red indicator               | Lights to indicate wrong polarization of the ac line or when 230 Vac is applied. |  |  |  |  |  |  |  |

| 30 AMP<br>(Circuit Breaker) | Controls the line power to the convenience outlets and protects the input line.  |  |  |  |  |  |  |  |

| REMOTE/LOCAL<br>(Switch)    | Selects either LOCAL or REMOTE mode of operation. (Refer to Paragraph 2.2.1.)    |  |  |  |  |  |  |  |

| POWER<br>(Switch)           | Controls line power to the dc power suppliers and DA10 system.                   |  |  |  |  |  |  |  |

## 2.2.1 Power Application

The DA10 has two power application modes selectable by the REMOTE/LOCAL switch on the power control panel. In the remote mode, power to the DA10 is controlled by the POWER switch on the control panel of the KA10 Processor when the following conditions are met.

a. The PDP-10 remote turn-on bus is connected to the DA10 power control.

b. The REMOTE/LOCAL switch on the power control panel of the DA10 is in the REMOTE position.

c. The circuit breaker and POWER switch on the DA10 power control panel are in the up position.

The local mode is in effect when the REMOTE/LOCAL switch is in the LOCAL position. This allows the 30A circuit breaker and POWER switch to control power to the unit.

#### 2.3 DEVICE SELECTION

The DA10 is selected via the I/O busses of the PDP-8 or PDP-9 or the PDP-10 central processors. Each central processor selects the DA10 in an independent manner, therefore, each method is explained separately in this section. For additional information on device selection, refer to Chapter 3, Installation.

#### 2.3.1 PDP-10 Device Selection

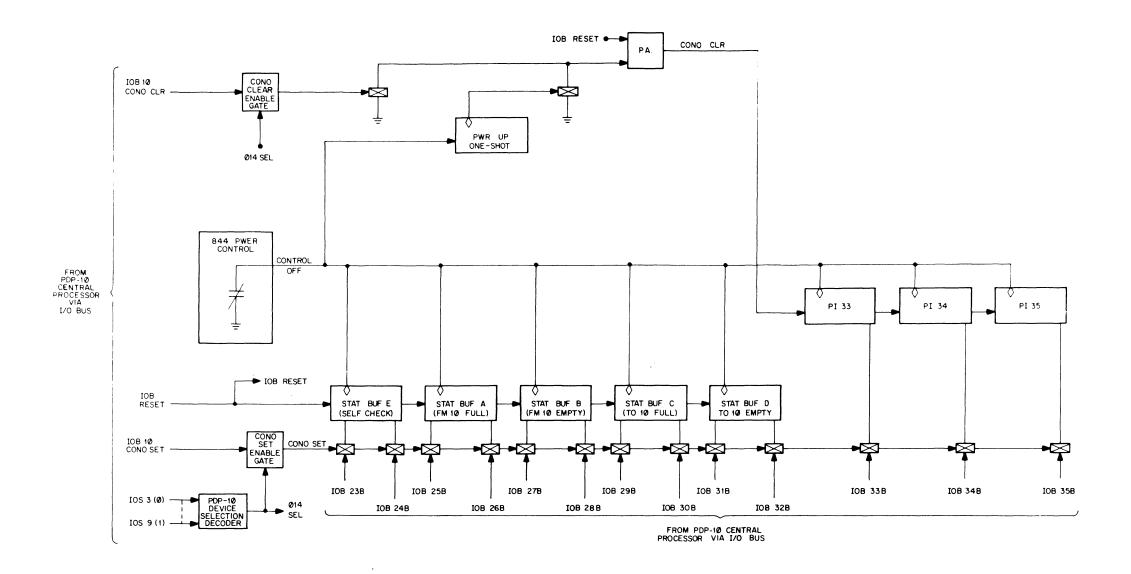

The DA10 is selected by bits 3 through 9 of the I/O instructions from the PDP-10 central processor. Seven complementary pairs of signals representing IOS3 through IOS9 are sent to the DA10 via the I/O bus. The IOS lines necessary to select code  $014_8$  (000 001  $1_2$ ) are connected to an AND gate shown on drawing D-BS-DA10-0-CS. When this code appears on the I/O bus, the AND gate is enabled and its output conditions the DATAO enable, DATAI enable, CONO enable, and CONI enable gates.

#### 2.3.2 PDP-9 Device Selection

The PDP-9 central processor uses bits 6 through 13 of IOT instructions for device selection. These eight levels form a 6-bit device selection code, DS0 through DS5, and two subdevice selection codes, SD0 and SD1. The PDP-9 device code  $22_8$  (010 010<sub>2</sub>) has been assigned to the DA10. When this code is present on the device selection lines of the I/O bus, it is decoded by the decoder shown on drawing D-BS-DA10-0-SI. The subdevice codes SD0 and SD1 are ANDed with the appropriate IOP signals to generate buffer clear and data transfer signals as shown on drawing D-BS-DA10-0-DTL.

#### 2.3.3 PDP-8 Device Selection

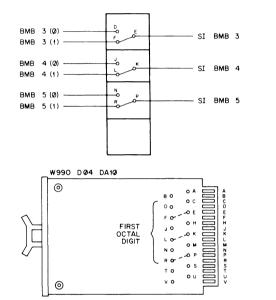

The PDP-8 central processor uses bits 3 through 8 of the IOT instructions for device selection. These lines are connected to a pair of W990 modules located in card slots D04 and D05, as shown on drawing D-BS-DA10-0-SI. Jumpers are inserted on the W990 modules to obtain the outputs that are used for decoding, and the decoders are shown in the upper left-hand corner of the drawing. The PDP-8 codes assigned to the DA10 are as follows;  $70_8$  (111 000<sub>2</sub>),  $71_8$  (111 001<sub>2</sub>), and 72 (111 010<sub>2</sub>). In the event that these codes conflict with another peripheral device in a particular system, they can be changed by modifying the jumpers on the W990 modules. It must be noted that the codes cannot overlap octal triads (i.e., the most significant octal bit must be the same for all selected codes). Refer to Paragraph 3.4.1 for additional information on jumper placement.

#### 2.4 PROGRAMMING NOTES

#### 2.4.1 PDP-10 Instructions

The DA10 responds to the standard PDP-10 I/O instructions. It requires one I/O device number (standard: 014) and provides program interrupt requests on one PI channel. Data, status, and control are transferred via the assigned I/O instructions. Various aspects of the I/O instructions are described below.

2.4.1.1 <u>CONO (Conditions Out)</u> - Control information is transferred to the DA10 via the right 18-bits of a CONO instruction. Figure 2-3 shows specifically which bits are used and the respective functions that are performed if the specific bit is a 1 during the performance of the CONO instruction. The CONO instruction is completed in two parts. First, the CONO clear pulse is sent to the DA10, and 1  $\mu$ s later, the CONO SET pulse is sent. Since the PI channel (bits 33 through 35) is cleared by the CONO clear pulse, the PI channel assignment must be placed on bits 33 through 35 whenever a CONO instruction is performed to set the PI channel.

| Clear  | Set    | Clear | Set  | Clear | Set   | Clear | Set   | Clear | Set   |    |       |    |

|--------|--------|-------|------|-------|-------|-------|-------|-------|-------|----|-------|----|

| Self   | Self   | FM10  | FM10 | FM10  | FM10  | TO10  | TO 10 | TO10  | TO10  |    | l Set |    |

| Check  | Check  | Full  | Full | Empty | Empty | Full  | Full  | Empty | Empty |    | el    |    |

| Enable | Enable | Flag  | Flag | Flag  | Flag  | Flag  | Flag  | Flag  | Flag  |    | I     |    |

| 23     | 24     | 25    | 26   | 27    | 28    | 29    | 30    | 31    | 32    | 33 | 34    | 35 |

Figure 2-3 CONO Data Word

2.4.1.2 <u>CONI (Conditions In)</u> - The status of the DA10 is transferred to the central processor by a CONI instruction. Figure 2-4 shows specifically which bits are transferred and their respective function. A 1 in any bit except bits 33 through 35 indicates that the associated flag is set. References to the CONI instruction include the CONSO and CONSZ instructions.

|    | Self<br>Check<br>Enable |    | FM 10<br>Full<br>Flag |    | FM10<br>Empty<br>Flag |    | TO 10<br>Full<br>Flag |    | TO 10<br>Empty<br>Flag | PI | Chann | el |

|----|-------------------------|----|-----------------------|----|-----------------------|----|-----------------------|----|------------------------|----|-------|----|

| 23 | 24                      | 25 | 26                    | 27 | 28                    | 29 | 30                    | 31 | 32                     | 33 | 34    | 35 |

Figure 2-4 CONI Data Word

2.4.1.3 <u>DATAO (Data Out)</u> - The DATAO instruction is performed in two parts. First the DATAO clear pulse is sent to the DA10, and 1 µs later, the DATAO SET pulse is sent. In the case of the DA10, the DATAO clear pulse performs the following functions: clears the FM10 buffer conditioning it for a data transfer; and clears the FM10 EMPTY flag removing the PI request to the PDP-10. The DATAO set pulse performs the following functions: strobes the data on the PDP-10 I/O bus into the FM10 buffer; and sets the FM10 FULL flag enabling the PI gate in the DA10 which sends a PI request to the PDP-8 or PDP-9. References to the DATAO instruction in this manual include the appropriate functions of the BLKO instruction.

2.4.1.4 <u>DATAI (Data In)</u> - When the DATAI instruction is performed, commands to the DA10 will transfer the contents of the TO10 buffer to the central processor via the 36 data lines of the I/O bus, clear the TO10 FULL flag, and set the TO10 EMPTY flag. The clearing of the TO10 FULL flag removes the PI request from the PDP-10, and the setting of the TO10 EMPTY flag sends a PI request to the PDP-8 or PDP-9. The references to DATAI instructions in this manual include the appropriate functions of the BLKI instruction.

#### 2.4.2 PDP-9 Programming

The DA10 is assigned device code 22<sub>8</sub> for the PDP-9. Both data and control to the DA10 pass via the assigned device codes. The PDP-9 receives a PI request when either the FM10 FULL flag or the TO10 EMPTY flag is set.

The DA10 status can be tested with the following instructions.

| Instruction | Test                                    |  |  |  |  |  |  |  |

|-------------|-----------------------------------------|--|--|--|--|--|--|--|

| 702221      | Skip one if the TO10 EMPTY flag is set. |  |  |  |  |  |  |  |

| 702241      | Skip one if the TO10 FULL flag is set.  |  |  |  |  |  |  |  |

A 702201 instruction will clear the TO10 buffer and the TO10 EMPTY flag.

The following instructions will load the TO10 buffer.

| Instruction | Function                                                                                                              |

|-------------|-----------------------------------------------------------------------------------------------------------------------|

| 702204      | Transfers the contents of the PDP-9 accumulator to bits 0 through 17 of the TO10 buffer.                              |

| 702224      | Transfers the contents of the PDP–9 accumulator to bits 18 through 35 of the TO10 buffer; and set the TO10 FULL flag. |

The following instructions will read the FM10 buffer.

| Instruction | Function                                                                                                                                         |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 702212      | Clears and loads the PDP-9 accumulator with bits 0 through 17 of the FM10 buffer.                                                                |

| 702232      | Clears and loads the PDP-9 accumulator with bits 18<br>through 35 of the FM10 buffer, clears the FM10 FULL flag<br>and sets the FM10 EMPTY flag. |

#### 2.4.3 PDP-8 Programming

35 36 37 The PDP-8 device selection codes **20**, **71**, **22** have been assigned to the DA10. Both data and control pass via the assigned selection codes. The PDP-8 receives a PI request when either the FM10 FULL flag or the TO10 EMPTY flag is set. The DA10 status can be tested with the following instructions.

| Instruction        | Test                                    |

|--------------------|-----------------------------------------|

| 3€<br>6 <b>₹</b> 1 | Skip one if the TO10 EMPTY flag is set. |

| 57<br>6721         | Skip one if the FM10 FULL flag is set.  |

| Z                  |                                         |

The  $6\frac{35}{10}$  instruction will clear the TO10 buffer and the TO10 EMPTY flag.

The following instructions load the TO10 buffer.

| Instruction        | Function                                                                                                               |

|--------------------|------------------------------------------------------------------------------------------------------------------------|

| 35<br>6 <b>704</b> | Transfers the contents of the PDP-8 accumulator to bits 0 through 11 of the TO10 buffer.                               |

| 36<br>6714<br>37   | Transfers the contents of the PDP–8 accumulator to bits 12 through 23 of the TO10 buffer.                              |

| 57<br>67/24        | Transfers the contents of the PDP–8 accumulator to bits 24 through 35 of the TO10 buffer, and sets the TO10 FULL flag. |

## The following instructions read the contents of the FM10 buffer.

| Instruction    | Function                                                                                                                                                             |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67802          | Loads the PDP-8 accumulator with the contents of bits 0 through 11 of the FM10 buffer (inclusive OR).                                                                |

| 6 <b>7</b> -12 | Loads the PDP-8 accumulator with the contents of bits 12 through 23 of the FM10 buffer (inclusive OR).                                                               |

| 6722           | Loads the PDP-8 accumulator with the contents of bits 24<br>through 35 of the FM10 buffer (inclusive OR), clears the<br>FM10 FULL flag and sets the FM10 EMPTY flag. |

## CHAPTER 3

#### INSTALLATION

The information necessary to connect the DA10 unit to the PDP-10 processor and to either a PDP-8 or PDP-9 processor is provided in the following section. It includes the special module and buffer wiring instructions and adjustment procedures required for a standard installation.

#### 3.1 POWER REQUIREMENTS

The DA10 unit connects to the ac line as specified in Table 1-2.

#### 3.2 ENVIRONMENTAL CONDITIONS

The operating environment for the DA10 unit is the same as that required for the PDP-10 processor. Refer to the appropriate section in the PDP-10 Maintenance Manual, Volume I for specific environmental limits.

#### 3.3 SPACE REQUIREMENTS

The DA10 cabinet can be installed at any location provided that the specified cable and power cord lengths are used. The dimensions of the cabinet and the minimum service area are illustrated in Figure 3-1.

#### 3.4 DEVICE SELECTION WIRING

Since a conflict with another peripheral device could occur, the PDP-8 device selection lines are sent to the PDP-8 device selection decoder through a pair of device selection cards. A brief description of these cards and the wiring information follow.

#### 3.4.1 PDP-8 Device Selection Cards

In the DA10, the PDP-8 device selection lines connect to the device selection cards located in slots D04 and D05. Jumpers located on these selection cards can be arranged so the DA10 will respond to three device selection codes within the PDP-8 repertoire. If special device selection codes have not been specified by the customer, the strapping on the device selection cards is connected so that the DA10 will respond to standard device selection codes of 70, 71, and 72.

Figure 3-1 DA10 Area Requirements

Figure 3-2 is provided to aid the maintenance personnel in understanding the PDP-8/DA10 device selection cards. A table at the top of the figure shows the condition of bits 3 through 8 for standard device selection codes. A schematic representation and a pictorial representation of the device selection cards show the jumper placement for the standard device selection codes. When different device selection codes are utilized by the DA10, the table at the bottom of the figure may be used to determine the new strapping requirements. It is important that the software must reflect any change from the standard device selection codes.

#### 3.5 DATA TRANSFER PULSE MIXERS

The DA10 is capable of transferring 12-bit words to and from a PDP-8 central processor and 18-bit words to and from a PDP-9 central processor. To fulfill these functions, a data transfer pulse mixer (a jumper network) has been designed into the DA10. Two W990 modules located in slots B23 and A09 contain the jumper network. When the DA10 is shipped, the data transfer pulse mixer is strapped for the central processor that is specified by the user. During installation, however, the data transfer pulse mixer modules should be checked to assure that the strapping is correct. The following discussions, which describe the data transfer pulse mixer, are intended to explain why the data transfer pulse mixer is required, describe its operation when strapped for the different central processors, and provide guidelines for changing the strapping, if required.

| DEVICE<br>SELECTION<br>CODE | FI  | DIG | TAL | SECOND OCTAL<br>DIGIT |     |   |     |   |     |   |     |   |

|-----------------------------|-----|-----|-----|-----------------------|-----|---|-----|---|-----|---|-----|---|

|                             | BIT | 3   | віт | 4                     | BIT | 5 | BIT | 6 | BIT | 7 | BIT | 8 |

| 70                          | 1   |     | 1   |                       | 1   |   | 0   |   | 0   |   | 0   |   |

| 71                          | 1   |     | 1   |                       | 1   |   | 0   |   | 0   | _ | 1   |   |

| 72                          | 1   |     | 1   |                       | 1   |   | 0   |   | 1   |   | 0   |   |

|       |           |               |    |   |                 |           |                           |    | DØ5 JU                     | MPERS |                           |    |

|-------|-----------|---------------|----|---|-----------------|-----------|---------------------------|----|----------------------------|-------|---------------------------|----|

|       | BIT NO.   | D Ø 4 JUMPERS |    | ] |                 | BIT NO.   | FIRST DEVICE<br>SEL. CODE |    | SECOND DEVICE<br>SEL. CODE |       | THIRD DEVICE<br>SEL. CODE |    |

|       | BIT NO.   | FROM          | то |   |                 |           | FROM                      | то | FROM                       | то    | FROM                      | то |

|       | BIT 3 = 1 | -             | F  |   |                 | BIT 6 = 1 | D                         | н  | F                          | н     | .1                        | н  |

| FIRST | BIT 3 = Ø | -             | D  |   | SECOND<br>OCTAL | BIT 6 = Ø | U                         | E  |                            | E     | v                         | E  |

| DIGIT | BIT 4 = 1 |               | L  |   | DIGIT           | BIT 7 = 1 | ~                         | N  |                            | N     | 0                         | N  |

|       | BIT 4 = Ø | ĸ             | J  |   |                 | BIT 7 = 0 | ĸ                         | L  | M                          | L     | Р                         | L  |

|       | BIT 5 = 1 |               | R  |   |                 | BIT 8 = 1 |                           | U  | -                          | U     |                           | U  |

|       | BIT 5 = 0 | 1 "           | N  |   |                 | BIT 8 = 0 | R                         | S  |                            | S     | v                         | S  |

Figure 3-2 PDP-8/DA10 Device Selection Cards

When a PDP-9 reads the FM10 buffer, data must be present on its I/O bus for approximately 1 µs to complete the data transfer. To complete a data transfer to a PDP-8, only the leading edge

transition of the data is required. In order to fulfill both of these requirements, a 100 ns DTL 8 READ A pulse (and DTL 8 READ D) and a 1 µs DTL 9 READ A pulse (and DTL 9 READ D) are generated in the data transfer logic and sent to the data transfer pulse mixer. The strapping on the data transfer pulse mixer is varied as explained below to select the appropriate pulse. (Refer to drawing D-BS-DA10-0-DTPM (sheets 1 and 2).)

Sheet 1 of drawing D-BS-DA10-0-DTPM shows the strapping for the PDP-8 configurations. When a PDP-8 is interfaced with the DA10, three sequential READ pulses that are generated under program control are required to transfer three 12-bit bytes out of the FM10 buffer and onto the PDP-8 I/O bus. Three sequential LOAD pulses are also required to load three 12-bit data words into the TO10 buffer via the PDP-8 I/O bus.

When the first byte is to be read, the DTL 8 READ A pulse is generated and sent to pin D of module A09 generating the DTPM READ AX pulse. The DTPM READ AX pulse is returned to the data transfer logic and is used to generate the DTL READ A pulse that enables the output gates for bits 00 through 11 of the FM10 buffer gating the first byte onto the PDP-8 I/O bus. When the second byte is to be read, the DTL READ MID pulse is generated and sent to pins K and S of module A09 generating the DTPM READ C pulses. The DTPM READ B pulse enables the output gates for bits 12 through 17 and the DTPM READ C pulse enables the output gates for bits 18 through 23. With bits 12 through 23 enabled, the second byte is gated onto the PDP-8 I/O bus. The last byte is transferred in a way similar to the first byte. The DTL 8 READ D pulse is sent to pin L of module A09 generating the DTPM READ DX pulse. It is returned to the data transfer logic generating the DTP READ DX pulse that enables the output gates for bits 24 through 35 of the FM10 buffer.

When the first data word from the PDP-8 is to be loaded into the TO10 buffer, the DTL LOAD A pulse is sent directly to the input gates for bits 00 through 11 of the TO10 buffer gating the data into the TO10 buffer. To load the second data word, the DTL LOAD MID pulse is generated and sent to pins K and S of module B23 generating the DTPM LOAD C pulses which enable the input gates for bits 12 through 23 of the TO10 buffer. The last data word is loaded by the DTL LOAD D pulse that is sent directly to the input gates for bits 24 through 35 of the TO10 buffer.

If the DA10 is to be interfaced with a PDP-9, the A09 and B23 modules require different strapping because of the 18-bit word length of the PDP-9. The PDP-9 configuration of the data transfer pulse mixers is shown on sheet 2 of drawing D-BS-DA10-0-DTPM. When the first 18-bit byte is read from the FM10 buffer, the DTL 9 READ A pulse is sent to pin F of module A09 generating the DTPM READ AX pulse. The DTPM READ AX pulse is used to generate the DTL READ A pulse that enables the output gates for bits 00 through 11 of the FM10 buffer; and after being applied to pin H of module A09, generates the DTPM READ B pulse that enables the output gates for bits 12 through 17 of the FM10 buffer. With output gates 00 through 17 enabled, the 18-bit byte is gated onto the PDP-9 I/O bus.

3-4

The second 18-bit byte from the FM10 buffer is gated onto the PDP-9 I/O bus in a similar manner except the DTL 9 READ D pulse initiates the data transfer by generating the DTPM DX pulse. The DTPM READ DX pulse is used to generate the DTL READ D pulse that performs the following data transfer functions: enables the output gates for bits 18 through 23. With the output gates for bits 18 through 35 enabled, the second byte is placed on the PDP-9 I/O bus.

To load the TO10 buffer, the PDP-9 performs two 18-bit data transfers. During the first data transfer, the DTL LOAD A pulse enables the input gates for bits 00 through 11 and generates the DTPM LOAD C pulse enabling the input gates for bits 18 through 23. With the input gates enabled, the data on the PDP-9 I/O bus is loaded into bits 18 through 35 of the TO10 buffer.

A comparison of sheets 1 and 2 of drawing D-BS-DA10-0-DTPM will show the differerences in the data transfer pulse mixer strapping. When a PDP-8 is interfaced with the DA10, the strapping shown on sheet 1 is utilized; sheet 2 shows the strapping required for interfacing a DA10 with a PDP-9.

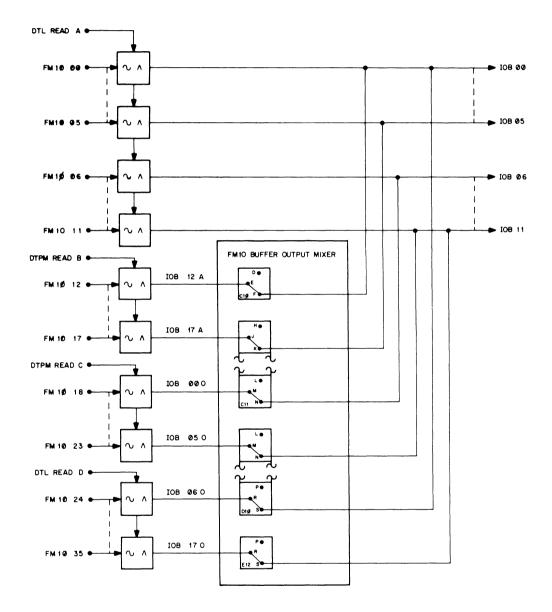

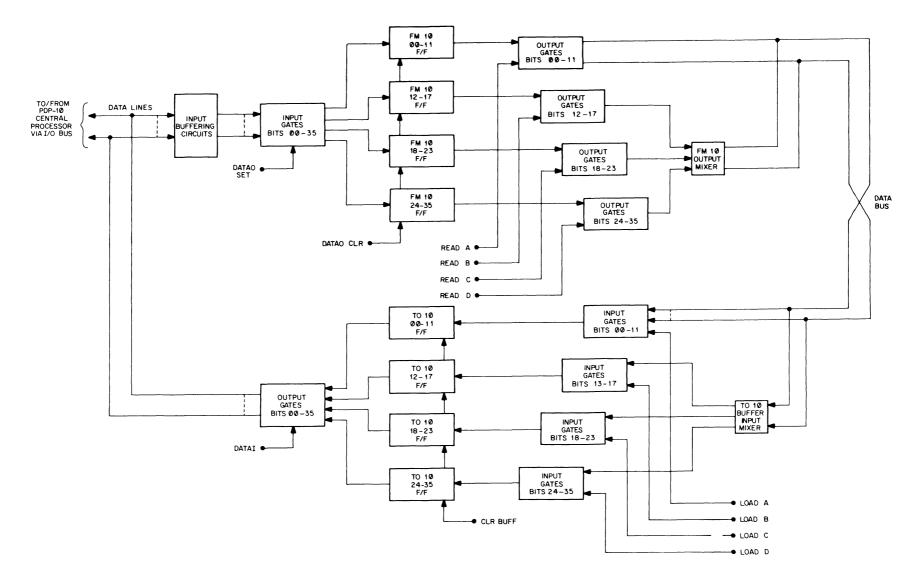

#### 3.6 FM10 BUFFER OUTPUT MIXER

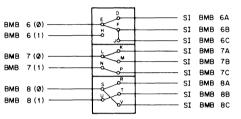

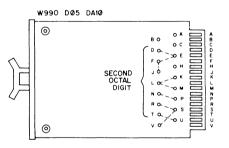

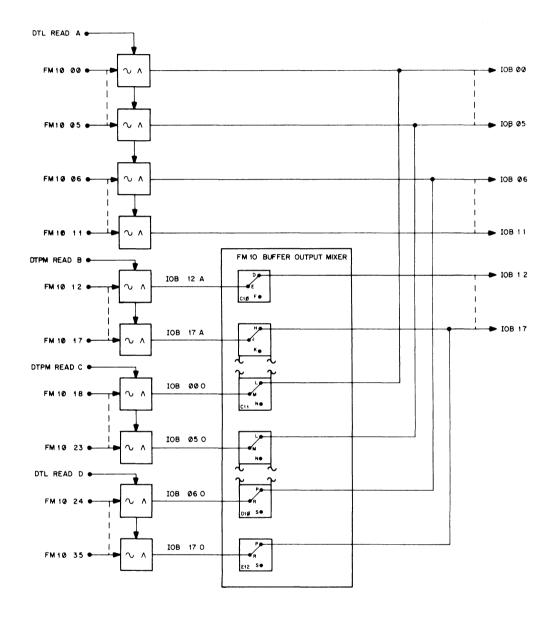

As stated in the discussion of the data transfer pulse mixer, the 36-bits of data stored in the FM10 buffer are read in the following manner: three 12-bit words are strobed onto the PDP-8 I/O bus; or two 18-bit words are strobed onto the PDP-9 I/O bus. The DA10 is made compatible with either the PDP-8 or PDP-9 by the strapping arrangment on the FM10 buffer output mixer, a jumper network contained on five W990 modules located in slots C10, C11, D10, D11 and E12. To illustrate the strapping arrangements for the PDP-8 and PDP-9, Figures 3-3 and 3-4 show a simplified view of output mixer along with the FM10 buffer output gates and the I/O busses.

As shown on Figure 3-3, bits 00 through 11 are strobed directly onto the PDP-8 I/O bus when the DTL READ A pulse reads the first byte. When the second byte is read, the DTPM READ B pulse storbes bits 12 through 17 and the DTPM READ C pulse strobes bits 18 through 23. The data on lines IOB 12A through IOB 17A and IOB 00O through IOB 05O are placed on the PDP-8 I/O bus via the strapping of the output mixer. To read the third byte, the DTL READ D pulse strobes the data onto lines IOB 06O through IOB 17O sending the data to the PDP-8 I/O bus via the strapping on the output mixer.

When a PDP-9 is interfaced with the DA10, the output mixer strapping is changed so that the DA10 will accommodate the 18-bit word length of the PDP-9. Figure 3-4 shows a simplified view of the PDP-9 strapping. When the first 18-bit byte is read, bits 00 through 11 are strobed directly onto the associated bits of the PDP-9 I/O bus by the DTL READ A pulse, and bits 12 through 17 are strobed onto lines IOB 12A through IOB 17A by the DTPM READ B pulse. Then, bits 12 through 17 are placed on the associated bits of the PDP-9 I/O bus via the output mixer strapping. To read the second byte,

the DTPM READ C pulse strobes bits 18 through 23 and the DTL READ D pulse strobes bits 24 through 35. The data on IOB 000 through IOB 170 is placed on the appropriate line of the PDP-9 I/O bus via the output mixer strapping.

Figure 3-3 FM10 Buffer Output Mixer - PDP-8 Strapping

Figures 3–3 and 3–4 show only a portion of the jumper network that is contained in the output mixer, but they do show the key jumpers that are required to understand the output mixer operation. For the complete strapping arrangement, refer to drawing D-BS-DA10–0-FBOM (sheets 1 and 2). Sheets 1 and 2 show the strapping required by a PDP-8 and PDP-9 respectively. The input signal names to the mixer (IOB 12A - IOB 17A, etc.) shown in Figures 3-3 and 3-4 should be prefixed with FTB 9 to obtain the signal names shown on drawing D-BS-DA10-0-FBOM. When the equipment is shipped, the output mixer is strapped for operation with the central processor specified by the user. To assure that the strapping arrangement is correct, check the output mixer modules when the equipment is installed.

Figure 3-4 FM10 Buffer Output Mixer - PDP-9 Strapping

#### 3.7 TO10 BUFFER INPUT MIXER

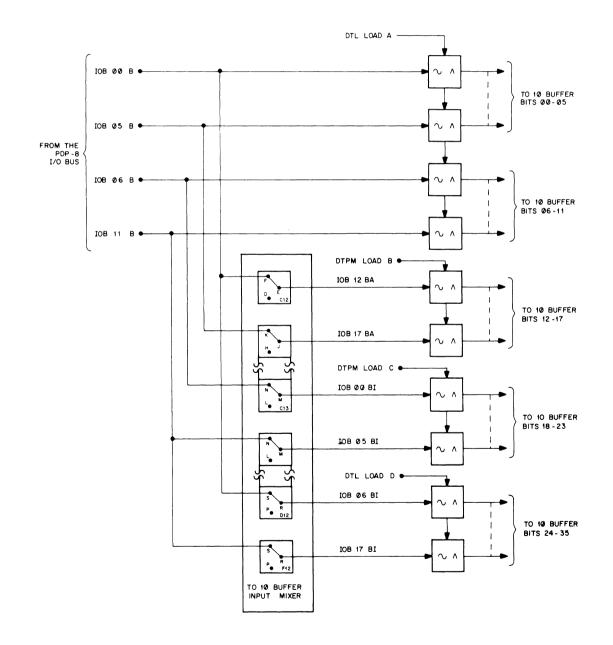

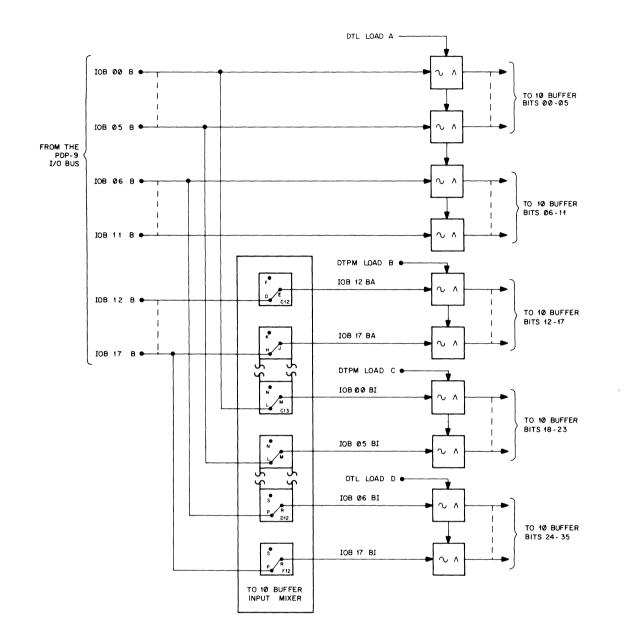

The TO10 buffer input mixer, a jumpering network, is contained on five W990 modules that are located in slots C12, C13, D12, D13, and F12. By varying the strapping arrangement of the input mixer, the DA10 is conditioned for operation with a PDP-8 or PDP-9. Figures 3-5 and 3-6 illustrate the two strapping arrangements in simplified block diagram form. As explained in the discussion of the data transfer pulse mixer, the 36-bit TO10 buffer is loaded in one of two ways described below.

Figure 3-5 TO10 Buffer Input Mixer - PDP-8 Strapping

Figure 3-6 TO10 Buffer Input Mixer - PDP-9 Strapping

A PDP-8 performs three 12-bit transfers; or a PDP-9 performs two 18-bit transfers. The input mixer strapping is one of the items which must be varied to make the DA10 compatible with either a PDP-8 or PDP-9. Both strapping arrangements are explained in the following discussions.

Figure 3-5 shows that data from the PDP-8 I/O bus is sent directly to the input gates for bits 00 through 11 of the TO10 buffer. Also, it can be seen that the data from the PDP-8 I/O bus is sent to the input gates for bits 12 through 23 and bits 24 through 35 via the input mixer strapping. To complete the first transfer, the DTL LOAD A pulse enables the input gates for bits 12 through 23; the data on lines IOB 12BA through IOB 17BA is loaded into the TO10 buffer by the DTPM LOAD B pulse; and the data on lines IOB 00BI through IOB 05BI is loaded by the DTPM LOAD C pulse. The third data word is placed on the I/O bus and sent to lines IOB 06BI through IOB 17BI via the input mixer strapping. Then, the DTL LOAD D pulse gates the data on the lines into bits 24 through 35 of the TO10 buffer.

Figure 3-6 shows the input mixer strapping arrangement used when the DA10 is interfaced with a PDP-9. The data on lines IOB 00B through IOB 11B is sent to the input gates for bits 00 through 11 and to the input gates for bits 18 through 29 via the input mixer strapping. The data on lines IOB 12B through 17B is sent to the input gates from bits 12 through 17 and 30 through 35 via the input mixer strapping. When the PDP-9 transfers the first data word, the DTL LOAD A and DTPM LOAD B pulses enable the input gates for bit 00 through 17 gating the data into the TO10 buffer. During the transfer of the second word, the DTPM LOAD C and DTL LOAD D pulses enable the input gates for bits 18 through 35 and gates the second PDP-9 data word into bits 18 through 35 of the TO10 buffer.

Only a portion of the input mixer is shown in Figures 3-5 and 3-6. Refer to drawing D-BS-DA10-0-TBIM (sheets 1 and 2) for the complete strapping arrangement. Sheets 1 and 2 show the strapping required for use with a PDP-8 and a PDP-9 respectively. The output signal names from the input mixer (IOB 12BA, IOB 17A, etc.) shown in Figures 3-5 and 3-6 should be prefixed with TBIM 9 to obtain the signal names shown on the drawing. When the equipment is shipped, the input mixer is strapped to operate with the central processor specified by the user. During installation, the input mixer strapping arrangement should be checked to assure that it is is correct.

#### 3.8 I/O BUS CONNECTIONS

The DA10 is connected to the PDP-10 central processor via the PDP-10 I/O bus and to either the PDP-8 or PDP-9 via their I/O busses. The I/O bus cables for each system are looped from the central processor through the options that operate from the specific I/O bus. These cables are ended with connector modules that are inserted into connector blocks on the module mounting panels. To insert the cables, access is gained through the rear of the DA10 cabinet. Drawing D-MU-DA10-0-2 (sheet 2) shows where the I/O bus cables are inserted. Drawing D-IC-DA10-0-IOBI (3 sheets) shows the I/O bus interface for the three systems as follows: sheet 1 shows the PDP-9; sheet 2 shows the PDP-10; and sheet 3 shows the PDP-8. Since the DA10 is a part of the three I/O bus systems, the maximum I/O bus cable lengths are as follows: 20 ft for the PDP-8; 100 ft for the PDP-9; and 150 ft for the PDP-10.

#### 3.8.1 PDP-10 I/O Bus Cables

Each PDP-10 bus cable is terminated by two W851 connector modules joined by mechanical hardware to form a cable assembly. Since the I/O bus is looped between the PDP-10 I/O devices, the

3-10

I/O bus cable assemblies from a preceding device are connected to the DA10 and the DA10 I/O bus cable assemblies are connected to the next device in the loop. The connections are completed by screwing the connector assemblies into the appropriate card slots. The margin cable and remote turn-on cable are also looped between the PDP-10 options to complete the margin and remote turn-on circuits. Table 3-1 indicates the location of the PDP-10 I/O bus cables in the DA10.

Table 3–1 PDP–10 I/O Bus Cables

| I/O Bus<br>Cable<br>Assembly | Connector<br>Module | DA10 Card Slots |      |  |  |

|------------------------------|---------------------|-----------------|------|--|--|

|                              | 1A and 1B           | EF25            | EF29 |  |  |

|                              | 1C and 1D           | EF26            | EF30 |  |  |

| 2                            | 2A and 2B           | EF27            | EF31 |  |  |

| 2                            | 2C and 2D           | EF28            | EF32 |  |  |

## 3.8.2 PDP-9 I/O Bus Cables

Each PDP-9 I/O bus cable is terminated by two W850 connector modules joined by mechanical hardware to form a cable assembly. A set of PDP-9 I/O bus cables are required to interface the PDP-9 to the DA10. The connections are completed by screwing the connector assemblies into the appropriate DA10 card slots shown in Table 3-2.

| I/O Bus<br>Cable<br>Assembly | Connector<br>Module | DA10 Card Slots |      |  |  |

|------------------------------|---------------------|-----------------|------|--|--|

|                              | 1A and 1B           | EF13            | EF17 |  |  |

| 1                            | 1C and 1D           | EF14            | EF18 |  |  |

| 2                            | 2A and 2B           | EF15            | EF19 |  |  |

| ۷                            | 2C and 2D           | EF 16           | EF20 |  |  |

Table 3-2 PDP-9 I/O Bus Cables

#### 3.8.3 PDP-8 I/O Bus Cables

Each PDP-8 I/O bus cable is terminated by a W021 connector module. A set of cables are required to interface the PDP-8 to the DA10. The connection is completed by inserting the connector module into the appropriate card slot shown in Table 3-3.

| Connector<br>No. | DA10 Ca    | rd Slots |

|------------------|------------|----------|

| ,                | E01        | E07      |

| 2                | E01<br>E02 | E07      |

| 3                | E03        | E09      |

| 4                | E04        | E010     |

| 5                | E05        | E011     |

| 6                | E06        | F06      |

| 7                | F01        | F07      |

| 8                | F02        | F08      |

| 9                | F03        | F09      |

| 10               | F04        | F10      |

| 11               | F05        | F11      |

Table 3-3 PDP-8 I/O Bus Cables

#### 3.9 ONE-SHOT ADJUSTMENT

The DA10 contains two one-shots as a part of the test logic. They are located on an R302 Delay module mounted in card slot A10. Because these one-shots are a part of the test logic, they do not affect the data transfer operation. If the one-shots are adjusted incorrectly, they could cause the self-test to fail. During factory checkout, the trimpots on the delay modules are adjusted to the maximum clockwise position (looking at the back of the module) and should remain in that position after shipment. When the DA10 is installed, the adjustment of the trimpots should be checked for correct adjustment before self-test is performed.

## CHAPTER 4 THEORY OF OPERATION

A functional description of the DA10 Interface on a simplified block diagram level is presented in the following paragraphs. This is followed by detailed theory information referencing both detailed block diagrams and the logic block diagrams that are contained in the Peripheral Device Engineering Drawing Set, Volume IV, Doc. No. DEC-10-16DA-D.

#### 4.1 FUNCTIONAL DESCRIPTION

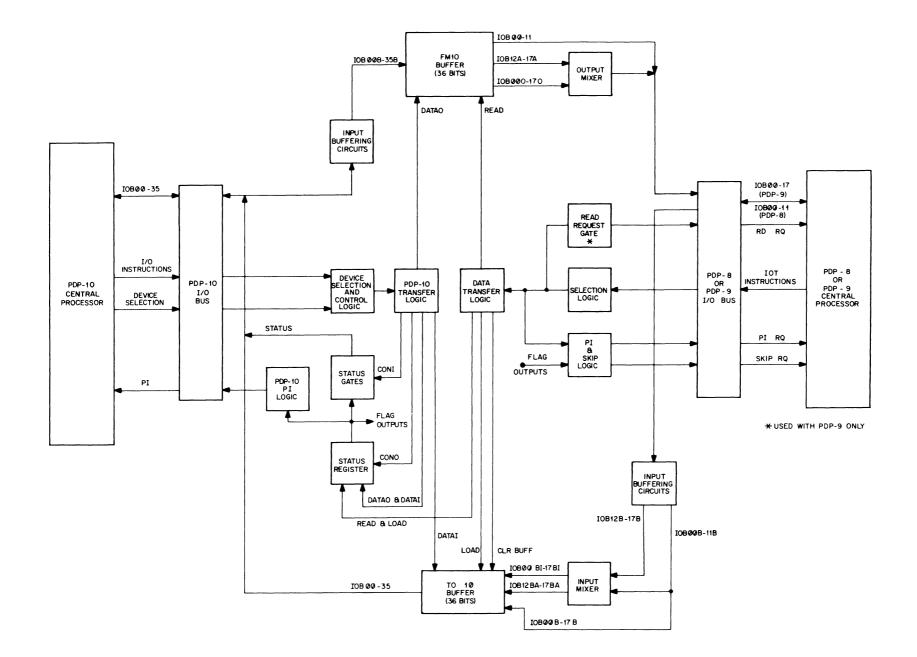

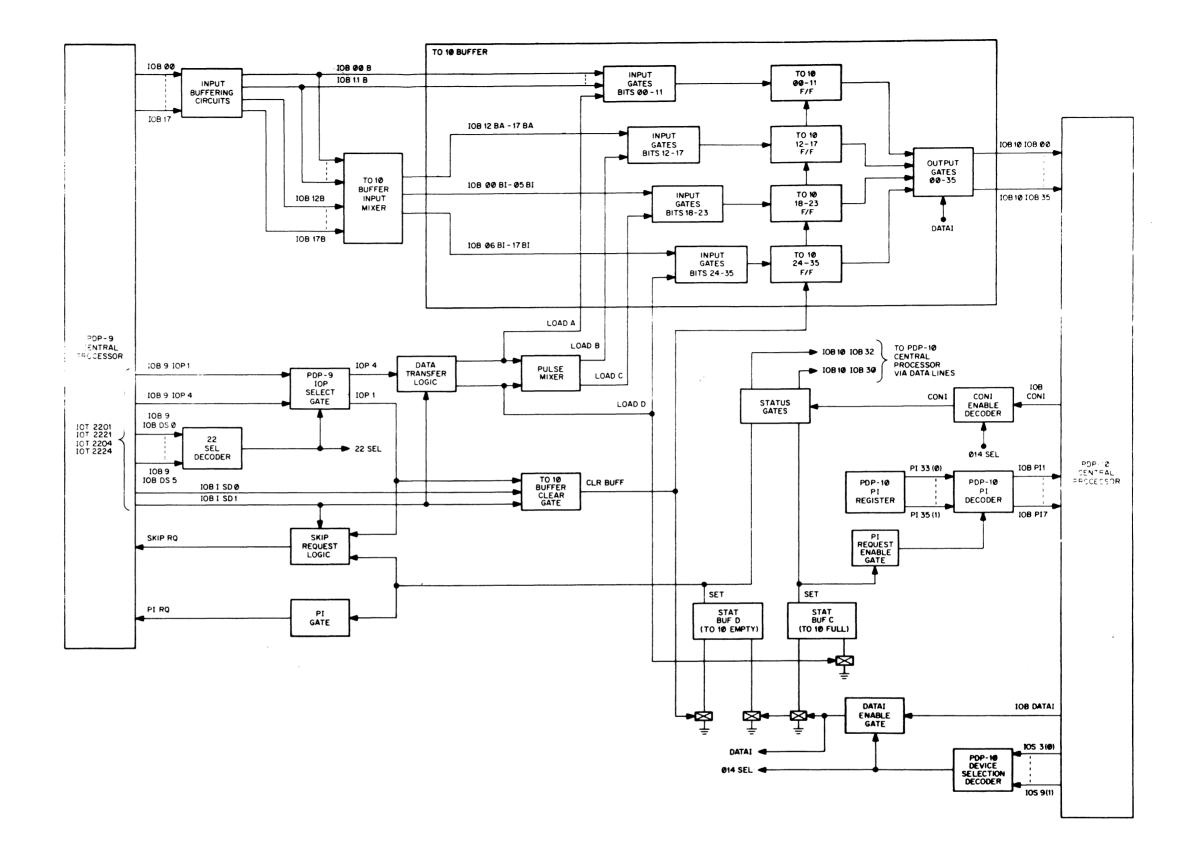

Figure 4-1 is a simplified block diagram of the DA10 Interface connected to a PDP-8 or PDP-9 processor. The DA10 contains two 36-bit buffers (FM10 and TO10), five status flags (located in the status register), and the control logic necessary for device selection and data transfer. To simplify the following discussion, all PDP-10 instructions and IOT instructions are performed by the central processor under program control.

Since data can be transferred through the DA10 in either direction, a data transfer from a PDP-10 is discussed first. When a transfer from a PDP-10 is to be executed, the PDP-10 central processor performs a DATAO instruction, during which the following events occur: a 36-bit data word is sent to the FM10 buffer via the I/O bus and the input buffering circuits; the FM10 buffer is cleared; the data from the input buffering circuits is loaded into the FM10 buffer; and the FM10 FULL flag is set. When the FM10 FULL flag is set, a program interrupt request (PI RQ) signal is sent to the PDP-8 or PDP-9 central processor.

After receiving the PI RQ signal, the PDP-8 or PDP-9 central processor enters a programmed routine to sequentially check the status flags connected to the PI line by performing a series of IOT instructions. When the IOT instruction that checks the FM10 FULL flag is performed, the skip logic generates a skip request (SKIP RQ) signal and program control is transferred to the appropriate service routine.

The PDP-8 or PDP-9 central processor completes the service routine by performing a series of IOT instructions. Each IOT instruction enables the data transfer logic to generate a READ pulse that is sent to the FM10 buffer. Each READ pulse transfers a portion of the data in the 36-bit FM10 buffer to the PDP-8 or PDP-9 central processor via the I/O bus. In the case of a PDP-9, the read request gate generates a RD RQ signal that is required by the PDP-9 during a data transfer.

When a PDP-8 is connected to the DA10, three IOT instructions are performed to fetch three 12-bit data words. When a PDP-9 is connected to the DA10, two IOT instructions are performed to fetch two 18-bit data words.

Figure 4-1 DA10 Interface - Simplified Block Diagram

4-2

During the last IOT instruction, the READ pulse is sent to the status register to set the FM10 EMPTY flag and clear the FM10 FULL flag. The FM10 EMPTY flag enables the PDP-10 PI logic and a program interrupt request (PI) signal is sent to the central processor.

The PDP-10 central processor performs a CONI instruction to fetch the status information via the I/O bus and detects that the FM10 EMPTY flag is set. If the PDP-10 central processor has additional data to be transferred, it places the next data word on the I/O bus and performs a DATAO instruction as explained above. These data transfers continue until the PDP-10 central processor has no additional data for the PDP-8 or PDP-9 central processor. At this time, the PDP-10 central processor may perform a CONO instruction to clear the status flags and remove the PI signal.

To perform a PDP-8 or PDP-9 data transfer to the PDP-10, the central processor performs a series of IOT instructions to load the TO10 buffer. Prior to a data transfer, an IOT instruction is performed to generate a clear buffer (CLR BUFF) pulse. The CLR BUFF pulse clears the 36 flip-flops in the TO10 buffer and clears the TO10 EMPTY flag. Then, the IOT instructions during which the data is transferred are performed.

During each data transfer, the PDP-8 or PDP-9 central processor places a data word on the I/O bus and sends the control signals to the DA10. In the data transfer logic, a LOAD pulse is generated and sent to the TO10 buffer. The LOAD pulses gate the data word into the 36-bit TO10 buffer. Three 12-bit data words are transferred to fill the TO10 buffer when a PDP-8 is connected to the DA10 and two 18-bit data words are transferred when the PDP-9 is connected.

The TO10 FULL flag is set by the last LOAD pulse and the TO10 FULL flag enables the PDP-10 PI logic sending a PI signal to the central processor. After receiving the PI signal, the PDP-10 central processor performs a CONI instruction to fetch the status information. From the status information, the PDP-10 central processor determines that the TO10 buffer is loaded and performs a DATAI instruction to gate the 36-bits of data out of the TO10 buffer and into the central processor via the I/O bus. During DATAI instruction the TO10 EMPTY flag is set and the TO10 FULL flag is cleared.

At this time, the PI signal is removed from the PDP-10 central processor and a PI RQ signal is sent to the PDP-8 or PDP-9 central processor. The PDP-8 or PDP-9 central processor enters a routine to sequentially check the status flags connected to the PI line by performing a series of IOT instructions. When the TO10 EMPTY flag is located in the set condition, program control is transferred to the appropriate service routine and the TO10 buffer is loaded. This action is repeated until the PDP-8 or PDP-9 has completed the necessary transfer of data.

## 4.2 DETAILED DESCRIPTION

The transfer of data and control information is discussed as data from the PDP-10 to a PDP-8 or PDP-9 and from a PDP-8 or PDP-9 to the PDP-10 processor.

#### 4.2.1 Data Transfer to a PDP-8 (Figure 4-2)

When data is transferred to a PDP-8, the PDP-10 central processor places up to 36-bits of data on data lines IOB 10, IOB 00 through IOB 10, IOB 35; places the DA10 device selection number  $(014_8)$  on the device selection lines IOS 3(0) through IOS 9(1) and performs a DATAO instruction. The central processor performs the DATAO instruction in two parts: the IOB 10 DATAO CLR pulse is sent to the DA10 and 1 µs later, the IOB 10 DATAO SET pulse is sent.

The device selection number is decoded in the PDP-10 device selection decoder and the resultant signal, 014 SEL, conditions the DATAO clear enable gate, DATAO set enable gate, and a number of other enable gates. When the IOB 10 DATAO CLR signal is sent to the DA10, the DATAO clear enable gate is enabled generating the DATAO CLR pulse. The DATAO CLR pulse conditions the FM10 buffer to receive the data transfer by clearing the 36 flip-flops in the buffer. If the STAT BUF B flip-flop is set causing a program interrupt request to the PDP-10, the DATAO CLR pulse also removes the program interrupt request by clearing the STAT BUF B flip-flop.

One microsecond later, the IOB 10 DATAO SET signal is sent to the DATAO set enable gate. Since the 014 SEL signal is still true, the DATAO set enable gate is conditioned and the DATAO SET pulse is generated. The DATAO SET pulse performs two major functions. It enables the input gates loading the data on the data lines into the FM10 buffer and sets the STAT BUF A flip-flop.

At this time, the 36 bits of data are loaded into the FM10 buffer and the data is ready to be transferred to the PDP-8 central processor. Since the PDP-8 has a word length of 12 bits, three 12-bit data transfers must be performed to unload the FM10 buffer.

The data transfers from the FM10 buffer to the PDP-8 central processor are performed in the following manner. When the STAT BUF A flip-flop is set, the set side of the flip-flop enables the PI gate sending a program interrupt request (PI RQ) signal to the PDP-8. After receiving the PI RQ signal, the PDP-8 central processor performs a series of IOT instructions to sequentially check the status flags of the various devices connected to its I/O bus.

One of these IOT instructions is IOT 721. When IOT 721 is performed, the signals on lines BMB 3(0) through BMB (1) are decoded, thus generating the 72 SEL signal. The IOP 1 signal, which is a part of IOT 721, is ANDed with the 72 SEL signal and the set side of STAT BUF A flip-flop to generate a skip request (SKIP RQ) signal that is sent to the PDP-8 central processor. After the PDP-8 central processor detects the SKIP RQ signal, program control is transferred to a service routine during which IOT 702, 712, and 722 are performed.

When IOT 702 is performed, the 70 SEL signal is generated in the selection logic and sent to the data transfer logic. In the data transfer logic, the 70 SEL and IOP 2 signals are ANDed and generate the READ A pulse. The READ A pulse enables the output gates for bits 00 through 11 and gates the data to the PDP-8 accumulator register via the PDP-8 I/O bus.

Figure 4–2 Data Transfer from PDP–10 to PDP–8, Simplified Block Diagram

Next, the PDP-8 central processor performs an IOT 712 instruction. The 71 SEL signal is generated in the selection logic and is ANDed with the IOP 2 signal in the data transfer logic generating the READ MID pulse. The READ MID pulse is applied to the pulse mixer, a jumper network, and the READ B and READ C pulses are generated. The READ B pulse enables the output gates for bits 12 through 17 and the READ C pulse enables the output gates for bits 18 through 23. With the output gates enabled, the data in bits 12 through 23 are gated to the PDP-8 accumulator register via the FM10 buffer output mixer and PDP-8 I/O bus.

To perform the last transfer, the PDP-8 central processor performs an IOT 722 instruction. The 72 SEL signal is generated and ANDed with the IOP 2 signal generating the READ D pulse. The READ D pulse enables the output gates for bits 24 through 35 gating the data to the PDP-8 accumulator register via the FM10 buffer output mixer and the PDP-8 I/O bus. At the same time, the READ D pulse clears the STAT BUF A flip-flop and sets the STAT BUF B flip-flop. The set side of the STAT BUF B flip-flop is applied to the PI request enable gate and the PDP-10 PI decoder is enabled. The PI channel assignment number that is stored in the PDP-10 PI register is decoded, and a PI request is sent to the PDP-10 central processor via the assigned line.

The PDP-10 services the PI request by performing a CONI instruction. The DA10 is selected and the 014 SEL signal that conditions the CONI enable gate is generated. When the IOB 10 CONI signal is applied to the CONI enable gate, the CONI signal is generated enabling the status gates. The status information is sent to the PDP-10 central processor via the assigned data lines of the I/O bus. In this case, the significant bit of status information is contained on IOB 10, IOB 28. With this bit a 1, the PDP-10 central processor is provided with an indication that the FM10 buffer is empty and ready to receive the next data transfer. Additional data transfers are performed in an identical manner as explained above.

#### 4.2.2 Data Transfer to a PDP-9

If the DA10 is connected to a PDP-9 instead of a PDP-8, the PDP-10 central processor loads the FM10 buffer in the same manner as it did when a PDP-8 was connected. There are differences in the data transfer from the FM10 buffer to the PDP-9 because the IOT instructions and the word length are different. In this section, the differences in data transfer are explained in detail, and the functions that are the same are only discussed. If additional detail is required to understand the PDP-10 operation, refer to Paragraph 4.2.1.

Reference to Figure 4-3 will help to clarify much of the following discussion. Figures 4-2 and 4-3, show that the PDP-10 interface connections to the DA10 are identical when either a PDP-8 or PDP-9 central processor is connected to the DA10. The PDP-10 central processor places the data and the device selection number on the I/O bus and performs a DATAO instruction to load the data

Figure 4–3 Data Transfer from PDP–10 to PDP–9, Simplified Block Diagram

into the FM10 buffer. The DATAO instruction also clears the STAT BUF B flip-flop and sets the STAT BUF A flip-flop. The set side of the STAT BUF A flip-flop is connected to the PI gate and a PI RQ signal is sent to the PDP-9 central processor.

The PDP-9 central processor services the PI request by performing a series of IOT instructions to sequentially check the status flags of the various devices connected to its I/O bus. Refer to Figure 4-4 for the PDP-9 IOT instruction format.

\*IOP4 is assigned to this bit because of its binary relationship to the other IOP bits. There is no IOP3.

Figure 4-4 PDP-9 IOT Instruction Format

When the PDP-9 central processor performs IOT 2241, the 22 SEL signal is generated by decoding the signals on the device selection lines IOB 9, IOB DS0 through IOB DS5. The 22 SEL signal enables the IOP select gate generating the 9 IOP 1 signal. The set side of the STAT BUF A flip-flop, the 9 IOP 1 signal and the IOB 1 SD0 signal (a 1 during this instruction) are ANDed in the skip request logic generating the SKIP RQ signal.

After the central processor detects the SKIP RQ signal, program control is transferred to a service routine during which the central processor performs IOT 2212 and IOT 2232.

When IOT 2212 is performed, the PDP-9 central processor clears its accumulator register and places the necessary control signals on the I/O bus. The 22 SEL signal is decoded and ANDed with the IOB 9 IOP 2 signal in the IOP select gate generating the 9 IOP 2 signal. The 9 IOP 2 signal performs two major functions: first, it is applied to the PDP-9 read request gate generating the read request (RD RQ) signal, a 1 µs pulse that is required to complete the data transfer; second, it is ANDed with IOB 1 SD1 (a 0 during this instruction) generating the READ A pulse. The READ A pulse is sent to the pulse mixer to generate the READ B pulse.

The READ A pulse enables the output gates for bits 00 through 11 and the READ B pulse enables the output gates for bits 12 through 17. The data in bits 00 through 11 are placed directly on the I/O bus, and the data in bits 12 through 17 are placed on the I/O bus via the FM10 buffer output mixer. A brief review of conditions up to this point show that the PDP-9 accumulator register has been cleared, the RD RQ signal has been sent to the PDP-9 central processor, and the data has been placed on the data line of the I/O bus. The PDP-9 central processor allows the data to settle and then strobes the data into the accumulator register to complete the transfer of the first 18-bits of data.

Then, the PDP-9 central processor performs the IOT 2232 instruction to fetch the second 18-bits of data stored in bits 18 through 35 of the FM10 buffer. During the IOT 2232 instruction, the PDP-9 central processor clears the accumulator register and places the necessary control signal on the I/O bus. Again, the 22 SEL signal is decoded and ANDed with the IOB 9 IOP 2 signal in the IOP select gate generating the 9 IOP 2 signal. The 9 IOP 2 signal causes the RD RQ signal to be generated and the READ D pulse to be generated after the 9 IOP 2 signal is ANDed with the IOB 1 SD 1 signal (a 1 during this instruction). The READ D pulse is sent to the pulse mixer to generate the READ C pulse. The READ C pulse then enables the output gates for bits 18 through 23 and the READ D pulse enables the output gates for bits 24 through 35. With the 18 output gates enabled, the second 18 bits of data are gated onto the PDP-9 I/O bus via the FM10 buffer output mixer. After the PDP-9 central processor has allowed time for the data on the I/O bus to settle, it strobes the data into the accumulator register to complete the transfer.

The READ D pulse also clears the STAT BUF A flip-flop to remove the PI RQ signal from the PDP-9; and it sets the STAT B flip-flop to send a PI request to the PDP-10. The PDP-10 services the PI request by performing a CONI instruction to fetch the status information via the data lines. As it was in the case of a PDP-8, IOB 10 IOB 28 is the significant bit of status information because it indicates that the FM10 buffer is empty. Additional data transfers are completed in an identical manner as controlled by the PDP-10 central processor until the required data has been transferred.

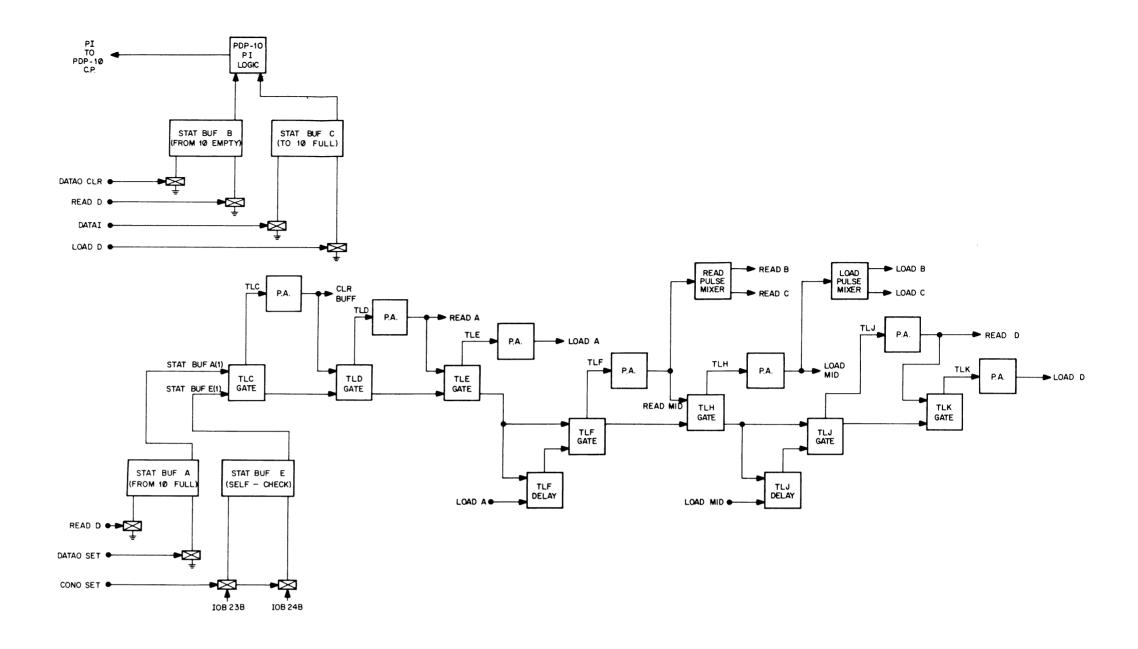

#### 4.2.3. Data Transfer From a PDP-8 to a PDP-10

The PDP-8 central processor performs a service routine consisting of a series of IOT instructions to transfer data to a PDP-10 central processor via the DA10. To transfer a full 36-bits of data, the PDP-8 central processor performs the following IOT instructions: IOT 701 to clear the TO10 buffer IOT 704 to load bits 00 through 11; IOT 714 to load bits 12 through 23; and IOT 724 to load bits 24 through 35 and set the STAT BUF C flip-flop. If only a partial transfer is to be performed, IOT 724 must be included to set the STAT BUF C flip-flop and send a PI request to the PDP-10 central processor. (Figure 4-5 should be referenced while reading the following functional description.)

Figure 4–5 Data Transfer from PDP-8 to PDP-10, Simplified Block Diagram

When IOT 701 is performed, the signals on the device selection lines BMB 3(0) through BMB 8(1) are decoded in the selection logic generating the 70 SEL signal. The 70 SEL and IOP 1 signals are ANDed in the TO10 buffer clear gate generating the CLR BUFF pulse. The CLR BUFF pulse performs two major functions. It clears the 36 flip-flops in the TO10 buffer, and it clears the STAT BUF D flip-flop (the STAT BUF D flip-flop will be set if the PDP-8 central processor has received a previous PI RQ signal).

The DA10 is now ready to accept data from the PDP-8. When an IOT 704 instruction is performed, the PDP-8 places 12 bits of data on data lines IOB 00 through IOB 11 and sends the necessary control signals to the DA10. The 70 SEL signal is generated and ANDed with the IOP 4 signal in the data transfer logic generating the LOAD A pulse. When the LOAD A pulse is generated, the input gates for bits 00 through 11 are enabled and the data is loaded into bits 00 through 11.

To load bits 12 through 23, the PDP-8 central processor performs an IOT 714 instruction. The PDP-8 central processor places 12 bits of data on the data lines and the data is routed to input gates 12 through 23 via the input buffering circuits and the TO10 buffer input mixer. When the control signals are sent out, the 71 SEL signal is decoded and ANDed with the IOP 4 signal generating the LOAD MID pulse. The LOAD MID pulse is sent to the pulse mixers to generate the LOAD B and LOAD C pulses.

The LOAD B pulse enables the input gates for bits 12 through 17 and the LOAD C pulse enables the input gates for bits 18 through 23. When the input gates are enabled, the data is loaded into bits 12 through 23.

To complete the loading of the TO10 buffer, the PDP-8 central processor performs an IOT 724 instruction. Again, the data is sent from the PDP-8 to the input gates via the input buffering circuits and the TO10 buffer input mixer. The 72 SEL signal is generated and ANDed with the IOP 4 signal generating the LOAD D pulse. The LOAD D pulse enables the input gates for bits 24 through 35 and loads the data into bits 24 through 35, and it sets the STAT BUF C flip-flop.

When the STAT BUF C flip-flop is set, the PI request enable gate is enabled and the PDP-10 PI decoder is enabled. The PI channel assignment number stored in the PDP-10 PI register is decoded sending a PI request to the PDP-10 central processor via the assigned PI line. The PDP-10 central processor performs a CONI instruction to fetch the DA10 status information. At this time, IOB 10 IOB 30 is a 1 indicating the presence of data in the TO10 buffer.