SMDs MAKE BIPOLAR QUICK AND QUIET

### FLAT PANEL FUTURE FADES

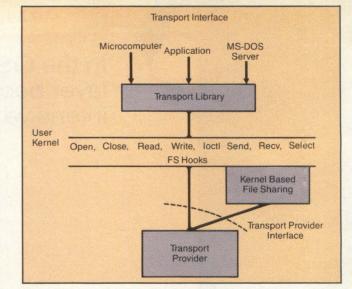

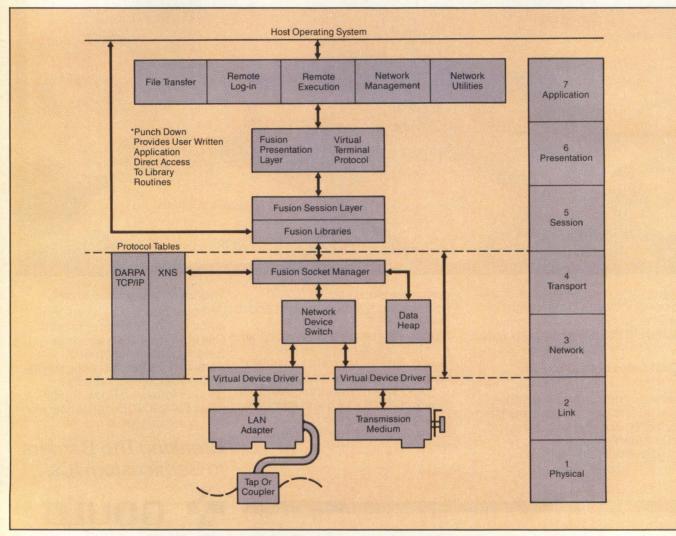

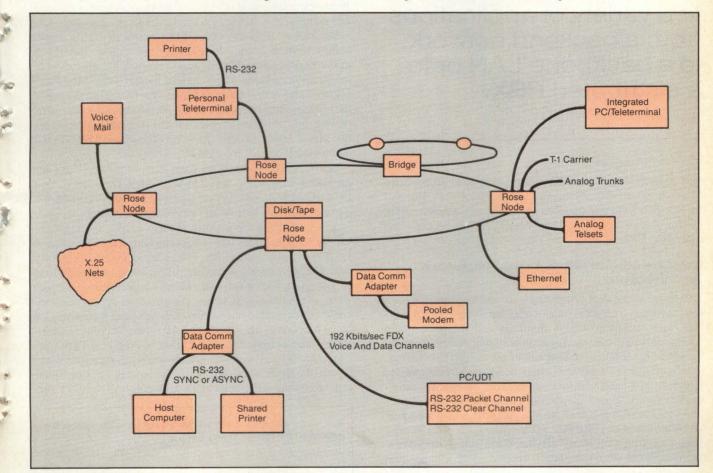

## COMMUNICATION NETWORKS AND PROTOCOLS

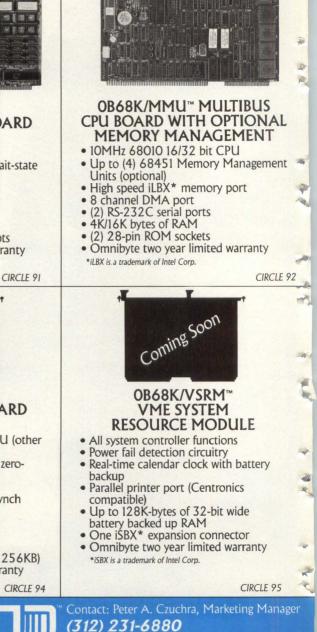

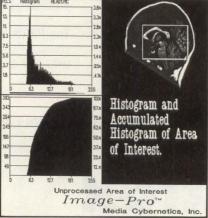

FPU BOOSTS 68020 PERFORMANCE Gould...Innovation and Quality in Image Processing.

Gould's FD5000 Image Processor Introduces a Whole New Idea:

#### Performance and Economy.

An image processor can be expensive.

Unless it's the FD5000. For \$11,500, you can purchase an 8 bit frame buffer with driver software. And the system doesn't stop there. As your needs expand, so will the FD5000 to a full

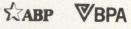

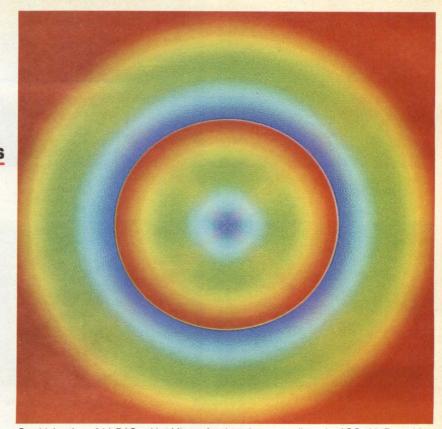

Bigern of 2 bit magnetic resonance medical images

32 bit image processing system for advanced applications.

Check these basic and optional features:

Flexible Architecture:

Two 12 bit deep images or three 8 bit images with 4 bits of color or monochrome overlay provide monochrome, pseudocolor, and true color.

60Hz Flicker-Free Display:

Bright, flicker-free image display at 60Hz; 30Hz for image processing and real time input.

#### Feedback Processor:

Five times faster than host-based operations for convolutions, digital filtering, interactive math, regions of interest, and recursive filtering.

#### 1024<sup>2</sup> × 32 Bit Memory Arrays:

Optional memory configuration provides user choice of image size and processing precision to display through 512<sup>2</sup> viewport.

#### MINI-LIPS Image Processing Software:

Interactive keyboard control; prompts for filters, real-time math, Look-Up Tables, histograms, geometric operations, utilities, and image storage; demo programs include source code.

#### The Closer Look:

The FD5000 will minimize the load on your host CPU and your processing staff. Peripheral or stand alone configurations are available.

#### Give Us A Call:

We'll be happy to discuss your application needs and the FD5000 at your convenience.

Gould Inc., Imaging and Graphics Division 46360 Fremont Boulevard, Fremont, CA 94538 USA Telephone (415) 498-3300 • TWX (910) 338-7656

#### European Headquarters

Tegernseer Landstrasse 161, D-8000 Munchen 90, West Germany Telephone (089) 6-92-79-06 Telex 5218078-GOUI D

FutureNet and DASH are trademarks of FutureNet Corporation. IBM is a registered trademark of International Business Machines Corporation.

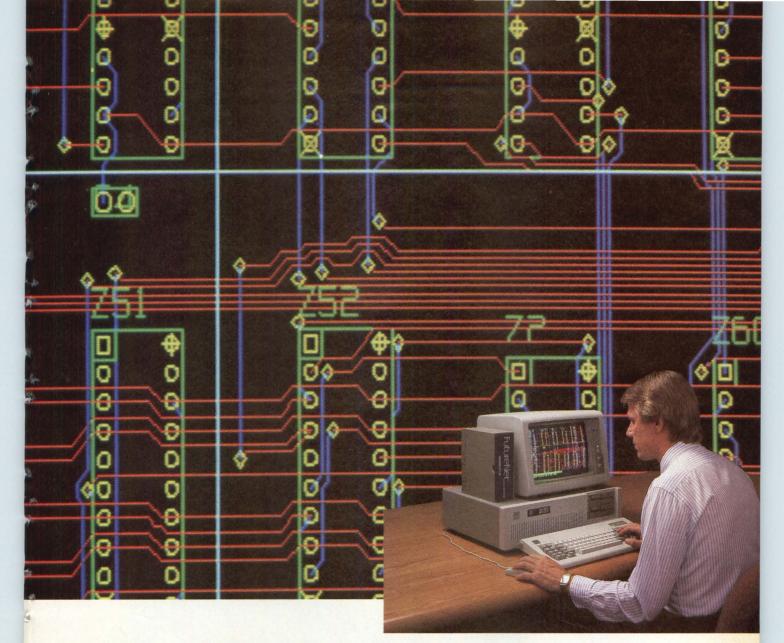

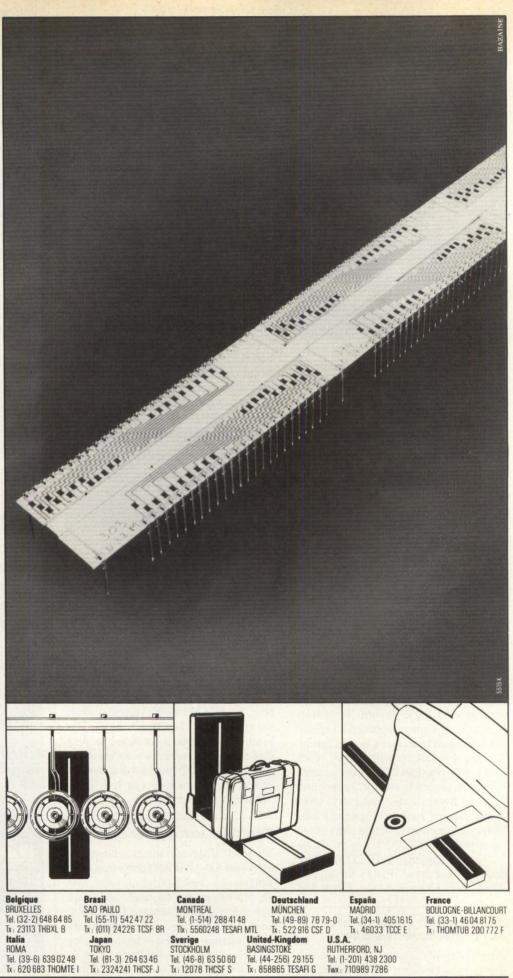

Rent or Lease from: • Electro Rent Corporation • United States Instrument Rentals, Inc. FutureNet's new DASH-PCB<sup>™</sup> is an innovative pc-based layout "expert." Now, features of a proven PCB layout system are yours to complement our famous DASH Schematic Designer. Exclusive features, previously available only on an expensive mainframe, are combined in a package that is costeffective, easy to learn, easy to use, and highly productive.

Here's an "Expert Multi-Strategy"™ router without equal. Your choice of routing strategies, plus trace

FutureNet

hugging, rubber-banding, fine line rules, 45 degree routing, large board capacity, 18 trace layers, and easy to use command menus. It's truly auto-routing with the mind of an expert.

#### FREE BROCHURE!

Call today for your copy of the complete description of FutureNet's exciting new DASH-PCB — the "expert" system that puts mainframe power on your IBM PC.

Authorized IBM<sup>®</sup> Value-Added Dealer

A DATA I/O Company

(818) 700-0691 Circle 7

FutureNet Corporation • 9310 Topanga Canyon Boulevard Chatsworth, California 91311-5728 USA • TWX: 910-494-2681

## WITH FORCE COMPUTERS

## **YOU'RE IN CONTROL\*!**

\*

con trol (kon-trohl) n. a standard of comparison for checking the results of an experiment or industrial process.

We understand setting the standard of comparison is your business. Our business is to provide you with a wide variety of high quality controllers for your experiments and industrial applications.

#### With FORCE, you easily control ...

- ... multi processing environments with our ASCU series of Advanced System Control Units, which offer IEEE 488 interface and 4-level bus arbitration.

- ... high resolution color displays (944 x 764 pixels) with our GDC intelligent graphics controller, which allows up to 2048 different colors.

- ... color or monochrome monitors with our CMC intelligent terminal controller, which features various interfaces and supports keyboard and lightpen.

- ... interfacing into high noise industrial environments using OPIO, the opto-isolated parallel I/O board with DMA.

- ... disk memories with our WFC multiple Winchester and Floppy controller with error correction.

- ... SASI interfaces with our intelligent SASI host adapter.

- ... local area networks with our intelligent LAN product, coming soon.

#### Do you want to be in control?

Call or write FORCE Computers today, the largest independent supplier of VMEbus products worldwide, to find out how you can be in control.

- Leading the way in VMEbus innovation

FORCE COMPUTERS INC. 727 University Ave. Los Gatos, CA 95030 Phone (408) 354-3410 Tix 172465 Telefax (408) 3957718

FORCE COMPUTERS GmbH Daimlerstraße 9 D-8012 Ottobrunn Telefon (0 89) 6 09 20 33 Telex 5 24 190 forc-d Telefax (089) 6 09 77 93

FORCE COMPUTERS FRANCE 11, Rue Casteja F-92100 Boulogne Tel. (1) 620 37 37 Telex 206 304 forc-f Telefax (1) 621 35 19

© Copyright

For US, Canada and Mexico Circle 1 on Reader Inquiry Card For International Countries Circle the Office Number Closest to You

## **DIGITAL DESIGN**

#### TECHNOLOGY TRENDS

21 **Design Tools / CAE/CAD Industry Accelerates Towards** Maturity 25 Imaging / Optics Finds A Niche In Imaging 27 Software / UNIX And MS-DOS Merge 29 ICs / Multiplier/Accumulator Manufacturers Multiply SIMD Architecture Takes Aim At Image Processing Users Tailor Standard Designs Through Silicon Compilation **Editor's Comment New Products** 15 83 Hotline **New Literature** 18 99 **Reader Service** Calendar 65 100 **New Product Focus** Advertiser Index 79 100

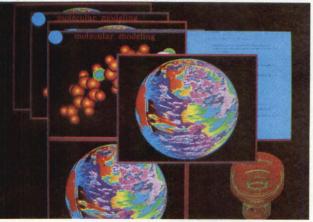

#### ON THE COVER

Vendor-independent networking software that interconnects a wide variety of normally incompatible processors, operating systems and network interfaces is the aim of second-generation LANs. Fusion network software from Network Research Corp. provides virtual terminal capabilities, remote command execution, internet routing, high-speed, high-performance file transfer and interprocess communication across processor, operating system and LAN hardware boundaries. Fusion also provides network management support with Ethernet monitoring, network statistics, network and node testing. It offers users a choice of the two widely used LAN protocols - Xerox XNS and/or DARPA TCP/IP. Photo courtesy Network Research Corp.

Published monthly thirteen times a year with two issues in March. Subscription rates for non-qualified subscribers (US and Canada) – \$40/yr; foreign – surface mail – \$50/yr; airmail – \$85/yr. Single copies – \$4. Copyright 1985 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, Berkshire Common, Pittsfield, MA 01201 ISSN 0147-9245.

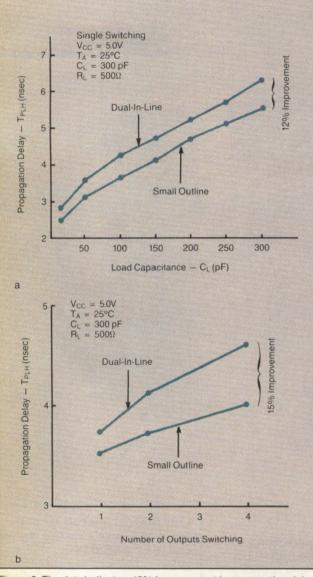

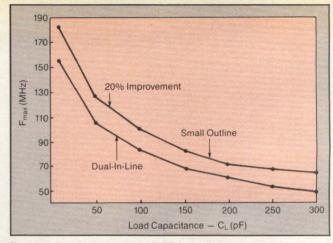

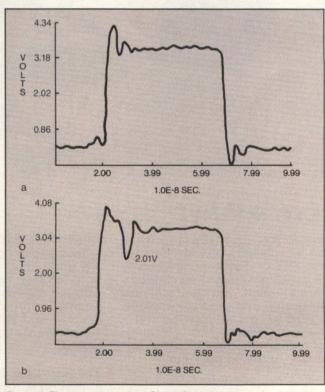

SMDs improve system performance

36 Network Protocols The move toward standardization will advance LAN development.

#### TABLE OF CONTENTS

#### FEATURES

#### SYSTEMS ARCHITECTURE

#### Protocols Set Course For Next-Generation Networks

#### by Joe Aseo

The driving force in local area network development remains the same as in the past several years. A network should be a common implementation available from multiple vendors.

#### X.25 Software: Transaction Scheduling Keys Efficiency

by David Grothe

As more data communications users turn to the X.25 standard for packet-switched networks, the need for X.25 software packages and implementation hardware is growing dramatically.

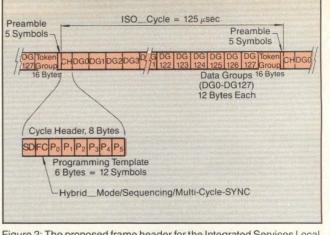

#### Hybrid Fiber Rings Implement Integrated Services Network

#### by Gary A. Nelson

The hybrid ring can adapt to a variety of applications from backend networks, to a backbone LAN or to a distributed PBX.

#### IMAGING AND GRAPHICS

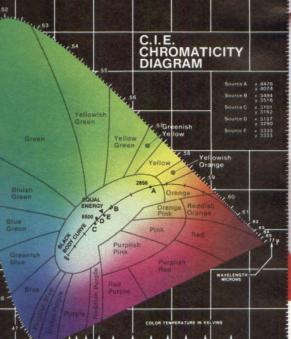

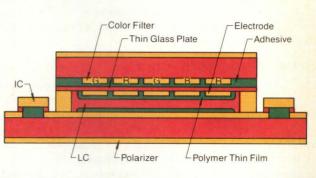

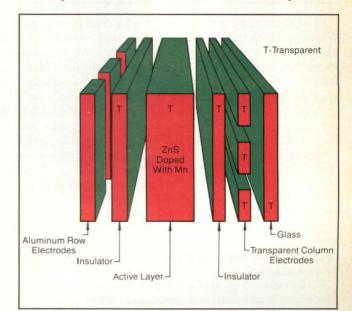

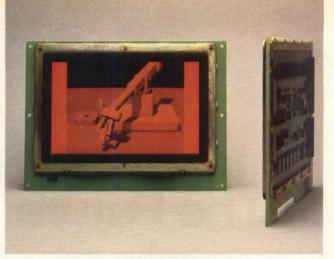

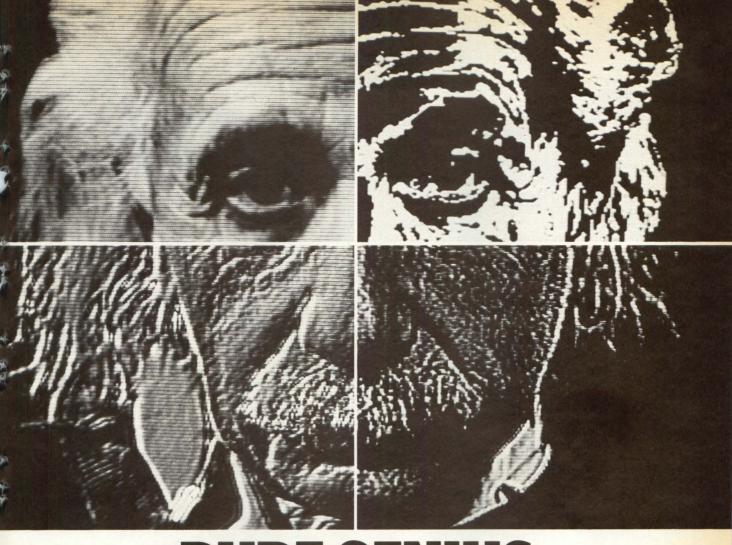

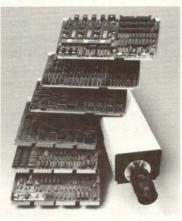

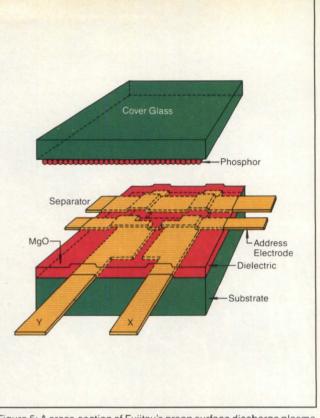

#### Flat-Panel Displays: Still In The Future

by Andrew Wilson

Flat-panel researchers continue to seek a CRT replacement and although the large scale application of high-resolution flat panels is distant, research points to ways these types of displays can be fabricated.

#### SEMICONDUCTOR TECHNOLOGY

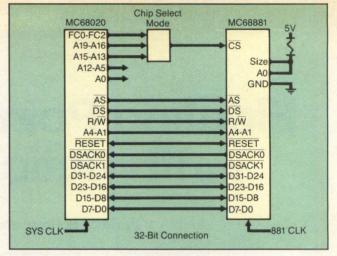

#### Floating Point Unit Extends Arithmetic Processing

by Bruce Hoffman and Donald Tietjen

Today, deciding which floating point coprocessor to use is difficult. But considering a few key points that distinguish coprocessor interface designs can ease coprocessor selection.

#### DESIGN TECHNOLOGY

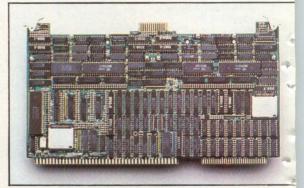

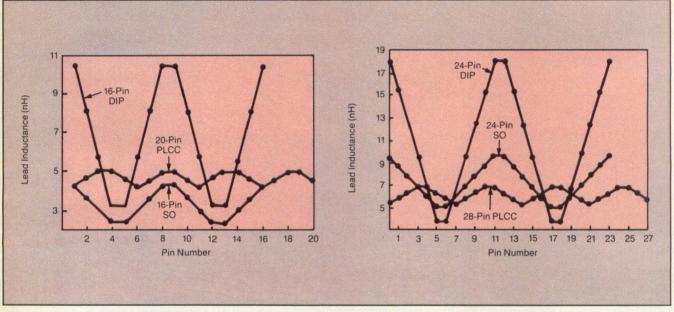

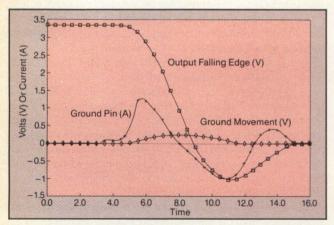

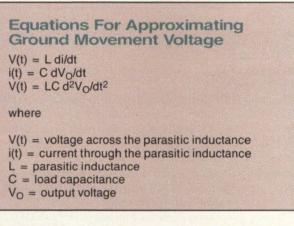

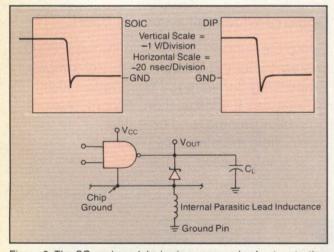

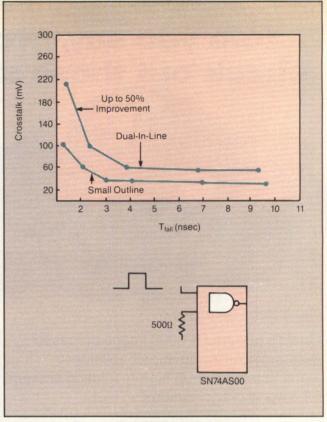

#### SMDs Make Bipolar Quick And Quiet

by Charles Hefner and Rick Moore

To get the highest system-level performance from advanced bipolar logic, designers should consider not only the device itself, but also the device's packaging.

## Datacube presents MaxVideo

The most powerful family of video image processors.

Choose modules that match your real-time image processing requirements.

MAXbus," the video interconnect standard, gives you flexibility to expand your MaxVideo system.

Write or call today.

ARRENT CONTRACTOR

ATTACK TRADITION

......

-----

....

······

-----

IL TITLE

## DATACUBE Datacube. Inc.

4 Dearborn Road, Peabody, MA 01960 (617) 535-6644

# The MaxVideo Family

VFIR

SNAP

MAX-SP

PROTOMAX

MAX-XFS

INTERPOLATOR

**ADDGEN-1**

FRAMESTORE

FEATUREMAX

MEbus

MAXbus

**DIGIMAX** is MaxVideo's A/D and D/A conversion module, featuring programmable analog input signal selection and conditioning, and 32 banks of Look-Up Tables.

**FRAMESTORE** is a digital video storage module, with three simultaneously accessible 8-bit framestores on a single board.

**VFIR** is the most powerful, single board, linear signal processing module available on the VMEbus. VFIR performs  $3 \times 3$  convolutions, or  $10 \times 1$  FIR filters on a full frame of video, in real time.

Real time, non-linear and morphological image processing is a **SNAP** with our Systolic Neighborhood Area Processor module.

**FEATUREMAX** is a programmable Histogram and Feature List Extraction module. It counts up to 1 million occurrences of 16K unique features and stores the result in high-speed memory.

**MAX-SP** is a general purpose processing module. It provides low cost image merging, FIR filtering, and minimum/ maximum operations in real time.

**PROTOMAX** is a blank wire-wrap module which includes VMEbus and MAXBUS interface connectors and circuitry. PROTOMAX puts your proprietary design into the MaxVideo family quickly and easily.

**MAX-XFS** is transposing framestore which contains two complete frames of video storage. Each frame can be read and/or written in row or column order to achieve real time 90 degree image rotations.

**INTERPOLATOR** is a module which performs sub-pixel, multirate sampling in real time. It can perform n-th order warps and discontinuous transformations. Its 8-point aperture and sinc interpolation algorithm yield an extremely precise 16-bit result.

**ADDGEN-1** is an address generator module which works in conjunction with the INTERPOLATOR module. It creates the addressing necessary to allow INTERPOLATOR to perform first order transformations to 32-bits of spatial resolution.

## DATACUBE

Datacube, Inc. 4 Dearborn Road, Peabody, MA 01960 (617) 535-6644

Circle 10

## EZ-PRO 2.1 + IBM PC = WINNER

**Complete Development Station.** EZ-PRO 2.1 connects to your personal computer via RS232 and supports the widest selection of in-circuit emulators. Check the tabulation for the microprocessors you're planning to use. Each emulator is supplied with macro cross-assembler, linker, and symbolic debugger. C Language cross compilers now available for selected microprocessors. **Deep Trace.** 4,096 real-time events, 256 break-points with zoning, complex triggering, scatter/gather trace management.

| Intel: 8031                                           | Motorola:                                                    | Hitachi:                                  | Rockwell:                                            |

|-------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------|------------------------------------------------------|

| 8032<br>8035<br>8039<br>8044                          | 6800<br>6801<br>68B00<br>68D2                                | 6301<br>6303<br>64180                     | 6502<br>6503<br>6504<br>6505                         |

| 8048<br>8748<br>8049<br>8050<br>8051<br>8052<br>8085A | 68B02<br>14680552<br>6803<br>6808<br>68B08<br>68B08<br>68809 | RCA:<br>1802<br>1805<br>1806<br>CDP6805E3 | 6506<br>6507<br>6512<br>6513<br>6513<br>6514<br>6515 |

| 8085A-2<br>8086<br>8088<br>8088<br>80186<br>80188     | 6809E<br>68B09<br>68B09E<br>68000<br>68008<br>68008<br>68010 | Zilog:<br>Z80A<br>Z80B<br>Z80H<br>Z8001   | Signetics:<br>8X300<br>8X305                         |

| Harris: 80C86<br>80C88                                |                                                              | Z8002                                     | National:<br>NSC800                                  |

... AND MORE.

#### american automation

14731 Franklin Avenue, Tustin, California 92680 (714) 731-1661 Telex II: 910-595-2670 AMAUTO TSTN

Circle 16

## REPRINTS

**DIGITAL DESIGN** will reprint any article from past or present issues. Reprints are custom printed. Minimum order: 1,000 copies. Purchase order or letter of authorization required.

Allow one month from receipt of order for delivery, unless previously arranged and confirmed.

Advertisements alone can also be reprinted. Call (617) 232-5470, and ask for reprints.

#### **DIGITAL DESIGN**

| Editor in Chief                                          | John Bond                                                          |

|----------------------------------------------------------|--------------------------------------------------------------------|

| Managing Editor                                          | Debra Lambert Steinfeld                                            |

| Features:                                                |                                                                    |

| Semiconductor Technole                                   | ogy Dave Wilson,<br>Executive Editor                               |

| Imaging and Graphics                                     | Andrew Wilson,<br>Senior Technical Editor                          |

| Design Technology                                        | Ronald E. Collett,<br>Senior Technical Editor                      |

| Systems Architecture                                     | Brita Meng,<br>Technical Editor                                    |

| Technology Trends                                        | Jack Vaughan<br>News Editor                                        |

| West Coast Technical Edite<br>(408) 356-0405             | or Joe Aseo                                                        |

| Editorial Assistant                                      | Tia Partin                                                         |

| Contributing Editor:<br>Peripherals                      | Bob Hirshon                                                        |

| Senior Art Director                                      | Tilly Berenson                                                     |

| Advertising Production Ma                                | anager Martha Watjen                                               |

| Production Director                                      | Paul Dadarria                                                      |

| Graphics: Supervisor<br>Sr. Technician<br>Jr. Technician | William Manning Jr.<br>Don Schaat<br>Jan B. Seymour                |

| Marketing Director                                       | Charlotte King                                                     |

| Promotion Manager                                        | Elaine Bull                                                        |

| Research                                                 | Peter Micheli                                                      |

| Circulation Director                                     | Hugh J. Dowling                                                    |

| Circulation Supervisor                                   | Nancy McPherson                                                    |

| Circulation Staff Mir                                    | iam Hlister, Kelly Kudlate                                         |

| Reader Service (413) 499-                                | 2550 Gertrude Bauer                                                |

| Marketing/Sales Specialist                               | t Dorothy Berlinguet                                               |

| Executive Administrator                                  | Suzanne Levecque                                                   |

| Corp. Services Administra                                | tor Janet R. Pitt                                                  |

|                                                          | Beth Giles,<br>ne Simpson, Mal Rankin,<br>pra James, Sharon Silver |

| Presid<br>Bonald V                                       |                                                                    |

|                                                          | <b>dent,</b><br>V. Evans                                           |

Publisher, James R. DiFilippo

Associate Publisher Terry L. Willins

#### **Advertising Sales**

Northeast: Terry L. Willins (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

IBM is a trademark of tional Business Machines. Inc

Middle Atlantic/Southeast: Richard V. Busch (609) 921-7763, 40 Stony Brook Lane, Princeton, NJ 08540

Central: Mike Prewitt (303) 696-6276, 11628 East Cornell Circle, Aurora, CO 80014

Northwest: Carole Sacino, Diane Ross (408) 356-0405, 15951 Los Gatos Blvd., Suite 7, Los Gatos, CA 95030

Southwest: Thomas A. Stillman (714) 851-8550, 2041 Business Center Dr., Suite 206, Irvine, CA 92715

National Recruitment Sales: Brenda Stillman (714) 851-8550, 2041 Business Center Dr., Suite 206, Irvine, CA 92715

National Postcard Sales: Krickett Cunningham (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

National List Rental Sales: Deb Goldstein (In MA) (617) 232-5470, (Outside MA) (800) 223-7126, 1050 Commonwealth Avenue, Boston, MA 02215

DECEMBER 1985 I DIGITAL DESIGN

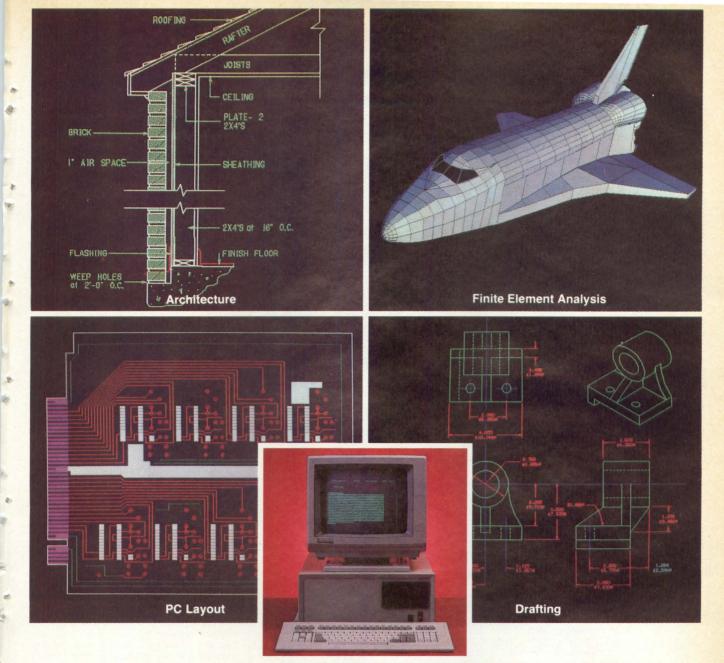

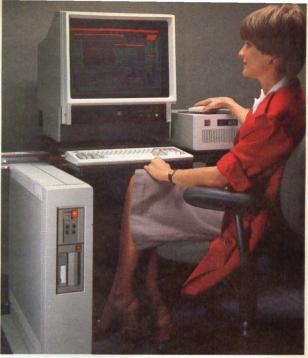

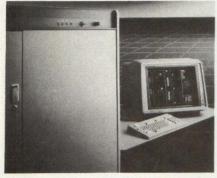

#### System Quality Graphics at a PC-Based Price. Introducing the Lundy 2000 Workstation.

Lundy 2000 is a powerful turnkey workstation that gives you sharp, high speed, high quality graphics for about what you'd pay for a fully configured pc-based system.

#### **Turnkey Simplicity**

Because it is a stand-alone workstation, you're spared from dealing with several manufacturers for different system components, as is common with most "put-together" systems. With the Lundy 2000, you're backed by a Company with a proven, solid reputation for providing fine quality graphics systems complete with service and support. The Lundy 2000 is as dependable and easy to operate as it is effective. All of this power is packaged as a highly compact turnkey system.

#### **Application Flexibility**

The Lundy 2000 workstation gives you fast, high quality design for finite element analysis, solids modeling, PC layout, mechanical design, and architectural applications, as well as business graphics and word processing. It displays up to 256 colors from a palette of 16.7 million and provides a 1536  $\times$  1024 addressable map with 768  $\times$  512 displayable resolution. Dual processor architecture and a high speed vector generator combine to provide full pan, zoom, and preview capabilities. This gives you operational flexibility to handle special graphics processing needs not met by standard host-dependent terminals.

For more information, contact: Graphics Marketing, Lundy Electronics & Systems, Inc., One Robert Lane, Glen Head, N.Y. 11545. (516) 671-9000.

#### Color Graphics Display Controllers

- High Resolution

1024 x 1024, 512 x 512 pixels

Non-interlaced and

interlaced formats available

- 16 Simultaneous colors

- Blink at 1 Hz

- High Performance

Graphics generated at up to 1,200,000 pixels-per-second Fill operations at up to

19,200,000 pixels-per-second All planes drawn simultaneously Line by line vertical scroll Multiple cursors

- GPS Subroutine Package Available for popular operating systems

- Other bus architectures available

High Resolution Color Monitors Standard or long-persistence phosphors

Available in 13 inch or 19 inch Analog or TTL inputs

0.31 mm pitch

Sunnyvale, CA 94086 (408) 745-6500 Telex: 856 587

Circle 19

TELL US YOUR THOUGHTS

design community. So let us know how we're doing and how we can serve you better in the future. We want to know what you like or dislike about *Digital Design*, the subjects you'd like to see us address, how you feel about the problems you face every day as design professionals.

If you have thoughts your peers should know about, put them in a letter in *Digital Design*. Have your say in *your* magazine! Send letters and comments to: Editor, *Digital Design*, 1050 Commonwealth Ave., Boston, MA 02215.

DIGITAL DESIGN

#### EDITORIAL AND SALES OFFICES

DIGITAL DESIGN, 1050 Commonwealth Avenue, Boston, MA 02215, Telephone: (617) 232-5470

#### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215, (617) 232-5470. Brian Rowbotham, Chairman; Ronald W. Evans, President; Charles Benz, Vice President.

#### **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 1050 Commonwealth Avenue, Boston, MA 02215 (617) 232-EXPO. The following is a list of conferences produced by the Expositions Group:

| ATE West                 | E'ssembly         |

|--------------------------|-------------------|

| Midwest Electronics Expo | ATE Central       |

| ATE Silicon Valley       | ATE East          |

| Arizona Electronics Expo | Electronic Imagin |

In addition to DIGITAL DESIGN, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronics Test

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronics Times • What's New in Electronics • What's New in Computing • Business Computing and Communications • Communications Systems Worldwide.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral manufacturers, integrating OEM's and commercial end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

#### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

Circulation Department, **DIGITAL DESIGN**, Berkshire Common, Pittsfield, MA 01201

Subscription rates: non-qualified subscribers (US and Canada) – \$40/yr; foreign – surface mail – \$50; air mail – \$85. Single copies – \$4.

Authorization to photocopy items for internal or personal use, or the internal or personal use of specific clients, is granted by Morgan-Grampian Publishing Co. for libraries and other users registered with the Copyright Clearance Center (CCC) Transactional Reporting Service, provided that the base fee of \$2.00 per copy, plus \$.25 per page is paid directly to CCC, 21 Congress St., Salem, MA 01970. 0147-9245/84 \$2.00 + \$.25.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

## At Last! Communications Processors For DEC Computers That You Can Program

The Simpact ICP1600 Family of Intelligent Communications Processors can offload your host system because they're versatile enough to handle the toughest communication tasks and are compatible with VAX and PDP-11s Use your host system utilities and our software tool kit to create your custom protocols, or let our communications specialists help you develop them. X.25 software is available from Simpact now, and more standard packages are on the way.

256 Kbytes on-board memory to store downloaded programs and buffer data

High-speed DMA transfers with host processor

Eight programmable, serial communications ports (expandable to 20) support multiple asynchronous and synchronous protocols at speeds up to 612 Kbaud

15 Kbytes PROM contains Boot Loader, Self-Test routines and Debugging firmware

DEC MICRO/T-11 processor engine executes the PDP-11 instruction set

Single hex-size card plugs into any UNIBUS slot

> Discuss your requirements with us. Call today: (619)565-1865, ext. 246

or write to:

9210 Skypark Court San Diego, California 92123

\* Four-port Q.Bus module available now

DEC, PDP, MICRO/T-11, UNIBUS and VAX are trademarks of Digital Equipment Corporation

# SIMPLE IN FORM. M

The best ideas are simple. And it simply makes good sense to build one good idea on top of another.

Take, for example, the MPA-2000. We started with this basic idea: Design the best Multibus CPU/Intelligent I/O processor possible. One with an 8 MHz iAPX-186 microprocessor...512 Kbytes of zero wait state dynamic RAM...256 Kbytes EPROM... 8 DMA channels to support I/O...and an optional 8 MHz 8087 numeric coprocessor...plus many other high performance features.

But our good idea didn't end there. We also provided two plug-in module sites on the MPA-2000 to support a family of I/O adapter modules specially designed to take full advantage of the board's superior capabilities. The MPX modules provide a

wide range of data communications, local area networking and disk I/O interfaces. Quite simply, you can choose a solution tailored to your exact requirements — no more tradeoffs associated with singlefunction boards with restricted capabilities.

The MPA-2000 concept gives you maximum processing power. And it gives

## DULAR BY DESIGN.

you significant flexibility in I/O enhancements when you select one or two MPX plug-in modules. Choose for instance...

...16 channels of full-duplex DMA serial I/O. With the MPX-2000-160, eight 8530 devices provide ASYNC, BISYNC and BITSYNC protocols.

Or **two high speed HDLC (LAPB) links** provided by two Western Digital 2511 devices on the MPX-2000-140 module.

There's the MPX-2000-510 **Ethernet I/O adapter module** with the 82586 coprocessor. Put it aboard the MPA-2000 to support LAN communications including the IEEE 802.3 Ethernet standard.

Or select the MPX-2000-310 or -320 for **SCSI interfaces** to connect floppy disk, Winchester hard disk and tape drive devices in one system.

The superior capabilities of the MPA-2000. The flexibility of its MPX family of plug-in modules. It all adds up to a simple solution. Modular by design.

Call or write METACOMP, Inc. today for complete details on the MPA-2000 and its full line of MPX modular solutions.

METACOMP, INC. 9466 Black Mountain Road San Diego, CA 92126 (619) 578-9840 TWX 910-335-1736 METACOMP SDG

> MPA-2000 and MPX are trademarks of METACOMP, Inc. Multibus is a registered trademark of Intel Corporation. Ethernet is a registered trademark of XEROX.

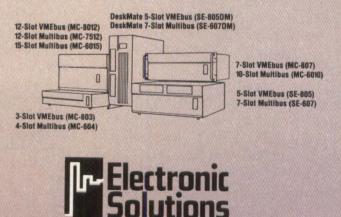

## VME and Multibus: Packaging That Makes The Difference

Now there's a complete, integrated line of Multibus \* and VMEbus system enclosures that lets you match your system needs today — with the flexibility to expand or reduce your requirements in the future.

For Multibus, choose from visually-compatible 4, 7, 10, 12, and 15-slot enclosures with Multi-Cage<sup>®</sup> card cages and backplanes, all designed to meet FCC class A EMI/RFI requirements with typical systems installed. The 7-slot upright DeskMate<sup>™</sup> and the 7-slot tabletop models have room for two half-height 5¼" peripherals, plus an additional 5¼" full height Winchester drive. All but the DeskMate are available for rack mounting.

For VMEbus, there are 3, 5, 7 and 12-slot models, with peripherals available on the DeskMate, rack mount and tabletop 5-slot versions. All use Electronic Solutions' VMEasy™ card cage and backplane design for rugged, reliable card mounting and easy servicing. If you're into Multibus now, you can even convert your enclosures later for VME.

Talk to us about your unique requirements. Build upon the industry's most comprehensive system of Multibus and VMEbus enclosures, and reduce your lead time to market. We'll provide front or rear card loading, or special slot spacing, special power supplies, or I/O connections. See how our custom design gives you an entire enclosure line instead of a single box.

Electronic Solutions' entire line is backed by our three year limited warranty—your assurance of built-in reliability.

Call us today, and find out how Electronic Solutions can make the difference in *your* system packaging.

**3 Year Limited Warranty**

9255 Chesapeake Drive, San Diego, CA 92123 • (619) 292-0242 Telex II (TWX): 910-335-1169 Call Toll Free: (800) 854-7086 In Calif: (800) 772-7086

Circle 20

#### EDITOR'S COMMENT

#### Exclusive!

**M** agazines devoted to the technical enlightenment of design engineers often run so-called exclusive feature articles. These exclusive articles are placed with the agreement that no other information on the subject will appear in print before the article is published. Trade magazine editors run exclusives because they make their magazines appear timely, even though the articles are prepared months in advance by the contributing companies. Editors enjoy this practice as do the firms who get to expound on the wonders of their technology. The audience may even find the article of some use although most could care less where they read it. Was it *ED*, *EDN*, *CD*, *DD* or somewhere else? It only becomes important if you want to go back and clip the article or look up something. So competition for exclusives is in most cases a harmless conceit of trade magazine editors – a bit silly perhaps, but harmless.

Consequently, most magazines have a more or less balanced attitude toward exclusives. We like them but wouldn't kill for them. There is an exception, however. One of the major design magazines (let's call it *Crazy-For-Exclusives Design* or *CFED*) has a policy to continually demand exclusives. *CFED* uses a not-so-subtle threat to restrict coverage of the topic or at least to downgrade its importance if it is not given to them on an exclusive basis.

Such bullying of PR agencies and companies by *CFED* does not serve the needs of either design engineers or industry. It is time that the industry realized that such practices have nothing to do with responsible journalism and refuse to make exclusive deals with any magazine that uses such tactics. Companies such as IBM and DEC learned this lesson years ago and try to keep the wraps on a new product until they are ready to announce it to the whole world.

Some of this tight-lipped approach is generated by fear of violating SEC insider rules if the announcement is expected to materially affect stock prices. More commonly, it is prompted by the desire not to impact the sales of present product lines before the new product is available in volume. In addition, early release of information may expose the company, especially if it is a large and major player, to restraint of trade charges.

Nonetheless, there are often compelling reasons to write an article exclusively for one magazine. For example, if the product is one that is not expected to generate a great deal of excitement in the press, then an exclusive may be the best deal a company can get. From the reader's viewpoint, that may be the worst type of article. The magazine may accept it only because it is exclusive and not because of technical merit.

On the other hand, an exclusive, in-depth article published after a general press announcement may be best for both the reader and the company. The reader gets to read about the product in broad outline in the weekly industry newspapers and gets the technical details in the article.

In addition to contributed, exclusive feature length articles, there are also news exclusives, written by the magazine staff. These should result from superior reporting – because an editor discovered something before other publications become aware of it. Sometimes this may lead to an exclusive article because the company wants the chance to explain their technology at a time of their own choosing. Unfortunately, exclusive news is often the result of the magazine's editors demanding that the information not be given to any other publication. That's not journalism – it's news manipulation and our old friend *CFED* is at the forefront of such questionable practice.

The company or PR agency that tries to manage their press relations through the use of exclusive announcements certainly has that right. Publications that demand exclusives have no such right and the industry should stand up to them.

- John Bond, Editor in Chief

# **TOSHBA. THE LARGEST SUPPLIER**

ALABAM, Milgray Electronics, Inc., (404) 393-9666, Time Electronics, (404) 449-4448; **ARKANSAS**, Diplomat Electronics, (214) 980-1888, Milgray Electronics, Inc., (214) 248-1603, Time Electronics, (214) 241-7441; **ARIZONA**, Time Electronics, (602) 967-2000, Western Microtechnology, (602) 948-4240; **CALIFORNIA**, Image Electronics, (714) 730-0303, (818) 707-0911, Integrated Electronics, (214) 980-1888, Milgray Electronics, (140) 248-1603, Time Electronics, (214) 241-7441; **ARIZONA**, Time Electronics, (619) 945-2400, (714) 837-9980, (408) 725-1600, COLRADAD, Diplomat Electronics, (303) 422-922, Integrated Electronics, (303) 429-4292, Integrated Electronics, (303) 799-8851, **COMPARTEDID**, Control Electronics, (203) 242-931, Time Electronics, (203) 242-932, Integrated Electronics, (203) 257-711, Time Electronics, (303) 942-920, Integrated Electronics, (203) 257-7311, Time Electronics, (303) 799-851, **COMPARETIDID**, Toring Tipe Orange, **1**(303), 799-8851, **COMPARETIDID**, Toring Tipe Orange, **1**(303), 799-8851, **COMPARETIDID**, Toring, Time Tipe Orange, **1**(303), 799-8851, **COMPARETIDID**, Toring, **1**(31), 799-8851, **COMPARETIDID**, Toring, **1**(31), 799-8851, **COMPARETIDID**, **1**(31), 797-700, **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700, **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700), **1**(31), 797-700),

# WORLD'S SECOND OF CMOS LOGIC.

#### But if you don't have our data book, how could you know we're that strong?

Toshiba is a CMOS logic pioneer, and in the 15 years since we first developed our CMOS logic line, we've become one of the world's largest suppliers.

Toshiba offers the most comprehensive CMOS logic line available. From the standard 4000/4500 series up to our new highest speed 74 HC series — tomorrow's standard logic family. With its high noise margin, high speed and low power consumption, the 74 HC series creates efficient device opportunities for designers of high speed portable instruments, telecommunications equipment, or any digital system.

#### **WE WROTE THE BOOK**

It's all in our book. Detailed specifications on our complete line. Our book is the definitive source for the newest and best in CMOS logic. If you don't have a current copy, get one today.

And remember, you can order Toshiba logic with confidence. Confidence that Toshiba can ship higher volumes of CMOS logic than anyone else. And ship it on time at competitive prices. Confidence, too, that Toshiba ships only quality assured products.

So when you select logic, talk to the people with the power. Talk with Toshiba.

| Characteristics/<br>Logic Families                 | New<br>HS-C <sup>2</sup> MOS<br>(74HC Series) | LSTTL      | *HS-C <sup>2</sup> MOS<br>(40H Series) | *Std. C2MOS<br>(4000/4500<br>Series) |  |

|----------------------------------------------------|-----------------------------------------------|------------|----------------------------------------|--------------------------------------|--|

| Prop. Delay Time<br>(typ) GATE ( $C_L = 15pF$ )    | 8ns                                           | 9ns        | 15ns                                   | 125ns                                |  |

| Max. Clock Freq.<br>(typ) J/K F•F ( $C_L = 15pF$ ) | 60MHz                                         | 45MHz      | 20MHz                                  | 2MHz                                 |  |

| Quiescent Power Diss.<br>(typ) (GATE)              | 0.01 μW                                       | 8mW        | 0.01 µ W                               | 0.01 μ W                             |  |

| Noise Margin<br>VIH(min)/VIL(max)                  | 3.5V/1.5V                                     | 2.0V/0.8V  | 4.0V/1.0V                              | 3.5V/1.5V                            |  |

| Output Current<br>IIOHI (min)/IOL<br>(min)         | 4mA/4mA                                       | 0.4mA/4mA  | 0.36mA/<br>0.8mA                       | 0.12mA/<br>0.36mA                    |  |

| Op. Volt. Range                                    | 2-6V                                          | 4.75-5.25V | 2-8V                                   | 3-18V                                |  |

| Op. Temp. Range                                    | -40-85°C                                      | 0-70°C     | -40-85°C                               | -40-85°C                             |  |

\*Data believed to be accurate and representative of each logic family.

#### TOSHIBA. THE POWER IN LOGIC.

| Logic Marketing Ma<br>2692 Dow Avenue<br>Tustin, CA 92680 | anager                   | RICA, INC.                |   |

|-----------------------------------------------------------|--------------------------|---------------------------|---|

| Send me your data                                         | book detailing the newes | t and best in CMOS Logic. |   |

| Name                                                      |                          | Senter State State        |   |

| Title                                                     |                          |                           | 1 |

| Company                                                   | Caller                   |                           | 1 |

|                                                           | ALC: THE ALC: NO         |                           | i |

|                                                           |                          | ZipDD12                   | 1 |

Milgray Electronics, Inc., (913) 236-8800, Time Electronics Midwest, (314) 391-6444; NEWBA, Integrated Electronics, (916) 424-5297, Time Electronics-Nor/Cal, (408) 734-9888, Westem Microtechnology, (408) 725-1660; NEW HAMPSNIRE, Cronin Electronics, Inc., (617) 449-5000, Milgray/New England, Inc., (617) 272-6800, Time Electronics-New England, (617) 532-6200; NEW JENEEY, General Components, Inc., (609) 768-6767, Milgray/Electronics, Inc., (516) 420-9800, (609) 983-5010, (800) 257-7808, (800) 257-7111, Time Electronics, (616) 275-0100; NEW MEXIGD, Time Electronics, (602) 967-2000, Westem Microtechnology, (402) 448-448, Vel VTMK, Milgray Electronics, Inc., (516) 420-9800, (716) 385-9300, Rome Electronics, (616) 257-7008, (800) 257-7808, (800) 257-7111, Time Electronics, (616) 246-7467, Wildow (404) 484-448, NURT/N3UTM AGNRID, Diplomat Electronics, (215) 532-500, Time Electronics, (161) 944-9520, Milgray/Electronics, Inc., (216) 447-1520, (800) 321-0006, Reptron, (614) 436-6675, Time Electronics, (161) 917-1000, ILALMOMA, Diplomat Electronics, (214) 487-1520, (303) 321-0006, Reptron, (614) 436-6675, Time Electronics, (161) 910-1000, ILALMOMA, Diplomat Electronics, (214) 940-188, Milgray/Electronics, Inc., (216) 447-1520, (300) 321-0006, Milgray/Neavare Valley, Inc., (609) 983-5010, (600) 227-7011, Time Electronics, (214) 247-1621, (303) 303-9000, (1617) 151-1100, ILALMOMA, Diplomat Electronics, (214) 940-188, Milgray/Delaware Valley, Inc., (609) 983-5010, (600) 327-7011, Time Electronics, (216) 337-900, (1617) 1611-1100, ILALMOMA, Diplomat Electronics, (217) 490-188, Reso Railejn, (104) 434-464, 404, 444-444; HEXAB, Diplomat Electronics, Inc., (617) 449-5000, Milgray/New England, Inc., (617) 248-1030, Time Electronics, (103) 337-900, (1617) 151-100, ILALMOMA, Diplomat Electronics, (161) 947-920, ILALMOMA, Diplomat Electronics, (161) 947-910, ILANDO, ILALMOMA, Diplomat Electronics, (161) 947-910, ILANDO, IL

#### HOTLINE

<u>CMOS GRAPHICS SYSTEM PROCESSOR</u>—By mid-1986, expect TI (Dallas, TX) to sample a 32-bit, 6-MIPS graphics processor with instruction cache, CRT controller, DRAM, VRAM and host interface. The  $1.5-\mu m$  CMOS part will hold about 200,000 transistors.

IMAGE PROCESSORS GO ON-CHIP—ISSCC in February will showcase several image processing ICs. Matsushita will unveil a microprogrammable real-time image processor done in bipolar technology, while Siemens will describe a 2D digital video filter. Mitsubishi will announce a processor for decoding composite TV into two DSP ICs—with the DSP chips allowing conversion of composite video into luminance and chrominance (and vice versa). And, Toshiba will show a 2O-MHz, 32-bit pipelined CMOS image processor capable of performing a 1024-point complex FFT in 1 msec.

<u>ISSCC TO FOCUS ON DSP</u>—National Semiconductor, Signetics/Philips and NEC will preview single-chip DSPs at ISSCC. The Signetics part contains two 16-bit data buses, executes a 40-bit instruction set and supports up to six concurrent arithmetic and datamove operations in each instruction. The NEC part has a 32-bit floating point multiplier and 55-bit floating point ALU. The 25,000-transistor National part, targeted at motor control, will boast 0.5- to 1.5-µsec instruction cycle time.

TOUCH SCREEN USES SOUND—Surface acoustic wave technology is at the heart of a touch screen system from Zenith (Glenview, IL). Exhibited at WESCON, it offers crosspoints in three dimensions. Fewer parts should mean lower cost versus competing technologies.

<u>BIT-SLICE GaAs</u>—A technology exchange agreement between AMD (Santa Clara, CA) and Vitesse Electronics (Camarillo, CA) will produce GaAs equivalents of the 2900 bitslice family. First members, which include a 4-bit-slice processor and a look-ahead carry generator—are scheduled for sampling in mid-1986.

PARALLEL PACTS—Vendors of little mainframes, or "Crayettes", are forming alliances with CAE vendors. Alliant Computer Systems (Acton, MA) and Apollo (Chelmsford, MA) inked a pact that will see Alliant's FX/l and FX/8 perform as servers on the Apollo DOMAIN. Meanwhile, Culler Scientific Systems (Santa Barbara, CA) and Sun Microsystems (Mountain View, CA) have announced a cooperative marketing effort.

PARITY BEGINS AT HOME—Zilog Systems Div. (Cupertino, CA) has by passed the Z80000 32-bit microprocessor for its upcoming System 8000/32 UNIX-based computers. Citing time-to-market demands, the division has selected the WE32100 chip from AT&T. Meanwhile, the Z80000 is still scheduled for sampling in early '86.

<u>NON-VON NEUMANN DEBUGGING</u>—Sequent Computer Systems (Beaverton, OR) has announced software that bolsters its 32032-based Balance computer family. A notable enhancement is a parallel debugger which lets the programmer stop and examine individual or multiple processes. Known as PDBX, it works with Fortran, C and Pascal.

## **GOOD LOOKS** RUN IN THE FAMILY.

LEXIDATA'S LEX 90 FAMILY OF HIGH PERFORMANCE DISPLAY PROCESSORS, LOOKING GOOD. LEX 90<sup>™</sup> is Lexidata's newest family of raster graphics display processors. Its performance excites designers.

ance. And what performance!

Our exclusive Virtual Windows, with real-time. color window management capability, allows you to define, manipulate and display eight viewports simultaneously. A True

Color configuration

offers two buffers of 640x512x24 with an 8-bit color lookup table for each color. **Exclusive SimulRes** functionality allows

simultaneous display of 640x512 and

1280x1024 images

on the same screen.

high performance

there's a LEX 90 model that can

interlaced refresh.

support up to eight planes of 1280x

1024 display memory at 60Hz non-

Intelligent List Language function-

ality enables enhanced local display

And where you need

with high resolution,

list management. The

extraordinary solid

capability of our pat-

ented SOLIDVIEW®

technology is availa-

GEOVIEW,™ a three-

ble. And for oil applications, there's

modeling display

LEX 90's exclusive Virtual Windows functionality allows real-time color window management of up to eight user-defined windows.

And its cost-effectiveness excites executives. Which makes it look very

good indeed. For example:

1

\*

3

Every model in the LEX 90 family has the same basic components which use the latest bitslice technology for rapid execution of complex graphics calculations.

And the family's flexible and ware/software

architectures have been designed to accommodate growth. So you'll never have to sacrifice your initial investment should you decide to enhance your LEX 90 system's perform-

This space station model, courtesy of Martin Marietta, was created with Lexidata's SOLIDVIEW display techcompatible hard- nology, and GEOMOD<sup>™</sup> application software from SDRC.

> the unique tilt-and-swivel movement of our monitor allows smooth and easy operation of your display.

> Of course, the entire family is compatible with a variety of leading appli-

This gallery "exhibits" LEX 90's true color capability and appears courtesy of Cornell University's Program of Computer Graphics.

cation software packages and minicomputers. Which makes everyone look even better.

For a good look at the LEX 90 family and its expanding capabilities, call us at 1-800-472-4747. In Massachusetts, call 617-663-8550. Or write Lexidata Corporation, 755 Middlesex Turnpike, Billerica, Massachusetts USA 01865. TWX: 710-347-1574.

In UNITED KINGDOM call: Lexidata Ltd., Hook (025672) 3411. In FRANCE call: Lexidata SARL, Rungis (1) 4686-56-71.

In JAPAN call: Lexidata Technical Center, Tokyo 486-0670.

Copyright 1985 Lexidata Corporation. All rights reserved. LEX 90, GEOVIEW, and Lexidata are trademarks of the Lexidata Corporation. SOLIDVIEW is a registered trademark of the Lexidata Corporation and is covered by U.S. Patent No. 4,475,104. GEOMOD is a trademark of Structural Dynamics Research Corporation (SDRC).

dimensional surface modeling package for geological interpretation.

On-board, microprocessor-controlled diagnostics help maximize uptime. And

LEXIDATA LOOKING GOOD.

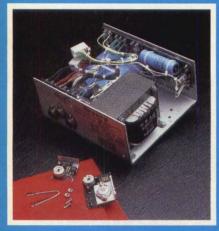

STANDARD LINEARS

• 8 Power levels: 3 to 250 watts • Over 100 standard models: single, dual and triple output . Mature, proven design • 115/230 ± 10% AC input • Built-in OVP on 5V outputs . UL/CSA approved

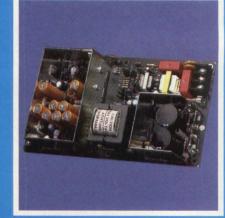

#### VALUE LINE SWITCHERS

- · 3 Power levels: 85 to 125 watts

- 15 Standard models Up to 5 outputs

- World-wide AC input ranges UL/ CSA/IEC/VDE approved

#### PAC" SWITCHERS

Enclosed, multi-output

4 Power models • UL/CSA/IEC/VDE approvals in process • World-wide AC input ranges with Auto-Switchover"

INTERNATIONAL LINEARS 6 Power levels • Over 50 models

UL/CSA/IEC/VDE approvals in process . World-wide AC input ranges.

201 Flynn Rd., Camarillo, CA 93010 (805) 484-2851/TWX 910-3330681

CONDOR is an experienced manufacturer of Linear and Switching D.C. Power Supplies. We've got the hottest power supplies on the market today, and with our competitive pricing, you can't go wrong. We have distributors throughout the U.S. and Western Europe. Please call the factory TOLL-FREE today for the representative or distributor nearest you.

#### (800) 235-5929 CALL TOLL-FREE OUTSIDE CALIFORNIA Circle 29

#### SDM SWITCHERS

• 5 Power levels; 45 to 200 watts • 29 Standard Models • UL/CSA/IEC/VDE approved • Multi-output: 3 to 5 outputs World-wide AC input ranges.

**CUSTOM & SPECIAL PRODUCTS** · Customized versions of all models available through factory . OVP 12 nectors for PAC<sup>™</sup> series • Angle bracket chassis kits for SDM & SDS models.

.CONDOR'S NEW 115,000 Sq. Ft. manufacturing plant makes it easier for us to get our product to you more (805) 987-4280 • TWX 910-3330681 (800) 235-5929 Toll-Free outside Cal.

#### SDS SWITCHERS

- Single output: -5 to 24 VDC

- 20 Models—all with built-in OVP

UL/CSA/IEC/VDE approved

- · World-wide AC input range.

#### TECHNOLOGY TRENDS

#### DESIGN TOOLS

#### CAE/CAD Industry Accelerates Toward Maturity

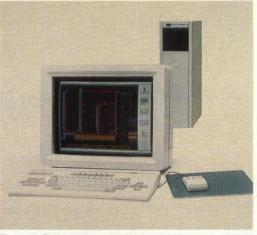

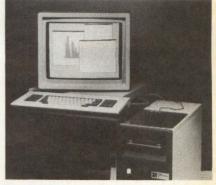

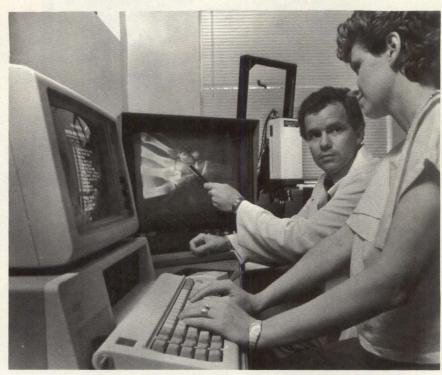

Figure 1: DEC's MicroVAX II is rapidly becoming a workstation standard. Daisy has combined a MicroVAX II workstation with its Logician software and a PC/AT graphics interface. Shown is the resulting Logician VX, available in the first quarter of 1986.

A s the CAE/CAD industry matures, many product introductions serve to round out product lines. Although the recent Automated Design and Engineering for Electronics (ADEE) show in Boston held few surprises, the products that were introduced fill some important gaps in vendors' lines. Most noteworthy, however, were announcements of support for DEC's MicroVAX II, which looks like a machine that will significantly impact the CAE/CAD industry.

Until now, standard CAE/CAD workstation platforms came from a variety of vendors such as Apollo (Chelmsford, MA), Sun Microsystems (Mountain View, CA) and IBM. But many companies do not consider such products to be standard machines. Although IBM's personal computer certainly fits the definition, it lacks the horsepower of a full 32-bit computer. Viewed in this light, the CAE/CAD user has been without a standard platform. Because many potential workstation buyers desire a true standard platform, several CAE/CAD vendors are either abandoning or complementing their proprietary machines in favor of the MicroVAX II.

Surprisingly, Daisy Systems (Mountain View, CA) changed its course by announcing a two-year, \$50 million OEM MicroVAX II agreement with DEC. Under the agreement, Daisy purchases MicroVAX IIs and equips them with its Logician CAE/CAD software and a PC/ AT graphics interface. The resulting Logician VX (**Figure 1**) workstation sells for \$90,000 and will be available in the first quarter of 1986. Daisy's shift from proprietary hardware eliminates a primary criticism of the Logician. Others joining Daisy's MicroVAX II strategy include Tektronix/CAE (Santa Clara, CA), Case Technology (Menlo Park, CA), Phoenix Data Systems (Mountain View, CA), FutureNet (Chatsworth, CA) and Valid Logic (San Jose, CA). Since Valid's Scald software already ran on VAX computers, the port to the MicroVAX II is relatively easy.

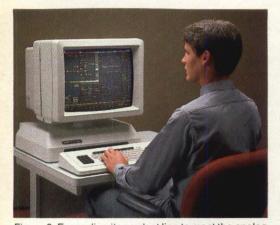

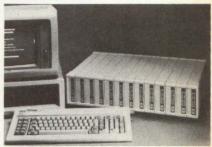

On the other hand, Cadnetix (Boulder, CO) chose the 68020 (running UNIX) as a platform. The company announced a family of seven 68020-based workstations: three monochrome systems and four color machines. On the monochrome side, the CDX-9100S (\$30,500) is a basic schematic capture system whereas the CDX-9150S (\$33,500) includes an additional virtual logic analyzer and a special graphics editor for analyzing simulation data. The CDX-9200S (\$39,500) is identical to the 9150S except that it includes the Cadat logic simulator from HHB Systems (Mahwah, NJ). In the color domain, the CDX-50000S (\$82,900) is a highperformance graphics CAD system supporting both PC board layout and schematic capture.

Another 68020-based workstation from Cadnetix, the CDX-59000S (\$96,900), handles schematic capture, logic simulation and PC board layout (**Figure 2**). Rounding out the family is the CDX-9300S (\$59,000) and CDX-5900S (\$71,400). Both perform schematic capture, logic simulation, logic analysis and custom postprocessing. However, the 5900S also handles automated PC board layout and manufacturing postprocessing.

At a time when proprietary hardware is on the decline, Buck Henry, Cadnetix's vice president of marketing defends the firm's strategy. "Standard platforms are excellent general purpose systems," says Henry, "but they do not deliver the performance found in a dedicated machine." For users, the trade-off is between exceptionally high performance or a more standardized design environment.

Following the recent unveiling of Intel's (Santa Clara, CA) 80386, both Daisy and Valid announced simulation support for the processor on the Physical Modeling Extension and Realchip hardware modeler, respectively. Daisy also introduced MegaFault, a high-performance fault simulator for the firm's Megalogician. MegaFault, priced at \$45,000, uses a concurrent fault simulation algorithm and the same simulation models as those in the Megalogician.

Traditional fault simulation algorithms, such as those used by MegaFault, Calma's (Austin, TX) Tegas and Gen-Rad's (Santa Clara, CA) Hilo, fault each node in the circuit and then determine whether the test vectors detect the fault. Faulting each node is a time-consuming task that often demands excessive processing power. However, Caedent (Colorado Springs, CO) takes a different approach to beat the problem. Instead of actually faulting the nodes, the company offers a probabilistic fault grading (PFG)

#### TECHNOLOGY TRENDS/DESIGN TOOLS

tool that statistically determines the percentage of faults detected by a set of test vectors. PFG reportedly yields results very close to those of traditional methods without the long run times.

Along a similar vein, Silicon Solutions (Menlo Park, CA) announced the Mach 100, a second hardware accelerator in its family of logic and fault simulation engines. Mach 100 executes 250,000 events per second and has a capacity of 32,000 modeling elements.

High accelerator prices have been a major deterrent to many potential buyers. Until recently, accelerator prices ranged from \$200,000 to several million dollars. But both Silicon Solutions' Mach 100 and Zycad's (St. Paul, MN) Sprintor represent systems in the \$20,000 to \$30,000 range. Sprintor (available only on an OEM basis) offers slightly lower performance and capacity than the Mach 100, but it costs \$5,000 less than the Silicon Solutions machine.

link, an option for its Logic Evaluator (LE) and Expeditor simulation engines that allows them to interactively exchange event data with other systems. According to Nicholas Van Brunt, leader of the company's R&D group, "Eventlink gives users of the LE and Expeditor the potential to link one of the simulation engines

At ADEE, Zycad introduced Event-

however, must write the software to support such an interface.

Both Daisy and Valid have begun to address the analog designer's needs. Daisy's recently-formed Analog Design Automation Division unveiled the Chip-SIM MOS simulator, which reportedly runs up to 20 times faster than Spice.

to almost any event-generating

CAE tool or peripheral. They can

operate concurrently with exter-

nal physical and behavioral

models as well as share a Zycad

simulation engine interactively

between design teams." Users,

ChipSIM was developed under an agreement with Shiva Multisystems (Menlo Park, CA), a firm specializing in analog simulation. In addition, Daisy introduced the Daisy Parameter Extraction Program (DPAX) and the Analog Device Library Builder (ADLiB). DPAX takes actual device parameters from test wafers and feeds the data into the analog simulator's models. This ensures that the simulator uses the most accurate device modeling parameters. ADLiB permits designers to construct their own models for inclusion in the analog simulator's library.

Although Valid and Daisy products compete with each other on most levels, Valid's recent analog offering is more in

> line with the software from Analog Design Tools (ADT) (Menlo Park, CA). In addition to Spice, Valid's Analog Designer includes a digital voltmeter, an oscilloscope, a network analyzer and a function generator (Figure 3). The package is priced at \$22,000, not including the Scaldsystem platform. ADT, however, offers the same kind of tools as Valid plus packages that perform spectrum analysis, Monte Carlo analysis and sensitivity analysis.

> Hewlett-Packard (Fort Collins, CO) also exhibited at the ADEE and is showing signs of commitment to the CAE/ CAD market.

Figure 2: Cadnetix launched several 68020-based UNIX workstations at the recent ADEE show. Shown is the CDX-59000S, a CAE/CAD system handling schematic capture, logic simulation and automatic PC board layout. Also included is a virtual logic analyzer and graphics accelerator.

In addition to its own recently-announced CAE/CAD product offerings, the test equipment giant is teaming up with VLSI Technology (VTI) (San Jose, CA), SDA Systems (Santa Clara, CA) and Analog Design Tools. VTI announced that its IC design software product line will run on the HP 9000 Series 300 engineering workstations. HP will also market and distribute the products. Similar agreements were signed with SDA and Analog Design Tools.

VLSI Technology introduced its longawaited standard cell library. Fabricated in 2-micron CMOS, the library consists of over 250 standard cells and is fully compatible with VTI's Megacells and silicon compilers. (VTI recently repositioned its cell compilers as silicon compilers.) Other newcomers to the standard cell market include Fujitsu (Santa Clara, CA) and Oki Semiconductor (Sunnyvale, CA). Fujitsu's standard cells have been available in Japan for several years, but the firm delayed its US debut. The library is based on the same 1.8-micron, twolayer metal, silicon-gate CMOS technology used in its gate arrays. Oki's standard cells also use this technology, but the firm offers both a 2-micron and 3-micron library.

Most CAE/CAD vendors attending the ADEE reported a leveling-off of sales, which stands in sharp contrast to the record revenues of 1984. Although the semiconductor slump is affecting the CAE/CAD sector, manufacturers are predicting an upturn.

- Collett

Figure 3: Expanding its product line to meet the analog designer's needs. Valid has introduced a workstation that includes a digital voltmeter, an oscilloscope, a network analyzer and a function generator.

# We run with a great crowd.

## Complete hardware/software compatibility.

Talk about easy interfacing. You can take a ZETA 824 or ZETA 836 plotter and plug it into virtually any computer made.

What's more, you'll be ready to run because our plotters understand a variety of computer protocols. Select the model for your application then just plug in and plot.

In fact, we're a plug compatible replacement for many plotters from HP, CalComp and Tektronix. Some models of our plotter can even run directly from your IBM cluster controller. Now that's easy interfacing.

When it comes to your favorite application packages, you'll be on safe ground too. Packages such as CADAM, TechniCAD, Euclid, P-CAD, AutoCAD and many more.

### *The most productive plotter for the money.*

7

You'll be getting the highest output plotters for the money with our new ZETA 824CS and ZETA 836CS. More

PRIME /

Tha

MANCOLEI

recision

tronix

finished plots. More productivity. Plus, these "D" and "E" format plotters let you run either single sheet or roll media.

#### Easy-to-use touch controls.

Your time is valuable. So we've made our touch controls simple – yet powerful. Set speed, pen pressure, liquid ink parameters, electronic limit sensing, windowing, scaling – all at the touch of a finger, Self-test and diagnostic plots too. Let us show you dozens of other time-saving operations in a brief demonstration.

#### Plotter specialists.

We've been designing hardware interfaces, plotting language emulators and high performance pen plotters for over 14 years. Nicolet also provides you with worldwide sales and service support.

Give us a call. See how easy it is to join the crowd.

Call (415) 372-7568. Nicolet Computer Graphics Division, 777 Arnold Drive, Martinez, CA 94553 TWX 910-481-5951

Computer Graphics Division

CADAM is a trademark of CADAM, Inc. TechniCAD is a trademark of Tektronix, Inc. Euclid is a trademark of MATRA DATAVISION, Inc. P-CAD is a trademark of Personal CAD Systems. AutoCAD is a trademark of Autodesk, Inc.

Circle 18 on Reader Inquiry Card

# "It's easy to spot the difference between our IBM PC-based frame grabber and the others."

High performance and affordable cost, just \$1495 for

A/D Input

Frame Grab

D/A Output

Frame Memory

LUT's

False Color

a single plug-in board.

Unlike other video I/O systems, the new DT2803 provides real-time image capture capabilities, digitizing a 6-bit video field every 1/30 second. An on-board, memory-mapped, dual-ported frame store memory (256  $\times$  $256 \times 8$ ) makes it ideal for the IBM PC's 64K buffer size. And for real number crunching,

the DT2803's external ports interface to high speed co-processors.

With our software package, VIDEOLAB,<sup>™</sup> the DT2803 is easy to use for image operations like averages, histograms, and convolutions.

So, if your application is manufacturing/automatic inspection, robotics, or medical research, our new high per-

Call for our new 576 pg. catalog/ handbook or see it in Gold Book 1985.

formance video I/O board will really open your eyes-at an unbeatable price.

Call (617) 481-3700

64 colors × 64 intensities, R-G-B; 64 grey levels, monochrome

**SPECIFICATIONS: DT2803**

$256 \times 256 \times 8$  (2-bits for graphic overlays)

RS-170 (CCIRR), 6-bits at 5MHz

8, 64 × 8 input; 4, 256 × 12 output

1/30 (1/25) second per field

World Headquarters: Data Translation, Inc., 100 Locke Dr., Marlboro, MA 01752 (617) 481-3700 Tlx 951 646. European Headquarters: Data Translation, Ltd., 13 The Business Centre, Molly Millars Lane, Wokingham Berks, RG112QZ, England TIx: 851849862 (#D) In Canada: (416) 625-1907 IBM PC is a registered trademark of IBM. VIDEOLAB is a registered trademark of Data Translation, Inc.

**Circle 14 on Reader Inquiry Card**

#### **TECHNOLOGY TRENDS**

#### IMAGING

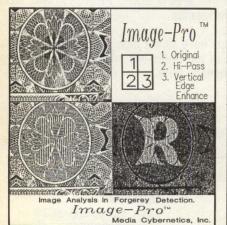

#### Optics Finds A Niche In Imaging

Technologies such as fiber optics, optical disks, software and graphics have combined to produce unique electronic imaging products. Emerging from the exhibit halls of the recent Electronic Imaging '85 show in Boston, products were launched by a variety of companies seeking to gain a specific niche within the image processing market.

In CAD/CAM applications, for example, a major problem has been the relatively large expense associated with flatbed scanners (Digital Design, June 1985, p. 20). At Galileo Electro-Optics Corp. (Sturbridge, MA), this problem has been overcome with a product called Glasscan, which converts most pen plotters into image digitizers. By replacing the Gurtz pen holder with a fiber-optic sensor, systems integrators can digitize 4-bit-deep images into IBM PC/XT or AT systems. Costing between \$3,000 and \$4,000, Glasscan transfers images over a fiber-optic cable to a 256  $\times$  1 linear charge coupled device from EG&G Reticon (Sunnyvale, CA) and digitizes the resulting signal across the IBM PC bus.

According to Brian Rhea of Galileo, the PC memory represents the only limitation to image size. The company is actively working with OEMs to develop interfaces for other computer systems including the MicroVAX II from DEC. In 1987, the company plans to announce a color version of Glasscan which will be able to digitize large size color drawings to 8-bits deep.

Image storage has also plagued imaging systems designers. Because of the large amounts of memory associated with image storage, system designers have been forced to consider new technologies such as optical disks. Aquidneck Data Corp. (Middleton, RI) has done much to address these problems with a line of IEEE controllers for the Gigadisc from Alcatel Thomson (Redondo Beach, CA).

In operation, the optical archiving system that Aquidneck has developed appears to the host as a 9-track 1,600 bit/in. PE tape formatter. Thus, a single 1,000-Mbyte optical disk can hold the contents of 20 or more 2,400'-tapes, depending on the amount of data stored on each. The controller interfaces to any Pertec-type tape controller over two standard I/O cables and accepts all standard tape commands. A 12"-optical disk is employed. This is removable and has a data retention life of over 10 years. As an option, the controller can encrypt data saved to the optical disk to provide information security and access restrictions.

Addressing the imaging software problem is the goal of many of the hardware companies. For example, Data Translation (Marlboro, MA), has announced an agreement with Camtrel Computer Systems (Cambridge, England) to distribute Camtrel's PC Semper in the US. PC Semper, an image processing package for the IBM PC family, has been tailored for use with Data Translation's DT2803 frame grabber. Developed initially at Cambridge University, the software package is written entirely in Fortran-77 code, allowing users equipped with the IBM Fortran compiler to either develop image processing routines using callable routines or to develop novel routines not included in the package. According to Camtrel, the package can support full IEEE floating point representations of images on the PC. Camtrel is also working on an array processor which will speed up imaging functions by up to 180 times. At present, distribution agreements for the AP have not been signed in the US.

Combined imaging and graphics has become one of the most important goals in the electronic imaging field. As a step in this direction, start-up Imagraph (Woburn, MA) has announced its AGC-1024P advanced color graphics and imaging controller for the IBM PC/XT and AT. Although the board uses the Hitachi ACRTC graphics controller, as is used in many other graphics boards, it also supports 1 Mbyte of on-board memory and three 8-bit DACs. This allows it to display  $1024 \times 1024 \times 8$  images producing 256 colors from a palette of 16.8 million. According to Bob Wang, president of Imagraph, two of the most novel features of the design are the ability of the board to perform hardware clipping of images and its speed versus existing 7220 designs.

-A. Wilson

Combining three 8-bit DACs with 1 Mbyte of on-board memory allows the AGC-1024P graphics controller from Imagraph to simultaneously display 256 colors from a palette of 16.8 million.

String Software<sup>™</sup> from Geobased Systems, Inc., Raleigh, North Carolina

2. 3D sphere from Vectrix

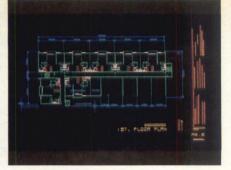

3. Created with VersaCAD<sup>™</sup> software from T&W Systems, Inc., Huntington Beach, California

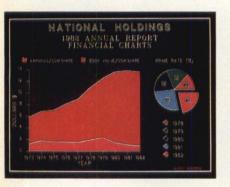

Business graphics created with D-PICT/B software from Dataplotting Services, Inc., Don Mills, Ontario, Canada

5. Courtesy of Wave Graphics, Cleveland, Ohio

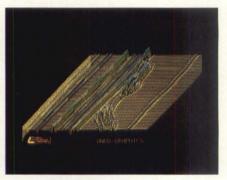

Seismic traces displayed in isometric projection using Ondo-Graphics software from Earth Technology Consultants, Inc., Houston, Texas

## PEPE—Six More Reasons Why Professionals Continue to Choose Vectrix For Quality IBM XT/AT Graphics.

The quality and detail displayed above are usually attributed to expensive CAD/CAM systems. Look again. These displays were generated with our new PEPE graphics board. This remarkable new product provides the performance of expensive CAD/CAM systems, at a fraction of the cost. Why? Because it's designed to operate with IBM XT/AT ™ computers.

PEPE gives you sophisticated high quality graphics at a surprisingly affordable price. So if you're considering a graphics system, consider this:

#### Power without the Price

The new PEPE graphics board boasts 1024  $\times$  1024 *viewable* resolution on a 19" 60 Hz non-interlaced monitor. It draws over 20 million pixels per second, simultaneously displays up to 4,096 different colors from a palette of 16.8 million, and contains its own on-board character generator.

What all of this means is power—power to increase your design productivity economically.

#### Text Overlay

PEPE is available in configurations of 4, 8 and 12 memory planes. In all configurations, an additional text overlay plane is provided. This separate plane can be used for menus, text description of onscreen graphics, operator prompts, or any other text-oriented application. Since this plane is separate from the graphics planes, on-screen graphics can be zoomed or panned without affecting the text data.

System-Type Graphics Capability PEPE is so powerful, it runs quality graphics programs previously available only on highly sophisticated and expensive—CAD/CAM systems. So, whether your application is solids modeling, cartogra-

phy, seismic analysis, architecture, business graphics, or general engineering design, PEPE does it all—quickly, brilliantly, and inexpensively.

For further information about PEPE or any of the other fine Vectrix graphics products, contact: Vectrix Corporation, 2606 Branchwood Drive, Greensboro, North Carolina 27408. Phone (919) 288-0520. Telex 574417.

Distributor inquiries welcome.

IBM XT, IBM AT, and IBM PC are trademarks of International Business Machines Corporation, White Plains, NY.

#### **TECHNOLOGY TRENDS**

#### SOFTWARE

#### **UNIX And MS-DOS Merge**

he UNIX operating system has achieved the support of the engineering and scientific community, perhaps due to the amount of CAE software written for it. But the emergence of PC-based workstations has led to numerous CAD/CAE software packages for the MS-DOS operating system. Several CAD/CAE vendors have had to split certain aspects of the design process between the two operating systems. Schematic capture may be able to run under MS-DOS: on the other hand, fault simulation, because of its heavier computational requirements, is better accomplished under a multitasking operating system such as UNIX. According to Terry Zimmerman, vice president of marketing at FutureNet (Canoga Park, CA), the integration and free flow of data between systems is the primary problem for PC-based workstations.

Most implementations of multiple operating systems partition the system disk between the operating systems, necessitating file transfer utilities for file access. Will Herman, director of product engineering at Viewlogic (Marlboro, MA), indicates that despite available tools for CAE, the development cycle has been hampered by the need to convert file formats from the MS-DOS-based schematic to UNIX-based simulation.

Connector from Uniforum (Santa Monica, CA) was the first system to allow MS-DOS applications to run as tasks under UNIX. However, George Strong, vice president and chief financial officer of Uniforum, notes that Connector's limitation was in rewriting MS-DOS programs so that they could run in the 80286 protected mode for multitasking systems. As a result, a tradeoff existed between doAT&T Information Systems (Morristown, NJ) will offer Multisystem

Merge as OS Merge on its AT lookalike, the 6300 Plus, available in the first quarter of 1986. The ability to run MS-DOS and UNIX programs concurrently may solve the problem of information flow that now exists for PC-based CAE workstations.

ing substantial software rewrites and limiting UNIX to a single user.

The announcement of Multisystem Merge from Locus Computing Corp. (Santa Monica, CA) enables 80286based microcomputers to run both MS-DOS and UNIX applications concurrently while maintaining the multitasking features of UNIX. It is a wholly software solution. Since UNIX and MS-DOS share the same CPU, no rebooting of the computer is necessary.

Multisystem Merge divides system resources into low-level resources, such as the disk, CPU and system memory, and high-level resources, which include the file system and application programs. Both levels are transparently sharable between the two operating systems. Recordlevel sharing of files by MS-DOS and UNIX is provided. As a result, all MS-DOS applications can run as tasks without modification under UNIX on a 80286-based computer. Data files created under MS-DOS can be immediately used by a UNIX application; MS-DOS and UNIX programs can both be used to develop other software.

Nevertheless, the question of performance is still at issue for Multisystem Merge. How well does a 16-bit processor run UNIX? Several UNIX/coprocessor subsystems with on-board UNIX ports and 32-bit processors are currently available. These boards, for example the Opus516 Personal Mainframe from Opus Systems (Los Gatos, CA), still require that the computer be rebooted after an MS-DOS to UNIX file transfer in order to change operating systems.

At Wescon, FutureNet announced the DASH-CADAT Plus, a coprocessor board that includes a 32016 microprocessor to control the two operating systems. A windowing environment buffers the user from having to know either UNIX or MS-DOS commands. The hardware approach to integrating operating systems differs from the software approach because either XT- or AT-compatibles can be configured to run UNIX. Multisystem Merge requires an AT-compatible. This fact may prove important with the large installed base of XT machines in the CAE arena.

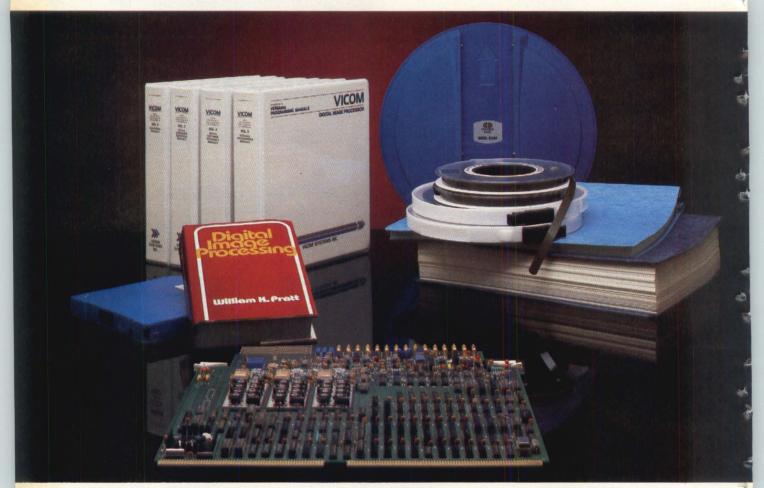

## VICOM. The image processor for those who deserve to get more than they thought they paid for.

#### Innovation has always been a VICOM hallmark.

From its beginning, Vicom Systems has built its business by delivering systems that exceed the performance expectations of the most critical scientists and engineers. It is against this background of unequivocal performance that Vicom Systems builds your specific image processor.

#### Configure the specific system you need.

The VICOM image processor is highly modular. By selecting the right combination of circuits our team of specialists can quickly and cost-effectively create the taskoriented image processor you need. Long term relationships

At Vicom Systems our objective is to build a working relationship. The initial sale is only the beginning. System upgrades, responsive service, training, special software routines, we have them in place ready to implement at

your call.

#### Vicom Systems, Inc. The image processing professionals.

Our business strategy is simple. We build-in quality. More than you thought you paid for. We help you get your system

For Immediate Interest, Circle 12 For Information Only, Circle 22 running, faster. We respond positively when you need us. The results: Productivity, not promises. Performance with lasting reliability.

Call or 8 Or v Jun San Tele VICO

We're Vicom Systems. Call us at 408-946-5660 or 800-538-3905. Or write us at 2520 Junction Avenue, San Jose, CA 95134. Telex 171603 VICOM SYS.

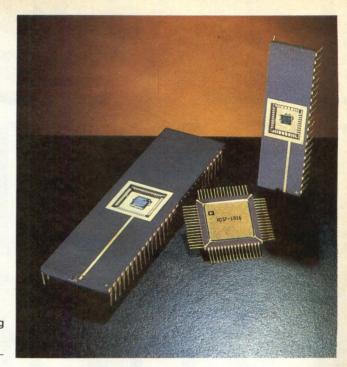

#### TECHNOLOGY TRENDS

#### ICs

1

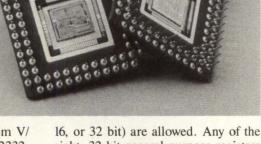

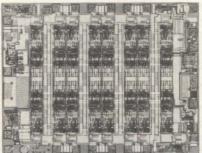

#### Multiplier/Accumulator Manufacturers Multiply

When TRW introduced the TDC1010, it set the standard by which 16 × 16 multiplier/accumulators were measured. Fabricated in TRW's bipolar process, the part offered the capability to specify input data as two's complement or unsigned magnitude, yielding a fullprecision 32-bit product. Products could be accumulated to a 35-bit result.

Since then, the company has gone on to offer both bipolar and CMOS pin-compatible versions of the part. Its TDC1043, for example, is compatible with the TDC1010, but does not provide the preload and least significant product output capabilities. However, what the part does offer is almost twice the speed of the 1010 at less than one-third the power dissipation.

Building on the success of the bipolar parts, the company recently disclosed

Photo courtesy Analog Devices.

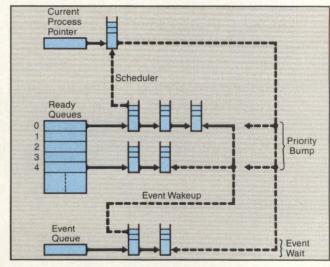

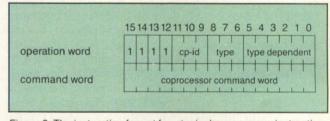

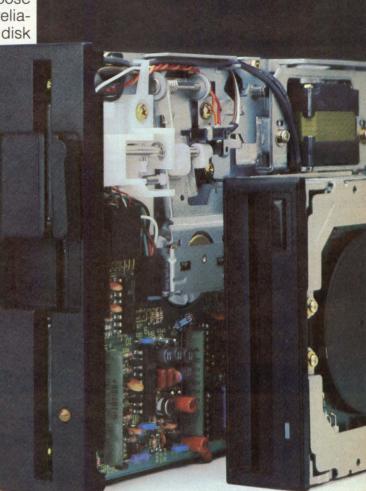

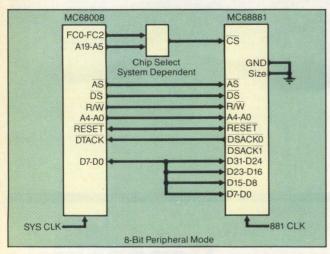

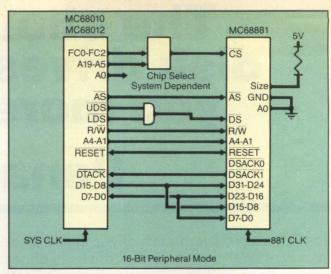

information on its  $16 \times 16$  CMOS multiplier/accumulators. The first, the TMC-2010, operates at a 160-nsec cycle time. Compatible with the TDC1010, the part consumes less than one-sixth the power of its bipolar cousin, depending on the multiply-accumulate rate.