# Four reasons why you should look at our Winchesters

- 1. 100% SMD format and interface compatible.

Just plug it in and it is ready to accept data.

- 2. The best price/performance ratio available.

Kennedy can save you an average of \$2000.00 per unit over comparable disk equipment.

- 3. Immediate availability.

Most models are ready to ship 30 days ARO.

- 4. Produced by an industry leader.

Kennedy has been manufacturing Winchesters since 1978 and its reputation for reliability is known world-wide.

# **KENNEDY**

n Allegheny International Company

1600 Shamrock Ave., Monrovia, CA. 91016 (213) 357-8831 TELEX 472-0116 KENNEDY TWX 910-585-3249

# KENNEDY INTERNATIONAL INC.

U.K. and Scandinavia McGraw-Hill House Shoppenhangers Road Maidenhead Berkshire SL6 2OL England Tel: (0628) 73939 Telex: (851) 847871 KEN UKS G

## KENNEDY INTERNATIONAL

Koningin Elisabethplein, 8 B-2700 Sint-Niklaas Belgium Tel: (031) 771962 Telex: 71870 KEN CO

The state of the s

\*\* KENNEDY

53150

165 Megabytes

82 Megabytes

KENNEDY • QUALITY • COUNT ON IT

Write I on Reader Inquiry Card

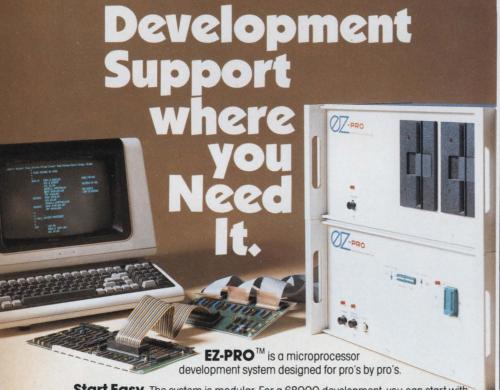

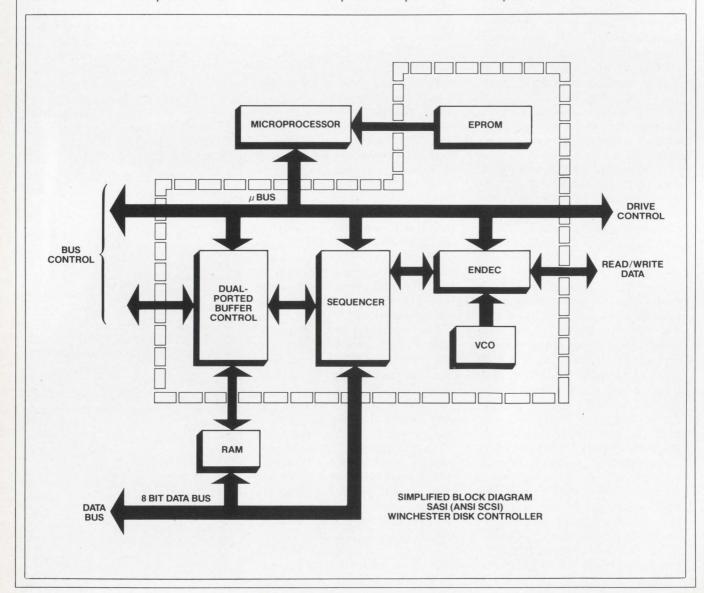

New WINC05 controller achieves 51/4" Winchester and floppy control with a single board.

The new WINC05 system from AED provides complete RL01/02 and RX02 emulation with one dual-wide board. So now you can combine 54" Winchesters with 54" floppy backup for the exact disk system package you need. It's like getting a floppy controller for FREE!

The WINC05 board plugs right into your DEC cpu to provide disk system capacities ranging from one 5-MB Winchester and a .5-MB floppy to two 10-MB Winchesters and two .5-MB floppies.

AED offers you a complete system: cables, controller, drives, and documentation. Or buy just the WINC05 board and add your own Winchester or floppy drives. It's easy, because AED supports any industrystandard drive interface.

Q-Bus® and UNIBUS® compatibility.

The WINC05 board is fully transparent to DEC operating software and diagnostics, and Q-Bus® compatible. A quad-wide UNIBUS® version will soon be available.

WINC05 offers you the highest data throughput of any Winchester/floppy disk system around—259 Kilobytes per second over the entire disk—and much, much more!

5.5 MB Winchester/floppy combination.

21 MB Winchester/floppy combination.

For instance: complete accommodation of all DEC's future 5¼" media through microcode changes only; an on-board bootstrap; DC drive motors for worldwide use without hardware changes; support of DEC's 22-bit addressing for later memory expansion; plus integral diagnostics and format routine.

Call or write AED today for more information on WINC05.

OEM quantity discounts available.

\*Reg. trademark of Digital Equipment Corp.

\*Seg. trademark of Digital Equipment Corp.

ADVANCED ELECTRONICS DESIGN, INC.

440 Potrero Avenue, Sunnyvale, ČA 94086. Phone 408-733-3555 Telex 357-498. Outside California, Hawaii and Alaska call 800-538-1730.

Sponsors of the U.S. Pavilion, 1982 Worlds Fair # APEL MY PERSONAL PROPERTY OF THE PERSONAL PR

Write 20 on Reader Inquiry Card

Domestic Sales Offices: Los Angeles 213-907-8811 Houston 713-688-0700 Detroit 313-352-4290 New Jersey 201-238-6322 New England 617-256-1700 Washington, D.C. 301-760-4310 Chicago 312-565-1718.

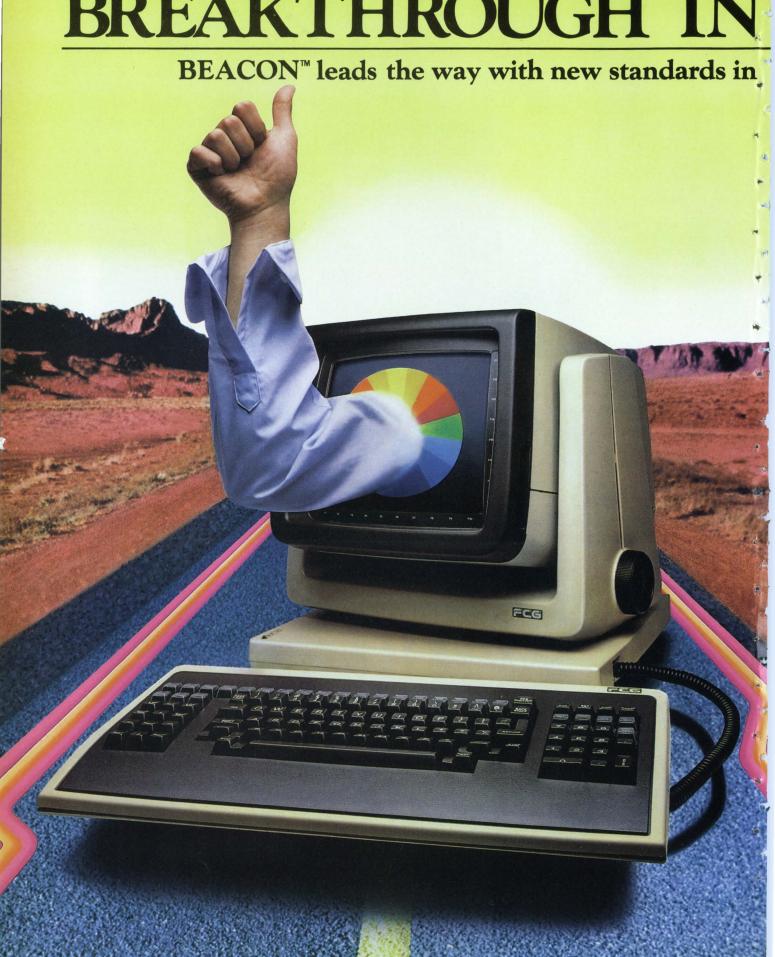

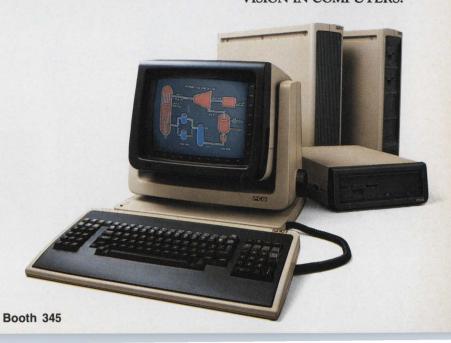

# BREAKTHROUGH IN

# COLOR GRAPHICS.

# price-performance and human-factors engineering.

Finally, a medium-priced color graphics system with the performance of much more expensive systems.

Introducing Beacon™ from Florida

Computer Graphics.

### Enhanced productivity for business and engineering.

The Beacon™ System displays a full spectrum of graphics capabilities. Not only multi-color graphs and charts, but engineering diagrams, as well.

As a stand-alone or host-dependent system, Beacon does it all. For enhanced productivity in engineering, marketing, manufacturing, and financial control.

# More power where it's needed.

The Beacon System can accommodate up to almost 1 MByte of main processing memory. With the addition of 640 KB of graphics memory, Beacon can create a 1280 x 960 image resolution used in many CAD/CAM applications. This high resolution, combined with standard zoom and roam features on a 13" or 19" display, make Beacon ideal for engineering applications. Beacon's own menu driven software and CP/M compatible operating system provide access to a comprehensive library of programs that cover virtually every aspect of business.

## Superior graphics features.

The extent and caliber of Beacon's graphics features is unmatched in its price range.

The System's brighter, more vivid colors stem from a unique electronic design and a superior raster scan display. The BeaconBRIGHT<sup>IM</sup> image, combined with an anti-glare filter eliminates the need for hooding the display-even in brightly lit areas.

Circles, vectors, arcs, rectangles and polygon fills are generated with hardware rather than software. As a result, image response is almost instantaneous.

Beacon's 16x zoom feature can be controlled from the keyboard in 1x increments. Both horizontal and vertical scrolling is variable in speed and exceptionally smooth. Beacon also provides reverse video and underline, as well as blinking and variable height characters.

Other graphics features include: 640 x 480 resolution (standard); 6 memory planes with 256 colors - up to 32 usable at a time (16 in the graphics plane and 16 in the alpha numeric plane)—and 18 programmable function keys on the keyboard and another 18 on the display bezel.

Write 5 on Reader Inquiry Card See us at the Federal Computer Conference, Booth 345

# Human-factors engineering.

The human factors, or ergonomics, that make a computer personally comfortable played an integral part in the Beacon System's design.

The critical area of reducing eye strain and fatigue has been accommodated through the development of a screen image twice as steady as the image in other computer systems, including those that are advertised as "flicker free." For extra visual comfort, the brightness of the Beacon image is controllable at the keyboard, and an anti-glare filter reduces distracting reflections.

And Beacon's commitment to superior ergonomic design doesn't stop there. To avoid back strain, the monitor tilts, swivels, and uniquely adjusts 5.5" in height. In addition, the keyboard is separate from the display and can, therefore, eliminate the sense of being tied down to the monitor.

Other hands-on features that make for greater comfort and productivity are: a three-degree adjustable tilt in the key-board, a palm rest, tactile feedback, sculptured keys, and a dimpled home key in the function and numerical key clusters.

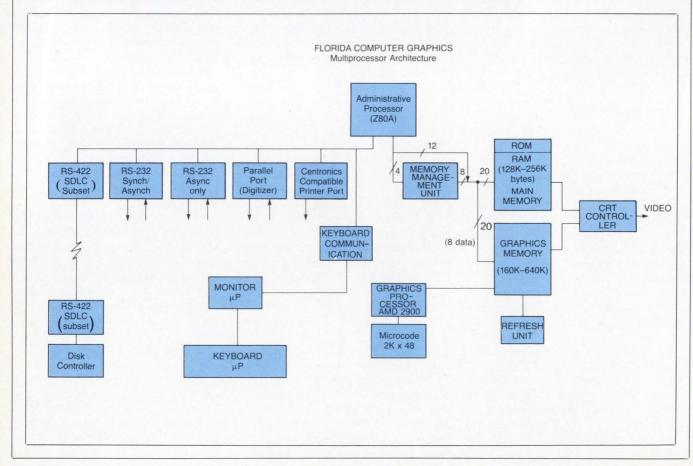

# The importance of MPA.

Our MPA, or Multiple Processor Architecture, is unique to the Beacon System. It incorporates six individual microprocessors, each chosen for its efficiency in the performance of specific tasks.

System throughput is optimized with the use of an administrative processor which distributes Beacon's internal workload. A 16-bit bit-slice processor is dedicated solely to graphics tasks and mathematical functions.

MPA is at the heart of Beacon's extraordinary performance.

# Quality and service assured.

All equipment is constantly monitored and evaluated from our corporate production facility, utilizing the most sophisticated automated test equipment available today. And our systems are supported by three levels of service, assuring you of minimal downtime.

# BEACON™—the beginning.

Beacon is available. NOW. And it's just the beginning of a comprehensive family of systems that will enhance your productivity. Contact us for more information on how the Beacon System can work for you. We'll send you our full color literature. Just write: Marketing Communications Manager, Florida Computer Graphics, 1000 Sand Pond Road, Lake Mary, Florida 32746. Or call (305) 321-3000. In the Continental U.S. outside Florida, dial 1-800-327-3170.

FLORIDA COMPUTER GRAPHICS VISION IN COMPUTERS.

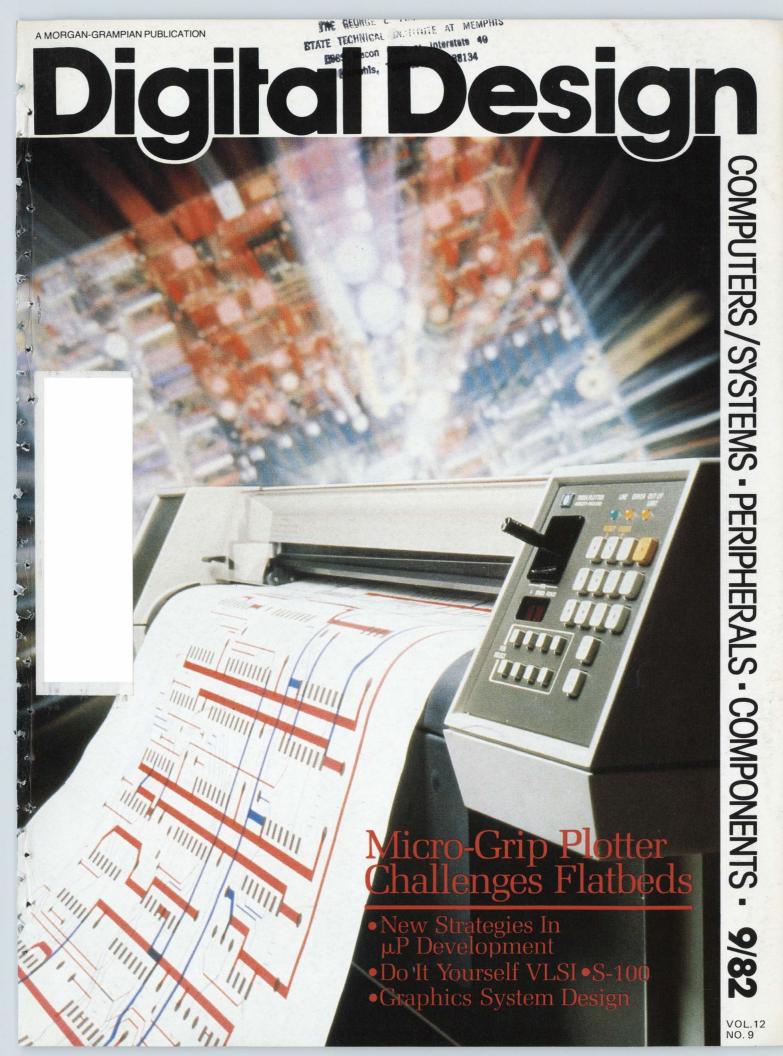

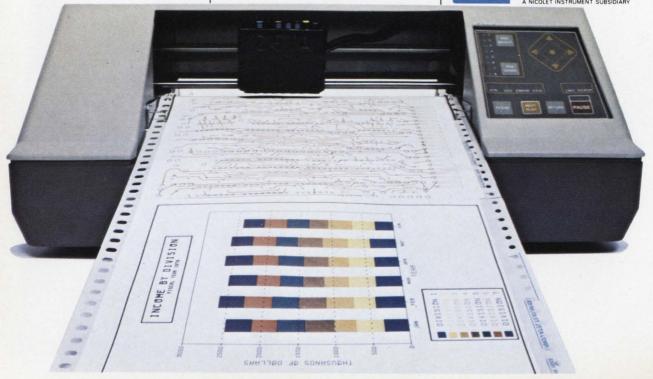

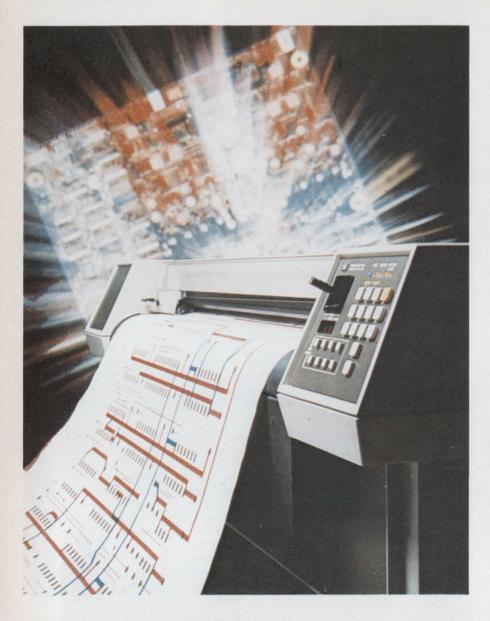

# CalComp's new 36" EPP plots from vector data. Thanks to our new 95X controllers.

CalComp adds an all new 36" Electrostatic Plotter/Printer to our family of EPPs. The new CalComp Electrostatic Model 5500 gives you high quality, full size plots of your CAD/CAM, seismic, mapping, or other engineering drawings.

New controllers drive EPPs and pen plotters. CalComp's new vector to raster controllers are the first in the industry to drive both electrostatics and pen plotters. These unique and versatile models—for online and online/offline applications—free your host computer from timely and costly conversion tasks. Plus, one controller can simultaneously be attached to eight CalComp

electrostatic plotters and a CalComp pen plotter. You add to the configuration as your operation continues to grow. All with one supplier...CalComp.

The best warranty and service available.

The CalComp exclusive one-year warranty on parts and labor is the only one of its kind. Plus, we offer the largest team of systems analysts and field service engineers to help guarantee prompt, quality product support.

There's a lot more to know about CalComp's newest EPP and vector to raster controllers. Contact your nearest CalComp sales office or write for more information.

# Digital Design

p. 74 (photo courtesy Florida Computer Graphics)

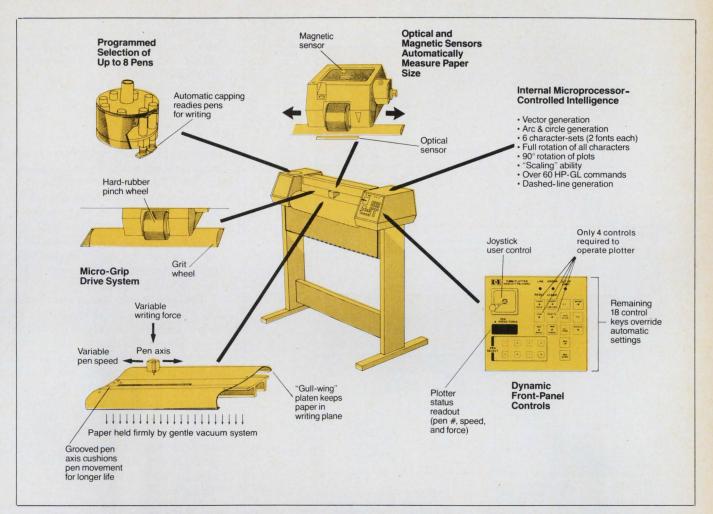

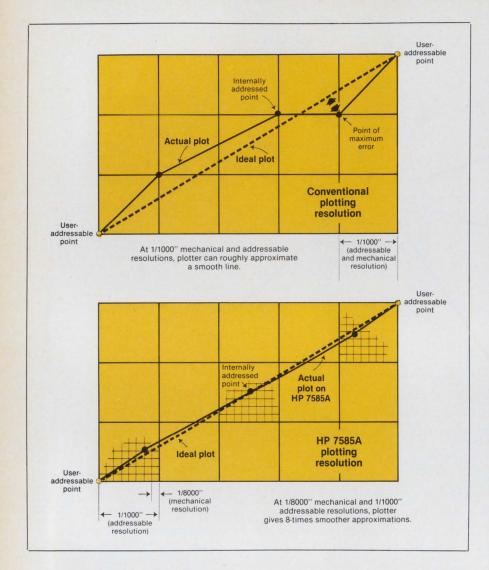

p. 44 (photo courtesy Hewlett Packard)

p. 60 (photo courtesy AMI)

## Cover

H-P's 7585A plotter represents a major step forward in making large-scale plotters smaller, cheaper and faster (see p. 44).

Published monthly and copyright © 1982 by Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215. Second class postage paid at Boston, MA and additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215

# COMPUTERS/SYSTEMS

# **PERIPHERALS**

# **COMPONENTS**

Byte Static CMOS RAMs.

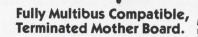

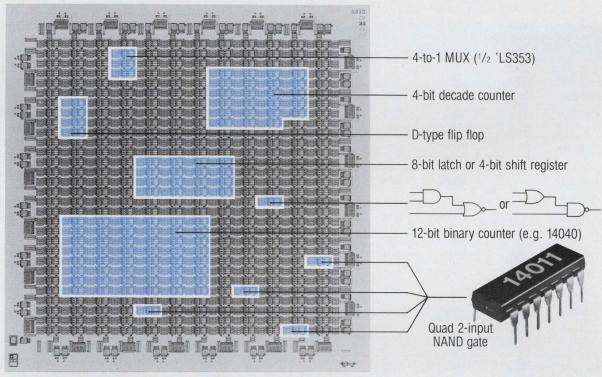

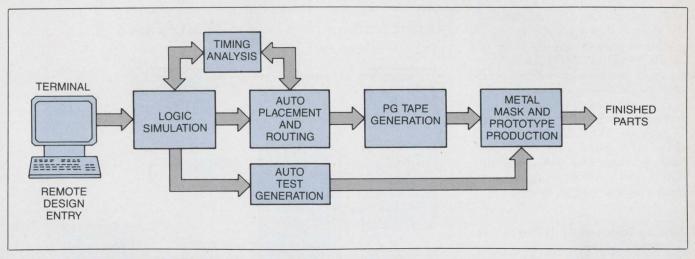

| The rapidly expanding custom logic field will provide designers the opportunize board space and to make proprietary designs. | inity to maxi- |

|------------------------------------------------------------------------------------------------------------------------------|----------------|

| Innovative Design                                                                                                            | 76             |

| Winchester Controller Designed For Multitasking Systems                                                                      |                |

| Technology Trends                                                                                                            | 18             |

| High Grouth Of Surface Mounted Booksess Earness & Stockable Medule                                                           | Hausas 16V     |

Do It Yourself VLSI ......60

| Letters10       | New Products77       |

|-----------------|----------------------|

| Calendar12      | Advertisers' Index82 |

| News Update14   | New Literature83     |

| Product Index48 | Viewpoint84          |

# Modgraph GMD Display Generators...

High Performance Graphics at an Unbeatable Price!

A tough statement backed by a unique modular approach. Buy only the capability you need.

Modular in design, configurations are available ranging from single

board B/W graphics to full color image display systems at resolutions from 512 X 512 to 1024 X 1024.

Graphics memory is switchable from 30HZ interlace to 60HZ repeat field for flicker free display at no additional cost.

□ Compact Modular Design□ 512 X 512 to 1024 X 1024 resolution

- □ Interlace or Repeat Field

- ☐ 128 ACII Character Generator

- ☐ 1-15 X Character Magnification

- ☐ On Board 8 or 16 Bit Interface

- ☐ RS-232 Interface

To fully appreciate the Modgraph GMD Display Generator, you have to see it in action. We'll arrange for a demonstration and show you the latest in high performance graphics at an unbeatable price.

# **Digital Design**

Publisher Jeffrey C. Hoopes

Managing Editor Bob Hirshon

Senior Technical Editor Dave Wilson

West Coast Bill Groves

Technical Editor (408) 371-9620

East Coast Nicolas Mokhoff

Technical Editor (212) 340-9700

New Products &

Directory Editor Martha Hawkins

Editorial Assistant Mary Rose Hanrahan

International Electronics Editor

Bon Neale

International

Computers Editor

Southwest Contributing Editor

Eric Wignall Irwin Carroll

Contributing Technical

Editor Edward Pevovar

Contributing Software

Editor William Ten Eick

Contributing Technical Editor Paul Snigier

Publication Services

Manager Charlotte King

Production Manager Jon Buchbinder

Art Director Richard D. Sarno

Assistant Art Director Tilly Berenson

Production/Graphics Mary-Jo Borkoski,

Judy Bielicki, Joan Scheffler, Vete Saulenas, Don Schaff

Promotion Manager Elaine Bull

Research Helen Obermayer

Circulation Manager Elizabeth MahonLaidlaw

Circulation Edie Almeleh, Sarah Binder, Gary Byrne, Susan Creamer

Regina Harrington, Deb Goldstein, Lynda Neue,

General Administration Karen Melanson,

Mal Rankin,

Linda Davis, Cassandra Ewing, Susan Joy Sager, Paul Christo

Group Publishing Director Albert J. Forman

# **Advertising Sales**

Northeast: John Moon (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic/Southeast: George Cominsky (212) 340-9700, Morgan-Grampian Publishing, 2 Park Avenue, New York, NY 10016

Midwest: Hank Bean (312) 346-4611, Morgan-Grampian Publishing, 2 North Riverside Plaza, Chicago, IL 60606

South Central: Jerry Ambroze (713) 780-3326, Ambroze and Associates, 2186 Augusta, Houston, TX 77057

Northwest: Jim Teller (408) 371-9620, 1901 S. Bascom, Suite 1005, Campbell, CA 95008

Southwest: Lindy Dolan (213) 981-3300, 15910 Ventura Boulevard, Suite 1215, Encino, CA 91436

Classified Manager: William L. Pryor (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

**Japan:** K. Yanagihara **(03) 350-0272,** 10-10 Shinjuka 3-chome, Shinjuku-ku, Tokyo 160, Japan Cable Address: Yanacour Tokyo.

ISSN 0147-9245

Published monthly and copyright © 1982 by Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215. Second class postage paid at Boston, MA and additional mailing offices.

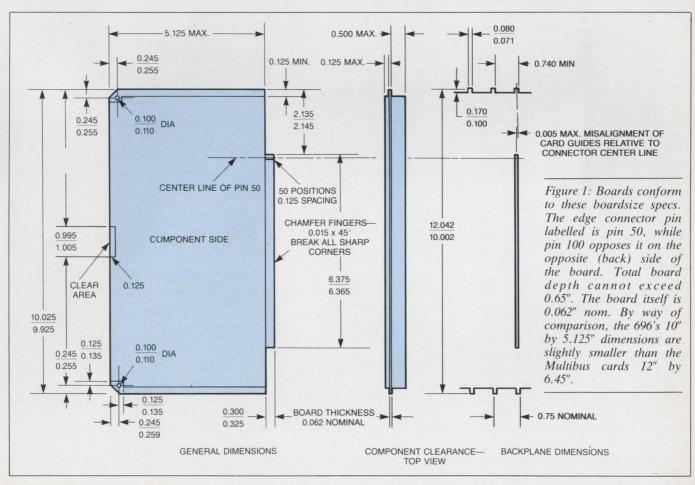

Our RIMFIRE controllers are full Bus Masters with a variety of options that make it easy to design them into any Multibus system. Their simple Parameter Block Interface offers numerous programming options such as Bus Lock, ECC and Retry Disable, Linked Commands and Mailbox Interrupts.

# CALL OR WRITE FOR COMPLETE INFORMATION

\*Multibus is a trademark of Intel Corporation © 1982 Computer Products Corporation

COMPUTER

PRODUCTS

CORPORATION

2405 Annapolis Lane

Suite 250

Plymouth, MN 55441

Phone (612) 559-2034

Write 34 on Reader Inquiry Card

MODEL 150

Write 29 on Reader Inquiry Card

# The Hecon with the Hopper.

The Hecon A0542 impact dot matrix ticket printer with hopper feed. Load up to 75 tickets in the easily accessible hopper. When you are ready to print, the A0542 automatically feeds, prints and transports the ticket for removal. You can even reinsert a ticket for additional printing thru the unique reprint feed slot.

The highly visible Time and Date feature is standard and can be printed with a single command.

The A0542 can print the 96 character ASCII set bidirectionally at 120 characters per second. The standard print head is rated at 200 Million characters minimum for long, dependable service.

It's got to be good. It's a Hecon.

Hecon Corporation, 31 Park Road, Tinton Falls, NJ 07724 • (201) 542-9200

Write 27 on Reader Inquiry Card

# HAS YOUR ADDRESS CHANGED— ARE YOU PLANNING TO MOVE IN THE NEAR FUTURE??

Please use the enclosed qualification form to notify us of your address change. A change of address requires that you fill out the entire form.

Please allow 6-8 weeks for your change to take effect.

# **Digital Design**

EDITORIAL, SALES, AND CIRCULATION OFFICES Digital Design

1050 Commonwealth Avenue Boston, MA 02215 Telephone: (617) 232-5470

#### MORGAN-GRAMPIAN

### **CORPORATE HEADQUARTERS**

Morgan-Grampian Publishing Company, 2 Park Avenue, New York, NY 10016. (212) 340-9700. Domenic A. Mucchetti, President.

### **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 2 Park Avenue, New York, NY 10016 (212) 340-9700. Robert Poggi, Director.

Morgan-Grampian publishes the following in the United States: American City & County • Circuits Manufacturing • Contractor • Design Engineering • Electronics Test • Industrial Distribution • Industrial Product Bulletin • Mart • Municipal Index.

### **New Publication Development**

H.G. Buchbinder, Director

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronic Times • What's New in Electronics • What's New in Computers.

## SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

Circulation Department

DIGITAL DESIGN

1050 Commonwealth Avenue

Boston, MA 02215

Subscription rates: non-qualified subscribers (US and Canada) — \$35/yr; foreign — surface mail — \$45; air mail — \$70. Single copies — \$4.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

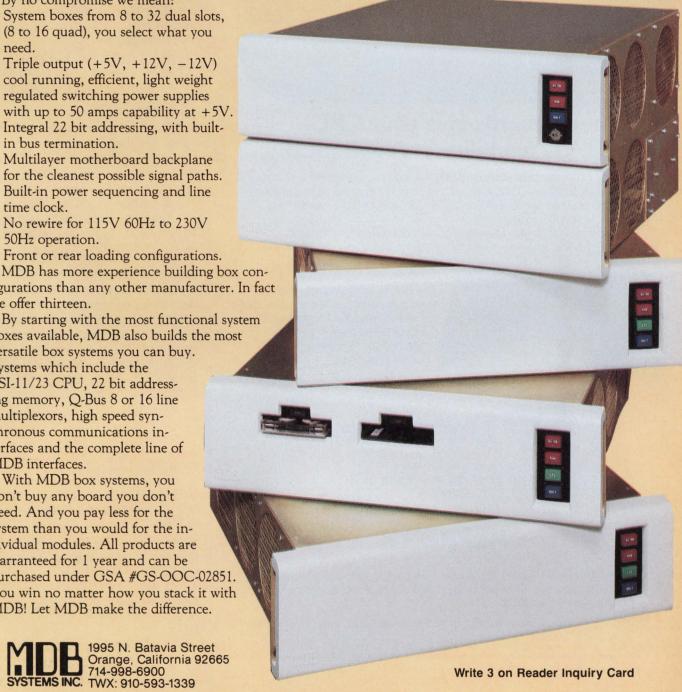

# **LSI-11 System Boxes and Box Systems**

Functionality

Versatility

Reliability

Cost Effective

# MDB makes the difference!

No compromise! You can get the LSI-11 system building blocks you need, from a system box to a box system, for fast, efficient system configuration. All with plenty of board space in the box for system applications that require specific user selected modules.

No matter what kind of system you're building, from support for battery back-up to core memory and everything in between, it doesn't pay to start with less than a no compromise enclosure.

By no compromise we mean:

• System boxes from 8 to 32 dual slots, (8 to 16 quad), you select what you

• Triple output (+5V, +12V, -12V) cool running, efficient, light weight regulated switching power supplies with up to 50 amps capability at +5V.

• Integral 22 bit addressing, with builtin bus termination.

Multilayer motherboard backplane for the cleanest possible signal paths.

• Built-in power sequencing and line time clock.

No rewire for 115V 60Hz to 230V 50Hz operation.

Front or rear loading configurations.

MDB has more experience building box configurations than any other manufacturer. In fact we offer thirteen.

boxes available, MDB also builds the most versatile box systems you can buy. Systems which include the LSI-11/23 CPU, 22 bit addressing memory, Q-Bus 8 or 16 line multiplexors, high speed synchronous communications in-

terfaces and the complete line of

MDB interfaces.

With MDB box systems, you don't buy any board you don't need. And you pay less for the system than you would for the individual modules. All products are warranteed for 1 year and can be purchased under GSA #GS-OOC-02851. You win no matter how you stack it with MDB! Let MDB make the difference.

# Datacube boards give your CPU video I/O capability...economically.

Put sight in your present system by mating your computer with our Video Graphics boards. They digitize and display information in real time from standard video cameras for MULTIBUS™ and Q-BUS™ systems... without host computer intervention.

Datacube boards provide reliable, low cost vision for robotics, inspection, medical imaging, teleconferencing, animation, etc. Available for both monochrome and color

monitors.

See how easy it is to make your computer see like a hawk. Call or write Datacube Incorporated, 4 Dearborn Road, Peabody, MA 01960, Telephone: (617) 535-6644.

Write 21 on Reader Inquiry Card

# REPRINTS

Digital Design will reprint any article from past or present issues. **Reprints** are custom printed. Minimum order: 1,000 copies. Purchase order or letter of authorization required.

Allow one month from receipt of order for delivery, unless previously arranged and confirmed.

Advertisements alone can also be reprinted. Call (617) 232-5470, and ask for **reprints.**

# Letters

# **Unpaid Overtime**

Dear Editor:

As an example of how engineers are being exploited during this recession due to the lack of a union or IEEE support, at our company (a large brewing company located in Milwaukee) all engineers are "expected" to work 4 hours on Saturdays, and if needed, on Sundays. On holidays, and even such days as Memorial Day, Independence Day, etc., a notice is sent out stating the engineering buildings will be open. This indicates all engineers are again expected to work 4 hours—all without pay!

Not satisfied with that, the Corporate Engineering Building has installed a time lock at the door, so all engineers must "clock in" and the door is "locked in" until 5PM. Engineers are expected to travel to other company plants on their own time and come home late (after 5PM)—all without pay. If you protest or do not show up on Saturdays/holidays it is construed as a "protest" and your salary increment/promotion is affected. Verbal protests have been settled by "firing."

How does one fight this situation? National publicity or a boycott is the only solution. Why don't you investigate this work situation? Salary is not all we should be fighting about! (Viewpoint 3/82)

A Brewing Co. Corporate Engineer Milwaukee, WI

# **Quite Impressed**

Dear Editor:

We just received your April issue of *Digital Design* and were quite impressed by the article written by Paul Snigier entitled, "Designer's Guide to the STD BUS." It's a very well written article and one that accurately portrays the design considerations of the STD BUS.

Mary C. McDougal Applied Micro Technology Tucson, AZ 85702

# DRAFTING SYSTEM 1

# The World's Leader in Computer Schematics and Automatic Data Base Preparation

# FREE-HAND SKETCH

"DS1" allows operator to digitize directly from a freehand sketch. Vocal Output prompts operator as IBM Microcomputer collects data. Enter a "D" size in 1 hour. NO GRIDS. EDITS are performed in minutes.

# **COMPUTER PROCESSING**

HP1000 DG Nova 4X, Eclipse, MV 8000 DEC VAX, PDP11 UNIVAC HARRIS IBM, plus others Computer straightens slanted lines, uses correct size symbols and enters alignments among symbols entered by user during input. Drum plotter or Electrostatic plotter output.

# **CONNECTION NET LISTING**

| AD123700    | GENE     | RATED | 4/19/80 A | T 3:01:00 PAGE 1 |

|-------------|----------|-------|-----------|------------------|

| BIGNAL NAME | UNIT     | PIN   | SHEET     | ZONE             |

| HETOOL      | 31       |       | 1         | Al               |

| HET OO!     | UI       | 1     | 1         | Al               |

| NET 002     | UI       | 1     | 1         | Al               |

| HET 662     | 31       | 1     | 1         | AI               |

| NET 003     | 41       | 3     | 1         | AI               |

| NET 003     | UI       | ;     | i         | Al               |

| HET 004     | UZ       | 2     | 1         | AI               |

| NET 004     | US       | 11    | 1         | Al               |

| NET 005     | uz       |       | 1         | 117              |

| NET 005     | UZ       | 13    | 1         | CI               |

| NET 005     | UII      | 13    |           | DI               |

| NETOOS      | UT       | 10    | 1         | DI               |

| NET 005     | U4 -     | 10    | 1         | CI               |

| MAD         | Už       |       | 1         | CI               |

| MAD         | UI       | •     | 1         | 81               |

| XIN         | US       | 11    | 1         | AI               |

| XIM         | UG       | 1     | 1         | W2               |

| XIN         | UB<br>UA |       | 1         | 82               |

| XIN         | U4       | 3     | 1         | 01               |

## **BILL OF MATERIALS**

|        |     | ALS FOR DRAWING |                       |

|--------|-----|-----------------|-----------------------|

| ITEM   | QTY | PART NUMBER     | DESCRIPTION           |

| 1      | 4   | 054-4000        | SN 7404N              |

| 2      | 12  | 054-002         | SN 7402N              |

| 3      | 8   | 054-6080-67     | RESISTOR 1.5K 1/2W 5% |

| •      | 2   | 079-5784-1      | ZENER DIODE 1N821 6.2 |

| REFERI |     | PART<br>NUMBER  | DESCRIPTION           |

| CR1    |     | 079-5784-1      | ZENER DIODE 1N821 6.2 |

| R1     |     | 054-6080-67     | RESISTOR 1.5K 1/2W 5% |

| U1     |     | 054-4000        | SN 7404N              |

| U2     |     | 054-002         | SN 7402N              |

"DS1" automatically provides Net and Bill Lists directly from data base of digitized schematic.

# P.C.B. ROUTER INTERFACES

ASI-PRANCE

AUTOMATE '80

COMPUTERVISION

REDAC

SCICARDS™

others available

"DS1" interfaces to P.C.B. Routers, Wire Wrap, Simulation and Test Programs.

# **UPDATED SCHEMATIC**

"DS1" performs Back-Annotation from a "Was-To" list derived from the P.C. Router. "Back-Annotation" automatically updates the schematic to agree with the circuit board component placement.

Write 7 on Reader Inquiry Card

# DESIGN AIDS inc.

27822 El Lazo Road, Laguna Niguel, California 92677 • (714) 831-5611

## September 29-October 2

COMMON Fall '82 Conference. Biltmore Hotel, Los Angeles, CA. An IBM Computer users' group features user and IBM speakers. Contact: David G. Lister, COMMON-F82, 435 N. Michigan Ave., Suite 1717, Chicago, IL 60611; (312) 644-0828.

### September 30-October 2

Phoenix Computer Expo. Phoenix Civic Plaza, Phoenix, AZ. Contact: Carol Houts, Judco Computer Expos, 2629 N. Scottsdale Rd., Scottsdale, AZ 85252; (800) 528-2355, (602) 990-1715 in Arizona.

## October 1

"Computer Animation." Essex House, New York, NY. Features presentations by six of the leading computer animation houses. Contact: Perry Jeffe, Pratt Center, 505 White Plains Rd., Tarrytown, NY 10591; (914) 631-8772.

## October 4-6

Convergence '82. International Congress on Transportation Electronics. Hyatt Regency, Dearborn, MI. Contact: M.J. Asensio, SAE, 3001 W. Big Beaver Rd., Suite 602, Troy, MI 48084; (313) 649-0402.

### October 4-6

VLSI and Software Engineering Workshop. Port Chester, NY. Contact: J.A. Rader, 7372 W. 83rd St., Los Angeles, CA 90045.

### October 4-8

AdaTec Tutorial and Conference on Ada. Arlington, Va. (Tutorial: Oct. 4–5; Conference: Oct. 6–8) Contact: Anthony Gargaro, Computer Sciences Corp., 304 West Route 38, Moorestown, NJ 08057; (609) 234-1100, ext. 2280.

## October 5-8

Microprocessor Troubleshooting Course. Boston, MA. A four-day course provides participants with the opportunity to learn practical troubleshooting techniques. \$895. Contact: Ruth Dordick, Integrated Computer Systems, 3304 Pico Blvd., PO Box 5339, Santa Monica, CA 90405; (213) 450-2060.

### October 5-7

MICRO 15. The 15th Annual Workshop on Microprogramming. Palo Alto, CA. Contact: Will Tracz, IBM-FSD, 101BM44, Owego, NY 13827.

### October 6-8

20th Annual Allerton Conference on Communication Control, and Computing. Monticello, IL. Contact: Prof. H.V. Poor, Coordinated Science Lab, University of Illinois at Urbana-Champaign, 1101 West Springfield Ave., Urbana, IL 61801.

## October 7, 13, 19

Invitational Computer Conference. Amsterdam, Oct. 7; Milan, Oct. 13; Munich, Oct. 19. These one-day shows of operating equipment displays and technical seminars are designed to reach OEMs, system houses and quantity end users. Contact: Susan Fitzgerald, B. J. Johnson & Associates, Inc., 3151 Airway Ave, #C2, Costa Mesa, CA 92626; (714) 957-0171.

### October 11-13

Seventh Conference on Local Computer Networks. Minneapolis, MN. (Tutorials: Oct. 11; Conference: Oct. 12–13.) Contact: Harvey A. Freeman, Architecture Technology Corp., PO Box 24344, Minneapolis, MN 55424.

### October 11-14

**INFO '82.** New York Coliseum, New York, NY. Information Management Exposition and Conference. Contact: Clapp and Poliak, Inc., 708 Third Ave., New York, NY 10164; (212) 661-8010.

### October 11-15

Computer Communications Systems and Networks. George Washington University, Washington, DC. Intensive program devoted to the state of the art of modern data communications systems. Course No. 596DC. Contact: Computer Engineering Education, George Washington University, Washington, DC 20052; (800) 424-9773.

## October 12

**NECOM '82.** Boston Marriott Hotel, Newton, MA. A single source computer show for OEMs, sophisticated end users, dealers and distributors. 1-7PM. Contact: Norm DeNardi Enterprises, 289 S. San Antonio Rd., Suite 204, Los Altos, CA 94022; (415) 941-8440.

### October 14-15

Man Machine Interface. Columbia Inn, Columbia, MD, and November 4–5, Hyatt Regency, Austin, TX. Contact: Continuing Education Institute, Oliver's Carriage House, 5410 Leaf Trader Way, Columbia, MD 21044; (301) 596-0111.

## October 17-20

**International Telecommunications Forum 1982.** Marriott Waterfront Hotel, Boston, MA. "The Changing Basis of Competition in the '80s." Sponsored by Arthur D. Little, Inc. Contact: Patricia K. Finnegan, Arthur D. Little, 25 Acorn Park, Cambridge, MA 02140; (617) 864-5770.

### October 17-20

MILCOM '82. IEEE Military Communications Conference. Stouffer's Bedford Glen, Bedford, MA. Contact: MILCOM '82, PO Box 208, Bedford, MA 01730; (617) 271-2809.

### October 18-22

**Third International Conference on Distributed Computing.** Ft. Lauderdale, FL. Contact: Distributed Computing, Box 639, Silver Spring, MD 20901; (301) 589-3386.

### October 19-20

**1982 International Display Research Conference.** Cherry Hill, New Jersey. Contact: Thomas Henion, Palisades Institute, 201 Varick St., New York, NY 10014; (212) 620-3384.

### October 19-22

Sixth International Conference on Pattern Recognition. Munich, Germany. Contact: Prof. Dr. H. Marko, Lehrstuhl für Nachrichtentechnik, der Technischen Universität München, 8000 München, Federal Republic of Germany.

#### October 25-28

First Annual Workshop on Interative Computing: CAD/CAM: Electrical Engineering Education. Charlottesville, VA. Contact: Dr. Harlan Mills, IBM-FSD, 6600 Rockledge Dr., Bethesda, MD 20034; (301) 493-1495.

## October 26-28

CAM-I 11th Annual Meeting and Fall Technical Conference. Reno, NV. "Beyond CAD/CAM — Extending the Limits" will focus on both immediate and long range user needs as well as the latest advances in computer aided design and manufacturing (CAD/CAM) technology. Contact: Rhonda Gerganess, CAM-I Conferences, 611 Ryan Plaza Dr., Suite 1107, Arlington, TX 76011; (817) 860-1654.

## October 26-27

The Ottawa High Technology Show. Civic Center, Lansdowne Park, Ottawa, Ontario, Canada. Contact: Ron Connelly, Show Manager, 2487 Kaladar Avenue, Suite 107, Ottawa, Ontario, Canada, K1V 8B9; (613) 731-9850.

### October 26-28

Fifth IEEE Symposium on Mass Storage Systems. Boulder, CO. Contact: Bernard T. O'Lear or Karen Friedman, National Center for Atmospheric Research, PO Box 3000, Boulder CO 80307; (303) 494-5151, ext. 293 or 387.

## October 28-31

Mid-Atlantic Computer Show. Armory/ Starplex, Washington, DC. Contact: Computer Expositions, Inc., PO Box 3315, Annapolis, MD 21403; (301) 263-8044.

# October 30-November 2

Sixth Annual Symposium on Computer Applications in Medical Care. Washington, DC. Contact: Bruce Blum, Symposium Program Chairman, Johns Hopkins University, Traylor 514, Baltimore, MD 21205; (301) 955-8375.

# HOLD MEMORY COSTS CHECK.

Ever feel rooked by memory prices? Well, you can play the game for less if you make the move to Plessey.

We've just converted our entire memory production to CAD/CAM. That means greater capability, even more consistent quality, and something else—low price.

In fact, when you buy Plessey memories, you get the first one at the 100-unit price. Like a PDP-11/44 1 Mbyte ECC for \$2580. Or an LSI-11 SV128 256 Kbyte for \$630. Or even a VAX \$730 1 Mbyte only \$2665.

The savings are the same on all our boards. Core and MOS. 16 Kbytes to 1.0 Mbytes. With Omnibus, Unibus, Q-bus, MJ11, SJ-780, or NOVA bus chassis compatibility.

In fully populated and depopulated versions. Plus, every Plessey memory comes with a free 1-year warranty. And if we install your memory for you, you also get free on-site repair for 30 days.

But chances are you'll never have any problems. Because we inspect and test every memory we make.

So if you want to hold your memory costs in check, mate your system with Plessey. It's the only move you need to remember.

# Plessey Peripheral Systems

1691 Browning Avenue, Irvine, CA 92714 (714) 557-9811/(800) 854-3581 (Outside CA)

Prices are applicable in U.S. only. rademarks of Digital Equipment Corporation. NOVA is a registered trademark of Data General Corporation.

Write 12 on Reader Inquiry Card

# TAL DESIGNATE OF THE PROPERTY OF THE PROPERTY

# Digital Research Develops NS16000 SW

Digital Research will develop and market a multi-tasking version of its CP/M operating system for National Semiconductor's NS16016 16/32-bit  $\mu P.$  The NS16016 was selected by Digital Research because it supports the industry standard 8080 instruction set. The NS16016 runs 8080 instructions more than four times faster than the currently available 8080 8-bit  $\mu P.$

# **AMD Announces Latches**

AMD has announced availability of six new members of its Am29800 Family of High-Performance Bus Interface devices. The new products, designated Am29841 through Am29846, are 8-, 9- and 10-bit parallel latches. Designed to eliminate the extra packages required to buffer existing latches and to provide extra data width for wider address/data paths or buses carrying parity, the 24-pin, 0.3-inch space-saving devices feature fully TTL-compatible inputs and outputs. All of the bipolar Am29800 latches are manufactured using AMD's proprietary IMOX ionimplanted oxide-isolated fabrication process.

# **Forward Technology Adopts Standard**

Forward Technology, Santa Clara, CA has announced that it has adopted the standard two-dimensional software graphics package proposed by the Association of Computing Machinery's Siggraph group for its Forward Gateway Workstation. The specific implementation of the standard package was developed by Graphic Software Systems, Wilsonville, OR. It operates under the Xenix operating system used by the Gateway Workstation.

## Rockwell/Seeq Agreement

The Electronic Devices Division of Rockwell International has signed a license agreement with Seeq Technology, San Jose, CA, under which the Division will obtain Seeq process technology and product design. It is also contemplated, Rockwell said, that the Division will be a second source for the Seeq 16K electrically erasable read-only memory (E<sup>2</sup>ROM, Part #5213) and the 64K ultraviolet-erasable programmable read-only memory (UV EPROM, Part #5133). The

D5213 has 5V programmability, a worldwide first in the semiconductor industry.

# **Graphics Standards**

Digital Equipment, Intel and Tektronix, have announced their adoption and joint support of two emerging graphics standards. The companies plan to incorporate the standards into their future products. The first is the North American Presentation Level Protocol Syntax (NAPLPS), developed by the Canadian Dept. of Communication. The Virtual Device Interface (VDI), the second proposed standard, is being developed by the ANSI Technical Committee X3H3, Computer Graphics Programming Languages.

# **Streaming Tape Standards Group**

Four manufacturers of ½" cartridge tape drives have formed an international group to promote widespread use of such drives by encouraging standards that will lead to industry-wide compatibility. Any other maker of ½" drives that wishes to become a member is welcome to join. Initial members of the Group are Archive, Costa Mesa, CA, Cipher Data Products, San Diego, CA, Data Electronics, San Diego, CA and Tandberg Data A/S Oslo, Norway.

## **Array Processors**

Perkin-Elmer and CSPI, have entered into a joint development agreement for operating 32-bit and 64-bit array processors with Perkin-Elmer's Series 3200 computer systems via a shared memory interface. The development effort is directed at the seismic and scientific calculation markets where Perkin-Elmer will be able to address computationally intensive requirements at a 10-100 times speed improvement.

## Zilog Samples Virtual Memory μP

Now available in sample quantities the Z8003 and Z8004 Virtual Memory Processor Units from Zilog are 16-bit MOS  $\mu$ Ps offering all the features of Z8001/2 CPUs, plus integral provisions for operation in a virtual-memory environment. The VMPUs operate at clock rates of up to 10 MHz and are fully binary-, function- and pin-compatible with the Z8001/2.

# IK Complex FFT in 0.5 msec and faster...

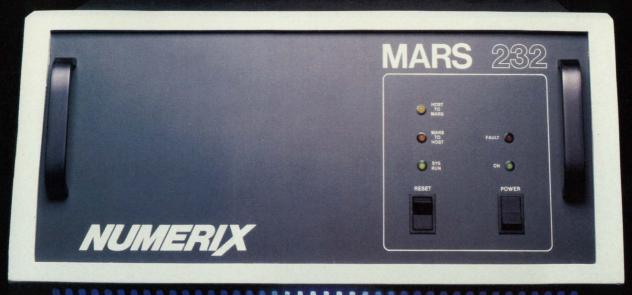

# MARS-232 Array Processors Support the User

who needs:

# Signal Processing

with programmable high-speed arithmetic, logical, and decisionoriented operations for real-time applications.

# **Data Acquisition**

directly into the processor at sample rates up to 20 MHz via a prioritized multi-port bus structure.

# Standard I/O Interfaces

using 32-bit digital I/O, A/D and D/A modules with speeds up to 5 MHz, all with software support for ease of integration.

## **Architectural Modularity**

to configure ultra-high performance multi-processor systems reaching to 300 million arithmetic operations per second and beyond.

# **OEM Capabilities**

where, as a development system, the MARS-232 supports low-cost ROM-based MARS-132's or customized user-defined VLSI implementations.

# MARS-232 Array Processor Features Include:

- ■1K Complex FFT Performance 1.05-msec Single Data Processor 0.5-msec Dual Data Processor

- 100-ns Clock

- DMA Transfers at I/O Bus Rates of 20 Mbytes/second

- Modularized 16- or 32-bit Arithmetic Units

- Multiple Processor Configurations for Application Flexibility

- Low-cost OEM Configurations

- Full Software Support at Systems/ Utilities/Applications Levels

# NUMERIX

# MARS-232 Array Processor Software

Ih today's world it is not enough to have outstanding hardware. Our interactive software system, GSP, allows hands-on assembly/disassembly, loading, debugging, and diagnostic services – with multiple processor support built-in. For the real-time environment, we use ESP, a host-resident executive. It provides intelligent supervision for host programs that call applications library or user-defined subroutines, without compromising the speed of MARS.

# **MARS-232 Applications**

With its high computational capacity and low cost, the MARS family provides solutions for a broad range of application areas—on-line video inspection and image analysis; front-end data acquisition, compression, and formatting; spectral analysis, filtering and thresholding.

**MARS.** a new world of performance for medical, seismic, radar, sonar, and communications systems.

For additional information on the MARS Family of High Speed Array Processors, write or call: Numerix Corp., 320 Needham Street, Newton, MA 02161 Tel. 617-964-2500

# **Eaton** printer power

Works fast and economically wherever hard copy is neededindustrial, commercial, consumer.

Eaton's line of alphanumeric dot matrix impact printers give you printer power plus. You get performance, exclusive product features, attractive prices—all designed and backed by Eaton—one of the great names in American industry.

Eaton printers feature a 100 million character life printhead,

easy interfacing and a simple, low maintenance design.

We'll assist in the design of the interface for your equipment and if you require a modified or custom printer unit, our engineers will be happy to work with you.

For additional technical information call or write: Eaton Corporation, Printer Products Operation, Riverton, Wyoming 82501. Phone: 307/856-4821.

#### Model 420/421

Split paper feed printer. For receipt/audit applications. Prints two 18 character columns. Printheads available to match paper and printing speed/density requirements

### Model M-400

Model M-400

Document printer. Prints bidirectionally up to 3 lines per second. Handles single and multi-ply tickets and forms. Speed 3 lps bidirectionally. Has a quiet, dependable stepper motor diven page radyance. driven paper advance mechanism.

### Model 410/411

Single roll printer. For single or multi-ply paper. Prints a 31/3" line up to 40 columns. Three printhead types available for various document thickness and dependable print quality

## **Printheads**

Choose from 3 printhead models for integration with your own equipment. All with a minimum of 100 million characters and lifetime, low maintenance reliability. Short, medium, and long stroke models Available in either 40 or 24 VDC

Write 11 on Reader Inquiry Card

Designed for commercial and industrial needs. Simple design, no special paper needed. Attractive case, 40 or 64 character

W-18-94 10000

Printer Products

# **News Update**

S DIGITAL

DIGITAL

23 DIGITAL

DIGITAL

DIGITAL

DIGITAL

# Arcnet To Be Sold On Open Market

Datapoint Corporation, San Antonio, TX, has signed an agreement under which Standard Microsystems Corp, Hauppauge, NY was granted a non-exclusive license to market Datapoint's Arcnet transceiver chip. Together with Datapoint's RIM (Resource Interface Module) chip, Arcnet provides the electronics necessary for Arcnet interfacing.

# **Archive Streaming Tape For Plexus**

Archive Corporation, Costa Mesa, CA, has been awarded a \$1 million contract from Plexus Computers, Santa Clara. Plexus will incorporate the 20 Mbyte Intelligent Sidewinder ½" streaming cartridge tape drives into their P/25 minicomputers. The Sidewinder will back up 8" Winchester disk drives with 22, 36, or 72 Mbytes of formatted capacity.

# iAPX 286 Development Packages

The first software development and high level language packages for the iAPX 286 microsystem were announced by Intel Corp of Santa Clara. The new packages provide the first system and application design tools geared to the 286.

A price cut of over 50% was recently effected for the Intel 8087 numeric processor device for the iAPX-86 and iAPX-88 systems. Volume pricing is projected to drop further by half in 1983.

# **Rockwell Relocates Electronic Devices**

The Electronic Devices Division of Rockwell Int. will relocate its headquarters from Anaheim to Newport Beach, CA, in an attempt to reduce facility costs and improve interdepartmental communication.

# EXATRON'S RS-232C STRINGY/FLOPPY MASS STORAGE SYSTEM.

# Mini-disk speed, capacity and reliability for only \$399.50.

- Standard RS-232C communications link

- Built-in operating system

- Two file management structures: ASCII and binary

- Three baud rates available: 300, 1200 and 9600

- Busy/ready handshaking supported

Call our HOTLINE . . . (800)-538-8559 In California, Call (408)-737-7111

Exatron, inc. 181 Commercial Street Sunnyvale, California 94086 (408)-737-7111

Write 35 on Reader Inquiry Card

# BUY DIRECT AND SAVE A BUNDLE!

# NEWI

Model 770 12" Monitor Housing with 5½" dual floppy disc drives

\$9554

Yearly orders of 5000 or more reduce the unit price to \$49.48! Choose from two keyboard sizes. \$19.29 and \$22.50

This handsome enclosure is molded by Hettinga's advanced stress-free TCM process that vastly improves on traditional structural foam molding. Combining beauty, function and durability, this housing has the most competitive price on the market.

Easy to build into, its exceptional sturdiness permits the monitor to be mounted directly to the bezel bosses and eliminates the cost of the wire frame. Standard inserts are molded in

- Meets all foreign and domestic standards

- EMI/RFI shielding available

- Made from UL VO 94-95 approved rating molding materials

- · Any size order welcome

- 24-hour shipment on stock items

- We do molding, shielding and painting in our plant

- Other sizes available, ask for our brochure

# HETTINGA, INC.

8000 University Avenue Des Moines, Iowa 50311 Telephone 515/224-1114 Telex 478315

Write 37 on Reader Inquiry Card

# High-Growth Of Surface Mounted Packages Forecast

The completion of a year-long study on electronic packaging has been announced by Integrated Circuit Engineering, Scottsdale, AZ. Entitled, "Electronic Packaging Strategies for the 80s," the major study encompasses seven volumes and represents distillation of technology gathered from Europe and Japan as well as the US.

ICE forecasts high growth of surface-mounted packages and makes a strong case for leaded, rather than leadless, chip carriers. The quad version of the cerdip (that ICE calls a "cerpack") could be a winning approach for hermetic packages that must mount on organic printed circuit boards—which ICE sees around for many years, yet. For non-hermetic packages, ICE sees the post-molded plastic quad pack as

the replacement for the plastic dual-in-line package (DIP), and the quad structure lends itself to future assembly automation.

With the price of metallized tape falling and I/O densities rising, ICE sees that automated bonding (TAB) will attain significant growth, after languishing as a niche technology for a number of years. For IC I/O counts between 100 and 300, ICE sees TAB-like connection pads in the active area of IC chips, as opposed to being constrained to the periphery of the die.

For very high pin counts, however, ICE sees the "flip-chip" approach championed by IBM as the best way. ICE feels that improved substrate material and advances in wafer processing will allow this controlled-collapse solder bonding technique to accommodate up to 1,000 interconnects per chip.

The study predicts return of US-owned offshore package assembly as overseas wages rise and the value of individual components increase drastically. Computer modeling was used to determine life cycle costs of a number of typical device/package configurations to review impact on packaging. In-process inventory and process control will become more critical than the hourly labor rate by the end of the decade. Cost per interconnect will be reduced by a factor of four over the decade, and good cost payoffs are seen for multilayer polyimide substrates, new hermetic approaches, TAB chips directly on substrates and automatic die bonding.

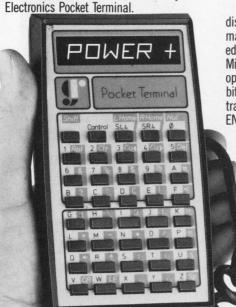

# Stackable Module Houses 16K-Byte Static CMOS RAMs

National Semiconductor has introduced a 16 Kbyte static CMOS RAM module, which includes decoding logic and decoupling capacitors, that not only requires only one-fourth the circuit board space of conventionally-packaged devices, but can also be stacked eight times to add memory up to 128 Kbytes.

The "stackability" feature of

Figure 1: National Semiconductor's 16 Kbyte static CMOS RAM module includes decoding logic and decoupling capacitors, requiring only a quarter of the circuit board space used by existing devices.

the MA2016 module, which enables increased packing densities, provides for vertical interconnection of up to eight modules to obtain a total memory capacity of 128 Kbytes. The module is also designed for horizontal "stacking" but requires suitable circuit board interconnection of the module.

The MA2016 stackable module was designed using a space-saving technology developed to reduce the number of parts required in the manufacture of calculators and handheld game modules. As the result of the substantial savings in board space, the MA2016 is suited for use in handheld computer terminals, handheld instrumentation, portable computer systems, telegraphics and telecommunications.

The MA2016 stackable module contains eight 6116 16 Kbyte RAMs, a high-speed P<sup>2</sup>CMOS decoder, several fast CMOS gates, and two power-supply de-

coupling capacitors.

The complete module measures only 1.6" by 2.5" and is 0.35" high—about twice the width and the same length as a standard 40-pin DIP. The package has 40 pins on the bottom with the leads spaced 1.3 inches apart to facilitate mounting directly onto a printed-circuit board. Sockets on the top enable additional modules to be easily plugged in.

The memory of each module is structured as a 16 Kbyte by 8-bit block with an access time of only 250ns. Two jumpers located in a notch in the side of the module determine the address range of the 16 Kbyte block.

The module requires low power for operation—only 40mW—obtained from a single supply voltage of only 5V. Data can be retained at voltages as low as 2V. All inputs and outputs are TTL-compatible. Evaluation units of the MA2016 are available for \$250 each.

Yesterday's ideas might not be good enough for today or tomorrow, and selecting the proper data display has never been more significant. Recent studies in the computer marketplace indicate the CRT display has become the single-most important element in today's computer systems. An easy-to-read, jitter-free display is of course a dynamic part of this critical man/machine interface.

If you want to look at things with a fresh point of view, an eye-pleasing Audiotronics data display can help insure maximum productivity for the end user.

With our full line of data products, in 5", 7", 9", 12" and 15", there is a good chance that we

have already solved your problems. We have developed and engineered data display products to satisfy almost every need for today's applications. Because we know what works and what doesn't, our expertise can be put to good use in developing your needs for today and tomorrow, with performance and quality that meet your budget objectives.

7428 Bellaire Avenue North Hollywood. California 91605 (213) 765-2645

Write 25 on Reader Inquiry Card

# Hiring Specialized Engineers

# Career Opportunities in

# **Digital Design**

# Readership:

Over 62,000 + qualified engineers and managers at 18,000 + important design locations.

### **Editorial**:

Look for a new column on employment trends to accompany recruitment advertising.

# Rates:

\$85 per column inch 3 column x 10" page — \$2500 (1x B&W)

Contact: Bill Pryor, Manager, Recruitment & Classified Advertising, Morgan-Grampian Publishing Co., 1050 Commonwealth Ave. Boston, MA 02215 (617) 232-5470.

# **Technology Trends**

# High Capacity 51/4" Winchester Offers 30ms Access Speed

The first products of a family of 51/4" Winchester disk drives that can store up to 46.3 Mbytes of data and can be accessed in 30ms was introduced at this year's Comdex Spring show, held in Atlantic City, NJ. These high-capacity and fast access speed hard disk drives compare favorably in capacity to current 51/4" disks on the market but also perform at speeds usually found in the larger 8" disks.

The breakthrough is attributed to the combination of drive technology and the type of heads used by Atasi engineers, according to the San Jose, CA company's president, Frank C. Gibeau. "The combination of high capacity and fast access is vital for multi-user, multi-tasking μC systems," says Mr. Gibeau. While 5¼" hard disk manufacturers have pushed the available capacity on their products they have generally not met the need for fast access time.

The drive is a closed-loop servo with a linear actuator and Winchester-type ferrite read/write heads. The units are interchangeable with standard 5½" floppy disk drives and can be mounted vertically and horizontally. Three initial members of the family are the 3020, 3033, and 3046—a 19.84 Mbyte, 33.07 Mbyte and 46.3 Mbyte-capacity units respectively.

Atasi's president says that the products are the first in the industry to use a closed-loop servo system with a linear voice coil positioner in the 51/4" package. Precise positioning is ensured through the ball bearing supported carriage. The bottom surface of the lowest disk contains the continuous servo code that is usually only found in the higher-priced 14" disks. Up to 4 disks may be loaded. The μC servo control provides self-test during the power-up sequence and access control during the track seeking mode. The servo system controls to within  $\pm 1\%$

Figure 1: Model 3033 is a 51/4" Winchester disk drive that offers 33M bytes and 30 ms access time.

the speed of the eight-pole dc brushless spindle motor.

The recording media consists of a lubricated thin magnetic oxide coating on a 130-mm diameter aluminum substrate and the recording heads are composed of manganese zinc ferrite sliders.

So sure are Atasi engineers of their products' ruggedness that the company does not require the user to conduct preventive maintenance.

In quantities of 1000 the 3033 and 3020 units are priced at \$1800 and \$1470, respectively. Production is scheduled to start in September while the 3046 will premier in the fourth quarter this year and production will start in the first quarter of 1983. Price will be determined at introduction.

Atasi, which was formed in 1981, is making its task to provide the OEM market with 5½" disk drives that will be price/performance competitive with their larger 8- and 14-in. counterparts. Two primary market segments will be served: the small business computer and local area network markets. Gibeau has assembled so far six individuals who together comprise 112 years of combined head, disk media, and drive manufacturing experience to meet that task—Nicolas Mokhoff

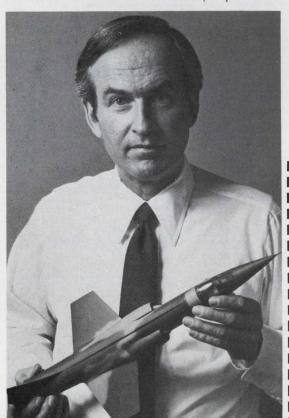

# TEST-FLY A \$20 MILLION JET ON AN APPLE? YES. WITH MICROSPEED.

At the Bethesda Naval Research Center, they've discovered the power of MicroSPEED. The Navy's engineers use this remarkable hardware/software combination to "fly" an advanced fighter aircraft in *real time*—even making vertical landings on a simulated carrier deck. A "crash" is merely another learning experience, and an opportunity to modify the research aircraft—inside the Apple—to improve tomorrow's combat planes.

Surprised that such a sophisticated task is possible on the Apple? So were the Navy's officials, and many others who have discovered...

**THE MICROSPEED DIFFERENCE** This extraordinary Language System exploits the real potential of the microcomputer for the first time. The difference between MicroSPEED and other programming languages is that with MicroSPEED, there is virtually *no limit* to what you can achieve. It may well be the ultimate language for the Apple II and III (and soon the IBM Personal Computer). MicroSPEED literally combines the performance of a *minicomputer* with an exhaustive set of user-friendly capabilities: hard-

ware math processing, fast hi-res graphics and text, turtle graphics, print formating, two text editors, unlimited data types, and incredible FORTH extensibility—all at speeds up to 100 times faster than Basic.

**USER-FRIENDLY, EASY-TO-LEARN** Starting with simple commands that are comfortable even for non-programmers, MicroSPEED extends and builds, allowing you to create your own tailored application languages. The capability of your computer will grow exponentially, as you work in an active partnership with the machine, exploring and developing new problem-solving facilities—creating, correcting, refining your increasingly powerful system.

by a team of standout computer professionals, MicroSPEED has been put to the test in fields as diverse as medicine, the stock market, oceanography, and the arts. In even the most challenging applications, MicroSPEED users have been unanimous in their praise of the System and manual. Typical comments are:

"Very bigh marks,"

Thomas Tosch Phd., Tosch Information Management.

"The more I use MicroSPEED, the more I love it," James L. Hockenhull, University of Washington.

"Great!...A joy to use,"

Henry Harris, Mission Designer, Cal Tech's Jet Propulsion Lab.

"If you plan to use the Apple or IBM Personal Computer for <u>any</u> demanding task, then we built MicroSPEED for <u>you</u>,"

Sam Cottrell, President of Applied Analytics

| in Courcii, i resident of Applied Analytics.                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| licroSPEED requires the Apple or IBM Personal Computer with single isk. MicroSPEED II includes 2 MHz math processor. MicroSPEED II + acludes 4 MHz math processor. |

| pplied Analytics Incorporated<br>910 Brookridge Drive<br>pper Marlboro, Maryland 20772 (301) 627-6650                                                              |

| m interested! My computer is:lease send me:MicroSPEED II, \$495.00160 Page Manual, \$15.00Detailed Information                                                     |

| ame:                                                                                                                                                               |

| ompany                                                                                                                                                             |

| ddress                                                                                                                                                             |

| ityStateZipPhone No.( )                                                                                                                                            |

| se this coupon to order, or for more information.                                                                                                                  |

| MicroSPEED #SPEED                                                                                                                                                  |

September 29, 30 and October 1, 1982 • Anaheim Convention Center • Anaheim, California

Sponsored by: Mini-Micro Systems magazine

# If you are an OEM, Systems Integrator, Dealer, Distributor or Multi-quantity End-User, here's a unique opportunity to examine, evaluate, compare and select equipment and products such as:

- Tape and disk drives

- Hardcopy terminals

- Computer graphics

- Software

- CRT terminals

- Add-on/Add-in memories

- Controllers and interfaces

- Data communications equipment

# ....from leading manufacturers and suppliers as:

Advanced Electronic Design, Inc. American Computer Hardware Corp. Amlyn Corporation AMPEX Memory Products Division Anadex, Inc. Applied Circuit Technology Applied Data Communications Archive Corporation ATASI Corporation Aviv Corporation Burr Brown Business Computer Systems Magazine Cahners Publishing Computer Business News Computerworld CW Communications Cameo Electronics, Inc. Century Data Systems A Xerox Company Cipher Data Products, Inc. Computer Products Custom Systems, Inc. Cynthia Peripheral Corporation Computer Equipment

Services

Data Flectronics, Inc. Data Peripherals

Dataram Corporation Data Technology Datum, Inc Decision Data Computer Corp. DI-AN Controls, Inc. Distributed Logic Corporation (Dilog)

Dylon Corporation Dataproducts, Corp.

Digital Design

Morgan Grampian

Publications **Emulex Corporation** Envision Falco Data Products Fujitsu America, Inc. G. R. Electronics Gryphon Systems of C. J. Wigglesworth Software Innovative Concepts Interlan International Memories, Inc.

Interphase Corporation Irwin International, Inc. C. Itoh Electronics Liberty Electronics U.S.A. MDB Systems

Mega Tape Corporation

Megavault, an SLI Company

Met One, Inc.

Micro Peripheral, Inc.

Micropolis Corporation

Microscience International Corporation Mini Micro Systems Magazine Cahners Publishing Miniscribe Corporation 3M Company Data Recording Products Moya Corporation NCR Corporation OEM Marketing Division NEC Information Systems Northern California Electronic News Southern California Electronic News Bender Publications Priam Corporation

Printek, Inc. Printronix, Incorporated Quantum Corporation Oubex Associates Quentin Research Oume Rodime Ltd. Rotating Memory Systems, Inc. Seagate Technology Selanar Corporation Shape Magnetronics Siemens Corporation Sigma Sales Spectra Logic Syquest Technology TAB Products Company Electronic Office Products Div. Tandon TEAC Corporation of America Trilog, Inc. Universal Data Systems Wespercorp

Western Peripherals Div.

Western Digital Corporation

Westrex OEM **Xylogics**

the latest developments in peripherals technology, as well iscover... as trends for the future, through an applications-oriented Technical Program. You'll learn from experts who will be on hand to share their ideas and expertise, and answer your questions.

Peripherals '82 is your best opportunity to survey the latest equipment and technology from the industry's leaders! Put PERIPHERALS '82 on your calendar today!

### Organized by:

Cahners Exposition Group Cahners Plaza 1350 E. Touhy Ave. P.O. Box 5060 Des Plaines, Illinois 60018 (312) 299-9311 telex 82882 CEG/CHGO

# Floppies To Pass The \$1 Billion Level In '84

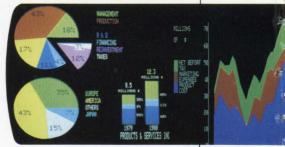

Very rapid increases in the use of 51/4" and 8" floppy disks, together with an upsurge in the new 31/2" size, will push shipments of floppy disk media past the \$1 billion mark by 1984, according to a new report from International Resource Development Inc. Flexible disk media (which recently overtook traditional hard disks in terms of media shipments) will lead the storage media market throughout the 1980's. Although optical disks will become commercially available in 1984, the principal applications will be in very large memory systems, leaving most of the memory market to magnetic media. By 1990 only about 9% of the media market will be for optical media, compared to almost 50% for floppies and 30% for Winchester media. (Figure 1)

# **Venture Capital**

According to the report there will be a new round of opportunities for innovative start-up firms, paralleling the success in the 1970's of such firms as Verbatim, Maxell and Dysan. "Drexler Technology looks like the leader today in the optical disk media market," said International Resource Development's Ken Bosomworth, who cautions industrywatchers to note, however, that Drexler's main sales to date have been of evaluation kits to optical drive manufacturers. Bosomworth sees BASF, 3M and DuPont as all being threatened in the magnetic media field by ultra-thin metal coatings, deposited on new types of substrate materials by sputtering techniques. "It may turn out to be a horserace between the Japanese manufacturers—particularly Sony-and a new set of Silicon Valley startups," suggests Bosomworth.

IBM, which pioneered the flexible disk concept and was the leading supplier of floppy drives and media for many years, has been pushed out of first place in the floppy media market by Ver-

|            | Optical V<br>(Percenta | ersus Magneti<br>ge By Shipme | c Media<br>nt Value |       |

|------------|------------------------|-------------------------------|---------------------|-------|

|            |                        | 1982                          | 1985                | 1990  |

| Floppy     |                        | 51.3                          | 52.8                | 46.9  |

| Winchester |                        | 8.4                           | 16.7                | 28.7  |

| Hard Pack  |                        | 40.3                          | 27.3                | 14.9  |

| Optical    |                        |                               | 3.3                 | 9.4   |

|            | TOTAL                  | 100.0                         | 100.0               | 100.0 |

Figure 1: By 1990 only about 9% of the media market will be for optical media, compared to almost 50% for floppies and 30% for Winchester media.

batim. Verbatim and other vendors frequently manufacture floppies on a "private label" basis to be sold by mail order companies, office supply stores, etc.

# **Computer Stores**

In an analysis of distribution channels for floppy media, IRD concluded that computer stores had now pulled ahead of other types of distribution channels (including mail order computer products vendors, office supply stores and hardware manufacturers). The trend is expected to continue, both because of attractive pricing (some computer stores use floppy disks as "loss leaders" to attract traffic) and because of the convenience factorwhen a user runs out of floppies. he tends to not want to wait one or two weeks for a new supply. \*

# 31/2" Disks

With the expected introduction this year of 3½" floppy disk drives from several manufacturers, a new market will open up for 3½" floppy disk media. According to the IRD report, Sony, Hitachi and Maxell are already gearing up to supply this market with media. IRD analysts expect Verbatim and 3M to follow quickly.

# **Optical Disk Media**

In analyzing the state of the art in optical disk technology, researchers are looking at several different materials for the substrate and the recording layers. Recording material might be metal and polymer

compositions, vesicular films, bilayers or infrared-absorbing organic materials. Metals considered for the recording layer include tellurium, silver, gold, platinum, selenium and bismuth. Other possibilities are absorbing organic materials such as cross linked gelatin, by Drexler; homogeneous grain free films, by Kodak; and metal composite films in polymerized plasma, by Nippon Telephone and Telegraph.

Substrate materials are also very important. Possible materials include aluminum, glass, polycarbonates and microtextured-Teflon based polymer materials. The latter enhances the heating effect and reduces the power required to modify the recording film. "Many of the aspiring optical disk drive manufacturers are faced with an awkward choice right now," reports Bosomworth. "Almost everyone is having pesky dropout problems with experimental optical media, and a number of manufacturers are leaning towards the use of Drexler's Drexon material. But industry rumors are that Control Data and at least two other vendors have rejected Drexon because of problems with error rates."

International Resource Development Inc.'s report (#502) entitled Optical And Magnetic Disk Media is available at \$1,285. For further information contact: IRD, 30 High Street, Norwalk, CT 06851 (800) 243-5008 (in CT or outside the U.S. (203) 866-6914); Telex 64 3452.

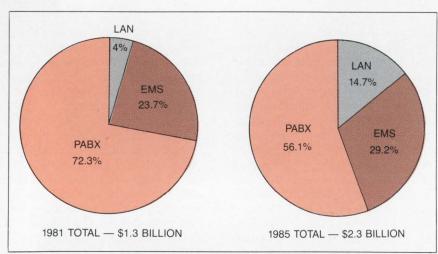

# PABX And LAN Integrate With Energy Management Systems

Strong market potential throughout the 1980s for PABX, local area network (LAN) and energy management markets will motivate suppliers to integrate systems to provide new applications. Combined revenues for shipments of PABXs, LANs and energy management systems (EMSs) will nearly double this market's current 1.3 billion figure to reach \$2.3 billion by 1985.

Technological achievements in the areas of wideband digital transmission and very large scale integration (VLSI), increased market competition, the deregulation of the communications industry, as well as continued energy conservation, are all factors driving the integration of energy management with communications networks. A complete breakdown of the LAN/EMS/PABX market is shown in **Figure 1.**

Energy management features are used to generate new revenues for PABX manufacturers while providing customers with energy savings to offset the costs of a PABX purchase. They may be provided on a PABX by total system integration or a two-vendor approach. Total system integration provides the highest market sophistication in which the PABX processes information in addition to switching information. Currently, one single-vendor approach exists and is used by

American Telephone and Telegraph Company (AT&T). However, a two-vendor approach will better meet the immediate needs of many suppliers and ensure adequate energy management and PABX expertise. The two methods for this approach are:

Separate processors and separate communications networks with a processor interface capability. This provides a single user interface and is used by Stromberg-Carlson.

Separate processors and shared communications networks. This approach is used by CEDCO, Inc. and Universal Communications Systems.

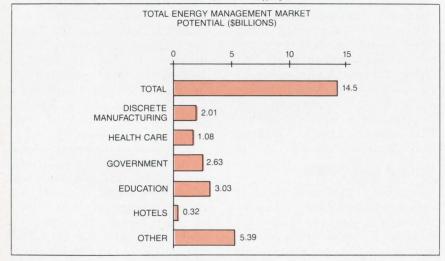

The large installed base of PABX systems is the first market for PABX suppliers to penetrate with energy management capabilities. The AT&T Dimension-based EMS, priced at \$400-\$700 per point, is not cost competitive and offers only basic energy management features. However, the industry-specific approach taken by the large Bell marketing network has been very successful. Initially, PABX-based systems have been marketed to the less sophisticated hotel and health care sectors. However, significant customer savings make systems appealing to other sectors as well, as shown in **Figure 2.** The maximum potential EMS market will reach \$14.5 billion if 100% penetration is achieved. New suppliers should provide advanced features including optimum start/stop and HVAC reset, demanding two-way communications capabilities to penetrate various industry sectors.

An analysis of this market potential is outlined in the recently published MAPTEK USA Worldwide Energy Opportunities Programs report entitled, "Energy Management Opportunities On PABX Systems." For further information, contact: Quantum Science Corp., 1114 Avenue of the Americas, New York, N.Y. 10036, (212) 997-0070.

Figure 1: Total PABX/Energy Management System/Local Area Network Shipment Forecast shows the market nearly doubling by 1985.

Figure 2: The maximum potential EMS market could reach \$14.5 billion.

# Keyboard Input Favored Over Touch And Voice

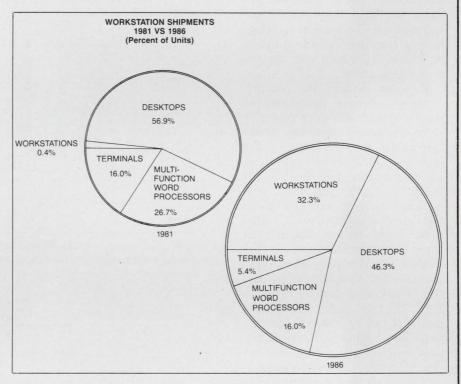

Managers place a significantly higher value on a full keyboard than on either a touch screen or voice input devices according to a recent market study on management workstations. Advanced Resources Development, a Boston area consulting firm, found that the recently acquired experiences of managers in the operation of interactive printer terminals, CRT terminals, word processors and personal computers are responsible for their increasing acceptance of keyboarding. Even though managers may not want to key in long documents or piles of data, they have come to view the full keyboard as the major control device on a computer system.

Office automation vendors have recently introduced new operator interface devices to allow managers to use workstations without keyboarding. The "mouse" cursor control used on the Xerox Star workstation allows the user to select icons or pictures representing common office functions or menu items listed on the screen. Touch sensitive screens provide another alternative to permit the user to point directly to items on the screen. Excalibur Technology has introduced voice recognition of simple commands on a workstation geared for executives. Preprogrammed keys, which perform a complex series of operations with one keystroke such as "find" or "select" are also being designed on workstations. Programmable keys, such as those offered on the Corvus workstation, allow changing functions for the keys with each application.

While managers will appreciate the added convenience of the new interface devices, most are not willing to trade in a full keyboard for a bank of "idiot" buttons, "cartoon" graphics, or a touch screen. Most of these workstation interface enhancements are best suited for aiding the infrequent user in accessing stored information.

IBM and Wang have recently announced voice messaging systems touting them as "breakthroughs" in overcoming resistance to office automation. Voice messaging systems enable users to record messages for electronic storage distribution while eliminating the need for keyboard input. However, ARD found that voice storage was not a highly valued workstation feature. While

tifunctional word processors, computer terminals, and specialized workstation devices will be configured with software and communications to support management workstation applications. By 1986, specialized workstation devices based largely on the microcomputers used on desktops today will account for 32.3% of the unit shipments. General purpose desktop computers will con-

Figure 1: By 1986, specialized workstation devices based largely on the  $\mu P$  used on desktops, will account for 32.3% of the unit shipments.

voice is the most heavily used communication method for business interaction, managers do not appear to be quite ready to talk to machines.

It is projected that the workstation market will grow at a healthy 40% per year through 1986. More than 4,500,000 workstations valued at \$25 billion will be shipped during the five year period from 1982-86. (Figure 1) Four types of computer products including desktop business computers, mul-

tinue to play an important role in the management workstation market due to their lower cost compared to more specialized products.

More information on this study of the management workstation market entitled, "Management Workstations: Markets and Strategies 1981-1986," is available from Advanced Resources Development, 28 A Park Street Station, Medfield, Massachusetts 02052. (617) 359-8090.

# Fiber Optic Modem Provides Good Noise Immunity

One of the most common applications of fiber optics is the transmission of RS-232 computer data. The outstanding noise immunity of fiber optic cables allows them to be installed in existing cable trays near noisy power cables without interference causing data errors.

Stricter FCC regulations regarding EMI (electro-magnetic interference) or RFI (radio frequency interference) also make a fiber optic system attractive because the fiber does not radiate interference. To prevent radiation a wire transmission line must be well shielded which increases its cost significantly.

In some parts of the country, frequent summer thunderstorms wreak havoc with data transmission. A nearby lightning strike can induce a tremendous voltage in long wire cables, not only causing errors in the data, but actually destroying any electronics connected to either end. Due to its all-dielectric construction, a fiber optic cable is not affected by these damaging transients.

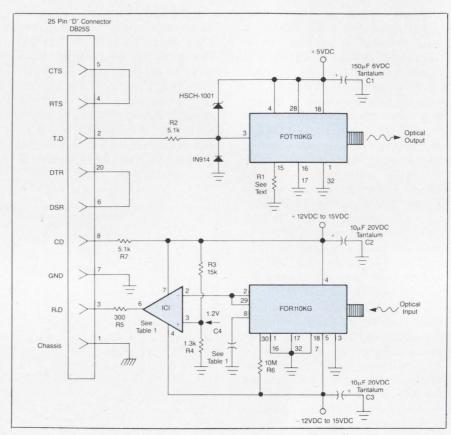

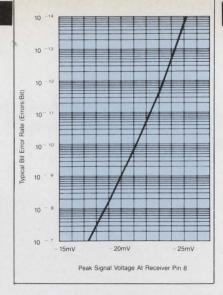

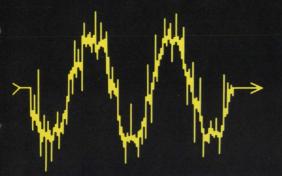

Most RS-232 applications don't use the full complement of control protocol spelled out by EIA RS-232C, so circuit complexity and cost can be reduced substantially by designing an optical modem without these functions. A simple circuit, shown in Figure 1, will give excellent performance at minimum cost. A bit error rate (BER) of 10<sup>-9</sup> or better can be achieved over a distance of more than 5 kilometers without a repeater. Cable selection will determine how far the modems will transmit. (Table 2)

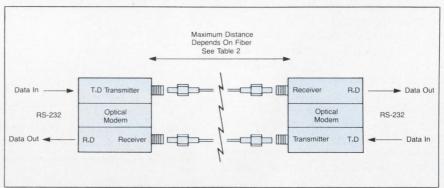

With the circuit shown in Figure 1, simplex, half-duplex or full duplex operation is possible between modems. A dual-fiber cable (or two 1-fiber cables) can be used to transmit the optical data. A system block diagram is shown in Figure 2.

The circuit **(Figure 1)** consists of a Burr-Brown fiber optic transmitter and receiver with level-

Figure 1: This simple circuit will provide bit error rates of 10<sup>-9</sup> or better over a distance of 5 kilometers without a repeater.

Figure 2: System block diagram.

shifting circuitry to convert the TTL levels required by the FOR110KG and FOT110KG to standard bipolar RS-232.

$R_2$  determines the input impedance and together with  $D_1$  and  $D_2$  clamps the  $\pm 3V$  to  $\pm 25V$  input to a safe level.  $R_1$  is used only when it is necessary to reduce the transmitter output power to prevent receiver overload which

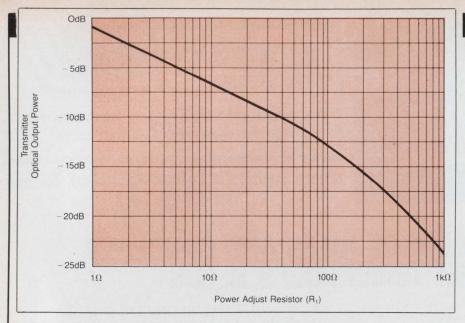

could occur with very short links. **Figure 3** shows the transmitter output power vs. R<sub>1</sub>. For maximum power, pin 15 is simply grounded. A "Mark" input will turn ON the transmitter LED.

The TTL output of the FOR110KG is converted to about  $\pm$  12V by using an op-amp, IC<sub>1</sub>, as a comparator. The voltage divider formed by R<sub>3</sub> and R<sub>4</sub> set a

# **PLAN TO ATTEND**

The Only Conference and Exhibition in the Midwest exclusively for **Automated Testing & Production**

**Automated Testing for Electronics Manufacturing Conference**

O'Hare Exposition Center, Rosemont, Illinois Oct. 25-28, 1982

# FOR THE PRODUCTS, IDEAS AND CONCEPTS TO MEET TOMORROW'S NEEDS

The ATE Conferences are recognized as the "learning place" for managers, supervisors and engineers engaged in quality control and testing for manufacturing and product development.