# SIGN CUMPUTERS/SYSTEMS - PERIPHERALS - COMPONENTS - 8/8: Digita Industrial SBCs **Brave Fire And Ice** Alterable µC Unit Offers Building Block Approach Display Technologies • WESCON • Free RAM Offer

5983 Mi :

ATE 5983 RGE & FREEMAN LIBRARM

A MORGAN-GRAMPIAN PUBLICATION

# TS-1 The Most Advanced Business Terminal And Designed To Stay That Way...

The TS-1<sup>M</sup> is truly designed with the future in mind, taking full advantage of the microprocessor technology. The TS-1 terminal emphasizes software driven features which provide a wide and unique range of user flexibility, as well as significantly reducing the possibility of obsolescence. All new emulations as offered by *Falco Data Products* as well as options, such as auto-dial 212 plus<sup>M</sup> modem 300/1200 bps...full Plot 10 graphics...and the new and powerful *SMART PAGING*,<sup>M</sup> can easily be incorporated into the standard TS-1; thereby configuring the TS-1 to exactly what you need when you need it. Never has one terminal had

so much to offer to a wide variety of users. But see for yourself just how much more advanced the TS-1 really is.

Some standard TS-1 features are:

Software-driven emulations • 28 nonvolatile user-programmable functions • User selectable personality features • User definable split screen scrolling • User selectable status line • Lightweight w/small footprint • 8 attributes not stored on screen

\*Optional

TS-1 BY FALCO DATA PRODUCTS

1286 Lawrence Station Road Sunnyvale, CA 94086 Telex: 172494

(408)745 - 7123

Write 1 on Reader Inquiry Card

the GEORGE & FREEMAR LIBEARS STATE TECHNICAL INSTITUTE AT MEMPHIS IN PROVIDE AT A STATE TECHNICAL INSTITUTE AT MEMPHIS IN PROVIDE AT A STATE TECHNICAL INSTITUTE AT MEMPHIS IN PROVIDE AT A STATE TECHNICAL INSTITUTE AT MEMPHIS IN PROVIDE AT A STATE AT A STATE

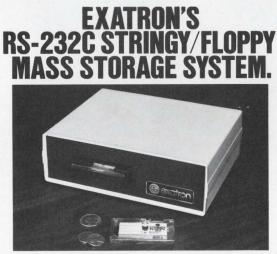

#### SYSTEMS

Whether you are a systems integrator or computer OEM, ADES subsystems provide the ultimate solution to your needs. As a fully supported product, ADES subsystems provide a revolutionary product capable of displacing cartridge disk drives and floppies.

#### SYSTEM 8

As a standalone table top or rackmount package, the *GYPSY* based SYSTEM 8 provides the user a disk of 10 MB, 34 MB, or 70 MB of disk capacity with 10 MB or 20 MB removability via the streaming tape.

#### SYSTEM 14

The SYSTEM 14 provides 33 MB or 66 MB of disk storage with 20 MB removability via the streaming tape, disk tape packaging.

#### THE ULTIMATE SOLUTION

With all the performance of the ADES GYPSY controller, the SYSTEM 8 or SYSTEM 14 can meet your total memory subsystem requirements.

#### GYPSY

At the heart of the *ADES* product line is the *GYPSY* Winchester/Streaming Tape formatter. By combining the disk and tape functions into a single card, the *GYPSY* provides unprecedented system capabilities. With a 5 Mbyte/minute offline disk to tape transfer rate, a user can backup or restore a 20 Mbyte logical drive in less than four minutes. When operating in the "Transparent Mode," the host can still access the disk while the *GYPSY* moves data between the disk and streaming tape. In multiuser systems, individual users can backup or restore logical elements without affecting other users on the system.

#### MORE THAN JUST BACKUP

Compiling the *GYPSY* disk/tape commands with the direct tape access commands provides a system capable of Operating System load, Program Exchange and Selective File storage and retrieval. The streaming tape thus provides more than just backup. EASY INTEGRATION

The power and flexibility of the *GYPSY* is only surpassed by the ease of host integration. With as few as five 7400-type components, the *GYPSY* can be interfaced to most mini or microcomputers.

#### EXPANDING HARDWARE SUPPORT ADES currently supports Priam and Century Data Disks in conjunction with DEI, Archive and Cipher ¼" cartridge streaming tapes.

#### SUPPORT

ADES supports the most widely used micro-computers, and their operating systems.

**GYPSY HOST INTERFACE ADAPTERS (GHIAs)** For the user who desires to bring up his system quickly, *ADES* offers S100 and Multibus host adapters in both Programmed 1/0 and DMA configurations. In conjunction with *ADES* software, the *GHIAs* provide a rapid means of integration, with minimal effort.

#### THE Z80 CONNECTION

For the Z80-based systems, *ADES* provides the GHIA-Z80 which allows connection of *GYPSY*, *SYSTEM8* or *SYSTEM 14* directly to the CPU, thus eliminating the problems of specialized base configurations.

#### SOFTWARE

ADES support of CP/M<sup>™</sup> and MP/M<sup>™</sup> makes the GYPSY and SYSTEMS 8 and 14 easy to integrate and use. Support levels range from the "non-programmer" and user to the systems integrator configuring high performance MP/M<sup>™</sup> systems.

#### CP/M

The ADES "BIOS ATTACH" program allows a user to configure the program to his system configuration, and begin using the disk/tape subsystem as an integral system resource under CP/M 2.2.

#### MP/M

For the system integrator who must design a complete BIOS or XIOS, *ADES* supplies a series of detailed application notes. These publications allow quick and complete integration of *ADES* subsystems into all system applications.

#### UTILITIES

All disk/tape subsystems running with CP/M are also supported with an array of utility programs. Format and Verify, Defect Compensation and Backup and Restore are only a few examples.

Adaptive Data & Energy Systems • 2627 Pomona Boulevard • Pomona, California 91768 Telephone: (714) 594-5858 TWX: (910) 581-1211

# BREAKTHROUGH IN

#### BEACON<sup>™</sup> leads the way with new standards in

FCG

# COLOR GRAPHICS.

#### price-performance and human-factors engineering.

Finally, a medium-priced color graphics system with the performance of much more expensive systems. Introducing Beacon™ from Florida

Introducing Beacon<sup>IM</sup> from Florida Computer Graphics.

#### Enhanced productivity for business and engineering.

The Beacon™ System displays a full spectrum of graphics capabilities. Not only multi-color graphs and charts, but engineering diagrams, as well.

As a stand-alone or host-dependent system, Beacon does it all. For enhanced productivity in engineering, marketing, manufacturing, and financial control.

#### More power where it's needed.

The Beacon System can accommodate up to almost 1 MByte of main processing memory. With the addition of 640 KB of graphics memory, Beacon can create a 1280 x 960 image resolution used in many CAD/CAM applications. This high resolution, combined with standard zoom and roam features on a 13" or 19" display, make Beacon ideal for engineering applications. Beacon's own menu driven software and CP/M compatible operating system provide access to a comprehensive library of programs that cover virtually every aspect of business.

#### Superior graphics features.

The extent and caliber of Beacon's graphics features is unmatched in its price range.

The System's brighter, more vivid colors stem from a unique electronic design and a superior raster scan display. The BeaconBRIGHT™ image, combined with an anti-glare filter eliminates the need for hooding the display—even in brightly lit areas.

Circles, vectors, arcs, rectangles and polygon fills are generated with hardware rather than software. As a result, image response is almost instantaneous.

Beacon's 16x zoom feature can be controlled from the keyboard in 1x increments. Both horizontal and vertical scrolling is variable in speed and exceptionally smooth. Beacon also provides reverse video and underline, as well as blinking and variable height characters.

Other graphics features include: 640 x 480 resolution (standard); 6 memory planes with 256 colors—up to 32 usable at a time (16 in the graphics plane and 16 in the alpha numeric plane)—and 18 programmable function keys on the keyboard and another 18 on the display bezel.

#### Human-factors engineering.

The human factors, or ergonomics, that make a computer personally comfortable played an integral part in the Beacon System's design.

The critical area of reducing eye strain and fatigue has been accommodated through the development of a screen image *twice as steady* as the image in other computer systems, including those that are advertised as "flicker free." For extra visual comfort, the brightness of the Beacon image is controllable at the keyboard, and an anti-glare filter reduces distracting reflections.

And Beacon's commitment to superior ergonomic design doesn't stop there. To avoid back strain, the monitor tilts, swivels, and uniquely adjusts 5.5" in height. In addition, the keyboard is separate from the display and can, therefore, eliminate the sense of being tied down to the monitor.

Other hands-on features that make for greater comfort and productivity are: a three-degree adjustable tilt in the keyboard, a palm rest, tactile feedback, sculptured keys, and a dimpled home key in the function and numerical key clusters.

#### The importance of MPA.

Our MPA, or Multiple Processor Architecture, is unique to the Beacon System. It incorporates six individual microprocessors, each chosen for its efficiency in the performance of specific tasks. System throughput is optimized with the use of an administrative processor which distributes Beacon's internal workload. A 16-bit bit-slice processor is dedicated solely to graphics tasks and mathematical functions.

MPA is at the heart of Beacon's extraordinary performance.

#### Quality and service assured.

All equipment is constantly monitored and evaluated from our corporate production facility, utilizing the most sophisticated automated test equipment available today. And our systems are supported by three levels of service, assuring you of minimal downtime.

#### BEACON™-the beginning.

Beacon is available. NOW. And it's just the beginning of a comprehensive family of systems that will enhance your productivity. Contact us for more information on how the Beacon System can work for you. We'll send you our full color literature. Just write: Marketing Communications Manager, Florida Computer Graphics, 1000 Sand Pond Road, Lake Mary, Florida 32746. Or call (305) 321-3000. In the Continental U.S. outside Florida, dial 1-800-327-3170.

FLORIDA COMPUTER GRAPHICS VISION IN COMPUTERS.

Write 13 on Reader Inquiry Card

The most complete line of Interface Products for PDP\*-11, LSI-11 and VAX\* Computers with features you can't get anywhere else

## For DEC users... MDB makes the difference!

0

You *can* have it all! Along with the benefits of your DEC computer, you can get interface products that significantly extend the capability, flexibility and economy of DEC systems. MDB makes more DEC system boards than any independent manufacturer—some with plain vanilla compatibility; others with plain incredible performance boosting features. For example—

- Line printer controllers for every major line printer, with complete self-testing capability and optional RS-422 "long lines."

- Peripheral device controllers for card readers, X-Y plotters, electrostatic printer/plotters and paper tape readers/punches.

- DZ11 compatible multiplexors for LSI-11 and PDP-11 users; some combine RS-232 and current loop or RS-422 with a single board.

- High speed synchronous serial interfaces; one DUP-11 compatible model has all bit and byte protocols even for LSI plus X.25 capability.

- Inter processor links between Unibus computers or between Unibus and Q-bus.

- System modules including DMA modules with RS-422, general purpose parallel and digital I/O interfaces, an IEEE 488 bus

controller and a programmable real time clock.

- PROM memory modules, some with an on-board PROM programmer.

- General purpose interface and bus foundation modules.

- LSI-11 based subsystems and systems with capabilities like TU-58 cartridge storage and memory management.

- LSI-11 system boxes with 22-bit addressing and switching power supplies.

- LSI-11 bus repeater and bus switches to allow sharing of memories and peripherals between processors.

All MDB products are available under GSA contract #GS-00C-02851.

Give your DEC system all the benefits. Discover the difference MDB interface products can make. \*Trademark Digital Equipment Corp.

MDDB1995 N. Batavia Street<br/>Orange, California 92665<br/>714-998-6900SYSTEMS INC.TWX: 910-593-1339See Us at Wescon/Mini Micro, Booth 211 & 213<br/>Next MDB DEC Compatible Show: 9-9-82 Sunnyvale, C<br/>Hilton Inn

Write 41 for LSI, 42 for PDP

# **Digital Design**

pg. 44

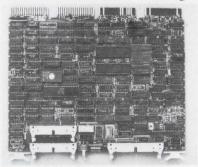

#### Cover

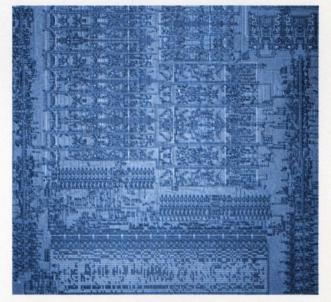

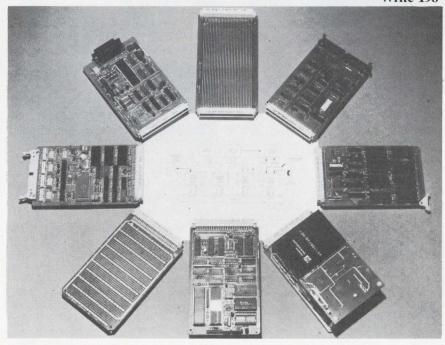

Our cover photo illustrates the latest series of industrial  $\mu P$  boards from National Semiconductor. The boards are targeted for harsh environment applications, tolerating a temperature range of -40 to +85 C (see p. 77).

Published monthly and copyright © 1982 by Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215. Second class postage paid at Boston, MA and additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215

#### COMPUTERS/SYSTEMS

| Wescon '82: The Word Is 16-Bits                                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Design Of Raster Scan Graphics Systems</b>                                                                                                                                                                  |

| Designer's Guide To The IEEE-488 Bus—Part 2 53                                                                                                                                                                 |

| In Part 4 of Paul Snigier's bus series, Snigier continues his discussion of the IEEE-488 (part 1 appeared in June), examining some of the disadvantages of the bus, as well as some implementation guidelines. |

| VMEbus—A µP Bus For The Future                                                                                                                                                                                 |

| An adaptation of the VERSAbus, VMEbus is a popularly supported bus using the Eurocard format and offering some unique capabilities.                                                                            |

| Technology Trends                                                                                                                                                                                              |

| Market Trends                                                                                                                                                                                                  |

#### PERIPHERALS

| New Tec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | hnologi  | es Increa | as | e Di | splay | Alter | nati | ives                      | 30 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|----|------|-------|-------|------|---------------------------|----|--|

| and the second se | advances |           |    |      |       |       |      | T, LCD and<br>Information |    |  |

#### COMPONENTS

| Alterable µCs: Tailoring Chip Design To Meet<br>Applications                                                           |

|------------------------------------------------------------------------------------------------------------------------|

| Designed to tolerate modifications to their basic elements, alterable $\mu$ Cs bring new flexibility to system design. |

| Market Trends                                                                                                          |

| Applications Notebook         26           Free Samples Of 4K × 4 Static RAMs.                                         |

| Innovative Design                                                                                                      |

| Calendar10       | New Products76     |

|------------------|--------------------|

| News Update12    | New Literature     |

|                  | Advertisers' Index |

| Reader Service57 |                    |

|                  |                    |

#### CONVERT RGB to COMPOSITE VIDEO with LENCO's CCE-850 ENCODER.

LENCO, INC

0

Lenco's CCE-850 Color Encoder is specifically designed to encode most RGB colorgraphics displays to NTSC type video.

This small, self-contained unit may be used in either tabletop or 19" rack mounted configuration, and includes a built-in color reference bar test pattern to ensure proper NTSC color monitor alignment.

Check these outstanding features:

999

- RGB To Composite Video

- Color Test Patterns

- Auto Sync Detector

A

Ħ

- Detailed Enhancement

- High Resolution

- Self-Contained

Call or write today for detailed specifications, application notes, and price.

#### LENCO, INC., ELECTRONICS DIVISION

300 N. Maryland St., Jackson MO 63755, (314) 243-3147

Diaital Des Jeffrey C. Hoopes Managing Editor **Bob Hirshon** Dave Wilson Senior Technical Editor **Bill Groves** West Coast Technical Editor (408) 371-9620 East Coast Nicolas Mokhoff **Technical Editor** (212) 340-9700 **New Products &** Martha Hawkins **Directory Editor Editorial Assistant** Mary Rose Hanrahan International Ron Neale **Electronics Editor** International **Computers Editor** Eric Wignall Southwest Contributing Editor Irwin Carroll **Contributing Technical** Edward Pevovar Editor **Contributing Software** William Ten Eick Editor **Contributing Technical Editor** Paul Snigier **Publication Services Charlotte King** Manager **Production Manager** Jon Buchbinder Richard D. Sarno Art Director Assistant Art Director **Tilly Berenson** Production/Graphics Mary-Jo Borkoski, Judy Bielicki, Joan Scheffler, Vete Saulenas, Don Schaff **Elaine Bull** Promotion Manager Helen Obermayer Research **Circulation Manager** Elizabeth Mahon-Laidlaw Edie Almeleh, Sarah Binder, Circulation Gary Byrne, Deb Goldstein, Regina Harrington, Lynda Neue, Laurie Poth **General Administration** Karen Melanson, Mal Rankin. Nanette Rayman, Linda Davis, Cassandra Ewing, Susan Joy Sager, Paul Christo

> Group Publishing Director Albert J. Forman

#### **Advertising Sales**

Northeast: John Moon (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic/Southeast: George Cominsky (212) 340-9700, Morgan-Grampian Publishing, 2 Park Avenue, New York, NY 10016

Midwest: Hank Bean (312) 346-4611, Morgan-Grampian Publishing, 2 North Riverside Plaza, Chicago, IL 60606

South Central: Jerry Ambroze (713) 780-3326, Ambroze and Associates, 2186 Augusta, Houston, TX 77057

Northwest: Jim Teller (408) 371-9620, 1901 S. Bascom, Suite 1005, Campbell, CA 95008

Southwest: Lindy Dolan (213) 981-3300, 15910 Ventura Boulevard, Suite 1215, Encino, CA 91436

Classified Manager: William L. Pryor (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

Japan: K. Yanagihara (03) 350-0272, 10-10 Shinjuka 3-chome, Shinjuku-ku, Tokyo 160, Japan Cable Address: Yanacour Tokyo.

#### ISSN 0147-9245

Published monthly and copyright © 1982 by Morgan-Grampian Publishing Company, 1050 Commonwealth Avenue, Boston, MA 02215. Second class postage paid at Boston, MA and additional mailing offices.

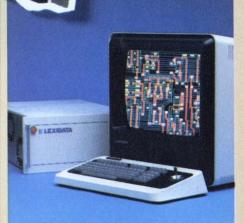

## Buy a Lexidata 8000 and get half a VAX free.

Or half a DG MV/6000. Or half a Perkin-Elmer 3230. Only one graphics processor is designed to free your host of a substantial portion of the processing load

imposed by CAD/CAM applications. The System 8000 features dual processor architecture, combining the 16/32 bit Motorola MC68000, the indus-

try's leading microprocessor, with a Lexidata-designed ultra high-speed display processor. The System 8000's unique architecture, graphics software (modeled after the ACM SIGGRAPH CORE), and database structure allow you to distribute the computer's workload to the most appropriate processor: the display controller, the graphics system controller, or the host CPU.

Our software package, LX/GP1, supports a 31-bit precision Object Data Structure™ (ODS) consisting of graphics primitives and functions for defining and changing the bitmap memory. The ODS is a high-level mathematical description of the graphics database maintained in a World Coordinate space. Like a display list, the ODS is kept in vector format; however, the Incorporating System 8000 hardware into your graphics environment ensures a strong processor balance, where no one element is consistently the bottleneck. System 8000 soft ware assures that all elements are equally efficient, leading to high

> performance and cost effective use of all the hardware in the interactive computer graphics system. For more details, call (617) 663-8550 or write to us at 755 Middlesex Turnpike, Billerica, MA 01865. TWX 710-347-1574.

local World Coordinate description allows multiple viewing operations of the database or sections of the database without requiring the host to redefine the objects. In addition, all graphics transformations are performed locally. Therefore, you can redraw the display quickly, without host processing or data retransmission. Unlike conventional display lists, ODS processing is proportional to the number of vectors being viewed, not the length of the display list.

The clear choice in raster graphics.

VAX is a trademark of Digital Equipment Corporation

## • ANNOUNCING • CI 1220

#### TWO MEGA-BYTE FLOPPY DISK SYSTEM FOR LSI-11 BASED SYSTEMS DUAL DRIVE — DOUBLE DENSITY — DOUBLE SIDED

- DEC RX02/RX01 COMPATIBLE

- DUAL WIDTH DMA CONTROLLER

- COMPATIBLE WITH LSI 11/2 OR LSI-11/23

- BOOTSTRAP, DIAGNOSTICS PROVIDED, RACK MOUNT ENCLOSURE

- 3 MONTH WARRANTY, PARTS AND LABOR

#### TWO MEGABYTES FOR LESS THAN THE PRICE OF ONE.

The Cl 1220 is completely compatible with DEC operating systems using DEC RX03 protocol and DEC standard DY handler. Compatible with RX01/RX02 media, IBM 3740 format. Dual width controller operates at +5VDC @ 2.7A supplied from LSI-11 backplane and is compatible with any Shugart interface floppy drives.

DON'T ASK WHY WE CHARGE SO LITTLE, ASK WHY THEY CHARGE SO MUCH.

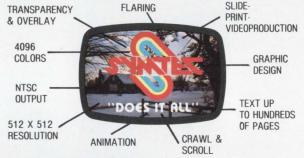

#### SYMTEC PGS III .... ONE GRAPHICS GENERATOR THAT DOES IT ALL Symtec's Hi-Res Graphics Generator is completely or text or graphics can be stored on disk for future

Symtec's Hi-Res Graphics Generator is completely software controllable so you can tell it what to do instead of it telling you! Create text or graphics and move them around on the frame. Create text in almost any font you can imagine, even foreign language characters. Store and run hundreds of text pages automatically. NTSC output can be broadcast or taped; made into 35mm slides and regular or instant prints; overlaid over tape, videodisc or video camera feed. Computer created frames

15933 West 8 Mile Road, Detroit, Mich. 48235 (313) 272-2950

\*Apple is registered trademark of Apple Computer, Inc

to tape to create "real animation". Standard PGS III is controlled by an Apple\* computer. Interface with other computers is optional at extra cost. PGS III. One Graphics Generator that does it all.

recall, sent via modem to

transferred frame-for-frame

distant locations, or

Generator that does it all. Priced at \$7000 retail. O.E.M. and quantity discounts available. Write or call for details. **Digital Design**

#### EDITORIAL, SALES, AND CIRCULATION OFFICES

Digital Design 1050 Commonwealth Avenue Boston, MA 02215 Telephone: (617) 232-5470

#### -----

#### CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 2 Park Avenue, New York, NY 10016. (212) 340-9700. Domenic A. Mucchetti, President.

4

43

#### **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 2 Park Avenue, New York, NY 10016 (212) 340-9700. Robert Poggi, Director.

Morgan-Grampian publishes the following in the United States: American City & County • Circuits Manufacturing • Contractor • Design Engineering • Electronics Test • Industrial Distribution • Industrial Product Bulletin • Mart • Municipal Index.

#### New Publication Development

H.G. Buchbinder, Director

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronic Times • What's New in Electronics • What's New in Computers.

#### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

> Circulation Department DIGITAL DESIGN 1050 Commonwealth Avenue Boston, MA 02215

Subscription rates: non-qualified subscribers (US and Canada) — \$35/yr; foreign — surface mail — \$45; air mail — \$70. Single copies — \$4.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

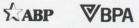

## Da Vinci would have traded all his notebooks for this new AED767 graphics terminal.

Today, Leonardo da Vinci's notebooks are priceless objets d'art. They also contain many unique engineering

concepts, like the one shown above of the iron framework he designed to reinforce the head and neck moulds for 'Il Cavallo', the horse. Although da Vinci worked periodically on 'Il Cavallo' for 16 years, the gigantic bronze statue, which was to stand some 26 feet tall, never materialized.

Instead, his patron, the Duke of Milan, used the casting bronze for canons in a war against France.

But what took Leonardo many years to devise could have been achieved in mere hours with the help of AED's new 767 color graphics and imaging terminal. Available in desktop or 31/2" high rackmount configuration, this new CAD machine has the kind of innovative features you'd expect only from AED. Features like built-in antialiasing (which virtually eliminates jagged lines common to raster-generated vectors). 1K x1K x 8 virtual address space. 768 x 575 pixel viewing window. Up-to-256 simultaneous colors from a palette of 16.8 million. A blue line

reference grid that doesn't utilize video memory. Plus a refresh rate, adjustable from ty standard to flicker-free 45 Hz.

The AED767 gives you smoother drawings than any CAD station on the market-and at lower cost. So be a latter-day 'da Vinci' and use the best computer-aided design tool at your disposal. The AED767.

Advanced Electronics Design, Inc., 440 Potrero Avenue, Sunnyvale, CA 94086. Phone 408-733-3555 Telex 357-498. Outside California, Hawaii and Alaska call 800-538-1730. All images shown taken from screen of AED767.

Sponsors of the U.S. Pavilion, 1982 Worlds Fair Sales Offices: LA 213-907-8811/Detroit 313-352-4290/New Jersey 201-238-6322/Boston 617-256-1700/Washington, D.C. 301-760-4310

Write 5 on Reader Inquiry Card

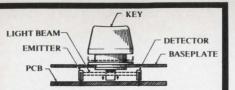

#### **NEW OPTICAL KEYBOARD**

Optical Techniques Inc. (OTI) has developed a cost-effective, full-travel optoelectronic keyboard without sacrificing either reliability or function. The optoelectronic components are multiplexed by pulsing the emitters and scanning the detectors, simultaneously reducing power consumption and component failure rates.

OTI's unique technology replaces obsolete mechanical and capacitive switches within an encoded keyboard while ensuring N-key rollover. Key depression is detected by interruption of an infrared light beam (see illustration).

Write 38 on Reader Inquiry Card

#### DC100 CARTRIDGE DRIVE HAS SMART I/O

MicroDrive/OEM now features a micro processor based I/O. This unit performs all control and formatting for quick systems integration. A high level command set (22 commands) allows full peripheral status for the model 125I/O. Serial and parallel options are available priced as low as \$400 in OEM qty.

MOYA CORPORATION 9001 Oso, Unit B Chatsworth, Ca. 91311 Tel: (213) 700-1200

Write 39 on Reader Inquiry Card

#### HAS YOUR ADDRESS CHANGED-ARE YOU PLANNING TO MOVE IN THE NEAR FUTURE??

Please use the enclosed qualification form to notify us of your address change. A change of address requires that you fill out the entire form.

Please allow 6-8 weeks for your change to take effect.

#### Calendar

#### September 7–10

**ICCC '82.** Sixth International Conference on Computer Communication. Barbican Center, London, England. Contact: ICCC '82, Box #23, Northwood Hills, HA6 ITT, Middlesex, UK. International Phone: 44 9274 27511.

#### September 8

Invitational Computer Conference. Boston Mariott Hotel, Boston, MA. Exhibits 2PM-7PM; Technical Seminars start at 9AM. Directed to OEM decision makers, systems houses, and quantity buyers. Contact: Susan Fitzgerald, Conference Mgr., B.J. Johnson & Associates, 3151 Airway Ave., #C2, Costa Mesa, CA 92626.

#### September 13-15

Autofact-Europe. Exhibition and Conference Center (Palexpo). Geneva. Switzerland. Combined conference and exhibition focusing on the technologies of automated and computer integrated manufacturing. Contact: Society of Manufacturing Engineers. One SME Drive. PO Box 930, Dearborn. MI 48128. (313) 271-1500.

#### September 13-16

Sixth International Conference on Software Engineering, Tokyo, Japan. Contact: Sixth Intl. Conference on Software Engineering, PO Box 639, Silver Spring, MD 20901. (301) 589-3386.

#### September 14-16

Wescon '82. Anaheim Convention Center, Anaheim Marriott Hotel, and the Inn at the Park. Anaheim, CA. Covers: active and passive electromechanical components: computers and peripherals: instrumentation and test equipment: tools and production equipment: control systems; and, power supplies Contact: Eileen Algaze, Communications Coordinator, 999 N. Sepulveda Blvd., El Segundo, CA 90245. (213) 772-2965.

#### September 14-16

Mini/Micro Computer Conference and Exhibition. Disneyland Hotel, Anaheim, CA. Contact: Eileen Algaze, Electronic Conventions, Inc., 999 N. Sepulveda Blvd., El Segundo, CA 90245. (213) 772-2965 or outside CA. (800) 421-6816.

#### September 15–17

LAN '82. The Marriott, Los Angeles, CA. Local Area Networks in an exhibition, applications program, and short courses. Covers: distributed data base services, print and file services, work stations, network monitoring and control. Contact: Information Gatekeepers, Inc., 167 Corey Rd., Brookline, MA 02146. (617) 730-2022.

#### September 20-24

**Compcon Fall '82.** Capital Hilton Hotel, Washington, DC. Conference on Computer Networking. Contact: Compcon Fall '82, PO Box 639, Silver Spring, MD 20901. (301) 589-3386.

#### September 21-23

Semicon East '82. Hynes Auditorium, Boston, MA. Contact: SEMI, 625 Ellis St., Suite #212, Mt. View, CA 94043. (415) 974-5111.

#### September 21-23

**SOFTWARE/expo-National.** Expocenter, Chicago, IL. Sponsored by Infosystems Magazine. Contact: SOFTWARE/expo, Suite 400, 222 W. Adams St., Chicago, IL 60606. (312) 263-3131.

#### September 21-23

Voice Data Entry Systems Applications '82. Villa Hotel, San Mateo, CA. Contact: Robert Burgess, Public Information Office, Lockheed Missiles & Space Company, Inc., Sunnyvale, CA 94086. (408) 742-6688.

#### September 23–25

**Computer Showcase Expo.** New York Coliseum, New York. Contact: The Interface Group, Box 927, 160 Speen St., Framingham, MA 01701. (617) 879-4502: outside MA (800) 225-4620.

#### September 28-30

Federal Computer Conference. Sheraton Washington Hotel, Washington, D.C. Intensive 3-day program of sessions and workshops includes special all-day "backgrounder" seminar on first day. Major ADP equipment/systems Exposition on second and third days. Contact: Federal Education Programs, P.O. Box 368. Wayland, MA 01778. (617) 358-5181.

#### September 28-October 1

**Computer Graphics.** San Diego, CA. 4-day course covers: technology fundamentals; raster scan, vector and color techniques; software and hardware availability and selection criteria; and equipment selection and implementation of graphics applications. Contact: Ruth Dordick, Integrated Computer Systems, 3304 Pico Blvd., PO Box 5339, Santa Monica, CA 90405.

#### September 29–October 1

**1982 International Conference on Circuits and Computers.** New York Hilton, N.Y., NY. Focus is on VLSI and large-scale systems. Contact: Circuits and Computers, PO Box 639, Silver Spring, MD 20901. (301) 589-3386.

# Smart Graphics<sup>™</sup> G-100 We Have Only Just Begun.

Modqraph

The **G-100** Graphics Terminal is only the beginning of a family of Computer/ Graphics products from Modgraph. The Modgraph **G-100** is a dual purpose expandable computer terminal. High resolution graphics, 8085 processor, 144K RAM, independent high speed alphanumeric overlay, and a wide range of performance characteristics unmatched in the graphics industry.

We call it **Smart Graphics™.** And with good reason. It gives you powerful graphics, multi-page alphanumerics, and more for under \$3,000.

#### GRAPHICS

As a graphics tool the **G-100** is a smart choice; two full pages of 768 x 585 viewable resolution, circle, rectangle, vectors, pattern draw, and of course Plot-10<sup>®</sup> compatibility.

#### ALPHANUMERICS

The independent alphanumeric plane allows alphanumeric overlay without overwriting graphics. Length and number of lines are programmable from 41 to 96 characters per line and from 1 to 46 lines per page. Scrollable page memory, split screen, ANSI X3.64 and VT-100<sup>®</sup> compatibility. All designed to help you work smarter, not harder.

#### **OTHER FEATURES**

CP/M Capability

Modgraph

- 15" P-39 Green Phosphor Screen

- Optional Disk Drive

- Special Function Keys

To fully appreciate the Modgraph G-100 you have to see it in action. Drop us a line, or give us a call. We'll arrange for a demonstration and show you how powerful graphics can be yours. With Smart Graphics<sup>TM</sup>.

Plot-10 Trademark Tektronix

\* VT-100 Trademark Digital Equip. Corp.

1393 Main Street Waltham, MA 02154 (617) 890-5764

Write 19 on Reader Inquiry Card

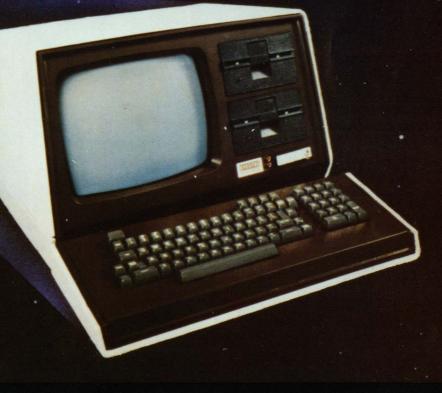

**NEC 16-bit Personal Computer**

NEC Information Systems, Lexington, MA, has developed the Advanced Personal Computer (APC) which utilizes the CP/M-86 operating system and is based on a NEC-manufactured 16-bit 8086-compatible  $\mu$ P.

#### **First Commercial Ada Product**

The new Ada Syntax Checker, AdaSynCh, from Intermetrics, Cambridge, MA, is a Pascal program which checks the grammatical form of an Ada source program. AdaSynCh determines whether a program is written with proper Ada grammar and format, but also indicates where errors exist.

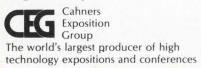

#### **NS16000 Cross Software Development**

The first version of the NS16000 cross software development package, NS-ASM-16, is now available from National Semiconductor Corp. Intended as a support package to facilitate the development of software for NS16032-based systems, NS-ASM-16 will initially be available on the DEC VAX 11 series. NS-ASM-16 cross software development package consists of an assembler, linker, librarian and symbolic debugger.

#### **SPI Offers CMOS Logic ICs**

WS DIGITAL

WS DIGITAL

WS DIGITA

Semi Processes, Santa Clara, has introduced a new family of 33 high-speed CMOS logic circuits available in sample quantities over the next three months. SPI plans to expand to more than 100 devices by early 1983.

#### **Kennedy Acquires BASF Winchesters**

Kennedy, Monrovia, CA, has purchased the 8" Winchester disk product line and manufacturing operations of BASF Systems, Los Gatos, CA, location. The transaction includes the assets, work in progress, spares, inventory and designs, as well as the rights to manufacture and market the BASF 5<sup>1</sup>/<sub>4</sub>" disk drive in the US.

#### **NEC Enters Gate Array Market**

The Electron Division of NEC Electronics has entered a new market area with the introduction of six high-performance gate arrays. Three TTL arrays range in complexity from 256 to 1,000 gates and have I/O levels that are compatible with 74 ALS series advanced low-power Schottky devices. The three CMOS arrays range from 858 to 2,112 gates and are compatible with standard TTL and CMOS devices.

DIGIT

DIGITA

NGITA

DIGITA

DIGITA

DIGITAŁ

HGITAR

#### **Seiko Enters Computer Graphics**

DESIGN NEWS DIGITAL DESIGN NEWS DIGITAL DESIGN NEWS DIGITAL DESIGN NEWS

DIGITAL DESIGN NEWS DIGITAL DESIGN NEW DIGITAL DESIGN NEWS DIGITAL

DESIGN NEWS DIGITAL DESIGN NEWS DIGITAL DESIGN NEWS DIGITAL DESIGN NEWS

With the introduction of advanced color and monochrome graphics display terminals, a CRT hard copier, and a pair of digitizing tablets, Seiko Instruments has expanded into the US computer graphics market. The first raster scan graphics display with hardware anti-aliasing is the latest in the series of graphics terminals.

#### **DEC And FPS Announce Agreement**

Digital Equipment Corp and Floating Point Systems have announced a cooperative marketing agreement to market a FPS Array Processor and VAX computer combination for use in computation-intensive applications. Floating Point System's FPS-164 Attached Array Processor interfaces with Digital's VAX-11/780 and VAX-11/750 32-bit computers.

#### **Pyramid To Market Supermini**

Pyramid Technology will market a general purpose supermini computer later this year, backed by \$3 million in venture capital. The 32-bit supermini includes a new proprietary design concept that will permit users to expand processing power and functionality in incremental stages.

#### **Biomation And Millenium Merge**

Gould has established a new unit targeted toward the high end of the test and measurement market by combining Millenium Systems, Cupertino, CA, and Gould Biomation, Santa Clara, CA. The new operation, with joint manufacturing, marketing and product development capabilities, is part of Gould's Instruments Division.

#### Lifeboat Offers EM80/86 Emulator

Lifeboat Associates has announced the publication of the new EM80 emulator which permits SB-80 and other CP/M-80 compatible software to run on the IBM Personal Computer under DOS with no hardware addition or change.

WS DIGITAL DESIGN NEWS DIGITAL WS DIGITAL DESIGN NEWS DIGITAL WS DIGITAL DESIGN NEWS DIGITAL WS DIGITAL DESIGN NEWS DIGITAL

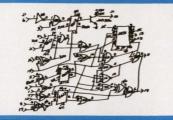

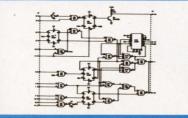

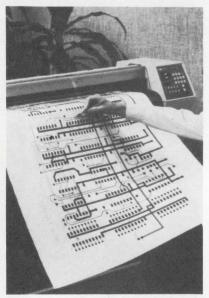

# DRAFTING SYSTEM 1

The World's Leader in Computer Schematics and Automatic Data Base Preparation

#### FREE-HAND SKETCH

"DS1" allows operator to digitize directly from a freehand sketch. Vocal Output prompts operator as IBM Microcomputer collects data. Enter a "D" size in 1 hour. NO GRIDS. EDITS are performed in minutes.

#### COMPUTER PROCESSING

HP1000 DG Nova 4X, Eclipse, MV 8000 DEC VAX, PDP11 UNIVAC HARRIS IBM, plus others

#### Computer straightens slanted lines, uses correct size symbols and enters alignments among symbols entered by user during input. Drum plotter or Electrostatic plotter output.

#### CONNECTION NET LISTING

\*\*\*\*

A1

51

ALL ST

11

62 3 1 A4 03 12 1 A2

U2 8 U2 13 U11 13 U7 10 U4 10

8 1 1

NATION AL

NATION.

-

-

=

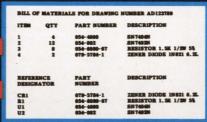

#### **BILL OF MATERIALS**

"DS1" automatically provides Net and Bill Lists directly from data base of digitized schematic.

#### P.C.B. ROUTER INTERFACES

ASI-PRANCE AUTOMATE '80 COMPUTERVISION REDAC SCICARDS™ others available "DS1" interfaces to P.C.B. Routers, Wire Wrap, Simulation and Test Programs.

#### UPDATED SCHEMATIC

"DS1" performs Back-Annotation from a "Was-To" list derived from the P.C. Router. "Back-Annotation" automatically updates the schematic to agree with the circuit board component placement.

Write 7 on Reader Inquiry Card

## **DESIGNAIDS inc.** 27822 El Lazo Road, Laguna Niguel, California 92677 • (714) 831-5611

#### **Technology Trends**

#### When Are 4 Crays Not Enough?

Truly a national computer resource, the Los Alamos facility, operated by the University of California for the US Department of Energy, is one of the most extensive computer complexes in the world. Early in May, the press was permitted to peek at the vast range of capabilities hidden in the Northern New Mexico mountains. A day packed with information stimulated discussion about the future super computers.

The extremely sophisticated staff at Los Alamos feel that the present facility is probably two super computer generations away from today's needs. Current needs are barely being met by the Cray 1 machines and by 1990, a machine 100 times more powerful than a Cray 1 or Cyber 205 will be needed for weapons design. They expressed concern that the next generation of super computer may not come soon enough or be good enough. They are also deeply concerned about the nationality of the next super computer generation.

Strong signals coming from Japan indicate that the next super computers may be Japanese. Los Alamos has already started looking at the proposed supers now being developed in Japan. On this side of the Pacific, little seems to be happening in the development of a new super; at least, not with the same level of R & D funding and government investment.

Certainly if the next generation of super computers does originate in Japan, there will be a few more American companies in troubleto say nothing about our technolgical leadership. It is a dilemma for an organization like the Los Alamos National Laboratory and for the US super computer producers, too. Can a government organization buy imported computers? Yes, under our present laws a US subsidiary of a foreign company can sell to the US government as though it were a domestic supplier, if it follows the

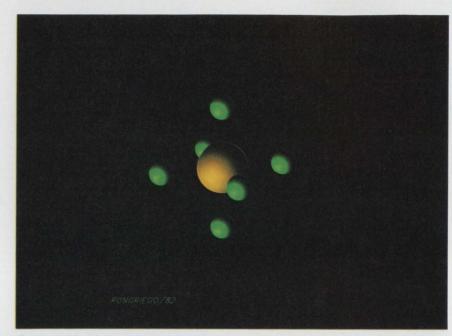

Figure 1: The above representation of an  $SF_6$  molecule was created at Los Alamos National Laboratories by Ronald Griego.

existing rules.

Of course, the other consideration in procuring foreign computers for a strategic resource like Los Alamos would be national security. Media day organizers at Los Alamos did not make this their main issue; however, it is one that the US government and the US computer industry must face in a very short time. Will the US computer manufacturers be able to leap ahead to meet the needs of Los Alamos and other government facilities, or will they concentrate their efforts on shortterm markets? The non-government users of the current Crays and other supers now include oil companies and other businesses that do not need to move ahead as fast as Los Alamos. This commercial market is also larger than the government market, so it will get the most attention.

#### **Super Computers**

From a few mechanical desk cal-

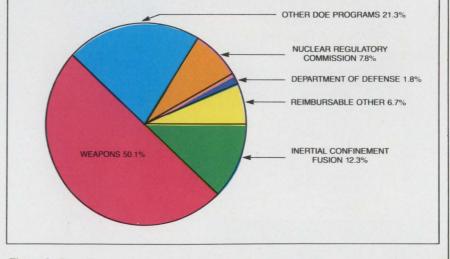

Figure 2: Distribution of computing services, fiscal year 1981.

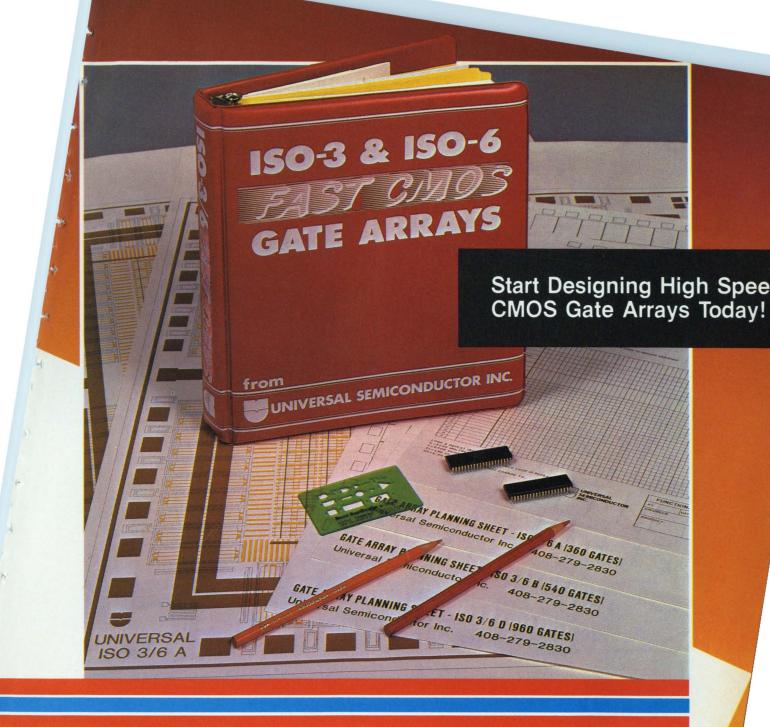

÷

Fast CMOS Arrays. Here's the design tool you've been waiting for! The ISO 3/6 Fast CMOS Design Manual contains all you need to know to implement your digital designs on high performance gate arrays. Sections on technology, CMOS logic design, macrocells, placement, interconnect, testing, and packaging—all clearly written and illustrated guide your engineering efforts. Design aids such as 200X layout sheets, macrocell planning sheets, test planning sheets, and special interconnect tools—all developed by IC experts—enable you to design in an integrated circuit format. Evaluation samples allow you to characterize the technology using your own equipment. **Start Today!** The 227 Page ISO 3/6 Design Manual is priced at \$69. and is available from stock. Order today and you can start designing new circuits or converting your old metal gate CMOS or TTL designs using modern Fast CMOS Arrays. You'll choose from a family of arrays ranging from 360 to 1500 gates with propagation delays as low as 1ns and toggle rates as high as 75MHz. Now is the time to reduce costs, save space, increase reliability, and lower consumption by employing gate arrays in your products.

To order the ISO 3/6 Design Manual, write or call: UNIVERSAL SEMICONDUCTOR, INC., 1925 Zanker Road, San Jose, CA 95112 (408) 279-2830

UNIVERSAL SEMICONDUCTOR INC.

Write 20 on Reader Inquiry Card

# Modgraph GMD Display Generators...

High Performance Graphics at an Unbeatable Price!

A tough statement backed by a unique modular approach. Buy only the capability you need.

Modular in design, configurations are available ranging from single

board B/W graphics to full color image display systems at resolutions from 512 X 512 to 1024 X 1024.

Graphics memory is switchable from 30HZ interlace to 60HZ repeat field for flicker free display at no additional cost.

Compact Modular Design

512 X 512 to 1024 X 1024 resolution

- Interlace or Repeat Field

128 ACII Character Generator

- 1-15 X Character Magnification

- On Board 8 or 16 Bit Interface

- □ RS-232 Interface

To fully appreciate the Modgraph GMD Display Generator, you have to see it in action. We'll arrange for a demonstration and show you the latest in high performance graphics at an unbeatable price.

Modgraph, Inc., 1393 Main Street, Waltham, MA 02154 (617) 890-5764

Write 23 on Reader Inquiry Card

#### **Technology Trends**

culators used in 1943 to design the first atomic bombs, the Los Alamos National Laboratory has become a world leader in using computers. Today, four Cray 1 machines with 6 trillion words of permanent memory form the nucleus of the Los Alamos computer operation. Over 3500 users are connected to one of the most complex computer networks ever assembled for interactive time sharing.

Crays are only the tip of the Los Alamos computer pyramid. In fact, a pair of DEC VAX 11/ 780 are used to operate the Crays. More than 50 other VAX machines are used along with four CDC 7600's, a CDC 6600, and a pair of CDC Cyber 73's to round out the main computing facility. At any given time, the 3500 users have access to about 2.7 trillion words of on-line storage in vast disk forms. Another 4 trillion are stored in IBM 3850 Mass Storage Systems, and these tapes perform like linear disks, with average access time running 10 seconds for any data. The 3850 storage system is managed by an IBM 370/148 and 4341 control processors. Two of the latest model Crays have internal memory capacities of 4 million, 64-bit words.

What can you do with all of this computing power and memory? Things most scientists would like to be able to try. Just think of the results that can be obtained running a program on a Crav for 10-20 or even 100 hours. Problems in hydrodynamics, Monte Carlo techniques, creating a data base for DNA studies, designing nuclear, laser, and particle beam weapons, or searching for safer, more efficient methods of disposing of nuclear wastes are only a few of the daily problems tackled at Los Alamos. By 1990, Los Alamos expects to have 5000 to 6000 users operating on an even bigger network.

Three separate types of computing services are carried out at Los Alamos. First, is open scientific calculation used for a wide range of energy, defense, earth

| QUANTITY | DESCRIPTION                                       |      | TOTAL POWER<br>(CDC 6600-1) |

|----------|---------------------------------------------------|------|-----------------------------|

| 3500     | USERS                                             |      |                             |

| 4        | CRAY-1                                            | CTSS | 64                          |

| 4        | CDC 7600                                          | LTSS | 16                          |

| 1        | CDC 6600                                          | NOS  | 1                           |

| 2        | CDC CYBER 73                                      | NOS  | 1                           |

| 50       | DEC VAX 11/780 (DP/s)                             | VMS  | 10                          |

| 1        | COMMON FILE SYSTEM (CFS)                          | VS1  |                             |

| 1        | OUTPUT STATION (PAGES) (TWO VAX 11/780)           | VMS  |                             |

| 1        | PRODUCTION CONTROLLER (FOCUS)<br>(TWO VAX 11/780) | VMS  |                             |

Figure 3: Los Alamos National Laboratory's major computing resources.

and space sciences, life sciences, chemistry, physics and mathematics. Second, is the administrative operations of the laboratory and its staff of near 7000 people (2700 are technical staff, and half of the staff holds a Ph.D). Third, is the classified computing involved in designing, developing, and testing nuclear and beam weapons for the national defense. This type of computing may account for more than half of the computer usage. It also presents very special problems of security with 3500 users on line.

#### A Real Computer Network

Keeping 3500 users happy is a challenge few computer installations have been forced to meet at the level of scientific computing performed at Los Alamos. Not only must the network manage the communications and time sharing on the vast array of computers, but the hardware must remain transparent to the users. This permits users to work on a variety of computers, depending on availability and the scope of the problem.

Network switching is performed by three VAX 11/780 machines with PDP-11's serving as concentrators and switches. The entire network is interconnected with miles of coax, and fiber optic links are being installed for new equipment.

User terminals have been standardized throughout the facility to TI Silent 700 series, DEC VT100, Tektronix 401X series, and Advanced Electronic Devices' 512's for color graphics. RS232 standards are used; however, by standardizing the network and all of the equipment uses, it becomes much easier to keep the network running without problems. Standard user equipment also helps make the entire system transparent. User codes, for example, are preserved even if the hardware is changed or modified. Users really don't care what equipment is operating.

Classified user access is very tightly controlled with special access codes and verification procedures. Few details were available on the exact system and procedures used, but considering the level of security involved in nuclear weapons design, it has not been incorrectly accessed even by accident since its inception.

#### Modeling

While most computer models are 2-dimensional, Los Alamos is producing some 3-dimensional models. The concept of modeling is straight forward for most applications. In dealing with explosives, modeling in 3 dimensions is almost a must if the results of an explosive reaction are to be predicted. This is a very new area at Los Alamos; however, they appear to to be making rapid progress. In nuclear engineering, the 3 dimensions added to modeling, for example, are of extreme value in predicting failure modes in a reactor core or determining the smoke plume of a coal-fired pow-

#### **Technology Trends**

er plant.

Modeling problems, even 2-dimensional, are not easy or fast. On a Cray 1, the designer and the computer can work together very efficiently. A demonstration program run during media day showed how fast the problem of deforming a solid cylindrical object could be solved. While only a demonstration, the process took about 15 minutes on the Cray. The same problem run on the CDC 7600 would have required more than two hours.

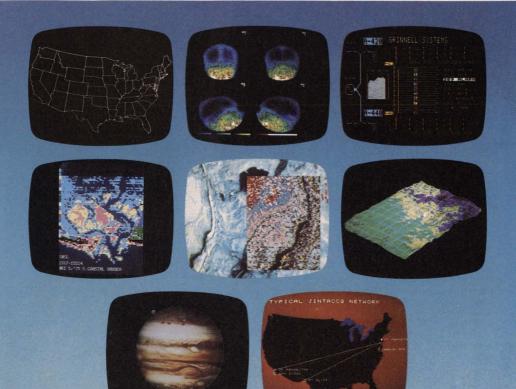

#### Graphics

Color graphics at Los Alamos are enough to make anyone envious. In addition to the CRT displays, hard copy capability is up to 80,000 printed pages per day. In addition, the graphics system can record 150,000 Microfiche images per day along with 6000 frames of 16 mm film and 3000 frames of 35 mm film. About 400 plots, 11 inches wide, and 75 plots, 36 inches wide, can also be turned out in a day. Turnaround time is one hour for paper copy, four hours for Microfiche, and overnight for color film.

#### **The Future**

It is hard to imagine that with all the computing power available, the Los Alamos National Laboratory has a problem getting the job done; but they do. Some of the problems they attempt to solve are so complex that they tax the power of the Crays to the limits.

The next step is bigger and faster parallel processors—100 times more powerful than the Crays. Better algorithms may have to do for now, but to support the modeling needs of Los Alamos alone, the only practical solution appears to come from higher speed, parallel processing. Josephenson Junction machines may be part of the solution, but for the short term, the problems with JJ machines may keep them from practical applications for some time. The US main frame manufacturers have a problem meeting the needs of Los Alamos and other government computer centers.

The number of super computers needed for this government segment of the market is too small to justify the large amounts of R & D necessary to solve the problems. Like the semiconductor industry, the computer business is driven by market share, and it can be very costly to serve such a small market with the highest technology. Japan, a country that has government support for its electronics industry, may be willing to risk the R & D investment to gain control of the high end of our computer business-then the middle and the low ends may follow.

-Groves

# Hiring Specialized Engineers CAREER OPPORTUNITIES in Digital Design

Readership: Over 62,000 + qualified engineers and managers at 18,000 + important design locations.

Editorial: Look for a new column on employment trends to accompany recruitment advertising.

Rates: \$85 per column inch

3 column x 10" page — \$2500 (1x B&W)

Contact: Bill Pryor, Manager, Recruitment & Classified Advertising, Morgan-Grampian Publishing Co., 1050 Commonwealth Ave., Boston, MA 02215 (617) 232-5470.

# LASTING MEMORIES.

#### **Plessey** makes memories you'll never forget.

how burn

The inspect every solder connection and component.

O.K. So a scrapbook may be stretching the point. But the fact is your Plessey memories are made so well, the only thing you'll forget is downtime.

Plessey memories are quality designed, 100% inspected, and fully burned in to insure dependable operation. And we exercise each memory with every diagnostic program in the book-using a computer just like yours.

You get complete documentation, lasting performance, and access times up to 40% faster than DEC\*. In either MOS or core.

Plus, every Plessey memory is covered by an extensive 12-month warranty. That's 4 times longer than DEC.

\*DEC is a registered trademark of Digital Equipment Corporation.

#### Focus on Plessey.

We've led the DEC-compatible memory market for more than a decade. And now we're really looking ahead.

diagnos insures your

With increased computer-controlled production. Our new warranty program. Tough, competitive pricing. Even local availability. Worldwide.

So if you need memories, focus on us. Forget about downtime.

When it comes to memories, Plessey's the one to watch.

**Plessey Peripheral Systems** TOLL FREE: 800-854-3581 714-557-9811

Plessey Peripheral Systems, Inc. warrants products of its manufactu from defects in workmanship and material as follows:

HWARRA

xerc

#### **Market Trends**

#### Japan Leads Robot Boom

In the exploding robot market, Japan is clearly the leader. There are more than 70 Japanese robot manufacturers—more than twice the number of second-ranked West Germany, and nearly three times as many as the United States. Japan also leads in number of installations, with 14 times more robots in use than in the US.

Despite Japan's high production levels, very few robots have been exported, primarily because demand in Japan has exceeded production. Another factor is that robots have not traditionally been mass-produced, making largescale exports unlikely. In 1974, only 2.9% of Japan's production was exported. This rose to 4.5% in 1977, but dropped again to 2.6% in 1980. According to this report, however, this trend is likely to reverse. Several Japanese manufacturers are looking toward increasing their exports; Dainichi Kiko Co, is exporting about 60% of its production, and Mitsubishi plans to export 30% of its production by next year. Another significant trend is the growing number of joint ventures between Japa-

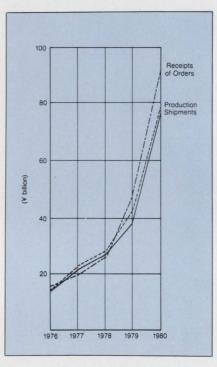

Figure 1: Japanese robot industry growth

nese, European, and US companies (e.g., Hitachi and General Electric; Fujitsu Fanuc and Siemens; and Kawasaki, Unimation, and ASEA).

Unimation has recently an-

nounced the receipt of over \$12 million in robot orders from major foreign and domestic automobile manufacturers. The Unimate robots are destined to go to Chrysler, Ford, British Leyland and Daimler-Benz. Unimation will soon supervise the installation of sixty-nine Kawasaki Unimate robots in the Nissan Motor manufacturing truck body assembly plant in Tennessee.

A 228-page report is available from Venture Development Corporation of Wellesley, MA. Industrial Robots Industry in Japan, published by Yano Economic Research Institute Co., Ltd. of Tokyo, presents a comprehensive analysis of the Japanese robotics industry. According to the report, nearly 20,000 robots were produced in Japan in 1980, and estimates for 1981 indicate a five-fold increase in unit production. Since 1976, annual growth in production has ranged from 26% to more than 100% leading to a cumulative total of 76,700 units produced in Japan since 1968. For more information, write: Venture Development Corp., One Washington St., Wellesley, MA 02181.

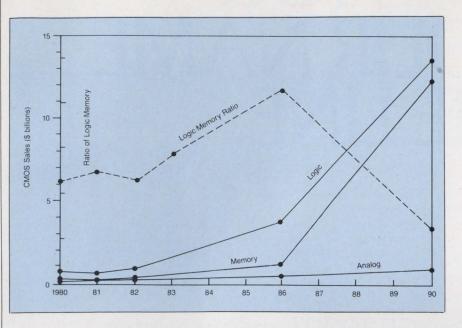

#### CMOS Markets Top \$26.8B In 1990

By 1985, CMOS will displace NMOS in one of the greatest evolutionary transitions in this decade. Although IC makers, board makers, and OEMs recognize that CMOS is improving in speed, many fail to comprehend the magnitude of this transition.

Once used only in watches and calculators due to its slow speed,

low power consumption, and its noise immunity, newer CMOS parts offer 2ns switching speeds, lower power consumption, greater alpha particle immunity, and ultimately lower per-cost functions than bipolar or NMOS.

Both US and Japanese companies are developing high-performance CMOS chips. National Semiconductor is aggressive and is developing CMOS versions of its NS16000 16- and 32-bit  $\mu$ Cs; Intel is backing into CMOS and has developed 1K, 4K, and 16K static RAMs; and Motorola has developed an 8-bit  $\mu$ P chip set compatible with its 6800 family. They and others are also developing CMOS gate array families.

# **AYCON 16/SERIES**

#### brings high performance color graphics down to earth.

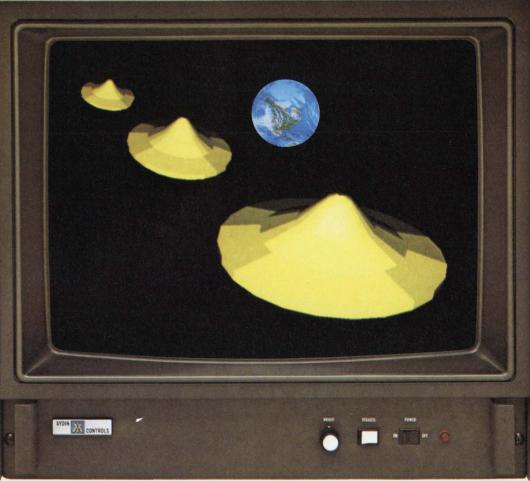

Only AYDIN CONTROLS' 15 years of experience in raster scan color graphics could bring you a display computer with the total capability of the AYCON 16/SERIES...and now at such an affordable price!

The overwhelming acceptance of the AYDIN original Model 5216 allows us to offer an enhanced version of this field-proven unit. Check this unmatched combination of systems/hardware features available with the AYCON 16/SERIES:

- Up to 1024 x 1024 pixel x 16 bit (Z-axis) color display.

- Refresh at up to 60Hz.

- A variety of video modules.

- Characters in three sizes.

- Vectors at 800 ns per pixel.

- 80 x 48 character A/N overlay.

- Multiple 16-bit micro's. AYDIN software or you program them... even up to 14!

- Single or multiple WORK-STATIONS...up to four!

- High-resolution RGB monitors

delta or in-line gun.

#### And when it comes to Software/ Firmware:

- Graphics Firmware with fill and zoom standard!

- AYGRAF/CORE 2-dimensional Firmware/Software with Worldto-Screen translation, rotation, and scaling...world coordinates of 64K x 64K!

- Plus AYGRAF/3D, AYGRAF/ LIST, and support Software.

But if all this is not enough to excite you, how about more economy with standard PACKAGED SYSTEMS, single or multiple WORKSTATION pre-engineered for the most common color display applications?

If you're ready to fly with your color graphics display application, we can help you "get off the ground" with a system to meet your industrial, business, scientific or commerical requirements.

Aydin Controls

414 Commerce Drive, Fort Washington, PA 19034 (215) 542-7800, TWX: 510-661-0518 Telex: 6851057

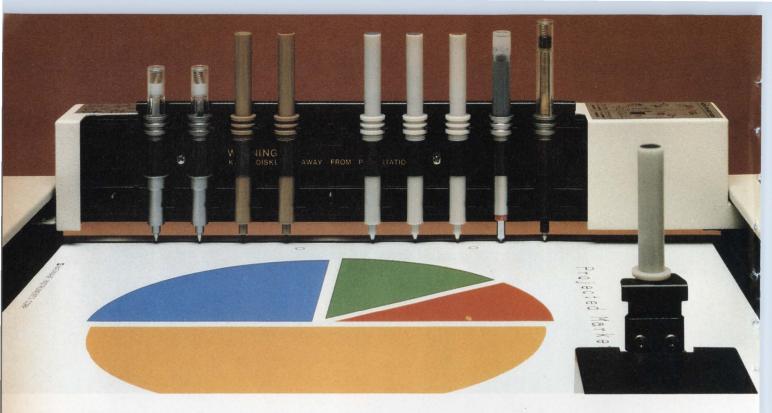

## Watanabe plots color. Fast, accurate and easy as pie.

Watanabe brings you a multi-pen digital plotter you can even use at your desk. Its low cost makes it affordable. And its sophistication makes it the answer to your need for economical high-speed, hard-copy graphics. Whether for engineering drawings, scientific plotting, architectural design, or business graphics.

**Easy to program and use.** You don't have to be an engineer to use a Watanabe plotter. Yet it can produce complex engineering drawings. Intelligence is built into the plotter through our unique microprocessor controllers.

So it can perform complex tasks using the single-letter commands you give it. Programs are also simple to write, making the plotter very convenient to use. Or you can

use one of the many software packages available for Watanabe plotters.

#### Choose the model that's

**right for you.** Why pay for features you don't need? Watanabe

plotters are available in a variety of models. One will be best for your budget and graphics needs. Choose from our low cost, single-pen plotter, through a range of multi-pen configura-

tions, to our high-speed, intelligent plotters. Or select a machine that blends analog and digital technology.

Use water or oil-based pens, or ink pens. Choose from sheet-feed or roll-feed models, or produce drawings on acetate for overhead projection. In addition to programmable graphics and function commands, the complete ASCII character set is standard. Each plotter can interface to any computer with an RS-232-C serial interface, IEEE-488 interface, or parallel port.

**Designed for long use.** Just one example of Watanabe's built-in reliability is the ingen-

iously simple, automatic mechanical pen pickup used on the multi-pen models.

When your plotter does need maintenance or repair,

one of our many locations worldwide will provide prompt service. We design, manufacture, and service our plotters ourselves. So we know we can stand behind them with confidence.

**Let us put a plotter at your fingertips.** Call Don Pierson toll-free at (800) 854-8385 to arrange a demonstration. In California call (714) 546-5344. Or write: Watanabe Instru-

ments Corporation, 3186 Airway Avenue, Costa Mesa, California 92626.

Write 12 on Reader Inquiry Card

#### **Market Trends**

By 1990, the worldwide CMOS market will grow to 26.8 billion. The market for CMOS, in billions of dollars, remained essentially flat up to this year, but will begin a moderate rise in logic, but little in memory, partly because of vendor commitments. In 1986, both logic and memory will assume spectacular growth. The logic/memory ratio (dotted line) will be greatest (about 4.4) in 1986, and rapidly plunge thereafter.

CMOS will not only impact bipolar manufacturers such as Precision Monolithics and Monolithic Memories, but even giants like IBM, DEC, Hewlett-Packard, and Western Electric that have large existing commitments in NMOS and bipolar, and little apparent interest in CMOS at this time. These captive suppliers and others with similar IC technology commitments may see their competitors gain market share in the future as a result of producing CMOS-based equipment with superior performance and lower cost.

These projections were excerpted from a comprehensive CMOS study, report no. 1004, "The Impact of CMOS On Competing IC Technologies" (\$1500). For more information, contact: Mrs. Alenne Glock, Customer Support, Strategic Inc., 4320 Stevens Creek Blvd., Suite 215, San Jose, CA 95129. Tel: (408) 243-8121.

# Brushless DC Motor Beau's Best

For applications requiring precise speed control, Beau Motors has a line of Brushless DC Motors with tachometer. Imagine these features for your next application: controllable to less than one  $\mu$ s/rev at 1800 rpm, high starting torque (over 200 oz/in) in a compact size and low shaft TIR of .0002.

Beau also offers competitively priced, general purpose brushless DC motors for applications requiring simple speed control. We will customize motor designs to suit your requirements. Call or write for our new product catalog.

Write 36 on Reader Inquiry Card

# IT'S TIME YOU PUT YOUR NAME ON THE LINE.

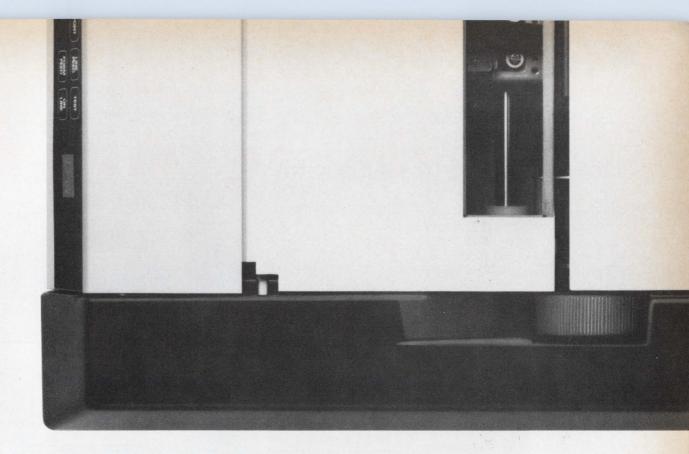

## Introducing the new GE 3000 family of printers.

FONT

FORM ON LINE

On

WHEN WE DESIGN A PRINTER, WE HAVE YOUR IDEAS IN MIND.

When you put your name on this line of printers, you'll find the GE 3000 family is the best idea you ever had.

At GE, we've developed a very basic philosophy...when an OEM speaks, we listen. It sounds simple, but just try talking to other suppliers.

The new GE 3000 family of serial printers is the perfect example. Compact, lightweight, and functionally styled, these tabletop matrix printers are specifically engineered for the OEM supplier.

Our new line of six printer models offers cost effective solutions to virtually all your printing requirements. Standard print quality from 180 to more than 500 cps. Near letter quality from 100 to almost 200 cps. 80 and 136 column models.

A full range of standard features such as  $72 \times 72$  dot/in. graphics with precision paper movement, self-threading paper load mechanism, close tear-off, six part forms capability, popular parallel and serial interface, and local and downline configuration selection with non-volatile storage. Plus a range of options and paper handling accessories for office and factory applications. And everything backed up by worldwide GE service.

> Now You Can Solve Your Customer's Needs Efficiently and Effectively.

The GE 3000 family is designed to offer OEM's the advantage of single-design simplicity...

without the application limitations of a single model product line.

GENERAL

The GE 3000 gives you configuration flexibility. Application flexibility. Design commonality and price/performance leadership.

#### OF COURSE, INNOVATIVE IDEAS ARE NOTHING NEW TO GE.

Our roots go back to Thomas Edison. It was in his tradition that in 1969 we introduced the first electronic data printer with modern LSI circuitry. Since then, we've continued in that inventive spirit, supplying OEM's with the finest in advanced printer solutions...longer than any other printer supplier.

General Electric. We're the industry leader in electronic printing. After all, we pioneered the industry in the first place.

Write 34 on Reader Inquiry Card

### First In Electronic Printing.

For the solution to your printing needs, call TOLL FREE 1-800-368-3182, General Electric Company, Data Communication Products Department IN3S1, Waynesboro, VA 22980. In Virginia, call 1-703-949-1170.

ELECTRIC

#### **Applications Notebook**

#### Free Samples Of 4K x 4 Static RAMs

The Inmos IMS1420 is a high performance 4K x 4 static RAM having maximum Chip Enable  $(\overline{E})$ access times of 45 and 55ns, with a maximum power dissipation of only 600mW. The use of innovative design techniques as well as the latest VLSI technology have combined to produce these characteristics. The IMS1420 features fully static operation requiring no external clocks or timing strobes, equal Address access and cycle times, full TTL compatibility and operation from a single +5V supply. A Chip Enable function provides standby operation reducing power consumption to less than 165mW maximum. The device is housed in a 20-pin, 300-mil DIP.

The Intel 2147H is a 4K x 1 static RAM, having maximum Address and Chip Select ( $\overline{CS}$ ) access times of 45 and 55ns. The maximum power dissipation is 990mW with a standby power dissipation of 165mW. As with the IMS1420, the device is fully TTL compatible and operates from a

+5V power supply. The 2147H is packaged in an 18-pin, 300-mil DIP.

When comparing the memory devices, the similarities in the pinouts show that both devices are identical in the number of address pins, and both have WRITE ( $\overline{W}$ , WE) and SELECT ( $\overline{E}$ ,  $\overline{CS}$ ) control input functions. The differences in the pinouts show that the IMS1420 has 4 common I/O data pins while the 2147H has separate data-in and data-out pins. Com-

Figure 2: The data I/O pins of the IMS1420 are each tied directly to a bidirectional data line of the data bus.

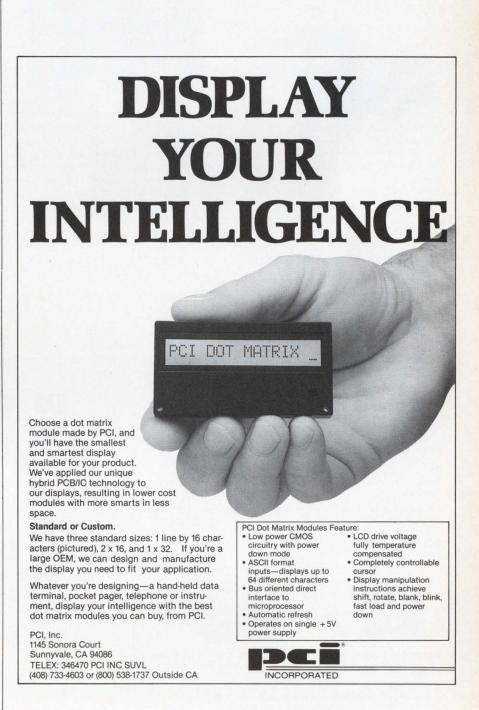

#### IF WORDS ALONE AREN'T GRAPHIC ENOUGH, USE DECO'S NEW HIGH RESOLUTION GRAPHIC DISPLAY MODULES!

DECO offers the latest in display technology. Close dot spacing and Vacuum Fluorescent technology make the display bright, sharp and highly readable even in daylight with proper filtering. Each dot is independently addressable allowing formation of almost any character or shape the mind can imagine! Graphs, charts, ideograms, waveforms and more can all be displayed. Even reverse video is possible. Complete drive, interface, control logic, refresh and buffer electronics are on board. Only +5 VDC is required to power the unit.

#### **3UI,** IF WORDS ARE WHAT YOU WANT, DECO'S

#### SUPER SMART

M128<sup>2</sup> Thin profile and low voltage made the M128<sup>2</sup> an ideal alternative to CRT in many applications.

intelligent

DECO.

Alphanumeric Displays are specified by engineers all over the world. The bright vacuum fluorescent characters are **highly readable** and filter from natural blue-green to blue, green, aqua, amber and red. VF tube technology offers **high reliability** and tube MTTF up to 100,000 hours. Low Power requirements (as low as 65 milliwatts/character) are well below the dissipation of LED or gas discharge displays. DECO's displays are **self-contained ready to use** subsystems. They are microprocessor controlled with all drive, refresh, interface, control logic and buffer circuitry on board. Some units have user programmable character generators. All models have on board power conversion circuitry. Just input +5 VDC and a 7-bit ASCII signal and you're in business!

> **M26 x 256** is ideal in many foreign language or mixed character size applications. Intermix graphics and alphanumerics at user option.

ateManomenic displays

**DECO'S SINGLE LINERS** come in a wide range of sizes from 10 to 40 character positions and 5mm to 9mm character height. 14 segment, 5x7 and even 5x12 matrices available.

#### WORLDWIDE DISTRIBUTION

United States Digital Electronics Corp. (415) 342-8333

United Kingdom/Ireland Auriema Ltd. 6286-4353

> France Alfatronic S.A. 791-44-44 ext 5735

W. Germany/Austria Bitronic GmbH 089-470-2098

Switzerland/Liechtenstein Memotec AG 063-281122

Sweden/Denmark Auriema AB 08-730-5160

Netherlands Auriema Nederland BV (040) 816-565

Norway Schive Electronics 02-785-160

Italy Auriema Italia SRL. 02-430602 Spain Unitronics S.A. 242 52 04 Israel

Talviton Electronics Ltd. 444572

Australia/New Zealand Romtech Pty. Ltd. 02-6014511

Brazil/Argentina/Greece Turkey/So. Africa/Taiwan Ad. Auriema Int. (212) 938-0930 (New York, N.Y., U.S.A.) Belgium/Luxembourg

Betea, SA/NV (02) 7368050

Canada John G. Weiss & Co. (514) 337-5022 (416) 624-7359

Finland Oy Gronblom AB 90-755-4411

Local representation throughout the U.S.

Additional and a second second

**JPER FAST**

These 5x7 dot matrix displays offer the fastest data transfer rate available and are completely flicker free.

M6400 6 lines x 40 characters M2400 2 lines x 40 characters

THE DISPLAY INNOVATORS

DIGITAL ELECTRONICS CORPORATION

197 AIRPORT BLVD., BURLINGAME, CA 94010 • (415) 342-8333 • TELEX: 334422 CHEMETRIC BRGM

Write 15 on Reader Inquiry Card

DIGITAL ELECTRONICS CORPORATION

parison of the READ and WRITE cycles of the devices shows equivalent Chip Enable access times, but shorter Address access and cycle times for the IMS1420.

#### Interfacing

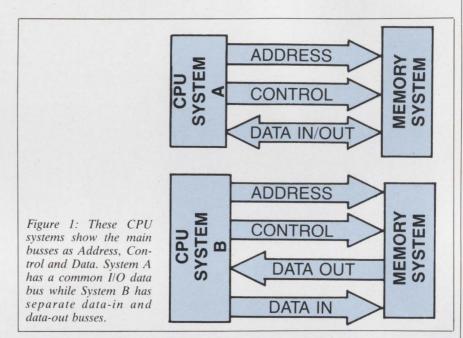

The CPU systems shown in **Figure 1** show the main busses as Address, Control and Data. System A has a common I/O data bus, while System B has separate data-in and data-out busses.

Interfacing to the address and control bus connections for both systems is straightforward and identical for the 2147H and the IMS1420, with one exception. The 2147H requires the use of a pullup resistor to V<sub>cc</sub> on the chip select pin, to prevent the device from powering up in the select mode when V<sub>cc</sub> is first applied. With the IMS1420, when  $V_{cc}$  is first applied to pin 20, a circuit associated with the  $\overline{E}$  input forces the device into the lower power standby mode regardless of the state of the  $\overline{E}$  input. Therefore, a pullup resistor from  $\overline{E}$  to V<sub>cc</sub> is unnecessary. After Vcc is applied for 2ms, the  $\overline{E}$  input controls device selections as well as standby and active modes.

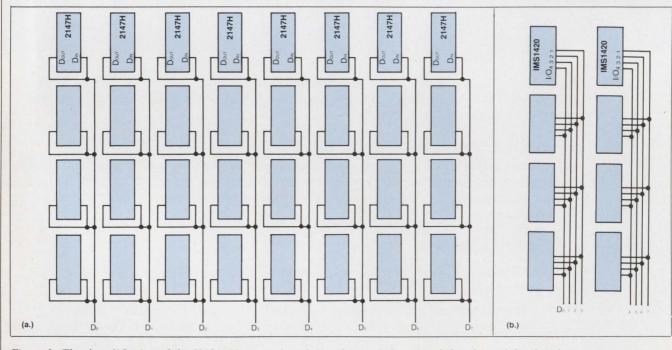

Interfacing to CPU System A is almost the same for the IMS1420 and the 2147H. The data-in and data-out pins of the 2147H are tied together, and then tied to a bidirectional data line of the data bus. The data I/O pins of the IMS1420 are each tied directly to a bidirectional data line of the data bus. (Figure 2a and 2b).

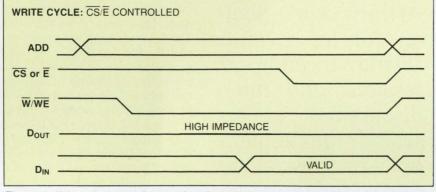

Bus contention between data coming into a memory device and data going out of a memory device is only a problem during the WRITE cycle. If  $\overline{CS}$  goes low a period of time before WE goes low, the device output driver could become active during the time that the input data is placed on the bus. Since both the CPU system and the memory device would try to drive the same data bus line, large current transients can occur. To prevent bus contention, the  $\overline{CS}$  must go low after  $\overline{WE}$  goes low, keeping the memory output driver in high impedance. Thus, when the input data is placed on the bus, no contention occurs between the output driver of the device and the output driver of the CPU system. This is called a Chip Enable controlled WRITE cycle (Figure 4).

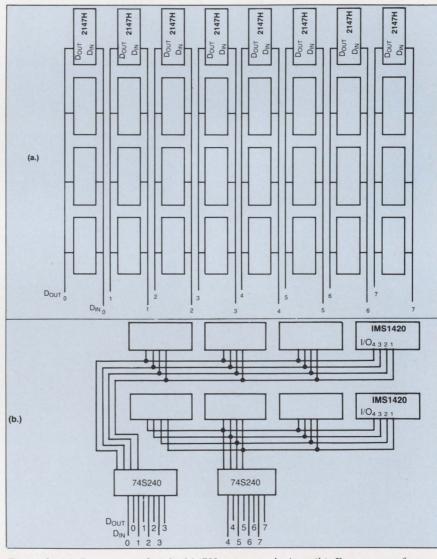

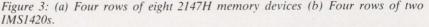

The most direct approach to interface 2147H memory devices to CPU System B is shown in **Figure 3a.** Four rows of eight 2147H memory devices are each connected directly to separate data-in and data-out lines. Because the data input and output lines are separate, no special timing during the WRITE cycle is necessary to prevent bus contention.

Four rows of two IMS1420's each can interface to CPU System B, using two 74S240's (or similar bus driver) to interface to the separate data-in and data-out busses. This can be accomplished as shown in **Figure 3b**. The timing for the READ cycle would remain the same, but in the WRITE cycle (**Figure 4**), only a Chip Enable controlled WRITE cycle

#### **Applications Notebook**

could be used. This would keep the data-out drivers of the IMS1420's in the high impedance state during the WRITE cycle, preventing any data bus contention with input data.

#### Savings

With CPU System A, each IMS1420 could replace four 2147H memory devices.

|          | 2147H               | IMS1420            | NET<br>SAVINGS      |

|----------|---------------------|--------------------|---------------------|

| No. of   |                     |                    |                     |

| Packages | 32                  | 8                  | 24                  |

| Area     | 17.6in <sup>2</sup> | 4.8in <sup>2</sup> | 12.8in <sup>2</sup> |

| Power    | 11.88W              | 2.2W               | 9.68W               |

With CPU System B, each IMS1420 could replace four

Figure 4: When the input data is placed on the bus, no contention occurs between the output driver of the device and the output driver of the CPU system; this is called a Chip Enable controlled WRITE cycle.

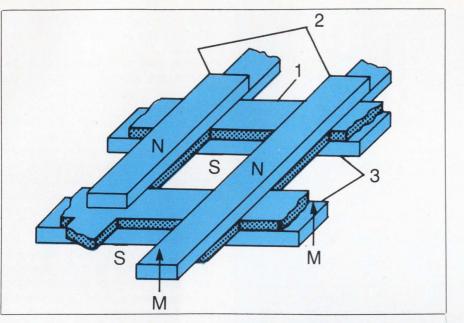

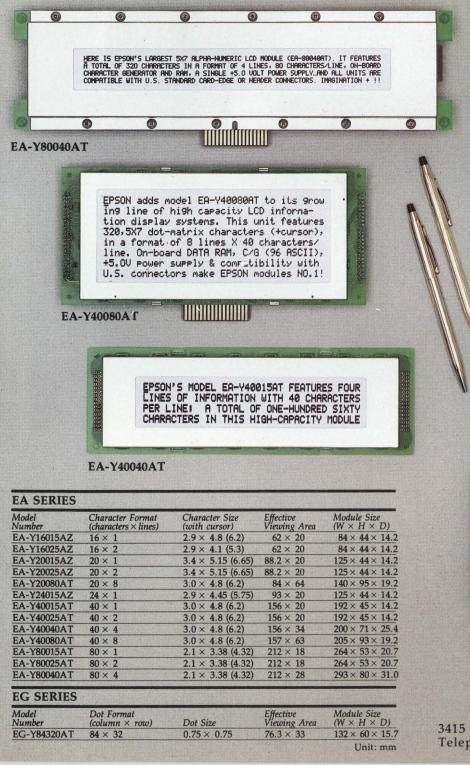

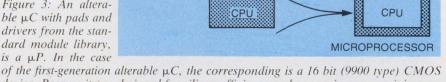

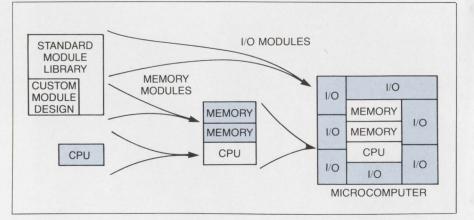

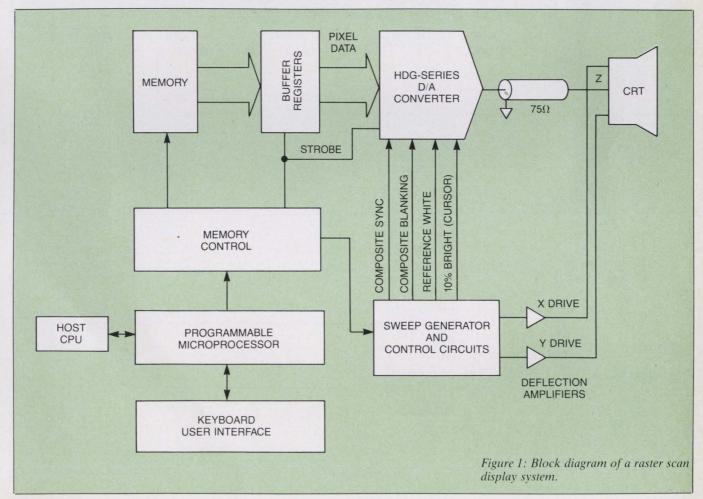

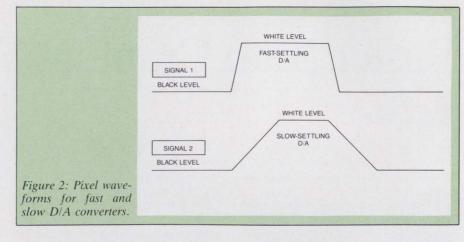

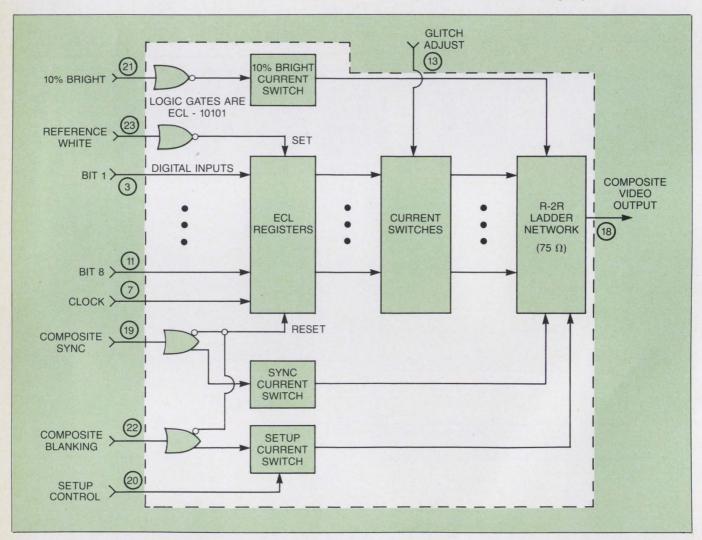

2147H memory devices, but two data bus drivers must be added. Still, a net savings can be seen.