Digital Design Computers • Peripherals • Systems DEC Directory

> GCR Improves Data Recording Shortened DFT Speeds Computation Controller Mates Disks To DEC Bus Cyclic Code Redundancy

> > distan

PDP 11/

SERIALS

LIBRARY

8109

485830

SERIALS

LIBRARY

8109

485330

SIRTE

TECHNICAL

INS

1L1

SIRTE

TECHNICAL

INS

44

SIRTE

TOV COVE

SUB

44

# When you ask some people about backup — they back off.

And for good reason. Ask any other supplier of peripheral products for system backup, and you'll find that some can supply a disk, some can supply a cartridge recorder, others a streaming transport. But none can supply the choice which Kennedy can offer.

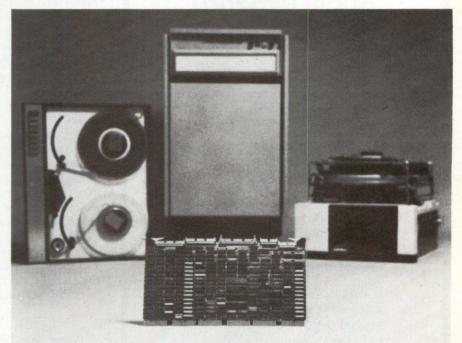

Kennedy is the only company that can offer an SMD compatible, 8" 40 MByte disk drive (Model 7300) and an 80 MByte 14" Winchester disk drive (Model 5380). To back them up, Kennedy has a  $\frac{1}{4}$ " cartridge recorder (Model 6450), and Model 6809,  $\frac{1}{2}$ " Data Streamer Tape Transport.

Kennedy was the first to utilize the 1/4" 3M cartridge for disk backup; Kennedy was the pioneer in Winchester disk technology, and was a leader in developing a low cost streaming tape drive.

All of these products were conceived and designed to meet the need for reliable, low cost backup — for our systems or for any other system.

Kennedy has always backed its products. That's why we're No. 1. Call or write us about your problem.

We won't back off.

1600 Shamrock Ave., Monrovia, CA. 91016 (213) 357-8831 TWX 910-585-3249

MODEL 7300

#### **KENNEDY INTERNATIONAL INC.**

U.K. and Scandinavia McGraw-Hill House Shoppenhangers Road Maidenhead Berkshire SL6 2QL England Tel: (0628) 73939 Telex: (851) 847871 KEN UKS G

KENNEDY INTERNATIONAL Koningin Elisabethplein, 8 B-2700 Sint-Niklaas Belgium Tel: (031) 771962 Telex: 71870 KEN CO

5380

### KENNEDY · QUALITY · COUNT ON IT

**Circle 2 on Reader Inquiry Card**

# Dec Users: Corvus Lowers the Price of Admission to the Winchester Club.

Attention DEC <sup>a</sup> users: Here's the price breakthrough you've been waiting for on DEC compatible Winchester disk systems. Our new 5<sup>1</sup>/<sub>4</sub>-inch 5-megabyte Winchester sells for one half the price (\$2900 in OEM quantities of 100) and takes up one half the space of the DEC RL01 it replaces. It's a complete disk sub-system, including disk drive, intelligent controller, and interface card. It brings sealed-environment reliability to your DEC LSI-11 system while directly emulating the RL01 with 100% hardware and software compatibility. Or if you need greater capacity, we can set you up with a 10 or 20 megabyte system.

\*\* CORVUS SYSTEMS

**5 MILLION BYTE**

MICRO WINCHESTER

DISK SYSTEM

Here are more of our exclusive features and benefits: • Single quad-size interface card to Q-bus • Compact rack or table top models • Multiprocessor backend network, the CORVUS CONSTELLATION, supports up to 8 LSI-11's • Low cost removable-media backup, the CORVUS MIRROR, uses proven video technology.

For the full story. contact CORVUS today.

an bi

PRICE: UNDER \$2900

WHEN: NOW!

WHERE: YOUR LOCAL CORVUS REPRESENTATIVE

CORVUS SYSTEMS

2029 O'Toole Avenue San Jose, California 95131 408 946-7700 TWX: 910-338-0226

8 Trademark of Digital Equipment Corporation

CORVUS SYSTEMS

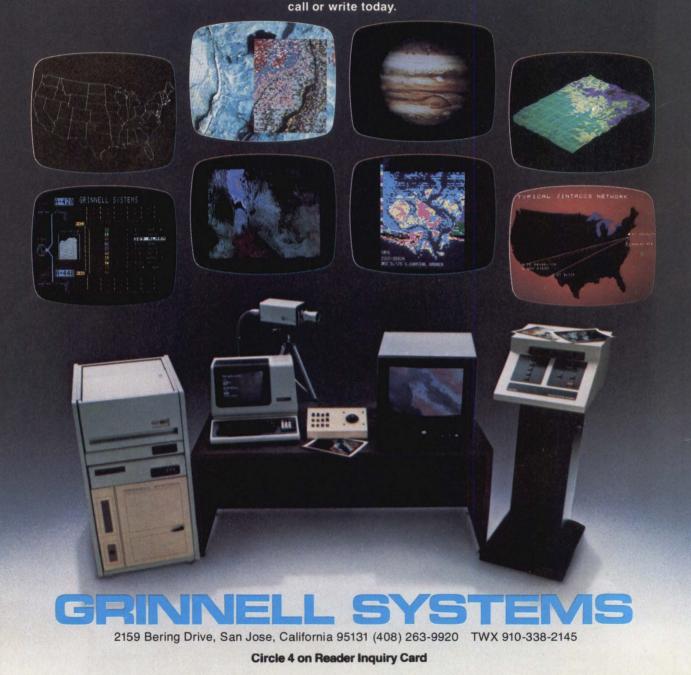

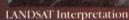

## Image processing systems Modular graphic display systems Frame buffers-Television monitors

Grinnell has them all, for almost any application: from simple black and white line drawing to full color image processing. Select a packaged system, or configure one "your way."

GMR 270 Series:  $512 \times 512$  frame buffers and full color pipeline image processing systems.

GMR 260 Series:  $1024 \times 1024$  frame buffers for greyscale, black and white, pseudo color and full color.

GMR 27 Series:  $256 \times 512$  to  $1024 \times 1024$  high speed, modular graphic and image display systems.

All systems are available in both U.S. and European versions, with plug-compatible interfaces to most minicomputers (including DEC, Data General and PRIME). Proven system designs ensure reliability, and an expanded FORTRAN library and driver package makes operation easy.

So, whether you need a complete system, or just a card set to embed in a larger system, Grinnell has an optimum cost/performance solution. For complete specifications and/or a quotation,

1.

Copyright © 1981 Benwill Publishing Corporation, a Morgan-Grampian company

Publication Number: USPS 407-010

### **Features**

### 22 Shortened Algorithm

9-W

5.

19-14 19-1

12.4

1

Q-4

jii.

23

-16

20

3

10 5

10

-10

14

. 9

-

mich

10

1

pr for

A shortened DFT algorithm achieves real time processing. This article describes both SDFT theory and its realization.

### 26 Microprogrammable Processor

The flag status bit storage concept fulfills microprogrammable processor needs.

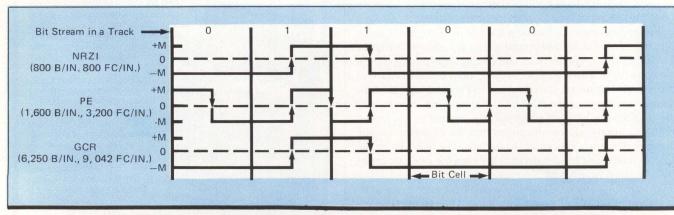

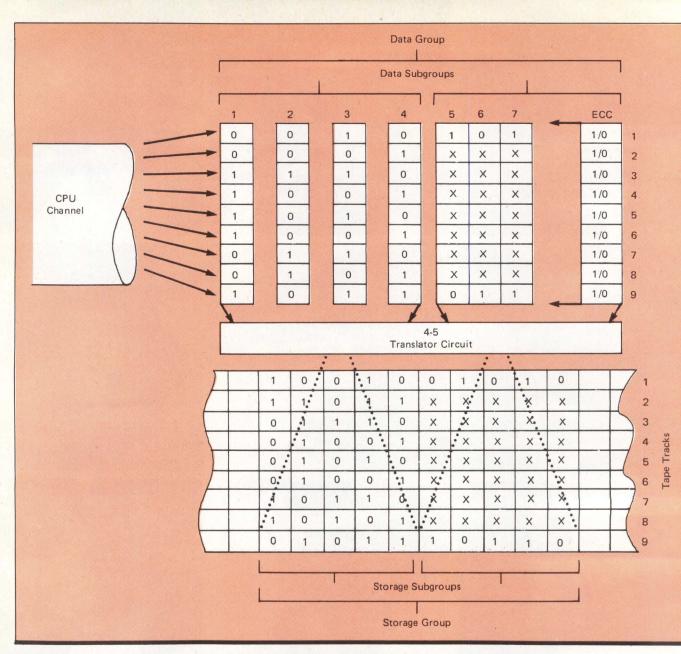

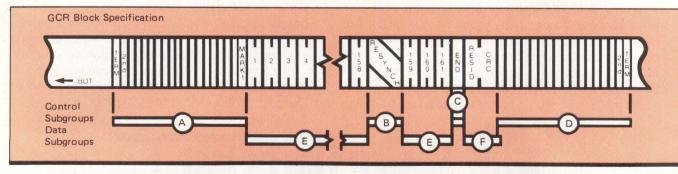

### 34 GCR Increases

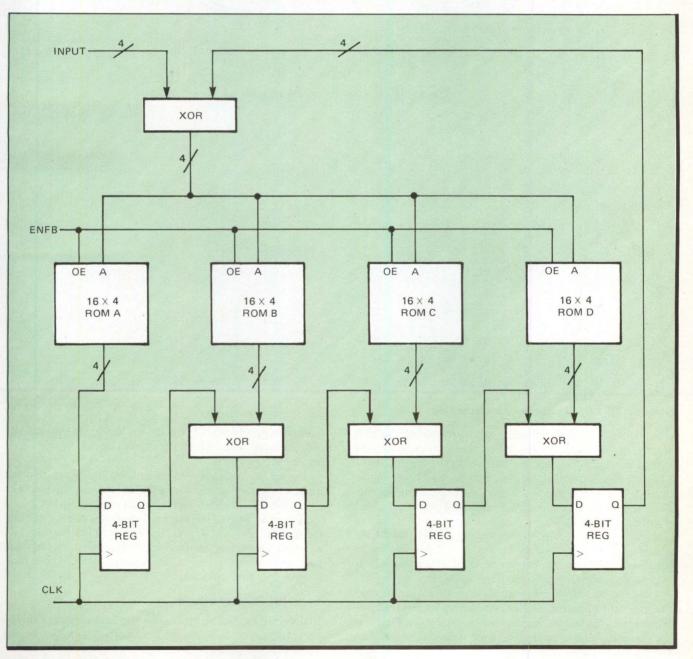

This article discusses data groups, AuxCRC or auxiliary cyclic redundancy character, ECC, resync bursts and other components that make up a CRC data block.

### 40 DEC Product Directory

A listing of DEC computer products — prepared for Digital Design by Digital Equipment Corporation.

**Departments**

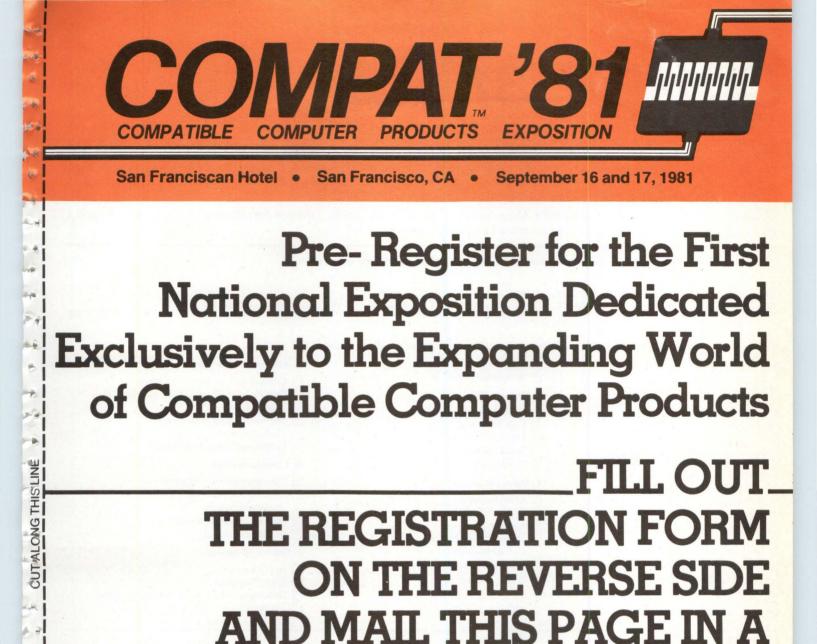

### 54 DEC Compatible Products Continue Upward Growth

The rapid growth of the DEC compatible market makes it all the more important that the OEM protects himself by carefully investigating.

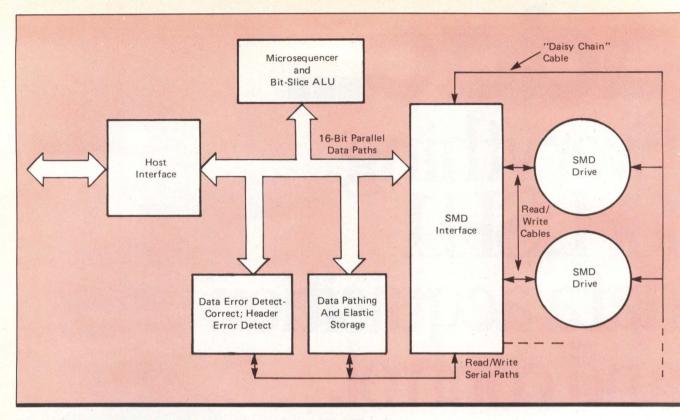

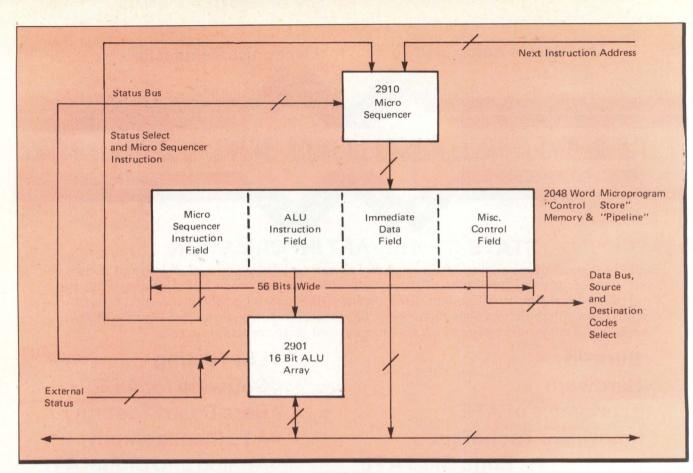

### 62 Bit-Slice Design

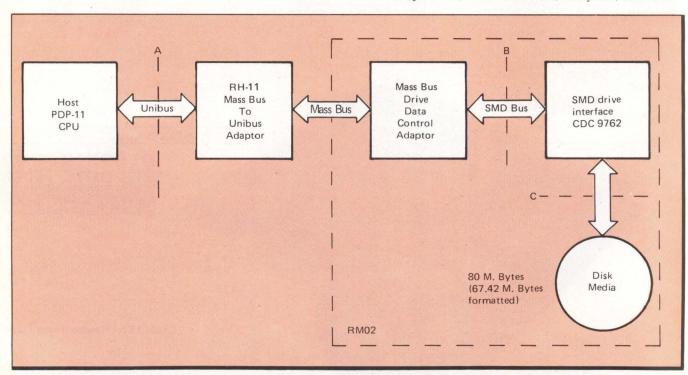

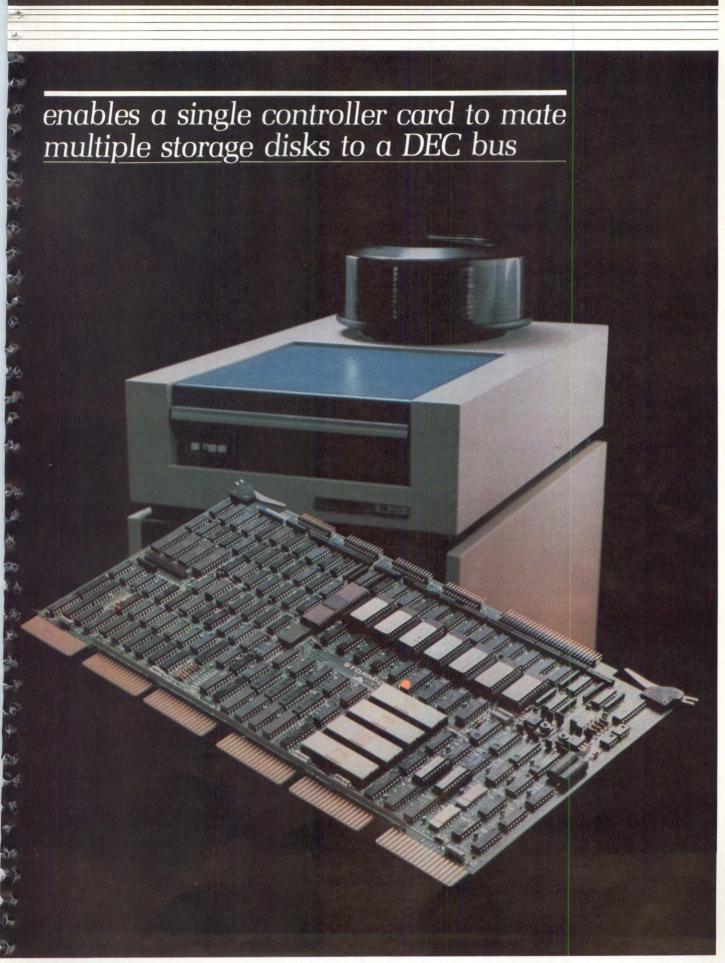

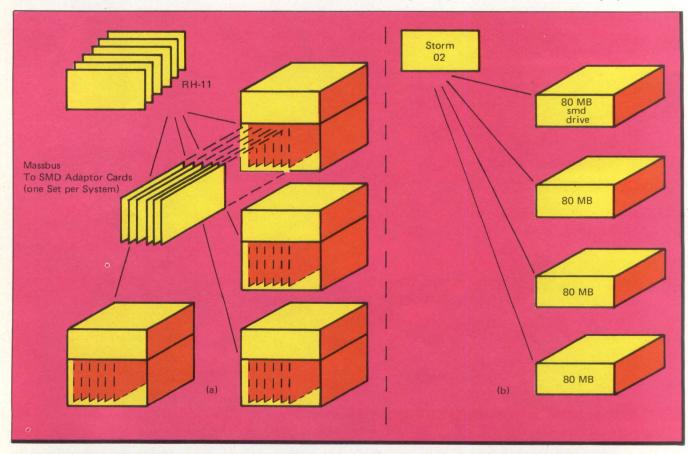

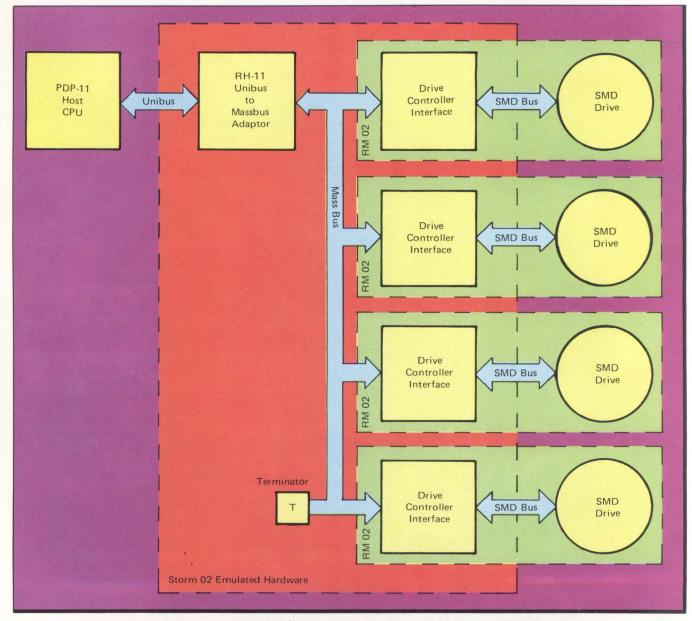

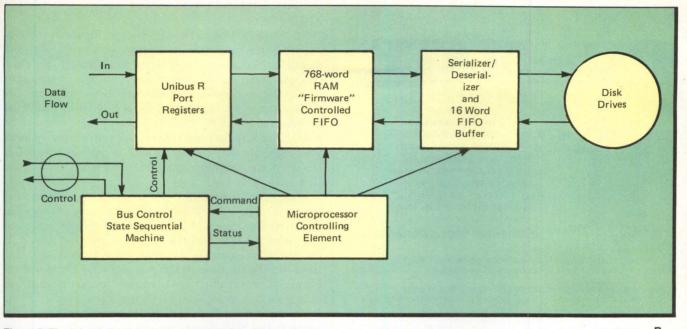

Interfacing up to four 80- to 300-MB disks to a Unibus backplane at low cost.

### 74 SIGGRAPH '81 Blends Art With Science

A showcase for the latest graphics razzle-dazzle, this eighth annual conference is an educational forum.

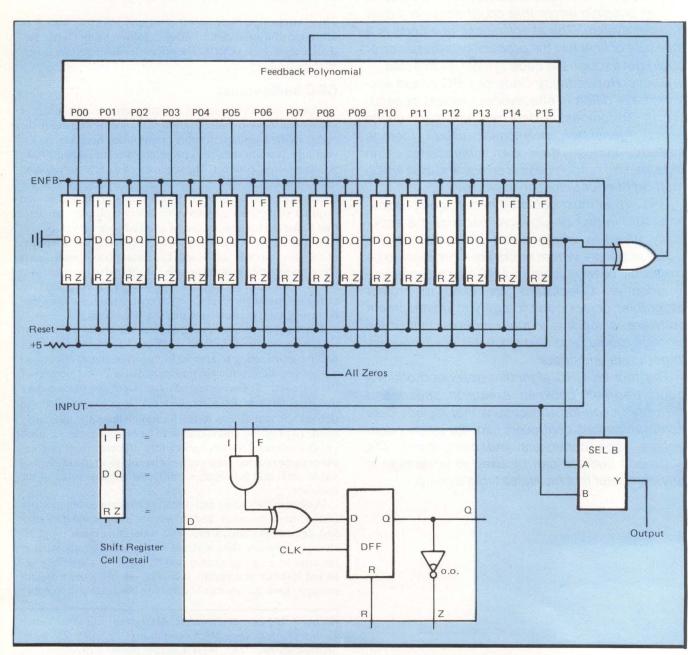

### 77 Cyclic Code Redundancy

Here is an efficient and effective means of accomplishing error detection using CRC.

### 6 Letters

### 8 Speakout

**Do Prices Count?**

### **10 Technology Trends**

- Users Graduate to Superminis

- Software Trends Spark

Competition

- Minis Continue To Gain On Mainframes

- Printers: Key To Computer Growth

- Low-Cost Graphics Systems

Aid OEM Designers

- CAD Package Improves Engineering Productivity

- Computer Graphics Will Improve Sagging Managerial Productivity

### **15 Remote Terminals**

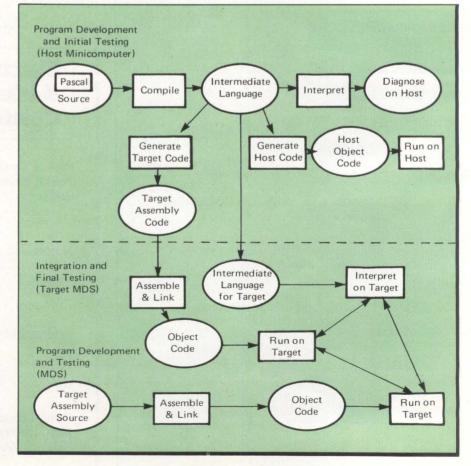

### 88 COMPAT Design

- PDP-11 Cross-Compiler Remedies "Brute-Force" μP Software Development

- Compatible Multifunction Controllers Deliver Backplane Breathing Room

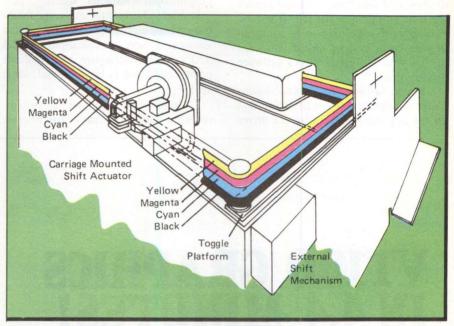

### 96 Innovative Design

- Glare Screen Provides Cure

For Terminal Eyestrain

- Printer Produces Color Graphics

- Smart Storage Tube

Terminal Displays Two Colors

### **100 New Products**

### **109 Designers Notebook**

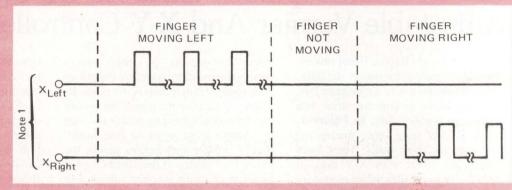

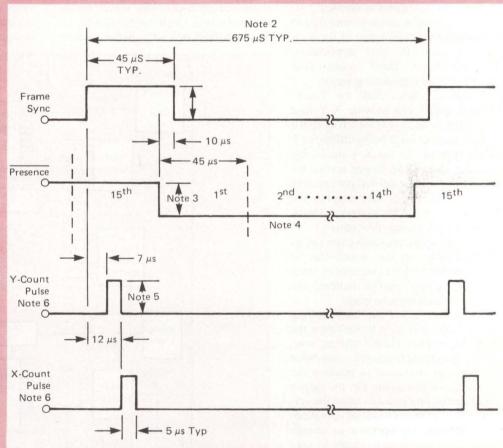

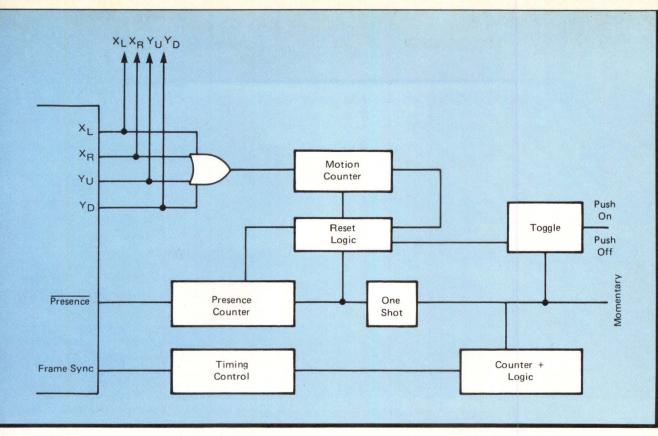

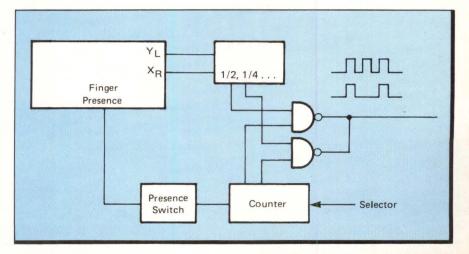

Use "TouchGraphics" Panels As On-Off Switch, Adjustable Vernier And X-Y Controller

112 Advertisers' Index

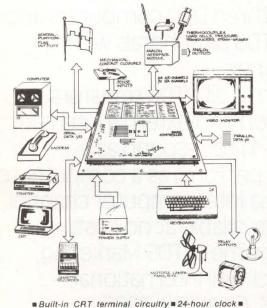

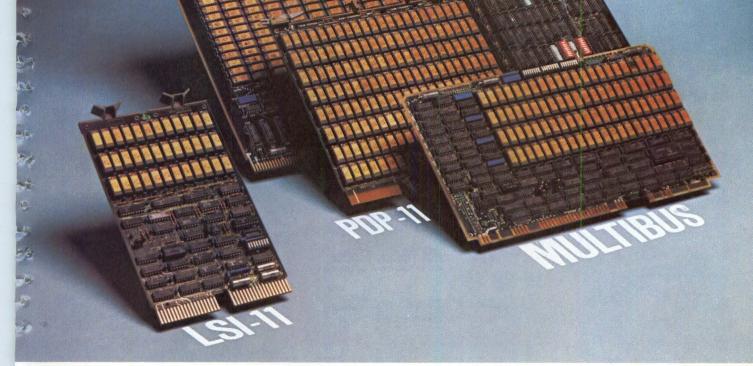

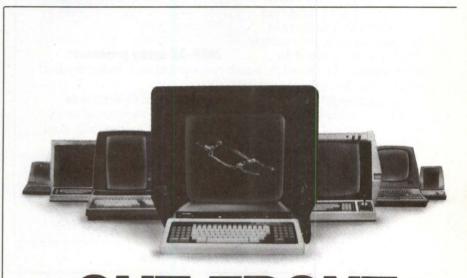

Symbolizing the growing trend toward DEC computer products in the minicomputer, microcomputer and ancillary processor and peripheral fields, this cover captures the essence of this issue, which includes an extensive DEC-prepared directory of DEC products, specs and prices.

> Photo courtesy of Digital Equipment Corp.

Controlled circulation paid at Long Prairie, MN 56347

Postmaster, send Form 3579 to Digital Design, 1050 Commonwealth Ave., Boston, MA 02215

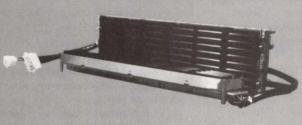

# Unibus repeater for PDP11 series systems.

Do you need to add peripherals or additional cable lengths to an overloaded bus? Do you have unknown system crashes such as caused by a type 4 trap — delayed

# response from a slave sync? Is your current repeater too slow for your current system?

If these questions are relevant, then Datafusion Corporation has a device that can answer your needs, the OSB11-A Bus Repeater. It is a functional equivalent of DEC's\* DB11-A, and is designed to drive at least 19 bus loads and 50 foot of bus cables.

**Ultra Fast:** 80 nanoseconds MSYNC to return SSYNC maximum (40 nsec one way). This is due, primarily, to the specially designed patented integrated circuit employed by the OSB11-A.

**Reliable:** Only 34 operational circuit components. Tested in environments from 0° to 70°C with virtually no degradation of signal quality.

**Easy to Install:** Remove a M920 Jumper and replace it with a OSB11-A. No extra system unit is needed; no wires or plugs to connect (or disconnect); no lost time in reconfiguration.

Available: Off-the-shelf. And, it's fully supported and warranted. Cost: About 25% below DEC.\* Quantity discounts are available.

Other PDP11 products available are a Busrouter (a Unibus\* Switch) to reconnect multiple peripherals to one or more PDP11 cpu's, a Unibus\* Cable Tester, and an Associative File Processor for high speed text search – a hardware approach.

We also have some ideas for the application of our products which might not have occurred to you. If you can't get the performance that

you would like from your PDP11 system, maybe we can help. Please telephone our Marketing Manager at (213) 887-9523 or write to Datafusion Corporation, 5115 Douglas Fir Road, Calabasas, California 91302.

\*TRADEMARK OF DIGITAL EQUIPMENT CORPORATION

**Circle 6 on Reader Inquiry Card**

| Group Publishe<br>Harold G. Buchbinde | r: Main Office<br>r (617) 232-5470                                                                             |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Editorial Director:<br>George King (7 | And and a second se |

| Editor: Ma<br>Paul Snigier (6         |                                                                                                                |

| Managing Editor                       | Harry Shershow                                                                                                 |

| <b>Book Review Editor</b>             | William Belt                                                                                                   |

| West Coast Editor                     | Peter Lichtgarn                                                                                                |

| Assistant Editor                      | Bob Hirshon                                                                                                    |

| Editorial Assistant                   | Martha Hawkins                                                                                                 |

| <b>Contributing Editor</b>            | Zachary Shpall                                                                                                 |

| Art Director                          | Richard D. Sarno                                                                                               |

| Assistant Art Director                | Josh Randall                                                                                                   |

| Staff Artists Jacky<br>Laurie R. G    | / Brill, Stephen Fisher<br>uptill, Donni Richman                                                               |

| <b>Production Manager</b>             | Erik W. Slickman                                                                                               |

| Production<br>Jon Buchbinde           | Noel J. Boulanger<br>r, Florence L. Daniels                                                                    |

| Marketing Services Ma                 | anager C. King                                                                                                 |

|                                       | Hiro Irie<br>er, Regina Harrington<br>aidlaw, Jennifer Wood                                                    |

|                                       | David Beckerman<br>oley, M. Yva Doricent<br>w, Deborah O'Connell<br>Don Spencer                                |

|                                       | Joan Carey<br>a Finichel, Mal Rankin<br>yan, Esther Shershow                                                   |

### SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers in all branches of industry, government institutions and universities. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

### Circulation Department DIGITAL DESIGN 1050 Commonwealth Ave.

Boston, MA 02215

Subscription rates: non-qualified subscribers (US and Canada) — \$35/yr.; non-qualified foreign — surface mail — \$45; air mail — \$70.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicited manuscripts.

1.1

Published monthly by Benwill Publishing Corporation, a Morgan-Grampian Company, Harold G. Buchbinder, Chief Executive Officer; George Palken, President; Domenic A. Mucchetti, Treasurer; Executive, Editorial and Subscription Offices, 1050 Commonwealth Ave., Boston, MA 02215. Telephone: (617) 232-5470.

Morgan-Grampian also publishes American City & County • Circuits Manufacturing • Contractor • Design Engineering • Electronics Test • Industrial Distribution • Industrial Product Bulletin • Mart • Municipal Index

# **Z NEW WAYS TO PROTECT YOUR INVESTMENT**

## from PLESSEY, Your Full Service Memory Bank

ý

5 3

and

19 19 19

12-5

4

See.

5- 20

Increase system speed. End single-bit errors. Plessey's two new dynamic MOS memories increase your system throughput. And maintain data integrity.

COMPLETE YOUR VAX\* MEMORY. Up to 4 Mbytes for maximum return on investment. Plessey's S780 provides 256 Kbytes of MOS memory on a single hexwide board. Hardware and software compatibility with VAX-11; 8-bit ECC for data integrity. IMMEDIATE DELIVERY. HIGH YIELD PDP-11/44\* MEMORY. Uses 64K RAM technology to achieve 512 Kbytes on a single hexwide board, the S11E/2. One bus load to the Unibus\* – either PDP-11/34 or 11/44. Integral ECC/ELR logic with LED indicators. AVAILABLE NOW.

# ALL MEMORY PRICES REDUCED!

Plessey Peripheral Systems is your full service memory bank for all your memory needs – LSI-11\*, PDP-8, PDP-11, VAX, and DG NOVA<sup>†</sup>. Plessey built its reputation on performance. Billions of bits strong and growing stronger. Backed by years of experience. Put your money in the bank. The Plessey Memory Bank. For memories you can trust.

Atten:

Marketing Dept.,

P.O. Box 19616

1691

Browning Avenue

Irvine,

CA 92714

(714) 557-9811

TOLL FREE:

800-854-3581

800-422-4217 (in California)

\*Trademark of Digital Equipment Corporation.

†Trademark of Data General Corporation

**Circle 8 on Reader Inquiry Card**

# LSI-11 USERS

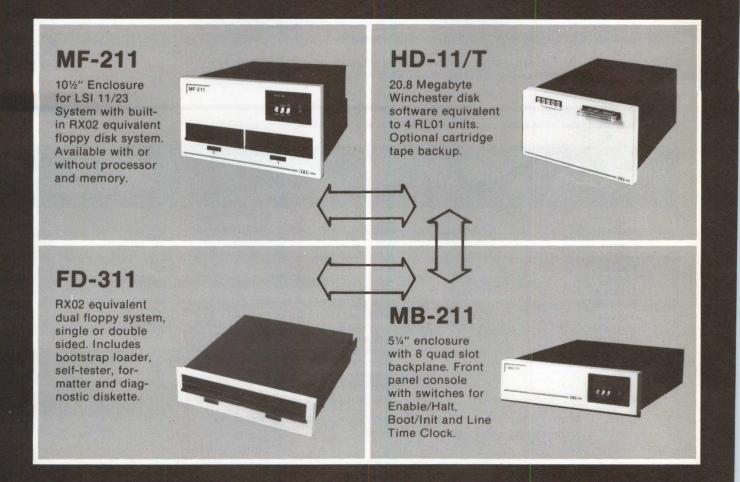

### MODULAR LSI-11 SYSTEMS ELIMINATE HARDWARE BOTTLENECKS!

The Microcomputer Products family of customized building blocks for LSI-11 based systems. From a series of modular enclosures for dual or quad height cards, to complete operational floppy or winchester systems. With integral front panel controls, high efficiency power supplies, and prewired Q-bus backplanes. Contact us today for further details!

A DIVISION NORTH ATLANTIC INDUSTRIES, INC. 60 Plant Avenue, Hauppauge, New York 11787 (516) 582-6500 • (800) 645-5292 Circle 9 on Reader Inquiry Card

# Letters

### AAES

Dear Editor:

I am writing to inform you of a very significant event that occurred at the conclusion of my talk on May 19, 1981 before IEEE's Philadelphia section. My talk, "Engineering Societies and Leaky Umbrellas" was about the new organization, the American Association of Engineering Societies, that you described in your May Speakout. IEEE forced members to support AAES. In my talk, I tried to point out how AAES benefits only college professors and corporate executives.

-

d al

100

1

At the conclusion of my talk, a very significant vote was taken: by an overwhelming margin, 16 to 1, the Philadelphia section voted that "IEEE should not be affiliated with the American Association of Engineering Societies." There were 9 abstentions and many others simply did not vote. I am informed that the turnout was slightly above average for a meeting of the Philadelphia section. Thus, this represents the first known break in the ranks of IEEE as regards participation in AAES.

> Irwin Feerst Committee of Concerned EEs Box 19 Massapequa Park, NY 11762

### programmable gain amplifier

Dear Editor:

Many adjustment problems of the programmable gain amplifier described in a Designers' Notebook (December 1980) would be eliminated if the designer had used a non-inverting amplifier configuration rather than the inverting configuration used.

> Prof. S. Ben-Yaakov Electronic Engr. Ben-Gurion University Beer-Sheva, Israel

Your letters are welcome. Send to: Editor **Digital Design** 1050 Commonwealth Ave. Boston, MA 02215

# Family pride.

Now there's an advanced technology family of single board controllers for DEC\* computers from Western Peripherals—the number one name in controllers.

The TC-131 (for PDP-11s\*) is the first TM-11 emulating controller to combine PE and NRZ on one standard hex board. It lets you mix 9-track, PE, NRZ or dual density tape units in any combination up to 125 ips. A 64 byte data buffer allows installation at any point on the unibus without consideration of NPR priority.

The TC-151 single board NRZI tape controller interfaces any industry-standard drive to the LSI-11.\* Add a dual width Phase Encode Board for the same performance as the TC-131.

The DC-231 accommodates up to four SMD disc drives of 40 to 600 mb each with RMO2 emulation. Its four sector

0.3

(2048 bytes) data buffer makes "data-late" errors a thing of the past. The advanced technology "micro-engine" allows a complete track to be written on a single drive revolution. A measurable performance advantage for your PDP-11. All three controllers are software com-

All three controllers are software compatible. All have self test. All are backed by one of the best factory service organizations in the business. And all can be delivered in 30 days.

For more information, call or write today: Western Peripherals Division, Wespercorp, 14321 Myford Road, Tustin, CA 92680, U.S.A. (714) 730-6250. TWX: 910 595-1775. CABLE: WESPER

Number 1 in controllers for DEC and Data General computers.

50

# Speakout

## **Do Prices Count?**

### Paul Snigier, Editor

Do you consider price an important factor when specifying a service or product? From the lack of pricing information on some new product releases that we've received, you'd get the distinct impression that prices don't matter to these firms, their agencies and their PR departments. Unfortunately, our readers see it in a different light: if a firm doesn't bother to give a price, it has something to hide — namely a price that's too steep. If written in this (or any other) computer publication, such items draw less response. Certain high-interest items draw more than those in highly-competitive product areas. Different magazines and tabloids have come up with different figures, but all agree that reader response to these "priceless wonders" is down significantly. We agree that it's a serious disservice to new \*\*

-

product editors, to readers and to the company introducing these products.

If a new product is priced high, then the press release should begin with the product's "claim to fame." Yes, a high price will turn off some readers. But it is far better to qualify readers and eliminate those uninterested engineers at the start and not force them to request material. They will not specify the product anyway, and it is a disservice to the firm and a waste of its money to send out material to such readers.

Other reasons for priceless product releases include the great variety of certain product lines. This applies to semiconductor families released at the same time, to cables, to power supplies and a few other items. In such cases, we suggest that it's better to include a price range or the price of a typical or anticipated best-selling member of the family rather than on price.

This type of reasoning, using the priceless new product as a come-on, has been with the trade press as far back as anyone remembers; it has constituted roughly 15% of all new product releases. Today, however, a new type of priceless product release is arriving with growing frequency; it is due to inflation and rapid product changes. Activity is so brisk that prices decline rapidly to meet competitors' price threats. All of this has created a hectic, chaotic and rapidly-changing price situation. It's not surprising that more manufacturers are leaving off prices on their new product releases; they reason that it's safer for them to be on the cautious side. This creates problems for everyone. The new product editors must phone the firms. Too often the individual authorized to provide the information isn't in; too frequently he may not return the call; or, if he does, cannot reach the editor. At times the new product editor may get an argument. This consumes time, and still does not get us the correct pricing information. Many times editors don't bother on many publications; and we notice that this trend is growing.

It's the privilege of any agency, PR department or firm not to include pricing on a new product release. We feel it's also the right of every new product editor to take this factor into consideration when he makes the decision to publish — or not publish — that particular product.

We would like your views on the matter of priceless new product releases. Do you feel that we should not publish new product releases that lack prices? Or, should we merely consider it as a negative factor in the overall judgment? If so, how would you want to see it weighted? Let us know.

Paul Snigier

# 1.0 MB ADD-IN FOR PDP-11/44

The DR-144S is another industry first from Dataram. This 1.0MB semiconductor ADD-IN quadruples the size of 16K RAM-based ADD-INs available from either Digital Equipment Corporation (DEC) or ADD-IN memory suppliers.

\*\*

10-14

jà.

2.3

. 16

24

3

4

.

1. 2

-4

T.A

\*

17

8

p pe

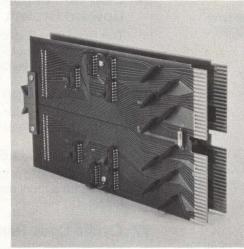

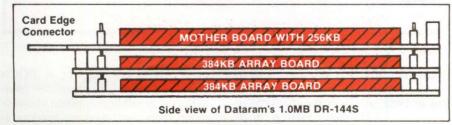

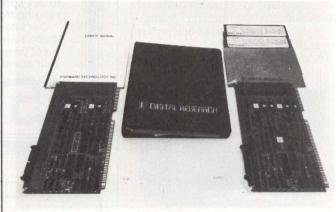

Unlike other manufacturers, Dataram's ADD-IN memory for the PDP-11/44 uses a double word organization with ECC (32 data + 7 ECC) making it completely software compatible with DEC's memory diagnostics. A Mother Board and two Array Boards are joined together by pluggable pins (as shown below) to provide the 1.0MB DR-144S system.

The Mother Board is the only board of the DR-144S assembly which interfaces to the host PDP-11/44. This means that there is only one unit load and that 1.0MB power requirements are dramatically reduced compared to the approach of using four separate 256KB modules. Also, the DR-144S current drains are much lower in the battery backup mode.

The DR-144S is available with only the Mother Board and in versions including one or two array boards. The DR-144S Mother Board provides a capacity of 256KB. The DR-144S Mother Board with one array board is 512KB; with two array boards, the DR-144S capacity can be either 768KB or 1.0MB.

The DR-144S is an exciting product, but we're not resting on our laurels. You can be assured that when 64K RAMs are more cost effective than the 16K RAMs, the DR-144S will be able to accommodate them. Think of it — a 4.0MB PDP-11/44 ADD-IN!

**Circle 11 on Reader Inquiry Card**

- Completely softwarecompatible with DEC® memory diagnostics

- \$9,000/MB in single quantity

- One unit load

- Doubles capacity of host PDP®-11/44 to 2.0MB

- Low power

- Low battery back-up current drains

- ECC standard

| □ I'd like to learn more about<br>PDP-11/44 compatible memory. |

|----------------------------------------------------------------|

| □ Also tell me about other<br>DEC-compatible products.         |

| □ Please send information.                                     |

| □ Please have a salesman contact me.                           |

| Name                                                           |

| TitlePhone                                                     |

| Company                                                        |

| Address                                                        |

| City                                                           |

| StateZip                                                       |

DEC and PDP are registered trademarks of Digital Equipment Corporation.

Princeton Road Cranbury, New Jersey 08512 Tel: 609-799-0071 TWX: 510-685-2542

# **Technology Trends**

### Users Graduate to Superminis

High-performance superminicomputers have become "hot" items, with more than a dozen suppliers struggling to keep pace with "scorching" user demand. IRD of Norwalk, CT, in a report, attributes supermini popularity to an increased user sophistication and "irresistible" price-performance characteristics. Shipments of 32-bit superminis this year should reach \$300 million, with 60% increase to \$480 million predicted for 1982.

### applications support growing

Although traditionally superminis have been sold as "barebones" hardware, tailored and programmed by users or systems houses for particular applications, vendors are tending to provide more sophisticated programming tools and special-purpose I/O equipment for such applications as aerospace simulators, oil drilling analysis, process control and business transactionprocessing, according to the report. Will the current phenomenal growth in this market last forever? No. Soon, indepth support of particular applications niches will become the deciding force in market leadership.

### major challenge from HP — not IBM

With almost 40% of the current market (in terms of the value of equipment installed), DEC is the leader in 32-bit superminis, with its VAXes. Runnersup are Perkin Elmer (22%), SEL/Gould (17%) and Prime (16%). IRD predicts an "important" new supermini, from H-P, which may be announced soon. The machine will be comparable in power to mid-range VAX equipment and configured as a desk-top. A headon competitive machine from IBM is unlikely; an IBM supermini product would damage IBM's 32-bit commercial offerings in the 4331 and 434n series, with which superminis compete in some applications.

### DGC readies "Fountainhead" for introduction

Data General, which introduced its MB/8000 series of superminis last

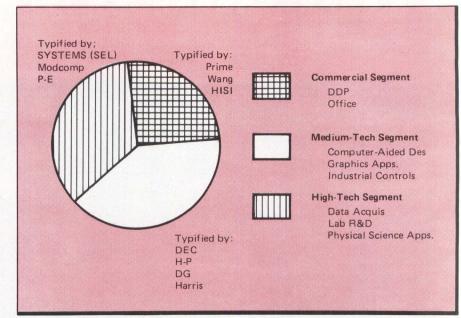

Figure 1. Superminicomputer Market Segmentation and Primary Positioning of Leading Suppliers

| KEY<br>1 - Strong<br>2 - Mcderate<br>3 - Weak                                                                    | High-Tech<br>(Lab & R&D                              | Medium-Tech<br>(Scientific<br>& Engineering) | Commercial                                |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------|-------------------------------------------|

| 32-Bit Superminis<br>Apollo<br>BTI<br>DGC<br>DEC<br>Honeywell (HISI)<br>Perkin-Elmer<br>Prime<br>Systems<br>Wang | 3<br>3<br>2<br>1<br>2<br>1-<br>2<br>1<br>2<br>1<br>3 | 1<br>2<br>1<br>1<br>2<br>1<br>2<br>2<br>3    | 3<br>1<br>2<br>1<br>1<br>2<br>1<br>3<br>1 |

| Other-Word-Length<br>High Performance<br>Superminis<br>Harris<br>H-P<br>Modcomp<br>Tandem                        | 1<br>1<br>1<br>3                                     | 1<br>1<br>1<br>2                             | 2<br>2<br>3<br>1                          |

Figure 2. Comparative Market Strengths of Superminicompter Manufacturers in 1981

year, is readying a new supermini for introduction to the market later in 1981 or in 1982, as reported earlier ("Minicomputers", December 1980 pp. 26-28, P. Snigier). The "Fountainhead Processor" is a key element in DGC's growth strategy. Linked with this product is the possible acquisition of one or more specialized systems vendors to provide DGC with "instant" applica2

F

the s

-

1.

tions expertise. DGC's abortive attempt to acquire Megatek, a computer graphics system manufacturer, is an example of a potential "short-cut" to obtaining computer-graphics software capability for DGC's supermini series.

1

1.1

1

¥

5 3

÷

8-4

×

2.4

100

-4

ph)

5.2

. .

24

P

-

-

-

2

T.A

44

h. 10

1- be

### no competition from Japan? Unlikely.

Micro and minicomputer suppliers brace themselves for a "tremendous" influx of new products from Japan. But is there an immediate prospect of severe Japanese competition in the supermini segment? No. But why? The Japanese and European computer suppliers overlooked the potential of this market sector, in their eagerness to ship large numbers of small business computers and traditional EDP systems. Meanwhile, most U.S. vendors of superminis are "doing rather well" in overseas markets.

### Software Trends -5 Spark Competition

Competition is intensifying among companies vying for control of vital software areas. The strengths of different software companies will establish their predominance in their respective market focuses over the next five years, relative to operating systems, languages utilities and specific market applications. Contention among several companies is the battle for dominance of 16-bit operating systems. Digital Research's CP/M operating system achieved the status of de facto standard for 8-bit µCs. However, efforts to control operating systems at the 16-bit level as well are encountering formidable competition from UNIX and UNIX-like operating systems produced by companies such as Micro-Soft Inc., Bell Labs, Onyx, Cromemco and others. Standards of 16-bit operating systems will be determined within the next two years, according to Creative Strategies International of San Jose, CA, in a new report.

As software houses solidify into major marketing forces for hardware, their allegiances to certain computers and/or operating systems will largely determine the success of those computers. Trends in the  $\mu$ C industry are toward standardization more than in any other aspect of the data processing industry. Especially at the operating system level, incompatibilities will severely hinder developments. Only those hardware manufacturers with very strong in-house software development can afford incompatible, proprietary operating systems. Software, and good documentation of that software, will control the sales of microcomputers. Hardware manufacturers that ignore this fact will not do well.

Most of the best software available today is from third-party software houses, and this trend will continue. With few exceptions, hardware manu-

facturers have not moved to develop software in-house, but have acquired software from suppliers outside the manufacturers' environment.

The fast-changing technology of  $\mu C$ industry requires distribution across as large a base of systems as possible. There is an escalating rush among software houses to generate "Lathe' type software converters, which allow quick transfer and translation from one machine to another, within and without a similar operating system and  $\mu P$ .

### Minis Continue To Gain On Mainframes

The sophisticated end user has become the rule, not the exception. This, in turn, has fueled demand for greater user control and encouraging the trend towards DP decentralization. Even within the minicomputer industry, effects of changing user needs can be seen. Conventional minis will continue to be well-suited for automation control and advanced communications work, as well as laboratory analysis and "number crunching." On the other hand, microminis, sometimes called microcomputers, are becoming increasingly attractive as an alternative to conventional minis. These small, oneboard systems are particularly cost effective for tasks such as control of machine tools where data handling requirements are modest.

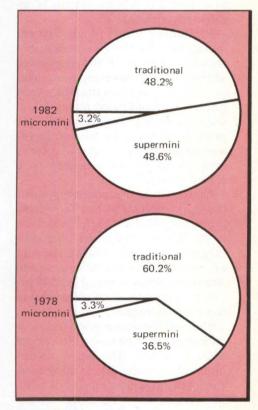

Minis with more powerful processors are evolving in the other direction to become "superminis." While the prices of these computers are substantially higher than those of conventional minis, the greatly increased data handling capability and ease of programming will make superminis the fastest growing minicomputer category.

Share of minicomputer shipments by type 1978 and 1982, in pie-chart form, are by factory value of U.S. shipments.

### Printers: Key To Computer Growth

What the computer world needs is a low-cost printer to solve the current dilemma of peripheral cost exceeding many basic computers. While lower mini and  $\mu C$  prices have made computers accessible to broader business and personal applications, the peripheral costs, particularly printers, inhibit their full development.

The 20-, 40-, and 80-column printers. such as offered by Alphacom. and others, will grow rapidly in the low-end small business and personal computing market, which will increase in the 1980-1985 window by over 23% a year, from today's \$1.2 billion, rising to \$3 billion.

Printers now range from thumbnailsized calculator-based printers to the largest and most refined thermal and impact printers at all market levels.

### markets are changing

The 20-, 40-, and 80-column alphanumeric and graphics printers are attractive to business and professional

end users, because hard copy of data, graphs, charts and tables are increasingly becoming a standard requirement. Now, hobby, educational and home computer users also have a feasible printer option. Professional and business users, lacking alternatives, use printers costing \$1000 to \$3000 for all hard copy, including rough draft. The cost limits their number to one per business computer. With the low cost of newer 80-column printing systems, more than one printer can be connected to a shared-logic type system in an office environment.

Presently, shared logic system throughput is slowed considerably because one printer is shared by every terminal. Now, however, one printer can be cost-effectively attached to each display keyboard-based terminal, and users operating each terminal can generate printouts for editing, proofreading and approval. After correction, final documents are generated on a central printer.

Currently in the printing systems market, companies such as Centronics, Printronix, Diablo, Qume and Data Products Corp. and others offer units ranging from \$900 to \$5,000. The most expensive 80-column printing system Alphacom offers is priced at \$595 per unit with print speed four times that of more expensive units.

Personal computer prices continue their drop, with the basic CPU price at \$500 to \$1500. The big fly-in-theointment is printer prices: many users cannot pay for a printer that costs two to four times the CPU! Big markets remain dormant. But, now the newer 20-, 40-, and 80-column printers, ranging from \$175 to \$595, provide many users hard copy capability at moreaffordable prices.

### but, can they deliver?

The printer boom continues. Inexpensive, fast and reliable models are the fuel behind sales. Can suppliers deliver? Key to this growth is suppliers meeting volume demands inherent in an expanding, price-competitive market. Will traditional, computer-oriented companies geared to lower-volume manufacturing requirements keep pace with demand and price changes? Not unless they change.

Some firms are well-positioned to take advantage of this growing market. For example, Alphacom of San Jose ensured its ability to deliver through an exclusive North American distribution agreement with Olivetti and manufacturing agreement with Rockwell, which invested over \$2 million in production facilities for Alphacom's Sprinter Series.

Quality, volume and engineering

support are keys to the printer field of the 1980s. Traditional companies specialize in limited-capability machines or market niches, making their products less flexible for the broader requirements of the OEM concerned with end users' immediate applications.

### Low-Cost Graphic Systems Aid OEM Designers

In a major expansion of CAD/CAM product lines, firms are introducing low-cost graphics workstations and software packages configured for use by OEMs.

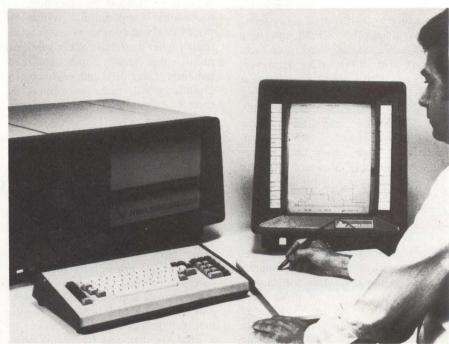

Avera of Scotts Valley, CA, has such a system. Its four workstations are built around a dual processor architecture based on Intel's 16-bit 8086 microprocessor and an OS with 200,000 lines of Pascal code. The four workstation configurations include the GS1100, including 2 diskette drives, 192-KB parity memory, dual processors, two RS-232C ports, keyboard and control electronics, B/W display and control electronics, data tablet and control, 64-KB bit map, supplies and enclosures. GS1120 is like GS1100 with one diskette drive and one 10-MB Winchester drive. The GS1200 is like GS1100, but with a 13" color display. GS1220 is like GS1200 with one diskette drive and one 10-MB Winchester drive.

### dual processor architecture

Key to the power of the workstations is a dual processor architecture with two 8086s sharing the command and graphics processing load, with the processor's arbitrating through a multitasking OS. One processor interprets commands; the other supports graphics. The main processor has 128 KB of RAM; the graphics processor, another 64-KB RAM plus a 64-KB bit map. Main storage RAM has parity checking, but the bit map does not. Memory (combined) can be expanded to a total of 1 MB.

### graphics input and software

A 564-by-832 pixel CRT display is oriented vertically, with a 9"-by-12" viewing area and 24 on-screen functions that respond to cursor control. The graphics area contains 512-by-512 pixels. The display unit also features a two-digit LED display for indicating

An Avera workstation user need not to know how to type or draw. This work station is configured so that users simply point a stylus at the proper command on the screen or draw a simple symbol on the drawing pad input.

self-diagnostic codes and speaker to acknowledge a command input.

St. P

500

\*

1

a.

2.00

-4

24

.

24

3

23

×

(m. 10

72

Software, designed for ease of use, is organized into five command groups: control, editing, manipulation, status and viewing — an organization that eliminates the need to display all commands simultaneously. Once a command category is selected, commands within that group are displayed. The user strings together functions and demands syntax of a given command. Using the data tablet, he draws symbols representing commands.

### recursive data structure

Via the Pascal-based OS (common to all systems), a flexible recursive data structure is utilized. A recursive structure allows users to associate any graphics or text components in the data structure with other components to an arbitrary level of complexity by nesting. It forms hard associations; for example, a line can be associated with a symbol so that if the line is later moved, the symbol cannot be inadvertently left behind. Via an intermediate data structure for external communications. these systems are amenable to design partitioning and uploading to larger computers, including IBM mainframes.

### CAD Package Improves Engineering Productivity

Advanced CAD software package Medusa provides complete 2-D and 3-D design, drafting and documentation. Based on Prime Computer's generalpurpose 32-bit computer systems, Medusa enables designers to customize their own design system, a capability unavailable with turnkey or softwareonly offerings.

The system is packaged with its own integrated workstation, available with color or B&W terminals. Workstations are configured for easy access to control elements and provide a high 1000line resolution display to enhance operation and increase performance.

The 2-D entry-level model is used for layouts, schematics and detailing tasks in mechanical, electrical, structural and electronic applications. The advanced 3-D model is for designing a complex 3-D object and then producing an engineering drawing. The workstation has a 19" display, joystick for easy manipulation and control of cursors, a data tablet, PT25 charcter-mode terminal and graphic controller.

Cost? Don't expect to buy one for your home computer lab. A typical entry-level Prime/Medusa system costs \$235K and includes one Prime 250 CPU, 768-MB memory, one 96-MB disk drive and two workstations with B&W terminals. Licensed software includes 3-D Medusa, Primos, Fortran, Midas and CPL. Medusa software can be licensed separately at \$30K and \$60K for the 2- and 3-D models, respectively.

### Computer Graphics Will Improve Sagging Managerial Productivity

Reams of printouts which computers have made available to today's managers are largely unabsorbable. We're at a point of diminishing returns in the benefits WP and DP can bring to the decision-making process. Computer graphics are emerging from

JULY 1981 Digital Design 13

### Technology Trends

scientific and engineering applications to combat this problem. A single glance can reveal in seconds subtle trends and relationships that can take hours to decipher from a table of numbers.

In a special OARS report, entitled "Graphics in the Office," IDC of Framingham, MA, forecasts a sharp rise in the overall use of computer graphics, averaging 35% growth per year through 1984. In dollars, this represents an increase in revenues from just over \$1 billion in 1979, to over \$4.5 billion in 1984. It certainly is no revelation that graphics — pie charts, bar graphics, etc. - are easier to comprehend than a table of numbers. Executives used graphics for presentation and analysis for years. What is new is the concept of generating graphics interactively without involving graphic arts to bring immediate answers to management's questions. An example of what can be done is the use of "what if" gaming techniques, which allow the manipulation of variables such as price. return on investment. etc.

CAD/CAM systems are the dominant force in the graphics market. While CAD/CAM systems are much more sophisticated and more expensive than business systems, it is actually the business applications market which will show the fastest growth: shipments of some \$1 billion are forecast by IDC for 1984. CAD/CAM systems may dominate the overall market dollarwise, but in terms of sheer numbers, the business graphics market will far surpass it in units shipped. In fact, business applications will soon rival CAD/CAM applications as the major driving force. Most of the technology is in place; all that is needed is to refine and tailor it to the specific needs of business.

Display devices accounted for a little over half of all graphics expenditures. Hard copy devices accounted for just over a third, while the remainder of the expenditures went for such other equipment as business/personal computers and photographic output devices.

Things will change rapidly, however, on the computer graphics scene over the next five years. Much of this change will be due to a sharp rise in the number of personal computers used for graphics. Additionally, as the technology improves, the price of low-cost, hard copy will begin to fall. These devices - dot matrix printers/plotters, color cameras, and ink jet printers, etc.

- will grow in numbers, though dollarwise shipments of these devices will drop to 22% of the total business graphics market by 1984. Furthermore, IDC is predicting that business/ personal computers will account for 20% of the graphics market (by dollar value) in 1984. Display devices will dip slightly — to under half of total expenditures at that point, while photographic equipment will rise to approximately 8% of the market.

12

4

4

B. T

+-

÷.

i de

2-

W.

the set

8-2

-

-

p.A

et al

2

F---

dial

\*

\*\*

the.

÷.

44

\*

1.0

Display devices use three primary technologies: the direct view storage tube (DVST), raster refresh tubes, and random scan tubes. Each of these technologies has its own cost/performance trade offs. IDC views raster tubes (which operate much like a TV set) as the technology of choice for business purposes mainly due to high-quality color, good resolution, selective erasure, and the ability to display photographic images. The big drawback to raster scans right now is cost. The images of raster scan must be refreshed many times a second, and this requires the definition and storage in memory of every pixel (picture element), whether part of the image or not. Obviously, the memory and processing cost in this method are prohibitive, but as memory costs continue to drop it will become less of a factor.

The other methods of display mentioned also have their pros and cons. Direct view storage tubes, for example, don't need to be refreshed 30-60 times a second, and they offer high resolution at low cost. However, selective erasure is not possible in a DVST, and low light output is another factor to be considered. Random scan tubes offer selective erasure and higher resolution than raster refresh tubes, but only limited color. These displays have been employed mainly by the engineering/ scientific community where resolution is very important and color less so.

Of the 180,000 shipments of display devices forecast in 1984 by IDC, 75% will be raster scan tubes. Additionally, approximately 90% of these will be color tubes, as compared to 63% for raster tubes shipped in 1979. Users will drive the graphics display market toward increasing use of color graphics for business applications.

With color displays soon to dominate the market, the demand for color hard copy will also increase dramatically. Color displays and color hard copy devices will grow hand in hand. If inexpensive, convenient hard copy output devices are slow in coming, we can expect this to have a dampening

effect on the color display market. By the same token, if color hard copy output becomes available quickly, then the color display market will be boosted.

-

2.3

\*

20.4

100

1.44

1

-

What's in store for users regarding output devices? Quite a few things, including: • color cameras -- useful for the preparation of slides, transparencies, and color microfilm, • photocomposition devices — offering superior resolution previously available only to graphics designers, and • dot matrix printer/plotters — simple adaptations of alphanumeric matrix printers, which can not only produce shades of gray, but by striking over can also produce color.

## **Remote Terminals**

JAPAN: Matsushita is planning to bring CAD into the Japanese home. The principle is that a lady customer, shopping for dresses is filmed by video camera. The video film, together with size statistics, is stored by company. Whenever the shopper wants to buy a dress, she telephones the company, her film is recalled from data and displayed on TV. Dresses are then superimposed on image as though she were trying them on. Hopefully, she will select one that looks good on her ... BARBADOS: A \$9 million plant (with more than 100 employees) for manufacturing resistors has opened on this Caribbean island. Backer is TRW of the US. The range of resistors is designed for a variety of electronic systems from basic telephone equipment to sophisticated space research . . . LONDON: Scientific Calculations has opened a London office. The company produces printed circuit designs and applications .... SOMALIA: This country has become the 106th member of INTELSAT (International Telecommunications Satellite Organization.) INTELSAT operates the global satellite system that provides 2/3 of the world's international telecommunications services . . . FRANCE: British and French telecommunications officials have agreed to adopt a new technical standard for Viewdata by the mid-1980's. This will end the rivalry between Britain's Prestel and the French Antiope. A working method with Germany is also being developed. Japan has been waiting for such an agreement and should be among the first to produce new standard Viewdata terminals. Viewdata transmits such things as telephone directories service (500,000 directory terminals for France alone); electronic mail; stock market; news; information; etc....IRELAND: A high technology research center is being set up in Limer-

ick. It will concentrate on the application of electronic technology and the material sciences with particular emenergy phasis on alternate sources . . . ITALY: The Italian Olivetti group is acquiring control of the Swiss company, Hermes Precisa, manufacturer of office equipment...WEST **GERMANY:** Production of West Germany's electronics industry rose 4.9% to \$44.5 billion in 1980. This increase occurred despite the recession. (1979, however, was a much better year.)...HAWAII: The Fourth Annual Pacific Telecommunications Conference takes place Jan. 18-20, 1982, at the Ilikai Hotel, Honolulu. (Never too early to plan for such events.) Papers and exhibits invited. Contact Richard J. Barber, (Director), 1110 University Ave., Suite 303, Honolulu, HI 96826 ... SINGAPORE: A conference and exhibition for the quality control/quality assurance field in Southeast Asia has been scheduled for June 17-19. 1982 in Singapore ... HONG KONG: A new firm has been launched to manufacture magnetic recording heads. The company is SAE Magnetics (H.K.) Ltd., a division of Stanford Applied Engineering Corp. of Santa Clara, CA... SCOTLAND: The worst recession in Great Britain since the 1930's has served as a stark contrast to the continuing growth and prosperity of the energy and electronics industries in Scotland. Scotland has been the home of several American firms for about half a century and has been attracting high-technology manufacturers for decades. The 1970s, however, has seen a strong burst of growth in the high technology areas, spurred by government financial incentives, a growing pool of skilled labor, research and development resources, and experienced executives willing to start new ventures.

Whether you have a need for three phase or single phase AC power control. Marway Products has a high quality. low cost unit available to satisfy you. In fact our DEC interchangeable units are so economical that we are attracting a large following of non-DEC OEM's. system integrators. and quantity end users.

Marway's three phase power controllers are mechanically and electrically interchangeable with the DEC/VAX model 869 and feature:

- Model MPD 416 for 240/416 VAC @ 45 amps Model MPD 208 for 120/208 VAC @ 90 amps

- 18 AC recepticles-6 unswitched:

- 12 switched

- High level control bus High performance EMI line filter Pricing: MPD 416-\$1375.00\*:

- MPD 208-\$1650.00\*

- Availability: 30 days ARO

Marway's MPD 115 and MPD 230 AC power controllers are mechanically and electrically interchangeable with the DEC model 861's and feature:

- Control of 115 or 230 VAC @ up to 30 amps Twelve AC recepticles-4 unswitched:

- 8 switched

- High performance EMI line filter

- Pricing: \$325\* (MPD 115) · Availability: off the shelf

Additional Marway models that are available to meet your needs are: The MPD 110, the lowest cost rack mountable unit. priced at \$149.00. and the MPD 117. the floor or wall mountable unit for use in the office or personal computer environments. priced at only \$89.00\*

For more information, please call or write:

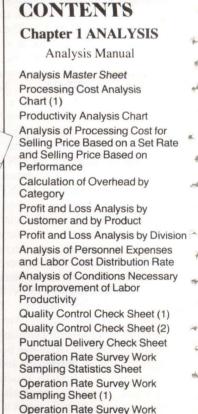

Based on the experience of hundreds of Japanese factories diagnosed and advised by the author during his ten years as a factory management and production control consultant. It is used by more than 4,000 factories in Japan today.

Factory Systems

With instructions on how to use them. All reproducible for in-plant use. Bound looseleaf in slipcover.

Price: \$80. Pre-Publication Price: \$60. Prepaid (Until August 1, 1981)

in 1

23 ANALYSIS SHEETS

PLANNING SHEETS

MANAGEMENT SHEETS

# Management in Japan By Tatsukichi Yanagawa

Equipment Related Operation Rate Analysis (1)

- Productivity of Plant and Equipment Analysis

- P Q Analysis Sheet (1) P Q Analysis Sheet (2)

- Balance Sheet, Profit and Loss Statement, Manufacturing Cost Statement

- **Business Operation Survey** Analysis Indicators

### **Chapter 2 PLANNING**

Planning Manual

- **Planning Master Sheet Total Production Planning** Support Chart

- Control System Planning Chart Calculation of Available Capacity (Labor Hours)

- Capacity Survey by Product Master Sheet for Establishing Work Time

- Labor Hours for Bolt Tightening Calculation Table for Machining Labor Hours

- Simple MTM Data

- Conveyor Line, Line Balance **Calculation Chart**

- Strategy for Making Profit and **Reducing Loss**

- **Pitch Diagram**

1- 7

**Cost Reduction Check Sheet** (Production Quantity and Pitch Time)

Equipment Planning Check Sheet ABC Analysis Sheet (1) ABC Analysis Sheet (2)

Materials Order Planning Sheet Standing Parts Planning List Standards for Deciding Whether to

Stock or Not **Economical Lot Calculation Table**

Order Timing Calculation Table Unit Price Estimate Calculation Table

Calculation Procedure for Unit Price Estimate

### **Chapter 3 MANAGEMENT**

Management Manual

Management Master Sheet Master Sheet by Order (1) Master Sheet by Order (2) **Production Performance Graph** Calculation of Profit and Loss Per Month by Division Selling Price Change Report Report of Change in Order Price or Source of Order **General Report** Management of Lent Drawings **Equipment Control Chart**

Manufacturing, Inspection **Equipment Control Chart** Major Purchases Control Chart Monthly Order Chart **Process Control System Evaluation List** x-R Control Chart Data Sheet (1)

Name

Company

Check must accompany order

Address

City

I am interested in \_\_\_\_\_

Enclosed is a check for \$\_

x-R Control Chart Data Sheet (2) -R Control Chart P Control Chart Data Sheet **Control Chart Frequency Distribution Record Control Standards Check Sheet**

Factory Management Systems in Japan

State

a Morgan-Grampian company

1050 Commonwealth Ave.

MAIL TO: Benwill Publishing Corporation

Boston MA 02215

Zip

# Total DEC Compatibility with the ComplI-LE

### And much more . . .

The CompII-LE, which is equivalent to the DEC BAII-LE™, is a general purpose PDP-II™ expansion mounting chassis.

The 120V ac input power unit supplies 32 amps of output power at +5Vdc with regulators to support either MOS or core expansion memory.

\*\*

-

a de

1

-

4.

-

\$3

ú.

de

- 20

d.

di.

10

The chassis can be equipped optionally with up to two **Comp-CK** or one **Comp-DK** (DEC DDII-CK and DDII-DK equivalent backplanes) units, enabling the CompII-LE to support a wide variety of PDP-II systems.

### . . For a lot less

For more information call or write:

### COMPUMATION

2326 Walsh Avenue Santa Clara, CA 95051 (408) 988-8600

"DEC BAII-LE is a trademark of Digital Equipment Corp.

# Unibus\* The Solution to Your DEC\* ∫Integration Problems =∑Sigma Products

SIGMA's chassis can be the beginning of DEC based systems or can provide expansion for Unibus or Q bus devices.

### ANOTHER $\sum$ SIGMA INFORMATION FIRST!

Sigma chassis provide low-cost, flexible configurations for your DEC systems The complete line of 5.25" and 10.5" chassis provide mounting space and power for Unibus and LSI-11 series systems, as well as almost any combination of floppy/Winchester/tape cartridge drives. Most chassis include an 8-row quad backplane and front operator control panel. Some are available in either tabletop or rackmount versions with styles that are easy on your eyes and prices that are easy on your total system cost.

+ DEC compatibility

×

\*

p.

100

a de

2

1

- + Easy access to installed modules

- + Well-planned cable egress

- + Tabletop and rackmount versions

- + Heavy duty, reliable power supplies

- + Custom mounting of user specified peripherals

Sigma is in the business of serving DEC users. Chassis are optionally available with CPU's, memories, controllers, interfaces, etc., depending on client needs.

Sigma personnel are experienced in design and development of DEC-related products and have a comprehensive background in system compatibility. This expertise is available to develop chassis with user-configured front panels, power supplies, backplanes and drive enclosures.

| Σ | Sigma<br>Informati<br>Systems | on             |

|---|-------------------------------|----------------|

|   | Systems                       | (714) 974-0166 |

| lame       |             |

|------------|-------------|

| itle       |             |

| ompany     |             |

| ddress     |             |

| ity, State |             |

| ip Code    | Telephone() |

Trademark of Digital Equipment Corporation

**Circle 34 on Reader Inquiry Card**

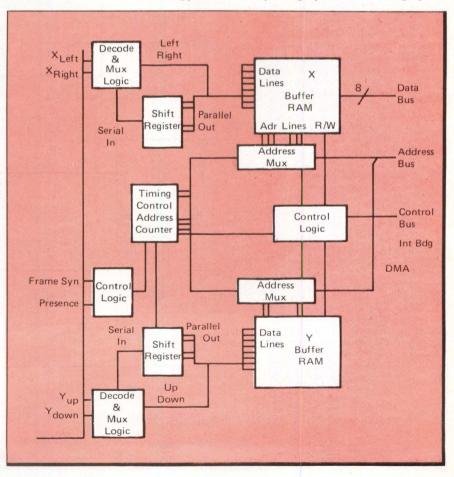

# CIRCUITS Shortened Algorithm

### speeds DFT computation

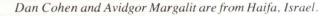

A shortened Discrete Fourier Transform (DFT) or SDFT algorithm was developed to achieve real time processing. Use is made of new fast components such as video A/D converter, multiplier/accumulator, RAM and PROM. A DFT processor based on the shortened algorithm can calculate power spectrum of 32 samples in about 300  $\mu$ s, giving a maximum sampling rate of 100 KHz.

### by Dan Cohen and Avidgor Margalit

A number of methods for the realization of a digital real time DRT processor has been published in recent years. In the past, contemporary technology limitations on the speed of digital components, especially multipliers, prevented the realization of a satisfactory processor. The introduction of new components, such as the monolithic multiplier/ accumulator family and video 30 ns- 6 to 10 bit ADCs helped solve some major problems. We describe a new method which, with the aid of new components, permits realization of a satisfactory real time DFT processor.

1

4 4

\*

### SDFT is fourfold faster

This shortened algorithm for DFT (SDFT) calculation method fills in the gap between a complicated fast FFT processing and a simple-but-relatively-slow direct DFT computation. Use of shortened DFT gives a four times faster processor in comparison with a direct DFT assuming the

Figure 1: Shortened DFT serial processor (N=32)

same techniques of realization. Such a processor for 32 points was designed and built by the authors, fulfilling the expectations of a fast, low power, low volume and low price unit. A 5-W, one-board processor computes a 32-point DFT in less than 300  $\mu$ s (100 KHz sampling rate), for less than \$500 (qty. 100).

### direct DFT

1

Ē

300

\*

24 1.4 1.4 1.4

7 0

2.0

\*

- 9

P

e

10

×

1

.

24

-

-

The DFT is defined as

$$S(m) = (1/N) \sum_{n=0}^{N-1} X_n \exp[(-2\pi j/N) (m n)]$$

(1)

where "exp" signifies a base e (or natural) exponential; m,n = 0, 1, 2...N-1;  $x_n$  samples are taken at  $\Delta t$  intervals;  $x_n$  are real or complex sample values; and N is the total number of samples in an integration.

Direct DFT is calculated by solving **Eq. 1** for each m separately. This is the simplest way to realize the processor, hence the name "direct." Despite it's simplicity, the introduction of such a processor does cause difficulties in fast real-time systems.

The shortened DFT method eliminates these difficulties by reducing the number of complex multiplications  $(N^2/4)$  by a factor of 4.

### shortened DFT or SDFT

As is well known, an FFT processor implies  $Nlog_2N$  multiplications, while direct DFT processing requires  $N^2$  multiplications (N is the processing block length). This number of multiplications can be reduced by partial realization of the FFT algorithm (theoretically it could be done until the complete FFT algorithm is achieved), according to the following equations:

$$\exp(-j2\pi m /N) (N/2 + r)] = (-1)^{m} \exp(-j2\pi m r/N)$$

(2)

$$S (m) = (1/N) \sum_{r=0}^{N/2-1} \left\{ \left[ X_r \exp(-j2\pi mr/N) + X(r+N/2) \right] \exp[(-j2\pi/N) m(r+N/2)] \right\}$$

(3)

Substituting Eq. 2 into the second expression on the rightmost side of Eq. 3 we obtain:

$$S(m) = (1/N) \sum_{r=0}^{N/2-1} \exp \left[ (-j\pi mr/N) \right]$$

$$[x_r + (-1)^m X(r + N/2)]$$

(4)

Eq 4 shows a reduction of the number of multiplications in the frequency domain. That means  $N^2/2$  multiplications instead of  $N^2$  in the direct DFT. On the other hand this algorithm adds N additions/subtractions in the time domain, which results in addition of 1 bit to the input dynamic range.

An additional reduction of the computing time for real signals is achieved by using:

$$S(N - m) = S^{*}(m)$$

(5)

This indicates that the whole procedure is reduced to computation of the spectrum S(m) for m = N/2, and then computation of its conjugate  $S^*(m)$ . Thus,  $N^2/2$  multiplications for computation of S(m) and N/2 additions for computation of  $S^*(m)$  will complete the procedure. When quadrature channels are used, each channel should be computed separately.

In summary, the shortened DFT algorithm will produce the spectrum after the following computations:

$N^2/4$  multiplications,

N complex additions in the time domain and N/2 real additions in the frequency domain.

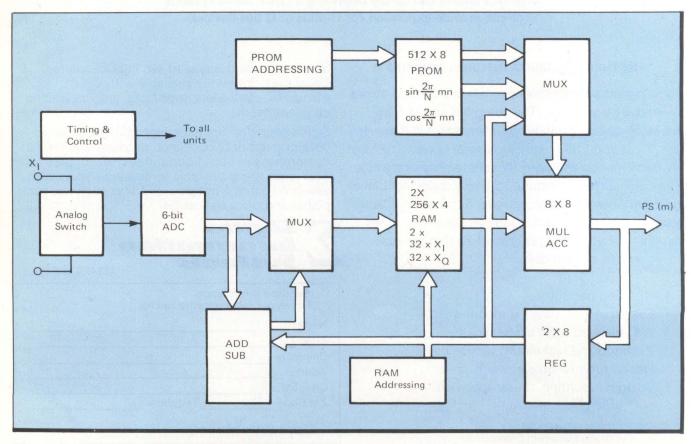

Figure 2: RAM organization (N=32)

### realization of shortened DFT

Realization of a direct DFT filter depends on desired specifications: sampling rate, block length, power dissipation, volume, price etc. The most convenient realization, the serial method, utilizes a multiplier/accumulator and satisfies most typical system requirements — except for the case of very high-sampling-rate systems. It is possible to overcome this shortcoming by paralleling two serial processors for a single channel or four serial processors for quadrature channels.

Fig 1 describes a serial realization of the shortened DFT method. Quadrature video signals  $X_I$  and  $X_Q$  are sampled by

an analog switch and converted by a single ultra-high-speed A/D converter, resulting into two binary words represented in fractional 2s complement notation. The classical A/D conversion of quadrature channels has been achieved by two parallel assemblies each containing S/H, A/D, and a register in series. Although the shortened method saves two S/H, one A/D and two registers, it requires a faster A/D and analog switch in order to reduce the inaccuracy due to delay between samples from the two channels. Fortunately, new components make possible the realization of this method. For our purpose we chose the 4066 bilateral switch and TDC 1014J A/D converter (6 bit, 30 nsec).

Assuming N = 32, the first 16 converted samples of each block are stored in a 8 bit word-length RAM (I and Q channels separately). Starting with the 17th sample, their binary equivalents are not stored directly but are transformed into new expressions according to **Eq. 4**. For example, X(16) transforms into X(16) + X(0) and X(16) - X(0), or X(31) into X(31) + X(15) and X(31) - X(15).

This transformation adds one bit to the original word length, so the RAM has to be enlarged accordingly. Therefore two 931422 TTL-Ts RAM were chosen (75-nsec access time, 250-mw power dissipation). Fig 2 describes RAM organization during the two phases, between the 1st and the 16th and between the 17th and the 32nd samples.

The procedure mentioned above occurs at the sampling rate and spends only a small portion of the time interval between two samples. For example, with sampling rate of 10 KHz, the duration of A/D conversion, read memory, add or subtract, and write memory for quadrature channels is about 400 nsec, or only 0.4% of the sampling cycle. The remaining 99.6% of the time is exploited for DFT processing of the preceeding block of samples (W and W<sub>Q</sub> in **Fig 2**).

The processing unit is based on an  $8 \times 8$  multiplier/ accumulator TDC 1008J (it could be  $12 \times 12$  or  $16 \times 16$ according to specific demands). This component performs multiplications, accumulations, squaring, and additions (A + B = A × 1 + B × 1; A - B = A × 1 + B × (-1)) according to the algorithm described in a following section, "shortened DFT algorithm," resulting in a power spectrum for each m (A.11). Word length considerations are presented in a following section, "word length considerations," indicating the specific bits that are ignored as noise, others that are compared with a calculated margin level and finally those that are detected directly by a limiter.

### shortened DFT algorithm

Spectral line S(m) normalized to 1/N is:

$$S(m) = \sum_{r=0}^{N/2-1} \left\{ \exp(-j2\pi mr/N) \left[ X_r + (-1)^m X(r+N/2) \right] \right\}$$

if

$$Y_r = X_r + (-1)^m X (r + N/2)$$

A2

then quadrature channels are expressed as:

$$Y_r = Y_{1r} + jY_{Qr}$$

A3

Combining **Eq A1** with **A3** and substituting the Euler expressions for the exponent we obtain:

$$\begin{split} S(m) &= \sum_{r=0}^{N/2-1} Y_{1r} \cos(2mr/N) + \sum_{r=0}^{N/2-1} Y_{Qr} \sin(2\pi mr/N) + \sum_{r=0}^{N/2-1} Y_{Qr} \cos(2\pi mr/N) - \\ &\sum_{r=0}^{N/2-1} Y_{1r} \sin(2\pi mr/N)] \end{split}$$

if:

$$a = \sum_{r=0}^{N/2-1} Y_{1r} \cos (2\pi mr/N)$$

A5

| b = | $\sum_{r=0}^{N/2-1}$ | $Y_{1r} \sin (2\pi mr/N)$ | A6        | 6 |

|-----|----------------------|---------------------------|-----------|---|

| c = | $\sum_{r=0}^{N/2-1}$ | $Y_{Qr} \cos (2\pi mr/N)$ | A7        | A |

| d = | $\sum_{r=0}^{N/2-1}$ | $Y_{Qr} \sin (2\pi mr/N)$ | <b>A8</b> | 4 |

|     |                      |                           |           | P |

| The real expression will be: $g = a + d$ | A9  |

|------------------------------------------|-----|

| The imaginary one will be; $h = c - b$   | A10 |

|                                          |     |

The final result for the power spectrum will be:

$$PS(m) = g^2 + h^2$$

A11

### word length consideration

The following explanation will be accompanied by a numerical example based on: number of DFT points per block (32), input dynamic range of quantized video signals (6 bits), noise level of white Gaussian noise ( $\Sigma_{Xn}=0$ );  $\sigma_{n=1}$  LSB and coefficient accuracy (for m = 32) (5 bits).

According to the SDFT algorithm, quantized input signals are processed to obtain new 7-bit-long expressions. The result is a 12-bit word. Accumulator of 32 multiplications adds to the result 5 bits at the most. In order to avoid truncation, a 17 bit word is needed. Assuming the noise level of 1 LSB is accumulated according to  $N^{0.5}$  law, at the end of the process the noise level will reach the 9<sup>th</sup> bit out of the 17<sup>th</sup> result.

Calculations of g, h (see the previous section), their squares and the PS(m), are performed while ignoring 8 LSB (which are considered noise). Thus, if the processing unit is based on an  $8 \times 8$  multiplier acumulator, only bits 9 to 16 are considered for obtaining PS(m). The 1 MSB indicates immediately existance of a signal for the proper m.

### calculation time

Calculation time of 32 points DFT processor based on the shortened algorithm is based on the following data: Q (quadrature) = 2, TSW (switch on) = 200 ns, TAD (A/D conversion) = 30 ns, TWR (write RAM) = 75 ns, TRR (read RAM) = 75 ns, TLS (LS-TTL operation) = 30 ns, TAP (read PROM) = 125 ns and TMA (multiply/accumulate) = 125 ns.

Duration of sampling, A/D conversion, additions and writing in RAM on 32 quadrature input signals:  $(N/2)(TSW + Q (TAD + TWR)) + (N/2)(TSW + Q (TAD + TRR + TLS + TWR)) = 16.5 \ \mu$ s. Multiplication/accumulation time of a complete block:  $4[(N/2)^2(TAP + TMA) + TLS) = 256 \ \mu$ s. PS(m) calculation time of 32 spectral lines:  $(2N/2)(2 \times 2 \times (TLS + TMA) + TLS + TMA) = 24.8 \ \mu$ s. Total calculation time is approximately 300 \mus; and maximum sampling rate, 100 KHz.

### references

- (1) C.M. Radar, "Discrete Fourier Transforms", *Proc. IEEE*, June 1968.

- (2) S. Winograd, "On Computing the DFT", Proc. nat. Acad. Sci., USA, Vol. 73, Apr. 1976.

- (3) S. Winograd, "A new Method for computing DFT", Proc. IEEE Int. Conf. Acoust., Speech, Signal Proc., 1977.

- (4) H.J. Nussbaumer, P. Quandale, "Fast Computation of DFT Using Polynomial Transforms", *IEEE Trans-on Acoust.*, *Speech*, *Signal Proc.*, Vol. Asst 27, Apr. 1979.

Barney Stevenson just spent two years programming and de-bugging a process control system in assembly code.

Now Barney thinks he deserves some congratulations for his efforts.

### Sorry Barney,

Barney Stevenson thought he deserved a pat on the back. As project manager at Smart Widgets, Inc., he had taken on the biggest realtime process control headache of his life. And after 24 months he'd finally succeeded in programming and de-bugging Smart's newest product.

A

1

- 0

\*

(Pr

14

We think Barney missed the boat.

Barney figured the choice was simple. High level languages like Pascal and Fortran could program quickly,

but would run too slowly and take up too much memory. Assembly code would take longer to program and debug, but was

the only answer for real-time applications.

Wrong.

Real wrong. Barney didn't know about FORTH: a language that runs nearly as fast as assembly, is just as compact (if not more so), yet can cut development time by a factor of 10 over assembly language. He also didn't know

about FORTH, Inc.

They're the people who invented this remarkable tool, evolved it, and for 10 years have seen it used in thousands of applications... from running an observatory to sorting baggage, from video games to industrial robotics. Virtually every real-time application imaginable.

The latest evolution of FORTH is called polyFORTH™ An incredible programming environment available for just about any mini or micro processor.

For Barney? Still no cigar. But for you, FORTH offers a software tool that in speed, compactness and extensibility, simply has no match.

So call us at (213) 372-8493. Or write FORTH, Inc., 2309 Pacific Coast Highway, Hermosa Beach, California 90254. We'll rush you the latest on polyFORTH,<sup>™</sup> and tell you where you can see it in action.

... the real-time saver.

ORTH.Inc.

**Circle 75 on Reader Inquiry Card**

# MICROPROCESSORS

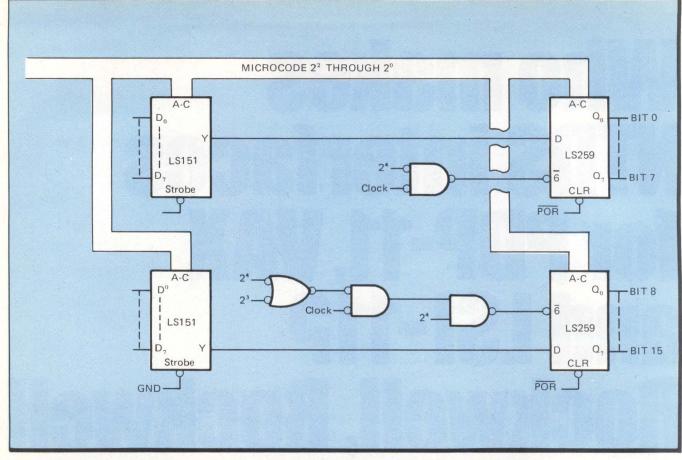

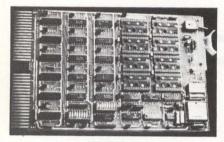

# Microprogrammable Processor

### single-bit storage concept

T he single bit storage concept is adaptable and may be varied to meet systems requirements. Expanding bit storage is an efficient method, and permits a doubling of total data bits stored for each added bit of microcode. The ease of enable control circuitry modification, which changes the division between latches assignable to status bits only, (or to either status or flag bits,) permits rationalization of system requirements and design implementation.

### by Alan W. Bentley

This design illustrates the principle of simultaneous and rapid processing. On a given microcode instruction, one flag status bit may be modified while several other bits may be referenced by different sectors of the microcode which are performing independent functions. Finally, latches differ from edgetriggered-storage devices as the latch-enable activates input gates, permintting track of D input during enable time.

At enable completion, the latch stores the last internally propagated input. Therefore, because the latch is enabled during the second half of the clock period, the latch input stabilization time is maximized to permit proper status storage. Specific instructions, however, may have long execution times.

Although instruction driven microprocessors fulfill the majority of processing applications, the high capability portion of the performance spectrum is dominated by microprogrammable processors. This follows from their architectural differences. An instruction driven microprocessor is a serial device with a fixed architecture and a given repertoire of instructions. Its performance is limited by the necessity of sequentially executing those instructions. Its operating modes are relatively inflexible and it is difficult to adapt either the instruction set or the architecture to increase performance. Conversely, the microprogrammable organization is more flexible. It is packaged as vertical slices

Alan W. Bentley is from Cubic Corp, of the Defense Systems Div. in San Diego, CA. through a register array, arithmetic and logic unit, instruction decoding and execution logic and connecting paths.

Interconnecting slices establishes bit widths of the data word and processing unit. To support and control the processing unit, additional hardware is added and microcode instruction control is implemented. Processor performance is improved by increasing the number of tasks that may be performed simultaneously. This is achieved by expanding the support hardware and the microcode, obtaining a finer division of tasks and an increased capability to manipulate control and enable lines. Thus, the increased performance of a microprogrammable processor system is due to its organization which permits a number of tasks to be performed simultaneously.

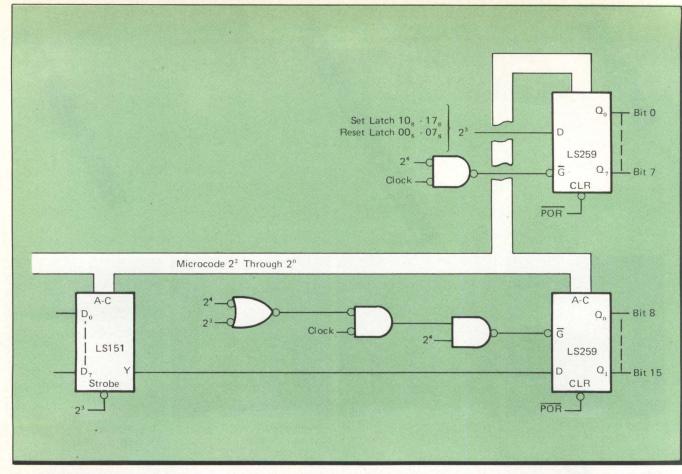

### single bit storage concept

In microprogrammable processor design, microcode controlled storage for status and flag bits must be provided. An approach has been developed that uses both microcode and hardware efficiently, and is adaptable, so it may fulfill varying system requirements. An 8-bit multiplexer (LS151) and an 8-bit addressable latch (LS259) perform the data selection and storage functions, controlled by 4 bits of microcode. The lower three bits of microcode  $(2^0 - 2^2)$ address both the multiplexer and the latch, the upper code bit,  $2^3$ , is used as a multiplexer strobe and when true, drives its output false. Also, the upper two code bits,  $2^2$  and  $2^3$ , when both true, suppress the latch enable. This divides the microcode word into three sectors;  $0_{16}$  through  $7_{16}$  stores the *(text continued on page 33)*

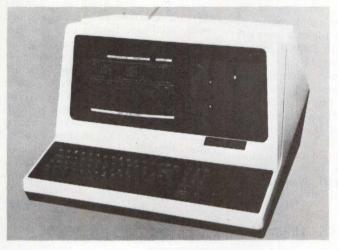

# Build your own DEC system with CRDS...

# Complete software compatibility at a savings!

With CRDS, you can configure your own DEC system and be assured of complete software compatibility. Each of the above systems is provided with slides for rack mounting or can be used in desk top applications. All DEC LSI 11 based modules and associated software packages are available through CRDS, if desired.

### **Attractive Packaging**

Careful attention is given the CRDS repertoire of enclosures in assuring you an attractive yet comfortable blending of product in the DEC environment.

### **Significant Savings**

Flexibility of procurement plus attractive OEM schedules allows you to optimize dollar savings in configuring your CRDS system. Use the time tested technique. Compare.

### Warranty and Maintenance

A 90 day warranty is offered with your CRDS system. In the event of malfunction, by use of provided diagnostic routines, the defective submodule is normally found within minutes. After verification with the CRDS Maintenance Department, a replacement for your defective module will be promptly forwarded. **Call or write** for a comprehensive literature package and prices.

Charles River Data Systems, Inc. 4 Tech Circle, Natick, MA 01760 Tel. (617) 655-1800 TWX (710) 386-0523

### **Circle 19 on Reader Inquiry Card**

| Usage      | Multiplexer |             | Output         | Microcode<br>Flag |       | Status  |

|------------|-------------|-------------|----------------|-------------------|-------|---------|

| Assignment | Input       | Connection  | Latch          | Set               | Reset | Storage |

| Flag 0     | D0          | VCC         | Qo             | 0                 | 8     |         |

| Flag 1     | D1          | VCC         | Q1             | 1                 | 9     |         |

| Flag 2     | D2          | VCC         | Q <sub>2</sub> | 2                 | Α     |         |

| Status A   | D3          | Parameter A | Q <sub>3</sub> |                   |       | 3       |

| Status B   | D4          | Parameter B | Q4             |                   |       | 4       |

| Status C   | D5          | Parameter C | Q5             |                   |       | 5       |

| Status D   | D6          | Parameter D | Q <sub>6</sub> |                   |       | 6       |

| Status E   | D7          | Parameter E | Q <sub>7</sub> |                   |       | 7       |

Microcode B<sub>16</sub> illegal — use unconditionally resets Q<sub>3</sub>, status a l

Microcodes C<sub>16</sub> - F<sub>160</sub> surpass latch Enable input

### Table 1: Microcode and input assignment for typical 8 bit storage application.

| Usage<br>Assignment | Multiplexer<br>Input | Connection  | Output<br>Latch | Microcode<br>Flag<br>Set | Reset | Status<br>Storage |