# COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS DECEMBER 1968

in this issue

ON-LINE MEMORY INTEGRITY EVALUATION AND IMPROVEMENT SYNTHESIS OF SEQUENTIAL MACHINES POLES AND ZEROS IN PERIPHERALS HOW TO SPECIFY A SPECIAL PURPOSE CORE MEMORY SYSTEM 2 YEAR INDEX TO COMPUTER DESIGN

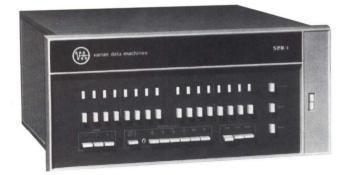

# The new Varian Data dual-environment 520/i.

#### Tag this one to upset the present balance of power and price.

We've hung some other powerful attractions on this system-oriented computer besides that price tag. Two complete sets of hardware registers, including index registers.

They allow the 520/i to run dual programs. A single 1.5  $\mu$ s instruction transfers control between programs, or between processing and I/O programs. Data may be manipulated in multiple 8-bit bytes—it'll do arithmetic in 8, 16, 24 or 32-bit lengths within the same program. Program precision is changeable any time.

Hardware includes two 32-bit accumulators, two 16-bit index registers, two program counters, and two overflow registers. Eleven interrupt lines with four hardware priority levels. Expandable 4K to 32K 1.5  $\mu$ s memory. IC construction. 50 basic instructions. Interface modules for I/O devices. Proven software. Current delivery: 60 days.

If you're comparing price/performance ratios, 520/i is the new power to be reckoned with-write for your brochure.

varian data machines

a varian subsidiary 2722 Michelson Dri (714) 833-2400

2722 Michelson Drive/Irvine/California 92664 (714) 833-2400

SALES OFFICES: U.S., Santa Monica and San Francisco, California; Vernon and Westport, Connecticut; Chicago, Illinois; Houston, Texas; Fort Washington, Pennsylvania; Washington, D.C.; Waltham, Massachusetts; Fort Lauderdale, Florida. INTERNATIONAL: Australia, France, Germany, Sweden, Switzerland, United Kingdom, Ireland and Belgium.

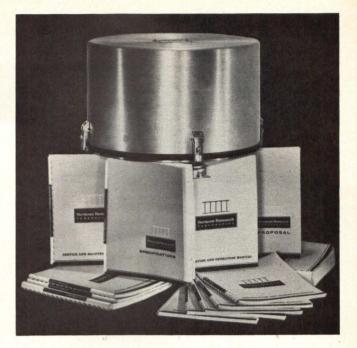

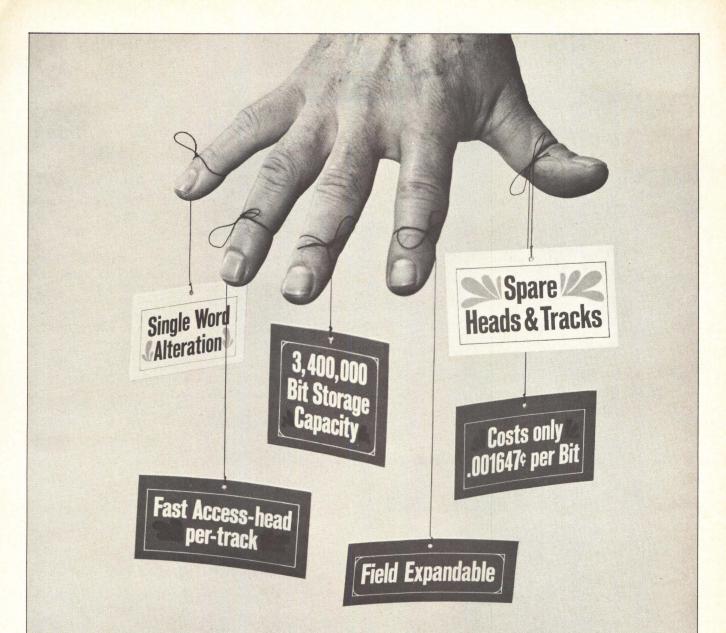

#### We support our drum memories

It's all done with paper. Start with the proposal ... a clear, complete, and factual summary of all performance figures ... all interface connections and levels ... all timing data ... all physical dimensions ... all you need to design and build a complete interface. Continue with an Installation and Operation Manual, with all you need to install and operate your drum. Behind that, there's a Service and Maintenance Manual, with detailed schematics, theory, trouble-shooting, adjustments, repairs, tool lists, diagrams, photos, test program outline ... all the facts and procedures you'll ever want. Behind these you'll find a comprehensive training course for your personnel. And behind that, there's another piece of paper-VRC's total warranty for one year on drum and electronics . . . backed by a staff of trained field engineers, who fly to your site for installations or emergencies.

It's surprising, the support you can get from pieces of paper. Try the first piece . . . our general drum memory brochure, DB-6808.

#### Computers are known by their MEMORIES...

...so is

Fact:

#### DRUM MEMORIES • SYSTEMS • DISK PACKS

Box 20a, Precision Park, North Springfield, Vermont 05150 • Telephone 802/886-2256 • TWX 710-363-6533

When it comes to engineering opportunities (and the good life, North Country style), the place to come is Vermont Research Corporation. For specific information, contact: RICHARD A. STOVER, Vice President-Engineering. CIRCLE NO. 2 ON INQUIRY CARD

#### This is the house that Jack built.

Inside is a single micro-logic circuit card from Control Logic. It's all the cards Jack needs. Only one, because a Control Logic card is compatible and versatile with capability in process control systems, and versatility in automatic wire-wrap assemblies and component combinations. And it fits his design easily. But, you may need more than one micro-logic circuit card from Control Logic. And your design may not be as simple as Jack's. No matter. Control Logic's packaging capability can adapt to your design. With its card frames, racks, cages, and power drawers, Control Logic can fit as many micro-logic circuit cards as you need... Into the house that you built! To find out how, call or write:

Natick, Massachusetts 01760 / Tel: (617) 235-1865

Publisher and Editorial Director ROBERT BROTHERSTON

> Associate Publisher ANTHONY SALTALAMACCHIA

> > Editor JOHN A. CAMUSO

Managing Editor JOHN J. COLANTINO, JR.

Editorial Consultants BERNARD M. GORDON GERHARD L. HOLLANDER GILBERT P. HYATT

Editorial Advisers Richard Ahrons Fli Anfenger James R. Bright Waldron S. MacDonald Harold H. Seward

Contributing Editors T. PAUL BOTHWELL A. S. BUCHMAN ROBERT P. FORAN MADELINE JOHNSON RUDOLPH J. KADLEC RICHARD B. LAWRANCE H. S. MIILLER

> Art Director JAMES FLORA

Production Manager BRYAN De LORENZO

> Editorial Production JUDY KELLEY

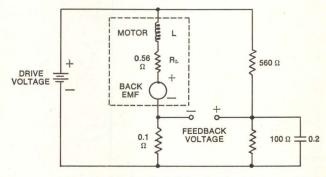

Technical Illustrator WILLIAM R. SULLIVAN

> Advertising Production TERRY ARMENTI

Circulation Manager ALMA BROTHERSTON

Vice President-Sales LINDSAY H. CALDWELL

Editorial & Executive Offices Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1968 by Computer Design Publishing Corporation. Controlled circulation postage paid at Bristol, Conn. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS-FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Winchester, Mass. 01890. Subscription rate to annqualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 42,000

## COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS

#### FEATURES

- 31 ON-LINE MEMORY INTEGRITY EVALUATION AND IMPROVEMENT F. BUJNOSKI Memory access integrity may be evaluated by the means discussed in this paper.

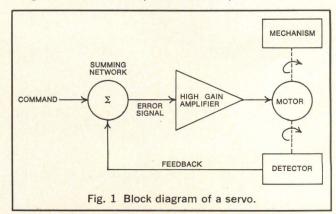

- 36 POLES AND ZEROS IN PERIPHERALS T. FITZGERALD This paper provides a review of the design and use of servomechanisms and discusses their advantages and peculiarities.

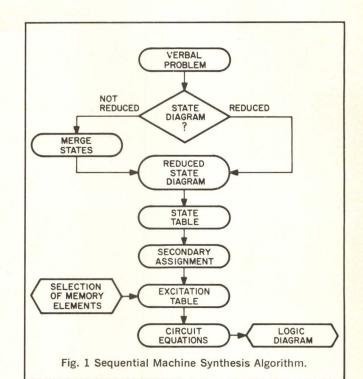

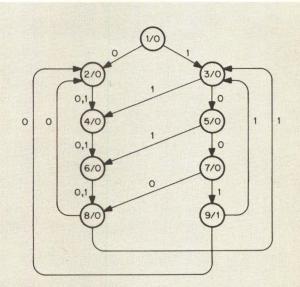

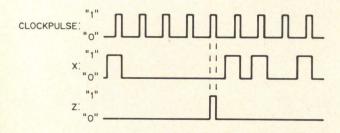

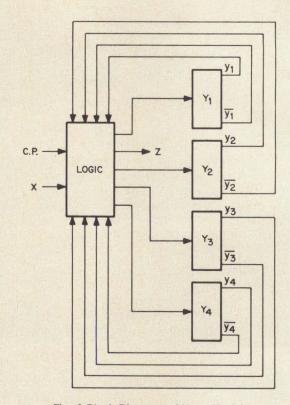

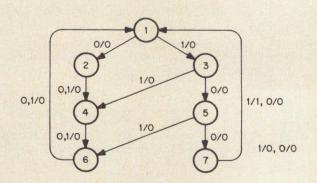

- 46 THE SYNTHESIS OF SEQUENTIAL CIRCUITS M. A. ETTINGER The Mealy sequential machine model is explained and is compared with Moore's model in this paper.

- 54 HOW TO SPECIFY A SPECIAL PURPOSE MEMORY SYSTEM B. W. RICKARD An application note which answers the question: How do you adequately specify a special purpose system?

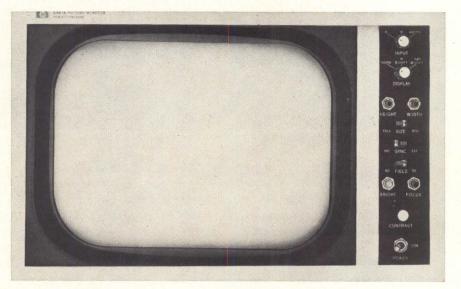

#### 62 A HIGH-RESOLUTION TV MONITOR This product feature describes a picture monitor designed for Alphanumeric Display Applications.

#### 84 COMPUTER DESIGN INDEX

A two-year index to feature articles that have appeared in Computer Design.

#### DEPARTMENTS

- 16 INDUSTRY NEWS

- 20 CD DEVELOPMENTS

- 24 CD COMMENTARY

- 64 NEW PRODUCTS

- 80 NEW LITERATURE

| Reader Subscription | Card | opposite page 1  |

|---------------------|------|------------------|

| Reader Service Card |      | opposite page 88 |

CIRCLE NO. 3 ON INQUIRY CARD

## If you're building any computer except a Computer, you need $CT\mu L$ .

CTμL integrated circuits will give you more speed for less money than any other ICs. They're perfect for process control systems, test instrumentation, central processing units, computer peripheral equipment just about anything short of an airborne computer.

#### Keep it in the family.

You can build a complete digital logic system with Fairchild's family of  $CT\mu L$  devices. We have gates, flip-flops, inverters and memory circuits. A dozen different devices that make a computer easy to package. And, you'll need only about 80 percent as many packages as required with TTL.

#### You get out of it what you put into it.

The key  $CT\mu L$  characteristic is nonsaturating logic. That means you get fast gate propagation delay (typically 3nsec) with slow rise and fall times (typically 6nsec). So, there's no need for transmission lines or complex packaging. You can build an entire computer with normal twosided circuit boards. Also,  $CT\mu L$  can handle signal swings as large as 3V. It also provides typical noise immunity of 500mV.

#### What we'll do for an encore:

MSI  $CT\mu L$  will be out before the year ends.  $CT\mu L$ -II will be out even sooner, offering improvements like gate propagation delay of 1.5nsec. (typical, loaded) and a buffer and

## The world's largest manufacturer

inverter with propagation delays of 5nsec, compared with 12nsec in standard  $CT\mu L$ . And, the new MSI and  $CT\mu L$ -II circuitry will interface beautifully with all these standard  $CT\mu L$  devices:

#### Device Price (100-999) 9952 Dual NOR Gate ..... \$1.25 9953 Triple AND Gate ..... 1.25 9954 Dual Four-input AND Gate ..... 1.25 9955 Eight-input AND Gate ..... 1.25 9956 Dual Buffer 1.25 9957 Dual-rank Flip-flop ..... 2.00 9964 Dual Three-input and Single-input AND Gates ..... 1.259965 Quad Single-input AND Gate ..... 1.25 9966 Quad Two-input AND Gates, one pair with OR-tie ..... 1.25 9967 JK Flip-flop 2.00 9968 Dual Latch 2.00 9971 Quad Two-input AND Gates with OR-tied pairs ..... 1.25 9972 Quad Two-input AND Gates, one pair with OR-tie ..... 1.25

If you want  $CT\mu L$ -II in sample quantities, call Fairchild. If you want standard  $CT\mu L$  in production quantities, call a Fairchild distributor. He has everything you need to build any computer. Even a Computer.

#### FAIRCHILD

SEMICONDUCTOR

Fairchild Semiconductor/A Division of Fairchild Camera and Instrument Corporation/313 Fairchild Drive, Mountain View, Calif. 94040 (415) 962-5011/TWX: 910-379-6435

## of LSI admits there's another way:

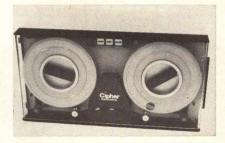

## Mag tape too expensive? Punched tape too slow?

### Your small computer deserves PEC data power!

#### High Speed - Low Price

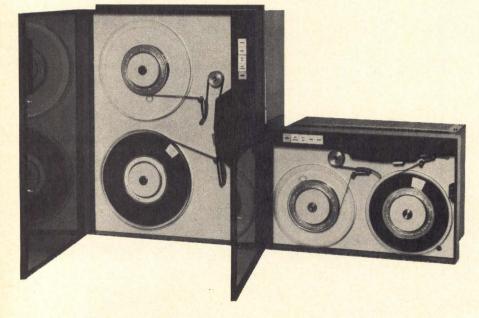

Seems a shame to shackle that fast new computer of yours with slow, maintenance-prone punched tape. Yet digital magnetic tape recorders are so expensive.

Not now, they aren't.

PEC can give your small computer real write/read data power. 10 KHz data transfer rates for under \$3,000. 20 KHz transfer rates from \$5,000. (Less than \$4,000 in quantities).

Discriminating computer users are demanding higher input/output performance on even the smallest machines.

That's why more and more major computer manufacturers are offering PEC digital magnetic tape recorders as standard equipment.

Insist on low cost-high performance PEC data power for your computer.

You can store ten characters on an inch of punched tape. You can store up to 800 characters on an inch of magnetic tape. That's 80 times more data per inch!

What about data transfer rates? A paper tape perforator plods along at 150 characters a second. Pretty slow for today's fast computers.

PEC digital magnetic tape recorders zip data in and out at speeds to 25 ips. Data transfer rates up to 20 KHz. That's 133 times faster than punched tape.

PEC data power costs just a little more than punched tape. Yet look at the tremendous increase in storage capacity and data transfer rates you get.

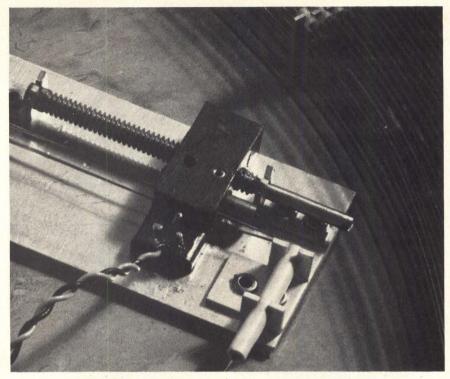

PEC digital magnetic tape recorders use an elegantly simple single capstan velocity servo system. Pinch roller, a major source of skew and tape wear, is eliminated.

PEC recorders cost half as much as competitive makes, yet perform even better.

IBM compatible? You bet. Including the precise requirements for System/ 360, 9 channel, 800 bpi operation.

Choose the speed you want from 4 to 25 ips, at 800, 556, or 200 bpi. 7 track dual density available too. And up to 4 PEC recorders can operate from a single computer.

Select the data capacity, transfer rate, rack height and price from 3 distinct models.

| Three Reel Sizes |                        |                  |

|------------------|------------------------|------------------|

| Reel Size        | Max.<br>Transfer Rates | Tape<br>capacity |

| 7 inch           | 10 KHz                 | 600 feet         |

| 81/2 inch        | 20 KHz                 | 1200 feet        |

| 101/2 inch       | 20 KHz                 | 2400 feet        |

PEC also makes synchronous writeonly and read-only recorders. A complete line of incremental models too. Perfect for data acquisition systems, off-line plotters, line printers, and data terminals. Perfect for just about any input or output requirement, for that matter.

Write or phone today for our 8 page brochure.

PERIPHERAL EQUIPMENT CORPORATION

9551 Irondale Avenue Chatsworth, California 91311 = (213) 882-0030 = TWX (910) 494-2093

CIRCLE NO. 5 ON INQUIRY CARD

## Is your computer ready for memory expansion?

You would be surprised how RCA's "plug-in" compatibility makes it easy and inexpensive to add more memory capacity.

Experience shows that every computer soon runs out of memory. If your computer has reached this point, RCA Memory Products Division can provide compatible high speed memory systems for significantly less than you would expect to pay. RCA offers standard off-the-shelf memories with cycle time as fast as 750 nanoseconds and access time of 290 nanoseconds, capacities of 4K x 4 to 32K x 72. We'll quickly work out the "plug-in" compatibility for you, including voltage levels, timing and hardware. Simply let us know what your interfacing requirements are, and we'll take it from there. Or, we'll assist you, if you wish to do

#### the job yourself.

An RCA Field Representative will be glad to discuss your needs. Or, call or write Marketing Department (617-444-7200, Ext. 233) RCA Memory Products Div., 150 "A" St., Needham Hts., Mass. 02194.

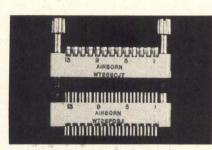

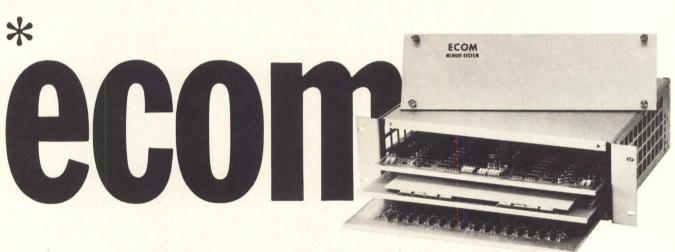

## Our economy model

It's our 8B Series. Made to Winchester standards of quality and reliability—but at an easy-on-the-pocketbook commercial price.

Frankly, you'd look long and hard for a better buy than our 8B Series connectors for computers, memory systems, process control systems—or just about any industrial or commercial application.

We offer them in single and double row termination. You have a choice of eight different contacts—with from six to thirty positions. And contacts are removable. Easily. With a simple hand tool. Polarizing pins are available, too.

Let us send you the facts about how the Winchester 8B Series gives you more for your money. Isn't that a nice thought? Write: Winchester Electronics, Main St. and Hillside Ave., Oakville, Connecticut 06779.

WINCHESTER ELECTRONICS

LITTON INDUSTRIES

CIRCLE NO. 7 ON INQUIRY CARD

Erma is gone, Erma's memory is alive and processing traveler's checks in San Jose, California. but her memory We built the core memories for Bank of America's ERMA comlives on.

puters back in 1959. They contained 80mil cores providing a cycle time of 32

microseconds and an access time of 12 microseconds. Capacity was 4000 words (28 bits/word). One of those memories is still in use. It's slow by today's standards but perfectly suited for its job.

> AMPEX THE ONE COMPANY THAT CAN REMINISCE ABOUT OLD MEMORIES.

### Meet our newest: The 500 nanosecond 25DM-500

The new Ampex 25DM-500 has a full cycle time of 500 nanoseconds and an access time of 300 nanoseconds. The basic memory module is 8K x 36 bits. It uses 18-mil cores in a 3-wire 2.5D configuration. Maximum capacity is 32K x 72 bits. This fast new memory is the latest in our wide line of core memories. They include small, inexpensive 1.5 microsecond memories (RF-1), the 1.0 microsecond RF-4, the fast access (350-nanosecond) 900 nanosecond RG memory, the 3-wire 3D 750 nanosecond 3DM750, and the new 500 nanosecond 25DM-500.

In addition to memories, Ampex produces stacks,

arrays and cores. We supply a full line of ferrite cores from 18 to 80-mils O.D., including a line of standard cores for wide temperature requirements. The memory designer will find help in our design assistance and our catalog of commercial

and military arrays. Stacks are available in 2.5D and 3D (3 or 4 wire) configurations; 18-, 22-, 30and 50-mil core sizes; regular or ruggedized to meet MIL-E-16400 or MIL-E-5400.

For full information about any of our memory products, circle the reader card number or write Ampex Corporation, 401 Broadway, Redwood City, California 94063.

CIRCLE NO. 8 ON INQUIRY CARD

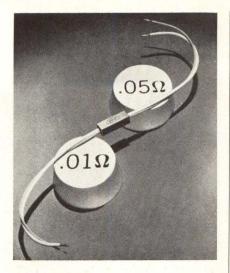

Standardizing a military memory has its ups and downs.

## The ups:

Apollo

Airborne navigation computer X-15 computer Missile re-entry Supersonic aircraft Side-looking radar

## The downs:

Counter-mortar radar Counter-measures computer Deep-submergence vehicle Underground bomb tests Ground-mobile marine radar Let's face it—there's no way to standardize on a single configuration for a product that goes into as many diverse applications as our military memories do, so we've built two types that fit a wide variety of requirements. Maybe yours? Our SEMS-5 has a cycle time of  $2\mu$ sec, storage capacity to 131,062 bits, and meets all the specs to qualify it as an airborne system, but you'll find it in ground-based and oceano-graphic applications. Our SEMS-7 has a cycle time of  $2\mu$ sec, storage capacity to 327,680 bits and was designed for ground-based applications, but it's also designed into a supersonic aircraft.

Delivery is fast for almost any application, and to help you choose the right configuration, we're offering a paper entitled "How to Specify a Special-Purpose Memory" as well as product literature. Just ask.

12021 Chadron Ave., Hawmome, Camornia 30250

CIRCLE NO 9 ON INQUIRY CARD

## We know somebody with connections.

## So we told them about wire insulation made of Kynar.

## That was five years ago.

Burroughs Corporation's computer plant in Pasadena runs 200,000 feet of wire a week, makes 120 terminations per minute. With that many connections, at that speed, the right kind of insulation is important—insulation that's not only tough, but absolutely reliable. That's why Burroughs has used wire insulated with Kynar for back planes since 1963.

Why Kynar? A Burroughs engineer answers: "It works better than many others we've tried ... so why argue with success?" Kynar works for some good solid reasons. It has twice the cut-through resistance of other common fluoroplastics and virtually eliminates cold-flow problems. Kynar runs economically in automatic wire-wrap equipment...it feeds, cuts, and strips smoothly. It's unaffected by cleaning solvents, and it won't degrade with age.

Tough arguments? You bet. Tough material ... that's Kynar. So take a tip from experience. Switch to wire insulated with Kynar. It's available from leading wire manufacturers. For additional information contact: Plastics Department, Pennsalt Chemicals Corporation, 3 Penn Center, Philadelphia, Pa. 19102.

### Kynar...the fluoroplastic that's tough! (PENNSALT)

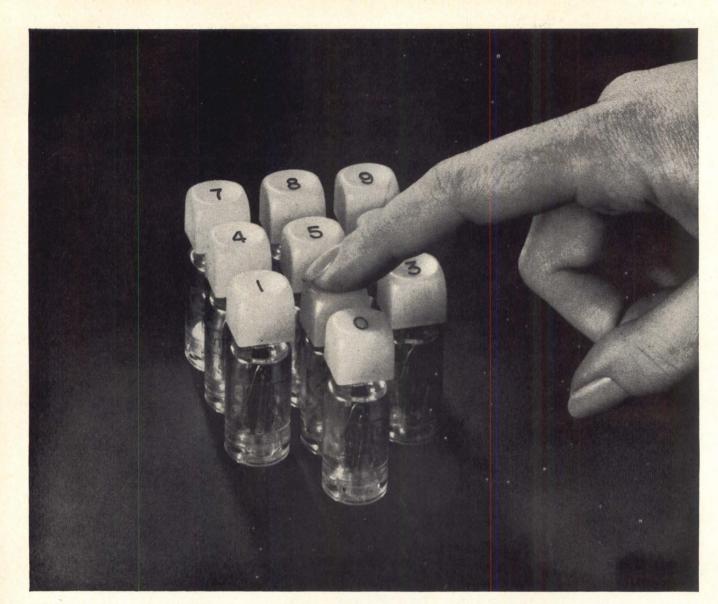

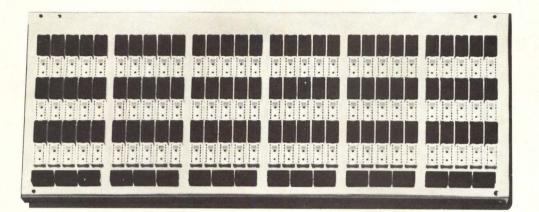

## These new keyboard switches feature unusually precise action and low-cost mounting. See for yourself—write for samples.

These elegantly styled key switches -designed for handling switching at logic levels—are especially suitable for computers, learning and business machines, and advanced control equipment.

**Designed by Raytheon,** they have a featherlight touch that is precise and reliable. Just a 3-oz. touch activates the switch. Because of the unique design, this action can be repeated more than 10 million times. Yet the switches cost less than \$1 in production quantities.

A wide range of standard- and custom-cap shapes, sizes, colors, and alphanumerics are available. Characters can be hot stamped, engraved or molded through. Bases can be flat or with 10° slope. Characters can be illuminated by backlighting. All switches are made of high-quality materials: stain-resistant caps; polycarbonate body parts; stainless steel springs; beryllium and stainless steel contacts. They are available in singleand double-level wipe-action types, and in dry-reed, hermetically sealed single- and double-level types.

For free samples, write on your letterhead describing your application to: Raytheon Company, Industrial Components Operation, Dept. 2351-CD, Quincy, Massachusetts 02169.

Simple, low-cost mounting. Raytheon switches plug into .125" PC board. Contact pins snap in, firmly lock switch in place for soldering. This permits you to use flow soldering techniques cut keyboard assembly time and costs.

CIRCLE NO. 11 ON INQUIRY CARD

#### Flexibility.

And we'll give you a good reason to buy our flexible circuits over anyone else's:

We make them with the same kind of precision our regular printed circuits are known for.

We can produce them in quantity to the most stringent specifications—single or multilayer.

We're probably the flexible circuit source you've been looking for.

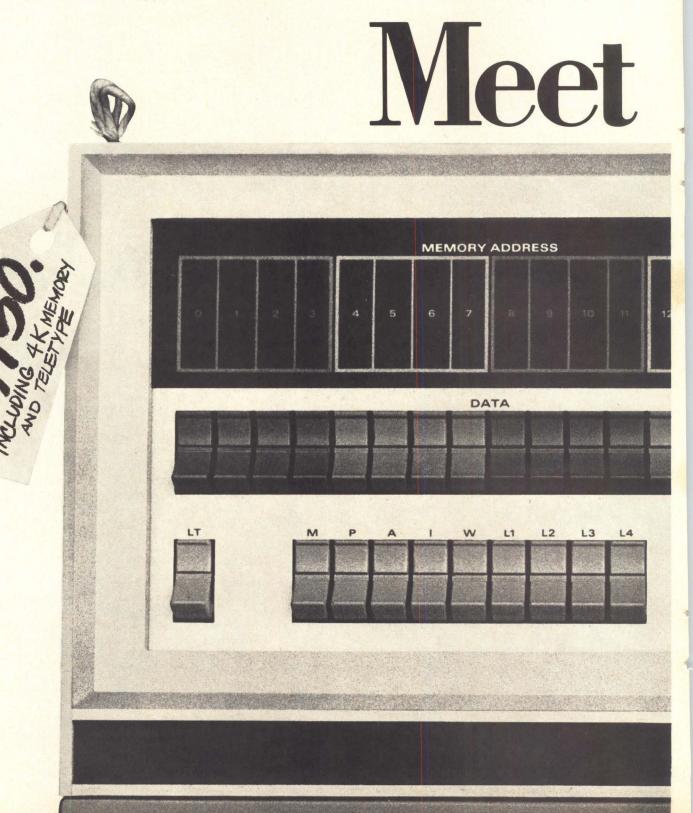

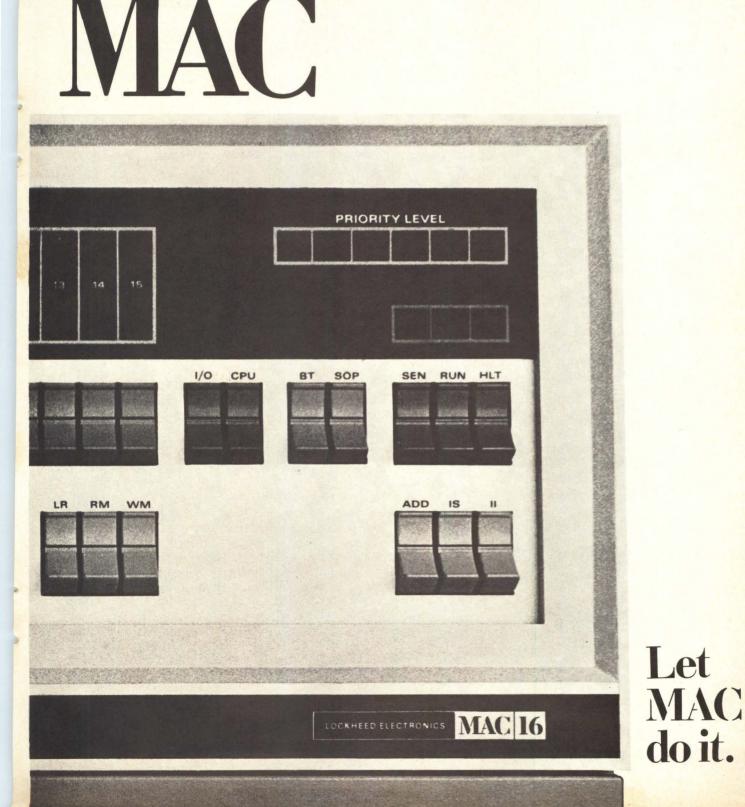

For your copy of "A Designer's Guide to Flexible Circuits," write to Printed Circuits, Lockheed Electronics Company, Data Products Division, 6201 E. Randolph St., Los Angeles, California 90022.

## We've added a new wrinkle to our printed circuits.

CIRCLE NO. 12 ON INQUIRY CARD

Alasa Ingana

LOCKHEED ELECTRONICS COMPANY A Division of Lockheed Aircraft Corporation

## with a screw driver and 15 minutes ... you can install a General Electric acoustic data set

Under the newly-filed tariffs, the use of customer owned acoustically-coupled data sets is authorized for use on all telephone company, public switched networks. If the economy of owning your own data transmission equipment is part of your plans for the new year, investigate the many reasons why the General Electric TDM-114 or TDM-115 Series can better satisfy your requirements.

Reliability? Eleven years (100,000 hours) Mean Time Between Failure.

Installation? A screw driver and 15 minutes does it. No adjustment or tune-up required.

**Operation?** Fully automatic.

Service? (if ever required) over 750 service

WERAL (S) ELECTRIC

facilities located throughout the United States.

Compatibility? Works with Teletype<sup>®</sup>, Kleinschmidt, Friden, GE, IBM, and other popular serial binary terminals at speeds up to 30 ASCII characters per second.

See for yourself how GE acoustic data sets are performance-proven to better satisfy your data transmission requirements. Complete specifications are yours for the asking. Write to Section 472-07, Fixed Point Communication, Communication Products Department, Lynchburg, Virginia 24502. In Canada, write to Canadian General Electric Company, Ltd., Information Systems and Defence Products Department, 830 Lansdowne Avenue, Toronto 4, Ontario.

TDM-114 TDM-115 CIRCLE NO. 13 ON INQUIRY CARD

GENERAL @ ELECTRA

#### WITH MDS LOW-SPEED LINE PRINTERS

MDS 4320 LOW-SPEED BUFFERED LINE PRINTER

LOW COST, HIGH RELIABILITY... MDS Series 4000 Low-Speed Line Printers, with print speeds up to 300 lines per minute, are especially designed for business or scientific applications where high speed is not needed.

> Low cost, reliability and performance are hallmarks of the MDS Series 4000 Line Printers. Designed for use with the newest compact data processing systems, the Series 4000 reflects the combined skills and engineering talent of MDS and a subsidiary, long recognized as a leading independent producer of highly dependable line printers.

> MDS Series 4000 features a rotating drum, on-the-fly, impact printer with long life reliability "built-in." Available in buffered (4320) and unbuffered (4300) console models; or as the MDS 4013 Printer Mechanism unit for integration with your own system.

> The 4320 has a ready strobe serial buffer and operates in three modes ... List Mode ... Line Edit Mode ... Edit Mode.

A few of the MDS 4013 features:

- Print hammers use MDS Penetration Control; energy and instant of impact are adjustable to very fine tolerances.

- Tape Control Vertical Format Unit ... provides 12 channels and 6 or 8 lines per inch.

- Up to six copies can be printed.

- Pin-Type chain drive shuttle paper feeding.

- New Fibre Optics System . . . only 3 light sources.

MDS 4320 and 4300 Console Units incorporate the 4013 print mechanism, power supply, power drive circuit, and I/O interface electronics.

Ask for: Folder-file on MDS Series 4000 Low-Speed Line Printers.

#### FOR MORE – MEET YOUR MAN FROM MDS

#### INDUSTRY NEWS

HP ENTERS COMPUTERIZED-CUSTOM TEST SYSTEM BUSI-NESS – The first computer-controlled custom test system from Hewlett-Packard's newly-formed Systems Division has been delivered to Magnavox Corporation, Fort Wayne, Indiana.

Marking the Palo Alto based instrument company's entry into the custom electronic test systems business, the system will automatically check out thick-film receiver circuits for new Magnavox radios. The company said the new division has four more computerized systems and about fifty other custom instrument sets currently in its backlog. "Our purpose in going into this business," Division Manager Richard J. Reynolds said, "was to solve the customer problems of getting new computer-controlled test systems working fast, at reasonable cost, with singlesource responsibility for the interface between the computer and test instruments. "We felt we could offer fast turn-around and economy by using a building-block approach to the hardware with standard interface cards.

The modular approach, HP explained, began about two years ago when the company embarked on a program to develop new digital computers with ability to interface to many instruments with plug-in cards. New programmable building-block instruments were also developed. The new division will also produce a line of standard computerized automatic test systems with a wide range of options for even faster delivery.

COMPUTER ROOM PACKAGE AVAILABLE FROM A SINGLE SOURCE – A pre-engineered packaged computer room that includes everything but the computer is now available from a single source. Design of the room, and manufacture and installation of all components—raisedfloor system, partitions, ceiling, air conditioning, lighting, and even light switches and cover plates—can be included.

The complete computer room package has the design flexibility to be custom engineered in modules to fit the individual needs of the user. From the initial design study and survey of customer facilities to the final onsite assembly, each component is integrated to overcome problems presented by either the computer system itself or the customer's existing facilities. This component tailoring results in accumulated savings for the user. Moreover, an entire room can be remodeled, enlarged, or totally relocated without scrapping components.

Modular design and rigid quality control standards insure the proper matching of all components to provide reliable performance. Components are shipped for fast field assembly with minimum disruption of the customer's operations.

Prebuilt packages for installation by the customer or local contractors are also available. The completed room is guaranteed if installation instructions are followed. Components are completely finished at the factory for immediate installation with little onsite cutting and fitting required. For more information write Westinghouse Architectural Systems Department, 4300 36th Street, Grand Rapids, Mich. 49508.

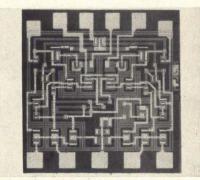

PHOTO-OPTICS LINKED TO COMPUTER TECHNOLOGY FOR PRECISION MEASURE-MENTS – An experimental device for measuring optical microdensity of an image to obtain positional accuracy has been developed by IBM's Boulder, Colo. Product Test Lab. The device links the photo-optical principles of the scanning registration densitometer to the electronic computer.

The system called RECI-B enables precise, accurate measurement of the positions of regularly spaced rows of microminiature images to insure proper registration on a master specimen; for example, a mask used to photo-etch integrated circuit chips. Each image must be positioned precisely to assure reliability of the circuits.

Positional accuracy is difficult to check optically because of variations in density at the edge of an image. REGI-B, however, assures that each image is measured at precisely the same edge point. By recording the distances between these specified points, it determines if an inscribed line is out of registration by as little as one ten-thousandth of an inch.

Optical density is measured by placing a photographic "step guide" on the light table ahead of the specimen. By reflection or direct transmission, a Kohler light source is passed through the specimen to a scanning microscope, which is controlled in the X axis by a variable speed motor and in the Y axis by a stepping motor. The light beam is converted to electrical pulses by a photomultiplier. These pulses, representing optical density, trigger the recording mechanism.

Density measurements are recorded on a strip chart or X-Y recorder. Image registration data are placed on digital tape for statistical analysis on an IBM System/360 computer.

When the master artwork is generated, small holes are punched near its edge at specified intervals. During data analysis, the computer reads the distance between the holes and automatically compensates for any stretch or shrinkage errors.

## The tradition breakers.

She's not the only one... five years ago TI advanced the state of the magnetic circuit breaker art with a smaller, lighter, simpler mechanism. It went over big. More recently, new TI magnetic circuit breakers show similar design breakthroughs. A 100-amp rating built into a 50-amp frame. A 50-amp rating squeezed into a 25% smaller package. A choice of 20-amp push-button and toggle twins that meet military specifications. A unique magnetic/ hydraulic time delay feature. And so on. These and other breaks with tradition make TI the logical choice to solve your circuit protection problems-quickly, economically, precisely. Write TI

Control Products Div., Attleboro, Mass. 02703, or tel. (617) 222-2800 Ext. 368

TEXAS INSTRUMENTS

#### INDUSTRY NEWS

HONEYWELL ADDS NEW DATA DISPLAY TERMINAL FAMILY – A new family of advanced desk-top terminals for remote on-line entry, retrieval and display of computer information will be marketed by Honeywell's Electronic Data Processing Division, Wellesley Hills, Mass.

The Series 2300 family of six Visual Information Projection (VIP) terminals will replace the current Honeywell VIP line manufactured by the Bunker-Ramco Corp. of Stamford, Conn. The Series 2300 also will be built to Honeywell specifications by Bunker-Ramo.

This series of VIPs may be used in such diverse computer applications as manufacturing production control, marketing data retrieval, library indexing, hospital patient records, stock and commodity market quotations, airline passenger or freight information and other similar management information systems, according to Eric N. Grubinger, group product manager of communications products at Honeywell EDP.

TAPED LECTURE COURSE COVERS BASICS OF PROCESS COMPUTERS – General Electric's Process Computer Department, Phoenix, Ariz. has announced the availability of a unique audio-taped course covering the basics of process computers and how they control industrial processes.

Requiring about four hours, the course consists of a taped lecture with a workbook of more than 100 pages which illustrates the material presented on tape. Quizzes are spotted throughout the book to assure the student understands each segment before he continues to the next.

The course describes the basic components common to any computer (EDP or process control), and through a simple analogy, the way they work together to achieve fast, consistent results. The communication devices which enable the computer to "talk" to the process being controlled, and the "languages" it uses in doing so, are also covered, as are the instruments which measure and control process performance.

The course was developed to acquaint plant management, instrumentation and process engineers, operators and others with the fundamentals of process control computers. The price for one complete course, audio tape and workbook pages packaged in an attractive binder, is \$125. SDS OFFERS ON-LINE CIR-CUIT DESIGN-ANALYSIS SOFT-WARE – Scientific Data Systems Time-Sharing Services is now offering an on-line circuit design-analysis package. This programming system, called CIRC, is offered exclusively to users of SDS Time-Sharing Services.

The system is a general-purpose program, conversationally structured to allow man-machine interaction in a computer-aided design process. CIRC allows a circuit designer, working at a remote input/output teletypewriter terminal in his own office, to analyze proposed design approaches while interacting conversationally with the computer, and thus to arrive at an optimum design in a very short time.

The CIRC-AC program handles both passive and active components. A transistor model, stored within the program, implements a sophisticated two-pole modeling technique that includes the often overlooked "excess phase" characteristic of transistors. This program allows tentative ac circuit designs to be evaluated over an automatically scanned frequency range. It also performs open-loop analyses with proper loading being handled automatically.

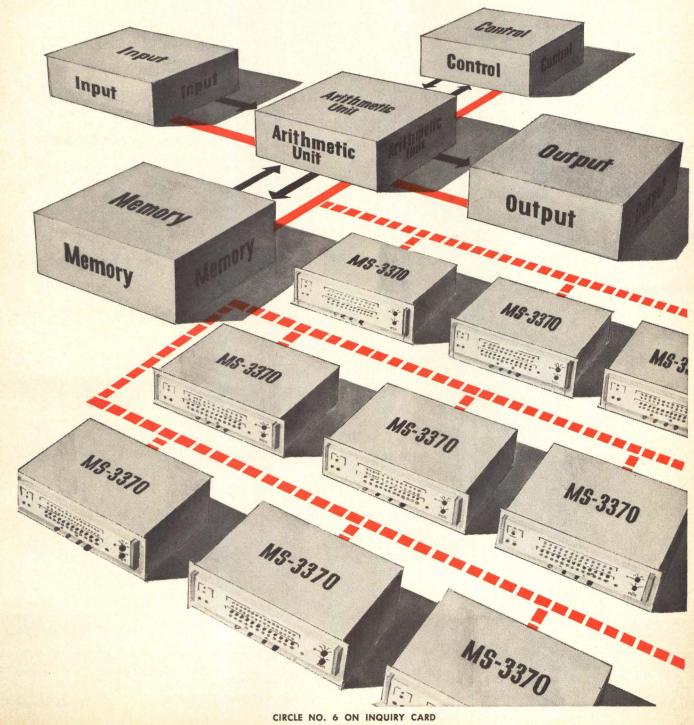

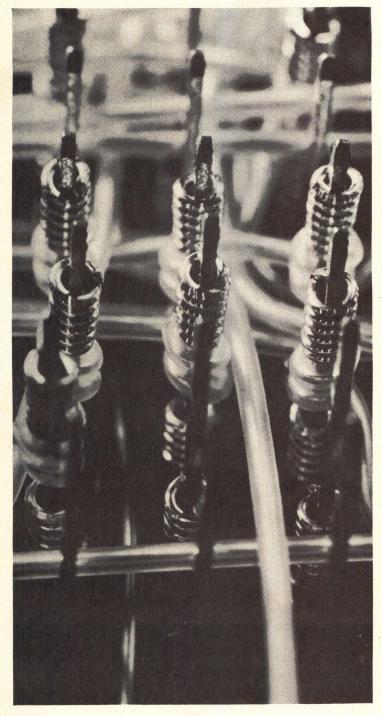

PLATED WIRE PRODUCTION CAPABILITY – Electronic Memories, Inc., Hawthorne, Calif., has developed and is producing plated wire and plated wire arrays in limited quantity. The wire and array capability was developed during the past two years under a company-funded research program headed by Dr. Judea Pearl.

The Core Division has been renamed the Magnetic Materials Division to reflect the company's broadened capability in the memory element field.

Richard J. Dadamo, V.P. and G.M. of the Magnetic Materials Division, pointed out that while EM will produce and market plated wire eventually through the system's level, the company will continue to promote and expand its ferrite core memory activity.

The Memory Components Division, presently producing enough plated wire to meet several customers' needs, expects to be in high volume production of plated wire products by midyear 1969.

The initial plated wire memory plane offered by the company has 64 words of 36 bits and is offered in either bi-polar or uni-polar modes, depending on customer need. The plane's cycle time is 200 nanoseconds, and may be operated over a temperature range of  $-50^{\circ}$  to  $+100^{\circ}$ C. NEW FIRM то MARKET PERIPHERAL EQUIPMENT-Tycore Inc. has recently been formed for the design and manufacture of data tape systems and other peripheral computer equipment. The company has completed design and manufacture of two prototype data tape systems. Designated the Series 7500 for 7 channel tape and the Series 9500 for 9 channel tape, both are keyboardto-tape systems and are aimed at replacing present equipment in the keyboard-to-card punch market.

The company occupies 15,000 square feet in a newly completed building at 80 Turnpike Road, Chelmsford, Mass., and is planning to expand into an adjacent 15,000 square feet as soon as production builds up. The first production data tape systems will be ready for shipment in early spring.

**CALL FOR PAPERS** – The 1969 IEEE Computer Group Conference will be held at the Leamington Hotel, Minneapolis, Minnesota, Tuesday through Thursday, June 17-19, 1969. The purpose of this Conference is to report and explore recent, original developments in "Today's World of Real Time Systems."

Subjects of interest cover the spectrum of real time considerations and include real time systems for process control, message switching, inventory control, time sharing, command and control, biomedical computing. Papers are solicited describing new developments in software, languages, system organization and interface design including peripheral equipment, special purpose systems, system models and analysis, and hardware.

Potential participants are requested to submit for consideration by the Conference Program Committee a 50 word abstract suitable for publication in the Computer Group News and a 1000 word illustrated digest suitable for publication in the Conference Digest. The phone number and complete mailing address of the senior author should be identified for possible later questions and revisions. Four copies of the abstract and digest should be submitted by January 10, 1969. Authors will be notified of the Program Committee's decision by March 1, 1969.

All material should be sent to: Donald L. Epley, Technical Program Chairman, 1969 IEEE Computer Group Conference, Department of Electrical Engineering, University of Iowa, Iowa City, Iowa 52240.

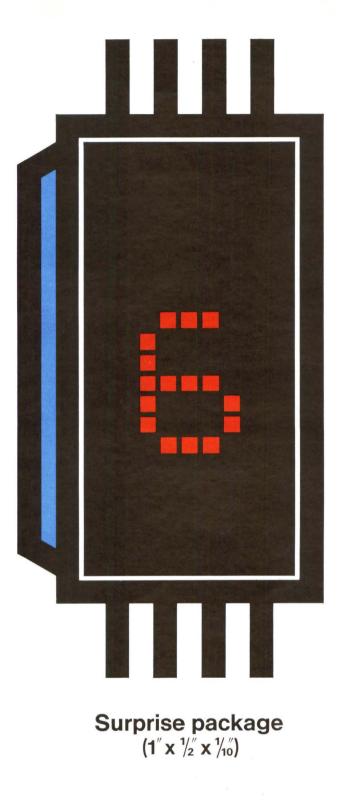

It's a completely new way to display digital information. The Hewlett-Packard solid state numeric display packs everything in one, small unit only 1"x 0.5"x 0.16". Gallium arsenide phosphide diodes and an IC driver/decoder chip deliver bright red numerals—bigger than life, visible for yards.

This new "total package" also gives you the edge on cost. You don't have to buy driver elements, or anything else. No special interfacing is needed. Only four line 8-4-2-1 BCD input and less than five volts to drive it. The modules are available in three-character packages, too.

The Hewlett-Packard solid state numeric display is ideal for instruments requiring smaller, tighter display panels. Or any application demanding either low power or resistance to shock and vibration, without catastrophic failures.

Get more information about the new technology for numeric indicators. Call your local HP field engineer or write Hewlett-Packard, Palo Alto, California 94304; Europe: 1217 Meyrin-Geneva, Switzerland.

CIRCLE NO. 16 ON INQUIRY CARD

01810

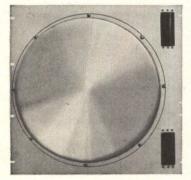

#### Holographic Memory System Exhibits Rapid Access

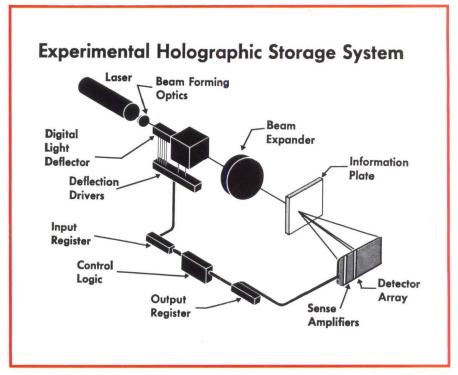

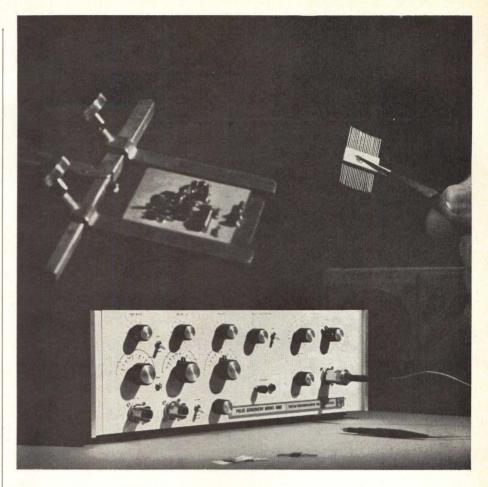

An experimental optical memory system that could lead to storage devices a thousand times faster than today's disk and drum storage units has been reported by IBM's Systems Development Division Laboratory, Poughkeepsie, N.Y. In the experimental system, blocks of information are accessed by a laser beam in 10 microseconds, and it could conceivably allow more than 100 million bits of information to be stored on a nine square inch holographic plate. Such a memory could significantly reduce storage costs, increase capacity and provide more reliable and rapid collection of stored data, according to IBM.

The system is described as a holographic, block-transfer, optically accessed store which uses a method of accurately deflecting a beam of light whose position does not change with variations within the deflecting subsystem. In the experimental memory system, the digital light deflector (DLD) consists of alternating electro-optical material (typically KD\*P) and birefringent material (calcite). By controlling the voltage across the electro-optical material, the polarization state and hence the position of the emergent light beam is controlled. The DLD accurately positions the light beam to any one of the blocks on the hologram. Each block is recorded with diffused illumination techniques using a photographically prepared mask containing the bits. The block size on the hologram is 2 mm and the beam from the deflector is approximately 0.3 mm, therefore, the beam must be expanded by approximately 6X. This expansion is done by pairs of astronomical doublets. The reconstructed image from the hologram is automatically focused on the detector bank. As the beam is deflected from block to block, the corresponding images remain focused on the detectors. The photodetector array is comprised of photodetector diodes, which consist of a PIN photodiode in series with a

blocking diode. Electronic drive circuits, sense amplifiers, and an output register complete the electronics circuitry.

An engineering model was built with several simplified specifications to show the feasibility of the experimental system. The feasibility model used a HeNe 80 mW laser. The deflector output was reduced to four deflectable positions; the beam expanders were eliminated and access to the full information plate diagonal was provided by a set of manually positioned mirrors. The hologram consisted of 3 groups of 4 blocks each with the two end groups separated by approximately 7 inches. Manual mirror positioning provided access to any of the 3 groups, with highspeed electronic access to any of the 4 blocks within a group. The detector array contained 81 detectors arranged in 3 x 3 groups in a square pattern; each group contained 3 x 3 or 9 active detectors. The sensitive area of each element was approximately 0.010" diameter, with centers at 0.032". Nine detector chips were bonded to a module, which was then pinned into a mother board. This board also contained the sense amplifiers.

The exposure of the hologram blocks was made using diffuse techniques. A coded mask with a  $3 \times 3$ pattern corresponding to the detector array was used; however, the size encompassed the full bit array. A memory exerciser was fabricated to drive the DLD, and to provide timing points for the readout of the detector array and a set of latch circuits was used to ensure error checking of the information.

The experimental optical memory system developed by IBM's Systems Development Division Laboratory, Poughkeepsie, N.Y., will access information recorded on a holographic plate one thousand times faster than conventional auxiliary storage devices such as disk and drum memories.

Dale Mrazek National Semiconductor

**MOS BRIEF 4**

#### MOS DELAY LINES

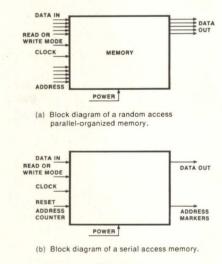

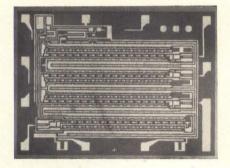

Integrated delay lines let digital system designers escape one of nature's small tyrannies—finding a match between system timing and the prefixed delay set by a glass or wire line's length, or a drum's rpm. In contrast, the input-output rates and storage time of an MOS shift register can be controlled individually to mate with any part of the system, be it instrumentation, data link, or computer.

The simplest, smallest, and least power-hungry delay lines are those made with MOS dynamic shift registers. Each silicon chip contains up to 200 storage nodes and the digital equivalents of input transducers and output detectors. All the designer supplies is a few microwatts of power per bit, clock signals, and data. Data can be shifted through the register at rates from near DC to greater than 15 MHz.

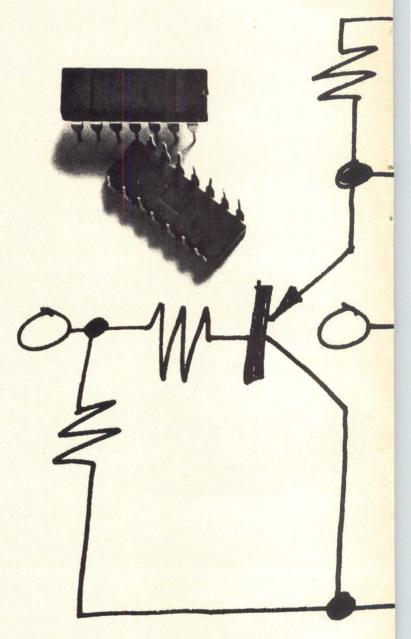

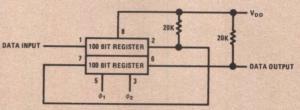

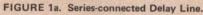

Lines that store only a few hundreds or thousands of bits are less expensive to build with MOS. The line in Figure 1a is just the series-connected halves of an MM506 dual 100-bit dynamic register and a few pull-down resistors. A dynamic register is run with a two phase clock, static registers require a single clock. At 700 KHz or less the clock driver (Figure 1b) can drive three or more MM506's or more than a dozen dual 16-bit static registers.

Delay duration is the product of the clock period and the number of bit-storage nodes in the registers. At 1 MHz, for instance, 200 bits would be delayed 200 microseconds. The longest delay possible in a dynamic register is determined by the minimum operating frequency, which ranges from about 10 to 25 Hz at 25°C to 10 KHz at 125°C. If the designer wants a shift rate in the megahertz

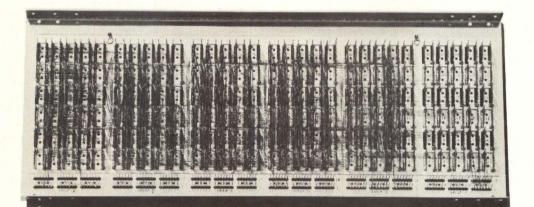

FIGURE 3. Synchronous Delay-line Array Operates as a 60,000-bit Drum Memory.

range, but wants to delay the data much longer than microseconds, he can inhibit the clock between loading and unloading of the register, or recirculate the bits at low frequency within the register while reading in and out at high speed. To overcome a data synchronization problem, data can be shifted in at one rate and out at another.

Dynamic registers would lose data if the clock is stopped indefinitely, since they don't contain latching devices. Static registers do have latches, and can therefore operate at DC dlock rates at any temperature. Their clocks can be stopped, allowing indefinite delays. The price of latching and other special features of static registers is less bit capacity per chip than dynamic registers.

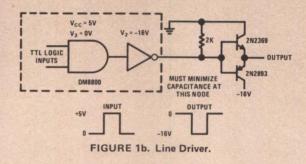

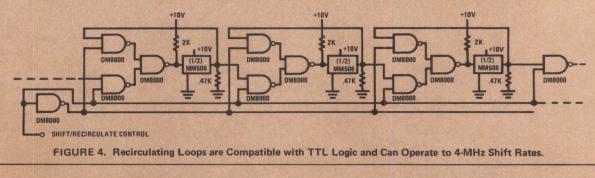

Clock rates much higher than the normal MOS speed limit of 1 to 5 MHz can be achieved by operating registers in parallel or interfacing them with TTL logic. Both methods are combined in the Figure 2 delay line, which has been clocked at 16 MHz. The high-speed clock and data inputs are distributed among the registers so that the upper MM506 transfers and delays bits numbers 1, 5, 9, 13, etc., of the data. The next two MM506 halves handle bits 2, 6, 10, 14, etc. The bits flow through the registers at a 4 MHz rate. When the four bit streams are reassembled in the DM8020 NAND gate, the data rate of 16 MHz is restored.

In an all-MOS system, an MM506 register could be clocked at 1 or 2 MHz. The limit is largely imposed by RC time constants raised by the high impedances of adjoining MOS elements. The register runs at 4 MHz in the Figure 2 configuration because TTL gates are fore and aft of each MM506 half. Thus, each register is driven at its input by a low-impedance source and each output terminates in a low impedance, low level sensor, making the outputs more easily detected. The TTL-MOS interfaces are simply pullup resistors at the register inputs and pull-down resistors at the outputs.

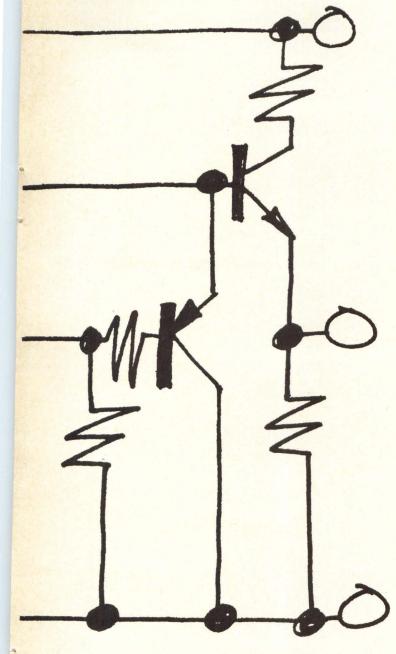

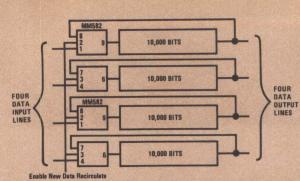

Parallel series of registers also make a fine "drum" memory—that is, a rectangular array of synchronous delay lines (Figure 3). When less than about 200,000 bits of storage are needed, MOS drums are less costly than electromechanical drums. An MOS multiplexer (MM582) does the gating required to write a word into a register, recirculate it and access it upon command. With counter addressing, the contents of a specific register in a series can be read out without disturbing the contents of other registers.

If the data stored in a line is recirculated within several minor loops in each line, the access time will be reduced proportionately. The recirculating loops in Figure 4 were designed to allow the continual shuttling of data from TTL logic into the MOS delay loops, and back out into TTL logic. The loop lengths should be kept to multiples of one another—say 100 or 50 bits—to avoid clocking complications. Here, too, the few additional TTL gates and resistors allow the registers to be clocked at up to 4 MHz.

Since each register in a delay line can operate independently, almost any combination of the basic operating modes in different segments of a line can be used. For instance, assemble a delay line with variable taps, build buffer memories with selectable delays to faciltate time-shared processing of data from several sources, or match low-speed sensor data to relatively high-speed logic circuits. Numerous specialized design-options are also available, such as clock formats that permit asynchronous operation of registers in a line or keep power dissipation well below the normal levels.

Write for data sheets on MOS and TTL devices used in delay lines.

#### **National Semiconductor Corporation**

2975 San Ysidro Way, Santa Clara, California 95051 (408) 245–4320/TWX (910) 339–9240

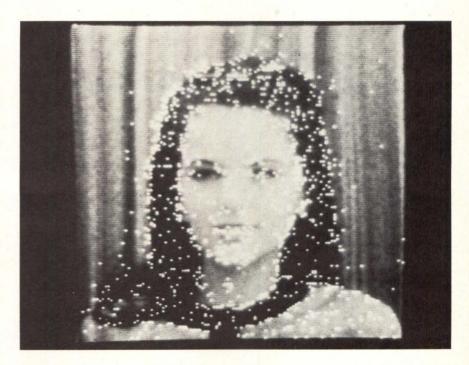

#### Video Editing Boosts Picturephone Service

An experimental method of "editing" video signals before transmitting them holds promise of allowing three PICTUREPHONE® calls to be made over some facilities that might otherwise carry only one.

The method, devised by F. W. Mounts of Bell Telephone Laboratories, Murray Hill, N.J., involves transmitting only significant differences that occur from picture-topicture in a video signal.

In Picturephone communications, in any short period of time, only a small portion of the picture changes-for example, an eyelash flutters, or lips move-but the rest of the picture remains the same. Picturephone service, which the Bell System is developing for commercial use in the 1970's, transmits all information about the picture 30 times each second. Since there is little change in a picture in one-thirtieth of a second-the position of a person's head generally remains the same-the present technique transmits much repeated information. This type of repetition is called "frame-to-frame" redundancy.

The new method removes most of this redundancy, and it does so without reducing picture clarity it is called "conditional replenishment."

In the conditional replenishment technique, digital frame-toframe processing is used to continuously store a reference picture and update or replenish only elements that change between frames. Then, only the picture information needed to update the reference picture is transmitted. Received picture information is used to update a similar stored reference picture, which tracks the one at the transmitter.

The new technique does this by expressing video signals as 8-bit

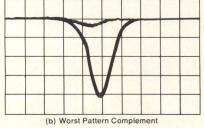

White dots in this actual video-telephone picture show areas of significant change during face-to-face communications in one-sixtieth of a second. An experimental technique (called conditional replenishment) developed by Bell Telephone Labs transmits only these changes to update the previous picture.

numbers, and position of the signals as 7-bit numbers. In order for the receiver to update the picture elements correctly, both these pieces of information must be conveyed to the receiver.

The frame memory consists of delay lines and stores one complete frame of video information encoded as 8-bit pulse code modulation (PMC). A subtractor circuit compares the new information from the camera with the reference picture stored in the frame memory and determines the difference between the stored and new picture.

Each sample period, control logic decides whether a significant difference exists between the signal values. A selector switch strobes the new signal value into the frame memory to update the reference picture if a significant change occurs; otherwise, the signal value stored in the memory is maintained. Each time a reference picture is updated, a buffer stores the value and position of the information needed to update, and it is then read out onto the transmission line at a constant rate on a first-in, first-out basis.

Although the principle of conditional replenishment is applicable to commercial television, it is limited by the amount of motion occuring from frame to frame. Thus, for commercial television, in which movement is usually constant, the technique is impractical.

## commentary

Comments and opinions on topics of current interest to digital design engineering personnel. A monthly column organized and prepared under the direction of **T. PAUL BOTHWELL, Contributing Editor.**

## **Interpretive Simulation**

RONALD D. MALCOLM

Interpretive simulation is a particularly desirable method for digital computer simulation. Its advantages are: short implementation time, low memory consumption and ease in handling changes in the original task program.

In the interpretive simulator, the operation performed by each instruction or command of the original computer is emulated by a programmed subroutine. A set of subroutines is written, one for each instruction in the original computer. An interpreter routine, in the simulator, examines each instruction of the task program and selects the corresponding simulator subroutine for execution.

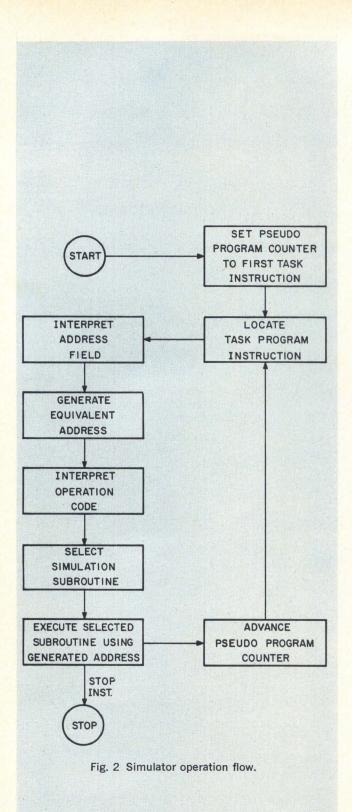

The program (sequence) counter of the simulator does not move through the task program itself. It moves from the interpreter routine to a simulation subroutine and back to the interpreter routine. A register or memory cell, used as a pseudo program counter, is updated by the interpreter and simulation routines to keep track of the current position in the task program. The original task program is thus executed a step at a time with each instruction performed in the same sequence and fashion as by the original computer.

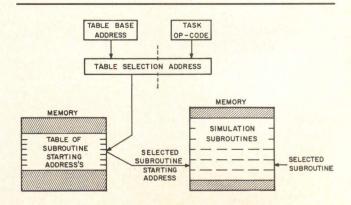

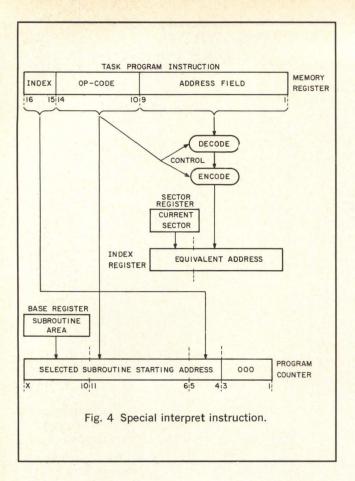

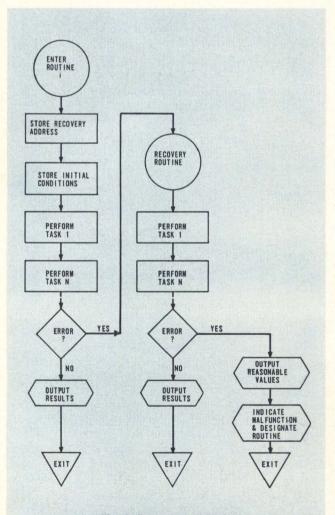

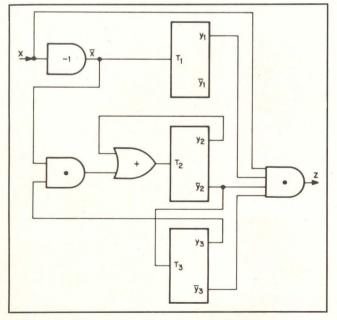

Ronald D. Malcolm, the author of this month's CD Commentary, is a Senior Systems Engineer at Honeywell's Computer Control Division. His responsibilities include design of digital computer base systems, custom computer options, and special purpose digital systems. The interpreter routine generally uses the task program operation codes to cause reference to a table of simulation subroutine starting addresses, with each code causing entry into a different place in the table. The interpretation is accomplished by adding the operation code to the address table base address to select the appropriate subroutine starting address, and then setting the program counter to this starting address. This operation is similar to "indexed indirect addressing." (Fig. 1).

The address fields of task program instructions are also interpreted and equivalent simulator addresses generated. Memory reference instructions reference equivalent memory locations in the simulator; register reference instructions are caused to reference an area of the simulator memory used to simulate the hardware registers of the original computer. Indexing

Fig. 1 Operation code interpretation.

DATA COMMUNICATIONS

equipment for on-line, real-time processing

### data arrives by jet at 1200 WPM

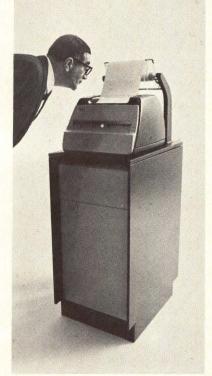

Teletype announces a new arrival: a high speed electronic terminal that takes data off the line as fast as it comes in. Teletype's new Inktronic® printer ("The Jet Set") prints without pausing for "fill" characters.

In modern data processing and communications, where economy is measured in milliseconds, a machine that can convert data into hard copy at transmission line speeds without lagging is a truly practical terminal—especially for time sharing operations, or high volume computer output.

Add the advantages of low cost and rugged endurance, and you begin to get an idea why we're proud of our new Inktronic RO (receive-only) printer: first terminal in a complete new 1200 wpm line which will include KSR (keyboard send-receive) and ASR (automatic send-receive) sets, with future plans for even higher speeds to completely utilize voice grade channels.

#### THE PRINTER WITH NO CHAI CHAI CHAI

The Inktronic printer is as different from ordinary machines as jets from props. The electrostatically deflected ink jet printing is continuous (character by character) instead of periodic (line by line). There is no cha-cha-cha printing rhythm. And there is no rhythmic printing noise —just a barely audible undertone accompanied by miles of incredibly unwinding copy.

#### A copy continuum!

NO BUFFER STORAGE We didn't cut out the printing

rhythm to keep the data from dancing. As a matter of fact, the Inktronic printer will make data dance all over the page, producing print wherever wanted. Its printing format is unrestricted.

What it doesn't do is store up full lines of characters, including blank fillers, for periodic print-out from buffer storage. The Inktronic printer simply takes the characters as they come off the circuit, and fires instant print through forty electronically controlled jets. It doesn't waste time storing imaginary characters to "fill" empty spaces after partial lines. By eliminating buffer storage, Teletype R&D engineers have achieved a higher effective speed. They have reduced the time and cost of data print-out. And they have produced a practical data terminal with few moving parts. Actually, only one part moves in the entire ink guidance system. So the "Jet Set" should not need much of the usual maintenance care.

Here, in fact, is an electronic printer that will maintain a 1200 wpm pace month after month without faltering. It's meant for heavy duty use in a variety of ways, including use as an on-line computer terminal; or as a monitor for high speed tape-totape systems.

FAST AND ECONOMICAL

The Inktronic printer's speed is combined with convenience and economy features that make it an ideal on-line terminal.

It will print up to 64 alphanumerics for which its transformer core memory is programmed.

It is available with either the 5-level code or U.S.A. Standard Code for Information Interchange (ASCII).

It uses inexpensive ink, and gives you more than 15 miles of fully printed lines to the pint—on regular, inexpensive, 8½ inch wide teletypewriter paper.

Incidentally, the ink is easier to insert then a typing ribbon. And cleaner.

Why not get all the available facts on how you can have data arrive faster by jet? Contact Teletype Corporation (71M), 5555 Touhy Avenue, Skokie, Illinois 60076.

machines that make data move

and indirect addressing is also simulated by the interpreter routine.

The results of simulated arithmetic computations must be identical to those of the original computer to allow for the modifying of task instructions (i.e., changing address fields of table referencing instructions) by the task program itself (Fig. 2).

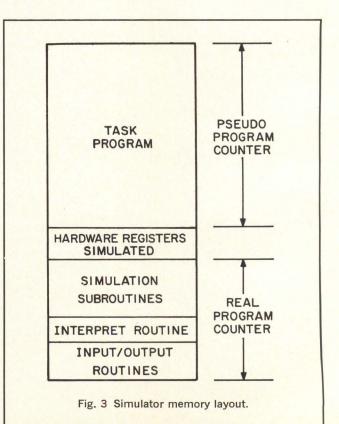

Fig. 3 is the layout of a typical simulator memory. The hardware registers of the original computer are simulated in memory locations in the simulator, allowing register access and manipulation when specified by task program instructions. The simulator's peripheral devices may require special routines to correct data formats or simulate block transfers, direct memory channels, etc.; the simulator's interrupt facility may require routines to handle it.

#### **Real-Time Simulation More Difficult**

It can be seen that the specification for an interpretive simulator is essentially equivalent to the functional specification of the original computer. This makes the production of the simulator a clearly defined task. Creating a non-real-time simulator by the interpretive method, using a general-purpose computer, poses no particularly difficult problems. Realtime simulation, on the other hand, requires very careful consideration, and certain relationships between the original and simulator computers must exist to allow practical real-time operation.

The real-time simulator must generally be faster than the original, or more powerful, or both. The probability of success is improved if the arithmetic conventions are the same, if the simulator word

### DATA COMMUNICATIONS

equipment for on-line, real-time processing

### fully datamated teleterminals!

Teletype's data oriented Model 33 equipment will handle all kinds of intelligence in a number of very intelligent ways.

Here is a practical answer for the systems designer who needs extraversatile data terminals. Teletype's Model 33 line of economical communications equipment may be mated to just about any application within a 100 words-per-minute system.

It can be used with equal facility on-line or off-line. To produce hard copy or punched paper tape. For real time and time sharing applications. For problem solving or data distribution. In BIS (business information systems) or CAI (computer assisted instruction). To handle variable, fixed or mixed data—in print or tape, or both.

#### ASR WITH PBDG

For example, the Model 33 ASR (automatic send-receive) set with PBDG (Push Button Data Generator) reduces the time consuming business of typing small amounts of fixed data to the simple act of pressing a button. A button that never makes stenographic errors!

Preparing computer input tapes off-line with this ASR set is a breeze. The various fixed data are entered by pushing appropriate PBDG buttons among a set of twelve. Variable data is typed in from the keyboard. The completed, punched tape is then put into the ASR's reader, and the computer is called. The intricate computer instructions, already programmed into the PBDG, are transmitted by simply pressing a single button.

Smooth, steady, timesaving, 100 wpm tape transmission begins immediately. Both line and computer time are saved.

machines that make data move

PBDG sets are available with as many as 96 pushbuttons, for reproducing fixed data in groups of 24 characters per button. They can be used with all other Teletype teletypewriter terminals, as well!

USERS LIKE MODEL 33

The dependability and low cost of Teletype Model 33 ASR (automatic send-receive), KSR (keyboard send-receive) and RO (receive only) sets have commended them to many users and developed many uses. Computer manufacturers use them as input/output terminals. Banks use them to contact investment firms for securities information. Model 33 employs the U.S.A. Standard Code for Information Interchange (ASCII), and can communicate with most computers

CIRCLE NO. 19 ON INQUIRY CARD

and other business machines. Manufacturers use them to transmit multicopy forms.

Computer assisted instruction in schools has developed more recent uses. In Chicago, a well-known university conducts a computer service involving problem solving for more than 1,000 students at 16 city and suburban high schools and junior colleges equipped with Teletype Model 33 terminals.

#### OPTIONS ABOUND

In addition to value and versatility, Model 33 sets offer a full array of special purpose options.

Automatic Answer-Back. Reader Control and Punch Control equip the Model 33 ASR set to automatically answer calls and transmit data (typed or taped or both) to distant stations. No attendant is necessary. A sprocket feed platen helps Model 33 to accurately handle multiplecopy business forms from 21/2 to 11 inches in length. Copies may be transmitted to any number of stations simultaneously, saving hours of typing.

Automatic form feed is a convenience feature that saves time in preparing business forms. It lets the operator advance new forms into typing position by striking a key.

Details on these and many other Model 33 product features are available from Teletype. If you are looking for terminals that will adapt to unique systems, contact Teletype Corporation, Dept. 71M, 5555 Touhy Avenue, Skokie, Illinois 60076.

length is equal to or greater than that of the original, if the addressing capabilities are similar, and if the input/output structures are similar.

The overhead (time) required for operation code and address field interpretation is the major stumbling block for interpretive simulation in real time. A number of general-purpose computers have "simulate" or "interpret" instructions to help reduce this overhead. An interpret instruction, tailored to a particular interpretation application, can be very effective in reducing the overhead. Special arithmetic and register manipulation instructions tailored to the application may also help increase simulation speed.

The special interpret instruction can be made to interpret both the task operation codes and address fields. The instruction automatically sets the program counter to the first instruction of the desired subroutine, and loads a hardware register (e.g., Index Register) with the generated equivalent address. The operation of such an instruction for an example simulation of a 16-bit computer with a six-bit operation code, nine-bit address field, and two-bit index specifier is shown in Fig. 4. The three low order zero bits in the program counter allow each simulation subroutine eight memory cells (enough for most operation simulations). The few instructions requiring larger subroutines have the remainder of their subroutines located outside of the primary subroutine area.

The special interpret instruction can make an interpret program routine unnecessary altogether by including an automatic increment of the pseudo program counter (index register) each time the interpret instruction is executed.

The simulation commences by loading an index register with the task program start location on the original computer. An interpret instruction is executed using the index register, and an augmenting address field generating a resultant memory address equal to the task program starting location in the simulator memory. This instruction will interpret the first task program instruction and cause the associated simulation subroutine to be executed. The last instruction of each sub-routine is an interpret instruction identical with the one described above. The program counter of the simulator thus moves from one subroutine to another, as controlled by task instruction codes, and the index register (used by the interpret instruction) becomes the task program pseudo program counter.

This type of special interpretive instruction, coupled with tailor-made arithmetic and register manipulate instructions, forms a very efficient simulator at reasonable cost. Even with this capability, the simulator must be inherently faster than the original computer to achieve real-time simulation. Fortunately, most special purpose air-borne or space-borne computers are designed to be relatively slow in order to achieve the high reliability required.

Other methods of simulation may be used in severe real-time applications. The simulator's tasks may be reprogrammed in the language of the simulator computer, or a task program translator used. Reprogramming results in the most efficient simulation, but has the disadvantages of high cost, long implementation time, and difficulty in keeping pace with changes in the original task programs. Program translation, although somewhat faster than interpretive simulation, produces a substantially dilated equivalent task program, consuming a great deal of memory. A translator is very difficult to produce, and may not be practical, in the event the original task program modifies its own instructions (as in moving pointer address fields and updating counting instruction address fields).

#### Conclusion

Interpretive simulation methods have been used successfully to simulate flight computers for astronaut training, for developing software for computers simultaneously with hardware development, in implementing conversational languages on time-shared computer systems, and for conserving memory space in space-borne computers. Micro-programming (simulation of a non-existent computer) is used in some of the latest computers to allow a computer with a relatively simple basic instruction repertoire to perform more complex programmed instructions by executing subroutines stored in a fast read-only memory. Indications are that future computers will use more of this mode of operation to conserve expensive read/write memory, as the speed and cost of logic circuits and read-only control memories continue to improve.

### DATA COMMUNICATIONS

equipment for on-line, real-time processing

### sorry, no hieroglyphics, but...

$(a + b)^2 = a^2 + 2ab + b^2$

0.+2H\_0+4e=40H

It's the Model 37—a new heavy-duty line of completely data oriented terminals that have incredible communications capabilities

Teletype's new data terminal is one that will have to be seen to be appreciated. Will handle algebraic equations, chemical and engineering formulae, charts, graphs—from the most complex to "everyday" data at speeds up to 15 characters per second.

#### FEATURES GALORE

The Model 37 will recognize and react to every code combination in the U.S.A. Standard Code for Information Interchange (ASCII), Print all code graphics, generate all control functionstype in upper and lower case, and even will be able to print in two colors if desired. The computer input/output capability of this machine is complete.

#### TRAVELING TABS

Model 37's transmission capability is unique. Now, for the first time, it will be possible for an operator to set tabs from the keyboard while the set is either on-line or off. Tabs will be able to be set on-line by a computer—or any remote terminal that uses the ASCII code. There is a tab stop for every *horizontal* and *vertical* space on the page. You can accommodate end-

machines that make data move

less tabular variations in copy format. An extremely important feature for those who have a variety of forms to transmit and receive.

Built into Model 37 equipment will be everything needed for easier computer utilization and data transmission. Forward and reverse halfline feed combined with backspace, horizontal and vertical tabulation capabilities—will make the Model 37

HO

F

CH-

ÇH3

$\dot{c} = 0$

the most flexible terminal Teletype has ever offered.

#### COMPLETE PACKAGE

The Model 37 line consists of RO (receive only) and KSR (keyboard send-receive) sets, and the ASR (automatic send-receive) set shown here plus paper tape punches and tape readers housed in modular units compatible with all Model 37 equipment. You will have a complete data moving system with all the important options you've been looking for.

THE QUICK BROWN FOX the LAZY DOGS BACK The Quick Brown Rox the Lazy Dogs Back

The KSR and ASR sets can be equipped with form feedout controls that enable an operator to advance multicopy forms into the printer by remote control. A real timesaver.

Keyboard sets incorporate many new features for easiest touch typing. An "aggregate motion" typebox prints more smoothly with fewer motions at 150 wpm, enabling the machine to operate at maximum speed six months at a stretch with normal servicing.

#### MORE INFORMATION

Heard enough to want all the facts? Write Teletype Corporation, Department 71M, 5555 Touhy Avenue, Skokie, Illinois 60076.

......

#### PSSST HEY BUDDY! You say you're looking for a good deal on a 24 bit computer for less than 17k. SCC's got it...just tell 'em Max sent you.

With over 70 systems installed, the word is getting around. SCC's 24-bit machines are compatible with the programs you've been using.

For \$16,800 you can own the 660 CPU with 59 instructions including a set of microinstructions. For \$35,500, SCC offers the 670 with 71 instructions that also include a comprehensive set of microinstructions for performing data transfers and logical and arithmetic operations. These fully parallel machines provide either single or multiple as well as simultaneous access to memory.

If you're looking for a computer system, SCC can give you 30-day delivery on a 660 CPU, a 1.75 usec memory with parity, memory adapter, character buffer I/O, 300 cps P.T. reader, 50 cps P.T. punch and Selectric typewriter with 8" platen.

Now that you have the word. . . you'll know where to come.

Whatever Your Computer Application - Be Sure You Talk With SCC Before You Buy

## ----

P.O. Box 34529 • Dallas, Texas 75234 • 214 - 241-2111 • TWX 910-860-5509

Scientific Control Corporation

EASTERN REGION: College Park, Md. Huntsville, Ala.

Parsippany, N. J. West Springfield, Mass.

CENTRAL REGION: Dallas, Tex. W Denver, Col. Des Plaines, III. Hazelwood, Mo. Houston, Tex.

WESTERN REGION: Palo Alto, Calif. El Monte, Calif. Total computing system integrity may be evaluated by exercising all instructions, performing sample problems, and comparing with precomputed results. Memory access integrity may be evaluated by the means discussed in this article.

## ON-LINE MEMORY INTEGRITY EVALUATION AND IMPROVEMENT

#### Frank Bujnoski

Honeywell Inc. Aerospace Div. St. Petersburg, Fla.

A processor consisting of a finite number of bistable elements may be considered a discrete-state device. At any time when all the bistable elements of such a device are in a stable state, the state of the system may be represented by an "n" dimensional vector (where "n" is the number of bistable elements). The state of such a device typically changes with time in coincidence with a quantized clock. Since "n" may be as high as several hundred, the number of unique states which the device may assume is astronomical. At any quantized clock time when one of the "n" elements is in error, an erroneous state exists.

State of the art Von-Neuman (stored-program) organized machines are organized so that the various discrete states of the machine are sequentially specified by instructions and data words stored in memory. The erroneous discrete states which may occur in stored computational or control program sequences can be catastrophic to the program; for example, an add command may be misinterpreted due to improper memory operation, producing a grossly erroneous state such as an unconditional transfer out of a program routine, thereby effecting loss of program control. Similarly, an add command may be misinterpreted due to improper memory operation as a multiply, an operand address may be misread effecting access to a wrong memory location, or a data word may have a misread bit in one of the more significant bit positions, thus providing grossly erroneous data.

It must also be noted that equally catastrophic results may be effected by improper operation of the control section of the processor; for example, a malfunctioning command decoder may similarly effect misinterpretation of an add command as a multiply or an unconditional transfer, or the memory address register or decoder may improperly command access to an erroneous data address similarly providing grossly erroneous data.

Thus, although control section errors may be just as catastrophic as memory errors, experience indicates that memory is generally the weakest link in the computer system in terms of reliability. Hence, some error detection for memory, such as parity circuitry (which detects one or an odd number of bit errors), or programmed error detection is usually justifiable.

The main consideration when considering the inclusion of some sort of memory error detection is a tradeoff evaluation of the required time and/or space redundancy versus the measure of memory integrity improvement achieved.

#### MEMORY ORGANIZATION

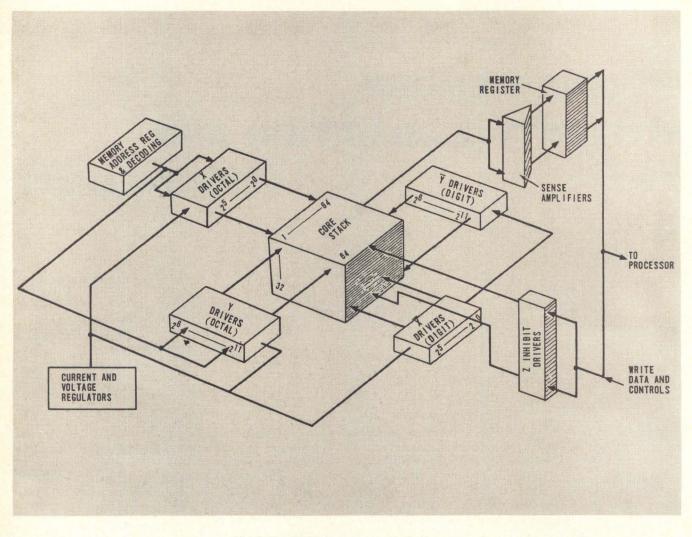

The ferrite toroidal core memory operated in a coincident-current threshold select mode has become the current standard memory system among both military and commercial computer suppliers.

Classically, in the toroidal core memory, the cores are physically arranged as points in a three dimensional coordinate system. The X and Y coordinates together specify a word address. The Z coordinate specifies which bit of the word the core represents.

Fig. 1 Toroidal core memory block diagram.

Thus, conventional memories are designed to be extremely symmetrical to conserve electronic components by functional sharing of circuitry. A typical memory organization is shown in Fig. 1.

The number of word drivers for a 4,096 word memory is  $4(N)^{1/4}$ ; in other words, for N = 4,096, 8 octal and 8 digit drivers for both the X and Y addresses will total 32 drivers. Add to this (typically) two diodes for each X and Y coordinate location, which totals 256 diodes, plus one Z inhibit driver and one sense amplifier for each bit of the word; all of which comprise the total electronics complement for a 4,096 word memory module.

A wide variety of less popular memory types with relatively slight organizational differences are also available. These include planar and wire-deposited film, multi-aperture ferrites, solid state semiconductor chip memories, and various "permanent" or read only devices.

#### HARDWARE PARITY BIT MEMORY CHECKING

The inclusion of a memory parity bit in typical memory organizations requires the addition of a redundant bit per word (or per each n bit byte) plus its associated read, write, inhibit and sense electronics. To this must be added the electronics for checking and generating the parity bit for each memory cycle.

Parity generation and checking is very easily performed in a word serial mode; however, state of the art memories are typically "word parallel", and the time required for parity checking and generation in a serial mode is prohibitive for most applications. Therefore, to preclude prohibitive time delay at present-day memory speeds, parity checking and generation must be performed in a parallel or hybrid serial/parallel mode, resulting in a considerably greater cost in hardware.

Parity bit inclusion penalties are nominally 6 to

15 percent in memory hardware component count and 18 to 20 percent in memory cycle time; for example, a 2 microsecond cycle time memory may become a 2.4 microsecond cycle time memory with 10 percent more components when parity detection is added. Parity bit hardware is essentially space redundancy, though it does require additional time for the parity detection and generation.

#### PROGRAMMED PARITY MEMORY CHECKING

It must be noted that memory integrity may be checked without the specific inclusion of a parity bit. Programmed read and check sum evaluation of critical instructions and constants prior to routine execution will evaluate parity on a bit-by-bit basis for all words checked. This method will detect persistent (fixed) errors, but could miss intermittent (noise type) memory errors. Intermittent errors may then be detected using output parameter reasonableness checks. This approach is "time redundancy" and does not require additional electronics.

#### PROGRAMMED MEMORY ELECTRONICS CHECKING

Memories are designed for a high degree of symmetry and functional circuit time sharing. The word selection process may be considered as a square matrix array organization of N elements (where N is the memory word size); thus, a word is uniquely specified by its row (X address) and column (Y address) locations. Refer to Fig. 1

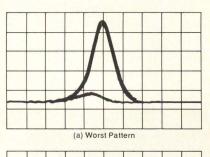

Since memory electronics failure rates are significantly higher than stack failure rates, a measure of memory integrity may easily be determined by checking the memory electronics. For example, reading out eight appropriately selected word addresses (one octal and one digital for both X and Y dimensions) containing selected word formats will evaluate all of the word drivers, many of the diodes, and all sense amplifiers. An automatic rewrite follows each memory read; inhibit drivers (write) are thus checked by rereading the same location. Memory-peculiar worst case word formats are included to detect marginal elements and worst case signal to noise ratios.

Thus, memory electronics can be easily evaluated with relatively few instructions, and gross integrity of the total memory subsystem may be evaluated with less expenditure of time and space redundancy than checking each memory readout cycle.

#### PROGRAMMED "REASONABLENESS" CHECKS

An additional malfunction detection scheme is the performance of "reasonableness" checks wherein computed routine results are compared with results of previous iterations. If results are not within specified limits, a malfunction (of some type) is assumed to have occurred.

#### CORRECTIVE ACTION

More important than detecting the malfunction is what to do when a malfunction occurs. Conventional parity checking and checksum evaluations detect, but cannot correct, an error. Once a memory word is read out in error in conventional Destructive Read Out (DRO) type memories, it is automatically rewritten and will be rewritten in error, resulting in a permanent compromise of stored information.

The only recourse then is:

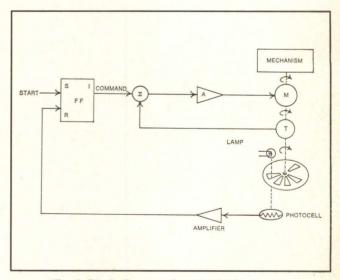

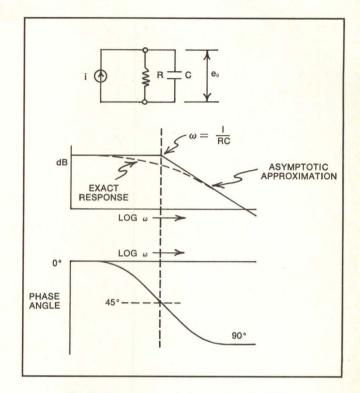

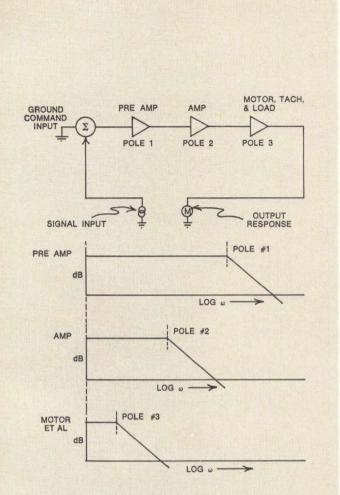

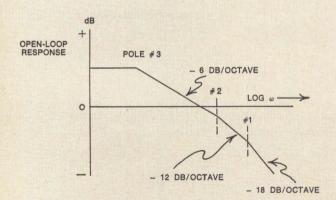

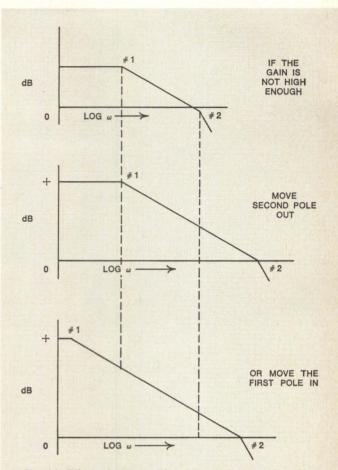

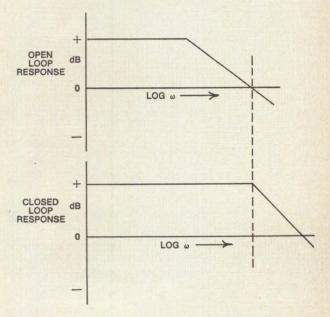

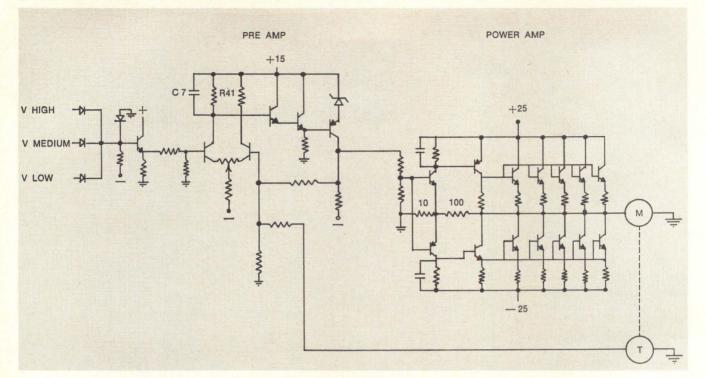

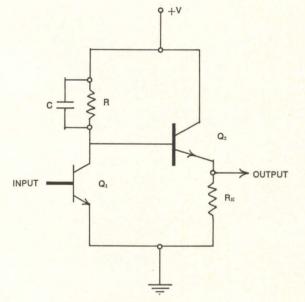

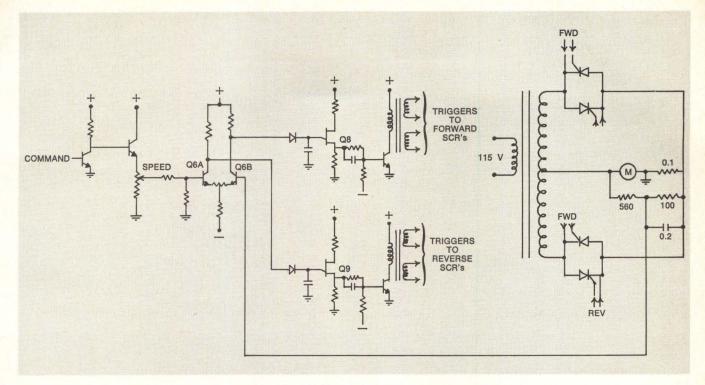

Continue and perform "reasonableness" checks Routine abort Program roll-back Reload the program from bulk memory Program mode check