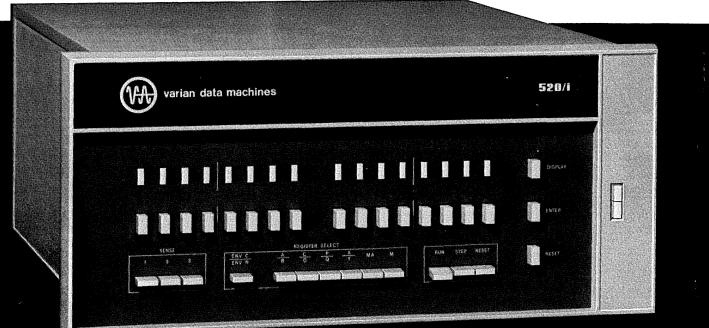

## Varian Data Machines' new 520/i dual environment computer gives you 2 computers in 1

### ....almost.

We've designed our new 520/i computer with enough hardware power to handle dual, independent tasks that would often require two computers. That's why we've called it a dual-environment computer.

With its two complete, independent sets of hardware registers, including index registers, the 520/i efficiently runs parallel programs or efficiently processes background and foreground information.

Since each program uses its own set of registers, a single 1.5 microsecond instruction transfers control from one environment to the other. This dual-programming capability keeps housekeeping to an absolute minimum. And whatever your data format or word length, the 520/i performs arithmetic in 8-, 16-, 24-, or 32-bit lengths within the same program! And each program can change its own precision at any time.

So if you think you have enough work for two computers—see if the 520/i will do the job. The new Varian Data 520/i with a 4K memory sells for \$7500. If you would like to know more about it, write for a Varian 520/i brochure.

### A varian data machines

2722 Michelson Drive • Irvine, California 92664 (714) 833-2400 • TWX (910) 596-1358

SALES OFFICES: U. S., Santa Monica and San Francisco, California; Vernon and Westport, Connecticut; Chicago, Illinois; Houston, Texas; Fort Washington, Pennsylvania; Washington, D. C. INTERNATIONAL: Australia, France, Germany, Sweden, Switzerland, United Kingdom and Ireland.

CIRCLE NO. 1 ON INQUIRY CARD

You may select from over 300 different digital and analog IC circuit cards to build your system. The MONILOGIC line consists of A/D's, D/A's, code converters, amplifiers, counters, oscillators, gates, inverters, expanders, delays, matrix gates, numerous interfaces, registers, flip-flops and reference voltages. Also, there are card file drawers and chassis, power suppliers and associated hardware. Request details.

CIRCLE NO. 2 ON INQUIRY CARD

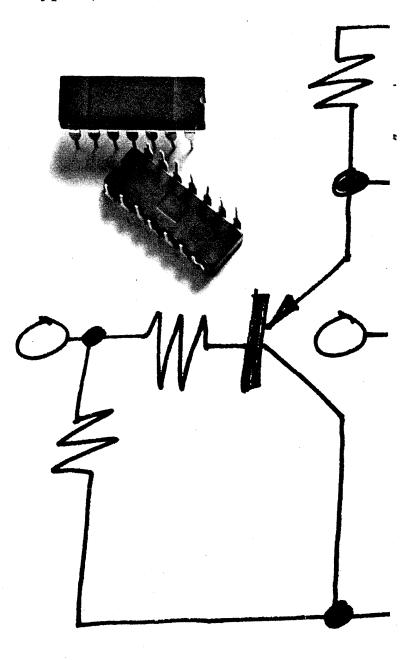

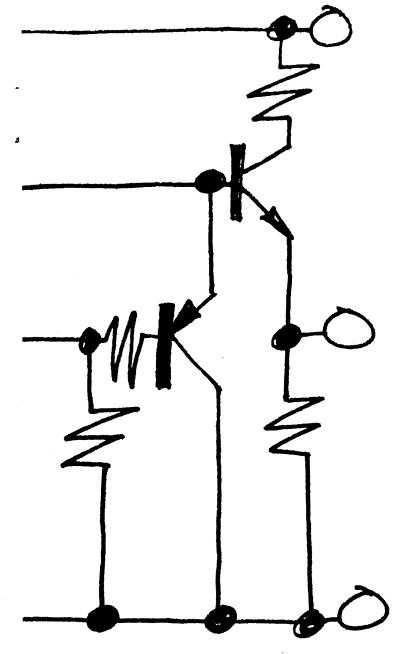

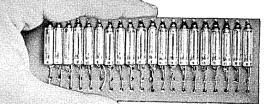

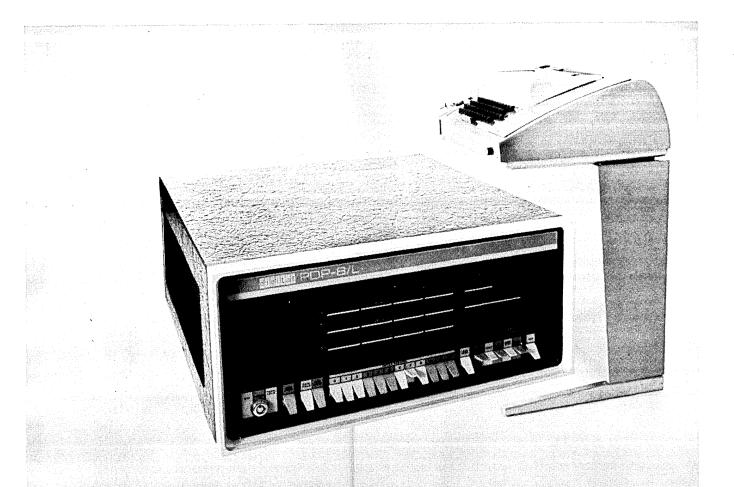

### In 60 minutes you can add 131,072 words to your small computer's memory

Order a VRC 1104S Drum Memory System *now* for your PDP-8, 8/S or 8/I computer. (Yes, the 1104S is compatible with the new 8/I.) When the system arrives in 90 days, follow the simple installation procedures in the accompanying manual. In one hour you will have connected the 1104S to the computer, run the drum diagnostic tape (included with the manual) to test every bit of the 131,072-word capacity, and have the system on-line.

Interfacing the 1104S *is* that easy. And it's available in three versions: PCT for program-controlled transfers; DCT for 3-cycle data break; and DMAT for direct mem-

ory access transfers. You get programs for transfer of single pages or entire fields, and non-destructive drum diagnostic routines. Single-word addressing simplifies programming. And don't overlook the benefits of proven VRC reliability: design life, 100,000 hours of operation; MTBF, 15,000 hours; error rate, 1 in  $10^{13}$  bits.

Cost? Modest. A PCT version—with 131,072-word capacity, 8.7msec average access, and three transfer programs plus diagnostic program—is yours for \$9,950. So place your order today . . . and start dreaming up new uses for a small computer that can think big.

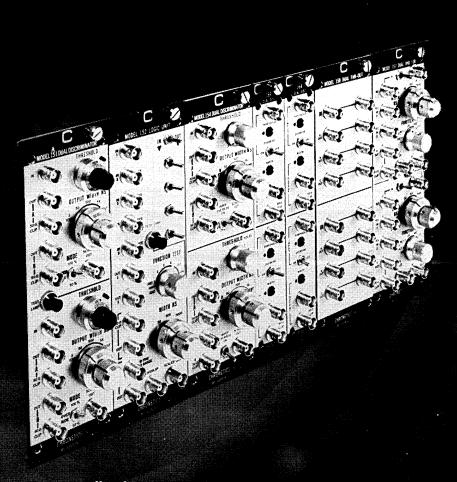

### Computers are known by their MEMORIES

...so is

When it comes to engineering opportunities (and the good life, North Country style), the place to come is Vermont Research Corporation. For specific information contact:

RICHARD A. STOVER Vice President-Engineering

CIRCLE NO. 3 ON INQUIRY CARD

Publisher and Editorial Director **ROBERT BROTHERSTON**

> Associate Publisher ANTHONY SALTALAMACCHIA

> > Editor JOHN A. CAMUSO

Managing Editor JOHN J. COLANTINO

Editorial Consultants BERNARD M. GORDON GERHARD L. HOLLANDER GILBERT P. HYATT

Editorial Advisers **RICHARD AHRONS** ELI ANFENGER JAMES R. BRIGHT WALDRON S. MACDONALD HAROLD H. SEWARD

Contributing Editors T. PAUL BOTHWELL A. S. BUCHMAN ROBERT P. FORAN MADELINE JOHNSON RUDOLPH J. KADLEC RICHARD B. LAWRANCE H. S. MIILLER

> Art Director JAMES FLORA

Production Manager BRYAN De LORENZO

> Editorial Production JUDY KELLEY

**Technical Illustrator** WILLIAM R. SULLIVAN

> **Advertising Production** TERRY ARMENTI

**Circulation Manager** ALMA BROTHERSTON

Vice President-Sales LINDSAY H. CALDWELL

**Editorial & Executive Offices** Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1968 by Computer Design Publishing Corporation. Controlled cir-culation postage paid at Chicago, Illi-nois. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS — FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Win-chester, Mass. 01890. Subscription rate to nonqualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 42,000

### COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS

#### **FEATURES**

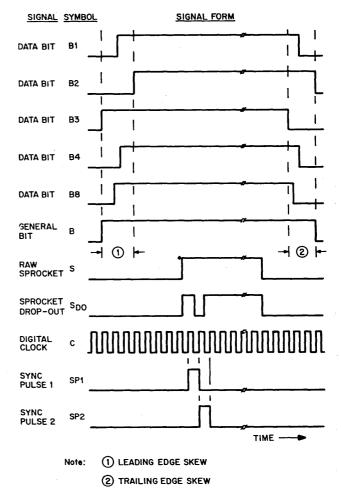

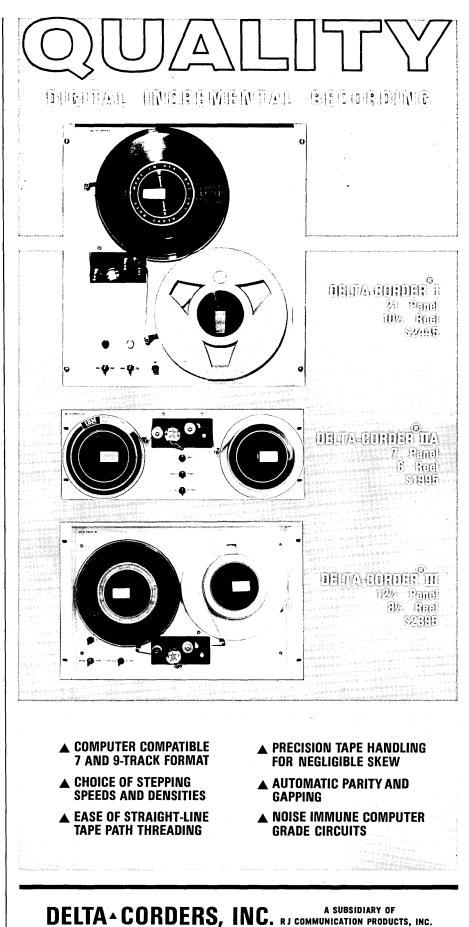

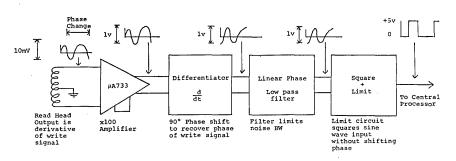

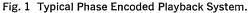

- 44 TECHNIQUES OF DIGITAL RECORDING F. LOESCHNER This tech note examines and compares various techniques of incremental and continuous IBM-compatible recording.

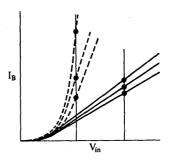

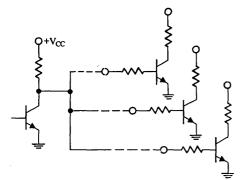

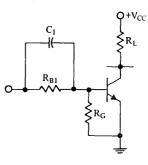

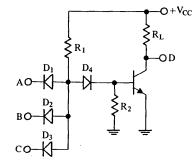

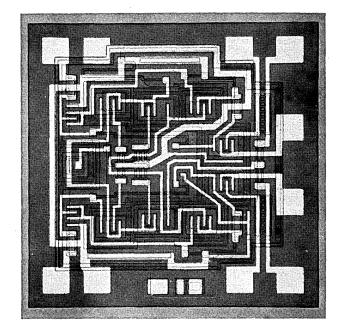

- DIGITAL INTEGRATED CIRCUIT DESIGN TECHNIQUES 52 H. R. CAMENZIND

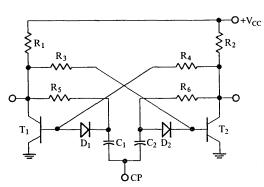

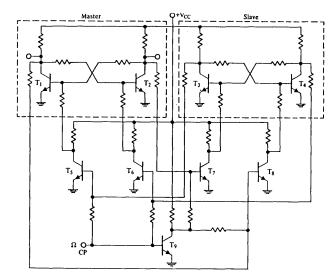

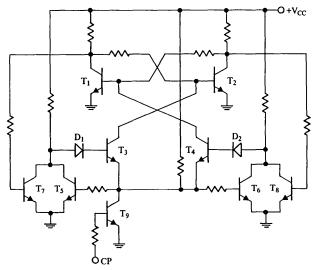

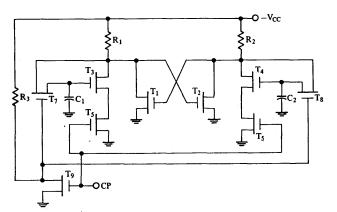

The design techniques discussed in this article will help the designer to more easily understand and use digital IC's.

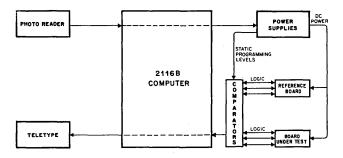

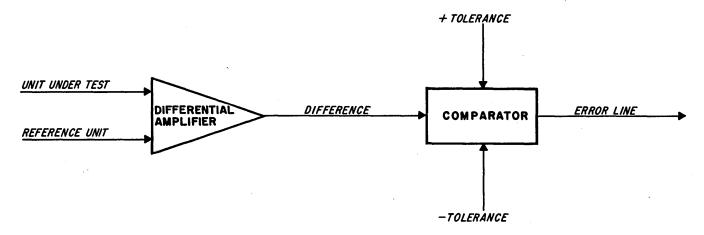

- A DIGITAL LOGIC MODULE COMPARISON TEST SYSTEM 63 J. F. WILLENBORG, S. C. VALLENDER and W. P. CARGILE Test signals are provided in a programmed sequence, results are compared and discrepancies printed as error messages in this test system.

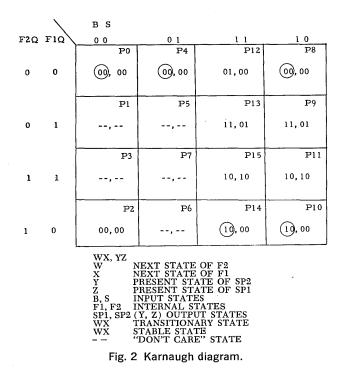

- UNIVERSAL COTROL LOGIC FOR PHOTOELECTRIC 68 PUNCHED TAPE READERS

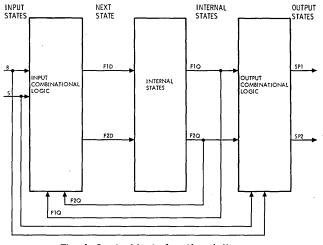

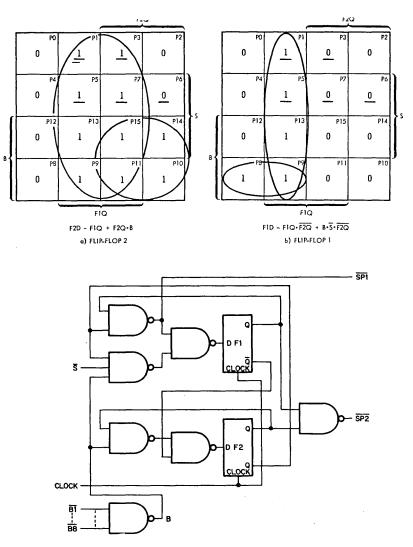

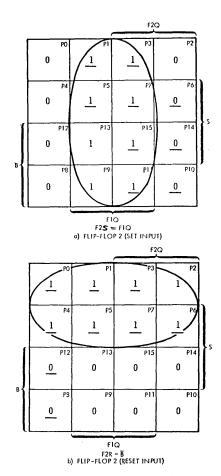

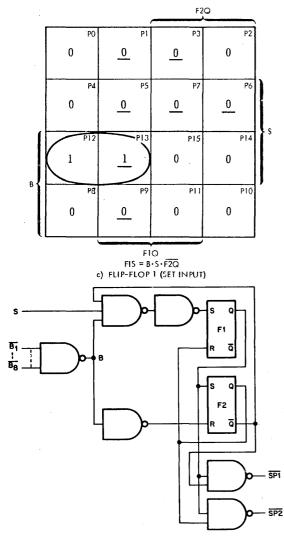

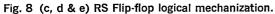

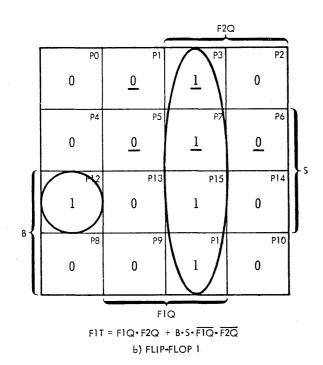

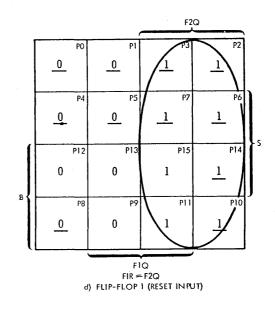

Part II — Sequential Logical Design G. P. HYATT The logical description of the tape reader signals and detailed logical design of universal control logic are presented in this article.

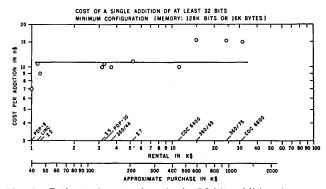

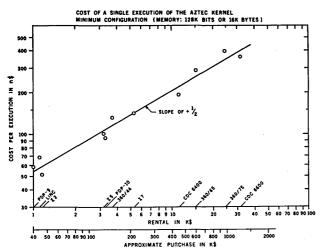

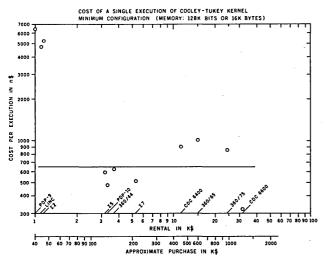

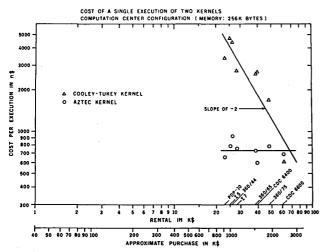

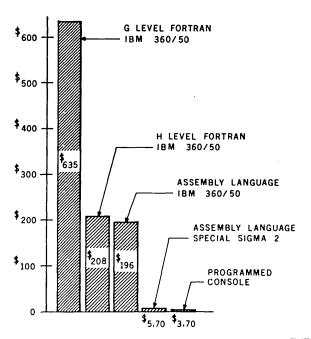

- ECONOMY OF SCALE AND SPECIALIZATION 77 IN LARGE COMPUTING SYSTEMS J. R. COX, JR. There are some economies of scale within the framework of present computation centers. Even more dramatic are the economies of specialization.

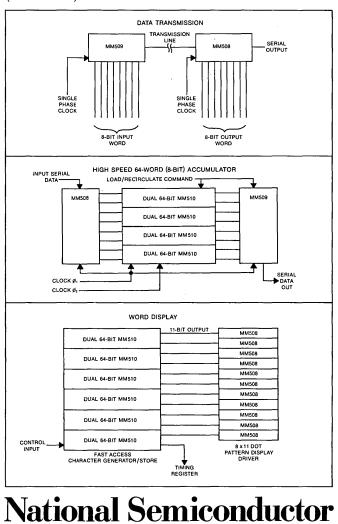

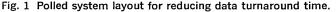

- 82 A METHOD OF DATA TRANSMISSION REQUIRING MINIMUM TURNAROUND TIME P. E. PAYNE An application note describing a modem arrangement for eliminating turnaround time.

- 88 1968 FJCC TECHNICAL PROGRAM EXCERPTS

- 96 1968 FJCC EXHIBITORS AND PRODUCTS

- A MONOLITHIC DIFFERENTIAL VIDEO AMPLIFIER 114

#### DEPARTMENTS

- 20 INDUSTRY NEWS

- 28 CD DEVELOPMENTS

- 34 CD COMMENTARY

- 116 NEW PRODUCTS

- **NEW LITERATURE** 128

- 132 **ADVERTISERS' INDEX**

Reader Subscription Card Reader Service Card \_\_\_\_\_\_opposite page 132

opposite page 1

•3

### If you're building any computer except a Computer, you need $CT\mu L$ .

$CT\mu L$  integrated circuits will give you more speed for less money than any other ICs. They're perfect for process control systems, test instrumentation, central processing units, computer peripheral equipment just about anything short of an airborne computer.

#### Keep it in the family.

You can build a complete digital logic system with Fairchild's family of  $CT\mu L$  devices. We have gates, flip-flops, inverters and memory circuits. A dozen different devices that make a computer easy to package. And, you'll need only about 80 percent as many packages as required with TTL.

#### You get out of it what you put into it.

The key  $CT\mu L$  characteristic is nonsaturating logic. That means you get fast gate propagation delay (typically 3nsec) with slow rise and fall times (typically 6nsec). So, there's no need for transmission lines or complex packaging. You can build an entire computer with normal twosided circuit boards. Also,  $CT\mu L$  can handle signal swings as large as 3V. It also provides typical noise immunity of 500mV.

#### What we'll do for an encore:

MSI  $CT\mu L$  will be out before the year ends.  $CT\mu L$ -II will be out even sooner, offering improvements like gate propagation delay of 1.5nsec. (typical, loaded) and a buffer and

# The world's largest manufacturer

inverter with propagation delays of 5nsec, compared with 12nsec in standard  $CT\mu L$ . And, the new MSI and  $CT\mu L$ -II circuitry will interface beautifully with all these standard  $CT\mu L$  devices:

| Device                        | <b>Price</b> (100-999) |

|-------------------------------|------------------------|

| 9952 Dual NOR Gate            | \$1.25                 |

| 9953 Triple AND Gate          | 1.25                   |

| 9954 Dual Four-input          |                        |

| AND Gate                      | 1.25                   |

| 9955 Eight-input AND Gat      | e 1.25                 |

| 9956 Dual Buffer              | 1.25                   |

| 9957 Dual-rank Flip-flop .    | 2.00                   |

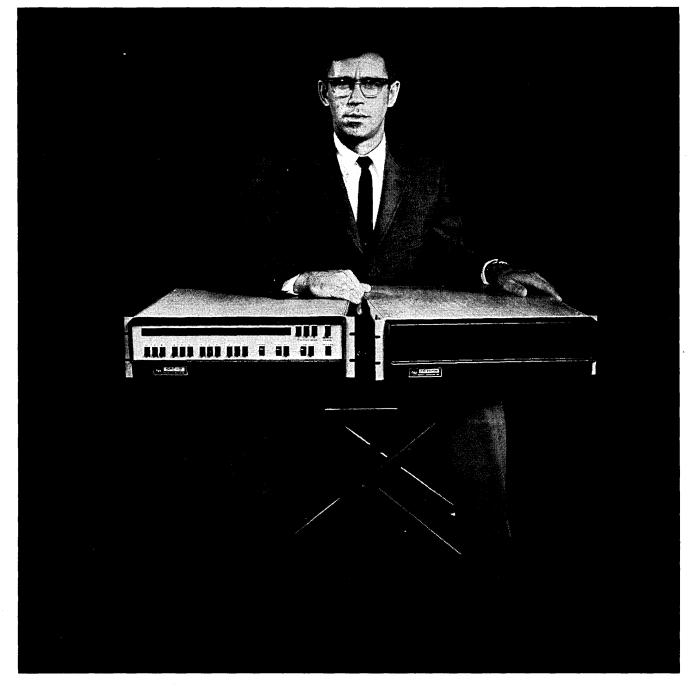

| 9964 Dual Three-input and     |                        |

| $\mathbf{Single}	ext{-input}$ |                        |

| AND Gates                     | 1.25                   |

| 9965 Quad Single-input        |                        |

| AND Gate                      | 1.25                   |

| 9966 Quad Two-input           |                        |

| AND Gates, one pair           |                        |

| with OR-tie                   |                        |

| 9967 JK Flip-flop             | 2.00                   |

| 9968 Dual Latch               | 2.00                   |

| 9971 Quad Two-input           |                        |

| AND Gates with                |                        |

| OR-tied pairs                 | 1.25                   |

| 9972 Quad Two-input           |                        |

| AND Gates, one pair           |                        |

| with OR-tie                   | 1.25                   |

|                               |                        |

If you want  $CT\mu L$ -II in sample quantities, call Fairchild. If you want standard  $CT\mu L$  in production quantities, call a Fairchild distributor. He has everything you need to build any computer. Even a Computer.

AIRCHILD SEMICONDUCTOR

Fairchild Semiconductor / A Division of Fairchild Camera and Instrument Corporation / 313 Fairchild Drive, Mountain View, Calif. 94040 (415) 962-5011 / TWX: 910-379-6435

# of LSI admits there's another way:

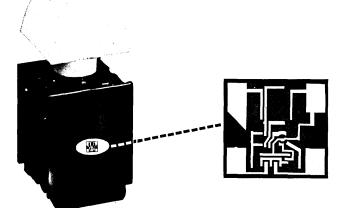

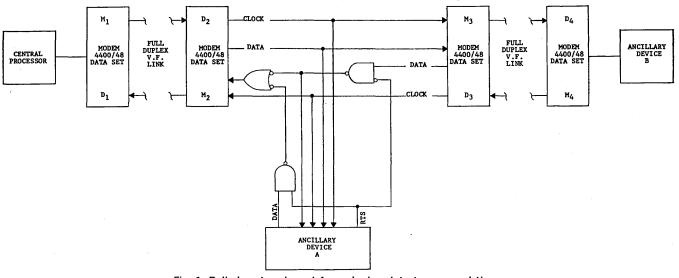

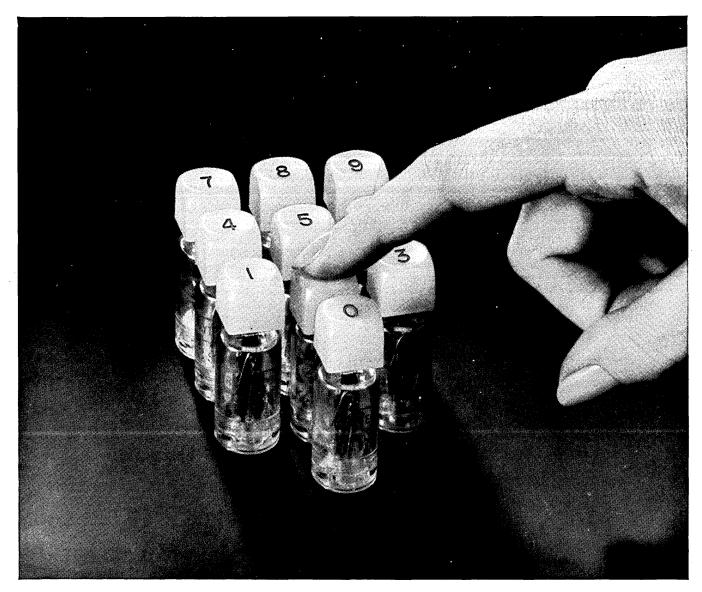

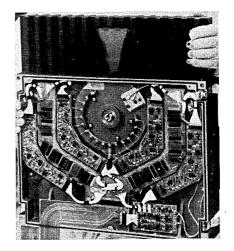

### Access time: 6 minutes

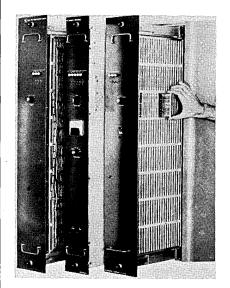

You need fast access to your system as well as your information. Our new medium capacity memory sys-

tem delivers both. The NANOMEMORY 2000 Series has unequaled reliability

mation into a single 2% cubic foot module (7"x19"x21.5"). Multiple units can be used for larger capacities. The basic package includes the power supply, 2½D-organized magnetics, IC electronics and an optional self tester. It does everything bulkier systems do-but does it in less space while delivering cycle times as fast as 650 nanoseconds and access times to 350 nanoseconds.

Should you need it, physical accessibility is just as outstanding. It took six minutes to

empty the unit shown. Normal maintenance is even faster. All stacks and electronics are mounted on functionally-oriented plug-in cards. One minute to open the case, then

and operating margin. It packs up to 295,000 bits of infor- way pull a card for easy access to any component. For added convenience, standard parts readily available from your local distributor are used throughout.

For access to more information on our NANOMEMORY 2650 (650ns cycle time) and NANOMEMORY 2900 (900ns cycle time), please write us.

12621 Chadron Ave., Hawthorne, Calif. 90250 (213) 772-5201

# The Brain Picker

#### Nanologic 150 Can Measure All Of Your Fast Memory's Output Parameters Automatically and Simultaneously At Scan Rates Up To 100 MHz With One Look Per Bit Regardless Of Plane Size.

You can use Nanologic 150 to measure output width, propagation delay, rise time, fall time and amplitude directly on your memory's sense line output. You can measure all these parameters simultaneously and automatically on a Go No Go basis or retain quantitative information. Width, delay, rise and fall times can be measured to within =35 psec with 50 psec stability. Peak amplitude and amplitude tolerance can be measured to within 1%.

3

Nanologic is a real time amplitude and time measurement system capable of operating repetitively at rates in excess of 200 million times per second. Use of strobing modules preceding the measurement modules allows selection of intervals of interest to 3 ns or multiplexing of several sense lines to alternate measurements. Upwards of seventeen multi-function modules are available "off the shelf". Cost? Well, it depends upon system complexity; it's a modular system. We're sure, though, you'll be pleasantly surprised.

Chronetics' Nanologic is the most widely used and thoroughly proven instrument system of its kind for data acquisition and reduction in nuclear physics research. Eight years of continuous development and use establishes Nanologic as the most stable, most reliable, highest performing, highest quality...

See for yourself. For specifications, applications notes and or a prompt demonstration at your plant and with your memory, just write or 'phone.

U.S.A.: 500 Nuber Avenue, Mt. Vernon, New York (914) 699-4400 TWX 710 560 0014 Europe: 39 Rue Rothschild, Geneva, Switzerland (022) 31 81 80 TELEX 22266

### I'm Edson de Castro, President of Data General. Seven months ago we started the richest new small computer company in history. This month we're announcing our first product: the best small computer in the world.

Data General wasn't started on a shoestring.

My associates and I had been with a company where we developed the most successful line of small computers in the business. And we knew the only way to go was big. Right from the beginning.

So we got the financing to be big. To build a plant that'll knock out these computers by the hundreds. To develop a large enough technical service organization to really support our customers.

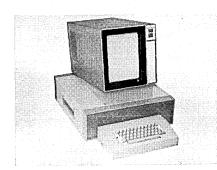

And we designed a revolutionary computer. The NOVA.

Other small general purpose computers are built around an obsolete architecture based on an old technology. NOVA is built around medium scale integration. It's the first with multi-accumulator/index register organization. The first with read-only memory you can program the same way you do core. The first low cost machine that allows you to expand memory or build interfaces within the basic configuration.

One more thing. The price with a 4096 16-bit word memory and Teletype interface is only \$7950. And we're offering the best discounts in the business.

Because if you make a small inexpensive computer, you have to sell a lot to make a lot of money. And we intend to make a lot of money.

CORPORATION 275 Cox Street, Hudson, Mass. 01749

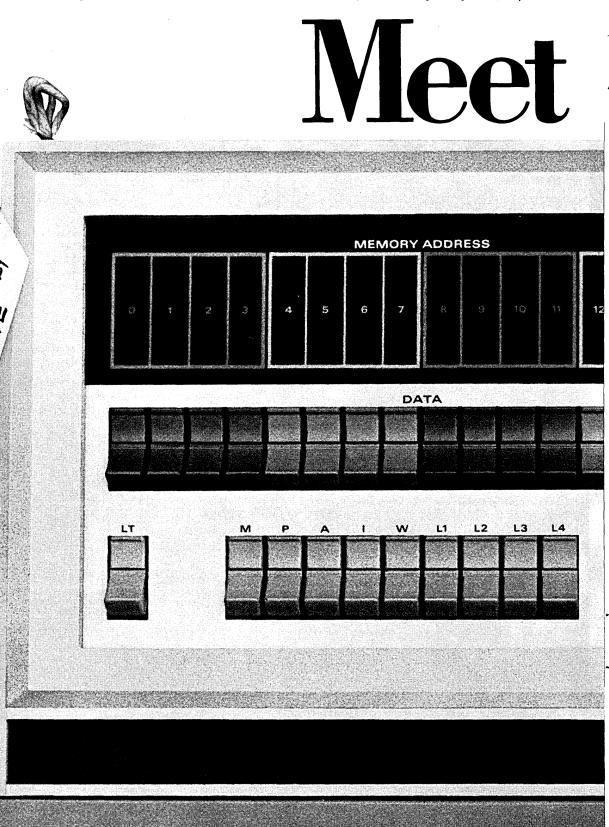

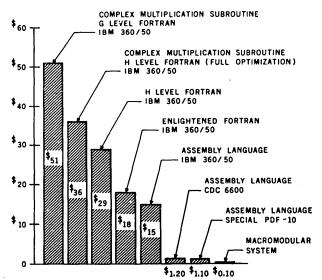

Specifications: NOVA is a 16-bit word general purpose computer. It has four accumulators, two of which may be used as index registers. It offers a choice of core or read-only memory of 1K, 2K, 4K, 8K, and up to 32K 16-bit words (or twice that many 8-bit bytes). NOVA comes in the desk top console shown here or a  $5\frac{1}{4}$ " tall standard rack mount package. Both the desk and rack versions can hold up to 20K 16-bit words of memory or interface for a large number of peripheral devices. NOVA has the most flexible 1/0 facility ever built into a machine of its class. It will include a high-speed Data Channel and automatic interrupt source identification as standard equipment. Write for more information today. Or see us at the Fall Joint Computer Conference on Wednesday.

COST

PER

TERM.

DATA DISC, INC. introduces a low-cost, high-performance, alphanumeric and graphic display system that displays:

- characters in UPPER and lower case - black on while or while on black

- super<sup>script</sup> and sub<sub>script</sub>

- 2560 characters (96 ASCII set)

- 4080 CHARACTERS (64 ASCII set)

- graphics on a 512 x 480 matrix

This time-shared display system can generate new displays at the rate of 60 pages per second. The control unit and CRT refresh disc memory can serve up to 128 display terminals, which contain standard TV monitors.

DATA DISC, INC.'s Television Display System (TDS), with only a few terminals, costs less than alphanumeric-only systems. With additional terminals even greater economy can be realized.

#### NO. OF TERMINALS

See this equipment at Booth L-3 during the Fall Joint Computer Conference. Or, contact William Stevens, Vice President, DATA DISC INC./Dispaly Division, 1275 California Avenue, Palo Alto, Calif. 94304 (415) 326-7602 You just can't find a more reliable high-density memory stack than you can get from RCA Reliability is important! Availability, too! So we use modular construction for flexibility, improved reliability and faster delivery of storage capacities from 4K x 6 to 4K x 32. And this type of construction offers the highest storage capacity for minimum size.

Improved reliability is inherent in the design, because we use an absolute minimum number of solder joints. Mean-time-between-failure has been calculated as 1.25 x 10<sup>6</sup> hours.

So *challenge* us on delivery. May we arrange for a demonstration for your specific application? Contact your RCA Field Representative for details. Or call Marketing Department, (617-444-7200, Ext. 242), RCA Memory Products Division, Needham Heights, Mass. 02194. For Technical Bulletin MP317, write RCA Electronic Components, Commercial Engineering Department F-ZB-11, Harrison, N.J. 07029

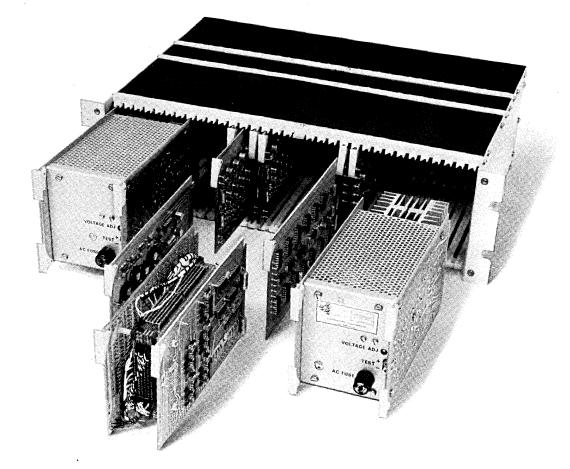

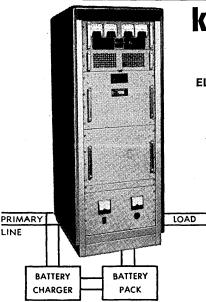

# The Ferroxcube FI-3 The World's First Plug-Out Memory

The FI-3 comes as a complete memory system ready to plug-in or you can plug-out those capabilities which exist within your system.

The flexibility of the FI-3 is limited only by the versatility of the system with which it will be used.

If your system already has +6 volts or -12 volts or both, we'll sell you the FI-3 without the plug-in power supplies.

If your system requirement is for a self-contained memory, we'll plugout the 19-inch rack-mounting chassis.

If you don't need 8192 words by 18 bits, we'll plug-out enough memory to give you only 1024 words by 6 bits or some capacity in between.

In fact, if you have the capability, we'll plug-out everything but the stack and give you the drawings for the rest.

For those busy engineers who want us to do the work, we'll be glad to plug-in all the modules and IC logic cards and supply an FI-3 with: •  $3 \mu$ sec full cycle time

- 2 μ sec half cycle

- multimode timing with full, half or split cycle

- address register/counter

- random or sequential operation option

- memory retention

- 3D, 4-wire construction

- 30-mil low temperature coefficient cores

MTTR is enhanced by having only five card types. Field adjustments and temperature compensation are unnecessary. Over 100 catalogstandard FI-3 models to choose from.

And we'll do it in less than 60 days for as little as \$2,000 per unit. The lowest price in the industry.

erroxcube

Systems Division, Englewood, Colorado

Write to Jack Buckwalter.

Baltimore—Eastern Components, (301) 322-1412; Burbank, Calif.—(213) 849-6631; Englewood, Col.—(303) 771-2000; Lansing, Mich.—(517) 482-7140; Minneapolis—(612) 920-7955; Northlake, III.—(312) 261-7880; Philadelphia—Eastern Components, (215) 927-6262; Phoenix—(602) 264-3120; San Francisco—Wm. J. Purdy Agents, (415) 863-3300; Saugerties, N.Y.— (914) 246-2811; Union, N.J.—(201) 964-1844; Waltham, Mass.—(617) 899-3110; Winston Salem, N.C.—(919) 725-6306; Toronto, Ontario—Philips Electron Devices, Ltd. (416) 425-5161.

# Who said you can't buy more 16-Bit computer capability for less than \$30,000?

### SCC Says you can — and you don't have to be a Dr. Livingston to find it.

Our NEW 4700, 16 bit, 920 Nanosecond Digital Computer is the first small machine with a throughput rate fast enough to handle those tough jobs ... It costs less than \$15,000 for the basic machine.

The 4700 can free a larger system for more important work. It can be the brains behind a satellite communications network ... a message switcher or a data terminal.

The 4700 can control processes while your engineers check out programs simultaneously. It gives you an economical way out of the communications bottleneck...a complete remote capability at a price you can afford.

Compare the 4700 with other computers.

You can spend \$30,000 for a 16-bit model that expands from 4K to 32K. The 4700 expands from 4K to 65K.

You can pay \$30,000 for a 16-bit machine with a 790 nanosecond cycle time. The 4700 does it in 920 nanoseconds, but it only costs half the price.

You can spend \$30,000 for a 16-bit machine and not get hardware double precision and floating point arithmetic. The 4700 offers this option for only \$5,000.

Furthermore, we don't know any 18-bit orange that dares to compare itself with our 16-bit apple.

"SEE US AT BOOTH 201-202-203 DURING FJCC"

Whatever Your Computer Application — Be Sure You Talk With SCC Before You Buy

P.O. Box 34529 • Dallas, Texas 75234 • 214 -- 241-2111 • TWX 910-860-5509

Scientific Control Corporation

EASTERN REGION: College Park, Md. Huntsville, Ala. Parcinnany, N. I.

Parsippany, N. J. West Springfield, Mass.

CENTRAL REGION: Dallas, Tex. WESTERN Hazelwood, Mo. Houston, Tex.

WESTERN REGION: Palo Alto, Calif. El Monte, Calif.

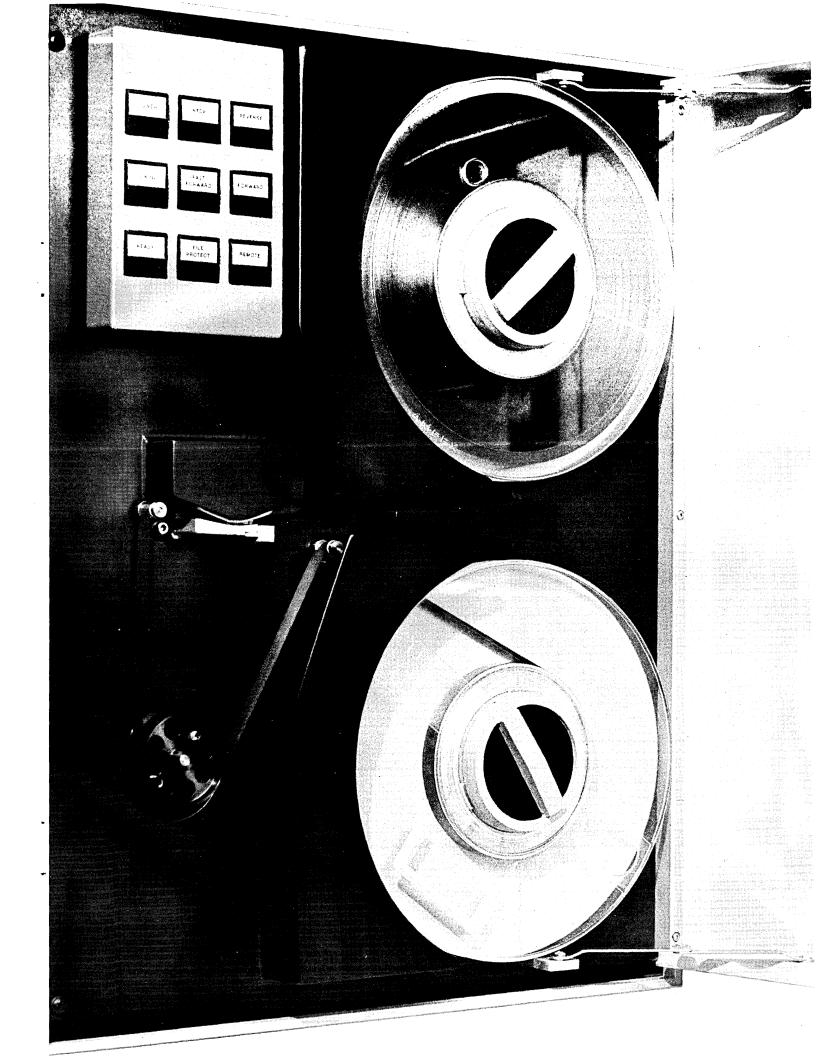

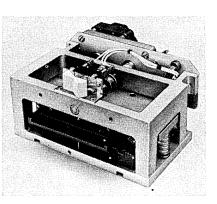

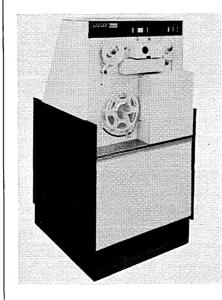

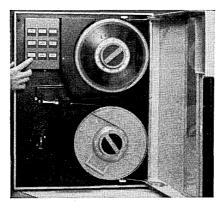

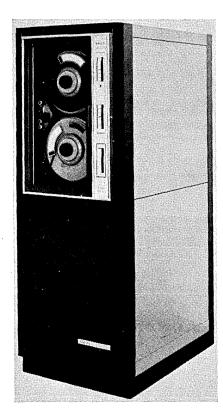

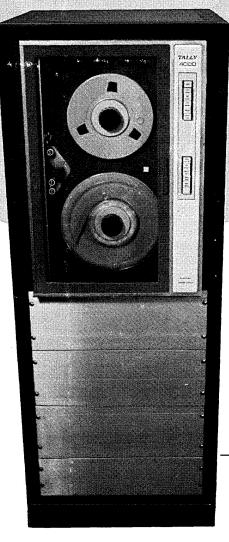

### A new Ampex computer tape drive for \$3500.\* Wow!

The new Ampex TM-Z is a complete computer-class tape memory system (including read/write electronics) that best fulfills the need for a low-cost, high performance, low speed unit for your computer, data terminal or data acquisition system. Completely computer-compatible, it conforms to all requirements of IBM and ASCII 7- and 9-track formats.

Simplicity of design results in the utmost in reliability and easy maintenance. This completely new, ready-to-plug-in tape memory system features the same precision as the higher speed Ampex TM-7 and TM-16 tape memories.

#### PERFORMANCE CHARACTERISTICS

#### Tape Speeds:

Standard speed is 24 inches per second, Read/Write (19.2 kHz transfer rate at 800 cpi). Any single tape speed between 10 and 24 ips can be obtained by utilizing a continuously variable adjustment.

#### Tape Width and Thickness:

$\frac{1}{2}$ -inch width, 1.5 mil by 2400 feet (732 meters)

#### **Recording Density:**

Standard: 556 and 800 cpi. Optional densities available.

#### **Recording Formats:**

Standard: 9-track ASCII 0.6 inch IRIG (IBM 360, 2400 Series compatible). Optional: 7-track, NRZ 0.75 inch IRIG (IBM 7330, 729 Series compatible).

#### Start/Stop:

Tolerances permit bilateral interchange of tapes with equipment compatible with IBM and ASCII 9-track standards.

#### Input Voltage and Frequency:

Voltage: 100-250 volts RMS with transformer taps.

Frequency: 48 to 63 Hz.

Consumption: Average, 400 watts. Peak, 500 watts.

#### Interface Characteristics, Data and Control Lines:

True: Logic "1" = 0.2 (-0.2 + 0.2 volts)False: Logic "0" = + 3.3 (-0.9 + 1.7 volts)

Logic: TTL units employed

#### Dimensions:

Complete tape memory system, including self-contained data electronics, can be mounted in a standard 19" or 24" rack. Height: 24" Width: 19" or 24"

Depth: 17" overall (141/2" rack depth)

#### Weight:

100 lbs. maximum

#### Functional Modes (selective):

- 1. Write Forward, Read Forward

- 2. Read Only Forward

- 3. Read Only Reverse

#### **Options:**

- 1. Vertical Parity Check

- 2. Vertical Parity Generate

- 3. Write Echo Check

- 4. Longitudinal Parity Check

- 5. Longitudinal Parity Generate

See our TM-Z at the FJCC in San Francisco. Or, write for more information: Ampex Corporation, 401 Broadway, Redwood City, California 94063.

#### CIRCLE NO. 12 ON INQUIRY CARD

\*Price including all read/write and control electronics, in lots of 100 per year.

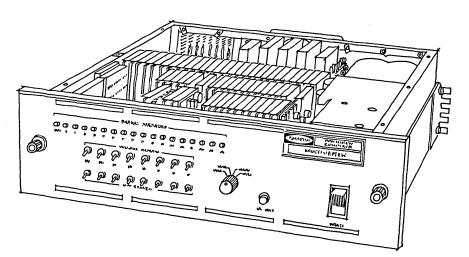

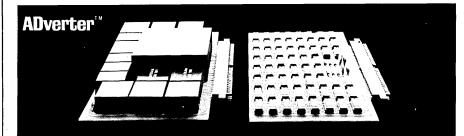

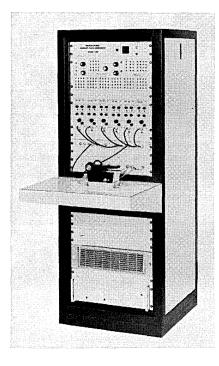

# Raytheon Computer's MULTIVERTER III. 100 kHz throughput.

Faster throughput is just one of the benefits offered by the MULTIVERTER III, newest version of our widely-used "analog front end in a box." Multiplexer capacity can be up to 128 channels, the sample-and-hold amplifier has a 2 microsecond settling time and 50 nanosecond aperture, and the converter is our new 15-bit, 0.01% ADC 100.

Options include • IC registers hold

up to 512 bits of buffer storage • Controls and indicators • ADC available as separate unit

• MUX available as separate unit

• Wiring for additional logic

• 32 channels simultaneous sample-and-hold.

However you want it, the sooner you write or call us, the sooner you'll have it. Raytheon Computer, 2700 S. Fairview St., Santa Ana, California 92704. Phone (714) 546-7160. In Europe and the Mid-East, write Raytheon Overseas, Ltd., Shelley

> House – Noble Street, London E. C. 2, England, Phone : 01 606 8991, Telex 851-25251. Ask for Data File CB-162.

CIRCLE NO. 13 ON INQUIRY CARD

# Lockheed has in production the world's fastest 2<sup>1</sup>/<sub>2</sub>D memory system.

### And one even faster.

Lockheed's CD-65 completes a memory cycle in 650 nanoseconds. It's the world's fastest production 2½ D memory system...except for one that's 150 nanoseconds faster: the Lockheed CD-50. □ Speed is just one advantage you get with the CD-65 and CD-50. They both offer a wide range of standard storage capacities-from 8,192 to 65,536 words. Their 2½ D organization provides inherently high operating margins. Total modularity gives them highly flexible interface capability, timing and control, and storage capacities. Plus, both the CD-65 and CD-50, subjected to worst-case design analysis and review, perform with exceptional reliability. For the world's fastest response with technical material — full details on the CD-65 and CD-50 --- write to: Memory Products. Lockheed Electronics Company, Data Products Division, 6201 E. Randolph Street, Los Angeles, California 90022. Or even faster, call (213) 722-6810.

Visit booths #307-402 at the F.J.C.C.

#### COMPAN A DIVISION OF LOCKHEED AIRCRAFT CORPORATION

**ELECTRONICS**

**LOCKHEED**

# your I/C logic system is only half as fast as it could be...

-where the priceless ingredient is care!

COMPUTER DESIGN/NOVEMBER 1968

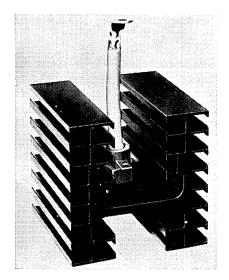

# MECL III picosecond logic is here !

At last, fourth-generation computer designs and highlysophisticated instrumentation designs have become a reality, thanks to the ultra-high speeds that are now possible through the current mode logic of MECL III!

Three different circuits in this new line of emitter-coupled devices are currently available for evaluation. MC1060S and MC1062S, dual 4 and quad 2-input gates, offer propagation delay times that are typically 900 picoseconds when operated into a 510 ohm load. Reduce the load an order of magnitude and the delay time is only 1.1 nanoseconds; still twice as fast as any comparable form of logic.

In addition, MC1070S, single phase, type "D" Flip-Flop, provides a toggle/shift frequency that is typically 350 MHz. And, it can be "tweaked" to higher frequencies by application of an external bias.

The standard MECL III package is a stud-mounted, 15pin ceramic flat pack. The stud, connected to  $V_{\text{ef}}$ , is designed to improve heat dissipation.

For further information about MECL III or for individual evaluation units, contact us at the address below. Don't wait another day to begin designing the picosecond logic of tomorrow's fourth generation computers.

### **MECL III** picosecond logic available in prototype kit

Six MECL III circuits plus a design information brochure are packaged in a useful, compact kit. Devices include two each of the three circuits described here. The advance information brochure contains device specifications plus design rules and applications information. The entire package is available through your Motorola Semiconductor Representative for \$154.00 (any quantity).

### **MOTOROLA** Integrated Circuits

MOTOROLA SEMICONDUCTOR PRODUCTS INC./P.O. BOX 20912/PHOENIX, ARIZONA 85036

#### INDUSTRY NEWS

#### **FREQUENCY HOPPING DIGI-TAL DATA MODEM SUCCESS-FULLY DEMONSTRATED** — Experimental tactical communications equipment which permits simultaneous access to satellite relays by many ground, airborne, shipboard, and vehicular terminals, has been successfully demonstrated by Sylvania Electric Products Inc., Buffalo, N.Y.

Known as a digital data modem (modulator-demodulator), the device breaks up the information output of a teletype into a sequence of pulses, according to Leonard E. Gough, Director of Engineering for the Central Division of Sylvania Electronic Systems.

By hopping the pulses over many frequencies, the modem permits simultaneous access to a satellite by several tactical terminals. Because terminals employ various pulse pat-

#### **PLATED WIRE MEMORY OR-DERS INCREASE** — Honeywell's Aerospace Division in St. Petersburg, Fla. reports that orders for plated-wire computer memories have given Honeywell "an encouraging lead" in the military and paragraphic memory merket that it

aerospace memory market that it forecasts will exceed \$200 million by 1971. "Plated wire has moved from the

research and development laboratory to the marketplace," said John W. Anderson, vice president and general manager of the division. "So far this year, Honeywell has received orders totaling several million dollars."

"Plated-wire memories are replacing ferrite-core memories in many military and aerospace computer memory applications because of greater speed, non-destructive readout capability, lower power consumption and higher reliability, Anderson said. terns, the hopping technique allows many messages to be transmitted simultaneously over the same band of frequencies.

The modem functions as a small digital processor, converting radio signals to binary information. This information can be added, subtracted, and multiplied in the same manner that a computer arithmetically processes data. Such a digital technique permits design of highly reliable, solid-state components, utilizing integrated circuits for significant over-all weight and volume reduction.

Installed in a mobile ground terminal, the compact unit was tested on a communications link between Sylvania's engineering laboratories in Williamsville, N.Y., and a second satellite communications terminal in Lexington, Mass. Both terminals were provided by the Lincoln Laboratory of the Massachusetts Institute of Technology, which designed a modem for the Tactical Transmission System (TATS) under an Air Force-sponsored research and development program.

Two-way communication was demonstrated for two and one-half hours between the two points, a distance of approximately 400 miles, via the Lincoln's experimental satellite LES-5.

"Establishment of the link proved the ability of the Sylvania unit not only to function as predicted, but demonstrated its compatibility with Lincoln's experimental TATS modem," Mr. Gough said.

Sylvania developed its modem for the Tactical Satellite Communications Program (TACSATCOM) under a \$3 million Air Force contract.

"These inherent advantages will permit increasing use of plated wire in air, sea and ground applications as improved fabrication techniques lead to lower production costs."

Honeywell's new memories first qualified for use on the U. S. Navy's new Poseidon missile. All Poseidon missile-borne guidance computers will be supplied with plated-wire memories, according to Raytheon, prime contractor to the Navy for prototype production units.

Honeywell's first major sale of plated-wire units to be used in spaceborne telemetry systems was made to Space Craft, Inc., Huntsville, Ala. Space Craft said it will use the memories in telemetry systems for major defense programs as well as on projects for NASA.

Thomas S. Crutcher, market manager for computer memories, said the most recent order came from RADC, Griffiss Air Force Base, N.Y. The contract calls for design and development of a plated-wire memory for advanced ballistic missile systems

Dr. John N. Dempsey, Honeywell Inc. vice president for research and engineering, said further refinements in plated-wire technology can be expected from work now being conducted at the company's Corporate Research Center in Minneapolis. The research center began plated-wire development work almost five years ago.

"Packaging research already has led to doubling memory capacity in one-half of the volume needed previously," Dempsey said. The fourto-one increase in packaging density has resulted, typically, in 16,000 word-2 bit memories occupying less than 300 cubic inches. Further studies are emphasizing the correlation of magnetic and structural properties of the wire, and changes in these properties during the aging process.

COMPUTER DESIGN/NOVEMBER 1968 CIRCLE NO. 15 ON INQUIRY CARD

#### You could build mountains out of our logic cards... if you had to

We've got that many. And you could build different kinds of mountains, too. We've got just that product line versatility. Build T<sup>2</sup>L SUHL I mountains, or T<sup>2</sup>L SUHL II mountains, or DTL mountains, or 7400 T<sup>2</sup>L mountains. We can supply enough for you to go as high as you want. And building mountains is a nice way to look at how our micrologic circuit cards are applied. But if you don't want to think in terms of mountains, you can build mole hills, too.

For more information, write or call: CNTROL LOGIC, INC. 3 Strathmore Road Natick, Massachusetts 01760 / Tel: (617) 235-1865

### What does your wife know from computers? She just wants a ticket to Camelot.

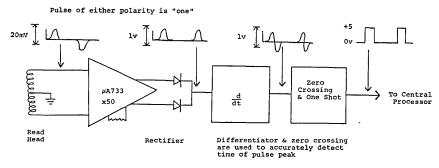

But she'll soon talk to a computer terminal at the supermarket when she buys a ticket for Camelot, a game against the Mets, or a rock concert starring the Northumberian Chamber Music Society. Computer terminals made by Wyle, for Computer Sciences' Computicket, will turn Southern California supermarkets into box offices. She'll pick an event, choose from available seats, and the terminal will print tickets on-the-spot. A central computer does the thinking, but Wyle does the talking for Computicket. Terminals<sup>\*</sup> are just one example of Wyle's computer involvement that includes research, components, assemblies, entire systems, and even testing other firm's computers. What does Wyle know from computer terminals? More than almost any other firm this side of Camelot. Scientific Services and Systems Group, Wyle Laboratories, 128 Maryland Street, El Segundo, California 90245

\* FOR VIRTUALLY ANY INPUT-OUTPUT TERMINAL APPLICATION

CIRCLE NO. 16 ON INQUIRY CARD

### **INDUSTRY NEWS**

NAVAL TACTICAL DATA SYSTEM

— Hughes Aircraft Company recent announced it has surpassed the \$125-million mark in the value of computerized shipboard command, control and communication display systems it has built and delivered to the U.S. Navy.

(The seagoing units are designated NTDS, for Naval Tactical Data System.)

Dr. Norman H. Enenstein, manager of the company's data processing products division, said the equipment — the first large-scale shipboard application of computer-driven displays — is operating on scores of U.S. and foreign naval warships.

The systems use radars, computers and the "nerve center" data display consoles to provide command personnel with an accurate electronic picture of the immediate tactical situation.

NTDS was originally applied to naval air defense. It has now been given additional roles of air traffic control, tracking of surface and subsurface ships, shore direction bombardment, and rescue coordination.

COMPUTING SYSTEM TO HELP DESIGN AND TEST FLY HELICOPTERS — Test pilots at Textron's Bell Helicopter Company, Forth Worth, Tex., soon will be able to test fly a newly designed helicopter before it has even been built. The pilots first will fly the "new helicopter" using a mock-up cockpit linked to a specially designed IBM computing system. James F. Atkins, executive vice president, said the computing system will electronically simulate a helicopter in flight, showing pilots and engineers how the aircraft would perform.

The computing system, called a hybrid, combines one digital computer — an IBM System/360 Model 44 — and two analog computers built to IBM specifications by Hybrid Systems Inc. of Houston. George Brooks, supervisor of Bell Helicopter's engineering-computing department, said that the same computing system is helping to develop new helicopter designs and is much faster than conventional computers.

COMPUTER DESIGN/NOVEMBER 1968

"The new system makes our design work more economical, gives engineers a better insight into their work and greatly reduces the time involved in setting up and solving design problems," he said. "For example, in one recent design study we found the new system provided approximately 100 solutions in the same time that conventional computers would provide a single solution. By making simulated studies on this advanced IBM computing system, we are able to prove the design of a helicopter that will meet a given set of specifications," Mr. Brooks said. "We can even show before building it — just how it will fly and what it will do."

**STANDARD COMPUTER-OP-ERATING-SYSTEM CONTROL LANGUAGE COMMITTEE FORMED** — An ad hoc committee is now being formed under the auspices of the United States of America Standards Institute (USASI) to investigate the need for and feasibility of a standard computer-operating-system control language.

Millard H. Perstein of System Development Corporation (SDC) has been appointed chairman of the committee (USASI X3.4.2F), which becomes a part of the committee structure concerned with data processing, in general, and programming language in particular.

The two-day committee organizational meeting will be held at SDC, Santa Monica, Calif., at 10 a.m. on Tuesday, February 4, 1969. All interested persons are invited to attend the initial meeting.

A wide range of interests will be represented on the committee, including producers and users of computing equipment, terminal equipment, and computing software; trade associations, user organizations and professional societies.

Mr. Perstein said this organizational meeting will be devoted to establishing committee rules, assigning tasks and reviewing work already accomplished in developing a standard.

All those who plan to attend are urged to write: Millard H. Perstein, chairman X3.4.2F, System Development Corporation, 2500 Colorado Avenue, Santa Monica, California 90406. Attendees will receive, in advance of the meeting, copies of the committee charter, some of the applicable rules of procedure and working papers concerned with standard computer-operating-system control language. The day of MAC is here!

#### Pages 66 and 67

### The one way printed circuit board

Rejects in the printed circuit business are about as popular as a northbound driver in a southbound lane. They simply must not happen. Since one in four of our employees is concerned with quality control, they almost never do. We know what rejects can cost you. Time, money, special handling. No rejects is the dictum where our shipping line begins.

Fewer rejects mean your programs can be completed on time and with complete accuracy. Your customers will appreciate it. Your P & L statement will look a little rosier. All because "ONE WAY" is the one way Cinch-Graphik knows to build PC boards. Try us?

### **INDUSTRY NEWS**

AFIPS APPOINTS EXECUTIVE DIRECTOR AND PLANS IN-CREASED SERVICES — Paul Armer, President of AFIPS, has announced the appointment of Dr. Bruce Gilchrist to the newly-established position of AFIPS Executive Director. In this capacity, Dr. Gilchrist will be responsible for developing increased AFIPS services to the AFIPS member societies, governmental bodies and the general public. All AFIPS Headquarters functions will report to Dr. Gilchrist.

Dr. Gilchrist has been a Council Member of the ACM since 1958, serving as Secretary from 1960 to 1962 and Vice President from 1962 to 1964. He was elected Vice President of AFIPS in 1965 and served as President of AFIPS from 1966 to 1968. He currently represents AFIPS on the Division of Engineering of The National Research Council and is the AFIPS liaison representative to the Computer Science and Engineering Board of the National Academy of Sciences.

When making the announcement, Mr. Armer commented that the appointment of a full-time Executive Director marked a key point in AFIPS history, and he looked forward to greatly increased AFIPS activities in many areas. Mr. Armer said that his personal priorities for increased AFIPS activities include providing information services, devoting more effort to educational activities directed at the public, the computer professionals themselves and the government, and, in general, providing a better image for the computer field.

Mr. Armen noted that in its decision to appoint an Executive Director, the Board of Governors of AFIPS recognized that this was just the first step in responsibly meeting a number of long-felt needs. The AFIPS Board has already approved a proposal to start an AFIPS Press to handle the publication of proceedings of AFIPS Conferences and to meet Member Society publishing needs. At its December meeting, the Board will be asked to approve a Public Information program.

Dr. Gilchrist will be responsible for developing plans and programs and assisting in the implementation of approved projects. Mr. Armer emphasized the word "assist," saying that the efforts of volunteers are, and will remain, the mainstay of AFIPS activities. **COMPUTER PROGRAM STORES AND RETRIEVES IN-FORMATION IN PLAIN ENG-LISH**— Data Corporation, Dayton, Ohio, has developed an information storage and retrieval system that permits operators to communicate with a computer in plain English instead of in codes or symbols, according to Data board chairman, William F. Gorog.

The system, called Data Central, holds nearly any kind of information in a central data bank. Operators ask questions and can receive answers through a remote console unit or from the computer's high speed printer ,as they prefer.

Earlier attempts at similar programs have required complicated codes and symbols or the establishment ahead of time of a filing system that depends on the knowledge of certain key words or symbols to retrieve information, according to Gorog.

Data Central organizes its own internal filing system from information stored in the computer and actually cross files each unit of information by every significant word in it. This means the operator can use any word, except articles like "the" and "a" and other common terms, as a handle to extract information.

The system, originally designed for use with an IBM 360 system, can be adapted to any similar size computer.

**COMPUTER LANGUAGE RE-SEARCH** — Computer scientists at the University of Colorado are modifying a number of computer languages to enable a person to conduct a running conversation with the machine while it solves his problem. The project is designed to permit a computer user to interject "what if" and "show me" type questions while a problem is in the computer — and to receive instantaneous replies.

The effort is supported by a \$225,000 grant to CU from the Control Data Corp. (CDC).

Dr. E. Rex Krueger, director of the CU Graduate School Computing Center, where the work is being done, said the project was conceived last spring after the computing center installed a microfilm recorder and a television-like graphic display unit, both of which are tied into a CDC6400 computer. He added that results of the two-year research project "are expected to bring a new dimension to the use of modern computers."

# We've never met an AC motor problem we couldn't lick...

### Almost.

At Diehl we solve better than 90% of the AC motor problems presented to us by designers. Sometimes right out of our vast stock. Very often by special design. With our long experience, our fine engineering and designing staff and our extensive production facilities, we can produce AC induction, reluctance or hysteresis synchronous motors to meet any specifications.

#### FOR EXAMPLE:

This **Spindle Drive Motor**. The problem was a motor to be used as a spindle drive in memory files having minimum shaft runout and concentricity tolerance.

The result was a motor with constant speed that is noise and vibration free and has total shaft runout and concentricity error of less than .0005.

If you have a motor in mind you'll find dealing with Diehl a profitable experience. Whether your design calls for an induction motor or a synchronous motor of the hysteresis or reluctance type, remember, our stock runs from 1/770 horsepower on up. Or we'll design one for you.

Call your Diehl representative today.

### THE SINGER COMPANY Diehl Division

Finderne Avenue, Somerville, N.J. 08876/(201) 725-2200 • TWX 710-480-9325 2221 Barry Avenue, Los Angeles, Calif. 90064/(213) 478-0896 actual composite

# 12 layers. 10 mil lines, 6 mil spaces. 1,004 intermediate and feed-thru plated-thru holes.

### Now you're talking multilayer.

Add this to a full production requirement manufactured from scratch in just five weeks—with a final acceptance yield of 97 percent...

And you're talking about National Technology.

The story behind National's complete precision multilayer capability starts with a fully departmentalized and equipped 20,000 sq/ft production facility. Processing standards and tolerances that beat even the toughest specs. Advanced production methods—including a proprietary etchback technique that ensures rule-straight 3-surface etchback for maximum interconnect and reliability. Process control and continuous inspections from receiving through final electrical tests.

And finally, the people and experience to put it all together into a quality product delivered when you want it—now.

Like to have all the facts? Call or write today for our new brochure.

### INDUSTRY NEWS

**OLIVETTI UNDERWOOD EN-TERS TELECOMMUNICATION EQUIPMENT MARKET**—Olivetti Underwood Corporation, New York, N.Y. announced its entry into the telecommunication equipment market in the United States by offering a complete family of teleprinters and on-line real time data terminals.

This new family of equipment includes machines designed for use in conventional telegraphic operations, as well as units specifically designed for connection to computers over telegraph or high speed telephone lines. With over 30 different models available in this new line, Olivetti Underwood is able to provide a machine to fit the many different application requirements encountered in a complete on-line communications system. Its systems specialists are in a position to design a total system satisfying these varying requirements at minimum cost.

In creating the Olivetti Underwood TE 300 Series of heavy duty teleprinters the primary objective was to produce a machine possessing the operating characteristics of an electric typewriter, rather than the somewhat cumbersome characteristics of the conventional teleprinter.

**LOCKHEED ELECTRONICS CHANGES DIVISION NAME** — Lockheed Electronics Company, Plainfield, N., has announced that its Avionics and Industrial Products Division is renamed the Data Products Division (DPD).

In making the announcement, A. J. Grant, president, stated, "the division's former name no longer describes or reflects is activities, products or services."

Since the Los-Angeles-based division is primarily a manufacturer and developer of computer memory systems, ferrite memory cores, and printed circuit boards, the new name Data Products Division better identifies the division within the electronic data processing marketplace.

The Data Products Division supplies memory systems and components to most of the major computer companies in the United States and overseas; therefore, it is important that these companies and future customers identify with a manufacturer whose name mirrors its primary products and interest.

**COMPUTER DESIGN/NOVEMBER 1968**

real-time processing

### say bye-bye to boo-boos

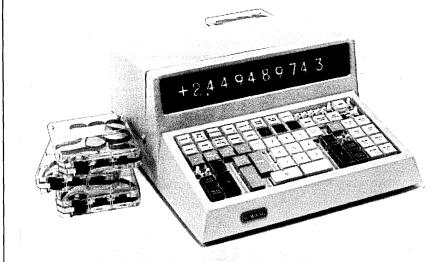

The data oriented **Teletype Model 35 ACS** with verifier helps fill forms fast, without errors

push-button box on the Model 35 ACS (Automated Communications Set) is helping eradicate costly errors in the preparation of forms in hundreds of applications. It's the optional verifier control that literally keeps flying fingers and wandering minds from entering errone-

ous characters or omitting vital facts in producing the many and varied forms necessary in keeping a business running smoothly. Forms such as sales and purchase orders; billing records; production; shipping; and distribution schedules.

#### CORRECTION, PLEASE!

Punched paper tape is really the key to the automated data preparation capability of the 35 ACS. The machine has two tape readers. When verifying, one handles format controls and fixed data-such as company name, address, etc. The other reads variable data-dates, prices, quantities, etc.

The verifier control verifies every character on the variable information tape. Stops operation instantly when the tape is incorrect or the operator leaves out a character, adds too many, or types the wrong one ... and enables her to take corrective action on the spot. Saves time, too, since the tape verifier concerns itself only with variable information and doesn't go through wasted motions of verifying established fixed data.

#### FILLS FORM AND VERIFIES AT SAME TIME

Because the fixed data tape also contains the program and format control codes, the form may be entirely filled out while being verified. The two readers alternately interoperate at programmed intervals. Fixed information goes into the proper position on the form automatically. The machine stops, switches over to verification and keyboard operation, so variable data can be added and verified against the prepunched variable data tape.

#### COMPOSITE TAPE

Besides printing the complete business form with carbons, the Model 35 ACS can simultaneously perforate an error-free composite tape containing all or any portion of fixed and variable data desired.

This tape can be used to transmit on-line to remote Teletype equipment; computers; or other business machines. The Model 35 ACS uses the U.S.A. Standard Code for Information Interchange (ASCII).

> The Model 35 ACS is available with sprocket feed platen for 81/3 inch continuousfold business forms, or friction feed platen for 81/2 inch single or multiple-ply paper.

#### MORE INFORMATION

If you would like detailed information on this goof-proof form filler, please write Teletype Corporation, Department 71L, 5555 Touhy Ave., Skokie, III. 60076.

### DEVELOPMENTS

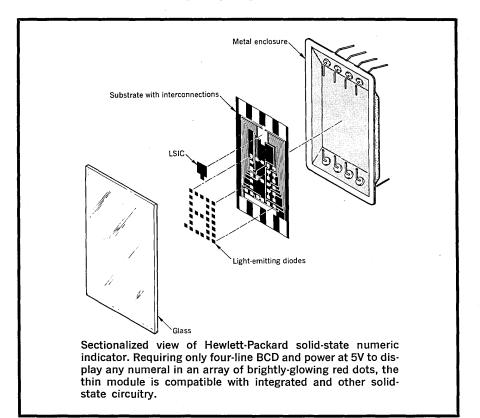

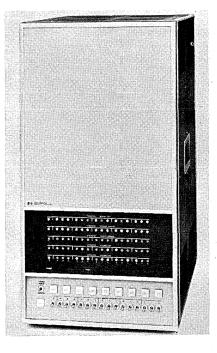

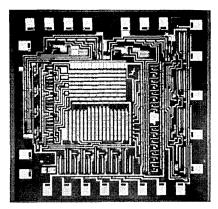

#### HP Develops BCD and IC-Compatible Low Voltage Numeric Display

Hewlett Packard, Palo Alto, California, has developed a display module which needs only conventional 4-line (8421) BCD and IC-compatible 5 volt power to display any numeral in an array of bright red dots. The flat, sealed module uses gallium arsenide phosphide lightemitting diodes for display, and a monolithic integrated circuit for decoding.

The monochromatic red (6550Å) numerals are produced by selectively energizing a matrix of the lightemitting diodes. The numerals are 0.25'' high, but actually appear much larger and are readily legible by people of ordinary vision at distances up to 10 feet, and at angles up to  $\pm 60$  vertically and  $\pm 70$  horizontally. In addition, the solid-state indicators present no parallax problem since all numerals are produced in the same plane.

Twenty-seven electroluminescent diodes are positioned within a  $5 \times 7$ matrix format and assembled with the IC on a dielectric which supports the electrical interconnections between diodes and the IC. This unit is then assembled in a metal case, and sealed with a glass cover.

The monolithic IC, containing more than 250 active elements, decodes the binary coded decimals and energizes the appropriate diodes to form a visible numeral. Starting with the four conventional BCD signals (8421), the IC logic first generates the complement of each, producing eight inputs to the decoder. These signals then determine a unique drive among ten alternatives, each corresponding to a decimal numeral.

Not all the 35 positions of the  $5 \times 7$  matrix were used to form the numerals (although all 35 would be used to form alphanumerics). Twenty-seven positions will produce all the numerals, and since certain combinations always occur together, the number of necessary diodedriving signals is reduced to 18.

Thus the third IC logic conversion is from ten signals to eighteen. This selection of 18 unique diode combinations preserves immunity from misreading should a single diode or diode set go out; this was considered a necessity, in view of experience with undetected misreadings in classical segmented displays.

Although the theory of light emitting diodes has been understood for some years, the achievement of high luminous efficiency is recent. Attaining it was in part a matter of new technology in growing the materials, and in part determination of optimum trade-offs among the many variables available in devising electroluminescent p-n junctions.

Starting with pure single crystal gallium arsenide, Hewlett Packard grows its own epitaxial layer of gallium arsenide phosphide alloy in production reactors designed and built by the company. Gallium arsenide phosphide wafers up to two inches in diameter can be grown, while holding the phosphorus-toarsenic ratio to within 1% throughout the layer, and holding thickness to 1 micron tolerances.

A principal advantage of the lowvoltage numeric indicators is their compatibility with integrated and conventional solid-state circuitry; drive and power-supply needs are the same. A further advantage is voltage-variable brightness which achieves optimum readability under widely varying ambient light conditions. Projected reliability is high. This is a result of assembling IC, light-emitting diodes, metallized interconnections, and substrate into a single sealed module. The lightemitting diodes themselves exhibit half-life characteristics; tests have shown that brightness (with constant current) declines to half its original value only after more than 20,000 hours. The compactness of the module makes it suitable for application in instrument panels, status boards, and information displays.

equipment for on-line, real-time processing

DATA

### sorry, no hieroglyphics, but...

$(a + b)^2 = a^2 + 2ab + b^2$

0,+2H,0+4e=40H

It's the Model 37—a new heavy-duty line of completely data oriented terminals that have incredible communications capabilities

Teletype's new data terminal is one that will have to be seen to be appreciated. Will handle algebraic equations, chemical and engineering formulae, charts, graphs—from the most complex to "everyday" data at speeds up to 15 characters per second.

#### FEATURES GALORE

The Model 37 will recognize and react to every code combination in the U.S.A. Standard Code for Information Interchange (ASCII). Print all code graphics, generate all control functionstype in upper and lower case, and even will be able to print in two colors if desired. The computer input/output capability of this machine is complete.

#### TRAVELING TABS

Model 37's transmission capability is unique. Now, for the first time, it will be possible for an operator to set tabs from the keyboard while the set is either on-line or off. Tabs will be able to be set on-line by a computer—or any remote terminal that uses the ASCII code. There is a tab stop for every *horizontal* and *vertical* space on the page. You can accommodate end-

machines that make data move

less tabular variations in copy format. An extremely important feature for those who have a variety of forms to transmit and receive.

Built into Model 37 equipment will be everything needed for easier computer utilization and data transmission. Forward and reverse halfline feed combined with backspace, horizontal and vertical tabulation capabilities—will make the Model 37

ÇН<sub>З</sub>

H\_C C=O

CH3

the most flexible terminal Teletype has ever offered.

COMPLETE PACKAGE

The Model 37 line consists of RO (receive only) and KSR (keyboard send-receive) sets, and the ASR (automatic send-receive) set shown here plus paper tape punches and tape readers housed in modular units compatible with all Model 37 equipment. You will have a complete data moving system with all the important options you've been looking for.

THE QUICK BROWN FOX the LAZY DOGS BACK The Quick Brown Fox the Lazy Dogs Back

The KSR and ASR sets can be equipped with form feedout controls that enable an operator to advance multicopy forms into the printer by remote control. A real timesaver.

Keyboard sets incorporate many new features for easiest touch typing. An "aggregate motion" typebox prints more smoothly with fewer motions at 150 wpm, enabling the machine to operate at maximum speed six months at a stretch with normal servicing.

#### MORE INFORMATION

Heard enough to want all the facts? Write Teletype Corporation, Department 71L, 5555 Touhy Avenue, Skokie, Illinois 60076.

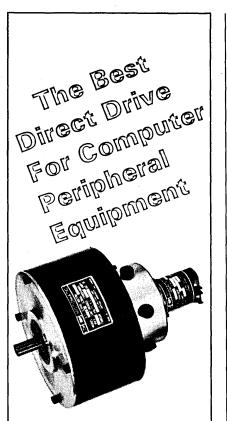

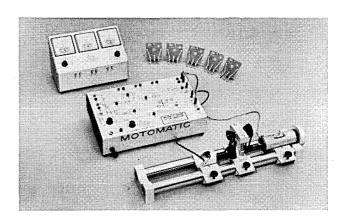

#### Moving Coil Motors

□ Electro-Craft offers a wide choice of MOTOMATIC<sup>®</sup> MCM low inertia, ultra high performance, dc servo motors and compatible driving amplifiers, available either as a complete package or as separate modules.

□ MOTOMATIC<sup>®</sup> MCM units are ideally suited for direct drive applications in computer printers, card readers, punch equipment, disc memory, magnetic and paper tape capstan drives, analog and digital positioning, recorders and XY plotters, machine tool positioning, film drives, incremental motion velocity and phase lock servos, and precision tensioning.

□ MOTOMATIC<sup>®</sup> MCM, moving coil motors feature; acceleration in excess of 10<sup>5</sup> rad/sec.<sup>2</sup>, time constant of 2m-sec., high pulse torque, extremely low inductance, high efficiency, long-life and integral feedback tach-generator.

For the best in direct drive servo systems . . . write or call today.

ELECTRO-CRAFT CORPORATION 1600 Second Street South Hopkins, Minn. 55343 Tel. (612) 935-8226

CIRCLE NO. 21 ON INQUIRY CARD

### DEVELOPMENTS

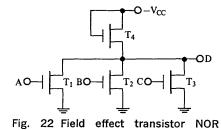

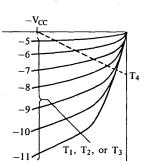

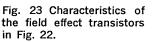

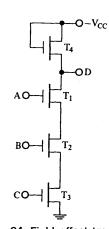

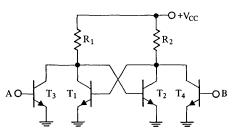

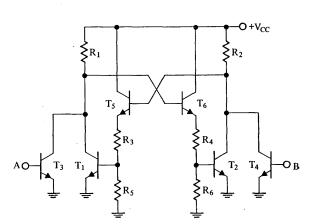

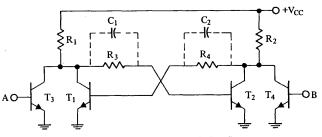

#### New MOSFET Offers Potential For Digital Applications

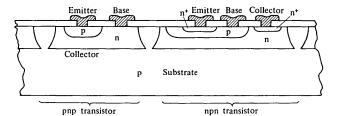

A new type of MOSFET (metaloxide-silicon field effect transistor) that may have several uses in integrated circuits for digital equipment has been recently developed by G. T. & E.

Devised by Messrs. Paul Richman and Walter Zloczower at General Telephone and Electronics Laboratories, Inc., Bayside, N.Y., the new device is called a  $P+\pi P+$  MOSFET. It exhibits all the electrical characteristics of a conventional P-channel MOSFET; however, it is fabricated on a P-type (or  $\pi$ ) silicon substrate with high resistance to electrical current instead of the N-type substrate usually used with conventional P-channel devices.

By using this device, Messrs. Richman and Zloczower also devised a complementary MOSFET structure which is unique in that both the N-channel and P-channel devices utilize the same high-resistivity P-type substrate. This achievement greatly simplifies the fabrication of complementary MOS-FET integrated circuits.

"Although we are still testing and evaluating our laboratory models, we foresee several important applications," Mr. Richman said. "These include use in memories for computers and in switching circuits employed in various other types of digital equipment."

Two types of MOSFETS, P-channel and N-channel, are commonly used in integrated circuits today. When both types are incorporated into the same integrated circuit, the configuration is called a complementary MOS circuit. The complementary MOSFETS offer faster operating speeds and negligible power dissipation when in the "stand-by" state.

"Despite the important advantages of complementary MOS circuits, their use has been limited up to now because of difficulties encountered in their fabrication," Mr. Richman added. "The difficulties have arisen because both the N- and P-channel MOSFETS must be put into separate opposite-conductivity type regions within the same silicon base."

#### Display Panel Does Not Emit Light

A five-inch by five-inch magnetooptic display has been designed by General Electric's Electronics Laboratory in Syracuse, New York, for the U.S. Army Electronics Command, to be used for the display of digital-generated information.

The unique characteristic of this display panel is that it does not emit light. The display image is produced by focusing a light source on the panel at a fixed angle and diffracting this light within the panel itself. The intensity of the display depends directly upon the intensity of the light source.

The display panel consists of a thin magnetic film that exhibits magnetization normal to the plane of the film resulting in the formation of "stripe" domains. The film has a thin layer of Bitter's solution encapsulated on its surface which conglomerates at the domain bounderies to form a diffraction grating, and has a set of orthogonal matrix conductors placed behind it.

In response to generated currents at a selected intersection of the matrix conductors, the grating reorients itself 90 degrees from the original direction. By correctly addressing the matrix conductors, the elements are thus turned "on" and left "off" to form an image. The only way to alter information written on the display is to re-orient the grating by introducing a magnetic field of sufficient magnitude. Other features of the display are a longterm, non-volatile memory which is unaffected by power failures and the ability to write on the display electronically or with a magnetic pen

In addition to this display, the Electronics Laboratory previously built a one-inch square development model of a magneto-optic display for the U.S. Army Electronics Command and a five-inch square, headup M-O Display on GE funds. Development of magneto-optics displays at the Electronics Laboratory evolved from the Lab's work in magnetic thin films and electrooptical devices. Future emphasis will be given to producing larger display panels and developing techniques to control the inherent color of the panels.

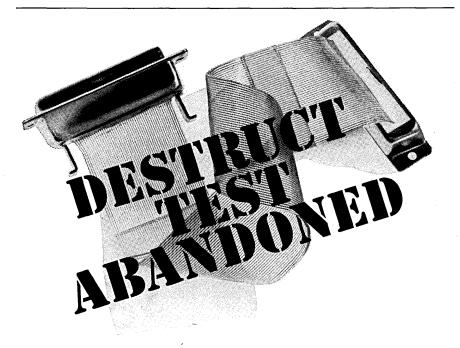

### whatever happened to red tape?

Nobody can afford it, these data oriented days. Now they use paper tape—to communicate by *Telespeed* terminals.

"Red tape," stalled orders, delayed deliveries, late paychecks, incorrect billings, unanswered letters... These and other evidences of administrative thumb twiddling are fast disappearing from the business scene. Teletype's *Telespeed* equipment is the reason, in many cases.

Telespeed terminals are a complete line of high speed tape-to-tape equipment used by all kinds of modern companies—usually for delivering company data to the processing center the fastest, most practical way. Telespeed terminals can transmit a full day's data load over regular telephone lines in a matter of economical minutes.

Information travels from its source to the home office so fast that administrators don't even have time for a good twiddle.

#### "ROLLS" ITS OWN

*Telespeed* sending and receiving sets are not only fast, but ultraeconomical. Because they "roll" their own tape, they can transmit data unattended, automatically.

Here's how they are used in branch sales offices, for example:

- The day's sales orders, receipts, etc., are entered in paper tape by a girl making off-line use of a regular Teletype ASR (automatic send-receive) set.

- (2) At end of working day, the girl puts the tape in the *Telespeed* sending set and goes home.

- (3) During the late night hours, when line rates are lowest, the home office computer automatically calls the *Telespeed* sender, and gives it a coded signal to transmit.

- (4) The Telespeed sending set automatically transmits all recorded data to the computer (or Telespeed receiver) at headquarters.

The transmission takes only a few minutes, at most. Some *Telespeed* sets automatically check the transmission for errors, *and make corrections*, at the same time.

*Telespeed* equipment means fewer procedural errors, too! Automatic transmission and retransmission of paper tape is many times more accurate than the constant reintroduction of the human element into data preparation.

#### SPEEDS, MODELS, FEATURES

*Telespeed* sending and receiving sets operate at 75 characters a second (750 words a minute), 105 cps (1050 wpm), or 120 cps (1200 wpm). None of them require any special code for transmission. The equipment will operate on any 5, 6, 7, or 8-level code including, of course, the U.S.A. Standard Code for Information Interchange (ASCII). Units are available in completely self-contained floor models, and the popular table top sending set of the "750" line. They will accommodate tape width sizes  $1\frac{1}{16}$ ,  $\frac{7}{6}$ , or 1 inch.

Sending sets consist of a paper tape reader and signal serializer. Receiving sets have a tape punch and signal deserializer. Sending sets have a sensing control to stop operation automatically at the end of the tape.

Optional features include:

Automatic Answer—enables unattended receiver to automatically answer a call from the sending set.

Line Break—when using certain data sets, operator can interrupt transmission to talk.

**Discrete Calling**—prevents sending set from being turned on by any but its own receiver (or computer).

At computer centers and outlying locations, *Telespeed* sending and receiving sets can be combined into a complete station. This is especially useful for economical computer input-output. Information is sent via *Telespeed* terminals to the processing center where it's fed into the computer. The processed data is then returned by *Telespeed* equipment.

HELPS THREE WAYS

There are three big reasons to investigate *Telespeed* equipment: Faster intelligence, lower costs, and fewer procedural and transmission errors.

With *Telespeed* terminals, you can expect smoother data flow, better customer relations. Reason enough for obtaining complete information on the three full model lines of *Telespeed* equipment, in speeds 750 wpm, 1050 wpm, and 1200 wpm.

Address all inquiries to Teletype Corporation, Dept. 71L, 5555 Touhy Avenue, Skokie, Illinois 60076.

### DEVELOPMENTS

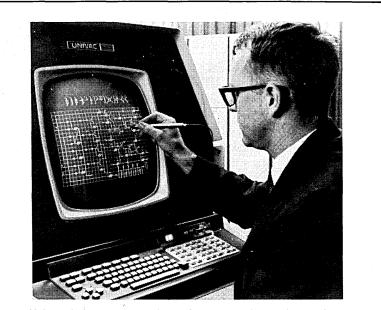

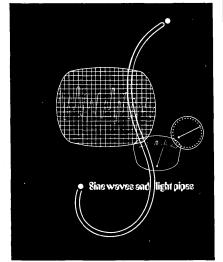

#### Graphic Display Subsystem Uses Digital Deflection Technique

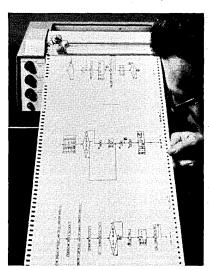

A "second-generation" man-machine communication system, featuring what is reported to be the first announced commercial digital deflection technique in graphic displays, has been developed by the Univac Division of Sperry Rand Corporation, Philadelphia, Pa.

In contrast to the typical analog system displays currently in use, the digital deflective technique produces displays of superior characteristics in terms of speed, resolution and accuracy. This capability is advanced enough to allow design of integrated circuits and detailed drawings of complex mechanical parts.

By using a digital technique, the process of converting digital inputs into analog signals and then amplifying them to high current levels is eliminated. Instead, the Univac digital deflection system permits a digital representation to drive the deflection system directly eliminating the differential amplifiers and feedback loops and their attendant adjustments. The digital technique also provides more stability of image position. Although the theoretical speed of the electron beam is not quite as high as in an electrostatic deflection system, the practical speed is faster because of the precise positioning control that can be achieved.

The graphic display subsystem is designed for direct inter-connection with a large-scale computer system or for remote operation with connections to a central processor via voice grade or wideband communication facilities. It provides instant direct two-way communication through the use of the alphabet, numerals, diagrams, charts and engineering drawings.

The display unit is equipped with a keyboard containing standard alphanumeric and 40 function keys plus a light pen for operator input, and has the capability of plotting randomly positioned points, vectors, and tabular mode alphanumeric data.

The cathode ray tube in the display unit has a usable viewing area measuring approximately 12 inches by 12 inches with data positioned in a 1024 by 1024 point matrix. Two programmable intensity levels and two programmable character sizes are provided. A 90 degree character rotation is also available under program control. Lines of full screen length may be specified as absolute (with respect to viewing area origin) or relative (with respect to the last position of the beam). Short relative lines may also be specified in a single display command word thus providing fast relative vector capability. A P31 phosphor is used with a beam spot size of 0.020 inches or less.

Character inputs are keyed in a 7-bit ASCII code. The input is decoded and entered into a diode matrix that generates a 3-bit description of the X coordinate, a 3-bit description of the Y coordinate, and a 2-bit description of the intensity level for each of the strokes used to form a character.

A display controller, which is a part of the subsystem, contains sufficient computing and control capabilities to provide an effective online response of the display system without placing an undue burden on the central processor. The controller has a 26 instruction repertoire and an 8,000 (expandable to 16,000) 18-bit, 600-nanosecond memory. Average instructions execution time is approximately 1.2 microseconds. Each controller can handle three consoles working on independent problems simultaneously.

As a result of these techniques, a number of special display devices have been produced. One such device is an ultraprecision display used for multi-layer printed circuit fabrication, which can draw lines and position the beam any place in a 15-inch square area to within plus or minus two-thousandths of an inch.

Using a light pen, an engineer designs an electronic circuit on the screen of a new UNIVAC graphic display subsystem which utilizes a digital deflection technique. From a number of component symbols shown in the upper part of the screen, the engineer can select those components he needs to construct the circuit on the grid provided by the system.

### © The New Arrival on — Memory Mountain

We're as proud as a new father about our latest brainchild. It's the spanking new 370 CORE MEMORY SYSTEM. And already it shows great promise of becoming the forerunner of an entire family of memories, ranging in speed from 750 nanoseconds to 1.5 microseconds, with capacities of up to 160,000 bits—in 2, 4, 8 or 16K organizations.

The 370 includes a bundle of joyful features like off-the-shelf pricing (even for small quantities)... fast delivery on any configuration... "building-block" modularity... expandable capacity and speeds... and flexibility that lets you use it in nearly any kind of data acquisition system.

If this fresh mountain heir makes you breathe faster, drop us a line and ask for more details. Or call a Fabri-Tek man (we've got sales offices around the globe)... he'll tell you the whole story on this baby.

> 5901 So. County Road 18, Minneapolis, Minn. 55436 Phone 612-935-8811 TWX 910-576-2913

### commentary

Comments and opinions on topics of current interest to digital design engineering personnel. A monthly column organized and prepared under the direction of **T. PAUL BOTHWELL, Contributing Editor.**

### **Reliability Considerations in Designing Industrial Control Computer Systems**

H. A. SPIVAK and L. E. HAWKINS, JR.

Industrial control computer systems perform data and control functions which are vital to the safe and efficient operation of industrial processes and plants. Therefore, system reliability is of vital importance, and reliability considerations must be an integral part of the initial circuit, thermal and mechanical design of any industrial control system.

The basic system reliability requirement is the prevention of sudden, gross misadjustment of a control loop. Since control action is applied frequently in a direct digital control (DDC) system to all loops, a hardware failure could conceivably cause such misadjustment in a matter of seconds.

#### How Reliability is Designed-In

The initial design stage, called the "concept review" is performed before the preliminary layout of the design. During this stage the various methods proposed by the development engineers will be evaluated, and design parameters will be traded off to achieve an optimum design. The reliability goal at this time is to achieve the proper functional operation with a minimum number of components, stressed well below maximum ratings. This technique provides the highest inherent reliability.

After these first considerations have been made, the

The authors of this month's CD Commentary are Herbert A. Spivack, Manager, and Leland E. Hawkins, Jr., Reliability Engineer in the Product Assurance Department at Honeywell, Inc., Computer Control Division. Mr. Spivack has the responsibility of assuring the design adequacy of CCD with regard to reliability. Mr. Hawkins is responsible for reliability analysis of computer systems and electronic components.

designer sketches out a preliminary drawing which details the proposed system. This is brought before a functional circuit review board for the purpose of discussing the design as it affects performance and reliability. With maturing of the initial design, a reasonably accurate estimate of part count by type evolves. By assigning average failure rates to each type and multiplying this rate by its respective quantities, an estimate of the system failure rate can be derived. This simple technique omits distinguishing details, such as operational stresses, thermal conditions, packaging orientation, etc.; therefore, the prediction is subject to inaccuracies. However, this method is used to point out the direction in which reliability design goals can best be achieved. It also is important for highlighting potential problem areas. By the conclusion of this second stage, the original logic diagram emerges complete and substantially verified.

After the detail design has been completed, a unit review is implemented and continued until the design is complete. During this period actual schematics and parts lists are generated. These documents are usually based on prototypes in which most specifications have been incorporated. During this period a thermal analysis is conducted by the packaging engineer. The reliability engineer at this time reviews parts lists to check for component selection and application, and verifies the authenticity of test specifications to be uniform with their intended use. He concludes this final design stage by performing a detailed system reliability estimate providing the design engineer with pertinent data relative to meeting specific reliability and to advise the future customer with average or mean time between anticipated down-times caused by random catastrophic type failures.

(continued on page 39)

#### NOTICE TO READER:

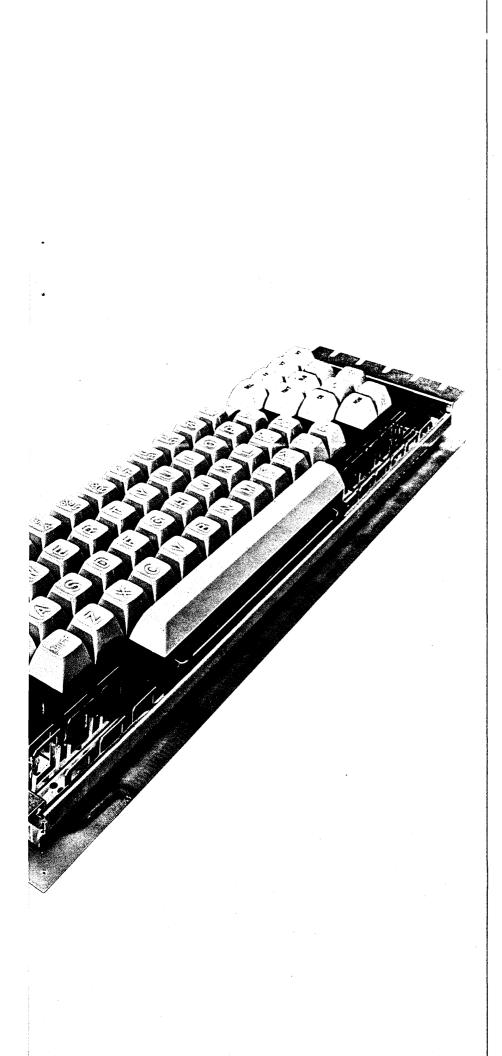

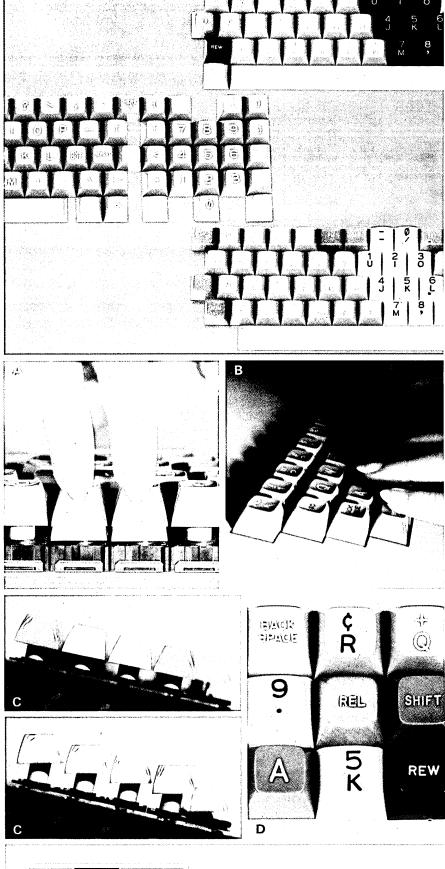

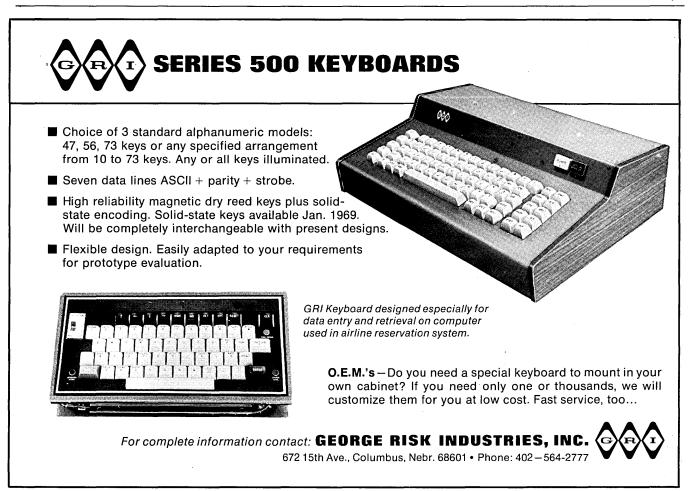

### What's happening tomorrow in keyboards has just happened

What's inside the little black box shown above has advanced keyboards into the next generation, overnight. For more on this major breakthrough, and what it can mean to you, turn the page.

# What's inside this little black box?

# A breakthrough in keyboard technology from MICRO SWITCH

Inside this key is a new discovery. Using the Hall effect, MICRO SWITCH has developed the world's first practical application of an integrated circuit as a keyboard switching element. An integrated-circuit chip (only .040" square) is actuated with a magnet mounted on a plunger. Thus, MICRO SWITCH has combined integrated circuitry with manual actuation to bring you an all solid state keyboard, unlike any other ever made. It is called SSK. A keyboard unmatched in reliability, flexibility and low cost!

# It makes possible this all solid state keyboard... SSK... the first of its kind

SSK is a keyboard that is compatible with your present *and* next generation communications and data preparation equipment. Assembled, wired and encoded—ready to plug into your equipment.

#### A breakthrough in keyboard reliability

From key to connector, every unit of the new SSK keyboard is all solid state. The only moving mechanical part is the plunger. There are no mechanical linkages and no moving contacts to wear or fail. The result is unequalled reliability.

#### A breakthrough in keyboard economy

You get triple economy. First, the initial cost is less, tailored to your high production commitments. Second, the bounce-free output of SSK requires no special interface circuitry to adapt it to your equipment; just plug it in. Finally, being solid state, SSK is practically maintenance free; cuts your service costs to the bone.

All in a completely flexible package!

For more facts on MICRO SWITCH SSK, turn the page.

# SSK...a completely flexible package...

MICRO SWITCH solid state keyboard flexibility adapts to your format and encoding needs. All standard key arrays and custom arrays, block or offset. Encoding of any 8-bit code (or less); hexadecimal; Baudot; BCD; USASCII mono-mode, dual-mode and trifunction; plus EBCDIC and custom codes.

You may choose from a complete selection of customized legends and colors. Let us know the control functions you require we'll match your needs to the letter. There's no reason anymore to compromise for any less—or pay for more—than what you want.

### Featuring the latest human factors considerations...