# COMPUTER DESIGN

#### THE MAGAZINE OF DIGITAL ELECTRONICS

### HIGH SPEED COMPUTER MECHANIZATION

**SIGN** THE CORRECT LIGHT CAN MAKE ALL THE DIFFERENCE. The Sloan Company is totally concerned with the design and manufacture of the finest quality indicator lights. Our in-house facility offers you complete selection – from the world's smallest indicator lights to Pee Cee lights with up-front replacement. If you need an indication...let Sloan light it up – brilliantly.

THE SLOAN COMPANY 7704 San Fernando Road Sun Valley, California Phone (213) 875-1123

### **RCA** announces **m-Power** DI 45 types / 3 package styles / 2 Temperature Ranges

at economy prices

Gates / Expanders / High Fanout Gates Clocked Flip-Flops / Hex Inverters  $2K\Omega$  and  $6K\Omega$  Output Pull-Up Options

- For Your Military Applications: CD2300 Series-15 circuits in RCA's Unique Ceramic Flat Package. CD2300D Series-15 circuits in RCA's Unique Ceramic Dual In-Line Package.

- For Industrial and Commercial Applications: CD2300E Series-15 circuits in RCA's Dual In-Line Silicone Package.

- Compatible with RCA CD2200 and 2200D Low-Power DTL Series.

### exact replacements for 830 and 930 series DTL

|                                                                  |                                 |                          | · ·                                        |                          |                                             |                          |

|------------------------------------------------------------------|---------------------------------|--------------------------|--------------------------------------------|--------------------------|---------------------------------------------|--------------------------|

| ·                                                                | –55°C to +125°C Operation       |                          |                                            |                          | 0°C to +75°C Operation                      |                          |

| Circuit and<br>Pull-up Option                                    | 14-Lead<br>Ceramic<br>Flat Pack | Price<br>(1000<br>Units) | 14-Lead Ceramic<br>Dual In-Line<br>Package | Price<br>(1000<br>Units) | 14-Lead<br>Dual In-Line<br>Silicone Package | Price<br>(1000<br>Units) |

| NAND Gates                                                       |                                 |                          |                                            |                          |                                             |                          |

| Dual-4 Expandable ( $6K\Omega$ )                                 | CD2300/930                      | \$2.50                   | CD2300D/930                                | \$2.50                   | CD2300E/830                                 | \$1.05                   |

| Dual-4 Expandable (2KΩ)                                          | CD2301/961                      | \$2.50                   | CD2301D/961                                | \$2.50                   | CD2301E/861                                 | \$1.05                   |

| Dual-4 High Fanout,<br>Expandable (transistor<br>output pull-up) | CD2306/932                      | \$2.75                   | CD2306D/932                                | \$2.75                   | CD2306E/832                                 | \$1.15                   |

| Dual-4 High Fanout<br>Expandable (no output<br>pull-up)          | CD2307/944                      | \$2.75                   | CD2307D/944                                | \$2.75                   | CD2307E/844                                 | \$1.15                   |

| Triple-3 Input (6KΩ)                                             | CD2308/962                      | \$2.75                   | CD2308D/962                                | \$2.75                   | CD2308E/862                                 | \$1.15                   |

| Triple-3 Input (2KΩ)                                             | CD2309/963                      | \$2.75                   | CD2309D/963                                | \$2.75                   | CD2309E/863                                 | \$1.15                   |

| Quadruple-2 Input (6KΩ)                                          | CD2302/946                      | \$2.75                   | CD2302D/946                                | \$2.75                   | CD2302E/846                                 | \$1.15                   |

| Quadruple-2 Input (2KΩ)                                          | CD2303/949                      | \$2.75                   | CD2303D/949                                | \$2.75                   | CD2303E/849                                 | \$1.15                   |

| Hex Inverters                                                    |                                 |                          |                                            |                          |                                             |                          |

| Diode Input (6KΩ)                                                | CD2310/936                      | \$2.90                   | CD2310D/936                                | \$2.90                   | CD2310E/836                                 | \$1.45                   |

| Diode Input (2KΩ)                                                | CD2311/937                      | \$2.90                   | CD2311D/937                                | \$2.90                   | CD2311E/837                                 | \$1.45                   |

| Expandable Input (6KΩ)                                           | CD2312                          | \$2.90                   | CD2312D                                    | \$2.90                   | CD2312E                                     | \$1.45                   |

| Expandable Input (2KΩ)                                           | CD2313                          | \$2.90                   | CD2313D                                    | \$2.90                   | CD2313E                                     | \$1.45                   |

| Flip-Flops<br>Clocked RS with                                    | •                               |                          |                                            |                          |                                             |                          |

| JK Capability (6KΩ)                                              | CD2304/945                      | \$3.00                   | CD2304D/945                                | \$3.00                   | CD2304E/845                                 | \$1.90                   |

| Clocked RS with<br>JK Capability (2KΩ)                           | CD2305/948                      | \$3.00                   | CD2305D/948                                | \$3.00                   | CD2305E/848                                 | \$1.90                   |

| Input Expander                                                   |                                 |                          |                                            |                          |                                             |                          |

| Dual 4-Diode                                                     | CD2314/933                      | \$2.25                   | CD2314D/933                                | \$2.25                   | CD2314E/833                                 | \$.90                    |

Ask your RCA Representative for details. See your RCA Distributor for his price and delivery. For technical information, write Commercial Engineering, Section ICZB-7, RCA Electronic Components, Harrison, N.J. 07029.

# Bob Thomason is your answer-man on the Varian Data 620/i.

# And on his nickel.

Bob Thomason knows more about the Varian Data 620/i systems computer and its use in systems than any other man in the company. He should—he's our engineering vice president. And now he is your personal answer-man, with our most authoritative answers on the 620/i and your application.

And he'll get you *immediate delivery on 620/i standard configurations,* a new availability resulting from the expanded production at our brand new plant.

Just to give you a base for talking to Bob Thomason, here are a few facts to start with:

The Varian Data 620/i is designed strictly for systems work, fully IC'd for reliability and small size. It is fast (1.8 usec cycle time, with hardware registers and our unique Micro-Exec addressing), capable (16- and 18-bit words, 4K to 32K word memory, 100plus basic commands), versatile (Party Line I/O, proven software, complete peripherals and options), and low price (\$13,900, in standard configuration, with teletypewriter).

We've delivered more than 150 620/i's already, so, we've had lots of experience in interfacing the 620/i with all types of systems, and we're currently filling orders for 400 more.

That's why Bob Thomason is ready for you. Phone him at (714) 833-2400. *Collect.*

2722 Michelson Drive • Irvine, California 92664 (714) 833-2400 • TWX (910) 596-1358

SALES OFFICES: U. S., Santa Monica and San Francisco, California; Vernon and Westport, Connecticut; Chicago, Illinois; Houston, Texas; Fort Washington, Pennsylvania; Washington, D. C. INTERNATIONAL: Australia, France, Germany, Sweden, Switzerland, United Kingdom

ST TOT DON

Wartan data machines

BATAIRE

Publisher and Editorial Director ROBERT BROTHERSTON

> Associate Publisher ANTHONY SALTALAMACCHIA

> > Editor John A. Camuso

Editorial Consultants Bernard M. Gordon Gerhard L. Hollander Gilbert P. Hyatt

Editorial Advisers Richard Ahrons Eli Anfenger James R. Bright Waldron S. MacDonald Robert S. Senator Harold H. Seward

Contributing Editors T. PAUL BOTHWELL A. S. BUCHMAN RUDOLPH J. KADLEC ROBERT P. FORAN RICHARD B. LAWRANCE H. S. MIILLER MADELINE SULLIVAN

> Art Director JAMES FLORA

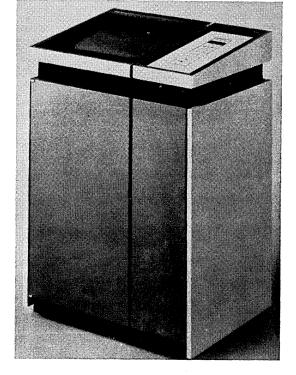

Office Manager TERRY ARMENTI

Production Manager BRYAN De LORENZO

> Editorial Production JUDY KELLEY

Technical Illustrator JOHN BROTHERSTON

Editorial Assistant PRISCILLA HANNON

Advertising Production JOAN WASIUK

Circulation Manager ALMA BROTHERSTON

Vice President-Sales LINDSAY H. CALDWELL

Editorial & Executive Offices Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1968 by Computer Design Publishing Corporation. Accepted as controlled circulation publication at Post Office at Chicago, Illinois. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS — FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Winchester, Mass. 01890. Subscription rate to anonqualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscripters is \$25.00 per year; \$2.50 per copy.

Circulation over 40,000

CIRCLE NO. 2 ON INQUIRY CARD

# COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS

#### FEATURES

26 HIGH SPEED COMPUTER MECHANIZATION G. P. HYATT Major considerations for high speed computer designs are described and related to a Micro-Electronic Modular Assembly (MEMA) packaging technique.

33 SYSTEM DESIGN OF A GENERAL PURPOSE AEROSPACE COMPUTER H. R. CHARNEY, D. W. LAMBERT and S. F. STANTEN

A computer system design that can be adapted to a variety of aerospace missions.

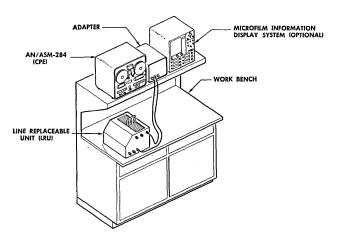

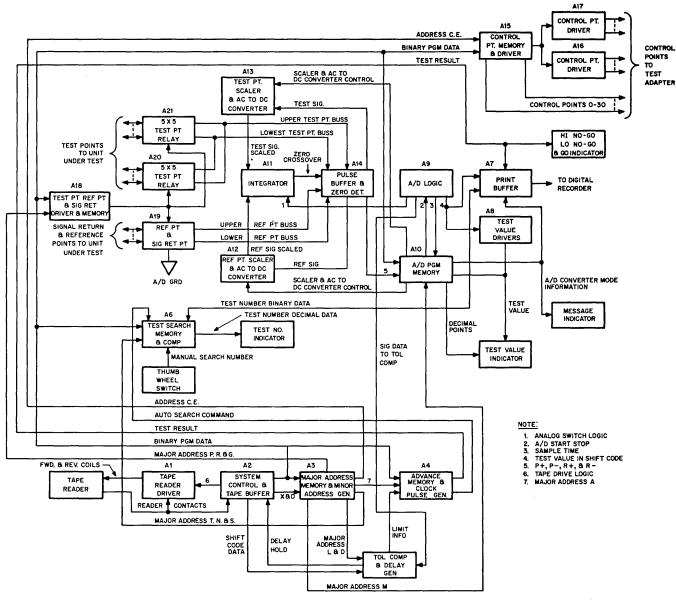

42 AN ECONOMICAL AND VERSATILE SOLUTION TO AUTO-MATIC TESTING REQUIREMENTS

D. L. SAUDER and R. T. STEVENS

An automatic testing philosophy resulting in the development of a Controller/Programmer/Evaluator (CPE), to serve as the nucleus of an automatic test station.

49 A THREE WIRE MEMORY SYSTEMS DESIGN

R. A. SCOTT and R. WHITE

Design features and operational capabilities of a series of three wire memory systems developed to provide reliable low cost memories.

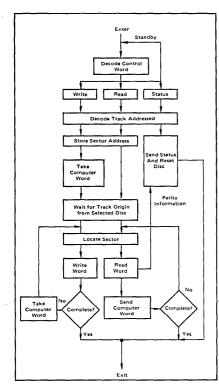

- 54 APPLICATION NOTE A Word Interlace Technique For Mating Disc Memories To Computers R. RONALD TROXELL

- 56 CD PRODUCT FEATURE MULTI-COPY SERIAL PRINTER Prints 600 Words Per Minute

#### DEPARTMENTS

- 10 INDUSTRY NEWS

- 18 CD DEVELOPMENTS

- 22 CD COMMENTARY

- 58 NEW PRODUCTS

- 70 NEW LITERATURE

- 74 ADVERTISERS' INDEX

Reader Subscription Card ......opposite page 1 Reader Service Card ......opposite page 74

# **Bypass your problems** or...how Components, Inc. can help clean up digital pulses in a small way

The problem of unpremeditated switching noise is apt to crop up in even the best of IC and hybrid logic arrays, once they are plugged into the system. When it does, the designer has the option of redesigning the circuitry or simply filtering out the spurious noise at appropriate stages. The second approach, although less heroic, is often more practicable if filter components can be found which are sufficiently economical of both space and cost.

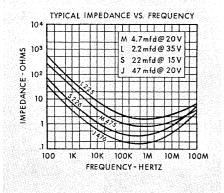

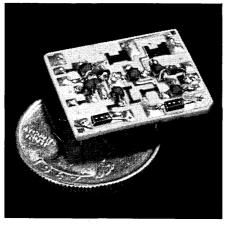

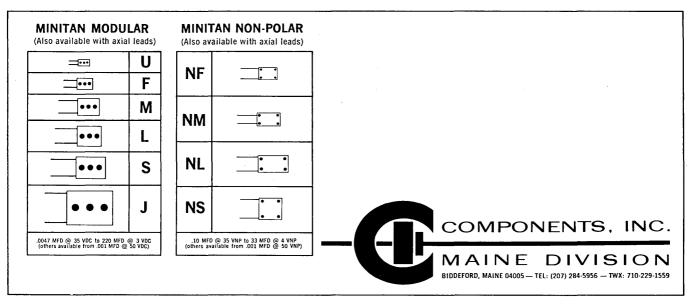

C.I.'s Minitan<sup>®</sup> Series, world's smallest electrolytic capacitors, are a natural solution here, just as they are wherever size and performance are critical. These micro-miniature, solid-tantalum electrolytics provide ideal physical and electrical properties for computer bypass and filtering applications. They are compatible with thick-film and integrated circuitry in both size and reliability, and present extremely low impedance and excellent temperature stability. Rated for use from --55°C to 125°C, they are available in values from .001 to 220 mfd., with axial or radial leads.

#### Need a Two-Way Street? ...

C.I.'s Non-Polar Minitan capacitors are available for use where ac or occasional voltage reversals are present. Unlike other non-polar solid-tantalums, these little capacitors were designed as non-polars from the ground up. Result: 1) they are available in standard, rather than off-beat capacitance ratings; 2) they are ½ to ¼ the size of other units; 3) they are extremely reliable, even with frequent voltage reversals.

When the squeeze is on . . . call Components, Inc. If you have a space problem, C.I. has the capacity to solve it. We offer more subminiature case styles and ratings than anyone else in the business. We welcome requests for samples, performance and reliability data, and application assistance. Standard prototypes normally shipped within 24 hours. Write or call today for data or samples.

CIRCLE NO. 3 ON INQUIRY CARD

### Is it possible to get a really good computer for less than \$10K? How about \$9,950 and some odd change?

That's what the new Hewlett-Packard 2114A will be pegged at. But it'll heave to just like its big brothers. Throwing around big 16-bit words. Storing 4000

(or 8000) of them at a time in memory. Fetching them out of memory in two microseconds. It'll tie in I/O devices with standard plug-ins and use the same set of programming languages – FORTRAN, ALGOL and Conversational BASIC. It may be the littlest computer in the HP family... but even at that it more than holds its own against its big brothers.

That's right. The HP 2114A offers the most desirable price/performance ratio of any computer on the market. And it won't take up much room, either, not even on your desk. One compact package 121/4 " tall houses both processor and power supply.

Yet the economy model is fully compatible with all the 2115/2116 software and I/O interfaces. The main frame accepts either 4K or 8K memory, has eight I/O plug-in slots and operates within a wide temperature range. Low-cost options include parity error check and power-fail protection.

If you think this powerful little computer is right for you, get more information from your local HP field engineer. Or write Hewlett-Packard, Palo Alto, Calif. 94304; Europe: 54 Route des Acacias, Geneva.

CIRCLE NO. 4 ON INQUIRY CARD

06810

# More about:

### Up/down decoded decade counter.

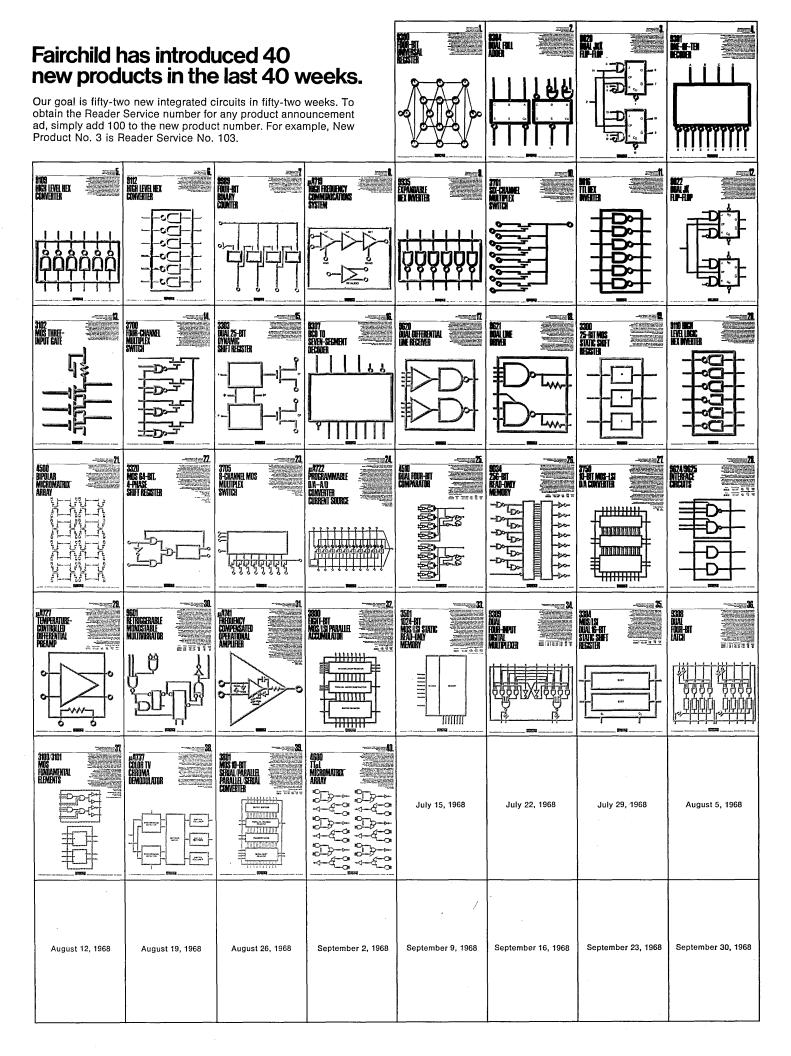

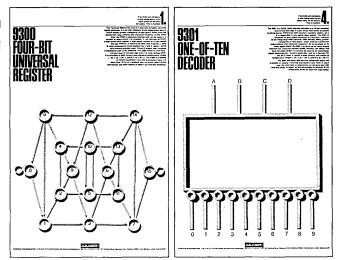

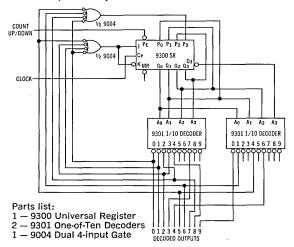

Combine New Products #1 and 4, and you have the basis of an up/down counter with decoded outputs for process control. If only the decoded outputs are used, you don't need a weighted up/down counter. A shift counter will do the job.

The 9300 universal register can be used to form a decade shift counter counting through a sequence of 10 stable states. A logic "1" or "0" is injected into the first stage of the register at each clock pulse and the previous contents shift one place. After 10 clock pulses, the shift counter has passed through all 10 stable states in a loop. On the next clock pulse, it arrives back at the starting state. A shift register can be made to count in this sequence by decoding the states through which it passes and by using the decoder outputs as a minterm generator to effectively force a logic "1" at the input of the shift register when the state sequence demands. The following block diagram shows a circuit of this type which requires only four devices.

Consider the up count sequence below with the desired input for the next state included:

In states 0000, 1000, 1100 and 0011 a logic "1" must be forced into the first stage of the shift register on the next clock pulse. This may be accomplished by using two 9301 one-of-ten decoders to decode all the sixteen possible minterms from four variables, then sum the appropriate minterms by a 4-input active low input OR gate and let the OR gate drive the JK inputs connected together on the 9300 shift register. Each 9301 decoder acts as a 1/8 decoder with the most significant A3 input acting as an enable input. The first three outputs of the shift register go to the first three inputs of the decoders and the first decoder has Q3 from the shift register as the A<sub>3</sub> input and the other decoder the Q<sub>3</sub> thereby producing a one-of-sixteen decoder. The outputs of the two decoders are so arranged as to give the decoded outputs in sequence which can then be used to select or drive external circuitry.

| 1                                         |               |                                           | C                                              | COUNT S                                   | EQUE                                           | NCE        |                                                |                                      |                                 |

|-------------------------------------------|---------------|-------------------------------------------|------------------------------------------------|-------------------------------------------|------------------------------------------------|------------|------------------------------------------------|--------------------------------------|---------------------------------|

| UP                                        |               |                                           | DOWN                                           |                                           |                                                |            |                                                |                                      |                                 |

| Q,                                        | Q1            | Q2                                        | Q3                                             | INPUT                                     | Q <sub>0</sub>                                 | Q,         | Q₂                                             | Q3                                   | INPUT                           |

| 0<br>1<br>1<br>0<br>0<br>1<br>0<br>0<br>0 | 0011100100100 | 0<br>0<br>1<br>1<br>1<br>0<br>0<br>1<br>0 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>1 | 1<br>1<br>0<br>0<br>1<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>1<br>0<br>0<br>1<br>1<br>1<br>0 | 0010011100 | 0<br>1<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0 | 1<br>0<br>1<br>1<br>0<br>0<br>0<br>0 | 0<br>1<br>1<br>0<br>0<br>0<br>1 |

The synchronous parallel enable facility can be employed to make the shift register effectively shift to the left rather than the right by connecting the three most significant shift register outputs to the corresponding lower stage parallel inputs and operating the 9300 in the parallel enable mode. The same shift count sequence can now be used. Appropriate minterms are summed by an additional active low input OR gate which drives the shift left counter, making it pass through the same 10 stable states as before, but in the opposite direction. By this means, the shift counter performs as an up/down decoded decade counter with the parallel enable/shift input as a count up/count down control. Since only the desired minterms are summed and logic "Os' ' are inserted into the first stage of the register rather than at specific states, no lock-up sequence can occur.

To obtain specifications and other applications information, simply circle Reader Service numbers 101 and 104. If you have an immediate requirement, call your local Fairchild distributor now.

# CEC digital recording heads don't exactly live up to their guarantee.

It's a matter of recorded history that they live far beyond it. Case on record: the *first* magnetic tape head replaced in a certain military data-processing installation in Germany logged more than 10,000 hours—or *five times the guaranteed life.*

An atypical performance perhaps? Yes. It was *subpar*. Unit records show an *average* utilization in excess of 12,000 tape passing hours. And a peak head life of 16,000 hours. The system operates around the clock at 120 ips.

CEC has conquered the tape head aging process through use of advanced materials developed by Bell & Howell's Research Center. The upshot has been outstanding magnetic properties, an extremely

low wear rate...and Methuselahian life-span.

You're assured that, whatever make or model recorder you're using, we've got the head for it. Regardless of interface parameters. And, although we're alone in guaranteeing our heads for 2000 hours, you're assured we try never to live down to it.

That's why we're known as the old heads in the business. For all the facts on the complete line, call your nearest CEC Field Office. Or write Consolidated Electrodynamics, Pasadena, California 91109. A subsidiary of Bell & Howell. Bulletin Kit 1711-X2. CEC/DATA INSTRUMENTS DIVISION

CIRCLE NO. 5 ON INQUIRY CARD

# Now-save vital space with 30-gauge hook-up wire

General Electric saved space and weight in wiring the back panels of its GE-PAC $^{\odot}$  Process Computers by using 30-gauge hook-up wire insulated with Kynar.

# ...Made with tough, durable Kynar®

Thirty gauge wire is nothing new... but what is new is wire insulated with Kynar, the fluoroplastic that's tough. It has twice the cut-through resistance of other fluoroplastics, cuts and strips smoothly, takes 180° bends without splitting, stands up to the punishment of automatic wiring machines or semi-automatic hand tools.

What's more, Kynar resists cleaning solvents, won't degrade with age, and operates at temperatures from  $-80^{\circ}$  to  $300^{\circ}$ F.

For samples of 30-gauge wire insulated with Kynar plus information on how you can save space, reduce weight, write Plastics Department, Pennsalt Chemicals Corporation, 3 Penn Center, Philadelphia, Pa. 19102.

Kymap...the fluoroplastic that's tough!

### INDUSTRY NEWS

**NEW COMPUTER CONTROL CONCEPT**—How can several computers linked together adapt automatically to an unexpected situation — such as a sudden fault — and continue to operate despite the fault?

A patent (No. 3,386,082) for a way to answer that question was awarded today to IBM engineers T. S. Stafford, D. C. Burnstine, J. R. Rogaski, and G. T. Paul of the company's Systems Development Laboratory, for their invention entitled Configuration Control in Multiprocessors.

**IFIP COUNCIL MEETING** — The council of IFIP held their spring meeting in Tbilissi, the state capital of Georgia, U.S.S.R. This, their first visit to the Soviet Union, was made at the invitation of Professor A. A. Dorodnicyn, the president-elect of IFIP.

A prominent item on the agenda was the report on preparations for IFIP Congress 68. F. Genuys, chairman of the programme committee, reported on the final selection of some 220 papers out of the 600 submitted.

A progress report prepared by B.

THICK-FILM RESEARCH — A broad-scope research program directed toward improved fabrication and performance of thick-film microcircuits has been recommended by Battelle Memorial Institute's Columbus Laboratories to manufacturers and users of thickfilm electronic components.

The proposed program, which would require the joint support of a number of companies, was described recently at a meeting at Battelle-Columbus. In attendance were 75 representatives of supplier, manufacturer, and user companies.

Through research, Battelle proposes to establish the inherent capabilities of selected thick-film components, investigate degradation and The ordinary computer control consists of many separate units that are interconnected to form a system, in much the same way that a house consists of separate units, or rooms, each room having its own wiring circuit, with all circuits linked together at a central fuse box. If a fault occurs, the central box suspends normal operation until the faulty unit is located and repaired.

With the new computer control there is no "central fuse box." Instead, each unit of the system contains a set of switches that connect

B. Swann, chairman of the Congress Committee, on the administrative arrangements for the congress and exhibition was also given.

Dr. H. Zemanek, chairman of technical committee TC-2, programming languages, reported that the draft of ALGOL 68 had been published, and it was hoped to have the final version ready by late July. Professor A. van Wijngaarden would present a paper on ALGOL 68 at the Congress.

The council reviewed the program of activities of the Administrative Data Processing Group (IAG),

failure mechanisms, and study new materials and processing procedures. This laboratory research would be coupled with the preparation of a definitive bibliography of literature in this area. The research program is designed to produce practical results in the design and use of thick-film circuits through a better understanding of the limits of their capabilities, and in the formulation of pastes and the fabrication of circuits.

In briefing company representatives on the purpose of the proposed research, Battelle specialists pointed out the evolutionary state of thickfilm technology and the need for exploring the capabilities and limitations of passive components comprising the latest material formulations. that unit with every other unit in the system. Special instructions or "commands" built into the computer keep watch over all the switches. This means that if a fault occurs in any unit, the computer releases its stored commands which take the faulty unit out of action and replace it with a standby unit. The change-over takes place automatically.

The invention is said to have dramatic significance in situations where system reliability is of paramount importance, as in computer monitoring of hospital patients, or surveillance of aircraft in flight.

and approved the proposals to publish a quarterly journal and the documentation of the six-month seminar held in London last year.

Council also approved plans to investigate the possibility of establishing an international abstracts service, and expressed their thanks to the representatives of the Netherlands, Soviet Union and United States for their offers of services, staff and finance.

The next meeting of the council will take place in Edinburgh, Scotland, on 31st July and 1st August prior to the opening of IFIP Congress 68.

"Compared with knowledge of other devices, little is known about operating limits and reliability of printed components and the factors that influence them," according to H. Clay Gorton, associate chief of electronic materials and devices at Battelle-Columbus. "Factors that should be investigated include processing variables, materials interactions, and operating conditions. Substrates and their influence on the quality, stability, and operating life of the components have received little attention. In addition, the interface between components and conducting interconnections is a subject requiring investigation. The proposed research program will consider these and related problems."

# 1024-bit **Read-Only Memory. Costs** less than 5° per bit!

Join system designers investigating the new Philco 1024-bit fixed-storage MOS memory arrays for nextgeneration computers.

At new economical prices, you can make use of prewired subroutines such as lookup tables, log or sinecosine generators.

A couple of big advantages. You can easily change the function without changing the program, and you can add functions to an existing system. Integral output buffers drive T<sup>2</sup>L devices directly. You can expand to any desired memory size.

Delivery? Three weeks if your bit pattern is typical. We use computerized software to transfer your bit pattern to the pM1024 with complete accuracy. Immediately available from our distributors is the pM1024. sine lookup table from 0° to 90°. For complete details and specs, contact Philco-Ford Corporation, Microelectronics Division, Santa Clara, California 95051. 408-245-2966.

| Model               | Temp. Rating           | Read Time                  | Price<br>(100-999) |

|---------------------|------------------------|----------------------------|--------------------|

| pM1024C<br>pM1024AC | 0 to 70°C<br>0 to 70°C | 2 microsec.<br>1 microsec. | \$45<br>\$60       |

| pM1024              | -55° to +125°C         | 2 microsec.                | \$70               |

| pM1024A             | –55° to +125°C         | 1 microsec.                | \$90               |

PHILCO-FORD CORPORATION

Bipolar • Hybrid • MOS • Discrete Devices • Electro-Optical & Microwave Products

# I he Clearest

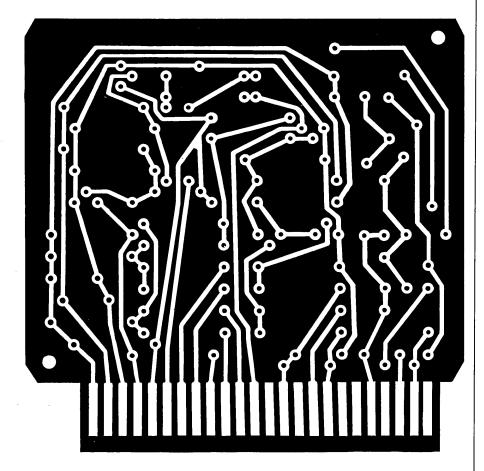

Logic modules are built on printed circuit cards. Hole location and front-to-back registration must be very accurate for machine assembly. Hand assembly is costly. Plated thru-holes must provide positive continuity. Rejects are costly. Circuit boards for logic modules must be easily solderable. Poor solderability is costly. Printed circuit cards must be delivered in volume quantity for large-scale logic module production. Time delays are costly.

These are the reasons that Cinch-Graphik boards are built with such exacting precision. Anything less is too costly.

CONSISTING OF CINCH MANUFACTURING COMPANY, CINCH-GRAPHIK, CINCH-MONADNOCK, CINCH-NULINE, UCINITE (ELECTRONICS) AND PLAXIAL CABLE DEPT.

AIR DEFENSE CONTROL TRAINER --- A digital training device which simulates air attacks to train air defense control personnel has been delivered to the U.S. Marine Corps by Sylvania Electric Products Inc.

The unit will prepare Marine air defense controllers and operators to track enemy airborne targets, direct interceptor aircraft, and designate hostile targets for surface-to-air missiles (SAMs). The trainer, which includes an instructor's console, 12 auxiliary consoles, a missile battery console, and associated electronics, was designed, produced, and installed under a \$1.3 million contract from the Naval Training Device Center, Orlando, Fla.

At the instructor's command, the trainer simulates air attacks, duplicating the movements of targets in actual battle conditions. Students at the TAOC consoles answer the "attacks" by controlling the launching of either interceptor aircraft or SAMs.

A training exercise, once started, can be modified by the instructor or interrupted to provide corrective instruction to the students. The performance of the trainees can be monitored on the instructor's console.

PATENT FOR SOFTWARE **SYSTEM** — A patent for a sorting system has been granted by the United States Patent Office to Applied Data Research, Inc. The significance of this event is that it is the first patent the Patent Office has granted for a computer system embodied in a computer program or software.

For many years patents have been granted for hardware forms of computer systems. However, legislation, which had been introduced in Congress to prevent the patenting of computer programs, had led to doubts that patent protection would be available for the software forms of such computer systems. Recently this legislation was withdrawn.

The patented system, initially developed in 1964, was described by Martin A. Geotz, of ADR, in a paper delivered to the Spring Joint Computer Conference that year. The sorting system uses a read-forward oscillating merge principle for the sorting of information on a computer and could be used with various computers.

12

Got a data block?

Maybe your computer doesn't handle incoming data efficiently. Maybe you're tired of buying and storing demodulator plug-ins — or using tunable demodulators that can't handle the range of bandwidths you need.

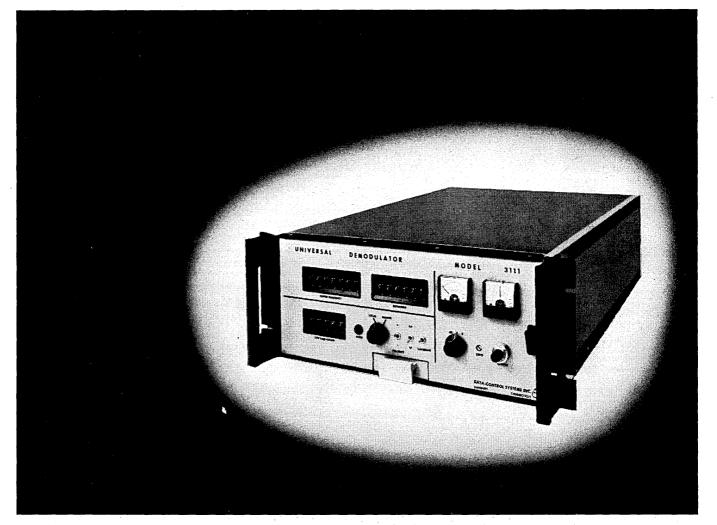

Here's the way to really bust your data block: the new DCS Series 3000 Universal Demodulator, a single unit that can process any subcarrier multiplex between 400 Hz and 1.5 MHz at any tape speed. Accuracy equivalent to the finest fixed-tuned demodulator. Reaction time in milliseconds. Manual or computer programmable. No need to recalibrate when changing set-up.

Sound fantastic? Just drop us a line and let us know about your data problem. We've got a man in your area who'll be glad to come around and bust your block for you.

Any time you say.

**DATA BLOCK BUSTER**

DATA-CONTROL SYSTEMS INC. Instrumentation for Research East Liberty Street, Danbury, Conn. 06810

CIRCLE NO. 8 ON INQUIRY CARD

## Beta • graphics™ HARD-COP **CRT PRI MODEL HC610**

#### PRODUCES 81/2 X 11" PRINTS OF COMPUTER-GENERATED GRAPH-ICS AND ALPHANUMERICS IN SECONDS . . . COMPLETELY DRY (NO LIQUIDS USED).

Model HC610 is designed to be interfaced to a computer, coupled to a display controller or slaved to any graphical computer display.

The Betagraphics Printer is a random-access X-Y device, featuring high-speed magnetic deflection, geometry correction and dynamic focus. Full format settling time is less than 12 microseconds, point-plotting rate is 500,000 points per second, line-writing rate is 2 microseconds per inch and character-writing bandwidth is greater than 1 megahertz.

Operation is simple, with only three controls in addition to the power switch - an exposure TIMER, an EXPOSE-DEVELOP switch for single exposure, development and delivery, and an EXPOSE switch for the multiple overlay or slow-buildup mode. All command and status interface signals are available for remote operation.

The Betagraphics line of peripheral display devices is here, now, to give you high quality computer graphics at reasonable prices. We'll be happy to send you complete specifications.

**TIME-SHARING SOFTWARE FOR SYSTEM 360/ MODEL 50** — A time-sharing system that combines an easy-to-use computer language and telephone access to a System/360 Model 50 has been announced by IBM.

The new system, Call/360 Basic, allows subscribers to communicate with the computer using a version of the "Basic" language. Originally developed at Dartmouth College, Basic consists of ordinary English and simple algebraic expressions.

"With about two hours of training almost anyone can take advantage of the wide-ranging capabilities of the system," said L. E. Donegan, Jr., director of IBM's Information Marketing Department.

"Fast response time, security controls, a large storage capacity and a ready-made library of IBM application programs are some of the system's features," Mr. Donegan said.

The version of the Basic language used with Call/ 360 includes new computer commands that are said to make it easier to store and handle data, format printed output and extend the precision of mathematical computations.

Since April, organizations in New York, San Francisco and Chicago have been using Call/360 Basic in an operational test, communicating with a remotely-located computer in San Francisco. Additional computer centers are scheduled to be opened in New York and Chicago this summer, with service extended to 34 major cities by year-end. Subscribers need only dial a local IBM telephone number to gain access to the computer from their terminals.

Subscribers have the option of using IBM 2741 communications terminals — with a keyboard designed especially for remote computing --- or Teletype terminals Models 33 and 35.

A minimum monthly usage charge of \$100 for Call/ 360 Basic covers various combinations of system use time, storage utilization and establishment of the user's own program library, as well as access to the IBM applications program library. Terminal and local telephone line costs are additional. Monthly rental for an IBM 2741 is \$103.50.

#### **DUAL-ACCESS ROLE BY COMPUTER SUCCESS-**FUL — Hughes Aircraft Company has announced that its H-3118M general purpose computer has successfully operated for the first time in a fully-extended 131,000word-memory configuration in a multi-processing mode.

Two arithmetic and control processors operate with a "floating executive" accessing the memory simultaneously.

The machine is said to be capable of 450,000 instructions a second, performing in the dual-processing mode with eight high-speed input-output channels.

The computer is contained in five cabinets, which include the two processing units, each in its own cabinet with more than 16,000 words of memory; and three additional cabinets, each of which contains about 32,00 words of memory.

Variations of the computer are available in single or dual processor capabilities. Either can contain up to 131,000 words of central memory.

Hughes is currently under contract to provide variations of the computer for a number of major systems, the largest of which is the \$300-million NATO Air Defense Ground Environment (NADGE) program for Europe.

CIRCLE NO. 11 ON INQUIRY CARD

COMPUTER DESIGN/JULY 1968

14

**IC BREADBOARD** — Canadian Westinghouse of Hamilton, Ontario, Canada, has recently announced the Insta-Board, a macroscopic breadboard for use in the design, development and study of integrated circuits.

The device can be used repeatedly in circuit design applications and is actually an enlarged version of the Westinghouse Insta-Circuit — a microscopic, monolithic integrated circuit breadboard.

Insta-Board features a printed circuit layout, approximately 7" by 10", containing a component ohmic contact pattern in a one-to-one correspondence with the component contact pattern on the actual monolithic breadboard. Another printed circuit layout behind the patterned board contains an array of 12 Insta-Circuits in 12-pin packages.

Internal connections between the two layouts bring out selected component terminals in the packaged devices to "jack-type" connection points on the patterned board which thus becomes an enlarged version of the monolithic Insta-Circuit.

Miniature patchcords, two to four inches in length, are provided for use in interconnecting the Insta-Board components into a desired circuit configuration. This interconnect procedure can be performed quickly so that the user can go from a circuit idea to a "monolithic" circuit in a matter of minutes.

Besides its applications in prototype circuit design, the Insta-Board is also an ideal tool for teaching integrated circuit concepts.

####

TIME SHARING SOFTWARE FOR SIGMA 5 COMPUTER — Scientific Data Systems has developed a time sharing software system for its Sigma 5 computer, thus adding simultaneous time sharing to the Sigma 5's batch processing capability, and increasing the number of time sharing computers in the SDS product line to four.

The new Sigma 5 time sharing system is a lower priced version of the time sharing system available with the Sigma 7.

The new software permits interactive time sharing for up to eight simultaneous users; at the same time the system runs batch problems written in Fortran, Cobol, or assembly language. Batch throughput is maintained at a high level by dedicating primary system resources and significant percentages of time to batch jobs and assigning on-line users to specified time slices as their demands require.

Sigma 5 time sharing configurations, including eight teletype terminals, 48,000 words of core memory, 6million bytes of Rapid Access mass storage, and the usual complement of peripherals, lease for less than \$13,500 per month. The minimum Sigma 7 time sharing configuration, which is slightly faster and offers greater growth capabilities, leases for under \$17,000 per month.

**MANAGEMENT CONTROL SYSTEM** — PROMPT (Program Monitoring and Planning Techniques), a new computer-based management control package developed by ARIES Corporation, is now available for purchase, according to an announcement by William T. Miller, Jr., vice president of the firm's Proprietary Products Division.

Describing PROMPT as a "fine-tuned" PERT, Miller explained that it provides detailed computerized reports, oriented to multiple levels of management, so *Continued on page 16*

CIRCLE NO. 12 ON INQUIRY CARD

## Beta · graphics™ **MICROFILM CRT RECORDER** MODEL MR606

#### PRODUCES HIGH-RESOLUTION 35 MM. MICROFILM RECORDINGS OF COMPUTER-GENERATED GRAPHICS AND ALPHANUMERICS.

Model MR606 is designed to be interfaced to a computer, coupled to a display controller or slaved to any graphical computer display.

The Betagraphics Recorder is a random-access X-Y device, featuring high-speed magnetic deflection, geometry correction of the image and dynamic focus of the electron beam. 1500 x 1500 resolvable elements are produced on film in a double-frame format. Positive fixed-pin registration provides  $\pm$ .0005" frame to frame registration accuracy.

Operation is simple, with only two controls in addition to the power switch — an EXPOSE-ADVANCE switch for single exposure and frame advance and an EXPOSE switch for the multiple overlay or slow-buildup mode. All command and status interface signals are available for remote operation.

The Betagraphics line of peripheral display devices is here, now, to give you high quality computer graphics at reasonable prices. We'll be happy to send you complete specifications.

# INVAC DATA LOGGERS PUNCH DATA AUTOMATICALLY

INVAC Data Loggers convert data signals directly into perforated tape in machine or computer format. Gone are costly, time-consuming, errorprone manual conversions. Compatible with the outputs from digital voltmeters, event or frequency counters, analog-to-digital converters, shaft or position encoders and other digital instrumentation.

- ... Single or multichannel inputs; simplex or multiplex

- ... Use any code or data format

- ... Punch speeds up to 60 cps

- ... Up to 60 digits per reading

- ... Up to 8 bits per character

- ... A-to-D converters available

- ... Optional Editing Keyboard or Typewriter

I/O TYPEWRITER is ideal for editing and data printout.

Write for Data

A Division of DIGITRONICS CORPORATION 26 Fox Road, Waltham, Massachusetts 02154 Tel. (617) 899-2380

Systems Incorporating TAPE PUNCHES READERS AND HANDLERS PHOTOELECTRIC KEYBOARDS I/O TYPEWRITERS AND PRINTERS CIRCLE NO. 9 ON INQUIRY CARD

#### Continued from page 15

that they know exactly what's happening at any phase of their program cycle down to the most basic task performed by each man, every hour of the day. The system is said to have been proven in over three years of implementation at Aries.

"This new, upgraded commercially-available package," Miller said, "will permit management personnel to pinpoint work slippages, make cost-effective analyses of labor, optimize deployment of available resources and evaluate individual performance — while providing historical data which can be used as a reliable basis for planning new jobs."

The basic package is written in COBOL and includes a specificallytailored program deck, three instruction manuals, an educational and usage indoctrination course, and technical assistance in setting up and running the program on the user's computer. Miller stated that the system is adaptable to any computer operation.

#### \*\*\*\*\*\*\*\*\*

**CANON INTRODUCES IC CAL-CULATORS** — A Tokyo camera manufacturer has reversed current trends in the business machine and semiconductor industries by building electronic office calculators in Japan with integrated circuits made in the United States.

Canon Camera Company Inc. has introduced one-memory and twomemory desk-top calculators using 120 and 170 Texas Instruments monolithic ICs, respectively. Only 22 Japanese-made ICs are used in the units. Increased use of ICs in the new calculators is said to result in wider arithmetic capability at lower cost and higher reliability than possible with semi-integrated units.

Model 161S, Canon's one-memory calculator, will cost \$1195. The twomemory Model 163 will cost \$1395. The two-memory model, 163, performs three functions automatically: 1) regular storage, 2) item count, and 3) sum of the multiplicand. The latter two functions have not been available on previous electronic calculators. Both units will be sold by dealers of Canon USA, the company's marketing organization here.

By applying ICs to all circuits except certain power areas — numeral-tube amplifiers and a few switching functions — TI engineers helped Canon designers reduce the number of transistors in both calculators to only 60. This compares with 250 to 317 transistors in existing imported IC calculators. The change also reduced the number of diodes to 100 instead of the 1,200 to 1,775 in the existing calculators.

TI will deliver 270,000 of its DTL (diode-transistor-logic) integrated circuits to Canon each month believed more than Japan's entire monthly production of DTL circuits. The ICs will be made at TI's semiconductor manufacturing facilities in Dallas.

#### \*\*\*\*\*

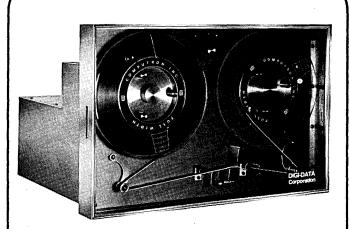

**PROTOTYPE TAPE TRANS-**PORTS FOR POSEIDON MIS-SILE — Potter Instrument Company, Inc., has delivered the first six prototypes of an advanced-design, dual magnetic tape transport system to the U. S. Navy's Fleet Ballistic Missile program. Developed under subcontract to the Sperry Systems Management Division of Sperry Rand for use in the Poseidon Navigation System, the prototypes are undergoing extensive environmental and other testing by the Navy and other facilities to the rigid specifications required for operation in electronic data processing systems aboard the Navy's missile firing submarines.

The transports contain more than one-thousand (1,000) micro-integrated circuits per system with each system being completely redundant for added reliability. The transports also possess diagnostic routine capability.

####

**BACHELORS OF COMPUTER SCIENCE**— The Purdue University Department of Computer Sciences will introduce an undergraduate degree program in computer science next fall.

Prof. S. D. Conte, head of the department, observed that needs are rapidly increasing in Indiana and throughout the country for computer scientists with bachelor's degree backgrounds.

"By permitting students to begin college thinking about computers as a focal point rather than a sidelight in their studies," Conte said, "we believe more will become interested in careers in the field."

As a further step in this direction, he said, Purdue will eventually implement similar bachelor's degree programs at its regional campuses in Indianapolis, Fort Wayne, Hammond and Westville. The four now have two-year associate degree programs in computer technology.

COMPUTER DESIGN/JULY 1968

#### NEED RELIABILITY IN YOUR SYSTEM?

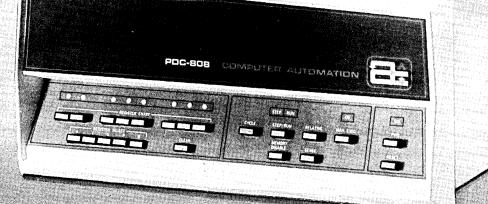

The PDC 808 Programmed Digital Controller was designed for those applications requiring long term reliability. We run the memory at eight micro-seconds to obtain low power consumption, broad operating margins, and complete interchangeability of parts.

Y COMPROMISE?

#### CONCERNED ABOUT PROGRAMMING COST?

The POC-808 is easy to learn and easy to program. There are no gimmicks. The instruction set is attaightforward and powerful. Liberal use of Macro instructions keeps programs short. The logic is in the machine, not in software.

#### WATCHING YOUR SYSTEMS COST?

If your system needs a controller, buy a controller; one that is designed for control applications. Avoid the inefficient, microprogrammable "core burner." An additional 4K memory module may wipe out any potential hardware savings.

Memory utilization in the PDC-808 is the highest in the field. A 12-word bootstrap for instance. The debug package requires only 512 words. Register change, control, skip and shift instructions use only 8 bits of memory, and use only 1 memory cycle. Memory Reference and I/O use 16 bit instructions for power and flexibility.

The PDC-808 interface is the most economical and powerful in the industry. Why spend money in logic outside the machine when the problems have been solved inside the PDC-808. This means bucks saved in parts cost and engineering time. Your bucks.

Your savings start with the purchase price. \$6600 for PDC-808 with 4K memory, console and power. No give-aways. Just the best buy going.

COMPUTER AUTOMATION, INC. 895 W. 16TH ST., NEWPORT BEACH, CALIF. 92660

O COPYRIGHT 1968 COMPUTER AUTOMATION, INC.

### DEVELOPMENTS

### Oscillator Invention Capable of Increasing Computer Speeds

Two Australian scientists Dr. F. Hirst, head of the Computation Department of the University of Melbourne, and Dr. P. Thorne, a research fellow of the department, have invented a device which they say is capable of increasing computer speeds by 500 times.

Dr. Hirst will deliver a paper about the discovery at the International Federation of Information Processing conference to be held in Edinburgh, Scotland, from August 5 to 10.

In 1961, Mr. T. Pearcey, of the division of computing research of the Australian Commonwealth Scientific and Industrial Research Organization, and Dr. Hirst began computer investigations of the nature of the solutions of a certain mathematical equation. In 1962, Dr. Hirst suggested that a certain feature of the solution of the equation could be used to design a computer memory cell. In 1963, Dr. Thorne began research into electrical networks that would be in practice the equivalent of the mathematical equation arrived at by Dr. Hirst and Mr. Pearcey.

These efforts led to the development of an oscillator which can operate in two modes of vibration. Since the computer counts in a scale of two's rather than decimals, the basic cells of a computer's memory must be able to operate in two states. In conventional computers this requirement is accomplished by using electromagnetic cores which can be magnetized in either of two directions. With available components the new device should achieve a speed of about one nano second.

#### New Type of Electronic Display Utilizes Liquid Crystals

Scientists at RCA Laboratories, Princeton, N. J., have developed flat, lowpower, low-cost displays using a newly discovered electro-optical effect in liquid crystals. The displays can reproduce any graphic data electronically and can be addressed and driven by solid-state, integrated circuits. They are said to be simple to operate, to have no moving parts, and to be compact and rugged.

Liquid crystals are organic compounds having the mechanical properties of a liquid and the regular molecular arrangements characteristic of a polycrystalline solid.

Early research disclosed that certain transparent, liquid crystals at high temperatures became milky white when exposed to electric fields, but returned to their transparent condition when the electric field was removed. Since then, new materials that exhibit this behavior at room temperature and over a range from 0° to 212°F have been developed.

When an electric field is set up on certain liquid crystals, its presence creates ions that travel through the material. These traveling ions then produce an effective turbulence that causes a dynamic scattering of light and give the liquid crystal a milky white appearance.

To construct a display, a thin film of liquid crystal only one one-thousandth of an inch thick is placed between two sheets of thin glass. The inner face of each sheet is coated with an electrode. At least one of the electrodes must be transparent so the display can be seen. This electrode is usually a conductive species of tin oxide. The other electrode may also be transparent, or it can be reflective, in which case it is ordinarily an evaporated film of metal such as nickel or aluminum. In effect, the display is a parallel plate capacitor with the liquid crystal acting as the dielectric.

Thus far, RCA has made liquid crystal displays up to 3 x 4 inches. However, there appears to be no reason why they cannot be made substantially bigger. Obviously, if there were no other way, very large displays could be formed from mosaics of smaller ones.

Liquid crystal displays have a grey scale that varies with the intensity of the applied voltage, which ranges from 6 to 60 volts. The power required for a reflective display is one milliwatt per square inch and can be either DC or pulsed. Pulsed power is used when the effect of motion is desired, the pulses being addressed to minute areas in proper sequence through integrated circuits. Operating tests of experimental liquid crystal displays thus far have shown that they last in excess of 3,000 hours.

#### Electron Gun Development Improves CRT Performance

A cathode-ray tube electron gun developed by Rank Electronic Tubes, Sidcup, Kent, England is reported to be the first to have its electron beam almost completely collimated by an electrostatic focusing system before the final aperture of the gun. Advantages include longer life, uniform brightness of spot and line, uniform spot size across the screen and increased current density.

The design allows tubes to be operated over a wide range of screen potentials while the gun potentials remain far below the level at which internal sparking and cold emission occur.

Widely different final anode potentials can be applied, according to application. For any potential, brightness is greater than that of a conventional tube, and peak cathode loading is said to be lower than that of other guns, thereby increasing life expectancy. Energy distribution (and therefore brightness) is substantially uniform across the spot and across a scanned line. The beam diameter at the point of deflection is small, so that deflection distortions are minimized. The spot size is substantially constant over the whole tube face.

Electron acceleration is provided by a helix on the inside of the tube which is integral with the electron optics. Deflection coils can be placed over the helix to introduce a post-deflection acceleration for increased sensitivity.

continued on page 20

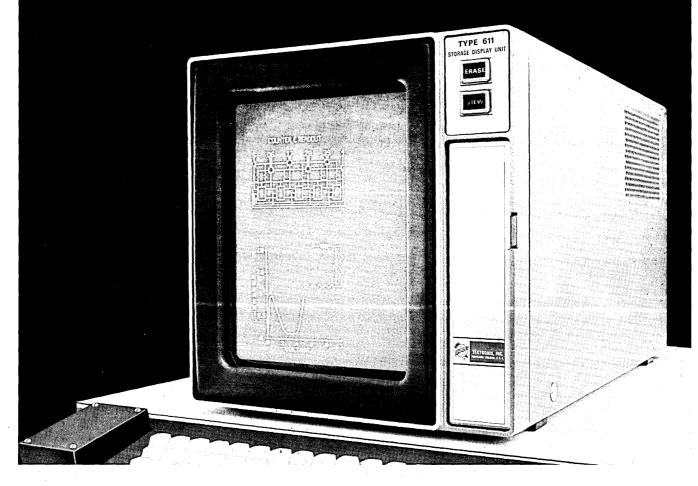

# Flicker-Free CRT Storage

# NEW Storage Display Unit from TEKTRONIX.

The Type 611 Storage Display Unit is designed to function as a computer console and remote terminal readout device. With X, Y, and Z inputs provided by peripheral equipment, this new instrument presents flicker-free displays of alphanumeric and graphic information without refreshing. The Type 611 Storage Display Unit features an 11-inch, magnetically deflected, bistable storage display tube. This new storage tube offers high information density and excellent resolution on a 21-cm x 16.3-cm screen. 4000 characters, 90 x 70 mils in size, may be clearly displayed with good spacing. Resolution is equivalent to 400 stored line pairs along the vertical axis and 300 stored line pairs along the horizontal axis. Dot settling time is  $3.5 \,\mu$ s/cm +  $5 \,\mu$ s and dot writing time is  $20 \,\mu$ s. Time required to erase and return to ready-to-write status is 0.5 seconds. Operating functions are remotely programmable through a rear-panel connector. A "Write-Through" feature provides an index to the writing beam position without storing new information or altering previously stored information.

Type 611 Storage Display Unit ...... \$2500 U.S. Sales Prices FOB Beaverton, Oregon

For a demonstration, contact your nearby Tektronix field engineer or write: Tektronix, Inc., P.O. Box 500, Beaverton, Oregon 97005.

#### continued from page 18

The spot shape on the screen is an exact image of an aperture of the gun, and spots of any shape can be produced. Size remains constant despite increase of drive voltage, and astigmatism and coma—distortions of the spot shape — are minimized. Spot size can be varied up to  $1/2^{"}$  in diameter by adjustment of the gun potentials without loss of focus or alteration in brightness. The variable spot size is said to make the gun suitable for use in data display applications where differing line widths are often required.

#### Magneto-Optic Memory Elements Successfully Demonstrated

Scientists at the Lockheed Research Laboratory Palo Alto, Calif. report they have successfully demonstrated the use of gadolinium iron garnet (GdIG) memory elements with stable bit densities of 10<sup>6</sup> per square inch.

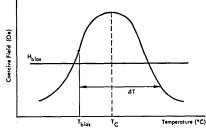

The GdIG magneto-optic memory element was proposed by Chang, Dillon and Gianola in 1965. The basic property of GdIG utilized for memory purposes is the coercivity of the magnetization as a function of temperature shown in Fig. 1.

Fig. 1. Coercive field vs. temperature for GdIG.

Procedure for operating GdIG as a memory element is as follows: A film or wafer of GdIG is magnetized to saturation normal to its surface. The field is then reversed and increased to a value below the coercive field at the bias temperature  $T_{bias}$ . A writing beam which can be a laser or electron beam is used to heat a small spot of the wafer to  $T_{bias} + \Delta T$ . Fig. 1 shows that, in this spot at this temperature, the magnetic bias field exceeds the coercivity. Therefore, at the heated spot the film will magnetically switch; that is, a bit is written.

To read the information thus written on the memory, the film is illuminated by polarized light. Direction of the magnetization is sensed by the sign of the Faraday rotation. In the written bit the rotation is opposite to the unwritten part of the film. By analyzing the polarization of the light, the bit can be interrogated electronically.

Thin wafers of GdIG, made by sectioning and polishing single- and polycrystals, were studied magneto-optically to determine the parameters useful in conjunction with the use of the crystals as memory elements. It was found that coercivity determined by Faraday rotation in these wafers was tenfold higher than that in bulk material determined by conventional means.

Thermal and coercivity considerations showed that for a given thermal input, a steep and wide peak in the coercivity versus temperature curve is desirable for small bit size and high writing speed. This was confirmed experimentally and a bit density of 10<sup>6</sup>/ sq. inch was obtained on poly-crystalline wafers. Bits were stable with time and with temperature up to 50°C. They could be erased selectively by the same writing beam with reversed magnetic bias. In addition, a memory cycling test, consisting of writing, erasing and rewriting of a point on the wafer, showed no degradation of performance after three million cycles.

For writing, a He-Ne laser beam (8mW at 6328Å) was focussed to about 10 microns in diameter. In a typical case, bits were spaced 1.5 mils between centers and were well resolved. With 1 mil between centers (106 bits per square inch), packing density approached the resolution limit of the wafer. Such a resolution limit is closely related to the grain size of the investigated sample. In the polycrystalline samples, grain sizes are in the order of 10 microns. Thus, on the average, the bits which are packed 1 mil between centers cover only three to four grains per bit. Smaller grains would give even higher density.

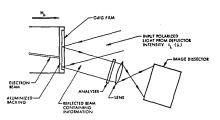

Because of the lack of an efficient optical deflector for large numbers of deflections, the arrangement of Fig. 2 is considered for implementation. A finely focussed electron beam is an efficient tool for heating a small spot and fast deflection of 1000 spots is achievable. For convenience in reading, bits in the film are organized into an array of submatrices. Instead of point-to-point deflection of a focussed optical beam to illuminate a bit, deflection of a large beam, e.g., from a discharge lamp, to illuminate the submatrix is used to lessen the requirement imposed on the deflector and light source. As an example, for a one square inch memory plane containing 10<sup>e</sup> bits, the number of deflections need only be 7 x 7; such a deflection at megahertz rates can be readily obtained by using electro-optic crystals.

The random access feature is preserved by interrogation of the large beam with either an image dissector or a photodiode array. Combination of the controls of the deflector and the sensor will then give precise access to the bit.

Since the GdIG film is a good insulator, a thin film of aluminum is evaporated over the GdIG to avoid any charging during electron beam writing. With such an arrangement, the most convenient way of reading is to interrogate the reflected light which has essentially double rotation due to the double pass of the light through the film, as shown in Fig. 2. The lamp and the dissector required in this scheme are commercially available. The magneto-optic memory element is under evaluation for use in airborne high density data storage applications.

> COMPUTER DESIGN/JULY 1968 Circle No. 14 on Inquiry Card

# Back up data on the smallest, fastest military memory weighs more than the smallest, fastest military memory.

rts Qualification Data

mai rest Da

Worst Case Circuit Analysis

MERMAL ANALY SIG

Which is just about as thorough a study as you'll ever come across for any memory system -let alone a high environmental one. So there's really nothing more to be added here other than to say our SEMS 5 tips in at 7 lbs., has a 2 µsec. cycle time, stores 4096 words of 32 bits, and meets all applicable portions of MIL-E-5400, MIL-E-4158, MIL-E-16,400.

For additional technical information, call or drop us a note. Ask for Litpak 101, our 8-page SEMS 5 brochure.

### electronic memories

12621 Chadron Avenue, Hawthorne, California 90250 Phone: (213) 772-5201

commentary

Comments and opinions on topics of current interest to digital design engineering personnel. A monthly column organized and prepared under the direction of **T. PAUL BOTHWELL, Contributing Editor.**

# FERRITE CORE MEMORIES Present & Future Status

#### R. W. Reichard

Just as the internal-combustion engine has survived the challenge of numerous contenders for its role in the automobile industry, the ferrite core memory continues to survive the onslaught of many contenders for its role in the digital computer industry. It would be generally conceded that the latter work-horse has undergone considerably greater evolution, however, as indicated in Table I.

The latter three columns indicate an order of magnitude increase in capability, which is a most impressive feat. Obviously, not all of this is attributable to ferrite core characteristics, but there certainly have been synergistic attainments in the areas of active devices, packaging, market demand, and other relevant factors.

Although Table I does not involve the parameter of time, it has been noted previously in this column and elsewhere that the cost and cycle time of core memories have simultaneously halved about every 21/2 years during the past decade. It is highly conjecturable that this can continue and there exists some tangible reasons for expecting the fall-off rate to decrease:

- 1. It appears, as noted in the table, that capacities are leveling off. At the moment, one is inclined to project that main memory will comprise several identical modules, each of a few hundred kilobits capacity. Since some contribution to falling costs in the past were due to amortization of fixed costs — registers, timing, control, hardware — over increasing number of bits, a leveling off of capacity curtails this possibility.

- 2. Considering fully switched cores of present materials, cycle time can decrease only via smaller cores. Cores cannot continually progress to smaller diameters unless smaller wire is used. There just may be practical limits on usable wire size. Number 44 wire has a fusion current rating of about 0.8 amperes, which is not too comforting, relative to 0.4-to-0.5 ampere drive currents for state-of-the-art small cores, especially in direct-coupled drive circuitry and arrays with limited heat-transfer ability.

- 3. The ferrite core plane industry has long been highly competitive and still suffers from a high ratio of labor cost to material cost in its product.

| TABLE I                   |                           |                                 |                              |                                        |  |  |

|---------------------------|---------------------------|---------------------------------|------------------------------|----------------------------------------|--|--|

| Cores of This<br>Diameter | With Switching<br>Time Of | Enabled System<br>Cycle Time Of | And System<br>Capacity up to | To Be Sold<br>at a Per-<br>Bit Cost Of |  |  |

| 80 mils                   | 1.5 μsec.                 | 12 µsec.                        | 20 kilobits                  | \$1                                    |  |  |

| 50 mils                   | $0.9 \ \mu sec.$          | 5 μsec.                         | 80 kilobits                  | \$.30                                  |  |  |

| 30 mils                   | 0.4 µsec.                 | $1 \ \mu sec.$                  | 200 kilobits                 | \$.12                                  |  |  |

| 23 mils                   | 0.25 µsec.                | 0.6 μsec.                       | 300 kilobits                 | \$.08                                  |  |  |

We solve voltage distribution problems with compact, highly efficient bus bars... like this

That's just one of scores of laminar bus configurations engineered and produced by Rogers for the IBM System/360.

As insulation specialists and pioneers of contemporary and advanced bus assembly concepts, we stand ready to design your voltage distribution components speedily and with economies born of long experience serving major computer manufacturers.

For high-capacitance, low-inductance bus bars to be used in communications wherever multiple circuits are to be fed precisely controlled power - call on Rogers. The reliable, carefully engineered component you need may already be substantially developed.

Technical data available on request

ROGERS CORPORATION Rogers, Connecticut 06263

# A NEW DIMENSION IN COMPUTER COMPATIBILITY

MODEL 1300 IBM 360 Computer Compatible Magnetic Tape Recorder

Slew mode write or read at speeds of 1000 to 3000 char/sec Incremental writing of 1200 char/sec. Choice of 200, 556 or 800 BPI, 7 track or 9 track. All computer compatibility features including IR GAP, LRCC, CRCC, EOF available—prices from \$2590.

The desire to lower labor costs by automating the process of threading cores may provide further restraint against continuing reduction in size of cores.

All of the factors above tend to indicate that the ferrite core memory business may be reaching a static state, which almost inevitably indicates demise in such a dynamic industry as digital computers. It is tempting to indulge in idle speculation on avoiding such a fate, and as electrical engineers are prone to do, we cast the blame for our ills upon the metallurgists or materials technologist.

In this case, we point out that the availability of a core material of several times the flux density and a fraction of the coercive force of present cores, with similar squareness ratio and switching constant, would enable us to score another giant step in the performance race. This latter step, incidentally, would probably seal the fate of flat-film memories, resulting in a copout for Uncle Sam who has invested several tens of millions of dollars in sponsoring flatfilm memory developments over the past decade. However, there are some newly emergent factors that may be considered which offer new possibilities.

- 1. The continual downward trend in monolithic integrated circuit costs, which has already enabled the decade-old 21/<sub>2</sub>D selection scheme to become an economic practicality, may enable other longsince pigeonholed ideas to be resurrected and economically applied. One plausible example is that the necessary complex circuitry for a common sense-digit scheme may be economically realized since the number of semiconductor devices is not a design restraint. The result of this might be, for example, practical two-wire arrays in high-performance systems.

- 2. A reduction in monolithic circuit costs, as in the previous section, must prompt reconsideration of linear selection schemes, which offer the possibility of faster cycle times with given core sizes.

- 3. Limited dissipation capability of IC's suggests partial switching of cores; the latter enables higher speed with given core size and limits self-heating effects as well. The penalty for partial switching historically has been the expense of providing stringent control on pulse current amplitudes and durations, particularly if an operating ambient temperature range of more than a few degrees was necessary. The improved uniformity of present-day cores mitigates these problems and in fact the technique of using two cores per bit would further alleviate it.

It is, therefore, to be expected that once more, advancing technology and techniques will further extend the applicability of core memories.

Mr. Robert W. Reichard, the author of this month's CD Commentary, is Manager of the Memory Products Engineering Department at Honeywell's Computer Control Division. He is responsible for the design, release and sustaining engineering for the division's high speed computer and product memories.

CIRCLE NO. 15 ON INQUIRY CARD

# If you're full of good ideas but just can't get the boss to listen... maybe you should be talking to us.

At AC Electronics, we didn't become a leader by turning a deaf ear to good ideas. Or because someone was afraid to rock the boat. Or rattle the cage. And we're not about to change.

If you aren't afraid to sound off with new and better ideas... if you warm to the challenge of projects like Apollo, LM, Titan III, SSCNS, Carousel IV and MAGIC Series Digital Computers, maybe you should be talking to us. We're looking for: Systems Analysis Engineers Digital & Analog Circuit Designers Digital Systems Engineers Mechanical Designers Commercial Programmers Semiconductor Engineers Systems Mechanization Engineers Logic Designers Digital Test Equipment Designers Scientific Programmers Industrial Engineers Optics Engineers

For more information on these and other career opportunities with the AC Electronics

CIRCLE NO. 900 ON INQUIRY CARD

Division of General Motors ... Write, phone or wire: Mr. R. W. Schroeder, Director of Professional and Scientific Employment, Box 508, AC Electronics Div., Milwaukee, Wisconsin 53201. An Equal Opportunity Employer

#### AC ELECTRONICS

MILWAUKEE • BOSTON • SANTA BARBARA

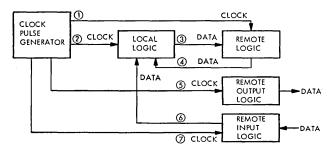

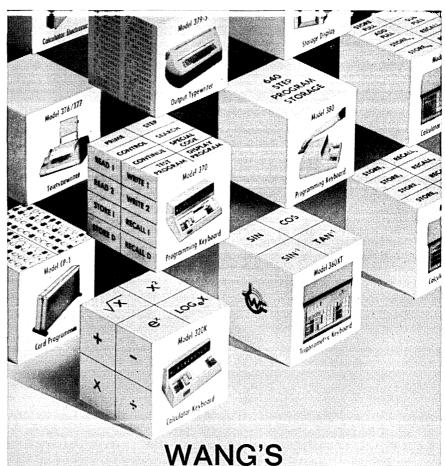

The major considerations for high speed computer designs are propagation delay, clock pulse skew, noise, crosstalk, and integrated circuit performance. All of these considerations can be significantly enhanced by the implementation of the Micro-Electronic Modular Assembly (MEMA) packaging technique.

### HIGH SPEED

The electrical characteristics of packaging and the interconnections in high speed digital computers can introduce limiting restrictions on computer operation. Therefore, it is necessary for the electronic designer to consider seriously the implications of the packaging and interconnections and for the package designer to consider the electrical characteristics of the physical design. The packaging techniques, described in this article, illustrate the approach developed from the collaboration of the logical, electronic, and mechanical designers at Teledyne. In addition, the Advanced Systems Division has maintained full cognizance over the detailed hardware design and system design to ensure compatibility on all levels of development.

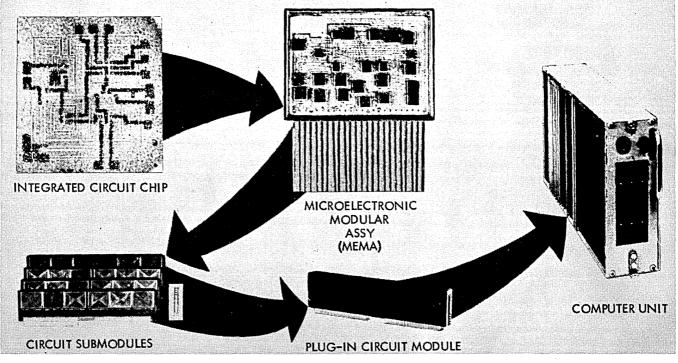

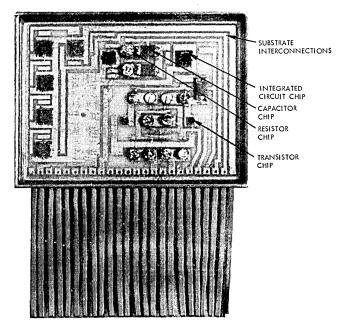

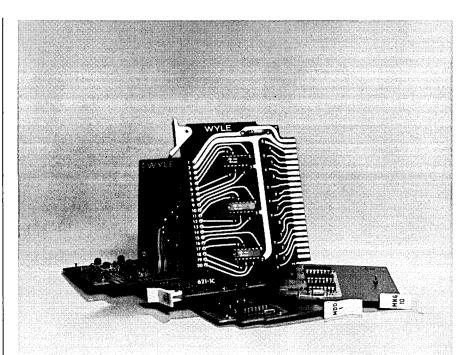

The approach to the micro-miniaturization of electronic equipment that has been adopted and developed, is one in which multiple components, including monolithic integrated circuits chips, are mounted and interconnected within a single flat pack. Designated as the Micro-Electronic Modular Assembly (MEMA), these multichip circuit modules have already found application in digital and analog equipment for major avionic systems. The advantages made possible by the use of this packaging technique are dramatic reductions in system size and weight, greatly simplified manufacturing and maintenance procedures, increased reliability and performance and considerable savings in recurring manufacturing costs.

This technique takes maximum advantage of the characteristics of integrated circuits. These are:

- 1. Preserving the small size characteristic of the integrated circuit chip by placing many chips in a single package.

- 2. Preserving the high speed characteristics of the integrated circuits by placing them in very close proximity with extremely short interconnections.

- 3. Preserving the inherent reliability of the integrated circuit by eliminating multiple packaging levels.

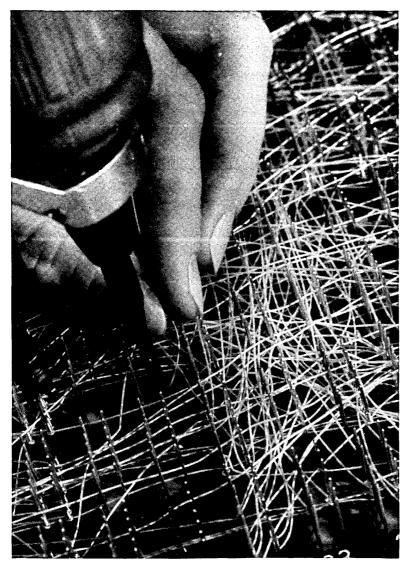

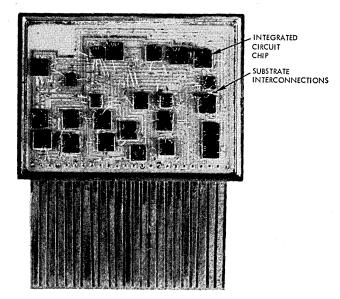

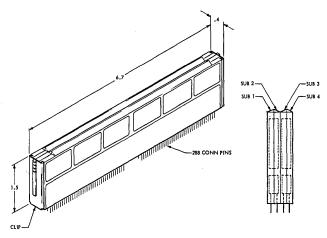

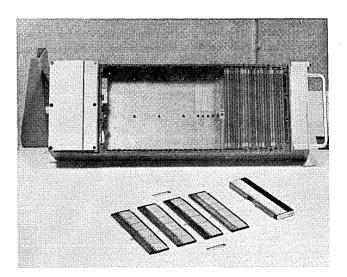

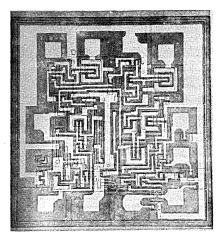

The MEMA is implemented by interconnecting up to thirty integrated circuit "bare chips" on a single ceramic substrate (Fig. 1). The substrate and associated electronics are then hermetically sealed to form the completed MEMA, which has the physical characteristics of a single flat pack, but contains the functional complexity of several large printed circuit cards with discretely packaged integrated circuits.

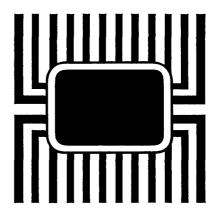

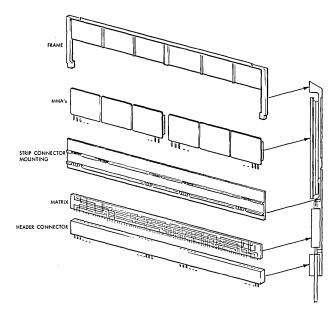

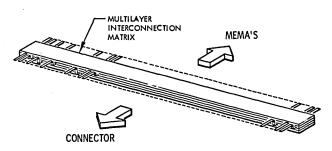

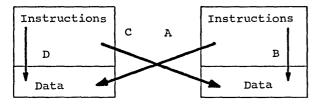

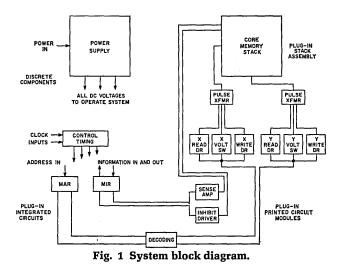

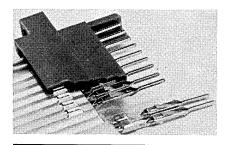

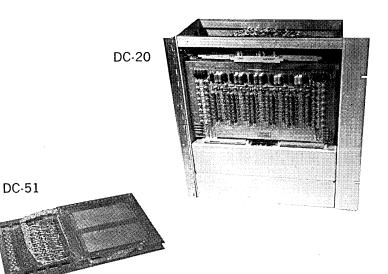

Several levels of functional modularity are mechanized to form a high speed digital computer (Fig. 2). The integrated circuit "bare chips" are mounted and interconnected within the MEMAS, which are mounted and interconnected on submodules. The submodules are clipped together to form modules, and the modules are plugged into the motherboard to form the computer.

High speed digital computers require special considerations involving propagation delay, clock pulse

Fig. 1 Micro-Electronic Modular Assembly (MEMA).

# **COMPUTER MECHANIZATION**

#### G. P. HYATT

Consulting Editor Computer Design

skew, noise, crosstalk, and integrated circuit performance. Each of these considerations can be significantly enhanced merely by reducing the physical size of the computer. Special design techniques will improve these considerations, but to a lesser degree than the physical size consideration. Miniaturized computers implemented with MEMA type techniques inherently minimize these considerations to the degree that they are not the predominating limitations associated with high speed computers. In addition, many of the special high speed computer implementation techniques may be eliminated merely by using the MEMA type packaging to miniaturize the computers.

#### **PROPAGATION DELAY CONSIDERATIONS**

Propagation delay of digital pulses is generally caused by two mechanisms, which are:

- (1) The switching delay through logic functions, determined by the switching speed of the logic.

- (2) The transmission delay through interconnections, determined by the velocity of propagation through the medium and settling of the signal due to impedance mismatches.

Interconnections in electronic systems are often treated as simple conductors. This approach is valid

Fig. 2 Levels of modular packaging.

only in relatively slow speed, small dimensional systems. In applications with clock periods that approach the transmission propagation delays, the interconnections must be considered as transmission lines. The high speed switching of the digital logic can introduce Fourier frequency components in the hundred megacycle frequency range, which is in the low radar band. Much of the theory associated with electromagnetic fields and waves as applied to radar systems is directly applicable to these systems.<sup>1</sup>

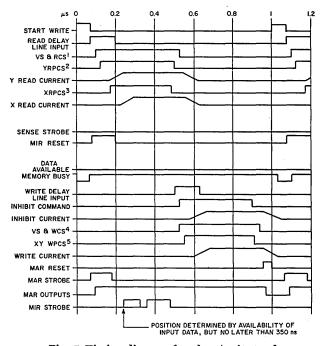

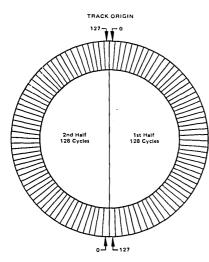

The criterion for the treatment of interconnections as either conductors or transmission lines is based upon a comparison of the clock periods and transmission propagation delays. If the propagation delay along a line is in the order of magnitude of the clock period, the interconnections should be treated as transmission lines. An electrical signal will propagate at approximately one foot per nanosecond for a nominal permitivity ( $\epsilon$ ) and permeability ( $\mu$ ) of the surrounding median. A transmitted signal will propagate along a line to an impedance mismatch interface, where a portion of the energy will be reflected. This reflection will propagate along the line in the reverse direction to another impedance mismatch interface, being reflected back and forth until the signal in the line stabilizes at the excitation level. The number of reflections that will occur prior to the signal stabilizing at an acceptable level is a function of the impedance mismatch. For larger mismatches, a larger number of reflections will occur prior to stabilization. For relatively longer transmission lines or lower propagation velocities, the delay for each reflection will be relatively longer. Therefore, the propagation delay through a wire is a function of the impedance mismatch in addition to the line length and propagation velocity.