### mini If you need a <u>A</u> computer and still haven't seen this one...

• Circle reader number 234, or

• Call "Mr. Eye-Dot".

201/229-4040 408/257-3418 617/369-7997 213/670-8386

IEEE 2A48 SJCC V7-8

### Series C:

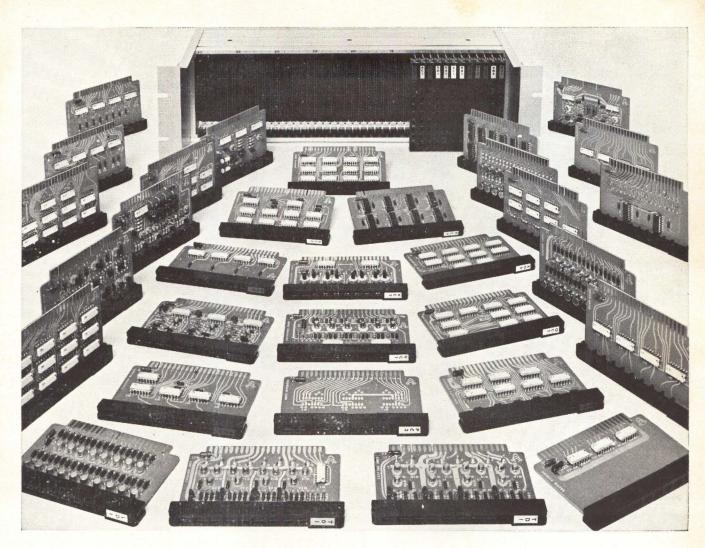

**Industry's most** complete family of compatible cards and packaging for system design Series C110 DTL 1/5MC Logic Cards for INDUSTRIAL CONTROL AND DATA SYSTEMS

Series C150 TTL 5/10MC Logic Cards for COMPUTER INTERFACE AND TEST EQUIPMENT

Series C120 TTL 20/30MC Logic Cards for MEMORY TEST AND INSTRUMENTATION

Series CA 0.01%, 10µs/bit Analog/Digital Cards for ANALOG CONVERSION

Series AW 110/150/120 Logic Cards and Packaging for **AUTOMATED WIRING**

Series P Cages, Test and Power Accessories for SYSTEM PACKAGING

SALES OFFICES :

EAST COAST CONTROL LOGIC, INC. 3 Strathmore Road Natick, Mass. 01760 TEL. (617) 235-1865

MIDWEST CONTROL LOGIC, INC. P.O. Box 461 Conneaut, Ohio 44030 TEL. (216) 599-7555

CIRCLE NO. 1 ON INQUIRY CARD

WEST COAST CONTROL LOGIC, INC. 10842 South Paramount Blvd. Downey, Calif. 90241 TEL. (213) 861-9223

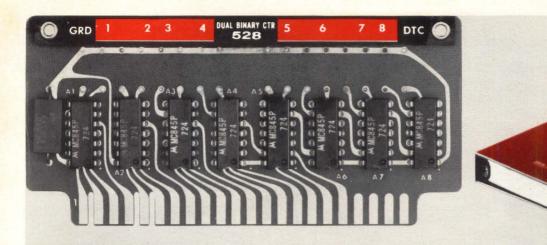

### FREE FROM DATA TECHNOLOGY. A 387 PAGE I.C. LOGIC MODULE APPLICATIONS AND DESIGN MANUAL.

Only Data Technology . . . the company that has shipped more integrated circuit logic cards to system manufacturers than any other supplier could make such an offer.\* •

With more than half a million dollars worth of cards and chassis in stock or production, Data Technology is in a unique position to provide:

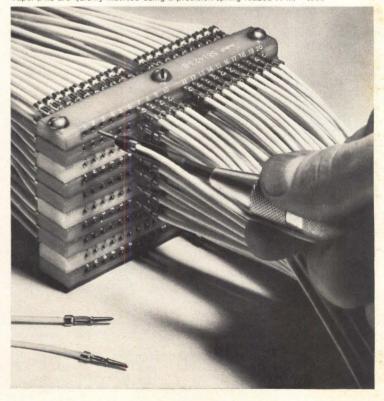

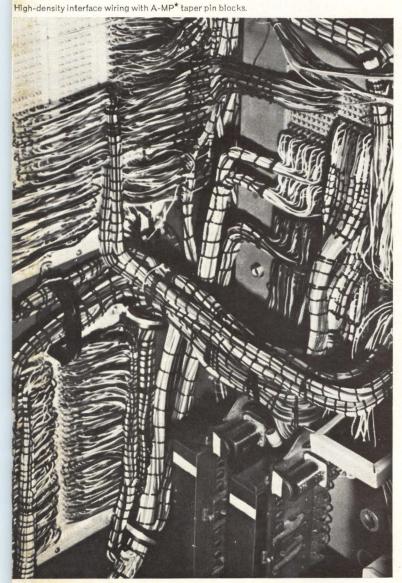

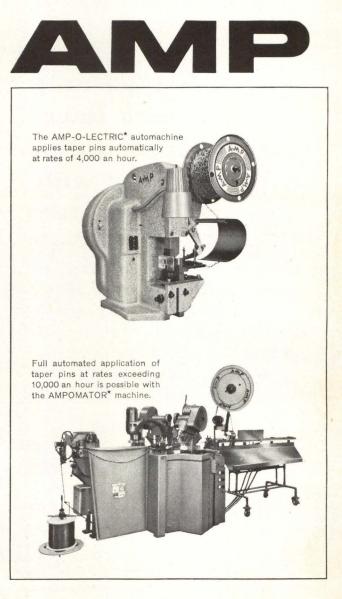

**5 types of connectors and wiring**—wire wrap, termi-point, solder-tab, taper pin, and machine wrappable back planes. Our own numerically controlled wiring machine allows us to provide complete and economical wire services.

Ease of application – Data Technology has the industry's most complete line. Over 100 types including DTL-TTL compatible, NAND/NOR logic, and dual-in-line ICs. Operation from dc to 20 MHz, between 0 and 70°C. ■

**Price**-You get more for your money with Data Technology logic cards. We include as standard features, color coded test points, unique keying, laminated power buss, distribution system, decals and design assistance.

**Delivery** – Off the shelf for almost every item with fast, complete design assistance. ■

\*Data Technology's application and design manual... the most complete of this type ever printed... is free to all users. Ask our representative, listed below, to show you **his** copy. To get a copy for evaluation contact us or circle the appropriate reader service card number. For general catalog information circle the companion number.

Data Technology Corporation, 2370 Charleston Road, Mountain View, California 94041. (415) 321-0551. TWX (415) 969-9150.

Eastern Region Applications Office: Geo. Glen, 8934 Victoria Blvd., Springfield, Va. (703) 461-9025

Alabama Huntsville – Gentry Associates, (205) 534-9771 Arizona Phoenix – T. Louis Snitzer Co., (602) 273-1673 California Del Mar –T. Louis Snitzer Co., (714) 454-2191 Los Angeles – T. Louis Snitzer Co., (213) 938-2073 Palo Alto – T. Louis Snitzer Co., (415) 968-8304 Colorado Englewood – Aztec Enterprises, (303) 761-0101 Connecticut New Haven – H. J. Schuft Co., (202) 865-1365 Florida Orlando – Gentry Associates, (305) 424-0730 St. Petersburg – Gentry Associates, (813) 867-7820 Eau Gallie – Gentry Associates, (305) 773-3411 Georgia Atlanta – Gentry Associates, (404) 233-3816 Illinois Chicago – H. H. Sales, (312) 642-4464 Kansas Olathe (Kansas City) – Technical Representatives, Inc., (913) 782-3775 Wichita – Technical Representatives, Inc., (316) 682-4140 Louisiana Slidell (New Orleans area) – Noakes Engineering, (504) 288-7122 Maryland Kensington – Electronic Marketing Assoc., (301) 946-0300 Massachusetts Newtonville – H. J. Schuft Co., (617) 527-5304 Michigan Detroit – Technitron, Inc., (313) 838-7324 New Mexico Albuquerque – Aztec Enterprises, (505) 268-6421 New York Great Neck – Harvey J. Krasner Assoc., Inc., (516) 487-0690 Palmyra – KLM Associates, (315) 597-9776 No. Syracuse – KLM Associates, (315) 458-6214 Whitesboro – KLM Associates, (315) 736-2450 North Carolina Jamestown – Gentry Assoc., (919) 454-1919 Ohio Dayton – Technitron, Inc., (513) 298-9964 North Olmsted – Technitron, Inc., (216) 734-0960 Pennsylvania Pittsburgh – Technitron, Inc., (412) 371-1231 Philadelphia – Electronic Marketing Assoc., (215) 248-5050 Texas Houston – Noakes Engineering, (713) 529-6213 Irving – (Dallas area), Noakes Engineering, (214) 255-0441 Wash-Ington Seattle – Harry Levinson Co., (206) 226-7800 Publisher and Editor ROBERT BROTHERSTON

Associate Publisher TONY SALTALAMACCHIA

Managing Editor WILLIAM G. KEYWORTH

Editorial Advisers RICHARD AHRONS ELI ANFENGER JAMES R. BRIGHT GERHARD L. HOLLANDER GILBERT P. HYATT BERNARD M. GORDON WALDRON S. MACDONALD ROBERT S. SENATOR HAROLD H. SEWARD

> Contributing Editors T. PAUL BOTHWELL A. S. BUCHMAN M. P. de REGT RUDOLPH J. KADLEC ROBERT P. FORAN RICHARD B. LAWRANCE WALTER A. LEVY H. S. MIILLER MADELINE SULLIVAN

Washington Editor HAROLD V. SEMLING, JR.

> Art Director JAMES FLORA

Production Manager TERRY ARMENTI

JOHN BROTHERSTON

Editorial Ass't. PRISCILLA HANNON

> Adv. Prod. JOAN WASIUK

Circ. Mgr. ALMA BROTHERSTON

Vice Pres.-Sales LINDSAY H. CALDWELL

Editorial & Executive Offices Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1968 by Computer Design Publishing Corporation. Accepted as controlled circulation publication at Post Office at Chicago, Illinois. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS – FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Winchester, Mass. 01890. Subscription rate to annualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 40,000

### COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS

#### **FEATURES**

### 28 FUNDAMENTALS OF TIME SHARED COMPUTERS (Continued)

"Time Sharing" is presented in its most general sense as any application of a computer system that involves simultaneous users. Concepts and equipment of time-shared systems are defined and described and criteria for system configurations are given in terms of application requirements.

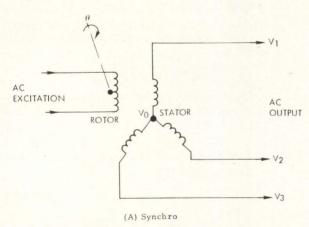

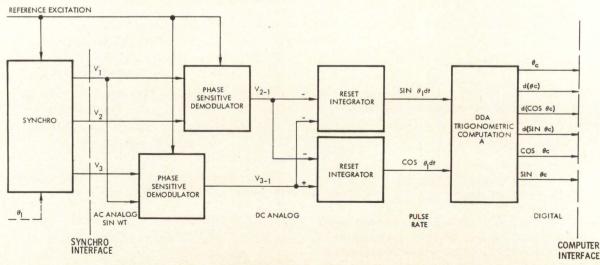

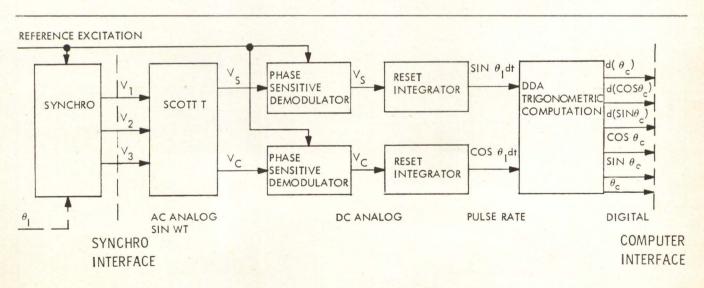

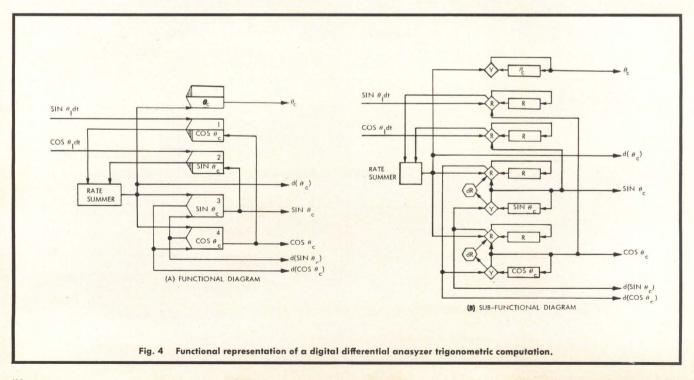

### 48 SOLID-STATE SYNCHRO-TO-DIGITAL CONVERTER

Placing the accuracy and speed burden for S-D conversion on the digital equipment minimizes the analog equipment and enhances system performance.

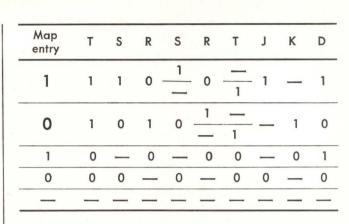

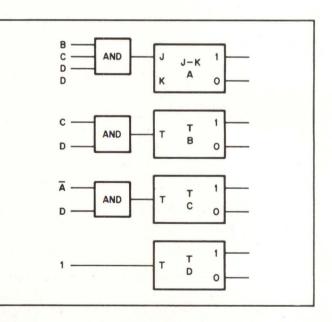

### 54 A ONE MAP METHOD FOR OBTAINING FLIP FLOP INPUT EXPRESSIONS

Most methods for obtaining flip flop input expressions require a Karnaugh map for each type of flip flop considered. This article presents a method that requires only one map, regardless of the number of different types of flip flops to be investigated.

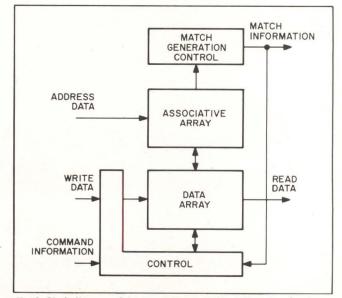

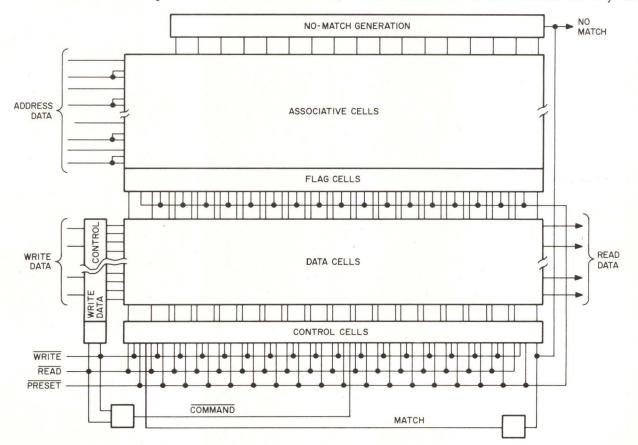

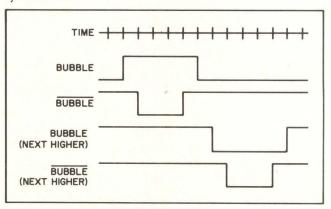

#### 60 A PROPOSED ASSOCIATIVE PUSH DOWN MEMORY

Small, high-speed semiconductor memories designed to store the most recently-used information contained in the main memory can increase the effective speed of computing systems.

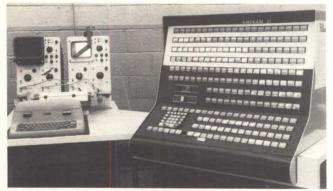

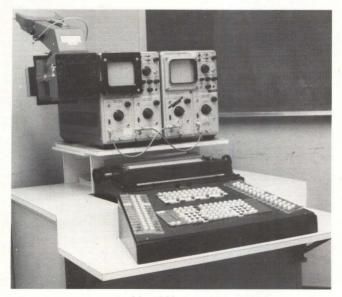

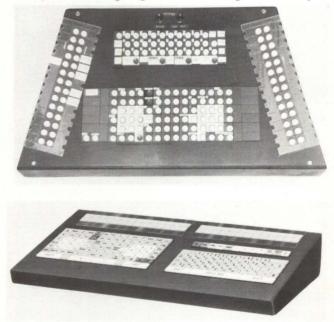

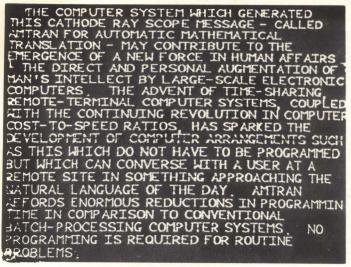

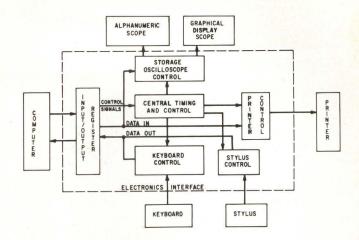

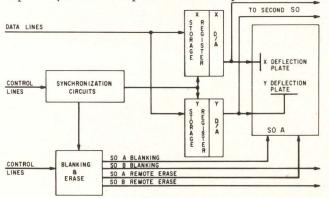

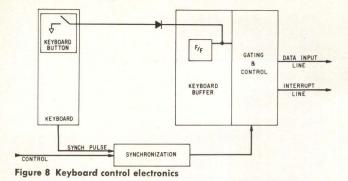

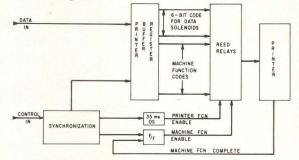

### 68 THE ANTRAM INPUT-OUTPUT TERMINAL

Operating simplicity, minimum cost, sophisticated programming and graphical display capability are achieved in the design of an input-output terminal.

#### DEPARTMENTS

- **20 INDUSTRY NEWS**

- 76 NEW PRODUCTS

#### **86 NEW LITERATURE**

| Reader subscription | card | opposite page 1  |

|---------------------|------|------------------|

| Reader service card |      | opposite page 88 |

### **NEW! Designed** for the Computer O.E.M.

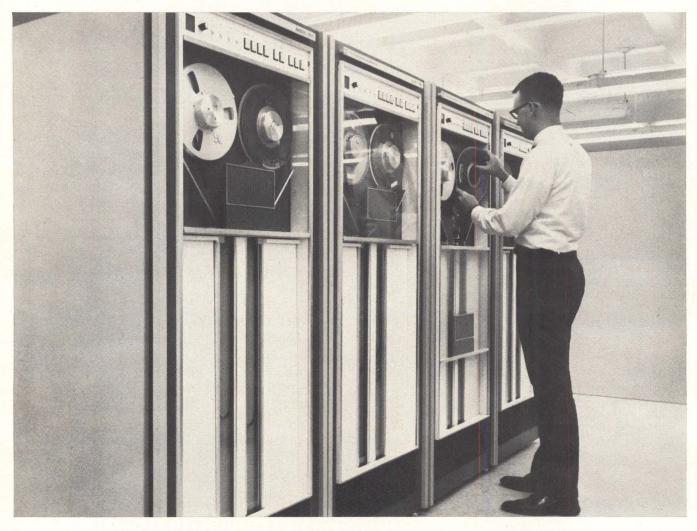

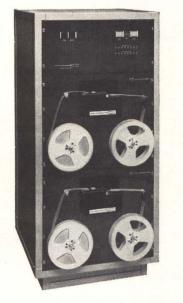

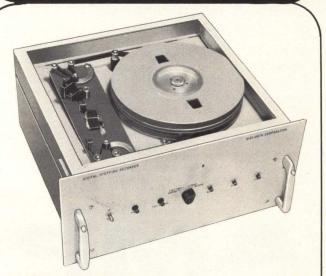

A simple, reliable and economical computer tape transport that meets the critical requirements of the original equipment manufacturer. It's called the Model 959 Computer Tape Transport, and it's made by Texas Instruments.

Advanced design is the reason why. You get a machine that handles from 200 to 800 bpi at 60 to 120 ips, yet has remarkable simplicity. Permanent magnet reel motors and a printed circuit capstan motor eliminate gears, belts, pulleys, clutches, and other cumbersome mechanical systems. No pinch rollers are used, and tape is automatically loaded without moving the read/write head.

The size and complexity of electronic circuitry has been reduced through the use of the latest linear and digital integrated circuits with advanced silicon power transistors.

Improve your price/performance ratio with the new TI Model 959 Computer Tape Transport. Lower maintenance costs improve system quality with a transport designed for the original equipment manufacturer. For more information, contact your TI representative or Texas Instruments, Industrial Products Division, P. O. Box 66027, Houston, Texas 77006 (713-227-3611).

See the Model 959 Computer Tape Transport at the IEEE - Booths 2F08-20

### TEXAS INSTRUMENTS

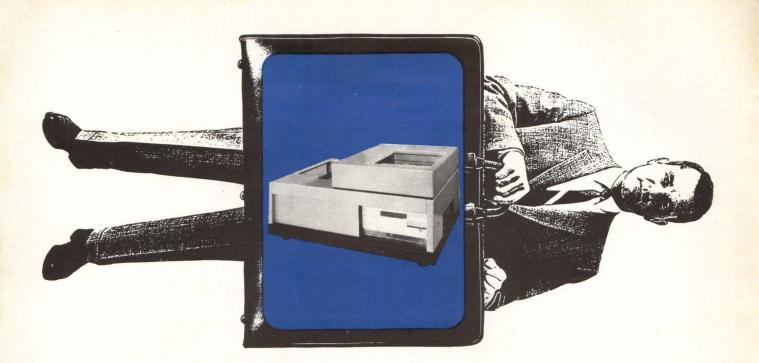

### Computers are big, expensive components. Bit for bit, ounce for ounce, some are a bargain.

When you tie another man's computer into your product, you're staking your reputation on his equipment. Your reputation is worth shopping for. Naturally you want the most for your dollar. Like reliability at 130° F. Hewlett-Packard computers are designed for rugged dependability—as well as high performance. All things considered, they're something of a bargain.

> We've been selling quality instruments to original equipment manufacturers for years. We know the problems. So we back our computers with excellent training, complete service and our traditional warranty. We'll train your people or your customer's people in maintaining the computer and in using the software.

> We supply plug-in I/O interfaces and the software drivers for peripheral devices. You buy only the equipment you need for interfacing your system. And you tie it in with minimum engineering time because both hardware and software are operational and fully documented.

> The 2115A pictured here measures 16% "x 12"x 24%" (its power supply is a bit smaller). It uses 16-bit words, operates with 4K or 8K memory, and has a two microsecond cycle time. Price: \$14,500.

For more information about a computer that will live up to your reputation, call your local HP field engineer. Or write Hewlett-Packard, Palo Alto, California 94304; Europe: 54 Route des Acacias, Geneva.

CIRCLE NO. 3 ON INQUIRY CARD

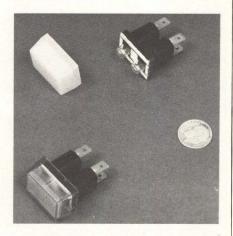

### Here's why you should now be using Datavue\* Indicator Tubes

CK1904—Interchangeable with B59956 and NL809.

.....

8422—Interchangeable with B5991 and NL8422.

CK1903—Interchangeable with B5992 and NL5992.

CK1901—Interchangeable with B5016 and NL5016; CK1902— Interchangeable with B5032, NL5032, B50911 and NL50911.

8754—Also available with right- and/or lefthand decimal points; Interchangeable with NL840/8754. Decimal-point types interchangeable with NL841, 842, 848.

These indicator tubes—just a few of Raytheon's wide selection—offer you advantages in design, economy and performance. For example:

You don't need to revise designs. Raytheon's Datavue round and rectangular end-view tubes conform to EIA ratings—interchange with other brands. And Raytheon also offers you a selection of side-view types and "specials" with up to 12 characters,  $\pm$  signs, symbols, etc., to your specifications.

You can buy them at low cost. All Datavue Indicator Tubes are priced

8421—Interchangeable with B5092 and NL8421; 8037—Interchangeable with B5031 and NL8037. Also available: 6844A.

competitively—or lower. Most sideview types, for example, cost less than \$5 each in lots of 500 or more.

Reliably trouble-free readouts. All Datavue characters are fully formed —not segmented. The fully formed characters are brightly displayed and easy to read—at distances up to 30 feet.

They last for years. They're made better because of Raytheon's experience—40 years of producing more than 100,000,000 cold cathode gasfilled tubes with carefully controlled electrical performance. Ultra-long-

CK1900 (used with CK8650, CK1905, CK1906); CK1907 (used with 8754)—Interchangeable with NL843.

life types, for example, have dynamic life expectances of 200,000 hours or more.

They're readily available—in sample and production quantities. For samples, prices, or technical information, call your Raytheon regional sales office or distributor. Or write: Raytheon Company, Industrial Components Operation, Quincy, Mass. 02169. \*Trademark of Raytheon Company

The Peripheral People announce the ultimate in reading reliabilitythe D4 punched card reader. It's great for companies that hate the sight of a maintenance man.

> NCR knows more about electro-mechanics than anyone. That's why the economical D4 300 cpm reader keeps up the good work longer, with minimal maintenance. Still we know that sooner or later a card will stick, so we made the card track fully accessible—an operator can free a jam in seconds. If you should ever need service (after an earthquake, fire or office party), the D4's modular construction makes it fast and easy. For information on speedy delivery, contact the Peripheral People today.

THE NATIONAL CASH REGISTER COMPANY . INDUSTRIAL PRODUCTS DIVISION . DAYTON, OHIO 45409 CIRCLE NO. 5 ON INQUIRY CARD

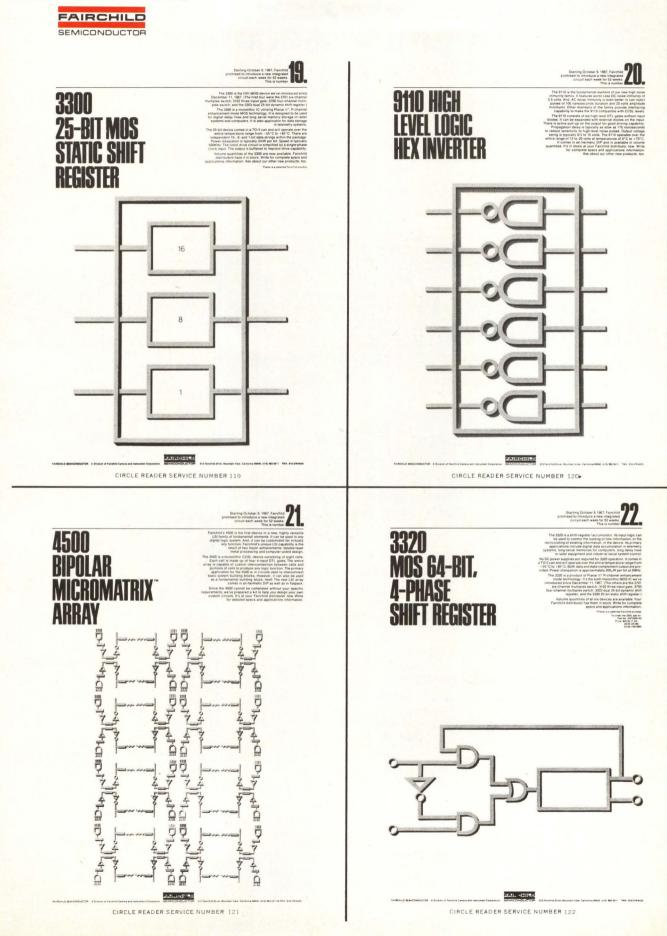

# Do you want to go LSI now?

If you really want LSI now, grab the next plane to Mountain View. (It lands in San Francisco.) It's the quickest, least expensive way to get LSI into your system.

Plan to bring along your blueprints. And be ready to answer a lot of questions. We'll need to know what you have in mind for sub-systems, functions and specs. And, don't be surprised when we ask "why" a couple of times. It's all part of Fairchild's systems approach to complex circuitry.

We'll take your requirements and match them against our family of fundamental building blocks. We've got LSIs (and MSIs) that work in any digital logic system. The most advanced circuitry on the market. Offspring of computer-aided design and double-layer metal technology. And, they're all so versatile, we can probably give you a counter that has a dozen other applications in your system.

But, you'll only be able to build half a system with standard building blocks. To finish the job, you'll need interface devices to tie the whole thing together. And, here's where Fairchild can really save you time and money. We don't have to custom design each LSI interface circuit. We use Micromatrix<sup>™</sup>-a unique cellular array that's completed when we add your specific interconnection pattern. Your specs customize the entire array for your system.

Of course, there's a lot more to the story. But, you ought to hear it in person. Just call your Fairchild salesman. He knows the flight schedule to San Francisco.

# Or do you want to think about it?

We've got an LSI design kit. It's based on our new 4500 Bipolar Micromatrix Array-the first device in a highly versatile LSI family. The 4500 is an eight-cell array that can be customized for virtually any function. All it needs is your interconnection pattern. You can determine the pattern by designing your own Micromatrix array with our kit. You can buy a kit from your Fairchild distributor for TALLAT. about \$100. And, in a couple of months, we'll see you in Mountain View. IRCHI SEMICONDUCTOR

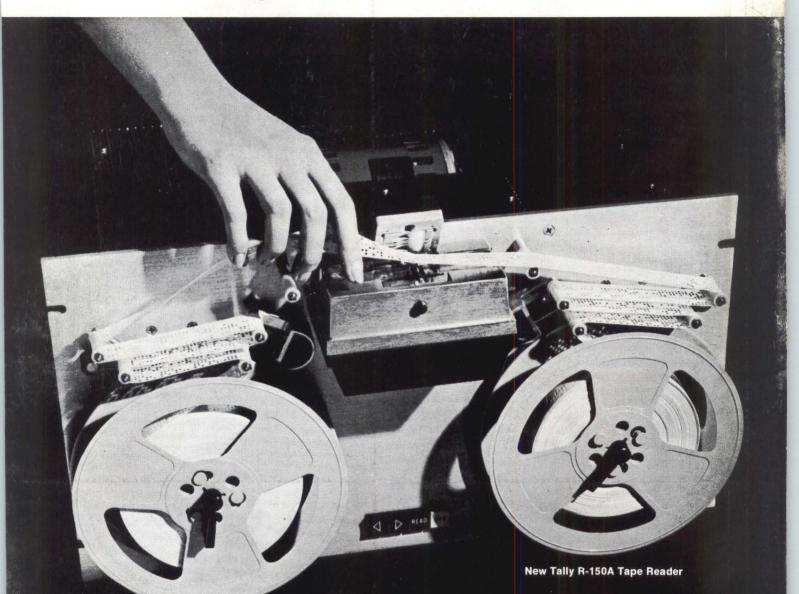

### Cheap mass storage for small computers and how to get the most out of it

For some people the only limitation of the small computer is the price of the extra memory. What's needed is low-cost mass storage, and lots of it. For filing data. For quick and convenient program manipulation.

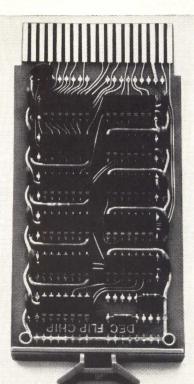

DIGITAL, the leader in small computers, has a low-cost disc and unique magnetic tape unit tailored for the small computer. Now, new spftware is available to take even better advantage of this low-cost memory.

DEC disc adds 32,768 words of memory for \$6,000. Additional expander discs (up to 3) can be added at \$3,000 each. That means a total of 131,072 words of disc memory for \$15,000. A full scale PDP-8/S computer with 36,864 twelve bit words

of memory, for example (4k core plus disc), costs \$18,500. DECtape, Digital's unique fixed address magnetic tape system, provides over 200,000 words of storage on a  $3\frac{1}{2}$ -inch reel. It's the lowest cost mass storage available anywhere. You can edit and debug programs on line. Then you can put your programs in your pocket and take them away until you want them again.

New keyboard monitor software all but eliminates the laborious use of paper tape and cards. You edit from the keyboard, compile from the keyboard, assemble, load, store, debug all from the keyboard. What might have been hours or days in getting the computer ready for use, is now just minutes.

Available now. PDP-8/S off-the-shelf. PDP-8 in one month. PDP-8/I in the spring. DECdisc and DECtape immediately available. Send for our new Small Computer Handbook. It's free.

NOITZ

DIGITAL EQUIPMENT CORPORATION, Maynard, Massachusetts 01754. Telephone: (617) 897-8821 • Cambridge, Mass. • New Haven • Washington, D.C. • Parsippany, N.J. • Princeton, N.J. • Rochester, N.Y. • Long Island, N.Y. • Philadelphia • Huntsville • Pittsburgh • Chicago • Derver • Ann Arbor • Houston • Albuquerque • Los Angeles • Palo Alto • Seattle. INTERNATIONAL, Careton Place and Toronto, Ont. • Montreal, Quebec • Reading and Manchester, England • Paris, France • Munich and Cologne, Germany • Oslo, Norway • Stockholm, Sweden • Sydney and West Perth, Australia • Modules distributed also through Allied Radio

### 4800 bps has grown up!

MODEM 4400/48

### **MODEM 4400/48**

No more costly delays in acquiring and operating over highly conditioned transmission lines. MODEM 4400/48 by-passes the troublesome bandwidth on any line, conditioned or not, just like our 2400 bps modem. Milgo's unique\* narrow-band concept allows transmission on unequalized voice grade Type 3002 lines, the lowest cost lines available. The cost per unit — much less than other 4800 bps data sets!

Let us show you how 4800 bps has grown up. Send for data sheets and information on nearby users.

Milgo Electronic Corporation 7620 N. W. 36th Avenue, Miami, Florida 33147 \*patent applied for

CIRCLE NO. 8 ON INQUIRY CARD

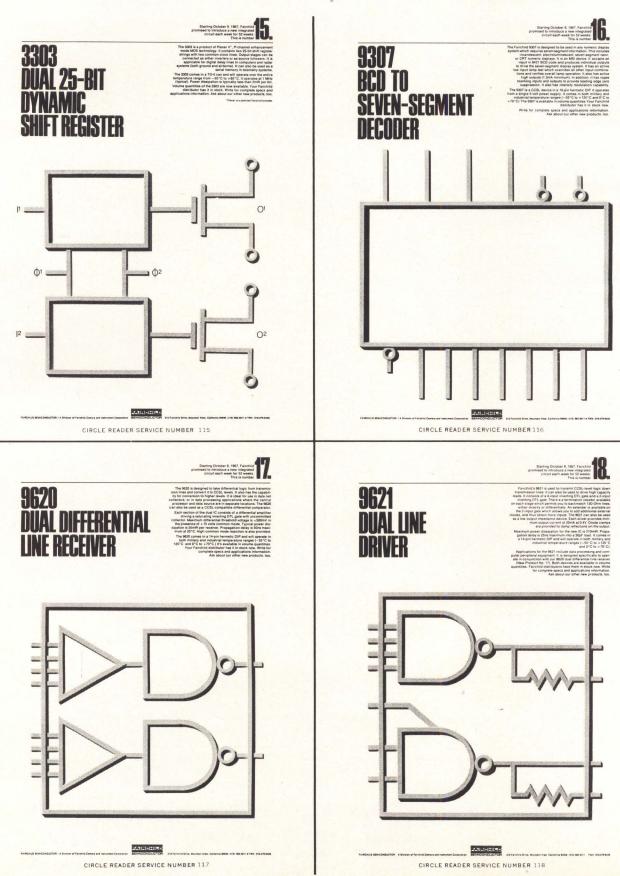

## **RECAP**:

Fairchild is introducing a new integrated circuit every week. The last two months look like this.

13

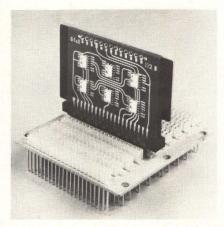

### Can a coincident-current memory system cycle faster than 1 microsecond?

#### Yes! And this completely new 3-wire 3-D design couples high speed with ease of maintenance in unique modular construction featuring plug-in integrated circuits.

An absolute "show-stopper" at the last Fall Joint Computer Conference, RCA's new integrated circuit system offers these outstanding features:

Temperature stable; 0°C to 50°C.

High Level TTL logic—excellent noise immunity, exceptional reliability, low power requirements.

Full range of options for wide flexibility: parity check circuit—sequential address register—memory retention—read, modify, write mode-voltage margin switch—special interfacing for most requirements—exerciser for self checking.

Available with short delivery schedules, RCA's new 3-wire 3-D coincident current core memory systems are designed with capacities of 4K x 8 to 32K x 72.

For complete details, contact your RCA Field Representative. Or call Marketing Department (617-444-7200), RCA Memory Products Division, Needham Heights, Mass. 02194. For Data Sheet and Application Note, write Commercial Engineering Section 0000. RCA Electronic Components and Devices, Harrison, N.J. 07029. RCA 4K x 20 system with integral power supply measures: 51/4"H, 19"W, 20"D.

CIRCLE NO. 9 ON INQUIRY CARD

Printed in U.S.A.

### How do you gruntle the buyer of memory stacks?

### (Take a powder and control it all the way).

The man who buys memory stacks (or planes or just cores) knows that a myriad of tiny variables which affect performance can pass right through the tightest spec. It's nobody's fault, but still it leaves the buyer disgruntled.

How to gruntle him? Well, this is what we do at Ferroxcube. We control the entire process from formulation of the powder for the cores to the planes or stacks that go out the door. To the naked eye

QC procedure. But some of it goes deeper. It's the kind of control you associate with a veteran airline pilot whose experience amounts prototype you approved. almost to intuition. As pioneers in ferrites and core memory compo- stacks, talk with the people who nents, we have people like that in control at every vital stage of man- a conversation piece, a sheaf of ufacture.

This is one reason why Ferrox- Write for it today. cube can design and build to ex-acting requirements (example: Ferroxcube 😪 military stacks that exceed the en- Saugerties, New York

much of this looks like textbook vironmental requirements of MIL-E-16400 and MIL-E-5400). And it's the main reason why every production unit performs like the

> If you specify cores, planes or pioneered ferrite technology. As technical literature awaits you.

### 1,000 Steps per second/800 bits per inch! and this elegant Incremental Recorder is SYSTEM/360 compatible too.

#### Born to Win

This new incremental/ continuous tape recorder was born to be a winner. While last year's tired entrees are busily being "hyped" up to meet the 9 channel 800 bpi requirement, this

simple new model from PERIPHERAL EQUIPMENT COR-PORATION breezes along in preconceived IBM SYSTEM/360 compatibility.

You see, PEC offers a single capstan velocity D.C. servo drive system with optical accuracy. This unusually wide bandwidth, low inertia drive employs printed circuit motors and single

shaft coupling. That's how the truly incremental rates of 350, 500, and 700 steps/second are easily met, with 1,000 steps/ second an available option.

You can say goodbye to those obsolete tired old stepping motor types of incremental recorders that are self-limiting in speed and accuracy.

#### The Taming of the Skew

This elegant PEC recorder has conquered skew exactly like the very expensive computer tape transports.

Do you benefit? You bet you do because you are guaranteed that a magnetic tape written on an inexpensive PEC recorder will read perfectly into your computer transport.

PEC tames the skew in three important ways. With a single capstan drive that eliminates pinch rollers (and skew) ... with

### **Elegance in Emptyness**

It's the little things that PEC has left out that count. (Those troublesome little things like gear trains, pinch rollers, and other mechanical linkages.) Using IC logic, we have figured out how to

> design "expensive" circuitry inexpensively. You are the winner. Both on initial cost and continuing maintenance.

> Continuous, Too

Not only can this r e v o l u t i o n a r y recorder prepare S Y S T E M / 3 6 0 compatible tapes at packing densities of 200, 556, and 800 bits per inch *incrementally*, but it can

also operate as a continuous recorder or reproducer at any speed up to 25 inches per second. The price saving over the big machines is considerable...the performance is even better.

#### Design PEC in

Data acquisition...computer peripheral ... integrated circuit testers ... digital plotters ... pulse height analyzers. If you are designing any of these systems the new PEC incremental/ continuous recorder will make your job easier. Phone or write us today.

an optical capstan position encoder which precisely positions data bits...and with electronic deskewing at 800 bpi (just like the big boys). A feature which is possible because PEC writes on the fly! And we even guide tape with IBM configuration and tape tension.

#### Racing Through the Gap

Another time saving advantage. You can race through the inter-block gap in 60 ms (50 ms for SYSTEM/360 compatibility). The gap time is independent of data density and doesn't cost you a penny more . . . compliments of our wideband servo drive.

PERIPHERAL EQUIPMENT CORPORATION

9551 Irondale Avenue Chatsworth, California 91311 (213) 882-0030

### THIS BOOKLET CONTAINS COMPLETE DATA, PLUS "HOW-TO-USE" IDEAS FOR THE WORLD'S MOST ADVANCED I/C LOGIC FAMILY!

### **IT'S YOURS FOR THE ASKING!**

Most data brochures contain specification sheets for all of the devices in the line. So does this one — for 56 MECL\* II integrated circuits (29 different circuit designs). But, it also includes applications information, right on the data sheet, for each circuit. And, that's not all . . . there's 10-pages devoted solely to the unique and interesting design philosophy of emitter-coupled logic. Then, to make it the highly-practical design tool that it is, this new MECL Data Brochure is designed for perpetual updating . . . New circuit information can be added easily; and, there's room for the MECL 300/350 series brochures that are currently in use.

Yes, the MECL Data Brochure is Extraordinary in many ways ... but then, so is the MECL line of integrated logic circuits. We felt that the world's fastest, most-advanced full complement line of digital integrated circuits deserved more than just ordinary technical data treatment ... so, we prepared this special approach for you.

It's Yours for the Asking! Just drop us a line on your company letterhead, at P.O. Box 955, Phoenix, Arizona 85001.

\*Trademark of Motorola Inc.

-where the priceless ingredient is care!

MOTOROLA Semiconductors

### This new memory may not do everything better. But it does everything. And it takes up less space doing it.

All together, the specs on our medium capacity memory systems are unsurpassed. Some systems may have slightly faster cycle times, but they don't offer speeds of 650 nanoseconds in a unit that's so small you'll be surprised to find a power supply and tester also included—just like the I.C. electronics and 2½ D magnetics. All are contained in only 2% cubic feet (7"x19"x21.5").

Capacities range up to 295,000 bits per unit. Multiple module capability is available for larger capacity requirements.

Compact as it is, the design doesn't get in the way of maintenance. The systems are extremely easy to repair. Stacks, electronics and tester are on plug-in modules—all are accessible and slip in and out easily.

Information on both the Nanomemory 2650 (650 nsecs cycle time) and Nanomemory 2900 (900 nsecs) are in our compact (8½x11") brochure. Write for Litpak 200.

12621 Chadron Avenue, Hawthorne, California 90250 (213) 772-5201

### **Programmers/Analysts**

### If you're interested in working five years ahead of the times, learn about IBM in Washington, D.C. area.

S

A

### We're working at state-of-the-art levels—and we need programmers and analysts now.

Our Federal Systems Division is involved in a series of real-time projects for the Government that are about as advanced as anything in the field of computer technology today: trajectory analysis, orbit prediction, multi-programming, multiple-access concepts, acoustic instrumentation. And most of this work is being done using the latest computers and peripheral equipment available.

Our positions are located in and around Washington, D.C. from the convenient downtown area to the gracious countryside near Gaithersburg, Maryland, 15 miles northwest of the nation's capital. Housing and recreational facilities are plentiful. And IBM's generous benefits program is company paid.

### Are you one of these people?

We need programmers and analysts with experience in one of two basic areas: information-handling systems and scientific-engineering programming.

Ideally, you should have a Bachelor's degree in Mathematics, Physics, Engineering, Economics, or Statistics. (Equivalent experience in some instances is acceptable.) You should have at least one year's experience.

### **Contact IBM today**

If you're interested in one of the hottest careers going in computer technology, we want to talk to you. Send a brief resume to: Mr. J. F. Ryan, IBM Corporation, Department SC6-M, 18100 Frederick Pike, Gaithersburg, Md. 20760. It could be the most important resume you've ever written.

An Equal Opportunity Employer

**NEWSPAPER TYPESETTING 95% COMPUTER CONTROLLED** — The Boston Globe has completed installation of a million dollar computer system to automate hot metal typesetting and photocomposition.

The newspaper installed its second Honeywell 1200 computer, making up the nucleus of what is said to be "the most advanced EDP system in the newspaper field." Both computers have been connected to 20 photo-electric keyboards and two teletypewriters to control printing functions, while other applications are being directed toward financial management, according to Robert J. Heyd, Globe EPD manager.

The keyboards are in the newspaper's composing room and are used to transmit advertising copy and news stories to the computers for automatic formatting and justification. The computers, following the typists' instructions, select the proper type style, size and column width, and handle hyphenation. The copy is then immediately transmitted on a coded perforated paper tape to any of 17 linecasting and photocomposition machines that set the type.

The teletype units, used exclusively for program control, indicate whether the copy was processed and which linecasting machine received it. They also can be used for sending messages from the composing room to the computer.

The most important feature of the Globe's system is that it eliminates the need for entering information into the computers via punched paper tape. Other newspapers using computers must generate a paper tape before the computer can select the type style and font.

Right now, about half the keyboards are running full time. At peak operation, Mr. Heyd said, the paper expects to average 4,000 lines an hour, or about 95 per cent of the total typesetting and photocomposition done by the Globe.

NEWS

**1968 DATA PROCESSING SER-VICES** — "It is estimated that in 1968 the data processing service center industry in the United States will serve more than 100,000 customers resulting in revenues approaching \$800,000,000, while providing jobs for approximately 30,000 people."

These projections, made by Jerome L. Dreyer, executive vice president of the Association of Data Processing Service Organizations, (ADAPSO), are based on a recently prepared economic study of the service center industry which was submitted to the FCC inquiry into the interdependence of the computer-common-communication carrier industries as background information.

"The figures cited," Mr. Dreyer said, "represent an estimated 20% increase in revenue and customers over 1967."

"The development of time-sharing communication - computer systems has opened many new markets. Although no definite information is available, it has been estimated that time-shared systems are presently the most rapidly growing segment of the data-processing service industry," he concluded.

**1967 COMPUTER SHIPMENTS ZOOM TO ALMOST \$6 BILLION** — The value of new computers and related peripheral equipment shipped by American manufacturers to customer locations, both in the United States and overseas, was approximately \$5.9 billion in calendar 1967. This represents an impressive 61.2% increase over the \$3.66 billion shipped in 1966. When the value of special-purpose machines, peripherals, supporting services, and supplies are included, the total size of the computer industry comes to more than \$9 billion for 1967. For 1968, computer shipments are predicted to be about \$6.5 billion, according to the results of a study just completed by the International Data Corp.

"The huge increase in shipments last year reflects the second of the two key step-up years in the sevenyear cycle of a computer generation," explains a company official.

"During the next three or four years" he claims, "we can expect a plateauing in the level of computer shipments. Manufacturers will smooth out their present product lines and introduce less expensive equipment that will give them a downward expansion of the marketplace. There was a similar period, naturally at much lower shipment levels, during the period of secondgeneration computer shipments.

IDC estimates that the \$5.9 billion in computer shipments represents 18,700 computers shipped during 1967, and brings the worldwide population of installed computers, made by American-based companies, to 57,600, up 41.9% over the 40,600 machines installed at the end of 1966.

As of December 31, 1967, the company estimates that the value of computers installed in the United States was \$13.6 billion, consisting of some 40,100 general-purpose computer systems. Outside the U. S., the value of computers manufactured by American companies either at plants in the U. S. or at foreign-operated plants, was \$5.3 billion, with 17,500 computers installed.

### A word to the do-it-yourself module builder:

### Don't.

Buy our J Series modules instead.

The J Series is our new family of general purpose, all integrated circuit logic modules. Their performance almost matches that of our famous T Series modules,

These will cost you less

but they cost about 25% less. They're made to the same dimensions as the T Series, with the same 52 pin connectors, so they're physically interchangeable. We make them for our own seismic recorder systems, so they're rugged and reliable. Now, as of January, you can buy them (complete with mounting hardware, racks and power supplies, if you wish) in any of 25 different functions.

And save yourself the time and cost of making your own: designing, assembling, testing, new procedures, new equipment, new personnel, additional training, to say nothing of the added paper work.

If you're building systems, you must have better things to do than go into the module assembly business. Such as reading our J Series catalog.

### WHEN WE SAY QUICK...

WE MEAN

### IN JUST 7 DAYS WE DELIVER POWER SUPPLIES

### REGULATED AC-TO-DC SOLID STATE POWER SUPPLIES

Frequency:  $50-60Hz \square$  Regulation:  $\pm$  (.003% + 1mv), line and load combined  $\square$  Ripple & noise: less than 1mv, p-p; 250 $\mu$ v rms Current limit: approx. 105% of full-load rating with fold-back  $\square$  Semiconductors: all silicon  $\square$  Panel height:  $5\frac{1}{4}$ " and 7".

#### TYPICAL PRICES:

6 volt, 21.3 amp, narrow-range, half-rack \$350 12 volt, 52.5 amp, narrow-range, full-rack \$510 33 volt, 48.0 amp, narrow-range, full-rack \$655

For catalogue describing the complete line of Chalco power supplies write, call or telegraph:

Electronic-Electromechanical Systems and Products 15126 SO. BROADWAY – GARDENA, CALIF. • FA 1-0121 (213) TWX 213-327-0167

CIRCLE NO. 15 ON INQUIRY CARD

**PLANS FOR EXPANDED SERVICE ACTIVITY** — Sperry Rand Corporation's Univac Division plans a major expansion in computing services through a nationwide network of data processing facilities, according to a recent announcement.

Univac has formed a new Information Services Division, headquartered in Philadelphia, that will utilize an integrated system of nationally deployed computers, communication lines, and terminals. The new division is a restructuring of Univac's Data Processing Centers Division, established in 1964, and represents a major expansion of its charter and service activities.

8\*\*\*\*\*\*

HIGH-SPEED MAGNETIC TAPE DATA TRANSMISSION SYSTEM — Communitype corporation has introduced a 6,000-character-per-minute magnetic tape transmission system designed to provide economical offline data receiving and sending facilities for a computer operation, and to enable economical, high-speed computer magnetic tape-to-tape data communication over telephone lines.

The system will receive and batch magnetic tape data and translate it to computer-compatible codes recorded on computer-compatible magnetic tape. It also will send computer-prepared data at 1,200 bits per second to magnetic tape systems located at branch office data processing centers anywhere in the world.

Batching of data at the computer location not only permits more efficent use of the computer but also helps keep the data communication lines open throughout the working day, thus providing a real time environment with batch-processing economy.

The device reads and writes on computer-compatible, 7-channel tapes at 556 bits per inch density. Its  $\frac{1}{2}$ -inch, IBM-type reels have a capacity of 14 million characters at 556 bpi. A 9-channel, 800 bpi version, designed for use with the new IBM-360 computer series, is presently under development by the company and will soon be made available.

**NEW GOLD CROSSOVERS INTER-CONNECT INTEGRATED CIR-CUITS** — A reliable new structure for interconnecting integrated circuits — an air-insulated, beam-lead crossover — has been invented by Bell Telephone Laboratories. The crossover is said to have a higher

breakdown voltage, greater reliability, and lower capacitance than conventional interconnection structures.

The new structure has been used successfull both in experimental integrated circuit chips and in larger, more complex substrates. Such circuits and substrates are expected to be used broadly, in electronic switching systems, telephone sets, and many other types of telephone equipment.

Where two conductors must cross, a gold beam lead is formed into a 10-micron-high "microbridge" over the lower conductor. The two conducting paths are separated by a thin layer of zirconium oxide and an air gap. This dual dielectric insulation can withstand over 200 volts, is immune to "pinhole shorts" through the dielectric, and has very low capacitance.

In conventional interconnection structures, the top conductor is deposited directly on a dielectric (usually silicon dioxide) that separates the crossing conductors. Because the top conductor is formed in initimate contact with the dielectric, any pinholes in the dielectric can cause short circuits between the two conducting paths.

In the new structure, however, any pinholes in the zirconium layer are harmless, because the top conductor is plated on top of a spacer that is later etched away. The resulting air gap insulates the top conductor from the zirconium layer, which is heated to form zirconium oxide, the other-half of the dual insulation.

The new crossover will not fail even if the top conductor is pushed down to the bottom level, because the zirconium oxide alone can withstand 100 volts. The top beam lead will spring back to its original position as soon as the extennal force is removed.

The crossover is formed by depositing layers of zirconium and copper over the bottom conductor, and then plating the gold beam lead on top of the copper. Next the copper is etched away to form the air gap, and the whole structure is heated to 350° centigrade to convert the zirconium layer into zirconium oxide. The last step does not affect the rest of the integrated circuit, because silicon does not oxidize at this temperature.

The new crossovers have been fabricated on experimental integrated circuits with high initial yields. Hundreds of the crossovers have been aged in room air at 350° centigrade for over 1000 hours with no apparent change.

# QUICK...

WE MEAN

IN JUST **7** DAYS WE DELIVER TAPE READERS

### HIGH SPEED PHOTO-ELECTRIC TAPE READERS

Occupies only  $3\frac{1}{2}$ " of panel space  $\Box$  Spoolers for 200 to 1,000 feet of tape  $\Box$  Operates asynchronously at any rate between 0 and 150 cps  $\Box$  Slews at 600 cps and stops "on character"  $\Box$  Lamp is unconditionally guaranteed for 1 year.

For catalogue describing the complete line of Chalco tape readers write, call or telegraph:

15126 SO. BROADWAY - GARDENA, CALIF. • FA 1-0121 (213) TWX 213-327-0167

### Digital makes 1½ million logic modules a year, 300 types. Here's why:

DIGITAL is the world's leading manufacturer of logic modules. Our high production capabilities assure low prices.

And versatility. DIGITAL supplies over 300 types of modules to meet exactly your special logic

control requirements. Our K Series, for example, are specifically designed to replace awkward relays, timers, etc., in industrial applications. K Series have been deliberately slowed to make them virtually noise immune. They're compact, inexpensive, and easily installed.

M Series is our new TTL monolithic I/C general purpose line, operating at computer speeds and using the latest advances in integrated circuit technology. W Series are designed specifically for data communications; A Series offers a full range of analog to digital conversion; R Series for computer interfacing. Other lines are available for special applications. Free copies of our 300 page Industrial Control and 450 page Logic Handbooks are

CIRCLE NO. 17 ON INQUIRY CARD

#### **READER FOR PUNCHED OR MARK-SENSE DATA** — Motorola Instrumentation and Control Inc., Phoenix, Ariz., a subsidiary of Motorola Inc., will display a new, inexpensive desk-top reader for acquiring data from mark-sense documents, mark-sense cards, punched cards, or combined mark-sense/punched cards, at its booth, No. AA, at the Spring Joint Computer Conference, April 30 - May 2, Convention Hall, Atlantic City, N. J.

The new MDR-1000 reader provides a simple means of entering into a data processing system, in computer language, data marked or punched on cards or marked on standard 81/2" x 11" documents. Cards can be fed into the new device singly or automatically in batches of up to 500 with an optional automatic hopper. It thus offers systems designers a new, low-cost method of getting raw data, right from the source, without need for skilled data processing equipment operators. In addition, the unit is small enough  $(16\frac{3}{4})^{"}$  wide by  $16\frac{1}{4}$ " deep by  $9\frac{3}{4}$ " high) to fit almost anywhere.

The reader produces a standard USASCII output that is compatible with standard telephone transmission interfaces for long-distance transmission or directly with standard data processing equipment, such as teletypewriters, tape recorders, or computers.

\$\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

**TRADITIONAL? SURREAL-ISM? AVANT GARDE?** — For lack of a better word, it's called computer/plotter art, a little known but increasingly important art form which was demonstrated at an informal showing held at the New York room of the Statler Hilton, Los Angeles, (2/29/68).

Around the walls were hung approximately a dozen framed drawings in color, and black and white, both original drawings and reproductions of masterpieces, the products of a collaboration between computers, a California Computer Products, Inc., Plotter, and, of course, human beings.

The showing was held in conjunction with the announcement by Calcomp that it is sponsoring an international "computer/plotter art" competition by offering scholarships of \$5000, \$3000 and \$2000 to accredited colleges or universities named by the winners, plus cash awards of \$500, \$300, and \$200 with additional awards of \$50 each to 50 runners-up.

Judging the contest, which will end on November 1, are Anthony La Rotonda, art director of Parade Magazine, Arnold C. Holywell, acting art director of Time-Life Books, and Peter Fingesten, editor of the Pace College (New York City) art department. Winning entries will be exhibited at leading art galleries and museums throughout the country.

Computer/plotter art has been hitherto little known except within the technical world. Increasing refinements, however, have produced beautiful pictures, so much so that the drawings, both originals and reproductions, are now being sought by collectors.

The CalComp Plotter, of course, is engaged in more materialistic pursuits such as generating garment patterns of various sizes from the designer's original pattern at a fraction of the time formerly required, producing contour maps for oil exploration, and a variety of other uses applicable to industry. Information on the awards contest and entries can be obtained by writing to California Computer Products, Inc., 305 North Muller Street, Anaheim, California.

WESCON TO PRESENT 'HY-BRIDS' SYMPOSIUM — A twoday lecture program on designing with hybrid microelectronics has been confirmed as a special feature of WESCON week in Los Angeles next August.

It is the second of the concurrent symposia announced for WES-CON. The 1968 International Electronic Circuit Packaging Symposium has been set for August 19 and 20 at the Statler Hilton Hotel, and the "hybrids" series will follow at the Statler on August 21 and 22. WESCON's own four-day technical program of 25 sessions will be held at the nearby Biltmore Hotel.

The 20 lectures on designing with hybrids are being organized under sponsorship of the IEEE Parts, Materials and Packaging Group. Wayne Martin, Radio Corp. of America (Aerospace System Division) is co-chairman of the series with S. M. Stuhlbarg (Raytheon), who was chairman of the 1967 WESCON symposium titled "Microelctronics Comes of Age." Like that program, the hybrids series will be a compact, followon version of an eight-week lecture program currently in presentation at MIT.

### Does your present custom power supply give you...

70% to 90% efficiency?

Instant fault repair by plug-in module replacement? Add-on power capability by using more modules? Ability to handle full load steps while maintaining out put in regulation band?

### **New Omnimod does!**

7

Omnimod power control module.

Omnimod control amplifier.

OMNIMOD gives you all these features—and more—and at a lower price! Want to know more?

OMNIMOD is a dc to dc converter using transistors in a CONSTANT PULSE WIDTH, variable repetition rate switching mode to regulate output voltage or current. Two small plug-in units make-up the OMNIMOD concept—a power control module and a control amplifier.

Output can be regulated between  $\pm$  2 and  $\pm$  60 dc at up to 20 amperes using the OMNIMOD family of modules WITHOUT MODIFICATION OR ADJUSTMENT. Higher current ratings are obtained by paralleling power control modules.

Any number of power controller modules can be controlled by one amplifier. OMNIMOD has a current limiting parameter, over voltage protection, voltage sequencing, and remote sensing.

To design a custom power supply, one must simply

**1.** design one input power converter to change unregulated line ac power to unregulated dc power

2. select the number of plug-in OMNIMOD power control modules to supply the power needed for each output

**3.** package these elements with filter capacitors and a plug-in amplifier module for each output

All the power used by every element in a typical data processing system could be supplied by custom power supplies constructed with interchangeable OMNIMOD modules.

Isn't this enough to consider OMNIMOD for your custom requirement? We will design an OMNIMOD custom power supply to your specs, or will help you design your own system using our plug-in OMNIMOD modules.

Write for the complete story. We'll have it to you within 48 hours.

CIRCLE NO. 18 ON INQUIRY CARD

### INVAC PERFORATED TAPE DUPLICATORS, VERIFIERS, and CODE-CONVERTERS

INVAC Off-Line Tape Preparation Systems, Series S10-S50 combine the capabilities of standard INVAC Tape Punches, Readers, and associated electronic logic circuitry to duplicate, verify, or code convert using any tape material or code.

- ... Optional Editing Switches

- ... Optional Parity Error Detection

- . . . Optional Blank Skip

- ... Optional Code Delete Skip

- ... Optional Character Recognition

- ... Optional Tape Rewind Panel.

HIGH SPEED KEYBOARD enhances system versatility. Makes new tape. Edits existing tapes. Write for data

26 Fox Road, Waltham, Massachusetts 02154 Tel. (617) 899-2380

PHOTOELECTRIC KEYBOARDS • TAPE PUNCHES READERS AND HANDLERS • I/O TYPEWRITERS PRINTERS AND SYSTEMS

#### INDUSTRY'S FIRST BI-POLAR LSI ARRAY WITH 2-LAYER METAL —

The industry's first bi-polar large scale monolithic array incorporating two-layer metalization is now available from Fairchild Semiconductor. Termed the 4500, this unit is the first of a full line of bi-polar and MOS arrays planned for introduction by the firm during 1968. Because of the custom interconnection between cells and parts of cells inherent in the Micromatrix technique, the 4500 is capable of producing a wide variety of CCSL compatible logic functions.

The 80 x 110-mil chip used in this unit is a 2 x 4 array containing eight distinct cells. A cell is subdivided into quarter cells, each of which is a four-input DTL NAND logic gate. For additional logic flexibility, each quarter cell has three further logic options: input AND expansion, internal OR expansion, or output opencollector.

Fairchild's Micromatrix approach uses a complex array of two-dimensional multi-gate building blocks or cells. Each cell contains a set of components that may be individually specialized by cell intraconnects to become one of a variety of fundamental logic building blocks (NOR, NAND, flip-flop, latch, etc.). By means of the two-layer metalization process, the cells may be interconnected to form a complex subsystem logic function analogous to the interconnection of conventional integrated circuits on a dual-sided printed circuit board.

#### 8--8--8--8--8--8--8--8--8--8--8--8

IMPATT DIODES CONNECTED IN SERIES FOR INCREASED POWER - IMPATT diodes have been connected in series to provide a power output which is the sum of the individual diode outputs. These diodes produce negative resistance at microwave frequencies based on a combination of avalanche current multiplication and transit time delay. While parellel connection has been used in the past, this is the first time the diodes have been connected in series. Although the power output is theoretically the same in both cases, the series connection offers the advantage that the combined structure works at a higher impedance level.

The result of these experiments was reported by F. M. Magalhaes and W. O. Schlosser of Bell Telephone Laboratories in a paper presented at the 1968 International Solid-State Circuits Conference in Philadelphia, Pa. To demonstrate that IMPATT (IMPatt Avalance

\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*\$\*\*

and Transit Time) diodes can be operated in series, three packaged 4.5 GHz diodes were placed in a coaxial cavity and biased in series. With approximately 250 milliwatts output each, the diodes provided 750 milliwatts of continuous wave output. This indicates that medium power millimeter-wave IMPATT oscillators with reasonable impedance levels are now foreseeable.

Virtually no significant drop in the power output was observed even when the spacings between the diodes were varied considerably. This consistency of output is due to variations in negative resistance with respect to rf current through the diodes. Also, since the spacing can be made relatively large, it becomes easier to extract heat from the operating diodes.

From the experiments, it was concluded that it is possible to operate IMPATT diodes in series. Also, because spacing between the diodes is not critical, it is possible that similar series connections are applicable to millimeter wave oscillators.

8--0--0--0--0--0--0--0--0--0--0

**DATA COMMUNICATIONS SUB-SYSTEM** — Multi-line communication between the UNIVAC 9200 and 9300 computers and remote termi nals is the function of the new DSC-4 Data Communications Subsystem announced recently by Sperry Rand Corporation's UNIVAC Division.

The DCS-4 can be employed with wideband (Telpak) service at speeds up to 230,400 bits per second (9200 communication is limited to 50,000 bits per second), telephone lines at up to 2400 bits per second, and telegraph lines at up to 150 bits per second.

With one DCS-4, concurrent communication is possible over up to four lines. With two DCS-4's, communication can be established over up to eight lines (telephone and telegraph line combinations only).

A UNIVAC 9000 series computer equipped with DCS-4 can communicate with the following UNIVAC systems—418, 494, 1107, 1108, DCT 2000, 1004, 1005, Uniscope 300, as well as with Teletype remote devices.

A feature of the DCS-4 is that processor functions, including magnetic tape reading and writing, can be overlapped with communication at voice-grade and telegraph rates. Deliveries of the DCS-4 are scheduled to begin in the Fall of 1968. The price for a DCS-4 configuration serving four telegraph lines will be \$522 per month or \$19,155 purchase.

COMPUTER DESIGN / MARCH 1968

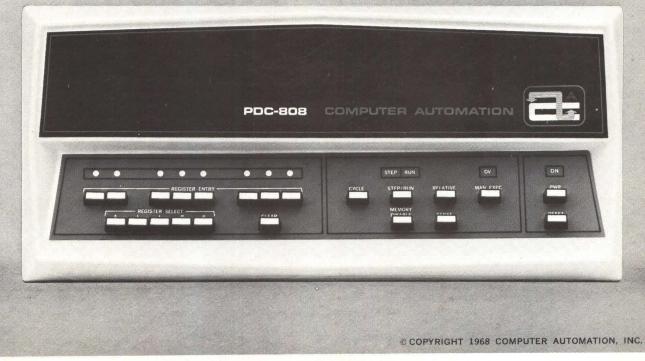

### LOGICALLY THERE IS NO OTHER CHOICE THAN THE MODEL PDC 808

- Available off the shelf for \$6,600

4,096-word core memory, expandable

- Parallel processing

- Fifty-eight basic instructions

- 24-µs ADD

Two priority interrupt lines

- 8-bit word length Extremely powerful and flexible I/O system, easily interfaced

For complete information on the PDC 808 and its optional features, write :

COMPUTER AUTOMATION, INC. Dept. CD-3, 2409 S. Broadway, Santa Ana, California 92707 (714) 540-5675

"Time Sharing" is presented in its most general sense as any application of a computer system that involves simultaneous users. Concepts and equipment of time-shared systems are defined and described and criteria for system configurations are given in terms of application requirements.

### **FUNDAMENTALS OF TIME-**

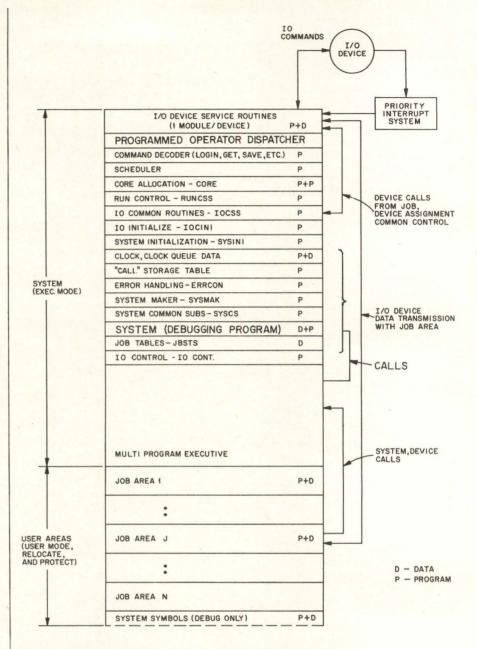

This is the second and concluding section of the article by C. Gordon Bell which appeared on pages 44 through 59 of the February issue of Computer Design. The first section discussed the hardware of time-shared computers and suggested advantages of time sharing. This section discusses operating system software and user components and includes an extensive bibliography on time sharing.

#### OPERATING SYSTEM SOFTWARE

Operating system, monitor, supervisor, and executive are names given to those processes that supervise and control the operation of the system for all users.

Unlike conventional operating systems that are static, a Time Sharing Operating system is growing and dynamic. New procedures may be added continuously.

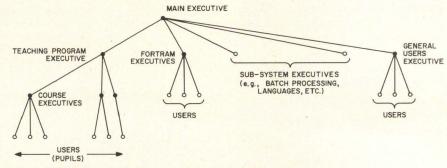

The additional languages and facilities have a structure that may have a rather complex operating system as a major part of the language. For example, consider the administration of a teaching program. The program would undoubtedly schedule its users (pupils), and the hierarchy of the whole system would be: the operating system for the entire computer managing a central teaching program to manage all courses managing a course teaching program which would manage all individual users taking the particular course.

The objectives of the system software are:

1. Provide many user functions or facilities with easy-to-use processes. 2. Effective or efficient hardware utilization. Perhaps allow users to utilize the hardware directly. Provide special user services which utilize special hardware.

The criteria for the design might: 1. Meet the requirements for Time-Sharing (computer time and memory space) per user.

2. Provide for flexibility in the operating system using modular construction. Individual components can be independently designed, tested, and modified (or improved). If possible, the system components should be written as user processes.

In general, all systems are constrained by cost considerations. A special system may concentrate on a single objective, while a general system is forced to find a balance between many objectives.

The system software contains: 1. System data base, or information necessary for system management, and management procedures. 2. Resource allocation, control, and management procedures.

3. Common procedures or processes for the users, the library.

4. Miscellaneous elements: System initialization and shut-down; error recovery; file backup; creation of new system; and system debugging.

### OPERATING SYSTEM DATA BASE

The operating system requires a large data base that is retained in primary memory and in files. Back-up files (copies of files) must be regularly written so that the system can be restarted in a correct state in the event of system failure.

The data for a user include: his memory map or process location, generally found in primary memory while running or active; the processor status (the location counter, processor flags, accumulators, index registers, etc.); identity information (name, number, project numbers, etc.); the time used, allotted, last run, etc.; the run state (e.g., presently running, waiting to run, requiring special service, waiting for file transaction, terminal action, additional memory, etc.); permanent user data to allow the assignment of terminals and file space; accounting information; system temporary storage to enact user requested procedures; and active terminal and file buffering storage.

### SHARED COMPUTERS

#### by

C. GORDON BELL

Associate Professor of Computer Science and Electrical Engineering, Carnegie Institute of Technology. Formerly manager of Computer Design, Digital Equipment Corporation, Maynard, Massachusetts.

In addition to the data base associated with each user there are inherent data associated with system components and resources. These include: hardware status and availability information; terminal names; file directories including descriptors of abilities, modes, etc.; primary memory free space; and file memory free space.

Historical, statistical, and accounting information are also kept, and historical or activity data provide tools for system improvement. They especially aid scheduling and memory allocation as well as indicate the system balance and load.

#### RESOURCE ALLOCATION, CONTROL AND MANAGEMENT

This responsibility includes: processor time or scheduling; process space (primary memory allocation) and assignment of a process to secondary memory or files; file space; and terminal/process/user allocation and assignment.

The two extreme philosophies that determine the number of users a system can have are "denied access" and "degraded service." "Denied access" provides for a fixed number of users, each of which will obtain a known or worse case response. "Degraded service" provides for more users and the service is at least inversely proportional to the number of active users.

#### Scheduling

The assignment of processors to processes is *scheduling*. The scheduling algorithms that compute the time a process is to run usually use the following input parameters: previous time used; memory space occupied; status of terminal or file data transmission; expected response time for the user; user information; and number of users.

The priority information available includes the user, his urgency, and willingness to pay. As economically realistic systems that charge for their actual uses come into existence, users will be able to get a broader range of service.

The round robin algorithm runs each user, in turn, for a fixed quanta of time, and when all users have been served, the process is repeated. If any user cannot run because he is waiting for input or output, or halted, he misses a turn. On completion of input or output the user is put at the head of the queue and run (subject to his allotted time).

The scheduling algorithm is a most subjective system component, and, therefore, might be written in a form that can be easily modified. How, when, and which components call the scheduler is also important.

#### **Memory Allocation**

Primary/secondary memory alloca-

tion occurs as users make demands for more space the system activates user processes. The hardware memory allocation scheme of Table 2 constrains the user map organization, and the process organization. This hardware constrains the user procedure with restrictions ranging from writing in interpretive languages; writing at particular addresses or using a convention determined index register as a base register; writing with no restrictions (over the basic machine); and finally providing a two-dimensional addressing space.

The memory paging-memory segmentation hardware will drastically influence future program structure and design. With two-dimensional addressing, the user is not required to manage primary memory, and is free to address data by two logical numbers rather than by physical numbers. (With such freedom, and ability one might expect a proportional cost.)

#### **File Allocation and Control**

File allocation and control are generally subject to extra-system constraints on the basis of user-size-restriction tables.

File allocation cannot easily be separated from detailed file management. The management includes the service of detailed user requests for data, while allocation is concerned with broader control of all file space.

Hardware's View of Files. The hardware parameters that affect file organization are: the hardware access time for words or sectors of the file; the word or record transfer time; the size of the records transferred; the total file size; and the file failure rate.

**Operating System's View of Files.** The apparent file parameters are: the size of files; the number of users and number of files per user; the access time to segments of a file; the nature of addressing the file information (sequential or random accessing); the file index; and the file data buffering. File activities can be divided into operations: naming, or declarations, inter-file manipulation, intra-file utilization, and file closing.

User's View of Files. Parameters associated with the directory or index of files for users provide a means of controlling a file's activity, flexibility, general usage, name, users, record of its activity, and actual location of the file components. File accessibility control for the user is on the basis of the originator (owner), group, and public. The modes of file activity include read/ write, read only, execute only (a procedure), and denied access. Other information about file access includes creation date, number of times used, last time used, times modified, etc. The user requests of functions for utilization include: reading, writing, naming, re-naming, deleting, appending, inserting, providing access restrictions, obtaining statistical information, or in general, any operation that can be done with the data in or about a file.

#### **Terminal Allocation**

Terminal allocation in general systems is either on a first-come-firstserved basis or on a completely reserved basis. Requests for terminal reservations are via a control terminal, and as a job is initiated, the terminals required for job completion are requested. The terminal is the means by which a process is

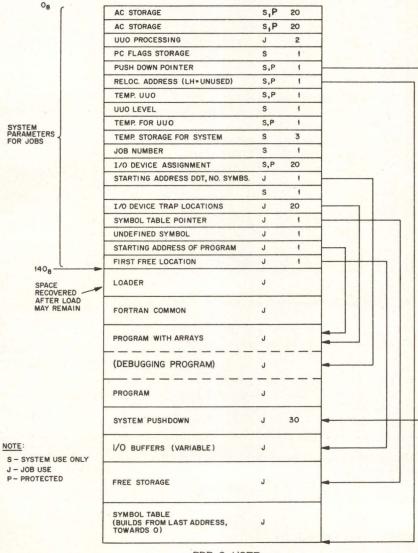

#### TABLE 2. MEMORY ALLOCATION METHODS

| Hardware Designation                                                                                        | Method of Memory Allocation<br>Among Multiple Users                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Limits of Particular<br>Method                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conventional computer — no memory al-<br>location hardware                                                  | No special hardware. Completely done by inter-<br>pretive programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Completely interpretive programming re-<br>quired. (Very high cost in time is paid for<br>generality.)                                                                                                                                                                                                      |

| 1 + 1 users. Protection for each memory<br>cell                                                             | A protection bit is added to each memory cell.<br>The bit specifies whether the cell can be written<br>or accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Only 1 special user + 1 other user is al-<br>lowed. User programs must be written at<br>special locations or with special conven-<br>tions, or loaded or assembled into place.<br>The time to change bits if a user job is<br>changed makes the method nearly useless.<br>No memory allocation by hardware. |

| 1 + 1 users. Protection bit for each mem-<br>ory page.                                                      | A protection bit is added for each page. (See above scheme.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No memory allocation by hardware.                                                                                                                                                                                                                                                                           |

| Page locked memory                                                                                          | Each block of memory has a user number which<br>must coincide with the currently active user num-<br>ber.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Not general. Expensive. Memory reloca-<br>tion must be done by conventions or by<br>relocation software. A fixed, small num-<br>ber of users are permitted by the hard-<br>ware. No memory allocation by hardware.                                                                                          |

| One set of protection and relocation reg-<br>isters (base address and limit registers).<br>Bounds register. | All programs written as though their origin were<br>location 0. The relocation register specifies the<br>actual location of the user, and the protection<br>register specifies the number of words allowed.<br>(See Fig. 7.)                                                                                                                                                                                                                                                                                                                                                                 | As users enter and leave, primary memory<br>holes form requiring the moving of users.<br>Pure procedures can only be implemented<br>by moving impure part adjacent to pure<br>part.                                                                                                                         |

| Two sets of protection and relocation reg-<br>isters, 2 pairs of bounds register.                           | Similar to above. Two discontiguous physical areas of memory can be mapped into a homo-geneous virtual memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Similar to above. Simple, pure procedures with one data array area can be imple-<br>mented.                                                                                                                                                                                                                 |

| Memory page mapping*                                                                                        | For each page $(2^{6}\cdot2^{12} \text{ words})$ in a user's virtual<br>memory, corresponding information is kept con-<br>cerning the actual physical location in primary or<br>secondary memory. *If the map is in primary<br>memory, it may be desirable to have "associative<br>registers" at the processor-memory interface to<br>remember previous reference to virtual pages,<br>and their actual locations. Alternatively, a hard-<br>ware map may be placed between the processor<br>and memory to transform processor virtual ad-<br>dresses into physical addresses. (See Fig. 8.) | Relatively expensive. Not as general as<br>following method for implementing pure<br>procedures.                                                                                                                                                                                                            |

| Memory page/segmentation mapping                                                                            | Additional address space is provided beyond a<br>virtual memory above by providing a segment<br>number. This segment number addresses or se-<br>lects the page tables. This allows a user an al-<br>most unlimited set of addresses. Both segmenta-<br>tion and page map lookup is provided in hardware.<br>(See Fig. 9.) May be thought of as two dimen-<br>sional addressing.                                                                                                                                                                                                              | Expensive. No experience to judge effec-<br>tiveness.                                                                                                                                                                                                                                                       |

intiated and requests for additional terminals, primary memory, time, etc., are made through it. It is the medium for job control.

Resource management deals with servicing user demands after resource allocation has occurred. It is imperative to provide users with a system that requires little or no knowledge of particular device or terminal idiosyncrasies. Even though terminals have differing characteristics it is desirable for the system to provide users with a single basic set of characteristics. More flexible terminals would, of course, leave abilities in access of the common characteristics which could be utilized. On the other hand, it is important to allow users the freedom to control special terminal activity directly. This is particularly necessary in mixed experimental-production systems involving terminals that differ widely. For example, in flight simulation systems, the usage may range from program debugging, new terminal hardware-software debugging, and simulation.

The terminal characteristics are: speed or data rate of the terminal; amount of primary memory used for buffering and the location of the buffers; system overhead time for data requests, including processing time required for the data; and device data acquisition modes, and terminal data usage. Detailed terminal management includes the process that buffers data from the terminal and synchronizer user demands with terminal performance.

### SYSTEM-PROVIDED PROCEDURES AND PROCESSES

In addition to providing the software framework within which users operate the hardware, the system also supplies many of the processes for a user. That is, the system includes a library of procedures for arithmetic function evaluation, special and procedure oriented language translations, computer aided instruction, file data conversion, text editing, program debugging, fact retrieval, simulation, etc. In fact, the difference between a user and a system process is that a user process can be altered.

The method of calling these procedures (or job setup) and the ability to have a hierarchy of procedure calls is important. A system-supplied procedure can be considered an extension of the system and called with the same mechanism with which a user would request file or terminal activity. In fact, the hardware instructions that provide communication between the system and the user should also be used for procedure calls. In this fashion, the system can conserve memory space by not providing duplicate copies of routines that are in use by multiple users. The data or temporary storage required by the system while enacting a procedure on behalf of a user is part of the user's memory. This structure conserves space both for users of small subroutines (e.g., arithmetic, data conversion, etc.) and large programs (translators, text editors, etc.).

A set of commands might include programmed floating point arithmetic (for a small system), common arithmetic functions, complex arithmetic, string processing, data conversion and operating libraries for the language translators, translators, editors, loaders, etc. Also desirable is the facility for a user to define and call his own functions in the same hierarchy and framework.

### MISCELLANEOUS SYSTEM FUNCTIONS

These processes include record keeping, the periodic recording of the system state for backup, error detection, error recovery, error handling for a device, and communication with the user terminals for system requests. The system clock is a part of the operating system that provides the actual time base and is used by the scheduler and the accountant, for example, to carry out their functions.

System start-up and shut-down procedures are necessary for initialization of system and the recording of history. Parts of the system can be written as pseudo users. This allows functions like data gathering and system analysis to go on by watching the system rather than being embedded in it. This operation is obtained by defining monitor instructions that allow a user to obtain behavioral characteristics on demand.

A debugging system for the operating system might have the following features: ability to examine or alter; ability to dump or save the complete system in the event of a "crash"; ability to control the substitution of a "new" system for the present one, etc. These features are extensions of a normal on line debugging program.

#### EXAMPLE OF TIME SHARING SYSTEM FOR THE DEC PDP-6

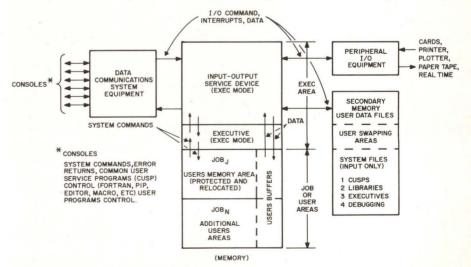

Figure 10 first presents a simplified view of the system in terms of the memory map of the user and operating system, together with terminals and files. The system runs either as a multi-programming or multi-programming/swapping system depending on whether a secondary memory device is available for program swapping.

A job for a user can be viewed as an area of memory which it occupies while running and I/O

Fig. 10 PDP-6 Multiprogramming System Diagram. (Courtesy of Digital Equipment Corporation.)

equipment assigned to the job, including the user's files and terminals. The operating system software has four main modules: the system files (e.g. FORTRAN, assembler, language translators); terminal control; file control; and the main body of the executive.

Figure 11 gives a more detailed view of what a user program looks like. The user program (e.g., a common user program such as a Fortran Compiler) has its own executive system which communicates with the operating system. The user executive translates user commands from a console into operating system commands for file and ters which store the processor state while the job is not running. These include:

1. Two groups of  $20_8$  registers to store the accumulators or general registers (AC's).

2. The Program Counter (PC) and processor flags.