# COMPUTER DESIGN

THE MAGAZINE OF MODERN DI

DIGITAL ELECTRONICS

**FEBRUARY 1968**

TIME-SHARING

We have a complete line of photodevices – from a 50-cent epoxy transistor to a \$4,000 custom photo array. Light-emittin light-sensing devices for everything from computers to electric organs. They can translate keyboard signals, read punched cards and tape, measure height and volume, perform character recognition, read motion picture sound track. You name it. Write for complete information and we'll throw in a glossary of the latest photometric and radiometric terms.

FAIRCHILD SEMICONDUCTOR / A Division of Fairchild Camera and Instrument Corporation = 313 Fairchild Drive, Mountain View, California 94040, (415) 962-5011 = TWX: 910-379-6435 SEMICONDUCTOR

# What this country needs is a good 50¢ phototransistor.

CIRCLE NO. 1 ON INQUIRY CARD

# New BCD MINIVERTER<sup>®</sup> A 16-channel multiplexer, sample & hold amplifier and 13-bit BCD, 80KHz analog/digital converter for under \$1900...

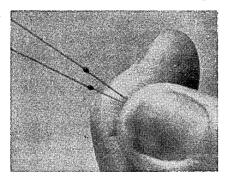

Test points in module handles.

The BCD configuration is the newest addition to the MINIVERTER family which includes the successful 10-bit MINIVERTER priced at \$1750.

The MINIVERTER can be expanded to a virtually unlimited number of channels. And there is a compatible logic system of M-Series analog and digital modules, plus cases and accessories, to go with it. You can buy the MINIVERTER in various size cases with controls, digital power supplies and displays.

The MINIVERTER includes 9 M-Series IC modules and an analog power supply, all mounted on a compact connector block, pre-wired, tested and ready to use.

Write or call today for detailed specifications.

Raytheon Computer, 2700 S. Fairview St. Santa Ana, California 92704 Phone: (714) 546-7160

CIRCLE NO. 2 ON INQUIRY CARD

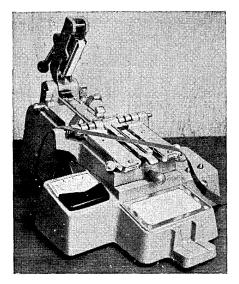

The Peripheral People announce the ultimate in reading reliabilitythe D4 punched card reader. It's great for companies that hate the sight of a maintenance man.

> NCR knows more about electro-mechanics than anyone. That's why the economical D4 300 cpm reader keeps up the good work longer, with minimal maintenance. Still we know that sooner or later a card will stick, so we made the card track fully accessible—an operator can free a jam in seconds. If you should ever need service (after an earthquake, fire or office party), the D4's modular construction makes it fast and easy. For information on speedy delivery, contact the Peripheral People today.

THE NATIONAL CASH REGISTER COMPANY . INDUSTRIAL PRODUCTS DIVISION . DAYTON, OHIO 45409

# Publisher and Editor ROBERT BROTHERSTON

Associate Publisher TONY SALTALAMACCHIA

Managing Editor WILLIAM G. KEYWORTH

Editorial Advisers RICHARD AHRONS ELI ANFENGER JAMES R. BRIGHT GERHARD L. HOLLANDER G. P. HYATT BERNARD M. GORDON WALDRON S. MACDONALD ROBERT S. SENATOR HAROLD H. SEWARD

> Contributing Editors T. PAUL BOTHWELL A. S. BUCHMAN M. P. de REGT RUDOLPH J. KADLEC ROBERT P. FORAN RICHARD B. LAWRANCE WALTER A. LEVY H. S. MIILLER MADELINE SULLIVAN

Washington Editor HAROLD V. SEMLING, JR.

> Art Director JAMES FLORA

Production Manager TERRY ARMENTI

Tech. Illus. JOHN BROTHERSTON

Editorial Ass't. PRISCILLA HANNON

> Adv. Prod. JOAN WASIUK

Circ. Mgr. ALMA BROTHERSTON

Vice Pres.-Sales LINDSAY H. CALDWELL

Editorial & Executive Offices Prof. Bldg., Baker Ave., W. Concord, Mass. 01781 Tel. 369-6660

Computer Design is published monthly. Copyright 1968 by Computer Design Publishing Corporation. Accepted as controlled circulation publication at Post Office at Chicago, Illinois. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS — FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box A, Winchester, Mass. 01890. Subscription rate to anonqualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 40,000

# COMPUTER DESIGN

THE MAGAZINE OF DIGITAL ELECTRONICS

#### FEATURES

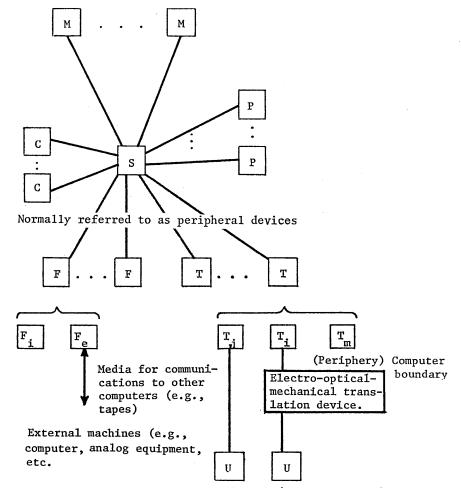

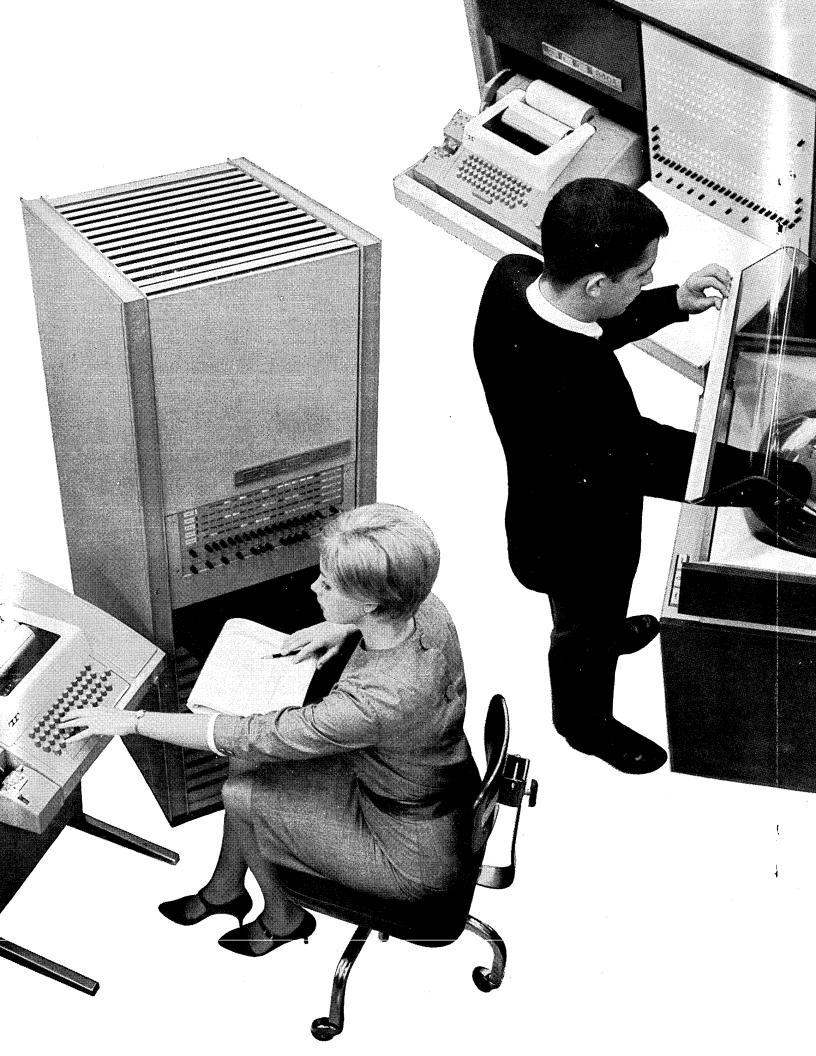

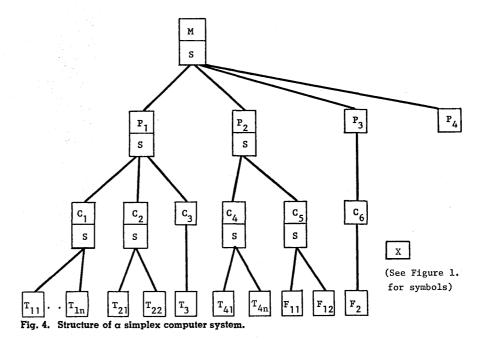

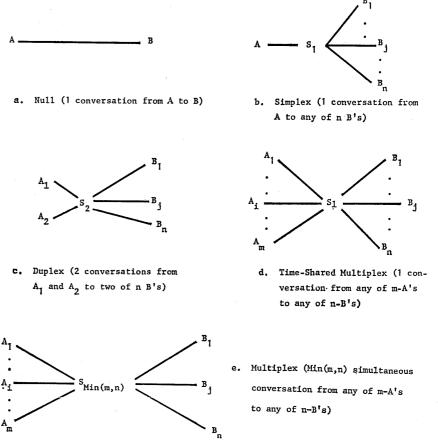

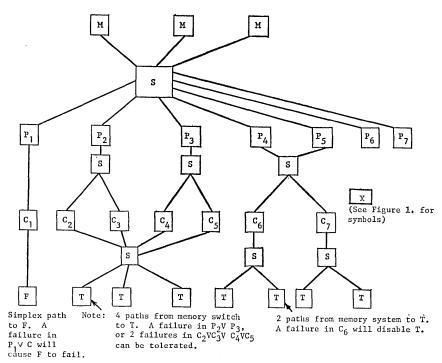

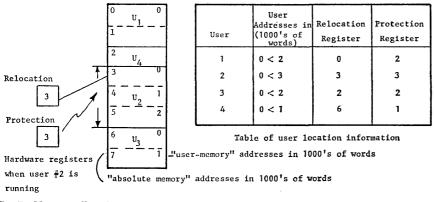

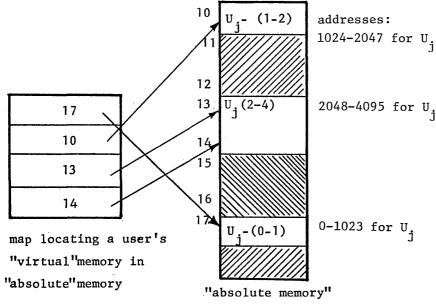

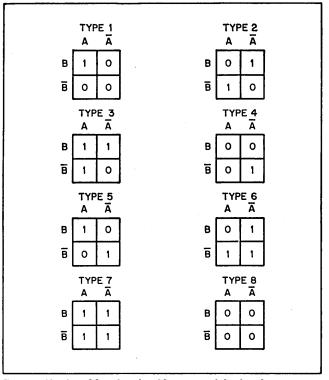

#### 44 FUNDAMENTALS OF TIME SHARED COMPUTERS

"Time Sharing" is presented in its most general sense as any application of a computer system that involves simultaneous users. Concepts and equipment of time-shared systems are defined and described and criteria for system configurations are given in terms of application requirements.

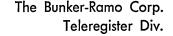

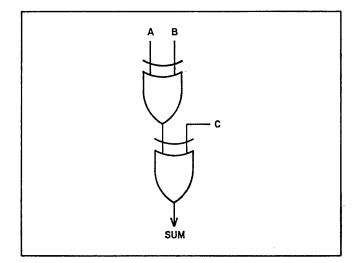

### **60 THE EXCLUSIVE-OR ELEMENT**

Failure of the exclusive-OR element to take its rightful place as one of the primary logic elements is based on historical reasons that are not valid today.

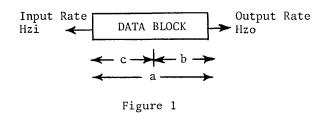

### 62 INTERPLACED CORE BUFFER APPLICATIONS

Correctly applied, the core buffer equation can reduce the cost of data acquisition systems.

#### 66 THE TERNARY NUMBER SYSTEM FOR DIGITAL COMPU-TERS

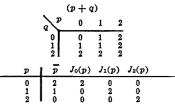

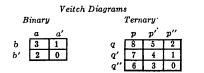

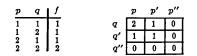

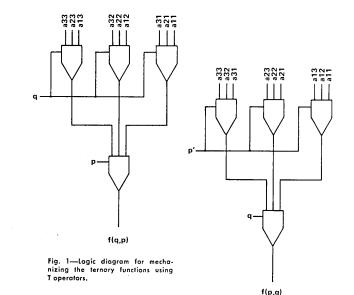

A ternary number system is shown to be more efficient than a binary system provided that the ternary-element costs are not 1.5 times greater than the cost of a binary element.

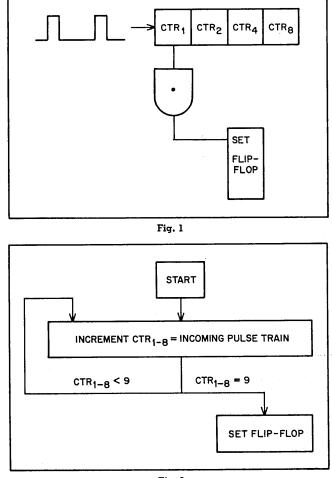

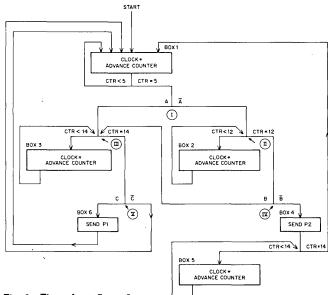

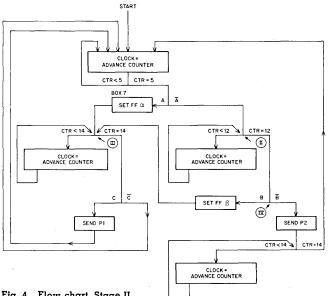

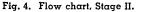

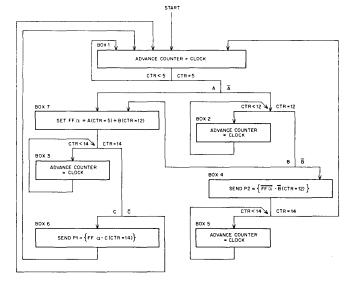

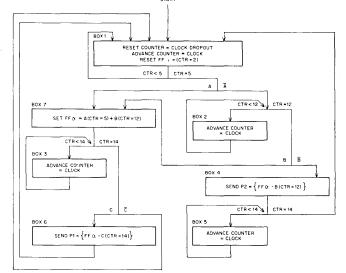

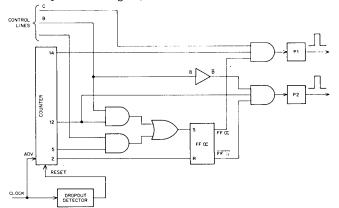

## 72 FLOW CHART METHODS OF LOGIC DESIGN

A simple example provides an introduction to using flow charts in logic design.

#### 76 TIME SHARING SCORECARD

A survey of on-line multiple user computer systems.

#### DEPARTMENTS

# **34** CD COMMENTARY: A CASE FOR MILITARY APPLICATION OF COMMERCIAL, GENERAL-PURPOSE

#### **38 INDUSTRY NEWS**

**80 NEW PRODUCTS**

#### **96 NEW LITERATURE**

| Reader subscription card | opposite page 1  |

|--------------------------|------------------|

| Reader service card      | opposite page 98 |

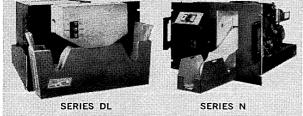

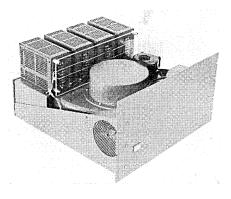

KATO Engineering is one of the major suppliers of matched motor-generator sets for line isolation and cycle conversion...at CDC and throughout the computer industry.

When precision equipment demands pure power, free from line transients, phase unbalance and frequency fluctuations, a KATO Motor-Generator Set is the answer. In the computer industry, in communications, ground-support operations and industrial process-control functions, KATO M-G Sets take imperfect commercial power and provide the exact, balanced, regulated output desired, with continuing efficiency and absolute minimum maintenance. KATO offers the widest possible range of M-G Sets and control equipment plus 40 years of power engineering experience. Why not get the details?

Free 8-page folder gives complete information on KATO M-G Sets. Write for your copy today.

KATO makes many power products . . AC Generators • DC Motors and Generators of <u>clean</u> power it takes to keep computers efficient, **Control Data** Corporation calls on KATO

For the kind

Typical KATO M-G Set supplied to CDC-common-frame, common-shaft construction. Motor is 30 H.P., 220 | 440 volt, 3-phase, low-slip, squirrel-cage induction type. Generator delivers 20 KVA, 120 / 205 volt, 400-cycle, 3-phase and features brushless excitation. Free-standing cabinet houses both motor and generator controls.

KATO ENGINEERING COMPANY 1403 First Avenue • Mankato, Minnesota 56001

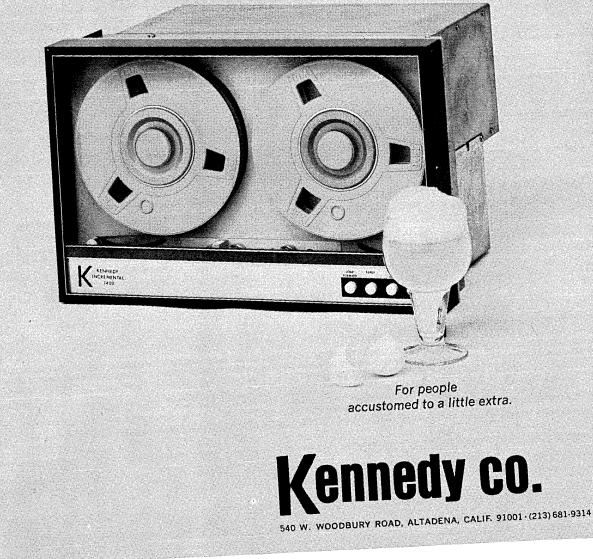

# MAGNETIC TAPE RECORDERS?

# ask Hewlett-Packard

# **ANALOG or DIGITAL...**

Reliability, ease of use, flexibility...these are the built-in extras you get with Hewlett-Packard magnetic tape recorders: today's most dependable tape transport; sturdy mechanical construction permitting long-term performance that can't be matched by more expensive recorders; electronics that are easy to adapt to your specific application; minimum maintenance. And, Hewlett-Packard service is only a phone call away. All this makes the low HP prices even more attractive.

For complete information on analog or digital magnetic tape recorders, call your local HP field engineer or write Hewlett-Packard, 690 Middlefield Road, Mountain View, California 94040; Europe: 54 Route des Acacias, Geneva.

#### ANALOG RECORDERS

IRIG compatible 7 or 14 tracks 1/2" or 1" tape Direct and FM recording Bandwidths to 1.5 MHz

### DIGITAL RECORDERS

IBM compatible 7 or 9 tracks 3 standard densities ½" tape Choice of tape speed to 75 ips Read and write

# If Brand-Rex is already supplying wire a cable to Burroughs, Control Data, G. E., Honeywell, IBM, NCR, Univac and RCA

# why are we so interested in making connections with you right now?

Brand-Rex can help make wire and cable procurement the easiest part of your next computer. Here's what we offer:

BROAD PRODUCT LINE Brand-Rex is the largest supplier of wire and cable to the computer industry. Our EDP line includes back-panel wires, hook-up wires, miniature air-spaced coaxial cables, power supply wires, patch cord wires, interconnecting and communication cables.

DESIGN CAPABILITY We're probably already making the wire and cable you need. If not, we can quickly develop new constructions for new applications. The miniature 95 ohm coaxial cable illustrated here was specifically designed for one of the leading data processing systems. Brand-Rex designs cable to standard specifications or to your specific requirements. (Over 3,000 new designs last year alone.)

#### Any insulation. Any configuration. U.L. APPROVAL We are well equipped to help you get U.L. approvals. Brand-Rex has more of them on computer wire and

cable than any other manufacturer. LNGINEERING KNOW-HOW With more than 16 years' experience serving the computer field, you'll find our engineers eager and able to work with you — from drawing board to production line. Call Brand-Rex now — while your next design project is only a gleam in your eye.

AMERICAN EXA CORPORATION BRAND-REX DIVISIO WILLIMANTIC, CONNECTICUT 0 PHONE 203 423-771

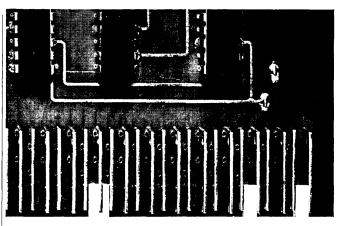

# MAGNE-HEAD BRINGS 9 CHANNEL HIGH DENSITY A MAGNETIC TAPE RECORDING INTO FOCUS

The MHTB-9 Digital Magnetic Tape Head now offers full IBM track compatibility at 800 and 1600 bits per inch: read, write or read after write heads are available in off-the-shelf configurations or to your specification.

For 9 channel and 7 channel or nonstandard format digital recording, write or call today. Write for: TECHNICAL DATA BULLETINS.

MAGNE-HEAD DIVISION

13040 South Cerise Avenue / Hawthorne, California 90250 / 213 679-3377 / 772-2351 / TWX 910-325-6203

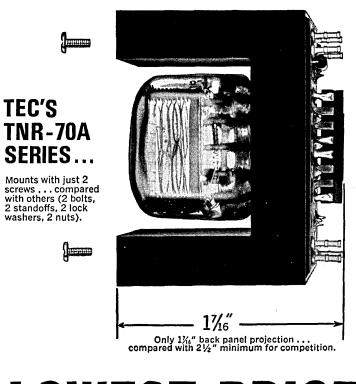

# This is the vintage year for BURGUN-D<sup>™</sup> connectors.

These sparkling new Mark IV D-Subminiatures are *low-cost* connectors with *rear release*, *crimp snap-in* contacts. They're intermateable and intermountable with existing D-Subminiatures. The wine-colored insulators we selected enhance the connector as well as your equipment.

Robust BURGUN-D Mark IV connectors operate in temperatures up to 250°F. They are ideal for plug-in module applications, cable-to-cable and cable-to-panel installation, computers, business machines and many other commercial applications.

Value analysis will tell you they're low in price because of highly developed pin and socket contacts. The contacts are available in two sizes (which accommodate 18 through 24 AWG stranded wire) and may be ordered separately. Contacts are rear inserted and extracted with a simple expendable plastic tool that's shown above. Closed-entry socket insulators correct any misalignment of pins during engagement.

Buy them off the shelf now along with a complete line of accessories from your nearest factory authorized distributor. For our new catalog, write to ITT Cannon Electric, a division of International Telephone and Telegraph Corporation, 3208

Humboldt Street, Los Angeles, California 90031.

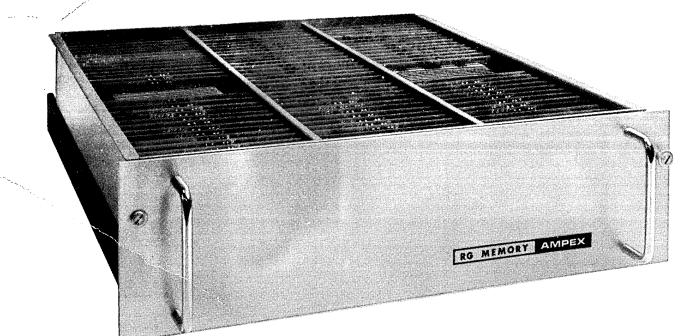

# Here's what your computer can do with the **NEW AMPEX RG MEMORY**

- 1. Access data in 350 nanoseconds

- 2. Expand in modules to 5 million bits

- 3. Sell for less

When you're outlining the requirements of your new computer or system, pause a moment and consider what our new RG core memory offers: 350 nsec access; 900 nsec full cycle time; integrated circuitry; and expansion from a 4K memory all the way to 64K by addition of modules.

We think you'll want to design these features into your next system. The RG is low in cost, too. You pay less for the RG; your customers pay less for your system.

### ALSO NEW FOR 512-TO-4096 WORD TASKS —THE RF-4 CORE MEMORY

This new, high-speed core memory, similar to our RF-1 memory, is built on one large PC board and is capable of word lengths to 20 bits. It uses integrated

circuitry and gives you high speed (1 microsecond cycle time) at low cost.

Check the specs. If they serve your purpose, please drop us a line, or circle the Reader Card number. We would like to send

you our literature about these new workhorse memories. We'll even tell you how little they cost.

| IMPORTANT SPECS |                                                                                        |                                             |

|-----------------|----------------------------------------------------------------------------------------|---------------------------------------------|

|                 | RG                                                                                     | RF-4                                        |

| Access time     | 350 nsec                                                                               | 400 nsec                                    |

| Full cycle      | 900 nsec                                                                               | 1000 nsec<br>(half cycle:<br>650 nsec)      |

| Size (inches)   | 5¼ x 19 x 21<br>(per memory<br>module)                                                 | 5¼ x 19 x 21<br>(including<br>power supply) |

| Capacity:       | 4096; 8192;<br>12,228; or 16,384<br>words, expandable<br>in modules to<br>65,536 words | 512 to<br>4096 words                        |

| Word length:    | 24 to 80 bits                                                                          | 4 to 20 bits                                |

CIRCLE ON. 9 ON INQUIRY CARD

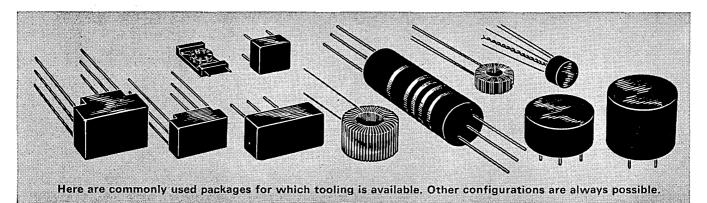

# Contemporary Electronics is one of the largest producers of computer pulse transformers in the U.S.

# **SO**?

So, maybe you're missing a bet if you haven't checked Contemporary Electronics for *quality, service* and *price.*

Contemporary Electronics *specializes* in pulse transformers. It's not a sideline, but a principal part of our business. Well over 100,000 pulse transformers are produced each month in 75 different designs.

#### Advantages? Here are some.

**Technical Capability.** Contemporary Electronics engineering staff knows computers and can design any special product for any application. **High Quality.** Most transformers have special high quality design features. All pulse transformers are 100% inspected as many as three times before shipment. QC system meets MIL-Q-9858, and has been approved for use on the Apollo program.

**Fast Sample Service.** Samples, small production lots and specials are normally shipped 24 to 72 hours after receipt of request.

Interested in what can be done in terms of performance, size, delivery, or MIL-specs? Get to us—we've got lots more to tell.

# WRITE, OR CALL COLLECT AND WE'LL HAVE THE FULL STORY TO YOU WITHIN 48 HOURS

4838 West 35th Street, Minneapolis, Minnesota 55416 612/920-6444 EXTRA SERVICE TO THE DATA PROCESSING INDUSTRY

CIRCLE NO. 10 ON INQUIRY CARD

COMPUTER DESIGN/FEBRUARY 1968 CIRCLE NO. 11 ON INQUIRY CARD --->

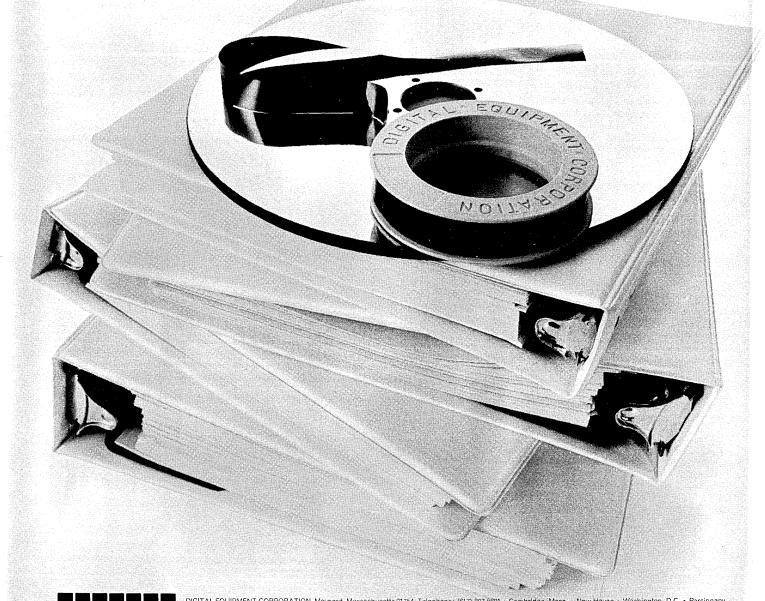

# Cheap mass storage for small computers and how to get the most out of it

For some people the only limitation of the small computer is the price of the extra memory. What's needed is low-cost mass storage, and lots of it. For filing data. For quick and convenient program manipulation.

DIGITAL, the leader in small computers, has a low-cost disc and unique magnetic tape unit tailored for the small computer. Now, new software is available to take even better advantage of this low-cost memory.

DECdisc adds 32,768 words of memory for \$6,000. Additional expander discs (up to 3) can be added at \$3,000 each. That means a total of 131,072 words of disc memory for \$15,000.

A full scale PDP-8/S computer with 36,864 twelve bit words of memory, for example (4k core plus disc), costs \$18,500. DECtape, Digital's unique fixed address magnetic tape system, provides over 200,000 words of storage on a  $3\frac{1}{2}$ -inch reel. It's the lowest cost mass storage available anywhere. You can edit and debug programs on line. Then you can put your programs in your pocket and take them away until you want them again.

New keyboard monitor software all but eliminates the laborious use of paper tape and cards. You edit from the keyboard, compile from the keyboard, assemble, load, store, debug all from the keyboard. What might have been hours or days in getting the computer ready for use, is now just minutes.

Available now. PDP-8/S off-the-shelf. PDP-8 in one month. PDP-8/I in the spring. DECdisc and DECtape immediately available. Send for our new Small Computer Handbook. It's free.

DIGITAL EQUIPMENT CORPORATION, Maynard, Massachusetts 01754. Telephone: (617) 897-8821 • Cambridga, Mass. • New Haven • Washington, D.C. • Parsippany, N.J. • Princeton, N.J. • Rochester, N.Y. • Long Island, N.Y. • Philadelphia • Huntsville • Pittsburgh • Chicago • Denver • Ann Arbor • Houston • Albuquerque • Los Angeles • Paio Alto • Seattle: INTERNATIONAL, Carleton Piace and Toronto, Ont. • Montreal, Quebec • Reading and Marchester, England • Paris, France • Munich and Cologne, Germany • Oslo, Norway • Stockholm, Sweden • Sydney and West Perth, Australia • Modules distributed also through Allied Radio

# We're looking for hardnosed design engineers

# who want to make the best investment in IC logic assemblies.

It's a buyer's market. Now you can get exactly the right logic cards to design your logic systems the way you want them . . . without settling for fall-out cards from general purpose computers . . . and without going to all the expense of building specials.

CAMBION<sup>®</sup> makes the odd-ball IC assemblies as standard . . . along with all the regulars. You're never stuck for the right logic card, even if you need only one. You design your systems with all compatible cards, spend less time in repeated back wiring and less time debugging back wiring. Think of

the money you'll save.

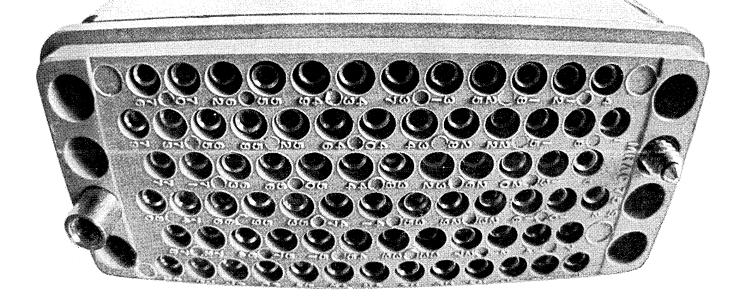

CAMBION's exclusive goldplated 70-pin input/output is

the key to your investment. It lets you bring more functions through to the outside world . . . reduces the total number of circuit connections . . . and provides for large scale integration . . . *now*.

And CAMBION's complex function logic assemblies give you more circuitry in the etch — permanently. You get more functions per card, use fewer cards and card racks and get more compact design at lower cost.

Compare CAMBION IC logic assemblies with all the others . . . card for card, function for function, capa-

bility for capability, line for line and price for price . . . you'll prove for yourself it's your best investment.

Our latest comprehensive Logic Manual has all the data. To get your copy circle the number below or write Cambridge Thermionic

Corporation, 453 Concord Avenue, Cambridge, Massachusetts 02138. Phone: (617) 491-5400. In Los Angeles, 8703 La Tijera Blvd., Phone: (213) 776-0472.

Standardize on CAMBION . . . the guaranteed logic assemblies

CIRCLE NO. 12 ON INQUIRY CARD

COMPUTER DESIGN/FEBRUARY 1968

®Reg. U.S. Pat. Off.

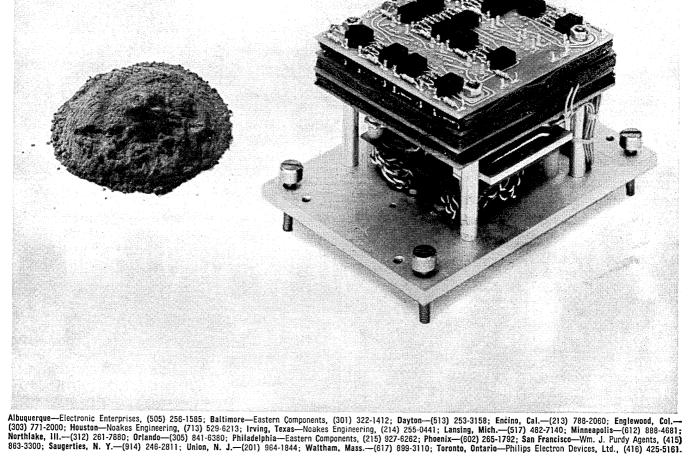

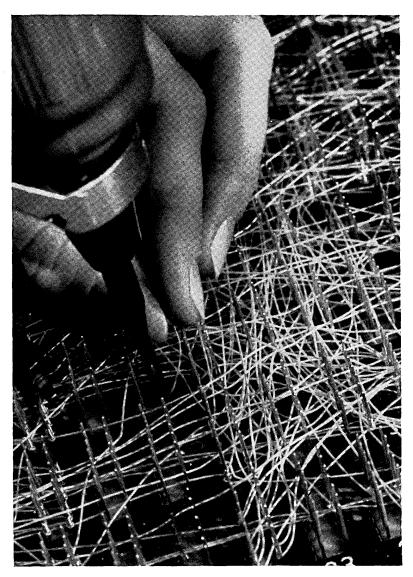

# How do you gruntle the buyer of memory stacks?

# (Take a powder and control it all the way).

The man who buys memory stacks (or planes or just cores) knows that a myriad of tiny variables which affect performance can pass right through the tightest spec. It's nobody's fault, but still it leaves the buyer disgruntled.

How to gruntle him? Well, this is what we do at Ferroxcube. We control the entire process from formulation of the powder for the cores to the planes or stacks that go out the door. To the naked eye

much of this looks like textbook vironmental requirements of MIL-QC procedure. But some of it goes deeper. It's the kind of control you associate with a veteran airline pilot whose experience amounts almost to intuition. As pioneers in ferrites and core memory compo- stacks, talk with the people who nents, we have people like that in control at every vital stage of manufacture.

This is one reason why Ferrox- Write for it today. cube can design and build to exacting requirements (example: military stacks that exceed the en- Saugerties, New York

E-16400 and MIL-E-5400). And it's the main reason why every production unit performs like the prototype you approved.

If you specify cores, planes or pioneered ferrite technology. As a conversation piece, a sheaf of technical literature awaits you.

Ferroxcube

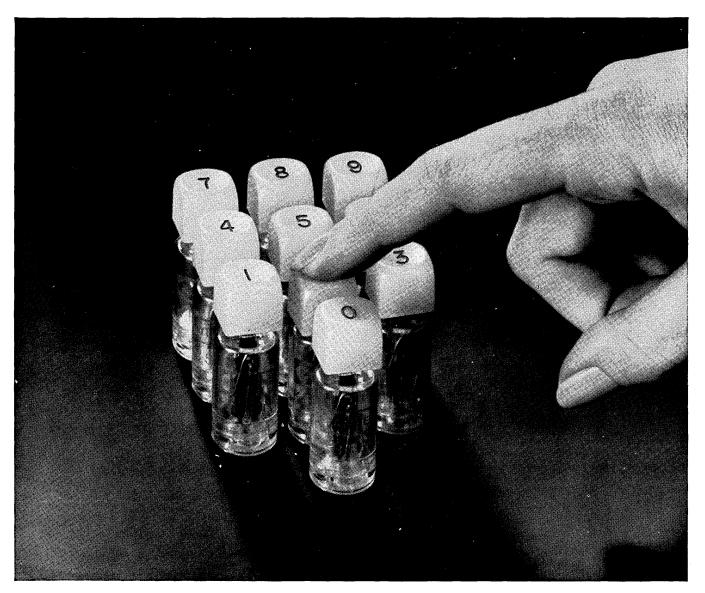

# These new keyboard switches feature unusually precise action and low-cost mounting. See for yourself—write for samples.

These elegantly styled key switches are especially suitable for computers, learning and business machines, and other advanced control equipment.

**Designed by Raytheon,** they have a featherlight touch that is precise and reliable. Just a 3-oz. touch activates the switch. Because of the unique design, this action can be repeated more than 10 million times. Yet the switches cost as little as 60¢ in production quantities.

**Raytheon key switches** are available in a wide range of standard- and custom-cap shapes, sizes, colors, and alphanumerics. The characters can be illuminated by backlighting. All switches are made of high-quality materials: stain-resistant caps; polycarbonate body parts; stainless steel springs; beryllium and stainless steel contacts. They are available in single- and double-level wipe-action types, and in dry-reed, hermetically sealed single- and double-level types.

Write for samples. For free samples, write on your letterhead describing your application to: *Raytheon Company, Industrial Components Operation, Dept. 2351-CD, Quincy, Massachusetts 02169.*

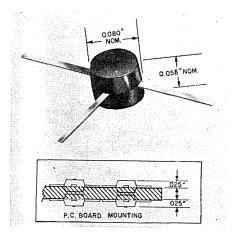

Simple, low-cost mounting. Raytheon switches plug into .125" PC board. Contact pins snap in, firmly lock switch in place for soldering. This permits you to use flow soldering techniques cut keyboard assembly time and costs.

CIRCLE NO. 14 ON INQUIRY CARD

# In 60 minutes you can add 131,072 words to your small computer's memory

Order a VRC 1104S Drum Memory System *now* for your PDP-8, 8/S or 8/I computer. (Yes, the 1104S is compatible with the new 8/I.) When the system arrives in 90 days, follow the simple installation procedures in the accompanying manual. In one hour you will have connected the 1104S to the computer, run the drum diagnostic tape (included with the manual) to test every bit of the 131,072-word capacity, and have the system on-line.

Interfacing the 1104S *is* that easy. And it's available in three versions: PCT for program-controlled transfers; DCT for 3-cycle data break; and DMAT for direct memory access transfers. You get programs for transfer of single pages or entire fields, and non-destructive drum diagnostic routines. Single-word addressing simplifies programming. And don't overlook the benefits of proven VRC reliability: design life, 100,000 hours of operation; MTBF, 15,000 hours; error rate, 1 in 10<sup>13</sup> bits.

Cost? Modest. A PCT version—with 131,072-word capacity, 8.7msec average access, and three transfer programs plus diagnostic program—is yours for \$9,950. So place your order today . . . and start dreaming up new uses for a small computer that can think big.

# Computers are known by their MEMORIES

...so is

When it comes to engineering opportunities (and the good life, North Country style), the place to come is Vermont Research Corporation. For specific information contact:

RICHARD A. STOVER Vice President-Engineering

# 6 new off-beat 21/2 D stacks.

**1** HEATED STACK — Built for a process control application, this has an extremely large bit length. (16K x 25 bits). Heaters keep the temperature a constant  $55^{\circ}C \pm 3^{\circ}C$ ; but the whole stack with heaters and large capacity only takes up 750 cubic inches.

**2** FOLDED STACK — We've built hundreds of these for SDS computers over the past year. With a 4K x 9 bit capacity, the stack uses our 20 mil cores, and turns out a cycle time of 830 nanoseconds.

(213) 772-5201

EM electronic memorie 12621 Chadron Avenue, Hawthorne, California 90250

1

**3** HIGH/LOW TEMP STACK— This 8K x 18 bit 2½ D, built for RCA, uses our special lithium cores. They have a low temperature coefficient and excellent stability over a 10°C to 55°C range. The beauty of this is that the customer doesn't have to bother with temperature compensation.

**4** COMPACT STACK WITH LARGE CAPACITY— For Honeywell, we put together a 32K x 18 bit prototype stack in a space of 600 cubic inches (10" x 20" x 3"). This stack uses our 20 mil cores and has a cycle time of less than 650 nanoseconds.

5 SPLIT MODULE STACK — This was a tricky one for Raytheon. It was a special 16K x 18 bit stack, and two sets of diode modules in the word direction had to be placed on each side of the stack. (Usually, they're all on one side.) The whole stack was designed, built, and shipped in 8 weeks. **6** NANOSTACK<sup>TM</sup>—We use this one in our large capacity NANOMEMORY system, but we've also been making a modified version for over a year and a half for Digital Equipment Corp. The stack has an 8K x 18 bit capacity and measures only  $10\frac{1}{2}$ " x  $20\frac{1}{2}$ " x 2".

If your 2½ D requirements are off-beat, call us, and we will see what we can do for you. Or write for Litpak 100 describing our stack capability.

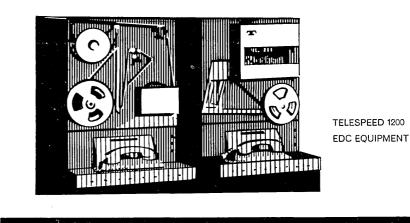

DATA COMMUNICATIONS equipment for on-line,

real-time processing

# no time for errors

Transmitting data at high speeds through large switching systems is a major factor in the effectiveness of sophisticated data systems. However, without some automatic method for detecting and correcting errors fast, an entire real-time operation could be in jeopardy.

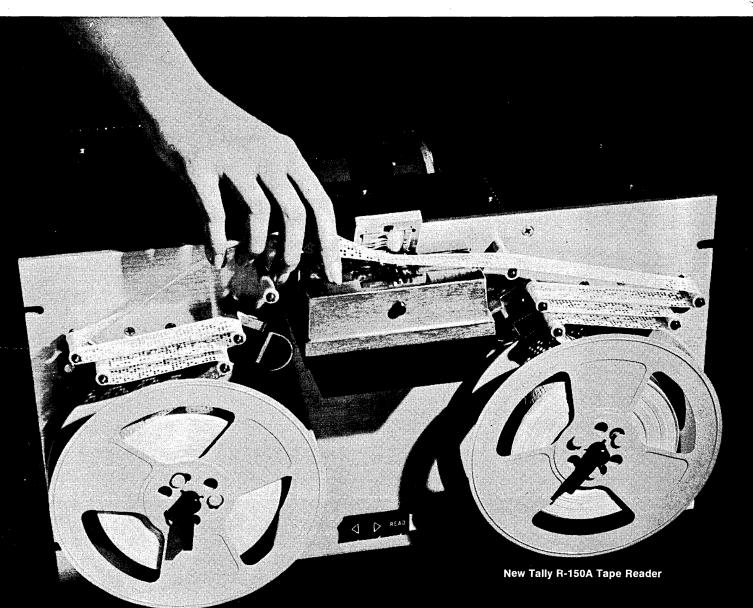

#### TELESPEED EQUIPMENT IS THE ANSWER

Telespeed 1200 EDC paper tape equipment is designed specifically to automatically detect and correct errors. It operates at 120 characters per second (1200 words per minute), or less when required. It can utilize any 5, 6, 7 or 8level code including the officially approved United States of America Standard Code for Information Interchange (USASCII).

Operation of the Telespeed 1200 EDC equipment is based on the transmission of redundant information. The sending set transmits data in blocks of 80 characters without the need for special tape format.

Two redundant check characters are generated by a separate tape-reading head on the sending set, and by a photoelectric reader on the receiving set. The two sets of characters are

compared by the receiving terminal, and transmission continues if the characters agree.

#### CORRECTING AN ERROR

When the Telespeed 1200 EDC receiving set detects an error, the tape containing the block in which the error occurred is pulled back and retransmitted. The receiving set also

machines that make data move

pulls back the erroneous tape block and overpunches all code levels prior to receiving the retransmitted block.

The fact that the two sets of check characters are generated from reading both the original tape and the output tape adds another benefit to the Telespeed 1200 EDC equipment. It not only detects any transmission errors, but also checks the accuracy of the terminal equipment.

For further information on Teletype error detection and correction equipment, send for free literature. Contact: Teletype Corporation, Dept. 71B, 5555 Touhy Avenue, Skokie, Illinois 60076.

# Reader's Choice

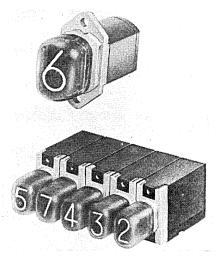

# IEE introduces 10-gun CRT Display Tube

# New readout offers 12 advantages over tubes now in use.

The state of the readout art took on a new dimension recently when IEE, world leader in rear-projection readouts, introduced the 10-gun CRT — an unparalleled method for electronic projection of numbers, letters, messages, etc. Observers report character brightness and clarity, viewed on a fluorescent screen, are optimum under any ambient light condition. Powerless control grid switching...extremely low power consumption...small grid control swing... exceptionally wide view angle... all are features which make the new device ideal for instrument applications. Now available in quantity, all it lacks is a name!

#### Name IEE's new display tube and win a portable TV set!

On your company letterhead, describe a particular application for the new tube. Then fill in the coupon, attach it to the letter and send them to:

| Sirs:                       | ADVERTISING DE<br>7720 Lemona Ave<br>Van Nuys, Calif. 9 |                |

|-----------------------------|---------------------------------------------------------|----------------|

|                             | r the new IEE 10-g                                      | un CRT display |

| tube is                     |                                                         |                |

| Name:                       |                                                         |                |

| Firm:                       | D                                                       | ept.:          |

| Address:                    |                                                         |                |

| City:                       | State:                                                  | Zone:          |

| Entries mus<br>judges' deci | t be in by Feb. 2<br>sion will be final.                | 28, 1968. The  |

# IEE bright, legible, wide-angle readouts:

Any characters desired Any colors or combinations Any input, BCD or decimal Any input signal level Any mounting, vertical or horizontal Many sizes Many configurations Many lamp lives (to 100,000 hours) Many brightness choices Many options and accessories

Standard Readouts: Rear projection principle, like all IEE readouts. A lamp in the rear of the unit illuminates one of the 12 film messages, and projects it to the front viewing screen. Unbeatable readability and versatility.

Large Screen Readouts: For reading distances up to 100 feet. Maximum character size  $3\frac{3}{6}$ ".

4 32

*Miniature Readouts:* Only 1" wide x 1-5/16" high, yet can be read at 30 feet because of clarity of one-plane projection. Character size:  $\frac{5}{6}$ ".

*Micro-Miniature Readouts:* Only  $\frac{1}{2}^{n}$  wide x  $\frac{3}{4}^{n}$  high, but 20 foot viewing distance and maximum 175° viewing angle because of front-plane display. Character size:  $\frac{3}{8}^{n}$

*Hi-Brite Readouts:* Special lens system increases character brightness 50%. Particularly good when high ambient light conditions exist.

*Cue-Switch Readouts:* Rear projection readout with push-button viewing screen. Combination switch and display device.

*Bina-View Readout:* Accepts binary or teletype code, decodes, and displays the proper character.

*Status Indicator Readout:* Displays up to 12 different messages, individually or in combination. Viewing screen only 3 sq. in.

*Indicator Assemblies:* Available with up to 11 rear projection readouts, for indicating seconds, minutes, hours, days, etc.

*Driver/Decoder Module:* Designed to work with IEE Readouts. Accepts a variety of binary codes for decimal conversion.

The new IEE Display Devices catalog gives complete information and specifications on these products, and their accessories. Ask for it.

"I-double-E", the world's largest manufacturer of rear projection readouts. Industrial Electronic Engineers, Inc. 7720 Lemona Avenue, Van Nuys, California

# keeping track of the ins and outs

Teletype data communications equipment serves as the terminals in a variety of computer systems. Many systems designers specify Teletype terminal equipment because they have found the sets to be the most reliable, versatile, and economical available.

The examples below point up the many capabilities of Teletype equipment as used in a number of different computer systems.

#### AIDS SCIENTIFIC COMPUTATIONS

Primarily designed for control applications and scientific computations, a computer that uses monolithic integrated circuits can be operated alone, as a multiprocessor system, or as a satellite to a larger computer system. A Teletype Model 35 KSR (keyboard send-receive) set is the system's terminal. It uses an 8-level code compatible with the United States of America Standard Code for Information Interchange (ASCII).

# AIDS BILLING AND INVOICING

An electronic billing and invoicing machine uses a Teletype Model 33 ASR (automatic send-receive) set to provide on-line communications involving a variety of accounting data. Continuous pin-feed invoice forms with multiple copies are used in the system. In addition, a punched byproduct tape is prepared for further analysis by management.

Users of a time shared computer system can contact the computer for service and inputs of all instructions, data, and plot programs through standard Teletype equipment. The computer processes the data and transmits via a Model 33 ASR set a complete plot program, including identification codes for that particular plotter and output signals for remote on-line plotting.

A compact 16-bit real-time computer provides high-speed data acquisition and control. The system multiplies and divides faster, has a faster throughput and costs less than many larger systems. It uses a Teletype Model 33 ASR set as its terminal.

## AIDS TO YOUR SYSTEMS

These are only a few of the many Teletype equipment applications in both large and small computer systems. To learn how Teletype equipment can aid the systems you're designing, send for our brochure, "ALL ABOUT TELETYPE EQUIPMENT." Contact: Teletype Corporation, Dept. 71B, 5555 Touhy Avenue, Skokie, Illinois 60076.

Yes. You can get every wire and cable you need for a computer system in one neat package...from Brand-Rex

You save a lot of shopping around because Brand-Rex makes:

- Back-Panel Wires

- Hook-Up Wires

- Miniature, Air-Spaced Coaxial Cable

- Power Supply Wires

- Patch Cord Wires

- Interconnecting cables and Communication Cables.

You can have just about any configuration ... single wire, round cable, ribbon cable, custom profiles ... and your choice of insulations including Kynar, Polysulfone, Teflon (FEP and TFE), PVC, semi-rigid PVC, PVC/nylon, polyethylene, foamed polyethylene, FEP/nylon, Rulan and Neoprene. Matched colors if you want. Our engineers are constantly developing new cable designs for leading computer manufacturers. So if existing Brand-Rex products don't meet your needs, we'll come up with new designs that will.

Hooking-up a computer system? Get all the wire and cable from one good source. Ask Brand-Rex.

AMERICAN TANA CORPORATION BRAND-REX DIVISION WILLIMANTIC, CHONECTICUT 62256 PHONE 203 433-777

communications equipment for on-line, real-time processing

DATA

# ... at the press of a button

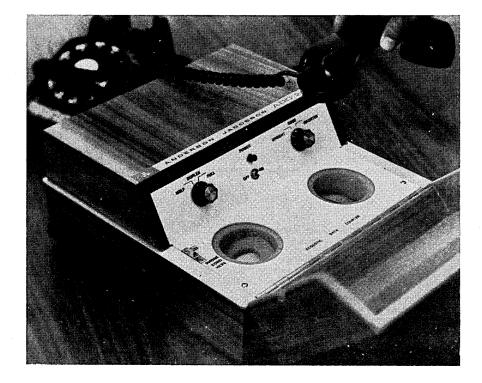

Time. In today's data communications and processing systems it is measured in microseconds. And Teletype R&D engineers know it. For instance, look at the Push Button Data Generator they have developed to cope with the situation.

The PBDG is an automatic data preparation unit that simplifies and speeds the flow of fixed data. By preprograming fixed data into the PBDG, you can automatically print up to 24 alphanumerics and other characters *by pressing a single button*.

#### AIDS COMPUTER OPERATION

The PBDG can be used wherever there is a need for automatic handling of repetitive data. For instance, in a time sharing system, the intricate instructions needed to activate the computer for a particular user can be programed into the PBDG, and transmitted automatically to the computer merely by *pressing the appropriate button.*

In addition, the PBDG offers many important advantages to data communications and processing operations. Information is stored and reproduced in the same form every time at the press of a button. Data is easily programed or reprogramed for automatic transmission of fixed data. This saves time, saves key strokes, and eliminates errors.

GENERATES 288 CHARACTERS

Operating on either a 5 or 8-level code, the basic Teletype PBDG unit consists of 12 pushbuttons capable

Cabinet at right of this Teletype Model 35 ASR set houses control panel and circuitry of Push Button Data Generator

of generating a total of 288 characters. The PBDG can be used as a self-contained unit or combined with other Teletype equipment to punch paper tape, print page copy, or transmit to a remote unit. Programing is made and/or changed simply by movement of push-on type terminals. Notechnical skill is needed to make or change a program. The unit also may be programed to stop on any predetermined character position. This permits insertion of variable information from a keyboard. After the variable data has been entered, automatic entry of fixed data is continued at the press of a button.

#### AVAILABLE IN SPECIAL CABINET

Where space permits, the PBDG control panel and its associated electronics can be housed in a Teletype printer console. When more than 24 pushbuttons are needed, special cabinets can be provided that contain as many as 96 buttons in units of 12.

For more information about transmitting your data *at the press of a button*, simply request our PBDG data sheet by contacting: Teletype Corporation, Dept. 71B, 5555 Touhy Avenue, Skokie, Illinois 60076.

machines that make data move

# The great LSI race.

While the rest of the semiconductor industry tried to squeeze enough ICs on a chip to get into the MSI/LSI business, Fairchild turned systems inside out. We were looking for an intelligent alternative to component mentality. Our investigation led to a whole new set of design criteria for medium and large scale integration devices.

# A computer isn't a computer.

It's a digital logic system. It has the same functional needs as any other digital system: control, memory, input/output and arithmetic. There's no logical reason to custom design a complex circuit for each system. That's why Fairchild MSIs and LSIs are

designed to function as fundamental building blocks in *any* digital logic system. Even if it's a computer.

A little complexity goes a long way. Anybody can package a potpourri of circuitry and call it MSI or LSI. But, that's not the problem. Why multiply components, when you should divide the system? Like we did. We found that sub-systems have a common tendency toward functional overlap. There are too many devices performing similar functions. More stumbling blocks than building blocks. Our remedy is a family of MSIs and LSIs with multiple applications. The Fairchild 9300 universal register, for example, can also function as a modulo counter, shift register, binary to BCD shift converter, up/down counter, serial to parallel (and parallel to serial) converter, and a half-dozen other devices.

# $\mathbf{W}_{ ext{atch out for that first step.}}$

There are all kinds of complex circuits. Some of them have a lot of headache potential. Especially if you want to interface them with next year's MSIs and LSIs. We decided to eliminate the problem before it got into your system. All Fairchild building blocks share the same compatible design characteristics.

We're also making the interface devices that tie them together. For example, our 9301 one-of-ten decoder can be used as an input/output between our universal

register, dual full adder and memory cell. (It could also get a job as an expandable digital demultiplexer, minterm generator or BCD decoder.)

# f Hurry. Before the price goes down.

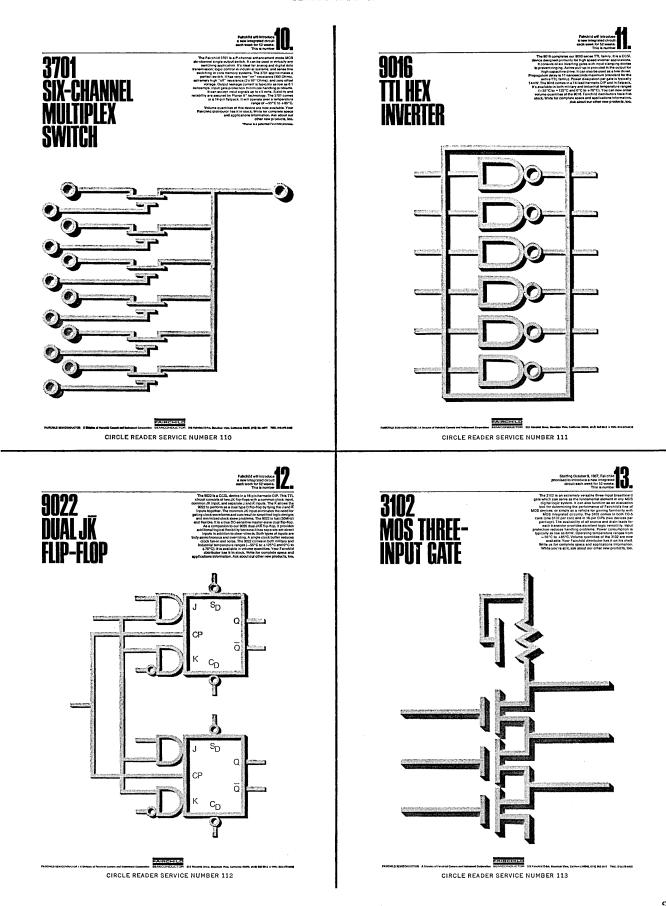

Gate for gate, today's complex circuits are about the same price as discrete ICs. But, by the time you're ready to order production quantities, the price should be a lot lower. At least ours will. The reason is simple: Fairchild devices are extremely versatile. There are fewer of them. But, they do more jobs. That means we'll be producing large quantities of each device. That also means low unit cost to you. And you'll have fewer devices to inventory. And fewer to assemble. If you agree with our approach to medium and large scale integration, we'd like to tell you more about it. There are two ways you can get additional information. One is by mail. Simply write us on your company letterhead. You can also get more data by watching the trade press. Fairchild is introducing a new integrated circuit each week for 52 weeks. (We started on October 9, 1967)

(We started on October 9, 1967.)

Many of them will be MSI and LSI. If you'd like to see the last few we've introduced, turn the page.

FAIRCHILD SEMICONDUCTOR A Division of Fairchild Camera and Instrument Corporation 313 Fairchild Drive, Mountain View, California 94040 (415) 962-5011, TWX: 910-379-6435

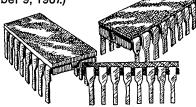

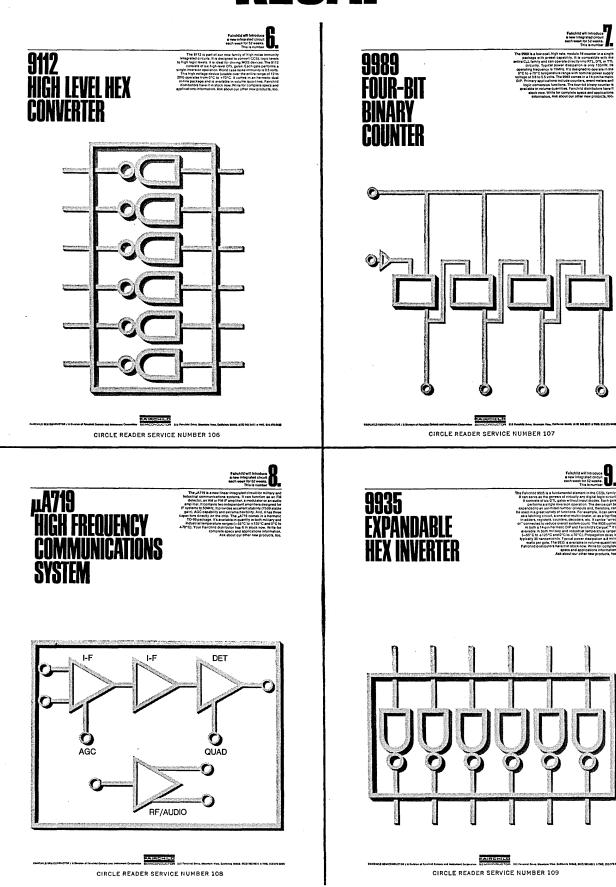

# RECAP:

### Fairchild is introducing a new integrated circuit every week. The last two months look like this.

# Having trouble communicating with the modern generation?

# HP software makes it easy.

Not only do Hewlett-Packard computers speak many common languages, but they also let you change your mind, your program and your equipment configuration —with minimum effort.

HP computers speak three higher level languages: FORTRAN, ALGOL and Conversational BASIC ... and in these languages you can perform scientific calculations or converse with the most elaborate instrumentation system. The compilers are only part of the package. A Basic Control System (BCS) simplifies programming and execution of all I/O operations — permitting device-independent programming. Assemblers (and compilers) generate relocatable code. Communication is easy on the hardware end, too — using standard plug-in cards.

The two computers — the HP 2115A and the 2116A offer a choice of memory and I/O capacity, and they're completely software compatible. Make it easy on yourself. Call your local HP field engineer for all the details. Or write Hewlett-Packard, Palo Alto, California 94304; Europe: 54 Route des Acacias, Geneva.

The 2115A Computer has 16-bit words, 2  $\mu sec$  cycle time, 4K memory. Price, including Teleprinter, \$16,500. Additional memory and options available.

COMPUTER DESIGN/FEBRUARY 1968

26

# 2400 bps data and worker...simultaneously...one line! 2400 bps data and intermediate ... simultaneously... one line! 2400 bps data and Supermissing delige...simultaneously...one line! 2400 bps data and woirce... simultanea 2400 bps data and intermore...si 2400 bps data and Supped 100111011010011101011010010001101111 2400 bps data and )100111011010011101011010010 2400 bps data a 10011101101001110101101001 MODEM 4400/24 PB 2400 bps data a 0100111011010011101011010010001 2400 bps data and waiter 2400 bps data and ieleime ... simultaneously.....

2400 bps data and SuperMiselly 色色色....simultaneously...one line!

Remember when you needed a premium-priced phone line to transmit high-speed data? And the data would use up the whole line ... no room for anything else. We've outdated all that with Modem 4400<sup>\*</sup>— the narrow band data set. Now you can transmit 2400 bps data over the lowest cost unconditioned telephone lines and, simultaneously, transmit voice conversation or up to 8 teletype channels over the same line.

Let us show you the new, low cost way to transmit data. Send for information on MODEM 4400/24PB.

Transmitting at 4800 bps? Ask about MODEM 4400/48... the narrow band 4800 bps data set.

୲୷୲୲୲ଌ୲ଡ଼

Milgo Electronic Corporation 7620 N.W. 36th Avenue Miami, Florida 33147 \* patent applied for The Kennedy model 1400/360 incremental magnetic recorder— IBM/360 compatible. Stock delivery

# \$5000.

CIRCLE NO. 24 ON INQUIRY CARD

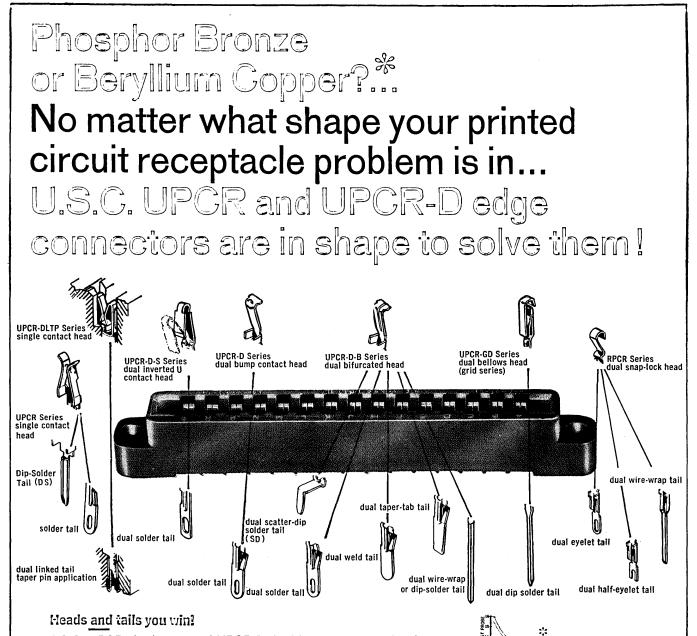

U.S.C. UPCR single row and UPCR-D double row printed circuit receptacles offer 1) high reliability, 2) excellent wiping action, 3) constant contact pressure, 4) low insertion force, 5) fool-proof contact alignment, plus...

A wide selection of contact and terminal configurations in different materials and finishes to suit every application. For example, some U.S.C. printed circuit receptacle users pressed for economy and delivery, have switched from beryllium copper to our UPCR-D spring phosper bronze contacts—with very good results. (See our comparative durability curves for proof.)

Like we said. No matter what shape or how far out your printed circuit connector problem is, call on U.S.C. ER\*\* for a down-to-earth solution. Start by writing for our UPCR-A catalog.

### \*\* U.S.C. Established Reliability can do!

Meet all applicable provisions of latest version of MIL-C-21097

U.S. Pat. 2,853,689, 2,909,755

U.S. COMPONENTS, INC.

1320 ZEREGA AVENUE • BRONX, N.Y. 10462 or use TWX: 710-593-2141: TEL: 212-824-1600 TELEX: 01-2411: or Cable: COMPONENTS NYK. ទំនើទំនឹង

CONTACT #1901-1

5 10 15 20 25 30 35 OF INSERTIONS & WITHDRAWALS OF

> COMPARATIVE DURABILITY CURVI UP TO 50 CYCLES CONTACT #1901 & #1901 1

> > :::

ZE VB. BERYLLIU

NTED CARD RECEPTACLES

COMPARATIVE DURABILITY CURVE UP TO 5000 CYCLES CONTACT #1901 & #1901-1

# Now-save vital space with 30-gauge hook-up wire

General Electric saved space and weight in wiring the back panels of its GE-PAC® Process Computers by using 30-gauge hook-up wire insulated with Kynar.

# ... Made with tough, durable Kynar<sup>®</sup>

Thirty gauge wire is nothing new... but what is new is wire insulated with Kynar, the fluoroplastic that's tough. It has twice the cut-through resistance of other fluoroplastics, cuts and strips smoothly, takes 180° bends without splitting, stands up to the punishment of automatic wiring machines or semi-automatic hand tools.

What's more, Kynar resists cleaning solvents, won't degrade with age, and operates at temperatures from  $-80^{\circ}$  to  $300^{\circ}$ F.

For samples of 30-gauge wire insulated with Kynar plus information on how you can save space, reduce weight, write Plastics Department, Pennsalt Chemicals Corporation, 3 Penn Center, Philadelphia, Pa. 19102.

# Kynar...the fluoroplastic that's tough! { PENNSALT

CIRCLE NO. 26 ON INQUIRY CARD

COMPUTER DESIGN/FEBRUARY 1968 CIRCLE NO. 27 ON INQUIRY CARD →

WA varian / DATA MACHINES

It's no longer \$30K and up to give your system big computer power.

The DATA 620/i comes in at less than onehalf that amount. And it gives you more raw computer muscle than the \$30K machine.

It's because the DATA 620/i was designed from scratch for *systems* work, no double-duty design, no we-cover-the-waterfront philosophy. It's a pure, lean computer for systems.

Fully IC'd for reliability and small size, the DATA 620/i handles 16 and 18 bit words, operates at 1.8  $\mu$ sec speed, with more than 100 basic commands and a 4K to 32K word memory. It comes with Party Line I/O, complete software proven out by the DATA 620, and a full selection of peripherals and options.

We know of more than 300 systems that couldn't afford not to have the DATA 620/i, because that's how many we sold in the first six months. We'd be happy to show you what it can do for your system, or at least send you our illustrated brochure full of functional and operational information. Just call or write.

# Now that the DATA 620/i computer is out can you afford <u>not</u> to use it in your system?

We need Senior Development Engineers and Programmers. Write to Mr. Bruce Ferris.

1590 Monrovia Ave., Newport Beach, Calif. TEL. (714) 646-9371 TWX (910) 596-1358

The advanced research and development we do here calls for engineers who can work effectively in two worlds. Engineers who have a solid knowledge and interest in contemporary technology, but who also have a curiosity and open mindedness towards new ideas and techniques.

If you enjoy working with contemporary and advanced technology, you'll appreciate the opportunities at Honeywell. Openings are available throughout the entire spectrum of computer technology, with special emphasis on the following.

# PRODUCTIVE RESTLESSNESS

# HARDWARE & SOFTWARE DEVELOPMENT

#### **Design Automation**

Provide analysis and programming, as related to digital logic design (simulation, logic synthesis, interconnection techniques). Analyze requirements of automated engineering documentation. Provide analysis and programming to automate Engineering Manufacturing interface. Specifically, your interests might be in one of the following areas:

DIGITAL SYSTEMS SIMULATION, AUTOMATED ENGINEERING DOCUMENTATION, AUTOMATED INTERCONNECTION TECHNIQUES, NUMERICAL CONTROL APPLICA-TIONS. Openings exist at all levels.

#### **Power Supply Design**

A highly challenging and pioneering effort in design and development of power supplies for computers and peripheral devices, demands outstanding individual capabilities as well as complete familiarity with current and advanced designs and components. Duties will involve circuits for future systems, analyzing component circuits and related activities encompassing design and development. Familiarity with magnetic circuit design would be helpful, but not mandatory. Minimum BSEE degree with at least 3 to 5 years' design experience.

#### **Advanced Memory Design**

Broadly, the assignments involved are concerned with investigations into advanced memory and circuit techniques. Specifically, we have a strong interest in the development, design and evaluation of high-speed ferrite core wire and planar memories. If you have an MS or BSEE and 2-5 years' circuit and memory design background, this position is an excellent advancement.

#### **Digital/Analog Circuit Engineers**

Senior and junior engineers to perform and recommend circuit design and tests of high performance magnetic recording systems. Previous experience or familiarity with solid state circuits and system test would be helpful.

#### **Logic Design Engineers**

Duties involved cut across several technical disciplines and include creation of functional specifications of peripheral equipment controls and central processors; feasibility analysis for proposed systems; determination of the logical sequences of machine operations; determination of circuit and other hardware requirements; improvement of design processing methods and the supervision of prototype test efforts. 1-3 years' of related experience in digital systems planning and specifications.

#### **Mechanical Engineers**

To perform in the design, development and testing of small, precision electromechanical devices from bread-board model to finished product. If you have a background of 2-4 years' in product-oriented design with experience in one or more of the following areas — high speed mechanisms, linkages, position transducers or computer peripherals, this is an excellent opportunity to perform original and vital development.

#### Systems Analyst

#### Marketing

This position requires a minimum of 2 years' EDP experience, preferably in computer sales, systems or systems implementation. Experience as a Marketing Analyst or Financial Analyst would be very appropriate.

#### Software Development

Current expansion plans have created openings at all levels of experience and background. These positions provide excellent personal and professional advancement opportunities within our Programming Systems Division.

#### Component Engineers

A knowledge of semi-conductor theory as applied to both semi-conductor properties and circuit design theory is necessary, so that devices can be adequately chosen and specified in conjunction with circuit design engineers. Experience in quality and reliability analysis of integrated circuits is desirable. Should be capable of conducting informal circuit design reviews with the responsible circuit design engineers to insure that reliability goals have been met. BS in Physics or EE with some experience in semi-conductor evaluation and applications.

#### **Systems Engineers**

Participate in synthesis, analysis, design, specifying, evaluating and development of new Honeywell central processor and peripheral equipment. These are excellent career and personal growth opportunities for individuals at all levels with related experience.

#### **Circuit Design Engineers**

To perform design of circuits and logic for manufacturable equipment, to design and evaluate sensor systems. Related experience in all or any of these areas would be helpful. Qualified BSEE's will find a selection of opportunities to further their experience and careers.

#### **Electrical Engineers or Physicists**

To do advanced research improving the technology concerning electro-magnetic heads. This will involve design and development and new concepts in head development. 3-5 years of related experience would be necessary.

#### Maintainability Engineer ----

#### Electro-Mechanical

The responsibilities involved include establishing maintainability goals, the planning and directing of maintainability programs, performing trade off studies and participating in maintainability studies. In addition, you will interface with our production and field organizations. A BSEE or ME with previous experience in maintenance support is a necessity.

#### **Programming Business Administrator**

This position is a natural for an administrator with 1 to 3 years' experience in a design-oriented atmosphere. Ideally the CREATIVE administrator we seek should have a technical background and an MBA or studying toward an MBA. The equivalent in experience would be perfectly acceptable.

#### IEEE INTERVIEWS

Available with Mr. Curt Collison in New York City. During the show (March 18-21), Mr. Collison can be reached at (212) LT-1-3318. If you desire to set up an appointment at this time for the IEEE Show, please call Mr. Collison (collect) (617) 891-8400.

If unable to meet with us at this time, please forward your resume to  $\operatorname{Mr.}$  Curt Collison

# ELECTRONIC DATA PROCESSING

200 Smith Street Dept. C D-2 Waltham, Massachusetts 02154 Opportunities exist in other Honeywell Divisions. Send resumes to F. E. Laing, Honeywell, Minneapolis, Minnesota 55408. An Equal Opportunity Employer.

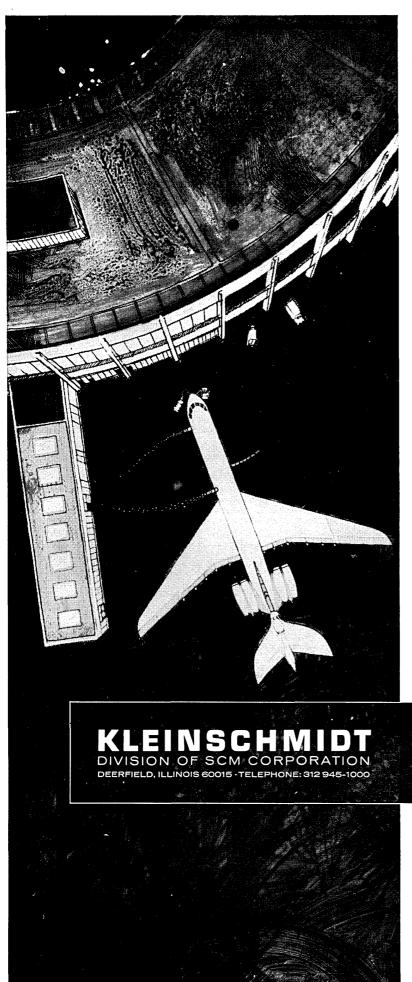

BOAC wants confirmation in print of every passenger reservation made anywhere in the world. Right now.

# Easy, when you ask Kleinschmidt.

Kleinschmidt is the language of modern telecommunications.

Home offices talk to division headquarters. Computers talk to production control. And in the case of BOAC, Kleinschmidt data printers in ticket offices provide passengers with fast, convenient flight reservations and confirmation.

Working in communications systems like BOAC's, the Kleinschmidt  $311^{TM}$ Data Printer "talks" with unbelievable speed and simplicity. It prints-out up to four times as fast as most other teleprinters. Operates with far fewer moving parts and far more reliability. *Outperforms* all competition.

And like other Kleinschmidt data printers, the 311 is compatible with telecommunications equipment of all makes. It can fit directly into the system you now have, or the one you are having designed for you.

Of course, Kleinschmidt is a language most original systems manufacturers already understand.

But we're always glad to repeat the message.

# commentary

Comments and opinions on topics of current interest to digital design engineering personnel. A monthly column organized and prepared under the direction of **T. PAUL BOTHWELL, Contributing Editor.**

# A Case for Military Application of Commercial, General-Purpose Digital Computers

R. P. BERKOWITZ, Manager, Product Assurance Dept. H. A. DELLICKER, Manager, Data Control Systems Section Computer Control Div., Honeywell, Inc.

Military people have generally been excluded from the advantages of commercial, general-purpose digital computers. Commercial computers are low in cost, flexible, available, backed by full system support, and field proven. Military users' problems and applications have much in common with those of commercial users, but the former are restrained because they cannot supply stable, air-conditioned, vibration-free environment for the equipment.

In recognition of the variety and extremes of the military environment, specifications have been developed (MIL specs) to ensure a guaranteed base of performance in military applications. Computers designed to comply fully with these specifications are usually limited in their general capabilities and intended for one function only. And because few are built for any one application, their cost is high.

It is our contention that commercial computers, without any loss of their advantages, can be used in operational military applications through relatively minor mechanical modifications.

### Certain Mil Specs Conformed to as a Matter of Course

In good commercial-computer companies, quality control practices conforming to MIL-Q-9858 are usually standard. Close attention is paid to certain military specifications, such as MIL-E-16400, for standard commercial parts procurement and manufacturing processes.

Modified or reconfigured to meet military specifications completely, a high-speed, general-purpose computer will perform the same functions as its commercial counterpart using existing documentation for spare provisioning maintenance, diagnostic routines, and other items of standard documents.

#### **Modification Requirements**

The primary purpose in reconfiguring the commercial machine is to have it function in extended operational environments and to accomplish this with no effect on operational capabilities.

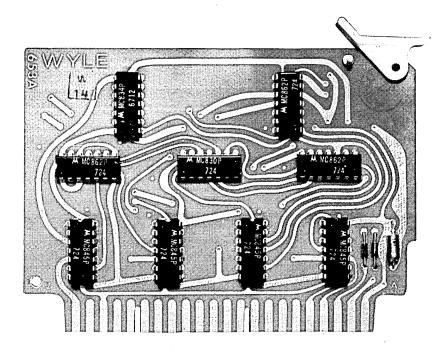

The wiring portion of the computer and the logic cards must remain the same, since they comprise the heart of the machine. Modifications in this area would cause expensive changes in manufacturing processes, software packages, and diagnostic routines.

The reconfigured version has to achieve as near a nonresonant system (below 500 cps) as practical to meet long-term vibration specifications. This has to be achieved while keeping maintenance a simple task, with full access through the front door. Also, each logic card must be removable within two minutes.

Electromagnetic interference suppression must be designed as an integral portion of this modification. Maintainability and full control-panel accessibility have to be possible while meeting the EMI specification MIL-STD-826A.

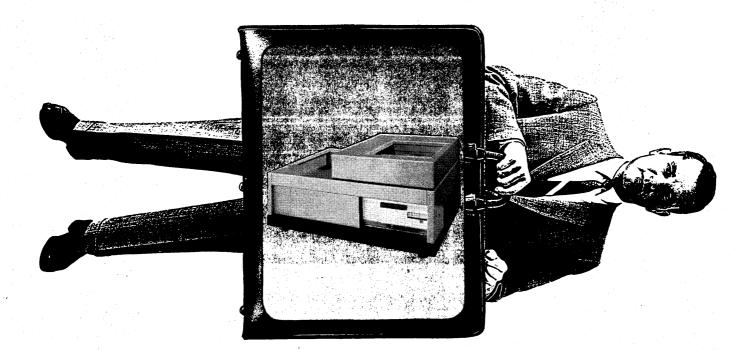

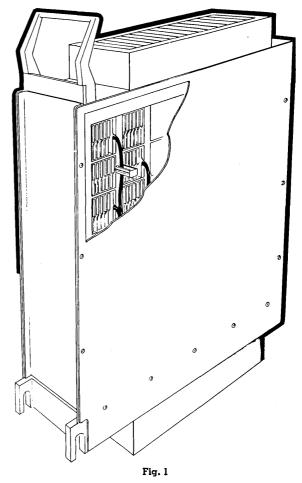

#### **Typical Modification Techniques**

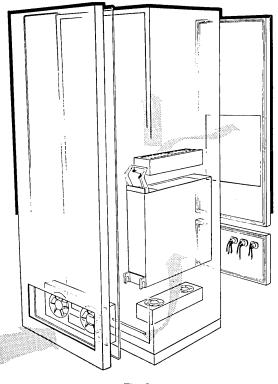

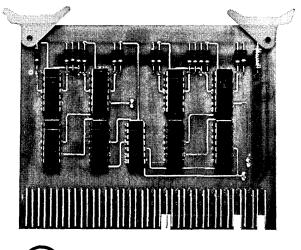

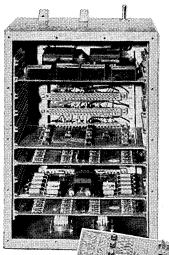

Shown in Figure 1 is a tilt-out drawer in a typical commercial general-purpose computer. The drawer, redesigned to mil-spec shock and vibration requirements, incorporates the standard wired portion of the machine and the standard printed-circuit logic modules. Internal bracing is used to secure the logic cards.

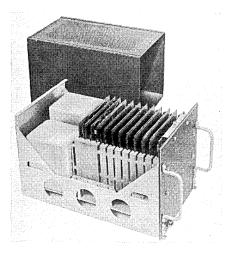

Shown in Figure 2 are four cooling fans which operate in a push-pull fashion with each tilt-out drawer. The fan assemblies, designed to incorporate 50/60 or 400 Hz fans, do not provide any structural support other than to accommodate the fans, whose direction can be reversed to effect various cooling conditions.

The cabinet, a steel enclosure of welded construction providing structural support for the internal parts of the computer, also serves as a shielded enclosure and comes with wire-mesh gaskets (See Figure 2). The cabinet can have casters, leveling feet, lifting eyebolts, and the like, as required.

As a shielded enclosure, the cabinet meets the EMI requirements stated in MIL-STD-826A. A modified

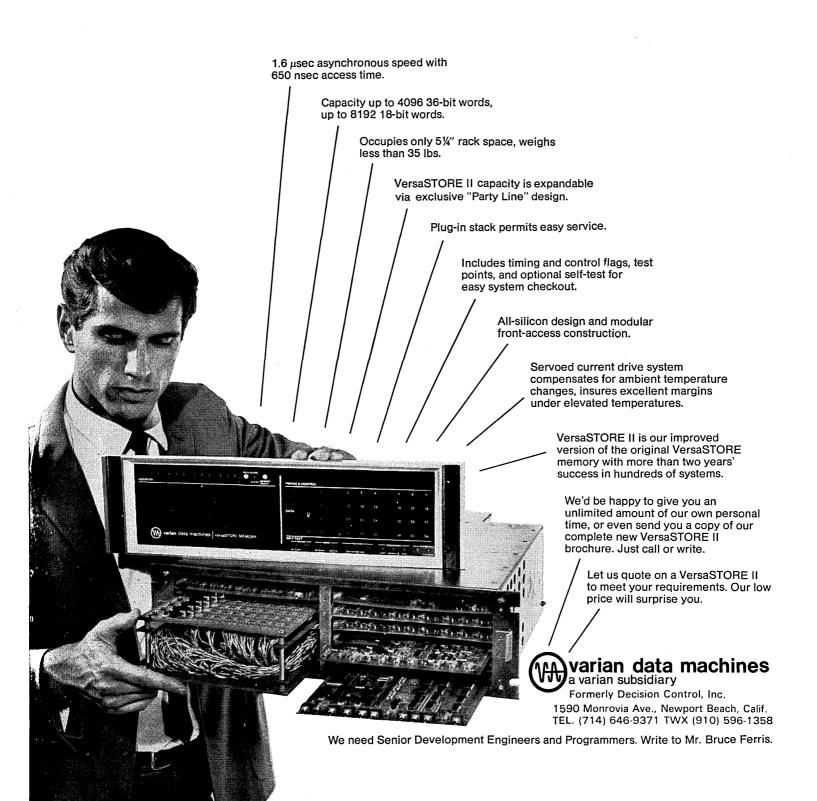

# The new VersaSTORE II core memory system can give you all the speed, capacity, and convenience you'll ever need.

## It can also save you a few bucks.

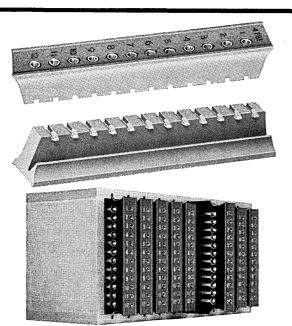

## **Save time** in testing and trouble-shooting

## New, convenient test point strip also serves as PC board handle

This unique component offers ready access to desired portions of the circuit without the use of jumper cables. Rapid mounting is accomplished by manual positioning, and the unit is secured permanently in the wave solder operation.

Low-loss polyamide body provides insulation resistance greater than 200 megohms after MIL-T-5422B humidity test. Individual test points rated 5 amperes maximum current capacity. Operating voltage 1500 volts RMS at sea level, 350 volts RMS at 50,000 feet. Contact resistance under 2 milliohms. Capacitance between two adjacent jacks less than 1 pf at 1 MHz. Special sizes for specific application requirements are available in production quantities.

Write today for more information on this and other E. F. Johnson quality electronic components.

control panel can be provided that is fully accessible and maintains full EMI suppression during all computer operational modes. Cabinet penetration can be accomplished with EMI connectors located on a connector panel (Figure 2), through which all input/ouptut lines are routed. Power-line filters can be part of the connector-panel assembly or located elsewhere. Air intake and exhaust ports are shielded to allow adequate cooling while maintaining EMI integrity.

A blower system in the cabinet maintains an internal positive pressure. During maintenance, when the tilt-out drawers are extended, sufficient air is forced through the drawer assembly to maintain normal operating temperatures. An alarm circuit indicates the loss of critical cooling air.

## Various Modified Computer Configurations and Applications

Commercial computers can be modified in many ways to meet a wide variety of military applications. These are some of them:

1. Electromagnetic interference suppressed — This configuration can be used for fixed ground installations where electro-magnetic interference suppression is required, but with a laboratory ambient environment. A standard computer is reconfigured to the extent necessary to achieve EMI suppression to MIL-STD-826A. Internal modifications include the shielded enclosure, control panel, grounding buses, and power-line filters.

2. Ruggedized — This configuration can be used for applications in aircraft, shipboard, and van-mounted installations. It includes an internal structure designed

COMPUTER DESIGN/FEBRUARY 1968

Fig. 2

to meet increased shock and vibration limits. Modifications are limited to the structural design.

3. Ruggedized and EMI suppressed — This configuration can be used for applications where shock, vibration, and EMI are part of the operating ambient environment. It encompasses configurations (1) and (2). Computer systems with these modifications can be packaged in either full-rack or half-rack cabinets.

#### Summary

The flexibility inherent in the real-time, high-speed digital computer allows trade-offs between input/output capability and computational requirements, between programming costs and hardware options. Memory size can be tailored to actual requirements.

The modified computers retain all the capabilities of the commercial version — software, price, delivery, flexibility, and proven design — while meeting the operational requirements of the military user. Other advantages are:

1. Availability of optional features — Present and future options can be incorporated. New government-sponsored development programs need not be undertaken. 2. Faster familiarization — The contracting agency can usually obtain a regular machine in advance of the modified one for systems-integration studies and familiarization.

3. Service support — The supplier's existing service organization can usually support the requirements of the user.

4. Lower price — The developments costs of the standard commercial computer have been amortized over the total number of computers manufactured for all uses. These savings are passed on to the military contracting agency.

5. Spare parts — The modified computers use the standard commercial logic modules and subassemblies.

Fat Model 0330

### Your "cup of tea"? Use it for Vacuum or Air Pressure

#### This little "tempest in a tea cup" has surprising capacity. Rotor diameter is just larger than a penny! Yet it delivers up to .35 cfm with 1/40 hp motor—or

Yet it delivers up to .35 cfm with 1/40 hp motor—or .67 cfm with 1/25 hp! Designed for portable instruments, air samplers, con-

trols—lab or field use. Oil-less construction—absolutely oil-free air. Vacuum to 22" Hg—pressure to 10 psig. AC or DC motors. Why not investigate? Model 0330 may be *your* "cup of tea!"

Send today for Gast Catalog.

#### Gast Manufacturing Corp. P.O. Box 117-Y, Benton Harbor, Mich. 49022

CIRCLE NO. 32 ON INQUIRY CARD

RCA's CSP-III communications processor. The computer will be used to perform circuit switching functions now performed by discrete hardware components.

### INDUSTRY NEWS

AUTOMATED CARGO FACIL-ITY — A new \$1.5 million automated cargo distribution center was opened this month in Atlanta by Eastern Airlines. Designed, engineered and installed by American Machine & Foundry Company (AMF), the high speed facility can handle more than 400,000 pounds of cargo a day. with a peak-hour capacity of 150,000 pounds. It can accommodate 20 simultaneous flight arrivals and departures, and automatically separate shipments for 18 primary destinations.

The entire 32,000 square foot cargo handling facility is controlled from a unique console computer/digital dial-a-system unit built by AMF specially for the Eastern facility. The console, manned by two men, controls and monitors all conveyor belts and the sortation system.

From the console position, the supervisor-operator can direct the entire cargo handling operation, including the retrieval of cargo in secondary lanes scheduled for later flights. This cargo can be directed to primary lanes for immediate shipment, to makeup tables for consolidation in pallet shipments, or through the sorting system for rescheduling.

In the second console position, a programmer using keyboard controls can instantaneously reprogram the system to meet increased and varied capacity and distribution needs. From the console's computer readout, he also obtains total shipment weights for transmittal to flight operations.

AUTOMATED STOCK QUOTA-TIONS — The Board of Governors of the National Association of Securities Dealers recently announced its approval of a com-

prehensive plan to develop an automated quotations system for the vast over-the-counter securities market.

Envisioned in the project is the use of electronic data processing equipment in combination with communications facilities to produce a three-level system responsive to 350,000 inquiries in any given eight-hour trading period and designed to aid both customers and professional traders in the OTC markets.

A Level I service, which is aimed at the requirements of registered representatives and securities customers of retail sales firms, will supply a current representative bid and asked quotation for any security registered in the system. This current representative bid and asked would be supplied initially through the more than 25,000 interrogation display units now in use by broker / dealers throughout the country. Additional display units would be supplied later to meet the growing needs of the industry.

#### **VARIABLE COMMUNICA-TIONS SYSTEMS**—RCA has announced receipt of a \$8 million U. S. Navy contract to develop a computer-controlled system that will enable shipboard communications to be reconfigured in minutes.

Called the Interior Communications System (ICS), the system will allow a ship's internal communications to be completely rearranged by simply changing computer programs instead of rewiring the system as is now necessary. ICS is being developed by RCA's Defense Communications System, Camden, N. J., for the Naval Ship System Command.

Heart of the system will be

LSI ARRAYS — Several large scale integrated circuits were described to the International Solid State Circuits Conference this month by Dr. Clare G. Thornton, director of research and development for Philco-Ford Corporation's Microelectronics Division in Blue Bell, Pa.

The LSI arrays include a 1024bit read-only memory (ROM) containing 1,250 transistors on a 70 x 100 mil chip and a 16 x 16 random axis serial memory containing 1,400 transistors on a 100 x 120 mil chip, plus an experimental 2048-bit memory (presently under development) containing 12,000 transistors on a 117 x 117 mil chip designed to operate at speeds in excess of 5 MHz – all in MOS; and a dualfunction bipolar complex array containing 400 components on a 110 x 88 mil chip and designed to operate either as a four-stage binary counter (divide by 16) or as a BCD counter (divide by 10) by changing the logic level of a control input.

Dr. Thornton also described methods whereby LSI circuits can be assembled by the silicon wafer-chip technique to produce monolithic subsystems containing as many as 120,000 transistors as a single system. This technique bonds individual LSI chips face down onto a silicon wafer containing a high density of interconnections which are produced by the same basic process as that used on the silicon chips.

In the wafer-chip assembly, Dr. Thornton said, level of complexity and cost per functional element are determined directly by the achievable component density on a given chip. He said key technological determinants for increasing this density include smaller geometry, multi-layer metalization, thin epi layers and shallow diffusions, choice of circuit form, pad locations, and operating voltage.

38

## A word to the do-it-yourself module builder:

## Don't.

Buy our J Series modules instead.

The J Series is our new family of general purpose, all integrated circuit logic modules. Their performance almost matches that of our famous T Series modules,

These will cost you less.

but they cost about 25% less. They're made to the same dimensions as the T Series, with the same 52 pin connectors, so they're physically interchangeable. We make them for our own seismic recorder systems, so they're rugged and reliable. Now, as of January, you can buy them (complete with mounting hardware, racks and power supplies, if you wish) in any of 25 different functions.

And save yourself the time and cost of making your own: designing, assembling, testing, new procedures, new equipment, new personnel, additional training, to say nothing of the added paper work.

If you're building systems, you must have better things to do than go into the module assembly business. Such as reading our J Series catalog. It's free.

## INVAC PERFORATED TAPE INPUT/OUTPUT SYSTEMS

INVAC Tapemaker Systems range from comprehensive I/O Typewriter-Punch-Reader Consoles to relatively simple desk-top units. Typical applications include check-out systems, computer programming, and data logging; machine control, data processing, and tape duplication.

- ... Many Standard Options Available

- ... Customized for Specific Applications

- ... Full Operational Mode Flexibility

- ... Complete Code Compatibility

- ... On Line or Off Line Capability

MODEL PKP-200 Keyboard-Punch Tapemaker is a tape preparation system designed for machine composition in the typographic industry. Readily customized for all tape making applications.

Write for Data.

26 Fox Road, Waltham, Massachusetts 02154 Tel. (617) 899-2380

Systems Incorporating TAPE PUNCHES READERS AND HANDLERS PHOTOELECTRIC KEYBOARDS I/O TYPEWRITERS AND PRINTERS CIRCLE NO. 34 ON INQUIRY CARD "In order to determine the expected level of improvement more precisely," Dr. Thornton said, "specific LSI circuits have been subjected to progressive design analysis incorporating what are considered to be a modest level of first, second, and third generation improvements, as related to the indicated determinants.

"Second generation technology, which requires no further technological advances beyond those already demonstrated, permits 1250-2500 bits of serial shift register per ship, or 500-1000 gates per chip (general logic). Third generation technology, represents a reasonable extrapolation into the early 70's and will allow more than 5000 bits and 2000 gates respectively.

"In each case new design rules have evolved incorporating the expected improvements, and a sufficient portion of the circuit and system topology drawn and, where necessary, fabricated, to measure the allowable complexity improvement."

Dr. Thornton reported results of the analysis derived from MOS circuit layouts, both for shift registers (best case) and arithmetic units (worst case).

Using this analysis to predict improvement in component density, he said an increase of X8 for bipolar and X16 for MOS are virtually certain.

SALES OF MEDIUM-SCALE **COMPUTERS TO SLACKEN: IN-CREASED SHIPMENTS OF RE-MOTE TERMINALS SEEN** — "During the next five years, there will be a significant shift in the distribution of computers by size. Medium-scale machines - those with monthly rentals in the \$5,000 to \$20,000 range — will decrease from the present 51% of the total value of computers installed to just under 28% in 1972. The distribution of large computers, during the same period, will increase from 32% in 1967 to over 48% in 1972." These estimates, which reflect the increasing use of small computers and the growing trend toward terminals on-line with giant computers, were given during a one-day briefing session for investment analysts conducted by EDP Industry Report, the semimonthly newsletter published by the International Data Corporation for executives concerned with the electronic data processing industry.

Throughout the meeting, a phenomenon termed the "IBM ripple effect" was pointed out by IDC speakers. "What IBM does - or, significantly, what it choses not to do — is one of the most important criteria upon which other companies base their marketing strategy," notes Patrick J. Mc-Govern, president of IDC. "This is true not only in the case of main-frame manufacturers," Mc-Govern points out, "but also in the case of peripheral equipment manufacturers, software houses, leasing companies, and service bureaus."

۱

i

4

The primary reason for this, the investment analysts were told, is the simple fact that IBM computers account for over 73% of the monthly rental value of all installed computers made by American manufacturers. And the situation is not likely to change, since IBM has almost 76% of all computer orders now on manufacturers' books.

#### **Growing Software Market**

In an examination of software suppliers, IDC Vice President John P. Breyer pointed out that the market for independent companies has been relatively small, representing only \$180 million of an estimated \$5 billion spent on software during 1967. The market for independent software suppliers, however, is estimated to grow to about \$1 billion out of the \$11 billion that will be spent on software by the year 1972. The independents are expected to be strongest in supplying proprietary packages and specialized applications software.

Breyer noted that most successful software firms fall into two distinct categories: Those with less than 100 employees and those with more than 1000 employees. As companies grow, he explained, there is a loss of management contact with the technical employees, and fragmentation is likely. This is particularly true because low capital requirements make it relatively easy for personnel to spin off and develop a new software company. Companies which reach a large size usually do so through acquisitions, and are quite widely diversified into such activities as service bureaus and/or education services.

ł

One big trend pointed out in the briefing session is that toward a rapidly expanding market for the independent peripheral manufacturer, especially for online terminal equipment. Remote terminals accounted for about 6% of the value of computer equipment shipped in 1967, or approximately \$350 million. By 1972, when computer equipment shipments are expected to increase from 1967's \$5.9 billion to over \$11 billion, the value of remote terminal shipments is expected to increase to 15%, or about \$1.75 billion.

"DID HOMER WRITE BOTH THE ILIAD AND THE ODYS-SEY?" — This question long has been a source of debate among classicists and philologists. However, they may be closer to agreement. Tufts University Prof. Frank P. Jones has subjected the masterpieces to the critical scrutiny of an IBM 1130 and concluded that Homer was the single author.

Jones, a professor of classics and a psychological researcher at Tufts, has spent the past two years studying the distribution of metrical patterns (hexameter patterns) in Homer's famous works.

Employing the computer to do the hackwork of counting, arranging, indexing, and composing, he arrived at a conclusion that will endear him to allunitarians, those scholars who attribute both epics to the 850-B.C. poet.

His findings were presented at the recent annual meeting of the American Philological Association in Boston. A session on Computer-Oriented Classicists gave an official blessing to the value of Jones' computer approach.

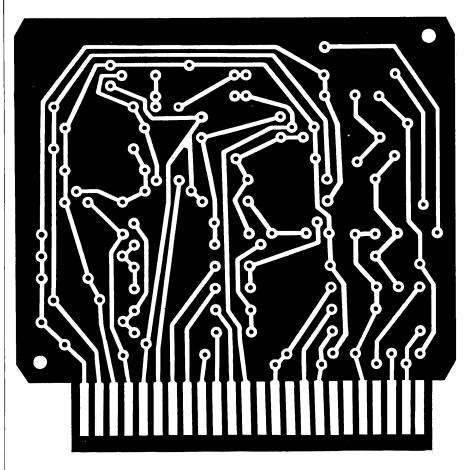

## The Clearest Logic:

Logic modules are built on printed circuit cards. Hole location and front-to-back registration must be very accurate for machine assembly. Hand assembly is costly. Plated thru-holes must provide positive continuity. Rejects are costly. Circuit boards for logic modules must be easily solderable. Poor solderability is costly. Printed circuit cards must be delivered in volume quantity for large-scale logic module production. Time delays are costly.

These are the reasons that Cinch-Graphik boards are built with such exacting precision. **Anything less is too costly.**

CONSISTING OF CINCH MANUFACTURING COMPANY, CINCH-GRAPHIK, CINCH-MONADNOCK, CINCH-NULINE, UCINITE (ELECTRONICS) AND PLAXIAL CABLE DEPT. CIRCLE NO. 35 ON INQUIRY CARD

Get the fastest solid state transfer switch anywhere — TRW's Minuteman.

It transfers power in a MAX-IMUM of ONE-FOURTH cycle! That means you'll have virtually uninterrupted power.

Use it for electronic controls, computers, communication systems or process instruments—wherever you need the highest reliability.

Minuteman switches are fast, dependable and maintenance-free. Built with the same care we use for Minuteman missile components.

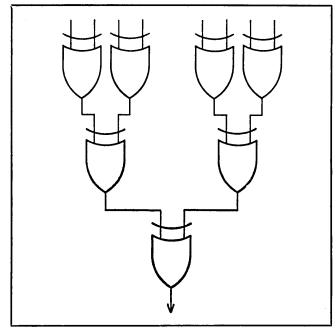

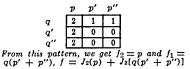

To find out more . . .