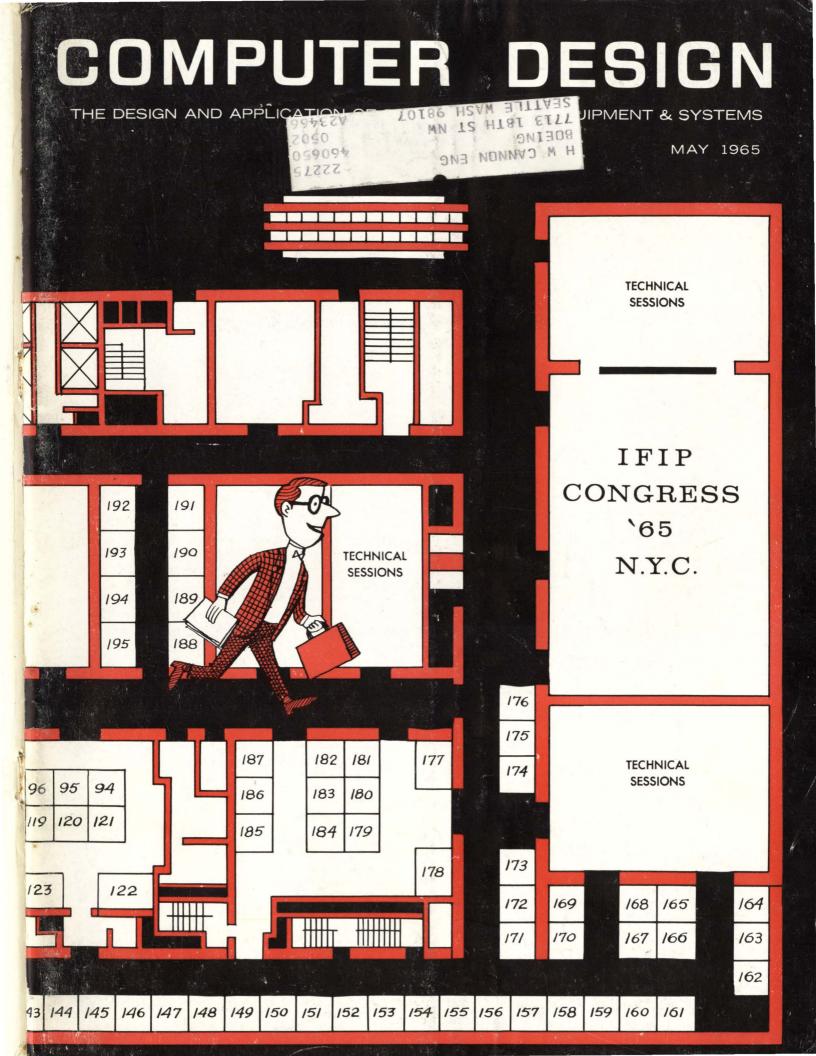

## TOM 35 MEMORY

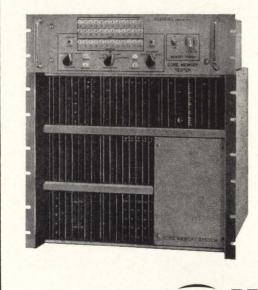

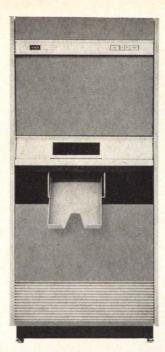

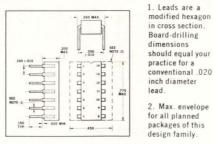

New TCM-35 family of coincident current core memories offers 1.4 to 2  $\mu$ sec full cycle times, 1.2  $\mu$ sec maximum half cycle time, and 0.75  $\mu$ sec maximum access time. Capacities up to 8,192 words; word lengths to 36 bits. All silicon circuitry. Advanced system design. Extremely compact packaging. Low input power. System height is 24<sup>1</sup>/<sub>4</sub> inches to 35 inches, including self-contained power supply, depending upon storage capacity and options. TCM-35, like the 5 microsecond TCM-32, has pull-out, front-of-rack access. Operating temperature is from 0°C to +50°C with broad margins. 3C quality is built in. Modular design allows custom selection of desired performance and interface characteristics from an extensive list of standard options at volume production prices. Write for TCM-35 brochure (for 5  $\mu$ sec memories, ask for TCM-32 brochure).

General Purpose Front Access TCM-35

#### **BASIC TCM-35 FEATURES\***

1.4-2 **USEC**

CORE MEMORY

Choice of Input/Output Logic Levels and Polarity

#### OPERATING MODES

Clear/Write Read/Restore Load Unload Read/Modify/Write

#### CONTROL INPUTS

Address Register Clear Information Register Clear Full Cycle/Half Cycle Hold Address

#### CONTROL OUTPUTS

Memory Busy Information Available End of Cycle

NON-DESTRUCTIVE START-UP/SHUT-DOWN BUILT-IN MARGINAL TEST

\* no extra cost

VOLTAGE FAILURE SENSING BUILT-IN COOLING SYSTEM

#### STANDARD OPTIONS\*\* INFORMATION REGISTER CONTROL Shift Input Count Partition (up to 4 zones)

ADDRESS REGISTER CONTROL Sequential

Sequential Up/Down Sequential Interlace Shift Input Marker Pulses (up to 3)

**DATA OUTPUT** Address Register

MEMORY CLEAR MEMORY TESTER VOLTMETER REGISTER DISPLAYS 400 CPS POWER INPUT

\*\* at extra cost

3C DISTRICT SALES OFFICES: NEEDHAM, MASS.; SYRACUSE, N.Y.; COM-MACK, L.L., N.Y.; LEVITTOWN, PA.; CLEVELAND, OHIO: SILVER SPRING, MD.; DES'PLAINES, ILL.; ORLANDO, FLA.; ALBUQUERQUE, N.M.; PALO ALTO, CALIF.; LOS ANGELES, CALIF.; HOUSTON, TEX.; HUNTSVILLE, ALA.

COMPUTER CONTROL COMPANY, INC. OLD CONNECTICUT PATH · FRAMINGHAM, MASSACHUSETTS

CIRCLE NO. 1 ON INQUIRY CARD

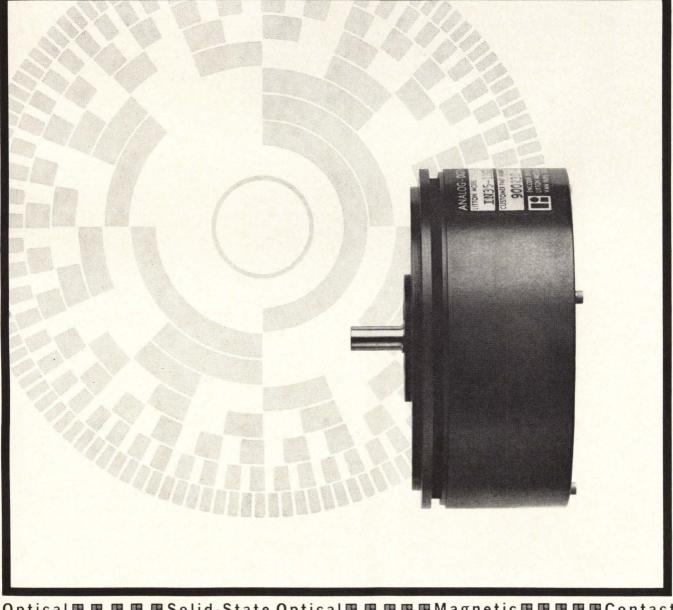

## **Produces the most complete** line of Optical Shaft-Angle Encoders

### **DIGISEC°** Highest Accuracy Direct Reading Encoders .... 1 Arcsecond, Peak and Better

DIGISEC achieves highest accuracy in small case sizes with direct reading, continuous outputs - without code conversion, gears, brushes or reference rotor.

| Optical | Unit Diameter |  |

|---------|---------------|--|

|         | 2.25"         |  |

|         | 3.5"          |  |

|         | 5.5"          |  |

|         | 10"           |  |

Resolution to 40 arcseconds to 10 arcseconds to 2 arcseconds to 1 arcsecond

Outputs available in decimal or natural binary codes. Accuracy is  $\pm 1$  quantum, peak. For example a  $2^{20}$ DIGISEC provides resolution of 1.24 arcseconds and accuracy of  $\pm 1.24$  arcseconds, peak. Complete system consists of Optical Unit and Translator containing electronics and display. The standard Translator weighs 15 lbs., is 6.5" x 17" x 7.5", and can be miniaturized. Total input power for standard system is 30 watts. Bulletin 6310-1.

#### **ARCSEC<sup>™</sup> Highest Accuracy Incremental Encoders**

Similar to DIGISEC Encoders in resolution, accuracy and size of Optical Unit, but providing incremental output with reduced electronic complexity. Available with direction sensing and zero reset signal. Bulletin 6310-1.

DIGISYN<sup>®</sup> Direct Reading Encoders for tracking, navigation, sampled data servos, indexing and positioning systems, and other readout applications.

CYCLIC CODE 210 to 215 Digits Case Diameter: 3.5" Bulletin 760-1C (photo: RD-15)

CYCLIC CODE 216 to 217 Digits Case Diameter: 10" Bulletin 162-1 (photo: RD-17)

NATURAL BINARY 2<sup>s</sup> to 2<sup>17</sup> Digits Case Diameters: 2.625" to 10" Bulletin 6302-2 (photo: NB-10)

**DIGITAK**<sup>®</sup> Incremental Encoders for rate measurement, angle counting, machine control, inertial platform systems — available with direction sensing and zero reset signal.

MINIATURE SYNCHROMOUNT 210 to 212 Digits Case Diameter: 1.437' Bulletin 6212-1

(photo: RI-12M)

STANDARD SYNCHROMOUNT 213 to 215 Digits Case Diameter: 3.5 Bulletin 861-1C (photo: RI-20K)

PANCAKE 213 to 215 Digits Case Diameter: 3.5' Bulletin 862-2 (photo: RI-15S)

Special encoders can be designed to meet particular requirements. Available accessories include Power Supplies and Test and Display Sets. Other Wayne-George products include inertial test systems and fluid bearings.

WAYNE-GEORGE CORPORATION 322 NEEDHAM STREET, NEWTON 64, MASSACHUSETTS (617) 969-7300

CIRCLE NO. 2 ON INQUIRY CARD

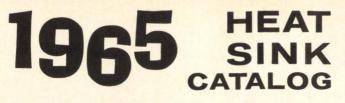

# COMPUTER DESIGN

#### FEATURES

#### 16 COMING EVENTS - IFIP CONGRESS 65

The largest international conference on information processing equipment opens in New York on May 24, 1965. Highlights of this important event are previewed in this issue.

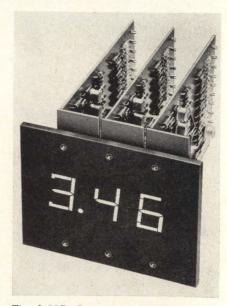

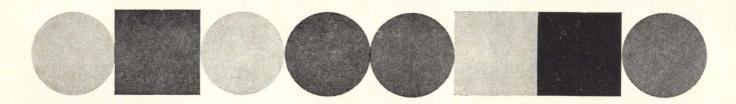

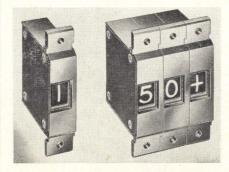

## **34** THE ELIMINATION OF FALSE DIGIT DISPLAY IN SEGMENTED-TYPE READOUTS

The possibility of false digit presentation has been the major disadvantage of segmented readouts. How a new unit overcomes this disadvantage is described here.

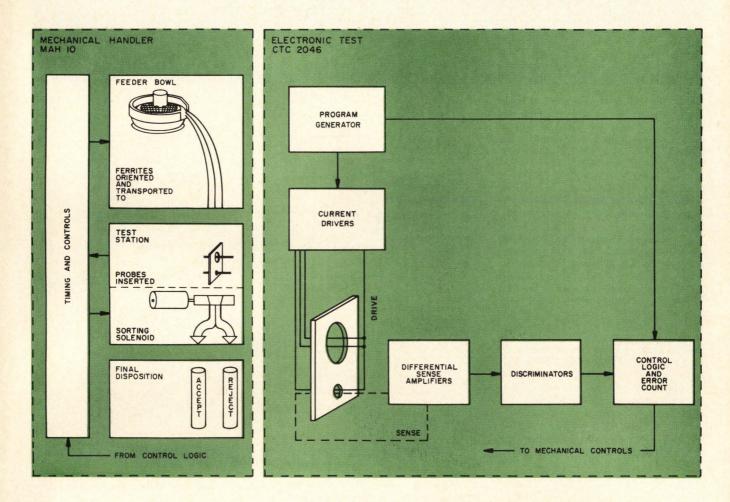

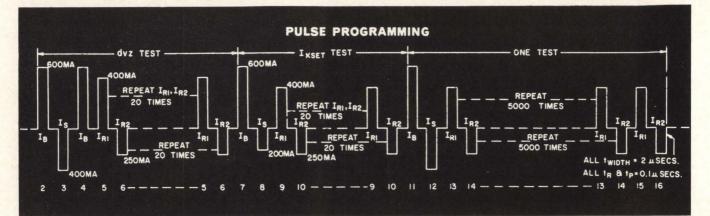

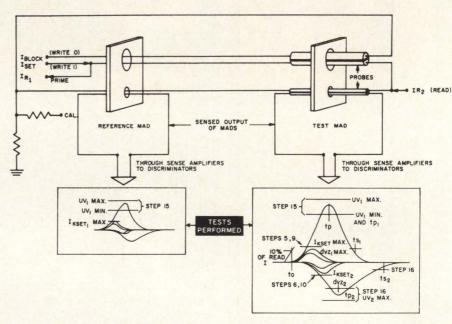

#### **36** MULTIAPERATURE CORE TESTING SYSTEM

New system may increase the exploitation of multiaperture cores as memory elements.

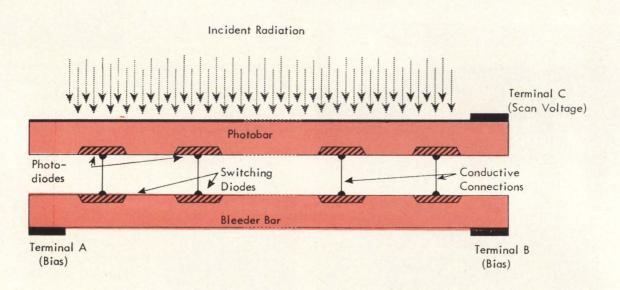

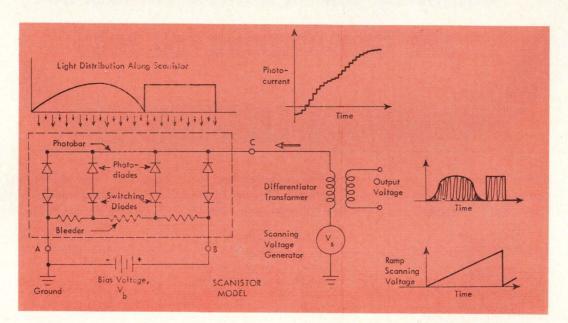

#### 46 EXPERIMENTAL SOLID-STATE SCANNING DEVICE

By providing an output that represents both the amount and position of light on its surface, this device may extend the use of optical scanning techniques.

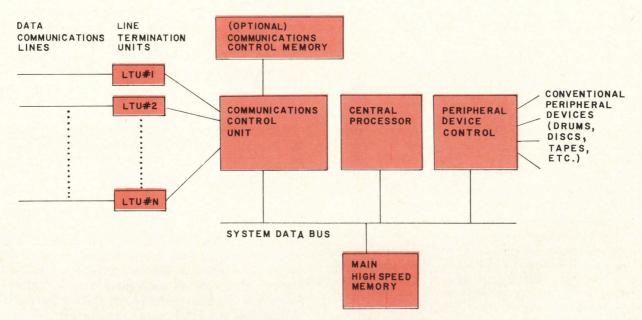

#### 54 DESIGN GUIDE FOR COMPUTER-COMMUNICATIONS SYSTEMS

#### PART 2-EQUIPMENT SELECTION CONSIDERATIONS

Following the discussion in Part 1 of this series, which introduced the basic system concepts of data communications, this part primarily considers the selection of a Communications Interface Sub-System. Its basic functions and characteristics are described and the techniques for its implementation are evaluated.

#### DEPARTMENTS

- **4** EDITORIAL NOTES

- **6** LETTERS TO EDITOR

- **8** INDUSTRY NEWS

#### **76 NEW PRODUCTS**

• Circuit Components • Circuit Packaging • Circuit Modules • Input-Output Equipment • Console Equipment • Power Supplies • Test Equipment • Memories • Systems

#### **96 LITERATURE**

#### **100** ADVERTISERS' INDEX

Reader subscription cards ...... opposite page 9

Reader inquiry cards ...... opposite page 92

FOR ENGINEERING PERSONNEL RE-SPONSIBLE FOR THE DESIGN & APPLICATION OF DIGITAL CIRCUITS, EQUIPMENT, AND SYSTEMS IN COM-PUTING, DATA PROCESSING, CONTROL AND COMMUNICATIONS.

ROBERT BROTHERSTON, Publisher S. HENRY SACKS, Editor

#### **Editorial Advisory Board**

HAROLD H. SEWARD JOSEPH D. SABO EDWARD M. COPPS, JR. DANIEL J. LICKLY

#### **Contributing Editors**

RICHARD AHRONS A. S. BUCHMAN H. S. MIILLER W. A. GANNON DAN M. BOWERS WALTER A. LEVY

JAMES FLORA Art Director THERESA SACKS Production Manager SANDRA M. MARTIN Adv. Prod. JANET RICH Circulation Mgr.

LINDSAY H. CALDWELL Vice Pres.-Sales

Editorial & Executive Offices Professional Bldg. Baker Ave. • W. Concord, Mass. Tel. 369-6660

Computer Design is published monthly. Copyright 1965 by Computer Design Publishing Corporation. Accepted as controlled circulation publication at Post Office at Boston, Massachusetts. No material may be reprinted without permission. Postmaster: CHANGE OF ADDRESS — FORM 3579 to be sent to Computer Design, Circulation Dept., P. O. Box B, Arlington, Mass. 02174. Subscription rate to nongualified subscribers is \$15.00 per year; \$1.50 per issue. Subscription rate to all foreign subscribers is \$25.00 per year; \$2.50 per copy.

Circulation over 24,000

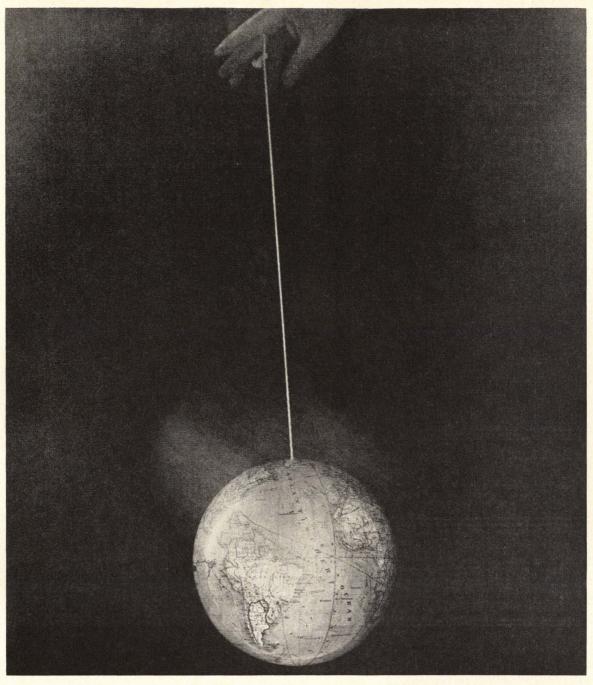

# CALL YOUR WIFE ... YOU'LL BE HOME LATE FOR DINNER!

Just read these "worst-case" specs on the new NAVCOR 1mc module line\* and you'll want to revise the specifications on your new design. We realize that your wife won't appreciate your excuse for working late, but your new "brainchild" deserves the best...

## And if you want to put the blame on someone . . . BLAME NAVCOR!

X Input noise immunity of 2.5v at frequencies of 1mc to 5mc.

- True 1mc speed through the use of parallel logic.

- Parallel operation of 120 binary counter stages at 1mc clock rate

. . with all outputs settling within 150 nanoseconds after the count pulse.

- Number of allowable stages of amplified logic between two flipflops is minimum of 8 at 1mc clock rate.

- No external clamp supply required—Zener clamp supply on every card to cut power supply and wiring costs.

- Rise and fall time maximum of 100 nanoseconds.

- Complete ground shielding and ringing clamps to cut backplane "debugging" expense.

When you add to these specifications: "System Function" versatility (one NAVCOR module can perform the functions of up to ten conventional cards); the most stringent quality

control check in the industry (heat cycling equivalent to

nine months use); instant check-out neon indicators; and one of the industry's most competitive pricing schedules

NAVCOR's new 1mc modules. Send in the quick-action

coupon for full technical data.

. you'll quickly realize that you should know more about

Where Advanced State of the Art is Expected

#### NAVIGATION COMPUTER CORPORATION

DEPT. CD-55 Valley Forge Industrial Park, Norristown, Pa. • 215-GL 2-6531

| NAMETITLE |

|-----------|

|           |

## describes Distributor Stock available in your locale . . .

CATALOG No. 1965 contains complete technical data and ordering instructions on all WAKEFIELD Distributor Lines.

2 NEW Series of Heat Sinks introduced in 1965 are included: Series 680 Circuit Board Coolers and Series MN King Size Heat Sinks for High Power Rectifiers and SCRs.

Series MN

Series 680

**REQUEST CATALOG No. 1965** TODAY . . . and also get roster of WAKEFIELD Distributors.

139 FOUNDRY ST. / WAKEFIELD, MASS (617) 245-5900 • TWX 617-245-9213

CIRCLE NO. 4 ON INQUIRY CARD

#### "PERFORATED TAPE READERS"

#### A 20-Page Reprint Now Available

The industry-wide survey of perforated tape readers that appeared as the Product Reference File feature in the January 1965 issue of COMPUTER DESIGN is now available as a 20-page reprint.

Providing a comprehensive analysis of the design and performance characteristics of commercially-available perforated tape reading equipment, this survey article serves as an excellent reference for evaluating and selecting a tape reader for a particular application.

**Order Your Copy Now!** Only 50 cents per copy.

Enclose check or money order payable to: Computer Design Publishing Corp.

And mail to: Computer Design Baker Ave. W. Concord, Mass. 01781

Editorial Notes

#### THE IFIP CONGRESS 65

The international conference on the "information sciences," sponsored by the International Federation on Information Processing (IFIP), is shaping up to be a "must" event for engineers working on data processing and related equipment. The technical program is not only wellbalanced in content but in form as well.

Covering just about every area of significant progress in the development of modern information processing systems, the program is divided into general and special sessions, symposia, and panel sessions. In general sessions, formal papers will view important research trends and examine the general stateof-the-art in information processing. Special sessions will consist of formal papers discussing in-depth important problems in specific areas. Shorter papers, with more time for informal discussion, will be presented in symposia and panel sessions.

Many of the program participants are from outside the U.S. Thus, to some extent, the program offers the attendees a global picture of the state-of-the-art.

A partial listing of scheduled topics is presented in this issue.

Plan now to attend the conference; we will be there at our booth No. 226, drop in and see us.

S. Henny Sacks Editor

## **IS YOUR TAPE CONVERSION STILL WORKING AT HORSE AND BUGGY SPEEDS?**

## THINK AHEAD...THE NEW KLEINSCHMIDT 321 ADS CONVERTS TAPE TO HARD COPY AT 400 WORDS PER MINUTE!...TODAY

Think of tape conversion four times faster than you may be getting now. Think of less tape backup. Think of the Kleinschmidt<sup>™</sup> 321<sup>™</sup> ADS. Whether it's used ''on line'' or ''off line,'' the 321 ADS gives you complete and reliable facilities for tape preparation, tape duplication and hard-copy print-out. For further information on the efficiency of the 321 ADS and other Kleinschmidt Electronic Data Communications equipment, write: KLEINSCHMIDT, Division of SCM Corporation, Lake Cook Road, Deerfield, Illinois.

Letters

## to Editor

#### LOGIC SYMBOL STANDARDS

#### To the Editor:

I read the article "Designing Shift Counters" in your December issue and was disturbed by the non-conformance to the generally accepted logic symbol standard, MIL-STD-806 or the IEEE equivalent. I feel that technical periodicals must pioneer in the use of this standard to aid in the elimination of the existing variations in logic symbology.

Very truly yours,

Harry D. Young R.C.A. Defense Electronic Products Moorestown, N.J.

#### Editor's Reply:

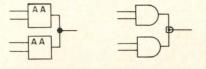

The IEEE logic symbol standard is the "American Standard Graphic Symbols for Logic Diagrams," approved by the American Standards Association on September 26, 1962. The task group which developed this standard was unable to agree upon a single standard, and thus two sets of symbols are presented, with no preference given between the two. Neither of these sets of symbols can presently be classified as "generally accepted," and there is apparently no technical periodical (including the IEEE Transactions on Electronic Computers) which adheres rigidly to either.

Extracts from the Standard are presented in the accompanying table; we invite our readers to comment generally upon this Standard, and the extent to which it is accepted in the industry.

#### PROPOSED ASA STANDARDS GRAPHICAL SYMBOLS FOR LOGIC DIAGRAMS

3.4 States in Binary Logic — The two physical states on each terminal of each signal line shall be referred to as the 0-state and the 1-state. The 0-state may be called the reference (inactive, antifiducial) state, and the 1-state the significant (active, fiducial) state.

The above must not be construed as implying that the 1-state requires more power, contains more energy, or is at a higher potential than the 0-state. The state designations are purely arbitrary as far as the physical interpretation is concerned.

3.5 Kinds of Logic. If all signal line terminals in a logic diagram of a system or device have the same pair of physical states, and if both are electric potentials (currents), and if the more positive potential (current) is consistently selected as the 1-state, the resultant system, or device, is said to have positive logic.

If the less positive potential (current) is consistently selected as the 1-state, the resultant system, or device, is said to have negative logic.

4.1 Consider a circuit whose output (F) is a function of two variables (A, B), and whose output and input levels are capable of assuming only +2 volts and -3 volts. Assume that the circuit behaves according to the following table of combinations:

| INPUTS |      | OUTPUT |  |

|--------|------|--------|--|

| А      | В    | F      |  |

| -3v    | -3v  | -3v    |  |

| -3v    | + 2v | -3v    |  |

| +2v    | - 3v | — 3v   |  |

| +2v    | + 2v | + 2v   |  |

4.1.1 In positive logic the -3v level is the O-state and +2v is the 1-state (see paragraph 3.5). Substitution of the logic values for the voltage levels results in the following table:

| INPUTS |   | OUTPUT |  |

|--------|---|--------|--|

| А      | В | F      |  |

| 0      | 0 | 0      |  |

| 0      | 1 | 0      |  |

| 1      | 0 | 0      |  |

| 1      | 1 | 1      |  |

This is the truth table for the AND function. Therefore, the circuit is said to perform the AND operation.

4.1.2 In negative logic the -3v level is the 1-state and +2v is the 0-state (see paragraph 3.5). Substitution of the logic

values for the voltage levels results in the following table:

| INPUT | S | OUTPUT |

|-------|---|--------|

| A     | В | F      |

| 1     | 1 | 1      |

| 1     | 0 | 1      |

| 0     | 1 | 1      |

| 0     | 0 | 0      |

|       |   |        |

This is the truth table for the OR function. Therefore, the circuit is said to perform the OR operation.

4.3 Given a physical device characterized by a table of combinations, the logic function performed by the device is determined by the specified choices of the 1states at its inputs and outputs.

Each choice of the 1-states at each input and each output of a logic circuit shall be specified on the detailed logic diagram in a manner that correctly represents the logic function designated by the logical designer.

4.4 In a diagram where positive logic, negative logic, or both is used, the state choices on the signal lines shall be identified as follows.

4.4.1 A small, open, right triangle at the point where a signal line joins a logic symbol indicates that the line's 1-state (activating) with respect to that logic symbol is the less positive potential.

4.4.2 A small, filled, right triangle at the point where a signal line joins a logic symbol indicates that the line's 1-state (activating) with respect to that logic symbol is the more positive potential.

4.4.3 The right triangle shall be so oriented as to point in the direction of signal flow.

4.4.4 Either of the two kinds of right triangles, open or filled, may be omitted providing the convention is suitably noted on the diagram. In diagrams in which both kinds of right triangles would appear, only one kind may be omitted.

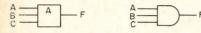

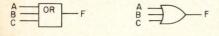

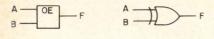

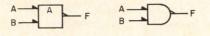

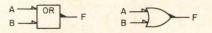

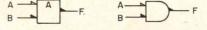

6.1 Use of Symbols — In the following listing of graphical symbols the Uniform Shape symbols are shown on the left and the Distinctive Shape symbols on the right. Logic diagrams must use symbols from one list or the other, not a mixture of the two. Symbols to be used on either list are shown in the center. The lines indicating input and output connections are not part of the symbol. (Taken from AIEE No. 91 published by the American Institute of Electrical Engineers)

6.2.1 The output of an AND assumes the 1-state if and only if all of the inputs assume the 1-state. An example of the symbols for an AND with three inputs is:

6.3.1 The output of an OR assumes the 1-state if one or more of the inputs assume the 1-state. An example of the symbols for an OR with three inputs is:

6.4.1 The output of an EXCLUSIVE OR with two inputs assumes the 1-state if one and only one input assumes the 1state.

#### 6.5.1 Symbol for LOGIC NEGATION O

The output of a LOGIC NEGATION operation takes on the 1-state if and only if the input does not take on the 1-state. A small circle drawn at the point where a signal line joins a logic symbol indicates a LOGIC NEGATION.

6.5.3.1 The output of an ELECTRIC IN-VERTER assumes the 1-state if and only

if the input assumes the 1-state. An example of the symbols for an ELECTRIC **INVERTER** is:

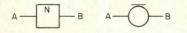

6.6.1 Flip-Flop Complementary - has outputs which are always of opposite states. This flip-flop has a third input, toggle (trigger) (T). The application of a 1-state signal to the toggle (T) input, or of simultaneous 1-state signals to the set and clear inputs, reverses the state of this flip-flop.

(The inputs are not required to be identified with S, T, and C, as shown.) The internal numbers, 1 and 0, are part of the symbol, and shall be in close proximity to their respective outputs. The set input shall be in proximity to the 1 output; the clear input shall be in proximity to the 0 output.

6.6.2 Flip-Flop Latch — has outputs which are not necessarily of opposite states. The application of simultaneous 1-state signals to the set and clear inputs causes both outputs to assume the same state for the duration of the inputs (both assume the 1-state

or both assume the Ostate, depending upon the design of the circuit.

6.7 Single Shot — is activated by the indicated significant transition of the input signal. Output signal shape, amplitude, duration, and polarity are determined by the circuit characteristics of the SINGLE SHOT, not by the input signal.

The normal (inactive) state of the SINGLE SHOT output is the 0-state. When activated, it changes to the indicated 1-state, remains there for the characteristic time of the device, and returns to the O-state. The duration of the on time of the SINGLE SHOT will normally need to be included on a tagging line inside the symbol. When required, stylized waveforms indicating duration, ampli-

tude, and rise and fall time may be used.

6.9.1 The output of an AMPLIFIER assumes the 1-state if and only if the input assumes the 1-state. An example of the symbols for an AMPLIFIER is:

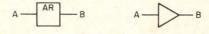

6.10 Symbol for Time Delay - the duration of the delay is included with the symbol. If the delay is tapped, the delay

time with respect to the input shall be included adjacent to the tap output.

6.11 Symbol for OSCILLATOR

6.12 Symbol for functions not elsewhere specified. The symbol shall be adequately labeled to identify the function performed. It is not intended that this symbol be used for functions which can be logically expressed by a single symbol established in this Standard.

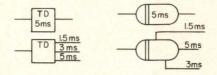

6.13 Relative Level Indicators below represent an AND with input 1-state at the more positive potential (current) level and an output with the 1-state at the less positive potential (current) level.

6.13.2 The symbols shown below represent the same device as paragraph 6.13. They depict an OR with input 1-state at the less positive potential (current) level and an output with the 1-state at the more positive potential (current) level.

6.13.4 The symbols shown below represent an AND with mixed inputs.

7.2 Use of Separate Circuits - Where circuits have the capability of being combined according to the AND (or OR) function, simply by having the outputs connected, that capability shall be shown by having an additiinal A (or OR) inside the Uniform Shape symbol. If needed for clarity, an additional A (or OR) shall be

added as a note adjacent to the connection (for the uniform shape). The Distinctive Shape symbol representation shall show this capability by enveloping the branched connection with a smaller sized AND or OR symbol.

INDUSTRY NEWS

THE AIR FORCE HAS ACCEPTED AND PLACED IN OPERATIONAL STATUS CONTROL DATA CORP.'S 3600 REAL-TIME COMPUTER SYS-TEM (RTCS) for missile impact prediction and tracking on the Eastern Test Range. The computer system will furnish the range safety officer with instant information in regard to a missile's track, possible point of impact, and other missile flight data from launch to "burn out". On the basis of the visual presentation of the missile's flight pattern and other data, the range safety officer will be able to make a "go-or-destruct" decision vital both to range safety and to the investment in the missile system of many millions of dollars. The system also will aid materially in the recovery of missiles thousands of miles down range.

A SYSTEM FOR THE DIGITAL PROCESSING OF SEISMIC REC-ORDS HAS BEEN ORDERED BY A MAJOR OIL COMPANY from Advanced Scientific Instruments of Minneapolis. The system, using an ASI Advance Series 6040 computer and some special seismic-oriented "black boxes", will be used to convert, correct, and correlate seismic records. Because of the capabilities of the Advance 6040 and the special hardware and software seismic package, the system is said to offer digital seismic processing faster and at a purchase cost up to \$120,000 less than currently available seismic data processing systems.

NASA'S MARSHALL SPACE FLIGHT CENTER HAS INSTALLED THREE GENERAL-PURPOSE PDP-5 COMPUTERS built by Digital Equipment Corp. The three computers and peripheral equipment form part of a ground-based testing complex for use in NASA's Saturn V program. The three PDP-5 computers will function as central control elements in an on-line data acquisition system in the center's Astrionics Laboratory. The system will test inertial components for the Saturn guidance system in a controlled laboratory environment.

THE NUMBER OF DIGITAL COM-INSTALLATIONS TN PUTER EUROPE INCREASED NEARLY 50% DURING 1964 according to a comprehensive study just released by Computer Consultants Ltd., a leading European consulting firm. This remarkable increase, representing a jump from 3919 computers installed at the end of 1963 to 5889 computers installed at the end of 1964, makes Europe the most rapidly growing market for computer systems in the world today, according to the report. During this same period existing orders for computer systems also increased by nearly 50%, from 2335 to 3485 according to the "European Computer Survey in 1965." The leading computer user in Europe is Germany with 1413 systems installed. Second is France with 1084 computers installed, followed by Great Britain with 948, and Italy with 882, according to figures provided in the report.

# SALES

#### BOSTON

Lindsay H. Caldwell Professional Bldg. Baker Ave. W. Concord, Mass. phone: (617) 369-6660

#### CHICAGO

Phil Holmes 410 N. Michigan Avenue Chicago 11, Illinois phone: (312) 467-6240

#### DETROIT

Edward A. Hale 424 Lafayette Building Detroit 26, Michigan phone: (313) WO 1-0278

#### LOS ANGELES

David Barton 672 So. Lafayette Park Pl. Los Angeles 57, California phone: (213) 382-1121

#### NEW YORK

Robert J. Bandini 1 Rockefeller Center New York 20, N. Y. phone: (212) CI 6-4712

#### SAN FRANCISCO

David Barton 672 So. Lafayette Park Pl. Los Angeles 57, California phone: (213) 382-1121

## **Get this Assembly Register Free**

## with this \$395 DtoA Converter

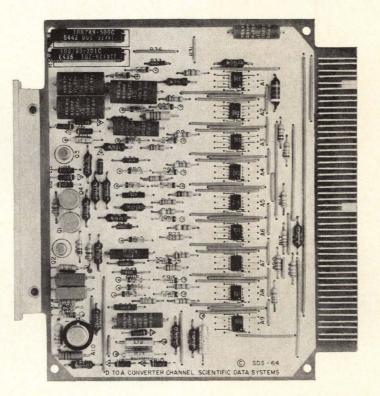

With an SDS D to A Converter, you get two registers per channel: A holding register like everybody else and an assembly register like only us. So what? So now, in addition to sequential conversion, you can simultaneously convert all of your system channels on demand. And it doesn't cost a penny more.

About the register shown above: You're right. It is an integrated circuit. All of our new analog system components utilize them to cram more reliability into less space. They also allow new systems set up flexibility (our 9-bit D to A, for example, is fully contained on a single card).

So add up our D to A converter advantages: both

assembly and holding registers; integrated circuits; 5 microsecond speeds; 200 Kc conversion rates; 9, 12 and 15-bit models; off-the-shelf delivery of individual channels or complete multi-channel systems. You'd get more for your money even if our prices weren't so low.

May we send you a brand new brochure on our complete digital and analog component line?

Sales offices in: Santa Monica, New York City, Boston, Washington, D.C., Philadelphia, Pittsburgh, Wilmington, Houston, Huntsville, Orlando, Dallas, Chicago, Detroit, Albuquerque, Denver, San Francisco, San Diego, Seattle. Foreign representatives: CECIS, Paris, France, Geneva, Switzerland; Kanematsu, Tokyo, Japan; RACAL, Sydney, Australia; Instronics, Ltd., Stittsville, Ontario, Canada.

CIRCLE NO. 6 ON INQUIRY CARD

## when one tape speed won't do the job...

Specify a **dual speed D 2020** computer magnetic tape unit from Datamec. The new economical answer to systems requirements for writing and reading computer format mag tapes at two different tape speeds. As many as six different data transfer rates can be handled on the same D 2020 tape unit. Any tape speeds from 1 to 45 ips. Any high-to-low tape speed ratio up to 10:1. Low density (200 cpi), dual density (200/556 cpi) or triple density (200/ 556/800 cpi) packing formats.

Dual speed D 2020's are supplied to exactly match your data system needs. For example, the two speeds may be selected to make the data transfer rate the same when using either 200 characters-per-inch or 556 characters-perinch recording densities.

The versatile DSI-1000 computer pictured here (manufactured by Data Systems Incorporated, a subsidiary of Union Carbide Corporation) makes most effective use of this dual speed D 2020 feature in data media conversion and data communications.

Other applications of the **dual speed D 2020** are numerous. What is your special data system requirement? Write Tom Tracy at Datamec Corporation, 345 Middlefield Road, Mountain View, California.

leadership in low-cost/high reliability digital magnetic tape handling CIRCLE NO. 7 ON INQUIRY CARD

## **INDUSTRY NEWS**

NATIONAL CASH REGISTER, IN RETURN FOR THE USE OF CER-TAIN PATENTS, has paid Navigation Computer Corp. a fixed amount of cash, plus an advance on royalties which will be paid over the five year span of the agreement. J. Paul Jones, president of Navigation Computer Corp. (NAVCOR) pointed out that NCR's exclusive rights to manufacture and sell the patented special input-output equipment are in the business machine field. The patents include an all electronic coding keyboard which has no mechanical levers or parts, high-speed printing techniques, and methods for simplified printing directly on punched paper tape. Additional patents cover tape perforation and simplified spool servo systems. Mr. Jones also stressed that one of the most important considerations in the signing of the agreement was that the International Service Organization of NCR will be equipped to service all machines, whether they are sold directly through NCR sales or through NAVCOR.

THE CONTROL SYSTEMS DIVI-SION OF RADIATION INC. AND DATA SYSTEMS, INC. WILL PUR-SUE MARKETING OPPORTUNI-TIES IN THE AUTOMATION OF CHEMICAL PROCESSING PLANTS. according to a recent agreement signed by the two companies. Data Systems, Inc., a subsidiary of Union Carbide Corporation, will provide a series of modern, high-speed, digital computers for chemical process control. Radiation Inc. will furnish data acquisition and signal conditioning products.

COMPUTER CONTROL COMPANY, INC., HAS RECEIVED AN ORDER FROM SANDERS ASSOCIATES, INC., FOR SEVEN DDP-224 GEN-ERAL PURPOSE DIGITAL COM-PUTERS in a contract totaling over one million dollars. The DDP-24's will be the digital computer portion of seven Saturn V operational display systems Sanders is building for NASA. The DDP-224's will collect data, format information. and distribute critical booster measurements to associated displays, thereby enabling personnel to evaluate the Saturn V vehicle's operational performance.

SYLVANIA ELECTRONIC SYS-TEMS HAS INSTALLED A CON-TROL DATA 3200 COMPUTER SYS-TEM FOR ITS WESTERN OPERA-TION AT MOUNTAIN VIEW, Cal. The 3200 computer system is used to acquire, process, reduce and analyze realtime data, as well as a scientific processor for engineering applications. The 3200 accepts information from a five-stage, 24-bit, cascaded buffer built by Sylvania and attached to the 3207 Data Channel. Sylvania engineers estimate that this buffer will accept 24bit words at burst rates up to 5 million words per second. In addition to the five-stage cascaded buffer, Sylvania engineers have attached to the data buss a register to allow 15 bits of information to be sent in or out of the computer in one computer cycle. This data buss register extension provides a means of communication between special input/output equipment and the computer. With the addition of these two devices. Sylvania has extended the over-all system capability in accepting and analyzing the high rate real-time input data.

CIRCLE NO. 8 ON INQUIRY CARD

## stunt box\*..your communication's girl friday

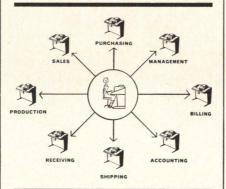

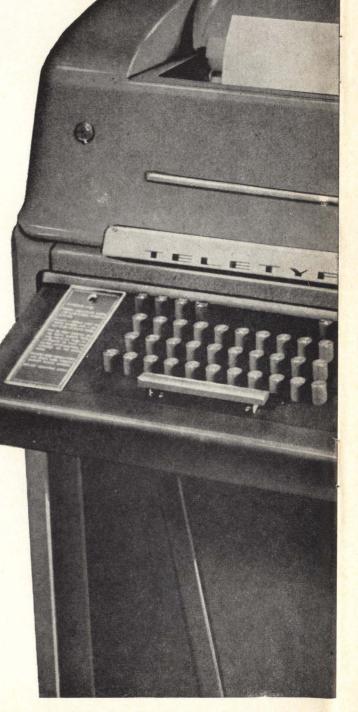

An important component of all Teletype Model 35 page printers and automatic send-receive sets is the stunt box. This is an automatic switching device which performs remote control functions usually expected only of larger, costlier, and more complex equipment.

The stunt box handles anything that can be electrically controlled-ranging from performing such non-typing functions as automatic carriage return and horizontal tabulation ... to activating remote apparatus, including tape punches and readers, business machines, and computers.

Basically, the stunt box does three

things-mechanically initiates internal

functions, electrically controls internal functions, and electrically controls

external equipment.

#### STATION CALLER

Remote stations can be selectively called through the stunt box. Thus, one station can call others simultaneously, individually, or in predetermined groups. In this way, specific information can be selectively directed only to the stations specifically concerned with the information being transmitted. For example: an operator types out a sales order on a Teletype Model 35 page printer. Such information as the order number is received by all departments, while cost information is directed by the stunt box only to accounting, billing, and management departments.

#### AUTOMATIC BACK TALK

Teletype Model 35 sets can be equipped with an answer-back drum, which stores up to 20 characters. In on-line uses, the stunt box at a remote unattended station can trigger the answer-back mechanism so that the station automatically returns its identification call letters to the sending station.

The stunt box can activate the mechanism that automatically feeds the information needed to program a computer so that it can accept the input data which follows.

The versatility that the stunt box gives to Teletype Model 35 page printers and automatic send-receive sets is another reason why they are made for the Bell System and others who require the most reliable communications equipment at the lowest possible cost. For more detailed information on the real-time uses of Teletype equipment, write to: Teletype Corporation, Dept. 71E, 5555 Touhy Avenue, Skokie, Illinois 60078.

\*This device is used in Teletype machines to perform non-printing functions such as carriage return, line feed, etc.

machines that make data move

DATA

**COMMUNICATIONS**

equipment for on-line, real-time processing

TELETYPE

#### INCREMENTAL MAGNETIC TAPE TRANSPORT

#### COMPLETELY COMPUTER COMPATIBLE

LOW COST RELIABLE OPERATION UP TO 400 STEPS/SEC HIGH DENSITY IBM COMPATIBILITY END OF TAPE SENSING

#### INTERNAL GENERATION

- INTER RECORD GAP

- LONGITUDINAL PARITY

- LATERAL PARITY

#### APPLICATIONS

- DATA COLLECTION

- DATA LOGGER RECORDER

- A/D TO MAG. TAPE

- PAPER TO MAG. TAPE

- CARDS TO MAG. TAPE

Write or phone for more information or assistance with your application.

CIRCLE NO. 57 ON INQUIRY CARD

INDUSTRY NEWS

A "DO-IT-YOURSELF" COMPUTER SERVICE THAT ALLOWS CUSTOM-ERS TO DRIVE IN AND PROCESS **INFORMATION MUCH AS A HOUSE-**WIFE DRIVES TO A LAUNDROMAT was inaugurated recently in Chicago. Originated by Statistical Tabulating Corp., the unusual service, which is called Data-Mat, permits a customer to bring unprocessed data to a mid-town center, obtain free parking, and the use of a private office to sort and prepare information, and perform all necessary computations on any of four computer systems, including a new, highspeed system — just as if he were using one of a battery of washing machines. Like a laundromat, cost of the service is based upon the number of hours the computer equipment is used. The center - located in modern quarters at 2 North Riverside Plaza — is open aroundthe-clock, seven days a week. Attendants are available at all times to assist customers. Prices for the new service start at \$20 an hour. Scheduled time is sold on a guaranteed basis, and customers may contract for as little as three hours a month.

FOR THE DEVELOPMENT OF A COMPUTER-BASED INFORMATION PROCESSING AND RETRIEVAL SYSTEM, System Development Corp. has been awarded an \$85,000 contract by the Job Corps' Office of Program Development and Analysis, Washington, D.C. SDC scientists and information processing technicians will adapt existing computer programs — originally designed for and currently in use by military organizations to allow Job Corps' personnel to accumulate, organize, retrieve and analyze information relative to the Job Corps' program. The information system will serve the early needs of the Job Corps' program and will be able to accommodate changes in the Corps' size, organization, functions, problems, relationship with other organizations, and other aspects of the program.

WHAT HAS BEEN TERMED THE STEEL INDUSTRY'S FIRST COM-PUTERIZED OPERATOR GUIDE CONTROL FOR ELECTRIC FURNACE STEELMAKING has been put into operation at Lukens Steel Co. in Coatesville. Pa. W. E. Mullestein, Lukens vice-president and general manager, said, "We are using computer equipment now to guide production of carbon steels in the company's two electric furnaces, while developing programs for alloy steels and improving existing programs. Results during two months of operation convince us we can anticipate achieving all goals set for the equipment." The IBM Operator Guide Control Svstem doesn't activate any portion of the furnace facility. Instead, it issues guide instructions for furnace operators to follow during the steelmaking processes. This feature of the equipment emphasizes the continued responsibility of the operator for production results. In addition to information fed to the computer through manual entry units, precisely detailed process information concerning such things as a temperature of the molten steel in the furnace, oxygen injection, pressure in the furnace, power input, etc., is picked up automatically by instrument sensors wired to the computer.

equipment for on-line, real-time processing

DATA

## the shift-less keyboard that isn't!

Shifting between letters and numbers is no longer necessary as a result of the new 4-row keyboard on Teletype Models 33 and 35 page printers and automatic send-receive sets. However, when used in real-time data communications, these machines are anything but shiftless on the job.

"COMPUTER" SPOKEN HERE

Operating on the same permutation code approved by the American Standards Association for information interchange, this Teletype equipment can communicate with most business machines and computers. It is being used as input/output terminal gear in such applications as communications between branch offices and a centralized computer, making a data processing center available to all company offices.

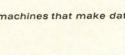

machines that make data move

The American Standard Code is composed of eight columns of 16 characters each. Control characters, found in the first two columns, include those required for the control of terminal devices, input and output devices, format, or transmission and switching operations. Common punctuation symbols are found in the third column, numbers in the fourth, and the alphabet in the fifth and sixth columns. The final columns are reserved for future standardizations. Teletype Models 33 and 35 sets generate an even parity in the eighth level.

#### PRINTS ON BUSINESS FORMS

Any business form, such as invoices, payroll checks, sales orders, freight records, and reservations, can be typed on these Teletype sets and transmitted directly to various departments. This minimizes recopying errors. The 4-row keyboard further reduces the possibility of errors, because it isn't necessary to shift when typing numbers. Notice the similarity to a regular typewriter keyboard, which is why any typist can easily learn to use these new machines.

#### VERSATILITY PLUS

Added to the versatility of the 4-row keyboard is the complete reliability and economy of Teletype equipment. It's built to last, with pneumatic shock absorbers, nylon pulleys and gears, and all-steel clutches that keep maintenance down to a bare minimum. And, these sets are surprisingly low in cost.

That's why Teletype Models 33 and 35 page printers and automatic sendreceive sets are made for the Bell System and others who insist on the most reliable communications equipment at the lowest possible cost. For more details on the capabilities of the Teletype 4-row keyboard in real-time data communications, write to: Teletype Corporation, Dept. 71E, 5555 Touhy Avenue, Skokie, Illinois 60078.

#### GOVERNMENT REPORTS $\star$ $\star$

#### PROPAGATION-LIMITED COMPUTER NETWORKS

The assumption of significant and indeterminate signal propagation delay between logic blocks in a computer system introduces uncertainties in the timing of logical operations. This condition sets limits to computation speed independently of the speed of the switching elements. Such uncertainties require careful design of timing and physical layout so as not to cause excessive loss in operation speed. The anti-parallel scheme, a new mode of coupling, has been developed. In this scheme the loss of a control pulse due to the accumulation of delay variations results only in the introduction of spaces into a symbol stream.

Order from the Office of Technical Services, U.S. Dept. of Commerce, Washington, D.C. 20230. Order No. AD603165N. Price: \$4.00.

#### INFORMATION SYSTEMS SUMMARIES

Second edition prepared by the Office of Naval Research covers general information sciences, machine interaction with humans, and improved machines. The ONR report represents an effort to acquaint interested personnel with their Information Systems Branch program and with a sampling of current significant research in the information sciences. Three distinct classes of interest exist, each having its own requirements. Development and engineering personnel need new ideas and techniques to solve their technical problems or to suggest new approaches. Members of the scientific community need detailed knowledge of both new research findings and also new research tools and techniques. And R&D management personnel need current and projected status information on the state of technology and the cost in time, dollars, and manpower of pushing it forward. ONR aims its report at each of these classes who have a need-to-knew.

Order from the Office of Technical Services, U.S. Dept. of Commerce, Springfield, Va. 22151. AD606772N. Price: \$3.00.

#### VARIABLE DISPLAY SYSTEM

With a light pen and an electronic display linked to a central computer, a user may perform tasks on-line that are usually done off-line with card sorting and reproduction machinery, electronic engineers report. A new variable display system drastically shortens response time and enables changing part or all of the stored information. The system will accommodate any set of tabular data arranged in proper format and placed on magnetic tape. Tabular data may be retrieved from up to 59,000 categories and manipulated on the display by application of the light pen to the surface of the cathode-ray tube. Data may be added, modified and deleted, rows sorted, columns added, columns and rows exchanged, deleted and compressed. Users require only a few minutes of training and practice to gain speed and confidence.

Order from the Office of Technical Service, U.S. Dept. of Commerce, Springfield, Va. 22151. AD 606179N. Price: \$1.00.

#### MICROMINIATURE PROGRAMMABLE LOGIC ELEMENTS

A microminiaturized, highly repetitive logic structure is feasible where microprogramming of elements individually or in groups is a characteristic of the structure. Air Force-sponsored researchers demonstrated feasibility in the successful miniaturization of the digital section of a pattern recognition system which they designated "Parapropagation Pattern Classifier." Major difficulties were encountered in obtaining isolation in homogeneous silicon wafers, but the researchers developed a promising isolation process and indicate process variations as well as results through following the recommended procedure.

Order from Clearinghouse, U.S. Dept. of Commerce, Springfield, Va. 22151. AD608525N. Price: \$3.00.

#### SOVIET TRANSLATION ON MANUFACTURE OF COMPUTERS

Report discusses overall planning and certain organizational and technical measures recommended for securing reliability. The author indicates that controllability of the manufacturing process at all stages is the basis for obtaining specified reliability. For each manufacturing process and operation, tolerances must be set, that is, limits of errors within which the item produced is considered to be sound.

Order from Clearinghouse, U.S. Dept. of Commerce, Springfield, Va. 22151. TT-64-41944N. Price: \$3.00.

## FJCC 1965 Call for Papers

The call for papers for the 1965 Fall Joint Computer Conference, to be held November 30-December 2 in Las Vegas, Nevada, has been issued by S. Nissim and T. B. Steel, Jr., co-chairmen of the technical program committee. No restrictions are placed on subject matter for the papers. In addition to state-of-the-art surveys and original research and development reports in the traditional areas of hardware and software, contributions emphasizing the design, selection, installation and management of information processing systems are invited.

Notification of intention to submit a paper is requested. Deadline for full papers is June 15. One complete draft copy, together with a 150word abstract, should be sent to:

Mr. Robert Gray, Secretary, Program Committee, 1965 FJCC; P.O. Box 49, Santa Monica, Cal.

## put punch in your communications...with paper tape

The continuous evolution of data processing systems has brought new uses for punched paper tape. In fact, paper tape has become an important communications link, and is still the most inexpensive and reliable continuous recording medium available.

Paper tape is easy to handle and accommodates data of any length. In addition, Teletype paper tape units can transmit most recognized codes, including the permutation code approved by the American Standards Association for information interchange. This makes Teletype sets capable of communicating directly with business machines and computers.

#### COLLECTION AGENT

Teletype punched paper tape units are versatile, flexible, and capable of collecting and distributing data from a large number of machines and transmitting to computers at high speeds. There is a paper tape unit for every need—from 60 to 2000 wpm.

Many business operations have been improved through the use of Teletype punched paper tape equipment within integrated data processing systems. This list includes: order entry, shipping, and invoicing for the accounts receivable procedure; production control; payroll computation; banking operations, insurance processes, etc. An important advantage of punched paper tape is that it can store fixed information, such as customers' names and addresses, which can be used over and over again to save retyping.

#### INDEPENDENT OPERATOR

On the Teletype Model 35 ASR (automatic send-receive) set, the tape punch and reader can operate independently of the page printer. Thus, messages can be received by the page printer, while the operator is preparing a tape for later transmission. This independent operation also means the keyboard can be used to prepare one tape, while the tape reader transmits the message of another tape.

VOICE OF A COMPUTER Applications of Teletype equipment as input/output terminals for computers and other business machines are numerous. For example: a national insurance company has demonstrated a system that will link a large multiprocessing computer with more than 900 district offices. Teletype Model 33 ASR sets will be used in this system to print out premium information from the district offices, and as tape output equipment for a centralized computer in order to update all premium transactions.

DATA

COMMUNICATIONS

equipment for on-line, real-time processing

This is another indication why these Teletype paper tape units and automatic send-receive sets are made for the Bell System and others who insist on the most reliable communications equipment at the lowest possible cost. To find out more on how they can be an important part in your data processing systems, write to: Teletype Corporation, Dept. 71E, 5555 Touhy Avenue, Skokie, Illinois 60078.

machines that make data move

CIRCLE NO. 10 ON INQUIRY CARD

## **IFIP CONGRESS 65**

## INTERNATIONAL CONFERENCE ON INFORMATION PROCESSING NEW YORK HILTON • MAY 24-29, 1965

Combined with an exciting technical program, the largest international exposition of information processing equipment will convene at the New York Hilton on May 24, 1965. More than 15,000 people from 50 countries are expected at the show.

The formal program will run from May 24 through May 29; the exhibition, called Interdata 65, will be open from May 24 through May 27. A number of special events will be held during and after the week as part of the total official activity of the Congress.

The first Congress of this type was held in Paris in 1959 and at that meeting the International Federation for Information Processing (IFIP) was born. Its formation was subsequently ratified by the national societies of 13 countries. By 1962, when IFIP Congress 62 was held in Munich, IFIP had become a 20-nation federation. Today IFIP represents professional societies of 23 member countries. Because the triennial meeting is being held in the United States, the American Federation of Information Processing Societies (AFIPS) has cancelled its own national meeting (The Spring Joint Computer Conference) so that its members may act as U. S. hosts and participate in the Congress.

The technical program will provide a comprehensive view of significant progress in techniques and development in the information sciences. Formal papers will be presented in general and special sessions. Shorter papers with more time for informal discussion will be presented in symposia and panel sessions. The opening and closing sessions, on May 24 and 29, will be single plenary sessions. Other sessions will run in parallel. The schedule presented here represents only a partial listing of proposed topics; the complete program will be available at the Congress registration booth.

## TECHNICAL PROGRAM

#### MONDAY, MAY 24

#### A1 GENERAL SESSION 10:00 AM-GRAND BALLROOM OPENING SESSION

Chairman: W. R. Lonergan, Congress Vice Chairman

WELCOME: I. L. Auerbach, IFIP President

THE TECHNICAL PROGRAM: B. Langefors, Program Chairman

THE CONGRESS:

W. Buchholz, Congress Chairman KEYNOTE SPEECH:

(Speaker to be announced)

#### B1 GENERAL SESSION...2:00 PM-EAST BALLROOM ORGANIZATION OF LARGE STORAGE SYSTEMS - 1

Chairman: J. A. Postley (USA) Vice Chairman: H. D. Huskey (USA)

HANDLING OF VERY LARGE PROGRAMS M. N. Perry (USA)

ADVANCED CONCEPTS OF UTILIZATION OF MASS STORAGE C. B. Poland (USA)

CONSIDERATIONS ON RANDOM AND SEQUENTIAL ARRANGEMENTS OF LARGE NUMBERS OF RECORDS

A. I. Dumey (USA)

#### B2 SPECIAL SESSION .... 2:00 PM-WEST BALLROOM MATHEMATICAL METHODS OF OPTIMIZATION

Chairman: H. W. Kuhn (USA)

SEMIGROUP THEORY AND CONTROL THEORY A. V. Balakrishnan (USA)

SEQUENTIAL OPTIMIZATION ALGORITHMS AND THEIR APPLICATIONS V. S. Mikhalevitch (USSR)

OPTIMIZATION IN OPERATIONS RESEARCH G. B. Dantzig (USA)

#### B3 SYMPOSIUM......2:00 PM-BALLROOM FOYER GENERAL PURPOSE PROGRAMMING LANGUAGES

Chairman: A. van Wijngaarden (Netherlands)

RECENT DEVELOPMENTS IN THE CONSTRUCTION OF A NEW ALGOL W. L. Van der Poel (Netherlands)

A GENERALIZATION OF ALGOL AND ITS FORMAL DESCRIPTION N. Wirth and H. Weber (USA)

SYNALGOL — AN ALGORITHMIC LANGUAGE CAPABLE OF GROWING H. J. Hauer (USA)

DAJA - A PROPOSED LANGUAGE FOR DATA PROCESSING

J. Vlcek, E. Outrata, and E. Kindler (Czechoslovakia)

RECENT APPLICATIONS OF A UNIVERSAL PROGRAMMING LANGUAGE K. Iverson (USA)

#### SPECIAL EVENTS

Participants in IFIP Congress 65 and especially their wives are invited to enjoy a number of special events being planned:

- IFIP-UNITED NATIONS EVENING

- PRINCETON TOUR

AND COMMUNITY THEATER

- IFIP BANQUET

- INFORMATION SCIENCES DAY

AT THE WORLD'S FAIR

- · MAJOR BROADWAY MUSICAL

- CONCERT

- SPORTS NIGHT

- SUNDAY OUTING (All day MAY 30)

- DAYTIME TRIPS

#### IFIP PEOPLE-TO-PEOPLE PROGRAM

To encourage an informal exchange of technical information on an individual basis, as well as to provide a more personal look at life in the USA and Canada, visitors to IFIP Congress 65, from outside North America, will be put in touch with hosts from a wide geographic area. Questionnaires for visitors residing in IFIP member countries are available from the national information processing societies. Other visitors, and those desiring to be hosts in the USA and Canada, can obtain questionnaires from the People-to-People Program, IFIP Congress Office, 345 East 47th Street, New York, N.Y. 10017.

#### REGISTRATION

Registration Fee: By April 1, 1965 . . \$25 At Congress . . . . . \$35 Wife (or husband) . Free

Each registrant will receive a two-volume conference proceedings at no charge.

For registration forms write:

IFIP CONGRESS 65 345 East 47th St. (at UN Plaza) New York, N.Y. 10017

IFIP Congress 65 (Continued) LEARNING ALGORITHMS FOR SEQUENTIAL DECISION GRAPHS M. Nadler (France)

LANGUAGE LEARNING, CONTINUOUS PATTERN RECOGNITION, AND CLASS FORMATION L. Uhr (USA)

#### B4 SYMPOSIUM.....2:00 PM-TRIANON BALLROOM PARALLEL AND CONCURRENT COMPUTER SYSTEMS

Chairman: D. L. Slotnick (USA)

THE SOLOMON II COMPUTING SYSTEM A. B. Carroll, J. G. Gregory, W. H. Leonard, and D. L. Slotnick (USA)

A REAL TIME MULTI-COMPUTER SYSTEM FOR TRAIN SEAT RESERVATION M. Hosaka and T. Tani (Japan)

A METHOD FOR THE SIMULTANEOUS PROCESSING OF SEVERAL PROGRAMS W. Rekowski and K. Leipold (Germany)

LARGE PARALLEL COMPUTERS J. Schwartz (USA)

AN APPROACH TO PARALLEL COMPUTING J. H. Pomerene (USA)

ORGANIZATION OF MULTIPROCESSING BY HARDWARE J. Oblonsky (Czechoslovakia)

####

Chairman: J. A. Robinson (USA)

A MULTIPURPOSE THEOREM-PROVING HEURISTIC PROGRAM THAT LEARNS J. R. Slagle (USA)

REALIZATION OF A PROGRAM WHICH CHOOSES THE THEOREMS IT PROVES

A SOLUTION TO THE TRANSLATION PROBLEM AND THE IMPORTANCE OF THE SET OF SUPPORT STRATEGY IN THEOREM PROVING

L. T. Wos, G. A. Robinson, and D. Carson (USA)

ASPECTS OF MECHANICAL THEOREM PROVING M. Davis (USA)

COMPUTER REALIZATION OF A DECISION PROCEDURE IN LOGIC Joyce Friedman (USA)

#### B6 SYMPOSIUM.....2:00 PM-MERCURY BALLROOM PATTERN RECOGNITION AND SELF-ORGANIZING SYSTEMS — I

Chairman: G. S. Sebestyen (USA)

ISODATA — A SELF-ORGANIZING COMPUTER PROGRAM FOR DESIGN OF PATTERN RECOGNITION PREPROCESSING G. H. Ball and D. J. Ball (USA)

ADAPTIVE PATTERN RECOGNIZERS SYNTHESIZED WITH WIENER CANONICAL FORMS D. B. Brick (USA)

AN ITERATIVE REALIZATION OF ADAPTIVE PATTERN RECOGNITION NETWORKS K. Fukunaga and T. Ito (Japan) TUESDAY, MAY 25

#### C1 SPECIAL SESSION .... 9:00 AM-EAST BALLROOM THE FUTURE OF SWITCHING ELEMENTS

Chairman: J. R. Pasta (USA)

THE INFLUENCE OF COMPUTER DESIGN ON SEMICONDUCTORS S. L. H. Clarke (UK)

CRYOGENICS — ACHIEVEMENT AND POTENTIAL V. L. Newhouse (USA)

ELECTRO-OPTICAL INFORMATION PROCESSING W. J. Poppelbaum (USA)

#### C2 SPECIAL SESSION .... 9:00 AM-WEST BALLROOM PARTIAL DIFFERENTIAL EQUATIONS

Chairman: A. A. Dorodynicyn (USSR) Vice Chairman: A. Ghizzetti (Italy)

ON USE OF MODIFIED SUCCESSIVE OVERRELAXATION METHOD WITH SEVERAL RELAXATION FACTORS D. M. Young, Jr., Mary F. Wheeler, and J. A. Downing (USA)

D. M. Toung, Jr., Mary F. Wheeler, and J. A. Downing (USA

SOME UNUSUAL PROBLEMS IN NUMERICAL ANALYSIS S. V. Parter (USA)

ESTIMATIONS IN NONLINEAR EQUATIONS J. Schroeder (Germany)

#### C3 SYMPOSIUM.....9:00 AM-BALLROOM FOYER METHODS FOR DESCRIBING INFORMATION SYSTEMS

Chairman: M. M. Pacelli (Italy) Organizer: L. A. Lombardi (Italy)

NON-PROCEDURAL FILE PROCESSING: A PROCEDURE GENERATOR M. M. Pacelli and G. M. Palermo (Italy)

THE REPRESENTATION OF STRUCTURED INFORMATION G. Salton (USA)

A GENERAL PURPOSE SYSTEM FOR THE STRUCTURING ON-LINE OF INFORMATION AND DECISION PROCESSES M. Greenberger (USA)

NOTATION, INSIGHT, AND PROBLEM DEFINITION METHODS M. S. Montalbano (USA)

ON THE REPRESENTATION OF LOGIC BLOCKS AND THEIR INTERCONNECTION IN SEQUENTIAL SWITCHING CIRCUITS H. Goerling (Germany)

SYSTEMS ANALYSIS IN AN ECONOMIC MANAGEMENT AUTOMATION PROJECT J. Vlcek (Czechoslovakia)

#### C4 SYMPOSIUM....9:00 AM-TRIANON BALLROOM REQUIREMENTS AND PROSPECTS FOR COMMERCIAL PROGRAMMING

Chairman: J. A. Gosden (USA)

THE GRADUAL ACCEPTANCE OF A VARIETY OF COMMERCIAL ENGLISH LANGUAGES R. M. Paine (UK)

FLIP CHIP<sup>™</sup>Modules are unconditionally guaranteed for 10 years. Any module which fails in use will be repaired or replaced for a five dollar handling charge.

WASHINGTON D C + PARSIPPANY, N J + LOS ANGELES + PALO ALTO + CHICAGO + ANN ARBOR + PITTSBURGH + HUNTSVILLE + ORLANDO + CARLETON PLACE, ONT. + READING, ENGLAND + MUNICH, GERMANY + SYDNEY, AUSTRALIA

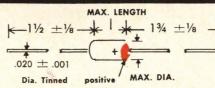

WHEN PENNIES COUNT... SPECIFY **\_\_\_\_\_\_**'S NEW GEM SILICONE MOLDED TRANSISTORS

### THE NEW\_\_\_\_\_ GEM IS:

• the smallest silicone molded transistor available

designed for automated assembly

• guaranteed to withstand shock, vibration and acceleration better than headermounted transistors

## SELECT FROM THE BROADEST LINE... AT THESE LOW PRICES

• The new GEM Silicone molded transistors are economically practical replacements for germanium transistors and are ideally suited for low cost industrial, computer and entertainment applications which require or can benefit by the stability, life and characteristics of silicon.

|                    |                                                                                                  | Replacement<br>for Silicon              | Replacement<br>for Germanium                        | 1 K Price |

|--------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------|-----------|

| SL 100             | UHF Small Signal<br>Silicon Epitaxial Transistor<br>for Amplifier and Oscillator<br>Applications | 2N 917<br>2N 918                        | 2N 1140 thru 43<br>2N 1405 thru 07                  | .60       |

| SL 200             | PNP Medium Power<br>Diffused Epitaxial Transistor                                                | 2N 328A<br>2N 329A                      | 2N 404<br>2N 1382-83<br>2N 651-52<br>2N 658 thru 62 | .67       |

| SL 300             | NPN Small Signal<br>(Low Level High Gain)<br>Transistors                                         | 2N 929<br>2N 930<br>2N 1566<br>2N 736   |                                                     | .45       |

| 2N 3793<br>2N 3794 | Medium Power NPN<br>Silicon Transistors                                                          | 2N 2219<br>2N 2222<br>2N 697<br>2N 1613 | 2N 1302<br>2N 1304<br>2N 1306<br>2N 1306<br>2N 1308 | .42       |

NATIONAL SEMICONDUCTOR CORPORATION DANBURY, CONN.

#### IFIP Congress 65 (Continued)

USA ACTIVITY IN CONVENTIONAL COMMERCIAL LANGUAGES H. Bromberg (USA)

FURTHER USA ACTIVITY AFFECTING COMMERCIAL PROGRAMMING LANGUAGES C. J. Shaw (USA)

#### C5 SYMPOSIUM.....9:00 AM-LE PETIT TRIANON PATTERN RECOGNITION DEVICES

Chairman: B. H. McCormick (USA)

STAR — A MACHINE TO RECOGNIZE SPOKEN WORDS D. R. Hill (UK)

AN ASYNCHRONOUS CHARACTER RECOGNITION SYSTEM

T. Sakai, M. Nagao, K. Nagamori, S. Sekiguchi, and K. Kiji (Japan)

ILLIAC III: A PROCESSOR OF VISUAL INFORMATION B. H. McCormick (USA)

A PATTERN RECOGNITION FACILITY WITH A COMPUTER-CONTROLLED LEARNING MACHINE J. H. Munson, A. E. Brain, G. E. Forsen, D. J. Hall, N. J. Nilsson, and C. A. Rosen (USA)

#### C7 PANEL......9:00 AM-MERCURY ROTUNDA TRENDS IN COMPUTER LOGIC FOR NON-ARITHMETIC PROCESSORS

Chairman: J. P. Anderson (USA) Panel Members: A. R. Barnum (USA), R. S. Barton (USA), and J. Weizenbaum (USA)

#### C8 SYMPOSIUM......9:00 AM-GIBSON SUITE MONTE CARLO METHODS

Chairman: B. Jansson (Sweden)

ANALYTICAL STUDIES OF PSEUDO-RANDOM NUMBER GENERATORS OF CONGRUENTIAL TYPES B. Jansson (Sweden)

MONTE CARLO METHODS AND SOME MULTIVARIATE PROBLEMS T. Tsuda (Japan)

MONTE CARLO METHODS AND STATISTICAL MECHANICS L. D. Fosdick (USA)

THE SIMULATION OF CONFLICT SITUATIONS J. L. Jenkins (USA)

#### C9 PANEL......9:00 AM-GREEN ROOM TESTING, CORRECTION, AND DOCUMENTATION OF PROGRAMMING

Chairman: J. C. Harwell (UK)

Panel Members: K. Bhagwandin (Sweden), G. E. Felton (UK), D. N. Freeman (USA), M. I. Halpern (USA), R. Rossheim (USA), and W. Turski (Poland).

#### D1 GENERAL SESSION....2:00 PM-EAST BALLROOM COMPUTER PROGRAMMING

Chairman: C. C. Gotlieb (Canada) Vice Chairman: M. Woodger (UK)

THE PLACE OF PROGRAMMING IN A WORLD OF PROBLEMS, TOOLS, AND PEOPLE P. Naur (Denmark)

THE CHANGING BASIS OF PROGRAMMING S. Gill (UK)

# ECONOTAN

#### SOLID TANTALUM CAPACITORS

Nickel Leads polarity

| METAL CASE |              | POLYESTER SLEEVE<br>INSULATION |        |              |                |

|------------|--------------|--------------------------------|--------|--------------|----------------|

| SERIES     | MAX.<br>DIA. | MAX.<br>LENGTH                 | SERIES | MAX.<br>DIA. | MAX.<br>LENGTH |

| CT.        | .090         | .240                           | СТ     | .095         | .260           |

| CM         | .128         | .300                           | СМ     | .133         | .320           |

| CL         | .175         | .325                           | CL     | .180         | .325           |

## SMALL SIZE

#### WITH MAXIMUM CAPACITANCE

LONG SHELF LIFE

ALL DRY CONSTRUCTION

### LOW COST

PRICES BELOW 20¢ EACH

IN 25,000 QUANTITIES

#### AVAILABLE RATINGS STANDARD CAPACITANCE TOLERANCE ± 20%

| NUMBER | CAP  | WV<br>DC | MAX<br>DF | MAX |

|--------|------|----------|-----------|-----|

| CT683  | .068 | 20       | .08       | 1.0 |

| CT104  | .10  | 20       | .08       | 1.0 |

| CT154  | .15  | 20       | .08       | 1.0 |

| CT224  | .22  | 20       | .08       | 1.0 |

| CT334  | .33  | 20       | .08       | 1.0 |

| CT474  | .47  | 20       | .08       | 1.0 |

| CT684  | .68  | 20       | .08       | 1.0 |

| CT105  | 1.0  | 20       | .08.      | 1.0 |

| CT155  | 1.5  | 20       | .08       | 1.0 |

| CT225  | 2.2  | 15       | .08       | 1.0 |

| СТ335  | 3.3  | 10       | .08       | 1.0 |

| CT475  | 4.7  | 6        | .10       | 1.0 |

| СТ685  | 6.8  | 4        | .12       | 1.0 |

| CT106  | 10.0 | 2        | .12       | 1.0 |

| NUMBER | MFD  | DC    | DF  | IL  |

|--------|------|-------|-----|-----|

| CM225  | 2.2  | 20    | .08 | 1.0 |

| CM335  | 3.3  | 20    | .08 | 1.0 |

| CM475  | 4.7  | 20    | .08 | 1.0 |

| CM685  | 6.8  | 15    | .08 | 1.0 |

| CM106  | 10.0 | 10    | .08 | 1.0 |

| CM156  | 15.0 | 6     | .10 | 1.0 |

| CM226  | 22.0 | 4     | .12 | 1.0 |

| CM336  | 33.0 | 2     | .12 | 1.0 |

|        | _    |       |     | _   |

| CL685  | 6.8  | 20    | .08 | 2.0 |

| CL106  | 10.0 | 20    | .08 | 2.0 |

| CL156  | 15.0 | 15    | 08  | 2.0 |

| CL226  | 22.0 | 10    | .08 | 2.0 |

| CL336  | 33.0 | 6     | .10 | 2.0 |

| CL476  | 47.0 | 4     | .12 | 2.0 |

| CL686  | 68.0 | 2     | .12 | 2.0 |

|        |      | 1.000 |     |     |

PART CAP WV MAX MAX

#### TECHNICAL BULLETIN AVAILABLE ON REQUEST

#### COMPONENTS, INC.

SMITH STREET, BIDDEFORD, MAINE Phone (Area code 207) ATlantic 4.5956

LOW-LEVEL RELAY MULTIPLEXER

STANDARD PRODUCTS

DIGITAL LOGIC MODULES

C Street Land

TELETYPE MESSAGE GENERATOR

0000000000000

A/D-D/A CONVERTER

LOW LEVEL AMPLIFIER/MULTIPLEXER

ACCESSORY HARDWARE

## PRODUCTS MADE TOGETHER-PLAY TOGETHER

Guarantee a happy marriage in your digital systems

Molecular Research, Inc.'s standard digital system products are designed to be completely compatible to eliminate marriage problems in system design

MRI offers a complete line of field-tested and proven digital system products such as: high-speed low-level multiplexers capable of microvolt resolution, high-speed anaog-to-digital converters, logic modules and mounting hardware, low-level relay multiplexers, message generators and digital-to-analog converters.

FOR MORE INFORMATION ON THIS HAPPY FAMILY CONTACT:

ELECTRONIC SYSTEMS DIVISION . 3105 BELVEDERE ROAD . WEST PALM BEACH, FLORIDA

#### IFIP Congress 65 (Continued)

PROGRAMMING IMPLICATIONS OF HARDWARE TRENDS R. F. Clippinger (USA)

#### D2 SPECIAL SESSION .... 2:00 PM-WEST BALLROOM OUTLOOK IN THE MEMORY AREA

Chairman: A. P. Speiser (Switzerland) Vice Chairman: B. Langefors (Sweden)

INTEGRATED MAGNETIC AND SUPERCONDUCTIVE MEMORIES J. A. Rajchman (USA)

**FUTURE OF MAGNETIC MEMORIES** G. Kohn (Switzerland)

THE EFFICIENT USE OF MULTI-LEVEL STORAGE G. G. Scarrott (UK)

####

Chairman: K. R. Wright (USA) Panel Members: C. W. Bachman (USA), R. H. Hill (USA), M. Kory (USA), R. C. McGee (USA), L. R. Pickel (USA), and H. Tellier (USA)

#### D4 SYMPOSIUM.....2:00 PM-TRIANON BALLROOM DIGITAL AUTOMATIC CONTROL

Chairman: T. Moto-Oka (Japan)

DIRECT DIGITAL CONTROL SYSTEMS FROM THE CONTROL-ORIENTED POINT OF VIEW A. S. Robinson (USA)

THE DIGITAL COMPUTER FOR PROCESS CONTROL APPLICATIONS H. T. Marcy (USA)

DETERMINATION OF PROCESS STABILITY BY LEARNING ALGORITHM W. Turski (Poland)

NUMERICAL CONTROL OF CAM-SHAFT GRINDING S. Inaba and T. Moto-Oka (Japan)

A DIGITAL CONTROL VALVE AND ITS USE H. H. Ernyei (France)

#### D5 SYMPOSIUM......2:00 PM-LE PETIT TRIANON AUTOMATED SOFTWARE PRODUCTION

Chairman: R. W. Bemer (France)

COMPILER CONSTRUCTION THROUGH MODELING J. R. Dunlap (USA)

AUTOMATED PROGRAM DOCUMENTATION FOR LARGE COMMAND AND CONTROL SYSTEMS R. J. Kot (USA)

A POSSIBLE FUTURE SYSTEM FOR AUTOMATING CONTROL OF THE DEVELOPMENT, DISTRIBUTION, AND MAINTENANCE OF PROGRAMMING SYSTEMS

SOFTWARE SYSTEMS CUSTOMIZED BY COMPUTER R. W. Bemer (France)

#### D7 SYMPOSIUM.....2:00 PM-MERCURY ROTUNDA HYBRID DIGITAL-ANALOG COMPUTATION IN THE AEROSPACE INDUSTRY

Chairman: M. S. Mason (USA) Organizer: R. Vichnevetsky (USA)

SATELLITE ORBITAL STABILITY PROGRAM WITH AN ANALOG-HYBRID COMPUTER J. Stricker and W. W. Miessner (USA)

LONGITUDINAL OSCILLATION INSTABILITY STUDY OF THE GEMINI LAUNCH VEHICLE W. W. Miessner and R. L. Goldman (USA)

INSTANT FLIGHT — JUST ADD DATA D. E. Fought and W. G. McClintock (USA)

SPACECRAFT MISSION SIMULATION J. J. Clancy (USA)

A HYBRID SIMULATION OF AN ABLATING NOSE CONE E. H. Hochman and A. J. Hanawalt (USA)

#### D8 SYMPOSIUM......2:00 PM-GIBSON SUITE SYSTEM SIMULATION BY COMPUTERS

Chairman: H. S. Krasnow (USA)

SIMULATION FOR ELECTRIC POWER SYSTEMS S. Miki (Japan)

GENERIC FEATURES OF MILITARY SIMULATIONS E. Levine (USA)

A PROCESS-ORIENTED APPROACH TO SIMULATION MODELING M. R. Lackner (USA)

STRUCTURE OF SEQUENCING ALGORITHMS FOR SIMULATION B. M. Leavenworth and R. J. Parente (USA)

SIMULATION OF SOCIAL ACTION PROGRAMS S. S. Ackerman (USA)

PROBLEMS IN THE DESIGN AND IMPLEMENTATION OF A SIMULATION LANGUAGE K. D. Tocher (UK)

#### WEDNESDAY, MAY 26

E1 SPECIAL SESSION . . . . 9:00 AM-EAST BALLROOM ORGANIZATION OF LARGE STORAGE SYSTEMS — II

Chairman: J. Carteron (France)

Vice Chairman: J. C. McPherson (USA)

#### E2 SPECIAL SESSION . . . . 9:00 AM-WEST BALLROOM ARTIFICIAL INTELLIGENCE

Chairman: C. K. Chow (USA) Vice Chairman: H. R. Ciancaglini (Argentina)

PRESENT AND FUTURE OF PATTERN RECOGNITION THEORY V. A. Kovalevsky (USSR)

DYNAMIC CONTROL OF CORE MEMORY IN A REAL TIME SYSTEM W. B. Elmore and G. J. Evans, Jr. (USA)

GENERAL PURPOSE EXTERNAL MEMORY SYSTEM FOR DATA BASE PROCESSING J. M. Unk (Netherlands)

DYNAMIC FLOW OF PROGRAMS AND DATA THROUGH HIERARCHICAL STORAGE A. Opler (USA)

## NOW AVAILABLE

A DESIGN REFERENCE GUIDE FOR ALL DIGITAL DESIGN ENGINEERS . . . .

### "CAUSES AND CURES OF NOISE IN DIGITAL SYSTEMS"

By J. Paul Jones, Jr.

#### A 56-PAGE POCKET-SIZE HANDBOOK

The material in this handbook originally appeared in a 3-part series of articles in the 1964 Fall issues of **COMPUTER DESIGN**. The large number of requests for copies prompted the printing of this handbook.

Excellent design tips and basic guideline rules for eliminating or minimizing noise in digital systems are given. Here is just a partial listing of topics:

• Electrostatic Interference in Backplane Wiring • Worst-Case Cabling of Wires • Inductive Noise in Systems Backplanes • Routing of Circuit Grounds • Use of Output Clamps • Test Points • Driving Diode Matrices • Output Filters • RFI-Proofing • AC Power Line Noise • Power Supplies for Very High Noise Locations

PRICE: \$1.75 per copy

Bulk quantity prices available on request.

To order your copy, simply fill out coupon below, enclose check or money order, for \$1.75 per copy, payable to Computer Design Publishing Corp. Shipment will be made immediately upon receipt of order.

COMPUTER DESIGN PUBLISHING CORP. BAKER AVE., W. CONCORD, MASS. 01781

**GENTLEMEN:**

Enclosed is \$..... for ..... copy(ies) of 56page Handbook — "CAUSES AND CURES OF NOISE IN DIGITAL SYSTEMS".

SHIP HANDBOOK(S) TO:

| NAME    |       |

|---------|-------|

| COMPANY |       |

| ADDRESS |       |

| CITY    | STATE |

IFIP Congress 65 (Continued)

MATTER, MIND, AND MODELS M. L. Minsky, (USA)

FORMAL PROOFS AND AUTOMATIC THEOREM PROVING H. Wang (USA)

#### E4 SYMPOSIUM.....9:00 AM-TRIANON BALLROOM MICROELECTRONICS AND INTEGRATED CIRCUITS

Chairman: I. A. Lesk (USA)

INTEGRATED CIRCUIT PROCESSING TECHNOLOGY I. A. Lesk (USA)

INTEGRATED CIRCUIT HIGH SPEED LOGIC CONSIDERATIONS J. A. Narud (USA)

INTEGRATED CIRCUITS -- COMMERCIAL COMPUTER APPLICATION E. M. Davis (USA)

CUSTOM INTEGRATED CIRCUITS — A MILITARY COMPUTER APPLICATION J. S. Kilby and R. C. Platzek (USA)

#### E5 SYMPOSIUM......9:00 AM-LE PETIT TRIANON HYBRID ANALOG-DIGITAL APPLICATIONS

Chairman: R. J. A. Paul (UK)

APPLICATIONS OF FAST ANALOG-HYBRID COMPUTERS TO RANDOM PROCESS SIMULATION (MONTE CARLO METHODS) G. A. Korn (USA)

ERROR ANALYSIS OF DIGITAL COMPUTER ORIENTED HYBRID SYSTEMS

W. J. Karplus (USA)

HYBRID SOLUTION OF INITIAL VALUE PROBLEMS FOR PARTIAL DIFFERENTIAL EQUATIONS H. Witsenhausen (USA)

AN INVESTIGATION OF NUMERICAL INTEGRATION AND MULTIPLE VARIABLE UPDATING RATES USING THE DES-1 L. Levine (USA)

THE APPLICATION OF HYBRID ANALOG DIGITAL TECHNIQUES TO THE STUDY OF PREDICTIVE CONTROL J. F. Coales (UK)

DESIGN OF A HYBRID COMPUTER FOR THE CALCULATION OF SIGNAL STATISTICS B. P. T. Veltman (Netherlands)

#### E7 SYMPOSIUM.....9:00 AM-MERCURY ROTUNDA COMPUTER ARITHMETIC — I

Chairman: A. Svoboda (USA)

SOME ASPECTS OF THE DESIGN OF A SIMULTANEOUS MULTIPLIER FOR A PARALLEL BINARY DIGITAL COMPUTER T. Lamdan and D. Aspinall (Israel)

ANALYSIS OF INHERENT ERRORS IN MATRIX DECOMPOSITION USING UNNORMALIZED ARITHMETIC N. C. Metropolis (USA)

PRELIMINARY LOGICAL DESIGN OF A TERNARY DIGITAL COMPUTER

J. Santos and H. Arango (Argentina)

METHODS OF SELECTION OF QUOTIENT DIGITS DURING DIVISION J. E. Robertson (USA)

A LOW COST PARALLEL BINARY ADDER B. G. Utley (USA)

#### F1 GENERAL SESSION....2:00 PM-EAST BALLROOM AUTOMATA THEORY AND SIMULATION OF THOUGHT PROCESS

Chairman: H. Zemanek (Austria) Vice Chairman: J. Kryze (Czechoslovakia)

AUTOMATA THEORY AND ITS APPLICATION V. M. Gloushkov (USSR)

AUTOMATIC PROCESSING OF NATURAL AND FORMAL LANGUAGES A. G. Oettinger (USA)

THE SEARCH FOR GENERALITY A. Newell (USA)

####

Chairman: J. Weizenbaum (USA)

ALGEBRAIC FORMULA MANIPULATION IN ALGOL A. J. Perlis (USA)

LIST PROCESSING AND THE SIMSCRIPT WORLD VIEW P. Kiviat (USA)

STORAGE ALLOCATION FOR A SYSTEM OF MIXED DATA TYPES M. Levin (USA)

FORMAL MANIPULATION OF SYMBOLIC EXPRESSIONS WITH AN ALGORITHMIC LANGUAGE M. Engeli (Switzerland)

TITLE TO BE ANNOUNCED C. Strachey (UK)

#### F5 SYMPOSIUM......2:00 PM-LE PETIT TRIANON OPTICAL AND ELECTRO-OPTICAL INFORMATION PROCESSING

Chairman: D. K. Pollock (USA) Organizers: D. F. Pollock, Mary E. Stevens, and J. Tippett (USA)

COMPUTERS AND OPTICS L. Clapp, J. Tippett, and Mary E. Stevens (USA)

ASPECTS OF OPTICAL INFORMATION PROCESSING L. J. Cutrona (USA)

RECENT PROGRESS IN DOUBLE DIFFRACTION FILTERING A. Marechal and S. Lowenthal (France)

QUANTUM ELECTRONIC LOGIC C. J. Koester (USA)

OPTICAL DEVICES AND INFORMATION PROCESSING N. S. Kapany (USA)

####

Chairman: R. R. Seeber (USA) Reporter: B. Lindquist (USA) Panel Members: P. M. Davies, R. J. Ferris, R. H. Fuller, J. E. McAteer, and J. P. Pritchard, Jr. (USA)

**SUMMARY:** To throw some light on past difficulties and future possibilities of content addressable memories, the panel will discuss system organizations, arithmetic algorithms, magnetic and cryogenic fabrication technology, and potential applications.

#### IFIP Congress 65 (Continued)

#### THURSDAY, MAY 27

#### G3 SYMPOSIUM......9:00 AM-BALLROOM FOYER ULTRA-HIGH SPEED COMPUTERS

Chairman: O. H. Bartlett (USA)

THE X03 TUNNEL DIODE COMPUTER P. Kellett (UK)

500 MC MICROLOGIC CIRCUITS IN AN EXPERIMENTAL DIGITAL ASSEMBLY Y. Cho, J. B. Connolly, and E. P. Edelson (USA)

ULTRA-HIGH FREQUENCY LOGIC CIRCUITS IN EXPERIMENTAL MACHINES W. Piel (USA)

SYSTEM 360 AND THE HIGH-PERFORMANCE MODEL 92 G. M. Amdahi (USA)

#### G4 SYMPOSIUM....9:00 AM-TRIANON BALLROOM MAN-MACHINE INTERACTION: REMOTE CONSOLES AND DISPLAYS

Chairman: J. C. R. Licklider (USA)

GRAPHICAL COMMUNICATION IN A TIME SHARING ENVIRONMENT L. G. Roberts (USA)

A UNIVERSAL DISPLAY CONSOLE

R. Stark, R. Mallebrein, and D. Matejka (Germany)

THE ULTIMATE DISPLAY I. E. Sutherland (USA)

PROBLEMS AND PRINCIPLES OF CONSOLE DESIGN J. C. R. Licklider (USA)

#### G6 SYMPOSIUM.....9:00 AM-MERCURY BALLROOM COMPUTER-CONTROLLED MESSAGE SWITCHING SYSTEMS

Chairman: A. B. Shafritz (USA)

IMPROVEMENTS AFFORDED STORE-FOREWARD MESSAGE SWITCHING NETWORK NODES USING DIGITAL COMPUTERS R. Thomas (USA)

SPECIAL SYSTEMS OR COMPUTER CONTROL FOR MESSAGE SWITCHING K. Gosslau (Germany)

COMPUTATION OF CAPABILITY AND PERFORMANCE CURVES FOR COMPUTER-CONTROLLED MESSAGE SWITCHING SYSTEMS

R. L. Sharma (USA)

MESSAGE SWITCHING AS A SUBSIDIARY FUNCTION OF CENTRALIZED INFORMATION PROCESSING J. F. Dudas, C. E. Skidmore, and R. C. Cheek (USA)

CONSIDERATIONS OF BASIC PROCESSOR AND REAL-TIME COMMUNICATIONS INTERFACE S. Tucker and E. Hillman (USA)

#### H1 GENERAL SESSION . . . . 2:00 PM-EAST BALLROOM TRENDS IN COMPUTER DESIGN

Chairman: J. G. Santesmases (Spain) Vice Chairman: C. V. L. Smith (USA)

COMPUTERS IN THE USA — TODAY AND TOMORROW S. Fernbach (USA)

THE FUTURE OF COMPUTER ARCHITECTURE F. P. Brooks (USA)

INTERNATIONAL COMPUTER APPLICATIONS AND THEIR IMPACT ON SYSTEMS DESIGN J. G. Miles (USA)

#### FRIDAY, MAY 28

#### J1 SPECIAL SESSION . . . . . 9:00 AM-EAST BALLROOM DESIGN OF INFORMATION SYSTEMS

Chairman: W. S. Humphrey, Jr. (USA)

THE AUTOMATIC DESIGN OF A DATA PROCESSING SYSTEM C. B. Greenberger (USA)

DESIGN OF A GENERAL PURPOSE SCIENTIFIC COMPUTING FACILITY F. V. Wagner and J. W. Granholm (USA)

DESIGN OF A REAL-TIME DATA PROCESSING SYSTEM E. C. Svendsen and D. L. Ream (USA)

CONCEPT OF A REAL-TIME SYSTEM AUTOMATING AIR TRAFFIC CONTROL J. Villiers (France)

#### J6 SYMPOSIUM.....9:00 AM-MERCURY BALLROOM MASS MEMORIES

Chairman: R. A. Shahbender (USA)

MASS RANDOM ACCESS CORE MEMORY R. W. Staats and E. E. Hanson (USA)

RANDOM ACCESS CARD MASS MEMORY J. F. Gates (USA)

A MASS MEMORY CENTERED PROCESSOR G. W. King (USA)

PERMALLOY SHEET RANDOM ACCESS MASS MEMORY H. W. Fuller (USA)

LARGE CAPACITY, LOW COST CORE MEMORY R. J. Petschauer (USA)

####

Chairman: E. A. Feigenbaum (USA) Panel Members: G. I. Marchuk (USSR), J. McCarthy, U. Neisser, A. Newell (USA), and G. Pask (UK)

#### K2 SPECIAL SESSION .... 2:00 PM-WEST BALLROOM AUTOMATA THEORY AND SWITCHING THEORY

Chairman: F. L. Bauer (Germany)

THE REALIZATION OF BOOLEAN FUNCTIONS WITH THE AID OF DIAGRAM AND FORMULAS Ju. Zhuravlev (USSR)

CLASSIFICATION OF COMPUTATIONS BY TIME AND MEMORY REQUIREMENTS

P. M. Lewis II, J. Hartmanis, and R. E. Stearns (USA)

ON THE ALGEBRAIC THEORY OF AUTOMATA M. P. Schutzenberger (France)

## A complete series of fixed-constant read-only memories, function generators, and look-up tables...

# **Magnetic Code Converters**

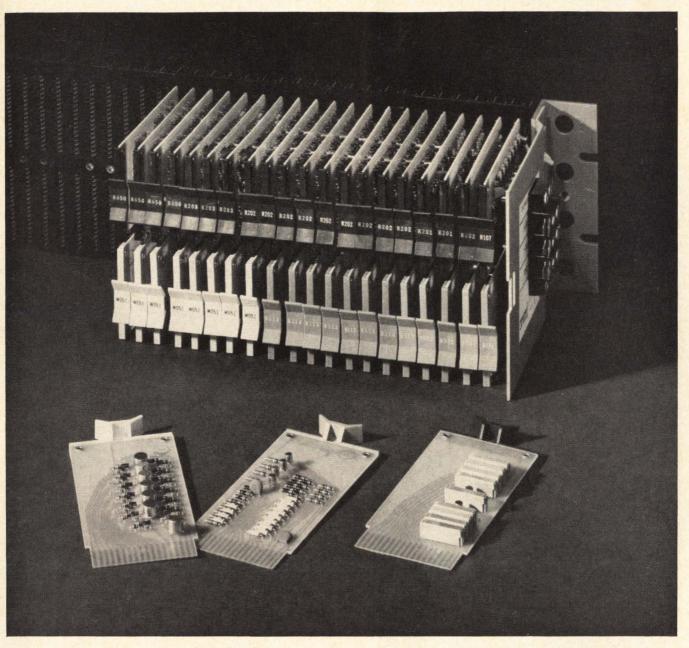

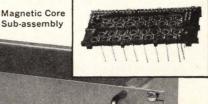

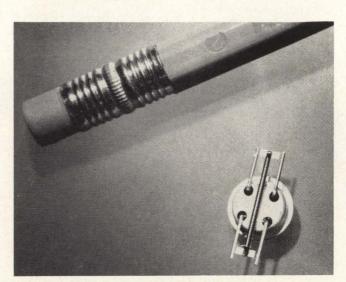

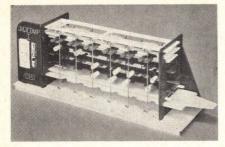

## model 4047 magnetic code converter (dual channel)

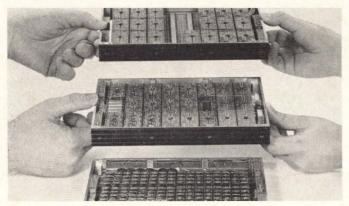

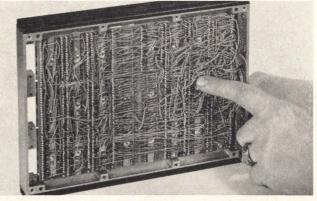

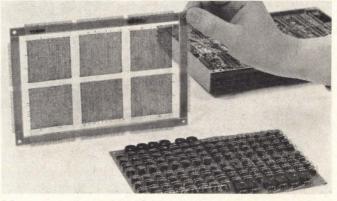

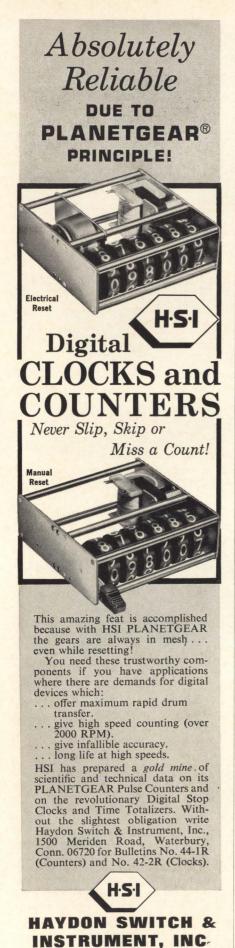

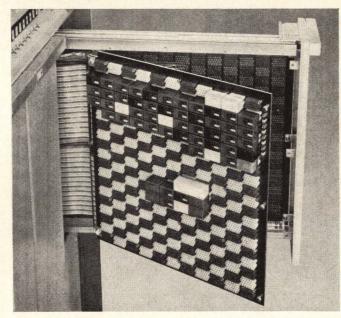

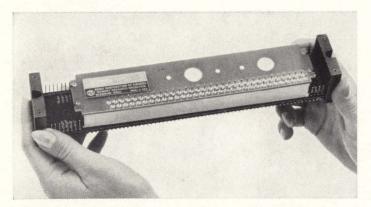

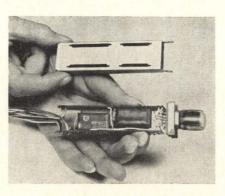

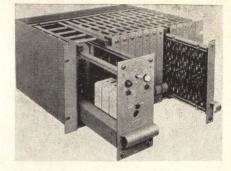

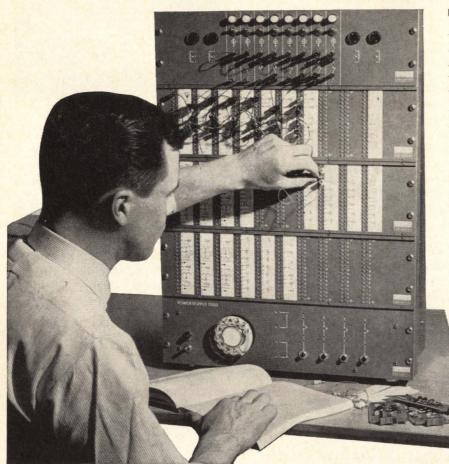

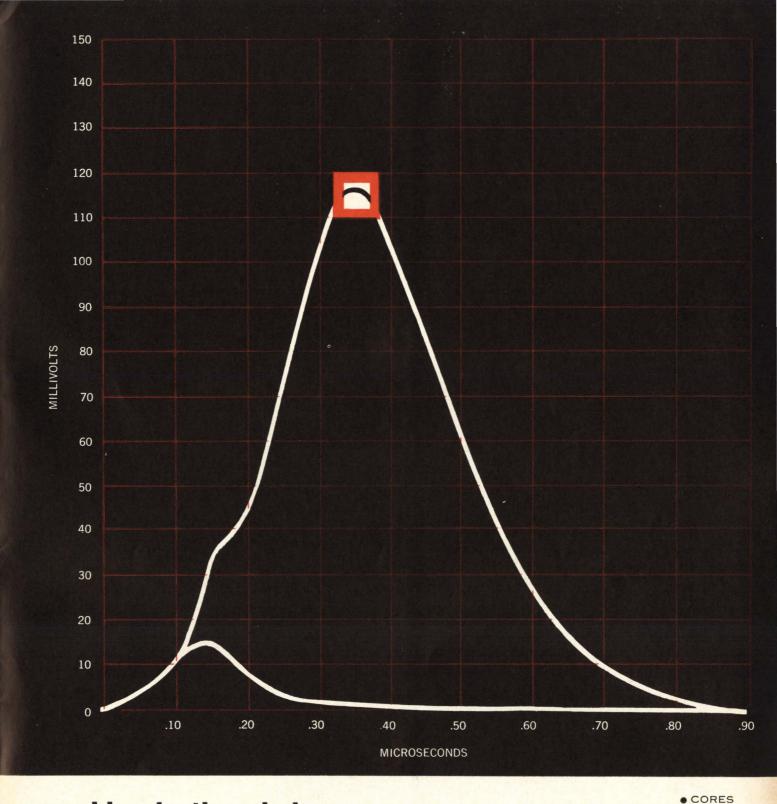

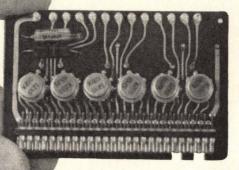

C & K's Model 4047 Magnetic Code Converter is designed for use in data processing operations for the conversion of one 7, 8 or 9-bit code to another 7,

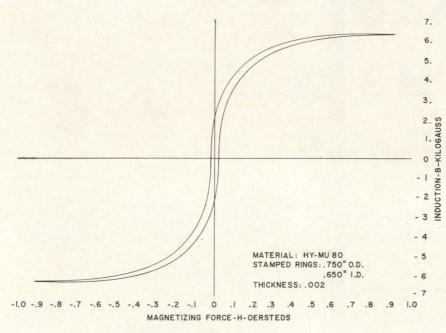

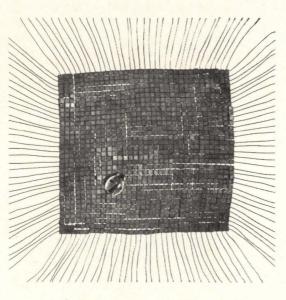

8 or 9-bit code. Two separate channels are provided in a single chassis  $(3^{1}/2^{\prime\prime})$  high) for mounting in any standard relay rack. Model 4047 utilizes magnetic tape-wound cores (see insert) and silicon circuitry to provide readouts of arbitrary binary functions.

Model

4292

### model 4043 magnetic code converter

Model 4043 Magnetic Code Converter accepts a parallel 8-bit "argument" as an input and produces a parallel 8-bit function as an output. The 256 binary "function" numbers are completely arbitrary — they are specified by the user and permanently wired into the 32-bit core matrix.

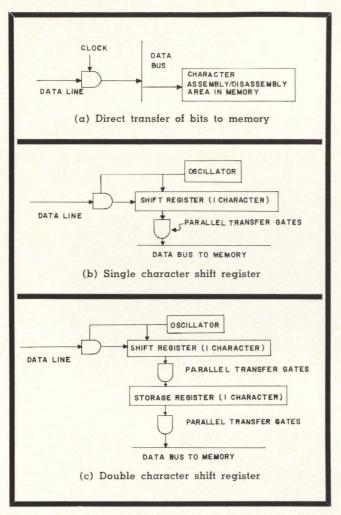

### magnetic Timers