# THE OCTOBER 1974 VOL. 53 NO. 8 BELLSYSTEM TECHNICAL IOI IRNAI

#### LAMP: LOGIC ANALYZER FOR MAINTENANCE PLANNING H. Y. Chang, G. W. Smith, Jr., 1431 System Description and R. B. Walford S. G. Chappell, C. H. Elmendorf, Logic-Circuit Simulators 1451 and L. D. Schmidt S. G. Chappell 1477 Automatic Test Generation for Asynchronous Digital Circuits H. Y. Chang and Controllability, Observability, and Maintenance 1505 G. W. Heimbigner Engineering Technique (Comet) T. T. Butler, T. G. Hallin, Application to Switching-1535 System Development J. J. Kulzer, and K. W. Johnson **GENERAL ARTICLES** T. S. Chu Rain-Induced Cross-Polarization at 1557 Centimeter and Millimeter Wavelengths J. McKenna, Design Considerations for a Two-Phase, 1581 N. L. Schryer, Buried-Channel, Charge-Coupled Device and R. H. Walden J. A. Arnaud Pulse Spreading in Multimode, Planar, 1599 Optical Fibers D. Marcuse Theory of the Single-Material Fiber 1619 J. A. Arnaud Theory of the Single-Material, Helicoidal 1643 Fiber E. A. Ohm A Proposed Multiple-Beam Microwave 1657 Antenna for Earth Stations and Satellites J. C. Candy Limiting the Propagation of Errors in 1667 One-Bit Differential CODECs Contributors to This Issue 1677

#### THE BELL SYSTEM TECHNICAL JOURNAL

#### **ADVISORY BOARD**

D. E. PROCKNOW, President,

Western Electric Company, Incorporated

W. O. BAKER, President,

Bell Telephone Laboratories, Incorporated

W. L. LINDHOLM, Vice Chairman of the Board,

American Telephone and Telegraph Company

#### **EDITORIAL COMMITTEE**

W. E. DANIELSON, Chairman

F. T. ANDREWS, JR.

C. B. SHARP

S. J. BUCHSBAUM

B. E. STRASSER

I. DORROS

D. G. THOMAS

D. GILLETTE

W. ULRICH

J. M. NEMECEK

F. W. WALLITSCH

#### **EDITORIAL STAFF**

- L. A. HOWARD, JR., Editor

- P. WHEELER, Associate Editor

- J. B. FRY, Art and Production Editor

- F. J. SCHWETJE, Circulation

- S. G. CHAPPELL, Coordinating Editor of LAMP System Articles

THE BELL SYSTEM TECHNICAL JOURNAL is published ten times a year by the American Telephone and Telegraph Company, J. D. deButts, Chairman and Chief Executive Officer, R. D. Lilley, President, J. J. Scanlon, Executive Vice President and Chief Financial Officer, F. A. Hutson, Jr., Secretary. Checks for subscriptions should be made payable to American Telephone and Telegraph Company and should be addressed to the Treasury Department, Room 1038, 195 Broadway, New York, N. Y. 10007. Subscriptions \$15.00 per year; single copies \$1.75 each. Foreign postage \$1.00 per year; 15 cents per copy. Printed in U.S.A.

# THE BELL SYSTEM TECHNICAL JOURNAL

DEVOTED TO THE SCIENTIFIC AND ENGINEERING

ASPECTS OF ELECTRICAL COMMUNICATION

Volume 53 October 1974 Number 8

Copyright @ 1974, American Telephone and Telegraph Company. Printed in U.S.A.

#### LAMP:

# **System Description**

By H. Y. CHANG, G. W. SMITH, Jr., and R. B. WALFORD (Manuscript received February 28, 1974)

A general description of the Logic Analyzer for Maintenance Planning (LAMP) system is presented. LAMP is a digital-logic simulation and analysis system used for logic-design verification, for generation and evaluation of fault-detection and diagnostic tests, and for generation of the trouble-location manual (or fault dictionary) data. It is implemented on the IBM 360/370 TSS and OS machines (for both interactive and batch operations), and has been in active use at Bell Laboratories in the development of electronic switching systems, data set facilities, transmission equipment, and advanced integrated circuit technologies.

#### I. INTRODUCTION

The explosive evolution of digital devices, computers, and systems since the invention of the transistor has necessitated a parallel industry-wide development of tools for the design and test of logic circuits. Whereas the oscilloscope was the mainstay of the digital circuit designer in the early days of discrete-transistor logic circuits, it soon proved to be inadequate for design verification and fault-behavior testing of large systems employing integrated, digital logic. In response to this need for better logic-circuit-development tools, a host of digital-simulator algorithms and simulator systems has been produced.<sup>1–3</sup>

The need for reliable and dependable electronic switching systems (ESS) poses critical design problems. Computer-aided techniques can be used effectively for:

- (i) Analysis and enhancement of system diagnosability.

- (ii) Logic-design verification.

- (iii) Generation of fault-detection tests.

- (iv) Analysis of faulty-circuit behavior.

- (v) Verification and evaluation of diagnostic-test designs.

- (vi) Production of trouble-location manuals (TLMs).

The LAMP system has been designed to attack these problems in a systematic manner.

This paper provides a brief description of the LAMP system organization and features, and is intended to serve as background for the four following papers. These provide details of the logic simulators, the automatic-test-generation system, and the techniques for organizing system design for diagnosability.<sup>4–6</sup> They include a specific example of how LAMP was employed in the development of a large processor for an electronic switching system.<sup>7</sup>

#### II. EVOLUTION OF THE LAMP SYSTEM

The decision to build a machine-aids system with digital-simulation capability was motivated by the successful use by Bell Laboratories designers of the sequential analyzer. The use of this simulator showed the great advantages of using simulation for logic testing and fault diagnosis. By 1966, Bell Laboratories was incorporating simulation techniques into the design cycle of electronic-switching-system equipment. However, there were several difficulties in the day-to-day use of this simulator. It had a restrictive logic model, long turnaround time due to remote computer location, and no capability for handling large circuits (for example, circuits having as many as 10,000 gates). Because no simulator then available could meet the growing demand for logic-simulation service, a decision was made to develop an advanced logic-simulator system which would grow and adapt to Bell Laboratories current and future needs.

It is instructive that the motivation to develop a design-aids system came from the potential users of that system. Likewise, the initial design objectives and the evolution of the system were influenced to a large extent by the intended users. This has resulted in a very sophisticated, user-oriented system which continues to grow and evolve to meet the changing requirements of the designer.

The initial system was made available to users in late 1969 on IBM System/360 TSS at Bell Laboratories, Naperville, Illinois. It had only a modest set of features. However, the user reactions were generally favorable. Since then, substantial improvements in system performance and capabilities have been incorporated. The TSS version of LAMP was converted to run on IBM System/360 OS in mid-1970 and was made available to Bell Laboratories users at Holmdel, New Jersey, and Columbus, Ohio. Automatic-test-generation capability was incorporated in early 1972; and the facilities to analyze system structural diagnosability were implemented in late 1972. The LAMP system is in active use in the development of many ESS projects as well as other non-ESS work such as the development of data-set facilities, transmission equipment, and advanced integrated-circuit technologies. The current user group includes twenty organizations from nine Bell Laboratories locations (Murray Hill, Whippany, Holmdel, Allentown, Columbus, Merrimack Valley, Indianapolis, Denver, and Naperville).

#### III. SYSTEM ORGANIZATION

LAMP is a system of programs designed to be used for logic-design verification, evaluation of fault-detection tests and diagnostic programs, and generation of the trouble-location manual (or fault dictionary) data. It is implemented on the IBM 360/370 TSS and OS machines (for both interactive and batch operations). The current version can handle circuits containing up to 65,000 gates. The system is composed of four basic parts:

- (i) A circuit-description-language compiler.

- (ii) A command-language interpreter.

- (iii) A collection of design tools composed of an automatic-test-generation (ATG) system; 4 a controllability, observability, and maintenance engineering techniques (COMET<sup>5</sup>) system; and a family of simulators. 6

- (iv) An output system.

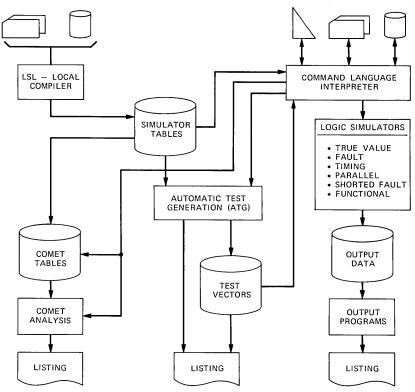

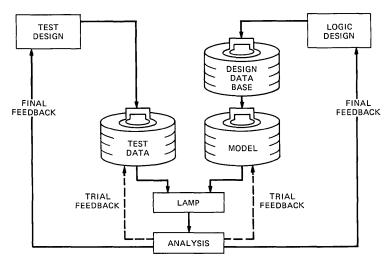

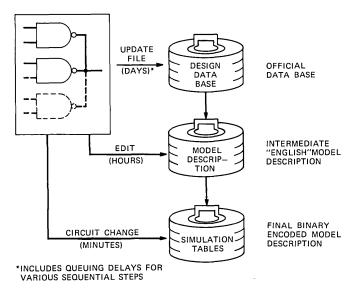

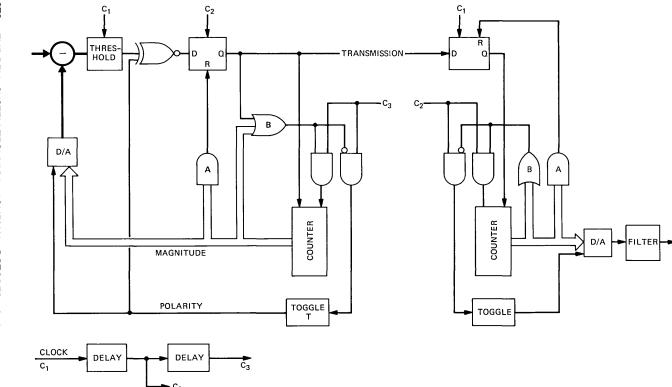

A block diagram showing the functional relationship of the various parts of the LAMP system is presented in Fig. 1. A logic circuit can be described to the LAMP system through a user-oriented language called *LSL-LOCAL*. The circuit description is then translated by the language compiler into *simulation tables*. The *command-language interpreter* directs all the actions of simulation, test generation, and diagnosability analysis in accordance with user-specified commands and information stored in the simulation table.

LAMP: SYSTEM DESCRIPTION 1433

Fig. 1—Block diagram of LAMP system.

For a given logic-circuit description, the ATG system can automatically produce the test-vector information. To verify logic design and to study faulty-circuit behavior, a family of *simulators* can be used. The inputs applied to the simulators can be manually generated and/or generated by the ATG programs. The simulators are capable of simulating circuit behavior in either fault-free or faulty mode, with facilities to handle race and oscillation conditions and to perform detailed timing analysis.

If the purpose at hand is to determine the diagnosability of the design, the *COMET system* can be used to assist the users to organize systems design for diagnosability by systematically determining the optimum placement of control-access and monitor points. Simulation and analysis results are then collected under the control of an *output system*. Numerous output options can be specified that allow users to obtain information concerning logic verification, timing analysis,

and other data-processing information at the time of simulation or afterwards.

In the following sections, the salient features of the various major functional blocks in the LAMP system will be described.

#### 3.1 Circuit description input language

A logic circuit is described to the LAMP system through a user-oriented language called LSL-LOCAL. This language permits the entry of all information concerning the particular circuit either at the gate level or at the functional level. At the gate level, circuits are described in terms of logic elements such as NANDS, NORS, ANDS, ORS, and NOTS, whereas the functional level the circuits are expressed as memories, registers, clocks, etc. LSL-LOCAL was designed as an easily extendible language, to be used by circuit designers and diagnosticians who may not be trained as programmers.

Once the circuit description is entered, the LSL-LOCAL language processor compiles the description into data tables to be used by the simulator(s), the ATG system, and the COMET analysis programs. The language processor has a substantial number of checks built into it to detect and intercept most errors before they can get into the system. These checks include syntax checks (for missing parameters, illegal characters, etc.) and circuit connectivity and consistency checks such as fan-in/fan-out limits. These features enable the users to check the coding of a circuit efficiently in terms of cost and time.

The original version of the language processor was developed in late 1969. Since then, three major revisions have been implemented to enhance its capability and performance. Many of the improvements were incorporated to support a wider range of applications, and the language has become a standard logic design input language in Bell Laboratories.

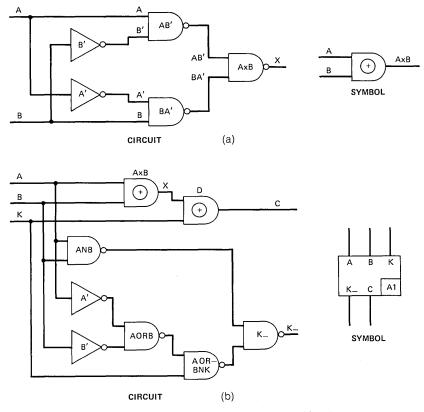

As an example of the LSL-LOCAL circuit description, an exclusiveor circuit as shown in Fig. 2a can be encoded as:

```

CKTNAME: XOR;

INPUTS:

A, B;

OUTPUTS:

X;

NOT:

A', A;

B', B;

NAND:

AB',

(A, B');

BA',

(B, A');

A \times B.

(AB', BA'),

(gate name) (input list) (output)

```

The description generally consists of three parts: (i) the CKTNAME statement, which introduces the circuit description and declares the name of the circuit; (ii) connection declarations, which specify the names and the types of all the input/output signals of the circuit; and (iii) interconnection blocks, which specify elements and networks used in the circuit and how these are interconnected. The hierarchical structure of the language allows the specification of circuits in a modular fashion. Thus, the exclusive-or circuit can be used as an element in describing a single-bit adder [see Fig. 2(b)]:

```

CKTNAME: ADDERI;

INPUTS: A, B, K;

OUTPUTS: C, K_;

XOR: A × B, (A, B), (X);

D, (X, K), (C);

NOT: A', A;

B', B;

NAND: ANB, (A, B);

AORB, (A', B');

AORBNK, (AORB, K);

K_, (ANB, AORBNK);

```

These single-bit circuits can then be used to describe an *n*-bit adder or other more complex logic element(s). There is no explicit limit on the number of levels of nesting in describing circuits using LSL-LOCAL. A user can very conveniently construct the data base of a large circuit or system by combining the various data bases from its component circuit modules.

#### 3.2 Command system

1436

The control of LAMP system action for test generation, simulation, and COMET analysis is accomplished by means of a command-language structure. A large selection of interactive commands is available which enables the users to compile and edit a circuit description, specify simulation-test vectors, make simulation runs, observe circuit behavior, gather circuit statistics, determine optimal placement of maintenance-access and observation points to enhance diagnosability, and specify types of simulation and analysis output. At present, there are approximately 80 commands in the system, many of which were implemented at the request of users. The commands are highly user-oriented so that one can easily learn the use of the system after a relatively minor amount of instruction.

Fig. 2—(a) Exclusive-or circuit. (b) One-bit adder circuit.

The system structure is implemented with four levels of hierarchy. On the base level is the executive routine which reads commands entered by the system user and interprets them as to type. It then calls the appropriate routine to handle the command. On the next level are the command handlers whose functions are to process the command line and call the appropriate functional processors and service routines. On the third level are the functional processors; they are designed to perform specific functions such as simulation, circuit-description and test-vector compilation, circuit modification, processing control, and interactive control. On the fourth level are the various service routines that perform such tasks as gate-name retrieval, print control, vector translation, preliminary processing of data lines, file accessing, and printing.

1437

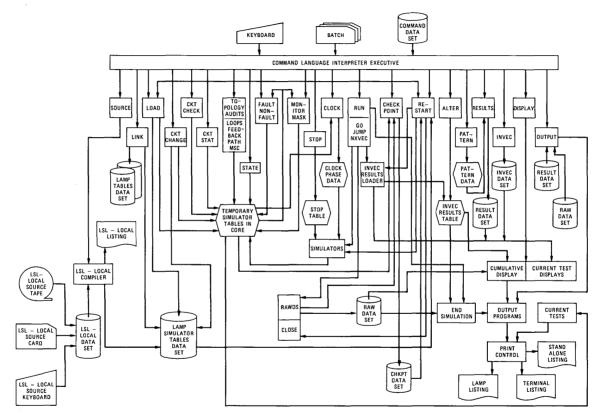

To illustrate the richness of the command language, a few of the most commonly used commands for logic simulation are described. Referring to Fig. 3, to enter circuit descriptions into LAMP, the LSL-LOCAL encoding of the circuit will be first compiled (using SOURCE) and the resultant simulator tables loaded (using LOAD). A circuit can also be formed by combining several circuits into one using LINK. Should it become necessary to modify the circuit logic without recompiling the entire circuit, then CKTCHANGE can be used to connect/disconnect gates, add gates, and rename, change, or remove gates.

The input test vectors for simulation can be described in either trinary (0, 1, and "don't know"), octal, or hexadecimal form (using INVEC), or in terms of vector names defined by PATTERN. In certain applications, the STATE command is used to set the circuit-state variables to initialize a circuit before a simulation run. Internal gates of the circuit can be treated as additional circuit outputs or test points by issuing the MONITOR command. Conversely, normal circuit-output leads can be MASKED out for a particular run.

The what, when, and how much of the simulation statistics that are to be processed after a run are defined through RESULTS. A simulation is initiated by the RUN command and can be temporarily halted by a STOP command. At a STOP, the user may interrogate the state of the simulation and obtain simulation statistics accumulated up to that point (by using the DISPLAY command), or he may overwrite the next input vector in the INVEC data set by issuing an ALTER command. The simulation can be resumed by issuing a GO command. If the user wishes to change the course of simulation during a STOP, he can use the JUMP feature to skip unwanted test vectors.

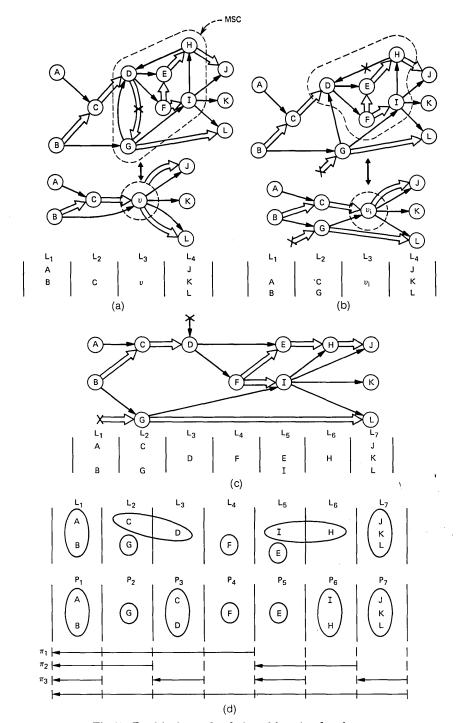

To facilitate the use of the LAMP system in the production mode, many commands have been developed for analyzing circuit topology, gathering circuit statistics, and performing audits. Some examples are the CKTCHECK command to check the consistency of simulation tables and to provide statistical information such as counts of gate and functional types, average fan-in and fan-out for each type, percentages of types to total, etc., and the CKTSTAT command which prints a brief summary of circuit statistics including number of gates, number of circuit inputs, number of circuit outputs, number of clocks, and number of nonfaulted gates. For topological analysis, the LOOPS command allows one to identify all loops within a circuit or contained by a specified gate, the FEEDBACK command identifies the minimum number of feedback loops within the circuit, the PATH command finds the shortest path between a specified gate and any input, and the MSC

Fig. 3—Examples of commands used in simulation.

command identifies all maximally strongly connected sets of gates within the circuit. All these commands have been proven to be extremely useful, especially in the course of simulating large circuits (e.g., those containing 50,000 gates) under fault conditions.<sup>7</sup>

While the LAMP commands generally assume interactive use of the system (on 360/TSS), they also permit the use of the system in the noninteractive mode (such as 360/TSS batch or 360/370 OS). In these cases, some advance planning must be done to enable the runs to be completed successfully.

#### 3.3 Major tools

There are three major tools in the LAMP system: an automatic-test-generation (ATG) system, a family of simulators, and a system for diagnosability analysis (COMET). Detailed descriptions of these tools are covered in the companion papers.<sup>4–6</sup> The purpose of this section is to describe the salient features of these systems and to briefly describe the interactions among them and the rest of the LAMP system.

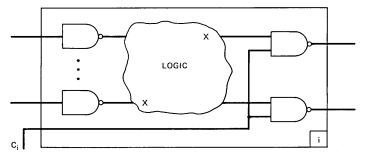

#### 3.3.1 Automatic-test-generation (ATG) system

ATG is a system of programs that can automatically produce the test-vector information for a given logic-circuit description. The faults considered are the classical input open, output stuck-at-one, and output stuck-at-zero for each gate in the circuit. There are two major differences between ATG and those test generators that have been discussed in the literature. First, ATG is capable of handling both combinational and sequential circuits without the need to identify feedback lines. Second, the system treats logic circuits as an interconnection of unit- and zero-time-delay gates, and thus improves the accuracy of the circuit modeling.

ATG interacts with other parts of the LAMP system via the command-language interpreter (see Fig. 1). A set of about 20 commands is available to the user to set the initial conditions (e.g., loading the circuit description, specifying sequence length of the test), select test-generation strategies, specify output procedure, and direct the general course of action. The fault-detection level achieved by the tests generated by ATG can be evaluated by using the fault simulators available in the LAMP system. If the evaluation results indicate that the detection level is not adequate, ATG can be called again to generate more tests, by using different test strategies and/or changing the sequence length of the tests. This test-generation and evaluation loop

can be repeated several times until a specified level of detectability is achieved.

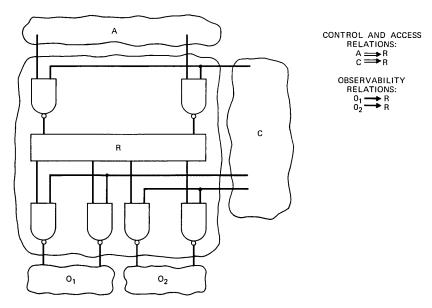

# 3.3.2 Controllability, Observability, and Maintenance Engineering Techniques (COMET)

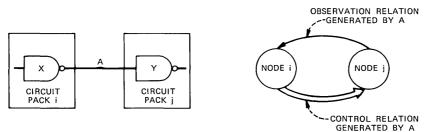

Past experience has indicated that the effectiveness of diagnostic testing depends not merely on the techniques used in deriving tests and test results, but also on the inherent structural diagnosability of the unit.\* The ATG system is a tool for aiding the derivation of test vectors for given circuits. The COMET system, on the other hand, employs a technique that enables one to determine for a given circuit the optimal placement of control-access and monitor points for diagnostic testing.

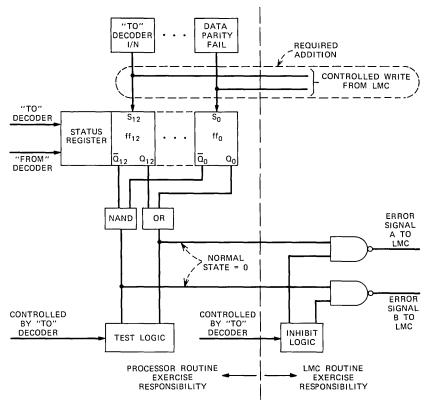

The COMET analysis is initiated by entering the connectivity of the functional blocks of a unit via LSL-LOCAL (see Fig. 1). The control and observation relations among the various functional nodes are automatically created from the connectivity (or simulator) tables. Through the use of the command-language interpreter, the user can then direct COMET to analyze, to examine, and to modify the topological structure of the unit. The modification of the structure for additional control and/or observation is performed automatically, or it can be explicitly directed by the user. Once the design has been COMETized, it enjoys the following advantages:

- (i) Trouble-location-manual data can be generated and updated without the use of fault simulation.

- (ii) Multiple faults and all nonclassical faults are locatable if they are detectable.

- (iii) Diagnostic information can be easily updated in accordance with hardware change(s).

- (iv) An orderly approach to the implementation of an overall diagnostic design is provided.

- (v) The fault-location procedure is substantially simplified.

#### 3.3.3 Logic simulators

In the heart of the LAMP system are the logic simulators. These are the programs that actually perform the simulation of the circuit under test. A total of six simulators is available, each of which is designed to

<sup>\*</sup> Depending on the level of integration and the purpose at hand, a unit can be interpreted as a processor, a functional module, a circuit pack, or an LSI chip.

suit a particular condition.\* Under the control of the command-language interpreter, one or more of the simulators can be called to simulate a particular circuit. The six simulators available in the LAMP system are:

- (i) True-value simulator—This simulator simulates only the true-value (or nonfaulted) conditions of the circuit. Simulation is done at the gate level.

- (ii) Fault simulator—This simulator can simulate the action of classical stuck-at-type faults (input open, output stuck-at-zero, and stuck-at-one) in addition to the true value. This enables one to study the behavior of faulty circuits, to evaluate the faultdetection capability of maintenance-check circuits and tests, and to generate diagnostic data for trouble-location-manual production.

- (iii) Timing simulator—This simulator allows the specification of individual rise and fall times of all gates in the circuit but does not simulate the effect of the stuck-at faults. It is designed primarily for detailed timing analysis to verify that the circuit will work under worst-case conditions.

- (iv) Parallel simulator—The features of this simulator are similar to the ones available in the fault simulator. The major difference is that the parallel simulator employs a technique whereby the true value and a small set of faults are simulated concurrently.

- (v) Shorted-fault simulator—This simulator allows for simulation of nonclassical faults such as crossover shorts and shorts between adjacent paths. It is useful in aiding the design of manufacturing tests for circuit pack check-out.

- (vi) Functional simulator—This simulator allows one to simulate the circuit behavior at a higher level (e.g., registers, memories, etc.) than at the gate level. Functional simulation is most useful in verifying initial logic design where detailed knowledge of gate-level logic is not available or the function(s) cannot be conveniently modeled by gate-level techniques.

The cost effectiveness of the LAMP system depends on the user's choosing the correct simulator or simulators for use in his application. Consequently, it was found necessary to combine the results of more

<sup>\*</sup> This was found desirable and cost effective especially in a production environment where system performance and accuracy are often weighted against each other in the search for an optimum mix.

than one simulator if the model of one simulator is not sufficient for a particular application. This is accomplished by the output system.

#### 3.4 Output system

In LAMP, a versatile output system is available that enables users to collect simulation and analysis results in one of several different formats (or in user-generated formats). Outputs may be specified at any time during or after the run. The results of several simulation runs may be combined together at some point after the simulation has taken place to produce the desired output. Simulation runs that are so combined may be from different simulators. All these options can be specified by the command language.

Among the various output options available, some of the most commonly used will be described here. To verify the validity of the logic design, the VALUES option is often used, which lists the inputs and outputs along with the (1, 0, and "don't know") values of outputs for a given input test vector. In some cases where one is interested in internal states of the circuit, one can use GATEIO option to display the value of selected gates and their driving and driven gates. This feature is especially useful during a simulation run when the run is temporarily halted or has gone into oscillation; another specific use of this feature is to display circuit connectivity. Another format often used to display the outputs of timing and the true-value simulators is TLGRAPH. TLGRAPH is an oscilloscope-like trace of the signals on the output gates, from the time the test is applied until the time the circuit settles down. Whenever the value of an output gate changes, the time interval is recorded as well as the output gate values. This format has proven to be extremely valuable in studying worst-case timing conditions.

A variety of output formats is also available for studying the completeness, accuracy, and resolution of diagnostic tests. The ATP format lists all the faults that have not been detected for the test sequence simulated. The RAW output format lists the output gate name, each gate's true value as well as the number of faults that causes each gate's true value to be complemented, and a listing of these faults. For a large run where a user is interested in only a summary of the run, the MATRIX output can be used to show the faults detected by each test; the result is presented in the form of a matrix or a fault table. If the user is interested in fault partitioning and diagnosability information, he can choose the TREE output that lists the test results in the form of a diagnostic tree by grouping all those faults causing the circuit to behave in the same manner for a particular test sequence.

Facilities are also provided to allow the user to write his own output processing program. The raw output data set (RAWDS) contains all the raw data on the output gates from a simulation, including information such as the input vector on each test for which raw data are collected, names of inputs and outputs, fault cross-referencing information, fault and nonfault information, and certain circuit statistics. The user can manipulate this information to create the desired output format. The availability of this feature has substantially reduced the burden that otherwise would be imposed on the LAMP system developers to meet the wide variety of user needs.

#### IV. THE ROLE OF LAMP IN THE DESIGN PROCESS

The process by which a logic design becomes a completed product has become very complex with the advent of integrated-circuit technology. This process is made even more difficult in the telephone industry because of the stringent up-time requirement of the switching machines.<sup>11</sup> The ability to diagnose any equipment failure thus becomes an important consideration in the design and implementation of these machines.

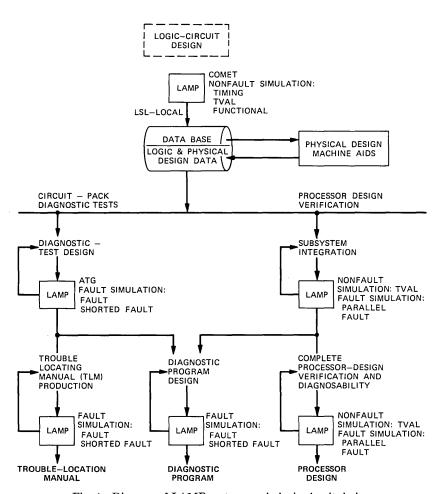

The design and implementation process for a new switching system processor is made feasible by the constant use of computer-aided-design tools. Figure 4 shows the overall implementation process from the initial logic designs through to the completed processor. It also illustrates how the various major features of the LAMP system can be used in each design step.

The start of any major logic design project is the specification of the system architecture along with the basic design decisions. The COMET feature of LAMP helps this process by providing information about the diagnosability of a proposed design. With this tool, the global diagnosability of a system design can be established. Once this overall design step has been completed, the logic can be partitioned into individual circuit packs and detailed circuit designs can begin. In this phase of the design, the designer uses the true-value simulator for design verification, and frequently uses the timing simulator to make sure that the logic-timing functions are correct.

The use of these simulators requires that the logic circuit be encoded in the LSL-LOCAL language. The encoding of the circuit in the LSL-LOCAL language at this point accomplishes two basic functions. The first function is to catch any circuit discrepancies through the use of audits in the language processor and the second is to provide a machine-readable form of the circuit design. This latter function is basic to the entire computer-aided-design function.

Fig. 4—Diagram of LAMP system use in logic-circuit design.

In addition to the basic circuit information, it is possible to input physical design information through the LSL-LOCAL language. When the designer is satisfied with the design of the circuit on a circuit-pack basis, the verified logic is then used as a base for the physical design process. Here the various additional machine-aided tools are used to perform partitioning, placement, and routing. The successful completion of physical design thus establishes a logical and physical design data base from which other uses of LAMP in the design process may take place. Some examples of these activities are: (i) derivation of circuit-pack diagnostic tests for manufacturing check-out purposes;

(ii) design verification of the subsystems (which are formed by combining circuit packs) and the complete processor (which is formed by combining the subsystems); and (iii) design and verification of diagnostic program(s) and generation of TLM data.

#### V. EXAMPLES OF LAMP SYSTEM USE

To provide some insight into the use of the LAMP system, a few examples of simple procedures performed with the LAMP system are presented. Because of the large number of ways the LAMP system is utilized, it is impossible to cover more than a small area of the system functions. The examples shown, however, are representative of typical activity.

All user communication with the LAMP system is by use of a command language. Each command represents an action to be taken by the system. In conversational use, the system prompts for the next input by means of a > character. Some commands which require additional information prompt the user with an @ character.

Example 1—Logic Verification Run (TSS Log-on Procedure)

System: LAMP DESIGN AUTOMATION SYSTEM

ENTER COMMANDS

>

User: load expl. tables

System: CKTNAME: EXAMPLE.CIRCUIT VERSION 06/24/73

>

User: run tval expl.test.vector,expl.output.results,p System: LAMP TVAL SIMULATOR—VERSION 2.5

>

User: display values,t

System: AT INPUT NO. = 3

INPUTS: SA SB CA CB

SEN CEN

OUTPUTS: SOUT COUT

INPUTS: 100001 OUTPUTS: 11

>

User: end

In this example, the user desires to test the "good" operation of his logic design by exciting his circuit with a series of prestored input vectors. The circuit description has been previously compiled from an

LSL-LOCAL encoding into a data set called "expl.tables." The prestored input vectors are located in the data set "expl.test.vectors." Since he is not interested in fault analysis, the TVAL (true-value) simulator is chosen. For nonfaulted operation, this simulator is the most efficient of the six available. The results he needs for his analysis can be obtained in two ways. The bulk of the output is produced via the computer high-speed printer. The particular types of results the user wants are specified by the contents of data set "expl.output. results." The "p" indicates that the results are to be printed as soon as possible. Because the user wants a quick check of some of the results before the other output is available, he instructs the system to display the input and output gate names along with their associated output values on the terminal after the simulation is completed. Satisfied with the results, he ends the simulation.

Example 2—Creation of the Controlling Data Sets (TSS Log-on Procedure)

System: LAMP DESIGN AUTOMATION SYSTEM

ENTER COMMANDS

>

User: source Isllocal expl.source, expl.tables

System: LOCAL LP START

LOCAL LANGUAGE PROCESSOR—VERSION 3

LOCAL LP END

>

User: results expl.output.results

System: ENTER SIMULATION RESULTS SPECIFICATIONS

(a)

User: after input \*every; values

System: @

User: [default]

System: >

User: invec expl.test.vectors

System: ENTER INPUT VECTORS

(a

User: t'101031'

System: @

User: t'100001'

System: @

User: [default]

System: > User: end

In this example, the user creates the data sets used to control the simulation run shown in Example 1. The first action is to compile the logic-circuit description written in LSL-LOCAL that has been stored in data set "expl.source" in a form that the compiler can use. The compiled information is stored in data set "expl.tables." Next the data set ("expl.output.results") that controls the output results is formed by use of the RESULTS command. The information put into this data set will instruct the simulator to print the values of the inputs and outputs after every input vector has excited the circuit.

Finally, the series of input vectors used to excite the circuit is created by use of the INVEC command. In this case, a series of these input vectors has been created. The input value "3" signifies a "don't care" value.

Only a few of the available commands and options have been shown. However, these should provide an idea of the ways in which the system can be used. Additional examples will be presented in the other papers of this series to illustrate specific points under discussion.

#### VI. CONCLUSION

Present and future designs of digital systems require computer aids during all phases of development, from initial architecture specifications to diagnostic-test design. The efficiency of these tools in performing their intended functions is of great importance, from both internal (efficiency of algorithms) and external (user convenience and usefulness) considerations. Viewed in this light, the LAMP system has been an outstanding success. The use of LAMP has been found to be cost effective in that LAMP provides the designers a convenient facility to assure design quality, to expedite error correction, and to reduce design-rework cost. LAMP also offers the designer a versatile tool to evaluate and verify the system diagnostics before hardware is committed. It has become an integral part of the design of new electronic switching systems and has strongly influenced the methodology of their design.

The other papers in the series will give more detailed descriptions of the use and design of selected portions of the LAMP system.

#### VII. ACKNOWLEDGMENTS

Many of our colleagues have contributed to the development of the LAMP system. Contributions made by R. E. Strebendt, R. E. Michael, and E. A. Rinaldy in the development of LSL-LOCAL, A. B. Marsh in the design of the command system, R. A. Elliott and R. B. Schmidt

in the implementation of output system, and J. R. Burnside, G. A. Raack, R. R. Riser, and F. J. Webb in the development of the OS version of LAMP are gratefully acknowledged. The authors would also like to thank J. A. Harr, W. Ulrich, and R. W. Ketchledge, and the many users for their continuous support and encouragement throughout the development of the system.

#### REFERENCES

- 1. S. Seshu and D. N. Freeman, "The Diagnosis of Asynchronous Sequential Switching Systems," IRE Trans. on Elec. Computers, EC-11 (August 1962), pp. 459–465.

- 2. S. A. Szygenda, "TGAS2—Anatomy of a General Purpose Test Generation and Simulation System for Digital Logic," Proc. ACM-IEEE Design Auto-

- and Similation System for Digital Logic," Proc. ACM-IEEE Design Automation Workshop (June 1972), pp. 116-127.

3. B. H. Scheff and S. P. Young, "Gate Level Logic Simulation," in Design Automation of Digital Systems, Vol. 1, edited by M. A. Breuer, New Jersey: Prentice-Hall, 1972, pp. 101-172.

4. S. G. Chappell, "LAMP: Automatic Test Generation for Asynchronous Digital Circuits," B.S.T.J., this issue, pp. 1477-1503.

5. H. Y. Chang and G. W. Heimbigner, "LAMP: Controllability, Observability, and Maintenance Engineering Technique (COMET)" RST I. this issue presented that the second presented in the second presented

- Maintenance Engineering Technique (COMET)," B.S.T.J., this issue, pp. 1505 - 1534.

- S. G. Chappell, C. H. Elmendorf, and L. D. Schmidt, "LAMP: Logic-Circuit Simulators," B.S.T.J., this issue, pp. 1451-1476.

T. T. Butler, T. G. Hallin, J. J. Kulzer, and K. W. Johnson, "LAMP: Application to Switching-System Development," B.S.T.J., this issue, pp. 1535-1555.

S. Seshu, "The Logic Organizer and Diagnosis Programs," Report R-226, Coordinated Science Laboratory, University of Illinois at Urbana (AD-05927).

D. K. Chia and M. Y. Hsiao, "Boolean Difference for Fault Detection in Asynchronous Sequential Machines," IEEE Trans. on Computers, C-20 (November 1971), pp. 1356-1361.

G. R. Putzolo and J. P. Roth, "A Heuristic Algorithm for the Testing of Asynchronous Circuits," IEEE Trans. on Computers, C-20 (June 1971), pp. 639-647.

- 639-647.

- R. W. Downing, J. S. Nowak, and L. S. Tuomenoksa, "No. 1 ESS Maintenance Plan," B.S.T.J., 43 (September 1964), pp. 1961–2020.

Copyright © 1974 American Telephone and Telegraph Company

THE BELL SYSTEM TECHNICAL JOURNAL

Vol. 53, No. 8, October 1974

Printed in U.S.A.

#### LAMP:

# **Logic-Circuit Simulators**

By S. G. CHAPPELL, C. H. ELMENDORF, and L. D. SCHMIDT (Manuscript received February 20, 1974)

The algorithms used for logic-circuit simulation in the Logic Analyzer for Maintenance Planning (LAMP) system are described. Several simulators are available to allow a cost-effective tradeoff between simulation cost and the level of detail needed for a particular application. The truevalue simulator provides efficient simulation of fault-free logic circuits. Two fault simulators simulate the classical stuck-at faults as well as shorted-gate-output faults. Hyperactive faults, those faults which cause an inordinate amount of simulation activity, are discussed along with their impact on simulation time. A four-value simulation logic is described which simplifies circuit initialization procedures.

#### I. INTRODUCTION

The use of digital simulation of logic circuits has been widely accepted in the computer and telephone industries to verify logic-circuit designs, to analyze the behavior of logic circuits in the presence of faults (such as gate outputs permanently stuck at logical 0 or logical 1, open gate inputs and shorted gate outputs), and to aid the generation of fault-detection tests for logic circuits.

Most simulators described in the literature can be divided into three categories. The first category includes the true-value simulators that simulate the circuit in the absence of any faults or, by altering the circuit description, simulate the circuit in the presence of one permanent fault.<sup>1,2</sup> The second category includes the parallel simulators that concurrently simulate the fault-free circuit and the effect on the circuit of a small set of single permanent faults.<sup>2–4</sup> The third category includes the deductive simulators that concurrently simulate the fault-

free circuit and the effect on the circuit of all single permanent faults. The Logic Analyzer for Maintenance Planning (LAMP) system contains simulators from each category.

The LAMP system has been extensively used over the last four years to simulate the No. 1A and No. 4 Electronic Switching Systems to verify the logic design, to aid the generation of diagnostic tests, and to analyze the behavior of the circuits in the presence of faults. Circuits containing 52,000 gates and 23,000 single faults have been simulated using the IBM 370 Model 168 as the host machine.

The simulators in the LAMP system provide a complete range of capabilities for the design of logic circuits. Circuits and subsets of circuits can be simulated at the gate level (NAND, AND, OR NOR, NOT), at the functional level (register, memory, etc.) or at the hybrid level (a combination of gates and functions). At the gate level, gates can be modeled in sufficient detail to account for variations of such parameters as temperature and wiring capacitance. Several different classes of faults can be considered including gate outputs stuck at logical 0 or logical 1, gate inputs open, and shorted gate outputs. Facilities have been provided to help the user debug his logic design and his diagonstic tests.<sup>6</sup>

This paper presents a description of the LAMP simulators. In the first section, the family of simulators are described including an example of their use in the design of a logic circuit. This is followed by a description of the common attributes of the LAMP simulators. In the second section, the basic LAMP simulator for fault-free circuits is described and is the basis for describing the other LAMP simulators. In the next sections, descriptions of the deductive fault simulators and functional simulators are presented. In the seventh section, the detection and elimination of a class of "hyperactive" faults is described. Finally, data on the performance of the various simulators are presented.

#### II. THE SIMULATOR FAMILY

This section describes the use of the various LAMP simulators during the design of a logic circuit. This is followed by a description of the common attributes of LAMP simulators.

As the level of logic-circuit integration increases, it becomes more difficult to build "breadboard" models. This often means that more emphasis must be placed on the results of logic-circuit simulation. Therefore, it is desirable to use an extremely accurate simulation model of the logic circuit. Unfortunately, as the accuracy (level of detail)

of the model increases, so does the cost of simulation. Since LAMP was designed for large circuits (up to 65,000 gates), cost is an important parameter. One way to partially circumvent this problem is to utilize several different simulators, each of which provides a detailed model especially tailored to optimize the simulation of a physical circuit.

#### 2.1 Use of simulation during circuit design

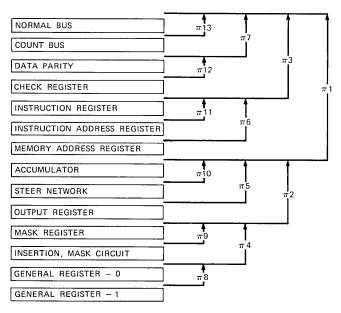

Consider the design of a small processor. Given the overall specifications for the processor, the designer can create a functional level model of the circuit where the building blocks include registers, memories, decoders and an arithmetic unit. Using the functional simulator, the design can be simulated at the functional level to verify the operation and timing of the processor. The processor can now be divided into functional units for detailed logic design of each unit. The functional units may be further divided into circuit packs containing a few hundred gates each.

The detailed logic design of the circuit pack is performed and is verified using the LAMP true-value simulator. The true-value simulator simulates only the fault-free circuit by modeling the logic gates as logic elements followed by pure time delays. This is a fast, economical simulator.

If the timing of the signals on the circuit pack is critical, the designer may wish to perform a more detailed timing analysis of his circuit using the LAMP timing simulator. The timing simulator<sup>7</sup> allows each gate to be assigned minimum and maximum time delays for the rising and falling signal transitions. The gate output is treated as unknown during the time between the minimum and maximum transition delays. This provides a more detailed analysis of circuit behavior in the presence of variations in gate time delays resulting from such factors as temperature change, gate loading, and capacitance. In addition, gate input pulses of shorter duration than the minimum transition delay are ignored and, therefore, do not affect the gate output value.

Once the designer has verified that his logic-circuit design meets the operational specifications, he must generate manufacturing test vectors (circuit input stimuli) to verify the integrity of the newly manufactured circuit pack. Whether the designer creates the test vectors by hand or uses the automatic-test-generation system, he may use the LAMP fault simulator to evaluate the quality of the resulting set of input test vectors. The fault simulator simulates the effect on a

logic circuit of the presence of all single classical (gate input open, gate output stuck-at-zero, and gate output stuck-at-one) faults. This is a deductive simulator<sup>5</sup> that associates with each gate output a fault list containing those faults that will complement the correct (true) logic value (logical 0 or 1) of that gate. The fault lists may contain any number of faults, which theoretically allows the simultaneous simulation of all classical faults. Because of the effort required to process the fault information, the fault simulator is considerably more expensive to use than the true-value simulator. Through the use of the fault simulator, tests can be designed, or the circuit can be modified, to attain the desired level of fault detection.

If the number of faults to be simulated is less than a few thousand, it may be more economical to use the LAMP parallel simulator instead of the fault simulator. The parallel simulator uses parallel fault-simulation techniques<sup>2-4</sup> to simulate up to 2048 single classical faults in one pass. A variable-width-fault word is utilized so that simulation time and storage are minimized. The relative merits of the parallel and deductive fault simulation techniques are presented in Ref. 9.

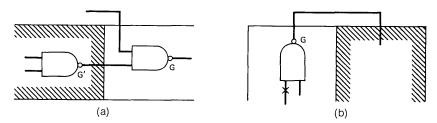

After the chip layout and printed-wire routing for the circuit pack is complete, the designer may choose to examine the effectiveness of his classical fault tests against possible shorted faults using the LAMP shorted-fault simulator, which simulates the effect on a logic circuit of the presence of single pairs of gate outputs shorted together. If two gate outputs, A and B, are shorted together where gate A has the value logical 1 and gate B has the value logical 0, it is assumed that the logical 0 will dominate and the output of gate A will be forced to logical 0. A user option is available which forces logical 1 to dominate logical 0. Potential shorted faults that may be simulated include shorted adjacent pins on chips, shorted adjacent paths on the printed wiring board, and shorted crossover points on the printed wiring board. These data are obtained from the manufacturing information for each circuit. The shorted-fault simulator uses the deductive simulation technique.

After the circuit packs are designed, the designer can link all the circuit packs together to form the complete processor and perform the same logic verification process on the larger circuit with a few minor differences. The true-value and timing simulators are used both to verify the logic design of the processor and to verify the diagnostic program for the processor. The various fault simulators are used to evaluate the effectiveness of the diagnostic throughout the design-change cycle until the design is complete.

#### 2.2 Common simulator attributes

The common attributes of the LAMP true-value, fault, timing, shorted-fault, parallel, and functional simulators are described below.

- (i) The version of LAMP that is described is implemented on the IBM 360 Model 67 and IBM 370 Model 168 under the IBM interactive, virtual-memory operating system TSS. A version of LAMP is also available under the IBM operating system OS.

- (ii) The first version of LAMP (1969) contained only the fault simulator. New simulators have been implemented as needed, and existing simulators have been improved to produce the complete system for logic simulation now available in LAMP.

- (iii) The simulators can be accessed from an interactive terminal or used in the batch mode via card input or prestored data. Interactive features include the ability to temporarily stop the simulation when any specified gate changes value and the ability to correct from the terminal errors in the circuit design or input data.

- (iv) Logic circuits are simulated at the gate level (NAND, AND, NOR, OR, and NOT) except in the functional simulator, which also accepts descriptions of higher-level blocks such as memories and registers.

- (v) Four simulation values (0, 1, 2, and 3) are used to simulate binary-logic circuits. The simulation values 0 and 1 represent the logic values 0 and 1. Values 2 and 3 represent unknown conditions in the logic circuit. This is explained in more detail in Section 3.2.

- (vi) Conditions that cause the output values of flip-flops to be unpredictable are detected and the flip-flop outputs are forced to the unknown state 3 by a process called race analysis. Possible circuit oscillations are detected by a process called oscillation analysis. Both procedures will be described in more detail in Sections 3.3 and 3.4.

- (vii) LAMP uses discrete event simulation where all activity occurs at integral multiples of the basic increment of simulation time. The basic increment definition is arbitrary and may represent such units as nanoseconds, microseconds, or gate delays. Lists, called timing lists, are maintained by each simulator such that one timing list is associated with each increment of simulation time. Each timing list contains a list of gate-

- output changes scheduled to occur at that increment of simulation time. The timing list associated with the current increment of simulation time is called the current timing list.

- (viii) Selective trace is used so that a gate output is computed only if any of the gate's input signals changed value.

- (ix) The circuit description is contained in a set of two-way, linked-list tables, which include information about each gate such as the driving and driven gates, logic function, time delay, and faults to be simulated. A subroutine, associated with each logic function, examines the gate-input values, computes the new output values, determines whether the output values have changed, and schedules the output change (if any) into some future timing list.

#### III. THE TRUE-VALUE SIMULATOR

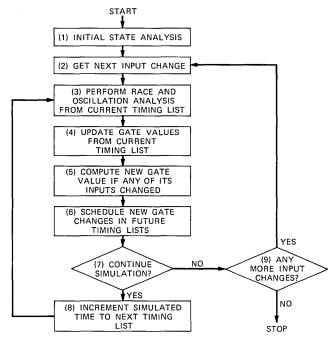

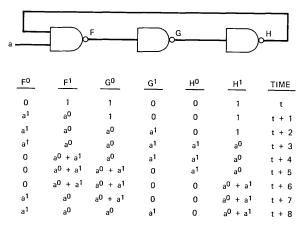

The operation of the true-value simulator will be used as the basis for the presentation of the fault simulators. A simplified flow chart of the operation of the true-value simulator is shown in Fig. 1. This

Fig. 1—Simplified simulation flow.

flow chart is also used in Section 3.5 to describe the overall simulator operation.

#### 3.1 The true-value calculation

The LAMP simulators use four logic values, 0, 1, 2, and 3, to simulate the Boolean logic functions. The 0 and 1 are simply the logical 0 and 1 of Boolean algebra. Values 2 and 3 represent nonpropagating and propagating "don't-know" conditions, respectively. The gate output calculation occurs in Step 5 of Fig. 1.

Value 2 is used to allow efficient initialization of the circuit. Prior to a simulation run, all gates are initially assigned a value of 2. Its nonpropagating feature is demonstrated by the following table of a two-input NAND gate:

| A    | В | $\overline{\mathbf{A} \cdot \mathbf{B}}$ |  |

|------|---|------------------------------------------|--|

| 2    | 0 | 1                                        |  |

| 2    | 1 | $\mathbf{Q}$                             |  |

| 2    | 2 | Q                                        |  |

| $^2$ | 3 | Q                                        |  |

where Q means no change in the previous true value.

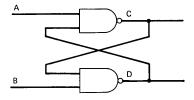

The nonpropagation is necessary to prevent destroying information specified by setting a priori the state of the circuit. For example, in Fig. 2, if the state specification sets C=0, nonpropagation is necessary to prevent the true value of C from being overwritten by a don't know. Value 2 allows C=0 to initialize the flip-flop to C=0 and D=1. A more detailed explanation of the behavior of 2s will be presented in the next section.

True-value 3 is a true "don't know" with full propagation features. The truth table for a two-input NAND gate is shown below:

| A | В | $\overline{\mathbf{A} \cdot \mathbf{B}}$ |

|---|---|------------------------------------------|

| 3 | 0 | 1                                        |

| 3 | 1 | 3                                        |

| 3 | 2 | Q                                        |

| 3 | 3 | 3                                        |

where Q means no change in the present true value.

In Fig. 2, if all 2s were replaced by 3s, then the output of C and D would become 3 even though the user initialized C to logical 0.

Fig. 2-NAND flip-flop.

#### 3.2 Initial-state analysis

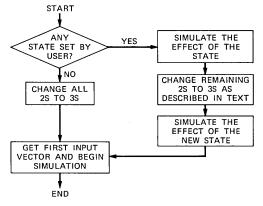

The purposes of the initial-state analysis (Step 1 in Fig. 1) are: (i) to extract as much information as possible from the user-specified circuit state (if any), and (ii) to guarantee that the output of each gate is consistent with its inputs. A flow chart of this procedure is shown in Fig. 3.

True-value 2 is used only during the initial-state analysis which occurs before the first input vector is applied to the circuit. The initial-state analysis is a three-pass procedure that attempts to propagate the effect of any user-specified state through the circuit. Pass 1 has two alternatives. If the user did not set any state, then pass 1 simply changes all of the gates whose output value is 2 to the "true" unknown-value 3 and the simulation of the input vectors begins.

However, if the user has set some initial state, then the initial-state analysis must propagate the effect of that state through the circuit. During pass 1, the circuit contains the logic-value 2 for the "don't-know" condition. The nonpropagation feature of the 2s allows as much information as possible to be extracted by the simulator using only a forward simulation. No attempt is made to set the inputs of

Fig. 3—Initial-state pass.

some NAND gate to logic-value 1 if the output of the gate is logical 0. Thus, LAMP requires that initial states should always be set using the "dominant" value of the particular logic type used. For example, because gate C of Fig. 2 was set to a logical 0, pass 1 would set D to value 1.

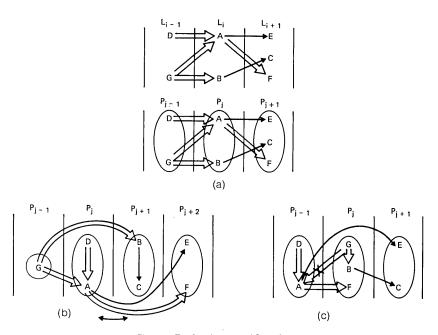

Pass 2 goes through the circuit and changes selected remaining gates whose output value is 2 to new output-value 3. This is necessary because the 3s propagate where the 2s do not. Therefore, leaving the 2s in the circuit can cause incorrect simulation results. However, it is only necessary to change to 3 those gates within maximally strongly connected subgroups (MSCs)<sup>10</sup> having output-value 2. This occurs because the circuit inputs are assumed to support any state which the user sets. Therefore, the input gates as well as any combinational circuitry driven by the inputs maintains true-value 2 until it is eliminated by the first input vector or the next pass.

Pass 3 propagates the newly injected 3s as far as possible. This may have the effect of destroying some incomplete state which the user specified because the circuit is unable to support the incomplete state for all possible complete states. If a complete self-supporting (stable) state is specified, no state information will be eliminated.

Initializing the circuit to some known value can introduce simulation inaccuracies during fault simulation. If the circuit is artificially initialized, there is no record of those faults whose presence would prevent the circuit from reaching the initial state specified. Therefore, it is preferable to apply a synchronizing sequence to the circuit to drive it from an unknown state (all gate output values set to 3) to some known state. The facility to artificially initialize the circuit is provided to help the user and to simplify his work.<sup>11</sup>

#### 3.3 True-value race analysis

Race analysis (Step 3 in Fig. 1) is performed on the basic NAND and NOR flip-flop. Previous simulation techniques attempted to treat the flip-flop as a "black box." However, the "black box" approach leads to inaccurate simulations or to unwieldy simulation algorithms. Therefore, the technique used in LAMP is to detect races as invalid conditions on a set of gates. Since both NAND and NOR flip-flops are handled in a similar manner, only the true-value race analysis for the NAND flip-flop will be discussed here. The basic NAND flip-flop is shown in Fig. 2.

The true-value race state for a NAND flip-flop is A=1, B=1, C=1, and D=1 at the same time, t. From this state, it is impossible

to predict (assuming identical gate behavior) whether C=1 and D=0 or C=0 and D=1 when the flip-flop settles. So as not to arbitrarily resolve races, true-value 3 is assigned to the output of both gates in the flip-flop.

To accomplish this, when the flip-flop was in the A=1, B=1, C=1, and D=1 state at time t, the simulator calculates C=0 and D=0 for the new intermediate output to be scheduled into a future timing list. Since the state C=0 and D=0 is impossible unless the previous state was A=1, B=1, C=1, and D=1, both outputs at logical 0 provide an efficient race-detection mechanism. Also, since C=0 and D=0 are unstable, both C and D will be scheduled to change values at the present increment of simulation time. Therefore, the outputs of a NAND flip-flop are set to true-value 3 and a race declared when:

- (i) The newly calculated, but not yet assigned, outputs of both gates are simultaneously 0.

- (ii) Both gate outputs are scheduled to be changed at the present time.

If the NAND gates are cross-coupled, as shown in Fig. 2, but are not specified as a flip-flop, then race analysis will not be performed. In this case, if the flip-flop is in a race state, the new output C=0 and D=0 will be assigned to the gates in the flip-flop. The next output (assuming the inputs to the flip-flop do not change) will be C=1 and D=1 and the flip-flop will oscillate between C=1, D=1, and C=0, D=0 causing a simulator oscillation.

In addition, because of the behavior of value 3, the condition where the newly calculated output values of the flip-flop are C=0 and D=3 or C=3 and D=0 will cause an oscillation. Therefore, this condition is also detected and declared to be a race. Extensive topological circuit analysis could isolate the undeclared flip-flops, but such analysis is not performed since the circuit designers seldom fail to declare the race-pair gates.

#### 3.4 True-value oscillation analysis

A true-value oscillation (Step 3 in Fig. 1) occurs when the circuit state is unstable as a result of some input conditions. An oscillation is declared if the simulator simulates an arbitrary number, N, of increments of simulation time and the circuit has not stabilized. The value of N is defaulted to be the number of gates in the logic circuit but can be adjusted by the user.

If a true-value oscillation is detected, the old and new true values for every gate B whose output is changing at the present increment of simulated time are compared. If the old and new true values are different for gate B, the new true value is replaced with value 3 since the output of B is changing (i.e., unknown). Value 3 is the new gate output that will be scheduled in some future timing list. When 3s are inserted, the oscillation automatically stops, since a 3 represents both a 0 and a 1.

#### 3.5 The true-value circuit model

The true-value circuit model defines the interactions among the initial-state-analysis, gate-calculation, race-analysis, and oscillation-analysis steps that were presented earlier. Thus, a description of the true-value circuit model is an overall description of the simulator operation.

A simplified flow chart of the basic simulator operation is shown in Fig. 1. The operation includes the following:

Step 1—The circuit is analyzed to check the validity and consistency of any user-supplied initial state, as described in Section 3.1.

Step 2—This step is repeated once for every circuit input vector to be simulated. During this step, the next input vector is obtained and the new input values are assigned to the circuit input leads. The effect of this input vector on the circuit is now propagated through the circuit. Every input gate whose value changed as a result of the new input vector is put into the appropriate future timing list. The future timing lists are examined, as the simulation time is incremented, until the first nonempty timing list is found. This timing list is called the current timing list. Let the present time be  $t_0$  and assume that the set of gates G,  $\{G_i, i = 1, 2, \dots, m\}$ , in the current timing list at  $t_0$  contains all the gates whose outputs are changing at time  $t_0$ . Steps 3 through 6 are performed once for each timing list.

Step 3—Race analysis is performed for each declared flip-flop formed by two gates, both of which are in G.

Step 4—The new outputs are assigned to every gate in G.

Step 5—After all the new outputs of G have been assigned, the output of each gate  $H_j$ ,  $j = 1, 2, \dots, n$ , which is driven by any  $G_i$  whose output has changed, is calculated according to gate model.

Step 6—If the output of some  $H_k$ ,  $1 \le k \le n$ , changed, then  $H_k$  is put into the timing list of gates whose output may change at time  $t_0 + t_i$ , where  $t_i$  is the transition time for  $H_k$ . If the output of  $H_k$  did not change, no further action is taken on the gate. The important feature of this circuit model is that the gates  $H_i$ ,  $i = 1, 2, \dots, n$ , have their inputs calculated based on all new values of the gates in  $\{G_i, i = 1, 2, \dots, m\}$ . That is, every change that is going to occur at  $t_0$  occurs before the output of any gate driven by any of the gates in G is calculated.

Step 7—Simulation may be allowed to continue or it may be interrupted to process a change on the input leads (Step 9) or to return to the command language to process user commands.

Step 8—The simulation time is incremented. This makes the timing list at time  $t_0 + 1$  the current timing list and the loop continues. Simulation is terminated if there are no more input changes.

#### IV. THE FAULT SIMULATOR

The fault simulator utilizes Armstrong's fault-list concept to allow concurrent simulation of all open gate input, output stuck-at-one (SA1), and output stuck-at-zero (SA0) faults in one pass per input vector. The input-open fault is assumed to force a nondominant value on that input. For example, for NAND and AND gates, the input open is assumed to force that gate input to logical 1. A number from 0 to k-1 is associated with each of the k faults in the circuit. Each gate G, except the inverter, is assigned N+2 faults, where N is the number of inputs to gate G. The inverter has only the two output SA1 and SA0 faults, since the input-open fault is indistinguishable from the output SA0 fault. These fault numbers are then carried in fault lists associated with each gate. The hard faults, or corresponding fault numbers, in the fault list on gate G represent exactly those faults in the circuit that will cause the true value (logical 0 or 1) of gate G to be complemented. Only gates having 1 and 0 true values can have fault lists. Similarly, the star faults in the fault list on gate G represent faults in the circuit for which the value of G is not predictable by the simulation model.

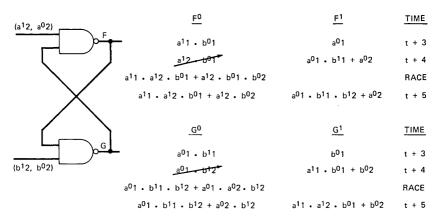

#### 4.1 Fault-simulator gate calculation

The fault-simulator gate calculation (step 5 in Fig. 1) involves the manipulation of the fault lists on each gate using the fault-list algebra.

In the description of the fault-list algebra, each fault list is treated as a set. The three set operations used for fault-list calculation are union  $(\bigcup)$ , intersection  $(\bigcap)$ , and difference  $(\Theta)$ .

The union of two fault lists A and B is defined for some fault f to form the output-fault list F:

#### Union Operation $A \cup B$

where

\*f = star fault corresponding to fault f,

$\lambda$  = absence of f and \*f from the set (fault list).

The *intersection* of two fault lists, A and B, is defined for some fault f to form the output-fault list F:

## Intersection Operation $A \cap B$

The difference of two fault lists A and B is defined for some fault f to form the output-fault list F:

## Difference Operation $A \Theta B$

|   | B  |    |   |    |

|---|----|----|---|----|

|   | F  | λ  | f | *f |

| A | λ  | λ  | λ | λ  |

|   | f  | f  | λ | *f |

|   | *f | *f | λ | *f |

Fig. 4—Fault-list calculation.

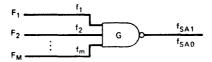

For an m input NAND gate G in Fig. 4, let:

$F_i$  = Fault list on the gate driving the *i*th input of G  $(1 \le i \le m)$ .

$f_i$  = Input open on the *i*th input of G.

$f_{SAk} = \text{Output of } G \text{ stuck at } k \ (k = 1, 0).$

F =Resulting fault list on gate G.

means form the union over all the fault lists on input leads whose true value is logical k, k = 0, 1.

means form the intersection over all the fault lists on input leads whose true value is logical j, j = 0, 1.

To calculate the new output fault list F from the input lists  $F_i$ ,  $1 \le i \le m$ , consider the following cases. First, assume all m inputs are logical 1. The output true value is 0 and

$$F = \{ \bigcup_{i=1}^{n} (F_i \ominus \{f_i\}) \} \ominus \{f_{SA0}\} \bigcup \{f_{SA1}\}.$$

(1)

This equation means that the output SA1 fault plus any fault on any input, except the respective input-open faults and the output SA0 fault, can cause the correct gate output to change values.

Second, assume that all inputs are logical 0. Then the output value is 1 and

$$F = \{ \bigcap_{i=1}^{0} (F_i \bigcup \{f_i\}) \} \bigcup \{f_{SA0}\} \Theta \{f_{SA1}\}.$$

(2)

This equation means that the output fault list contains the SAO fault plus any fault present on every input lead. A fault is present on an input lead if it occurs in the lead's fault list or is the lead's input open fault. The output fault list does not contain the SA1 fault.

Third, assume that some inputs are logical 0 (those denoted by i) and the remaining inputs are 1 (those denoted by j). The output value is 1 and

$$F = \{ [\bigcap^{0} (F_i \bigcup \{f_i\})] \ominus [\bigcup^{1} (F_j \ominus \{f_j\})] \} \bigcup \{f_{SA0}\} \ominus \{f_{SA1}\}. \quad (3)$$

The meaning of the equation follows directly from the meaning of eqs. (1) and (2).

Fourth, if there is a value 2 or 3 on any input and a logical 0 on some other input, then the output true value is 1 and  $F = \{f_{SA0}\}$  only.

The fault-list computation equations can be derived by considering two input gates. Consider a two-input gate G with inputs A and B. If A = B = 1, then eq. (1) can be shown to be true by exhaustive analysis. Similarly, if A = B = 0, then eq. (2) is obviously true. Again if A = 1 and B = 0, then eq. (3) is true. The Nand is simply and followed by a not gate and the and operation is associative and commutative. Then eqs. (1) and (2) represent simple cascades of pairs of two input gate operations. Similarly, eq. (3) means treat all the logical 0 inputs as one and gate  $G_0$ , then all the logical 1 inputs as an and gate  $G_1$ , and then form the difference of  $G_0$  and  $G_1$ . In this explanation, the internal faults were ignored. However, their handling is apparent from eqs. (1) through (3). Equations (1) through (3) describe how the LAMP fault simulator is implemented.

An alternate and more detailed implementation can be achieved by associating two fault lists with each gate whose true value is 3. The fault lists contain those faults that will cause the faulty gate output to be logical k for k=0, 1. This allows more detailed analysis of faulty circuit behavior during initialization. However, this approach will significantly increase the storage required for the fault lists and the CPU time required to perform the simulation. For that reason, eqs. (1) through (3) were chosen as a realistic compromise between detail and cost.

## 4.2 Fault-simulator race analysis

Race analysis under fault conditions (Step 3 in Fig. 1) is performed on the basic NAND and NOR flip-flop (Fig. 2). An analogous situation to the true-value race can occur because of faults; that is, because of one or more of the faults in the fault list on gate C or D (Fig. 2). Each hard fault f in a fault list on gate G means that if f physically exists in the circuit, then the true value of G will be complemented. Therefore, the behavior of faults is identical to the behavior of true values in the faulty circuit. Then with some modification, the algorithm for detecting true-value races can also be used to detect fault-induced races. A fault f on the output gate(s) of a flip-flop (FF) is a race fault (star fault) if it satisfies all of the following conditions:

- (1) Fault f will cause both outputs (D and C) of FF to be 0.

- (2) Both gates of FF are scheduled to change at the present increment of simulation time.

# (3) Fault f is not:

- (a) The input open on D from C or the input open on C from D.

- (b) The output of C SA1 or SA0.

- (c) The output of D SA1 or SA0.

The first two conditions are the same as the conditions for a true-value race. The third restriction is apparent since, if either of the cross-coupled inputs were open, the gates would not form a flip-flop and could not race. Similarly, either output SA1 or SA0 would make a race impossible since there is no uncertainty about the outcome. As with the true-value race, faults which force C=0 and D=3 or C=3 and D=0 will cause oscillations and are declared as race faults.

Let  $F_C$  and  $F_D$  be the set of faults (or the fault list) on C and D, respectively. Let  $F_I$  represent the set of faults that cannot cause a race on FF [those faults listed in condition (3) above]. Consider three cases:

Case 1: C = 1 and D = 1; then the race faults  $F_R$  are given by:  $F_R = (F_C \cap F_D) \ominus F_I$ .

Case 2: C = 1 and D = 0; then the race faults  $F_R$  are given by:  $F_R = (F_C \Theta F_D) \Theta F_I$ .

Case 3: C=0 and D=1; then the race faults  $F_R$  are given by:  $F_R=(F_D\ominus F_C)\ominus F_I.$

The faults in the set  $F_R$  are the star faults. These star faults are then merged into the fault list on gates C and D. That is,

$$F_{C} \leftarrow (F_{C} \ominus F_{R}) \bigcup {}^{*}F_{R}$$

$$F_{D} \leftarrow (F_{D} \ominus F_{R}) \bigcup {}^{*}F_{R},$$

where  $F_C$  and  $F_D$  are the fault lists on gates C and D, and  $F_R$  is the fault list produced by race analysis. The left arrow  $(\leftarrow)$  means "is replaced by." The new  $F_C$  and  $F_D$  are assigned to gates C and D at the same time the other new output values are assigned to their gates.

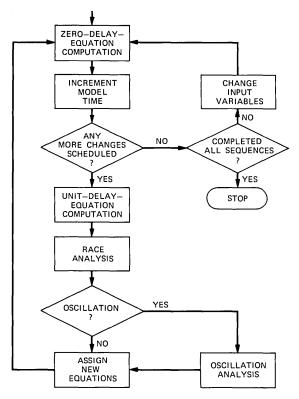

#### 4.3 Fault-simulator oscillation analysis

A fault oscillation (Step 3 in Fig. 1) is declared if the circuit does not stabilize after N increments of simulation time and no true values are changing. The number N may be set by the user as described earlier.

If a fault oscillation is detected, the old and new fault lists for each gate in the set  $\{G_i, i = 1, 2, \dots, m\}$  whose inputs changed during the previous increment of simulation time are compared. Let  $F_{ni}$  = new fault list and  $F_{oi}$  = old fault list for some gate in  $\{G_i\}$ . Then the set of faults that are causing the fault-list changes,  $F_s$ , is determined as

$$F_s = \bigcup_{i=1}^m F_{si}$$

and

$$F_{si} = (F_{ni} \Theta F_{oi}) \bigcup (F_{oi} \Theta F_{ni}).$$

Since single faults are assumed, no fault can cause another fault to be in a fault list. Therefore, the set of faults that alternately appears and disappears in the fault lists must be causing the oscillation. The set of faults causing the oscillation,  $F_s$ , is flagged as star faults (or unioned as star faults) in the new list  $F_{ni}$ . That is,

$$F_{ni} \leftarrow (F_{ni} \Theta F_{si}) \bigcup *F_{si}$$

.

Once a true-value or fault oscillation has been detected, oscillation analysis is performed until the circuit has been stabilized. By adding star faults or adding the value 3, the circuit should eventually stabilize and the oscillation will be resolved.

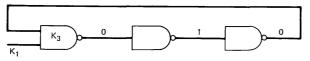

Figure 5 shows a circuit that illustrates both true-value and fault-list oscillations. If K1 = 1, then the circuit will oscillate in true values. However, if K1 = 0, the input-open fault from K1 on gate K3 will cause the circuit to exhibit a fault-list oscillation.

Since the calculations involving the star faults are expensive, a simulator is available (logic simulator) that immediately terminates simulation of any star fault when it occurs. Thus, the logic simulator does not simulate the effect of faults that cause "don't-know" conditions. This approximate simulation yields faster simulation times.

# V. OTHER LAMP SIMULATORS

Sections I through IV of this paper explain the fundamental ideas behind logic-circuit simulation in LAMP. In this section, a brief description of the shorted-fault simulator and the functional simulator

Fig. 5—Oscillating circuit.

is presented. The overall operation of the shorted-fault and functional simulators is similar to the operation of the simulators presented earlier. The fundamental difference lies in the method used to compute the output of the gate or functional element. Therefore, only the basic differences are discussed here.

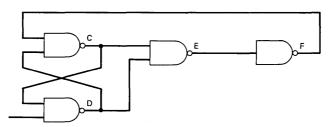

#### 5.1 The shorted-fault simulator

The shorted-fault simulator uses the deductive technique to simulate the effect on a logic circuit of a single electrical short between two gate outputs, where logical 0 is assumed to dominate logical 1. That is, if two gates, A and B, are shorted together and (in the absence of the short) A has the value 1 and B has the value 0, then in the presence of the short, gate A will have its output forced to logical 0. An option is available that causes logical 1 to dominate logical 0; however, since both cases are similar, only the case dominated by logical 0 is described here.

The shorted-fault simulator is a recent addition to the LAMP system. Because run time was expected to be considerably longer than for the fault simulator, the shorted-fault simulator was implemented to detect and immediately terminate simulation of all star faults.

The operation of the shorted-fault gate calculation requires that two fault lists, the constrained and free fault lists, be associated with each gate. The free fault list for gate A, called  $F_A$ , is computed using eqs. (1) through (3). The constrained fault list on gate A, called  $C_A$ , reflects the effects of the signals on any gates that can short to gate A. For the computation of the constrained fault lists, consider two gates, A and B, and a fault, s, whose occurrence causes the output of gate A to be shorted to the output of gate B, as shown in Fig. 6. Consider two cases:

(i) If

$$A = B = 1$$

,

$$C_A \leftarrow C_A \cup \{s \cap (F_A \cup F_B)\} \tag{4}$$

$$C_B \leftarrow C_B \cup \{s \cap (F_A \cup F_B)\}. \tag{5}$$

(ii) If

$$A = 1$$

and  $B = 0$ ,

$$C_A \leftarrow C_A \cup \{s \ominus (F_B \ominus F_A)\} \tag{6}$$

$$C_B \leftarrow C_B \Theta \{ s \Theta (F_B \Theta F_A) \}. \tag{7}$$

The initial constrained fault list on each gate is exactly the free fault list on that gate. The constrained fault list is then altered as described in eqs. (4) through (7). These equations can be verified by examining

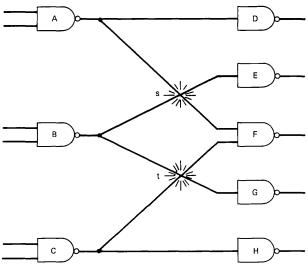

Fig. 6-Two shorted faults.

all eight cases since the only difference between the old and new constrained fault lists is fault s. This procedure must be repeated for every shorted fault that can affect the output of gates A and B (such as fault t in Fig. 6). However, since only one fault is assumed to exist at any time, all the applications of eqs. (4) through (7) are independent.

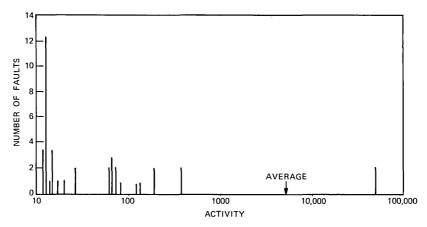

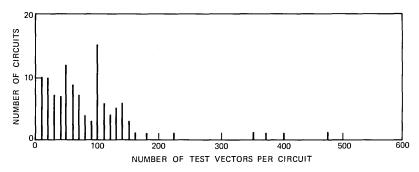

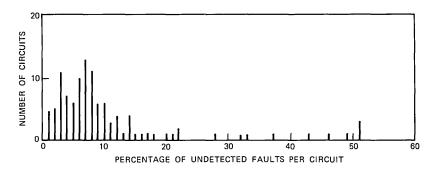

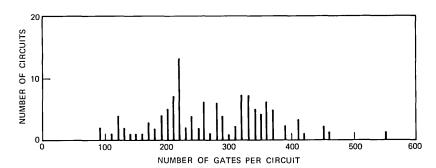

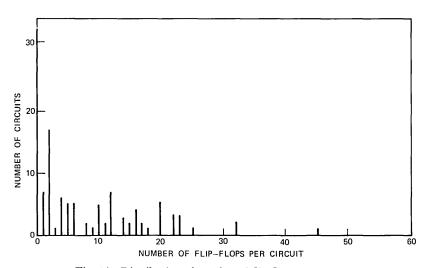

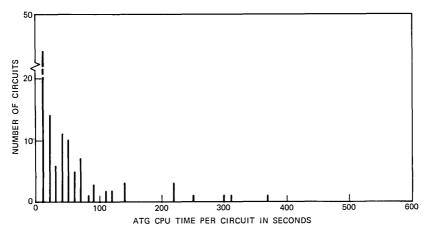

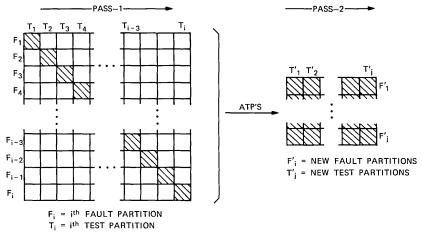

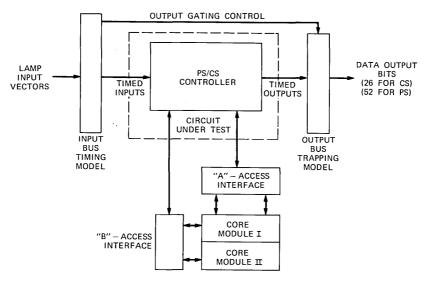

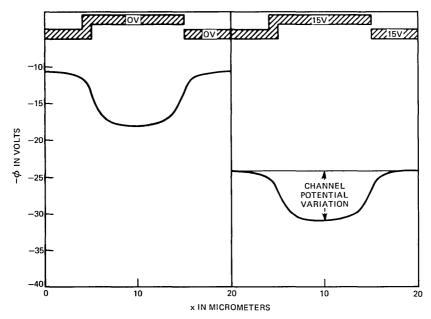

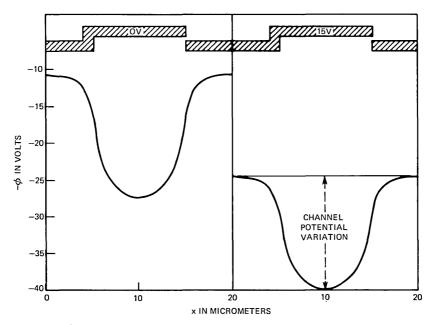

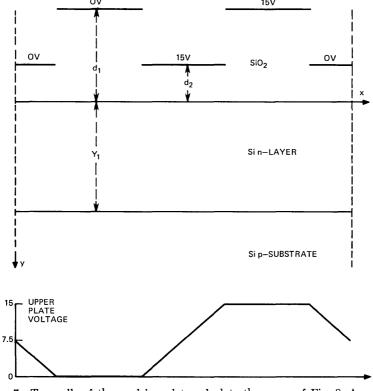

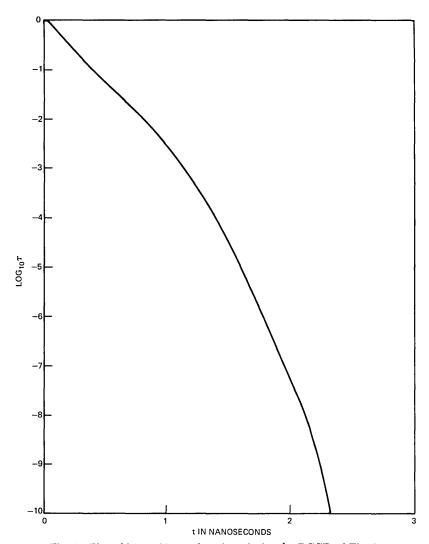

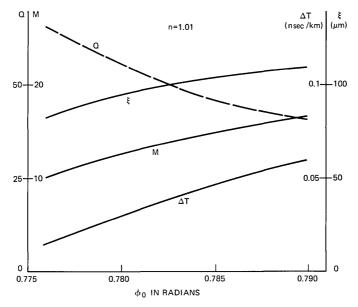

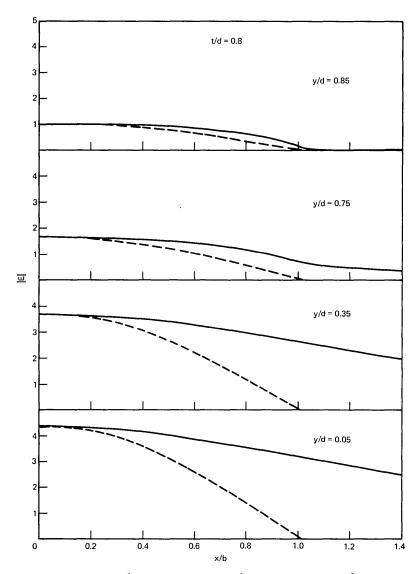

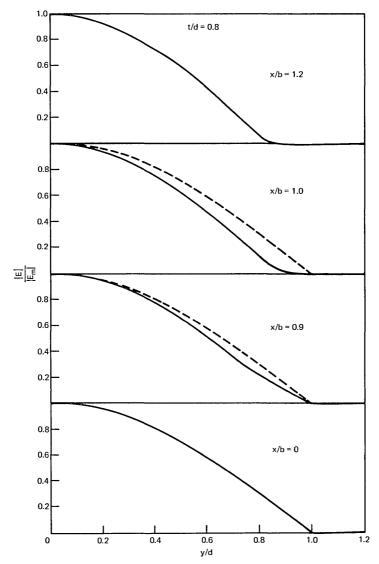

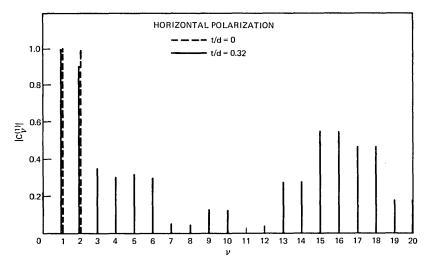

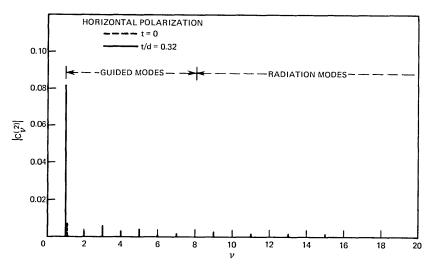

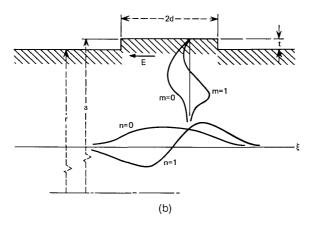

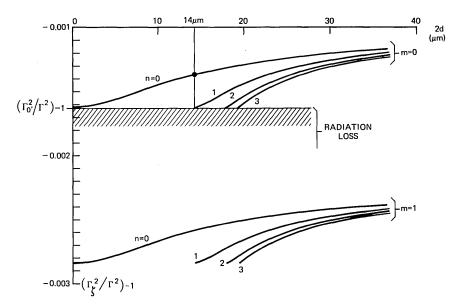

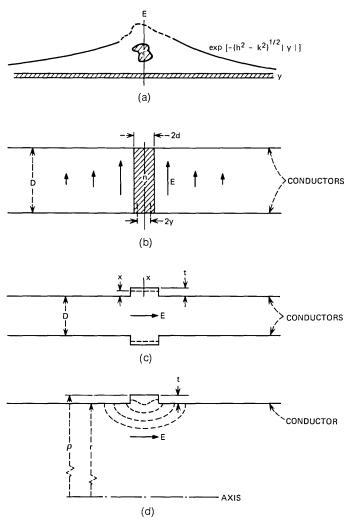

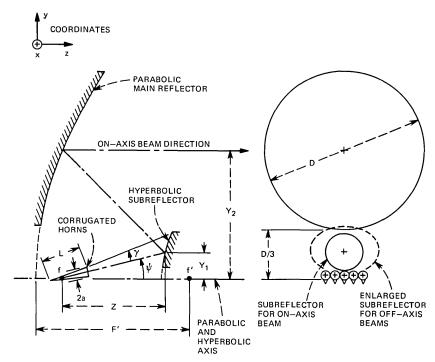

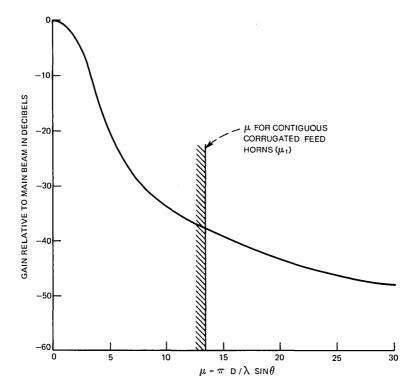

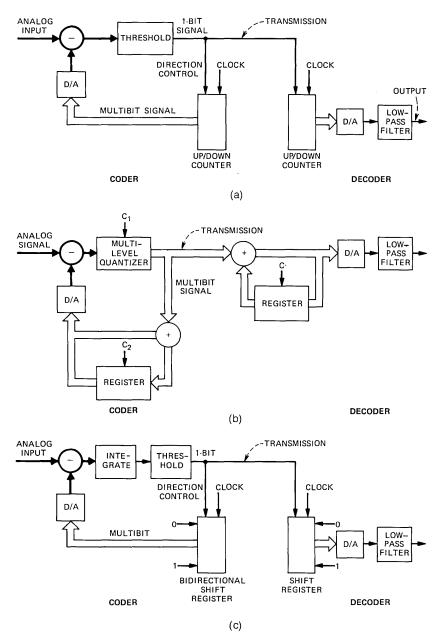

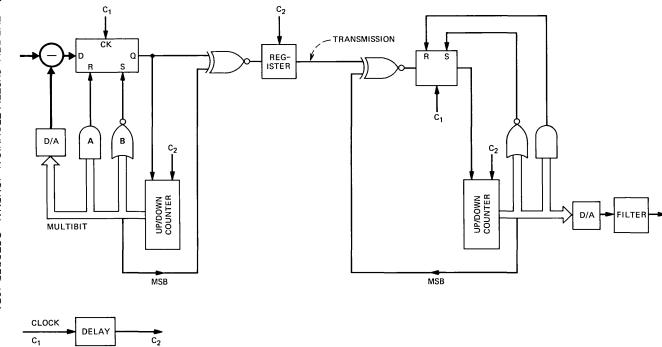

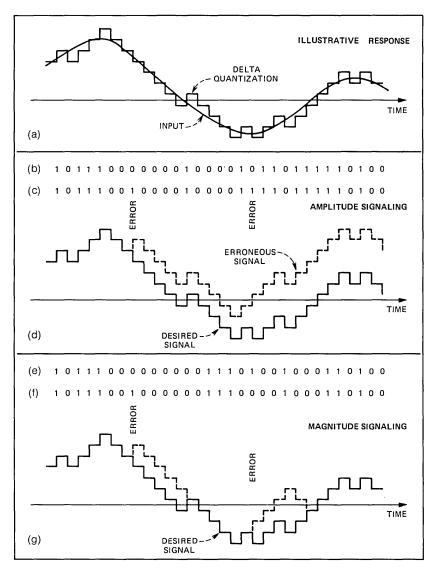

The constrained fault list on gate G is the "true" fault list for the gate since it reflects the effects of potential shorts to gate G. The free fault list on gate G is used as the starting point to compute the constrained fault list. If the free fault list were discarded after use, it would be necessary to go to the inputs of G and recompute the free fault list on G wherever it was necessary to derive a new constrained fault list on G (e.g., when a gate that could be shorted to G changes values).