VOLUME XLIII

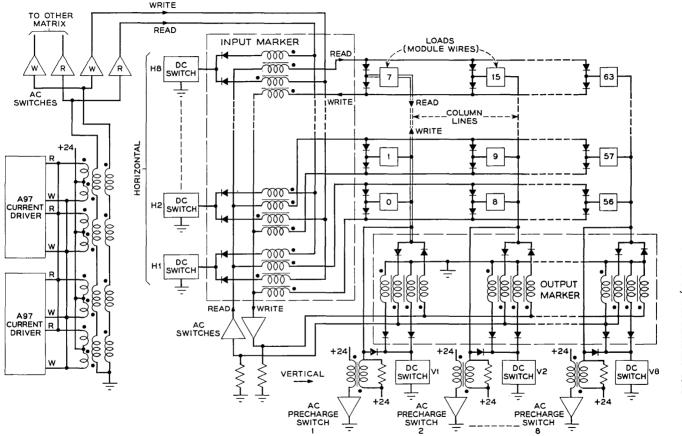

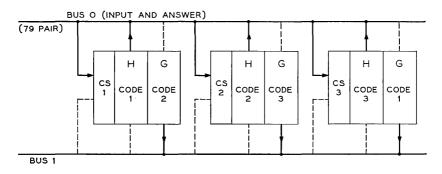

SEPTEMBER 1964 NUMBER 5, PART 1

COPYRIGHT 1964 AMERICAN TELEPHONE AND TELEGRAPH COMPANY

# THE BELL SYSTEM TECHNICAL JOURNAL

# ADVISORY BOARD

P. A. GORMAN, President, Western Electric Company

J. B. FISK, President, Bell Telephone Laboratories

J. E. DINGMAN, Executive Vice President American Telephone and Telegraph Company

# EDITORIAL COMMITTEE

| <b>A</b> . | c. | DICKIESON, Chairman |                 |

|------------|----|---------------------|-----------------|

| F.         | т. | ANDREWS, JR.        | K. E. GOULD     |

| A.         | J. | BUSCH               | W. C. HITTINGER |

| R.         | Р. | CROSS               | J. R. PIERCE    |

| R.         | ь. | DIETZOLD            | D. E. PROCKNOW  |

| R.         | w  | EHRLICH             | E. C. READ      |

#### EDITORIAL STAFF

- G. E. SCHINDLER, JR., Editor

- L. M. COLE, JR., Assistant Editor

- J. T. MYSAK, Production and Illustrations

- T. N. POPE, Circulation Manager

THE BELL SYSTEM TECHNICAL JOURNAL is published six times a year by the American Telephone and Telegraph Company, E. J. McNeely, President, C. E. Wampler, Vice President and Secretary, J. J. Scanlon, Vice President and Treasurer, 195 Broadway, New York, N. Y. 10007. Subscriptions are accepted at \$5.00 per year. Single copies \$1.25 each. Foreign postage is \$1.08 per year or 18 cents per copy. Printed in U.S.A.

# THE BELL SYSTEM TECHNICAL JOURNAL

VOLUME XLIII

September, 1964\*

NUMBER 5, PART 1

Copyright 1964, American Telephone and Telegraph Company

Contents, Part 1

No. 1 ESS: System Organization and Objectives w. KEISTER, R. W. KETCHLEDGE AND H. E. VAUGHAN 1831

Organization of No. 1 ESS Central Processor J. A. HARR, F. F. TAYLOR AND W. ULRICH 1845

Organization of the No. 1 ESS Stored Program J. A. HARR, MRS. E. S. HOOVER AND R. B. SMITH 1923

No. 1 ESS Maintenance Plan R. W. DOWNING, J. S. NOWAK AND L. S. TUOMENOKSA 1961

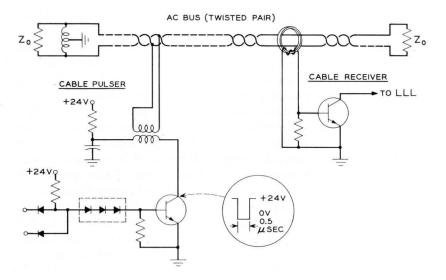

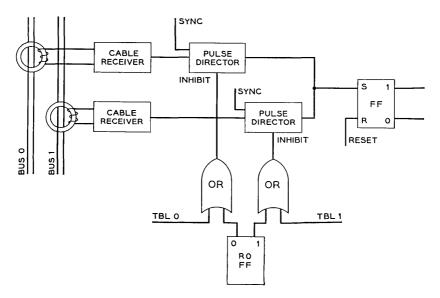

No. 1 ESS Bus System J. B. CONNELL, L. W. HUSSEY AND R. W. KETCHLEDGE 2021

No. 1 ESS Logic Circuits and Their Application to the Design of the Central Control W. B. CAGLE, R. S. MENNE, R. S. SKINNER, R. E. STAEHLER AND M. D. UNDERWOOD 2055

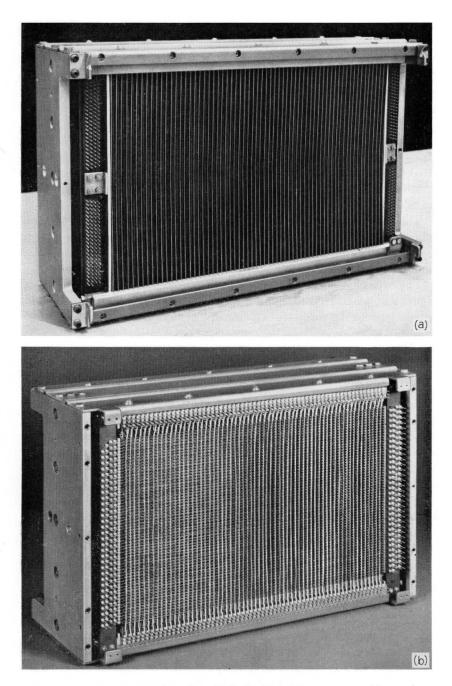

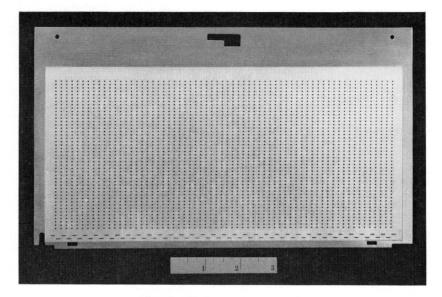

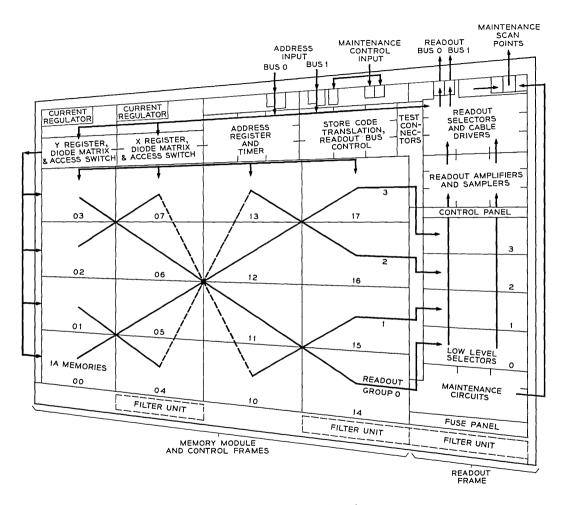

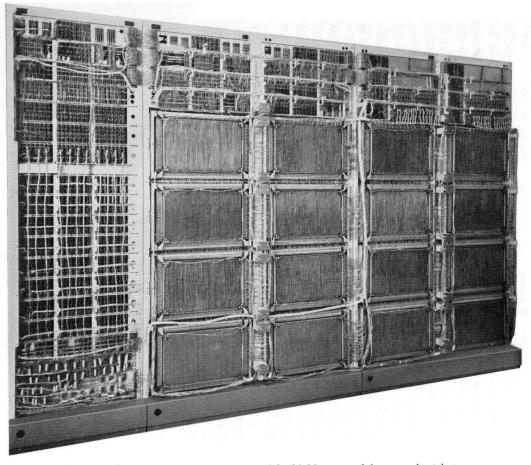

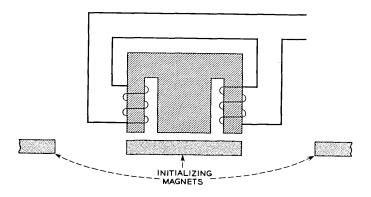

No. 1 ESS Program Store T. S. GREENWOOD AND D. C. KOEHLER 2097

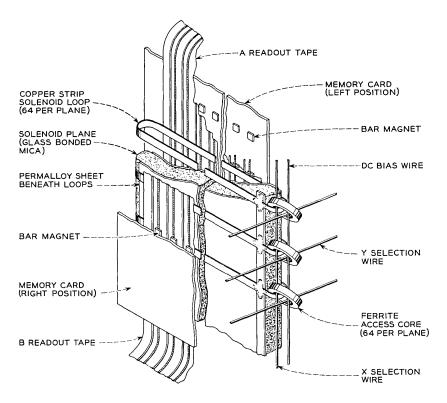

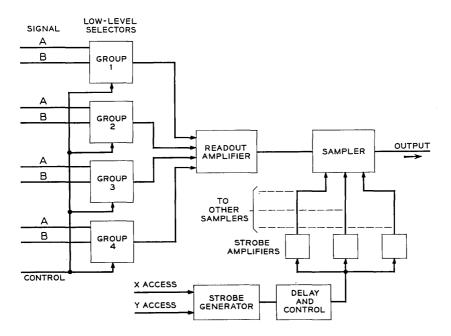

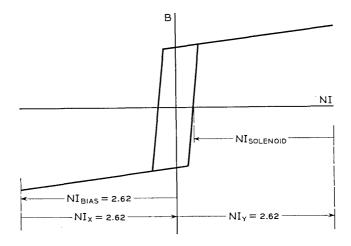

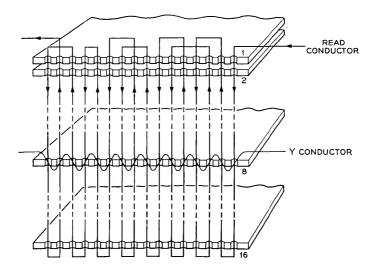

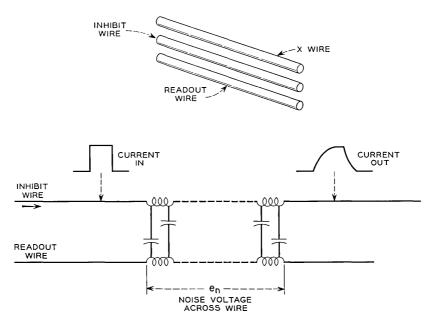

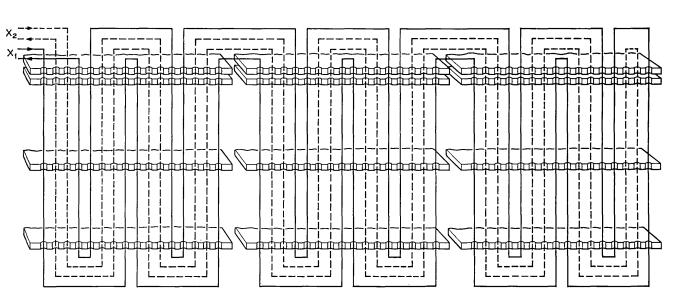

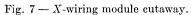

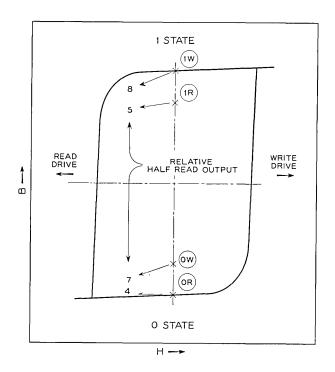

No. 1 ESS Call Store—A 0.2-Megabit Ferrite Sheet Memory R. M. GENKE, P. A. HARDING AND R. E. STAEHLER 2147

\* This issue of the Bell System Technical Journal was not published until after October 15, 1964.

# No. 1 ESS: System Organization and Objectives

# By W. KEISTER, R. W. KETCHLEDGE and H. E. VAUGHAN

(Manuscript received January 22, 1964)

This paper is an introduction to the No. 1 electronic switching system, a new general-purpose switching system developed for use in the Bell System. Organization and objectives of the system are outlined to provide a background for the detailed technical papers which follow.

#### I. INTRODUCTION

# 1.1 General

The continuing expansion of present-day services, the demand for additional types of service, and the anticipation of new service offerings in the future all indicate a need for a new general-purpose switching system for the Bell System. The No. 1 electronic switching system (ESS) has been developed to meet this need. It is a general-purpose telephone switching machine capable of providing either two-wire or four-wire switching for local, toll, or tandem applications. No. 1 ESS provides today's services as well as several new ones, and is sufficiently flexible to provide for the ever-changing need for future services. It is economically competitive for present applications and will provide new services at relatively low cost.

The purpose of this paper is to outline the objectives of the system and to provide a brief description as background for the several more

technical and more detailed papers which follow. Switching systems are, in general, complex and not easy to describe. No. 1 ESS not only entails many new concepts of switching system organization, but the equipment and apparatus used are also different from those of previous switching systems. As a consequence of this, No. 1 ESS is the largest development project ever undertaken by Bell Laboratories for the Bell System. The papers in this issue should give an adequate description of all the major concepts and techniques used in the system. Other papers, particularly those treating programming and testing aspects, will be published in forthcoming issues of this and other journals.

#### 1.2 History

Since 1945, Bell Laboratories has conducted an active program of research and exploratory development in electronic switching. The Morris, Illinois, trial<sup>1</sup> of the world's first electronic switching office demonstrated the value of many of the basic concepts used in No. 1 ESS, in particular the use of a stored program and the basic maintenance philosophy. The system at Morris provided customers regular commercial-grade service and some additional new services. The trial established valuable guides for production design in hardware, data formats and programming. In addition, the trial also provided excellent training for many young engineers who later had a major part in the design of the No. 1 ESS. Although all of the hardware units and data processing programs for No. 1 ESS are new, their design relied heavily on the experience gained at Morris. The development of No. 1 ESS has now relegated the Morris system to history.

#### II. OBJECTIVES

#### 2.1 Economics

Essential objectives for a new switching system are that it be at least the equivalent in service features of existing systems and be economically competitive with these systems for some significant segment of the market. These objectives must be attained on the basis of today's market rather than some hypothetical market of the future. The new system must be introduced in an environment of a very large number of older systems, and the general capability of the over-all switching network will be determined largely by the capability of the majority of the offices. The process of achieving improvements in the over-all system must be one of evolution over a period of years. However, the new system must have greater capability than the older systems in order that this improvement can be realized as the percentage of new offices increases. This points up another important essential. A new office must be compatible with the older offices with which it must operate, since modification of older units in service is inconceivable if we would attain the economic advantages of a new office design.

The economic balance over a range of sizes in the No. 1 ESS plan is quite different from that in electromechanical common control offices such as crossbar. The electronic system is based on a single high-speed central processor which is essentially the same in both large and small offices. In a system like No. 5 crossbar, a multiplicity of control units must be used due to their slower speed. This allows the amount of control equipment — as, for instance, the number of registers and markers in the crossbar system — to be increased as the office grows, so that the full burden of a control capable of handling a large office need not be borne by a small initial installation.

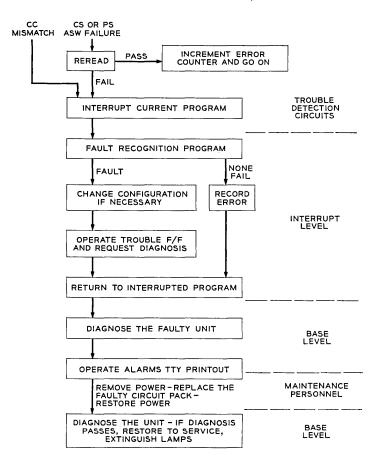

The new system must meet the standards of reliability that have been established by electromechanical systems. The operation of a complete office by a single central processor is a definite problem when reliability is considered. In a multi-marker office of No. 5 crossbar, the failure of a single marker merely reduces the traffic capacity of the office. However, the failure of the controller in an office depending on a single central processor would make the office completely inoperative. The solution followed in No. 1 ESS is to duplicate all units essential to proper operation of the office.

The economic objectives of No. 1 ESS are being realized through a basic design which has been optimized in its details and will be economical in production and in operation over a period of years. The economics of the equipment design have been based on quantity manufacture of its component parts. By the use of the stored program, it has been possible to plan a system which requires no wired options during manufacture and therefore leads to efficiency in production. The system units are designed for a minimum of interconnections between frames, so that most of the wiring and much of the detailed testing can be done at the factory rather than on location during the process of installation. Trouble detection and fault location have been highly automated through the use of stored program. Since most of the system logic involving telephone service features has been placed in the stored program, the introduction of new service features and modifications of existing features will be greatly simplified. In many cases, modifications will be made by changing programs rather than by wiring changes.

1833

It is believed that important savings will be realized in the current development effort required to maintain the system design over a period of years during which its service features and operational environment change.

# 2.2 Size

An important item in planning the system was to determine the range of sizes over which the system would be applicable. Two major parts of the system are greatly influenced by size. One is the network, which must be planned to serve the entire range, with systematic growth from the smallest to the largest size encompassed by the design. The other is the central processor, whose call handling capability must be sufficient to care for the largest office while also being economical when used at only a fraction of its total capacity in smaller offices.

The appropriate size range was determined by making a survey of the range of office sizes. Information for this survey was obtained from the operating telephone companies, who provided information on the number of wire centers and the size of each wire center in each company. This information, covering a total of over thirty million lines in the Bell System, was analyzed by a digital computer to provide statistical information on the makeup of the potential market. The general nature of the results is indicated in Tables I and II. From these it is apparent that there are a very large number of very small wire centers, but that there is a large volume of business in large wire centers. Fifty per cent of the total lines are served from wire centers of 19,000 lines or greater. It was decided that it was not necessary to design an office large enough to accommodate the largest wire centers, because the differential cost per line becomes negligibly small in the higher office sizes. For example, the cost of two 50,000-line units will not be significantly more than the cost of a single 100,000-line unit. For this reason, a decision was made and verified by a number of studies that an upper size limit of 65,000 lines would be reasonable. The lower size limit is determined purely by

TABLE I — TOTAL BELL SYSTEM LINES IN SERVICE VS CENTRAL OFFICE SIZE\*

| Per Cent of Total No. of Lines | Office Size |  |

|--------------------------------|-------------|--|

| 75                             | over 7,500  |  |

| 50                             | over 19,000 |  |

| 25                             | over 32,000 |  |

\* Data as of January 1, 1960 (includes community dial offices).

| Per Cent of Total No. CO Buildings | Lines Served                    |  |

|------------------------------------|---------------------------------|--|

| 25                                 | less than 230                   |  |

| 50<br>75                           | less than 750<br>less than 3000 |  |

TABLE II — CENTRAL OFFICE BUILDING TOTALS VS NUMBER OF LINES SERVED\*

\* Data as of January 1, 1960 (includes community dial offices).

economics, but should extend down to at least the 4,000- to 5,000-line size, since the survey showed that a large number of offices are initially installed in this size range.

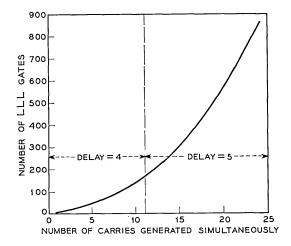

From a traffic standpoint, the maximum size of the system is set by the capacity of the central processor for handling calls in real time. The maximum capacity of the No. 1 ESS has been set at 100,000 calls in the busy hour. This figure was determined through studies of the cost and complexity of central processors of various designs, weighed against the traffic needs in the wire centers in the Bell System. The capacity of the central processor is determined by the basic speeds of the electronic circuits, its basic clock cycle time, the complexity of its individual logic operations and the amount of processing done in parallel.

#### 2.3 Flexibility

The system has been planned to make maximum use of the flexibility inherent in a stored program. Central control is designed so that its wired logic represents basic logic operations which are related to telephone switching functions only through the sequences of instructions in the program. By means of the stored program, most of the logic decisions in call processing have been converted to basic logic operations. This philosophy is extended to items such as trunk circuits. The physical equipment in a trunk circuit is in most cases limited to that necessary for detecting and generating the signals required on these trunk circuits and performing basic switching operations, including timing of the duration of signals, is performed by central control under instructions from the program. This has the effect of minimizing the variety of trunk circuits required and reducing their cost, since changes in timing or sequence of operation can be made through changes in the program.

The switching network has been designed for flexibility in a variety of situations. The basic pattern consists of line frames and trunk frames connected together by groups of junctors of three types. Junctors are provided between line frames and trunk frames for connections between lines and trunks. Junctors from line frames back to line frames are used for line-to-line connections, and likewise junctors between trunk frames are used for tandem traffic and other trunk-to-trunk connections. The number of line frames and trunk frames can be varied independently and the junctor group sizes adjusted according to the mix of interand intra-office and tandem traffic. The network has been designed so that frames of four-wire ferreed switches can be used without modification of the central processor complex or its basic network control programs. In this way, the single basic system design can be adapted to a variety of local, toll, and tandem applications which in the past have required quite different system designs.

#### III. SYSTEM ORGANIZATION

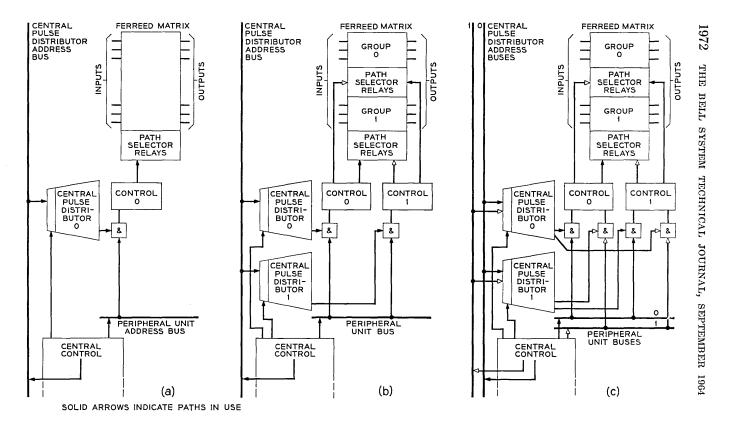

#### 3.1 Outline of System Plan

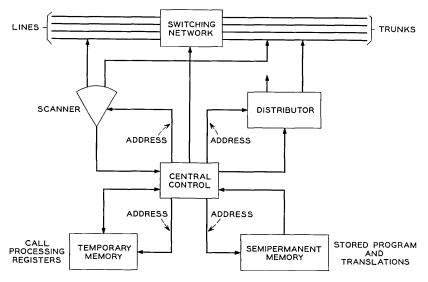

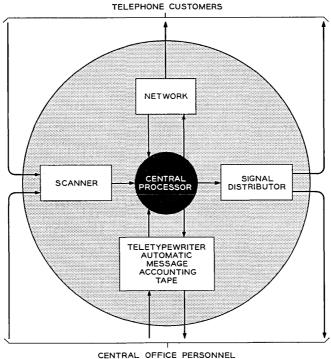

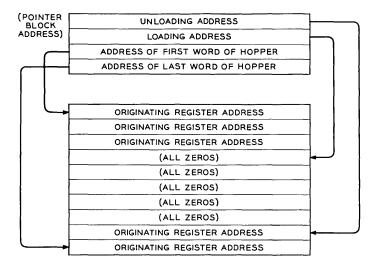

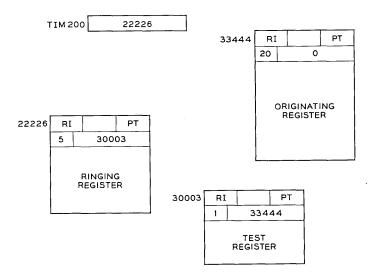

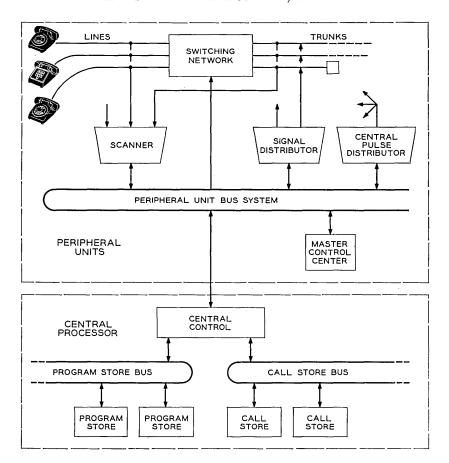

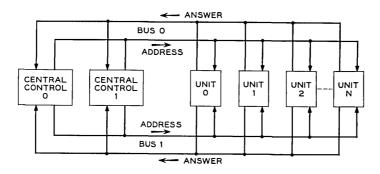

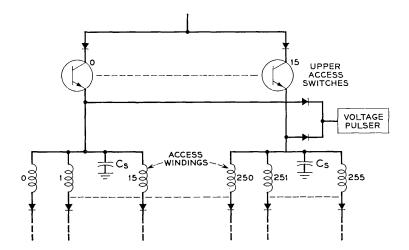

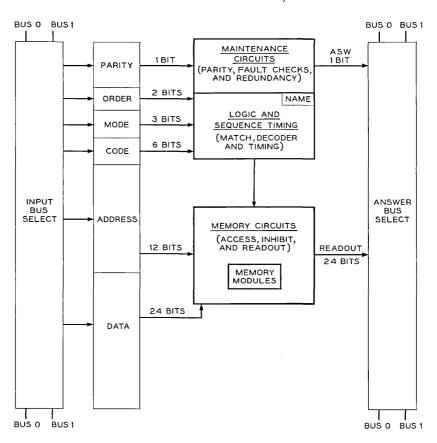

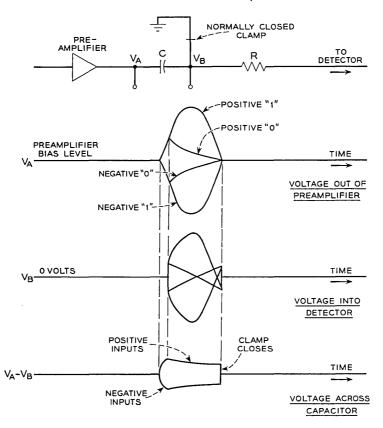

The basic concept of the No. 1 ESS is that of a high-speed electronic central processor operating with a stored program to control the actions of the central office on a time-sharing basis. The general system organization is illustrated in the block diagram (Fig. 1). The switching network provides the means for making interconnections between the lines and trunks to be served by the system and also provides access to the various service circuits required in handling telephone calls. These include tone sources, signaling detectors, ringing sources and the like. All information processing is handled by a central processor consisting of central control and the temporary and semipermanent memories. The temporary memory is used for storage of the transient information required in processing calls, such as the digits dialed by the subscriber or the busy and idle states of lines and trunks. The semipermanent memory contains the stored program and translation information. The contents of this memory need not change during the processing of a call. When the semipermanent information must be changed for any reason, these changes can be made on a manual basis without interfering with the operation of the office. The semipermanent memory also has the advantageous characteristic that its stored information is not erased by circuit malfunctions.

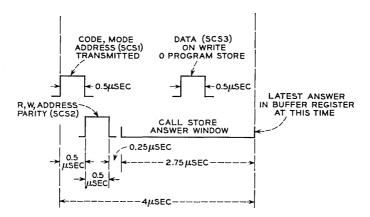

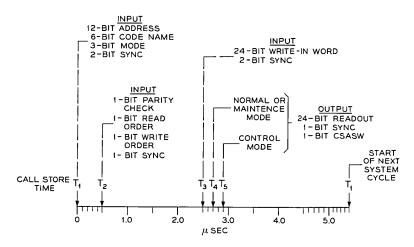

The central control consists of wired logic for performing information processing operations. It is organized on a word basis, with a word length of 24 bits, and operates on a basic cycle time of 5.5 microseconds. It is important to realize that the logic wired in central control is designed for information processing. The telephone switching logic is contained

Fig. 1 — Central information processor with stored program (No. 1 ESS).

in the stored program. Thus, the hardware of the control complex is largely independent of the type of telephone service to be provided and the service treatments to be offered to the subscribers. This leads to great flexibility, since the same equipment can be used with different programs to provide a variety of services.

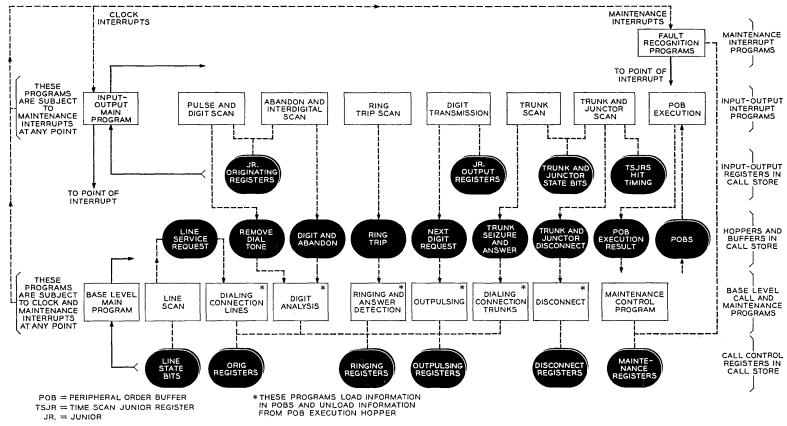

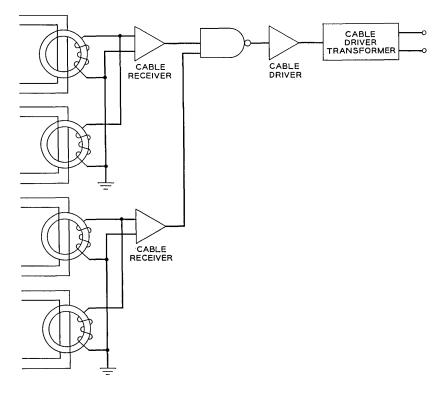

Input information for the central processor is provided by scanners connected to various points in the system where information must be obtained. These include the lines and trunks and signal receivers. The scanners are directed periodically to the lines to detect service requests, to the trunks to detect incoming calls, and to the signal receivers for detecting dialed digits and other control information. The process of recognizing this information involves periodic scanning and recording the results of these scans in temporary memory.

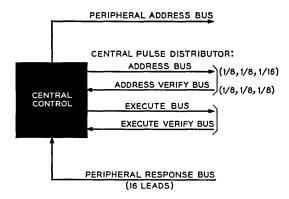

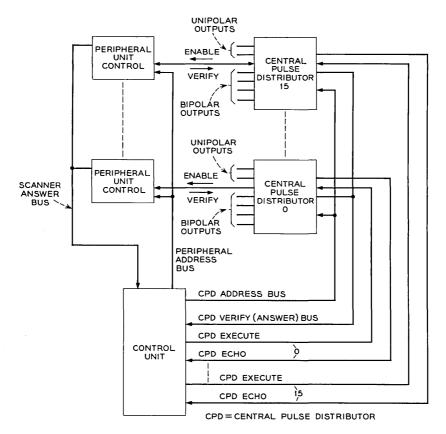

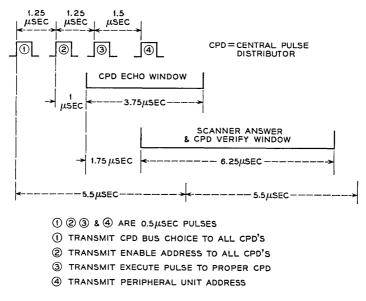

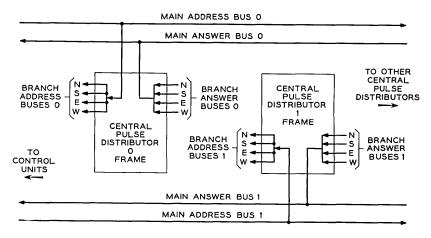

The signal distributor is the inverse of the scanner. It is connected to the various points in the system where actions must be controlled by the central processor. Central control can address the distributor to a particular terminal where a flip-flop or other memory device can be set to start an action. At a later time, central control can address the distributor to terminate this action. In the present design, the system handles this distributor action through two types of units. One is the central pulse distributor, which is all-electronic and is used for high-speed actions. The other, the signal distributor, makes use of a relay tree to perform lower-speed actions such as the control of trunk relays,

Thus the facilities provided in the system can be divided into several categories, such as the switching network with its associated terminal circuits which perform the physical functions required in making connections and detecting and producing signals; the central processor, with its wired logic to perform basic information-processing functions; the scanner and distributor, providing input and output communication for the central processor; and the stored program, which contains instructions for performing all the switching tasks in ordered lists of instruction words.

Particular distinction needs to be made between the program and translation information contained in the semipermanent memory. The program is the lists of instructions for performing all of the service features. It is part of the basic design of the machine and is not influenced by the characteristics of the particular installation. Ordinarily, it will not be changed except for some significant change in features or the sequence in which actions are to be performed, which would correspond to redesign and wiring changes in electromechanical offices. The translation section, on the other hand, contains the specific layout of facilities in the particular office: the association of subscriber directory numbers with the equipment location of their lines, the classes of service to be provided — such as individual and two-party, coin, extended area dialing and so on — and also the specification of trunk routes and their location and alternate routes to be used when available. This information must be changed periodically with the inward and outward movement of subscribers, changes in their class of service, and readjustment of trunk routes. Means are provided for making these changes on a periodic routine basis.

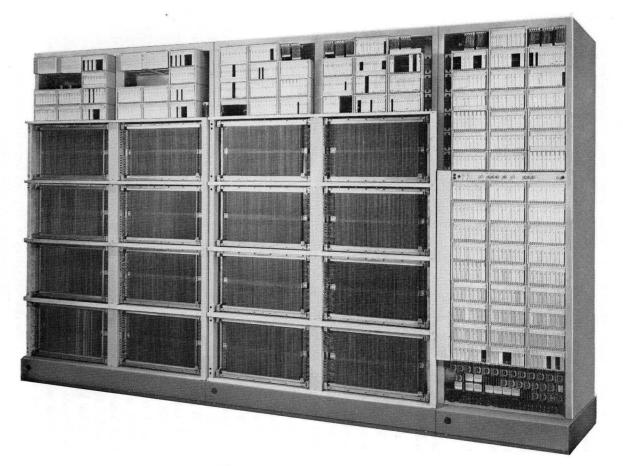

#### 3.2 Hardware

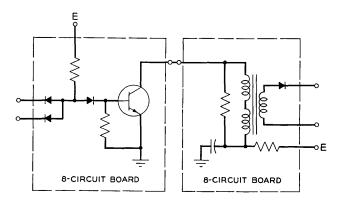

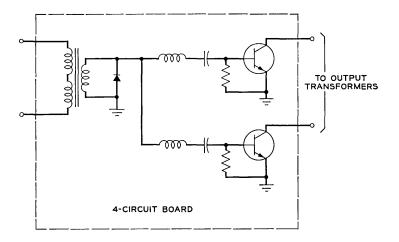

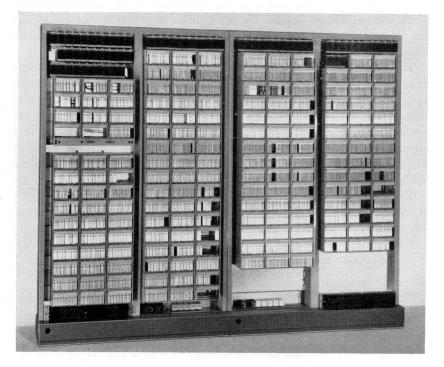

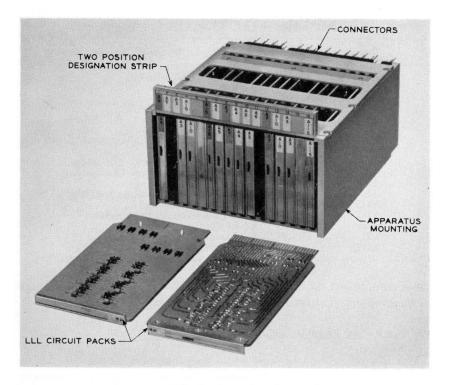

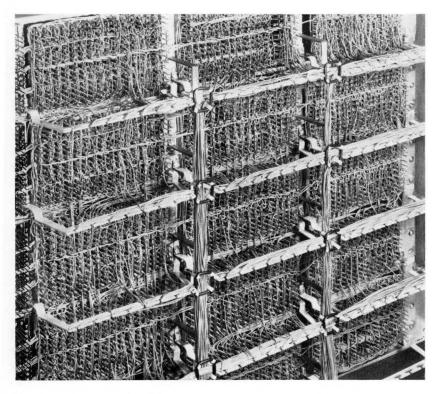

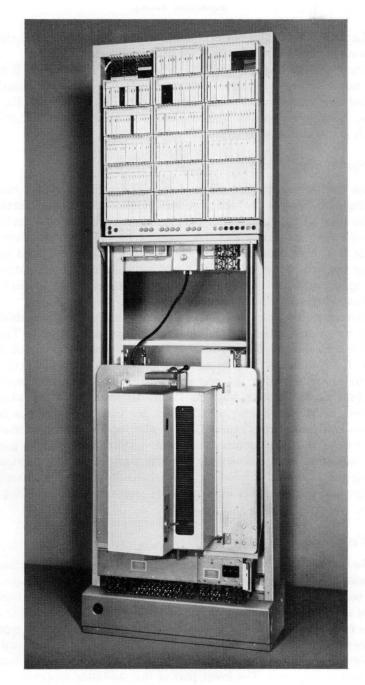

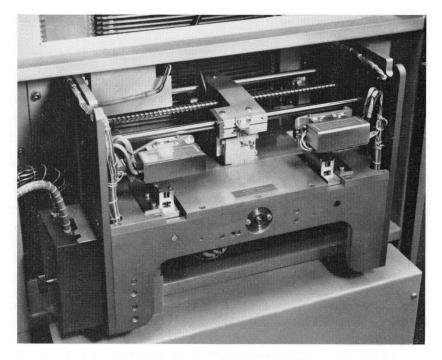

The equipment and apparatus of No. 1 ESS has been designed for large-volume manufacture at minimum cost. Note that even a volume of only one million lines a year means over 15 million ferreed crosspoints,  $1\frac{1}{2}$  million electronic circuit packages, 5 million transistors, 15 million diodes, etc. Obviously, such production rates must be highly mechanized.

Equipment and apparatus must be of special design to be adaptable to low-cost mechanized manufacture. Further, the high manufacturing volume justifies greater development effort and the creation of special devices and components. Thus No. 1 ESS uses many apparatus items that were developed for this particular application and whose design was tailored for mass manufacture. The ferreed switch is a good example. It is designed to be made as an array, not as an assembly of individual crosspoints. The control coils are not wound individually and then connected in series. Rather they are wound in simultaneous rows and columns from continuous lengths of wire.

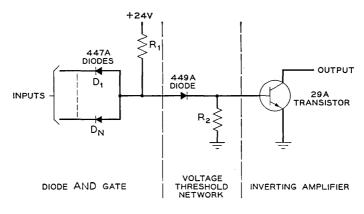

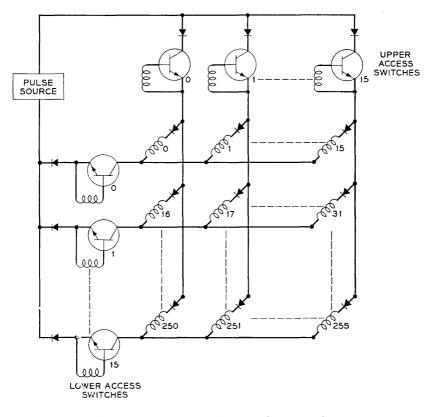

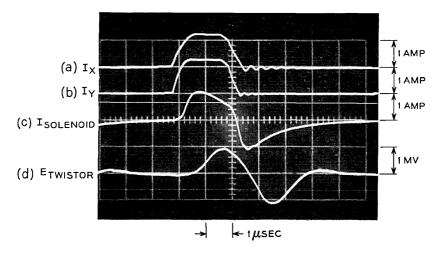

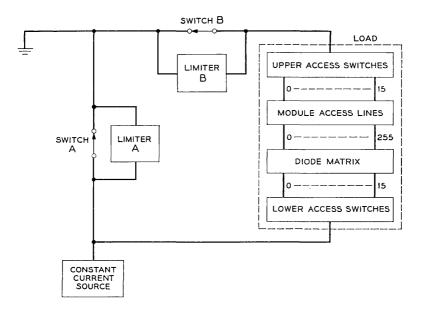

Choice of technology is based on function and cost. In No. 1 ESS, relays are used in substantial quantities. The relay has cost advantages over an electronic approach where speed and function permit. For example, control of ferreed switches involves routing a high-current pulse through a selected path in the matrix of windings. This can be done by means of diodes and PNPN triodes, and indeed such a control structure was developed initially. However, by appropriate design of the control circuits one can, in effect, substitute a relay contact for a high-current diode. The cost advantage of the relay approach is substantial.

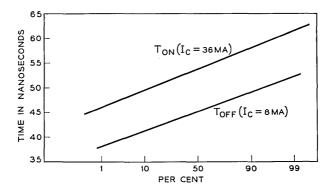

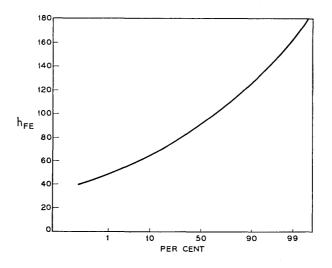

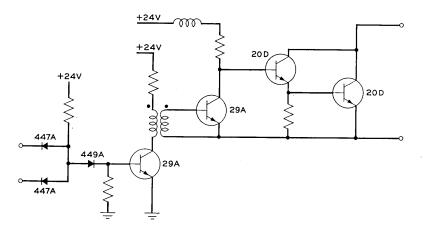

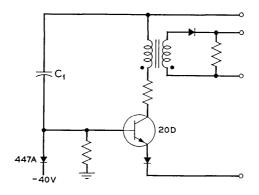

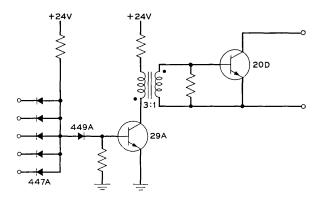

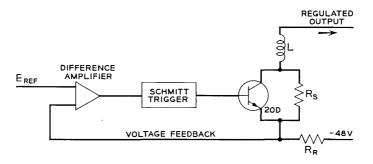

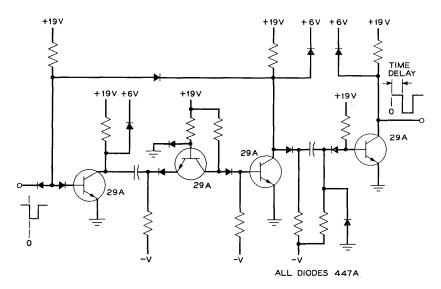

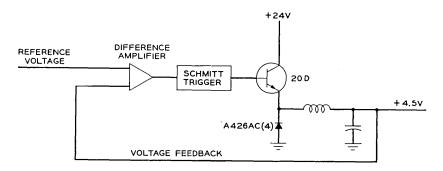

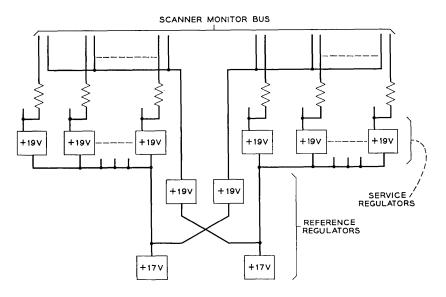

Standardization and minimization of codes are other important steps to low-cost volume manufacture. In No. 1 ESS strong efforts were made to standardize the hardware and to achieve the necessary variability by program or translation methods. An example of equipment standardization is the network equipment. Only six codes of frames permit assembly of a switching network suitable for any local office. Two additional codes take care of four-wire networks for toll offices. An example of device standardization is the use of only two codes of transistors, the low-power 29A and the relatively higher-power 20D. The 29A is used in the many logic circuits, in audio amplifiers and oscillators, and in broadband feedback amplifiers and regulators. Another effect of standardization has been the virtual elimination of wired options. Most electromechanical switching equipment makes liberal use of wired options to meet the variations of size and features of different installations. Thus the equipment is specially wired and tested at the factory. In No. 1 ESS the corresponding variations are stored in memory. The factory makes a particular frame the same way every time to a fixed set of test requirements.

The choice of seven-foot-high equipment arrangements (instead of 11.5-foot) eliminates the need for special buildings and allows maintenance from the floor, without ladders. This also contributes to the objective of simplified installation and growth. As a part of the general objective of dependability, and to permit reuse of existing buildings, air conditioning is not required. While most offices will doubtless be air conditioned, it will not be required for machine operability.

No. 1 ESS uses unregulated storage battery power fed by silicon-controlled rectifiers. The equipment has therefore been designed to operate over a  $\pm 10$  per cent voltage range. This design eliminates the need for end cells, counter cells and their associated switches.

Transmission has received particular attention. All outgoing trunks include loop compensation networks to improve return loss characteristics. Tones are generated by precision transistor oscillators and are fed to lines and trunks out of precisely balanced terminations. These and other similar measures, including careful control of noise, were taken in recognition of the role of the switching center in the maintenance and improvement of transmission objectives.

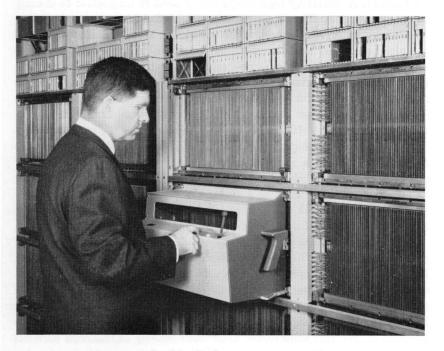

#### 3.3 Programs

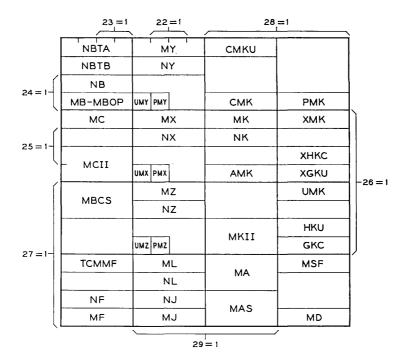

Approximately 90 programs totaling about 100,000 words are used to control the operations required for telephone service and to control the maintenance of the system. These programs, each an ordered set of instructions to provide a particular function, are stored in the program store. The call programs provide the solution to any problem a customer can present to the system, either directly or through some other switching system. An assembly of call programs must tailor-make a connection according to the demands of the customer.

Several approaches toward providing programs for a large number of different offices could be used. A generic program, which is the same for each office, with detailed differences listed in a parameter table, is the approach used in No. 1 ESS. The generic program includes all features for a large number of offices, covering sizes from 2,000 to 65,000 lines and means for handling growth and changing traffic conditions. This approach simplifies record keeping, because only the parameter tables which specify present size and operating conditions are unique to each office. Additional data which characterize a particular office are found in translation tables also in the program store. Typically, 18 different sets of translations are required in each office. These include directory number to equipment number translations for both lines and trunks, class of service, and special treatment for lines and trunks.

In the future, economics may dictate the need for several generic programs—for instance, one for small offices, one for large offices, one for four-wire offices, and perhaps some combinations of these.

The development and preparation of programs for the system require the use of several utility programs written for a commercial computer, an IBM 7094 in this case. These programs are used to convert the language of the programmer to the language of the machine, to assemble and compile the individual pieces of call and maintenance programs, and to load information onto a tape which finally controls the writing of the magnets on the twistor cards. Additional programs are used to assemble, compile, and load parameters and translations. Utility programs will be used by the Western Electric Co. as tools for manufacturing the programs put into commercial installations.

#### IV. DEPENDABILITY

#### 4.1 Objectives

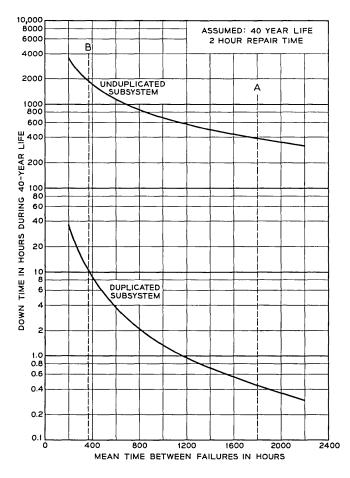

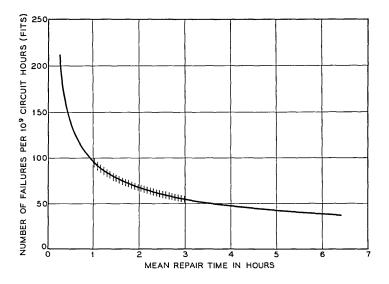

The dependability requirement on a telephone office is limited only by what the state of the technology can provide. Certainly a new system must at least be comparable to existing offices. This means outages of no more than a few minutes in 40 years. Heretofore no large electronic machines have been able to approach this kind of dependability. In fact, the dependability objective represented one of the major challenges of the No. 1 ESS development. Since No. 1 ESS is a large digital information processor, it is a cousin to the general-purpose digital computer. However, the dependability requirement requires that No. 1 ESS be a very different kind of system with a much higher level of redundancy.

#### 4.2 The Large Immortal Machine

The large size of No. 1 ESS and the unique dependability requirement lead to the term "large immortal machine." It also implies that No. 1 ESS is a new kind of information processor, a kind that has never been developed before.

Another way of contrasting No. 1 ESS with a computer is to compare the relative hazards of a machine data processing error and a total machine failure. In a general-purpose computation center a machine stoppage is a nuisance: the problem must be rerun. But a data processing error could be called a "disaster" because the results come out wrong. In a telephone office it is the other way around. A data processing error may cause a particular call to be mishandled. This is a nuisance, particularly to the customer whose call must be redialed. A total machine failure in a telephone office, however, means no telephone service during the outage, and the magnitude of such a disaster need not be argued. The key point is, of course, that the dependability requirement on No. 1 ESS is both remarkably severe and quite different from that of generalpurpose computers.

#### 4.3 Duplication

Since some failures of individual components are bound to occur over decades of system service, duplication is essential. Every system unit required to maintain service must be provided in duplicate. Not only

must there be duplication, but troubles must be found and corrected quickly to minimize exposure to system failure due to multiple troubles. This implies that all units must be continually monitored so that trouble in the standby can be found just as quickly as in the unit giving service. This further implies automatic detection of troubles and automatic switching of service when units fail. These processes are covered in detail in other papers.

# 4.4 Repair

When a trouble occurs, the telephone actions are interrupted as briefly as possible to reestablish an operational machine. Then, on a less urgent basis, the defective unit is diagnosed by the system itself and the results printed on the maintenance teletypewriter.

Where offices are unattended during at least part of the day, alarms and a remote teletypewriter are provided at some other location where 24-hour attendance is available. For minor troubles, not affecting service, the repair can be deferred. A defective trunk circuit can be taken out of service with a teletypewriter message. Major troubles may, on the other hand, need prompt attention to insure service continuity.

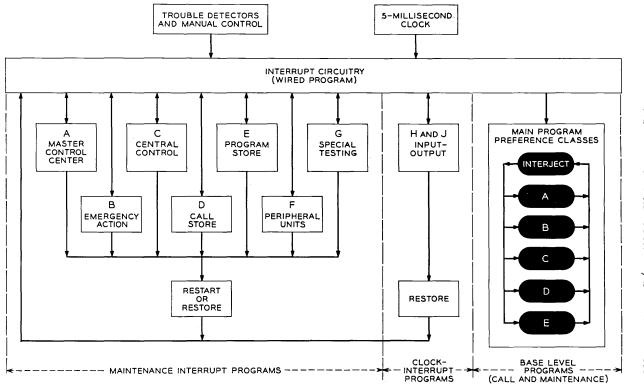

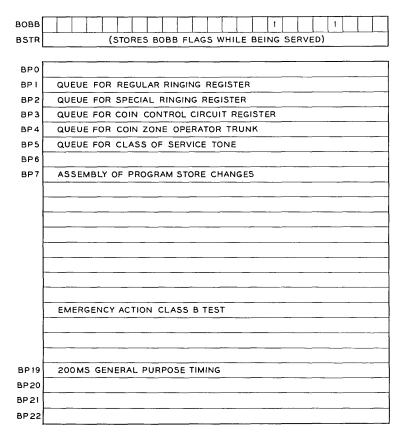

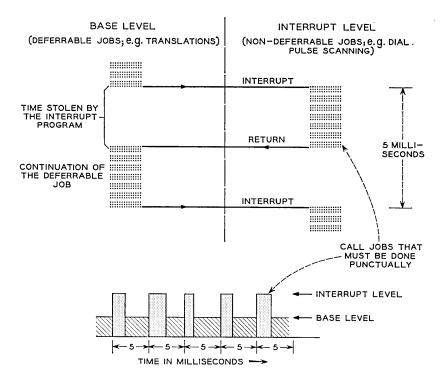

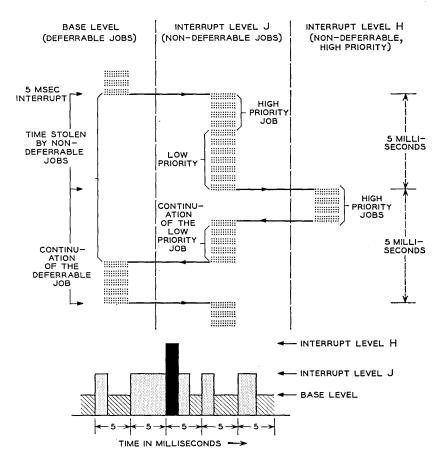

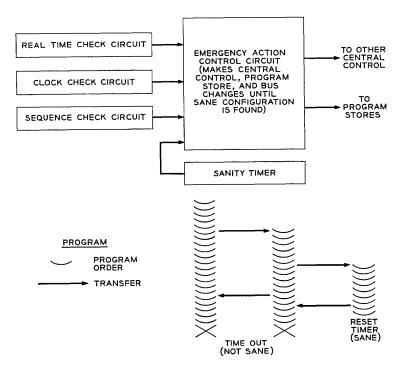

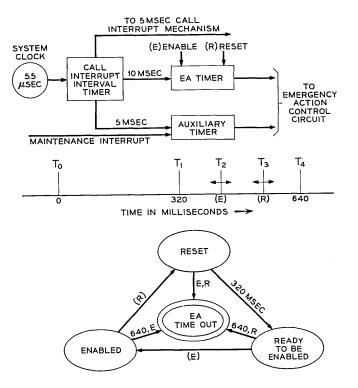

#### 4.5 Maintenance Programs

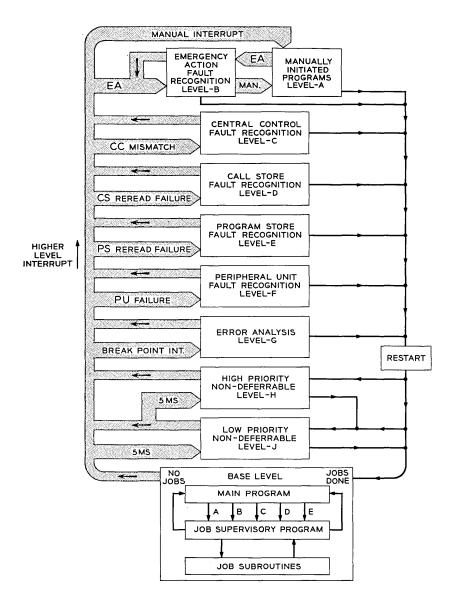

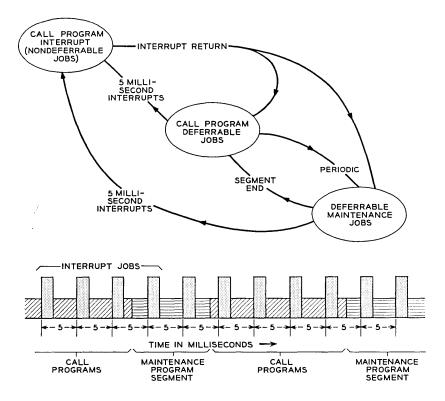

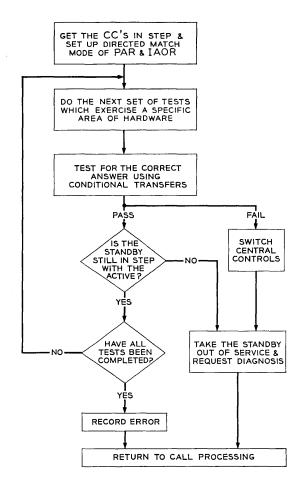

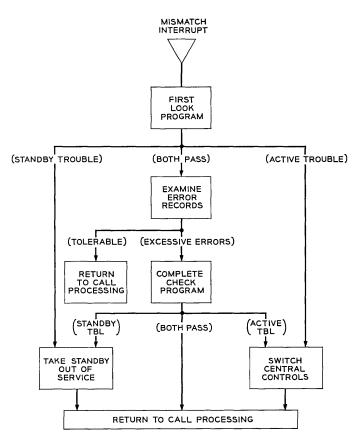

More than half of the stored instructions are used for maintenance programs. Some of these programs, in conjunction with logic wired into the hardware, detect and report faults and troubles; others control routine tests and diagnose troubles and control emergency actions to insure a satisfactorily operating system, either by eliminating faulty subsystems or by reorganizing usable subsystems into a new operating combination. The classes of maintenance programs are arranged in a hierarchy of interrupt levels, so that when an error is detected the control system can be forced to stop what it is doing, keep a record of where it is, and after proper maintenance action is taken, restore itself to proceed with normal operation. In the hierarchy, a higher class can interrupt any lower class of maintenance or operating program.

#### V. TESTING

The separate development of major sections of hardware as individual subsystems, and of programs as other subsystems, and their subsequent successful combination into an operable system present major problems. First, the operation of all hardware subsystems working together to form a single system must be verified. Each of the hardware subsystems is factory tested by a combination of manual and automatic tests. The over-all system operation is checked by a special set of programs known as X-ray programs, which check step-by-step the sequences of operation. Such programs will also be used by Western Electric installation people for checking new installations.

This procedure was also used on the Holmdel, New Jersey, No. 1 ESS as the first over-all check of the system design, and it was here that many interface problems were solved. The solution of these required changes in hardware, program, or both. After the hardware was checked and operating satisfactorily, testing of the call and maintenance programs was begun on the actual system. However, some simulation was usually done on the IBM 7094 computer before the program was submitted to the No. 1 ESS laboratory system. When all programs operate satisfactorily, the system will be tested under simulated traffic conditions and finally under actual traffic conditions.

#### VI. STATUS

At the time of writing of this article, all of the hardware has been tested by means of the test programs and proved to operate satisfactorily. Many of the call and maintenance programs are now operating on both the laboratory and Succasunna, New Jersey, systems. Other programs are still in preparation. Maintenance programs are usually the last prepared because they must be designed after the operating peculiarities of the hardware have been identified. Publication of untested plans, in general, is dangerous. However, some of the authors of the following articles, on programs as yet only partially tested, have decided to present their plans so that a relatively complete story of No. 1 ESS can be presented under a single cover. When the plans have been fully tested, additional details will be reported.

#### VII. SUMMARY

This paper has attempted to present a general outline of the organization and objectives of No. 1 ESS. It also serves as an introduction to the papers that follow.

# VIII. ACKNOWLEDGMENTS

Because No. 1 ESS is such a large undertaking the efforts of many hundreds of people are involved. Even listing the numerous organiza-

1843

tions within Bell Telephone Laboratories would be difficult and this would exclude the many people in the Western Electric Company, the American Telephone and Telegraph Company, and the operating companies who have contributed in important ways.

#### REFERENCE

Keister, W., Ketchledge, R. W., and Lovell, C. A., Proc. IEE, 107, Part B, Suppl. No. 20, 1960.

# Organization of No. 1 ESS Central Processor

# By J. A. HARR, F. F. TAYLOR and W. ULRICH

(Manuscript received January 28, 1964)

The central processor controls the operation of the No. 1 electronic switching system by executing sequences of program instructions. The logical organization of the central processor is described by the simultaneous evolution of:

(1) an instruction repertoire to carry out the required telephone and system maintenance tasks efficiently, and

(2) a circuit logic design to provide the necessary circuits (flip-flop registers, accumulators, etc.) to execute the instructions at a high data processing rate.

The design aims, order structure, timing, internal sequencing, and communications with the peripheral equipment of the system are described.

#### I. INTRODUCTION

Telephone central offices must cover a wide range of sizes and provide a large variety of services to customers; in addition, they must be compatible with existing systems, adaptable to varied and changing operating conditions, dependable, reliable, and economical. The development of an electronic switching system capable of satisfying these requirements presented many new problems to the designers. As a result, many techniques new to the telephone switching field were introduced in the system.<sup>1</sup> One of the most important new techniques is the control philosophy, which utilizes a stored program.

A system employing a stored program is one which consists of memories for storing both instructions and data, and a logic unit which monitors and controls peripheral equipment by performing a set of operations dictated by a sequence of program instructions. The stored program philosophy permitted the designers to use centralized logic circuitry and large-capacity memory units as a means of attaining flexibility and over-all economy in the system.

In this paper some of the design characteristics of the central processor are described, followed by a step-by-step development of the central control order structure and the corresponding logic circuitry needed for its implementation.

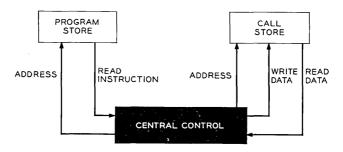

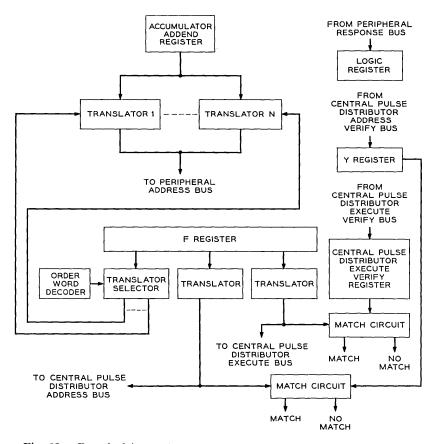

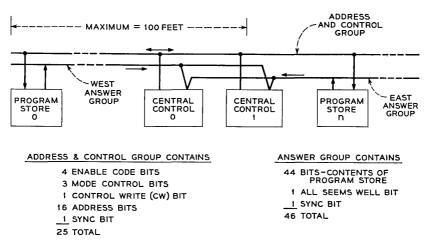

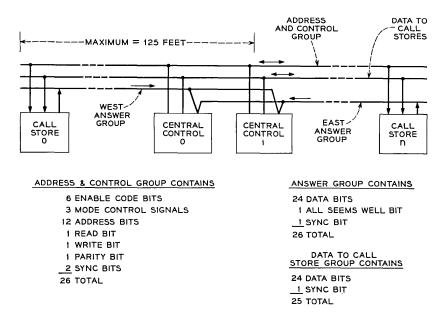

#### II. DESIGN CHARACTERISTICS

A simplified diagram of the electronic switching system (ESS) is shown in Fig. 1. The outer circle represents the entire No. 1 ESS, having primary inputs from lines and trunks<sup>2</sup> via scanners,<sup>3</sup> and outputs to the network<sup>4</sup> and signal distributor,<sup>3</sup> with teletypewriters as administrative input-output devices and with a magnetic tape for automatic message accounting (AMA)<sup>5</sup> output. The inner circle, the central processor, contains a central control<sup>6</sup> unit which executes program instructions and memory units used for storing program instructions and data.

In order for the central processor to handle traffic submitted by offices

Fig. 1 — Simplified diagram of the No. 1 ESS.

serving 5000 to 60,000 customers, the number of memory units in the system must be expandable over a wide range. Therefore the central processor address registers, memory word size, and address buses are designed to accommodate the largest office. The system design must not only meet initial office size requirements, but must also include growth capability.

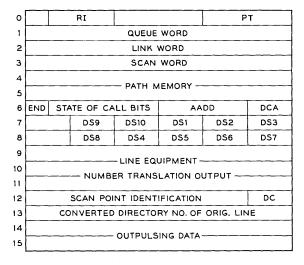

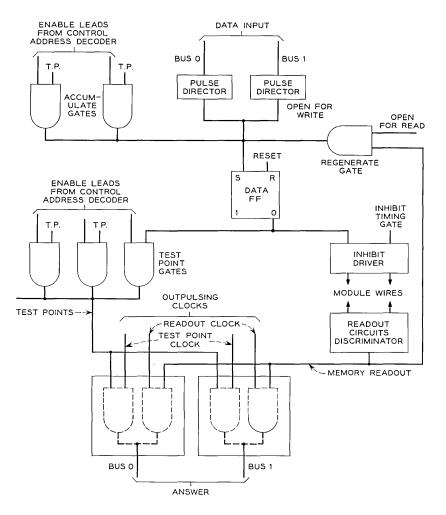

Since the data processing operations required for performing telephone functions are accomplished by executing a stored program<sup>7,8</sup> which must be error-free and remain error-free\* at all times to insure the proper behavior of the system and good service for the customers, the memory chosen for storing the program is semipermanent and requires off-line operations to change it. (This avoids the risk of an error in operation introducing an error in the program.) Therefore the central processor contains two types of memory: a semipermanent memory system (program store)<sup>9</sup> for storing programs and a high-speed readable and writable memory (call store)<sup>10</sup> for storing call progress data.

An address of at least 21 binary bits is needed to gain access to the total number of words required in both the program and temporary memories. To meet this requirement, along with memory store design considerations, the designers decided upon a word length in the call store of 24 bits, comprising a parity check bit and 23 information bits. For convenience, the same word length is used throughout the central control. Most instructions which operate on memory words require a 21-bit address field. Instructions which contain a data field must allow for 23 bits in the data field to be compatible with the length of temporary memory words. Accordingly, the operation fields of each of these types of instructions are 16 and 14 bits in length, respectively, to accommodate the many types of instructions needed in each category. Therefore the instruction word length is 37 bits. To check and correct program instructions with single errors and to determine whether a word read has a double error in it, 7 check bits are also needed for each program instruction, making a total of 44 bits stored for each entry in the program store.

Engineering studies of the number and kind of telephone functions which the system must perform dictated a need for an efficient instruction repertoire with specific attributes. Some of these attributes will now be described.

To perform the functions required to handle the busy-hour traffic submitted by the largest office, the system can spend only approximately

<sup>\*</sup> As will be seen later, facilities are available for detecting and correcting single errors.

5000 machine cycles per call. To meet this requirement, the instruction repertoire must include efficient multifunctional program instructions.

Since the repertoire must include the storage of data of variable bit length in the temporary memory and retrieval of these data, both readfrom-memory and write-to-memory instructions include masking facilities. As used here, the masking of words read from memory means changing all of the bits of the word to zero except those which specify the item of interest; these remain in the same state as they were in memory. Masking of words written into memory is a facility for inserting an item of variable length into a word already in memory; the remaining bits of the word are unchanged.

To assist in achieving program word efficiency, in most cases the same functional program is used for all calls in progress requiring the execution of a given function.<sup>7,8</sup> For reliability, instructions in this system are not changeable at run-time (i.e., while the machine is actually processing calls). Indexing facilities provide means by which the programmer can change the addresses of memory words acted upon by the same program. Also, the indexing facilities can be used to vary the sequence of programs to be read and executed.

To carry out data processing of call information, the repertoire includes the arithmetic operations of addition, subtraction, comparison, shifting, and rotation, and the following logic operations: AND, OR, EXCLUSIVE-OR, and COMPLEMENT. Since the functions which the system must perform do not require multiplication and division operations, it was not necessary to include these in the central processor. To perform the logic functions required to carry out the many telephone functions, a variety of decision instructions are required to transfer control to specific program sequences based on the condition of internal central control registers after data manipulations have been performed on them. For example, a program of three instructions capable of performing the following three operations illustrates the primary way the central processor can vary the sequence of its operations according to input data it has received.

(1) Read, at an address specified by an index register, the word from memory containing the first dialed digit of a call; mask out all of the bits in the word other than the four bit positions used for the first digit; and load the word into an accumulator register.

(2) Compare the word just loaded into the accumulator with the value 10 (i.e., the number of pulses counted when a customer dials zero) specified by the data field of the instruction.

(3) Transfer to the program specified in the address field of the in-

struction if the two compared quantities are equal (this program will cause the customer to be connected to an operator); otherwise, continue the present program sequence.

For efficient operation, the central control should be capable of executing instructions which combine a number of the operations listed above. For example, the repertoire includes an instruction which reads the word at a temporary memory address specified by an index register, masks the word read, complements it, and then AND's the result with the accumulator register in the central control during one operational cycle.

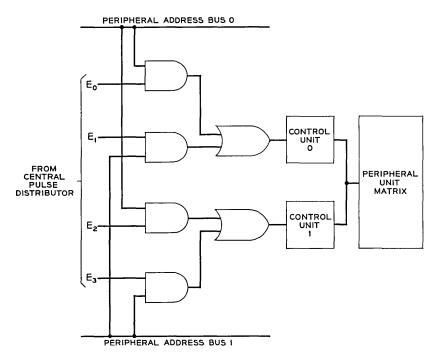

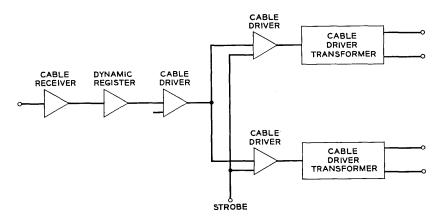

To make efficient use of data processing time the repertoire must include a class of special instructions designed to facilitate the reading and making of logical decisions on input data and special orders for delivering output data to both the network controllers and trunk control circuitry. Therefore the central control can be described as an inputoutput processor superimposed on a general-purpose data processor.

Since the fundamental task of the central processor is continuous monitoring and controlling of its rapidly changing environment, consisting of wide variations of traffic submitted by customer lines and trunks, real time must be carefully considered when planning the system and writing the program. Programs to monitor and gather input data and to deliver output signals and data must be especially efficient in their use of central processor cycle time.

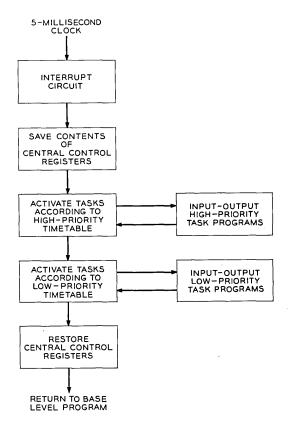

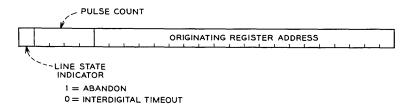

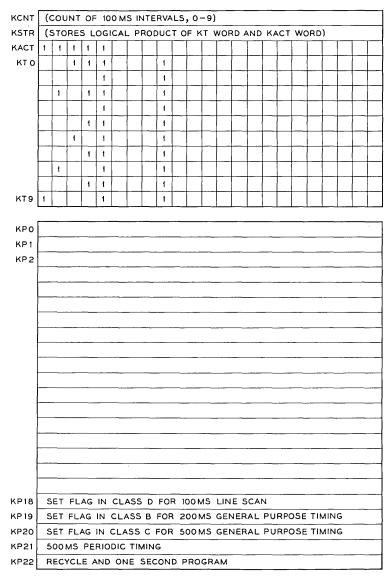

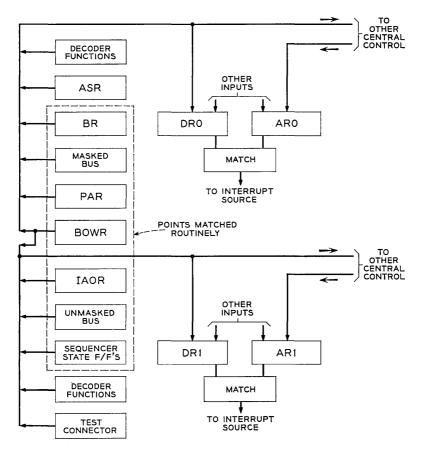

Input-output programs must be executed on a strict schedule. For example, the program to detect and receive dial pulses must be performed every 10 milliseconds. In order to accomplish this, an interrupt mechanism is included in the central processor. The interrupt mechanism, when activated by a source such as a clock or check circuitry, generates a new program address, thus transferring control of the system to an interrupt program sequence. When this occurs, the address of the next instruction which normally would have been executed is automatically stored. When the interrupt program completes its task, control is returned to the interrupted program.

To make the system capable of continuous operation during malfunction of circuit components, the central processor is duplicated. In order to detect and ultimately pinpoint hardware malfunctions, the central processors include:

(1) circuitry which compares the execution of instructions in both central processors,

(2) circuitry for generating a parity bit for each word stored in the temporary memory,

(3) circuitry for checking the parity of words read from temporary memory,

(4) circuitry for detecting and correcting single-bit errors in instructions read from the program memory,

(5) circuitry within the peripheral equipment for checking data received and for notifying the central processor when either data it receives or its own check circuitry indicates trouble,

(6) circuitry within the central control for verifying signals sent back by peripheral equipment, and

(7) circuitry for special-purpose instructions for controlling and interrogating stores and peripheral equipment.

# III. BASIC DESCRIPTION OF CENTRAL CONTROL

In this section an order structure, including the symbolic names of the instructions, and a central control block diagram will be concurrently explained.

#### 3.1 Basic Facilities

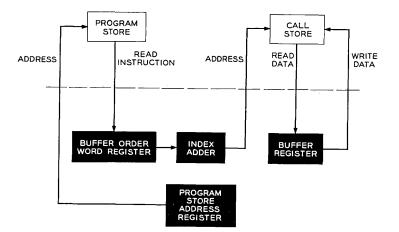

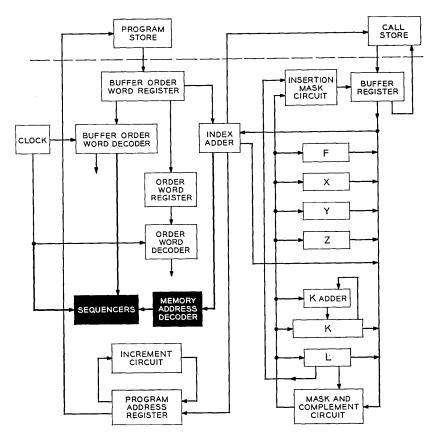

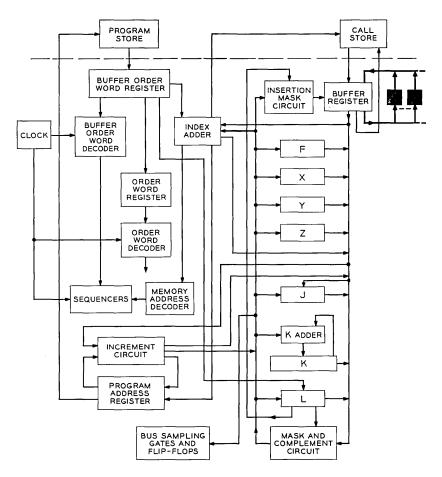

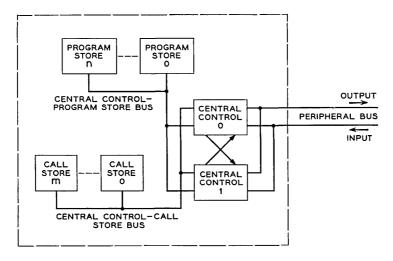

In the simplest form (see Fig. 2), the central processor consists of a central control, a program store which receives an address from central control and returns the corresponding instruction, and a call store, which receives an address and either receives data to be recorded at that location or returns the data previously stored at that location.

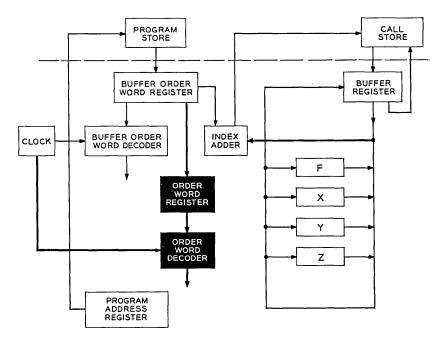

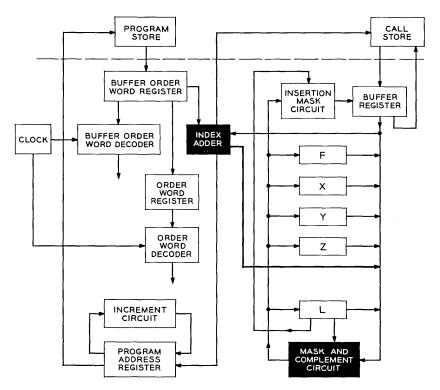

As a starting point, central control must contain registers for receiving program store instructions and call store data, and facilities for generating and transmitting addresses to both stores and data to the call store (see Fig. 3). The buffer order word register (BOWR) receives instructions from the program store, and the data buffer register (BR) receives data from the call store. The program store address register (PAR) is

Fig. 2 — Block diagram of the data processor.

Fig. 3 -Derivation of the central control (1).

used as the source of addresses of instructions to the program store, and the index adder is used to generate addresses for the call store.

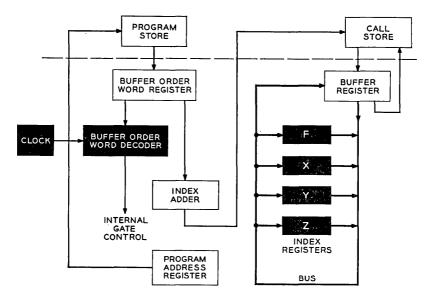

These facilities must be augmented by an instruction decoder, the buffer order word decoder (BOWD) attached to the buffer order word register (see Fig. 4). This decoder is used to control the gating of information inside central control.

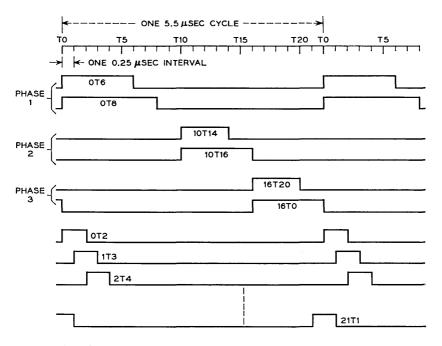

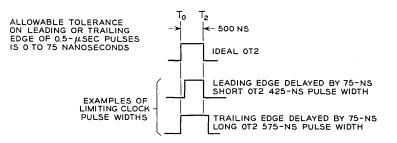

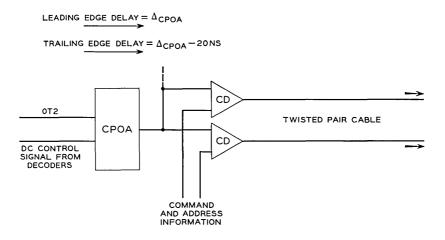

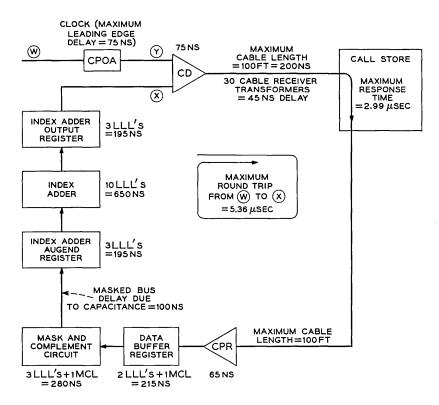

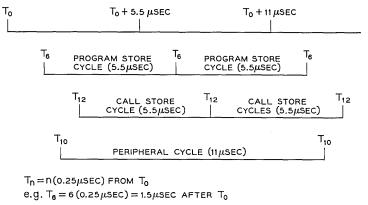

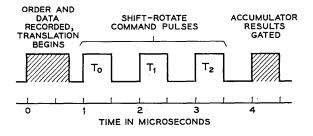

Also needed to control such gating and to synchronize the decoding with the reading of information from the stores is a clock. In the No. 1 ESS central control, the clock is a synchronous 5.5-microsecond clock, with 22 distinct phases separated by 0.25 microsecond. Arbitrary-length clocking pulses are derived by setting a flip-flop circuit with one arbitrary phase, resetting it with another, and using the output of the flipflop as the clocking pulse. Such pulses are repeated once every 5.5 microseconds.

Gates are therefore controlled by decoding the output of the buffer order word register and combining the decoded output with a suitable clock pulse.

#### 3.2 Index Registers

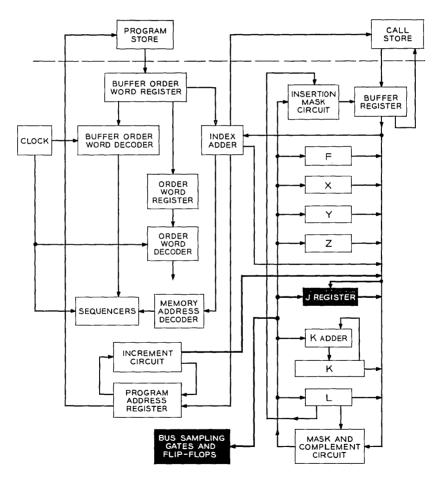

In addition to the buffer register, there are a number of generalpurpose flip-flop index registers, F, X, Y, and Z (see Fig. 4). The index registers are 23 bits long, the basic word length of the central control and the call store. (The 24th bit of the call store, a parity check bit, does not store useful information; this bit need not be carried along in central control data processing, although it must be generated anew when-

Fig. 4 — Derivation of the central control (2).

ever information is stored in the call store and checked whenever information is read from the call store.)

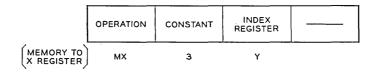

Indexing is useful for developing a program which is general for any telephone central office. It is the process of deriving a memory address by adding a constant from the instruction to a variable previously derived and stored in an index register. For example, the index register might contain the starting address of a block of call store words used for accumulating dialed information; the constant might be the location of a word within such a block, containing information known to be needed at a certain stage of a call. Such an instruction may be described as follows: fetch the call store reading in the third word of a block whose starting address is stored in the Y index register, and store the reading in the X index register. The description of the operation is divided into three parts (see Fig. 5): the basic operation (fetch data from memory

Fig. 5 - Basic instruction format 1.

and store in the X register), the constant of the instruction (3), and the index register used in indexing (Y). In the basic mnemonics of the system, memory to X register is written as MX; therefore this instruction is written as MX,3,Y. Instructions which read or write in memory contain M in their mnemonic representation and are collectively designated M instructions.

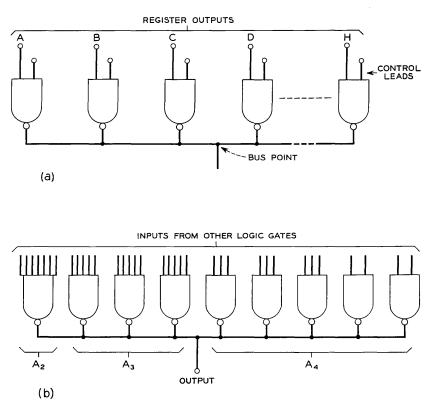

# 3.3 Bus

Information is transmitted among the index registers via a bus (Fig. 4) consisting of 23 parallel information paths. The F, X, Y, and Z registers plus the buffer register, which can also be treated as an index register, all have output gates to and input gates from the bus.

#### 3.4 Index Adder

In order to perform indexing, an adder (see Fig. 6) is required. The index adder receives one input (the constant of the instruction) from the buffer order word register, and the other input (the variable, i.e., the contents of the specified index register) from the bus. The output

Fig. 6 — Derivation of the central control (3).

of the index adder, as previously indicated, is the source of addresses to the call store.

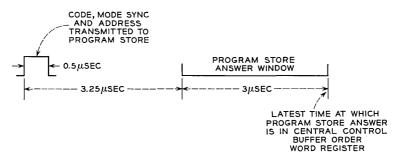

#### 3.5 Order Word Register

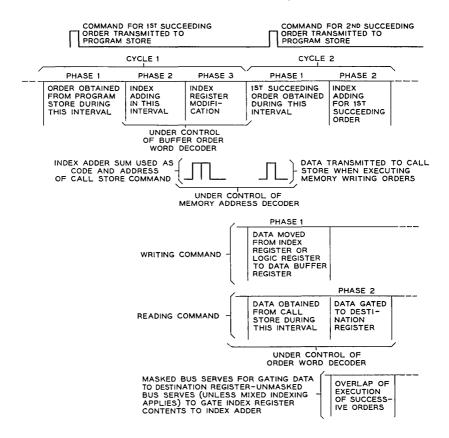

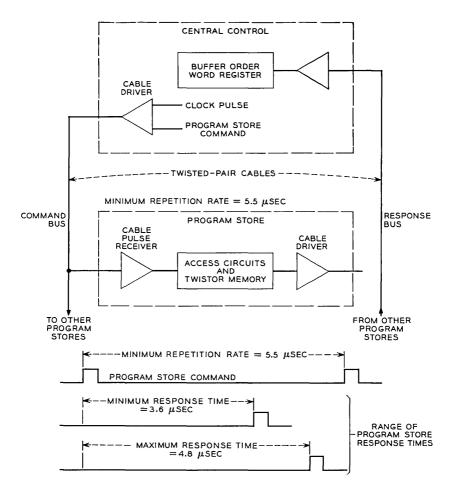

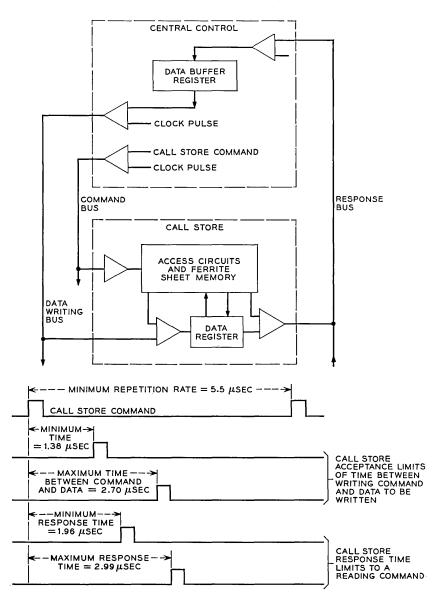

The basic cycle time of the program store is 5.5 microseconds, and the maximum time from the reception of an instruction such as MX,3,Y until the specified reading from a call store is in the data buffer register is about 6.0 microseconds. When one considers the additional data processing of a call store reading after it has been received by central control, it can be seen that the execution time of an instruction occupies major fractions of two machine cycles. Thus there is overlap in the execution of two consecutive instructions. This overlap is described in Section VIII. An order word register and decoder are therefore provided to control part of the execution of an instruction. The buffer order word decoder and the order word decoder simultaneously control the execution of two consecutive instructions.

The buffer order word decoder controls the addressing of the call store. On a reading instruction, the order word decoder controls the gating of information from the call store to the data buffer register and thence, via the bus, to the destination register; on a writing instruction, the order word decoder controls the gating of data from some source register to the data buffer register and thence to the call store. The actions of the two decoders are sufficiently independent that the division of decoders into a buffer order word decoder and an order word decoder does not cost very much compared to the use of a single decoder.

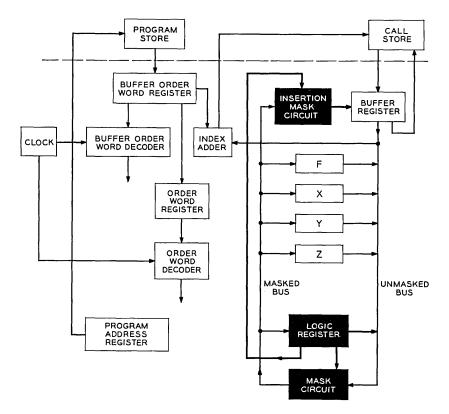

# 3.6 Masking: Logic Register, Unmasked Bus, Masked Bus, and Mask Circuit

The 23-bit word length is much longer than many of the basic quantities of data. A long useful quantity of data is a 21-bit memory address. A typical short quantity is a single binary-coded decimal digit, 4 bits long; several such short quantities may be packed in a single word. In order to treat partial words efficiently, the central control has masking facilities (see Fig. 7). Since most data words pass over the bus, a single mask circuit on the bus accomplishes most of the masking functions. The mask circuit has two inputs, the unmasked bus, which is connected to the gates at the outputs of index registers, and the output of a logic register whose chief function is to control the masking function. The output of the mask circuit is called the "masked bus" and is connected to the input gates of index registers.

Fig. 7 — Derivation of the central control (4).

The logic register is 23 bits long; each bit controls the masking of 1 bit on the bus. The logic register is itself connected to the unmasked and masked bus so that it may be controlled and read as easily as any index register.

Masking is an option of most instructions. If in the previously described instruction (MX,3,Y) only the four least significant bits were of interest and the logic register were already set up with these four bits equal to one and the rest of the bits equal to zero, then by specifying masking only the four least significant bits would be transmitted to the X register (see Fig. 8). The rest of the bits would be transmitted as zero. This form of masking is called PL masking (P = product, L = state of the logic register; therefore, product with the state of the logic register). This instruction would then be written as MX,3,Y,PL.

|                         | OPERATION | CONSTANT | INDEX<br>REGISTER | MASK AND       |

|-------------------------|-----------|----------|-------------------|----------------|

| /                       | мх        | 3        | Y                 | PL (MASK)      |

| X REGISTER<br>TO MEMORY | ХМ        | 3        | Y                 | EL (INSERTION) |

PL OR EL WILL USE THE CURRENT CONTENTS OF THE LOGIC REGISTER L WHICH WAS SET BY A PREVIOUS INSTRUCTION

Fig. 8 - Basic instruction format 2.

#### 3.7 Insertion Masking

Another form of masking that is used frequently is insertion masking. Insertion masking permits all but a selected group of the bits of a certain register to remain unchanged. The selected group of bits is then set up according to the instruction. Because of the requirement that certain bits remain intact, it is convenient to associate the insertion mask circuit with only one of the registers. The most logical choice is the buffer register, since insertion masking is most frequently used when only a portion of a word in the call store is to be altered. The insertion mask circuit is also controlled by the logic register, since in most cases the bits to be inserted and the position associated with these bits have been set up in the logic register for some previous masking (PL) operation. Insertion masking is indicated by specifying EL masking. (E = insertion, and L = the state of the logic register.) If, for example, the four least significant bits of the X register are to be stored in the address  $Y + 3^*$  while leaving the other bits of that memory location intact, this action could be performed with the following two-step program (provided that the logic register is already set up to 1's in the four least significant bits and 0's elsewhere): MB,3,Y (read the contents of memory at the address Y + 3 into the data buffer register); XM,3,Y,EL (insert the contents of X into the BR for all bit positions of the logic register equal to one, leaving the rest of the bits of the BR intact; then write the buffer register into memory at address Y + 3). If PL, instead of EL, masking had been specified, the contents of memory would be all 0's except in the four least significant bits; by specifying EL the upper bits remain the same as they appear in the BR.

There is no circuitry available at the call store for performing the equivalent of insertion. Therefore, insertion into memory must always

<sup>\*</sup> For simplicity, the following convention is used in this paper: the contents of a register, such as Y, plus a constant, such as 3, are represented by an unbracketed expression, such as Y + 3.

be a two-step operation: the first step to read the word at which information is to be inserted; the second step to insert this information and then write a complete word back. Insertion is entirely a central control function, not a store function.

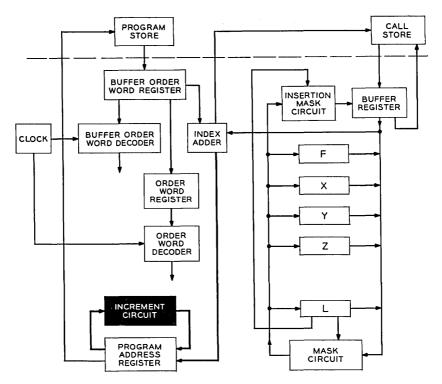

# 3.8 Transfer Facilities

So far the details of addressing a program store have not been shown except for a program store address register (PAR) which transmits such an address. In the program, one of two things can happen. Normally, the program advances from one instruction to the next, so the contents of the program store address register are simply incremented by one. This is accomplished by attaching an increment circuit to the program store address register (see Fig. 9). (The program stores themselves do not have any incrementing facilities. A program store is always addressed with a complete address.) However, sometimes in a program a transfer is necessary. A transfer instruction is an instruction which causes the program to go to another set of instructions, not the immediately following instruction. The most convenient source of the address to which the program would transfer is the output of the index adder, since this is the place where the contents of the instruction are combinable with the contents of registers and thus indirectly with memory readings. A connection from the index adder to the program address register is therefore provided (see Fig. 9).

Direct transfers are transfers to an indexed address. Indirect transfers — i.e., transfers to an address stored in memory, the memory being read through the use of an indexed address — are also possible in No. 1 ESS. An indirect transfer is indicated by an M suffix in the index register field. An input (for simplicity, left out of the diagram) from the call store to the buffer order word register transmits the transfer address to the index adder, thence to the program store address register.

# 3.9 Complement Option

Another option existing in the system is the complement option. When numbers are considered numerical rather than logical data, a negative number is stored as the complement of the positive number whose absolute value is the same. The most significant bit, 22, is the sign bit of the entire quantity. This means that both a positive and a negative quantity 0 exist in the system, since the complement of all 0's (+0) is all 1's (-0). Such a system has the advantage of having very simple adder circuits, even though it does introduce occasional programming

Fig. 9 — Derivation of the central control (5).

problems. The complement circuit is in series with the mask circuit (see Fig. 10); masking takes place before complementing. The complementing is specified as part of the mask field. Thus if we wish to load into X the masked and complemented contents of memory found at the address Y + 3 we may specify this instruction (see Fig. 11) by writing MX,3,Y,PLC.

#### 3.10 Data Instructions

So far only instructions which deal with memory readings have been considered. There is another large class of instructions which deal with internal data manipulations and with the setting up or altering of registers by some constant (data word) within the instruction. These instructions are defined as W (for word) instructions. (It is important to bear in mind the fundamental property that instructions in this machine are not variable. A constant in an instruction is truly a constant until such a time as the program itself is altered, which can be done only by CENTRAL PROCESSOR ORGANIZATION

Fig. 10 — Derivation of the central control (6).

writing new permanent magnet twistor cards.) A natural channel for performing such data manipulations is via the index adder. Therefore the index adder has an output onto the unmasked bus (see Fig. 10). Thus, for example, we can increment register X by a constant by gating the X register to the index adder, adding the constant of the instruction and gating the output of the index adder via the bus back into the X register. All these operations are performed by the instruction WX (W equals indexed word, i.e., output of the index adder). This instruction is executed by circuit actions equivalent to generating a mem-

Fig. 11 — Basic instruction format 3.

ory address, except that the address is gated to the unmasked bus instead of the memory.

W instructions are also maskable, since the output of the index adder has to go through the mask circuit before it arrives at the destination register. Thus the instruction WX,3,Y,PL takes the Y register, increments it by 3, and places the result in the X register after first masking it according to the present contents of the logic register.

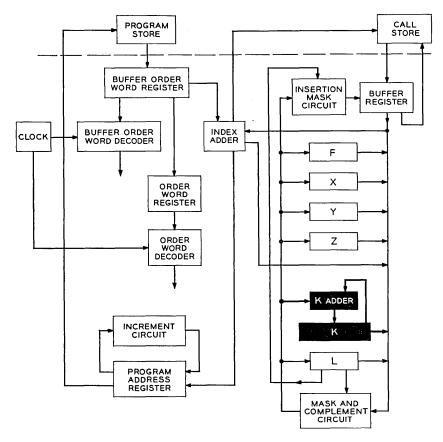

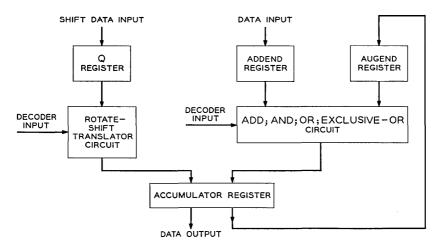

#### 3.11 Accumulator

The central control must perform many additions and logical combinations of two quantities. It is convenient to use one register as an accumulator (K) and to permit this register to be combined readily with masked memory and W-type data. The accumulator adder (see Fig. 12)

Fig. 12 — Derivation of the central control (7).

is capable of combining the present contents of the accumulator with indexed data or memory readings, both optionally masked, by adding, ANDing, ORing, or EXCLUSIVE-ORing the two. The timing problems are sufficiently severe that a single adder system cannot serve both as an index adder and an accumulator adder for combining two data operands. Accordingly, central control contains two adder systems to handle both operations concurrently.

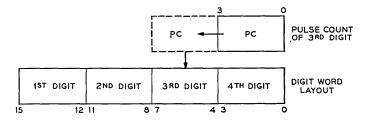

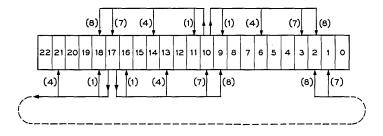

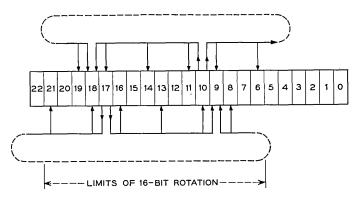

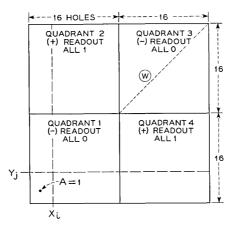

Data in the accumulator can also be shifted and rotated. The shifting is not usually done for multiplication purposes, but to line up two items of information found in different positions within two data words to a position where the two items may be logically combined or treated in some other standard manner. For example, a pulse count for a decimal digit may always be accumulated in bit positions 0 through 3 (see Fig. 13). However, it may have to be stored in positions 4 through 7, or 8 through 11, or 12 through 15, according to which digit of a number it represents. To get data accumulated in positions 0 through 3 to positions 4 through 7, a shifting operation is necessary.

The rotation operation is similar to the shift operation except that for a left rotate the contents of the most significant bit, instead of being shifted out, are shifted back into the least significant bit, and vice versa for a right rotate. A special-purpose rotation within 16 positions of K is also available in central control. This rotation is extensively used in the network path hunt program.

Shifting is also performed very frequently when a number is composed of two parts, the first part indicating the location of an appropriate table of information and the second part indicating the location within that table.<sup>11</sup> For example, a line equipment number consists of a line link network and line switch frame indication, which is used to find a table, each table containing line translation information for one line switch frame and a position within that line switch frame which is used to find the line translation information within such a table. Without the ability to split such numbers into parts, it would be very diffi-

Fig. 13 — Use of shifting.

cult to organize the memory layout of the system for both rapid access and compact storage.

#### 3.12 Data from the Program Store

So far the simplifying assumption has been made that data always come from a call store and instructions always come from a program store. In practice, however, much of the data is stored in the program store — specifically, the translation data. The process of reading a program store for data is a complicated one, especially in view of the overlap operation that is used.

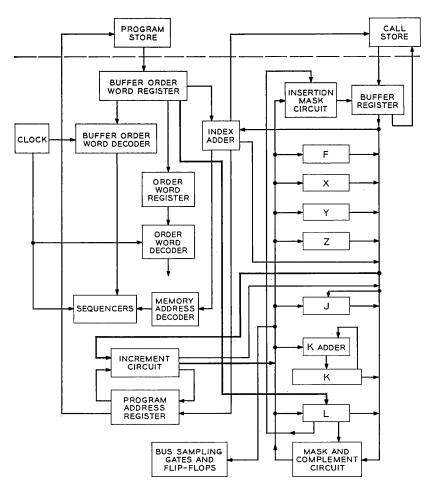

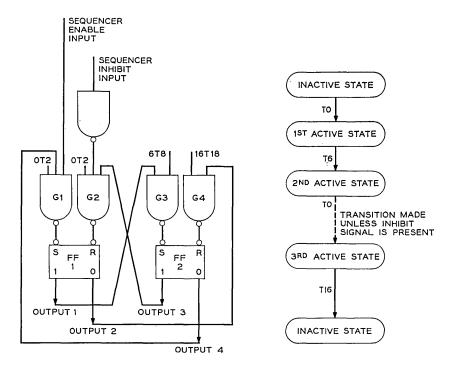

The same types of instructions are used to read data from the program store and from the call store. This helps programming, since it does not fix a memory location at the time the program is written and helps to relieve the programmer from the burden of considering two different types of memories. A memory address decoder (see Fig. 14) connected to the output of the index adder recognizes when the output of this adder specifies an address that is not in the call store but is in program store.\* It triggers a sequencer (see Fig. 14) which takes care of a special group of operations to be described below.

A sequencer is necessary to prevent the data that are coming from the program store from being incorrectly interpreted as an instruction. This sequencer must cause the program store to be read at the address specified by the output of the index adder and must then go on to the next instruction.

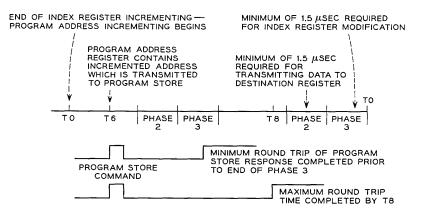

Fig. 15 shows the contents of the buffer order word register, order word register and program store address register during the processing of an instruction for reading data from the program store. The instruction is MX,BB,Y.† Y + BB specifies an address which happens to be in the program store. This instruction is located at the address AA. At time 1 the buffer order word register contains the instruction at address AA, the order word register contains the instruction at address AA, the order word register contains the instruction at address AA, the program store address register contains the number AA + 1 in preparation for the reading of the next instruction. At time 2 the buffer order word register has the instruction at address AA + 1 but it cannot execute this instruction because the data word called for by the previous instruction has not yet been fetched. The order word register, in the

<sup>\*</sup> Blocks of memory addresses assigned to program stores and call stores are fixed for all No. 1 ESS installations; the wiring pattern of the memory address decoder is therefore the same in all installations.

$<sup>\</sup>dagger$  BB is a symbolic representation of some constant; AA represents a program address.

CENTRAL PROCESSOR ORGANIZATION

Fig. 14 — Derivation of the central control (8).

meantime, has the instruction at address AA, while the program store address register has received a data address from the index adder. This data address Y + BB is now being used to read the program store. At time 3 the buffer order word register contains the information located at address Y + BB, and the order word register continues to hold the instruction at address AA, while the program store address register has now been incremented to the value AA + 1 to prepare for the reading of the next instruction. At time slot 4 this instruction has been read into the buffer order word register, the output of the buffer order word register has gone via the index adder to the appropriate destination (the X register) under the control of the order word register, and the program address register is preparing to read the instruction at address

| TIME SLOT | BUFFER ORDER<br>WORD REGISTER | ORDER WORD | PROGRAM<br>ADDRESS<br>REGISTER |

|-----------|-------------------------------|------------|--------------------------------|

| 1         | (AA)                          | (AA - 1)   | AA + 1                         |

| 2*        | IAAKI                         | (AA)       | BB+Y                           |

| з*        | (BB + Y)                      | (AA)       | AA + 1                         |

| 4         | (AA + 1)                      | (AA)       | AA+2                           |

| 5         | (AA + 2)                      | (AA + 1)   | AA + 3                         |

(−)→ SYMBOL MEANING WORD STORED AT THIS ADDRESS OR IN THIS REGISTER.

INSTRUCTION AT ADDRESS AA IS MX, BB,Y;

BB+Y IS AN ADDRESS OF DATA IN THE PROGRAM STORE.

\*THESE ACTIONS ARE CONTROLLED BY CENTRAL CONTROL INTERNAL SEQUENCE CIRCUITS SINCE THE OPERATION COVERS MORE THAN ONE CENTRAL CONTROL CYCLE TIME.

Fig. 15 — Time sequence of words passing through BOWR, OWR, and PAR when reading data from program store.

AA + 2. At time 5 this instruction is in the buffer order word register and the order word register has the instruction located at address AA +1, while the program store address register has been incremented to AA + 3. Since the order word decoder is strictly a combinational circuit, the sequencer must be used to control the actions of fetching the data; otherwise the order word register would simply control the execution of the instruction at address AA three consecutive times. Note that the instruction for reading data from the program store consumes three cycles: one basic cycle, one cycle to read the data from the program store, and one cycle to reread the next instruction.

### 3.13 Conditional Transfers

A very important part of any data processing machine instruction repertoire is the set of conditional transfer instructions. These instructions cause a transfer of program control to a specified address if some data word or bit of data appearing in central control is some predetermined value. If the word or bit does not have that value, the transfer is not made, and the instruction immediately following the transfer instruction is executed.

Eight transfer instructions are provided to interrogate the contents of the accumulator for the following values: positive, negative, arithmetic zero, \* all but arithmetic zero, logical zero (+0 only), all but logical zero, less than or equal to arithmetic zero, and greater than or equal to arithmetic zero.

<sup>\*</sup> Arithmetic zero includes +0 (all zeros) and -0 (all ones). In both cases all 23 bits are alike, and arithmetic zero is therefore also referred to as "homogeneity."

A pair of control (C) flip-flops connected to the masked bus (see Fig. 16) store the homogeneity and sign of data words read from memory as the words appear on the masked bus. Another eight transfer orders test the C flip-flops for the same combinations of values available for testing the accumulator register.

Normally, the conditional transfer instructions follow immediately after the condition is registered, either in the accumulator or the C flipflops. The usual instructions for gating information into registers may set the accumulator or the C flip-flops. In addition, there is a set of compare instructions (see Fig. 17) which do not alter any register but

Fig. 16 - Derivation of central control (9).

Fig. 17 — Basic instruction format 4.

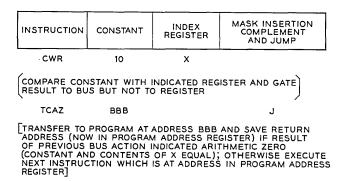

which set the C flip-flops according to the result of the comparison. For example, the instruction CWR,10,X compares 10 with X and places the result in the C flip-flops. The comparison is performed by subtracting 10 from X, placing the result on the bus, and gating it only to the C flip-flops. One way to check whether the X register was actually equal to 10 is to follow the first instruction with an instruction TCAZ, BBB: transfer to the address BBB if the C flip-flops are equal to arithmetic 0; if not, advance to the next instruction.

#### 3.14 J Option and Register

Associated with transfer instructions is a return address (jump) option (see Fig. 17). Unconditional or conditional transfer instructions occur frequently in the middle of a program and are used to transfer to a subroutine to do a common task; subsequently the subroutine returns control to the original program. Since the subroutine must know where to return, a J register (see Fig. 16) has been provided which may be set up at the discretion of the programmer whenever a transfer is executed. If the transfer is actually executed, the J register is set to the address of the instruction immediately following the transfer instruction. To set up the J register, a path must be provided from the output of the increment circuit to the unmasked bus and thence to the J register (see Fig. 16).

# 3.15 Index Register Modification Options

Index register modification options are available in the No. 1 ESS order structure. If some task is being performed on a number of successive memory locations, it is sometimes convenient to set an index register to the value of the first memory address, then to increment the register by +1 as successive words are read from memory. This incrementing can be performed as an option on most reading instructions. For example, the instruction MX,3,Y simply gates the contents of memory at the address Y + 3 into the X register. The instruction MX,3,YA (see Fig. 18) gates the contents of memory at the address Y + 3 into the X register. The instruction is performed by connecting the increment circuit input to the unmasked bus (see Fig. 19); this allows the index register to be gated into the increment circuit; the output of the increment circuit may later be gated to the index register via an output connection to the masked bus.

Two other index register modification options exist which change the indicated index register to the indexed quantity. Thus, the instruction MX,3,YW reads the memory at address Y + 3 and gates this into the X register and also changes Y to the value W, the indexed quantity, which is Y + 3. Another index register modification option is the setup index register modification. For example, MX,30000,SY would read the contents of memory at address 30,000 into the X register and would place the quantity 30,000 into the Y register (SY = set up Y).

# 3.16 Logic Register Setup Options

The logic register is changed very frequently in the course of a typical program. Furthermore, many of the programs that are encountered include effectively indirectly addressed readings,\* i.e., one instruction is used to read a quantity, and the reading is then used as the address of the quantity which is actually desired. In such a case, the register being used for the second reading usually contains the complete address so that no additional data are required as the constant of the instruction. Consequently, it is desirable to be able to use the constant of the second instruction to set up the logic register instead of performing unnecessary indexing. A direct path has therefore been provided between the buffer order word register and the logic register (see Fig. 19). If setup masking is specified, then the constant of the instruction is used to set up the logic register and is not used in indexing.

The interplay of index register modification and setup masking options can be illustrated by the following programming problem: complement the 3 least significant bits of memory at the address Y + 3.

<sup>\*</sup> Indirect addressing was not considered worthwhile for data operations, because it never saves time and rarely saves instructions in this system.

| INSTRUCTION | CONSTANT | INDEX REGISTER<br>AND<br>MODIFICATION | MASK INSERTION<br>COMPLEMENT<br>AND JUMP |

|-------------|----------|---------------------------------------|------------------------------------------|

| мх          | 3        | YA                                    |                                          |

[READ CONTENTS OF MEMORY AT ADDRESS Y+3 INTO X REGISTER; THEN INCREMENT Y BY +1]

Fig. 18 — Basic instruction format 5.

Fig. 19 — Derivation of the central control (10).

. . . . .

Using straightforward programming, this can be done by the following three-step program: MX,3,Y (read memory into the X register); WL,7 (set up the logic register to the value seven, i.e., 1's in the 3 least significant bits, 0's elsewhere); XM,3,Y,ELC (store X in memory using insertion masking and complementing at the address Y + 3). This program will result in 3 least significant bits of X — i.e., the bits selected by the logic register — being complemented (C option) and inserted (EL option) into, first the buffer register, thence the memory, at the location Y + 3. A two-step program for performing the same task is the following: MX,3,YW (read from memory at address Y + 3into the X register and set up Y to the value Y + 3; XM,7,Y,ESC (set up the logic register to the quantity 7 as indicated by the S in the ESC mask option; complement, as indicated by C, the X register, and insert, as indicated by E, into the buffer register the 3 least significant bits as selected by the L register; and gate this information to memory at the address which is now in Y, and which is 3 greater than the original value of Y). Note that the first program repeated the constant 3 twice, whereas the second program used it only once. The index register modification option permitted the constant of the instruction to be remembered for subsequent instructions without using any extra steps. Similarly, the constant 7 for setting up the mask was useful in the second instruction of the modified program because, since no constant was necessary for addressing the memory, a constant could be used for setting up the logic register.

It is important to remember that these options not only conserve memory space for instructions but save the time necessary to execute additional instructions. In this system, each instruction takes one cycle whether it be a memory instruction (M) or a register setup instruction (W).

### 3.17 Rightmost One Function

One function that occurs frequently in the type of data processing work that constitutes the call processing program of the No. 1 ESS is that of detecting and identifying a one in the midst of a group of zeros in a word. The one might signify a request for action, the zeros, inactivity; the position of the one would represent which member of the group requires the action. By concentrating always on the least significant one, successively all requests will eventually be handled.

It is important to have some instruction which identifies the position within a word of the rightmost one, because this operation is performed often and is awkward to do using more conventional instructions. The

## 1870 THE BELL SYSTEM TECHNICAL JOURNAL, SEPTEMBER 1964

word to be examined is placed in the accumulator; a rightmost one detect circuit connected to the accumulator gates the binary position of the rightmost one onto the unmasked bus. This information is then transmitted via the buses to the F (for "first-one") register. A circuit to reset this bit in the accumulator then receives its selection information from the F register.

Two instructions exist for the first-one function: TZRFZ transfers if the accumulator is zero; otherwise, it gates the position of the rightmost one to the F register and resets that bit; TZRFU performs the same actions, except that the bit in K is not reset. The programmer specifies the transfer address information in the same way that it is specified for any conditional transfer instruction.

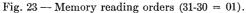

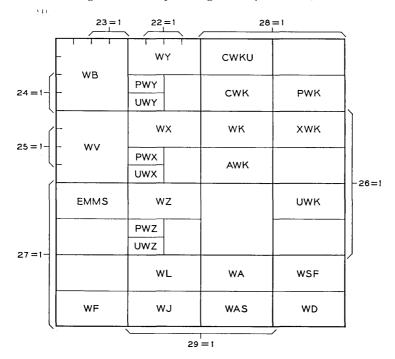

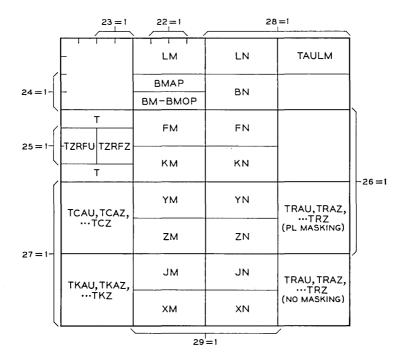

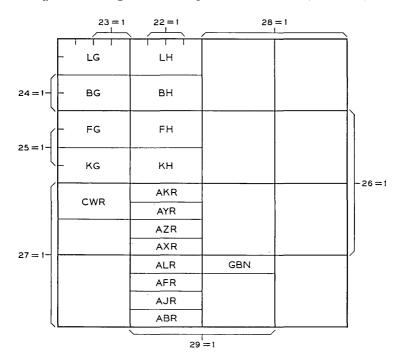

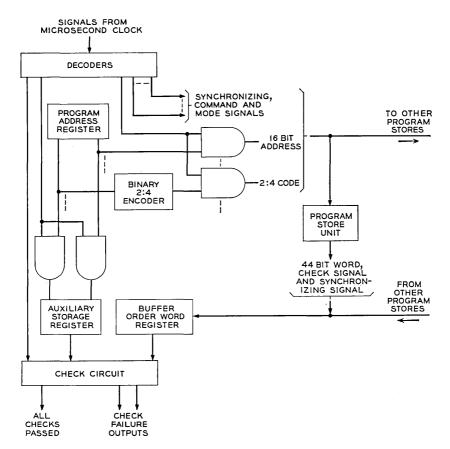

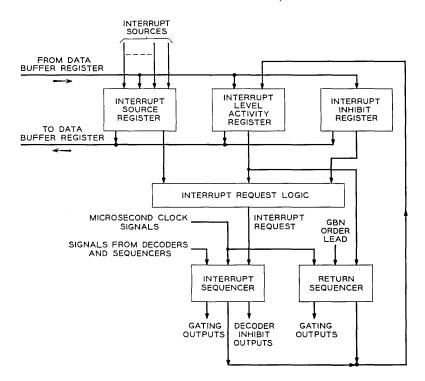

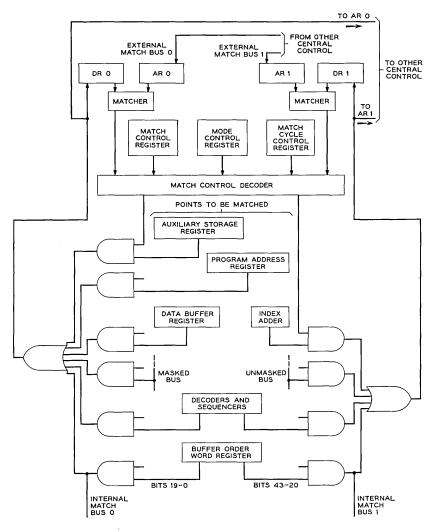

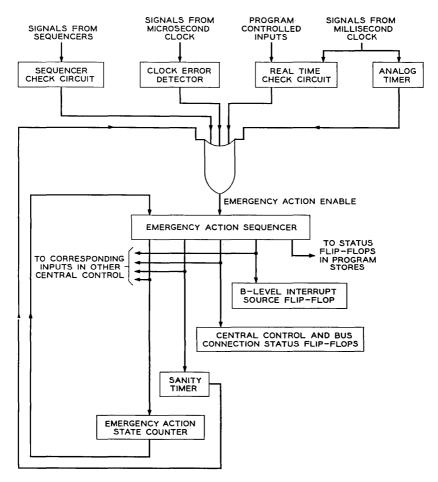

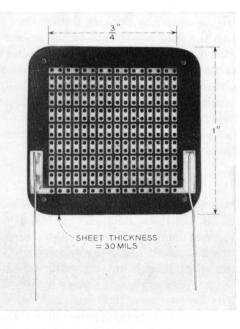

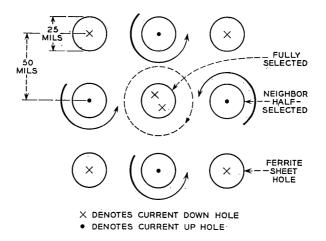

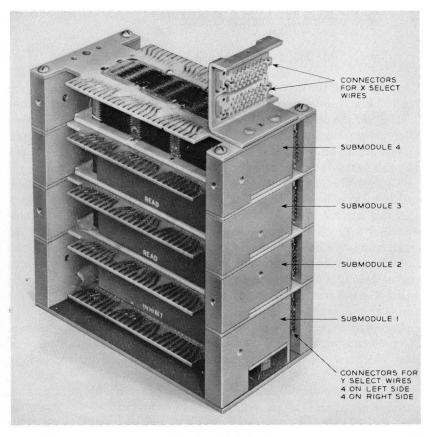

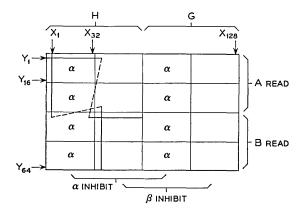

## 3.18 Buffer Bus Registers