# Z8000 CPU Technical Manual

## **Z8000 CPU** Technical Manual

og

# **Table of Contents**

|       | Introduction 1-1                             | Z8000 Processor                       |

|-------|----------------------------------------------|---------------------------------------|

| 1.2   | General Organization                         | Overview                              |

| 1.3   | Architectural Features                       | · · · · · · · · · · · · · · · · · · · |

|       | General-Purpose Register File 1-2            | L                                     |

|       | Instruction Set 1-2                          |                                       |

|       | Data Types 1-2                               |                                       |

|       | Addressing Modes 1-2                         |                                       |

|       | Multiple Memory Address Spaces 1-3           |                                       |

|       | System/Normal Mode of Operation1-3           |                                       |

|       | Separate I/O Address Spaces 1-3              |                                       |

|       | Interrupt Structure                          |                                       |

|       | Multi-Processing                             |                                       |

|       | Large Address Space of the Z8001             |                                       |

|       | Segmented Addressing of the Z8001            |                                       |

|       |                                              |                                       |

| 1 4   | Memory Management                            |                                       |

| 1.4   | Benefits of the Architecture                 |                                       |

|       | Code Density                                 |                                       |

|       | Compiler Efficiency 1-5                      |                                       |

|       | Operating System Support 1-5                 |                                       |

|       | Support for Many Types of Data Structures1-6 |                                       |

|       | Two CPU Versions: Z8001 and Z8002 1-6        |                                       |

| 1.5   | Extended Instruction Facility 1-6            |                                       |

| 1.6   | Summary                                      |                                       |

|       |                                              |                                       |

| 2.1   | Introduction                                 | Architecture                          |

| 2.2   | General Organization                         |                                       |

| 2.3   | Hardware Interface                           | 2                                     |

|       | Address/Data Lines                           |                                       |

|       | Segment Number (Z8001 only)                  |                                       |

|       | Bus Timing                                   |                                       |

|       | Status                                       |                                       |

|       | CPU Control                                  |                                       |

|       |                                              |                                       |

|       | Bus Control                                  |                                       |

|       | Interrupts                                   |                                       |

|       | Segment Trap Request (Z8001 only) 2-4        |                                       |

|       | Multi-Micro Control                          |                                       |

|       | System Inputs                                |                                       |

|       | Timing                                       |                                       |

| 2.5   | Address Spaces                               |                                       |

|       | Memory Address Space                         |                                       |

|       | I/O Address Space                            |                                       |

| 2.6   | General-Purpose Registers                    |                                       |

|       | Special-Purpose Registers                    |                                       |

|       | Program Status Registers                     |                                       |

|       | Program Status Area Pointer                  |                                       |

|       | Refresh Counter                              |                                       |

| 20    | Instruction Execution                        | •                                     |

|       |                                              |                                       |

| 2.9   | Instructions                                 |                                       |

| ~ . ~ | Instruction Formats                          |                                       |

|       | Data Types                                   |                                       |

|       | Addressing Modes                             |                                       |

| 2.12  | Extended Processing Architecture 2-8         |                                       |

|       |                                              |                                       |

# Table of Contents (Continued)

| 2.1:              | B Exceptions       2-9         Reset       2-9         Traps       2-9         Interrupts       2-9         Trap and Interrupt Service Procedures       2-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Architecture<br>(Continued)<br>2 |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3.2<br>3.3        | Introduction       3-1         Types of Address Spaces       3-1         I/O Address Space       3-1         Memory Address Spaces       3-2         Addressable Data Elements       3-2         Segmented and Nonsegmented Addresses       3-2         Segmentation and Memory Management       3-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Address Spaces                   |

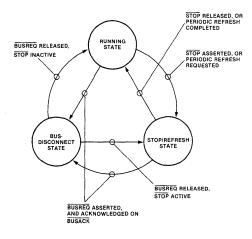

| 4.2<br>4.3        | Introduction4-1Operating States4-1Running State4-1Stop/Refresh State4-1Bus-Disconnect State4-1Effect of Reset4-1Instruction Execution4-2Running-State Modes4-2Segmented and Nonsegmented Modes4-2Normal and System Modes4-3Extended Instructions4-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CPU Operation                    |

| 5.2<br>5.3<br>5.4 | Introduction       5-1         Use of CPU Registers       5-2         Addressing Mode Descriptions       5-2         Descriptions and Examples (Z8002 and Z8001 Nonsegmented Mode)       5-3         Register (R)       5-3         Inmediate (IM)       5-3         Indirect Register (IR)       5-3         Direct Address (DA)       5-4         Index (X)       5-4         Relative Address (BA)       5-5         Base Address (BA)       5-5         Base Index (BX)       5-6         Descriptions and Examples (Segmented Z8001)       5-6         Indirect Register (IR)       5-7         Direct Address (DA)       5-6         Base Index (BX)       5-6         Indirect Register (R)       5-6         Indirect Register (IR)       5-7         Direct Address (DA)       5-7         Indirect Register (IR)       5-7         Direct Address (DA)       5-7         Index (X)       5-8         Relative Address (BA)       5-8         Base Address (BA)       5-9         Base Index (BX)       5-9         Base Index (BX)       5-10 | Addressing Modes<br>5            |

|            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                          |                 |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 6.3        | Introduction6-1Functional Summary6-1Load and Exchange Instructions6-2Arithmetic Instructions6-2Logical Instructions6-3Program Control Instructions6-3Bit Manipulation Instructions6-4Rotate and Shift Instructions6-4Block Transfer and String Manipulation Instructions6-5Input/Output Instructions6-6CPU Control Instructions6-6Extended Instructions6-7Processor Flags6-7Condition Codes6-8 | Instruction Set |

| 6.6<br>6.7 | Instruction Interrupts and Traps       6-8         Notation and Binary Encoding       6-9         Z8000 Instruction Descriptions and Formats       6-11         EPA Instruction Templates       6-167                                                                                                                                                                                          |                 |

| 7.2        | Introduction       7-1         Interrupts       7-1         Non-Maskable Interrupt (NMI)       7-1         Vectored Interrupt (VI)       7-1         Nonvectored Interrupt (NVI)       7-1                                                                                                                                                                                                     | Exceptions<br>7 |

|            | Traps       7-1         Extended Instruction Trap       7-1         Privileged Instruction Trap       7-1         System Call Trap       7-1         Segment Trap       7-1         Privileged Trap       7-1                                                                                                                                                                                  |                 |

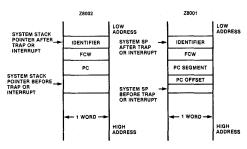

| 7.5        | Reset7-2Interrupt Disabling7-2Interrupt and Trap Handling7-2Acknowledge Cycle7-2Status Saving7-2Loading New Program Status7-3Executing the Service Routine7-4                                                                                                                                                                                                                                  |                 |

| 7.7        | Returning from an Interrupt or Trap                                                                                                                                                                                                                                                                                                                                                            |                 |

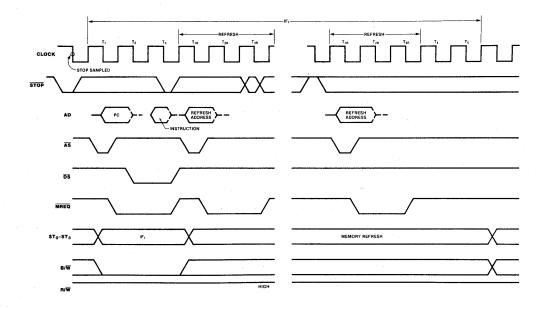

| 8.2<br>8.3 | Introduction8-1Refresh Cycles8-1Periodic Refresh8-1Stop-State Refresh8-1                                                                                                                                                                                                                                                                                                                       | Refresh<br>8    |

v

# Table of Contents (Continued)

| 9.1<br>9.2<br>9.3 |                                                                                                                                                                                                                             | External | Interface<br>9       |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------|

|                   | Transaction Pins       9-2         Bus Control Pins       9-2         Interrupt/Trap Pins       9-2         Multi-Micro Pins       9-3                                                                                      |          |                      |

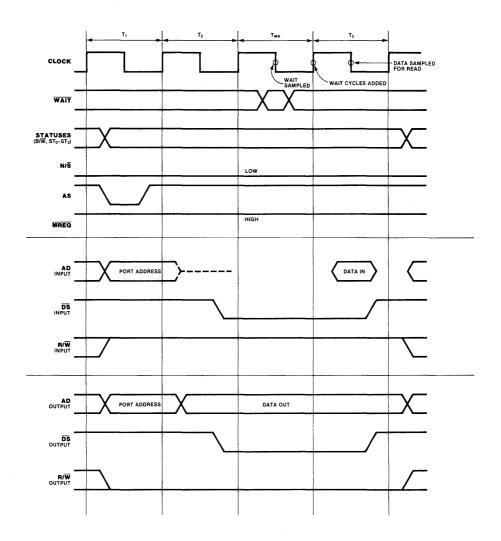

| 9.4               | CPU Control         9-3           Transactions         9-3           WAIT         9-4                                                                                                                                       |          | • • •                |

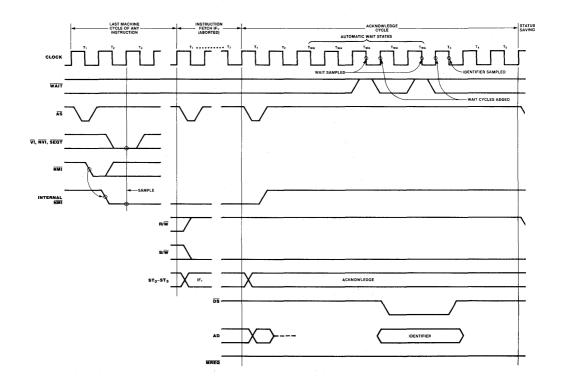

|                   | Memory Transactions       9-4         I/O Transactions       9-6         EPU Transfer Transactions       9-7         Interrupt/Trap Acknowledge Transactions       9-8                                                      |          |                      |

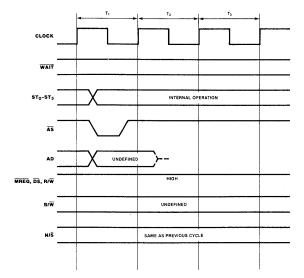

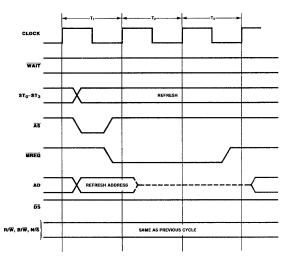

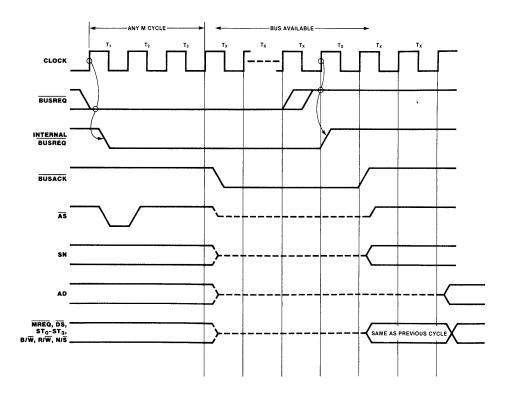

|                   | Internal Operations and Refresh Transactions       9-8         CPU and Extended Processing Unit Interaction       9-10         Requests       9-10         Interrupt/Trap Request       9-11         Bus Request       9-11 |          |                      |

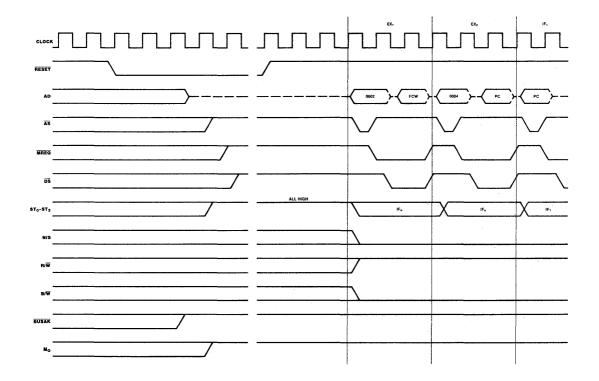

| 9.7               | Resource Request       9-12         Stop Request       9-12         Reset       9-13                                                                                                                                        |          |                      |

|                   | Hardware Information A-1                                                                                                                                                                                                    | į        | Appendix<br><b>A</b> |

|                   | Z8000 Family Specifications                                                                                                                                                                                                 |          | Appendix<br><b>B</b> |

| <br>-             | Programmers Quick Reference C-1                                                                                                                                                                                             |          | Appendix<br><b>C</b> |

|                   | Glossary of Terms                                                                                                                                                                                                           |          | Appendix<br><b>N</b> |

1

Zilog

### Chapter 1 **Z8000 Processor Overview**

1.1 Introduction

This chapter provides a summary description of the advanced architecture of the Z8000 Microprocessor, with special attention given to those architectural features that set the Z8000 CPU apart from its predecessors. A complete

1.2 General Organization

Zilog's Z8000 microprocessor has been designed to accommodate a wide range of applications, from the relatively simple to the large and complex. The Z8000 CPU is offered in two versions: the Z8001 and the Z8002. Each CPU comes with an entire family of support components: a memory management unit, a DMA controller, serial and parallel I/O controllers, and extended processing units-all compatible with Zilog's Z-Bus. Together with other Z8000 Family components, the advanced CPU architecture provides in an LSI microprocessor design the flexibility and sophisticated features usually associated with mini- or mainframe computers.

The major architectural features of the Z8000 CPU that enhance throughput and processing power are a general purpose register file, system and normal modes of operation, multiple addressing spaces, a powerful instruction set, numerous addressing modes, multiple stacks, sophisticated interrupt structure, a rich set of data types, separate I/O address spaces and, for the Z8001, a large address space and segmented memory addressing. Each of these features is treated in detail in the next section.

These architectural features combine to produce a powerful, versatile microprocessor. The

1.3 Architec-

The architectural resources of the Z8000 tural Features CPU include sixteen 16-bit general-purpose registers, seven data types ranging from bits to 32-bit long words and byte strings, eight userselectable addressing modes, and an instruction set more powerful than that of most minicomputers. The 110 distinct instruction types combine with the various data types and addressing modes to form a rich set of 414 instructions. Moreover, the set exhibits a high degree of regularity: more than 90% of the instructions can use any of five main addressing modes, with 8-bit byte, 16-bit word, and 32-bit long-word data types.

> The CPU generates status signals indicating the nature of the bus transaction that is being attempted; these can be used to implement sophisticated systems with multiple address spaces-memory areas dedicated to specific

overview of the architecture is provided in Chapter 2, with detailed descriptions of the various aspects of the processor provided in succeeding chapters.

benefits that result from these features are code density, compiler efficiency, support for typical operating system operations, and complex data structures. These topics are treated in Section 1.3.

The CPU has been designed so that a powerful memory management system can be used to improve the utilization of the main memory and provide protection capabilities for the system. This is discussed in Section 1.3.12. Although memory management is an optional capability-the Z8000 CPU is an extremely sophisticated processor without memory management-the CPU has explicit features to facilitate integrating an external memory management device into a Z8000 system configuration.

Finally, care has been taken to provide a very general mechanism for extending the basic instruction set through the use of extern al devices (called Extended Processing Units-EPUs). In general, an EPU is dedicated to performing complex and time-consuming tasks so as to unburden the CPU. Typical tasks for specialized EPUs include floating-point arithmetic, data base search and maintenance operations, network interfaces, and many others. This topic is treated in Section 1.5.

uses. The CPU also has two operating modes, system and normal, which can be used to separate operating system functions from normal application processes. I/O operations have have been separated from memory accesses, further enchancing the capability and integrity of Z8000-based systems, and a sophisticated interrupt structure facilitates the efficient operation of peripheral I/O devices. Moreover, the Extended Processing Unit (EPU) capability of the Z8000 allows the CPU to unload many time-consuming tasks onto external devices.

Special features of the Z8000 have been introduced to facilitate the implementation of multiple processor systems. In addition, the Z8001 CPU has a large, segmented addressing capability that greatly extends the applicability of microprocessors to large system applications.

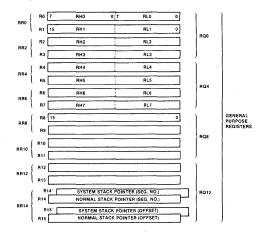

1.3 Architectural Features heart of the Z8000 CPU architecture is a file of (Continued) sixteen 16-bit general-purpose registers. These general-purpose registers give the Z8000 its power and flexibility and add to its regular instruction structure.

> General-purpose registers can be used as accumulators, memory pointers or index registers. Their major advantage is that the particular use to which they are put can vary during the course of a program as the needs of the program change. Thus, the general-purpose register file avoids the critical bottlenecks of an implied or dedicated register architecture, which must save and restore the contents of dedicated registers when more registers of a particular type are needed than are supplied by the processor.

> The Z8000 CPU register file can be addressed in several ways: as 16 byte registers (occupying one half of the file) or as 16 word registers or, by using the register pairing mechanism, as eight long-word (32-bit) registers or as four quadruple-word (64-bit) registers. Because of this register flexibility, it is not necessary (for example) for a Z8000 user to dedicate a 32-bit register to hold a byte of data. Registers can be used efficiently in the Z8000.

1.3.2 Instruction Set. A powerful instruction set is one of the distinguishing characteristics of the Z8000. The instruction set is one measure of the flexibility and versatility of a computer. Having a given operation implemented in hardware saves memory and improves speed. In addition, completeness of the operations available on a particular data type is frequently more important than additional, esoteric instructions, which are unlikely to affect performance significantly. The Z8000 CPU provides a full complement of arithmetic, logical, branch, I/O, shift, rotate, and string instructions. In addition, special instructions have been included to facilitate multiprocessing, multiple processor configurations, and typical high level language and operating system functions. The general philosophy of the instruction set is two-operand registermemory operations, which include as a special subset register-register operations. However, to improve code density, a few memorymemory operations are used for string manipulation. The two-address format reflects the most frequently occurring operations (such as  $A \leftarrow A + B$ ). Also, having one of the operands in a rapidly accessible generalpurpose register facilitates the use of intermediate results generated during a calculation.

The majority of operations deal with byte, word, or long-word operands, thereby providing a high degree of regularity. Also included in the instruction set are compact, one-word instructions for the most frequently used operations, such as branching short distances in a program.

The instruction set contains some notable additions to the standard repertoire of earlier microprocessors. The Load and Exchange group of instructions has been expanded to support operating system functions and conversion of existing microprocessor programs. The usual arithmetic instructions can now deal with higher-precision operands, while hardware multiply and divide instructions have also been added. The Bit Manipulation instructions can use calculated values to specify the bit position within a byte or word as well as to specify the position statically in the instruction. The Rotate and Shift instructions are considerably more flexible than those in previous microprocessors. The String instructions are useful in translating between different character codes. Multiple-processor configurations are supported by special instructions.

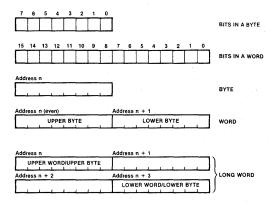

1.3.3 Data Types. Many data types are supported by the Z8000 architecture. A data type is supported when it has a hardware representation and instructions which directly apply to it. New data types can always be simulated in terms of basic data types, but hardware support provides faster and more convenient operations. The basic data type is the byte, which is also the basic addressable element. The architecture also supports the following data types: words (16 bits), long words (32 bits), byte strings, and word strings. In addition, bits are fully supported and addressed by number within a byte or word. BCD digits are supported and represented as two 4-bit digits in a byte. Arrays are supported by the Indexed addressing mode (see 1.3.4 and Chapter 5). Stacks are supported by the instruction set and by an external device (the Memory Management Unit, MMU) available with the Z8001.

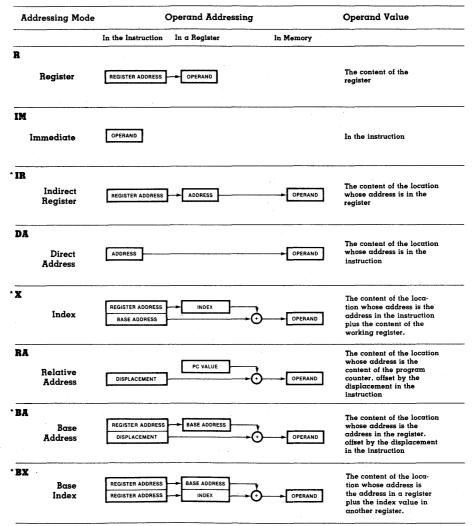

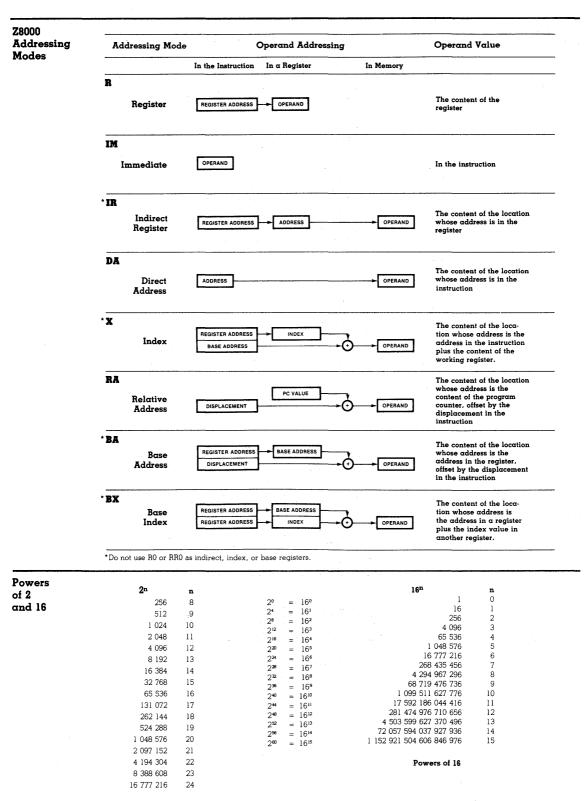

1.3.4 Addressing Modes. The addressing mode, which is the way an operand is specified in an instruction, determines how an address is generated. The Z8000 CPU offers eight addressing modes. Together with the large number of instructions and data types, they improve the processing power of the CPU. The addressing modes are Register, Immediate, Indirect Register, Direct Address, Index, Relative Address, Base Address, and Base Index. Several other addressing modes are implied by specific instructions, including autoincrement. The first five modes listed

1-2

1.3 Architec-(Continued)

above are basic addressing modes that are tural Features used most frequently and apply to most instructions having more than one addressing mode. (In the Z8002, Base Address and Index modes are identical, and in the Z8001. Base Addressing capabilites can be simulated with all instructions, using Based Addressing or the Memory Management Unit and the Direct or Indexed Addressing mode.)

> 1.3.5 Multiple Memory Address Spaces. The Z8000 CPU facilitates the use of multiple address spaces. When the Z8000 CPU generates an address, it also outputs signals indicating the particular internal activity which led to the memory request: instruction fetch, operand reference, or stack reference. This information can be used in two ways: to increase the memory space available to the processor (for example, by putting programs in one space and data in another); or to protect portions of the memory and allow only certain types of accesses (for example, by allowing only instruction fetches from an area designated to contain proprietary software). The Memory Management Unit (MMU) has been designed to provide precisely these kinds of protection features by using the CPUgenerated status information.

1.3.6 System/Normal Mode of Operation.

The Z8000 CPU can run in either system mode or normal mode. In system mode, all of the instructions can be executed and all of the CPU registers can be accessed. This mode is intended for use by programs performing operating system functions. In normal mode, some instructions may not be executed (e.g., I/O operations), and the control registers of the CPU are inaccessible. In general, this mode of operation is intended for use by application programs. This separation of CPU resources promotes the integrity of the system, since programs operating in normal mode cannot access those aspects of the CPU which deal with time dependent or system-interface events.

Programs executing in normal mode which have errors can always reproduce those errors for debugging purposes simply by re-executing the program with its original data. Programs using facilities available only in system mode may have errors due to timing considerations (e.g. based upon the frequency of disk requests and disk arm-position) that are harder to debug because these errors are not easily reproduced. Thus, the preferred method of program development is to partition the task into a portion which can be performed without those resources accessible only in system mode (which will usually be the bulk of the task) and a portion requiring system mode resources. The classic example of this partitioning comes from current minicomputer and mainframe systems: the operating system runs in system

mode and the individual users write their programs to run in normal mode.

To further support the system/normal mode dichotomy, there are two copies of the stack pointer-one for a system mode stack and another for a normal mode stack. These two stacks facilitate the task switching involved when interrupts or traps occur. To insure that the normal stack is free of system information, the information saved on the occurrence of interrupts or traps is always pushed on to the system stack before the new program status is loaded.

1.3.7 Separate I/O Address Spaces. The Z8000 Architecture distinguishes between memory and I/O spaces and thus requires specific I/O instructions. This architectural separation allows better protection and has more potential for extension. The use of separate I/O spaces also conserves the limited Z8002 data memory space. There are in fact two separate I/O address spaces: standard I/O and special I/O. The main advantage of these two spaces is to provide for two types of peripheral support chips-standard I/O peripherals and special I/O peripherals—devices such as the Z8010 Memory Management Unit that do not respond to standard I/O commands, but do respond to special I/O commands. A second advantage of these two spaces is that they allow 8-bit peripherals to attach to the low-order eight bits (standard I/O) or to the high-order eight bits (special I/O) of the processor Address/Data bus.

The increased speed requirements of future microprocessors are likely to be achieved by tailoring memory and I/O references to their respective, characteristic reference patterns and by using simultaneous I/O and memory referencing. These future possibilities require an architectural separation today. Memorymapped I/O is still possible, but loss of protection and lack of expandability are severe problems.

**1.3.8 Interrupt Structure.** The sophisticated interrupt structure of the Z8000 allows the processor to continue performing useful work while waiting for peripheral events to occur. The elimination of periodic polling and idling loops (typically used to determine when a device is ready to transmit data) increases the throughput of the system. The CPU supports three types of interrupts. A non-maskable interrupt represents a catastrophic event which requires immediate handling to preserve system integrity. In addition, there are two types of maskable interrupts: non-vectored interrupts and vectored interrupts. The latter provides an automatic call to separate interrupt processing routines for each peripheral, depending on the vector presented by the peripheral to the Z8000.

1.3 Architec-(Continued)

The Z8000 has implemented a priority system tural Features for handling interrupts. Vectored interrupts. have higher priority than non-vectored interrupts. This priority scheme allows the efficient control of many peripheral devices in a Z8000 system.

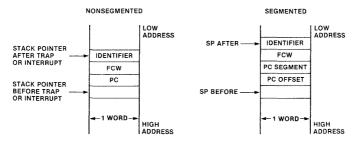

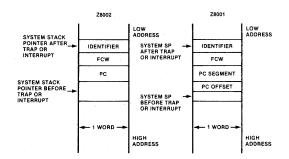

An interrupt causes information relating to the currently executing program (program status) to be saved on a special system stack with a code describing the reason for the switch. This allows recursive task switches to occur while leaving the normal stack undisturbed by system information. The program state to handle the interrupt (new program status) is loaded from a special area in memory, the program status area, designated by a pointer resident in the CPU.

The use of the stack and of a pointer to the program status area is a specific choice made to allow architectural compatibility if new interrupts or traps are added to the architecture.

1.3.9 Multi-Processing. The increase in microprocessor computing power that the Z8000 represents makes simple the design of distributed processing systems having many low-cost microprocessors running dedicated processes.

The Z8000 provides some basic mechanisms that allow the sharing of address spaces among different microprocessors. Large segmented address spaces and the support for external memory management make this possible. Also, a resource request bus is provided which, in conjunction with software, provides the exclusive use of shared critical resources. These mechanisms, and new peripherals such as the Z-FIO, have been designed to allow easy asynchronous communication between different CPUs.

1.3.10 Large Address Space for the Z8001.

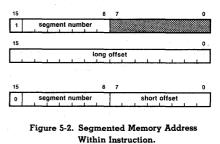

For many applications, a basic address space of 64K bytes is insufficient. A large address space increases the range of applications of a system by permitting large, complex programs and data sets to reside in memory rather than be partitioned and swapped into a small memory as needed. A large address space greatly simplifies program and data management. In addition, large address spaces and memories reduce the need for minimizing program size and permit the use of higher level languages. The segmented version of the Z8000 generates 23-bit addresses, for a basic address space of 8 megabytes (8M or 8,388, 608 bytes).

1.3.11 Segmented Addressing of the Z8001.

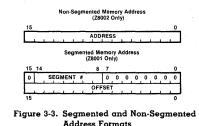

The segmented version of the Z8000 CPU divides its 23-bit addresses into a 7-bit seqment number and a 16-bit segment offset. The segment number serves as a logical name of a segment; it is not altered by the effective

address calculation (by indexing, for example). This corresponds to the way memory is typically used by a program—one portion of the memory is set aside to hold instructions, another for data. In a segmented address space, the instructions could reside in one segment (or several different modules in different segments), and each data set could reside in a separate segment. One advantage of segmentation is that it speeds up address calculation and relocation. Thus, segmentation allows the use of slower memories than linear addressing schemes allow. In addition, segments provide a convenient way of partitioning memory so that each partition is given particular access attributes (for example, read-only). The Z8000 approach to segmentation (simultaneous access to a large number of segments) is necessary if all the advantages of segmentation are to be realized. A system capable of directly accessing only, say, four segments would lack the needed flexibility and would be constrained by address space limitations.

1.3.12 Memory Management. Memory management consists primarily of dynamic relocation, protection, and sharing of memory. It offers the following advantages: providing a logical structure to the memory space that is independent of the actual physical location of data, protecting the user from inadvertent mistakes such as attempting to execute data, preventing unauthorized access to memory resources or data, and protecting the operating system from disruption by the users.

The addresses manipulated by the programmer, used by instructions, and output by the segmented Z8000 CPU are called logical addresses. The external memory management system takes the logical addresses and transforms them into physical addresses required for accessing the memory. This address transformation process is called relocation, which makes user software independent of the physical memory. Thus, the user is freed from specifying where information is actually located in the physical memory.

The segmented Z8000 CPU supports memory management both with segmented addressing and with program-status information. A segmented addressing space allows individual segments to be treated differently.

Program status information generated by the CPU permits an external memory management device to monitor the intended use of each memory access. Thus, illegal types of access can be suppressed and memory segments protected from unintended or unwanted modes of use. For example, system tables could be protected from direct user access. This added protection capability becomes more important as microprocessors are applied to large, complex tasks.

#### 1.4 Benefits of the Architecture

The features of the Z8000 Architecture combine to provide several significant benefits: improvements in code density, compiler efficiency, operating system support, and support for high level data structures.

1.4.1 Code Density. Code density affects both processor speed and memory utilization. Code compaction saves memory space—an especially important factor in smaller systems—and improves processor speed by reducing the number of instruction words that must be fetched and decoded. The Z8000 offers several advantages with respect to code density. The most frequently used instructions are encoded in single-word formats. Fewer instructions are needed to accomplish a given task and a consistent and regular architecture further reduces the number of instructions required.

Code density is achieved in part by the use of special "short" formats for certain instructions which are shown by statistical analysis to be most frequently used by assemblers. A "short offset" mechanism has also been provided to allow a 2-word segmented address to be reduced to a single word; this format may be used by assemblers and compilers.

The largest reduction in program size and increase in speed results from the consistent and regular structure of the architecture and from the more powerful instruction set—factors that substantially reduce the number of instructions required for a task. The architecture is more regular relative to preceding microprocessors because its registers, address modes, and data types can be used in a more orderly fashion. Any general-purpose register except RO can be specified as an acculumator, index register, or base register. With a few exceptions, all basic addressing modes can be used with all instructions, as can the various data types.

General-purpose registers do not have to be changed as often as registers dedicated to a specific purpose. This reduces program size, since frequent load and store operations are not required.

1.4.2 Compiler Efficiency. For microprocessor users, the transition from assembly language to high-level languages allows greater freedom from architectural dependency and improves ease of programming. However, rather than adapt the architecture to a particular highlevel language, the Z8000 was designed as a general-purpose microprocessor. (Tailoring a processor for efficiency in one language often leads to inefficiency in unrelated languages.) For the Z8000, language support has been provided through the inclusion of features designed to minimize typical compilation and code-generation problems. Among these features is the regularity of the Z8000 addressing modes and data types. Access to parameters and local variables on the procedure stack is supported by the "Index With Short Offset" addressing mode, as well as the Base Address and Base Index addressing modes. In addition, address arithmetic is aided by the Increment and Decrement instructions.

Testing of data, logical evaluation, initialization, and comparison of data are made possible by the instructions Test, Test Condition Codes, Load Immediate Into Memory, and Compare Immediate With Memory. Since compilers and assemblers frequently manipulate character strings, the instructions Translate, Translate And Test, Block Compare, and Compare String all result in dramatic speed improvements over software simulations of these important tasks. In addition, any register except R0 can be used as a stack pointer by the Push and Pop instructions.

**1.4.3 Operating System Support.** Interrupt and task-switching features are included to improve operating system implementations. The memory-management and compilersupport features are also quite important.

The interrupt structure has three levels: nonmaskable, non-vectored, and vectored. When an interrupt occurs, the program status is saved on the stack with an indication of the reason for this state-switching before a new program status is loaded from a special area of memory. The program status consists of the flag register, the control bits, and the program counter. The reason for the occurrence is encoded in a vector that is read from the system bus and saved on the stack. In the case of a vectored interrupt, the vector also determines a jump table address that points to the interrupt processing routine.

The inclusion of system and normal modes improves operating system organization. In the system mode, all operations are allowed; in the normal mode, certain system instructions are prohibited. The System Call instruction allows a controlled switch of mode, and the implementation of traps enforces these restrictions.

Traps result in the same type of program status-saving as interrupts: in both cases, the information saved is pushed on to a system stack that keeps the normal stack undisturbed. The Load Multiple instruction allows the contents of registers to be saved efficiently in memory or on the stack. Running programs can cause program status changes under direct software control with the Load Program Status instruction.

Finally, exclusion and serialization can be achieved with the "atomic" Test And Set instruction that synchronizes asynchronous cooperating processes.

#### 1.4 Benefit of 1.4.4 Support for Many Types of Data Struc-

the Architecture (Continued)

Facility

tures. A data structure is a logical organization of primitive elements (byte, word, etc.) whose format and access conventions are welldefined. Common data structures include arrays, lists, stacks, and strings. Since data structures are high-level constructs frequently used in programming, processor performance is significantly enchanced if the CPU provides mechanisms for efficiently manipulating them. The Z8000 offers such mechanisms.

In many applications, one of the most frequently encountered data structures is the array. Arrays are supported in the Z8000 by the index and the Base Index addressing mode and by segmented addressing. The Base Index addressing mode allows the use of pointers into an array (i.e., offsets from the array's starting address). Segmented addressing allows an array to be assigned to one segment, which can be referenced simply by segment number.

Lists occur more frequently than arrays in business applications and in general data processing. Lists are supported by Indirect Register and Base Address addressing modes. The Base Index addressing mode is also useful for more complex lists.

Stacks are used in all applications for nesting of routines, block structured languages, and interrupt handling. Stacks are supported by the Push and Pop instructions, and multiple stacks may be implemented based on the general-purpose registers of the Z8000. In

1.5 Extended The Z8000 architecture has a mechanism for Instruction extending the basic instruction set through the use of external devices. Special opcodes have been set aside to implement this feature. When the CPU encounters an instruction with these opcodes in its instruction stream, it will perform any indicated address calculation and data transfer; otherwise, it will treat the "extended instruction" as being executed by the external device. Fields have been set aside in these extended instructions which can be interpreted by external devices (Extended Pro-

1.6 Summary The architectural sophistication of the Z8000 microprocessor is on a level comparable with that of the minicomputer. Features such as large address spaces, multiple memory spaces, segmented addresses, and support for multiple processors are beyond the capabilities of the traditional microprocessor. The benefits of this

addition, two hardware stack pointers are used to assign separate stacks to system and normal. operating modes, thereby further supporting the separation of system and normal operating environments discussed earlier.

Byte and word strings are supported by the Translate and Translate And Test instructions. Decimal strings use the Decimal Adjust instruction to do decimal arithmetic on strings of BCD data, packed two characters per byte. The Rotate Digit instructions also manipulate 4-bit data.

#### 1.4.5 Two CPU Versions: Z8001 and Z8002.

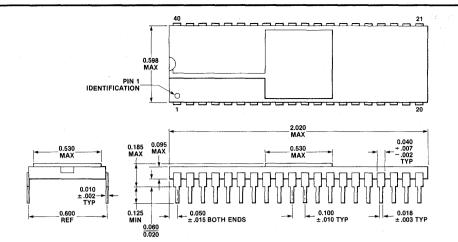

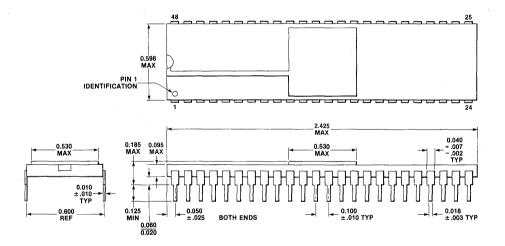

The Z8000 CPU is offered in two versions: the Z8001 48-pin segmented CPU and the Z8002 40-pin nonsegmented CPU. The main difference between the two is addressing range. The Z8001 can directly address 8M bytes of memory; the Z8002 directly addresses 64K bytes. The Z8001 has a non-segmented mode of operation which permits it to execute programs written for the Z8002.

Not all applications require the large address space of the Z8001; for these applications the Z8002 is recommended. Moreover, many multiple-processor systems can be implemented with one Z8001 and several Z8002s, instead of exclusively using Z8001s. Since the same assembler generates code for both CPUs. users can buy only the power they require without having to worry about software incompatibility between processors.

cessing Units-EPUs) as opcodes. Thus, by using appropriate EPUs, the instruction set of the Z8000 can be extended to include specialized instructions.

In general, an EPU is dedicated to performing complex and time-consuming tasks in order to unburden the CPU. Typical tasks suitable for specialized EPUs include floatingpoint arithmetic, data base search and maintenance operations, network interfaces, graphics support operations-a complete list would include most areas of computing.

architecture-code density, compiler support, and operating system support-greatly enhance the power and versatility of the CPU. The CPU features that support an external memory management system also enhance the CPU's applicability to large system environments.

Zilôg

2

|                                           |  |  | 1. Marca and |  |

|-------------------------------------------|--|--|--------------|--|

|                                           |  |  |              |  |

| 1. A. |  |  |              |  |

|                                           |  |  |              |  |

|                                           |  |  |              |  |

### Chapter 2 Architecture

| 2.1 Intro-<br>duction       | This chapter provides an overview of the<br>Z8000 CPU architecture. The basic hardware,<br>operating modes and instruction set are all<br>described. Differences between the two ver-<br>sions of the Z8000 (the nonsegmented Z8002                                                                                                                                                                                                                          | and the segmen<br>appropriate. Ma<br>are also treated<br>chapters of the                                                                                                                                                          |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

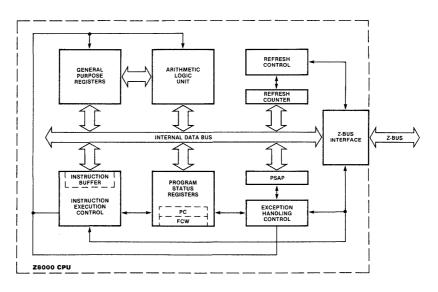

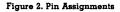

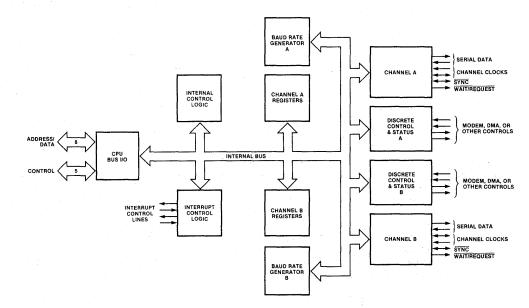

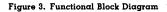

| 2.2 General<br>Organization | <ul> <li>Figure 2.1 contains a block diagram that shows the major elements of the Z8000 CPU, namely:</li> <li>A 16-bit internal data bus, which is used to move addresses and data within the CPU.</li> <li>A Z-Bus interface, which controls the interaction of the CPU with the outside world.</li> <li>A set of 16 general-purpose registers, which is used to contain addresses and data.</li> <li>Four special-purpose registers, which con-</li> </ul> | <ul> <li>An exception<br/>cesses interru</li> <li>A refresh con<br/>refresh cycles</li> <li>Each of these<br/>following section<br/>common to both<br/>CPU. The difference<br/>of the Z8000 are<br/>bits in the addree</li> </ul> |  |

- Four special-purpose registers, which control the CPU operation.

- An Arithmetic and Logic Unit, which is used for manipulating data and generating addresses.

- An instruction execution control, which fetches and executes Z8000 instructions.

and the segmented Z8001) are noted where appropriate. Most of the subjects covered here are also treated with greater detail in later chapters of the manual.

- An exception-handling control, which processes interrupts and traps.

- A refresh control, which generates memory refresh cycles.

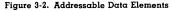

Each of these elements is explained in the following sections. All of the elements are common to both the Z8001 CPU and the Z8002 CPU. The differences between the two versions of the Z8000 are derived from the number of bits in the addresses they generate. The Z8002 always generates a 16-bit linear address, while the Z8001 always generates a 23-bit segmented address (that is, an address composed of a 7-bit segment number and a 16-bit offset).

Figure 2-1. Z8000 CPU Functional Block Diagram

2.2 General Organization (Continued)

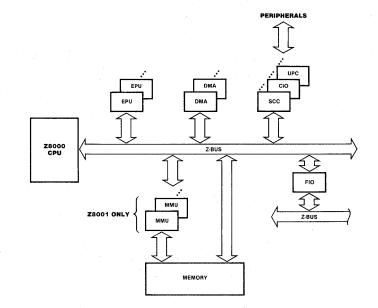

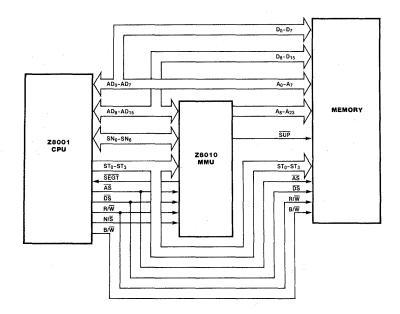

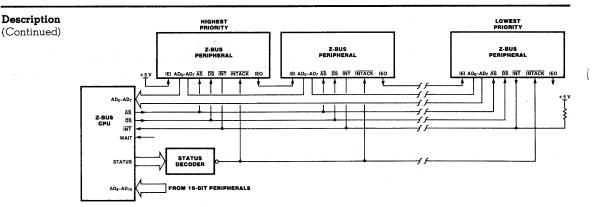

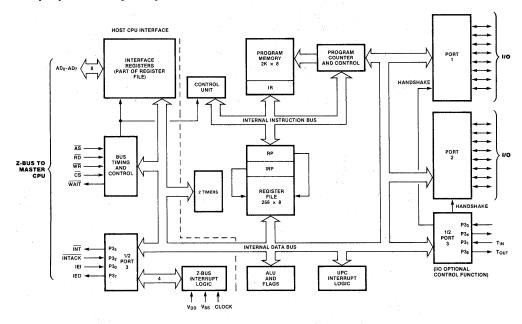

Figure 2.2 gives a system-level view of the Z8000. It is important to realize that the Z8000 CPU comes with a whole family of support components. The Z8000 Family has been designed to allow the easy implementation of powerful systems. The major elements of such a system might include:

- The Z-Bus, a multiplexed address/data shared bus that links the components of the system.

- A Z8001 or Z8002 CPU.

- One or more Extended Processing Units (EPUs), which are dedicated to performing specialized, time-consuming tasks.

- A memory sub-system, which in Z8001 systems can include one or more Memory

Management Units (MMUs) that offer sophisticated memory allocation and protection features.

- One or more Direct Memory Access (DMA) controllers for high-speed data transfers.

- A large number of possible peripheral devices interfaced to the Z-Bus through Universal Peripheral Controllers (UPCs), Serial Communication Controllers (SCCs), Counter-Timer and Parallel I/O Controllers (CIOs) or other Z-Bus peripheral controllers.

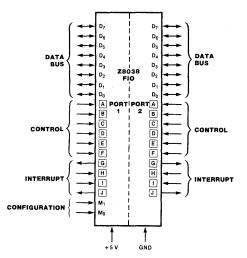

- One or more FIFO I/O Interface Units (FIOs) for elastic buffering between the CPU and another device, such as another CPU in a distributed processing system.

Figure 2-2. Z8000 System Configuration

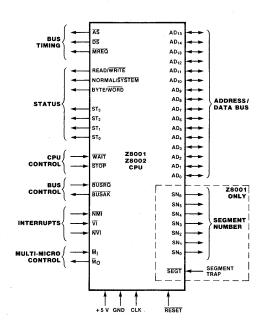

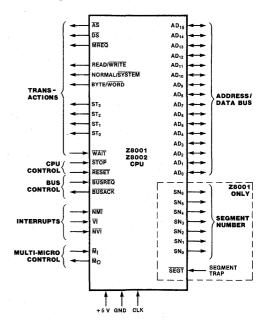

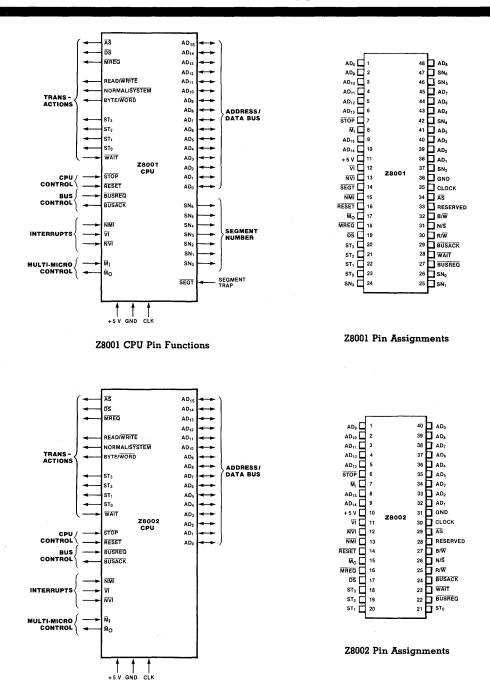

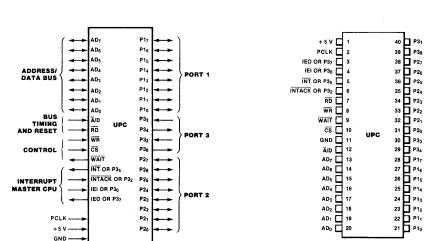

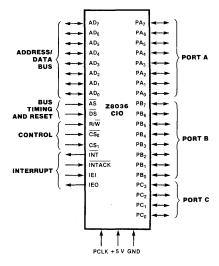

Figure 2.3 shows the Z8000 pins grouped according to function. The Z8001 is packaged in a 48-pin DIP and the Z8002 is packaged in a 40-pin DIP. The eight additional pins on the Z8001 are the seven segment-number lines and the segment trap. Except for those eight, all pins on the two CPU versions are identical.

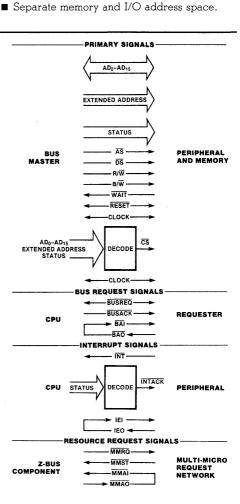

The Z8000 is a Z-Bus CPU; thus, activity on the pins is governed by the Z-Bus protocols (see The Z-Bus Summary). These protocols specify two types of activities: transactions, which cover all data movement (such as memory references or I/O operations), and requests, which cover interrupts and requests for bus or resource control. The following is a brief overview of the Z8000 pin functions; complete descriptions are found in Chapter 9.

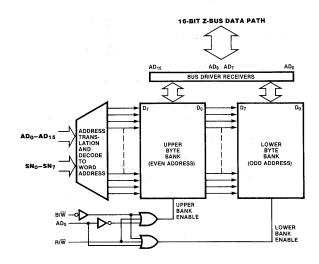

**2.3.1 Address/Data Lines.** These 16 lines alternately carry addresses and data. The addresses may be those of memory locations or I/O ports. The bus timing signal lines described below indicate what kind of information the Address/Data lines are carrying.

**2.3.2 Segment Number (Z8001 only).** These seven lines encode the addresses of up to 128 relocatable memory segments. The segment signals become valid before the address offset signals, thus supporting address relocation by the memory managment system.

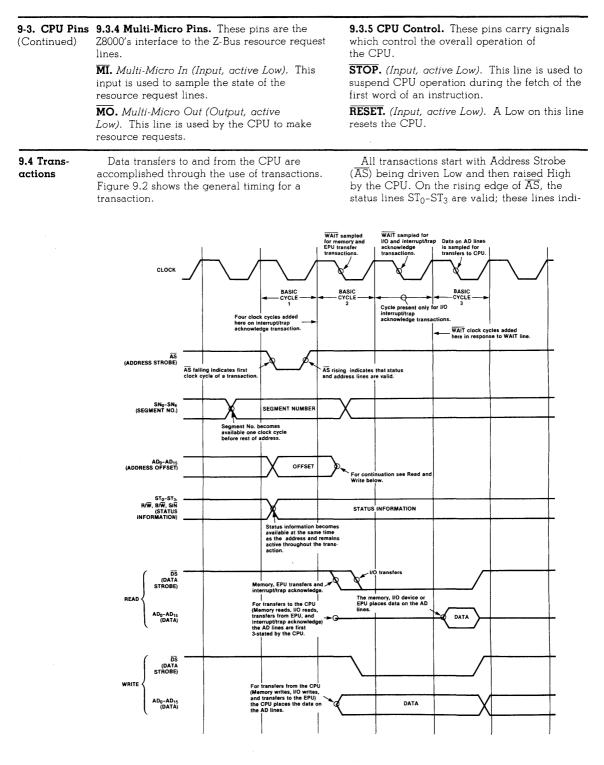

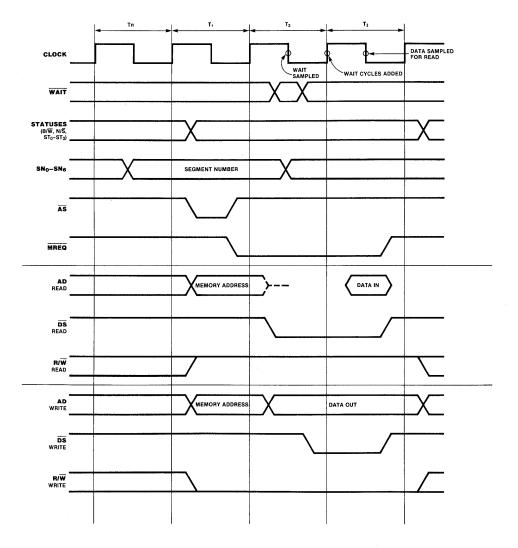

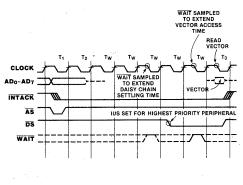

**2.3.3 Bus Timing.** These three lines include Address Strobe ( $\overline{AS}$ ), Data Strobe ( $\overline{DS}$ ) and Memory Request ( $\overline{MREQ}$ ). They are used to signal the beginning of a bus transaction and

| ST3-ST0         | Definition                         |

|-----------------|------------------------------------|

| 0000            | Internal operation                 |

| 0001            | Memory refresh                     |

| 0010            | I/O reference                      |

| 0011            | Special I/O reference              |

| 0100            | Segment trap acknowledge           |

| 0101            | Non-maskable interrupt acknowledge |

| 0110            | Non-vectored interrupt acknowledge |

| 0111            | Vectored interrupt acknowledge     |

| 1000            | Data memory request                |

| 1001            | Stack memory request               |

| 1010            | Data memory request (EPU)          |

| 1011            | Stack memory request (EPU)         |

| 1100            | Instruction space access           |

| 1101            | Instruction fetch, first word      |

| 1110            | EPA Transfer                       |

| $1 \ 1 \ 1 \ 1$ | Reserved                           |

Table 2.1 Status Line Codes

Figure 2-3. Z8000 Pin Functions

to determine when the multiplexed Address/ Data Bus holds addresses or data. The Memory Request signal can be used to time control signals to a memory system.

**2.3.4 Status.** These lines function to indicate the kind of transaction on the bus  $(ST_0-ST_3)$ , whether it is a read or write  $(R/\overline{W}, where High is Read and Low is Write)$ , whether it is on byte or word data  $(B/\overline{W}, High = byte, Low = word)$ , and whether the CPU is operating in normal mode or system mode  $(N/\overline{S}, High = normal, Low = system)$ . The  $ST_0-ST_3$  lines also encode additional characteristics of the bus transactions, as Table 2.1 shows. The availability of status information defining the type of bus transaction in advance of data transmission allows bidirectional drivers and other external hardware elements to be enabled before data is transferred.

Interface (Continued)

2.3 Hardware 2.3.5 CPU Control. These inputs allow external devices to delay the operation of the CPU. The WAIT line, when active (Low), causes the CPU to idle in the middle of a bus transaction, taking extra clock cycles until the WAIT line goes inactive; it is typically used by memory or I/O peripherals which operate more slowly than the CPU. The Stop (STOP) line halts internal CPU operation when the first word of an instruction (or the second word of an EPA instruction) has been fetched. This signal is useful for single-step instruction execution during debugging operations and for enabling Extended Processing Units to halt the CPU temporarily.

> 2.3.6 Bus Control. These lines provide the means for other devices, such as direct memory access (DMA) controllers, to gain exclusive use of the system bus, i.e., the signal lines that are common to several devices in a system. The external device requesting control of the bus inputs a bus request (BUSREQ); the CPU responds with a bus acknowledge (BUSACK) after three-starting, or electrically neutralizing, the Address/Data Bus, Bus Timing lines, Status lines, and Control lines. The Z-Bus allows a daisy chain to be used to

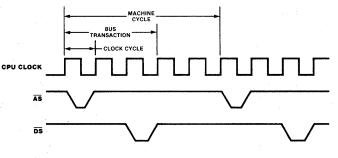

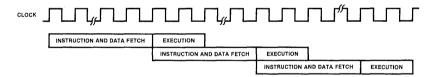

Figure 2.4 shows the three basic timing periods of the Z8000; a clock cycle, a bus transaction, and a machine cycle. A clock cycle (sometimes called a T-state) is one cycle of the CPU clock, starting with a rising edge. A bus transaction covers a single data movement on the CPU bus and will last for three or

more clock cycles, starting with a falling edge

enforce a priority among several external devices.

2.3.7 Interrupts. Three interrupt inputs are provided: non-maskable interrupts (NMI), vectored interrupts (VI) and non-vectored interrupts (NVI). These permit external devices to suspend the CPU's execution of its current program and begin executing an interrupt service routine.

### 2.3.8 Segment Trap Request (Z8001

only). This input to the CPU is used by an external memory-management system to indicate that an illegal memory access has been attempted.

2.3.9 Multi-Micro Control. The Multi-Micro In (MI) and Multi-Micro Out (MO) lines are used in conjunction with instructions such as MSET and MREQ to coordinate multiple-CPU systems. They allow exclusive use by one CPU of a shared resource in a multiple-CPU system.

2.3.10 System Inputs. The four inputs shown at the bottom of Figure 3 include +5 V power, ground, a single-phase clock signal and a CPU reset. The reset function is described in Chapter 7.

of  $\overline{\text{AS}}$  and ending with a rising edge of  $\overline{\text{DS}}$ . A machine cycle covers one basic CPU operation and always starts with a bus transaction. A machine cycle can extend beyond the end of a transaction by an unlimited number of clock cycles. Appendix A contains a complete description of Z8000 timing.

2.5 Äddress Spaces

2.4 Timing

The Z8000 supports two main address spaces corresponding to the two different kinds of locations that can be addressed:

- Memory Address Space. This consists of the addresses of all locations in the main memory of the computer system.

- I/O Address Space. This consists of the addresses of all I/O ports through which peripheral devices are accessed.

For more information on address spaces, consult Chapter 3.

2.5.1 Memory Address Space. Memory address space can be further subdivided into Program Memory address space, Data Memory address space, and Stack Memory address space, each for both normal and system modes.

The particular space addressed is determined by the external circuitry from the code appearing at the CPU's output status pins (ST<sub>0</sub>-ST<sub>3</sub>) and the state of the Normal/System signal (N/S pin). Data memory reference, stack memory reference, and program memory

2.5 Address Spaces (Continued) reference each correspond to a different status code at the ST<sub>0</sub>-ST<sub>3</sub> outputs, allowing three address spaces to be distinguished for each of two operating modes, giving six address spaces in all. Each of the six address spaces has a range as great as the addressing ability of the processor. For the nonsegmented Z8002, each address space can have up to 64K bytes, giving a potential total system capacity of 384K bytes of directly addressable memory. The segmented Z8001, on the other hand, provides up to 48M bytes of directly addressable memory due to the 23-bit segmented addresses.

Segmentation is a means of partitioning memory into variable-size segments so that a variety of useful functions may be implemented, including:

- Protection mechanisms that prevent a user from referencing data belonging to others, attempting to modify read-only data or overflowing a stack.

- Virtual memory, which permits a user to write functioning programs under the assumption that the system contains more memory than is actually available.

- Dynamic relocating which allows the placement of blocks of data in physical memory

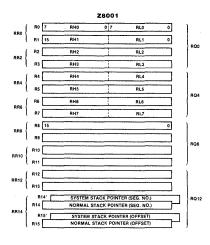

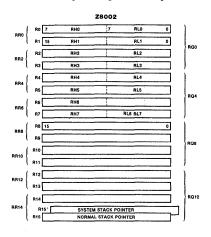

2.6 General-Purpose Registers The Z8000 CPU contains 16 general-purpose registers, each 16 bits wide. Any generalpurpose register can be used for any instruction operand (except for minor exceptions described at the beginning of Chapter 5).

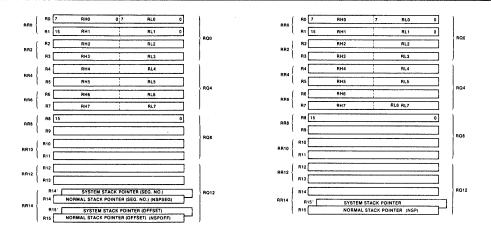

Figure 2.5 shows these general-purpose registers. They allow data formats ranging from bytes to quadruple words. The word registers are specified in assembly-language statements as R0 through R15. Sixteen byte registers,

independently of user addresses, allowing better management of the memory resources and sharing of data and programs.

The signals provided on the segmented Z8001 CPU assist in implementing these features, although additional software and external circuitry (such as the Z8010 MMU) are generally required to take full advantage of them. Chapter 3 contains an extensive discussion of segmentation and the Z8001.

**2.5.2 I/O Address Space.** I/O addresses are represented as 16-bit words for both the Z8001 and Z8002.

There are two I/O address spaces, Standard I/O and Special I/O, which are both separate from the memory address space. Each I/O space is accessed through a separate set of I/O instructions, which can be executed only when the CPU is operating in system mode.

Standard I/O instructions transfer data between the CPU and peripherals and Special I/O instructions transfer data to or from external CPU support circuits such as the Z8010 MMU. Access to Standard or Special I/O space is distinguished by the status lines  $(ST_0-ST_3)$ .

RH0-RL7, which may be used as accumulators, overlap the first eight word registers. Register grouping for larger operands includes eight double-word (32-bit) registers, RR0-RR14, and four quad-word registers, RQ0-RQ12, which are used by a few instructions such as Multiply, Divide, and Extend Sign.

As Figure 2.5 illustrates, the CPU has two hardware stack pointers, one dedicated to each of the two basic operating modes, system and

2.6 General-Purpose Registers (Continued) normal. The segmented Z8001 uses a two-word stack pointer for each mode (R14'/R15' or R14/R15), whereas the nonsegmented Z8002 uses only one word for each mode (R15' or R15).

The system stack pointer is used for saving status information when an interrupt or trap occurs and for supporting calls in system

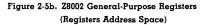

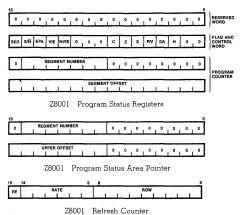

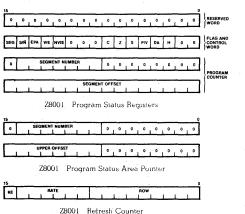

2.7 Special-Purpose Registers In addition to the general-purpose registers, there are special-purpose registers. These include the Program Status registers, the Program Status Area Pointer, and the Refresh Counter; they are illustrated for both CPU versions in Figure 2.6. Each register can be manipulated by software executing in system mode, and some are modified automatically by certain operations.

**2.7.1 Program Status Registers.** These registers include the Flag and Control Word (FCW) and the Program Counter (PC). They are used to keep track of the state of an executing program.

In the nonsegmented Z8002, the Program Status registers consist of two words: one each for the FCW and the PC. In the segmented Z8001, there are four words: one reserved word, one word for the FCW and two words for the segmented PC.

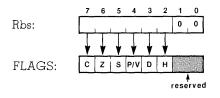

The low-order byte of the Flag and Control Word (FCW) contains the six status flags, from which the condition codes used for control of program looping and branching are derived. The six flags are:

**Carry (C)**, which generally indicates a carry out of the high-order bit position of a register being used as an accumulator.

**Zero (Z)**, which is generally used to indicate that the result of an operation is zero.

**Sign (S)**, which is generally used to indicate that the result of an operation is a negative number.

mode. The normal stack pointer is used for subroutine calls in user programs. In normalmode operation only the normal stack pointer is accessible. In system mode, the normal stack pointer can be directly accessed as a special control register. The normal mode stack pointer can be assessed as a special control register.

**Parity/Overflow (P/V)**, which is generally used to indicate either even parity (after logical operations on byte operands) or overflow (after arithmetic operations).

**Decimal-Adjust (D)**, which is used in BCD arithmetic to indicate the type of instruction that was executed (addition or subtraction).

Half Carry (H), which is used to convert the binary result of a previous decimal addition or subtraction into the correct decimal (BCD) result.

Section 6.3 provides more detail on these flags.

The control bits, which occupy the highorder byte of the FCW, are used to enable various interrupts or to control CPU operating modes. The control bits are:

Non-Vectored Interrupt Enable (NVIE), Vectored Interrupt Enable (VIE). These bits determine whether or not the CPU will accept nonvectored or vectored interrupts (see Section 2.13).

System/Normal Mode  $(S/\overline{N})$ . When this bit is set to one, the CPU is operating in system mode; when cleared to zero, the CPU is in normal mode (see Section 2.8). The CPU output status line  $(N/\overline{S} \text{ pin})$  is the complement of this bit.

**Extended Processor Architecture (EPA) Mode.** When this bit is set to one, it indicates that the system contains Extended Processing Units, and hence extended instructions

Z8002 Refresh Counter

Figure 2-6. CPU Special Registers

2.7 Special Purpose Registers (Continued) encountered in the CPU instruction stream are executed (see Section 2.12). When this bit is cleared to zero, extended instructions are trapped for software emulation.

Segmentation Mode (SEG). This bit is implemented only in the Z8001; it is always cleared in the nonsegmented Z8002. When set to one, the CPU is operating in segmented mode, and when cleared to zero, the CPU is operating in nonsegmented mode (see Section 2.8).

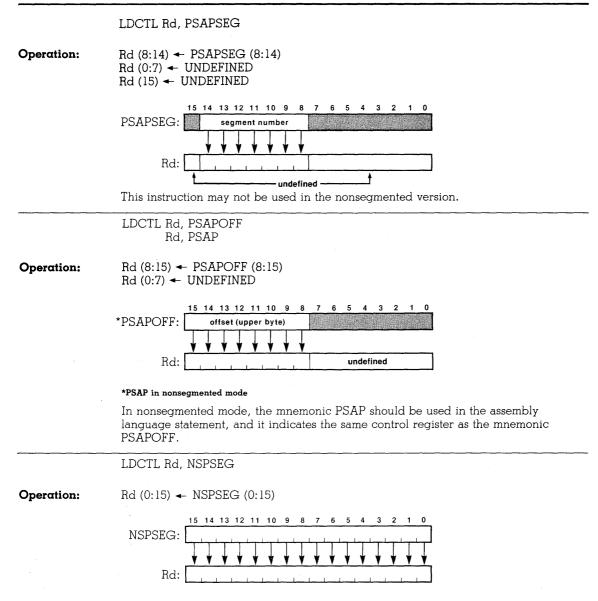

#### 2.7.2 Program Status Area Pointer

**(PSAP).** The Program Status Area Pointer points to an array of program status values (FCWs and PCs) in main memory called the Program Status Area. New Program Status reg-

2.8 Instruction In the normal course of events, the Z8000 Execution CPU will spend most of its time fetching instructions from memory and executing them. This process is called the *running state* of the CPU. The CPU also has two other states that it occasionally enters. Stop/Refresh State. This is really one state, although it may be entered in two different ways: either automatically for a periodic memory refresh; or when the STOP line is activated. In this state, program execution is temporarily suspended and the CPU makes use of the Refresh Counter to generate refreshes. For more information, consult Chapter 8.

**Bus-Disconnect State.** This is the state the CPU enters when the DMA, or some other bus requester, takes over the bus. Program execution is suspended and the CPU disconnects itself from the bus.

While the CPU is in the running state, it can either be handling interrupts or executing

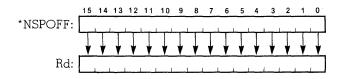

ister values are fetched from this area when an interrupt or trap occurs. As shown in Figure 2.6, the PSAP comprises either one word (nonsegmented Z8002) or two words (segmented Z8001); for either configuration, the lower byte of the pointer must be zero. Refer to Chapter 7 for more details about the Program Status Area and its layout.

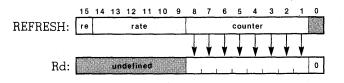

**2.7.3 Refresh Counter.** The CPU contains a programmable counter that can be used to refresh dynamic memory automatically. The refresh counter register consists of a 9-bit row counter, a 6-bit rate counter and an enable bit (Figure 2.6). Refer to Chapter 8 for details of the refresh mechanism.

instructions. If it is executing instructions, the Z8000 can be in the system or normal execution mode. In system mode, privileged instructions (such as those which perform I/O) can be executed; in normal mode they cannot. This dichotomy allows the creation of operating system software, which controls CPU resources and is protected from application program action.

In addition, the CPU will be in either segmented or nonsegmented mode. In segmented mode, which is available only on the Z8001, the program uses 23-bit segmented addresses for memory accesses; in nonsegmented mode, which is available on both CPUs, the program uses 16-bit nonsegmented addresses for memory accesses.

While executing instructions, the mode of the CPU is controlled by bits in the FCW (Section 2.8). While handling interrupts, the CPU is always in system mode and, for the Z8001, in segmented mode.

**2.9 Instructions** The Z8000 instruction set contains over 400 different instructions which are formed by combining the 110 distinct instruction types (opcodes) with the various data types and addressing modes. The complete set is divided into the following groups:

Load and Exchange for register-to-register and register-to-memory operations, including stack management.

**Arithmetic** for arithmetic operations, including multiply and divide, on data in either registers or memory. Compare, increment, and decrement functions are included.

**Logical** for Boolean operations on data in registers or memory.

**Program Control** for program branching (conditional or unconditional), calls, and returns.

**Bit Manipulation** for setting, resetting and testing individual bits of bytes or words in registers or memory.

Rotate and Shift for bytes, words, or, for shifts only, long words within registers.

**Block Transfer and String Manipulation** for automatic memory-to-memory transfers of data blocks or strings, including compare and translate functions.

**Input/Output** for transfers of data between I/O ports and memory or registers.

**Extended** for operations involving Extended Processing Units.

**CPU Control** for accessing special registers, controlling the CPU operating state, synchronizing multiple-processor operation, enabling/ disabling interrupts, mode selection, and memory refresh.

Chapter 6 contains details on the full instruction set.

2.9 Instructions (Continued)

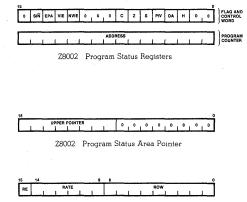

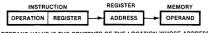

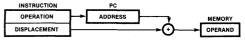

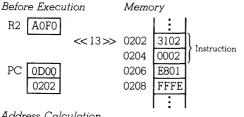

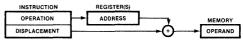

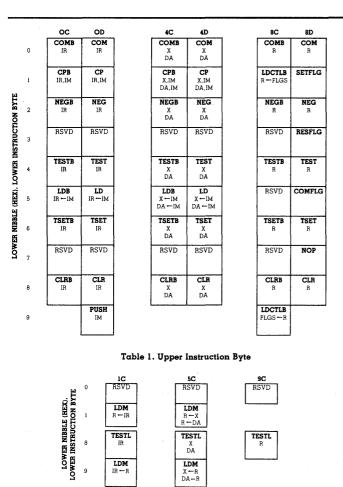

2.9.1 Instruction Formats. Formats of the instructions are shown in Figure 2.7. The two most significant bits in the instruction word determine whether the compact instruction format (A) or the general instruction format (B) is used. Compact formats encode the four most frequently used instructions into single words, thereby saving on instruction-memory usage and increasing execution speed. As long as the two most significant bits are not logic ones, the general format applies. In the general format, the two most significant bits in conjunction with the source-register field are sufficient for specifying any of the five main addressing modes. Source and destination fields are four bits wide for addressing the 16 generalpurpose registers.

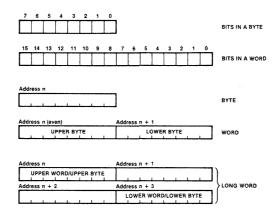

2.10 Data Types

2.11

The Z8000 supports manipulation of eight data types. Five of these have fixed lengths; the other three have lengths that can vary dynamically. Each data type is supported by a number of instructions which operate upon it. directly. These data types are:

Bit

- Signed and unsigned byte, word, long word, or quadruple word binary integer

- Byte or word-length logical value

- Word (nonsegmented) or long word (segmented) address

The information included in Z8000 instruc-Addressing tions consists of the function to be performed. Modes the type and size of data elements to be manipulated, and the location of the data elements. Locations are designated using one of the following eight addressing modes:

> Register Mode. The data element is located in one of the 16 general-purpose registers.

> Immediate Mode. The data element is located in the instruction.

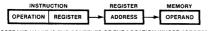

> Indirect Register Mode. The data element can be found in the location whose address is in a register.

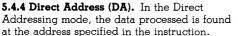

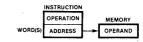

Direct Address Mode. The data element can be found in the location whose address is in the instruction.

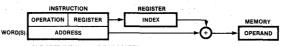

Index Mode. The data element can be found

An important feature of the Z8000 CPU 2.12 Extended Processing architecture is the Extended Processing Architecture Architecture (EPA) facility. This facility provides a mechanism by which the basic instruction set of the CPU can be extended via external devices, called Extended Processing Units (EPUs). A special set of instructions, called extended instructions, is used to control this feature. When the CPU encounters one of

| LDI                | 3 1 1                                            | 0'0 7                 |        | 1-1-1   | n intri     |  |  |

|--------------------|--------------------------------------------------|-----------------------|--------|---------|-------------|--|--|

|                    | CALL RE                                          | LATIVE                |        |         |             |  |  |

| CA                 |                                                  | 0 1                   |        | offset  |             |  |  |

| JUMP RELATIVE      |                                                  |                       |        |         |             |  |  |

| JR                 | 1 1                                              | 1 0 cc                |        |         | fset        |  |  |

|                    | DECREM                                           | ENT AND JUM           | ON N   | ON-ZERO |             |  |  |

|                    |                                                  | 1 1 1 1               | - T.   |         |             |  |  |

| DJM                |                                                  | N FORMAT (F           |        |         | fiset       |  |  |

|                    | INSTRUCTIC                                       | 1 1 r<br>DN FORMAT (F |        |         | 11561       |  |  |

| GENERAL<br>BYTE OR | INSTRUCTIO                                       | sing                  | IRST W | ORD)    | 1 1 1 1     |  |  |

| GENERAL            | INSTRUCTIC<br>address<br>mode                    | opcode                |        |         | destination |  |  |

| GENERAL<br>BYTE OR | INSTRUCTIC                                       | opcode                | IRST W | ORD)    | 1 1 1 1     |  |  |

| GENERAL<br>BYTE OR | INSTRUCTIC<br>address<br>mode<br>address<br>mode | opcode                | IRST W | ORD)    | 1 1 1 1     |  |  |

- Unsigned byte decimal integer

- Dynamic-length string of byte data

- Dynamic-length string of word data

- Dynamic-length stack of word data

Bits can be manipulated in registers or memory. Binary and decimal integers and logical values can be manipulated in registers only, although operands can be fetched directly from memory. Addresses are manipulated only in registers, and strings and stacks are manipulated only in memory.

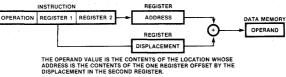

in the location whose address is the sum of the contents of a 16-bit index value in a register and an address in the instruction.

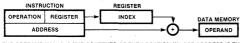

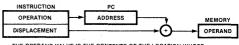

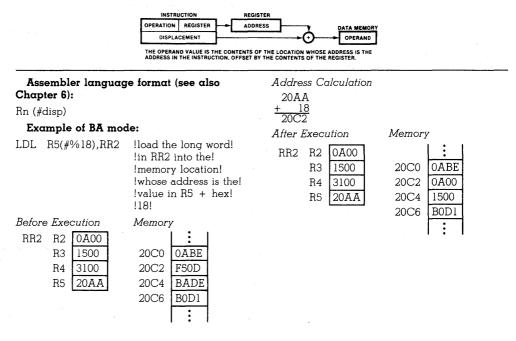

Relative Address Mode. The data element can be found in the location whose address is the sum of the contents of the program counter and a 16-bit displacement in the instruction.

Base Address Mode. The data element can be found in the location whose address is the sum of a base address in a register and a 16-bit displacement in the instruction.

Base Index Mode. The data element can be found in the location whose address is the sum of a base address in one register and an index value in another register.

Chapter 5 defines and illustrates the eight addressing modes.

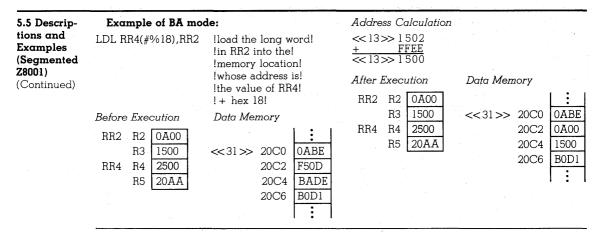

these extended instructions in its instruction stream, it will either trap to a software trap handler to process the instruction or it will perform the data transfer portion of the instruction (leaving the data manipulation part of the instruction to the EPU). Whether the CPU traps or transfers data depends on the setting of the EPA bit in the FCW.