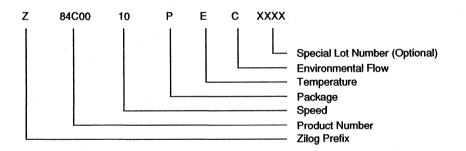

# Z80 FAMILY DATA BOOK JANUARY 1989

Z80 FAMILY DATA BOOK

January 1989

**Product Specification**

# Z80<sup>®</sup> Family Data Book

# Z80® Family Data Book Table of Contents

# **Product Specifications**

| Zilog Z80 Family                               | . 1  |

|------------------------------------------------|------|

| Z8400/Z84C00 NMOS/CMOS Z80 CPU                 | . 3  |

| Z84C01 Z80 CPU with Clock Generator/Controller | . 25 |

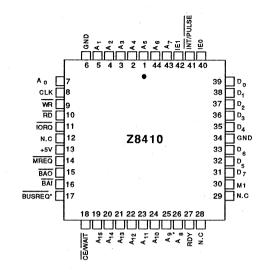

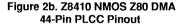

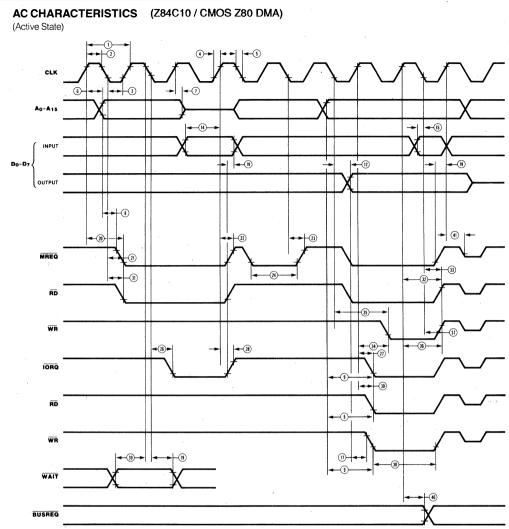

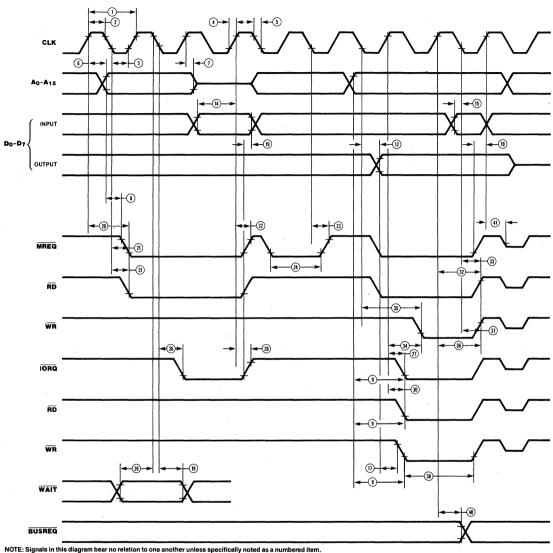

| Z8410/Z84C10 NMOS/CMOS Z80 DMA                 | 57   |

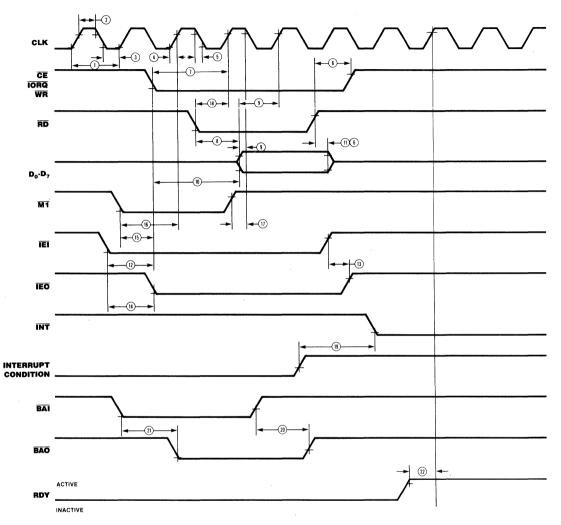

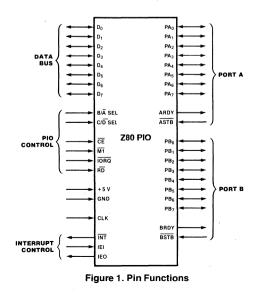

| Z8420/Z84C20 NMOS/CMOS Z80 PIO                 | 81   |

| Z8430/Z84C30 NMOS/CMOS Z80 CTC                 | . 97 |

| Z8440/1/2/4 Z84C40/1/2/3/4 NMOS/CMOS Z80 SIO   | .113 |

| Z8470 Z80 DART                                 | .137 |

| Z84C80 CMOS Z80 GLU                            | .149 |

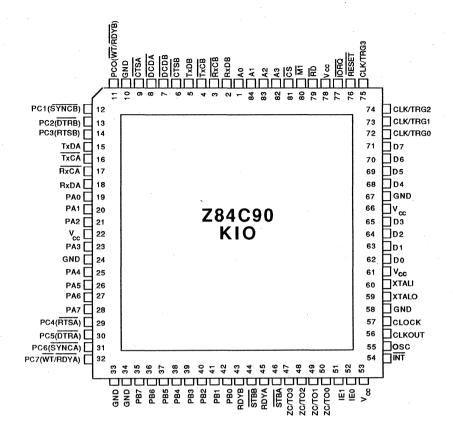

| Z84C90 CMOS Z80 KIO                            | .167 |

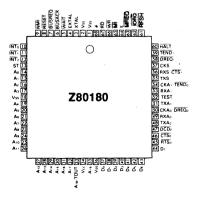

| Z80180 Z180 MPU                                |      |

| Z280 MPU                                       | .227 |

|                                                |      |

٠

# **Application Notes**

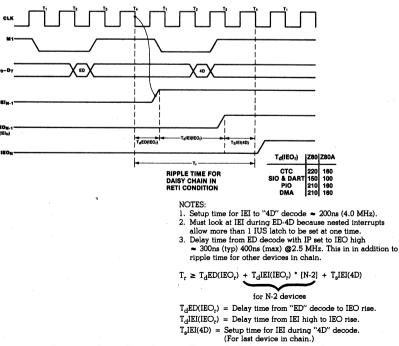

| Z80 Family Interrupt Structure                       |  |

|------------------------------------------------------|--|

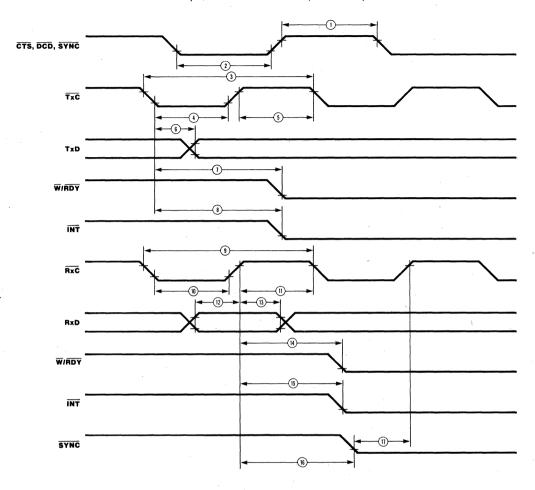

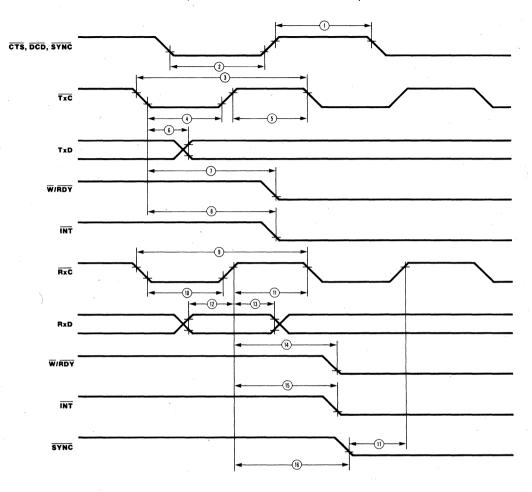

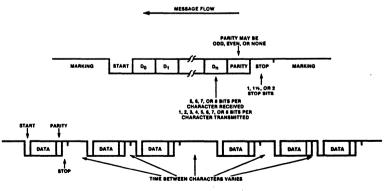

| Using the Z80 SIO In Asynchronous Communications     |  |

| Using the Z80 SIO with SDLC                          |  |

| Binary Synchronous Communication Using the Z80 SIO   |  |

| Serial Communication with the Z80A DART              |  |

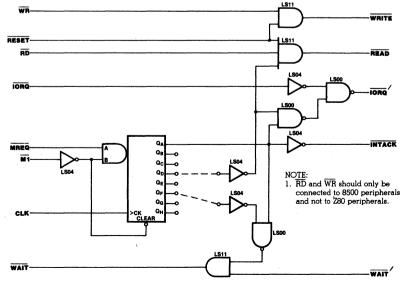

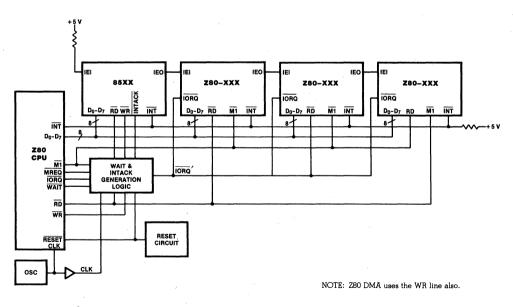

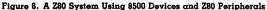

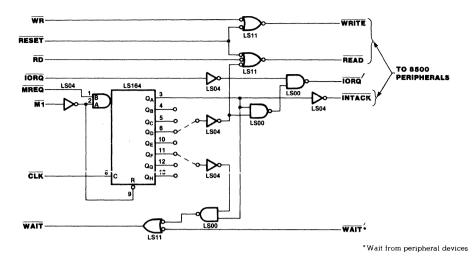

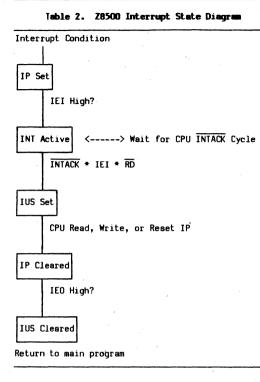

| Interfacing 8500 Peripherals to the Z80              |  |

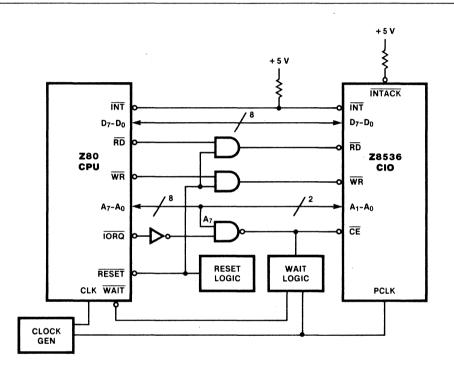

| Serial Clock Generation Using the Z8536C10           |  |

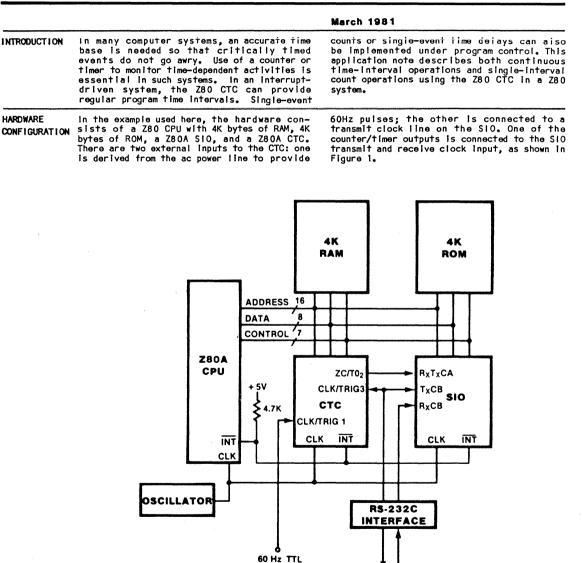

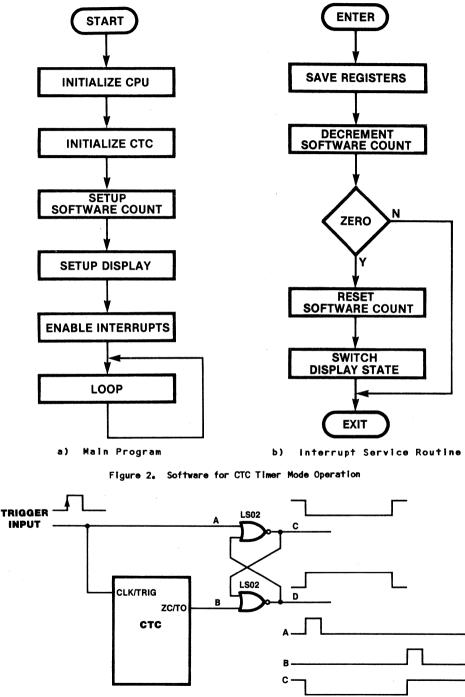

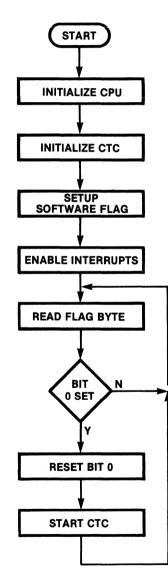

| Timing in an Interrupt-Based System with the Z80 CTC |  |

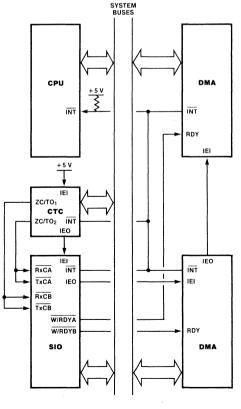

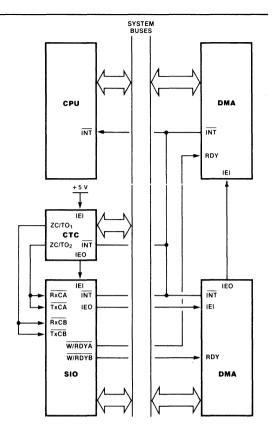

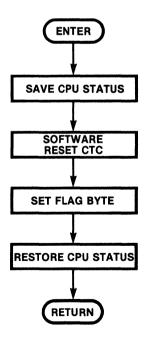

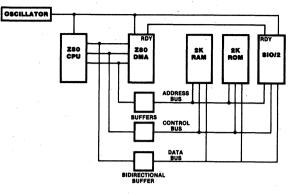

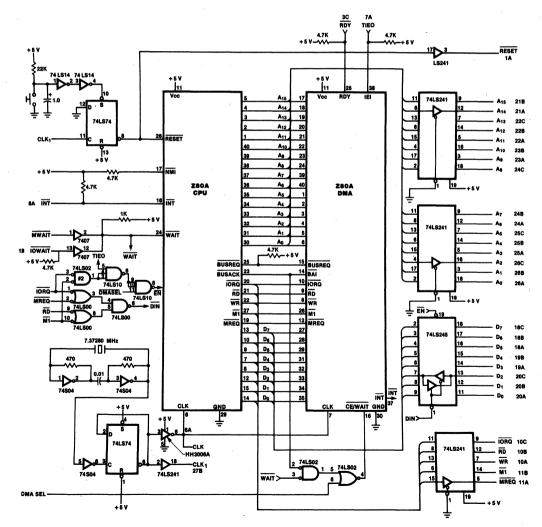

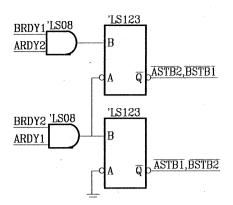

| A Z80-Based System Using the DMA with the SIO        |  |

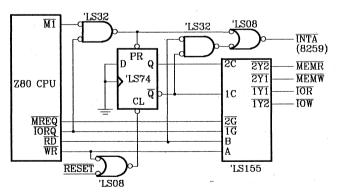

| Interfacing Z80 CPUs to the Z8500 Peripheral Family  |  |

| Z80 Family Questions and Answers                     |  |

| Zilog Quality and Reliability                        |  |

| Literature Guide                                     |  |

| Ordering Information                                 |  |

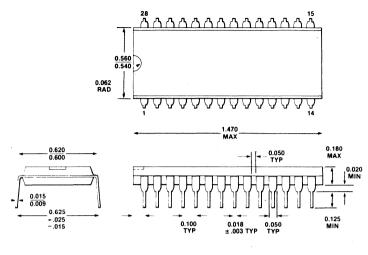

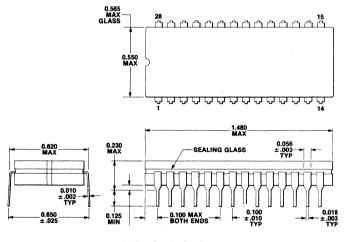

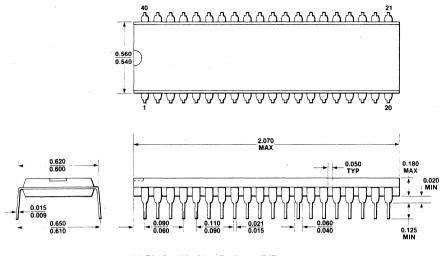

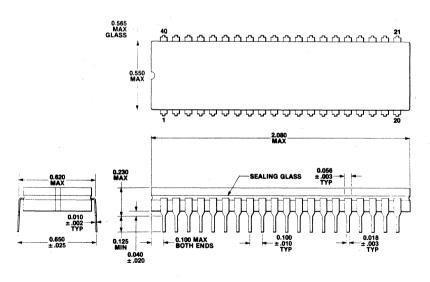

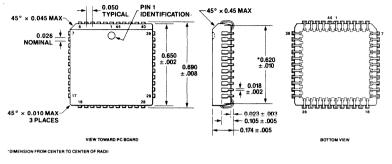

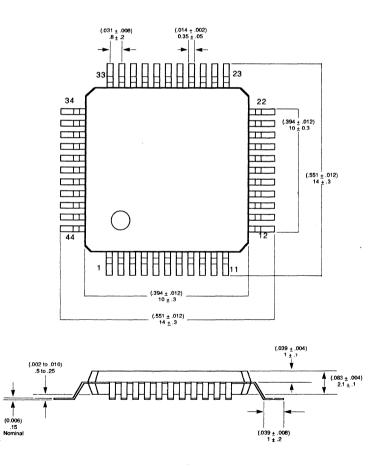

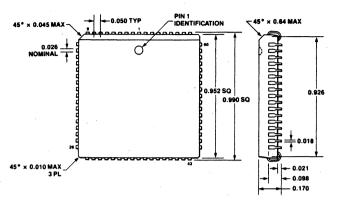

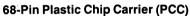

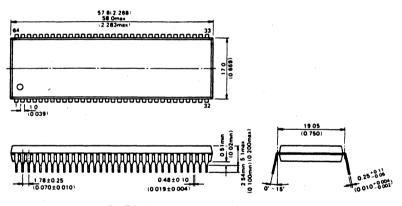

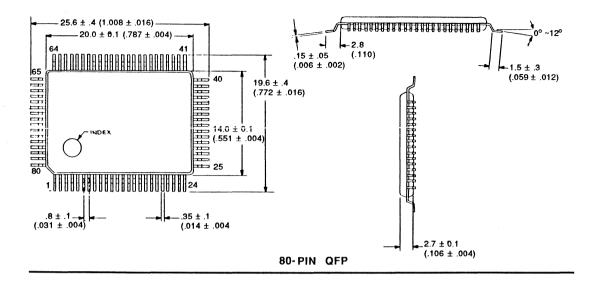

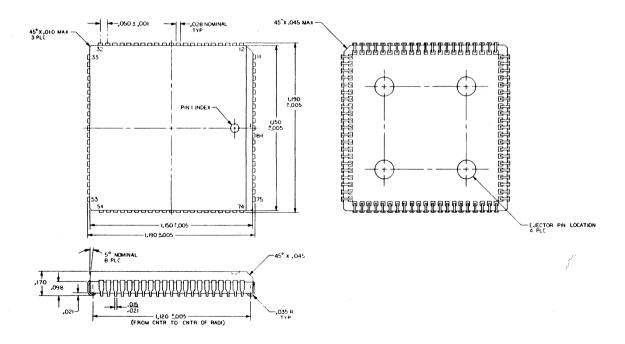

| Package Information                                  |  |

|                                                      |  |

January 1989

Zilog Z80 Family An Industry Standard 8-Bit Architecture with 16-Bit Migration Path

Zilog remains an industry leader, thanks to continuing innovation in integrated design and new superintegration technology. At Zilog, innovation means using proven, sophisticated mainframe and minicomputer concepts and translating them into the latest LSI technologies. Integration means more than designing an ever-greater number of functions onto a single chip.

This guide to the Z80 family of state-of-the-art microprocessors and intelligent peripheral controllers demonstrates Zilog's continued support for the Z80 microprocessor and the other members of the Z80 product family - family first introduced in 1976 that continues to enjoy growing customer support while family chips are upgraded to newer and ever-higher standards.

The Z8400/84C00 CPU Central Processing Unit rapidly established itself as the most sophisticated, most powerful, and most versatile 8-bit microprocessor in the world.

In addition to being source-code compatible with the 8080A microprocessor, the Z80 offers more instructions than the 8080A (158 vs 78) and numerous other features that simplify hardware requirements and reduce programming effort while increasing throughput. The dual-register set of the Z80 CPU allows high-speed context switching and more efficient interrupt processing. Two index registers give additional memory addressing flexibility and simplify the task of programming. Interfacing to dynamic memory is simplified by on-chip, programmable refresh logic. Block moves plus string and bit manipulation instructions reduce programming effort, program size, and execution time. The CMOS versions of the family retain all the functions of the standard NMOS components while providing dramatic power savings and increased reliability.

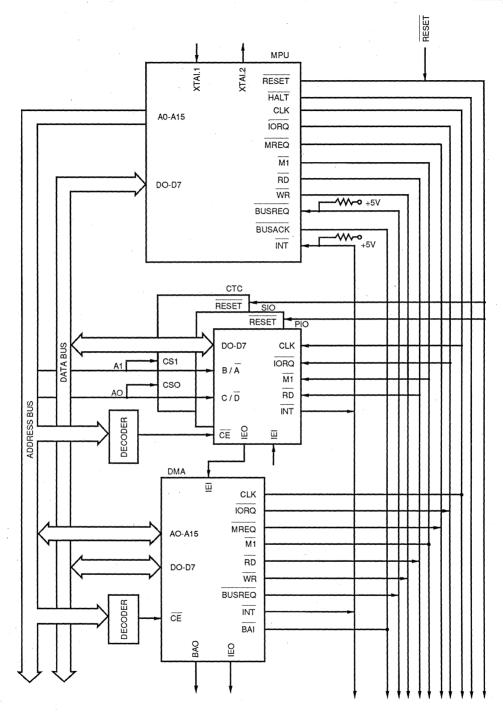

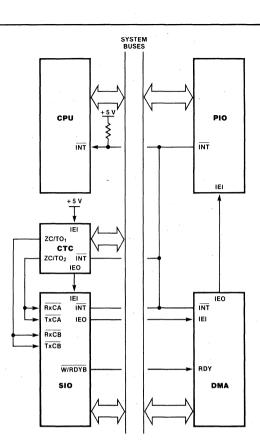

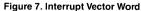

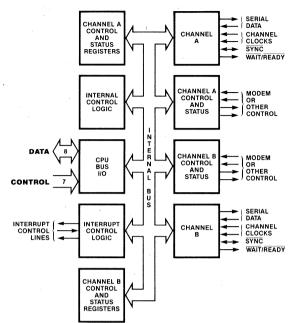

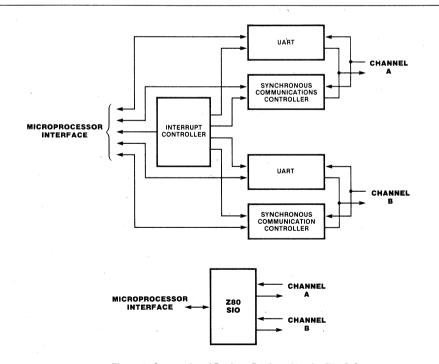

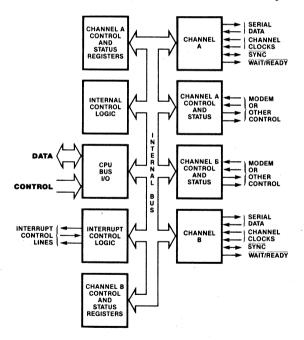

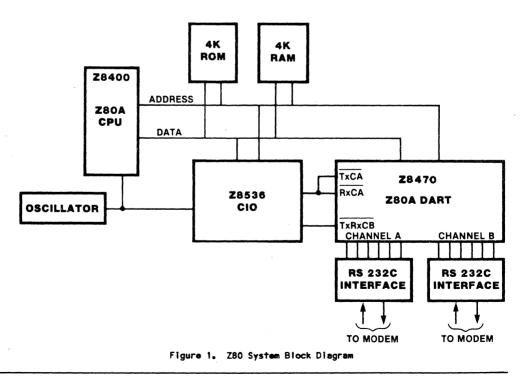

The four traditional functions of a microcomputer system (parallel I/O, serial I/O, counting/timing, and direct memory access) are easily implemented by the following well-proven family of Z80 peripheral devices: Z80 PIO, Z80 SIO, Z80 DART, Z80 CTC, and Z80 DMA.

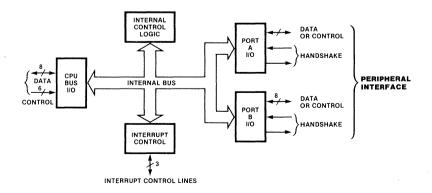

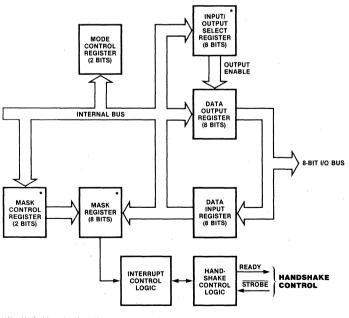

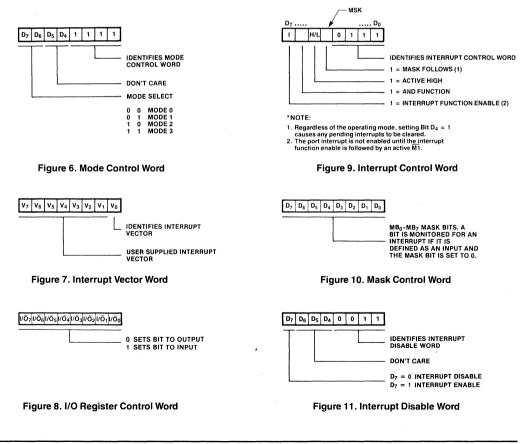

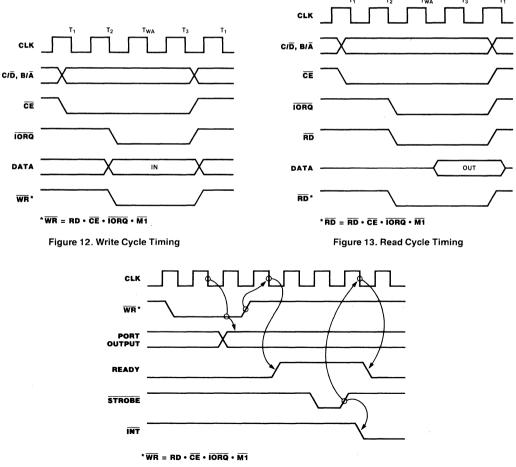

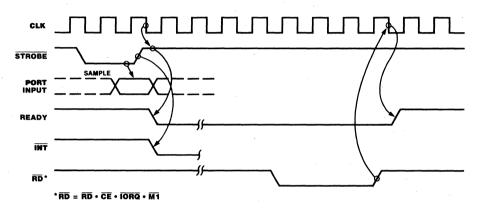

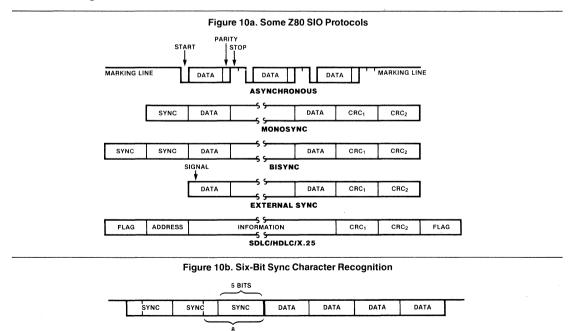

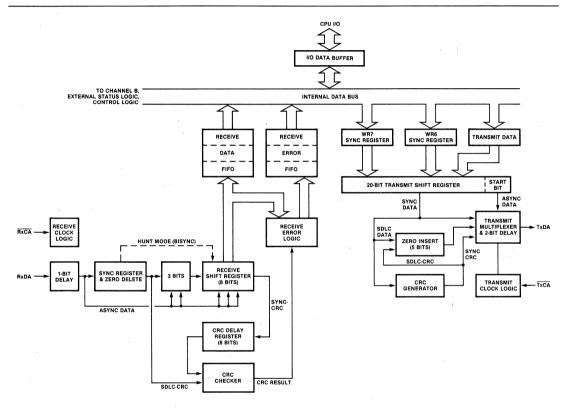

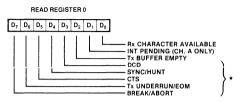

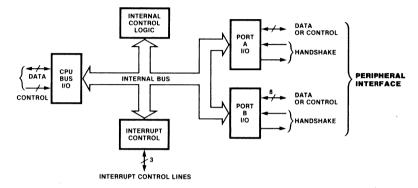

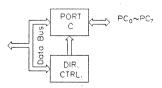

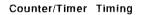

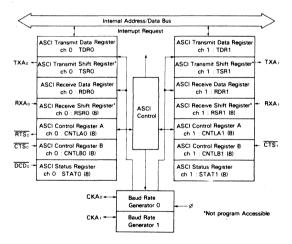

The easily programmed, dual channel **Z8420/84C20 Z80 PIO Parallel Input/Output Controller** offers two 8-bit I/O ports with individual handshake and pattern recognition logic. Both I/O ports operate in either a byte or a bit mode. In addition, this device can be programmed to generate interrupts for various status conditions. All common data communications protocols, asynchronous as well as synchronous, are remarkably well handled by the **Z8440/84C40 Z80 SIO Serial Input/Output Controller**. This dual-channel receiver/transmitter device offers on-chip parity and CRC generation/checking. FIFO buffering and flag and frame detection generation logic are also offered.

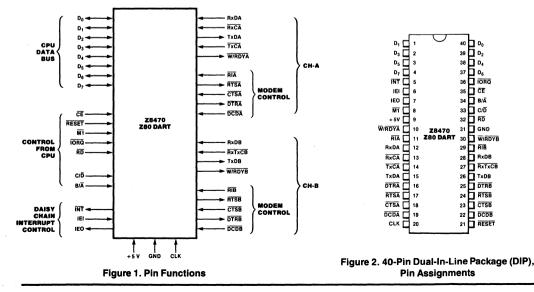

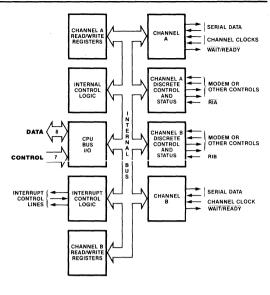

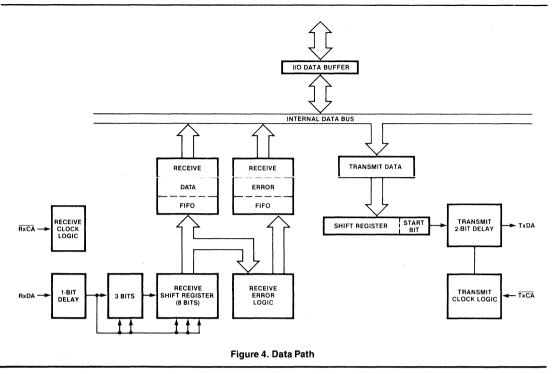

If asynchronous-only applications are required, the cost effective Z8470 Z80 Dart Dual Asynchronous Receiver/ Transmitter can be used in place of the Z80 SIO. The Z80 Dart offers all Z80 SIO asynchronous features in two channels.

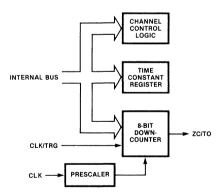

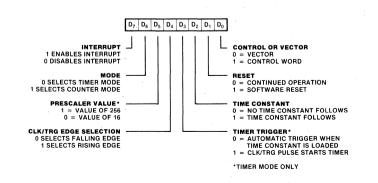

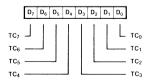

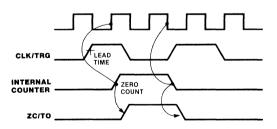

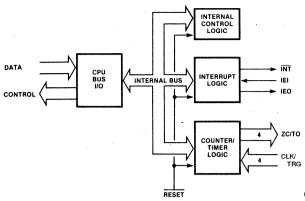

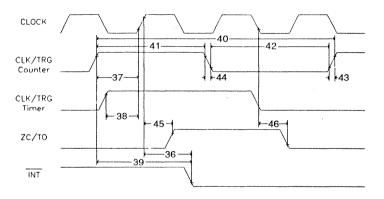

Timing and event-counting functions are the forte of the **Z8430/84C30 Z80 Counter/Timer Controller**. The CTC provides four counters, each with individually programmable prescalers. The CTC is a convenient source of programmable clock rates for the SIO.

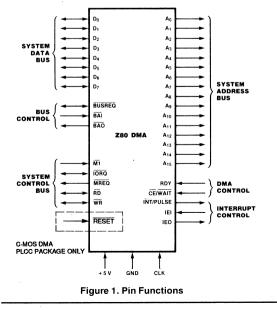

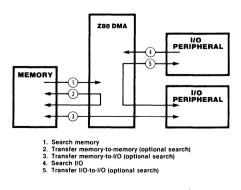

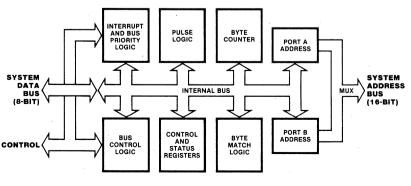

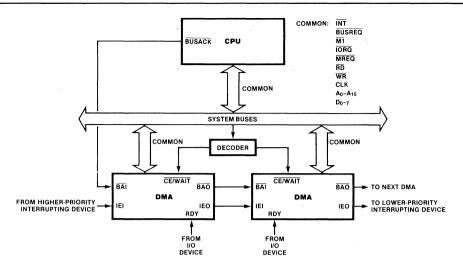

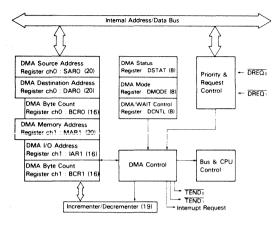

With the Z8410/84C10 Z80 DMA Direct Memory Access Controller, data can be transferred directly between any two ports (typically, I/O and memory). The DMA transfers, searches, or search/transfers data in Byte-by-Byte, Burst, or Continuous modes.

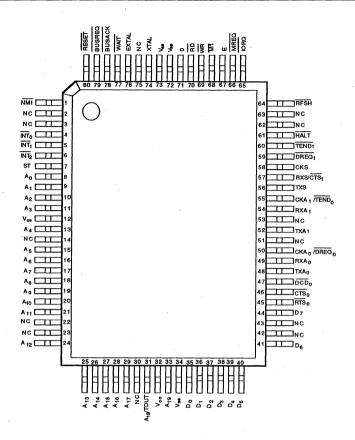

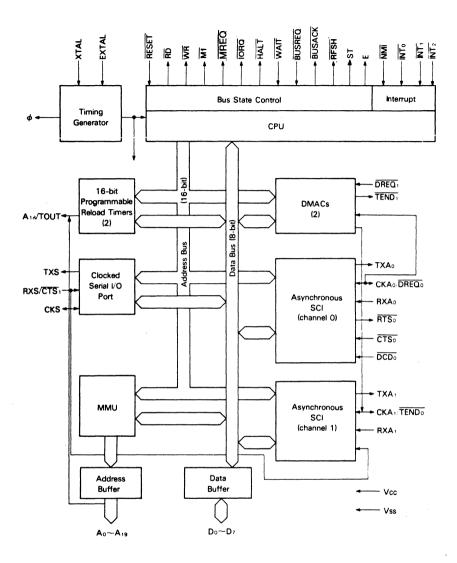

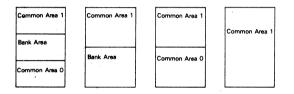

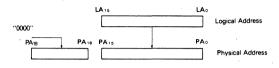

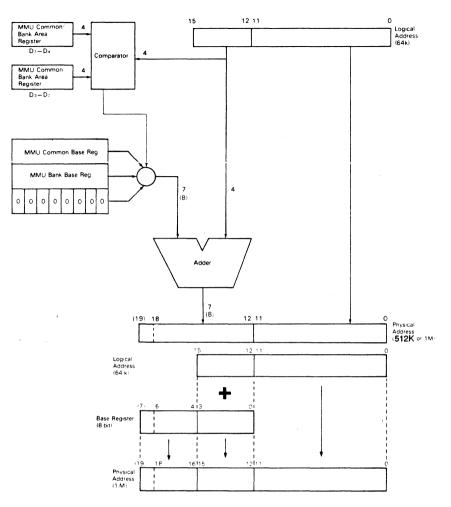

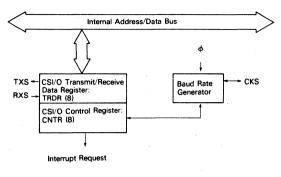

The Z180 microprocessor integrates an enhanced Z80 CPU and many of the functions traditionally assigned to peripheral circuits onto a single chip. The Z180 provides an easy software upgrade path. Old Z80 designs can be converted to the Z180 with essentially no loss in software investment. New designs will benefit from the processor's low cost, powerful instruction set, real low power consumption, and high level of integration. Recent advances in CMOS technology and chip-packing densities inspired the Z180. The processor is essentially a Z80 core (with a few added instructions), and a number of on-board peripherals. The most important of these is Memory Management Unit (MMU), which translates 16 bit addresses to 20 bits. Although this translation gives programs access to 1 MB of memory, the code uses only 16 bit (64K) addresses. Z80 software compatibility is thus completely maintained. Other Z180 peripherals include two 16 bit counter/timers, programmable refresh and wait state generation, a pair of DMA controllers, and three serial ports with on-chip baud rate generation.

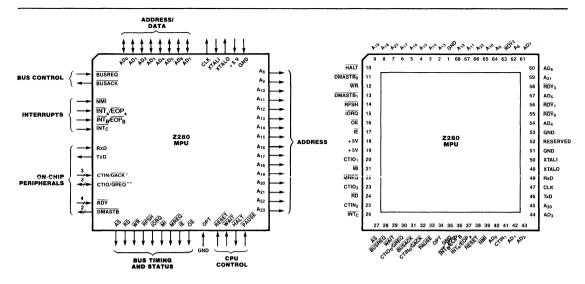

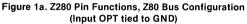

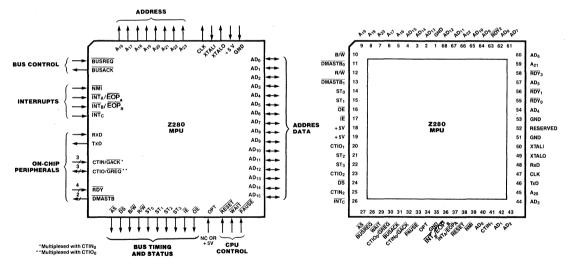

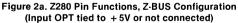

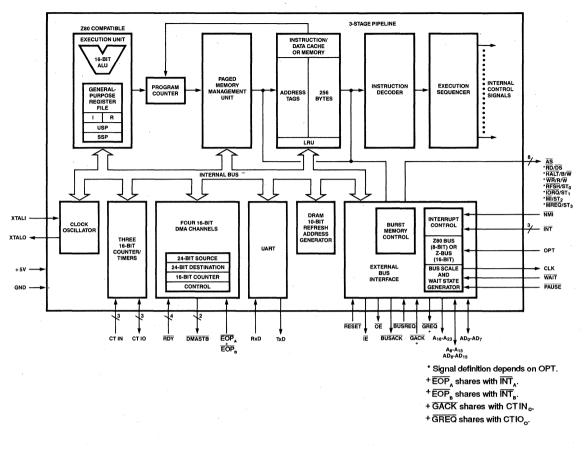

The Z80280 brings 16-bit CPU and sophisticated features

required by complex, high performance applications to the Z80 architecture. Z280 maintains complete object code compatibility with the Z80. One of the unique features of the Z280 is its bus size. By strapping a single pin on the chip, the designer can select 8 or 16 bit bus widths. Thus to use existing designs, an 8-bit Z80 compatible bus can be used. Higher performance systems can be designed using the Z280's 16 bit mode, in which all memory references use true 16 bit accesses. A single processor can be used in both medium and high performance products, without changing the software. The Z280 includes a Memory Management Unit (MMU), which gives the processor access to 16 MB of memory. Other features of the Z280 include on-chip instruction and cache memory, 3-stage pipeline, dual operating modes, four channel DMA Controller, three 16 bit counter/timers, programmable refresh and wait state generation, and a serial port with on-chip baud rate generation.

#### Zilog's Superintegration Strategy

In these days, when success in the semiconductor business requires that each competitor have a significant "edge", Zilog finds itself in a unique position. Customers have welcomed ASIC products specifically tailored for their particular needs. As these chips grow larger, however, economics dictates that there be a higher degree of organization in the architecture of the chips than exists with conventional gate arrays and standard cells; the microprocessor "core" offers the ideal, may be even unique solution to this requirement.

There are only three or four microprocessor families which are sufficiently well known in the industry to be recognized by a wide user base. The Zilog Z80 microprocessor family is well positioned in that ranking. Zilog is making its microprocessor cores and peripheral cells available to the industry in a concept we have called "Superintegration". In this concept, popular one-chip arrangements of the Zilog cores and cells are offered to our customers as "standard products" which may be tailored in software to meet particular customer needs.

The Zilog Superintegration concept offers three major benefits:

- The economics, quality and reliability of standard structures.

- The familiar Zilog product architectures and operating systems.

- User customization via software.

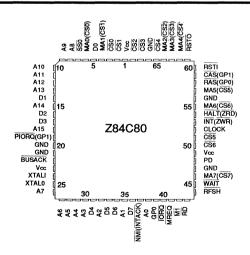

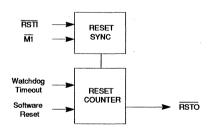

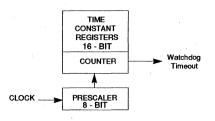

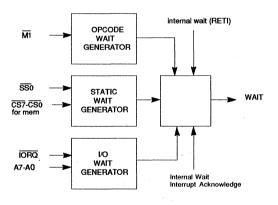

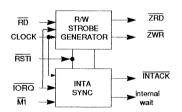

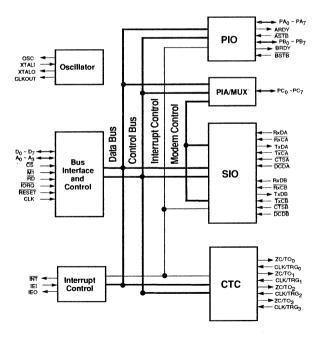

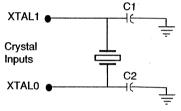

One of the first "Superintegration" products of the Z80 family is the Z84C90 Killer I/O (KIO). This chip combines the features of Z84C30 (CTC), Z84C4x (SIO), Z84C20 (PIO), a byte-wide bit programmable I/O port, and a crystal oscillator on a single chip. The Z84C01 is the Z80 CPU with a built-in clock generator/controller. The Z84C80 GLU is a collection of various circuits required to interface Z80 with memory and I/O peripheral devices. The features included on this chip include; the crystal oscillator, dynamic memory interface controller, static memory interface, memory and chip I/O selects, watch-dog timer, five types of wait state generators, and Z8500 peripheral interface.

### ADVANCED INFORMATION **Product Specification**

# Z8400/Z84C00 NMOS/CMOS Z80<sup>®</sup> CPU Central Processing Unit

January 1989

#### **FEATURES**

- The extensive instruction set contains 158 instructions. including the 8080A instruction set as a subset.

- Single 5 volt power supply.

- NMOS version for low cost high performance solutions, CMOS version for high performance low power designs.

- NMOS Z0840004 4 MHz, Z0840006 6.17 MHz, Z0840008 - 8 MHz.

CMOS Z84C0004 - DC to 4 MHz. Z84C0006 - DC to 6.17 MHz, Z84C0008 - DC to 8 MHz, Z84C0010 - DC to 10 MHz.

6 MHz version can be operated at 6.144 MHz clock.

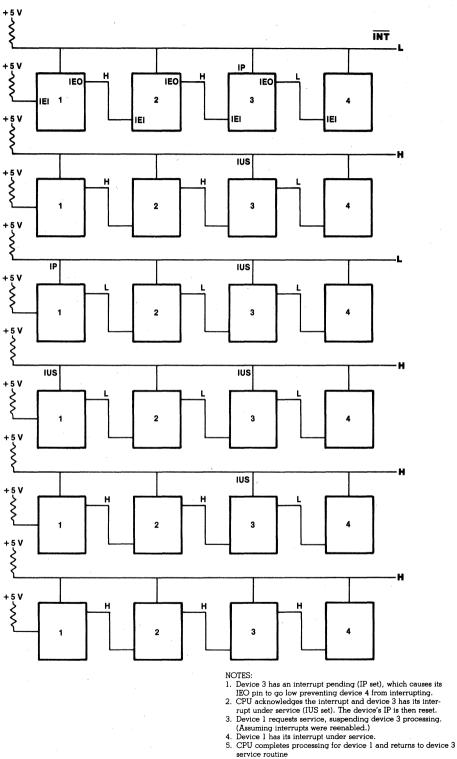

- The Z80 microprocessors and associated family of peripherals can be linked by a vectored interrupt system. This system can be daisy-chained to allow implementation of a priority interrupt scheme.

- Duplicate set of both general-purpose and flag registers.

- Two sixteen bit index registers. -

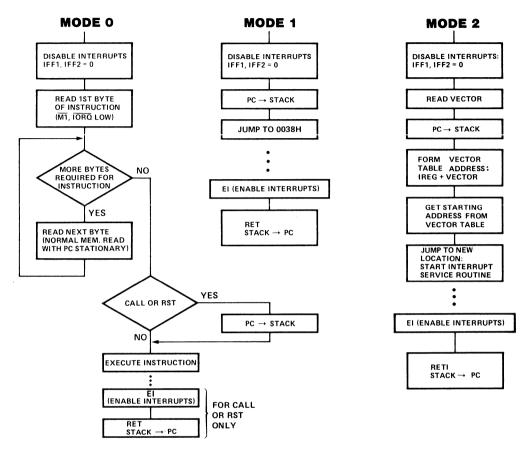

- Three modes of maskable interrupts: Mode 0-8080A similar; Mode 1-Non-Z80 environment, location 38H; Mode 2-Z80 family peripherals, vectored interrupts.

- On-chip dynamic memory refresh counter.

#### **GENERAL DESCRIPTION**

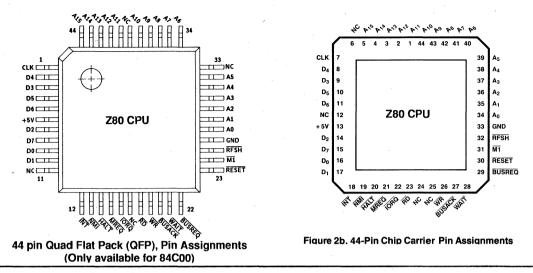

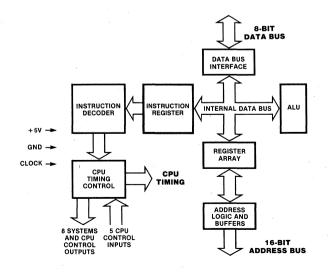

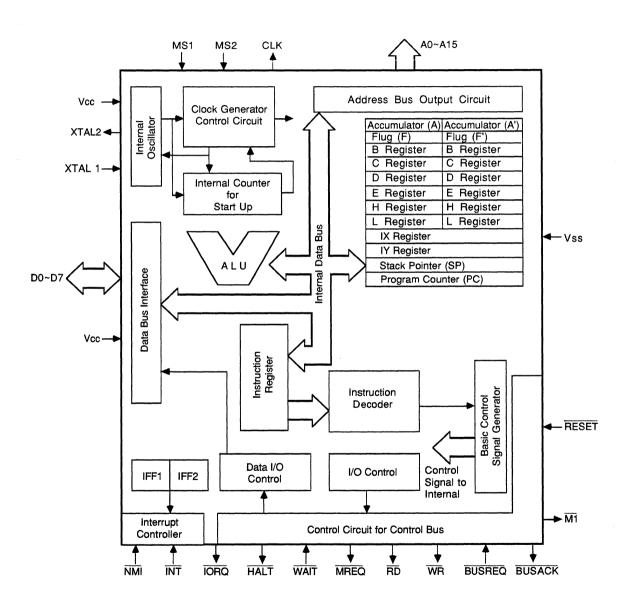

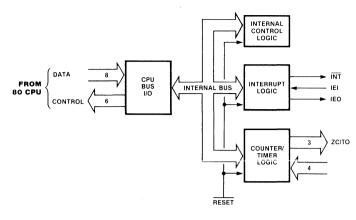

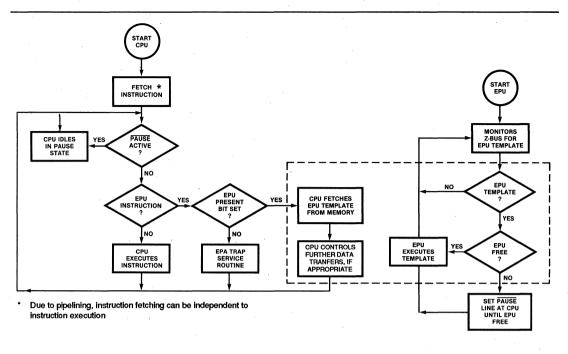

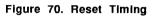

The CPUs are fourth-generation enhanced microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable second- and third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six general-purpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may be reserved for very fast interrupt response. The CPU also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single + 5V power source. All output signals are fully decoded and timed to control standard memory or peripheral circuits; the CPU is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 3) shows the primary functions of the processors. Subsequent text provides more detail on the I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 3. Z80C CPU Block Diagram

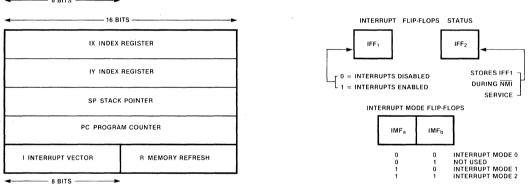

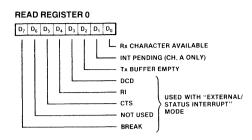

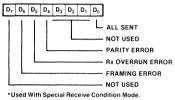

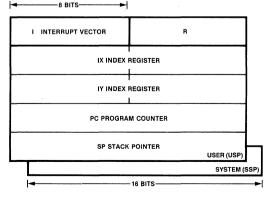

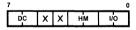

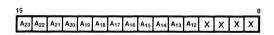

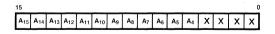

#### CPU REGISTERS

Figure 4 shows three groups of registers within the CPU. The first group consists of duplicate sets of 8-bit registers: a principal set and an alternate set [designated by ' (prime), e.g., A'l. Both sets consist of the Accumulator register, the Flag register, and six general-purpose registers. Transfer of data between these duplicate sets of registers is accomplished by use of "Exchange" instructions. The result is faster response to interrupts and easy, efficient implementation of such versatile programming techniques as background-foreground data processing. The second set of registers consists of six registers with assigned functions. These are the I (Interrupt register), the R (Refresh register), the IX and IY (Index registers) the SP (Stack Pointer), and the PC (Program Counter). The third group consists of two interrupt status flip-flops, plus an additional pair of flip-flops which assists in identifying the interrupt mode at any particular time. Table 1 provides further information on these registers.

ALTERNATE REGISTER SET

| A ACCUMULATOR     | F FLAG REGISTER   | A' ACCUMULATOR     | F' FLAG REGISTER   |

|-------------------|-------------------|--------------------|--------------------|

| B GENERAL PURPOSE | C GENERAL PURPOSE | B' GENERAL PURPOSE | C' GENERAL PURPOSE |

| D GENERAL PURPOSE | E GENERAL PURPOSE | D' GENERAL PURPOSE | E' GENERAL PURPOSE |

| H GENERAL PURPOSE | L GENERAL PURPOSE | H' GENERAL PURPOSE | L' GENERAL PURPOSE |

MAIN REGISTER SET

#### **INTERRUPTS: GENERAL OPERATION**

The CPU accepts two interrupt input signals: NMI and INT. The NMI is a non-maskable interrupt and has the highest priority. INT is a lower priority interrupt and it requires that interrupts be enabled in software in order to operate. INT can be connected to multiple peripheral devices in a wired-OR configuration.

The Z80 has a single response mode for interrupt service on the non-maskable interrupt. The maskable interrupt, INT, has three programmable response modes available. These are:

- Mode 0 similar to the 8080 microprocessor.

- Mode 1 Peripheral Interrupt service, for use with non-8080/Z80 systems.

#### Mode 2 - a vectored interrupt scheme, usually daisychained, for use with the Z80 Family and compatible peripheral devices.

The CPU services interrupts by sampling the NMI and INT signals at the rising edge of the last clock of an instruction. Further interrupt service processing depends upon the type of interrupt that was detected. Details on interrupt responses are shown in the CPU Timing Section.

Non-Maskable Interrupt (NMI). The nonmaskable interrupt cannot be disabled by program control and therefore will be accepted at all times by the CPU. NMI is usually reserved for servicing only the highest priority type interrupts, such as that for orderly shutdown after power

| I         | Register           | Size (Bits) | Remarks                                                                                                                                                      |

|-----------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A, A'     | Accumulator        | 8           | Stores an operand or the results of an operation.                                                                                                            |

| F, F′     | Flags              | 8           | See Instruction Set.                                                                                                                                         |

| B, B′     | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                                       |

| C, C′     | General Purpose    | 8           | Can be used separately or as a 16-bit register with C.                                                                                                       |

| D, D'     | General Purpose    | 8.          | Can be used separately or as a 16-bit register with E.                                                                                                       |

| E, E′     | General Purpose    | 8           | Can be used separately or as a 16-bit register with E.                                                                                                       |

| H, H′     | ` General Purpose  | 8           | Can be used separately or as a 16-bit register with L.                                                                                                       |

| L, L′     | General Purpose    | 8           | Can be used separately or as a 16-bit register with L.                                                                                                       |

|           |                    |             | Note: The (B,C), (D,E), and (H,L) sets are combined as follows: $B - High$ byte $C - Low$ byte $D - High$ byte $E - Low$ byte $H - High$ byte $L - Low$ byte |

| 1         | Interrupt Register | 8           | Stores upper eight bits of memory address for vectored interrupt processing.                                                                                 |

| R         | Refresh Register   | 8           | Provides user-transparent dynamic memory refresh. Automatically<br>incremented and placed on the address bus during each<br>instruction fetch cycle.         |

| IX        | Index Register     | 16          | Used for indexed addressing.                                                                                                                                 |

| IY        | Index Register     | 16          | Used for indexed addressing                                                                                                                                  |

| SP        | Stack Pointer      | 16          | Holds address of the top of the stack. See Push or Pop in instruction set.                                                                                   |

| PC        | Program Counter    | 16          | Holds address of next instruction.                                                                                                                           |

| IFF1-IFF2 | Interrupt Enable   | Flip-Flops  | Set or reset to indicate interrupt status (see Figure 4).                                                                                                    |

| IMFa-IMFb | Interrupt Mode     | Flip-Flops  | Reflect Interrupt mode (see Figure 4).                                                                                                                       |

#### Table 1. Z80C CPU Registers

failure has been detected. After recognition of the  $\overline{\text{NMI}}$  signal (providing  $\overline{\text{BUSREQ}}$  is not active), the CPU jumps to restart location 0066H. Normally, software starting at this address contains the interrupt service routine.

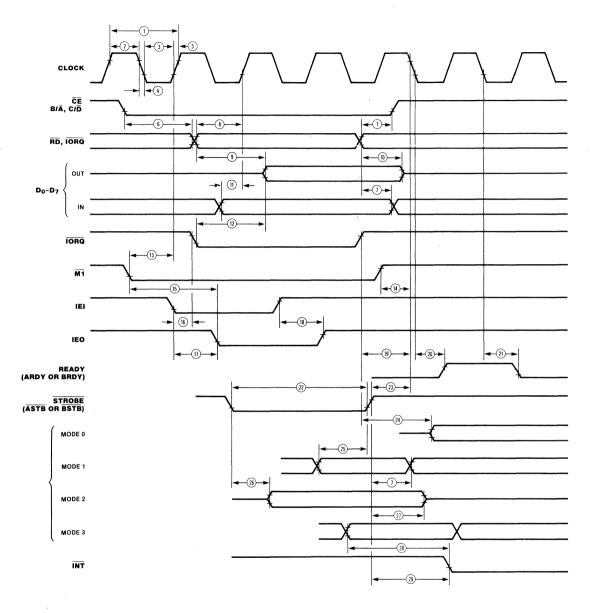

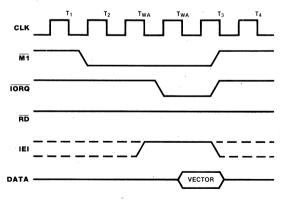

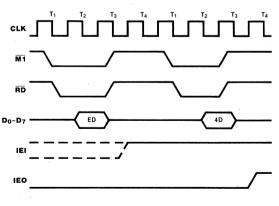

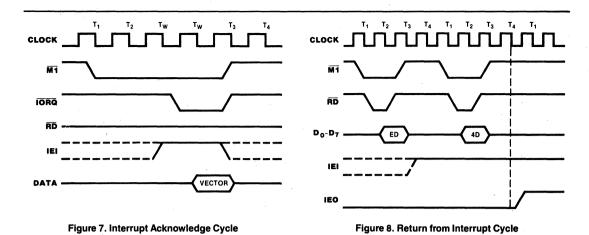

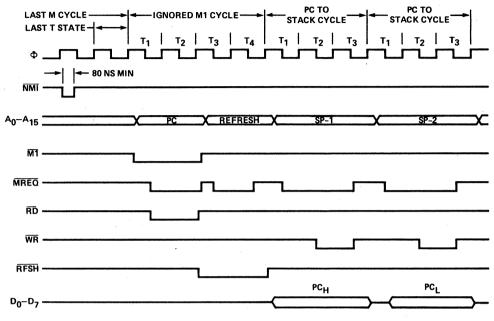

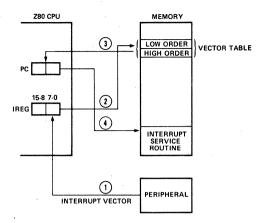

**Maskable Interrupt (INT).** Regardless of the interrupt mode set by the user, the CPU response to a maskable interrupt input follows a common timing cycle. After the interrupt has been detected by the CPU (provided that interrupts are enabled and BUSREQ is not active) a special interrupt processing cycle begins. This is a special fetch (M1) cycle in which IORQ becomes active rather than MREQ, as in a normal M1 cycle. In addition, this special M1 cycle is automatically extended by two WAIT states, to allow for the time required to acknowledge the interrupt request.

**Mode 0 Interrupt Operation.** This mode is similar to the 8080 microprocessor interrupt service procedures. The interrupting device places an instruction on the data bus. This is normally a Restart instruction, which will initiate a call

to the selected one of eight restart locations in page zero of memory. Unlike the 8080, the Z80 CPU responds to the Call instruction with only one interrupt acknowledge cycle followed by two memory read cycles.

**Mode 1 Interrupt Operation.** Mode 1 operation is very similar to that for the NMI. The principal difference is that the Mode 1 interrupt has only one restart location, 0038H.

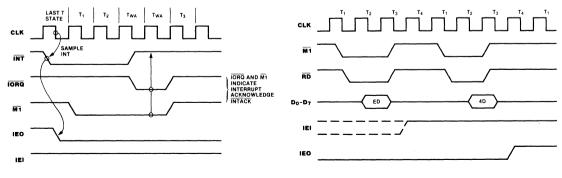

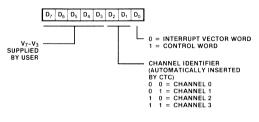

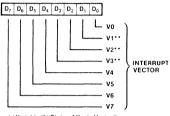

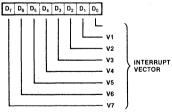

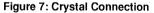

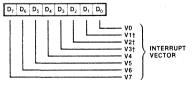

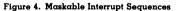

Mode 2 Interrupt Operation. This interrupt mode has been designed to most effectively utilize the capabilities of the Z80 microprocessor and its associated peripheral family. The interrupting peripheral device selects the starting address of the interrupt service routine. It does this by placing an 8-bit vector on the data bus during the interrupt acknowledge cycle. The CPU forms a pointer using this byte as the lower 8 bits and the contents of the I register as the upper 8 bits. This points to an entry in a table of addresses for interrupt service routines. The CPU then jumps to the routine at that

Z80

address. This flexibility in selecting the interrupt service routine address allows the peripheral device to use several different types of service routines. These routines may be located at any available location in memory. Since the interrupting device supplies the low-order byte of the 2-byte vector, bit 0 ( $A_0$ ) must be a zero.

**Interrupt Enable/Disable Operation.** Two flip-flops, IFF<sub>1</sub> and IFF<sub>2</sub>, referred to in the register description, are used to signal the CPU interrupt status. Operation of the two flip-flops is described in Table 2. For more details, refer to the Z80 CPU Technical Manual (03-0029-01) and Z80 Assembly Language Programming Manual (03-0002-01).

| Action                       | IFF <sub>1</sub> | IFF <sub>2</sub> | Comments                                                                              |

|------------------------------|------------------|------------------|---------------------------------------------------------------------------------------|

| CPU Reset                    | 0                | 0                | Maskable interrupt                                                                    |

| DI instruction execution     | 0                | 0                | Maskable interrupt                                                                    |

| El instruction execution     | 1                | 1                | Maskable interrupt                                                                    |

| LD A,I instruction execution | •                | •                | $IFF_2 \rightarrow Parity flag$                                                       |

| LD A,R instruction execution | •                | ٠                | $IFF_2 \rightarrow Parity flag$                                                       |

| Accept NMI                   | 0                | •                | Maskable interrupt                                                                    |

| RETN instruction execution   | IFF <sub>2</sub> | •                | IFF <sub>2</sub> → IFF <sub>1</sub> at<br>completion of an<br>MMI service<br>routine. |

| Table | 2        | State | of  | Flin  | -Flops |  |

|-------|----------|-------|-----|-------|--------|--|

| Iavic | <u> </u> | Juaie | UI. | 1 110 |        |  |

#### **INSTRUCTION SET**

The microprocessor has one of the most powerful and versatile instruction sets available in any 8-bit micro-

processor. It includes such unique operations as a block move for fast, efficient data transfers within memory, or between memory and I/O. It also allows operations on any bit in any location in memory.

The following is a summary of the instruction set which shows the assembly language mnemonic, the operation, the flag status, and gives comments on each instruction. For an explanation of flag notations and symbols for mnemonic tables, see the Symbolic Notations section which follows these tables. The *Z80 CPU Technical Manual* (03-0029-01), the *Programmer's Reference Guide* (03-0012-03), and Assembly Language Programming Manual (03-0002-01) contain significantly more details for programming use.

The instructions are divided into the following categories:

- 8-bit loads

- □ 16-bit loads

- □ Exchanges, block transfers, and searches

- B-bit arithmetic and logic operations

- □ General-purpose arithmetic and CPU control

- □ 16-bit arithmetic operations

- Rotates and shifts

□ Bit set, reset, and test operations

- 🗆 Jumps

- □ Calls, returns, and restarts

- Input and output operations

A variety of addressing modes are implemented to permit efficient and fast data transfer between various registers, memory locations, and input/output devices. These addressing modes include:

- Immediate

- Immediate extended

- Modified page zero

- □ Relative

- □ Extended

- □ Indexed

- Register

- Register indirect

- Implied

- 🗆 Bit

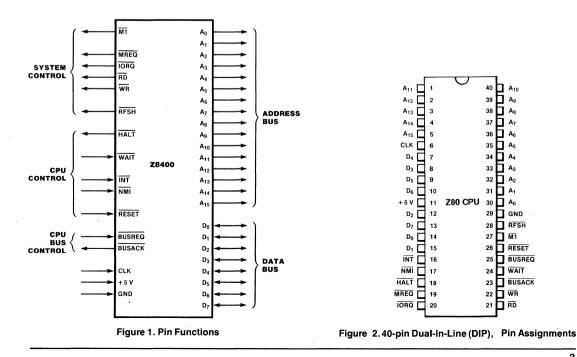

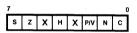

#### **PIN DESCRIPTIONS**

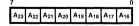

**A<sub>0</sub>-A<sub>15</sub>.** Address Bus (output, active High, 3-state). A<sub>0</sub>-A<sub>15</sub> form a 16-bit address bus. The Address Bus provides the address for memory data bus exchanges (up to 64K bytes) and for I/O device exchanges.

**BUSACK.** Bus Acknowledge (output, active Low). Bus Acknowledge indicates to the requesting device that the CPU address bus, data bus, and control signals MREQ, IORQ, RD, and WR have entered their high-impedance states. The external circuitry can now control these lines.

**BUSREQ.** Bus Request (input, active Low). Bus Request has a higher priority than NMI and is always recognized at the end of the current machine cycle. BUSREQ forces the CPU address bus, data bus, and control signals MREQ, IORQ, RD, and WR to go to a high-impedance state so that other devices can control these lines. BUSREQ is normally wired-OR and requires an external pullup for these applications. Extended BUSREQ periods due to extensive DMA operations can prevent the CPU from properly refreshing dynamic RAMs.

**D<sub>0</sub>-D<sub>7</sub>.** *Data Bus* (input/output, active High, 3-state). D<sub>0</sub>-D<sub>7</sub> constitute an 8-bit bidirectional data bus, used for data exchanges with memory and I/O.

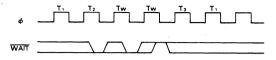

**HALT.** *Halt State* (output, active Low). HALT indicates that the CPU has executed a Halt instruction and is awaiting either a nonmaskable or a maskable interrupt (with the mask enabled) before operation can resume. While halted, the CPU executes NOPs to maintain memory refresh.

**INT.** Interrupt Request (input, active Low). Interrupt Request is generated by I/O devices. The CPU honors a request at the end of the current instruction if the internal software-controlled interrupt enable flip-flop (IFF) is enabled. INT is normally wired-OR and requires an external pullup for these applications.

**IORQ.** Input/Output Request (output, active Low, 3-state). IORQ indicates that the lower half of the address bus holds a valid I/O address for an I/O read or write operation. IORQ is also generated concurrently with M1 during an interrupt acknowledge cycle to indicate that an interrupt response vector can be placed on the data bus. **M1.** Machine Cycle One (output, active Low). M1, together with MREQ, indicates that the current machine cycle is the opcode fetch cycle of an instruction execution. M1, together with IORQ, indicates an interrupt acknowledge cycle.

**MREQ.** *Memory Request* (output, active Low, 3-state). MREQ indicates that the address bus holds a valid address for a memory read or memory write operation.

**NMI.** Non-Maskable Interrupt (input, negative edgetriggered). NMI has a higher priority than INT. NMI is always recognized at the end of the current instruction, independent of the status of the interrupt enable flip-flop, and automatically forces the CPU to restart at location 0066H.

**RD.** *Read* (output, active Low, 3-state). RD indicates that the CPU wants to read data from memory or an I/O device. The addressed I/O device or memory should use this signal to gate data onto the CPU data bus.

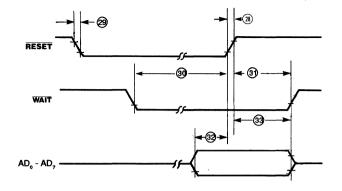

**RESET.** *Reset* (input, active Low). RESET initializes the CPU as follows: it resets the interrupt enable flip-flop, clears the PC and Registers I and R, and sets the interrupt status to Mode 0. During reset time, the address and data bus go to a high-impedance state, and all control output signals go to the inactive state. Note that RESET must be active for a minimum of three full clock cycles before the reset operation is complete.

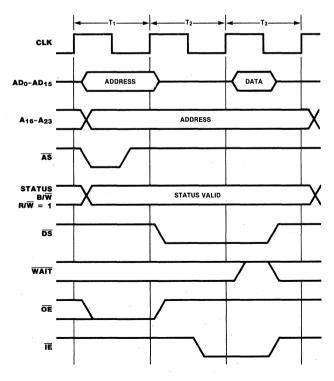

**RFSH.** *Refresh* (output, active Low). RFSH, together with MREQ, indicates that the lower seven bits of the system's address bus can be used as a refresh address to the system's dynamic memories.

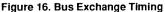

**WAIT.** *Wait* (input, active Low). WAIT indicates to the CPU that the addressed memory or I/O devices are not ready for a data transfer. The CPU continues to enter a Wait state as long as this signal is active. Extended WAIT periods can prevent the CPU from properly refreshing dynamic memory.

**WR**, Write (output, active Low, 3-state). WR indicates that the CPU data bus holds valid data to be stored at the addressed memory or I/O location.

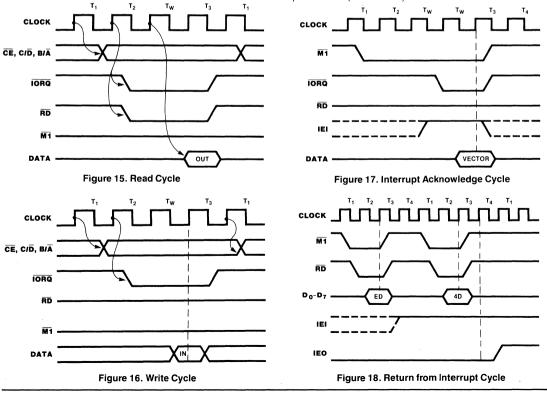

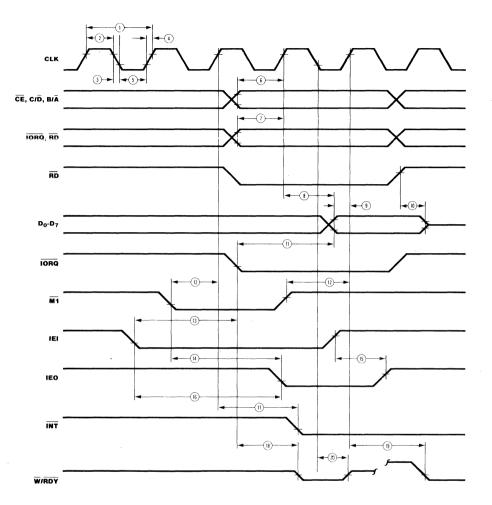

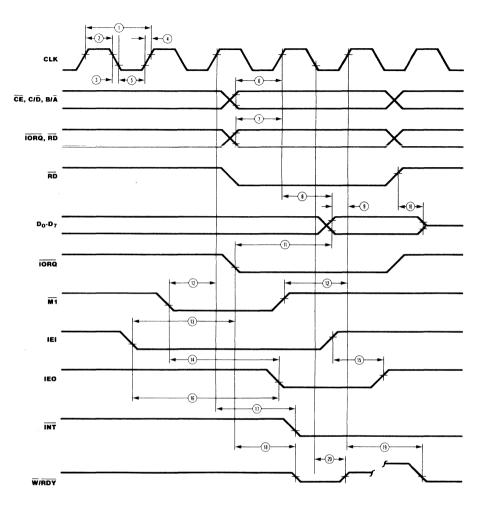

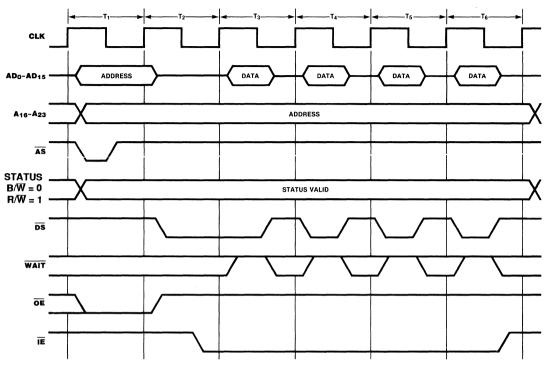

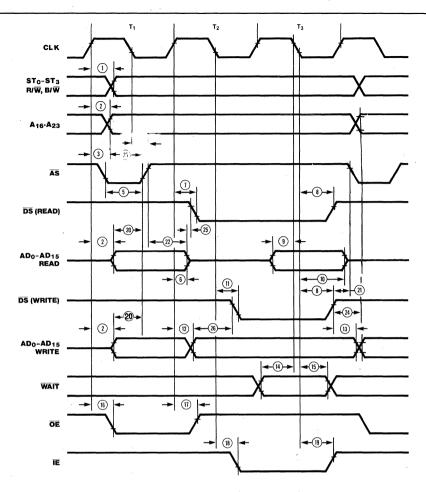

#### **CPU TIMING**

# The Z80 CPU executes instructions by proceeding through a specific sequence of operations:

- Memory read or write

- I/O device read or write

- Interrupt acknowledge

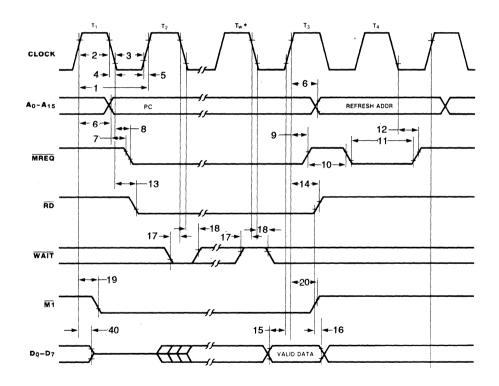

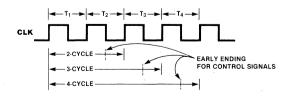

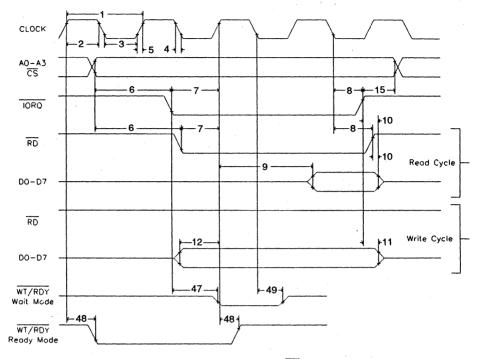

The basic clock period is referred to as a T time or cycle, and three or more T cycles make up a machine cycle (M1, M2 or M3 for instance). Machine cycles can be extended either by the CPU automatically inserting one or more Wait states or by the insertion of one or more Wait states by the user.

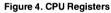

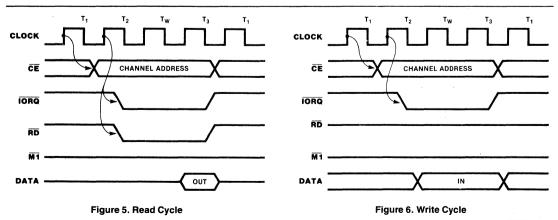

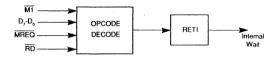

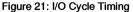

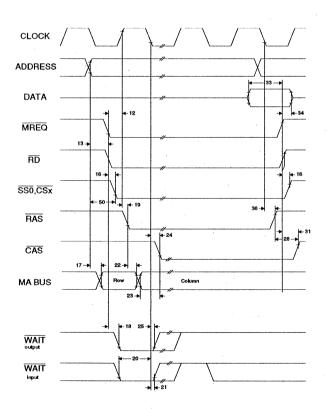

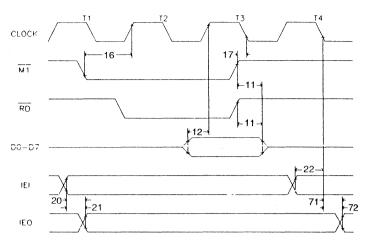

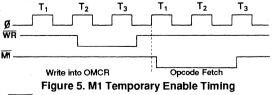

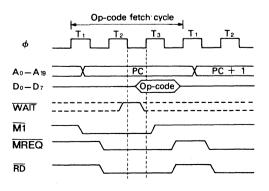

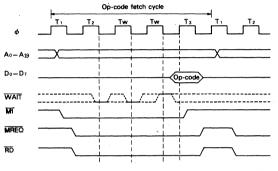

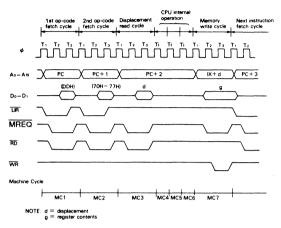

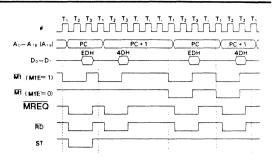

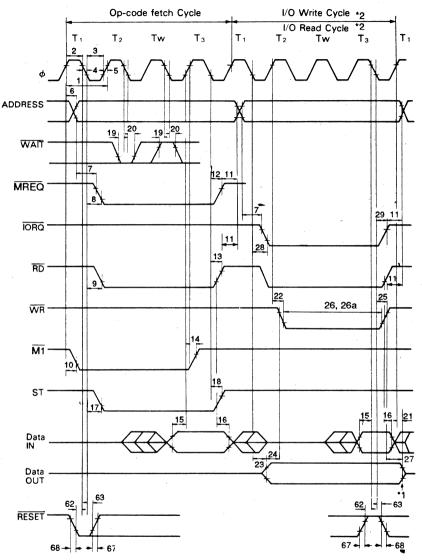

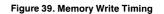

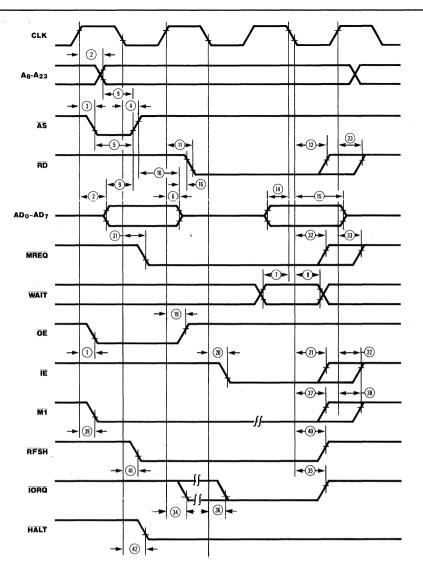

Instruction Opcode Fetch. The CPU places the contents of the Program Counter (PC) on the address bus at the start of the cycle (Figure 5). Approximately one-half clock cycle later, MREQ goes active. When active, RD indicates that the memory data can be enabled onto the CPU data bus.

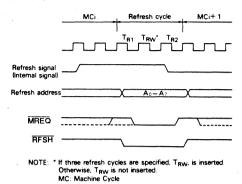

The CPU samples the WAIT input with the falling edge of clock state  $T_2$ . During clock states  $T_3$  and  $T_4$  of an M1 cycle, dynamic RAM refresh can occur while the CPU starts decoding and executing the instruction. When the Refresh Control signal becomes active, refreshing of dynamic memory can take place.

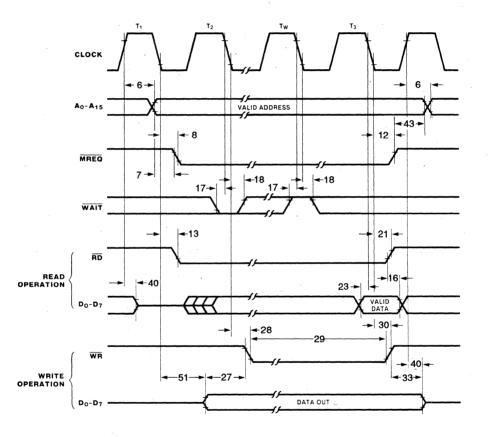

Figure 5. Instruction Opcode Fetch

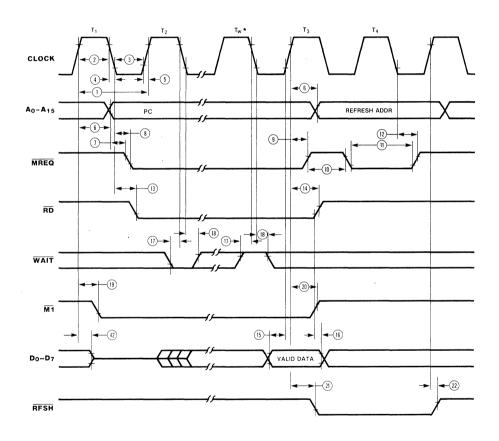

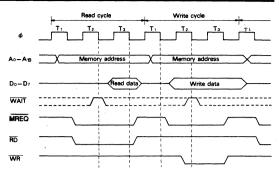

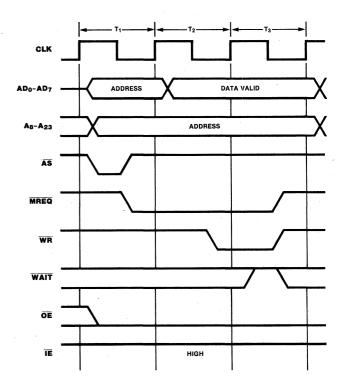

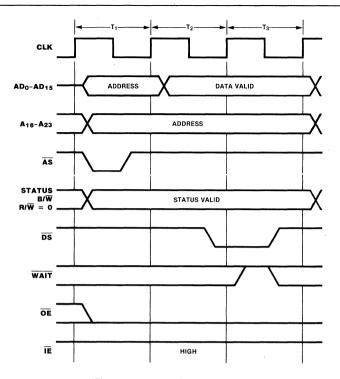

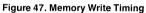

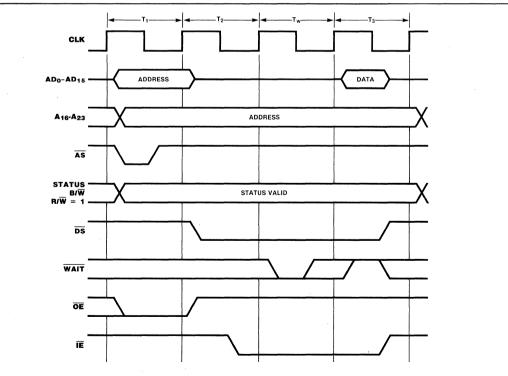

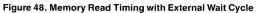

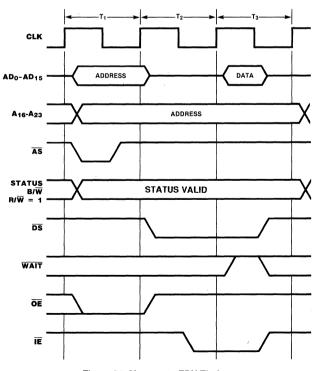

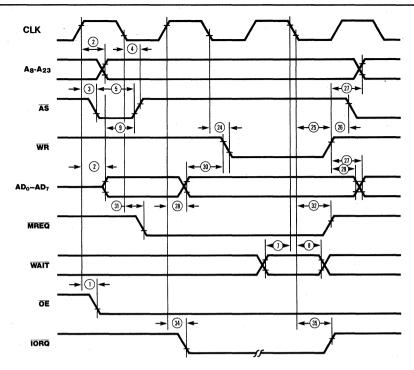

**Memory Read or Write Cycles.** Figure 6 shows the timing of memory read or write cycles other than an opcode fetch ( $\overline{M1}$ ) cycle. The  $\overline{MREQ}$  and  $\overline{RD}$  signals function exactly as in the fetch cycle. In a memory write cycle,  $\overline{MREQ}$  also

becomes active when the address bus is stable. The  $\overline{WR}$  line is active when the data bus is stable, so that it can be used directly as an  $R/\overline{W}$  pulse to most semiconductor memories.

10

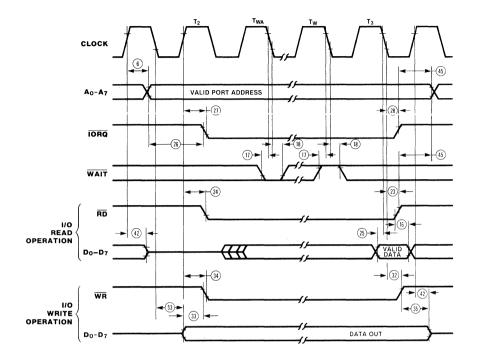

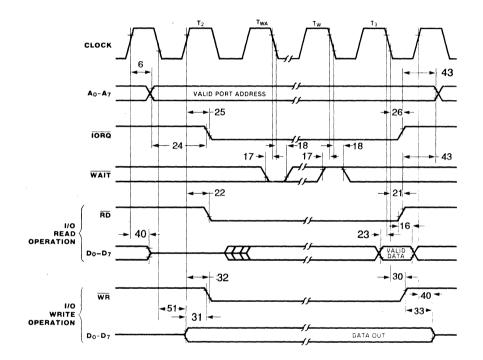

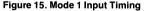

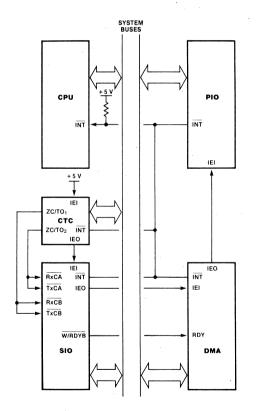

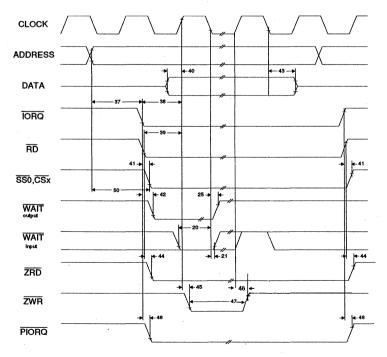

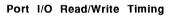

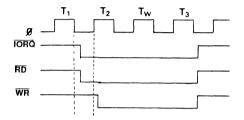

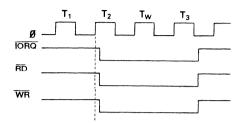

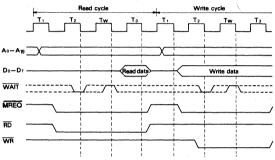

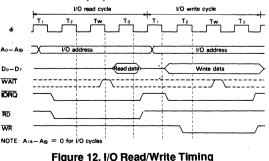

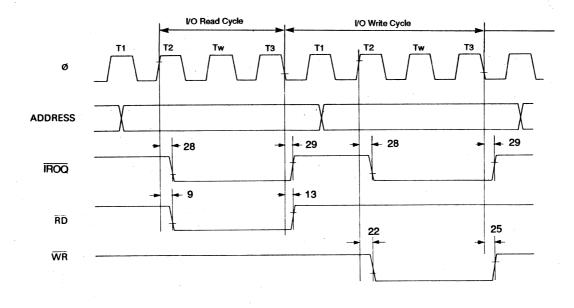

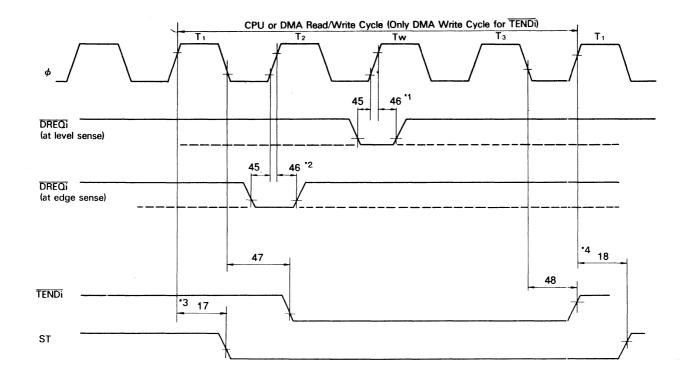

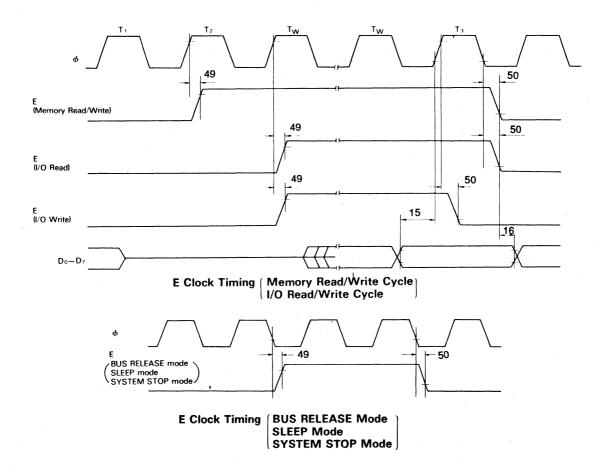

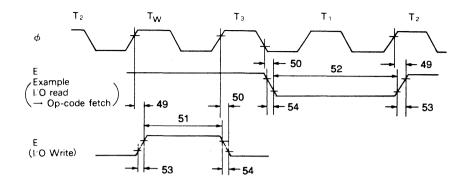

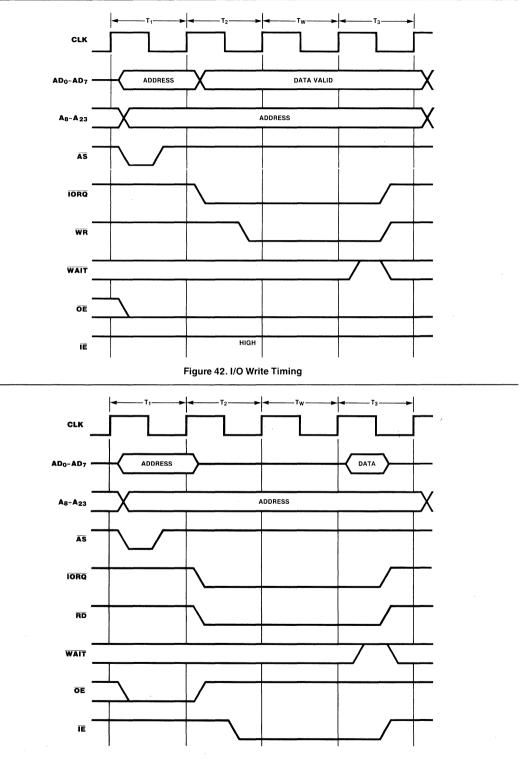

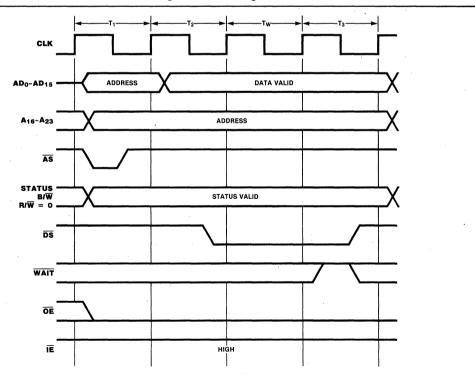

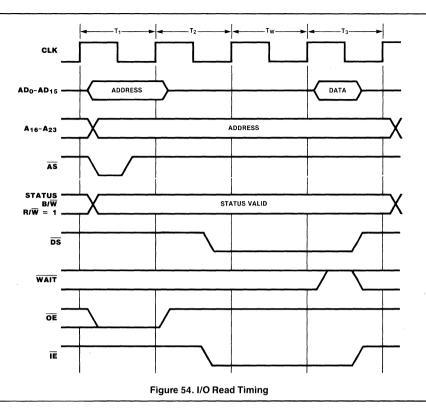

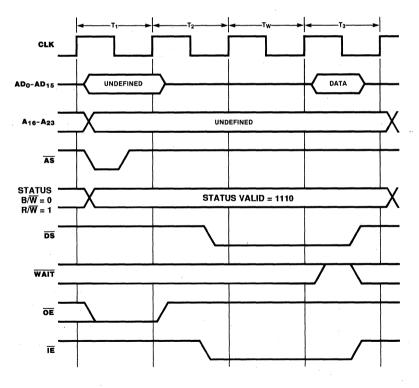

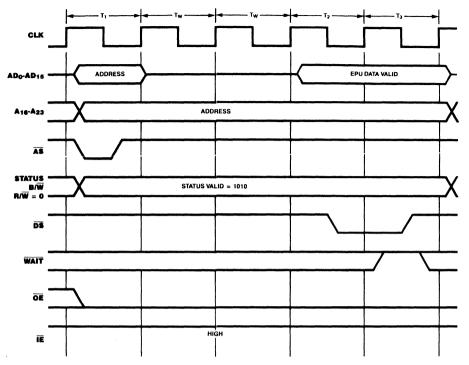

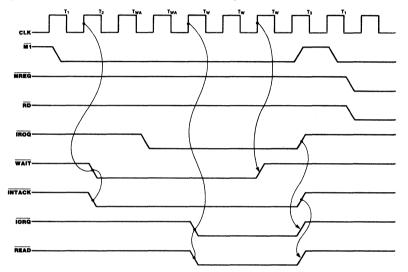

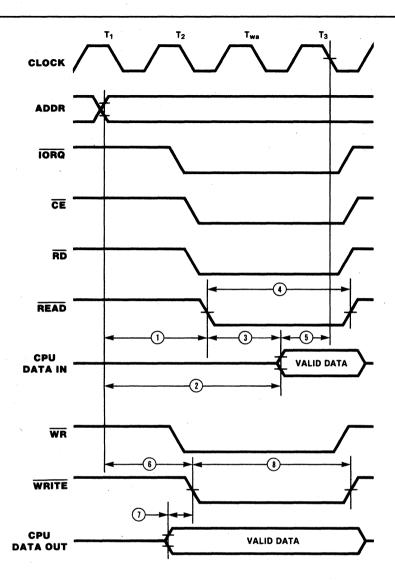

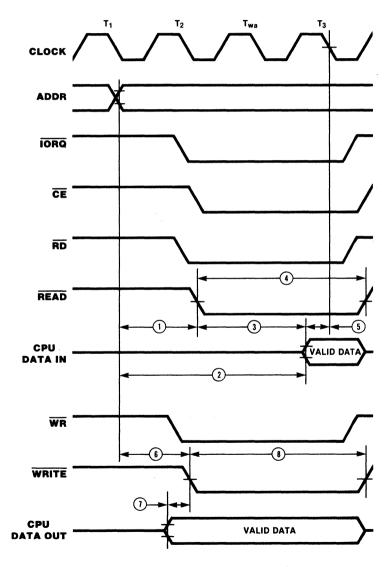

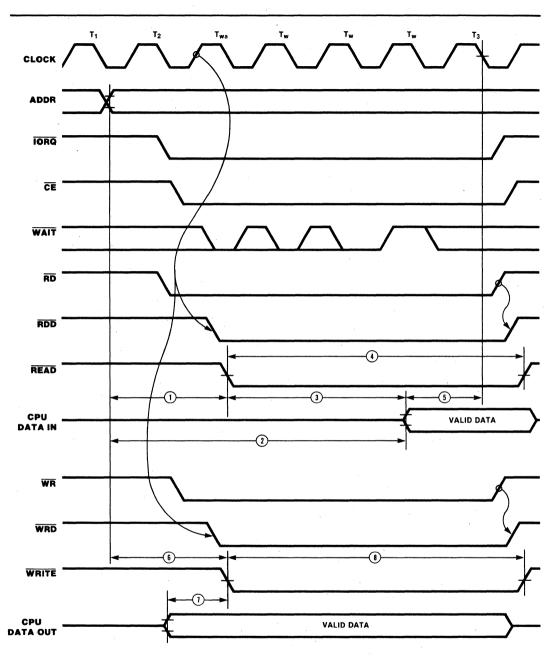

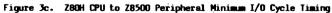

**Input or Output Cycles.** Figure 7 shows the timing for an I/O read or I/O write operation. During I/O operations, the CPU automatically inserts a single Wait state ( $T_{WA}$ ). This

extra Wait state allows sufficient time for an I/O port to decode the address from the port address lines.

T<sub>WA</sub> = One wait cycle automatically inserted by CPU.

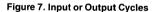

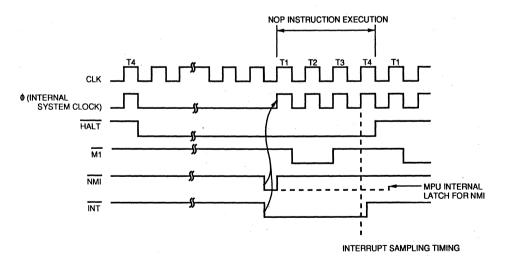

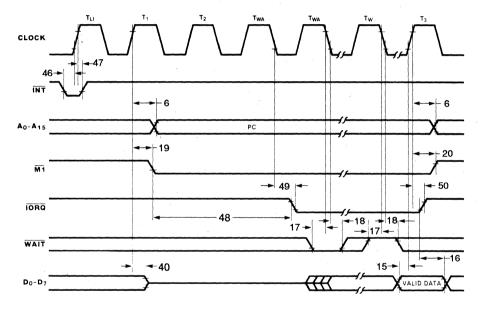

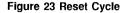

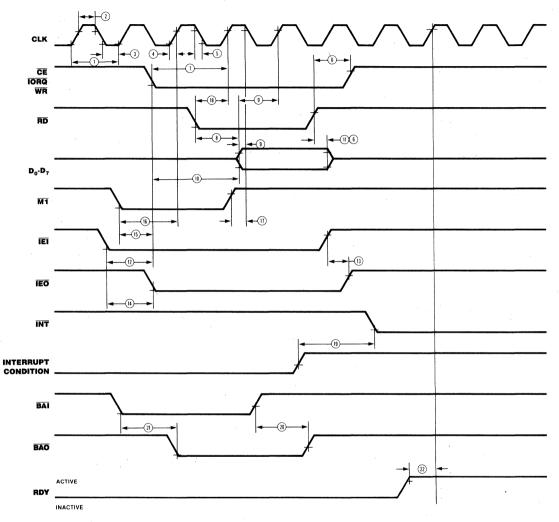

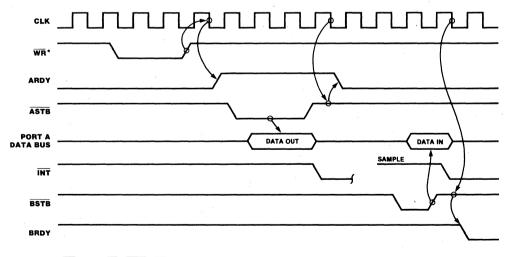

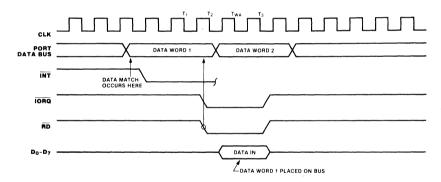

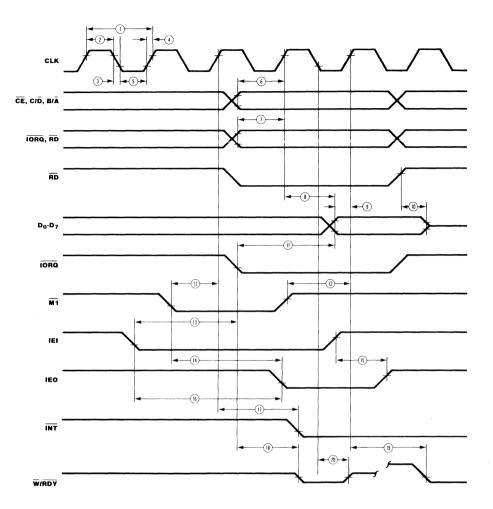

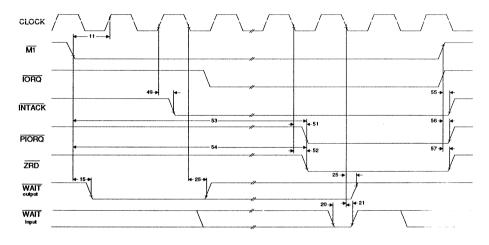

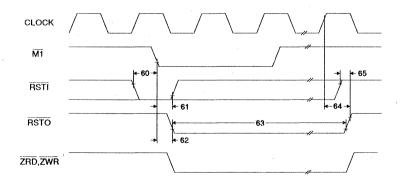

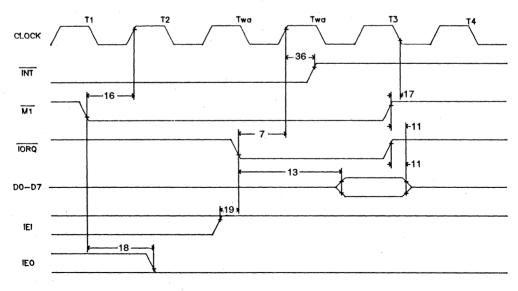

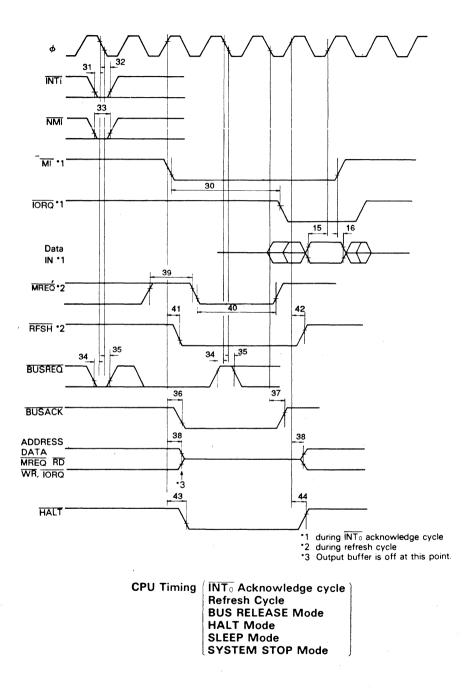

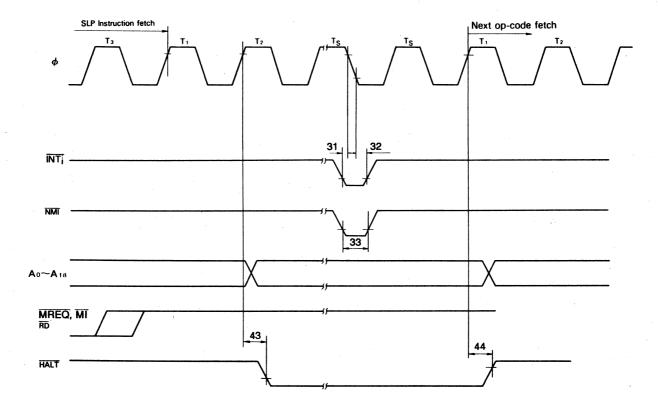

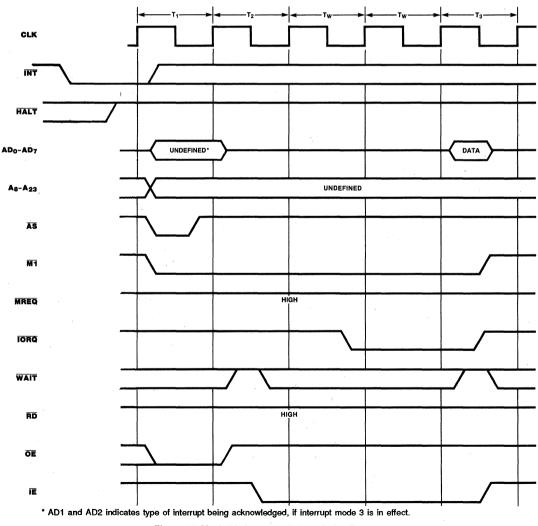

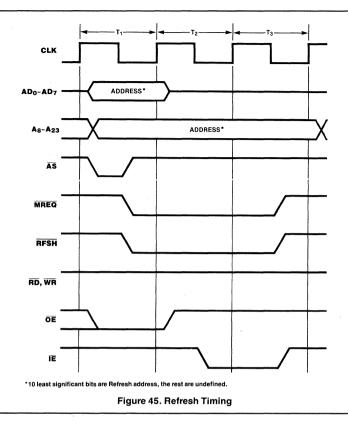

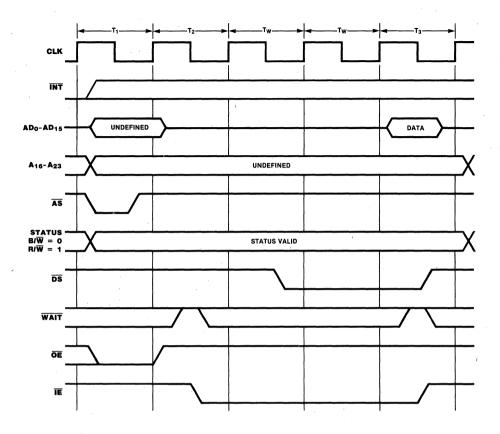

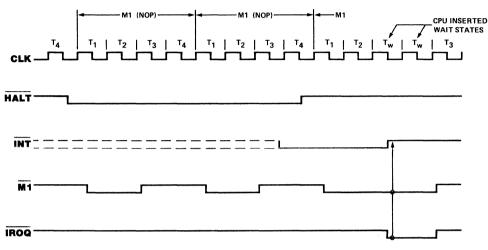

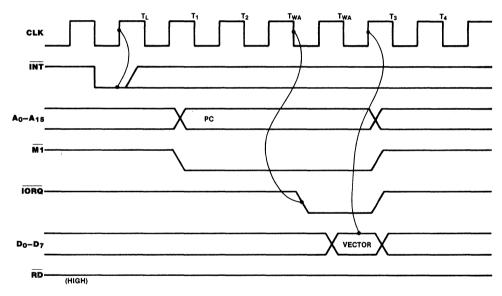

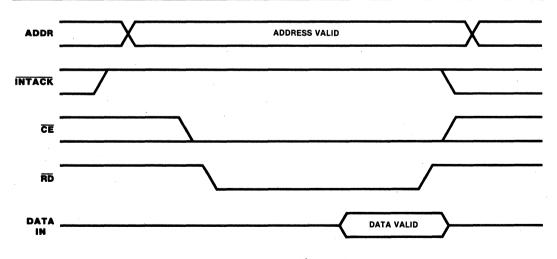

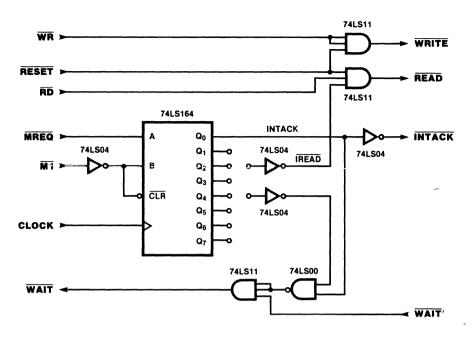

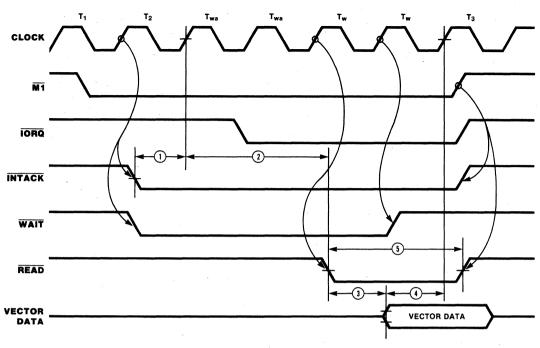

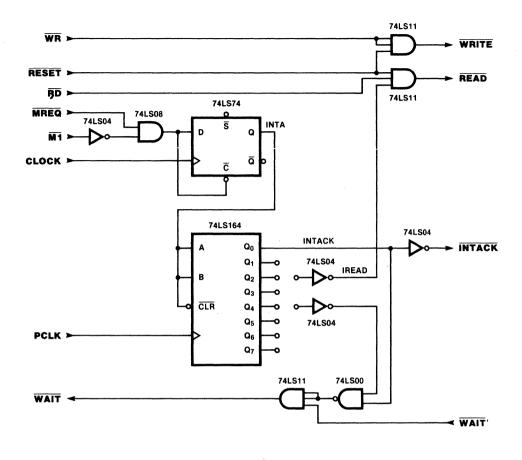

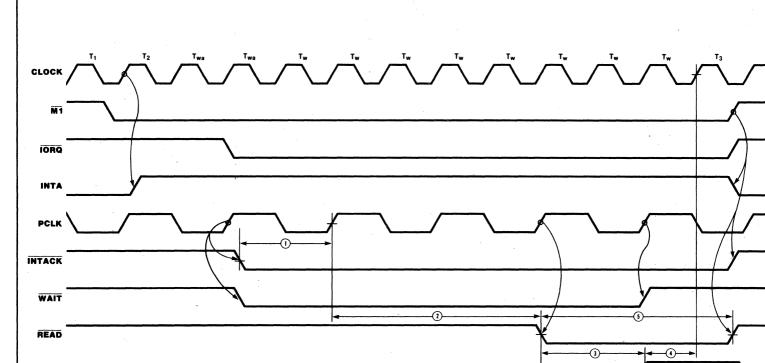

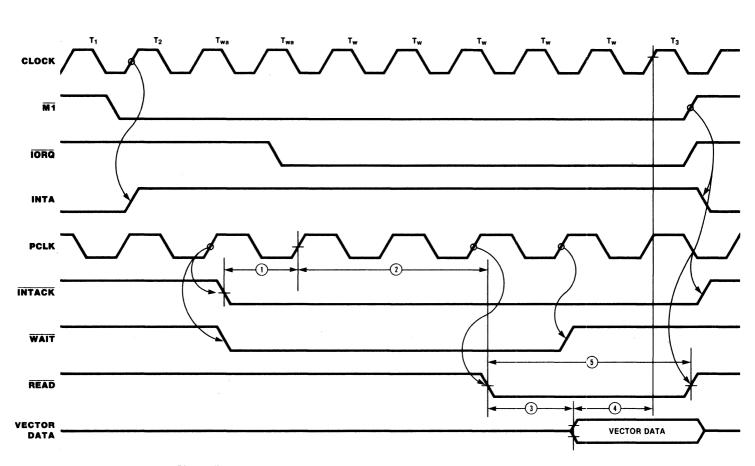

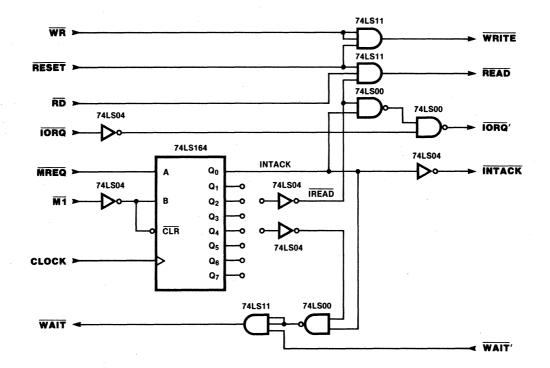

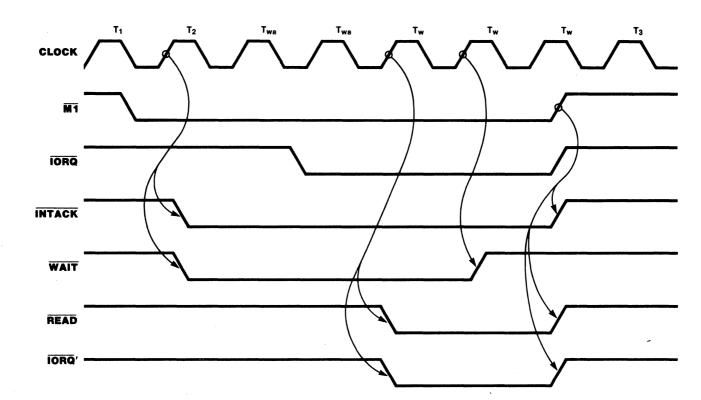

**Interrupt Request/Acknowledge Cycle.** The CPU samples the interrupt signal with the rising edge of the last clock cycle at the end of any instruction (Figure 8). When an interrupt is accepted, a special  $\overline{M1}$  cycle is generated.

During this  $\overline{\text{M1}}$  cycle,  $\overline{\text{IORQ}}$  becomes active (instead of  $\overline{\text{MREQ}}$ ) to indicate that the interrupting device can place an 8-bit vector on the data bus. The CPU automatically adds two Wait states to this cycle.

NOTES: 1)  $T_{L1}$  = Last state of any instruction cycle. 2)  $T_{WA}$  = Wait cycle automatically inserted by CPU.

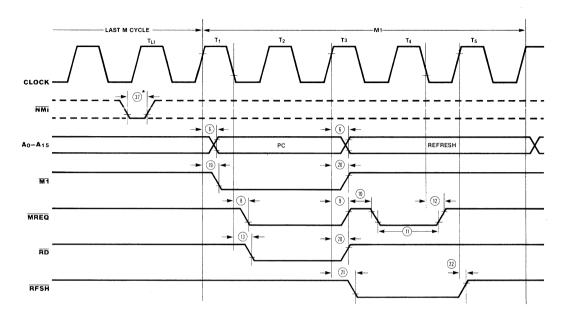

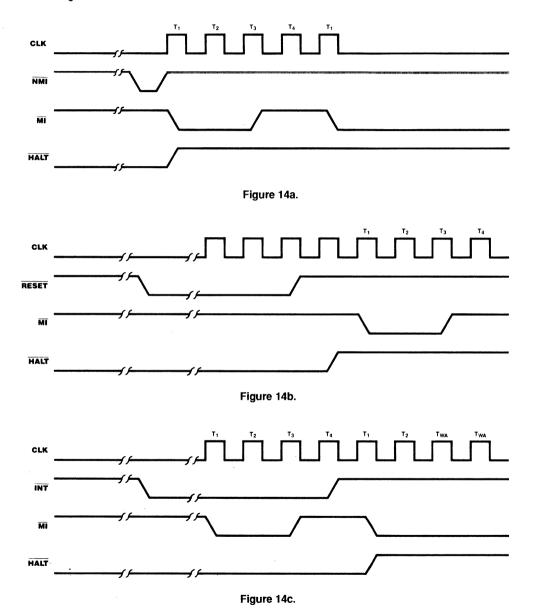

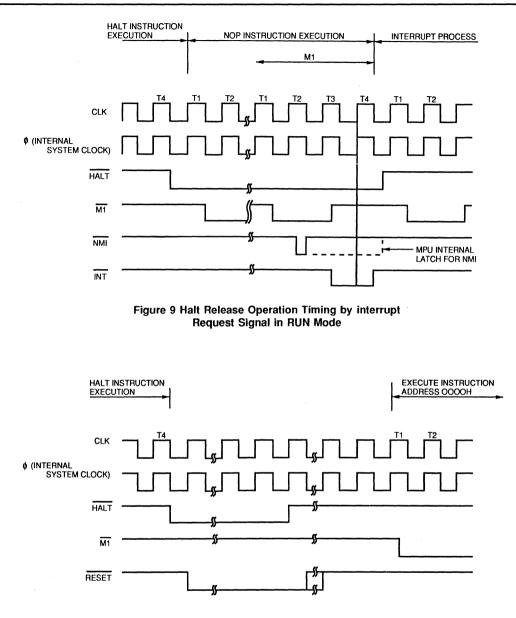

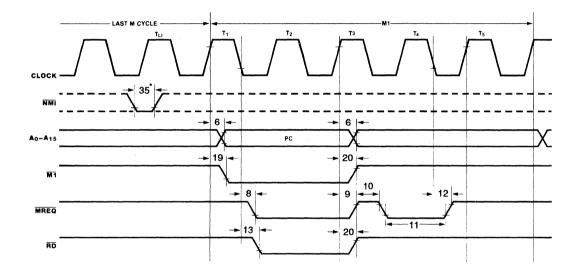

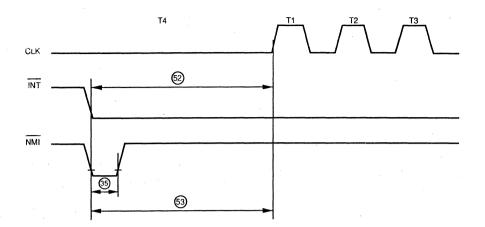

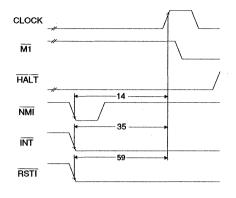

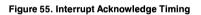

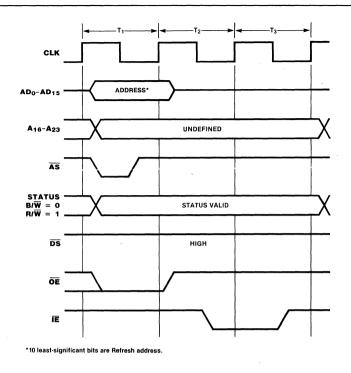

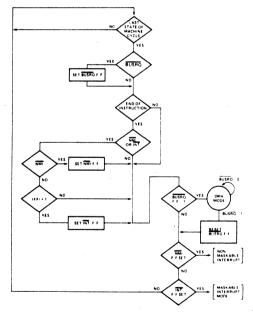

Non-Maskable Interrupt Request Cycle. NMI is sampled at the same time as the maskable interrupt input INT but has higher priority and cannot be disabled under software control. The subsequent timing is similar to that of a normal memory read operation except that data put on the bus by the memory is ignored. The CPU instead executes a restart (RST) operation and jumps to the  $\overline{\text{NMI}}$  service routine located at address 0066H (Figure 9).

\*Although NMI is an asynchronous input, to guarantee its being recognized on the following machine cycle, NMI's falling edge must occur no later than the rising edge of the clock cycle preceding the last state of any instruction cycle (TLI).

#### Figure 9. Non-Maskable Interrupt Request Operation

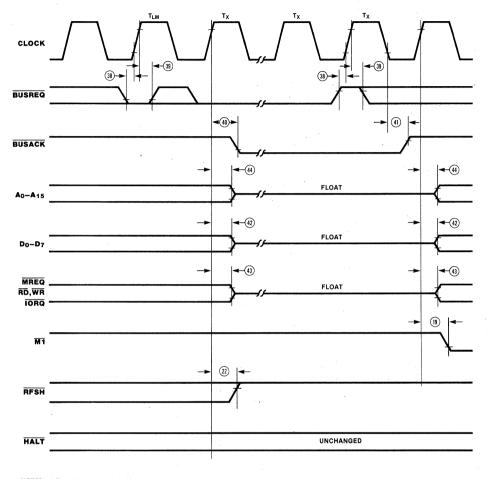

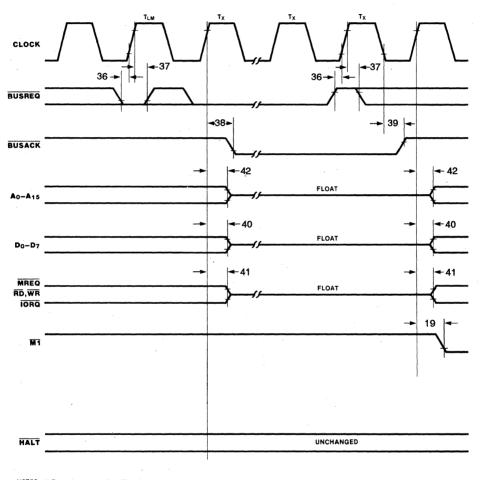

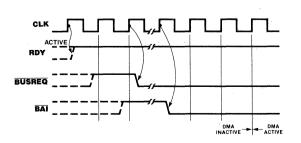

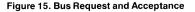

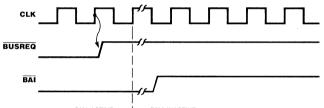

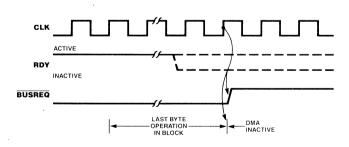

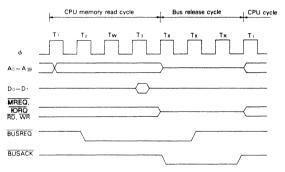

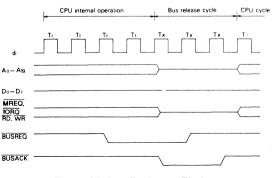

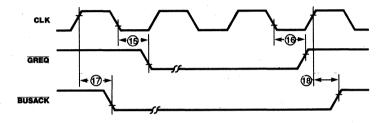

**Bus Request/Acknowledge Cycle.** The CPU samples BUSREQ with the rising edge of the last clock period of any machine cycle (Figure 10). If BUSREQ is active, the CPU sets its address, data, and MREQ, IORQ, RD, and WR lines

to a high-impedance state with the rising edge of the next clock pulse. At that time, any external device can take control of these lines, usually to transfer data between memory and I/O devices.

NOTES: 1) T<sub>LM</sub> = Last state of any M cycle. 2) T<sub>X</sub> = An arbitrary clock cycle used by requesting device.

Figure 10. BUS Request/Acknowledge Cycle

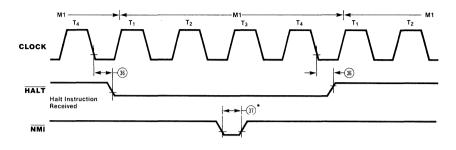

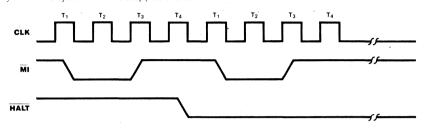

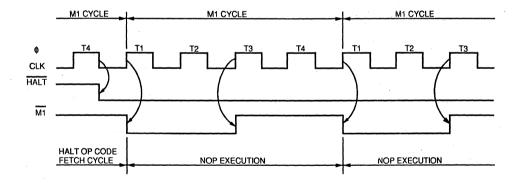

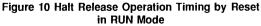

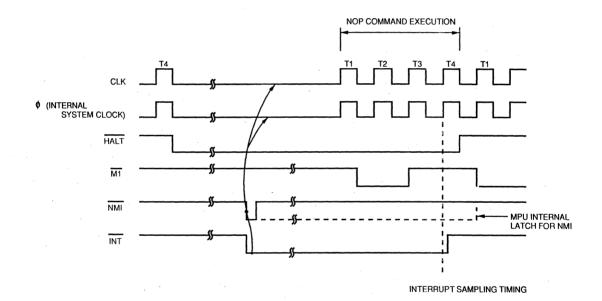

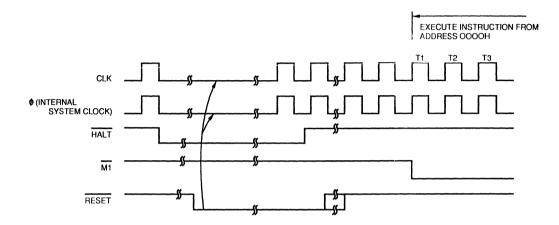

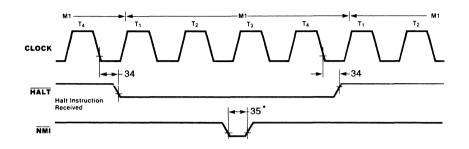

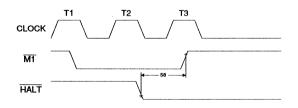

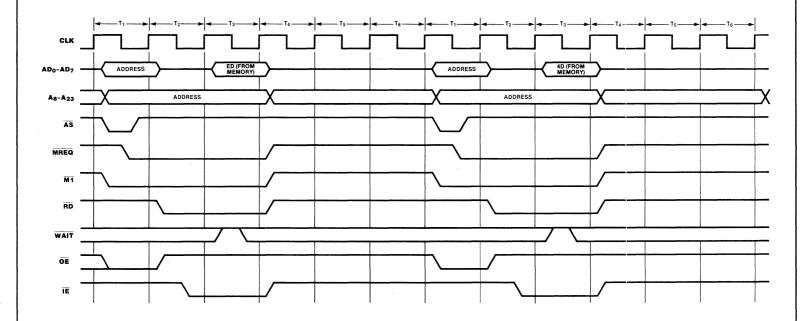

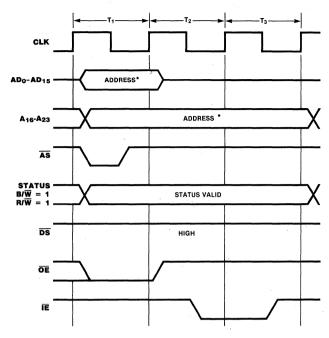

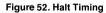

Halt Acknowledge Cycle. When the CPU receives a HALT instruction, it executes NOP states until either an INT or NMI input is received. When in the Halt state, the HALT output is

active and remains so until an interrupt is received (Figure 11). INT will also force a Halt exit.

\*Although NMI is an asynchronous input, to guarantee its being recognized on the following machine cycle, NMI's falling edge must occur no later than the rising edge of the clock cycle preceding the last state of any instruction cycle (T<sub>L</sub>).

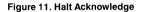

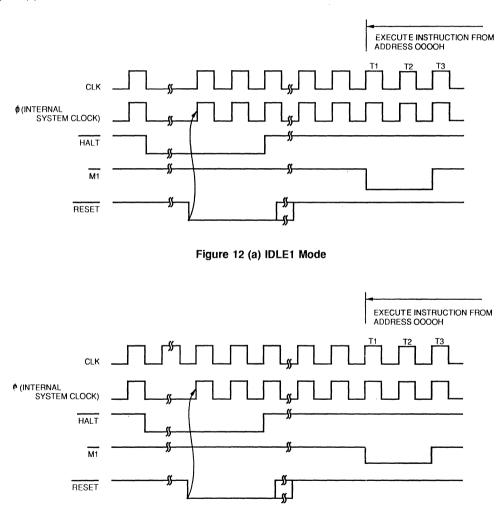

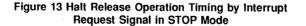

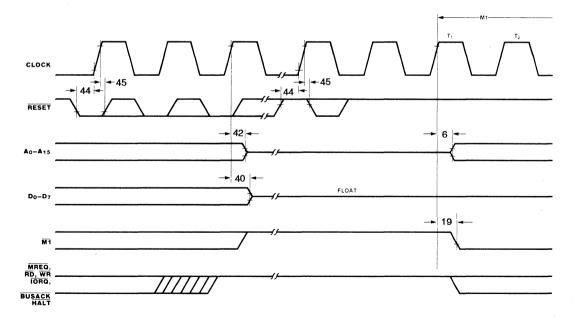

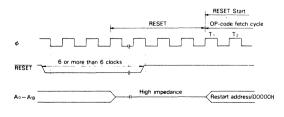

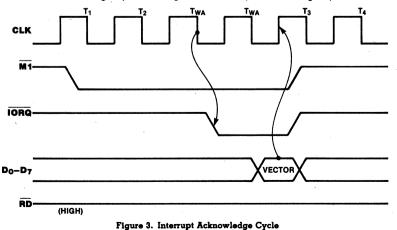

**Reset Cycle.** RESET must be active for at least three clock cycles for the CPU to properly accept it. As long as RESET remains active, the address and data buses float, and the control outputs are inactive. Once RESET goes inactive, two

internal T cycles are consumed before the CPU resumes normal processing operation. RESET clears the PC register, so the first opcode fetch will be to location 0000H (Figure 12).

Figure 12. Reset Cycle

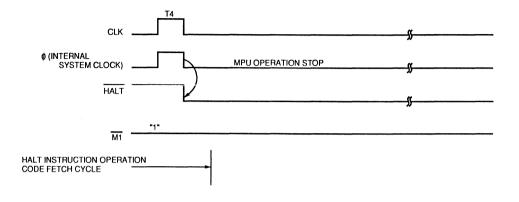

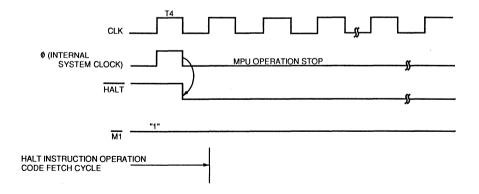

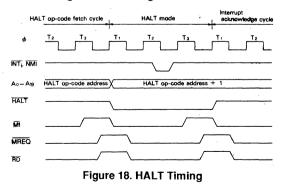

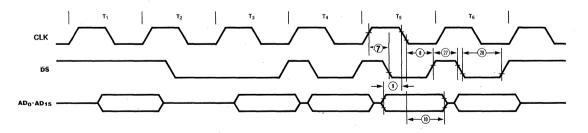

Power-Down mode of operation (Only applies to CMOS Z80 CPU).

CMOS Z80 CPU supports Power-Down mode of operation.

**Power-Down Acknowledge Cycle.** When the clock input to the CPU is stopped at either a High or Low level, the CPU stops its operation and maintains all registers and control signals. However,  $I_{cc2}$  (standby supply current) is guaranteed only when the system clock is stopped at a Low

This mode is also referred to as the "standby mode", and supply current for the CPU goes down as low as 10 uA (Where specified as  $lcc_2$ ).

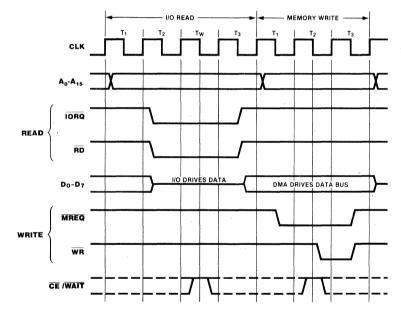

level during  $T_4$  of the machine cycle following the execution of the HALT instruction. The timing diagram for the power-down function, when implemented with the HALT **instruction, is shown in Figure 13.**

Figure 13. Power-Down Acknowledge

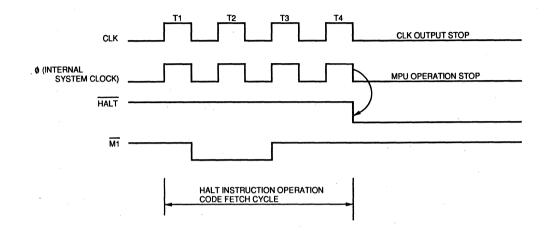

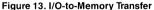

**Power-Down Release Cycle.** The system clock must be supplied to the CPU to release the power-down state. When the system clock is supplied to the CLK input, the CPU restarts operations from the point at which the power-down state was implemented.

NOTES:

When the external oscillator has been stopped to enter the power-down state. some warm-up time may be required to obtain a stable clock for the release.

The timing diagrams for the release from power-down mode are shown in Figure 14.

2) When the HALT instruction is executed to enter the power-down state, the CPU will also enter the Halt state. An interrupt signal (either NMI or INT) or a RESET signal must be applied to the CPU after the system clock is supplied in order to release the power-down state.

Figure 13. Power-Down Release

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on $V_{CC}$ with respect to $V_{SS}$ |

|----------------------------------------------|

| Voltages on all inputs with respect          |

| to V <sub>SS</sub>                           |

| Operating Ambient                            |

| Temperature                                  |

| Storage Temperature                          |

|                                              |

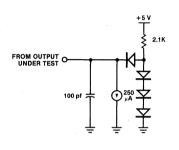

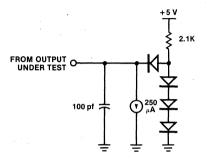

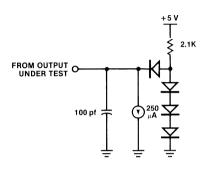

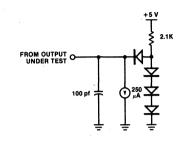

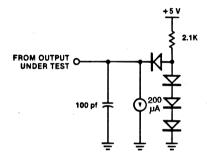

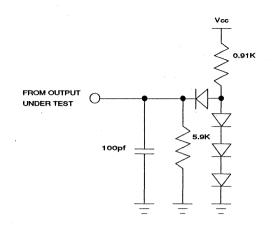

#### STANDARD TEST CONDITIONS

The DC Characteristics and capacitance sections below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND (0V). Positive current flows into the referenced pin.

Available operating temperature ranges are:

- S = 0°C to +70°C Voltage Supply Range:

- NMOS: +4.75V ≥ V<sub>cc</sub> ≥ +5.25V

CMOS: +4.50V ≥ V<sub>cc</sub> ≥ 5.50V

■ E = -40°C to 100°C, +4.50V ≥ V<sub>cc</sub> >+5.50V

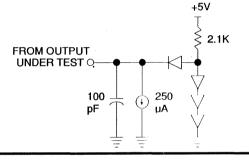

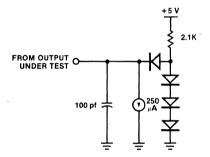

All ac parameters assume a load capacitance of 100 pf. Add 10 ns delay for each 50 pf increase in load up to a maximum of 200 pf for the data bus and 100 pf for address and control lines. AC timing measurements are referenced to 1.5 volts (except for clock, which is referenced to the 10% and 90% points). Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

The Ordering Information section lists temperature ranges and product numbers. Package drawings are in the Package Information section. Refer to the Literature List for additional documentation.

## DC CHARACTERISTICS (Z84C00/CMOS Z80 CPU)

| Symbol                       | Parameter                               | Min                   | Мах                 | Unit     | Condition                              |

|------------------------------|-----------------------------------------|-----------------------|---------------------|----------|----------------------------------------|

| VILC                         | Clock Input Low Voltage                 | - 0.3                 | 0.45                | V        | ······································ |

| VIHC                         | Clock Input High Voltage                | V <sub>CC</sub> – .6  | V <sub>CC</sub> +.3 | V        |                                        |

| VIL                          | Input Low Voltage                       | -0.3                  | 0.8                 | V        |                                        |

| ViH                          | Input High Voltage                      | 2.2                   | V <sub>CC</sub>     | V        |                                        |

| Vol                          | Output Low Voltage                      |                       | 0.4                 | V        | $I_{OL} = 2.0  mA$                     |

| VOH1                         | Output High Voltage                     | 2.4                   |                     | V        | $I_{OH} = -1.6  mA$                    |

| <sup>V</sup> OH <sub>2</sub> | Output High Voitage                     | V <sub>CC</sub> – 0.8 |                     | V        | $I_{OH} = -250 \mu A$                  |

| lcc1                         | Power Supply Current 4 MHz              |                       | 20                  | mA       | $V_{CC} = 5V$                          |

|                              | 6 MHz                                   |                       | 30                  | mA       | $V_{IH} = V_{CC} - 0.2V$               |

|                              | 8 MHz<br>10 MHz                         |                       | 40<br>50            | mA<br>mA | $V_{IL} = 0.2V$                        |

| CC2                          | Standby Supply Current                  |                       | 10                  | μA       | $V_{CC} = 5V$                          |

|                              |                                         |                       |                     |          | CLK = (0)                              |

|                              |                                         |                       |                     |          | $V_{\rm IH} = V_{\rm CC} - 0.2V$       |

|                              |                                         |                       |                     |          | $V_{IL} = 0.2V$                        |

| LI                           | Input Leakage Current                   |                       | 10                  | μA       | $V_{IN} = 0.4$ to $V_{CC}$             |

| LO                           | 3-State Output Leakage Current in Float | - 10                  | 10 <sup>2</sup>     | μA       | $V_{OUT} = 0.4$ to $V_{CC}$            |

|                              |                                         |                       |                     |          |                                        |

Measurements made with outputs floating.

A<sub>15</sub>-A<sub>0</sub>, D<sub>7</sub>-D<sub>0</sub>, MREQ, IORQ, RD, and WR.

I<sub>CC2</sub> standby supply current is guaranteed only when the supplied clock is stopped at a low level during T<sub>4</sub> of the machine cycle immediately following the execution of a HALT instruction.

## CAPACITANCE

| Symbol             | Parameter          | Min | Max | Unit |

|--------------------|--------------------|-----|-----|------|

| C <sub>CLOCK</sub> | Clock Capacitance  |     | 10  | pf   |

| C <sub>IN</sub>    | Input Capacitance  |     | 5   | pf   |

| C <sub>OUT</sub>   | Output Capacitance |     | 15  | pf   |

$T_A = 25^{\circ}C, f = 1 \text{ MHz.}$

Unmeasured pins returned to ground.

# AC CHARACTERISTICS<sup>†</sup> (Z84C00/CMOS Z80 CPU)

|          |              |                                               |         | Z84C0004 |                            | Z84C0006 |         | Z84C0008 |              | Z84C0010 |  |

|----------|--------------|-----------------------------------------------|---------|----------|----------------------------|----------|---------|----------|--------------|----------|--|

| Nu       | umber Symbol | Parameter                                     | Min     | Max      | Min                        | Max      | Min     | Max      | Min          | Max      |  |

| 1        | TcC          | Clock Cycle Time                              | 250*    | DC       | 162*                       | DC       | 125     | DC       | 100          | DC       |  |

| 2        | TwCh         | Clock Pulse Width (High)                      | 110     | DC       | 65                         | DC       | 55      | DC       | 42           | DC       |  |

| 3        | TwCl         | Clock Pulse Width (Low)                       | 110     | DC       | 65                         | DC       | 55      | DC       | 42           | DC       |  |

| 4        | TfC          | Clock Fall Time                               |         | 30       |                            | 20       |         | 10       |              | 10       |  |

| 5        | TrC          | Clock Rise Time                               |         | 30       |                            | 20       |         | 10       |              | 10       |  |

| 5        | TdCr(A)      | Clock † to Address Valid Delay                |         | 110      |                            | 90       |         | 80       |              | 65       |  |

| <b>7</b> | TdA(MREQf)   | Address Valid to MREQ ↓ Delay                 | 65*     |          | 35*                        |          | 20*     |          | 22*          |          |  |

| 3        | TdCf(MREQf)  | Clock ↓ to MREQ ↓ Delay                       |         | 85       |                            | 70       |         | 60       |              | 55       |  |

| )        | TdCr(MREQr)  | Clock † to MREQ † Delay                       |         | 85       |                            | 70       |         | 60       |              | 55       |  |

| 10       | TwMREQh      | MREQ Pulse Width (High)                       | 110* ++ |          | <b>65*</b> ††              |          | 45*++   |          | 32*+-        | t        |  |

| 11       | TwMREQI      | MREQ Pulse Width (Low)                        | 220* ++ |          | 135* ++                    |          | 100* ++ |          | <b>75*</b> + | +        |  |

| 12       | TdCf(MREQr)  | Clock 🖡 to MREQ † Delay                       |         | 85       |                            | 70       |         | 60       |              | 55       |  |

| 13       | TdCf(RDf)    | Clock ↓ to RD ↓ Delay                         |         | 95       |                            | 80       |         | 70       | ,            | 65       |  |

| 14       | TdCr(RDr)    | Clock 🕇 to RD 🕇 Delay                         |         | 85       |                            | 70       |         | 60       |              | 55       |  |

| 15       | TsD(Cr)      | Data Setup Time to Clock †                    | 35      |          | 30                         |          | 30      |          | 25           |          |  |

| 16       | ThD(RDr)     | Data Hold Time to RD 1                        |         | 0        | CANNY STATISTICS AND AND A | 0        |         | 0        |              | 0        |  |

| 17       | TsWAIT(Cf)   | WAIT Setup Time to Clock                      | 70      |          | 60                         |          | 50      |          | 25           |          |  |

| 18       | ThWAIT (Cf)  | WAIT Hold Time after Clock                    | 10      |          | 10                         |          | 10      |          | 10           |          |  |

| 19       | TdCr(M1f)    | Clock † to M1 ↓ Delay                         |         | 100      |                            | 80       |         | 70       |              | 65       |  |

| 20       | TdCr(M1r)    | Clock † to M1 † Delay                         |         | 100      |                            | 80       |         | 70       |              | 65       |  |

| 21       | TdCr(RRSHf)  | Clock † to RFSH ↓ Delay                       |         | 130      |                            | 110      |         | 95       |              | 80       |  |

| 22       | TdCr(RFSHr)  | Clock † to RFSH † Delay                       |         | 120      |                            | 100      |         | 85       |              | 80       |  |

| 23       | TdCf(RDr)    | Clock ↓ to RD ↑ Delay                         |         | 85       |                            | 70       |         | 60       |              | 55       |  |

| 24       | TdCr(RDf)    | Clock ↑ to RD ↓ Delay                         |         | 85       |                            | 70       |         | 60       |              | 55       |  |

| 25       | TsD(Cf)      | Data Setup to Clock ↓ during M <sub>2</sub> , | 50      |          | 40                         |          | 30      |          | 25*          |          |  |

|          |              | $M_3$ , $M_4$ , or $M_5$ Cycles               |         |          |                            |          |         |          |              |          |  |

| 26       | TdA(IORQf)   | Address Stable prior to IORQ +                | 180*    |          | 110*                       | 1        | 75*     |          | 70*          |          |  |

| 27       | TdCr(IORQf)  | Clock ↑ to IORQ ↓ Delay                       |         | 75       |                            | 65       |         | 55       |              | 50       |  |

| 28       | TdCf(IORQr)  | Clock ↓ to IORQ ↑ Delay                       |         | 85       |                            | 70       |         | 60       | 401          | 55       |  |

| 29       | TdD(WRf)Mw   | Data Stable prior to WR I                     | 80*     |          | 25*                        |          | 5*      |          | 40*          |          |  |

\*For clock periods other than the minimums shown, calculate parameters using the table on the following page.

Calculated values above assumed TrC = TfC = 20 ns.

†Units in nanoseconds (ns).

$\uparrow\uparrow$  For loading  $\geq$  50 pf. Decrease width by 10 ns for each additional 50 pf.

# AC CHARACTERISTICS<sup>†</sup> (Z84C00/CMOS Z80 CPU; Continued)

|       |              |                                                        |       | 20004 | Z84C0006 |     | Z84C0008 |          | Z84C0010 |     |

|-------|--------------|--------------------------------------------------------|-------|-------|----------|-----|----------|----------|----------|-----|

| Numb  | er Symbol    | General Parameter                                      | Min   | Max   | Min      | Max | Min      | Max      | Min      | Max |

| 30 T  | dCf(WRf)     | Clock ↓ to WR ↓ Delay                                  |       | 80    |          | 70  |          | 60       |          | 55  |

| 31 T  | wWR          | WR Pulse Width                                         | 220*  |       | 135*     |     | 100*     |          | 75*      |     |

| 32 T  | dCf(WRr)     | Clock ↓ to ₩R ↑ Delay                                  |       | 80    |          | 70  |          | 60       | 10       | 55  |

| 33 T  | dD(WRf)IO    | Data Stable prior to ₩R↓                               | -10*  |       |          |     |          |          | -8*      |     |

| 34 T  | dCr(WRf)     | Clock ↑ to WR ↓ Delay                                  |       | 65    |          | 60  |          | 55       |          | 50  |

| 35 T  | dWRr(D)      | Data Stable from WR †                                  | 60*   |       | 30*      |     | 15*      |          | 12*      |     |

| 36 T  | dCf(HALT)    | Clock ↓ to HALT ↑ or ↓                                 |       | 300   |          | 260 |          | 225      |          | 90  |

| 37 T  | wNMi         | NMI Pulse Width                                        | δŪ    |       | 70       |     | 60       |          | 60       |     |

| 38 T  | sBUSREQ(Cr)  | BUSREQ Setup Time to Clock †                           | 50    |       | 50       |     | 40       |          | 30       |     |

| 39 T  | hBUSREQ(Cr)  | BUSREQ Hold Time after Clock †                         | 10    |       | 10       |     | 10       |          | 10       |     |

| 40 T  | dCr(BUSACKf) | Clock 1 to BUSACK ↓ Delay                              |       | 100   |          | 90  |          | 80       |          | 75  |

| 41 T  | dCf(BUSACKr) | Clock ↓ to BUSACK ↑ Delay                              |       | 100   |          | 90  |          | 80       |          | 75  |

| 42 T  | dCr(Dz)      | Clock 🕇 to Data Float Delay                            |       | 90    |          | 80  |          | 70       |          | 65  |

| 43 T  | dCr(CTz)     | Clock † to Control Outputs                             |       | 80    |          | 70  |          | 60       |          | 60  |

|       |              | Float Delay(MREQ, IORQ,<br>RD, and WR)                 |       |       |          |     |          |          |          |     |

| 44 To | dCr(Az)      | Clock † to Address Float Delay                         |       | 90    |          | 80  |          | 70       |          | 65  |

| 45 To | dCTr(A)      | MREQ †, IORQ †, RD †, and<br>WR † to Address Hold Time | i 80* |       | 35*      |     | 20*      | <u> </u> | 32*      |     |

| 46 T  | sRESET(Cr)   | <b>RESET</b> to Clock † Setup Time                     | 60    |       | 60       |     | 45       |          | 40       |     |

| 47 TI | hRESET(Cr)   | <b>RESET</b> to Clock <sup>†</sup> Hold Time           | 10    |       | 10       |     | 10       |          | 10       |     |

| 48 Ts | sINTf(Cr)    | INT to Clock † Setup Time                              | 80    |       | 70       |     | 55       |          | 50       |     |

| 49 TI | hINTr(Cr)    | INT to Clock † Hold Time                               | 10    |       | 10       |     | 10       |          | 10       |     |

|       | dM1f(IORQf)  | M1 ↓ to IORQ ↓ Delay                                   | 565*  |       | 365*     |     | 270*     |          | 222*     |     |

|       | dCf(IORQf)   | Clock ↓ to IORQ ↓ Delay                                |       | 85    |          | 70  |          | 60       |          | 55  |

|       | dCf(lORQr)   | Clock † to IORQ † Delay                                |       | 85    |          | 70  |          | 60       |          | 55  |

| 53 To | dCf(D)       | Clock ∔ to Data Valid Delay                            |       | 150   |          | 130 |          | 115      |          | 110 |

\*For clock periods other than the minimums shown, calculate parameters using the following table. Calculated values above assumed TrC = TfC = 20 ns.

†Units in nanoseconds (ns).

# FOOTNOTES TO AC CHARACTERISTICS

| Number            | Symbol           | General Parameter       | Z84C0004                           | Z84C0006 | Z84C0008 | Z84C0010 |

|-------------------|------------------|-------------------------|------------------------------------|----------|----------|----------|

| 1                 | TcC              | TwCh + TwCl + TrC +     | TfC                                |          |          |          |

| 7                 | TdA(MREQf)       | TwCh + TfC              | -65                                | -50      | -45      | -45      |

| 10                | TwMREQh          | TwCh + TfC              | -20                                | -20      | -20      | -20      |

| 11                | TwMREQ           | TcC                     | -30                                | -30      | -25      | -25      |

| 26                | TdA(IORQf)       | TcC                     | -70                                | -55      | -50      | -50      |

| 29                | TdD(WRf)         | TcC                     | -170                               | -140     | -120     | -60      |

| 31                | TwWR             | TcC                     | -30                                | -30      | -25      | -25      |

| 33                | TdD(WRf)         | TwCi + TrC              | -140                               | -140     | -120     | -60      |

| 35                | TdWRr(D)         | TwCl + TrC              | -70                                | -55      | -50      | -40      |

| 45                | TdCTr(A)         | TwCl + TrC              | -50                                | -50      | -45      | -30      |

| 50                | TdM1f(lÓRQf)     | 2TcC + TwCh + TfC       | -65                                | -50      | -45      | -30      |

| C Test Conditions |                  | V <sub>OH</sub> = 1.5 V | V <sub>IHC</sub> = V <sub>CC</sub> |          | = ±0.5 V | ·        |

|                   | $V_{IL} = 0.8 V$ | V <sub>OL</sub> = 1.5 V | $V_{ILC} = 0.45$                   | V        |          |          |

#### DC CHARACTERISTICS (Z8400/NMOS Z80 CPU)

All parameters are tested unless otherwise noted.

| Symbol | Parameter                               | Min                  | Max                  | Unit | <b>Test Condition</b>       |

|--------|-----------------------------------------|----------------------|----------------------|------|-----------------------------|

| VILC   | Clock Input Low Voltage                 | - 0.3                | 0.45                 | V    |                             |

| VIHC   | Clock Input High Voltage                | V <sub>CC</sub> – .6 | V <sub>CC</sub> + .3 | V    |                             |

| VIL    | Input Low Voltage                       | - 0.3                | 0.8                  | V    |                             |

| VIH    | Input High Voltage                      | 2.0 <sup>1</sup>     | Vcc                  | V    | ,                           |

| VOL    | Output Low Voltage                      |                      | 0.4                  | V    | $I_{OL} = 2.0 \text{ mA}$   |

| VOH    | Output High Voltage                     | 2.41                 |                      | V    | I <sub>OH</sub> = -250 μA   |

| Icc    | Power Supply Current                    |                      | 200                  | mA   | Note 3                      |

| ILI    | Input Leakage Current                   |                      | 10                   | μA   | $V_{IN} = 0$ to $V_{CC}$    |

| ILO    | 3-State Output Leakage Current in Float | - 10                 | 10 <sup>2</sup>      | μA   | $V_{OUT} = 0.4$ to $V_{CC}$ |

For military grade parts, refer to the Z80 Military Electrical Specification.

A<sub>15</sub>-A<sub>0</sub>, D<sub>7</sub>-D<sub>0</sub>, MREQ, IORQ, RD, and WR.

Measurements made with outputs floating.

#### CAPACITANCE

Guaranteed by design and characterization.

| Symbol             | Parameter          | Min   | Max | Unit |

|--------------------|--------------------|-------|-----|------|

| C <sub>CLOCK</sub> | Clock Capacitance  | · · · | 35  | pf   |

| C <sub>IN</sub>    | Input Capacitance  |       | 5   | pf   |

| C <sub>OUT</sub>   | Output Capacitance |       | 15  | pf   |

NOTES:

$T_A = 25 \circ C$ , f = 1 MHz.

Unmeasured pins returned to ground.

# AC CHARACTERISTICS<sup>†</sup> (Z8400/NMOS Z80 CPU)

| Number | Symbol       | Parameter                                                                                                   | <b>Z084</b><br>Min | 10004<br>Max | <b>Z08</b> 4<br>Min | 0006<br>Max | Z084<br>Min  | 0008<br>Max |

|--------|--------------|-------------------------------------------------------------------------------------------------------------|--------------------|--------------|---------------------|-------------|--------------|-------------|

| 1      | TcC          | Clock Cycle Time                                                                                            | 250*               |              | 162*                |             | 125*         |             |

| 2      | TwCh         | Clock Pulse Width (High)                                                                                    | 110                | 2000         | 65                  | 2000        | 55           | 2000        |

| 3      | TwCl         | Clock Pulse Width (Low)                                                                                     | 110                | 2000         | 65                  | 2000        | 55           | 2000        |

| 4      | TfC          | Clock Fall Time                                                                                             |                    | 30           |                     | 20          |              | 10          |

| 5      | TrC          | Clock Rise Time                                                                                             |                    | 30           |                     | 20          |              | 10          |

| 6      | TdCr(A)      | Clock to Address Valid Delay                                                                                |                    | 110          |                     | 90          |              | 80          |

| 7      | TdA(MREQf)   | Address Valid to MREQ ↓ Delay                                                                               | 65*                |              | 35*                 |             | 20*          |             |

| 8      | TdCf(MREQf)  | Clock ↓ to MREQ ↓ Delay                                                                                     |                    | 85           |                     | 70          |              | 60          |

| 9      | TdCr(MREQr)  | Clock ↑ to MREQ ↑ Delay                                                                                     |                    | 85           |                     | 70          |              | 60          |

| 10     | TwMREQh      | MREQ Pulse Width (High)                                                                                     | 110*-              | #            | 65*                 | Ħ           | 45* <b>†</b> | t           |

| 11     | TwMREQI      | MREQ Pulse Width (Low)                                                                                      | 220*               | #            | 135* <b>1</b>       | +           | 100*†        | t           |

| 12     | TdCf(MREQr)  | Clock ↓ to MREQ ↑ Delay                                                                                     |                    | 85           |                     | 70          |              | 60          |

| 13     | TdCf(RDf)    | Clock↓to RD↓Delay                                                                                           |                    | 95           |                     | 80          |              | 70          |

| 14     | TdCr(RDr)    | Clock ↑ to RD ↑ Delay                                                                                       |                    | 85           |                     | 70          |              | 60          |

| 15     | TsD(Cr)      | Data Setup Time to Clock ↑                                                                                  | 35                 |              | 30                  |             | 30           |             |

| 16     | ThD(RDr)     | Data Hold Time to $\overline{RD}$ †                                                                         |                    | 0            |                     | 0           |              | 0           |

| 17     | TsWAIT(Cf)   | WAIT Setup Time to Clock ↓                                                                                  | 70                 |              | 60                  |             | 50           |             |

| 18     | ThWAIT(Cf)   | WAIT Hold Time after Clock ↓                                                                                |                    | 0            |                     | 0           |              | 0           |

| 19     | TdCr(M1f)    | Clock↑to M1↓Delay                                                                                           |                    | 100          |                     | 80          |              | 70          |

| 20     | TdCr(M1r)    | Clock ↑ to M1 ↑ Delay                                                                                       |                    | 100          |                     | 80          |              | 70          |

| 21     | TdCr(RFSHf)  | Clock ↑ to RFSH ↓ Delay                                                                                     |                    | 130          |                     | 110         |              | 95          |

| 22     | TdCr(RFSHr)  | Clock ↑ to RFSH ↑ Delay                                                                                     |                    | 120          |                     | 100         |              | 85          |

| 23     | TdCf(RDr)    | Clock ↓ to RD ↑ Delay                                                                                       |                    | 85           |                     | 70          |              | 60          |

| 24     | TdCr(RDf)    | Clock ↑ to RD ↓ Delay                                                                                       |                    | 85           |                     | 70          |              | 60          |

| 25     | TsD(Cf)      | Data Setup to Clock ↓ during M <sub>2</sub> , M <sub>3</sub> ,<br>M <sub>4</sub> , or M <sub>5</sub> Cycles | 50                 |              | 40                  |             | 30           |             |

| 26     | TdA(IORQf)   | Address Stable prior to IORQ ↓                                                                              | 180*               |              | 110*                |             | 75*          |             |

| 27     | TdCr(IORQf)  | Clock ↑ to IORQ ↓ Delay                                                                                     |                    | 75           |                     | 65          |              | 55          |

| 28     | TdCf(IORQr)  | Clock ↓ to IORQ ↑ Delay                                                                                     |                    | 85           |                     | 70          |              | 60          |

| 29     | TdD(WRf)     | Data Stable prior to WR↓                                                                                    | 80*                |              | 25*                 |             | 5*           |             |

| 30     | TdCf(WRf)    | Clock↓to WR↓Delay                                                                                           |                    | 80           |                     | 70          |              | 60          |

| 31     | TwWR         | WR Pulse Width                                                                                              | 220*               |              | 135*                |             | 100*         |             |

| 32     | TdCf(WRr)    | Clock ↓ to WR ↑ Delay                                                                                       |                    | 80           |                     | 70          |              | 60          |

| 33     | TdD(WRf)     | Data Stable prior to $\overline{WR}$ $\downarrow$                                                           | -10*               |              | -55*                |             | 55*          |             |

| 34     | TdCr(WRf)    | Clock ↑ to WR ↓ Delay                                                                                       |                    | 65           |                     | 60          |              | 55          |

| 35     | TdWRr(D)     | Data Stable from WR↑                                                                                        | 60*                |              | 30*                 |             | 15*          |             |

| 36     | TdCf(HALT)   | Clock ↓ to HALT ↑ or ↓                                                                                      |                    | 300          |                     | 260         |              | 225         |

| 37     | TwNMI        | NMI Pulse Width                                                                                             | 80                 |              | 70                  |             | 60*          |             |

| 38     | TsBUSREQ(Cr) | BUSREQ Setup Time to Clock ↑                                                                                | 50                 |              | 50                  |             | 40           |             |

\*For clock periods other than the minimums shown, calculate parameters using the table on the following page. Calculated values above assumed TrC = TfC = 20 ns. †Units in nanoseconds (ns).

# For loading  $\geq$  50 pf., Decrease width by 10 ns for each additional 50 pf.

# AC CHARACTERISTICS<sup>†</sup> (Z8400/NMOS Z80 CPU; Continued)

|        |               |                                                                                                                                        | <b>Z08</b> 4 | 0004 | <b>Z0</b> 84 | 0006 | Z084 | 8000 |

|--------|---------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|------|--------------|------|------|------|

| Number | Symbol        | Parameter                                                                                                                              | Min          | Max  | Min          | Max  | Min  | Max  |

| 39     | ThBUSREQ(Cr)  | BUSREQ Hold Time after Clock 1                                                                                                         | 0            |      | 0            |      | 0    |      |

| 40     | TdCr(BUSACKf) | Clock ↑ to BUSACK ↓ Delay                                                                                                              |              | 100  |              | 90   |      | 80   |

| 41     | TdCf(BUSACKr) | Clock ↓ to BUSACK ↑ Delay                                                                                                              |              | 100  |              | 90   |      | 80   |

| 42     | TdCr(Dz)      | Clock ↑ to Data Float Delay                                                                                                            |              | 90   |              | 80   |      | 70   |

| 43     | TdCr(CTz)     | Clock t to Control Outputs Float Delay<br>(MREQ, IORQ, RD, and WR)                                                                     |              | 80   |              | 70   | ,    | 60   |

| 44     | TdCr(Az)      | Clock ↑ to Address Float Delay                                                                                                         | ĸ            | 90   |              | 80   |      | 70   |

| 45     | TdCTr(A)      | $\overline{\text{MREQ}}$ †, $\overline{\text{IORQ}}$ †, $\overline{\text{RD}}$ †, and $\overline{\text{WR}}$ † to<br>Address Hold Time | 80*          |      | 35*          |      | 20*  |      |

| 46     | TsRESET(Cr)   | RESET to Clock 1 Setup Time                                                                                                            | 60           |      | 60           |      | 45   |      |

| 47     | ThRESET(Cr)   | RESET to Clock ↑ Hold Time                                                                                                             |              | 0    |              | 0    |      | 0    |

| 48     | TsINTf(Cr)    | INT to Clock ↑ Setup Time                                                                                                              | . 80         |      | 70           |      | 55   |      |

| 49     | ThINTr(Cr)    | INT to Clock ↑ Hold Time                                                                                                               |              | 0    |              | 0    |      | 0    |

| 50     | TdM1f(IORQf)  | M1 ↓ to IORQ ↓ Delay                                                                                                                   | 565*         |      | 365*         |      | 270* |      |

| 51     | TdCf(IORQf)   | Clock ↓ to IORQ ↓ Delay                                                                                                                |              | 85   |              | 70   |      | 60   |

| 52     | TdCf(IORQr)   | Clock ↑ IORQ ↑ Delay                                                                                                                   |              | 85   |              | 70   |      | 60   |

| 53     | TdCf(D)       | Clock ↓ to Data Valid Delay                                                                                                            |              | 150  |              | 130  |      | 115  |

\*For clock periods other than the minimums shown, calculate parameters using the following table. Calculated values above assumed TrC = TfC = 20 ns.

†Units in nanoseconds (ns).

#### FOOTNOTES TO AC CHARACTERISTICS

| Number | Symbol       | General Parameter       | Z0840004 | <b>Z0840006</b>                                   | Z0840008 |

|--------|--------------|-------------------------|----------|---------------------------------------------------|----------|

| 1      | TcC          | TwCh + TwCl + TrC + TfC |          | han analy a surveyork to some the analysis of the |          |

| 7      | TdA(MREQf)   | TwCh + TfC              | - 65     | - 50                                              | - 45     |

| 10     | TwMREQh      | TwCh + TfC              | - 20     | - 20                                              | - 20     |

| 11     | TwMREQI      | TcC                     | - 30     | - 30                                              | - 25     |

| 26     | TdA(IORQf)   | TcC                     | - 70     | - 55                                              | - 50     |

| 29     | TdD(WRf)     | TcC                     | - 170    | - 140                                             | - 120    |

| 31     | TwWR         | ТсС                     | - 30     | - 30                                              | - 25     |

| 33     | TdD(WRf)     | TwCl + TrC              | - 140    | - 140                                             | - 120    |

| 35     | TdWRr(D)     | TwCl + TrC              | - 70     | - 55                                              | - 50     |

| 45     | TdCTr(A)     | TwCl + TrC              | - 50     | - 50                                              | - 45     |

| 50     | TdM1f(IORQf) | 2TcC + TwCh + TfC       | - 65     | - 50                                              | - 45     |

|        |              |                         |          |                                                   |          |

AC Test Conditions:

January 1989

# PRELIMINARY Product Specification

# Z84C01 Z80<sup>®</sup> CPU with Clock Generator/Controller

#### FEATURES:

- Commands compatible with the Zilog Z80 MPU

- Low power consumption

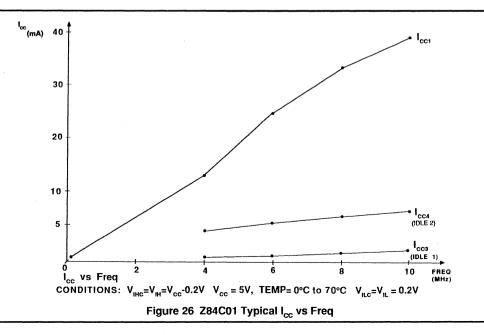

40mA Typ (5V, 10 MHz under RUN mode) 2mA Typ (5V, 10 MHz under IDLE1 mode) 10mA Typ (5V, 10 MHz under IDLE2 mode) .5 $\mu$  A Typ (5V under STOP mode)

- DC to 10 MHz operation (at 5V±10%)

- Single 5V power supply (at 5V±10%)

- Operating temperature (0° C to 70° C)

- On-chip clock generator

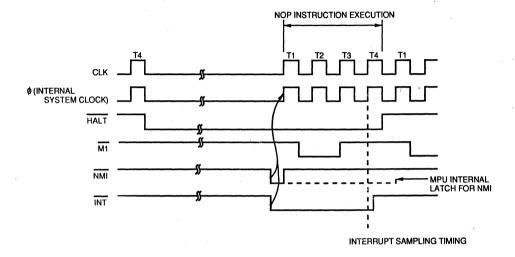

- In the HALT state, the following 4 modes are selectable:

RUN mode IDLE 1 mode IDLE 2 mode STOP mode

- Powerful set of 158 instructions

- Powerful interrupt function

Non-maskable interrupt terminal (NMI)

Maskable interrrupt terminal (INT)

- The following three modes are selectable: 8080 compatible interrupt mode (interrupt by Non-Z80 family peripheral LSI) (Mode 0) Restart interrupt (Mode 1) Daisy-chain structure interrupt using Z80 family peripheral LSI (Mode 2)

- An auxiliary register provided to each of general purpose registers.

- 2 index registers

- 10 addressing modes

- Built-in refresh circuit for dynamic memory

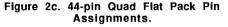

- Molded in 44-pin PLCC package

#### **GENERAL DESCRIPTION:**

The Z84C01 is an 8-bit microprocessor (hereinafter referred to as MPU) with a built-in clock generator/controller, which provides low power operation and high performance.

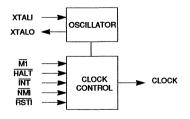

Built into the Z84C01 is a control function and clock generator for the standby function in addition to:six paired general purpose registers, accumulator, flag registers, an arithmetic-and-logic unit, bus control, memory control and timing control circuits.

The Z84C01 is fabricated with Zilog CMOS technology and molded in a 44-pin PLCC package.

Further, in the following text and explanations for charts and tables, hexadecimal numbers are directly used without giving an identification to explanation of address, etc. so as not to cause confusions.

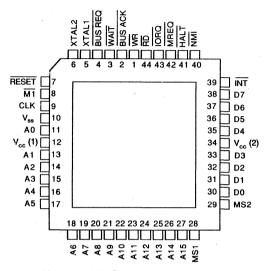

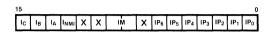

#### **PIN CONNECTIONS AND PIN FUNCTIONS:**

The pin connections and I/O pin names and brief functions of the Z84C01 are shown below. Pin Names and Functions. I/O pin names and functions are as shown in Table 1.

**Pin Connections.** The pin connections of the Z84C01 are as shown in Fig. 1.

Figure 1. Pin Connections (Top View)

| Pin Name | Number<br>of Pin | Input/Output<br>3-state | Function                                                                                                                                                                                                                                                  |

|----------|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 - A15 | 16               | Output<br>3-state       | 16-bit address bus.<br>Specify addresses of memories and I/O to be<br>accessed. During the refresh period, addresses<br>for refreshing are output.                                                                                                        |

| MS1, MS2 | 2                | Input                   | Mode selection input.<br>One of 4 modes (Run, IDLE1/2, STOP) is<br>selected according to the state of these 2 pins.                                                                                                                                       |

| D0 - D7  | 8                | I/O<br>3-state          | 8-bit bidirectional data bus.                                                                                                                                                                                                                             |

| INT      | 1                | Input                   | Maskable interrupt request signal.<br>Interrupt is generated by peripheral LSI. This signal is<br>accepted if the interrupt enable flip-flop (IFF) is set at "1".<br>INT is normally wired-OR and requires an external pull up<br>for these applications. |

| Table | 1 | Pin | Names | and | Functions |

|-------|---|-----|-------|-----|-----------|

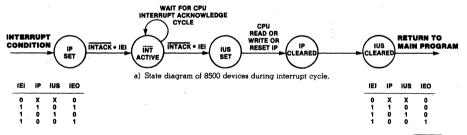

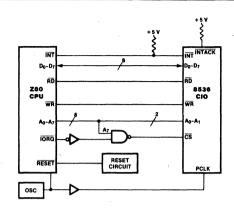

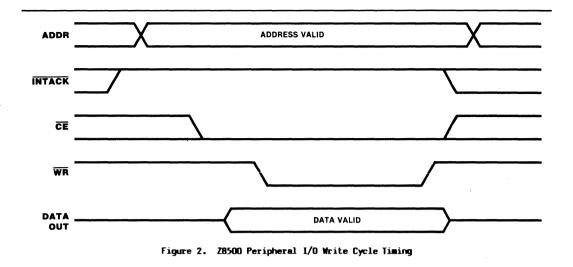

|-------|---|-----|-------|-----|-----------|