# Assembly Language Programming Manual

Zilog

# **Z8 PLZ/ASM**

# Assembly Language Programming Manual

December 1980

Copyright 1980 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog.

Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied. and the second

# Preface

This reference manual describes assembly language programming for Zilog's Z8 single-chip microcomputer. The first three sections of the manual focus on Z8 design features and the assembly-language instruction set. Sections 4 and 5 provide additional information needed to build a source program, including the use of high-level PLZ statements.

This manual is one in a series describing the Z8. You will need several other manuals to develop, debug, and run Z8 assembly-language programs. Programs are developed on either Zilog's microcomputer system (MCZ) or the Zilog development system (ZDS) using the software capabilities of the RIO operating system. The manuals needed to use the operating system are:

Z80 RIO Operating System User's Manual, 03-0072-01

Z80 RIO Text Editor User's Manual, 03-0074-00

The Z8 assembler produces relocatable object modules. Operation of the assembler and object module linkage and relocation are described in the:

Z8 PLZ/ASM Assembler User Guide, 03-3048-02

PLZ Linker User Guide, 03-3098-02

Finally, while this programming manual includes an overview of the Z8 architecture, you will need the following manual for detailed hardware and configuration information:

Z8 Microcomputer Technical Manual, 03-3047-02

# Contents

| SECTION 1 | ARCH              | IITECTURAL OVERVIEW                                                                                                                                                                                                                                          |                      |

|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|           | 1.1<br>1.2        | Introduction 1-1<br>Memory Segments 1-2                                                                                                                                                                                                                      |                      |

|           |                   | 1.2.1Program Memory1-31.2.2External Data Memory1-31.2.3Register Memory1-31.2.4Data Lengths1-3                                                                                                                                                                | 3<br>3               |

|           | 1.3               | Input/Output 1-8                                                                                                                                                                                                                                             | В                    |

|           |                   | 1.3.1       Port 1       1-8         1.3.2       Port 0       1-8         1.3.3       Port 2       1-1         1.3.4       Port 3       1-1                                                                                                                  | 8<br>1(              |

|           | 1.4<br>1.5<br>1.6 | Interrupts 1-1<br>Timers/Counters 1-1<br>Status Flags and Program Controls 1-1                                                                                                                                                                               | 1 ]                  |

|           |                   | 1.6.1       Carry Flag       1-1         1.6.2       Zero Flag       1-1         1.6.3       Sign Flag       1-1         1.6.4       Overflow Flag       1-1         1.6.5       Decimal Adjust Flag       1-1         1.6.6       Half Carry Flag       1-1 | 1:<br>1:<br>1:<br>1: |

|           | 1.7               | Stack Memory 1-1                                                                                                                                                                                                                                             | 1!                   |

| SECTION 2 | Z8 A              | SSEMBLER CONVENTIONS                                                                                                                                                                                                                                         |                      |

|           | 2.1<br>2.2        | Assembler Overview 2-1<br>Assembly Language Statement Format 2-1                                                                                                                                                                                             |                      |

|           |                   | 2.2.1Program Labels and Identifiers2-22.2.2Instruction2-32.2.3Operand Field2-32.2.4Comments2-5                                                                                                                                                               | 3<br>3               |

|           | 2.3               | Arithmetic Operands 2-5                                                                                                                                                                                                                                      | 5                    |

|           |                   | <ul> <li>2.3.1 Run-Time Versus Assembly-Time<br/>Arithmetic</li></ul>                                                                                                                                                                                        | 7<br>8               |

#### CONTENTS (cont.) SECTION 2 Z8 ASSEMBLER CONVENTIONS (cont.) 2.4 Z8 Addressing Modes ..... 2-13 2.4.1 Register Address ..... 2-13 Indirect-Register Address ..... 2-15 2.4.2 2.4.3 Indexed Address ..... 2-16 2.4.5 Relative Address ..... 2-17 Immediate Data ..... 2-18 2.4.6 2.4.7 A Note on the Register Pointer ..... 2-19 SECTION 3 ASSEMBLY-LANGUAGE INSTRUCTION SET Functional Summary ..... 3-1 3.1 3.2 3.3 SECTION 4 STRUCTURING A Z8 PROGRAM 4.1 4.2 Program Structure ..... 4-1 4.2.1 Modules ..... 4-1 4.2.2 Procedures ..... 4-2 4.2.3 DO Loops ..... 4-3 4.2.4 IF Statements ..... 4-4 4.2.5 Scope ..... 4-5 4.2.6 Summary ..... 4-6 4.3 Relocatability ..... 4-8 4.3.1 Sections ..... 4-8 4.3.2 Location Counter Control ..... 4-10 4.3.3 Modes of Arithmetic Expressions ..... 4-10 SECTION 5 PLZ/ASM HIGH-LEVEL STATEMENTS 5.1 5.2 Program Structuring Statements ..... 5-2 5.2.1 Module Declaration ..... 5-2 5.2.2 5.2.3 DO Statement ..... 5-4 5.2.4 IF Statement ..... 5-5 IF-CASE Statement ..... 5-7 5.2.5

Jump Optimization ..... 5-8

5.2.6

## SECTION 5 PLZ/ASM HIGH-LEVEL STATEMENTS (cont.)

| 5.3 | .3 Defining Data                 |                                                                                                                      |                              |  |  |  |

|-----|----------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|

|     | 5.3.2<br>5.3.3<br>5.3.4<br>5.3.5 | Constant Definition<br>Data Types<br>Type Definition<br>Variable Declaration<br>Label Declaration<br>SIZEOF Operator | 5-11<br>5-14<br>5-14<br>5-19 |  |  |  |

- APPENDIX A ASSEMBLY-LANGUAGE INSTRUCTION SUMMARY

- APPENDIX B HIGH-LEVEL STATEMENT SUMMARY

## APPENDIX C ASSEMBLER DIRECTIVES AND PSEUDO INSTRUCTIONS

|            | C.1 Assembler Directives C-1<br>C.2 Pseudo Instructions C-4<br>C.3 Conditional Assembly C-4 |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| APPENDIX D | RESERVED WORDS AND SPECIAL CHARACTERS                                                       |  |  |  |  |

|            | D.1 Reserved Words D-1<br>D.2 Special Characters D-2                                        |  |  |  |  |

|            |                                                                                             |  |  |  |  |

APPENDIX E ASCII CHARACTER SET

INDEX

## LIST OF ILLUSTRATIONS

## Figure

| 1-1 | Z8 Memory Segments               | 1-2   |

|-----|----------------------------------|-------|

| 1-2 | Working-Register Groups          | 1 - 4 |

|     | Control Registers                |       |

|     | Data Lengths                     |       |

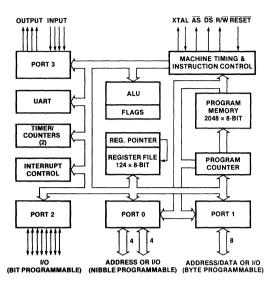

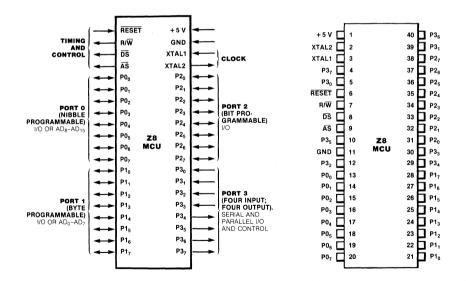

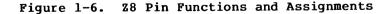

| 1-5 | Z8 Architecture Diagram          | 1-9   |

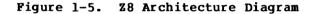

| 1-6 | Z8 Pin Functions and Assignments | 1-9   |

## Section 1 Architectural Overview

## 1.1 Introduction

Zilog's Z8 microcomputer introduces a new generation of single-chip architecture. Compared to earlier single-chip microcomputers, the Z8 offers faster execution, more efficient use of memory, more sophisticated interrupt, input/output (I/O), and bit-manipulation capabilities, and easier system expansion. Under program control, the Z8 configuration can be tailored to the needs of its user. It can serve as an I/O-intensive microcomputer, as an intelligent peripheral controller within a larger system, or as a memory-intensive microprocessor.

The Z8's features include a powerful repertoire of 43 instructions, similar in form to the instruction sets of the Z80 and Z8000 microprocessor families. The efficiency of these instructions and of the Z8's internal register-addressing scheme not only speeds program execution, but also packs more program into the Z8 chip than would be possible with comparable microcomputers. This is, of course, extremely important for single-chip devices where on-chip memory space is limited.

Real-time control applications, for which the Z8 is particularly suited, require fast instruction execution and fast interrupt response. Operating from an 8 MHz clock source (internal 4 MHz clock rate), the Z8 executes most instructions in 1.5 to 2.5 microseconds (6 to 10 machine cycles). The longest instruction takes 5 microseconds (20 cycles).

The following summarizes the main features of the Z8:

- 40-pin package, offering more I/O program control than previously available in single-chip microcomputers;

- On-chip, 2K-byte, read-only (ROM) program memory with possible expansion by 62K of external program memory;

- On-chip, 144-byte, random-access (RAM) register memory, including 4 I/O ports and 16 control registers;

- Possible 62K bytes external data memory;

- Six maskable and prioritized interrupts;

- Two on-chip interval timers, also programmable as event counters;

- Independent on-chip UART with hardware parity generator and checker;

- On-chip clock for internal timing.

The remainder of this section describes in more detail those 28 features of primary interest to assembly-language programmers. See the 28 Technical Manual for detailed architectural and configuration information.

#### 1.2 Memory Segments

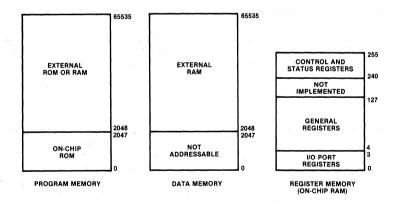

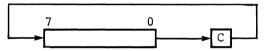

As shown in Figure 1-1, the Z8 has three separate memory segments for storing program instructions and data.

- Program memory (chip resident or external)

- Data memory (external)

- Register memory (chip resident)

The latter includes I/O registers, control and status registers, and general purpose data registers.

Figure 1-1. Z8 Memory Segments

The Z8 hardware environment must be specifically configured to access external program or data memory. Both segments can be accessed by 16-bit addresses.

#### 1.2.1 Program Memory

The first 2048 bytes of program memory consist of on-chip programmable storage addressed by the program counter. For addresses 2048 or greater, the Z8 automatically executes external program memory fetches (provided the Z8 is configured accordingly). The first example below jumps to address 1500 if the Zero flag (Z) is set. The second calls a procedure whose starting address is location 20000 in external program memory.

> JP Z,1500 CALL 20000

The first 12 bytes of program memory are reserved for the Z8's interrupt mechanism. Addresses 0-11 contain six 16-bit addresses corresponding to the six possible interrupts available on the Z8, IRQO through IRQ5, respectively. When an interrupt occurs, control passes to the address corresponding to that particular interrupt. A system reset forces the program counter to 12, the first address available for the user program. See the discussion of interrupts in Section 1.4.

## 1.2.2 External Data Memory

A Z8 system can directly access as much as 62K bytes of external data memory. This segment is addressed beginning with data address 2048. External I/O is also mapped into this segment.

#### 1.2.3 Register Memory

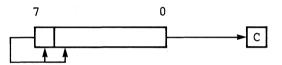

Register memory includes 124 general-purpose registers, 4 I/O ports, and 16 status and control registers. The I/O port and control registers are included in register memory to allow any 28 instruction to process I/O or control information directly, thus eliminating the need for special I/O or control instructions. The 28 instruction set permits direct access to any of these 144 registers. Each of the 124 general-purpose registers can function as an accumulator, an address pointer, or an index register. Z8 instructions can access registers directly or indirectly using an 8-bit address field. The Z8 also allows 4-bit addressing of registers, which generally saves bytes, and speeds program execution and task switching. In this 4-bit addressing mode, the register file is divided into 9 working-register groups, each occupying 16 contiguous register locations (Figure 1-2). A register pointer (one of the control registers) addresses the starting location of the currently active working-register group.

Figure 1-2. Working-Register Groups

NOTE: Changing the value of the register pointer is an easy way to save the 16 currently-active working registers (as during interrupt processing). Reserving one or more working-register groups for the use of interrupt-handling routines is a recommended programming practice.

In the following example, the Set Register Pointer (SRP) instruction sets the register pointer to 240, the starting address of the control register group. The following Load (LD) instruction initializes register 252 to ten.

| SRP #240 |     | !Register  | Pointer  | contains FO | (hex)!   |

|----------|-----|------------|----------|-------------|----------|

| LD R12,  | #10 | !Working n | register | 12 occupies | register |

|          |     | location   | 252!     |             |          |

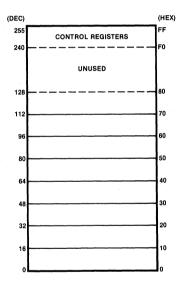

Because of their special significance, the I/O port registers (0-3) and control registers (240-255) are referenced later in this section. The control registers are particularly pervasive in all Z8 operations, since they are used in the handling of I/O, interrupts, the timer/counter, program control flags, and the program stack, as well as to point to the current working-register group. To provide a quick reference in the following sections, the control registers are listed in Figure 1-3. They are described in bit-level detail in the Z8 Technical Manual. Z8 instructions can reference control registers by number or by their predefined symbolic identifiers shown in the following figure.

NOTE

Register memory addresses 128-239 do not exist and should not be specified in Z8 instructions. The result of accessing these locations is undefined.

| LOCATION |                                          | IDENTIFIERS                              |

|----------|------------------------------------------|------------------------------------------|

| 255      | STACK POINTER (BITS 7-0)                 | SPL                                      |

| 255      | STACK POINTER (BITS 7-0)                 | SPL                                      |

| 254      | REGISTER POINTER                         | RP                                       |

| 253      |                                          |                                          |

| 252      | PROGRAM CONTROL FLAGS                    | FLAGS                                    |

|          | INTERRUPT MASK REGISTER                  | IMR                                      |

| 250      | INTERRUPT REQUEST REGISTER               | IRQ                                      |

| 249      | INTERRUPT PRIORITY REGISTER              | IPR                                      |

| 248      | PORTS 0-1 MODE                           | P01M                                     |

| 247      | PORT 3 MODE                              | P3M                                      |

| 246      | PORT 2 MODE                              | P2M                                      |

| 245      | TO PRESCALER LOAD                        | PRE0                                     |

| 244      | TIMER/COUNTER 0 LOAD                     | то                                       |

| 243      | T1 PRESCALER LOAD                        | PRE1                                     |

| 242      | TIMER/COUNTER 1 LOAD                     | T1                                       |

| 241      | TIMER MODE                               | TMR                                      |

| 240      | SERIAL I/O                               | SIO                                      |

|          | NOT<br>IMPLEMENTED                       |                                          |

| 127      |                                          | an a |

| 1.14     |                                          |                                          |

|          | GENERAL-PURPOSE<br>REGISTERS             |                                          |

|          | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 |                                          |

| 4        |                                          |                                          |

| 3        | PORT 3                                   | P3                                       |

| 2        | PORT 2                                   | P2                                       |

| 1        | POBT 1                                   | P1                                       |

| 0        | PORT 0                                   | P0                                       |

Figure 1-3. Control Registers

1-6

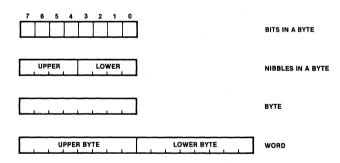

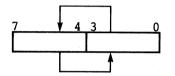

## 1.2.4 Data Lengths

Z8 instructions can operate on individual bits, 4-bit Binary Coded Decimal (BCD) digits or nibbles, 8-bit bytes, or 16-bit words (Figure 1-4). Bits can be set, reset, or tested. Nibbles are used in BCD arithmetic operations. Bytes are used for character or small integer values (in the range 0 to 255 if unsigned, or in the range -128 to 127 if signed). Words are used for larger integer values (in the range 0 to 65535 if unsigned, or in the range -32768 to 32767 if signed).

The basic data element of the Z8 is the byte. Memory locations (whether they reside in program, data, or register memory segments) are ordinarily accessed eight bits at a time. Increment Word (INCW) and Decrement Word (DECW) are the only instructions that operate on 16-bit words.

Figure 1-4. Data Lengths

## 1.3 Input/Output

Thirty-two of the Z8's 40 lines are dedicated to input and output. These 32 lines are grouped into 4 ports of 8 lines each and can be configured as input, output, or address/data. Under software control, the ports can be programmed to provide timing, interrupt requests, status signals, and serial or parallel I/O features with or without handshake.

In the following explanation of the various port functions, Port 1 is described before Port 0 for convenience. The Z8 architecture diagrams (Figures 1-5 and 1-6) show the I/O lines and signals referenced. Although they are pictured separately in Figure 1-5, remember that from a programming standpoint the I/O ports, timers, interrupt controls, flags, and register pointer are all manipulated through register memory.

## 1.3.1 Port 1

Port 1 can be programmed as a byte I/O port or as an address/data port for interfacing to external memory. Associated with Port 1 are the Address Strobe (AS), Data Strobe (DS) and Read/Write (R/W) timing signals. Under program control, two lines from Port 3 (lines P33 and P34) can be used with Port 1 as the handshake control lines (DAV1 and RDY1) or as a Port 1 interrupt request input (IRQ1) and an external data memory access (DM) status output.

If external data memory is to be accessed, Port 1 is programmed as an address/data port through which the external address and data are passed. In this case, the lower eight bits of the address (A0-A7) are multiplexed with data bits (D0-D7). If an address longer than eight bits is required, the additional address bits (A8-A15) originate from Port 0.

## 1.3.2 Port 0

Port 0 can be programmed to be either an I/O port or an address output for external memory. Depending on the size of the address, Port 0 provides either bits 8-11 or bits 8-15 of the address. (Port 1 provides bits 0-7). If the address is 12 bits or less, the upper four bits (nibble) of Port 0 can be programmed independently as I/O while the lower nibble is used for addressing. When Port 0 is used in the I/O mode, two lines from Port 3 (lines P32 and P35) can be used for the handshake controls DAVO and RDYO.

1-9

## 1.3.3 Port 2

Port 2 can be programmed for input or output on a line-by-line (bitwise) basis. As in the case of Ports 0 and 1, two lines from Port 3 (lines P31 and P36) can be programmed as the handshake control lines DAV2 and RDY2. The output buffers of Port 2 have a programmable option for inhibiting the active pull-ups to provide open-drain type outputs.

#### 1.3.4 Port 3

Port 3 can be programmed for I/O and/or as a control port. In I/O mode, the direction of the eight lines is fixed as four in and four out. The control functions of Port 3 are handshake, interrupt request, timer in and out, and status out.

Two lines of Port 3 can be programmed as a serial input and a serial output interface. Each line has an 8-bit serial/ parallel register associated with it. Serial I/O uses an asynchronous format with the bit rate controlled by the internal timer. Interrupts are generated when a character is received or transmitted.

#### 1.4 Interrupts

The Z8 allows six different interrupts from eight possible sources -- the four input lines of Port 3, serial in and out, and the two timers (T0 and T1, discussed in Section 1.5).

Six bits in the Interrupt-Mask control register can enable/ lisable the six interrupts IRQ0-IRQ5 individually. When more than one interrupt is pending, priorities are resolved by a priority encoder, controlled by the Interrupt-Priority control register.

Interrupt requests are stored in an Interrupt-Request control register, which can also be used for polling. When an interrupt request is granted, the Z8 enters an "interrupt machine cycle" that globally disables all other interrupts, saves the program counter (address of the next program instruction to be executed) and status flags, and finally branches to the vector location for the interrupt. It is only at this point that control passes to the interrupt-handling procedure for the interrupt.

before the Z8 can recognize interrupts following RESET, some nitialization tasks must be performed. RESET causes the interrupt Request Register (IRQ0 - IRQ5) to be cleared and held o zero, and interrupts to be globally disabled (bit 7 of the nterrupt Mask Register = 0). The initialization routine should onfigure the Z8 interrupt requests to be enabled/disabled (via the IMR) as required by the target application, and prioritized for vectored interrupts (via the Interrupt Priority Register). Because RESET holds the IRQ register to zero, one final step is required before interrupts can function, even in polled mode. Specifically, interrupts must be globally enabled via the EI instruction; simply setting bit 7 of IMR is not sufficient. Subsequent to this EI, interrupts can be enabled either by IMR register manipulation or by use of the EI instruction, with equivalent effects.

Additionally interrupts must be disabled by executing a DI instruction before the IPR or IMR control registers can be modified. Interrupts can then be enabled by executing an EI instruction.

#### 1.5 Timers/Counters

The Z8 has two 8-bit counters (T0 and T1), each driven by its own 6-bit prescaler. The prescalers can be driven, in turn, by either an internal (T0 and T1) or external (T1 only) clock source. T0 and T1 can operate independently of the processor instruction sequence and, consequently, can unburden the program from time-critical operations like event counting or elapsed-time calculation.

Each prescaler can be programmed to divide the input frequency of its clock source by any number from 1 to 64. The prescaler drives its counter, which decrements a value (0 through 255) stored in the timer register. When the timer register reaches end-of-count, a timer interrupt request--IRQ4 (T0) or IRQ5 (T1)--is generated.

Under program control, counters/prescalers can be started, stopped, restarted to continue counting, or restarted from the initial value of the counters. The counters can also be programmed to stop on reaching end-of-count, or to <u>automatically</u> reload the initial counter value and continue counting. Either counter can be read at any time without disturbing its value or count mode.

The clock source for the Tl counter/prescaler can be either the microprocessor clock or an external timer input. Under program control, the external timer input can function as an external clock (maximum frequency 1 MHz), a trigger input that can be retriggerable or not, or as a gate input for the internal clock.

One line of Port 3 also serves as a timer output through which T0, T1, or the internal clock can be output. The timer output coggles whenever an end-of-count occurs. If the timer is programmed to reload the count value and continue at end-of-count, this line produces a 50% duty cycle. The counters can be cascaded by feeding the timer input line with the timer putput.

#### 1.6 Status Flags and Program Controls

The ability to test data and make decisions based on the result is especially important in single-chip microcomputers. Programs written for these computers tend to be dominated by control instructions (conditional and unconditional jumps, calls, etc.) and by test and mask instructions.

control register 252 contains six flags for the use of the Z8 processor and programmer.

| Carry          | (C) |

|----------------|-----|

| Zero           | (Z) |

| Sign           | (S) |

| Overflow       | (V) |

| Decimal Adjust | (D) |

| Half Carry     | (H) |

he half carry and decimal adjust flags are used only by the Z8. he other flags can be used by the programmer with the Jump (JP) nd Jump Relative (JR) instructions to provide a repertoire of 19 onditional tests.

xamples:

| JP | NC, SUBTOT | !Jump to routine named<br>SUBTOT if carry is not set!        |

|----|------------|--------------------------------------------------------------|

| JR | OV, \$+50  | !Jump 50 bytes ahead in program<br>if overflow has occurred! |

#### .6.1 Carry Flag

he carry flag (C) is affected by Addition (ADD, ADC), ubtraction (SUB, SBC), Compare (CP), Decimal Adjust (DA), Rotate RL, RLC, RR, RRC), Swap (SWAP), and the Interrupt Return (IRET) nstructions. When set, it generally indicates a carry out of ne bit 7 position of a register being used as an accumulator. or example, adding two 8-bit numbers as in the following nstructions would cause a carry out of bit 7 and set the carry lag.

The carry flag can be set to one by the Set Carry Flag (SCF) instruction, cleared to zero by the Reset Carry Flag (RCF) instruction, and complemented (changed to 0 if 1, and vice-versa) by the Complement Carry Flag (CCF) instruction.

## 1.6.2 Zero Flag

The zero flag is affected by the same instructions as the carry flag plus the Logical (AND, OR, XOR, COM), Increment and Decrement (INC, INCW, DEC, DECW), and Test (TCM, TM) instructions. In general, the zero flag is set when the "accumulator" register's contents following one of the above operations is zero.

| DEC | 20      | <pre>!Decrement location 20 contents!</pre> |

|-----|---------|---------------------------------------------|

| JP  | Z, 1500 | Jump to program location 1500               |

|     |         | if location 20 is zero after                |

|     |         | decrementing!                               |

#### 1.6.3 Sign Flag

The sign flag is affected by the same instructions as the zero flag. The sign flag is set to one when bit 7 of the register used as an accumulator in these operations contains a one (a negative number in twos complement representation) following the operation.

| LD  | 20, | SUB1  | Load value of variable named!       |

|-----|-----|-------|-------------------------------------|

|     |     |       | SUB1 into location 20!              |

| SUB | 20, | SUB 2 | <pre>!Subtract value of SUB2!</pre> |

| JP  | MI, | NEG   | !If S=l (result is "minus"),        |

|     |     |       | jump to location labeled NEG!       |

1-13

#### 1.6.4 Overflow Flag

The overflow flag is affected by the same instructions as the zero and sign flags. When set, the overflow flag indicates that a twos-complement number in a result register is in error since it has exceeded the largest (+127) or is less than the smallest (-128) number than can be represented in twos-complement notation. Consider the following, as an example:

|   | <u>Bit</u>                        | 7 | 6             | 5  | 4   | 3   | 2  | 1   | 0 |

|---|-----------------------------------|---|---------------|----|-----|-----|----|-----|---|

| + | $\frac{120}{105}$ $\frac{225}{2}$ | 0 | $\frac{1}{1}$ | 1  | 0   | 1   | Ō  | Ō   | 1 |

|   |                                   |   |               | са | arı | ; y | £] | Lac | 1 |

The result in this case (-95) is incorrect. In this case, the overflow flag would be set.

| SUB | 20, | 21    | Subtract location 21's contents                             | from |

|-----|-----|-------|-------------------------------------------------------------|------|

|     |     |       | location 20's!                                              |      |

| JR  | ov, | \$-50 | !Jump back 50 bytes in program<br>if overflow has occurred! |      |

#### 1.6.5 Decimal Adjust Flag

The decimal adjust flag is used for BCD arithmetic. Since the algorithm for correcting BCD operations is different for addition and subtraction, this flag is used to specify what type of instruction was executed last so that the subsequent Decimal Adjust (DA) operation can do its function correctly. The decimal adjust flag cannot normally be used as a test condition by the programmer.

## L.6.6 Half Carry Flag

The half carry flag indicates a carry out of, or a borrow into bit 3 as the result of adding or subtracting two 8-bit bytes, each representing two BCD digits. The half carry flag is used by the Decimal Adjust (DA) instruction to convert the binary result of a previous addition or subtraction into the correct decimal (BCD) result. As in the case of the decimal-adjust flag, this flag is not normally accessed by the user.

#### 1.7 Stack Memory

To support the power of its interrupt capability, the Z8 has a flexible stack scheme and a fast "context-switching" mechanism. Context switching refers to the saving and restoration of working registers, the program counter, flags, and other pertinent information when an interrupt occurs.

Under program control, the Z8 can use an internal (register memory) or external (data memory) stack, limited in size only by the available memory space. An 8-bit or 16-bit stack pointer occupies control register 255 or the control register pair 254-255.

CALL instructions use the stack to store the program counter before branching to a procedure. Interrupts automatically save the program counter and flag register. The RET instruction restores the program counter from the stack upon return from a procedure, while IRET also restores the flag register upon return from an interrupt procedure. In addition, the Z8 has PUSH and POP instructions that can save and restore any register of the register file.

## Section 2 **Z8 Assembler Conventions**

## 2.1 Assembler Overview

The Z8 microcomputer is programmed in a symbolic assembly language (PLZ/ASM). This marks a significant improvement over coding in binary notation. The operation codes for assembly-language statements are easily memorized (DEC for decrement and DECW for decrement word). In addition, meaningful symbolic names can be assigned to program addresses and data (MULTIPLY ROUTINE as the label of the first statement in a multiply procedure).

A Z8 <u>source module</u> consists of PLZ/ASM assembly language statements. These statements are then translated by the Z8 assembler into an <u>object module</u> that can either be separately executed by the Z8 microcomputer, or can be linked with other object modules to form a complete program. Because the assembler has some high-level features, a source module can also include PLZ constructs such as D0 and IF statements. The user can also embed <u>assembler directives</u>, which control the operation of the assembler, in the source module. High-level statements and assembler directives are discussed in Sections 4 and 5.

Depending on the assembler directives used, addresses within an object module or program can be <u>absolute</u> (meaning addresses in the source program correspond exactly to Z8 program memory addresses) or <u>relocatable</u> (meaning addresses can be assigned relative to some base address at a later time). Object modules should be made relocatable wherever possible so they can be linked with other object modules, and so that object programs can be loaded anywhere in memory. It also allows the creation of libraries of commonly used procedures (including math or input/output routines) that can be linked selectively into several programs as desired.

Operation of the assembler, module linkage, address relocation, and program execution are discussed in the Z8 PLZ/ASM Assembler User Guide.

## 2.2 Assembly Language Statement Format

The most fundamental component of a PLZ/ASM program is the assembly-language statement consisting of an instruction and its operands. The instruction describes an action to be taken; the operands supply the data to be acted upon.

An assembly language statement can actually include four fields:

- Statement labels

- An instruction

- Operands

- Comments

The statement label and comment fields are always optional. The statement has zero, one, or two operands, depending on the instruction selected. The following statements have the same effect in a Z8 program, but the second is much more descriptive (and consequently more helpful in program debugging).

| Label   | Instruction | Operand(s) | Comment                                 |

|---------|-------------|------------|-----------------------------------------|

|         | LD          | T1, #255   |                                         |

| INITT1: | LD          | T1, #255   | <pre>!Load Timer 1 initial value!</pre> |

Each of the elements of a PLZ/ASM program must be separated from other elements by one or more delimiters. A delimiter is one of the characters: space (blank), comma, semicolon, tab, carriage return, line feed, or form feed. Note that carriage return is treated the same as any other delimiter, so that a single statement may span several lines, or several statements may appear on a single line. The delimiter used in a specific situation is up to the programmer. For the sake of illustration, this manual uses blanks to separate statement fields and commas to separate operands.

#### 2.2.1 Program Labels and Identifiers

Any assembly-language (or high-level) statement in a Z8 program can be preceded by any number of labels. Any statement referenced by another statement must be labeled. A label consists of an identifier followed by a colon (:) in the form:

labell: label2: ... labeln: statement

A PLZ/ASM identifier can contain up to 127 characters, of which the first must be a letter. The remaining characters can be letters, digits, or the special character underscore (\_). Letters can be capitalized or lower-cased, but each time an identifier is used, it must be written in exactly the same way. The following are valid identifiers: START\_UP\_ROUTINE Program\_Initialization A Loop\_12 N1 sort

In addition to their statement-labeling function, identifiers serve as symbolic names for constants (Section 2.3.2), data variables (Section 2.3.3), and procedures (Section 5.2.2). Certain identifiers serve as PLZ/ASM keywords and should not be used as programmer-defined identifiers (see Appendix D).

An identifier can be associated with only one item within the scope of its definition. Section 4.2.5 explains the scope of identifiers, including the scope of labels. For the moment, we can say that labels are accessible within the module in which they are defined, and are not accessible outside that module unless specifically declared to be GLOBAL or EXTERNAL.

### 2.2.2 Instruction

The instruction is the assembly-language mnemonic describing a specific action to be taken.

LD R5, R10 !Load register 5 from register 10!

SRP #%10 !Set Register Pointer to 10 (hex)!

The instruction must be separated from its operands by a delimiter.

#### 2.2.3 Operand Field

Depending on the instruction specified, this field can have zero, one, or two operands. If two operands are needed, they must be separated by a delimiter.

CCF !No operand!

SRP #%10 !One operand!

ADD R6, #210 !Two operands!

Operands supply the information the instruction needs to carry out its action. An operand can be:

- Data to be processed (immediate data);

- The address of a location from which data is to be taken (source address);

- The address of a location where data is to be put (destination address);

- The address of a program location to which program control is to be passed;

- A condition code, used to direct the flow of program control.

When these operand types are combined, the possible orderings are as follows:

Instruction Destination, Immediate

Instruction Destination, Source

Instruction Condition Code, Program Location

Immediate data can be in the form of a constant, an address, or an expression (constants and/or addresses combined by operators). Each of these forms is described in Section 2.3.

|     |     | <b>#K</b>    | !Load constant K into reg 0!                                     |

|-----|-----|--------------|------------------------------------------------------------------|

| LD  | R0, | #COUNTER     | <pre>!Load address of COUNTER into<br/>reg 0!</pre>              |

| ADD | R0, | #(CON/3 + 5) | !Add value of expression<br>(CON/3 + 5) to contents of<br>reg 0! |

Source, destination, and program addresses can also take several forms. PLZ/ASM addressing modes are described in Section 2.4. Some examples are:

| LD | R0, @R5       | !Load value whose address is in<br>register 5 into register 0!                    |

|----|---------------|-----------------------------------------------------------------------------------|

| LD | 55, VAR1      | !Load value located at address<br>labeled VARl into register<br>file location 55! |

| JP | Z, LOOPl      | !Jump to program address<br>labeled LOOP1 if zero flag (Z)<br>is set!             |

| JP | NZ, LOOP1 + 5 | !Otherwise, jump to location<br>five bytes after LOOP1!                           |

Condition codes are listed in Section 3.2. They are used only by the Jump (JP) and Jump Relative (JR) instructions.

## 2.2.4 Comments

Comments are used to document program code as a guide to program logic and to simplify present or future program debugging. Comments can be inserted anywhere a program delimiter can appear. Comments are bounded by exclamation points (!) and can contain any characters except the exclamation point itself.

!Module 3, Changed 7-25-78!

RES R13, #3 !Turn off "convert" flag!

A single comment can cross line boundaries; that is, carriage returns can occur within a comment.

Comments can also start with //. This type of comment does not need a closing symbol; the carriage return, <CR>, at the end of the line on which this comment appears terminates the comment.

//Module 3, Changed 7-25-78 <CR>

RES R13, #3 //Turn off "convert" flag <CR>

#### 2.3 Arithmetic Operands

Constants and data variables are types of operands that can be used in assembly-time arithmetic expressions, or singly as operands for a Z8 instruction. This section describes the differences between assembly-time and run-time arithmetic, defines constants and data variables, and explains how expressions are formed using operators.

## 2.3.1 Run-Time Versus Assembly-Time Arithmetic

Arithmetic is performed in two ways in an assembly-language program. Run-time arithmetic is done while the program is actually executing.

SUB R10, R12 !Subtract the contents of reg 12 from the contents of reg 10!

Assembly-time arithmetic is done by the assembler when the program is assembled and involves the evaluation of arithmetic expressions in operands, such as the following:

LD R0, #(22/7 + X) JP Z, LOOP1 + 12 ADD R2, @HOLDREG-1

Assembly-time arithmetic is more limited than run-time arithmetic in such areas as signed versus unsigned arithmetic and the range of values permitted.

Only unsigned arithmetic is allowed in assembly-time expression evaluation. Run-time arithmetic uses both signed and unsigned modes, as determined from the assembly-language instruction specified and the meaning attached to operands by the programmer.

All assembly-time arithmetic is computed using 16-bit arithmetic, "modulo 65536". Values greater than or equal to 65536 are divided by 65536 and the remainder of the division is used as the result. If the result of assembly-time arithmetic is to be stored in a single byte location, the resulting value must be representable in 8 bits; that is, the range 0 to 255 (or -128 to 127 if signed representation is intended).

| LD | R10, | #X+22 | !Result of (X+22) must be in |

|----|------|-------|------------------------------|

|    |      |       | range -128 to 255!           |

| JP | X+22 |       | !Modulo 65536. Result is the |

|    |      |       | address 22 bytes beyond X!   |

## 2.3.2 Constants

A constant value is one that does not change throughout the program. Constants can be expressed as numbers, as character sequences, or as a symbolic name representing a constant value.

Numbers can be written in decimal, hexadecimal, binary, or octal notation. The latter three are preceded by a percent sign (%) and, in the case of binary and octal, by a base specifier enclosed in parentheses. If a number has no prefix, decimal is assumed.

| 10                  | decimal     |

|---------------------|-------------|

| <b>%</b> 10         | hexadecimal |

| %AF0F               | hexadecimal |

| <b>%(2)10110010</b> | binary      |

| <b>%(8)70</b>       | octal       |

A <u>character</u> sequence is a sequence of one or more characters enclosed in <u>single</u> quote marks. Any ASCII character (except a percent sign or single quote) can be included in the character sequence. Since constants are represented as 32-bit values, only the first four characters in a string literal, used as a constant, are meaningful, for example, 'ABCD = ABCDE'.

> 'A' 'This is a character sequence'

A character can also be represented in a character sequence in the form "%hh," where "hh" is the hexadecimal equivalent of the ASCII code for the character. (See Appendix E for the ASCII character set and its hexadecimal equivalents.)

'Here is an ESC character: %1B'

For convenience, certain ASCII characters have been assigned shorter, more mnemonic codes as follows:

| ۶L | or | 81 | Linefeed         |

|----|----|----|------------------|

| γT | or | 8t | Tab              |

| ۶R | or | 8r | Carriage Return  |

| ۶P | or | %p | Page (Form Feed) |

| 88 |    |    | Percent Sign     |

| ۶Q | or | %q | Single Quote     |

Example:

'First line%rSecond line%r' 'Quote%Qinside a quote%Q'

A constant can be assigned a symbolic name by a constant definition (CONSTANT) statement. A symbolic identifier, once

associated with a constant value, retains that value through the entire program module.

Constant symbols are defined by the CONSTANT statement in the form shown below. Identifiers follow the rules outlined in Section 2.2.1. The special character pair ":=" can be read "is defined as".

| CONSTANT      |                          |

|---------------|--------------------------|

| REC LENGTH    | := 64                    |

| BUFFER LENGTH | $:= 4 \times REC LENGTH$ |

| SEMICOLON     | := ';'                   |

| BIGNUMBER     | := 65000                 |

| smallnumber   | := -1                    |

Certain constants are predefined by the assembler and should not be used for programmer-defined constant symbols (see Appendix D).

## 2.3.3 Data Variables

A data variable can be thought of as a container that can hold different values from time to time. An 8-bit (BYTE or SHORT INTEGER) variable can hold values in the range 0 to 255 if unsigned, or -128 to 127 if signed twos-complement representation is intended. Similarly, a 16-bit (WORD or INTEGER) variable can hold values in the range 0 to 65535 if unsigned, or -32768 to 32767 if signed.

#### NOTE

BYTE and WORD variables should be used for unsigned values, and SHORT INTEGER and INTEGER variables should be used for signed values; there are no restrictions on whether a particular variable is signed or unsigned. Therefore, BYTE and SHORT INTEGER are treated as equivalent, as are WORD and INTEGER; the appropriate interpretation is made by the programmer.

A data variable name can be associated with either a register or data memory location; the value of the variable is the contents of that location at the time the variable is referenced. A data variable name is a symbolic identifier and follows the rules for identifiers in Section 2.2.1.

| LD R5, MPLIER        | Load the value contained in the location symbolized by MPLIER! |

|----------------------|----------------------------------------------------------------|

| ADD R5, 3 + SUBTOTAL | !Add the value contained in the location 3 bytes after the     |

|                      | location named SUBTOTAL to the contents of reg 5!              |

If a data variable operand is preceded by #, it is treated as immediate data and the value used is the data address associated with the variable, not the contents of the location. For example, suppose register 50 has the symbolic name COUNTER and contains the bit pattern lllllll (decimal 255).

| LD | T1, COUNTER      | 255 is loaded into Timer l!                     |

|----|------------------|-------------------------------------------------|

| LD | Tl, #COUNTER     | !50 is loaded into Timer l!                     |

| LD | Tl, COUNTER - 5  | !Contents of reg 45 are loaded<br>into Timer l! |

| LD | Tl, #COUNTER - 5 | !45 is loaded into Timer l!                     |

Every data variable name has a type and scope associated with it, as well as a value. The type and scope (and, optionally, the initial value) are defined in a variable declaration statement like the following:

#### INTERNAL SWITCH1 BYTE

In this example, INTERNAL is the scope of the variable SWITCH1, and BYTE is its type.

Variable declaration is the subject of Section 5.3.4. For the purposes of this section, variables can have GLOBAL, EXTERNAL, INTERNAL, or LOCAL scope. They can be one of the simple types, BYTE or SHORT INTEGER (for 8-bit values) or WORD or INTEGER (for 16-bit values). They can also be one of the structured types, ARRAY or RECORD.

## 2.3.4 Expressions and Operators

Expressions are formed using arithmetic, logical, shift, and relational operators in combination with constants and variables. These operators allow both unary (one-operand) and binary (two-operand) expressions, as shown below.

#### Arithmetic Operators

The arithmetic operators are as follows:

| Operator | Operation                       |

|----------|---------------------------------|

| +        | Unary plus, binary addition     |

|          | Unary minus, binary subtraction |

| *        | Unsigned multiplication         |

Operator

Operation

1.

MOD Unsigned modulus

The division operator (/) truncates any remainder. The MOD operator returns the remainder from dividing its operands.

Unsigned division

17/4 = 417 MOD 4 = 1

If zero is specified as the right operand for either of these division operators, the result is undefined.

Examples:

| ADD | R5, | #-3        | !A minus 3 is added to reg 5!                               |

|-----|-----|------------|-------------------------------------------------------------|

| ADD | R5, | #K + (5*3) | <pre>!Value of constant K + 15 is<br/>added to reg 5!</pre> |

Once again, expressions containing these operators are evaluated at assembly time and, consequently, the arithmetic performed is unsigned. Signed arithmetic can still be done at run time, however. Signed multiplication, for example, can be done by looping through a series of Shift and Add instructions.

## Logical Operators

The logical operators are as follows:

| Operator | <u>Operati</u> | on                 |

|----------|----------------|--------------------|

| LNOT     | (Unary)        | Logical complement |

| LAND     | Logical        | AND                |

| LOR      | Logical        | OR                 |

| LXOR     | Logical        | EXCLUSIVE OR       |

LNOT simply complements the bit pattern of its (single) operand. All one bits are changed to zero and vice-versa.

| LD | Ρ2Μ, | LNOT | MASK | !Reve | se  | the   | bits | in   | the    |    |

|----|------|------|------|-------|-----|-------|------|------|--------|----|

|    |      |      |      | mask  | use | ed to | prog | gran | n Port | 21 |

The effect of LAND, LOR, and LXOR can be seen from the following examples. Assume two constants A and B have the bit patterns 11110000 and 01010101, respectively. The expressions:

A LAND B A LOR B A LXOR B

will result in the following evaluations of the operands:

| LAND | 11110000 | LOR | 11110000 | LXOR | 11110000 |

|------|----------|-----|----------|------|----------|

|      | 01010101 |     | 01010101 |      | 01010101 |

|      | 01010000 |     | 11110101 |      | 10100101 |

LAND sets a one bit whenever both ANDed bits are one; LOR sets a one bit whenever either ORed bit is one; LXOR sets a one bit when the two EXCLUSIVE-OREd bits are different.

The assembly-time logical operations performed by LNOT, LAND, LOR, and LXOR can also be done at run time by the Z8 instructions COM, AND, OR, and XOR. The assembly-time operations require less code and register manipulation. The run-time operations allow greater flexibility, however. For example, they can operate on registers (variables) whose contents are not known at assembly time, as well as on known constant values.

#### Shift Operators

The shift operators are as follows:

| SHR | Logical | shift | right |

|-----|---------|-------|-------|

| SHL | Logical | shift | left  |

When used in expressions, the shift operators have the form

d operator n

where "d" is the data to be shifted and "n" specifies the number of bits to be shifted. Vacated bits are replaced with zeros. For example, if the constant PRODUCT is equal to 10110011, the statement

LD RO, #(PRODUCT SHL 2)

would load the value 11001100 into working register 0.

If the second operand supplied is negative (that is, if the sign bit is set), it has the effect of reversing the direction of the shift.

> ADD PRODUCT, #(MPLIER SHR -1) !MPLIER is shifted left one bit position!

#### Relational Operators

The relational operators are as follows:

| <  | Less than             |

|----|-----------------------|

| <= | Less than or equal    |

| =  | Equal                 |

| <> | Not equal             |

| >= | Greater than or equal |

| >  | Greater than          |

These six relational operators return a logical TRUE value (all ones) if the comparison of the two operands is true, and return a logical FALSE value (all zeros) otherwise. The operators assume both operands are unsigned.

| LD | RO,#(1=2)      | !Reg  | 0 | is | loaded | with | zeros! |

|----|----------------|-------|---|----|--------|------|--------|

| LD | R0, #(2+2) < 5 | ! Reg | 0 | is | loaded | with | ones!  |

Precedence of Operators. Expressions are generally evaluated left to right with operators having the highest precedence evaluated first. If two operators have equal precedence, the leftmost is evaluated first.

The following lists the PLZ/ASM operators in order of precedence:

1. Unary operators: +; -, LNOT

2. Multiply/Divide/Shift/AND: \*, / , MOD, SHR, SHL, LAND

3. Add/Subtract/OR/XOR: +, -, LOR, LXOR

4. Relational operators: <, <=, =, <>, >=, >

Parentheses can be used to change the normal order of precedence. Items enclosed in parentheses are evaluated first. If parentheses are nested, the innermost are evaluated first.

20/5 - 12/3 = 0

20/(5 - 12/3) = 20

Modes of Arithmetic Expressions. All arithmetic expressions have a mode associated with them: absolute, relocatable, or external. These modes are defined in detail in Section 4.3.3.

#### 2.4 Z8 Addressing Modes

With the exception of immediate data and condition codes, all assembly-language operands are expressed as addresses: register addresses, program memory addresses, and external data memory addresses. The various address modes recognized by the Z8 assembler are as follows:

- Register

- Indirect Register

- Indexed Address

- Direct Address

- Relative Address

- Immediate

Special characters are used in operands to identify certain of these address modes. The characters are:

- "R" preceding a working-register number;

- "RR" preceding a working-register pair;

- "@" preceding an indirect-register reference;

- "#" preceding immediate data;

- "()" used to enclose the index register part of an indexed address;

- "\$" signifying the current program counter location, usually used in relative addressing.

The use of these characters is shown in the following sections.

Not every address mode can be used by every instruction. The individual instruction descriptions in Section 3 describe which address modes can be used for each instruction.

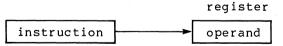

#### 2.4.1 Register Address

In register addressing mode, the operand value is the contents of the specified register.

The register can be addressed in either of two ways. The address can be:

- an 8-bit address in the range 0-127, 240-255, or

- a 4-bit working-register address.

The full 8-bit address is indicated in the operand field by supplying an expression (see Section 2.3.4) which evaluates to either the number of the register or a variable name associated with a register. Neither of these has a special-character prefix.

| LD  | 55, #%F3      | !Load register 55 with the<br>hexadecimal value F3!                                          |

|-----|---------------|----------------------------------------------------------------------------------------------|

| LD  | FLAGS, #ZEROS | !Load register named FLAGS<br>(i.e., reg 252) with the value<br>of the constant named ZEROS! |

| ADD | 120, SUBTOTAL | !Add contents of register named<br>SUBTOTAL to register 120!                                 |

#### Working-Register Address

Designating a register by a 4-bit working-register address, rather than an 8-bit register address, often reduces the length of an instruction and results in a shorter execution time. In this case, the full address is formed by concatenating the 4-bit field (address range 0-15) with the upper 4 bits of the Register Pointer; thus the working-register set can be varied dynamically simply by changing the value of the Register Pointer (control register 253).

A working-register operand is indicated by a number in the range 0-15 preceded by the letter "R".

| LD R0, R15     | Load the contents of working<br>register 15 into working register 0! |

|----------------|----------------------------------------------------------------------|

| LD 53, R15     | Load the contents of working register<br>15 into register 53!        |

| ADD R6, AUGEND | Add contents of register named AUGEND to working register 6!         |

#### Register Pair Address

Registers can be used in pairs to designate 16-bit values or memory addresses. A register pair can be specified as an expression which evaluates to an even number in the range 0,2,4...126 or 240,242...254. It can also be designated as the variable name of an even-numbered register. DECW 20 !Decrement contents of registers 20 and 21!

#### Working-Register Pair Address

Working-register pairs are indicated by an even number in the range 0, 2, 4, 6, ... 14. If the low-order (odd) byte of a pair is specified, an error will result. In the case of a working register pair, the register number is preceded by the letters "RR." For example, RR0 refers to R0 and R1.

INCW RR10 !Increment contents of working registers 10 and 11!

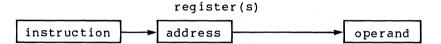

#### 2.4.2 Indirect-Register Address

In indirect addressing, the value of the operand is <u>not</u> the contents of a register. Instead, the register (register pair, working register or working-register pair) contains the address of the location whose contents are to be used as the operand value.

Depending on the instruction selected, the address may point to a register, program memory, or external data memory location. Register pairs or working-register pairs are used to hold the 16-bit addresses when accessing program or external data memory. Pairs are indicated by an even number (see Section 2.4.1).

The indirect-register address mode may save space and improve execution speed when data is accessed from consecutive locations. This mode can also be used to simulate more complex addressing modes, since addresses can be computed before the associated data is accessed.

An indirect address can be an expression which evaluates to a register number, the variable name of a register file location, or a register-pair designator. It can also be a working-register designator, or a working-register-pair designator. In all cases, the register specification must be preceded by a commercial at symbol (@).

2-15

| JP | @RRO         | Pass control (jump) to the<br>program memory location<br>addressed by working<br>register pair 0-1! |

|----|--------------|-----------------------------------------------------------------------------------------------------|

| JP | @20          | !Jump to program location<br>addressed by register pair<br>20-21!                                   |

| LD | @TOTALS, 30  | Load contents of register<br>30 into location addressed by<br>register named TOTALS!                |

| LD | @TOTALS, #30 | Load immediate value 30 into!<br>location addressed by TOTALS!                                      |

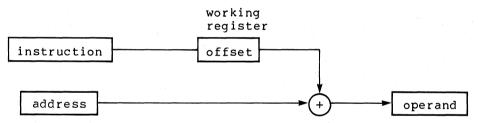

### 2.4.3 Indexed Address

An indexed address consists of a register address offset by the contents of a designated working register (the index). This offset is added to the register address and the resulting address points to the location whose value is used by the instruction. This address mode is used only by the Load (LD) instruction.

The register address is specified as an expression which evaluates to a register-file number or to the variable name of a register file location. This address is followed by the index, a working-register designator enclosed in parentheses.

| LD R10, | TABLE (RO) | !Load the | contents of the    |

|---------|------------|-----------|--------------------|

|         |            | location  | addressed by TABLE |

|         |            | plus the  | contents of reg 0  |

|         |            | into req  | 10!                |

LD 240(R0), R10

!Load the contents of reg 10 into the control register whose address is 240 plus the contents of reg 0!

Since the specified register address and working register contents are both 8-bit values, the indexed-address mode can be used for base addressing. The base address is loaded into the working register and the offset (register address) then completes the address field.

#### 2.4.4 Direct Address

Direct-address mode is used only by the Jump (JP) and Call (CALL) instructions to specify the destination where program control is to be transferred. The address may be specified as an expression which evaluates to a number or a program label.

instruction

address

| CALL | MATH_ROUTINE | !Transfer control to the procedure labeled MATH_ROUTINE! |

|------|--------------|----------------------------------------------------------|

| JP   | C,%2000      | !Jump to location 2000(hex) if the carry flag is set!    |

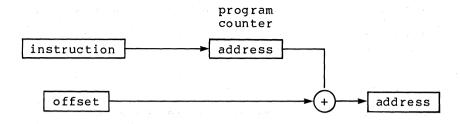

### 2.4.5 Relative Address

Relative-address mode is implied by its instruction. It is used only by the Jump Relative (JR) and the Decrement and Jump If Nonzero (DJNZ) instructions and is the only mode available to these instructions. The operand, in this case, represents an offset that is added to the contents of the program counter to form the destination address (the program address where control is to be transferred). The original contents of the program counter is taken to be the address of the instruction byte following the JR or DJNZ instruction, while the offset value is an 8-bit signed value in the range -128 to 127.

The offset value can be expressed in two ways. In the first case, the programmer provides a specific offset in the form "\$+n" where n is a constant expression in the range +129, -126 and \$ represents the contents of the program counter at the start of the JR or DJNZ instruction (each instruction is two bytes in length).

JR OV, \$+K !Add value of constant K to program counter and jump to new location if overflow has occurred!

In the second method, the assembler calculates the offset. The programmer simply specifies an expression which evaluates to a number or a program label as in direct addressing. The address specified by the operand must be in the same module and section as the JR or DJNZ instruction and must be within the offset range (+127, -128).

#### JR OV, MATH ERROR

DJNZ R5, LOOP !Decrement reg 5 and jump to LOOP if the result is not zero!

The Jump (JPR) control instruction causes the assembler to produce a JR whenever possible. Refer to Section 5.2.6 for letailed information on the Jump optimization.

#### 2.4.6 Immediate Data

Immediate data is an address mode for the purposes of this liscussion. The operand value used by the instruction in this ase is the value supplied in the operand field itself.

> instruction operand

Immediate address mode is often used to load registers with their initial values. The Z8 is optimized for this function, providing several short immediate data instructions to reduce the byte count of programs.

Immediate data is preceded by the special character # and may be a constant (including character constants and symbols representing constants) or an expression as described in section 2.3.4. Remember, if a variable name is prefixed by #, the value used is the address represented by the variable, not the contents of the address. Immediate data values must be in the range -128 to 255 (that is, expressible in 8 bits), or an error message will be generated.

| LD 100, #%12          | !Load 12(hex) into reg 100!                                                        |

|-----------------------|------------------------------------------------------------------------------------|

| LD COUNTER, #COUNT-50 | !Load register named<br>COUNTER with value of<br>constant COUNT-50!                |

| LD POINTER, #ITEM     | !Load register named<br>POINTER with the value of the<br>address of variable ITEM! |

Two special operators are provided to ease the manipulation of 16-bit addresses: the HI operator gives the high-order byte, and LO gives the low-order byte of a 16-bit expression. Since HI and LO can only be used where the immediate addressing mode is applicable, the # character must precede them.

| LD | R6,#HI DLABEL | !Load bits 8-15 of 16-bit<br>address of DLABEL into reg 6! |

|----|---------------|------------------------------------------------------------|

| LD | R7,#LO DLABEL | !Load bits 0-7 of 16-bit<br>address of DLABEL into reg 7!  |

#### 2.4.7 A Note on the Register Pointer

For the assembly-language programmer, dealing with working registers is an automatic procedure. The assembler determines the appropriate binary instruction code so that the specified working-register address can be formed at run time using the current value of the register pointer. The upper four bits of the memory address are taken from the register pointer; the lower four bits are taken from the instruction code, and together they specify the designated working register.

When programming in binary code, an additional possibility exists. When a full 8-bit register designator is required by the instruction format (register or register-pair address modes), a working register or working-register pair can be specified without knowing the current value of the register pointer. If the upper nibble of the register field is coded as a hexadecimal E, the lower nibble is interpreted as a working-register (EO-EF hex are not implemented register addresses). The final register address is formed at run time by replacing E with the register pointer value. This mechanism is handled automatically by the assembler whenever a working register designator is used.

The working-register mechanism allows sections of code using different register-pointer values to share a common procedure and pass parameters to it via the working registers.

# Section 3 Assembly Language Instruction Set

#### 3.1 Functional Summary

PLZ/ASM instructions can be divided functionally into the following eight groups:

- Load

- Arithmetic

- Logical

- Program Control (Branch)

- Bit Manipulation (Test)

- Block Transfer

- Rotate and Shift

- CPU Control

The following summary shows the instructions belonging to each group and the number of operands required for each, where "src" is the source operand, "dst" is the destination operand, and "cc" is a condition code.

### Load Instructions

| Instruction | Operands | Name of Instruction |

|-------------|----------|---------------------|

| CLR         | dst      | Clear               |

| LD          | dst,src  | Load                |

| LDC         | dst,src  | Load Constant       |

| LDE         | dst,src  | Load External Data  |

| POP         | dst      | Pop                 |

| PUSH        | src      | Push                |

#### Arithmetic Instructions

| Instruction | Operands | Name of Instruction |

|-------------|----------|---------------------|

| ADC         | dst,src  | Add With Carry      |

| ADD         | dst,src  | Add                 |

| CP          | dst,src  | Compare             |

| DA          | dst      | Decimal Adjust      |

| DEC         | dst      | Decrement           |

| DECW        | dst      | Decrement Word      |

| INC         | dst      | Increment           |

| INCW        | dst      | Increment Word      |

| SBC         | dst,src  | Subtract With Carry |

| SUB         | dst,src  | Subtract            |

3-1

# Logical Instructions

| Instruction | Operands | Name of Instruction  |

|-------------|----------|----------------------|

| AND         | dst,src  | Logical And          |

| COM         | dst      | Complement           |

| OR          | dst,src  | Logical Or           |

| XOR         | dst,src  | Logical Exclusive Or |

# Program-Control Instructions

| Instruction | Operands | Name of Instruction              |

|-------------|----------|----------------------------------|

| CALL        | dst      | Call Procedure                   |

| DJNZ        | r,dst    | Decrement and Jump<br>If Nonzero |

| IRET        |          | Interrupt Return                 |

| JP          | cc,dst   | Jump                             |

| JR<br>RET   | cc,dst   | Jump Relative<br>Return          |

# Bit-Manipulation Instructions

| Instruction | Operands | Name of Instruction        |  |  |

|-------------|----------|----------------------------|--|--|

| TCM         | dst,src  | Test Complement Under Mask |  |  |

| TM          | dst,src  | Test Under Mask            |  |  |

# Block-Transfer Instruction

| Instruction | Operands | Name of Instruction                 |

|-------------|----------|-------------------------------------|

| LDCI        | dst,src  | Load Constant Autoincrement         |

| LDEI        | dst,src  | Load External Data<br>Autoincrement |

# Rotate and Shift Instructions

| In | struction | Operand | Name of Instruction        |

|----|-----------|---------|----------------------------|

|    | RL        | dst     | Rotate Left                |

|    | RLC       | dst     | Rotate Left Through Carry  |

|    | RR        | dst     | Rotate Right               |

|    | RRC       | dst     | Rotate Right Through Carry |

|    | SRA       | dst     | Shift Right Arithmetic     |

|    | SWAP      | dst     | Swap Nibbles               |

### CPU Control Instructions

| CCFComplement CarryDIDisable InterruptEIEnable InterruptsNOPNo OperationRCFReset Carry FlagSCFSet Carry FlagSRPsrcSet Register Poin | s |

|-------------------------------------------------------------------------------------------------------------------------------------|---|

#### 3.2 Notation

Operands and status flags are represented by a notational shorthand in the detailed instruction descriptions that make up the rest of this chapter. The notation for operands (condition codes and address modes) and the actual operands they represent are as follows:

| Notation | Address Mode                                          | Actual Operand/Range                                                                                                                                  |

|----------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| cc       | Condition Code                                        | See condition code list below                                                                                                                         |

| r        | Working register<br>only                              | $\underline{Rn}$ , where $n = 0-15$                                                                                                                   |

| R        | Register or<br>working register                       | reg=0-127, 240-255 or<br>Rn as defined above                                                                                                          |

| RR       | Register pair or<br>working register<br>pair          | reg, where reg is an<br>even number in the range<br>above or a variable whose<br>address is even or <u>RRp</u> where<br>p = 0,2,4,614                 |

| Ir       | Indirect working<br>register only                     | $\underline{@Rn}$ , where n = 0-15                                                                                                                    |

| IR       | Indirect register<br>or working<br>register           | <pre>@reg, where reg is as defined above or @Rn, as defined above</pre>                                                                               |

| Irr      | Indirect working<br>register pair only                | $\frac{(RRp)}{614}$ , where p = 0,2,4,                                                                                                                |

| IRR      | Indirect register<br>pair or working<br>register pair | <u>@reg</u> , where reg is an<br>even number in the range<br>defined above, or a<br>variable whose address is<br>even or <u>@RRp</u> as defined above |

| Notation | Address Mode        | Actual Operand/Range                                                                                                                                        |

|----------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| x        | Indexed             | <u>reg(Rn)</u> , where reg<br>and Rn are as defined<br>abo e                                                                                                |

| DA       | Direct Address      | Program label or expression                                                                                                                                 |

| RA       | Relative<br>Address | Program label or \$ + or -<br>offset, where the location<br>addressed must be in the<br>range +127, -128 bytes<br>from the start of the<br>next instruction |

| IM       | Immediate           | <u>#data,</u> where data is an<br>expression                                                                                                                |

Status Flags are represented as follows:

| С | Carry flag          |

|---|---------------------|

| Z | Zero flag           |

| S | Sign flag           |

| V | Overflow flag       |

| D | Decimal adjust flag |

| H | Half carry flag     |

The condition codes and the flag settings they represent are:

| Code    | Meaning               | Flag Settings            | Binary |

|---------|-----------------------|--------------------------|--------|

| F       | Always false          |                          | 0000   |

| (blank) | Always true           |                          | 1000   |

| Z       | Zero                  | Z = 1                    | 0110   |

| NZ      | Not zero              | Z = 0                    | 1110   |

| С       | Carry                 | C = 1                    | 0111   |

| NC      | No carry              | C = 0                    | 1111   |

| PL      | Plus                  | S = 0                    | 1101   |

| MI      | Minus                 | S = 1                    | 0101   |

| NE      | Not equal             | $\mathbf{Z} = 0$         | 1110   |

| EQ      | Equal                 | Z = 1                    | 0110   |

| ov      | Overflow              | V = 1                    | 0100   |

| NOV     | No overflow           | V = 0                    | 1100   |

| GE      | Greater than          | (S XOR V) = 0            | 1001   |

|         | or equal              |                          |        |

| LT      | Less than             | (S XOR V) = 1            | 0001   |

| GT      | Greater than          | (Z  OR  (S  XOR  V)) = 0 | 1010   |

| LE      | Less than or<br>equal | (Z  OR  (S  XOR  V)) = 1 | 0010   |

| Code       | Meaning                                        | Flag Settings              | Binary       |

|------------|------------------------------------------------|----------------------------|--------------|

| UGE        | Unsigned greater<br>than or equal              | C=0                        | 1111         |

| ULT<br>UGT | Unsigned less than<br>Unsigned greater<br>than | C=1<br>((C=0) & (Z=0)) = 1 | 0111<br>1011 |

| ULE        | Unsigned less than<br>or equal                 | (C OR Z) = 1               | 0011         |

Note that some of the condition codes correspond to identical flag settings: Z-EQ, NZ-NE, C-ULT, NC-UGE.

#### 3.3 Assembly-Language Instructions

In the remainder of this section, Z8 assembly-language instructions are described in detail in alphabetical order. Each description includes:

- The name of the instruction

- The binary instruction formats

- The operation performed by the instruction

- The status flags affected by the instruction

- The number of machine cycles used to execute the instruction

- The number of bytes used by the instruction

- A short example showing the use of the instruction

The description of each instruction's operation includes a shorthand summary. In addition to symbols already listed above, the following are also used in these summaries.