# **Z8® Microcontrollers**

Embedded Controllers can be used in a variety of applications.

User's Manual

# **Z8<sup>®</sup> Microcontrollers**

# **User's Manual**

#### 1990 - An 1

,

# **Overview**

# Zilog's Focus on Application-Specific Products Helps You Maintain Your Technological Edge

# **The Z8® Microcontroller User's Manual consists** of the following:

- Z8<sup>®</sup> Architecture Technical Description

- Zilog Software User's Guides

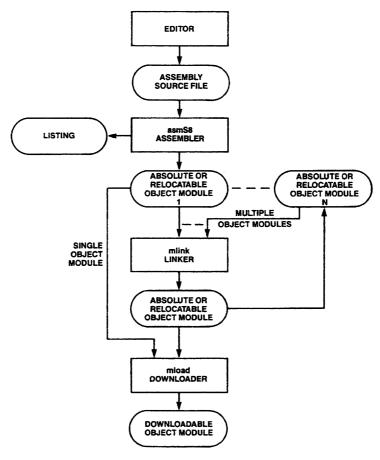

- asm Z8<sup>®</sup> Cross Assembler

- Zilog Universal Object File Utilities

- Zilog General Information

- General Terms and Conditions

- Zilog Sales Offices, Representatives, and Distributors

- Zilog Literature Guide

Application notes and other information on Zilog specialty software and documentation is available through the Zilog Bulletin Board Service (ZBBS), which can be reached by calling 408-370-8024 (up to 28.8 baud supported, 8-N-1 connections, and ANSI/BBS terminal emulation setup recommended). © 1994, 1995 by Zilog, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Zilog, Inc. The information in this document is subject to change without notice. Devices sold by Zilog, Inc. are covered by warranty and patent indemnification provisions appearing in Zilog, Inc. Terms and Conditions of Sale only. Zilog, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Zilog, Inc. makes no warranty of may appear in this document. Zilog, Inc. makes no commitment to update or keep current the information contained in this document.

Zilog's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and Zilog prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

Zilog, Inc. 210 East Hacienda Ave. Campbell, CA 95008-6600 Telephone (408) 370-8000 Telex 910-338-7621 FAX 408 370-8056 Internet: http://www.zilog.com/zilog

# ZILOG Z8® MICROCONTROLLERS USER'S MANUAL

# TABLE OF CONTENTS

## I. Z8® MICROCONTROLLER TECHNICAL DESCRIPTION

| CHAPTER TITLE AND SUBSECTIONS                        | PAGE |

|------------------------------------------------------|------|

| CHAPTER 1: DISCRETE Z8 <sup>®</sup> PRODUCT OVERVIEW |      |

| 1.1 Z8 MCU Family Overview                           | 1-1  |

| CHAPTER 2: ADDRESS SPACE                             |      |

| 2.1 Introduction                                     | 2-1  |

| 2.2 Z8® Standard Register File                       |      |

| 2.3 Z8 <sup>®</sup> Expanded Register File           |      |

| 2.4 Z8 <sup>®</sup> Control and Peripheral Registers |      |

| 2.5 Program Memory                                   |      |

| 2.6 Z8 <sup>®</sup> External Memory                  |      |

| 2.7 Z8 <sup>®</sup> Stacks                           |      |

|                                                      |      |

| CHAPTER 3: CLOCK                                     | 0.4  |

| 3.1 Clock                                            |      |

| 3.2 Clock Control                                    |      |

| 3.3 Oscillator Control                               |      |

| 3.4 Oscillator Operation                             |      |

| 3.5 LC Oscillator                                    |      |

| 3.6 RC Oscillator                                    |      |

| Chapter 4: Reset—Watch-Dog Timer                     |      |

| 4.1 Reset                                            |      |

| 4.2 /Reset Pin, Internal POR Operation               | 4-1  |

| 4.3 Watch-Dog Timer (WDT)                            |      |

| 4.4 Power-On-Reset (POR)                             |      |

| CHAPTER 5: I/O PORTS                                 |      |

| 5.1 Introduction                                     | 5-1  |

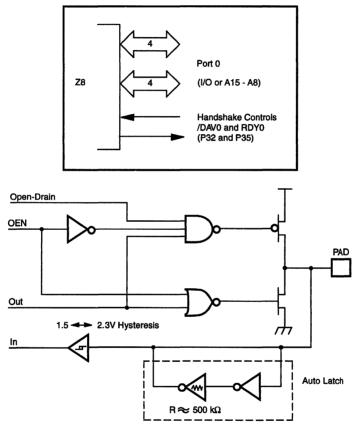

| 5.2 Port 0                                           |      |

| 5.3 Port 1                                           |      |

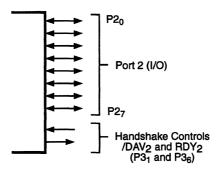

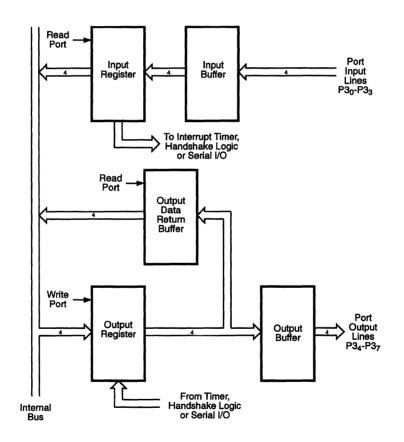

| 5.4 Port 2                                           |      |

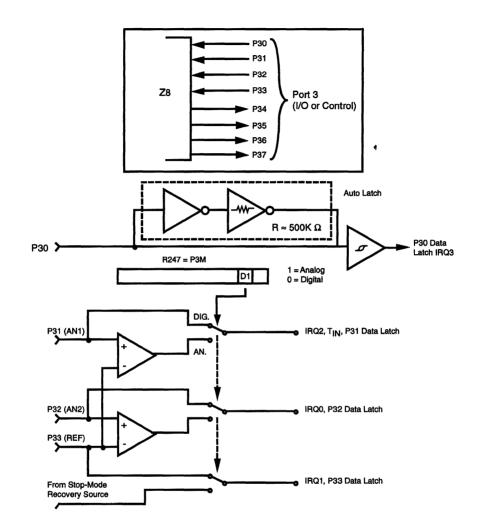

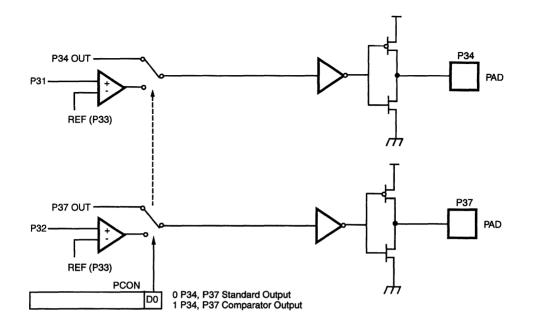

| 5.5 Port 3                                           |      |

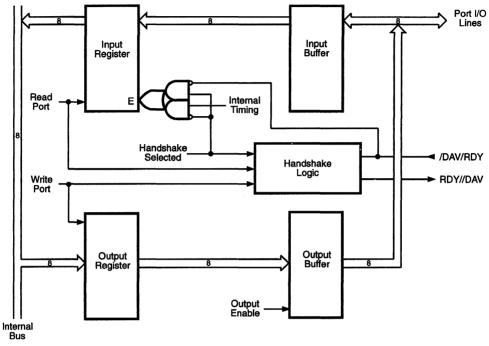

| 5.6 Port Handshake                                   |      |

| 5.7 I/O Port Reset Conditions                        |      |

|                                                      |      |

# PAGE

# CHAPTER 5: I/O PORTS (CONTINUED)

| 5.8 Analog Comparators       | 5 |

|------------------------------|---|

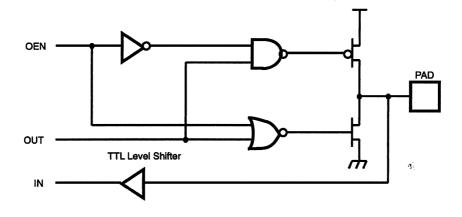

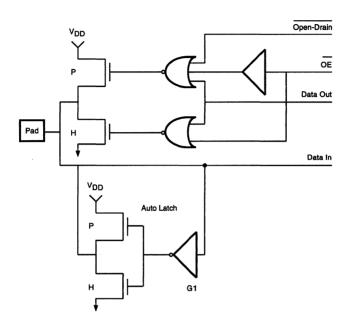

| 5.9 Open-Drain Configuration |   |

| 5.10 Low EMI Emission        |   |

| 5.11 Input Protection        |   |

| 5.12. CMOS Z8® Auto Latches  |   |

# CHAPTER 6: COUNTER/TIMERS

| 6.1 Introduction                                                                                                      | 6-1  |

|-----------------------------------------------------------------------------------------------------------------------|------|

| 6.2 Prescalers and Counter/Timers                                                                                     | 6-2  |

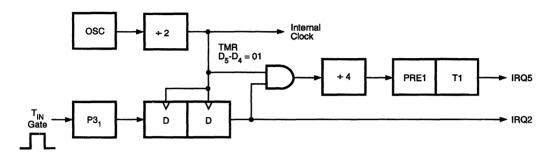

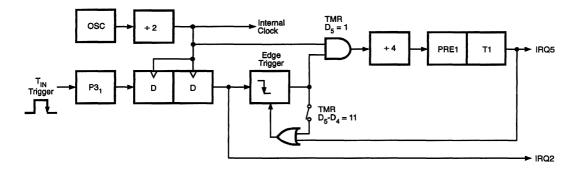

| 6.3 Counter/Timer Operation                                                                                           | 6-3  |

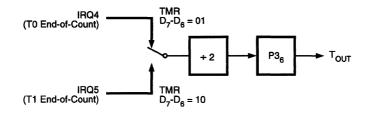

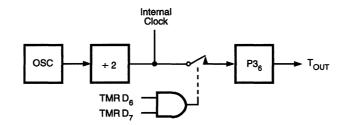

| 6.4 Tour Modes                                                                                                        | 6-5  |

| <ul> <li>6.4 T<sub>out</sub> Modes</li> <li>6.5 T<sub>IN</sub> Modes</li> <li>6.6 Cascading Counter/Timers</li> </ul> | 6-7  |

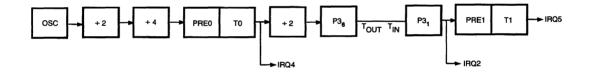

| 6.6 Cascading Counter/Timers                                                                                          | 6-11 |

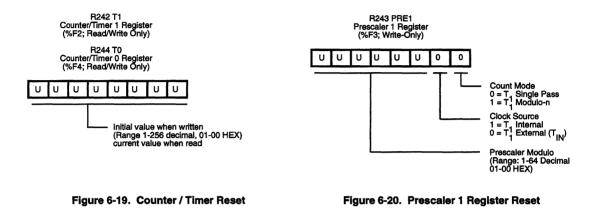

| 6.7 Reset Conditions                                                                                                  | 6-12 |

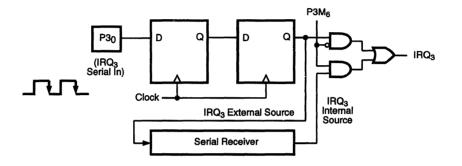

#### **CHAPTER 7: INTERRUPTS**

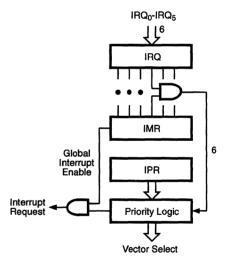

| 7.1 Introduction                                        | 1 |

|---------------------------------------------------------|---|

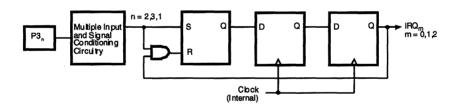

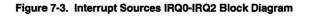

| 7.2 Interrupt Sources                                   | 2 |

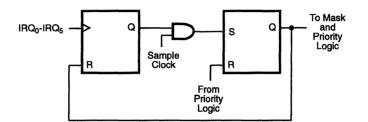

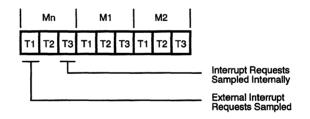

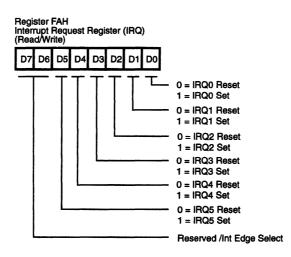

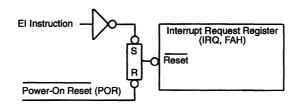

| 7.3 Interrupt Request (IRQ) Register Logic and Timing7- | 4 |

| 7.4 Interrupt Initialization                            | 5 |

| 7.5 IRQ Software Interrupt Generation                   | 9 |

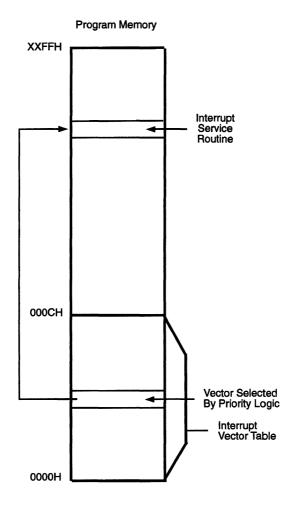

| 7.6 Vectored Processing                                 | 9 |

| 7.7 Polled Processing                                   | 2 |

| 7.8 Reset Conditions                                    | 2 |

# CHAPTER 8: POWER-DOWN MODES

| 8.1 Introduction                      | 8-1 |

|---------------------------------------|-----|

| 8.2 Halt Mode Operation               | 8-1 |

| 8.3 STOP Mode Operation               |     |

| 8.4 STOP-Mode Recovery Register (SMR) |     |

### CHAPTER 9: SERIAL I/O

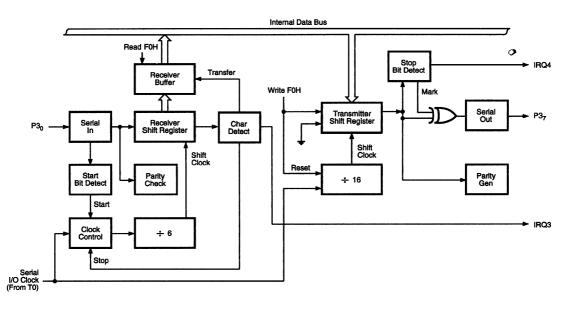

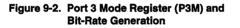

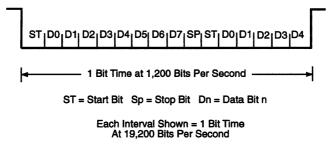

| 9.1 UART Introduction                        | 9-1  |

|----------------------------------------------|------|

| 9.2 UART Bit-Rate Generation                 | 9-2  |

| 9.3 UART Receiver Operation                  | 9-4  |

| 9.4 Transmitter Operation                    | 9-6  |

| 9.5 UART Reset Conditions                    | 9-8  |

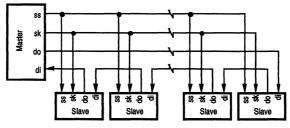

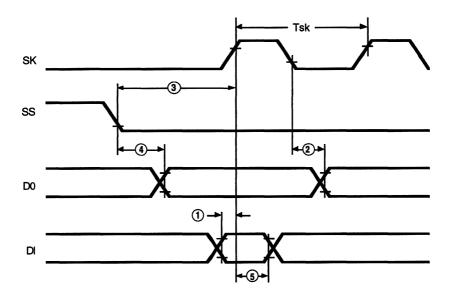

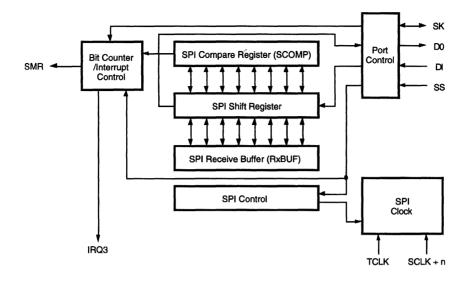

| 9.6 Serial Peripheral Interface (SPI)        | 9-9  |

| 9.7 SPI Operation                            | 9-10 |

| 9.8 SPI Compare                              | 9-10 |

| 9.9 SPI Clock                                | 9-10 |

| 9.10 Receive Character Available and Overrun | 9-12 |

|                                              |      |

# PAGE

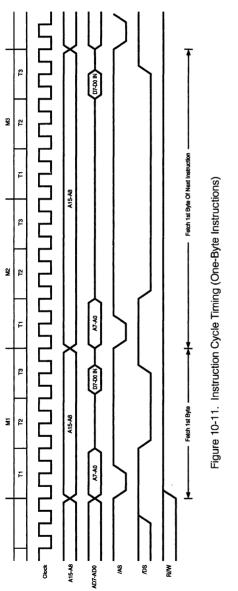

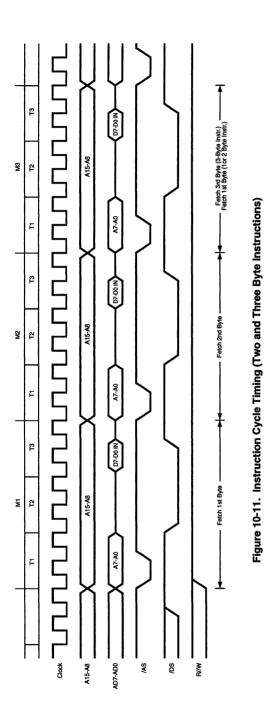

## CHAPTER 10: EXTERNAL INTERFACE

| 10.1 Introduction                      | 10-1 |

|----------------------------------------|------|

| 10.2 Pin Descriptions                  |      |

| 10.3 External Addressing Configuration | 10-3 |

| 10.4 External Stacks                   |      |

| 10.5 Data Memory                       |      |

| 10.6 Bus Operation                     | 10-5 |

| 10.7 Extended Bus Timing               |      |

| 10.8 Instruction Timing                |      |

| 10.9 Z8® RESET CONDITIONS              |      |

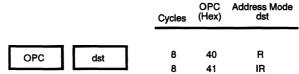

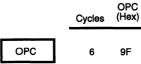

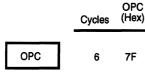

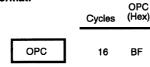

#### CHAPTER 11: ADDRESSING MODES

| 11.1 Introduction                          | . 11-1 |

|--------------------------------------------|--------|

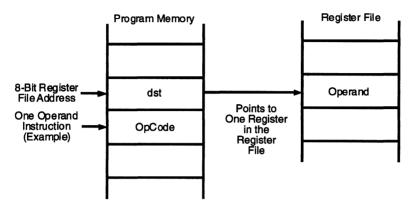

| 11.2 Z8® Register Addressing (R)           | .11-2  |

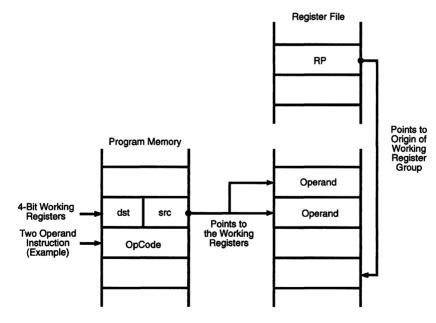

| 11.3 Z8® INDIRECT REGISTER ADDRESSING (IR) | 11-3   |

| 1.4 Z8® INDEXED ADDRESSING (X)             | . 11-5 |

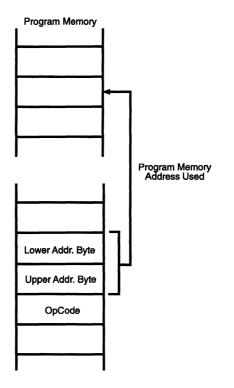

| 11.5 Z8® Direct Addressing (DA)            |        |

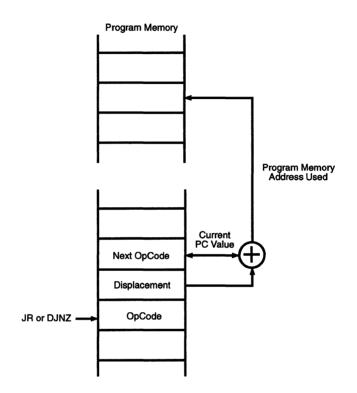

| 11.6 Z8® Relative Addressing (RA)          | .11-7  |

| 11.7 Z8® Immediate Data Addressing (IM)    |        |

# CHAPTER 12: INSTRUCTION SET

| 12.1 Z8® Functional Summary               | 12-1  |

|-------------------------------------------|-------|

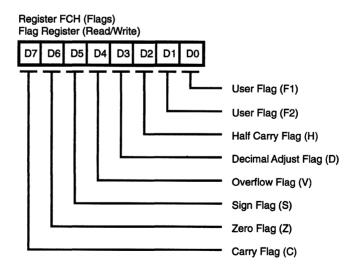

| 12.2 Processor Flags                      | 12-2  |

| 12.3 Condition Codes                      | 12-4  |

| 12.4 Notation and Binary Encoding         | 12-5  |

| 12.5 Z8 Instruction Summary               | 12-7  |

| 12.6 Instruction Descriptions and Formats | 12-10 |

### CHAPTER 13: ZILOG EMULATORS/SOFTWARE

| 13-2  |

|-------|

| 13-3  |

|       |

| 13-5  |

|       |

|       |

|       |

| 13-8  |

| 13-12 |

|       |

| 13-14 |

| 13-14 |

|       |

| 13-16 |

|       |

# PAGE

| 13.14 Timer/Counter Functions |  |

|-------------------------------|--|

| 13.15 I/O Functions           |  |

| 13.16 Arithmetic Routines     |  |

| 13.17 Conclusion              |  |

## CHAPTER 14: THIRD-PARTY SUPPORT TOOLS

| 14.1 Third-Party Support—Emulators/Programmers  | 14-1 |

|-------------------------------------------------|------|

| 14.2 Third-Party Support—Assemblers/C Compilers | 14-1 |

PAGE

#### II. ZILOG Z8® SOFTWARE

# ASM Z8® CROSS ASSEMBLER USER'S GUIDE

# CHAPTER TITLE AND SUBSECTIONS

#### CHAPTER 1: OVERVIEW

| 1.1 Introduction           | 1-1 | 1 |

|----------------------------|-----|---|

| 1.2 Assembler Overview     | 1-2 | 2 |

| 1.3 Relocation and Linking | 1-3 | 3 |

#### CHAPTER 2: ASSEMBLY LANGUAGE SYNTAX

| 2.2 Symbolic Notation2-12.3 Operations and Operands2-62.4 Comments2-62.5 Arithmetic Expressions2-72.6 Expressions and Operators2-7 |

|------------------------------------------------------------------------------------------------------------------------------------|

| 2.3 Operations and Operands       2-6         2.4 Comments       2-6         2.5 Arithmetic Expressions       2-7                  |

| 2.4 Comments       2-6         2.5 Arithmetic Expressions       2-7                                                                |

| 2.5 Arithmetic Expressions                                                                                                         |

|                                                                                                                                    |

|                                                                                                                                    |

| 2.7 Constants                                                                                                                      |

| 2.8 Location Counter                                                                                                               |

#### CHAPTER 3: PSEUDO-OPS

| 3.1 Introduction                      | 3-1   |

|---------------------------------------|-------|

| 3.2 Relocation Pseudo-Ops             | 3-1   |

| 3.3 Label Definition Pseudo-Ops       | 3-3   |

| 3.4 Module and Section Pseudo-Ops     | . 3-6 |

| 3.5 General Data Definition Operation | . 3-8 |

| 3.6 Conditional Assembly Pseudo-Ops   | 3-12  |

| 3.7 Assembler Control Pseudo-Ops      | 3-13  |

#### CHAPTER 4: MACROS

| 4.1 General Description      | 4-1 |

|------------------------------|-----|

| 4.2 MACRO or String MACRO    |     |

| 4.3 PROC or Procedure MACRO  |     |

| 4.4 Special MACRO Pseudo-Ops | 4-4 |

| 4.5 Special MACRO Operators  |     |

#### CHAPTER 5: PROGRAM INVOCATION

| 5.1 Assembler Command Lines and Options | 5-1 |

|-----------------------------------------|-----|

| 5.2 Listing Format                      | 5-2 |

| 5.3 Program Termination                 | 5-2 |

#### APPENDICES

| Appendix A. | Pseudo-Op Summary               | A-1 |

|-------------|---------------------------------|-----|

| Appendix B. | Special Symbols                 | B-1 |

|             | ASCII Character Set             |     |

|             | Error Messages and Explanations |     |

|             | Program Example                 |     |

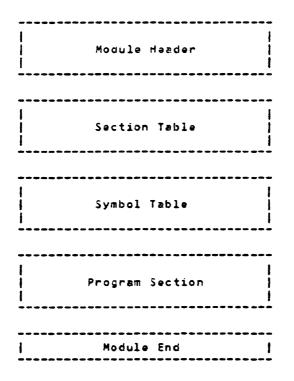

# ZILOG UNIVERSAL OBJECT FILE UTILITIES USER'S GUIDE

# CHAPTER TITLE AND SUBSECTIONS PAGE

#### CHAPTER 1: INTRODUCTION

| 1.1 Overview              | 1-  | 1 |

|---------------------------|-----|---|

| 1.2 Utilities Description | 1-2 | 2 |

| 1.3 Utility Invocation    | 1-6 | 3 |

#### **CHAPTER 2: MCONV**

| 2.1 Ir | 1troduction2                | -1 |

|--------|-----------------------------|----|

| 2.2 C  | command Syntax and Options2 | -1 |

#### CHAPTER 3: MDUMP

| 3.1 Introduction                 | 3-1 |

|----------------------------------|-----|

| 3.2 Command Syntax and Options   | 3-1 |

| 3.3 Display Formats and Examples | 3-2 |

## CHAPTER 4: MLIB

| 4.1 Introduction               | .4•1 |

|--------------------------------|------|

| 4.2 Command Syntax and Options | .4-1 |

| 4.3 Examples                   | .4-2 |

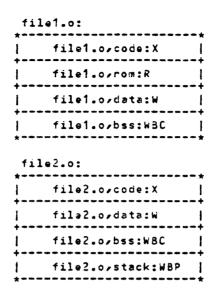

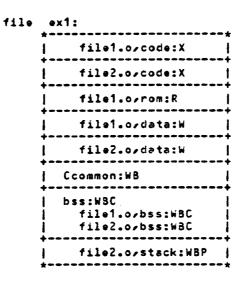

## CHAPTER 5: MLINK

| 5.1 Introduction                    | 5-1  |

|-------------------------------------|------|

| 5.2 Command Line Syntax and Options | 5-4  |

| 5.3 Constraints                     | 5-13 |

| 5.4 Using MLINK: Some Examples      | 5-14 |

## CHAPTER 6: MLIST

| 6.1 Introduction                      | 6-1   |

|---------------------------------------|-------|

| 6.2 Command Syntax and Options        | 6-1   |

| 6.3 Usage, Output Format and Examples | . 6-1 |

# CHAPTER 7: MLIST

| 7.1 Introduction               | .7-1 |

|--------------------------------|------|

| 7.2 Command Syntax and Options | .7-1 |

| 7.3 Operation                  | .7-2 |

| 7.4 Using MLOAD: Some Examples | 7-3  |

#### CHAPTER 8: MLORDER

| 8.1 Introduction               | 8-1 |

|--------------------------------|-----|

| 8.2 Command Syntax and Options | 8-1 |

#### CHAPTER 9: MMM

| 9.1 Introduction               | 9-1 |

|--------------------------------|-----|

| 9.2 Command Syntax and Options | 9-1 |

| 9.3 Output Format and Examples | 9-1 |

# CHAPTER 10: PROTOCOL

| 10.1 Introduction                      | 1 |

|----------------------------------------|---|

| 10.2 Command Syntax and Options10-     | 1 |

| 10.3 Using PROTOCOL: Some Examples 10- |   |

# CHAPTER 11: OTHER PROGRAMS

| 11.1 MAR1      | 1-1 |

|----------------|-----|

| 11.2 M2A       | 1-1 |

| 11.3 MUIMAGE 1 | 1-2 |

#### APPENDICES

| Appendix A. MUFOM File Format    | A-1 |

|----------------------------------|-----|

| Appendix B. Tektronix Hex Format |     |

| Appendix C. Intel Hex Format     |     |

| Appendix D. Error Messages       |     |

|                                  |     |

| Glossarv                         | G-1 |

# **III. ADDITIONAL INFORMATION**

| General Terms and Conditions                           |  |

|--------------------------------------------------------|--|

| ZILOG SALES OFFICES, REPRESENTATIVES, AND DISTRIBUTORS |  |

| ZILOG LITERATURE GUIDEL-1                              |  |

•

# Z8® Microcontroller Technical Description

Zilog Z8° Software

Zilog General Information

USER'S MANUAL

# <sup>⊗</sup>ZiLŒ

#### **1.1 Z8 MCU FAMILY OVERVIEW**

The Zilog Z8<sup>®</sup> microcontroller product line continues to expand with new product introductions. Zilog MCU products are targeted for cost-sensitive, high-volume applications including consumer, automotive, security, and HVAC. It includes ROM-based products geared for high-volume production (where software is stable) and one-time programmable (OTP) equivalents for prototyping as well as volume production where time to market or code flexibility is critical (Table 1-1). A variety of packaging options are available including plastic DIP, SOIC, PLCC, and QFP.

# **CHAPTER 1** DISCRETE Z8<sup>®</sup> PRODUCT OVERVIEW

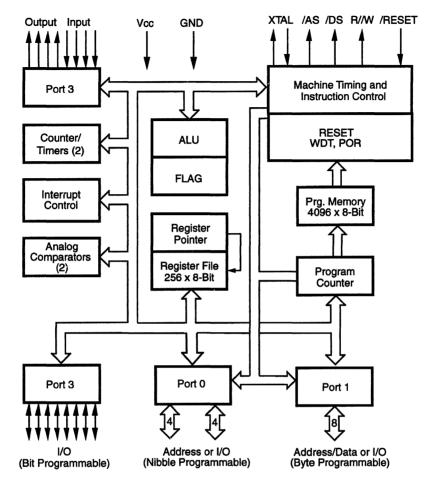

A generalized Z8 MCU block diagram is shown in Figure 1-1. The same on-chip peripherals are used across the MCU product line with the primary differences being the amount of ROM/RAM, number of I/O lines present, and packaging/temperature ranges available. This allows code written for one MCU device to be easily ported to another family member.

#### **1.1.1 Key Product Line Features**

- General-Purpose Register (GPR) File Architecture: Every RAM register acts like an accumulator, speeding instruction execution and maximizing coding efficiency. Working register groups allow fast context switching.

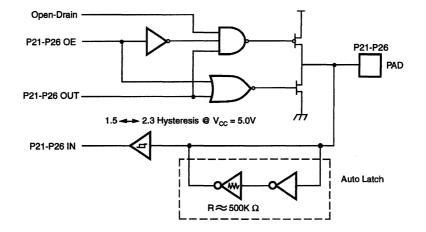

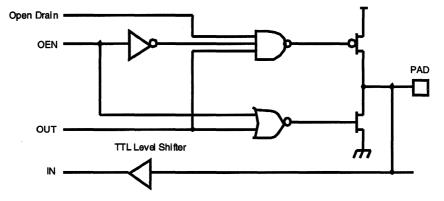

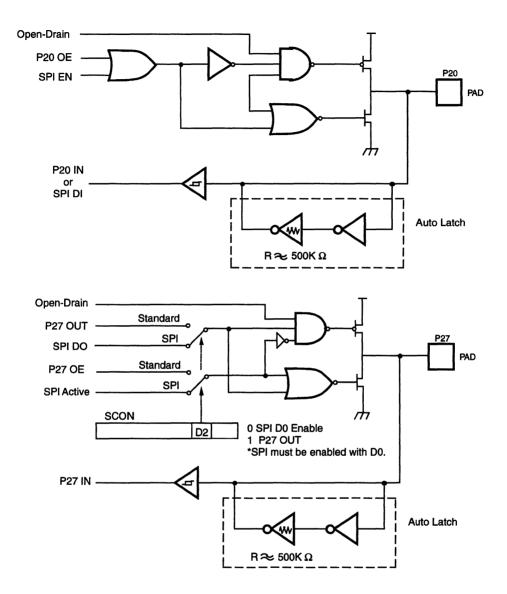

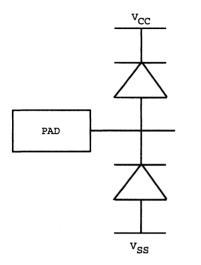

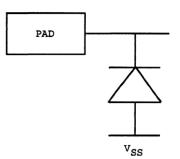

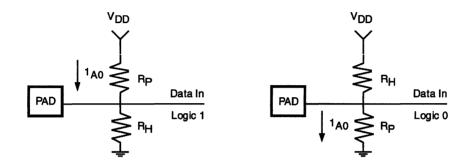

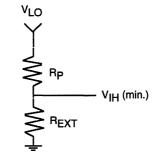

- Flexible I/O: I/O byte, nibble, and/or bit programmable as inputs or outputs. Outputs are software programmable as open-drain or push-pull on a port basis. Inputs are Schmitt-triggered with auto latches to hold unused inputs at a known voltage state.

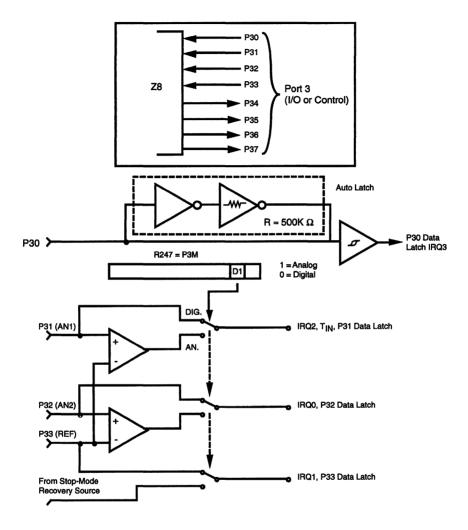

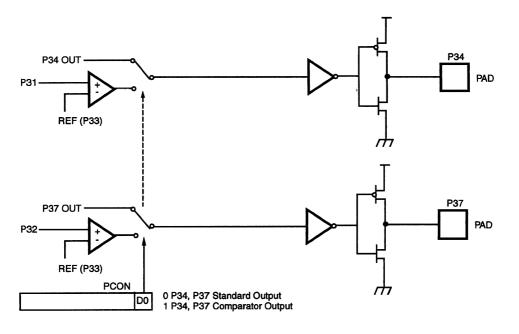

- Analog Inputs: Three input pins are software programmable as digital or analog inputs. When in the analog mode, two comparator inputs are provided with a common reference input. These inputs are ideal for a variety of common functions, including threshold level detection, analog-to-digital conversion, and short circuit detection. Each analog input provides a unique maskable interrupt input.

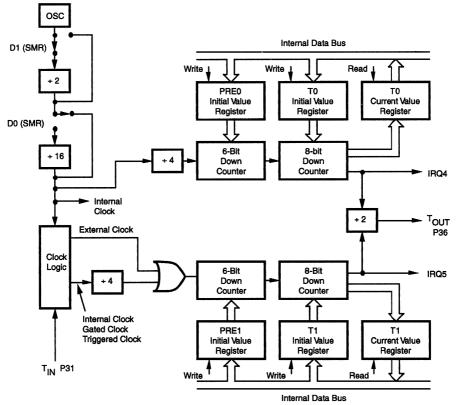

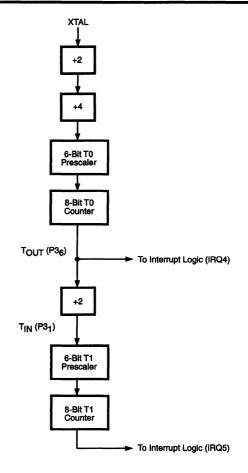

- Timer/Counter(T/C): The T/C consists of a programmable 6-bit prescaler and 8-bit downcounter, with maskable interrupt upon end-of-count. Software controls T/C load/start/stop, countdown read (at any time on the fly), and maskable end-of-count interrupt. Special functions available include T<sub>IN</sub>(external counter input, external gate input, or external trigger input) and T<sub>our</sub> (external access to timer output or the internal system clock.) These special functions allow accurate hardware input pulse measurement and output waveform generation.

- Interrupts: There are six vectored interrupt sources with software-programmable enable and priority for each of the six sources.

- Watch-Dog Timer (WDT): An internal WDT circuit is included as a fail-safe mechanism so that if software strays outside the bounds of normal operation, the WDT will timeout and reset the MCU. To maximize circuit robustness and reliability, the default WDT clock source is an internal RC circuit (isolated from the device clock source).

- Auto Reset/Low-Voltage Protection: All family devices have internal Power-On Reset. ROM devices add low-voltage protection. Low-voltage protection ensures the MCU is in a known state at all times (in active RUN mode or RESET) without external hardware (or a device reset pin).

- Low-EMI Operation: Mode is programmable via software or as a mask option. This new option provides for reduced radiated emission via clock and output drive circuit changes.

- Low-Power: CMOS with two standby modes; STOP and HALT.

- Full Z8 Instruction Set: Forty-eight basic instructions, supported by six addressing modes with the ability to operate on bits, nibbles, bytes, and words.

Figure 1-1. Z8® MCU Block Diagram

#### **1.1.2 Product Development Support**

The Z8<sup>®</sup> MCU product line is fully supported with a range of cross assemblers, C compilers, ICEBOX emulators, single and gang OTP/EPROM programmers, and software simulators.

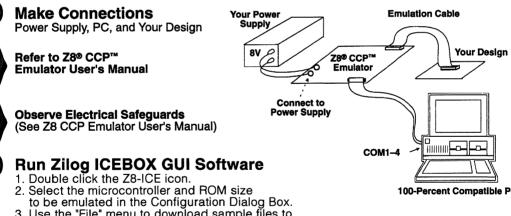

The Z86CCP00ZEM low-cost Z8 CCP™ real-time emulator/programmer kit was designed specifically to support all the products outlined in Table 1-1.

| Table 1-1. Zilog General-Purpose Microcontroller Product Family |             |     |     |          |     |     |     |     |    |                |              |

|-----------------------------------------------------------------|-------------|-----|-----|----------|-----|-----|-----|-----|----|----------------|--------------|

| PRODUCT                                                         | ROM/<br>RAM | 1/0 | T/C | AN<br>IN | INT | WDT | POR | Vbo | RC | SPEED<br>(MHz) | PIN<br>COUNT |

| Z86C03                                                          | 512/60      | 14  | 1   | 2        | 6   | F   | Y   | Y   | Y  | 8              | 18           |

| Z86C03                                                          | 512/60      | 14  | 1   | 2        | 6   | F   | Y   | Ν   | Y  | 8              | 18           |

| Z86C04                                                          | 1K/124      | 14  | 2   | 2        | 6   | F   | Y   | Y   | Ν  | 8              | 18           |

| Z86E04                                                          | 1K/124      | 14  | 2   | 2        | 6   | F   | Y   | N   | Ν  | 8              | 18           |

| Z86C06                                                          | 1K/124      | 14  | 2   | 2        | 6   | Р   | Y   | Y   | Y  | 12             | 18           |

| Z86E06                                                          | 1K/124      | 14  | 2   | 2        | 6   | Р   | Y   | N   | Y  | 12             | 18           |

| Z86C08                                                          | 2K/124      | 14  | 2   | 2        | 6   | F   | Y   | Y   | Ν  | 12             | 18           |

| Z86E08                                                          | 2K/124      | 14  | 2   | 2        | 6   | F   | Y   | Ν   | Ν  | 12             | 18           |

| Z86C30                                                          | 4K/236      | 24  | 2   | 2        | 6   | Р   | Y   | Y   | Y  | 12             | 28           |

| Z86E30                                                          | 4K/236      | 24  | 2   | 2        | 6   | Р   | Y   | N   | Y  | 12             | 28           |

| Z86C31                                                          | 2K/124      | 24  | 2   | 2        | 6   | Р   | Y   | Y   | Y  | 8              | 28           |

| Z86E31                                                          | 2K/124      | 24  | 2   | 2        | 6   | Р   | Y   | N   | Y  | 8              | 28           |

| Z86C40                                                          | 4K/236      | 32  | 2   | 2        | 6   | Р   | Y   | Y   | Y  | 12             | 40/44        |

| Z86E40                                                          | 4K/236      | 32  | 2   | 2        | 6   | Р   | Y   | N   | Y  | 12             | 40/44        |

Note: Z86Cxx signify ROM devices; Z86Exx signify EPROM devices; F = fixed; P = programmable.

The Z86CCP00ZEM kit comes with:

- Z8 CCP Emulator/Programmer Module

- 18-pin Target Connection Cable

- WINDOWS-based GUI Host Software

- DOS-based ZASM LINKER/LOADER

- Documentation: Z8MOBJ Linker/Loader User's Guide, Z8 Cross Assembler User's Guide, Z8 Emulator GUI User's Guide, Discrete Z8 MCU Product Specifications Databook, and Z8 MCU Technical Manual.

A Z8 CCP Emulator Accessory Kit (Z8CCP00ZAC) is also available and provides an RS-232 cable and power cable along with the 28- and 40- pin ZIF sockets and 28 and 40 pin target connector cables required to emulate/program 28/40 pin devices.

USER'S MANUAL

# **CHAPTER 2**

**ADDRESS SPACE**

## 2.1 INTRODUCTION

<sup>⊗</sup>ZiLŒ

Four address spaces are available for the Z8® microcontroller:

- The Z8 Standard Register File contains addresses for peripheral, control, all general-purpose, and all I/O port registers. This is the default register file specification.

- The Z8 Expanded Register File (ERF) contains

addresses for control and data registers for additional peripherals/features.

- Z8 External Program Memory contains addresses for all memory locations having executable code and/or data.

- Z8 External Data Memory contains addresses for all memory locations that hold data only, whether internal or external.

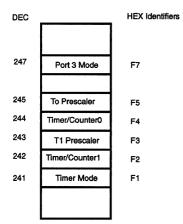

Table 2-1. Z8 Standard Register File

#### 2.2 Z8 STANDARD REGISTER FILE

The Z8 Standard Register File totals up to 256 consecutive bytes (Registers). The register file consists of 4 I/O ports (00H-03H), 236 General-Purpose Registers (04H-EFH), and 16 control registers (F0H-FFH). Table 2-1 shows the layout of the register file, including register names, locations, and identifiers.

| Hex<br>Address | Register<br>Description         | Register<br>Identifier |  |

|----------------|---------------------------------|------------------------|--|

| FF             | Stack Pointer Low Byte          | SPL                    |  |

| FE             | Stack Pointer High Byte         | SPH                    |  |

| FD             | Register Pointer                | RP                     |  |

| FC             | Program Control Flags           | FLAGS                  |  |

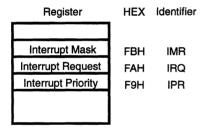

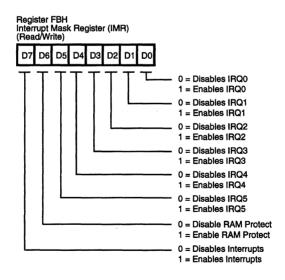

| FB             | Interrupt Mask Register         | IMR                    |  |

| FA             | Interrupt Request Register      | IRQ                    |  |

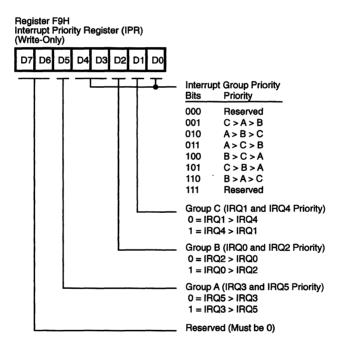

| F9             | Interrupt Priority Register     | IPR                    |  |

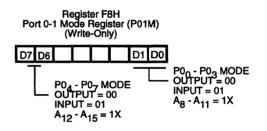

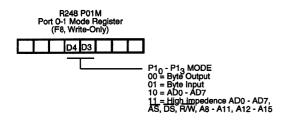

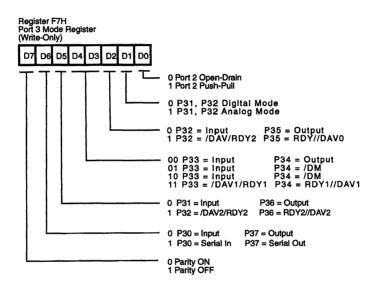

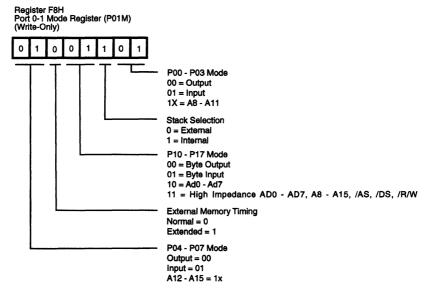

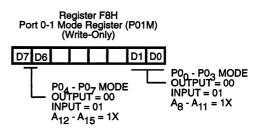

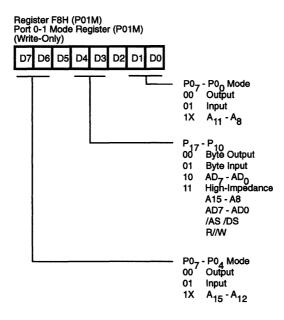

| F8             | Port 0-1 Mode Register          | P01M                   |  |

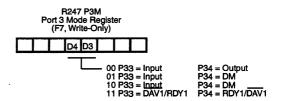

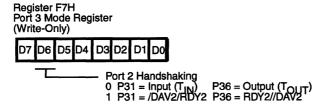

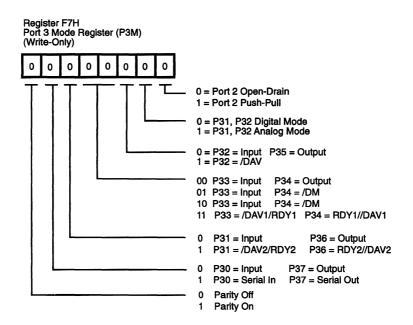

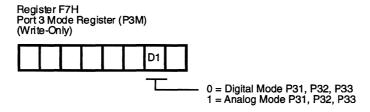

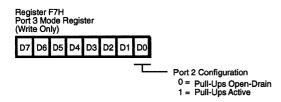

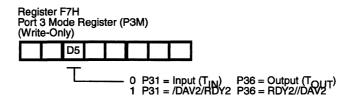

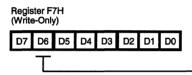

| F7             | Port 3 Mode Register            | P3M                    |  |

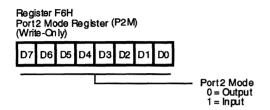

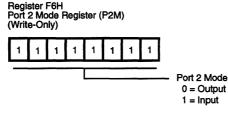

| F6             | Port 2 Mode Register            | P2M                    |  |

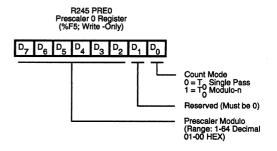

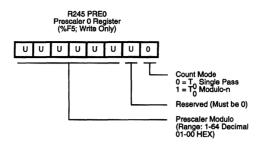

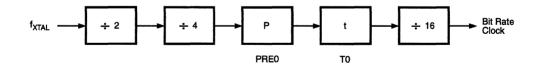

| F5             | T0 Prescaler                    | PREO                   |  |

| F4             | Timer/Counter 0                 | TO                     |  |

| F3             | T1 Prescaler                    | PRE1                   |  |

| F2             | Timer/Counter 1                 | T1                     |  |

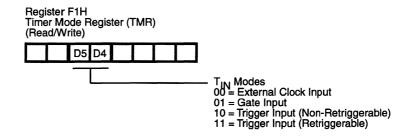

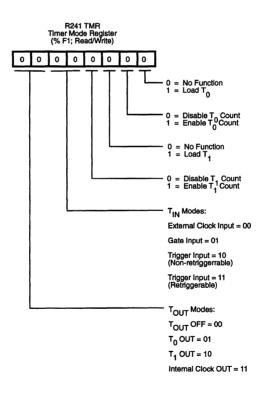

| F1             | Timer Mode                      | TMR                    |  |

| F0             | Serial I/O                      | SIO                    |  |

| EF             |                                 | R239                   |  |

|                |                                 |                        |  |

| •              | General-Purpose Registers (GPR) | •                      |  |

| 04             |                                 | R4                     |  |

|                |                                 |                        |  |

| 03             | Port 3                          | P3                     |  |

| 02             | Port 2                          | P2                     |  |

| 01             | Port 1                          | P 1                    |  |

| 00             | Port O                          | P 0                    |  |

**Note:** Refer to the product specification to determine which registers are available for use on any specific device.

# 2.2 Z8 STANDARD REGISTER FILE (Continued)

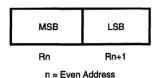

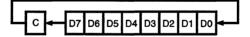

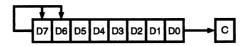

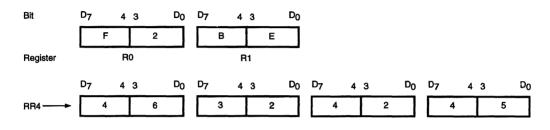

Registers can be accessed as either 8-bit or 16-bit registers using Direct, Indirect, or Indexed Addressing. All 236 general-purpose registers can be referenced or modified by any instruction that accesses an 8-bit register, without the need for special instructions. Registers accessed as 16 bits are treated as even-odd register pairs (there are 118 valid pairs). In this case, the data's Most Significant Byte (MSB) is stored in the even numbered register, while the Least Significant Byte (LSB) goes into the next higher odd numbered register (Figure 2-1).

Figure 2-1. 16-Bit Register Addressing

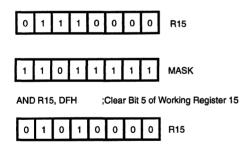

By using a logical instruction and a mask, individual bits within registers can be accessed for bit set, bit clear, bit complement, or bit test operations. For example, the instruction AND R15, MASK performs a bit clear operation. Figure 2-2 shows this example.

Figure 2-2. Accessing Individual Bits (Example)

When instructions are executed, registers are read when defined as sources and written when defined as destinations. All General-Purpose Registers function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

#### 2.2.1 General-Purpose Registers

General-Purpose Registers (GPR) are undefined after the device is powered up. The registers keep their last value after any reset, as long as the reset occurs in the  $V_{cc}$  voltage-specified operating range. It will not keep its last state from a  $V_{LV}$  reset if  $V_{cc}$  drops below 1.8v.

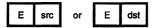

**Note:** Registers in Bank E0-EF may only be accessed through the working register and indirect addressing modes. Direct access cannot be used because the 4-bit working register address mode already uses the format [E I dst], where dst represents the working register number from 0H to FH.

#### 2.2.2 RAM Protect

The upper portion of the register file address space 80FH to EFH (excluding the control registers) may be protected from reading and writing. The RAM Protect bit option is mask-programmable and is selected by the customer when the ROM code is submitted. After the mask option is selected, the user activates this feature from the internal ROM code to turn off/on the RAM Protect by loading either a 0 or 1 into the IMR register, bit D6. A 1 in D6 enables RAM Protect. Only devices that use registers 80H to EFH offer this feature.

#### 2.2.3 Working Register Groups

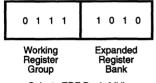

Z8® instructions can access 8-bit registers and register pairs (16-bit words) using either 4-bit or 8-bit address fields. 8-bit address fields refer to the actual address of the register. For example, Register 58H is accessed by calling upon its 8-bit binary equivalent, 01011000 (58H).

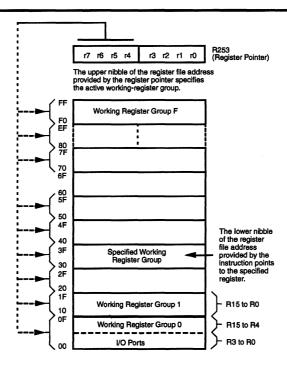

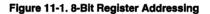

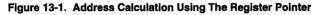

With 4-bit addressing, the register file is logically divided into 16 Working Register Groups of 16 registers each, as shown in Table 2-2. These 16 registers are known as Working Registers. A Register Pointer (one of the control registers, FDH) contains the base address of the active Working Register Group. The high nibble of the Register Pointer determines the current Working Register Group.

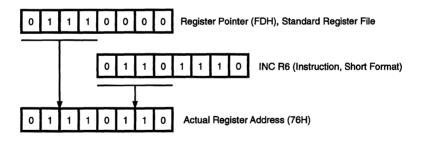

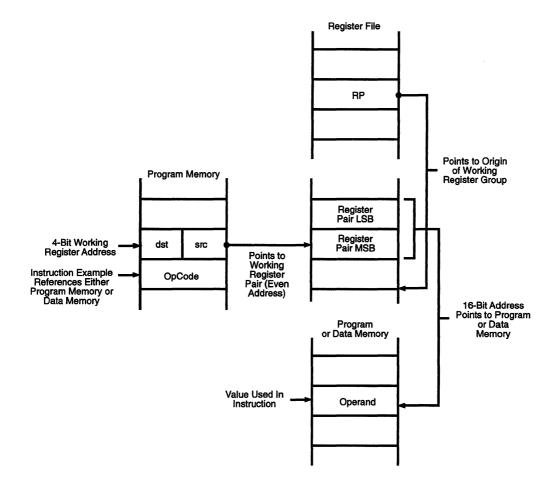

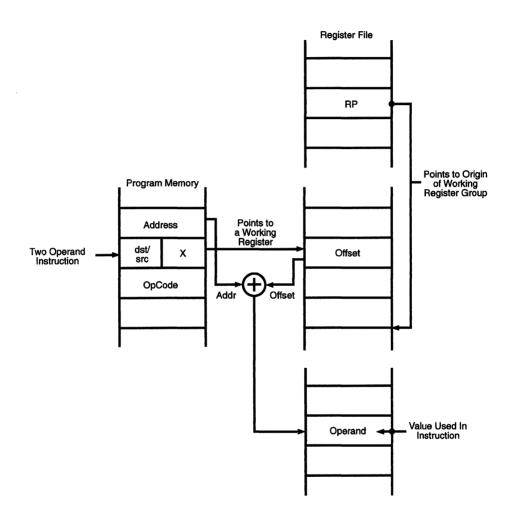

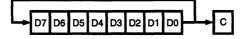

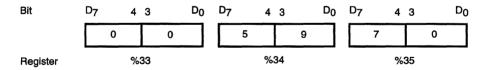

When accessing one of the Working Registers, the 4-bit address of the Working Register is combined within the upper four bits (high nibble) of the Register Pointer, thus forming the 8-bit actual address. Figure 2-3 illustrates this operation. Since working registers are typically specified by short format instructions, there are fewer bytes of code needed, which reduces execution time. In addition, when processing interrupts or changing tasks, the Register Pointer speeds context switching. A special Set Register Pointer (SRP) instruction sets the contents of the Register Pointer.

|                                          |                                    | _                            |

|------------------------------------------|------------------------------------|------------------------------|

| Register Pointer<br>(FDH)<br>High Nibble | Working<br>Register Group<br>(HEX) | Actual<br>Registers<br>(HEX) |

| 1111(B)                                  | F                                  | F0-FF                        |

| 1110(B)                                  | Е                                  | E0-EF                        |

| 1101(B)                                  | D                                  | D0-DF                        |

| 1100(B)                                  | С                                  | C0-CF                        |

| 1011(B)                                  | В                                  | B0-BF                        |

| 1010(B)                                  | Α                                  | A0-AF                        |

| 1001(B)                                  | 9                                  | 90-9F                        |

| 1000(B)                                  | 8                                  | 80-8F                        |

| 0111(B)                                  | 7                                  | 70-7F                        |

| 0110(B)                                  | 6                                  | 60-6F                        |

| 0101(B)                                  | 5                                  | 50-5F                        |

| 0100(B)                                  | 4                                  | 40-4F                        |

| 0011(B)                                  | 3                                  | 30-3F                        |

| 0010(B)                                  | 2                                  | 20-2F                        |

| 0001(B)                                  | 1                                  | 10-1F                        |

| 0000(B)                                  | 0                                  | 00-0F                        |

Figure 2-3. Working Register Addressing Examples

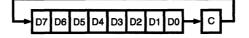

Figure 2-4. Register Pointer

Note: The full register file is shown. Please refer to the selected device product specification for actual file size.

#### 2.2.4 Error Conditions

Registers in the Z8<sup>®</sup> Standard Register File must be correctly used because certain conditions produce inconsistent results and should be avoided.

- Registers F3H and F5H-F9H are write-only registers. If an attempt is made to read these registers, FFH is returned. Reading any write-only register will return FFH.

- When register FDH (Register Pointer) is read, the least significant four bits (lower nibble) will indicate the current Expanded Register File Bank. (Example: 0000 indicates the Standard Register File, while 1010 indicates Expanded Register File Bank A.)

- When Ports 0 and 1 are defined as address outputs, registers 00H and 01H will return 1s in each address bit location when read.

- Writing to bits that are defined as timer output, serial output, or handshake output will have no effect.

- The Z8 instruction DJNZ uses any general-purpose working register as a counter.

- Logical instructions such as OR and AND require that the current contents of the operand be read. They therefore will not function properly on write-only registers.

- The WDTMR register must be written within the first 64 internal system clocks (SCLK) of operation after a reset.

# 2.3 Z8 EXPANDED REGISTER FILE

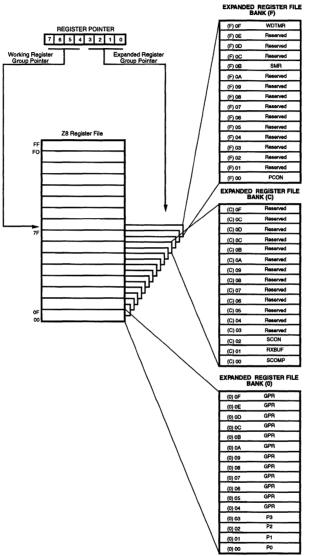

The standard register file of the Z8® has been expanded to form 16 Expanded Register File (ERF) Banks (Figure 2-5). Each ERF Bank consists of up to 256 registers (the same amount as in the Standard Register File) that can then be divided into 16 Working Register Groups. This expansion allows for access to additional feature/peripheral control and data registers.

Figure 2-5. Expanded Register File Architecture

Note: The fully implemented register file is shown. Please refer to the specific product specification for actual register file architecture implemented.

# <sup>©</sup> Silas

Currently, three out of the possible sixteen Z8<sup>®</sup> ERF Banks have been implemented. ERF Bank 0, also known as the Z8 Standard Register File, has all 256 bytes defined (Figure 2-1). Only Working Register Group 0 (register addresses 00H to 0FH) have been defined for ERF Bank C and ERF Bank F (Table 2-4). All other working register groups in ERF Banks C and F, as well as the remaining thirteen ERF Banks, are not implemented. All are reserved for future use.

When an ERF Bank is selected, register addresses 00H to 0FH access those sixteen ERF Bank registers - in effect replacing the first sixteen locations of the Z8 Standard Register File.

For example, if ERF Bank C is selected, the Z8 Standard Registers 00H through 0FH are no longer accessible. Registers 00H through 0FH are now the 16 registers from ERF Bank C, Working Register Group 0. No other Z8 Standard Registers are effected since only Working Register Group 0 is implemented in ERF Bank C.

Access to the ERF is accomplished through the Register Pointer (FDH). The lower nibble of the Register Pointer determines the ERF Bank while the upper nibble determines the Working Register Group within the register file (Figure 2-6).

Table 2-3. ERF Bank Address

| Register Pointer<br>(FDH) |     |                               |  |  |

|---------------------------|-----|-------------------------------|--|--|

| Low Nibble                | Hex | Register File                 |  |  |

| 0000(B)                   | 0   | Z8® Standard Register File *  |  |  |

| 0001(B)                   | 1   | Expanded Register File Bank 1 |  |  |

| 0010(B)                   | 2   | Expanded Register File Bank 2 |  |  |

| 0011(B)                   | 3   | Expanded Register File Bank 3 |  |  |

| 0100(B)                   | 4   | Expanded Register File Bank 4 |  |  |

| 0101(B)                   | 5   | Expanded Register File Bank 5 |  |  |

| 0110(B)                   | 6   | Expanded Register File Bank 6 |  |  |

| 0111(B)                   | 7   | Expanded Register File Bank 7 |  |  |

| 1000(B)                   | 8   | Expanded Register File Bank 8 |  |  |

| 1001(B)                   | 9   | Expanded Register File Bank 9 |  |  |

| 1010(B)                   | Α   | Expanded Register File Bank A |  |  |

| 1011(B)                   | в   | Expanded Register File Bank B |  |  |

| 1100(B)                   | С   | Expanded Register File Bank C |  |  |

| 1101(B)                   | D   | Expanded Register File Bank D |  |  |

| 1110(B)                   | E   | Expanded Register File Bank E |  |  |

| 1111(B)                   | F   | Expanded Register File Bank F |  |  |

**Note:** The Z8 Standard Register File is equivalent to Expanded Register File Bank 0.

Selects ERF Bank A(H), Working Register Group 7(H)

#### Figure 2-6. Register Pointer (FDH) Example

The value of the lower nibble in the Register Pointer (FDH) corresponds to the ERF Bank identification. Table 2.3 shows the lower nibble value and the register file assigned to it.

**Z8®** MICROCONTROLLERS

The upper nibble of the register pointer selects which group of 16 bytes in the Register File, out of the full 256, will be accessed as working registers.

#### For example:

(See Figure 2-4)

| R253 RP = 00H | ;ERF Bank 0, Working Reg. Group 0.<br>R0 = Port 0 = 00H<br>R1 = Port 1 = 01H<br>R2 = Port 2 = 02H<br>R3 = Port 3 = 03H<br>R11 = GPR 0BH<br>R15 = GPR 0FH  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| lf:           |                                                                                                                                                           |  |

| R253 RP = 0FH | ;ERF Bank F, Working Reg. Group 0.<br>R0 = PCON = 00H<br>R1 = Reserved = 01H<br>R2 = Reserved = 02H<br>R11 = SMR = 0BH<br>R15 = WDTMR = 0FH               |  |

| lf:           |                                                                                                                                                           |  |

| R253 RP = FFH | $\begin{array}{l} (ERF \; Bank \; F, \; Working \; Reg. \; Group \; F. \\ 00H = PCON \\ R0 = SI0  01H = Reserved \\ R1 = TMR  02H = Reserved \end{array}$ |  |

R2 = T10BH = SMR

R15 = SPL 0FH = WDTMR

Note that since enabling an ERF Bank (C or F) only changes register addresses 00H to 0FH, the working register pointer can be used to access either the selected ERF Bank (Bank C or F, Working Register Group 0) or the Z8 Standard Register File (ERF Bank 0, Working Register Groups 1 through F).

Note: When an ERF Bank other than Bank 0 is enabled, the first 16 bytes of the Z8 Standard Register File (I/O ports 0 to 3, Groups 4 to F) are no longer accessible (the selected ERF Bank, Registers 00H to 0FH are accessed instead). It is important to reinitialize the Register Pointer to enable ERF Bank 0 when these registers are required for use.

The SPI register is mapped into ERF Bank C. Access is easily done using the following example:

| LD | RP, #0CH | ;Select ERF Bank C working<br>;register group 0 for access. |

|----|----------|-------------------------------------------------------------|

| LD | R2,#xx   | access SCON                                                 |

| LD | R1, #xx  | access RXBUF                                                |

| LD | RP, #00H | Select ERF Bank 0 so I/O ports                              |

|    |          | are again accessible.                                       |

#### Table 2-4. Z8 Expanded Register File Bank Lavout

| Expanded   |                                   |

|------------|-----------------------------------|

| Register F |                                   |

| Bank       | ERF                               |

| F(H)       | PCON, SMR, WDT;                   |

|            | (00H, 0BH, 0FH),                  |

|            | Working Register Group 0          |

|            | only implemented.                 |

| E(H)       | Not Implemented                   |

|            | (Reserved)                        |

| D(H)       | Not Implemented                   |

|            | (Reserved)                        |

| C(H)       | SPI Registers: SCOMP,             |

|            | RXBUF,                            |

|            | SCON (00H, 01H, 02H),             |

|            | Working Register Group 0          |

|            | only implemented.                 |

| B(H)       | Not Implemented                   |

|            | (Reserved)                        |

| A(H)       | Not Implemented                   |

|            | (Reserved)                        |

| 9(H)       | Not Implemented                   |

| · · /      | (Reserved)                        |

| 8(H)       | Not Implemented                   |

| · · /      | (Reserved)                        |

| 7(H)       | Not Implemented                   |

| ( )        | (Reserved)                        |

| 6(H)       | Not Implemented                   |

| ( )        | (Reserved)                        |

| 5(H)       | Not Implemented                   |

| 0(1)       | (Reserved)                        |

|            | Not Implemented                   |

| -(1)       | (Reserved)                        |

| 2/11/      | · ·                               |

| 3(H)       | Not Implemented<br>(Reserved)     |

| <b>-</b>   |                                   |

| 2(H)       | Not Implemented                   |

|            | (Reserved)                        |

| 1(H)       | Not Implemented                   |

|            | (Reserved)                        |

| 0(H)       | Z8 Ports 0, 1, 2, 3,              |

|            | and General-Purpose Registers     |

| 1          | 04H to EFH, and control registers |

|            | F0H to FFH.                       |

Please refer to the specific product specification to determine the above registers are implemented.

#### 2.4 Z8 CONTROL AND PERIPHERAL REGISTERS

#### 2.4.1 Standard Z8 Registers

The standard Z8<sup>®</sup> control registers govern the operation of the CPU. Any instruction which references the register file can access these control registers. Available control registers are:

- Interrupt Priority Register (IPR)

- Interrupt Mask Register (IMR)

- Interrupt Request Register (IRQ)

- Program Control Flags (FLAGS)

- Register Pointer (RP)

- Stack Pointer High-Byte (SPH)

- Stack Pointer Low-Byte (SPL)

The Z8 uses a 16-bit Program Counter (PC) to determine the sequence of current program instructions. The PC is not an addressable register.

Peripheral registers are used to transfer data, configure the operating mode, and control the operation of the on-chip peripherals. Any instruction that references the register file can access the peripheral registers. The peripheral registers are:

- Serial I/O (SIO)

- Timer Mode (TMR)

- Timer/Counter 0 (T0)

- T0 Prescaler (PRE0)

- Timer/Counter 1 (T1)

- T1 Prescaler (PRE1)

- Port 0-1 Mode (P01M)

- Port 2 Mode (P2M)

- Port 3 Mode (P3M)

In addition, the four port registers (P0-P3) are considered to be peripheral registers.

#### 2.4.2 Expanded Z8 Registers

The expanded Z8 control registers govern the operation of additional features or peripherals. Any instruction which references the register file can access these registers.

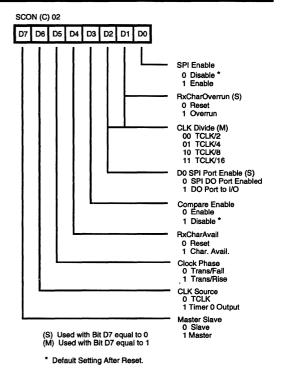

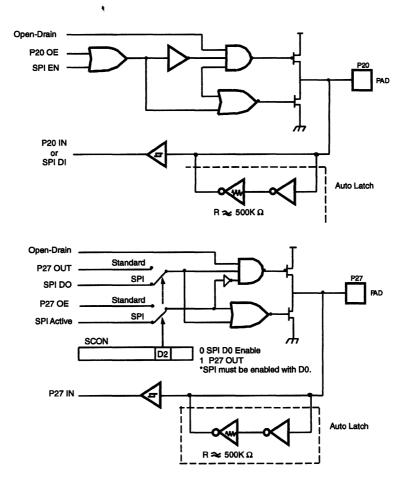

The ERF contains the control registers for WDT, Port Control, Serial Peripheral Interface (SPI), and the SMR functions. Figure 2-4 shows the layout of the Register Banks in the ERF. Register Bank C in the ERF consists of the registers for the SPI. Table 2-5 shows the registers within ERF Bank C, Working Register Group 0.

#### Table 2-5. Expanded Register File Register Bank C, WR Group 0

|          | -                      |                     |

|----------|------------------------|---------------------|

| Register | •                      | Vorking<br>Register |

| F        | Reserved               | R15                 |

| E        | Reserved               | R14                 |

| D        | Reserved               | R13                 |

| С        | Reserved               | R12                 |

| B        | Reserved               | R11                 |

| А        | Reserved               | R10                 |

| 9        | Reserved               | R9                  |

| 8        | Reserved               | R8                  |

| 7        | Reserved               | R7                  |

| 6        | Reserved               | R6                  |

| 5        | Reserved               | R5                  |

| 4        | Reserved               | R4                  |

| 3        | Reserved               | R3                  |

| 2        | SPI Control (SCON)     | R2                  |

| 1        | SPI Tx/Rx Data (RxBuf) | R1                  |

| 0        | SPI Compare (SCOMP     | ) R0                |

Working Register Group 0 in ERF Bank 0 consists of the registers for Z8 General-Purpose Registers and ports. Table 2-6 shows the registers within this group.

Working Register Group 0 in ERF Bank F consists of the control registers for STOP mode, WDT, and port control. Table 2-7 shows the registers within this group.

| Table 2-6. | Expanded Register File Bank 0, |  |

|------------|--------------------------------|--|

| WR Group 0 |                                |  |

| Register | Register<br>Function     | Working<br>Register |

|----------|--------------------------|---------------------|

| F        | General-Purpose Register | R15                 |

| Е        | General-Purpose Register | R14                 |

| D        | General-Purpose Register | R13                 |

| С        | General-Purpose Register | R12                 |

| В        | General-Purpose Register | R11                 |

| А        | General-Purpose Register | R10                 |

| 9        | General-Purpose Register | R9                  |

| 8        | General-Purpose Register | R8                  |

| 7        | General-Purpose Register | R7                  |

| 6        | General-Purpose Register | R6                  |

| 5        | General-Purpose Register | R5                  |

| 4        | General-Purpose Register | R4                  |

| 3        | Port 3                   | R3                  |

| 2        | Port 2                   | R2                  |

| 1        | Port 1                   | R1                  |

| 0        | Port 0                   | R0                  |

| Table 2-7. | Expanded Register File Bank F, | , |

|------------|--------------------------------|---|

|            | WR Group 0                     |   |

| Register | Register<br>Function | Working<br>Register |

|----------|----------------------|---------------------|

| F        | WDTMR                | R15                 |

| E        | Reserved             | R14                 |

| D        | Reserved             | R13                 |

| C        | Reserved             | R12                 |

| В        | SMR                  | R11                 |

| Α        | Reserved             | R10                 |

| 9        | Reserved             | R9                  |

| 8        | Reserved             | R8                  |

| 7        | Reserved             | R7                  |

| 6        | Reserved             | R6                  |

| 5        | Reserved             | R5                  |

| 4        | Reserved             | R4                  |

| 3        | Reserved             |                     |

| 2        | Reserved             | R2                  |

| 1        | Reserved             | R1                  |

| 0        | PCON                 | R0                  |

The functions and applications of the control and peripheral registers are described in subsequent sections of this manual.

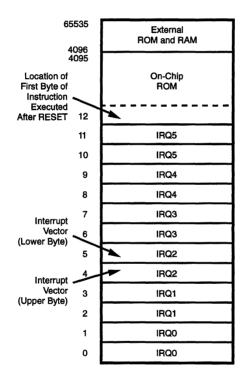

#### 2.5 PROGRAM MEMORY

The first 12 bytes of Program Memory are reserved for the interrupt vectors (Figure 2-7). These locations contain six 16-bit vectors that correspond to the six available interrupts. Address 12 up to the maximum ROM address consists of on-chip mask-programmable ROM. See the product data sheet for the exact program, data, register memory size, and address range available. At addresses outside the internal ROM, the Z8<sup>®</sup> executes external program memory fetches through Port 0 and Port 1 in Address/Data mode for devices with Port 0 and Port 1 featured. Otherwise, the program counter will continue to execute NOPs up to address FFFFH, roll over to 0000H, and continue to fetch executable code (Figure 2-7).

The internal program memory is one-time programmable (OTP) or mask programmable dependent on the specific device. A ROM protect feature prevents "dumping" of the ROM contents by inhibiting execution of the LDC, LDCI, LDE, and LDEI instructions to Program Memory in all modes. ROM look-up tables cannot be used with this feature.

The ROM Protect option is mask-programmable, to be selected by the customer when the ROM code is submitted. For the OTP ROM, the ROM Protect option is an OTP programming option.

Figure 2-7. Z8 Program Memory Map

#### 2.6 Z8 EXTERNAL MEMORY

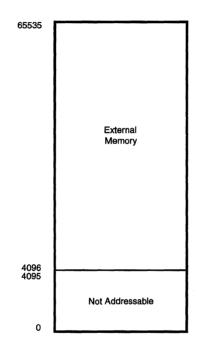

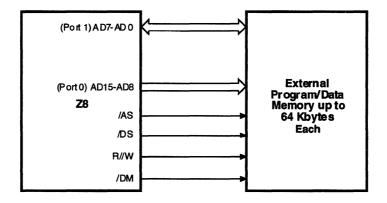

The Z8<sup>®</sup>, in some cases, has the capability to access external program memory with the 16-bit Program Counter. To access external program memory the Z8 offers multiplexed address/data lines (AD7-AD0) on Port 1 and address lines (A15-A8) on Port 0. This feature only applies to devices that offer Port 0 and Port 1. The maximum external address is FFFF. This memory interface is supported by the control lines /AS (Address Strobe), /DS (Data Strobe), and R/W (Read/Write). The origin of the external program memory starts after the last address of the internal ROM. Figure 2-8 shows an example of external program memory for the Z8.

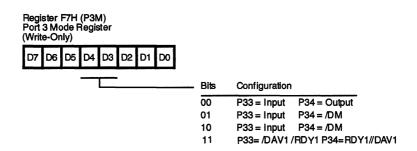

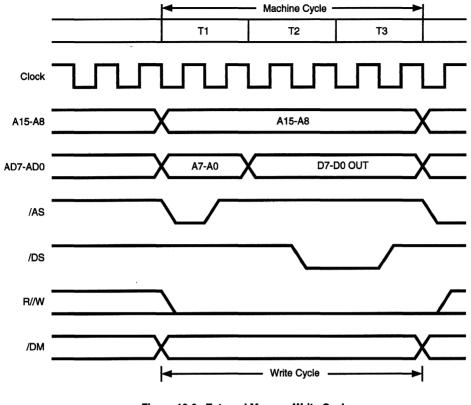

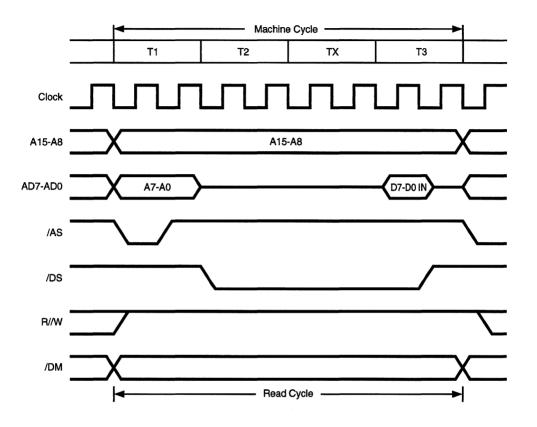

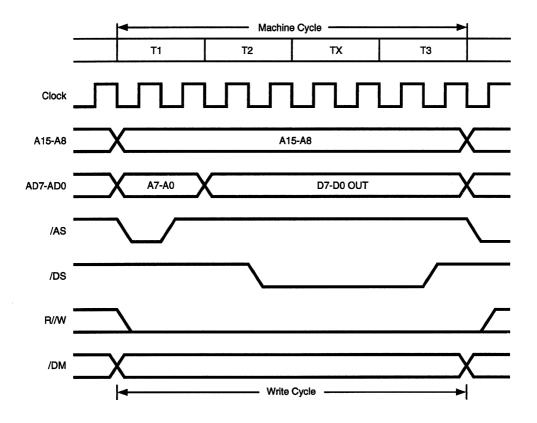

#### 2.6.1 External Data Memory (/DM)

The Z8, in some cases, can address up to 60 Kbytes of external data memory beginning at location 4096. External Data Memory may be included with, or separated from, the external Program Memory space. /DM, an optional I/O function that can be programmed to appear on pin P34, is used to distinguish between data and program memory space. The state of the /DM signal is controlled by the type of instruction being executed. An LDC opcode references Program (/DM inactive) Memory, and an LDE instruction references Data (/DM active Low) Memory. The user must configure Port 3 Mode Register (P3M) bits D3 and D4 for this mode.

Figure 2-8. External Memory Map

Note: For additional information on using external memory, see Chapter 10 of this manual. For exact memory addressing options available, see the device product specification.

# 2.7 Z8 STACKS

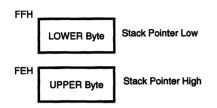

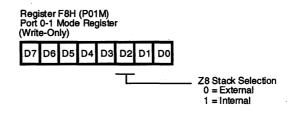

Stack operations can occur in either the Z8<sup>®</sup> Standard Register File or external data memory. Under software control, Port 0-1 Mode register (F8H) selects the stack location. Only the General-Purpose Registers can be used for the stack when the internal stack is selected.

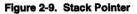

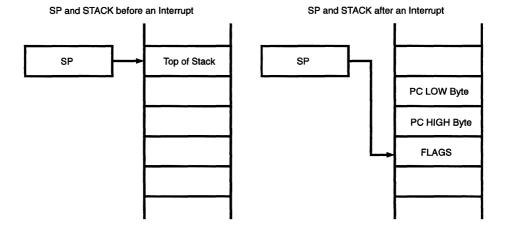

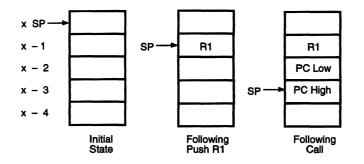

The register pair FEH and FFH form the 16-bit Stack Pointer (SP), that is used for all stack operations. The stack address is stored with the MSB in FEH and LSB in FFH (Figure 2-9).

The stack address is decremented prior to a PUSH operation and incremented after a POP operation. The stack address always points to the data stored on the top of the stack. The Z8<sup>®</sup> stack is a return stack for CALL instructions and interrupts, as well as a data stack.

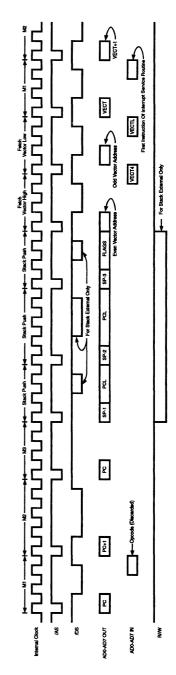

During a CALL instruction, the contents of the PC are saved on the stack. The PC is restored during a RETURN instruction. Interrupts cause the contents of the PC and Flag registers to be saved on the stack. The IRET instruction restores them (Figure 2-10).

When the Z8 is configured for an internal stack (using the Z8 Standard Register File), register FFH serves as the Stack Pointer. The value in FEH is ignored. FEH can be used as a general-purpose register in this case only.

An overflow or underflow can occur when the stack address is incremented or decremented during normal stack operations. The programmer must prevent this occurrence or unpredictable operation will result.

Figure 2-10. Stack Operations

<sup>⊗</sup>ZiLŒ

USER'S MANUAL

# CHAPTER 3 CLOCK

#### 3.1 CLOCK

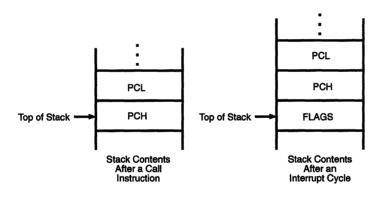

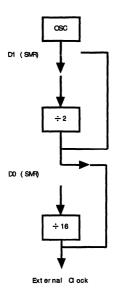

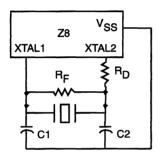

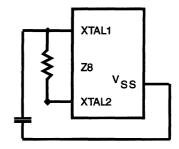

The Z8® derives its timing from on-board clock circuitry connected to pins XTAL1 and XTAL2. The clock circuitry consists of an oscillator, a divide-by-two shaping circuit, and a clock buffer. Figure 3-1 illustrates the clock circuitry. The oscillator's input is XTAL1 and its output is XTAL2. The clock can be driven by a crystal, a ceramic resonator, LC clock, RC, or an external clock source.

#### 3.1.1 Frequency Control

In some cases, the Z8 has an EPROM/OTP option or a Mask ROM option bit to bypass the divide-by-two flip flop in Figure 3-1. This feature is used in conjunction with the low EMI option. When low EMI is selected, the device output drive and oscillator drive is reduced to approximately 25 percent of the standard drive and the divide-bytwo flip flop is bypassed such that the XTAL clock freauency is equal to the internal system clock frequency. In this mode, the maximum frequency of the XTAL clock is 4 MHz. Please refer to specific product specification for availability of options and output drive characteristics.

Figure 3-1. Z8 Clock Circuit

#### **3.2 CLOCK CONTROL**

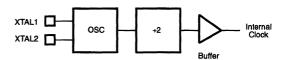

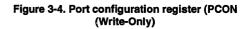

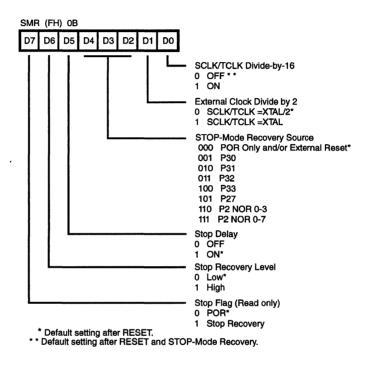

In some cases, the Z8 offers software control of the internal system clock via programming register bits. The bits are located in the Stop-Mode Recovery Register in Expanded Register File Bank F, Register 0BH. This register selects

the clock divide value and determines the mode of Stop-Mode Recovery (Figure 3-2). Please refer to the specific product specification for availability of this feature/register.

Figure 3-2. Stop-Mode Recovery Register (Write-Only Except D7, Which is Read-Only)

### 3.2.1 SCLK/TCLK Divide-By-16 Select (D0)

This bit of the SMR controls a divide-by-16 prescalar of SCLK/TCLK. The purpose of this control is to selectively reduce device power consumption during normal processor execution (SCLK control) and/or HALT mode (where TCLK sources counter/timers and interrupt logic).

## 3.2.2 External Clock Divide-By-Two (D1)

This bit can eliminate the oscillator divide-by-two circuitry. When this bit is 0, SCLK (System Clock) and TCLK (Timer Clock) are equal to the external clock frequency divided by two. The SCLK/TCLK is equal to the external clock frequency when this bit is set (D1 = 1). Using this bit, together with D7 of PCON, further helps lower EMI (D7 (PCON) = 0, D1 (SMR) = 1). The default setting is 0. Maximum frequencyis4MHzwithD1=1 (Figure3-3).

#### 3.3 Oscillator Control

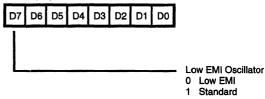

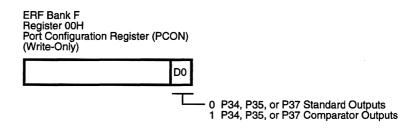

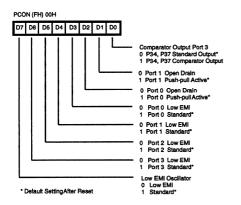

In some cases, the Z8<sup>®</sup> offers software control of the oscillator to select low EMI drive or standard drive. The selection is done by programming bit D7 of the Port Configuration (PCON) register (Figure 3-4). The PCON register is located in Expanded Register File Bank F, Register 00H.

A 1 in bit D7 configures the oscillator with standard drive, while a 0 configures the oscillator with Low EMI drive. This only affects the drive capability of the oscillator and does not affect the relationship of the XTAL clock frequency to the internal system clock (SCLK).

PCON (FH) 00H

Figure 3-3. External Clock Circuit

## 3.4 OSCILLATOR OPERATION

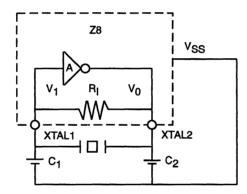

The Z8<sup>®</sup> uses a Pierce oscillator with an internal feedback (Figure 3-5). The advantages of this circuit are low cost, large output signal, low-power level in the crystal, stability with respect to  $V_{cc}$  and temperature, and low impedances (not disturbed by stray effects).

One draw back is the need for high gain in the amplifier to compensate for feedback path losses. The oscillator amplifies its own noise at start-up until it settles at the frequency that satisfies the gain/phase requirements A x B = 1, where A =  $V_0 V_i$  is the gain of the amplifier and B =  $V_i V_0$  is the gain of the feedback element. The total phase shift around the loop is forced to zero (360 degrees). Since  $V_{\rm IN}$  must be in phase with itself, the amplifier/inverter provides 180 degree phase shift and the feedback element is forced to provide the other 180 degrees of phase shift.

$\rm R_1$  is a resistive component placed from output to input of the amplifier. The purpose of this feedback is to bias the amplifier in its linear region and to provide the start-up transition.

Capacitor  $C_2$  combined with the amplifier output resistance provides a small phase shift. It will also provide some attenuation of overtones.

Capacitor  $C_1$  combined with the crystal resistance provides additional phase shift.

$C_1$  and  $C_2$  can affect the start-up time if they increase dramatically in size. As  $C_1$  and  $C_2$  increase, the start-up time increases until the oscillator reaches a point where it does not start up any more.

It is recommended for fast and reliable oscillator start-up (over the manufacturing process range) that the load capacitors be sized as low as possible without resulting in overtone operation.

Figure 3-5. Pierce Oscillator with Internal Feedback Circuit

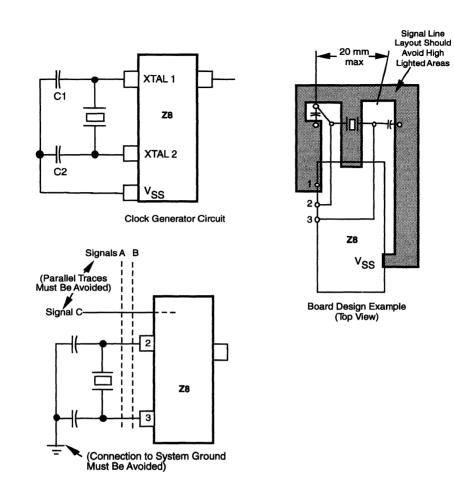

## 3.4.1 Layout

Traces connecting crystal, caps, and the Z8<sup>®</sup> oscillator pins should be as short and wide as possible. This reduces parasitic inductance and resistance. The components (caps, crystal, resistors) should be placed as close as possible to the oscillator pins of the Z8.

The traces from the oscillator pins of the IC and the ground side of the lead caps should be guarded from all other traces (clock,  $V_{cc}$ , address/data lines, system ground) to reduce cross talk and noise injection. This is usually accomplished by keeping other traces and system ground trace planes away from the oscillator circuit and by placing a Z8 device  $V_{ss}$  ground ring around the traces/components. The ground side of the oscillator lead caps should be connected to a single trace to the Z8  $V_{ss}$  (GND) pin. It should not be shared with any other system ground trace or components except at the Z8 device  $V_{ss}$  pin. This is to prevent differential system ground noise injection into the oscillator (Figure 3-6).

#### 3.4.2 Indications of an Unreliable Design

There are two major indicators that are used in working designs to determine their reliability over full lot and temperature variations. They are:

Start-up Time. If start -up time is excessive, or varies widely from unit to unit, there is probably a gain problem.  $C_1/C_2$  needs to be reduced; the amplifier gain is not adequate at frequency, or crystal Rs is too large.

Output Level. The signal at the amplifier output should swing from ground to  $V_{cc}$ . This indicates there is adequate gain in the amplifier. As the oscillator starts up, the signal amplitude grows until clipping occurs, at which point the loop gain is effectively reduced to unity and constant oscillation is achieved. A signal of less than 2.5 volts peakto-peak is an indication that low gain may be a problem. Either  $C_1$  or  $C_2$  should be made smaller or a low-resistance crystal should be used.

#### 3.4.3 Circuit Board Design Rules

The following circuit board design rules are suggested:

- To prevent induced noise the crystal and load capacitors should be physically located as close to the Z8<sup>®</sup> as possible.

- Signal lines should not run parallel to the clock oscillator inputs. In particular, the crystal input circuitry and the internal system clock output should be separated as much as possible.

- V<sub>oc</sub> power lines should be separated from the clock oscillator input circuitry.

- Resistivity between XTAL1 or XTAL2 and the other pins should be greater than 10 Mohms.

Figure 3-6. Circuit Board Design Rules

### 3.4.4 Crystals and Resonators

Crystals and ceramic resonators (Figure 3-7) should have the following characteristics to ensure proper oscillator operation:

| Crystal Cut        | AT (crystal only)          |

|--------------------|----------------------------|

| Mode               | Parallel, Fundamental Mode |

| CrystalCapacitance | <7pF                       |

| Load Capacitance   | 10pF < CL < 220 pF,        |

|                    | 15 typical                 |

| Resistance         | 100 ohms max               |

Depending on operation frequency, the oscillator may require the addition of capacitors  $C_1$  and  $C_2$  (shown in Figures 3-7). The capacitance values are dependent on the manufacturer's crystal specifications.

Figure 3-7. Crystal/Ceramic Resonator Oscillator

Figure 3-8. LC Clock

In most cases, the  $R_p$  is 0 Ohms and  $R_p$  is infinite. It is determined and specified by the crystal/ceramic resonator manufacturer. The  $R_p$  can be increased to decrease the amount of drive from the oscillator output to the crystal. It can also be used as an adjustment to avoid clipping of the oscillator signal to reduce noise. The  $R_p$  can be used to improve the start-up of the crystal/ceramic resonator. The Z8 oscillator already has an internal shunt resistor in parallel to the crystal/ceramic resonator.

Figure 3-9. External Clock

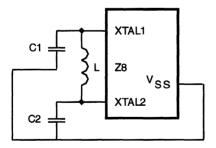

It is recommended in Figures 3-7, 3-8, and 3-9 to connect the load capacitor ground trace directly to the V<sub>ss</sub> (GND) pin of the Z8<sup>®</sup>. This ensures that no system noise is injected into the Z8 clock. This trace should not be shared with any other components except at the V<sub>ss</sub> pin of the Z8.

In some cases, the Z8 XTAL1 pin also functions as one of the EPROM high-voltage mode programming pins or as a special factory test pin. In this case, applying 2 V above  $V_{cc}$  on the XTAL1 pin will cause the device to enter one of these modes. Since this pin accepts high voltages to enter these respective modes, the standard input protection diode to  $V_{cc}$  is not on XTAL1. It is recommended that in applications where the Z8 is exposed to much system noise, a diode from XTAL1 to  $V_{cc}$  be used to prevent accidental enabling of these modes. This diode will not affect the crystal/ceramic resonator operation .

Please note that a parallel resonant crystal or resonator data sheet will specify a load capacitor value that is the series combination of  $C_1$  and  $C_2$ , including all parasitics (PCB and holder).

#### 3.5 LC OSCILLATOR.

ş

The Z8 oscillator can use a LC network to generate a XTAL clock (Figure 3-8).

The frequency stays stable over  $V_{cc}$  and temperature. The oscillation frequency is determined by the equation:

Frequency =

$$2\pi(LCT)1/2$$

where L is the total inductance including parasitics and  $C_{\tau}$  is the total series capacitance including the parasitics.

Simple series capacitance is calculated using the following equation:

$$\frac{1}{C_{T}} = \frac{1}{C_{1}} + \frac{1}{C_{2}}$$

$$fC_{1} = C_{2}$$

$$\frac{1}{C_{T}} = \frac{2}{C_{1}}$$

$$C_{2} = 2CT$$

Sample calculation of capacitance  $C_1$  and  $C_2$  for 5.83 MHz frequency and inductance value of 27 uH:

5.83 (10^6) =

$$\frac{1}{2\pi [2.7 (10^6) C_T] 1/2}$$

CT = 27.6 pf

Thus  $C_1 = 55.2 \text{ pf and } C_2 = 55.2 \text{ pf}.$

#### 3.6 RC OSCILLATOR

In some cases, the Z8<sup>®</sup> has a RC oscillator option. Please refer to the specific product specification for availability. The RC oscillator requires a resistor across XTAL1 and XTAL2. An additional load capacitor is required from the XTAL1 input to V<sub>ss</sub> pin (Figure 3-9).

Figure 3-9. RC Clock

**ASILOS**

USFR'S MANUAL

# CHAPTER 4 **RESET—WATCH-DOG TIMER**

# 4.1 RESET

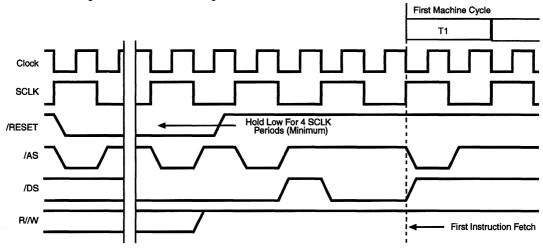

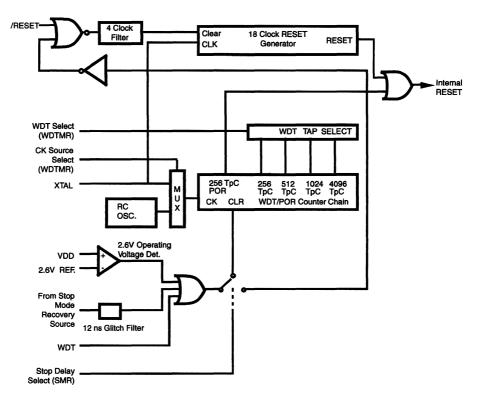

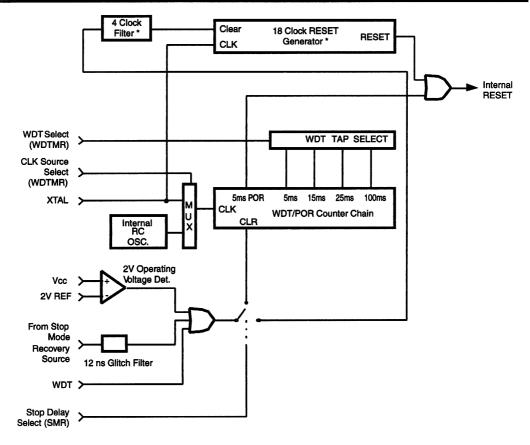

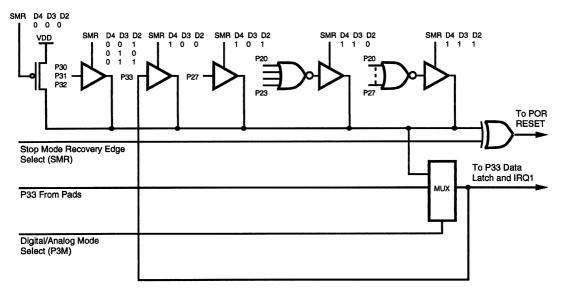

This section describes the Z8® reset conditions, reset timing, and register initialization procedures. Reset is generated by Power-On Reset (POR), Reset Pin, Watch-Dog Timer (WDT), and Stop-Mode Recovery.

A system reset overrides all other operating conditions and puts the Z8 into a known state. To initialize the chip's internal logic, the /RESET input must be held Low for at least 4 internal system clock periods. The control register and ports are reset to their default conditions after a POR, a reset from the /Reset pin, or Watch-Dog Timer timeout while in RUN mode and HALT mode. The control registers

and ports are not reset to their default conditions after Stop- Mode Recovery and WDT timeout while in STOP mode.

While /RESET is Low, /AS is output at the internal clock rate, /DS is forced Low, and R//W remains High. The program counter is loaded with 000CH. I/O ports and control registers are configured to their default reset state.

Resetting the Z8 does not effect the contents of the general-purpose registers.

#### 4.2 /Reset Pin, Internal POR Operation

In some cases, the Z8 hardware /RESET pin initializes the control and peripheral registers, as shown in Tables 4-1, 4-2, 4-3, and 4-4. Specific reset values are shown by 1 or 0, while bits whose states are unknown are indicated by the letter U. The Tables 4-1, 4-2, 4-3, and 4-4 show the reset conditions for the generic Z8.

Note: The register file reset state is device dependent. Please refer to the selected device product specifications for register availability and reset state.

| Register | Register             |   |   |   | Bit | 5 |   |   |                |   |                                                  |

|----------|----------------------|---|---|---|-----|---|---|---|----------------|---|--------------------------------------------------|

| (HEX)    | Name                 | 7 | 6 | 5 | 4   | 3 | 2 | • | 1 (            | 0 | Comments                                         |

| FO       | Serial I/O           | U | U | U | U   | U | U | ι | υı             | U |                                                  |

| F1       | Timer Mode           | 0 | 0 | 0 | 0   | 0 | 0 | ( | 0 (            | 0 | Counter/Timers Stopped                           |

| F2       | Counter/Timer1       | U | U | U | U   | U | U | l | U I            | U |                                                  |

| F3       | T1 Prescaler         | U | U | U | U   | U | U | ( | 0 (            | 0 | Single-Pass Count Mode, External Clock Source    |

| F4       | Counter/Timer0       | U | U | U | U   | U | U | ι | JI             | U |                                                  |

| F5       | TO Prescaler         | U | U | U | U   | U | U | ι | J              | 0 | Single-Pass Count Mode                           |

| F6       | Port 2 Mode          | 1 | 1 | 1 | 1   | 1 | 1 | • | 1              | 1 | All Inputs                                       |

| F7       | Port 3 Mode          | 0 | 0 | 0 | 0   | 0 | 0 | ( | 0 (            | 0 | Port 2 Open-Drain, P33-P30 Input, P37-P34 Output |

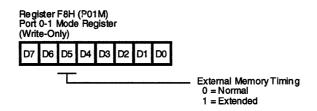

| F8       | Port 0-1 Mode        | 0 | 1 | 0 | 0   | 1 | 1 | ( | о <sup>-</sup> | 1 | Internal Stack, Normal Memory Timing             |

| F9       | Interrupt Priority   | U | U | U | U   | U | U | ι | JI             | U |                                                  |

| FA       | Interrupt Request    | 0 | 0 | 0 | 0   | 0 | 0 | ( | ) (            | 0 | All Interrupts Cleared                           |

| FB       | Interrupt Mask       | 0 | U | U | U   | U | U | ι | JI             | U | Interrupts Disabled                              |

| FC       | Flags                | U | U | U | U   | U | U | ι | JI             | J |                                                  |

| FD       | Register Pointer     | 0 | 0 | 0 | 0   | 0 | 0 | ( | 0 0            | 0 |                                                  |

| FE       | Stack Pointer (High) | U | U | U | U   | U | U | ι | JI             | J |                                                  |

| FF       | Stack Pointer (Low)  | U | U | U | U   | U | U | ι | J              | U |                                                  |

Table 4-1. Sample Control and Peripheral Register Reset Values (ERF Bank 0)

Program execution starts 5 to 10 clock cycles after /RESET has returned High. The initial instruction fetch is from location 000CH. Figure 4-1 shows reset timing.

After a reset, the first routine executed should be one that initializes the control registers to the required system configuration.

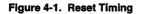

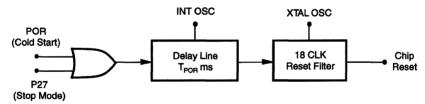

The /RESET pin is the input of a Schmitt-triggered circuit. Resetting the Z8® will initialize port and control registers to their default states. To form the internal reset line, the output of the trigger is synchronized with the internal clock. The clock must therefore be running for /RESET to function. It requires 4 internal system clocks after reset is detected for the Z8 to reset the internal circuitry. An internal pull-up, combined with an external capacitor of 1 uf, provides enough time to properly reset the Z8 (Figure 4-2). In some cases, the Z8 has an internal POR timer circuit that holds the Z8 in reset mode for a duration (T<sub>POR</sub>) before releasing the device out of reset. On these Z8 devices, the internally generated reset drives the reset pin low for the POR time. Any devices driving the reset line must be open-drained in order to avoid damage from possible conflict during reset conditions. This reset time allows the on-board clock oscillator to stabilize.

To avoid asynchronous and noisy reset problems, the Z8 is equipped with a reset filter of four external clocks (4TpC). If the external reset signal is less than 4TpC in duration, no reset occurs. On the fifth clock after the reset is detected, an internal RST signal is latched and held for an internal

#### Figure 4-2. Example of External Power-On Reset Circuit

register count of 18 external clocks, or for the duration of the external reset, whichever is longer. During the reset cycle, /DS is held active low while /AS cycles at a rate of the internal system clock. Program execution begins at location 000CH, 5-10 TpC cycles after /RESET is released. For the internal Power-On Reset, the reset output time is specified as  $T_{POR}$ . Please refer to specific product specifications for actual values.

| Register | Register                                  |   |   | 1 | Bits | 5 |   |   |   |                                     |

|----------|-------------------------------------------|---|---|---|------|---|---|---|---|-------------------------------------|

| (HEX)    | Name                                      | 7 | 6 | 5 | 4    | 3 | 2 | 1 | 0 | Comments                            |

| 00       | Port 0                                    | U | U | U | U    | U | U | U | U | Input mode, output set to push-pull |

| 01       | Port 1                                    | U | U | U | U    | U | U | U | U | Input mode, output set to push-pull |

| 02       | Port 2                                    | U | U | U | U    | υ | U | U | U | Input mode, output set to push-pull |

| 03       | Port 3                                    | 1 | 1 | 1 | 1    | U | U | U | U | Standard Digital input and output   |

| 04-EF    | General-<br>Purpose<br>Registers<br>04-EF | U | U | U | U    | U | U | U | Ū | Standard Digital input and output   |

#### Table 4-2. Sample Expanded Register File Bank 0 Reset Values

| Register | Register                  |   |   | 1 | Bit | 5 |   |   |     |            |

|----------|---------------------------|---|---|---|-----|---|---|---|-----|------------|

| (HEX)    | Name                      | 7 | 6 | 5 | 4   | 3 | 2 | 1 | C   | 0 Comments |

| 00       | SPI Compare<br>(SCOMP)    | 0 | 0 | 0 | 0   | 0 | 0 | 0 | ) ( | 0          |

| 01       | Receive Buffer<br>(RxBUF) | U | U | U | U   | U | U | U | π   | U          |

| 02       | SPI Control<br>(SCON)     | U | U | U | U   | 0 | 0 | 0 | ) ( | 0          |

| Table 4-3. S | ample Expan | nded Register | <sup>·</sup> File Bank | C Reset Values |

|--------------|-------------|---------------|------------------------|----------------|

|--------------|-------------|---------------|------------------------|----------------|

| Register | ister Register Bits                |   |   |   |   |   |   |   |   |   |                                                                                                                                            |

|----------|------------------------------------|---|---|---|---|---|---|---|---|---|--------------------------------------------------------------------------------------------------------------------------------------------|

| (HEX)    | Name                               | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | I | Comments                                                                                                                                   |

| 00       | Port Configuration<br>(PCON)       | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |   | Comparator outputs disabled on Port 3<br>Port 0 and 1 output is push-pull<br>Port 0, 1, 2, 3, and oscillator with standard output<br>drive |

| OB       | STOP-Mode Recovery<br>(SMR)        | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |   | Clock divide by 16 off<br>XTAL divide by 2<br>POR and / OR External Reset<br>Stop delay on<br>Stop recovery level is low, STOP flag is POR |

| OF       | Watch-Dog Timer<br>Mode<br>(WDTMR) | U | U | υ | 0 | 1 | 1 | 0 | 1 |   | 512 $T_pC$ for WDT time out, WDT runs during STOP and HALT mode, on-board RC drives WDT                                                    |

Table 4-4 Sample Expanded Register File Bank F Reset Values

Figure 4-3. Example of Z8 Reset with /RESET Pin, WDT, SMR, and POR

Figure 4-4. Example of Z8 Reset with WDT, SMR, and POR

# 4.3 Watch-Dog Timer (WDT)

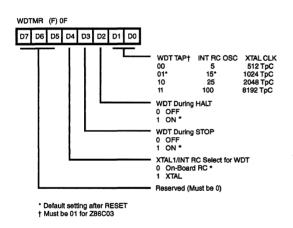

The WDT is a retriggerable one-shot timer that resets the Z8<sup>®</sup> if it reaches its terminal count. When operating in the RUN or HALT modes, a WDT reset is functionally equivalent to a hardware /POR reset. The WDT is initially enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT carinot be disabled after it has been initially enabled. Permanently enabled WDTs are always enabled and the WDT instruction is used to refresh it. The WDT circuit is driven by an onboard RC oscillator or external oscillator from the XTAL1 pin. The POR clock source is selected with bit 4 of the Watch-Dog Timer Mode register (WDTMR). In some cases, a Z8 that offers the WDT but does not have a WDTMR register, has a fixed WDT timeout and uses the on board RC oscillator as the only clock source. Please refer to specific product specifications for selectability of timeout, WDT during HALT and STOP modes, source of WDT clock, and availability of the permanently-on WDT option.

**Note:** Execution of the WDT instruction affects the Z (zero), S (sign), and V (overflow) flags.

#### Figure 4-5. Example of Z8 Watch-Dog Timer Mode Register (Write-Only)

**Note:** The WDTMR register is accessible only during the first 64 processor cycles from the execution of the first instruction after Power-On Reset, Watch-Dog Reset or a Stop-Mode Recovery. After this point, the register cannot be modified by any means, intentional or otherwise. The WDTMR is a write-only register.

The WDTMR is located in Expanded Register File Bank F, register 0FH. The control bits are described as follows:

**WDT Time Select (D1, D0).** Bits 0 and 1 control a tap circuit that determines the time-out period. Table 4-5 shows the different values that can be obtained. The default value of D1 and D0 are 0 and 1, respectively.

| Table 4-5. Time-Out Period of the WD1 | Table 4-5. | Time-Out | Period | of the | WDT |

|---------------------------------------|------------|----------|--------|--------|-----|

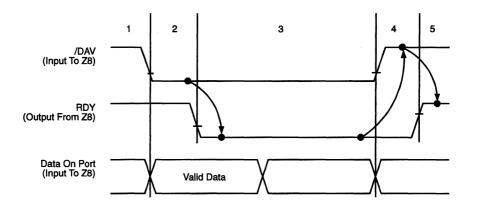

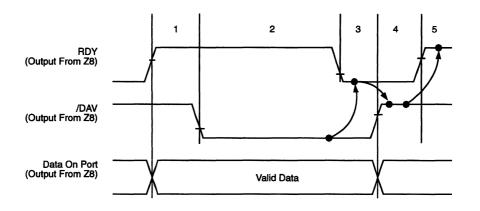

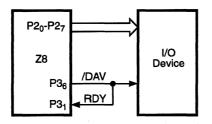

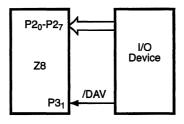

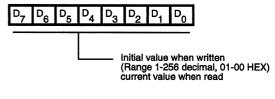

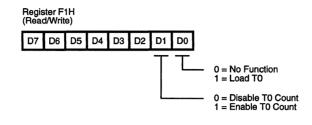

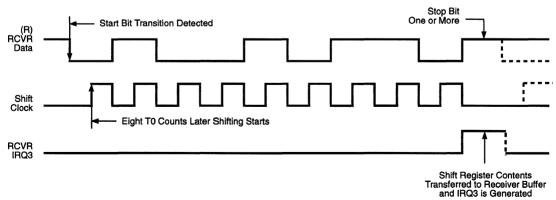

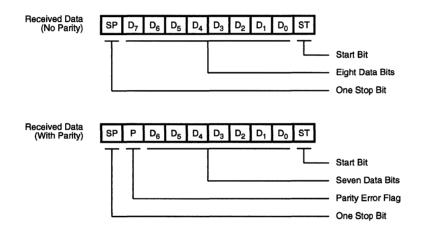

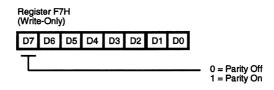

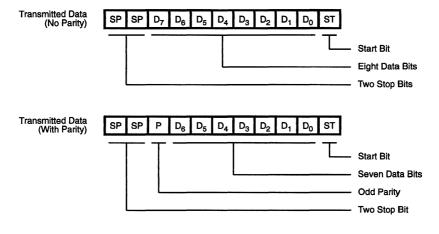

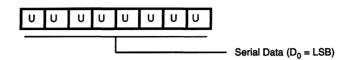

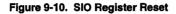

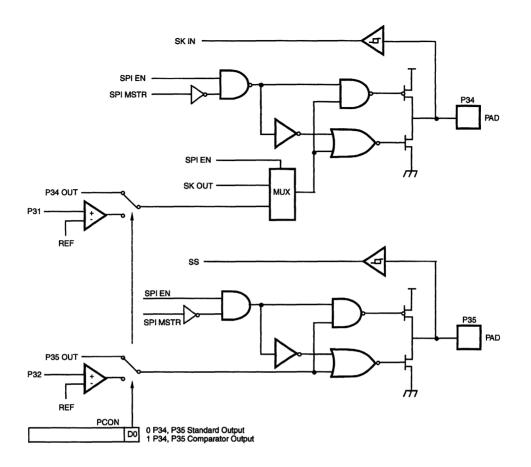

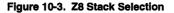

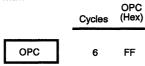

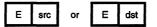

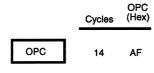

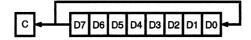

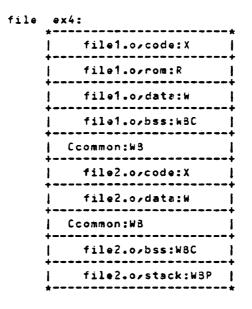

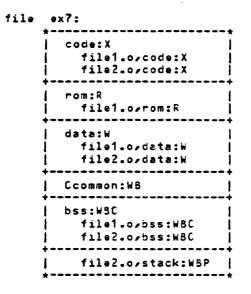

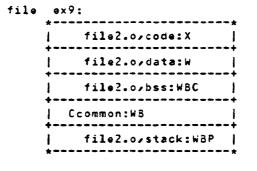

|---------------------------------------|------------|----------|--------|--------|-----|