# MICROPROCESSOR APPLICATIONS REFERENCE BOOK

# **VOLUME** 2

Copyright 1983 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog. The information contained herein is subject to change

The information contained herein is subject to change without notice. Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

# Introduction

Zilog's name has become synonymous with logic innovation and advanced microprocessor architecture since the introduction of the Z80® CPU in 1975. The Zilog Family of microprocessors and microcomputers has grown to include the products listed in the table below. Each product exhibits special features that make it stand above similar products in the semiconductor marketplace. These special features have proven to be of substantial aid in the solution of microprocessor design problems.

This reference book contains a collection of application information and Zilog microprocessor products. It includes technical articles, application notes, concept papers, and benchmarks. This book is the second of an expected series of such volumes. We at Zilog believe that designing innovative microprocessor integrated circuit products is only half the key that unlocks the future of microprocessor-based end products: the other half is the creative application of those Advanced microprocessor products and products. their creative applications lead to end product designs with more features. more simply implemented, and at a lower system cost. It is hoped that this reference book will stimulate new product design ideas as well as fresh approaches to the design of traditional microprocessor-based products.

The material in this book is believed to be accurate and up-to-date. If you do find errors, or would like to offer suggestions for future application notes, we would appreciate hearing from you. Correction inputs should be directed to Components Division Technical Publications, and application suggestions should be directed to Components Division Application Engineering.

| Z8 FAMILY               | 8-Bit Single-Chip Micro-<br>computer, 2K/4K Bytes<br>ROM and 144 Bytes RAM |

|-------------------------|----------------------------------------------------------------------------|

| Z8601/Z8603/Z86L01 MCU  | Microcomputer Unit                                                         |

| Z8611/2/3 MCU           | Microcomputer Unit                                                         |

| Z8671 MCU               | Microcomputer Unit with<br>BASIC Debug                                     |

| Z8681/2                 | ROM1ess                                                                    |

| Z8090/4 & Z8590/4 Z-UPC | Universal Peripheral                                                       |

|                         | Controller                                                                 |

| Z80 FAMILY              | 8-Bit General-Purpose<br>Microprocessor                                    |

| Z8400 CPU               | Central Processing Unit                                                    |

| Z8410 DMA               | Direct Memory Access                                                       |

| Z8420 PIO               | Parallel I/O Controller                                                    |

| Z8430 CTC               | Counter/Timer Circuit                                                      |

| Z8440/1/2 SIO           | Serial I/O Controller                                                      |

| Z8470 DART              | Dual Asynchronous<br>Receiver/Transmitter                                  |

|                         | Low-Power 8-Bit General-                                                   |

| Z80L FAMILY             | Purpose Microprocessor                                                     |

| Z8300 CPU               | Central Processing Unit                                                    |

| Z8320 PIO               | Parallel Input/Output                                                      |

| Z8330 CTC               | Counter/Timer Circuit                                                      |

| Z8340 SIO               | Serial Input/Output                                                        |

| Z8000 FAMILY                  | 16-Bit General-Purpose<br>Microprocessor             | Z8500 FAMILY   | Universal Peripherals<br>(Continued)   |  |  |

|-------------------------------|------------------------------------------------------|----------------|----------------------------------------|--|--|

| Z8001/2 CPU<br>Z8003/4 Z-VMPU | Central Processing Unit<br>Virtual Memory Processing | Z8536 CIO      | Counter/Timer and<br>Parallel I/O Unit |  |  |

|                               | Unit                                                 | Z8581 CGC      | Clock Generator and                    |  |  |

| Z8010 Z-MMU                   | Memory Management Unit                               |                | Controller                             |  |  |

| Z8015 Z-PMMU                  | Paged Memory Management<br>Unit                      |                |                                        |  |  |

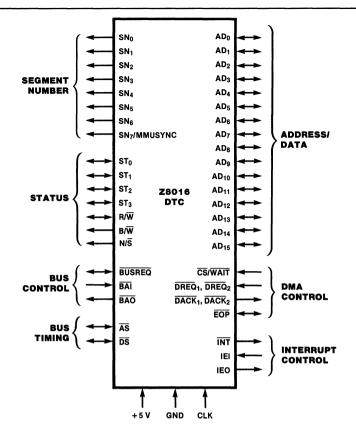

| Z8016 Z-DTC                   | Direct Memory Access                                 |                |                                        |  |  |

|                               | Transfer Controller                                  |                | 8/16-Bit General-Purpose               |  |  |

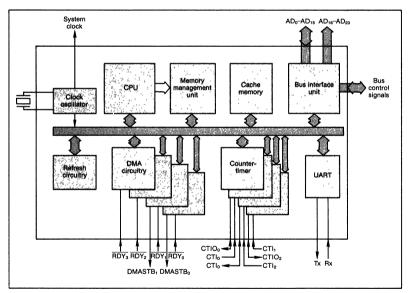

| Z8030 Z-SCC                   | Serial Communications<br>Controller                  | Z800 FAMILY    | Microprocessors                        |  |  |

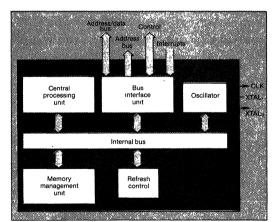

| Z8031 Z-ASCC                  | Asynchronous Serial                                  | Z8108 MPU      | Microprocessing Unit                   |  |  |

|                               | Communications                                       | Z8208 MPU      | Microprocessing Unit                   |  |  |

|                               | Controller                                           | Z8116 MPU      | Microprocessing Unit                   |  |  |

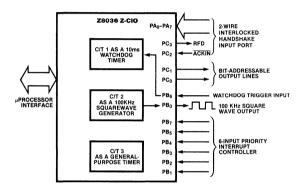

| Z8036 Z-CIO                   | Counter/Timer and<br>Parallel I/O Unit               | Z8216 MPU      | Microprocessing Unit                   |  |  |

| Z8038 Z-FIO                   | FIFO I/O Interface Unit                              |                |                                        |  |  |

| Z8060 Z-FIF0                  | Z-FIFO Buffer Unit and<br>FIO Expander               |                | 32-Bit General-Purpose                 |  |  |

| Z8065 Z-BEP                   | Burst Error Processor                                |                | Microprocessor and 80-Bit              |  |  |

| Z8068 Z-DCP                   | Data Ciphering Processor                             | Z80,000 FAMILY | Arithmetic Processor                   |  |  |

|                               |                                                      | Z8070 APU      | Arithmetic Processing<br>Unit          |  |  |

| Z8500 FAMILY                  | Universal Peripherals                                | Z80,000 CPU    | Central Processing Unit                |  |  |

| Z8530 SCC                     | Serial Communications<br>Controller                  |                |                                        |  |  |

| Z8531 ASCC                    | Asynchronous Serial<br>Communications                |                |                                        |  |  |

Controller

# **Table of Contents**

| Z8 Family                                                             | 1 |

|-----------------------------------------------------------------------|---|

| Z8 Subroutine Library                                                 |   |

| Z8 MCU Test Mode                                                      |   |

| Build a Z8-Based Control Computer with BASIC                          |   |

| Z8671 Seven-Chip Computer                                             |   |

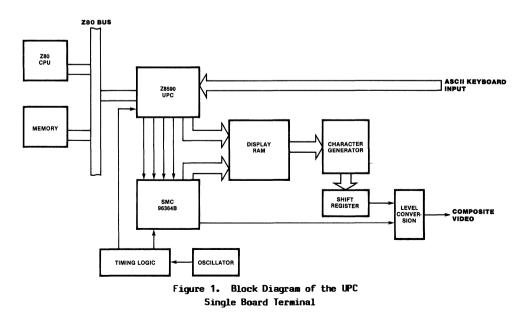

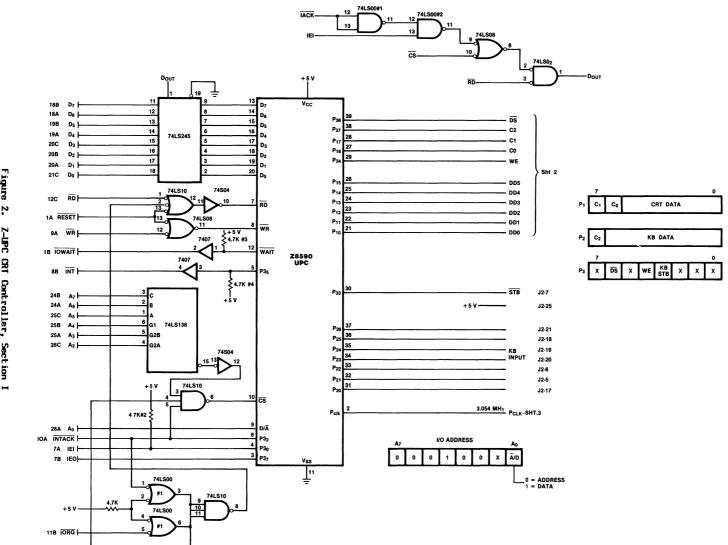

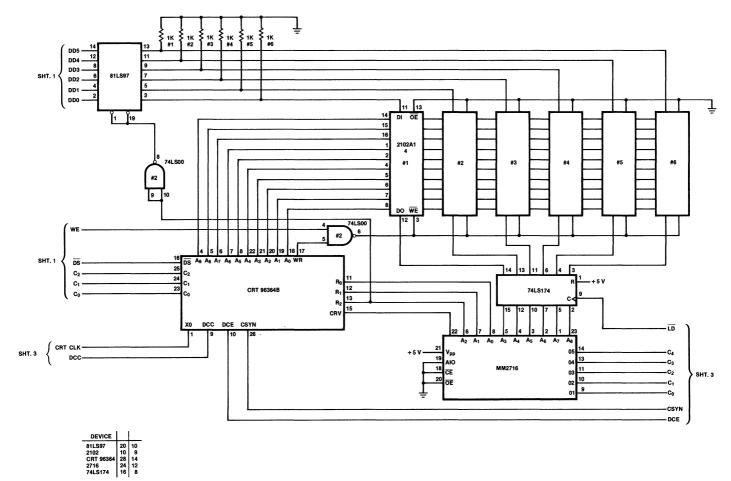

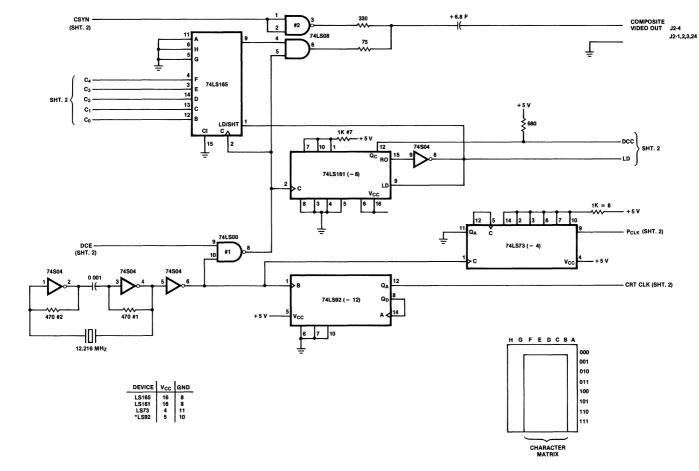

| A Single-Board Terminal Using the Z8590 Universal                     |   |

| Peripheral Controller                                                 |   |

|                                                                       |   |

| Z80 Family                                                            | 2 |

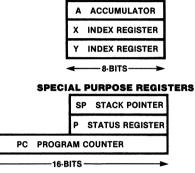

| Z80 CPU vs. 6502 CPU Benchmark Report                                 |   |

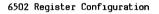

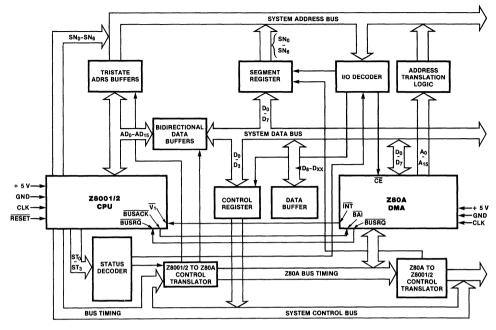

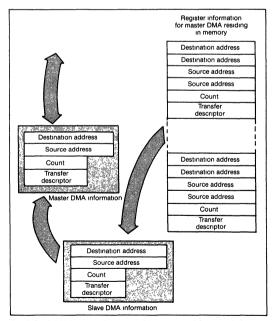

| Integrating 8-Bit DMA to 16-Bit System Tutorial                       |   |

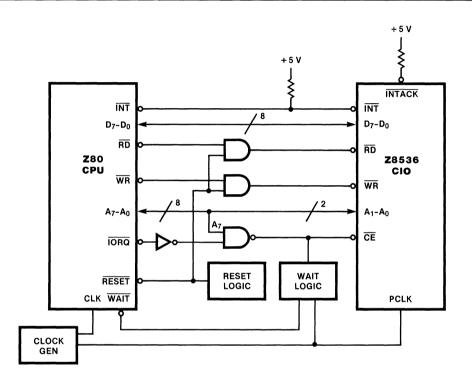

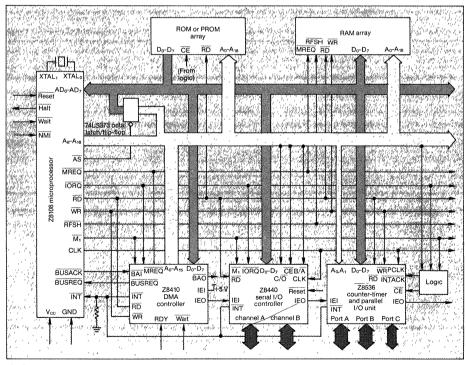

| Interfacing Z80 CPUs to the Z8500 Peripheral Family                   |   |

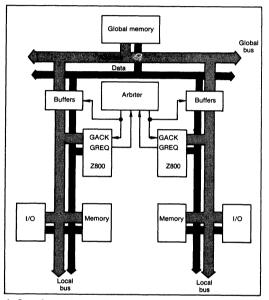

| Z800 Family                                                           | 3 |

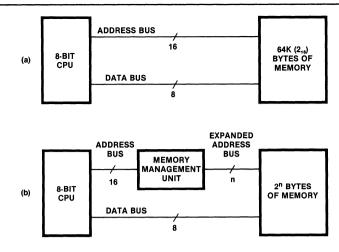

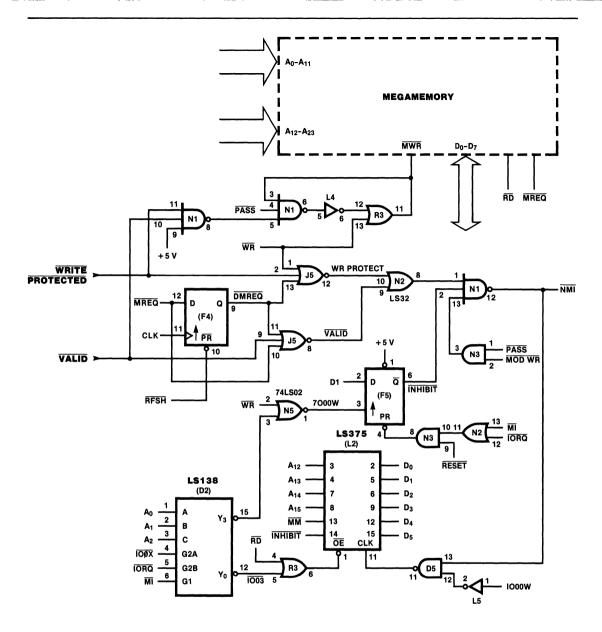

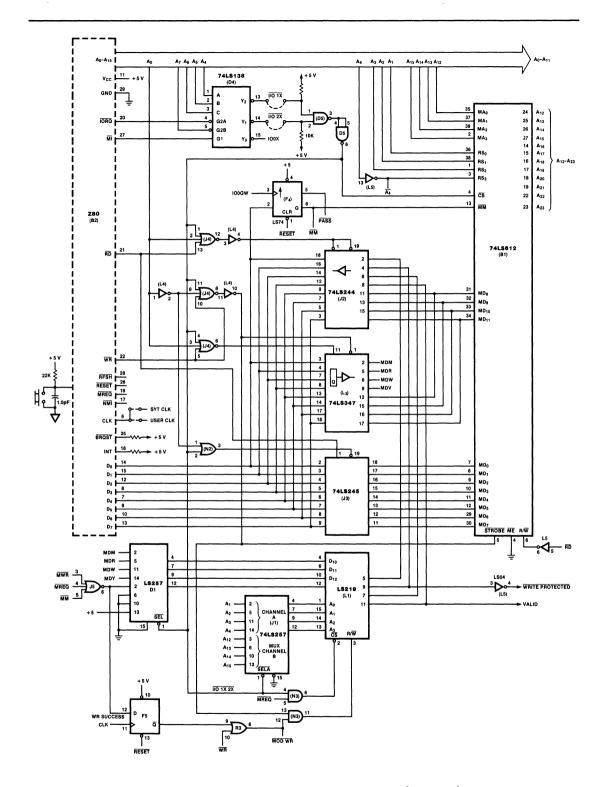

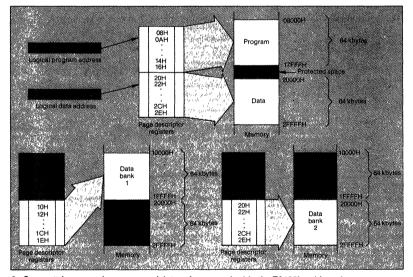

| Z80 Memory Expansion for the Z800                                     |   |

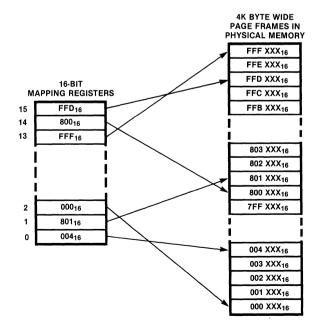

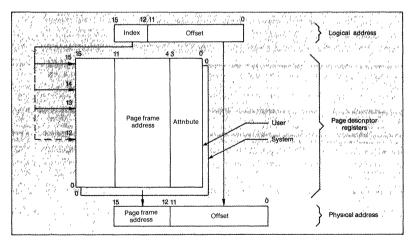

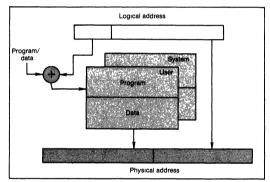

| On-Chip Memory Management Comes to 8-Bit Microprocessors              |   |

| 8- and 16-Bit Processor Family Keeps Pace with Fast RAMs              |   |

| Z8000 Family                                                          | 4 |

| Cost-Effective Memory Selection for Z8000 CPUs                        | • |

| Benchmark Report: Z8000 vs. 68000 vs. 8086                            |   |

| Operating System Support - The Z8000 Way                              |   |

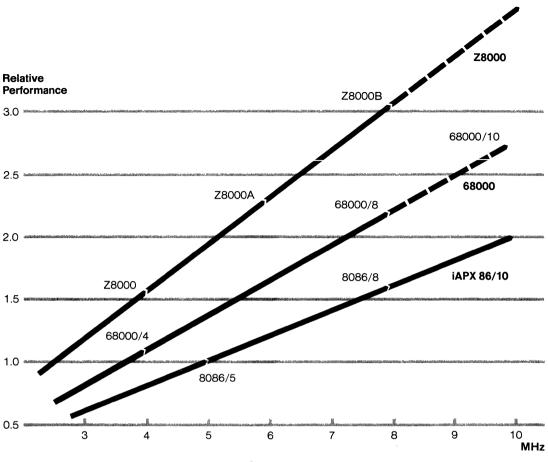

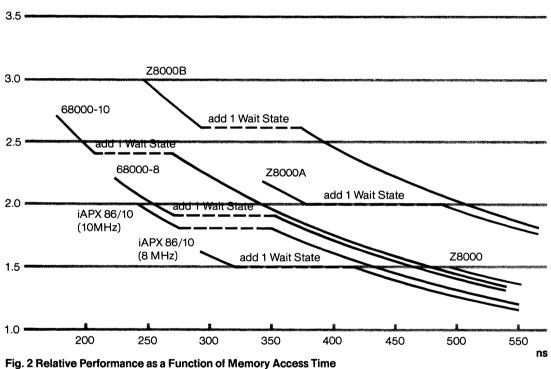

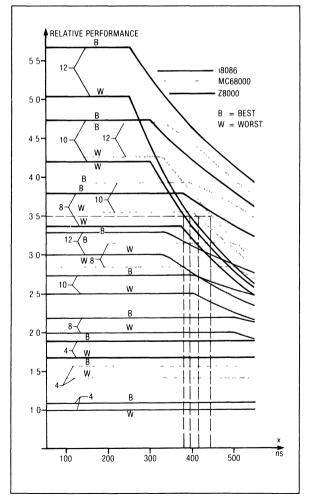

| A Performance Comparison of Three Contemporary 16-Bit Microprocessors |   |

| 16-Bit Microprocessors Get a Boost from Demand-Paged MMU              |   |

| Segmentation Advances Microcomputer Memory Addressing                 |   |

| Initializing the Z8001 CPU for Segmented Operation with the Z8010 MMU |   |

|                                                                       |   |

| Nonsegmented Z8001 CPU Programming                                    |   |

| Calling Conventions for the Z8000 Microprocessor                      |   |

| Fast Block Moves with the Z8000 CPU                                   |   |

| Character String Translation: Z8000 vs. 68000 vs. 8086 4-79           |   |

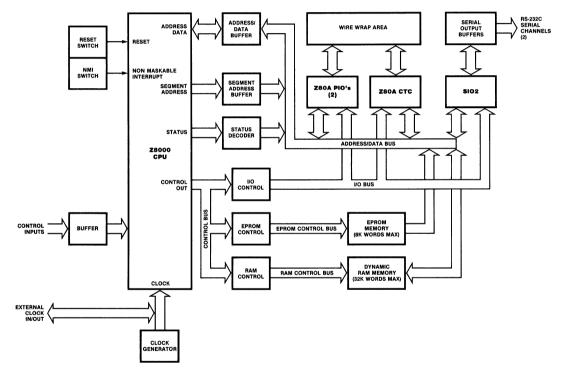

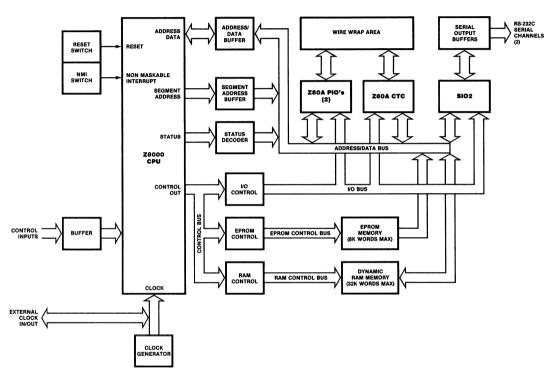

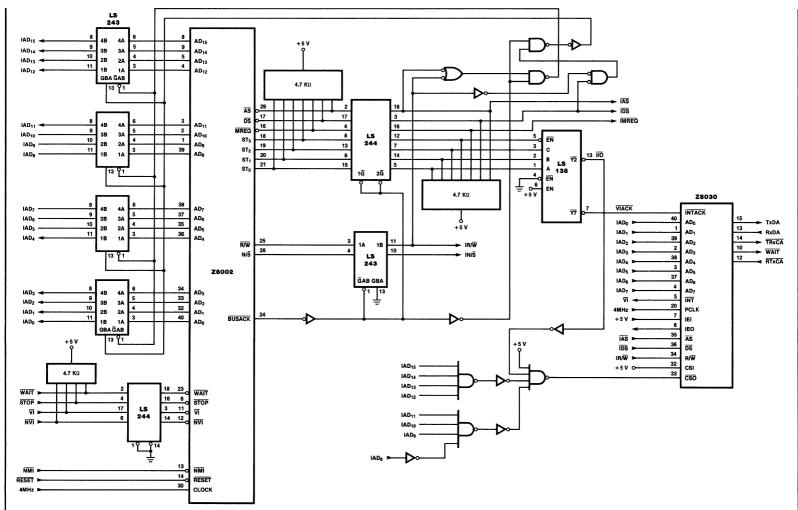

| Z8002 CPU Small Single-Board Computer                                 |   |

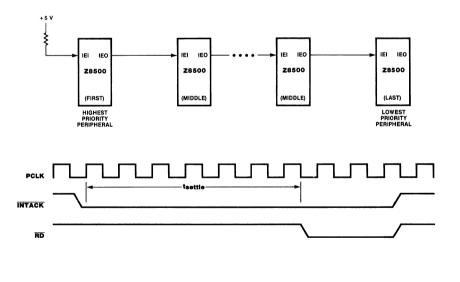

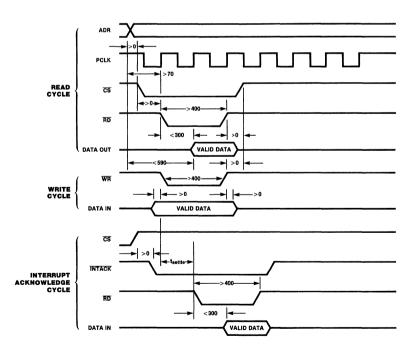

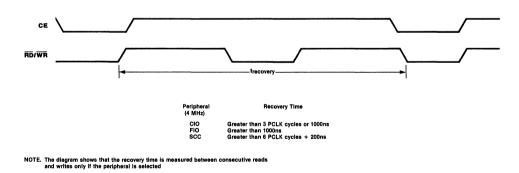

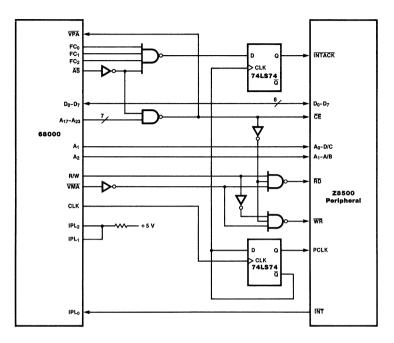

| Interfacing the Z8500 Peripherals to 68000                            |   |

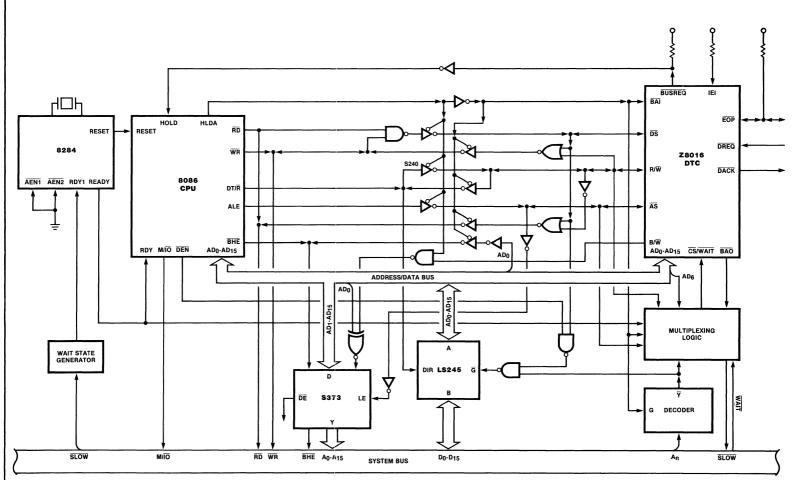

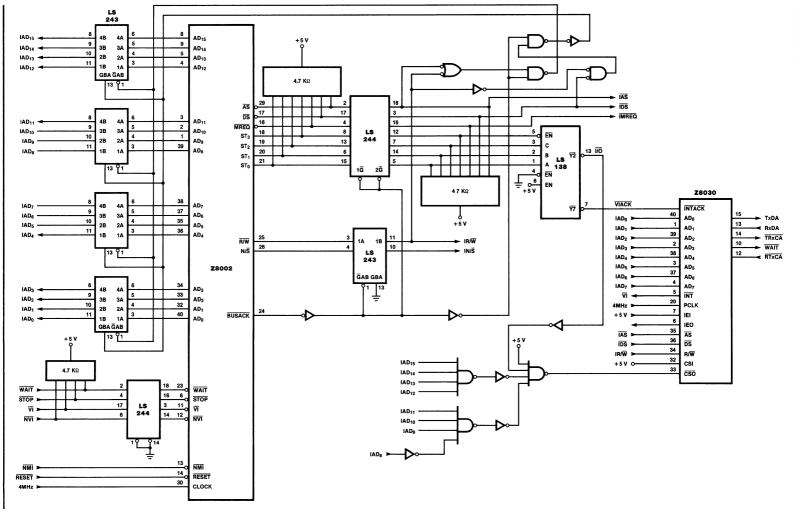

| Interfacing the Z-BUS Peripherals to the 8086/8088                    |   |

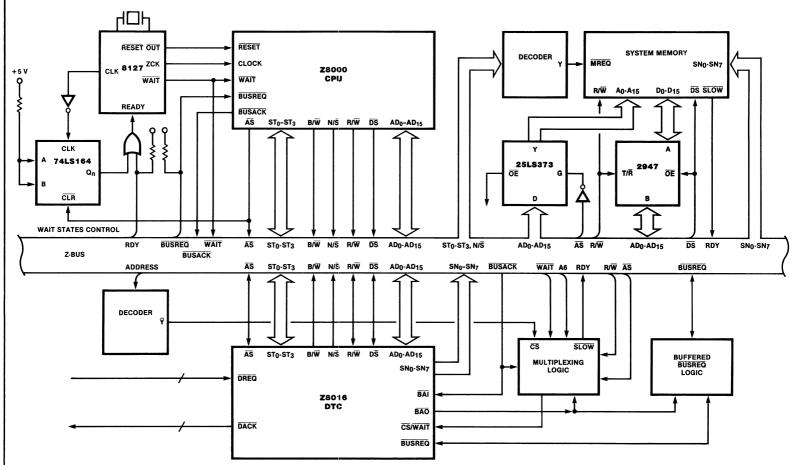

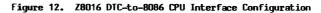

| Z8016/Z8000 DTC DMA Transfer Controller                               |   |

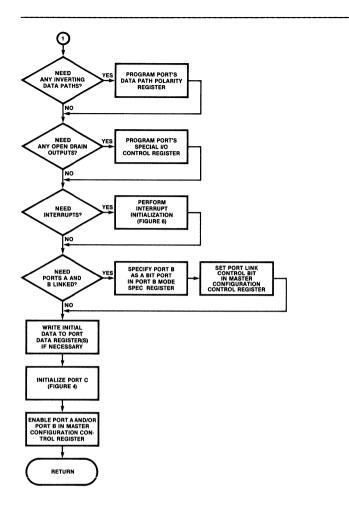

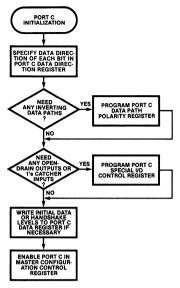

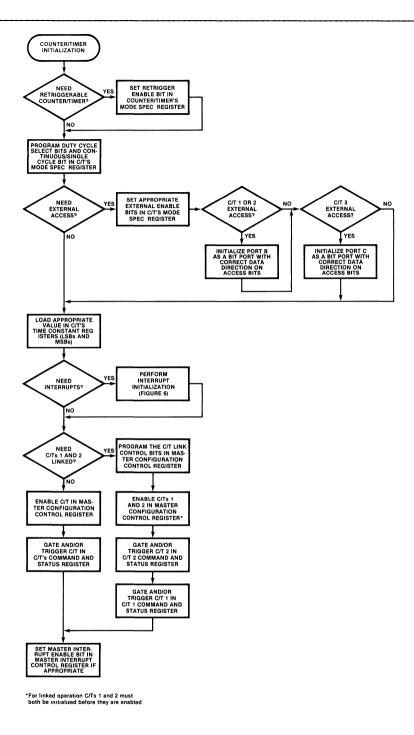

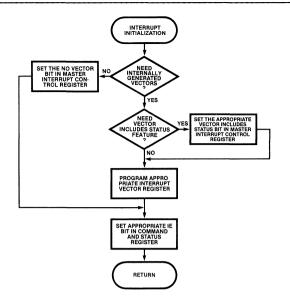

| Initializing the CIO                                                  |   |

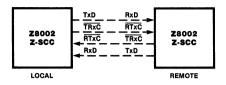

| Using SCC with Z8000 in SDLC Protocol                                 |   |

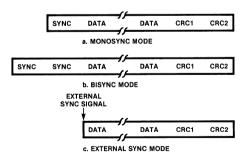

| SCC in Binary Synchronous Communication                               |   |

| Z8530/Z8030 SCC Initialization: A Worksheet and Example               |   |

| The Z-FIO in a Data Acquisition Application                           |   |

**Z8<sup>m</sup>Single Chip Microcomputer Family 1**

Z; og

# **Z8<sup>®</sup> Subroutine Library**

# Zilog

## Application Note

#### April 1982

#### INTRODUCTION

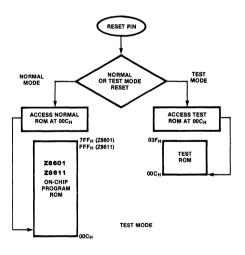

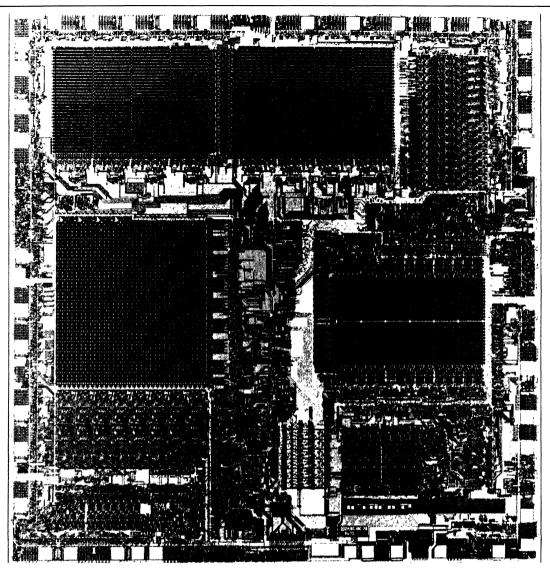

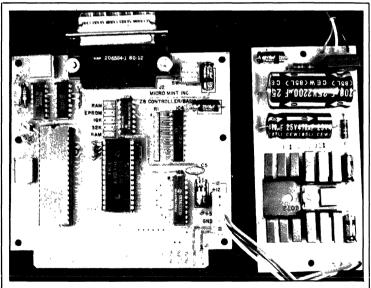

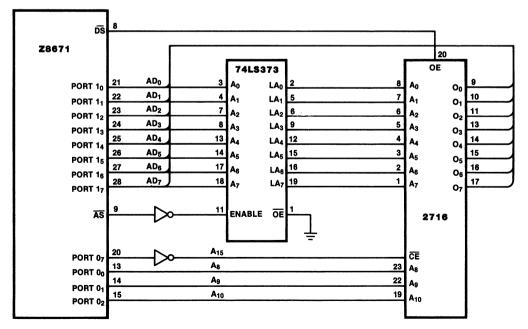

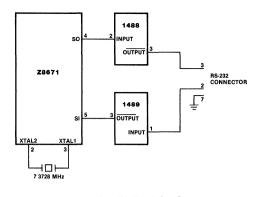

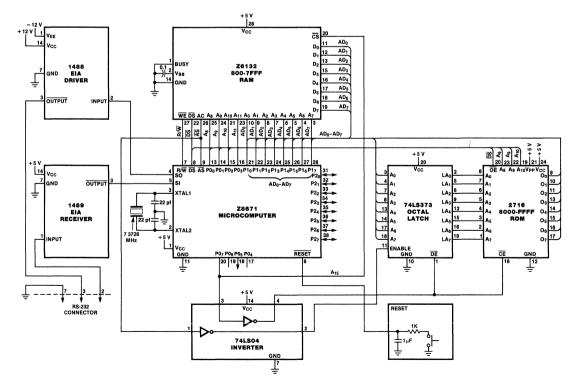

This application note describes a preprogrammed Z8601 MCU that contains a bootstrap to external program memory and a collection of general-purpose subroutines. Routines in this application note can be implemented with a Z8 Protopack and a 2716 EPROM programmed with the bootstrap and subroutine library.

In a system, the user's software resides in external memory beginning at hexidecimal address 0800. This software can use any of the subroutines in the library wherever appropriate for a given application. This application example makes certain assumptions about the environment; the reader should exercise caution when copying these programs for other cases.

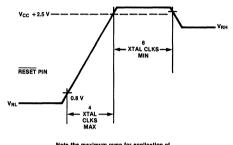

Following RESET, software within the subroutine library is executed to initialize the control registers (Table 1). The control register selections can be subsequently modified by the user's program (for example, to use only 12 bits of Ports 0 and 1 for addressing external memory). Following control register initialization, an EI

| Contro | l Register |               |                                                                                                                                                                                          |  |

|--------|------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name   | Address    | Initial Value | Meaning                                                                                                                                                                                  |  |

| TMR    | F1H        | OOH           | TO and T1 disabled                                                                                                                                                                       |  |

| P2M    | F6H        | FFH           | P2 <sub>0</sub> -P2 <sub>7</sub> : inputs                                                                                                                                                |  |

| РЗМ    | F7H        | 10H           | P2 pull-ups open drain;<br>P3 <sub>0</sub> -P3 <sub>3</sub> : inputs;<br>P3 <sub>5</sub> -P3 <sub>7</sub> : outputs;<br>P3 <sub>4</sub> : DM                                             |  |

| P01M   | F8H        | D7H           | P1 <sub>0</sub> -P1 <sub>7</sub> : AD <sub>0</sub> -AD <sub>7</sub> ;<br>PO <sub>0</sub> -PO <sub>7</sub> : A <sub>8</sub> -A <sub>15</sub> ;<br>normal memory timing;<br>internal stack |  |

| IRQ    | FAH        | OOH           | no interrupt requests                                                                                                                                                                    |  |

| IMR    | FBH        | OOH           | no interrupts enabled                                                                                                                                                                    |  |

| RP     | FDH        | ООН           | working register file<br>OOH-OFH                                                                                                                                                         |  |

| SPL    | FFH        | 65H           | 1st byte of stack is<br>register 64H                                                                                                                                                     |  |

|        |            |               | 00H-OFH<br>1st byte of stac                                                                                                                                                              |  |

Table 1. Control Register Initialization

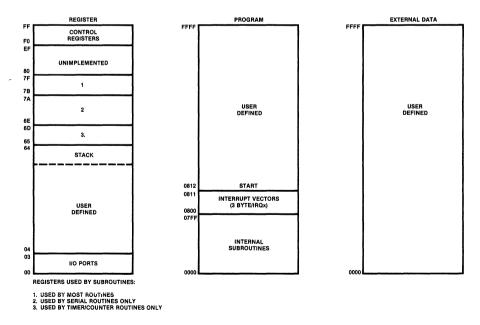

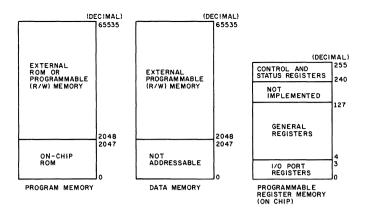

instruction is executed to enable interrupt processing, and a jump instruction is executed to transfer control to the user's program at location 0812<sub>11</sub>. The interrupt vectors for IRQ<sub>0</sub> through IRQs are rerouted to locations O800<sub>H</sub> through O80F<sub>H</sub>, respectively, in three-byte increments, allowing enough room for a jump instruction to the appropriate interrupt service routine. That is. IRQ<sub>0</sub> is routed to location O800<sub>H</sub>, IRQ<sub>1</sub> to  $0803_{\rm H}$ ,  $IRQ_2$  to  $0806_{\rm H}$ ,  $IRQ_3$  to  $0809_{\rm H}$ ,  $IRQ_4$  to OBOCH, and IRQ5 to OBOFH. Figure 1 illustrates the allocation of Z8 memory as defined by this application note.

The subroutines available to the user are referenced by a jump table beginning at location 001BH. Entry to a subroutine is made via the jump table. The 32 subroutines provided in the library are grouped into six functional classifications. These classifications are described below, each with a brief overview of the functions provided by each category. Table 2 defines one set of entry addresses for each subroutine in the library.

- Binary Arithmetic: Multiplication and division of unsigned 8- and 16-bit quantities.

- BCD Arithmetic: Addition and subtraction of variable-precision floating-point BCD values.

- Conversion Algorithms: BCD to and from decimal ASCII, binary to and from decimal ASCII, binary to and from hex ASCII.

- Bit Manipulations: Packs selected bits into the low-order bits of a byte, and optionally uses the result as an index into a jump table.

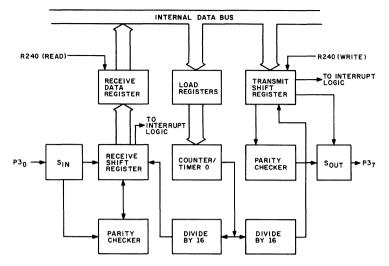

- Serial I/0: Inputs bytes under vectored interrupt control, outputs bytes under polled interrupt control. Options provided include:

odd or even parity

BREAK detection

echo

input editing (backspace, delete)

auto line feed

- Timer/Counter: Maintains a time-of-day clock with a variable number of ticks per second, generates an interrupt after a specified delay, generates variable width, variable frequency pulse output.

The listings in the "Canned Subroutine Library" provide a specification block prior to each subroutine, explain the subroutine's purpose, lists the input and output parameters, and gives pertinent notes concerning the subroutines. The following notes provide additional information on data formats and algorithms used by the subroutines.

Figure 1. "ROMLess Z8" Subroutine Library Memory Usage Map

1. Although the user is free to modify the conditions selected in the Port 3 Mode register (P3M, F7<sub>H</sub>), P3M is a write-only register. This subroutine library maintains an image of P3M in its register P3M\_\_save  $(7F_H)$ . If software outside of the subroutine package is to modify P3M, it should reference and modify P3M\_save prior to modification of P3M. For example, to select P32/P35 for handshake, the following instruction sequence could be used:

> OR P3M\_save, #04H LD P3M, P3M\_save

- 2. For many of the subroutines in this library, the location of the operands (source/destination) is flexible between register memory, external memory (code/data), and the serial channel (if enabled). The description of each parameter in the specification blocks tells what the location options are.

- The location designation "in reg/ext memory" implies that the subroutine allows the operand to exist in register or in external data memory. The address of such an operand is contained in the designated register pair. If the high byte of that pair is 0, the operand is in register memory at the address held in the low byte of the register pair. Otherwise, the operand is in external data memory (accessed via LDE).

- The location designation "in reg/ext/ser memory" implies the same considerations as above with one enhancement: if both bytes of the register pair are 0, the operand exists in the serial channel. In this case, the register pair is not modified (updated). For example, rather than storing a destination ASCII string in memory, it might be desirable to output the string to the serial line.

- 3. The BCD format supported by the following arithmetic and conversion routines allows representation of signed variable-precision BCD numbers. A BCD number of 2n digits is represented in n+1 consecutive bytes, where the byte at the lowest memory address (byte 0) represents the sign and post-decimal digit count, and the bytes in the n higher memory locations (bytes 1 through n) represent the magnitude of the BCD number. The address of byte 0 and the value n are passed to the subroutines in specified working registers.

Digits are packed two per byte with the mostsignificant digit in the high-order nibble of byte 1 and the least-significant digit in the low-order nibble of byte n. Byte 0 is organized as two fields:

Bit 7 represents sign: 1 = negative; 0 = positive.

Bits 0-6 represent post-decimal digit count.

For example:

- byte 0 =  $05_{\text{H}}$  = positive, with five postdecimal digits =  $80_{\text{H}}$  = negative, with no postdecimal digits

- = 90<sub>H</sub> = negative, with 16 postdecimal digits

- 4. The format of the decimal ASCII character string expected as input to the conversion routines "dascbcd" and "dascwrd" is defined as:

( + 1 - ) ( <digit> ) [ ( <digit> ) ]

in which

- ( ) Parentheses mean that the enclosed times or can be omitted.

- [] Brackets denote that the enclosed element is optional.

Table 3 illustrates how various input strings are interpreted by the conversion routines.

5. The format of the decimal ASCII character string output from the conversion routine "bcddasc" operating on an input BCD string of 2n digits is

1 sign of character ( + 1 - )

2n-x pre-decimal digits

1 decimal point if x does not equal 0

x post-decimal digits

- The format of the decimal ASCII character string output from the conversion routine "wrddassc" is

- 1 sign character (determined by bit 15 of input word) 6 pre-decimal digits no decimal point no post-decimal digits

## Table 2. Subroutine Entry Points

| Address    | Name             | Description                          |

|------------|------------------|--------------------------------------|

| Binary Ari | thmetic Routines |                                      |

| 001B       | divide           | 16/8 unsigned binary division        |

| 001E       | div 16           | 16/16 unsigned binary division       |

| 0021       | multiply         | 8x8 unsigned binary multiplication   |

| 0024       | mult_16          | 16x16 unsigned binary multiplication |

| BCD Arithm | etic Routines    |                                      |

| 0027       | bcdadd           | BCD addition                         |

| 002A       | bcdsub           | BCD subtraction                      |

| Conversion | Routines         |                                      |

| 002D       | bcddasc          | BCD to decimal ASCII                 |

| 0030       | dascbcd          | Decimal ASCII to BCD                 |

| 0033       | bcdwrd           | BCD to binary word                   |

| 0036       | wrdbcd           | Binary word to BCD                   |

| 0039       | bythasc          | Binary byte to hexadecimal ASCII     |

| 003C       | wrdhasc          | Binary word to hexadecimal ASCII     |

| 003F       | hascwrd          | Hexadecimal ASCII to binary word     |

| 0042       | wrddasc          | Binary word to decimal ASCII         |

| 0045       | dascwrd          | Decimal ASCII to binary word         |

| Bit Manipu | lation Routines  |                                      |

| 0048       | clb              | Collect bits in a byte               |

| 004B       | tmj              | Table jump under mask                |

| Serial Rou | ltines           |                                      |

| 004E       | ser_init         | Initialize serial I/O                |

| 0051       | ser_input        | IRQ3 (receive) service               |

| 0054       | ser_rlin         | Read line                            |

| 0057       | ser_rabs         | Read absolute                        |

| 005A       | ser_break        | Transmit BREAK                       |

| 005D       | ser_flush        | Flush (clear) input buffer           |

| 0060       | ser_wlin         | Write line                           |

| 0063       | ser_wabs         | Write absolute                       |

| 0066       | ser_wbyt         | Write byte                           |

| 0069       | ser_disable      | Disable serial I/O                   |

| Timer/Cour | ter Routines     |                                      |

| 006C       | tod_i            | Initialize for time-of-day clock     |

| 006F       | tod              | Time-of-day IRQ service              |

| 0072       | delay            | Initialize for delay interval        |

| 0075       | pulse_i          | Initialize for pulse output          |

| 0078       | pulse            | Pulse IRQ service                    |

7. Procedure name: ser input

The conclusion of the algorithm for BREAK detection requires the Serial Receive Shift register to be cleared of the character currently being collected (if any). This requires a software wait loop of a one-character duration. The following explains the algorithm used (code lines 464 through 472, Part II):

1 character time =

$$\frac{(128 \times PRE0 \times T0)}{XTAL} \frac{\sec}{bit} \times 10 \frac{bit}{char}$$

=  $\frac{1280 \times PRE0 \times T0}{XTAL} \frac{\sec}{char}$

A software loop equal to one character time is needed:

1 character time =

$$\frac{2}{XTAL} \frac{\sec}{\text{cycle}} \times n \frac{\text{cycle}}{100p}$$

=  $\frac{2n}{XTAL} \frac{\sec}{100p}$

Solve for n:

$$\frac{(1280 \times PRE0 \times T0)}{XTAL} = \frac{2n}{XTAL}$$

$n = 640 \times PRE0 \times TO$

The register pair SERhtime, SER1time was initialized during ser init to equal the product of the prescaler and the counter selected for the baud rate clock. That is,

SERhtime, SER1time = PRE0 x TO

The instruction sequence

inlop: ld rSERtmpl, #53 (6 cycles)

lpl: djnz rSERtmpl, lpl (12/10 cycles taken/not taken)

executes in

$6 + (52 \times 12) + 10$  cycles = 640 cycles

8. BREAK detection on the serial input line requires that the receive interrupt service routine be entered within a half-a-bit time, since the routine reads the input line to detect a true (=1) or false (=0) stop bit. Since the interrupt request is generated halfway through reception of the stop bit, half-a-bit time remains in which to read the stop bit level. Interrupt priorities and interrupt nesting should be established appropriately to ensure this requirement.

$$1/2 \text{ bit time} = \frac{(128 \times PRE0 \times T0)}{XTAL \times 2} \text{ sec}$$

| Table 3. Decimal ASCII Character String Interpret | tion |

|---------------------------------------------------|------|

|---------------------------------------------------|------|

| Input String | <br>Sign | Result<br>Pre-Decimal<br>Digits | Post-Decimal<br>Digits | Terminator |

|--------------|----------|---------------------------------|------------------------|------------|

| +1234.567,   | +        | 1234                            | 567                    | 9          |

| ++•789+      | -        |                                 | 789                    | +          |

| 1234         | +        | 1234                            |                        | •          |

| 4976-        | +        |                                 | 4976                   | -          |

|              |          |                                 |                        |            |

NOTE: The terminator can be any ASCII character that is not a valid ASCII string character.

## ROMLESS Z8 SUBROUTINE LIBRARY PART I

| Z 8 A SM<br>LOC | 3.02<br>OBJ CODE | STMT S                                                             | SOURCE STATEMENT                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------|------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                  | 4<br>5                                                             | PART_I MODULE                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                 |                  | 6 <b>!</b><br>7                                                    | 'ROMLESS Z8' SUBROUTINE LIBRARY PART I                                                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                  | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19 | <pre>Initialize: a) Port 0 &amp; Port 1 set up to address<br/>64K external memory;<br/>b) internal stack below allocated<br/>RAM for subroutines;<br/>c) normal memory timing;<br/>d) IMR, IRQ, TMR, RP cleared;<br/>e) Port 2 inputs open-drain pull-ups;<br/>f) Data Memory select enabled;<br/>g) EI executed to 'unfreeze' IRQ;<br/>h) Jump to \$0812.</pre>                                                                                      |

|                 |                  | 20 M<br>21<br>22<br>23<br>24                                       | Note: The user is free to modify the initial<br>conditions selected for a, b, and c above,<br>via direct modification of the Port 0 & 1<br>Mode register (P01M, %F8).                                                                                                                                                                                                                                                                                 |

|                 |                  | 25<br>26<br>27<br>28<br>29<br>31<br>32<br>33                       | The user is free to modify the conditions<br>selected in the Port 3 Mode register (P3M, %F7).<br>However, please note that P3M is a write-only<br>register. This subroutine library maintains<br>an image of P3M in its register P3M save (%7F).<br>If software outside of the subroutine package<br>is to modify P3M, it should reference and modify<br>P3M_save, prior to modification of P3M. For<br>example, to select P32/P35 for handshake, use |

|                 |                  | 34<br>35<br>36<br>37<br>38                                         | an instruction sequence such as:<br>OR P3M save,#\$04<br>LD P3M,P3M_save                                                                                                                                                                                                                                                                                                                                                                              |

|                 |                  | 39<br>40<br>41<br>42 !                                             | This is important if the serial and/or timer/<br>counter subroutines are to be used, since these<br>routines may modify P3M.<br>!                                                                                                                                                                                                                                                                                                                     |

44 !Access to GLOBAL subroutines in this library should be made via a CALL to the corresponding entry in the 45 jump table which begins at address \$000F. The jump 46 47 table should be referenced rather than a CALL to the 48 actual entry point of the subroutine to avoid future conflict in the event such entry points change in 49 50 potential future revisions. 51 52 Each GLOBAL subroutine in this listing is headed by a comment block specifying its PURPOSE and calling 53 sequence (INPUT and OUTPUT parameters). For many of 54 55 the subroutines in this library, the location of the 56 operands (sources/destinations) is quite flexible between register memory, external memory (code/data), and the serial channel (if enabled). The description 57 58 59 of each parameter specifies what the location choices 60 aret 61 62 - The location designation 'in reg/ext memory' implies that the subroutine allows that the operand 63 exist in either register or external data memory 64 The address of such an operand is contained 65 66 in the designated register pair. If the high byte of that pair is zero, the operand is in register memory 67 at the address given by the low byte of the register pair. Otherwise, the operand is in external data 68 69 memory (accessed via LDE). 70 71 72 - The location designation 73 'in reg/ext/ser memory' implies the same 74 considerations as above with one enhancement: if both 75 bytes of the reg. pair are zero, the operand exists in the serial channel. In this case, the register 76 77 pair is not modified (updated). For example, rather 78 than storing a destination ASCII string in memory, it 79 might be desirable to output such to the serial line.

80 1

```

82 CONSTANT

83 !Register Usage!

84

85 RAM START

%7F

:=

86

87 P3M save

:=

RAM START

88 TEMP 3

89 TEMP 2

P3M save-1

TEMP_3-1

TEMP_2-1

TEMP_1-1

:=

:=

90 TEMP 1

:=

91 TEMP 4

:=

92

93 !The following registers are modified/referenced

by the Serial Routines ONLY. They are

94

available as general registers to the user

who does not intend to make use of the

95

96

97

Serial Routines!

98

99 SER char

:=

TEMP 4-1

SER char-1

100 SER_tmp2

101 SER_tmp1

:=

:=

SER tmp2-1

102 SER put

103 SER len

104 SER buf

SER tmp1-1

:=

SER_put-1

SER_len-2

: =

:=

105 SER imr

SER buf-1

:=

106 SER cfg := SEI

107 !Serial Configuration Data

SER imr-1

108 bit 7 : =1 => odd parity on

109 bit 6 : =1 => even parity on

(bit 6,7 = 11 => undefined)

110

111 bit 5 : undefined

112 bit 4 : undefined

113 bit 3 : =1 => input editting on

114 bit 2 : =1 => auto line feed enabled

115 bit 1 : =1 => BREAK detection enabled

116 bit 0 : =1 => input echo on

117 !

$80

118 op

:=

119 ep

$40

:=

120 ie

$08

:=

121 al

$04

:=

122 be

:=

$02

123 ec

$01

:=

124 SER_get

125 SER_flg

SER cfg-1

:=

SER_get-1

:=

126 !Serial Status Flags

127 bit 7 : =1 => serial I/O disabled

128 bit 6 : undefined

129 bit 5 : undefined

130 bit 4 : =1 => parity error

131 bit 3 : =1 => BREAK detected

132 bit 2 : =1 => input buffer overflow

133 bit 1 : =1 => input buffer not empty

134 bit 0 : =1 => input buffer full

135 1

136 sd

$80

:=

137 pe

$10

:=

138 bd

$08

:=

139 bo

%04

:=

140 bne

$02

:=

141 bf

$01

:=

142

143 RAM TMR

:=

RAM START-$10

144

145 SERltime

SER_flg-1

:=

```

146 SERhtime SER1time-1 : -147 148 !The following registers are modified/referenced 149 by the Timer/Counter Routines ONLY. They are available as general registers to the user who does not intend to make use of the 150 151 Timer/Counter Routines! 152 153 154 TOD\_tic 155 TOD\_imr 156 TOD\_hr RAM TMR-2 TOD\_tic-1 TOD\_imr-1 TOD\_hr-1 := := := 157 TOD min 158 TOD sec := TOD\_min\_1 TOD\_sec\_1 := 159 TOD\_tt 160 PLS\_1 := TOD\_tt-1 PLS\_1-1 := 161 PLS\_tmr 162 PLS\_2 := PLS tmr-1 : -163 164 RAM END PLS 2 := 165 STACK RAMEND := 166 167 !Equivalent working register equates 168 for above register layout! 169 170 !register file \$70 - \$7F! Ifor SRP! 171 RAM STARTr := \$70 172 173 rP3Msave R15 := 175 rTEMP\_3 175 rTEMP\_2 176 rTEMP\_1 R14 := R13 := R12 := 177 rrTEMP 1 178 rTEMP 1 178 rTEMP 1 179 rTEMP 1 180 rTEMP 1 181 rTEMP 4 **RR12** := R12 := := R13 R11 := 181 rSERchar R10 := 182 rSERtmp2 R9 R8 := 183 rSERtmp1 := 184 rrSERtmp RR8 := 185 rSERtmpl R9 := 186 rSERtmph R8 := 187 rSERput 188 rSERlen R7 := R6 := 189 rrSERbuf := RR4 190 rSERbufh R4 := 191 rSERbufl R5 := 192 rSERimr R3 R2 := 193 rSERcfg := 194 rSERget R 1 := 195 rSERflg RO := 196 197 198 !register file \$60 - \$6F! 199 RAM TMRr 200 rTODtic := \$60 Ifor SRPI R13 := 201 rTODimr R12 := 202 rTODhr := R11 203 rTODmin R10 := 204 rTODsec := R9 205 rTODtt R8 := 206 rPLS 1 := R7 207 rPLSTmr := RĠ 208 rPLS 2 := R5

|                            |                                                                                                                                                                                                                                                                                       |              | and the second                                                                                |    |         |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|

|                            | 210 EXTERNAL<br>211 ser_init<br>212 ser_input<br>213 ser_rlin<br>214 ser_rabs<br>215 ser_break<br>216 ser_flush<br>217 ser_wlin<br>218 ser_wabs<br>219 ser_wbyt<br>220 ser_disable<br>221 ser_get<br>222 ser_output<br>223 tod_i<br>224 tod_<br>225 delay<br>226 pulse_i<br>227 pulse |              | PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE<br>PROCEDURE |    |         |

|                            | 229<br>230                                                                                                                                                                                                                                                                            | + S E C      | TION PROGRAM                                                                                                                                                                                    |    |         |

|                            |                                                                                                                                                                                                                                                                                       |              | TION PROGRAM                                                                                                                                                                                    |    |         |

|                            | 231                                                                                                                                                                                                                                                                                   | GLOBAL       |                                                                                                                                                                                                 |    |         |

|                            | 232                                                                                                                                                                                                                                                                                   |              |                                                                                                                                                                                                 |    |         |

|                            | 233                                                                                                                                                                                                                                                                                   |              |                                                                                                                                                                                                 |    |         |

|                            | 234                                                                                                                                                                                                                                                                                   | !Interrupt v |                                                                                                                                                                                                 |    |         |

| P 0000 0800                | 235                                                                                                                                                                                                                                                                                   | IRQ_O ARRA   |                                                                                                                                                                                                 | := | [%0800] |

| P 0002 0803                |                                                                                                                                                                                                                                                                                       | IRQ 1 ARRA   |                                                                                                                                                                                                 | := | [%0803] |

| P 0004 0806                | 237                                                                                                                                                                                                                                                                                   | IRQ 2 ARRA   |                                                                                                                                                                                                 | := | [%0806] |

| P 0006 0809                | 238                                                                                                                                                                                                                                                                                   | IRQ 3 ARRA   |                                                                                                                                                                                                 | := | [%0809] |

| P 0008 080C<br>P 000A 080F | 239<br>240                                                                                                                                                                                                                                                                            | IRQ 4 ARRA   |                                                                                                                                                                                                 | := | [%080C] |

| I COUR DOUR                | 240<br>241<br>242                                                                                                                                                                                                                                                                     | IRQ_5 ARRA   | Y [1 word]                                                                                                                                                                                      | := | [%080F] |

|                  |                              |          |                                  | 244 GLOBAL<br>245                            |                   |                 |                                                                           |

|------------------|------------------------------|----------|----------------------------------|----------------------------------------------|-------------------|-----------------|---------------------------------------------------------------------------|

| P                | 000C                         |          |                                  | 245<br>246 !Jump 1<br>247 ENTER<br>248 ENTRY | Table!<br>PROCEDU | RE              |                                                                           |

| P<br>P           | 000C<br>000F                 | 8D       | 007B'                            | 249<br>250 END<br>251                        | JP<br>Enter       | INIT            |                                                                           |

| P<br>P<br>P<br>P | 000F<br>0012<br>0015<br>0018 | 31<br>30 | 43 29<br>39 38<br>5A 49<br>4F 47 | 252<br>253 copyrig<br>254                    | ght ARRAY         | [* BYTE] := '(( | C)1980ZILOG'                                                              |

| P                | 001B                         |          |                                  | 255 !Subrou<br>256 JUMP<br>257 ENTRY<br>258  | PROCEDU           |                 |                                                                           |

|                  |                              |          |                                  | 259 !Binary                                  | Arithme           | tic Routines!   |                                                                           |

| Ρ                | 001B                         | 8D       | 0099'                            | 260<br>261<br>262                            | JP                | divide          | !16/8 unsigned binary<br>division!                                        |

| Ρ                | 001E                         | 8D       | 00B7'                            | 263<br>264                                   | JP                | div_16          | !16/16 unsigned binary<br>division!                                       |

| Ρ                | 0021                         | 8D       | 00E2'                            | 265<br>266                                   | JP                | multiply        | !8x8 unsigned binary<br>multiplication!                                   |

| Ρ                | 0024                         | 8D       | 00F6'                            | 267<br>268                                   | JP                | mult_16         | <pre>#ditipileation:<br/>!16x16 unsigned binary<br/>multiplication!</pre> |

|                  |                              |          |                                  |                                              | ithmetic          | Routines!       |                                                                           |

| P                | 0027                         | 8D       | 0114'                            | 271<br>272<br>273                            | JP                | bcdadd          | !BCD addition!                                                            |

| Ρ                | 002A                         | 8D       | 0117'                            | 274<br>275                                   | JP                | bcdsub          | !BCD subtraction!                                                         |

|                  |                              |          |                                  | 276 !Conver                                  | sion Rout         | tines!          |                                                                           |

| P                | 002D                         | 8D       | 0205'                            | 277<br>278<br>279                            | JP                | beddase         | !BCD to decimal ASCII!                                                    |

| Ρ                | 0030                         | 8D       | 0363'                            | 280                                          | JP                | dascbcd         | !Decimal ASCII to BCD!                                                    |

| Ρ                | 0033                         | 8D       | 0284'                            | 282                                          | JP                | bedwrd          | !BCD to binary word!                                                      |

| Ρ                | 0036                         | 8D       | 02CD'                            | 284<br>285                                   | JP                | wrdbcd          | !binary word to BCD!                                                      |

| Ρ                | 0039                         | 8D       | 0250'                            | 286<br>287                                   | JP                | bythasc         | !Bin. byte to Hex ASCII!                                                  |

| Ρ                | 003C                         | 8D       | 0257 <b>'</b>                    | 288                                          | JP                | wrdhasc         | !Bin. word to hex ASCII!                                                  |

| Ρ                | 003F                         | 8D       | 0319'                            | 289<br>290                                   | JP                | hascwrd         | !Hex ASCII to bin word!                                                   |

| Ρ                | 0042                         | 8D       | 03BE'                            | 291<br>292                                   | JP                | wrddasc         | !Bin. word to dec ASCII!                                                  |

| Ρ                | 0045                         | 8D       | 034D'                            | 293<br>294                                   | JP                | dascwrd         | !dec ASCII to bin word!                                                   |

|                  |                              |          |                                  |                                              | nipulatio         | on Routines!    |                                                                           |

| P                | 0048                         | 8D       | 0441'                            | 297<br>298<br>299                            | JP                | clb             | <pre>!collect bits in a byte!</pre>                                       |

| Ρ                | 004B                         | 8D       | 0489'                            | 300<br>301                                   | JP                | tjm             | !Table Jump Under Mask!                                                   |

|                  |                              |          |                                  | 302 !Serial<br>303                           | Routines          | s !             |                                                                           |

| Ρ                | 004E                         | 8D       | 0000*                            | 304                                          | JP                | ser_init        | !initialize serial I/O!                                                   |

| -                              |                              |                                  |                                  |                      |                                                                     |                           |                                                        |                                                                                   |                                                                                                                                                                            |

|--------------------------------|------------------------------|----------------------------------|----------------------------------|----------------------|---------------------------------------------------------------------|---------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P                              | 0051                         | 8D                               | 000                              | 0#                   | 305<br>306                                                          |                           | JP                                                     | ser_input                                                                         | !IRQ3 (receive) service!                                                                                                                                                   |

| P                              | 0054                         | 8D                               | 000                              | )#                   | 307<br>308                                                          |                           | JP                                                     | ser_rlin                                                                          | !read line!                                                                                                                                                                |

| Ρ                              | 0057                         | 8 D                              | 000                              | 0#                   | 309<br>310                                                          |                           | JP                                                     | ser_rabs                                                                          | !read absolute!                                                                                                                                                            |

| P                              | 005A                         | 8D                               | 000                              | 0*                   | 311<br>312                                                          |                           | JP                                                     | ser_break                                                                         | !transmit BREAK!                                                                                                                                                           |

| Ρ                              | 005D                         | 8D                               | 000                              | 0*                   | 313<br>314<br>215                                                   |                           | JP                                                     | ser_flush                                                                         | !flush (clear)<br>input buffer!                                                                                                                                            |

| P                              | 0060                         | 8D                               | 000                              | 0#                   | 315<br>316<br>317                                                   |                           | JP                                                     | ser_wlin                                                                          | !write line!                                                                                                                                                               |

| P                              | 0063                         | 8D                               | 000                              | 0*                   | 318<br>319                                                          |                           | JP                                                     | ser_wabs                                                                          | !write absolute!                                                                                                                                                           |

| Ρ                              | 0066                         | 8D                               | 000                              | 0*                   | 320<br>321                                                          |                           | JP                                                     | ser_wbyt                                                                          | !write byte!                                                                                                                                                               |

| P                              | 0069                         | 8D                               | 000                              | ) <b>#</b>           | 322<br>323                                                          |                           | JP                                                     | ser_disable                                                                       | !disable serial I/O!                                                                                                                                                       |

|                                |                              |                                  |                                  |                      | 324<br>325                                                          | !Timer/(                  | Counter                                                | Routines!                                                                         |                                                                                                                                                                            |

| Ρ                              | 006C                         | 8D                               | 000                              | 0#                   | 326<br>327                                                          |                           | JP                                                     | tod_i                                                                             | linit for time of day!                                                                                                                                                     |

| Ρ                              | 006F                         | 8D                               | 000                              | ) <b>#</b>           | 328<br>329                                                          |                           | JP                                                     | tod                                                                               | <pre>!tod IRQ service!</pre>                                                                                                                                               |

| Ρ                              | 0072                         | 8D                               | 000                              | 0#                   | 330<br>331                                                          |                           | JP                                                     | delay                                                                             | init for delay interval!                                                                                                                                                   |

| Ρ                              | 0075                         | 8D                               | 000                              | ) <b>*</b>           | 332<br>333                                                          |                           | JP                                                     | pulse_i                                                                           | !init for pulse output!                                                                                                                                                    |

| Ρ                              | 0078                         | 8D                               | 000                              | <b>)</b> *           | 334<br>335                                                          |                           | JP                                                     | pulse                                                                             | <pre>!pulse IRQ service!</pre>                                                                                                                                             |

| Ρ                              | 007B                         |                                  |                                  |                      |                                                                     | END                       | JUMP                                                   |                                                                                   |                                                                                                                                                                            |

| ٩                              | 007B                         |                                  |                                  |                      | 339                                                                 | !Initia]<br>INIT<br>ENTRY | lization<br>PROCEDU                                    |                                                                                   |                                                                                                                                                                            |

| P                              | 007B                         | E6                               | F8                               | D7                   | 342<br>343<br>344<br>345<br>346                                     |                           | LD                                                     | P01M,#%(2)11010                                                                   | 111<br>!internal stack;<br>ADO-A15;<br>normal memory<br>timing !                                                                                                           |

| P                              | 007E                         | E6                               | 7F                               | 10                   | 347<br>348<br>349<br>350<br>351                                     |                           | LD                                                     | P3M_save,#%(2)0                                                                   |                                                                                                                                                                            |

| ዋ<br>ዋ ዋ<br>ዋ ዋ<br>ዋ<br>ዋ<br>ዋ | 008C<br>008E<br>0090<br>0092 | E6<br>B0<br>B0<br>B0<br>B0<br>E6 | 7F<br>FF<br>F6<br>F8<br>F0<br>70 | F7<br>65<br>FF<br>80 | 352<br>3553<br>3554<br>3556<br>3556<br>3558<br>3558<br>3559<br>3590 |                           | LD<br>LD<br>CLR<br>LD<br>CLR<br>CLR<br>CLR<br>LD<br>EI | P3M,P3M_save<br>SPL,#STACK<br>TMR<br>P2M,#%FF<br>IRQ<br>IMR<br>RP<br>SER_f1g,#%80 | <pre>!set up Port 3 ! !stack pointer ! !reset timers! !all inputs! !reset int. requests! !disable interrupts ! !register pointer! !serial disabled! !globally enable</pre> |

|                                | 0095                         |                                  |                                  |                      | 361                                                                 |                           |                                                        |                                                                                   | interrupts !                                                                                                                                                               |

| P<br>P                         | 0095                         |                                  | 081                              | 2                    | 362<br>363                                                          | END                       | JP<br>INIT                                             | \$0812                                                                            | interrupts !                                                                                                                                                               |

# Binary Arithmetic Routines

| P 0099                       | 397 CONSTANT<br>398 div LEN<br>399 DIVISOR<br>400 dividend HI<br>401 dividend_LO<br>402 GLOBAL<br>403 divide PROCEDU<br>404 !********** | := R10<br>:= R11<br>:= R12<br>:= R13                                      |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|                              | 405 Purpose =<br>406                                                                                                                    | To perform a 16-bit by 8-bit unsigned<br>binary division.                 |

|                              | 407<br>408 Input =<br>409                                                                                                               | R11 = 8-bit divisor<br>RR12 = 16-bit dividend                             |

|                              | 410                                                                                                                                     |                                                                           |

|                              | 411 Output =                                                                                                                            | R13 = 8-bit quotient                                                      |

|                              | 412                                                                                                                                     | R12 = 8-bit remainder                                                     |

|                              | 413<br>414                                                                                                                              | Carry flag = 1 if overflow<br>= 0 if no overflow                          |

|                              | 414                                                                                                                                     | R11 unmodified                                                            |

|                              |                                                                                                                                         | ***************                                                           |

|                              | 417 ENTRY                                                                                                                               |                                                                           |

| P 0099 A9 7C                 | 418 ld                                                                                                                                  | TEMP_1,div_LEN !save caller's R10!                                        |

| P 009B AC 08                 | 419 ld                                                                                                                                  | div_TEN,#8 !LOOP COUNTER!                                                 |

|                              | 420                                                                                                                                     | T UTL FTT TN O DITCH                                                      |

| P 009D A2 BC                 |                                                                                                                                         | T WILL FIT IN 8 BITS!<br>DIVISOR,dividend HI                              |

| P 009F BB 02                 | 422 cp<br>423 jr                                                                                                                        | UGT,LOOP TCARRY = 0 (FOR RLC)!                                            |

| 1 0091 00 02                 | 424 !overflow!                                                                                                                          |                                                                           |

| P OOA1 DF                    | 425 SCF                                                                                                                                 | !CARRY = 1!                                                               |

| P 00A2 AF                    | 426 ret                                                                                                                                 |                                                                           |

|                              | 427                                                                                                                                     |                                                                           |

| P 00A3 10 ED<br>P 00A5 10 EC | 428 LOOP: RLC<br>429 RLC                                                                                                                | dividend_LO                                                               |

| P 00A5 10 EC<br>P 00A7 7B 04 | 430 jr                                                                                                                                  | c.subt                                                                    |

| P 00A9 A2 BC                 | 431 cp                                                                                                                                  | DIVISOR, dividend HI                                                      |

| P OOAB BB 03                 | 432 jr                                                                                                                                  | UGT, next ICARRY = 0!                                                     |

| P OOAD 22 CB                 | 433 subt: SUB                                                                                                                           | dividend HI, DIVISOR                                                      |

| P OOAF DF                    | 434 SCF                                                                                                                                 | TO BE SHIFTED INTO RESULT!                                                |

| P OOBO AA F1                 | 435 next: djnz<br>436                                                                                                                   | div_LEN,LOOP !no flags affected!                                          |

|                              | 437 IALL DONE!                                                                                                                          |                                                                           |

| P 00B2 10 ED                 | 438 RLC                                                                                                                                 | dividend_LO                                                               |

| P 00B4 A8 7C                 | 439<br>440 1d                                                                                                                           | <pre>iCARRY = 0: no overflow! div LEN,TEMP 1 !restore caller's R10!</pre> |

| P 00B4 A8 70                 | 440 10<br>441 ret                                                                                                                       | dra pruliteut i ilescole carrel 2 MIOI                                    |

| P 00B7                       | 442 END divide                                                                                                                          |                                                                           |

|                              |                                                                                                                                         |                                                                           |

|              | 444 CONSTANT                                                                                                             |

|--------------|--------------------------------------------------------------------------------------------------------------------------|

|              | 445  d16 LEN := R7                                                                                                       |

|              | 446 dvsr hi := R8                                                                                                        |

|              | 447 dvsr <sup>-</sup> lo := R9                                                                                           |

|              | 448 rem hi := R10                                                                                                        |

|              | 449 rem_lo := R11                                                                                                        |

|              | 450 quot_hi := R12                                                                                                       |

|              | 451 quot_lo := R13                                                                                                       |

| _            | 452 GLOBAL                                                                                                               |

| P 00B7       | 453 div 16 PROCEDURE                                                                                                     |

|              |                                                                                                                          |

|              | 455 Purpose = To perform a 16-bit by 16-bit unsigned                                                                     |

|              | 456 binary division.                                                                                                     |

|              | 457<br>458 Input = RR8 = 16-bit divisor                                                                                  |

|              | $458  \text{Input} = \qquad \text{RR} = 10-\text{bit divisor}$ $459 \qquad \qquad \text{RR} 12 = 16-\text{bit dividend}$ |

|              | 460                                                                                                                      |

|              | 460<br>461 Output = RR12 = 16-bit quotient                                                                               |

|              | 462 	RR10 = 16-bit remainder                                                                                             |

|              | 463 RR8 unmodified                                                                                                       |

|              | 464 *********************                                                                                                |

|              | 465 ENTRY                                                                                                                |

| P 00B7 79 7C | 466 ld TEMP 1,d16 LEN !save caller's R10!                                                                                |

| P 00B9 7C 10 | 467 1d d16 LEN, #16 !LOOP COUNTER!                                                                                       |

| P OOBB CF    | 468 rcf !carry = 0!                                                                                                      |

| P OOBC BO EA | 469 clr rem_hi                                                                                                           |

| P OOBE BO EB | 470 clr rem lo                                                                                                           |