## MICROPROCESSOR APPLICATIONS REFERENCE BOOK

# **VOLUME 1**

Copyright 1981 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog.

The information contained herein is subject to change without notice Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

## Introduction

Zilog's name has become synonomous with logic innovation and advanced microprocessor architecture since the introduction of the Z80  $^{IM}$  CPU in 1975. The Zilog Family of microprocessors and microcomputers has grown to include the products listed in the table below. Each product exhibits special features that make it stand above similar products in the semiconductor marketplace. These special features have proven to be of substantial aid in the solution of microprocessor design problems.

This reference book contains a collection of application information about Zilog microprocessor products. It includes technical articles, application notes, concept papers, and benchmarks. The reference book is intended as the first of several such volumes. We at Zilog believe that designing innovative microprocessor integrated circuit products is only half the key that unlocks the future of microprocessor-based end products: the other half is the creative application of those products. Advanced microprocessor products and their creative application lead to end product designs with more features, more simply implemented, at a lower system cost. It is hoped this reference book will stimulate new product design ideas as well as fresh approaches to the design of traditional microprocessor-based products.

The material in this book is believed to be accurate and up-to-date. If you do find errors, or would like to offer suggestions for future application notes, we would appreciate hearing from you. Correction inputs should be directed to Components Division Technical Publications, and application suggestions should be directed to Components Division Application Engineering.

| Z8600 FAMILY | 8-bit Single Chip Microcomputer,<br>2K Bytes ROM and 144 Bytes RAM | Z8000 FAMILY | 16-bit General Purpose<br>Microprocessor |

|--------------|--------------------------------------------------------------------|--------------|------------------------------------------|

| Z8601        | Mask Programmed                                                    | Z8001 CPU    | Segmented CPU                            |

| Z8602        | Development Package                                                | Z8002 CPU    | Non-Segment ed CPU                       |

| Z8603        | Protopack                                                          | Z8003 VMPU   | Segmented Virtual Memory                 |

| Z8671        | Basic/Debug                                                        |              | Processing Unit                          |

| Z8681        | ROMless                                                            | Z8010 MMU    | Memory Management Unit                   |

|              |                                                                    | Z8015 PMMU   | Paged Memory Management Unit             |

|              | 8-bit Single Chip Microcomputer,                                   | Z8030 Z-SCC  | Serial Communications Controller         |

| Z8610 FAMILY | 4K Bytes ROM and 144 Bytes RAM                                     | 28036 Z-CIO  | Counter Timer and I/O                    |

|              |                                                                    | Z8038 Z-FIO  | FIFO I/O Interface                       |

| Z8610        | Mask Programmed                                                    | Z8052 Z-CRIC | CRI Controller                           |

| Z8612        | Development Package                                                | Z8060 Z-FIF0 | FIFO Buffer and FIO Expander             |

| Z8613        | Protopack                                                          | Z8065 Z-BEP  | Burst Error Processor                    |

|              |                                                                    | Z8068 Z-DCP  | Data Ciphering Processor                 |

|              | 8-bit General Purpose                                              | Z8090 Z-UPC  | Universal Peripheral Controller          |

| Z80 FAMILY   | Microprocessor                                                     |              |                                          |

|              |                                                                    | Z8500 FAMILY | Universal Peripherals                    |

| Z8400 CPU    | CPU                                                                |              |                                          |

| Z8410 DMA    | Direct Memory Access                                               | Z8530 SCC    | Serial Communications Controller         |

| Z8420 PIO    | Parallel I/O Controller                                            | Z8536 CIO    | Counter Timer and I/O                    |

| Z8430 CTC    | Counter Timer Circuit                                              | Z8590 UPC    | Universal Peripheral Controller          |

| Z8440 SIO    | Serial I/O Controller                                              |              |                                          |

| Z8449 SIO/9  | Serial I/O Controller                                              | Z6000 FAMILY | Microprocessor Memories                  |

| Z8470 DART   | Dual Asynchronous                                                  |              |                                          |

|              | Receiver/Transmitter                                               | Z6132        | Quasi-Static RAM                         |

## **Table of Contents**

| Z8 Single-Chip Microcomputer Family                                               |       | 1 |

|-----------------------------------------------------------------------------------|-------|---|

| Advanced Architecture of the Z8 Microcomputer                                     | 1-3   | • |

| A Comparison of MCU Units                                                         | 1-15  |   |

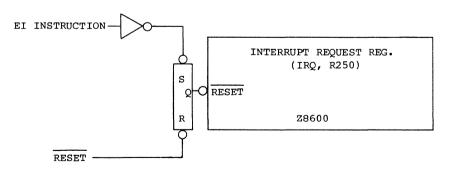

| Z8600 Interrupt Request Register                                                  | 1-29  |   |

|                                                                                   | 1-31  |   |

| 12-Bit Addressing with the Z8600 Family                                           |       |   |

| 28 Family Software Framing Error Detection                                        | 1-33  |   |

| A Programmer's Guide to the Z8 Microcomputer                                      | 1-35  |   |

| Z80 8-Bit Microprocessor Family                                                   |       | 2 |

| Get Powerful Microprocessor Performance                                           | 2-2   |   |

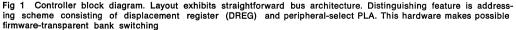

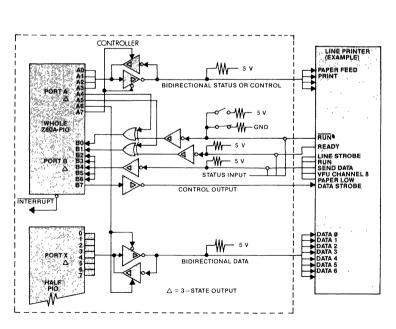

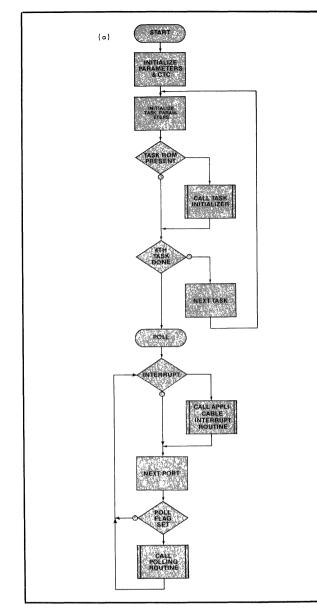

| Designing a Microprocessor Driven Multipurpose Peripheral Controller              | 2-13  |   |

| Z80 Family Interrupt Structure                                                    | 2-23  |   |

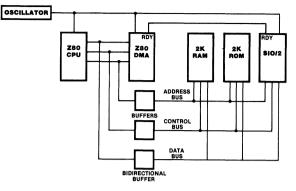

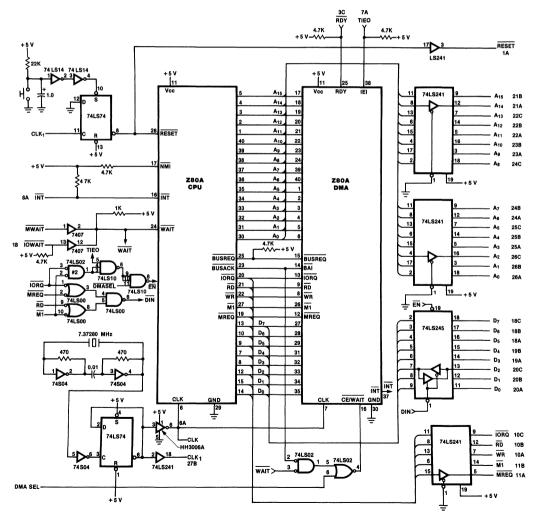

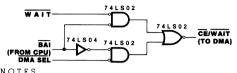

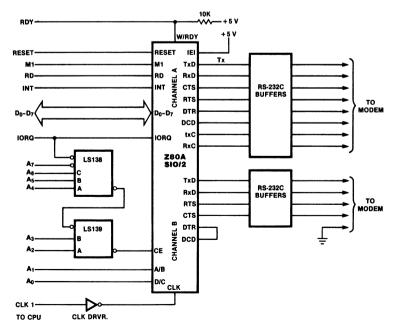

| A Z80-Based System Using the DMA with SIO                                         | 2-35  |   |

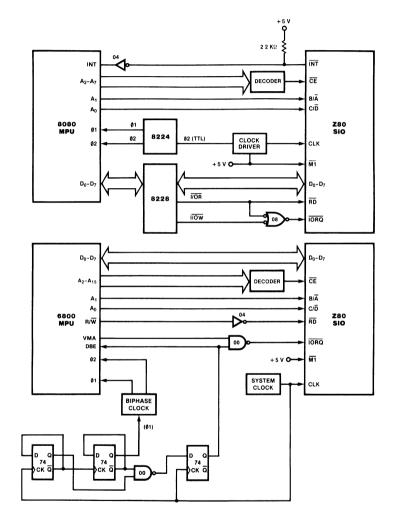

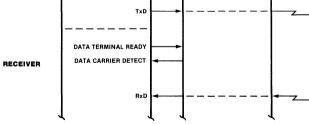

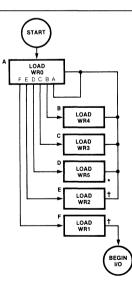

| Using the Z80 SIO in Asynchronous Communications                                  | 2-47  |   |

| Using the Z80 with SDLC                                                           | 2-71  |   |

| Binary Synchronous Communication Using the Z80 SID                                | 2-83  |   |

| Serial Communication with the Z80A DART                                           | 2-87  |   |

|                                                                                   | 2-97  |   |

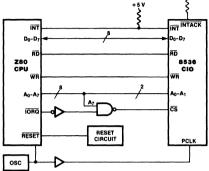

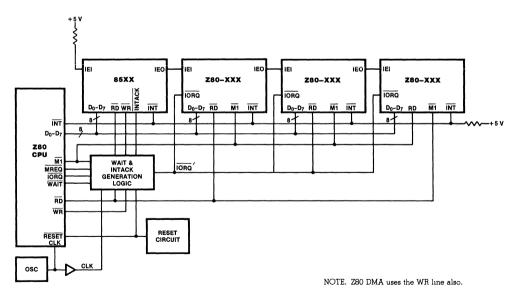

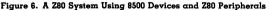

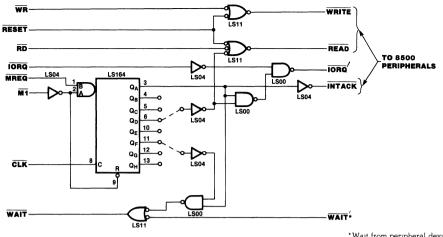

| Interfacing 8500 Peripherals to the Z80                                           |       |   |

| Serial Clock Generation Using the Z8536 CIO                                       | 2-103 |   |

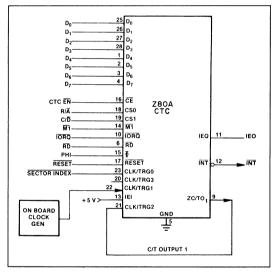

| Timing in an Interrupt-Based System with the Z80 CTC                              | 2-107 |   |

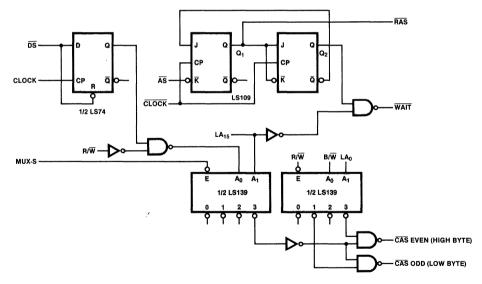

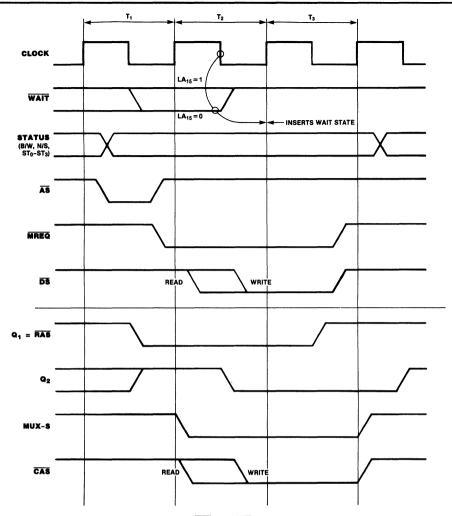

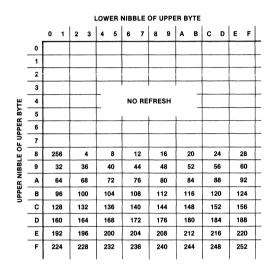

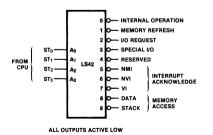

| Interfacing 16-Pin Dynamic RAMs to the Z80A Microprocessor                        | 2-119 |   |

| Controlling Z80 Microcomputer I/O? An Interrupt-Driven Program Could Help         | 2-147 |   |

| Z8000 16-Bit Microprocessor                                                       |       | 3 |

| Advanced Architectural Features of the Z8000 CPU                                  | 3-3   |   |

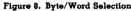

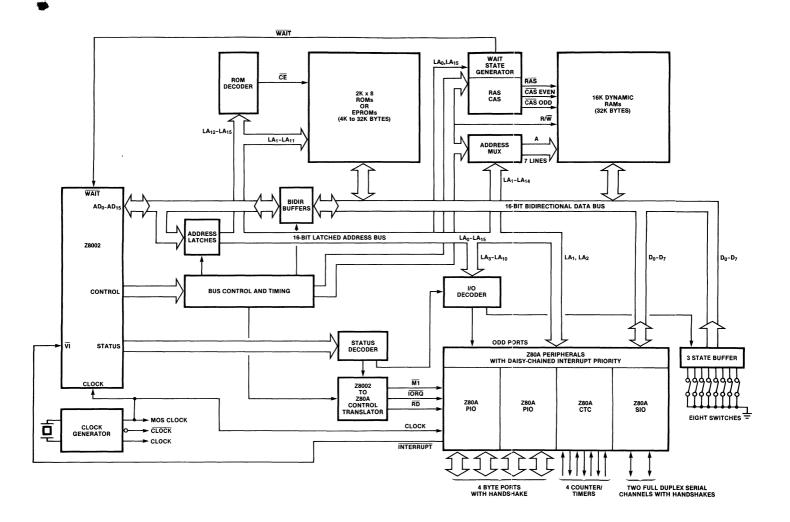

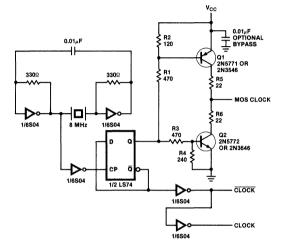

| A Small Z8000 System                                                              | 3-17  |   |

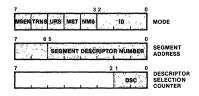

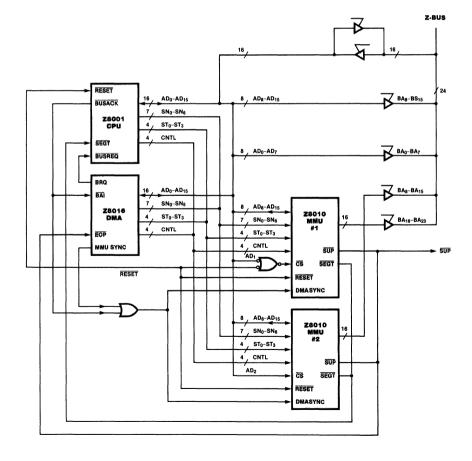

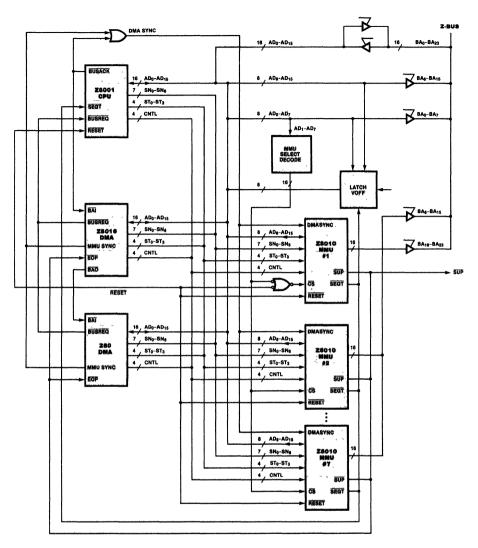

| An Introduction to the Z8010 MMU Memory Management Unit                           | 3-29  |   |

| An Introduction to Memory Management                                              | 3-49  |   |

| The Z8000 and the 68000 Concept Papers: Introduction                              | 3-57  |   |

| Z8000 vs 68000 Register Architecture                                              | 3-59  |   |

| Memory-Mapped vs Explicit I/O                                                     | 3-61  |   |

|                                                                                   |       |   |

| Address/Data Bus                                                                  | 3-63  |   |

| Segmented vs Linear Addressing                                                    | 3-65  |   |

| Operating System Support Features                                                 | 3-75  |   |

| A Tale of Four Microprocessors: Benchmarks Quantify Performance                   | 3-85  |   |

| Architectural Concepts for Microprocessor Peripheral Families                     | 3-105 |   |

| Z-Family Memories                                                                 |       | 4 |

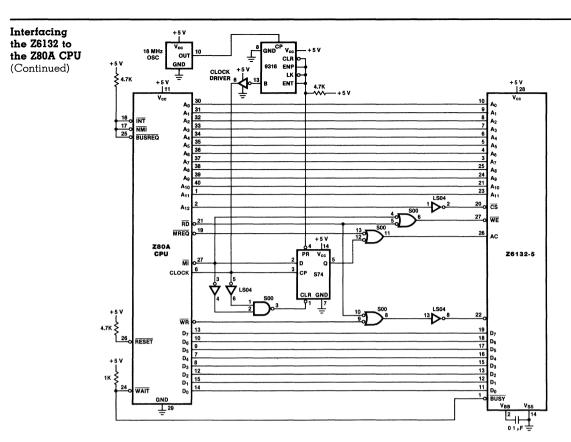

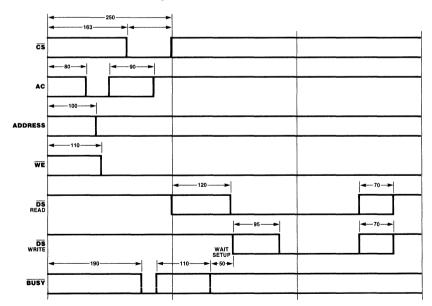

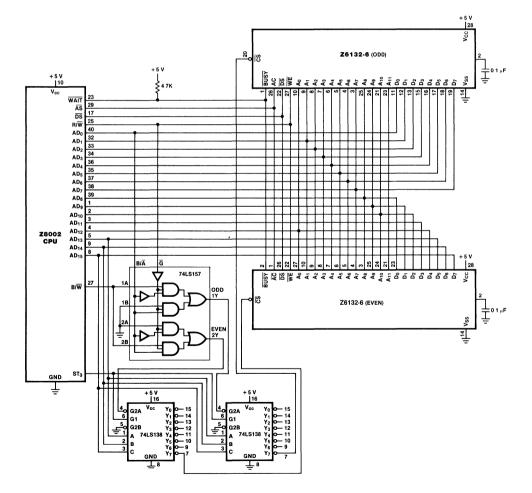

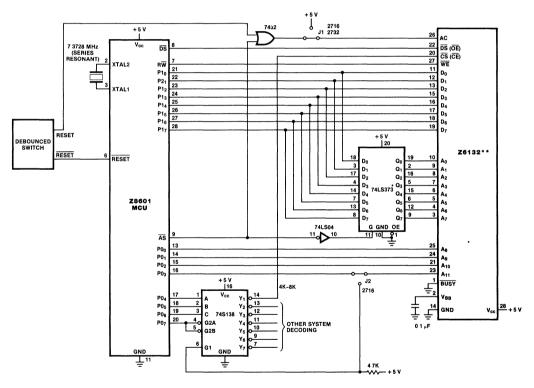

| Interfacing the Z6132 Intelligent Memory                                          | 4-3   |   |

| Z-BUS                                                                             |       | 5 |

| Z-BUS Component Interconnect                                                      | 5-3   | , |

|                                                                                   |       |   |

| Z-BUS and Peripheral Support Packages Tie Distributed Computer Systems Together . | 5-19  |   |

| General                                                                           |       | 6 |

| An Optimizing Driver for NEC Spinwriters and Diablo Printers                      | 6-3   |   |

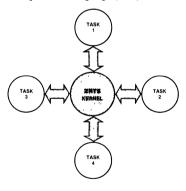

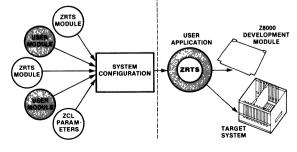

| ZRIS 8000 Zilog Real-Time Software for the Z8000 Microprocessor                   | 6-61  |   |

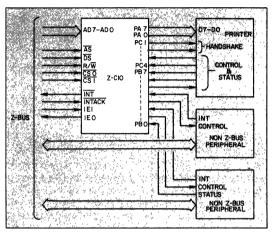

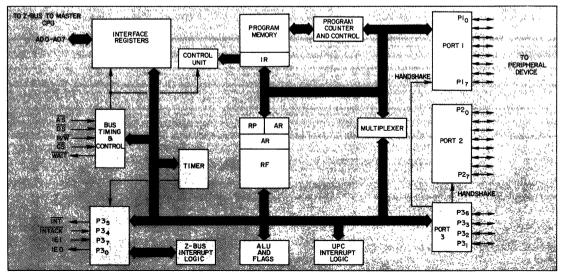

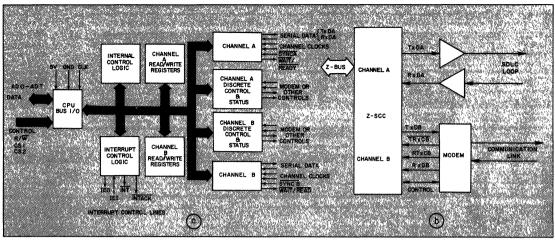

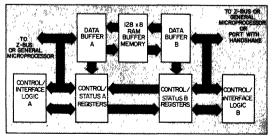

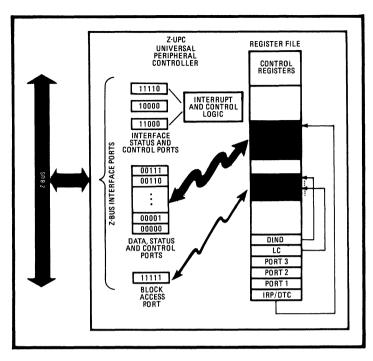

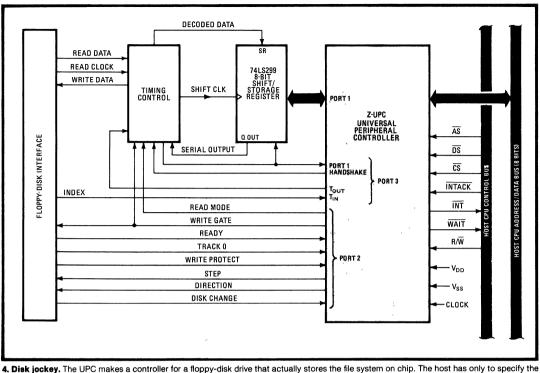

| Peripheral Controller Chip Ties into 8- and 16-Bit Systems                        | 6-65  |   |

| Adapting Unix to a 16-Bit Microcomputer                                           | 6-71  |   |

| Major Firms Join Unix Parade                                                      | 6-77  |   |

1

**Z8<sup>m</sup>Single Chip Microcomputer Family**

-*7*. Zi log

## The Advanced Architectural Features of the Z8 Microcomputer

Stephen Walters Manager of Component Applications Zilog, Inc. 10460 Bubb Road Cupertino, CA 95014

#### INTRODUCTION

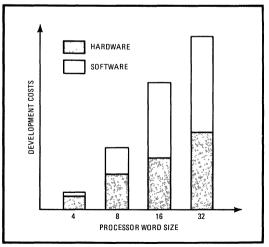

The semiconductor industry accomplished dramatic technological advances in the area of MOS integrated circuit microprocessors during the 1970's, and as the next decade begins two trends are very clear. The first is the continued increased capability of the high-end general purpose microprocessors. Sixteen bit microprocessors will mature with additional "big machine" features, and 32-bit microprocessors will develop.

The second trend is in the area of single chip microcomputers. Single chip microcomputers are offering substantially greater processing power than when they were first introduced. Microcomputers are no longer limited to low end applications where unit cost and power dissipation are the primary design considerations.

Zilog is applying classical computer architecture concepts to the design of its microcomputer products. Upon close examination of the Zilog Z8 Microcomputer, one notices features that once were available only on general purpose bus oriented microprocessor products such as;

- separate program and data space

- the stack pointer and the PUSH and POP instructions

- 126K byte total memory address space

- vectored interrupts

- the CALL and RET (Return) instrucions for procedure calls.

The trend in high-end single chip microcomputer architecture is clear and the consequences are obvious. The multi-chip solutions of today that employ 8-bit general purpose microprocessors will be replaced by more powerful 8-bit or 16bit single chip microcomputers in the future.

This paper will discuss the architectural teatures of the Z8 Microcomputer and describe an application of the Z8 that takes advantage of the off chip expansion capability. ARCHITECTURAL OVERVIEW

The architecture of the Z8 microcomputer offers many advanced processing features not previously available with single chip microcomputers. The Z8 combines a powertul instruction set, simplified system expansion off chip, and tlexible serial and parallel I/O capabilities to provide design solutions for a wide range of application problems.

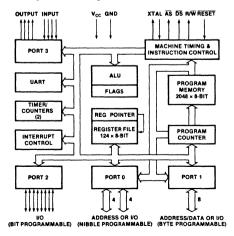

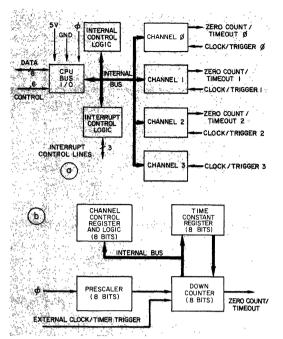

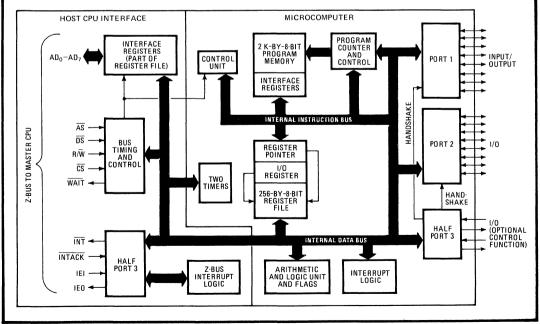

The Z8 has a 16-bit Program Counter and a separate 16-bit Stack Pointer. The memory space may be extended beyond the 2K bytes of ROM and 124 bytes of RAM on chip, up to 126K bytes of program and data memory. There are 32 bits of I/O which can be configured into a variety of bit, nibble, and byte organizations, and the serial I/O port is a complete full duplex asynchronous receiver/transmitter. The Z8 interrupt structure allows the user to mask and prioritize the interrupt functions under program control, and the interrupts are directed to the appropriate service routine through 16-bit vectors in the first 12 locations of program memory. Two counter/timers are provided to off load time base generation and interval detection tasks from the Z8. The Z8 will operate with an 8 MHz clock and the exact frequency up to 8 MHz may be set with an external crystal, an external RC, or an external clock source. The Z8 operates from a single 5 volt power supply and offers a power down mode that allows the 124 general purpose registers on chip to operate from a back up battery. A Block Diagram of the Z8 is given in Figure 1.

Figure 1 Z8 Block Diagram

1-3

#### MEMORY SPACE AND REGISTER

#### ORGANIZATION

#### Memory Space

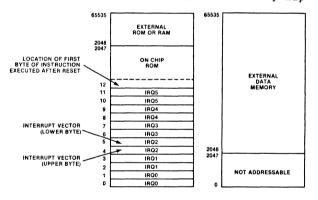

The Z8 can address up to 126K bytes of program and data memory separately from the on chip registers. The 16-bit program counter provides for 64K bytes of program memory, the first 2K bytes of which are internal to the Z8. The remaining 62K bytes of program memory are located externally and can be implemented with ROM, EPROM, or RAM.

The 62K bytes of data memory are also located external to the Z8 and begin with location 2048. The two address spaces, program memory and data memory, are individually selected by the Data Memory Select output (DM) which is available from **Port** 3.

The Program Memory Map and the Data Memory Map are shown in Figure 2.

Program Memory Map Data Memory Map

Figure 2 Program Memory Map And Data Memory Map

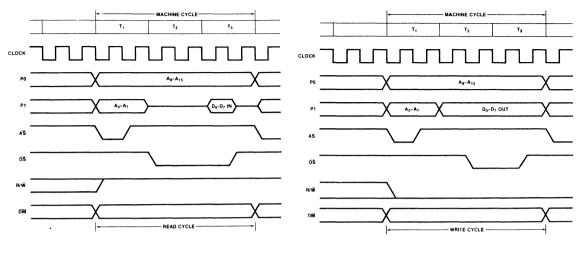

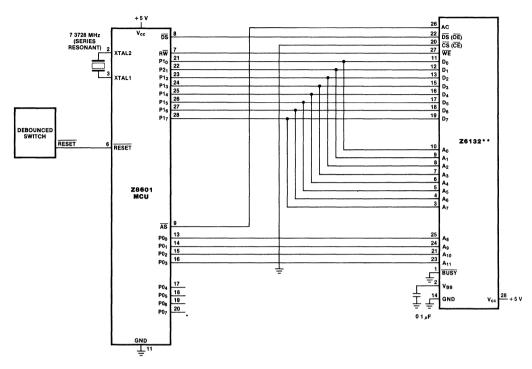

External memory access is accomplished by the Z8 through its I/O Ports. When less than 256 bytes of external memory are required, Port 1 is programmed for the multiplexed address/data mode (ADØ-AD7). In this configuration 8-bits of address and 8-bits of data are time multiplexed on the 8 I/O lines for memory transfers. The memory "handshake" control lines are provided by the Address Strobe (AS), Data Strobe (DS), and the Read/Write (R/W) pins on the Z8. If program and data are included in the external memory space, the Data Memory Select (DM) function may be programmed into the Port 3 Mode register. When this is done, the IM signal is available on line 4 of the Port 3 (P34) to select between program and data memory for external memory operations.

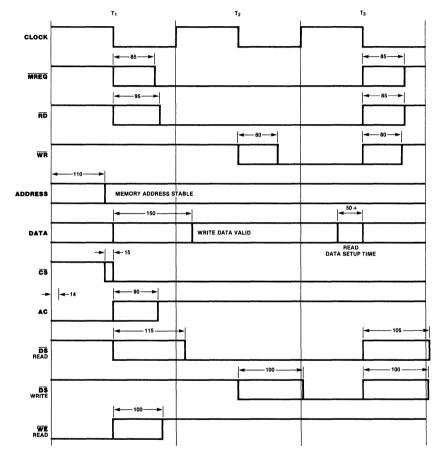

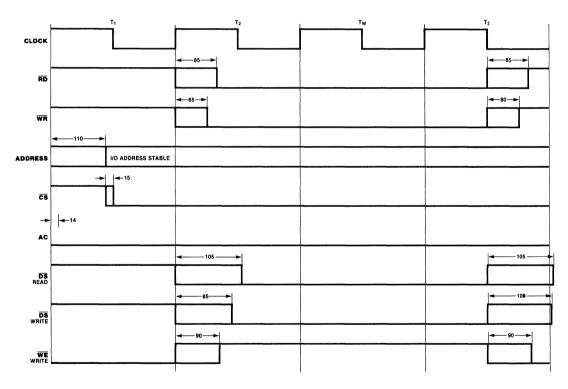

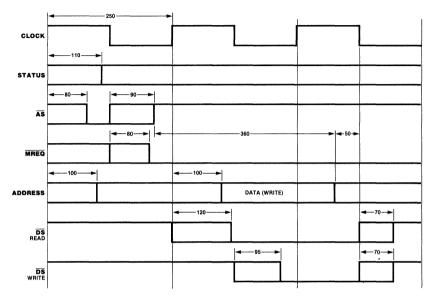

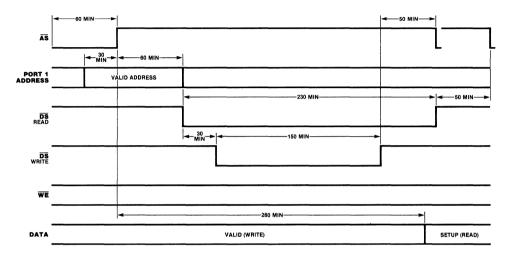

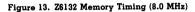

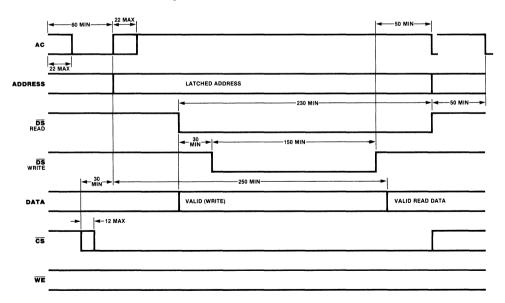

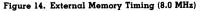

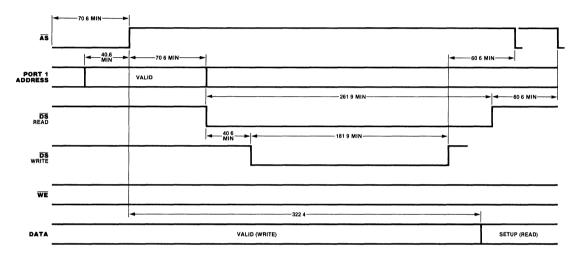

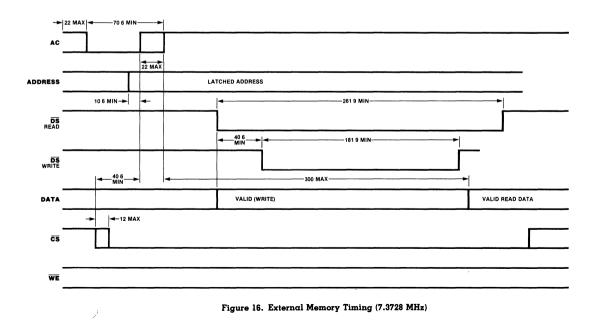

Port 0 is used to provide the additional address bits for external memory beyond the first 256 locations up to a full 16-bits of external memory address. It becomes immediately obvious that the first 8-bits of external memory address from Port 1 must be latched externally to the Z8 so that program or data may be transferred over the same 8 lines during the external memory transaction machine cycle. The AS, DS, and R/W control lines simplify the required interface logic. The timing for external memory transactions is given in Figure 3.

#### Registers

The Z8 has 144 8-bit registers including four Port registers (RO-R3), 124 general purpose registers (R4-R127), and 16 control and status register (R240-R255). The 144 registers are all located in the same 8-bit address space to allow any Z8 instruction to operate on them. The 124 general purpose registers can function as accumulators, address pointers, or index registers. The registers are read when they are referenced as source registers, and written when they are referenced as destination registers. Registers may be addressed directly with an 8-bit address, or indirectly through another register with an 8-bit address, or with a 4-bit address and Register Pointer.

The entire Z8 register space may be divided into 16 contiguous Working Register Areas, each having 16 registers. A control register, called the Register Pointer, may be loaded with the most significant nibble of a Working Register Area address. The Register Pointer provides for the selection of the Working Register Area, and allows registers within that area to be selected with a 4-bit address.

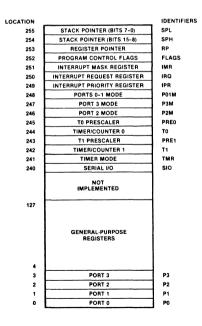

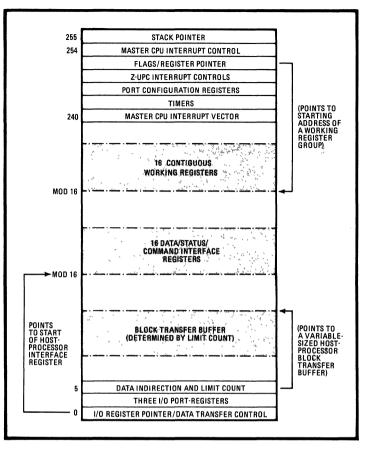

The Z8 register organization is shown in Figure 4.

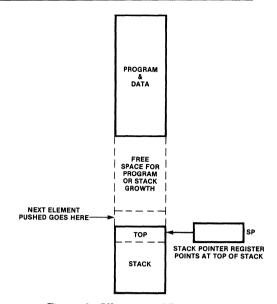

#### Stacks

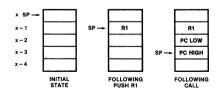

The Z8 provides for stack operations through the use of a stack pointer, and the stack may be located in the internal register space or in the external data memory space. The "stack selection" bit (D2) in the Port 0-1 Mode control register selects an internal or external stack. When the stack is located internally, register 255 contains an 8-bit stack pointer and register 254 is available as a general purpose register. If an external stack is used, register 255 or registers 254 and 255 may be used as the stack pointer depending on the anticipated "depth" of the stack. When registers 254 and 255 are both used, the stack pointer is a full 16-bits wide. The CALL, IRET, RET, PUSH, and

Memory Read Cycle

Memory Write Cycle

## External Memory Transaction Cycle Figure 3

Figure 4 Register File Organization

POP instructions are Z8 instructions which include implicit stack operations.

#### I/O STRUCTURE

#### Parallel I/O

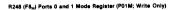

The Z8 microcomputer has 32 lines of I/O arranged as four 8-bit ports. All of the I/O ports are TTL compatible and are configurable as input, output, input/output, or address/data. The handshake control lines for Ports 0, 1, and 2 are bits from Port 3 that have been programmed through a Mode control register, except for  $\overline{AS}$ ,  $\overline{DS}$ , and R/W which are available as separate 28 pins. The I/O ports are accessed as separate internal registers by the Z8. Ports 0 and 1 share one Mode control register, and Ports 2 and 3 each have a Mode control register for configuring the port.

Port 0 can be programmed to be an I/O port or as an address output port. More specifically Port 0 can be configured to be an 8-bit I/O port, or a 4-bit address output port (A8-A11) for external memory and one 4-bit I/O port, or an 8-bit address output port (A8-A15) for external memory.

Port 1 can be programmed as an I/O port (with or without handshake), or an address/data port (ADØ-AD7) for interfacing with external memory. If Port 1 is programmed to be an address/data port, it cannot be accessed as a register.

Port 2 can be configured as individual input or output bits, and Port 3 can be programmed to be parallel I/O bits, and/or serial I/O bits, and/or handshake control lines for the other ports. Figure 5 shows the port Mode registers.

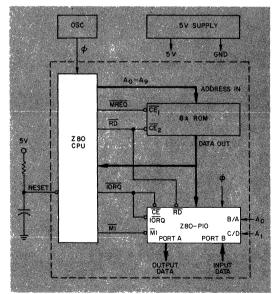

The off chip expansion capability using Ports 0 and 1 offers the added feature of being Z-Bus compatible. All Z-Bus compatible peripheral chips that are available now, and will be available in the future, will interface directly with the 28 multiplexed address/data bus.

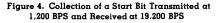

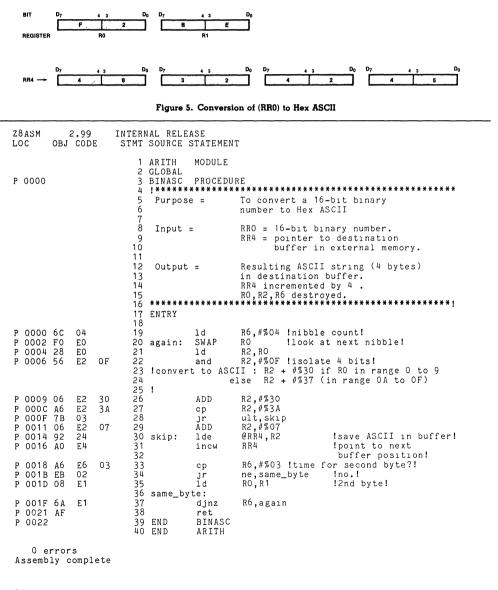

#### Serial I/O

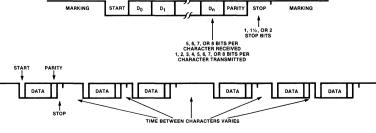

As memtioned in the last section, Port 3 can be programmed to be a serial I/O port with bits 0 and 7, the serial input and serial output lines respectively. The serial I/O capability provides for full duplex asynchronous serial data at rates up to 62.5K bits per second. The transmitted format is one start bit, eight data bits including odd parity (if parity is enabled), and two stop bits. The received data format is one start bit, eight data bits and at least one stop bit. If parity is enabled, the eighth data bit received (bit 7) is replaced by a parity error flag which indicates a parity error if it is set to a ONE.

Timer/Counter  $T_0$  is the baud rate generator and runs at 16 times<sup>0</sup> the serial data bit rate. The receiver is double duffered and an internal interrupt (IRQ3) is generated when a character is loaded into the receive buffer register. A different internal interrupt (IRQ4) is generated when a character is transmitted.

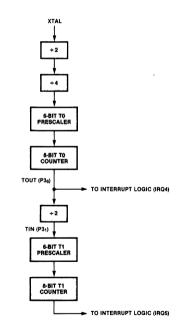

#### COUNTER/TIMERS

The 28 has two 8-bit programmable counter/ timers, each of which is driven by a programmable 6-bit prescaler. The T<sub>1</sub> prescaler can be driven by internal or external clock sources, and the T<sub>0</sub> prescaler is driven by the internal clock only. The two prescalers and the two counters are loaded through four control registers (see Figure 4) and when a counter/timer reaches the "end of count" a timer interrupt is generated (IRQ4 for T<sub>1</sub>, and IRQ5 for T<sub>1</sub>). The counter/timers can be programmed to stop upon reaching the end of count, or to reload and continue counting. Since either counter (one at a time) can have its output available external to the 28, and Counter/Timer T<sub>1</sub> can have an external input, the two counters can be cascaded.

Port 3 can be programmed to provide timer outputs for external time base generation or trigger pulses.

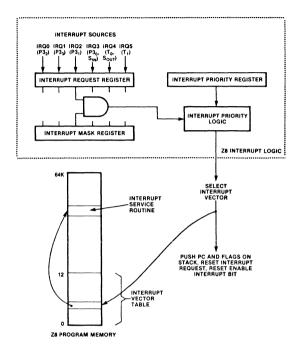

#### INTERRUPT STRUCTURE

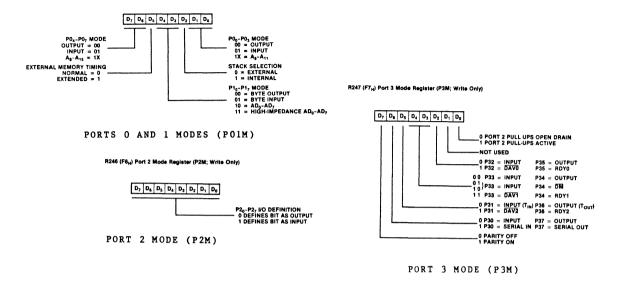

The Z8 provides for six interrupts from eight different sources including four Port 3 lines (P30-P33), serial in, serial out, and two counter/timers. These interrupts can be masked and prioritized using the Interrupt Mask Register (register 251) and the Interrupt Priority Register (register 249). All interrupts can be disabled with the master interrupt enable bit in the Interrupt Mask Register.

Each of the six interrupts has a 16-bit interrupt vector that points to its interrupt service routine. These six 2-byte vectors are placed in the first twelve locations in the program memory space (see Figure 2).

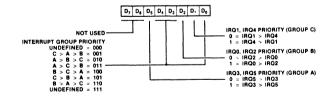

When simultaneous interrupts occur for enabled interrupt sources, the Interrupt Priority Register determines which interrupt is serviced first. The priority is programmable in a way that 1s described by Figure 6.

When an interrupt is recognized by the Z8, all other interrupts are disabled, the program counter and program control flags are saved, and the program counter is loaded with the corresponding interrupt vector. Interrupts must be re-enabled by the user upon entering the service

Figure 5 Port Mode Registers

## R249 INTERRUPT PRIORITY REGISTER (IPR)

Figure 6

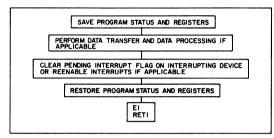

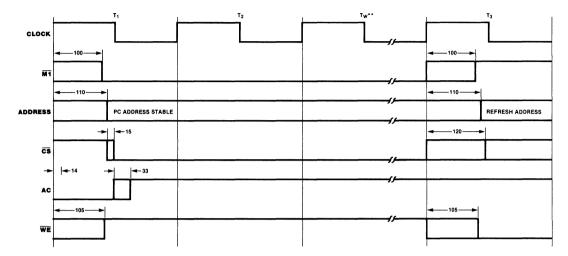

routine (for nested interrupts), or upon returning from the interrupt service routine using the IRET instruction. The interrupt cycle process is shown in Figure 7.

Figure 7 Interrupt Cycle Process

#### INSTRUCTION SET

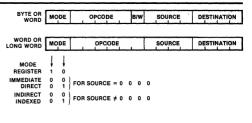

The Z8 uses six address modes; Register, Indirect Register, Indexed, Direct, Relative, and Immediate. The Register mode refers to a register for operands. The Indirect Register mode refers indirectly through a register to an operand in a second register; indirectly through a register pair to an operand in program memory; or indirectly through a register pair to an operand in data memory. The Indexed mode is used only by the Load (LD) instruction and provides a method for generating an effective address which is the sum of a register address (contained in the instruction) and the content of the index register. The Indexed mode employs Working Register area shortened notation for specifying the Index register. The Direct mode provides for a transfer of control to anywhere in program memory with a two byte address in the instruction. The Relative mode is used only with the Jump Relative, and Decrement And Jump instructions. The relative offset contained in the instruction allows a jump to an address

which is-128 locations or +127 locations from the address of the instruction following the jump instruction. The Immediate mode provides the operand in the instruction.

There are eight instruction functional groups;

| Load            | Bit Manipulation |

|-----------------|------------------|

| Arithmetic      | Block Transfer   |

| Logical         | Rotate and Shift |

| Program Control | CPU Control      |

A summary of the Z8 instructions by function is given in Appendix A.

The Z8 addressing modes are optimized for using the internal ROM and RAM memories. Two of the reasons why this was done were; to improve code density (fewer bytes per instruction), and to reduce execution time.

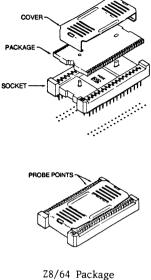

#### THE Z8 FAMILY

The Z8 family emerged with three versions of the basic microcomputer; the 40-pin ROM version, the 40-pin EPROM version, and the 64-pin version. The 40-pin EPROM version is offered in a Zilog proprietary package called a Protopak (see Figure 8), that has a socket for an EPROM mounted permanently on top of a 40-pin DIP. This device will plug directly into the socket of a product designed for the ROM version, or can be the initial production component for a product that may ultimately be converted to the ROM version of the Z8. The 64pin version has no internal ROM and comes in a 64-pin leadless chip carrier (see figure 9). The eleven ROM address lines and eight ROM data lines are brought to pins on this version of the Z8. A 4K ROM version of the Z8 is planned for release toward the end of 1980.

Z8 Protopak Figure 8

28/64 Package Figure 9

#### **Z8 APPLICATION**

Typeset Innovations, Inc. is a company based in Austin, Texas, that has designed a graphics computing system based on the Z8 microcomputer. The ProGrafix is a specialized electronic computational aid for use by graphics arts professionals in the sizing and pricing of graphic elements. Graphics arts professionals are exemplified by typesetting job estimators, typographers, graphic designers, printers, advertising layout artists, and book and magazine designers.

Graphic artists have in the past performed copyfitting through trial and error. With the increasing costs of graphics materials, the trial and error method has become a noticable expense that can be minimized with a more accurate copyfitting technique.

The ProGrafix performs the following functions;

Entry and display of values in the units of measurement which are commonly used in the typographical arts, including:

> picas points picas and points inches

ciceros didots cieros and didots centimeters

relative units

- Instantaneous, one keystroke conversion of values between any of the above units of measurement.

- Arithmetic operations using values which are expressed in any of the above units of measurement.

- One keystroke execution of an extremely accurate copyfitting algorithm which finds any unknown copyfitting value after the five known ones have been entered, from among the following copy descriptors:

width depth size leading type style density character count

Graphic proportional enlargement/ reduction computations by finding any one of the following values after the other two are entered:

> original size reproduction size enlargement/reduction ratio

• Memory storage and recall of intermediate results, pricing constants, and other user-created values.

When final packaging is complete the Pro-Grafix will appear similar to the drawing shown in Figure 10. The computational aid will have an 8 digit display, 7 annunciator LED's to indicate measurement units, an on/off switch, and a 40 key keyboard matrix. The key functions are defined in Table 1.

When Typeset Innovations began the design of the ProGrafix early in 1980, they looked for a microcomputer that had the following characteristics;

- A real (available) microcomputer powerful enough to do the job

- Compact coding

- Fast

- Easy to program

- External expansion of memory and I/O

1-9

ProGrafix Computational Aid Figure 10

The Z8 offered all of these characteristics and more. By the second quarter of 1980, the Pro-Grafix prototypes were working.

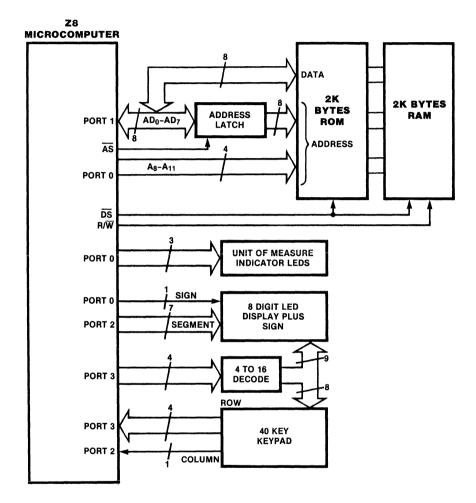

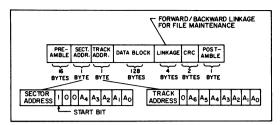

The prototype implementation is shown in Figure 11. External ROM and RAM were added using Port 1 and half of Port 0 (A8-A11). The ability to add more than 2K bytes of external memory with only 12 address lines (A0-A11) is possible because the Data Strobe (DS) line is only active when locations above the first 2K bytes are accessed. Memory locations from 0 to 2K bytes are internal to the Z8; locations from 2K bytes to 4K bytes (ROM) are external to the Z8 and selected by address line Al1=1 and DS; and locations from 4K bytes to 6K bytes (RAM) are external to the Z8 and selected by address line Al1 = 0 and DS active.

The remaining four bits of Port 0 were used to drive the Unit of Measure LED's and the "sign" for the numeric display.

Four of the I/O lines available from Port 3 were used to select one of eight digits on the numeric display through a 4 to 16 decoder and to scan the rows of the keypad. The other four I/O lines were used to read back the columns from the keypad.

One line from Port 2 was used for the fifth column input to the Z8 from the 40 key keypad. The remaining 7 I/O lines available from Port 2 were used for segment select on the numeric display.

The numeric display is "scan refreshed" by the Z8 at a rate that is approximately 100 times per second. As the digits of the display are being refreshed the keypad is scanned as a matrix of 8 by 5 keys. The counter/timers on the Z8 are both used; one to time the display refresh, and the other as a timer for keypad debounce. An external stack is used for temporary variable storage and during the servicing of interrupts. Only two Z8 interrupts are used by the ProGrafix, one for the display refresh counter and the other for the key debounce timer.

The development of the software for the ProGrafix, which included a BCD Floating Point package, was done on a Zilog development system with the Z8 PLZ/ASM assembler. The object code was down loaded to a Z8 Development Module (DM) where the hardware was initially debugged. The external memory was added to the Z8DM in the space provided for wire wrap. When the system was 90% - 95% debugged, a prototype circuit board was built and the Z8 in a Protopak package with an EPRCM was used for final system debug.

The production version of the ProGrafix will use an LCD numeric display instead of the LED display. This will make additional address lines available for expanding off chip memory. In addition, a printer option is planned that will connect to the serial port of the Z8.

The ProGrafix is expected to sell for under \$500 without a printer and under \$750 with a printer. The availability of the ProGrafix has been targeted for May of 1981.

The configuration of the ProGrafix computational aid around the Z8 provided a very flexible and powerful microcomputer system that can be expanded to accomodate a wide variety of applications by simply changing the software. Typeset Innovations is currently looking for other products that can be implemented with the hardware that was developed for the ProGrafix.

#### CONCLUSION

The 28 represents the coming of age of the more powerful microcomputers. While the 28 can be a cost effective design solution for low end applications, it can also be expanded to attack much more sophisticated design problems. The architecture of the 28 was designed in a forward looking manner, and the integration of more capability onto the same chip is now limited only by the constraints of the integrated circuit technology.

#### ProGrafix Key Functions

Key 10 designated as C clears display register X and the operand register Y.

Key 11 designated as CE, the clear-entry function, clears only the last value entered into display register X.

Key 12 designated as RECALL enters the contents of a designated memory register 0 through 9 into register X and into the display.

Key 13 designated STORE stores display register X into memory registers 0 through 9, and into the parameter registers.

Key 14 designated as ORIG which is used to store or recall the value of the original size parameter in the proportional sizing algorithm.

Key 15 designated as WIDTH which is used to store or recall the value of the width (line length) parameter of the copyfitting algorithm.

Key 16 designated as PICA which provides for the function of entering information in picas and points and for converting information on the display into either picas and points or decimal picas.

Key 17 designated as CICERO which provides for the function of entering information in ciceros and for converting information on the display into either ciceros and didots or decimal ciceros.

Key 18 designated as REL-UN which provides for the function of entering information in relative units and for converting information on the display into relative units.

Key 19 designated as REPRO which is used to store or recall the value of the reproduction size parameter in the proportional sizing algorithm.

Key 20 designated as DEPTH which is used to store or recall the value of the depth (vertical measure) parameter of the copyfitting algorithm.

Key 21 designated as POINT which provides for the function of entering information in points and for converting the information on the display into points.

Key 22 designated as DIDOT which provides for the function of entering information in didot points and for converting the information on the display into didot points.

Key 23 designated as RU/EM which is used to store or recall of the relative units per em space parameter.

Key 24 designated as RATIO which is used to store or recall the value of the ratio parameter in the proportional sizing algorithm. Key 25 designated as SIZE which is used to store or recall the value of the type size parameter for the copyfitting algorithm and for the relative units conversion algorithm.

Key 26 designated as INCH which provides for the function of entering information in inches and for converting the information on the display into inches.

Key 27 designated as CM which provides for the dual function of entering information in centimeters, and for converting the information on the display into centimeters.

Key 28 designated as "double arrow" interchanges the contents of display register X and operand register Y.

Key 29 designated as '/. (the divide sign) divides operand register Y by display register X.

Key 30 designated as LEAD which is used to store or recall the value of the leading (line spacing) parameter of the copyfitting algorithm.

Key 31 designated as x multiples display register X by operand register Y.

Key 32 designated as DENSITY which is used to store or recall the value of the type style density parameter of the copyfitting algorithm.

Key 33 designated as + adds display register X to operand register Y.

Key 34 designated as CHAR which is used to store or recall the value of the character count parameter of the copyfitting algorithm.

Key 35 designated as - subtracts display register X from operand register Y.

Key 36 designated as FIND invokes the calculation of an unknown copyfitting parameter given five known copyfitting parameters. This key is also used to solve for an unknown proportional sizing parameter given two known proportional sizing parameters.

Key 37 designated . is used to enter the decimal point of a floating-point number.

Key 38 designated as +/- reverses the sign of the value in display register X.

Key 39 designated as = invokes the last entered arithmetic operation using the X and Y registers as operands and places the result in display register X.

Key 40 designated as ON/OFF powers the microcomputer system on and off.

Ś

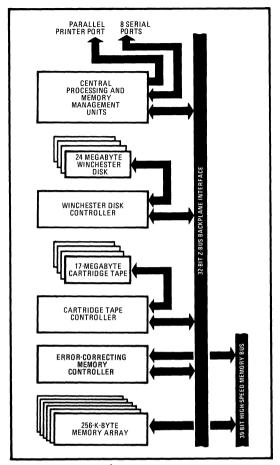

PROGRAFIX BLOCK DIAGRAM Figure 11

## APPENDIX A

Z8 Instruction Set: Functional Groups

## Load Instructions

| Instruction             | Operand (s)                             | Name of<br>Instruction                          |

|-------------------------|-----------------------------------------|-------------------------------------------------|

| CLR<br>LD<br>LDC<br>LDE | dst<br>dst, src<br>dst, src<br>dst, src | Clear<br>Load<br>Load Constant<br>Load External |

| POP<br>PUSH             | dst<br>src                              | Data<br>Pop<br>Push                             |

#### Arithmetic Instructions

| Instruction | Operand (s) | Name of<br>Instruction |

|-------------|-------------|------------------------|

| ADC         | dst, src    | Add With Carry         |

| ADD         | dst, src    | Add                    |

| CP          | dst, src    | Compare                |

| DA          | dst         | Decimal Adjust         |

| DEC         | dst         | Decrement              |

| DECW        | dst         | Decrement Word         |

| INC         | dst         | Increment              |

| INCW        | dst         | Increment Word         |

| SBC         | dst, src    | Subtract With          |

|             |             | Carry                  |

| SUB         | dst, src    | Subtract               |

## Logical Instructions

| Instruction      | Operand (s)                 | Name of<br>Instruction                  |

|------------------|-----------------------------|-----------------------------------------|

| AND<br>Com<br>Or | dst, src<br>dst<br>dst, src | Logical And<br>Complement<br>Logical Or |

| XOR              | dst, src                    | Logical<br>Exclusive<br>Or              |

## Program-Control Instructions

| Instruction     | Operand (s)        | Name of<br>Instruction                   |

|-----------------|--------------------|------------------------------------------|

| CALL<br>DJNZ    | dst<br>r, dst      | Call<br>Decrement and<br>Jump If Nonzero |

| IRET            |                    | Interrupt Return                         |

| JP<br>JR<br>RET | cc, dst<br>cc, dst | Jump<br>Jump Relative<br>Return          |

|                               | APPENDIX A (cont.)             |                                                                                                                                                  |

|-------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|                               | Bit-Manipulation In            | structions                                                                                                                                       |

| Instruction                   | Operands                       | Name of<br>Instruction                                                                                                                           |

| TCM                           | dst, src                       | Test Complement<br>Under Mask                                                                                                                    |

| TM                            | dst, src                       | Test Under Mask                                                                                                                                  |

| AND                           | dst, src                       | Logical And                                                                                                                                      |

| OR                            | dst, src                       | Logical Or                                                                                                                                       |

| XOR                           | dst, src                       | Logical<br>Exclusive<br>Or                                                                                                                       |

|                               | Block-Transfer Inst            | ructions                                                                                                                                         |

| Instruction                   | Operands                       | Name of                                                                                                                                          |

|                               |                                | Instruction                                                                                                                                      |

| LDCI                          | dst, src                       | Load Constant                                                                                                                                    |

|                               |                                | Autoincrement                                                                                                                                    |

| LDEI                          | dst, src                       | Load External                                                                                                                                    |

|                               |                                | Data Auto-<br>increment                                                                                                                          |

| Instruction                   | Operand                        | Name of<br>Instruction                                                                                                                           |

| RL                            | dst                            | Rotate Left                                                                                                                                      |

| RLC                           | dst                            | Rotate Left                                                                                                                                      |

| RR                            | dst                            | Through Carry                                                                                                                                    |

| RRC                           | dst                            | Rotate Right<br>Rotate Right                                                                                                                     |

|                               |                                | Through Carry                                                                                                                                    |

| SRA                           | dst                            | Shift Right                                                                                                                                      |

| SWAP                          | dst                            | Arithmetic<br>Swap Nibbles                                                                                                                       |

|                               |                                | - · · · · · · · · · · · · · · · · · · ·                                                                                                          |

|                               | CPU Control Instruc            | _                                                                                                                                                |

| Instruction                   | CPU Control Instruc<br>Operand | _                                                                                                                                                |

| Instruction<br>CCF            |                                | tions<br>Name of<br>Instruction<br>Complement Carry                                                                                              |

| CCF                           |                                | tions<br>Name of<br>Instruction<br>Complement Carry<br>Flag                                                                                      |

|                               |                                | tions<br>Name of<br>Instruction<br>Complement Carry                                                                                              |

| CCF                           |                                | tions<br>Name of<br>Instruction<br>Complement Carry<br>Flag<br>Disable<br>Interrupts<br>Enable                                                   |

| CCF<br>DI<br>BI               |                                | tions<br>Name of<br>Instruction<br>Complement Carry<br>Flag<br>Disable<br>Interrupts<br>Enable<br>Interrupts                                     |

| CCF<br>DI<br>EI<br>NOP        |                                | tions<br>Name of<br>Instruction<br>Complement Carry<br>Flag<br>Disable<br>Interrupts<br>Enable<br>Interrupts<br>No Operation                     |

| CCF<br>DI<br>EI<br>NOP<br>RCF |                                | tions<br>Name of<br>Instruction<br>Complement Carry<br>Flag<br>Disable<br>Interrupts<br>Enable<br>Interrupts<br>No Operation<br>Reset Carry Flag |

| CCF<br>DI<br>EI<br>NOP        |                                | tions<br>Name of<br>Instruction<br>Complement Carry<br>Flag<br>Disable<br>Interrupts<br>Enable<br>Interrupts                                     |

## 1-14

## **Benchmark Report**

#### MAY 1981

#### INTRODUCTION

The microcomputer industry has recently developed single-chip microcomputers that incorporate on one chip functions previously performed by peripherals. These microcomputer units (MCUs) are aimed at markets requiring a dedicated computer. This report describes and compares the most powerful MCUs in today's market: the Zilog Z8611, the Intel 8051, and the Motorola MC6801. Table 1 lists facts that should be considered when comparing these MCUs.

| FEATURES                                                                  | Zilog<br>Z8611                                 | Intel<br>8051                                | Motorola<br>MC6801                                     |

|---------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------|--------------------------------------------------------|

| On-Chip ROM                                                               | 4K×8                                           | 4K×8                                         | 2K×8                                                   |

| General-Purpose<br>Registers                                              | 124                                            | 128                                          | 128                                                    |

| Special-Function<br>Registers<br>Status/Control<br>I/O ports              | 16<br>4                                        | 16<br>4                                      | 17<br>4                                                |

| <b>I/O</b><br>Parallel lines<br>Ports<br>Handshake                        | 32<br>Four 8-bit<br>Hardware on<br>three ports | 32<br>Four 8-bit<br>None                     | 29<br>Three 8-bit,one 5-bit<br>Hardware on<br>one port |

| Interrupts<br>Source<br>External source<br>Vector<br>Priority<br>Maskable | 8<br>4<br>6<br>48 Programmable<br>orders<br>6  | 5<br>2<br>5<br>2 Programmable<br>orders<br>5 | 7<br>2<br>7<br>Nonprogrammable<br>6                    |

| External<br>Memory                                                        | 120K bytes                                     | 124K bytes                                   | 64K bytes                                              |

| <b>Stack</b><br>Stack pointer<br>Internal stack                           | 16-Bit<br>Yes, uses<br>8-bits                  | 8-Bit<br>Yes                                 | 16-Bit<br>Yes                                          |

| External stack                                                            | Yes                                            | No                                           | Yes                                                    |

#### Table 1. MCU Comparison

## Table 1. MCU Comparison (Continued)

| FEATURES                                                    | Zilog<br>Z8611                                          | Intel<br>8051                                         | Motorola<br>MC6801                                       |

|-------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|

| Counter/                                                    |                                                         |                                                       |                                                          |

| Timers                                                      |                                                         |                                                       |                                                          |

| Counters                                                    | Two 8-bit                                               | Two 16-bit<br>or two 8-bit                            | One 16-bit                                               |

| Prescalers                                                  | Two 6-bit                                               | No prescale<br>with 16-bits;<br>5-bit prescale        | None                                                     |

|                                                             |                                                         | with 8-bits                                           |                                                          |

| Addressing                                                  |                                                         |                                                       |                                                          |

| Modes                                                       |                                                         |                                                       |                                                          |

| Register                                                    | Yes                                                     | Yes                                                   | No                                                       |

| Indirect Register                                           | Yes                                                     |                                                       | No                                                       |

| -                                                           |                                                         | Yes                                                   |                                                          |

| Indexed                                                     | Yes                                                     | Yes                                                   | Yes                                                      |

| Direct                                                      | Yes                                                     | Yes                                                   | Yes                                                      |

| Relative                                                    | Yes                                                     | Yes                                                   | Yes                                                      |

| Immediate                                                   | Yes                                                     | Yes                                                   | Yes                                                      |

| Implied                                                     | Yes                                                     | Yes                                                   | Yes                                                      |

| Index                                                       |                                                         |                                                       |                                                          |

| Registers                                                   | 124, Any                                                | 1, Uses the                                           | 1, Uses                                                  |

| -                                                           | general-                                                | accumulator                                           | 16-bit index                                             |

|                                                             | purpose                                                 | for 8-bit                                             | reqister                                                 |

|                                                             | register                                                | offset                                                |                                                          |

| Serial<br>Communication<br>Interface<br>Full duplex<br>UART | Yes                                                     | Yes                                                   | Yes                                                      |

| Interrupts<br>for transmit                                  | Tes                                                     | Tes                                                   | Tes                                                      |

| and receive<br>Registers                                    | One for each                                            | One for both                                          | One for both                                             |

| Double buffer<br>Serial Data Rate                           | Recelver<br>62.5K b/s<br>@8 MHz<br>93.5K b/s<br>@12 MHz | Receiver<br>187.5K b/s<br>@12 MHz                     | Transmitter/Receiver<br>62.5K b/s<br>@4 MHz              |

| Speed                                                       |                                                         |                                                       |                                                          |

| Instruction                                                 | 1                                                       |                                                       | 1                                                        |

| execution average                                           | 2.2 Usec                                                | 1.5 Usec                                              | 3.9 Usec                                                 |

| 2                                                           | 1.5 Usec @12 MHz                                        |                                                       |                                                          |

| Longest                                                     |                                                         |                                                       | 1                                                        |

| instruction                                                 | 4.25 Usec<br>2.8 Usec @12 MHz                           | 4 Usec                                                | 10 Usec                                                  |

| Clock Frequency                                             | 8 and 12 MHz                                            | 12 MHz                                                | 4 MHz                                                    |

| Power Down<br>Mode                                          | Saves first<br>124 registers                            | Saves fırst<br>128 registers                          | Saves fırst<br>64 registers                              |

| Context<br>Switching                                        | Saves PC<br>and flags                                   | Saves PC;<br>proqrammer<br>must save all<br>registers | Saves PC, PSW,<br>accumulators,<br>and Index<br>register |

#### Table 1. MCU Comparison (Continued)

| FEATURES     | Zilog<br>Z8611                                                           | Intel<br>8051 | Motorola<br>MC6801 |

|--------------|--------------------------------------------------------------------------|---------------|--------------------|

| Development  | 40-Pin<br>Protopack (8613)<br>64-Pin (8612)<br>40-Pin ROMless<br>(Z8681) | 40-Pin (8751) | 40-Pin (68701)     |

| Eprom        | 4K bytes (2732)<br>2K bytes (2716)                                       | 4K bytes      | 2K bytes           |

| Availability | Now                                                                      | ТВА           | Now                |

#### ARCHITECTURAL OVERVIEW

This section examines three chips: the on-chip functions and data areas manipulated by the Zilog, Intel and Motorola MCUs. The three chips have somewhat similar architectures. There are, however, fundamental differences in design criteria. The 8051 and the MC6801 were designed to maintain compatability with older products, whereas the Z8611 design was free from such restrictions and could experiment with new ideas. Because of this, the accumulator architectures of the MC6801 and the 8051 are not as flexible as that of the Z8611, which allows any register to be used as an accumulator.

#### Memory Spaces

The Z8611 CPU manipulates data in four memory spaces:

- 60K bytes of external data memory

- 60K bytes of external program memory

- 4K bytes of internal program memory (ROM)

- 144-byte register file

The 8051 CPU manipulates data in four memory spaces:

- 64K bytes of external data memory

- 60K bytes of external program memory

- 4K bytes of internal program memory

- 148-byte register file

The MC6801 manipulates data in three memory spaces:

- 62K bytes of external memory

- 2K bytes of internal program memory

- 149-byte register file

**On-Chip ROM.** All three chips have internal ROM for program memory. The Z8611 and the 8051 have 4K bytes of internal ROM, and the MC6801 has 2K bytes. In some cases, external memory may be

required with the MC6801 that is not necessary with the Z8611 or the 8051.

**On Chip RAM.** All three chips use internal RAM as registers. These registers are divided into two catagories: general-purpose registers and special function registers (SFRs).

The 124 general-purpose registers in the Z8611 are divided into eight groups of 16 registers each. In the first group, the lowest four registers are the I/O port registers. The other registers are general purpose and can be accessed with an 8-bit address or a short 4-bit address. Using the 4-bit address saves bytes and execution time. Four-bit short addresses are discussed later. The generalpurpose registers can be used as accumulators, address pointers, or Index registers.

The 128 general-purpose registers in the 8051 are grouped into two sets. The lower 32 bytes are allocated as four 8-register banks, and the upper registers are used for the stack or for general purpose. The registers cannot be used for indexing or as address pointers.

The MC6801 also has a 128-byte, general-purpose register bank, which can be used as a stack or as address pointers, but not as Index registers.

As pointed out in Table 1, any of the Z8611 general-purpose registers can be used for indexing; the MC6801 and the 8051 cannot use registers this way. The Z8611 can use any register as an accumulator; the MC6801 and the 8051 have fixed accumulators. The use of registers as memory pointers is very valuable, and only the Z8611 can use its registers in this way.

The number of general-purpose registers on each chip is comparable. However, because of its flexible design, the Z8611 clearly has a more powerful register architecture. The Z8611 has 20 special function registers used for status, control, and I/0. These registers include:

- Two registers for a 16-bit Stack Pointer (SPH, SPL)

- One register used as Register Pointer for working registers (RP)

- One register for the status flags (FLAGS)

- One register for interrupt priority (IPR)

- One register for interrupt mask (IMR)

- One register for interrupt request (IRQ)

- Three mode registers for the four ports (PO1M, P2M, P3M)

- Serial communications port used like a register (SIO)

- Two counter/timer registers (TO, T1)

- One Timer Mode Register (TMR)

- Two prescaler registers (PREO, PRE1)

- Four I/O ports accessed as registers (PORTO, PORT1, PORT2, PORT3)

The 8051 also has 20 special function registers used for status, control, and I/0. They include:

- One register for the Stack Pointer (SP)

- Two accumulators (A,B)

- One register for the Program Status Word (PSW)

- Two registers for pointing to data memory (DPH, DPL)

- Four registers that serve as two 16-bit counter/timers (THO, TH1, TLO, TL1)

- One mode register for the counter/timers (TMOD)

- One control register for the counter/timers (TCDN)

- One register for interrupt enable (IEC)

- One register for interrupt priority (IPC)

- One register for serial communications buffer (SBUF)

- One register for serial communications control (SCON)

- Four registers used as the four I/O ports (PO, P1, P2, P3)

The MC6801 has 21 special function registers used for status, control, and I/0. These include:

- One register for RAM/EROM control

- One serial receive register

- One serial transmit register

- One register for serial control and status

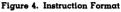

- One serial rate and mode register

- One register for status and control of port 3

- One register for status and control of the timer

- Two registers for the 16-bit timer

- Two registers for 16-bit input capture used with timer

- Two registers for 16-bit output compare used with timer

- Four data direction registers associated with the four I/O ports

- Four I/O ports

The special function registers in the three chips seem comparable in number and function. However, upon closer examination, the SFRs of the MC6801 prove less efficient than those of the Z8611. The MC6801 has five registers associated with the I/O ports, whereas the Z8611 uses only three registers for the same functions. The MC6801 uses four registers to perform the serial communication function, whereas the Z8611 uses only one register and part of another.

The 8051 uses two registers for the accumulators; the Z8611 is not limited by this restriction. The 8051 also uses two registers for the serial communication interface, whereas the Z8611 accomplishes the same job with one register. Another two registers in the 8051 are used for data pointers; these are not necessary in the Z8611 since any register can be used as an address pointer.

The Z8611 uses registers more efficiently than either the MC6801 or the 8051. The registers saved by this optimal design are used to perform the functions needed for enhanced interrupt handling and for register pointing with short addresses. The Z8611 also supplies the extra register required for the external stack. These features are not available on the 8051 or the MC6801.

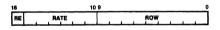

External Memory. All three chips can access external memory. The Z8611 and the 8051 can generate signals used for selecting either program or data memory. The Data Memory strobe (the signal used for selecting data or program memory) gives the Z8611 access to 120K bytes of external memory (60K bytes in both program and data memory). The 8051 can use 124K bytes of external memory (64K bytes of external data memory and 60K bytes of external program memory). The MC6801 can access only 62K bytes of external memory and does not distinguish between program and data memory. Thus, the Z8611 and the 8051 are clearly able to access more external memory than the MC6801.

#### **On-Chip Peripheral Functions**

In addition to the CPU and memory spaces, all chips provide an interrupt system and extensive I/0 facilities including I/0 pins, parallel I/0 ports, a bidirectional address/ data bus, and a serial port for I/0 expansion.

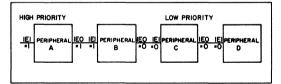

Interrupts. The Z8611 acknowledges interrupts from eight sources, four are external from pins  $IRQ_0-IRQ_3$ , and four are internal from serial-in, serial-out, and the two counter/timers. All interrupts are maskable, and a wide variety of priorities are realized with the Interrupt Mask Register and the Interrupt Priority Registers (see Table 1). All Z8611 interrupts are vectored, with six vectors located in the on-chip ROM. The vectors are fixed locations, two bytes long, that contain the memory address of the service routine. The 8051 acknowledges interrupts from five sources: two external sources (from INTO and INT1) and three internal sources (one from each of the internal counters and one from the serial I/O port). All interrupts can be disabled individually or globally. Each of the five sources can be assigned one of two priorities: high or low. All 8051 interrupts are vectored. There are five fixed locations in memory, each eight bytes long, allocated to servicing the interrupt.

The MC6801 has one external interrupt, one nonmaskable interrupt, an internal interrupt request, and a software interrupt. The internal interrupts are caused by the serial I/O port, timer overflow, timer output compare, and timer input capture. The priority of each interrupt is preset and cannot be changed. The external interrupt can be masked in the Condition Code register. The MC6801 vectors the interrupts to seven fixed addresses in ROM where the 16-bit address of the service routine is located.

When an interrupt occurs in the 8051, only the Program Counter is saved; the user must save the flags, accumulator, and any registers that the interrupt service routine might affect. The MC6801 saves the Program Counter, acumulators, Index register, and the PSW; the user must save all registers that the interrupt service routine might affect. The Z8611 saves the Program Counter and the Flags register. To save the 16 working registers, only the Register Pointer register need be pushed onto the stack and another set of working registers is used for the service routine. For more detail on working registers and interrupt context switching, see the <u>Z8 Technical Manual</u> (03-3047-02).

With regard to interrupts, the Z8611 is clearly superior. The Z8611 requires only one command to save all the working registers, which greatly increases the efficiency of context switching.

**I/O Facilities.** The Z8611 has 32 lines dedicated to I/O functions. These lines are grouped into four ports with eight lines per port. The ports can be configured individually under software control to provide input, output, multiplexed address/data lines, timing, and status. Input and output can be serial or parallel, with or without handshake. One port can be configured for serial transmission and four ports can be configured for parallel transmission. With parallel transmission, ports 0, 1, and 2 can transmit data with the handshake provided by port 3.

The 8051 also has 32 I/O lines grouped together into four ports of eight lines each. The ports can be configured under program control for parallel or serial I/O. The ports can also be configured for multiplexed address/data lines, timing, and status. Handshake is provided by user software.

The MC6801 has 29 lines for I/O (three 8-bit ports and one 5-bit port). One port has two lines for

handshake. The ports provide all the signals needed to control input and output either serially or in parallel, with or without multiplexed address/data lines. They can be used to interface with external memory.

The main differences in I/O facilities are the number of 8-bit ports and the hardware handshake. The Z8611 and the 8051 have four 8-bit ports, whereas the MC6801 has three 8-bit ports and an additional 5-bit port. The Z8611 has hardware handshake on three ports, the MC6801 has hardware handshake on only one port, and the 8051 has no hardware handshake.

**Counter/timers.** The Z8611 has two 8-bit counters and two 6-bit programmable prescalers. One prescaler can be driven internally or externally; the other prescaler is driven internally only. Both timers can interrupt the CPU when counting is completed. The counters can operate in one of two modes: they can count down until interrupted, or they can count down, reload the initial value, and start counting down again (continuously). The counters for the Z8611 can be used for measuring time intervals and pulse widths, generating variable pulse widths, counting events, or generating periodic interrupts.

The 8051 has two 16-bit counter/timers for measuring time intervals and pulse widths, generating pulse widths, counting events, and generating periodic interrupts. The counter/timers have several modes of operation. They can be used as 8-bit counters or timers with two 5-bit programmable prescalers. They can also be used as 16-bit counter/timers. Finally, they can be set as 8-bit modulo-n counters with the reload value held in the high byte of the 16-bit register. An interrupt is generated when the counter/timer has completed counting.

The MC6801 has one 16-bit counter which can be used for pulse-width measurement and generation. The counter/timer actually consists of three 16-bit registers and an 8-bit control/status register. The timer has an input capture register, an output compare register, and a free-running counter. All three 16-bit registers can generate interrupts.

Serial Communications Interface. The Z8611 has a programmable serial communication interface. The chip contains a UART for full-duplex, asynchronous, serial receiver/ transmitter operation. The bit rate is controlled by counter/timer 0 and has a maximum bit rate of 93.500 b/s. An interrupt is generated when an assembled character is transferred to the receive buffer. The transmitted character generates a separate interrupt. The receive register is double-buffered. A hardware parity generator and detector are optional.

The 8051 handles serial I/O using one of its parallel ports. The 8051 bit rate is controlled

by counter/timer 1 and has a maximum bit rate of 187,500 b/s. The 8051 generates one interrupt for both transmission and receipt. The receive register is double-buffered.

The MC6801 contains a full-duplex, asynchronous, serial communication interface. The bit rate is controlled by a rate register and by the MCU's clock or an external clock. The maximum bit rate is 62,500 b/s. Both the transmit and the receive registers are double-buffered. The MC6801 generates only one interrupt for both transmit and receive operations. No hardware parity generation or detection is available, although it does have automatic detection of framing errors and overrun conditions.

The 8051 and the MC6801 generate only one interrupt for both transmit and receive, whereas the Z8611 has a separate interrupt for each. The ability to generate separate interrupts greatly enhances the use of serial communications, since separate service routines are often required for transmitting and receiving.

Other differences between the Z8611, MC6801, and the 8051 occur in the hardware parity detector. the double-buffering of registers, framing error detectors and overrun conditions. The 8051 has a faster data rate than either the Z8611 or the MC6801. The MC6801 has the advantage of a hardware framing error detector and automatic detection of overrun conditions. The MC6801 also has both its transmit and receive reaisters double-buffered. The Z8611 has a hardware parity detector. For detection of framing errors and overrun conditions, a simple, low-overhead software check is available that uses only two instructions. See Z8600 Software Framing Error Detection Application Brief (document #617-1881-0004).

#### INSTRUCTION ARCHITECTURE

The architecture of the Z8611 is designed specifically for microcomputer applications. This fact is manifest in the instruction composition. The arduous task of programming the MC6801 and the 8051 starkly contrasts that of programming the Z8611.

#### Addressing Modes

The Z8611 and the 8051 both have six addressing modes: Register, Indirect Register, Indexed, Direct, Relative, and Immediate. The MC6801 has five addressing modes: Accumulator, Indexed, Direct, Relative, and Immediate. A quick comparison of these addressing modes reveals the versatility of the Z8611 and the 8051. The addressing modes of the MC6801 have several restrictions, as shown in Table 1. While the 8051 has all the addressing modes of the Z8611, its use of them is restricted. The Z8611 allows many more combinations of addressing modes per instruction, because any of its registers can be used as an accumulator. For example, the instructions to clear, complement, rotate, and swap nibbles are all accumulator oriented in the 8051 and operate on the accumulator only. These same commands in the Z8611 can use any register and access it either directly, with register addressing, or with indirect register addressing.

Indexed Addressing. All three chips differ in their handling of indexing. The Z8611 can use any register for indexing. The 8051 can use only the accumulator as an Index register in conjunction with the data pointer or the Program Counter. The MC6801 has one 16-bit Index register. The address located in the second byte of an instruction is added to the lower byte of the Index register. The carry is added to the upper byte for the complete address. The MC6801 requires the index value to be an immediate value.

The MC6801 has only one 16-bit Index register and an immediate 8-bit value from the second byte of the instruction. Hence, the Indexed mode of the MC6801 is much more restrictive than that of the Z8611. The 8051 must use the accumulator as its only Index register, loading the accumulator with the register address each time a reference is made. Then, using indexing, the data is moved into the accumulator, eradicating the previous index. This forces a stream of data through the accumulator and requires a reload of the index before access can be made again. The Z8611 is clearly superior to both the MC6801 and the 8051 in the flexibility of its indexed addressing mode.

Short and Long Addressing. Short addressing helps to optimize memory space and execution speed. In sample applications of short register addressing, an eight percent decrease in the number of bytes used was recorded.

All three chips have short addressing modes, but the Z8611 has short addressing for both external memory and register memory. The 8051 has short addressing for the lowest 32 registers only.

The Z8611 has two different modes for register addressing. The full-byte address can be used to provide the address, or a 4-bit address can be used with the Register Pointer. To use the working registers, the Register Pointer is set for a particular bank of 16 registers, and then one of the 16 registers is addressed with four bits. Another feature for addressing external memory is the use of a 12-bit address in place of a full 16-bit address. To use the 12-bit address, one port supplies the eight multiplexed address/data lines and another port supplies four bits of the second port can be used for I/O. This feature allows access to a maximum of 10K bytes of memory. The 8051 uses short addresses by organizing its lowest 32 registers into four banks. The bank select is located in a 2-bit field in the PSW, with three bits addressing the register in the bank.

The MC6801 uses extended addressing for addressing external memory. With a special, nonmultiplexed expansion mode, 256 bytes of external memory can be accessed without the need for an external address latch. The MC6801 uses one 8-bit port for the address and another port for the data.

#### Stacks

The Z8611 and the MC6801 provide for external stacks, which require a 16-bit Stack Pointer. Internal stacks use only an 8-bit Stack Pointer. The 8051 uses only a limited internal stack requiring an 8-bit Stack Pointer. Using an external stack saves the internal RAM registers for general-purpose use.

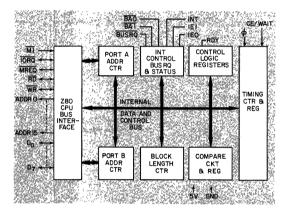

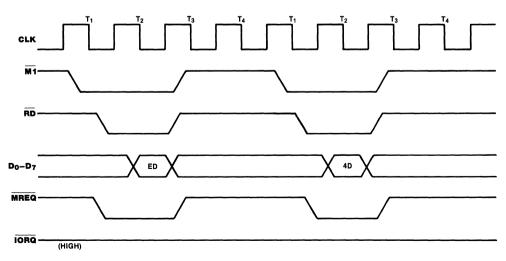

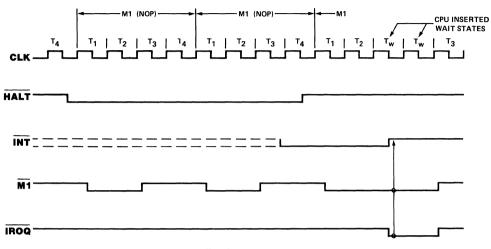

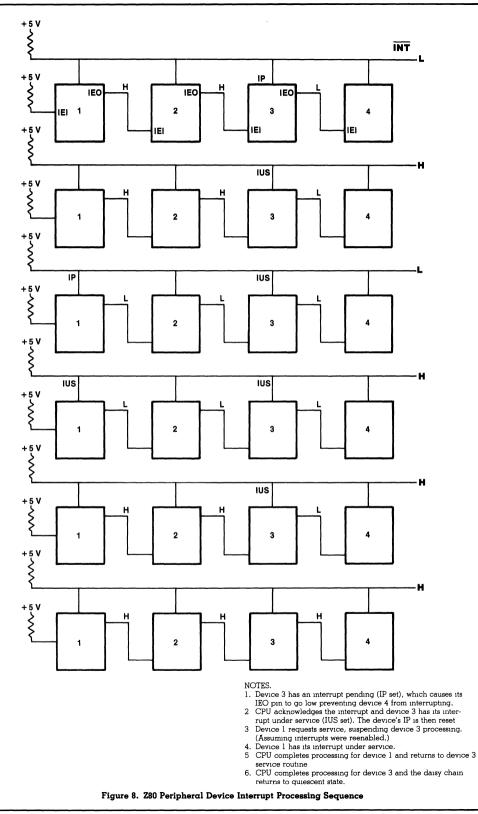

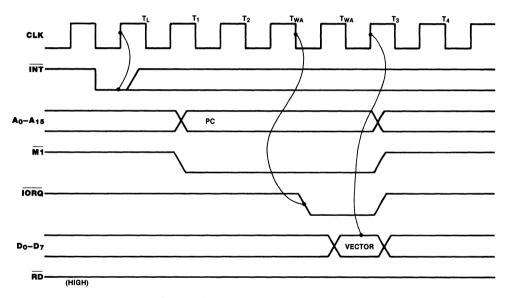

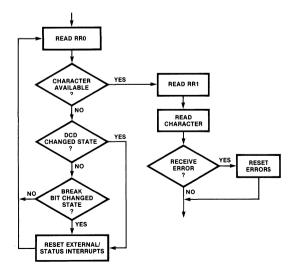

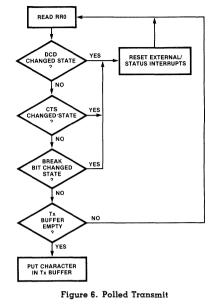

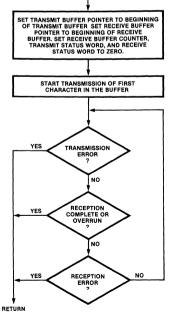

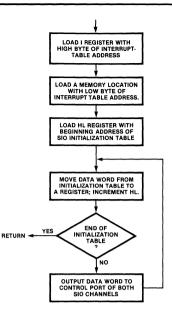

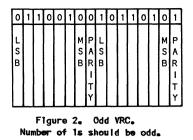

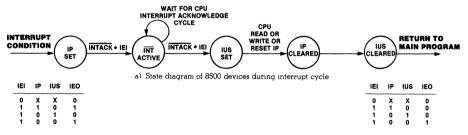

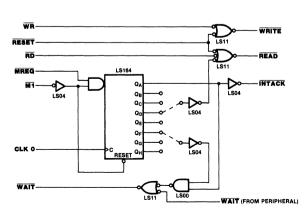

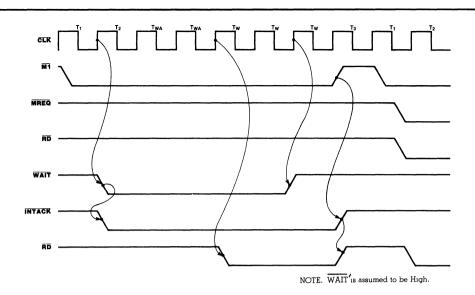

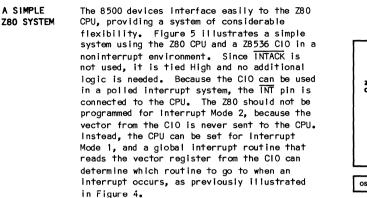

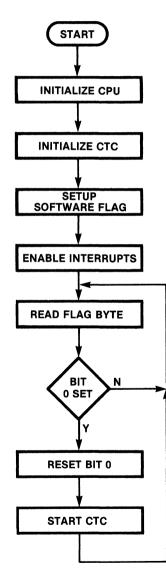

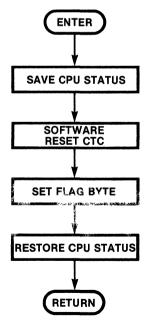

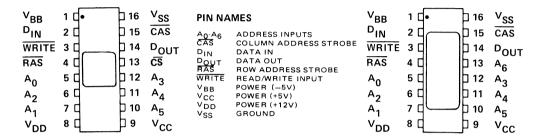

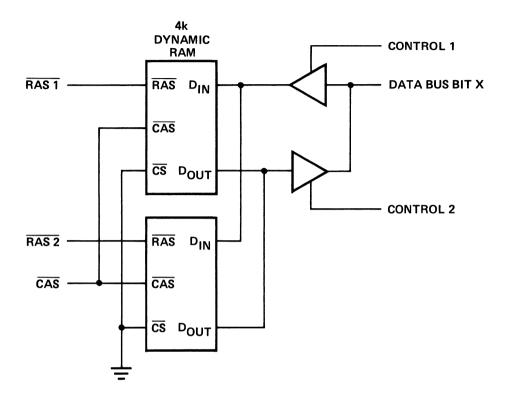

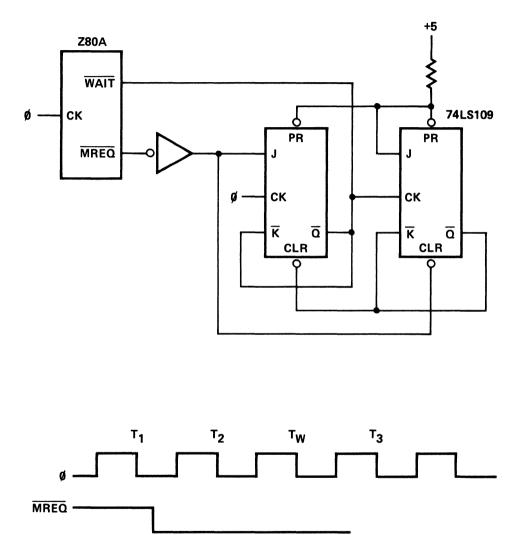

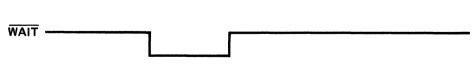

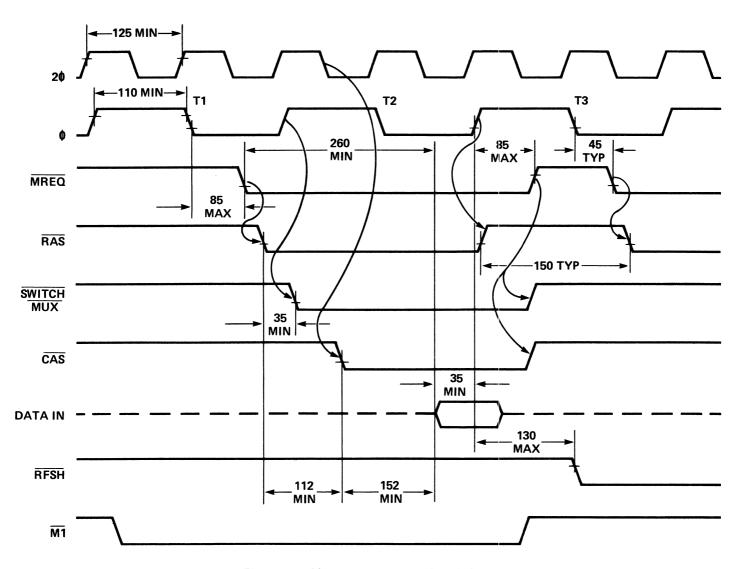

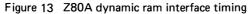

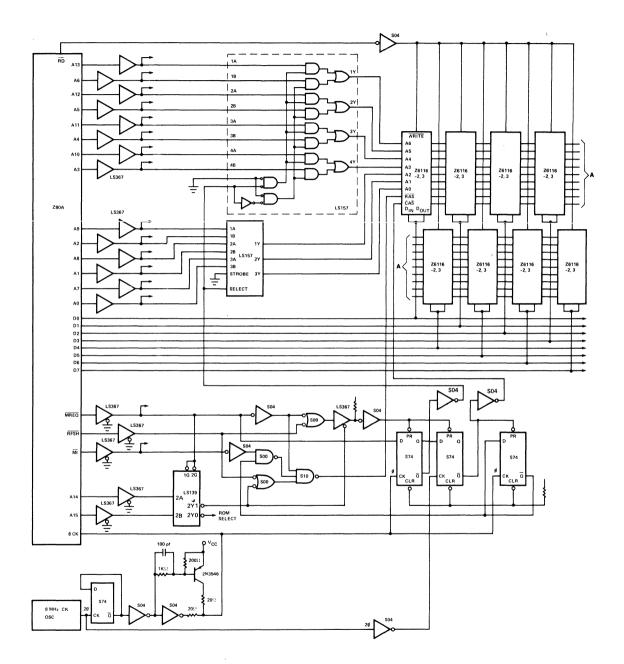

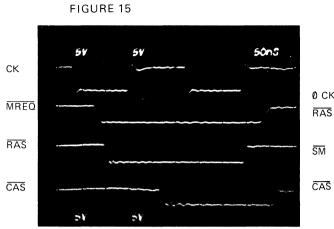

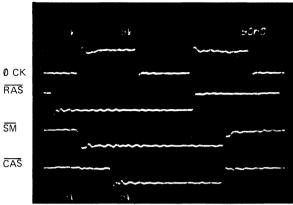

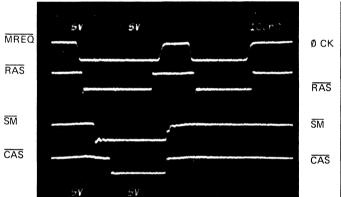

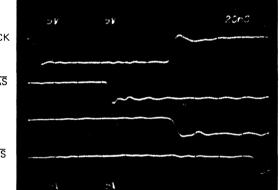

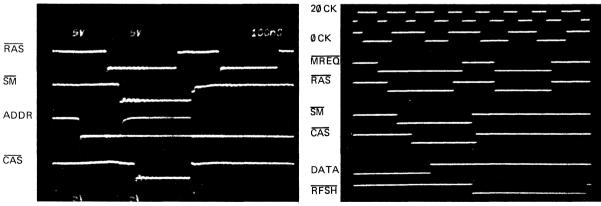

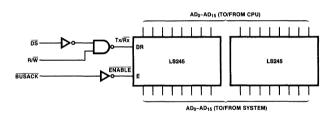

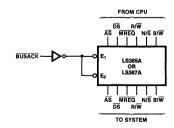

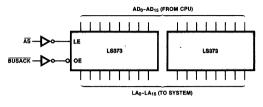

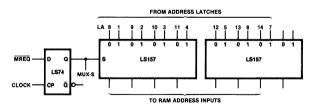

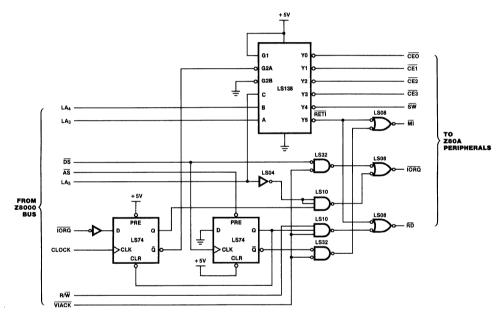

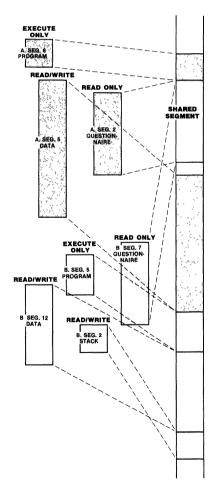

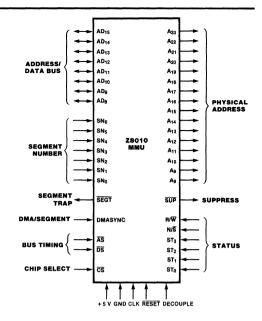

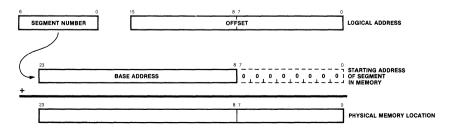

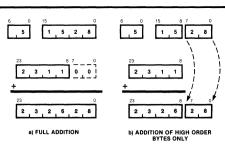

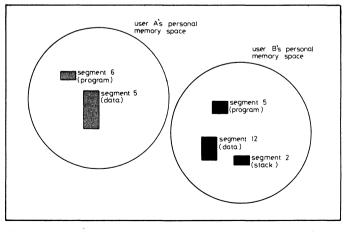

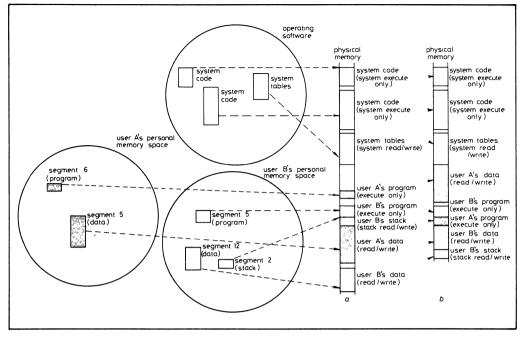

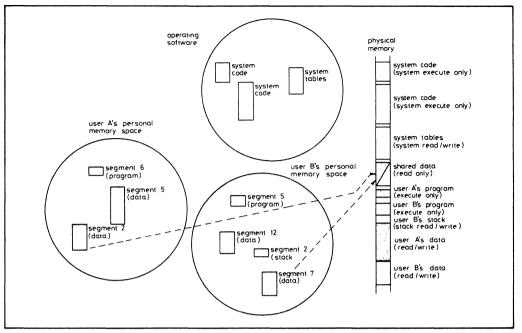

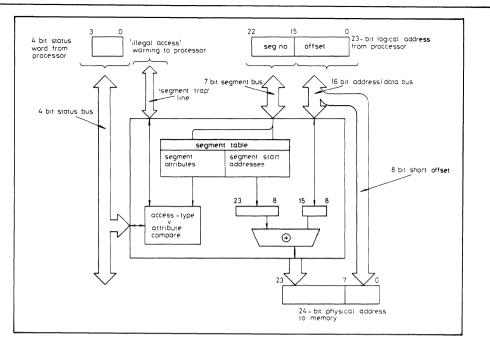

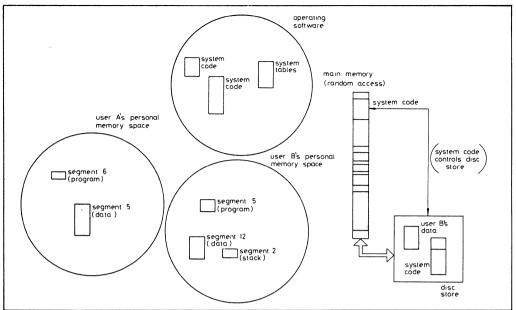

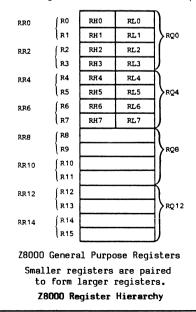

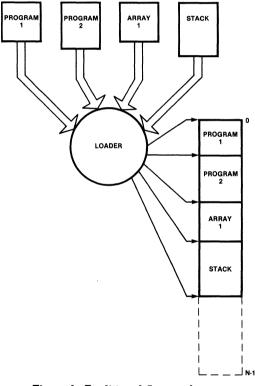

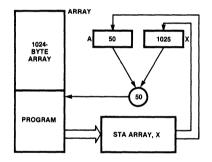

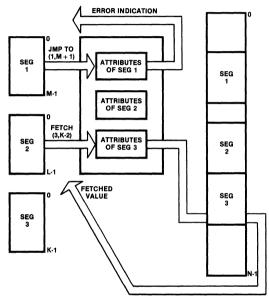

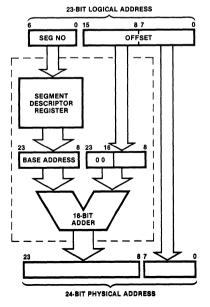

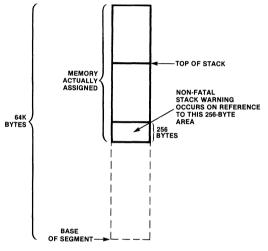

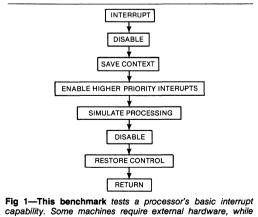

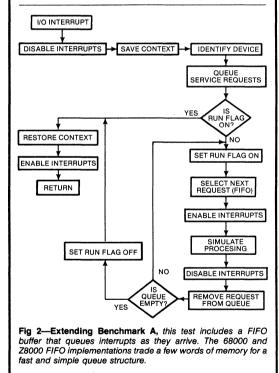

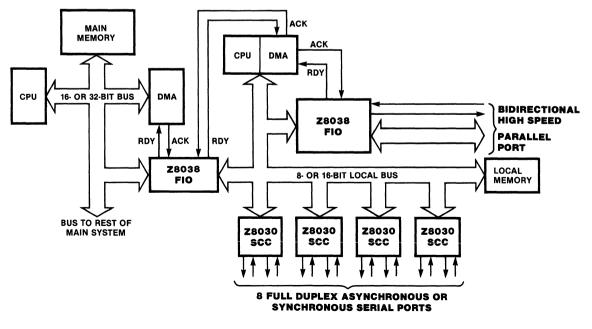

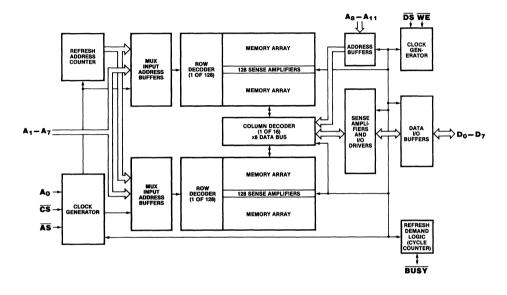

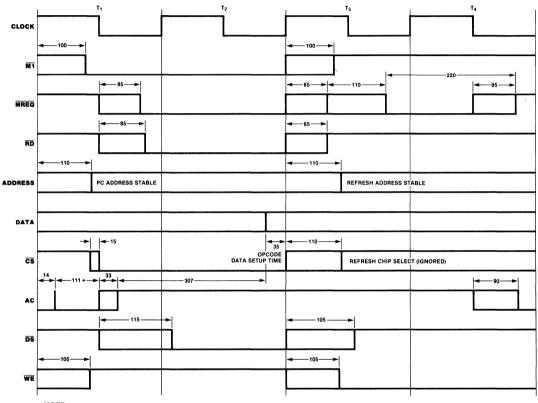

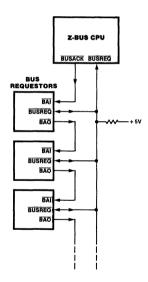

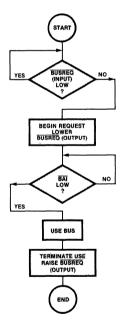

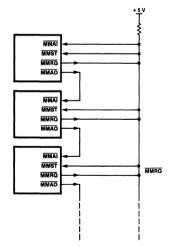

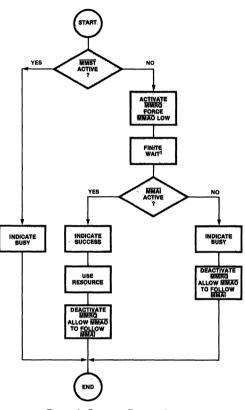

#### Summary