| V6366アプリケーションマニュアル        |

|---------------------------|

| CATALOG No. : LSI-2463660 |

| 1987.6                    |

# PREFACE

This Manual is a collection of interfacing information and sample applications which focuses on the internal register functions and methods for use of the V6366 PCDC (Panel Display & CRT Display Controller). We hope this Manual will be a useful reference during your use of the V6366.

The V6366 incorporates the MC6845 CRT Controller and is compatible with the IBM PC, so we recommend that you refer to the following materials in conjunction with this Manual:

• The MC6845 Data Book (for example, the sections regarding "HD6845" and "HD6845S" of the Hitachi Microcomputer Data Book)

• The sections regarding the "Monochrome Display" and "Color/Graphics Monitor Adapter" of the IBM PC Technical Reference

• The Owner's Manual for the Hercules Graphics Card

We hope that you will inform us of any comments and questions that you might have regarding the contents of this Manual.

November 1986

NIPPON GAKKI, Ltd. Semiconductor Division

# TABLE OF CONTENTS

| 1. | GENERAL DESCRIPTION                                  | page 1 |

|----|------------------------------------------------------|--------|

|    | 1-1. FEATURES                                        | 1      |

| 2. | FUNCTIONAL OVERVIEW                                  | 2      |

|    | 2-1. BLOCK DIAGRAM                                   | 2      |

|    | 2-2. PIN ASSIGNMENT                                  | 3      |

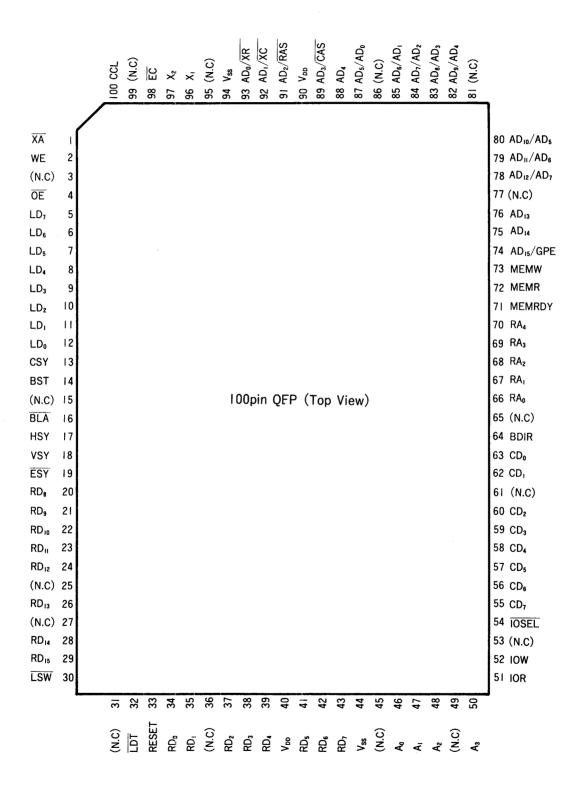

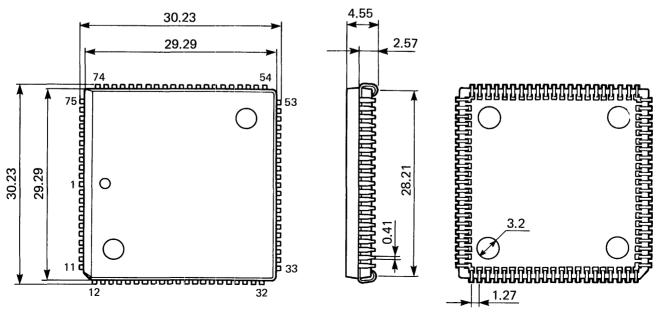

|    | 2-2-1. 100-Pin QFP                                   | 3      |

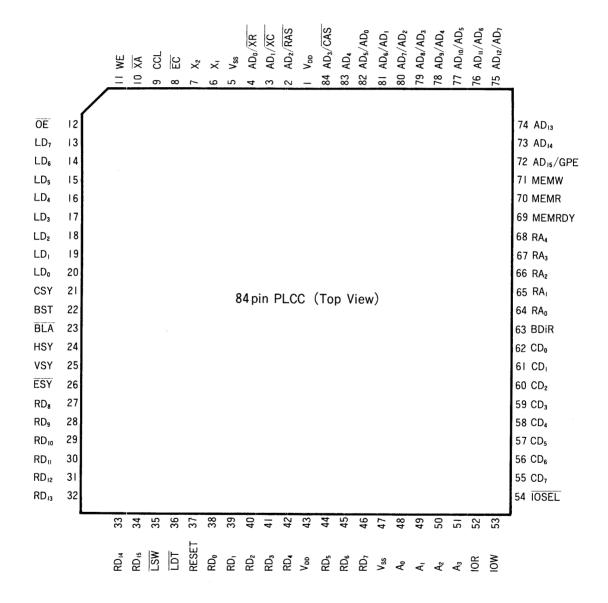

|    | 2-2-2. 84-Pin PLCC                                   | 4      |

|    | 2-3. DESCRIPTION OF TERMINAL FUNCTIONS               | 5      |

| 3. | I/O REGISTERS                                        | 7      |

|    | 3-1. 6845 INDEX/DATA REGISTERS                       | 8      |

|    | 3-1-1. Index Register                                | 9      |

|    | 3-1-2. Horizontal Total Register (R0)                |        |

|    | 3-1-3. Horizontal Displayed Register (R1)            |        |

|    | 3-1-4. Horizontal Sync Position Register (R2)        |        |

|    | 3-1-5. Sync Pulse Width Register (R3)                |        |

|    | 3-1-6. Vertical Total Register (R4)                  |        |

|    | 3-1-7. Total Raster Adjust Register (R5)             | 9      |

|    | 3-1-8. Vertical Displayed Register (R6)              | 10     |

|    | 3-1-9. Vertical Sync Position Register (R7)          | 10     |

|    | 3-1-10. Interlace Register (R8)                      |        |

|    | 3-1-11. Maximum Raster Address Register (R9)         | 10     |

|    | 3-1-12. Cursor Start Raster Register (R10)           | 10     |

|    | 3-1-13. Cursor End Raster Register (R11)             | 10     |

|    | 3-1-14. Start Address Registers (R12, R13)           | 11     |

|    | 3-1-15. Cursor Address Registers (R14, R15)          | 11     |

|    | 3-1-16. Light Pen Registers (R16, R17)               | 11     |

|    | 3-1-17. Precautions on Usage                         |        |

|    | 3-1-18. Sample Setting Values using IBM PC           | 12     |

|    | 3-2. MODE REGISTER (I/O Register 8)                  |        |

|    | 3-3. COLOR REGISTER (I/O Register 9)                 |        |

|    | 3-4. STATUS REGISTER (I/O Register A)                |        |

|    | 3-5. CLEAR/PRESET LIGHT PEN                          |        |

|    | 3-6. BANK ADDRESSES AND DATA                         |        |

|    | 3-6-1. Color Palette (Addresses 00H-1FH)             | 19     |

|    | 3-6-2. Gray Scaling and Hatching                     | 20     |

|    | 3-6-3. 6845 Preset Data (Addresses 30н-36н, 38н-3Ен) | 21     |

|    | 3-6-3-1. Horiz. Total (Addresses 30н, 38н)           | 21     |

|    | 3-6-3-2. Sync. Width (Addresses 33н, 3Вн)            |        |

|    | 3-6-3-3. Vert. Total (Addresses 34H, 3CH)            |        |

|    | 3-6-3-4. Vert. Adjust (Addresses 35н, 3Dн)           |        |

|    | 3-6-3-5. Max. Scan (Addresses 36н, 3Ен)              |        |

|    | 3-6-3-6. Hsy. Offset (Addresses 31H, 39H)            | 22     |

|    |               | 3-6-3-7. | Vsy. Offset (Addresses 32H, 3AH) pa | ge 22 |

|----|---------------|----------|-------------------------------------|-------|

|    |               | 3-6-3-8  | Light Pen Address                   | 22    |

|    |               | 3-6-4.   | Address 37H                         | 24    |

|    |               | 3-6-5.   | Address 3FH                         | 27    |

|    |               | 3-6-6.   | Address 20H (Duty)                  | 28    |

|    |               | 3-6-7.   | Address 21H (H size)                | 28    |

|    |               |          | Address 22H (V Adj)                 |       |

|    |               |          | Address 23H (H Adj)                 |       |

|    |               |          | Address 24H                         |       |

|    |               |          | Address 25H                         |       |

|    |               |          | Address 26H                         |       |

|    |               |          | Address 27H                         |       |

|    |               |          | Address 28H                         |       |

|    |               |          | Address 29H                         |       |

|    |               |          | Address 2AH                         |       |

|    |               | 3-6-17.  | Address 2BH (Control Data)          | 45    |

|    | 3-7.          | CONTR    | OL/ID REGISTER (I/O Register F)     | 45    |

|    |               |          | Control                             |       |

|    |               |          | ID                                  |       |

|    |               | 572.     |                                     | ד     |

| 4. | OP            | ERATIN   | G MODES                             | 46    |

|    | 4-1           | TEXT M   | ODES                                | 46    |

|    |               |          | CS MODES                            |       |

|    | 7 4.          |          |                                     |       |

|    |               |          | 1 Byte Modes                        |       |

|    |               | 4-2-1-1. | 640 x 1 Bit Mode                    |       |

|    |               | 4-2-1-2. |                                     |       |

|    |               | 4-2-1-3. | 160 x 4 Bit Mode                    | 49    |

|    |               | 4-2-2.   | 2 Byte Modes                        | 50    |

|    |               | 4-2-2-1. | 640 x 2 Bit Mode                    | 50    |

|    |               | 4-2-2-2. | 320 x 4 Bit Mode                    | 50    |

|    |               | 4-2-3.   | 4 Byte Modes                        | . 50  |

|    |               |          | 640 x 4 Bit Mode                    |       |

|    |               |          | 320 x 8 Bit Mode                    |       |

|    |               | 4-2-3-2. | 520 X 8 Bit Mode                    | 51    |

| 5. | ME            | MORY.    |                                     | 52    |

|    | 5-1           | ADDRE    | SS CONNECTION                       | 53    |

|    |               |          | REFRESH                             |       |

| _  |               |          |                                     |       |

| 6. |               |          |                                     |       |

|    |               |          | INPUT CRT                           |       |

|    |               |          | RGB MONITOR                         |       |

|    |               |          | OSITE INPUT CRT                     |       |

|    |               |          |                                     |       |

|    |               |          | A DISPLAY                           |       |

|    | 6 <b>-</b> 6. | el pane  | E                                   | 59    |

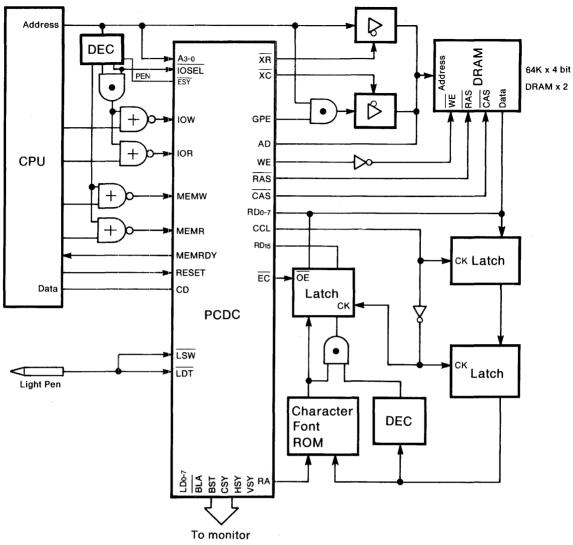

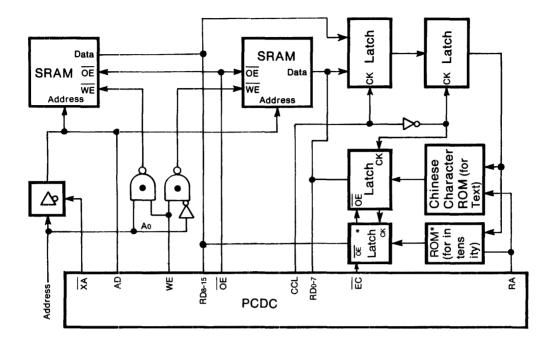

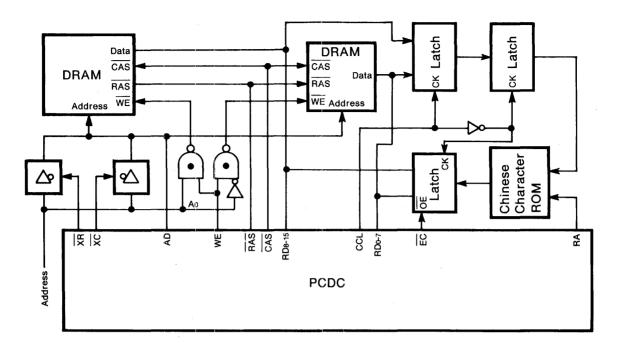

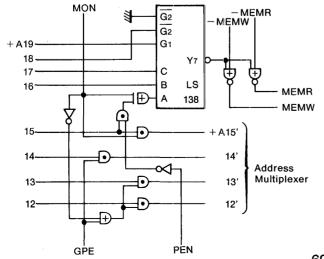

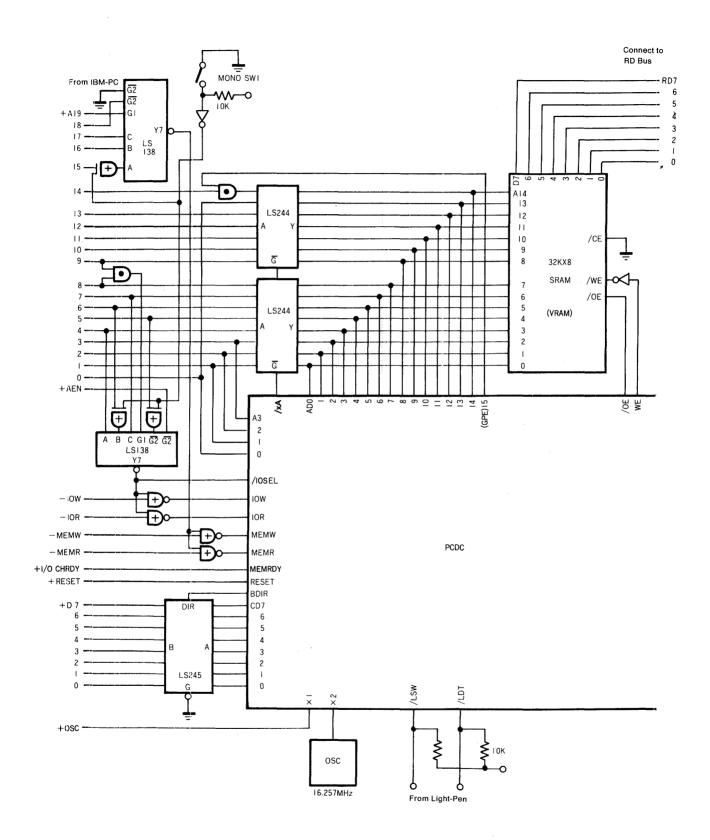

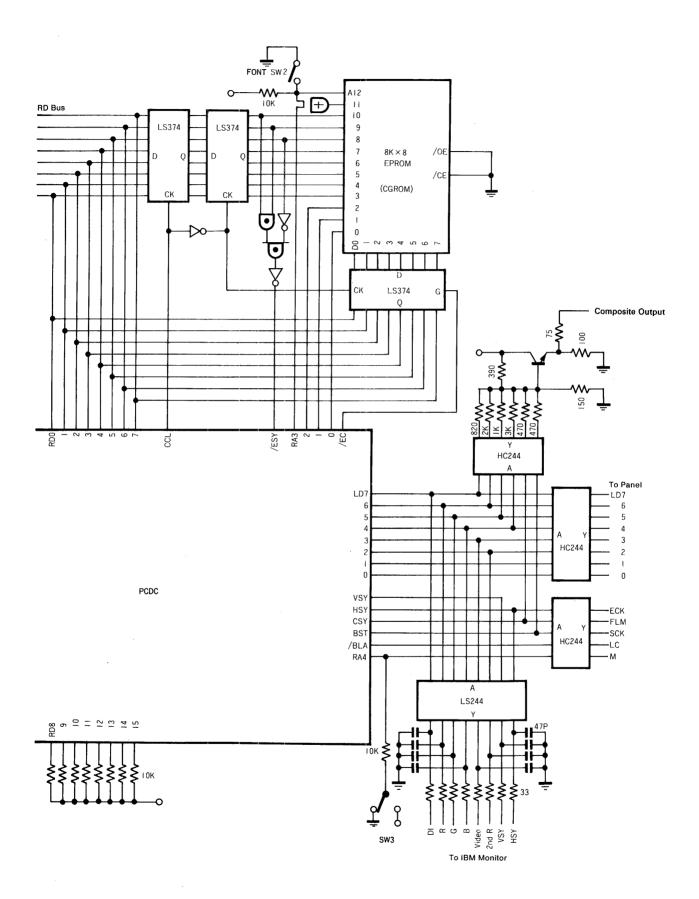

| 7.  | SYSTEM CONFIGURATIONS pag                                           | e 60 |

|-----|---------------------------------------------------------------------|------|

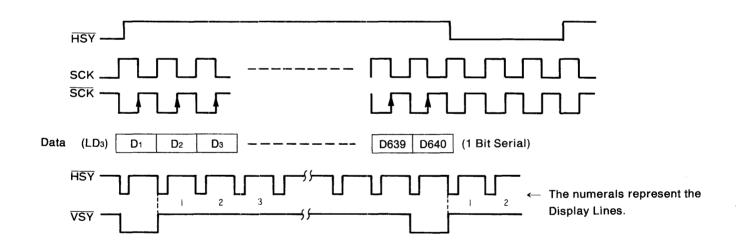

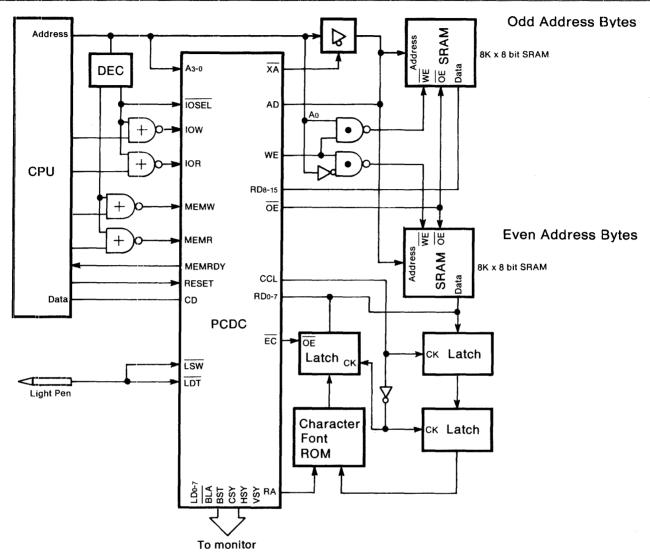

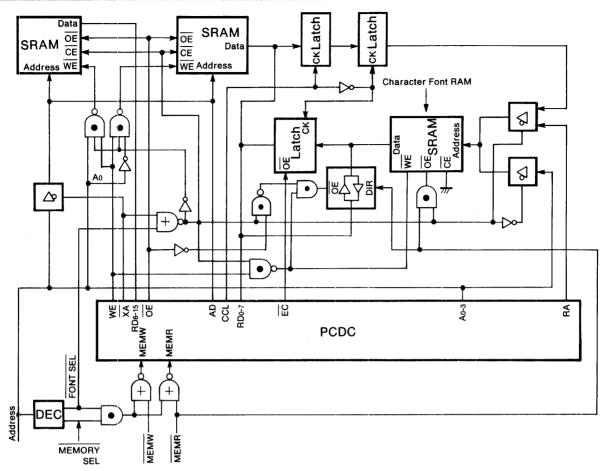

|     | 7-1. USE OF SRAM (For 16-Bit Bus, CGA)                              | 60   |

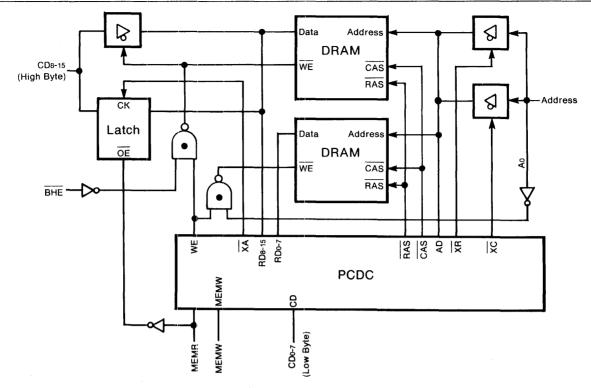

|     | 7-2. USE OF DRAM (For 8-Bit Bus, Hercules)                          |      |

|     | 7-3. KANJI DISPLAY                                                  |      |

|     | 7-3-1. For 8 x n (Fon = 101)                                        | 62   |

|     | 7-3-2. For 16 x n (Fon = 110)                                       | 63   |

|     | 7-4. USE OF A CHARACTER FONT RAM                                    | 64   |

|     | 7-5. USE OF A 16-BIT BUS CPU                                        | 65   |

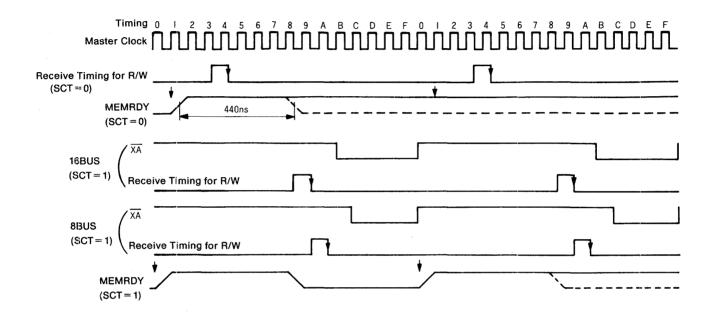

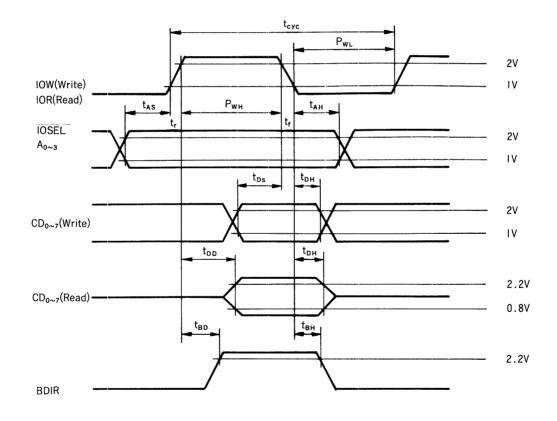

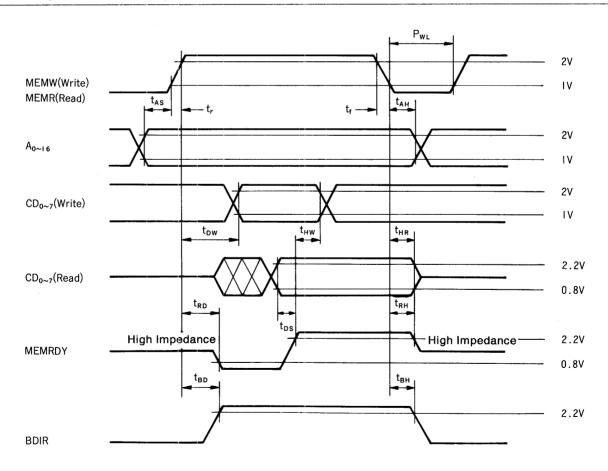

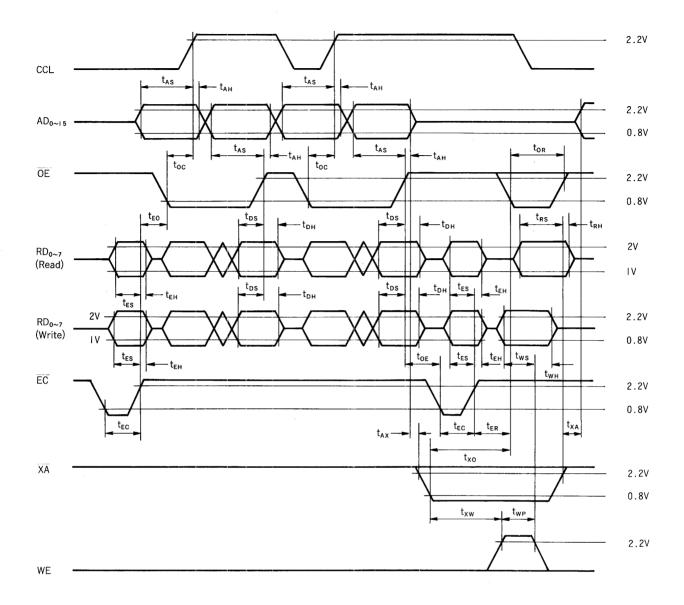

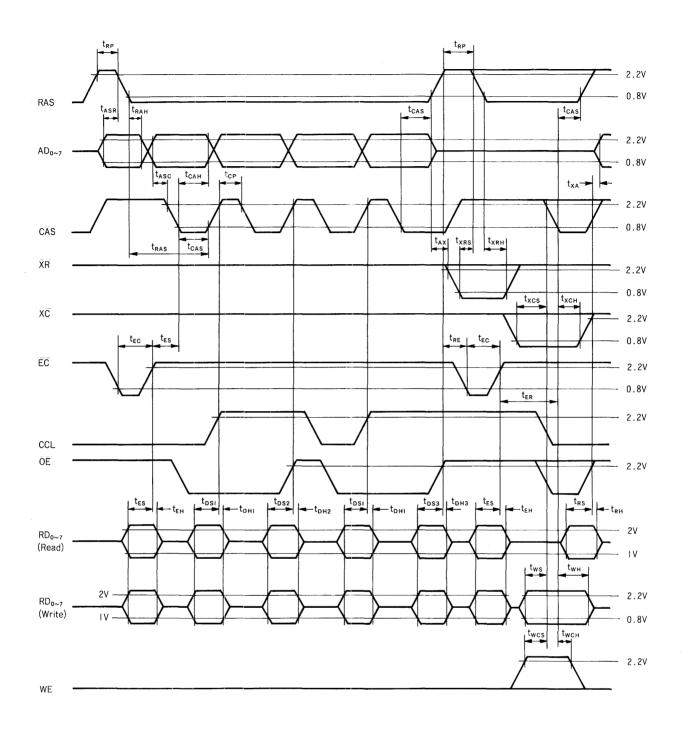

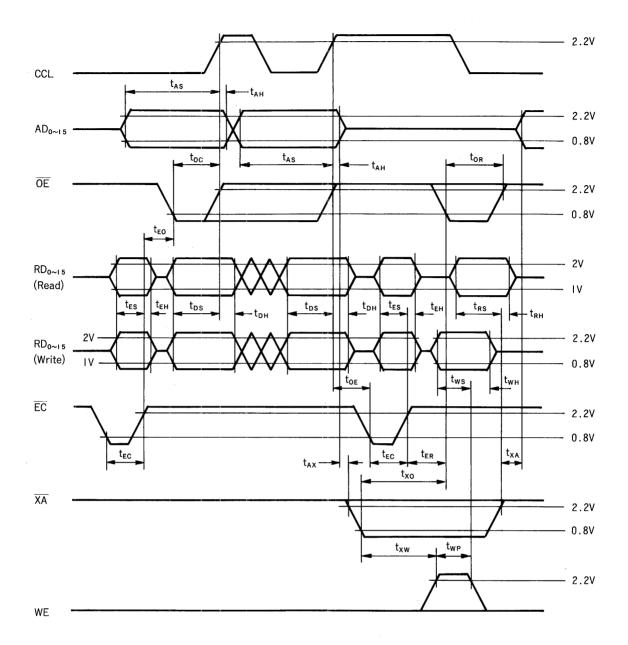

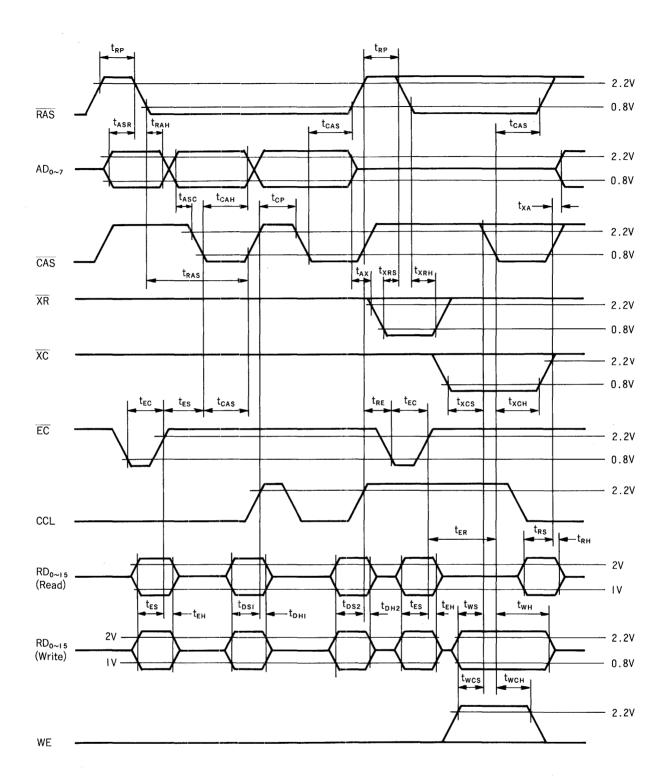

|     | 7-6. OPERATING TIMING                                               | 66   |

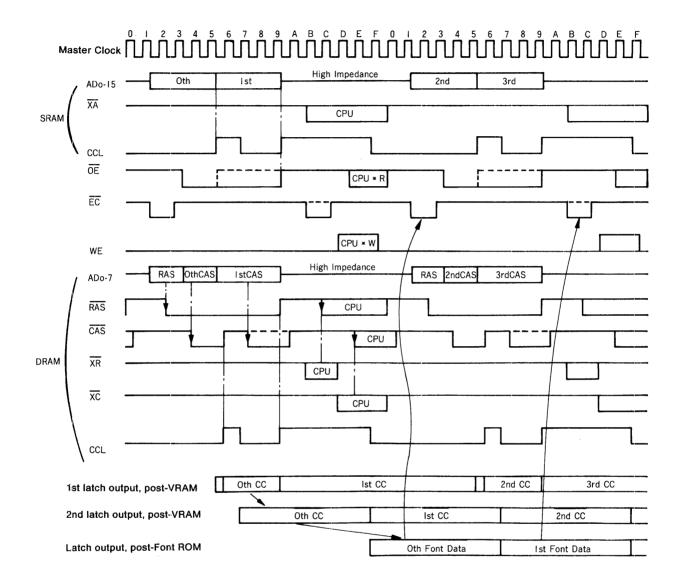

|     | 7-6-1. 16-Bit Bus Configuration                                     | 66   |

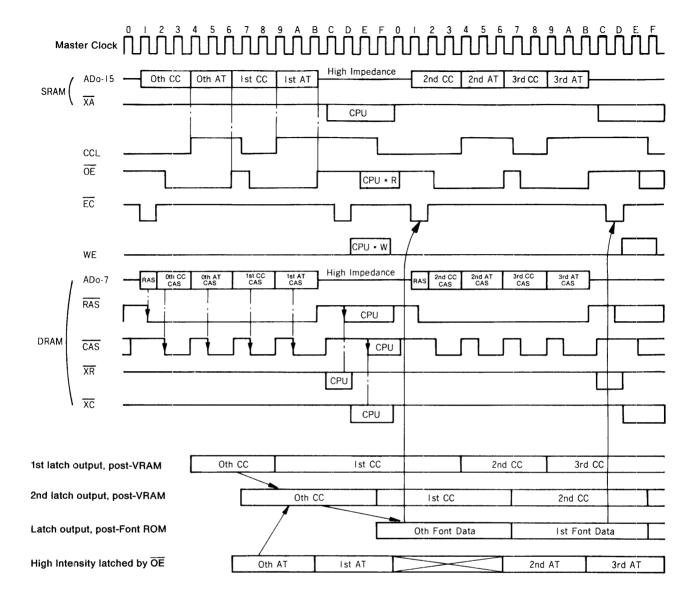

|     | 7-6-2. 8-Bit Bus Configuration                                      | 68   |

|     | 7-7. OTHER PRECAUTIONS                                              | 69   |

| 8.  | ELECTRICAL CHARACTERISTICS                                          | 71   |

|     | 8-1. ABSOLUTE MAXIMUM RATINGS                                       | . 71 |

|     | 8-2. RECOMMENDED CONDITIONS FOR USE                                 | 71   |

|     | 8-3. DC CHARACTERISTICS                                             |      |

|     | 8-4. AC CHARACTERISTICS                                             |      |

|     | 8-4-1. I/O Registers-CPU Interface                                  |      |

|     | 8-4-2. VRAM-CPU Interface                                           |      |

|     | 8-4-3. VRAM-PCDC Interface                                          |      |

|     | 8-4-3-1. 8-Bit Bus in SRAM Mode                                     |      |

|     | 8-4-3-2. 8-Bit Bus in DRAM Mode<br>8-4-3-3. 16-Bit Bus in SRAM Mode |      |

|     | 8-4-3-4. 16-Bit Bus in DRAM Mode                                    |      |

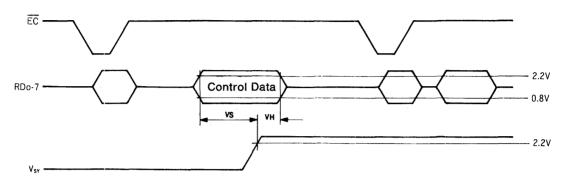

|     | 8-4-4. Control Data Interface                                       |      |

|     | 8-4-5. Monitor Interface                                            |      |

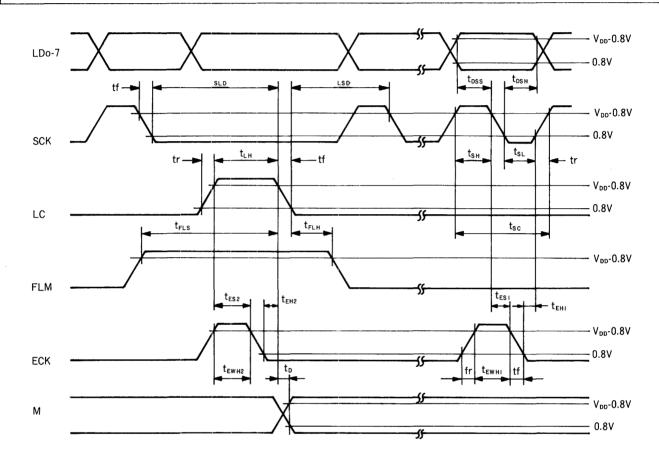

|     | 8-4-5-1. LCD                                                        | 82   |

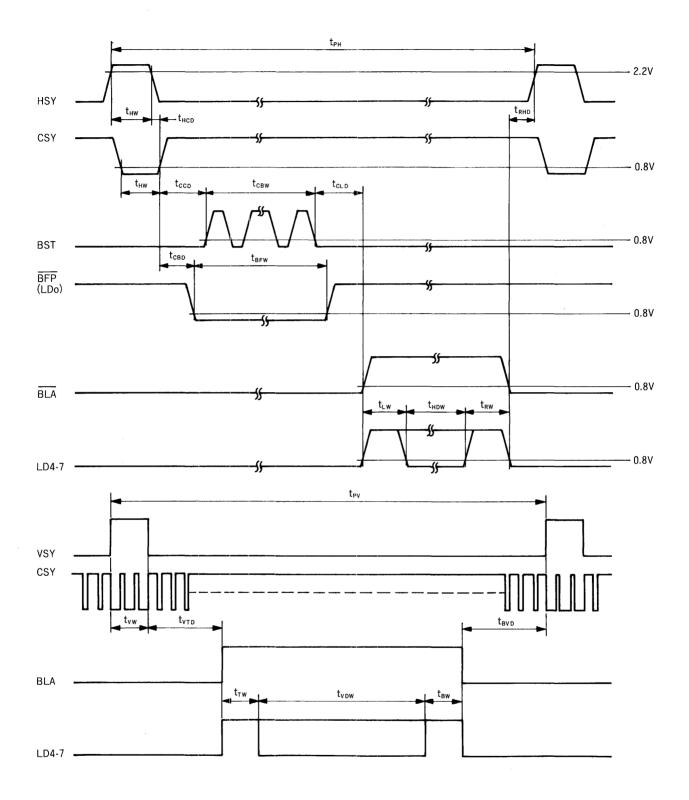

|     | 8-4-5-2. CRT                                                        | . 84 |

|     | 8-4-6. External Clock                                               | . 86 |

|     | 8-4-7. Terminal Capacity                                            | 86   |

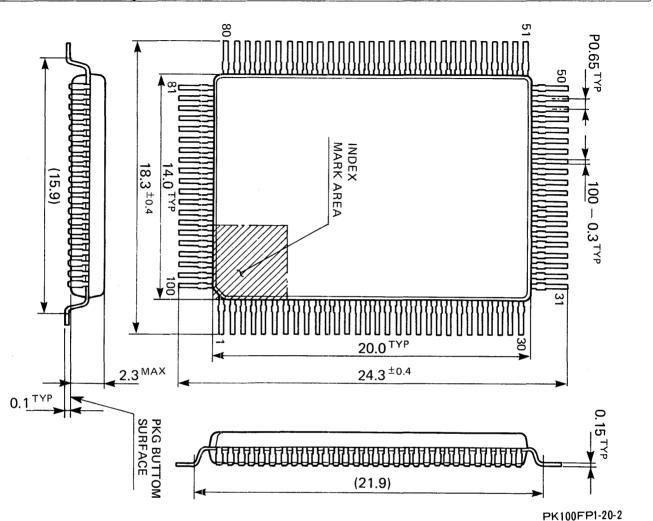

| 9.  | PACKAGE OUTLINES                                                    | 87   |

|     | 9-1. 100-PIN QFP                                                    | . 87 |

|     | 9-2. 84-PIN PLCC                                                    | 87   |

| 10. | PCDC EVALUATION BOARD                                               | 88   |

|     | 10-1. LIST OF CONNECTORS                                            | . 89 |

|     | 10-2. CIRCUIT DIAGRAM                                               |      |

|     | 10-3. INITIALIZATION SETTINGS                                       | 92   |

# 1. GENERAL DESCRIPTION

The PCDC (Panel Display & CRT Display Controller) is a display controller that has the two functions: (1) the display control of a high-capacity flat-panel display (hereafter referred to as a "Panel") and (2) the display control of a raster-scan type CRT. By merely performing initialization, however, even the Panel can be used without changing the software for conventional CRTs, enabling the simple system configuration of a handheld or portable computer which uses the Panel. (If so required, the PCDC can also be used to switch the display monitor between a CRT and a Panel.)

The PCDC is compatible with the CGA (Color Graphics Adapter), MDA (Monochrome Display Adapter), and HGC (Hercules Graphics Card), all for IBM PC application. In case the software and hardware for connecting a regular monitor come as a pair, the PCDC offers compatibility without requiring software changes (initialization is also unnecessary). Even in case of connecting different monitors, initialization will only be performed once at Power Start-Up, then compatibility will be available without requiring any software changes. It is thus possible, for example, to run CGA software using an IBM monochrome monitor and the Panel. (A gray scaling/hatching display can be used with a monochrome monitor.)

Because the PCDC has the display capacity of the IBM PC as well as numerous other expansion functions, including Kanji display, Color Palette, and the capability to simultaneously display up to 256 colors, a high-performance display system can be easily configured.

## 1-1. FEATURES

- All functions of MC6845 are built in (excluding the Interlacing & Video Mode and the Skew function).

- In addition to a CRT or LCD, a EL and Plasma Display can also be connected.

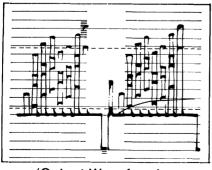

- A 640 by 400 PEL Panel can be driven (a 720 by 350 PEL Panel can also be driven).

- A one-screen Panel or two-screen Panel (split into top and bottom halves) can be used.

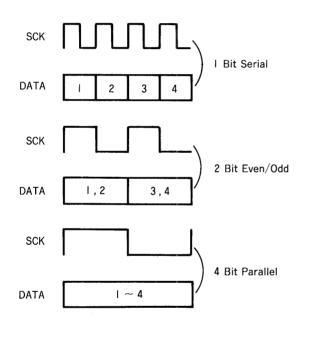

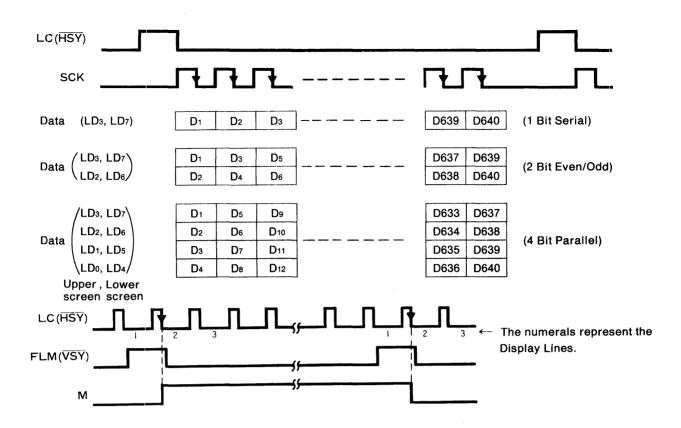

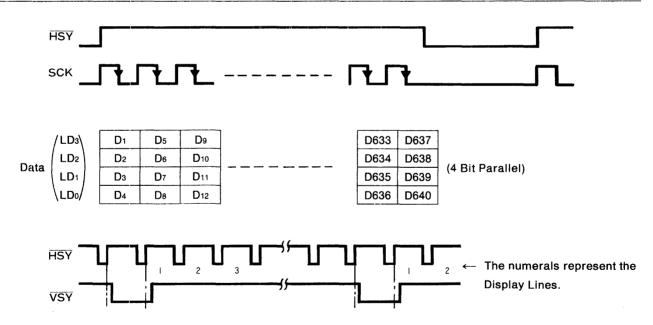

- Selection of 1-, 2-, 4- or 8-bit parallel transmission of data to the Panel.

- A two-screen panel allows, at a maximum 1/256 duty, display of up to 512 lines.

- A gray scaling/hatching display can be used with the Panel or a monochrome monitor.

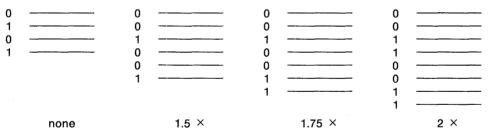

- IBM PC software for 640 by 200 PELs can be directly displayed on a 640 by 400 PEL screen. (An 8 by 16 character font can be used, and can be displayed even in Double Scan Mode.)

- In addition to the standard IBM PC Graphics Modes, a variety of other Graphics Modes are provided: 320 by 200 PELs x 16 or 256 colors, 320 by 400 PELs x 4 or 16 colors, 640 by 200 PELs x 4 colors, 640 by 350 PELs x 16 colors, and so on.

- A Protect Bit is provided for software protection.

- An SRAM or DRAM can be used as the VRAM. (Because the timing for display and the CPU are separate, the CPU can access VRAM at any time (without awaiting the retrace-timing.))

- Built-in interface for the Light Pen

- With a linear RGB monitor, 16 out of 512 colors can be simultaneously displayed.

- With an EGA monitor, 16 out of 64 colors can be simultaneously displayed.

- A Color Lookup Table can even be used with an IBM color monitor.

- A Standby function is provided to conserve power dissipation.

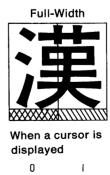

- Kanji display capacity of 16 by 16, 24 by 24 or 32 by 32 "PELs" (picture elements or pixels). (Attributes can also be used).

- The font configuration can be selected. Horizontal: 6, 7, 8, 9, 10, or [8 x integer] PELs (capable of a mixed display of half-width and full-width text); Vertical: 1 to 32 PELs.

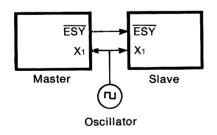

- Capable of smooth scrolling and (in Interlace Mode only) external synchronization

- The simultaneous display capability with an IBM color monitor and a one-screen LCD of 640 x 200.

- CMOS, 5V power supply, 100-pin QFP or 84-pin PLCC

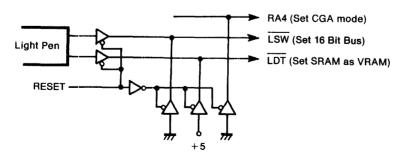

#### 2-1. EC OE **BLOCK DIAGRAM** LDT RA₀-₄ LSW CCL ESY AD0-15 MPX Reg. Adr Timing Gen. Control Raster Vertical Light Pen Control Control Cursor Int. Refresh Address Gen. Control **O** MEMRDY Register MEMW MEMR Array CPU Int. **P**IOSEL T $\mathbf{T}$ CD0-7 **b** BDIR **O** A<sub>0-3</sub> Half-Tone Control Panel Interface Color Palette -Color Encoder Horizontal Burst Gen. Control Sync Gen. Clock Gen. Select Ο BST BLA CSY HSY VSY X1-2 LD0-7 Vss V<sub>DD</sub> RESET

2. FUNCTIONAL OVERVIEW

Ν

## 2-2. PIN ASSIGNMENT

### 2-2-1. 100-Pin QFP

3

4

# 2-3. DESCRIPTION OF TERMINAL FUNCTIONS

| Signal Name     | I/O | Terminal Functions                                                                      |

|-----------------|-----|-----------------------------------------------------------------------------------------|

| Ao              | l   |                                                                                         |

| 2               |     | Address for I/O register selection. Ao is also used for selecting the high or low byte. |

| A3              | 1   |                                                                                         |

| CD <sub>0</sub> | 1/0 |                                                                                         |

| 2               |     | Data Bus for the CPU                                                                    |

| CD7             | I/O |                                                                                         |

| MEMRDY          | 0   | Read/Write Ready signal for the Memory ( <sup>`</sup> 0`: Wait)                         |

| MEMW            | 1   | Controls writing to Memory                                                              |

| MEMR            | I   | Controls reading from Memory                                                            |

| IOW             | I   | Controls writing to the I/O registers                                                   |

| IOR             | I   | Controls reading from the I/O registers                                                 |

| IOSEL           | I   | Enable signal to the I/O Register D and E (`0`: Enable)                                 |

| RESET           | I   | Reset signal                                                                            |

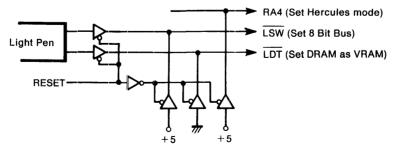

| LSW             | 1   | Light Pen Switch signal (At RESET, specifies an 8- or 16-bit Data Bus for VRAM)         |

| LDT             | 1   | Light Pen Detection signal (At RESET, specifies VRAM from SRAM or DRAM)                 |

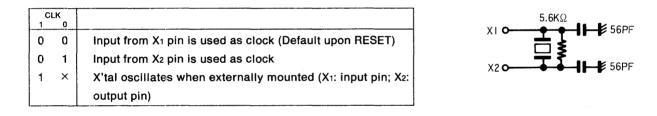

| X1              | 1   |                                                                                         |

| X2              | 1/0 | ) For X'tal oscillation or external clock input                                         |

| BDIR            | 0   | Direction control of the bi-direction buffer for the CPU Data Bus                       |

| RAo             | 0   |                                                                                         |

| 2               |     | Raster Address                                                                          |

| RA₃             | 0   |                                                                                         |

| RA4             | 1/0 | Raster Address or AC Conversion signal (At RESET, specifies the Hercules or CGA         |

|                 |     | Mode)                                                                                   |

| RD <sub>0</sub> | 1/0 |                                                                                         |

| 2               |     | Data bus for VRAM (Low side)                                                            |

| RD7             | I/O |                                                                                         |

| RDa             | 1/0 |                                                                                         |

| 2               |     | Data bus for VRAM (High side)                                                           |

| RD15            | I/O |                                                                                         |

| ĒC              | 0   | Transmission control for the RD Bus of Character Font Data                              |

| OE              | 0   | Output control (for SRAM)                                                               |

| CCL             | 0   | Latch clock for character codes                                                         |

| WE              | 0   | Controls writing of VRAM                                                                |

| XA              | 0   | CPU-related timing for VRAM                                                             |

| Vss             | 1   |                                                                                         |

| Vss             | I   | ) 0V                                                                                    |

| VDD             | I   |                                                                                         |

| VDD             |     | ) +5V                                                                                   |

| Signal Name | ١/٥ | Terminal Functions                                                       |  |  |  |  |  |  |  |  |

|-------------|-----|--------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| AD0/XR      | о   | CPU RAS Address timing for DRAM                                          |  |  |  |  |  |  |  |  |

| AD1/XC      | 0   | CPU CAS Address timing for DRAM                                          |  |  |  |  |  |  |  |  |

| AD2/RAS     | 0   | RAS for DRAM                                                             |  |  |  |  |  |  |  |  |

| AD3/CAS     | 0   | CAS for DRAM                                                             |  |  |  |  |  |  |  |  |

| AD4         | 0   |                                                                          |  |  |  |  |  |  |  |  |

| AD5/AD0     | 0   |                                                                          |  |  |  |  |  |  |  |  |

| AD6/AD1     | Ö   |                                                                          |  |  |  |  |  |  |  |  |

| AD7/AD2     | 0   | Addresses of                                                             |  |  |  |  |  |  |  |  |

| AD8/AD3     | ο   | SRAM Addresses of                                                        |  |  |  |  |  |  |  |  |

| AD9/AD4     | 0   | DRAM                                                                     |  |  |  |  |  |  |  |  |

| AD10/AD5    | 0   |                                                                          |  |  |  |  |  |  |  |  |

| AD11/AD6    | ο   |                                                                          |  |  |  |  |  |  |  |  |

| AD12/AD7    | 0   |                                                                          |  |  |  |  |  |  |  |  |

| AD13        | ο   |                                                                          |  |  |  |  |  |  |  |  |

| AD14        | 0   |                                                                          |  |  |  |  |  |  |  |  |

| AD15/GPE    | 0   | Also, OR output of Bits 0 and 1 of the Control Register in Hercules Mode |  |  |  |  |  |  |  |  |

| L.D4        | ο   | DB Primary B B0 LD4                                                      |  |  |  |  |  |  |  |  |

| L.D5        | 0   | DG for IBM color Primary G for B1 LD5                                    |  |  |  |  |  |  |  |  |

| L.D6        | 0   | DR monitor Primary R EGA B2 LD6                                          |  |  |  |  |  |  |  |  |

| LD7         | 0   | DI Secondary G Monitor Go LD7                                            |  |  |  |  |  |  |  |  |

| L.Do        | 0   | $\overrightarrow{BFP} \leftarrow \qquad \overleftarrow{for linear} LD_0$ |  |  |  |  |  |  |  |  |

| LD1         | 0   | G1 (RGB monitor LD1 for                                                  |  |  |  |  |  |  |  |  |

| LD2         | 0   | Secondary R G2 LD2 Panel                                                 |  |  |  |  |  |  |  |  |

| l_D₃        | 0   | Video Secondary B Ro LD3                                                 |  |  |  |  |  |  |  |  |

| BLA         | 0   | BLANK ← R1 HSY                                                           |  |  |  |  |  |  |  |  |

| BST         | 0   | Color Burst                                                              |  |  |  |  |  |  |  |  |

| CSY         | 0   | Composite Sync $\leftarrow$ $\leftarrow$ $\overline{VSY}$                |  |  |  |  |  |  |  |  |

| HSY         | ο   | Horizontal ← ← (ECK)                                                     |  |  |  |  |  |  |  |  |

| VSY         | О   | Vertical ← ←                                                             |  |  |  |  |  |  |  |  |

| ESY         | 1/0 | for external synchronization                                             |  |  |  |  |  |  |  |  |

# 3. I/O REGISTERS

All operations of the PCDC are controlled by the settings of the I/O registers. For example, the setting of the monitor's cycle and Sync signal position is performed by the 6845 Index/Data Register, and the switching between the alphanumeric display and graphics display is performed by the Mode Register. A large number of the I/O registers have IBM PC-compatible addresses and functions. The expansion functions for IBM PC, beginning the setting for the connection method with the Panel, are organized within the Register Bank. Therefore, by merely performing initialization at Power Start-Up, IBM PC software can be used without requiring any changes. (In case of the standard combination consisting of software and a monitor which do not require the expansion functions, initialization also becomes unnecessary.)

| ADDRESS    |    |    |            |    |             | DATA       |              |      |     |       | R/W |                   |     |                                       |

|------------|----|----|------------|----|-------------|------------|--------------|------|-----|-------|-----|-------------------|-----|---------------------------------------|

| Hex        | Аз | A2 | <b>A</b> 1 | Ao | D7          | D6         | D5           | D4   | Dз  | D2    | D1  | Do                |     |                                       |

| 0, 2, 4, 6 | 0  | ×  | ×          | 0  | ×           | ×          | ×            |      | 684 | 15 In | dex |                   | w   |                                       |

| 1, 3, 5, 7 | 0  | ×  | ×          | 1  |             |            | 6845 Data    |      |     |       | R/W | ( × : Don't care) |     |                                       |

| 8          | 1  | 0  | 0          | 0  | Mode        | ×          |              | Mode |     |       |     | R/W               | *   |                                       |

| 9          | 1  | 0  | 0          | 1  | ×           | ×          |              |      | Co  | lor   |     |                   | R/W | ★ Preset Light-Pen (in Hercules Mode) |

| A          | 1  | 0  | 1          | 0  | Sta-<br>tus | ×          | ×            | ×    |     | Sta   | tus |                   | R   |                                       |

| В          | 1  | 0  | . 1        | 1  | ×           | ×          | ×            | ×    | ×   | ×     | ×   | ×                 | w   | Clear Light-Pen                       |

| С          | 1  | 1  | 0          | 0  | ×           | ×          | ×            | ×    | ×   | ×     | ×   | ×                 | w   | Preset Light-Pen (in CGA Mode)        |

| D          | 1  | 1  | 0          | 1  | ×           | ×          | Bank Address |      |     |       | w   |                   |     |                                       |

| E          | 1  | 1  | 1          | 0  |             |            | Bank Data    |      |     |       | w   |                   |     |                                       |

| F          | 1  | 1  | 1          | 1  |             | Control/ID |              |      |     |       |     |                   | R/W | *                                     |

NOTES:\_\_\_

- 1. The register marked with a "\*" symbol can be read when RREG = '1' (for a multi-tasking OS; see subsection 3-6-15, "Address 29H").

- 2. Registers D and E (Bank Address and Data) can only be written when the IOSEL pin is '0'. (Furthermore, they cannot be written unless Bit 7 (Protect) of the Control/ID Register is '1'.)

- 3. When a write-only register is read, it will assume high-impedance status (and the BDIR pin will also output '0').

Writing to the registers is controlled by the IOW pin. (While  $IOW = 1^{\circ}$ , the contents of Data Bus CD0-CD7 are written to the registers). Reading of the registers is controlled by the IOR pin. (While  $IOR = 1^{\circ}$ , the data from the registers are output to Data Bus CD0-CD7.) With a 80 type CPU, writing to the registers is executed by the I/O OUT command, whereas reading of the registers is executed by the I/O IN command. A register is selected according to the lower four bits of the Address signal from the CPU at the A0-A3 pins.

When an I/O register has been read, the conditions for output to Data Bus CD0-CD7 are as follows: [(I/O Registers 8 + 9) x RREG + (I/O Registers A + F) + 6845 Data Register] x IOR

In all other cases, the I/O register will assume high-impedance status. The BDIR pin will also be set to '1' under the preceding conditions. Consequently, when PCDC is used as an MDA, the I/O Registers C, D, and E will be assigned for printer use by IBM PC; however, even when those registers are read, there is no fear of their data colliding on the Data Bus. If the IOSEL pin is set to a decode value that differs from "3BH" for monochrome use, any attempts to write to the Register Bank will be unsuccessful (That is, even if the IOSEL pin is decoded as "3BH", the registers will be protected by Bit 7 (Protect) of the Control/ID Register.), thereby maintaining the PCDC's compatibility with IBM PC.

## 3-1. 6845 INDEX/DATA REGISTERS

6845 performs such functions as the generation of Horizontal and Vertical Sync signals, generation of the Refresh address to the VRAM for storing the Display Data, cursor control, Light Pen detection, and so on.

| [  | l  | Index | <          |    | Reg.        | Dec Trees      |    |    |    | Da | ata |    |    |    | D (14) | Preset | Preset Mode         |

|----|----|-------|------------|----|-------------|----------------|----|----|----|----|-----|----|----|----|--------|--------|---------------------|

| A4 | Аз | A2    | <b>A</b> 1 | Ao | No.         | Reg. Type      | D7 | D6 | D5 | D4 | Dз  | D2 | D1 | Do | R/W    | Mode   | Pre:                |

| 0  | 0  | 0     | 0          | 0  | Ro          | Horiz. Total   |    |    |    | ·  |     |    |    |    | W      | Pre    | Preset value        |

| 0  | 0  | 0     | 0          | 1  | R1          | Horiz. Disp    |    |    |    |    |     |    |    |    | w      |        | Offset value        |

| 0  | 0  | 0     | 1          | 0  | R2          | Hsy. Position  |    |    |    |    |     |    |    |    | w      | OS     | Fix:                |

| 0  | 0  | 0     | 1          | 1  | R₃          | Sync. Width    | V3 | V2 | V1 | V٥ | Нз  | H2 | H1 | Ho | w      | Pre    | Non-Inter-          |

| 0  | 0  | 1     | 0          | 0  | R₄          | Vert. Total    |    |    |    |    |     |    |    |    | w      | Pre    | lace Mode<br>Blank: |

| 0  | 0  | 1     | 0          | 1  | R٥          | Vert. Adjust   | ×  | ×  | ×  |    |     |    |    |    | w      | Pre    | Use of 6845         |

| 0  | 0  | 1     | 1          | 0  | Re          | Vert. Disp     |    |    |    |    |     |    |    |    | w      |        | Register            |

| 0  | 0  | 1     | 1          | 1  | R7          | Vsy. Position  |    |    |    |    |     |    |    |    | w      | os     | û<br>When PRE = 1   |

| 0  | 1  | 0     | 0          | 0  | R٥          | Interlace      | ×  | ×  | ×  | ×  | ×   | ×  | ×  | s  | w      | Fix    |                     |

| 0  | 1  | 0     | 0          | 1  | Rø          | Max. Scan      | ×  | ×  | ×  |    |     |    |    |    | w      | Pre    |                     |

| 0  | 1  | 0     | 1          | 0  | <b>R</b> 10 | Cur. Start     | ×  | в  | Р  |    |     |    |    |    | w      | OS     |                     |

| 0  | 1  | 0     | 1          | 1  | <b>R</b> 11 | Cur. End       | ×  | ×  | ×  |    |     |    |    |    | w      | OS     |                     |

| 0  | 1  | 1     | 0          | 0  | R12         | Start Adr. (H) | ×  | ×  |    | -  |     |    |    |    | R/W    |        |                     |

| 0  | 1  | 1     | 0          | 1  | <b>R</b> 13 | Start Adr. (L) |    |    |    |    |     |    |    |    | R/W    |        |                     |

| 0  | 1  | 1     | 1          | 0  | <b>R</b> 14 | Cur. Adr. (H)  | ×  | ×  |    |    |     |    |    |    | R/W    |        |                     |

| 0  | 1  | 1     | 1          | 1  | R15         | Cur. Adr. (L)  |    |    |    |    |     |    |    |    | R/W    |        | (×:Don't care)      |

| 1  | 0  | 0     | 0          | 0  | <b>R</b> 16 | Light Pen (H)  | ×  | ×  |    |    |     |    |    |    | R      |        |                     |

| 1  | 0  | 0     | 0          | 1  | <b>R</b> 17 | Light Pen (L)  |    |    |    |    |     |    |    |    | R      |        |                     |

#### NOTES:\_

1. A11<sup>°</sup>O' will be output when a write-only register is read (and the BDIR pin will also output <sup>°</sup>1<sup>°</sup>).

- 2. When a read/write register is read, the registers marked with an "X" will output '0'.

- 3. Bit 7 of R4, R6, and R7 as well as V3-V0 of R3 are valid only when 45S = 1. (The default status after Reset is 45S = 0. See subsection 3-6-5, "Address 3FH.")

## 3-1-1. Index Register

The Index Register is a five-bit address register for specifying R0 to R17 of the 6845 Register. Prior to writing to or reading R0-R17, it is necessary to write the addresses to this register.

## 3-1-2. Horizontal Total Register (Ro)

This register sets the cycle for horizontal scanning. When the total quantity of horizontal characters is "M", "M-1" shall be written to this register. In Interlace Mode, the "M" value must be an even number. Set this "M" value to an even number in High Resolution Text Mode as well (because if the value is set to an odd number, it will be regarded as "an odd number + 1").

## 3-1-3. Horizontal Displayed Register (R1)

This register sets the total quantity of display characters per line, and is set with an arbitrary value that is smaller than the total quantity of horizontal characters. In High Resolution Text Mode, an even number shall be set (because the setting of an odd number will be regarded as "an odd number - 1").

## 3-1-4. Horizontal Sync Position Register (R2)

This register sets the position of the Horizontal Sync signal, and is set in horizontal character units. An arbitrary value that is smaller than the total quantity of horizontal characters can be set. When the horizontal sync position is set to the "Hth" character, "H - 1" will be written to this register.

## 3-1-5. Sync Pulse Width Register (R3)

This register sets the respective pulse widths for Horizontal and Vertical Sync signals. The pulse width for Horizontal Sync signals is set in horizontal character units within a range of 1-15 ("0" cannot be used) at the lower four bits of this register. The pulse width for Vertical Sync signals is set in horizontal scan units at its upper four bits. When  $45S = 1^{\circ}$ , a value in the 1-16 range (an "0" setting will be regarded as "16") can be set at the upper four bits; when  $45S = 0^{\circ}$ , the upper four bits will be set to "16" regardless of their contents.

## 3-1-6. Vertical Total Register (R4)

This register sets the cycle for vertical scanning. When the total quantity of character-lines is "N", "N - 1" will be written to this register.

## 3-1-7. Total Raster Adjust Register (R5)

This register adjusts the total quantity of scan lines per field, and the raster quantity that is appended to the end of one field shall be set within a 0-31 range. Write "0" when a two-screen panel is in use. (In case the software prevents "0" from being written, assume Preset Mode then set Vert. Adjust to "0".)

## 3-1-8. Vertical Displayed Register (R6)

This register sets the time period for vertical display, and shall be set in character-line units to an arbitrary value that is smaller than the total quantity of vertical characters.

#### 3-1-9. Vertical Sync Position Register (R7)

This register sets the position of the Vertical Sync signal, and is set in character-line units. An arbitrary value that is smaller than the total quantity of vertical characters can be set. When the vertical sync position is set to the "Vth" line, "V - 1" will be written to this register.

NOTE: \_\_\_\_

```

When 45S = 1^{\circ}, writing to Bit 7 of R4, R6 and R7 can be performed; when 45S = 0^{\circ}, however, 0^{\circ} will be compulsorily written.

```

## 3-1-10. Interlace Register (R8)

This register specifies the Raster Scan Mode. Setting the LSB "S" to 0 will select Non-Interlace Mode; setting it to 1 will select Interlace Mode. (The Interlacing & Video Mode is not supported.) The CUDISP Skew and DISPTMG Skew functions are also not supported.)

In Interlace Mode, scanning will be performed so that the rasters of the odd fields will interpolate those of the even fields.

In Non-Interlace Mode, these rasters of even and odd fields follow the same track.

The Panel can only use the Non-Interlace Mode.

## 3-1-11. Maximum Raster Address Register (R9)

This register sets the quantity of rasters for one character-line, including the space between lines. When the raster quantity for one line is "RN", "RN - 1" will be written to this register.

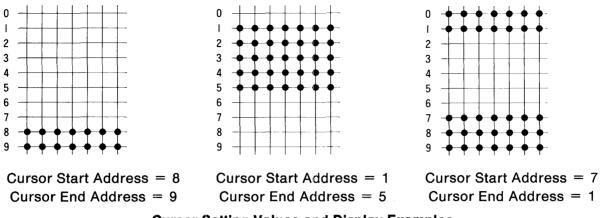

## 3-1-12. Cursor Start Raster Register (R10)

This register specifies the Raster address for starting the cursor display as well as specifying the cursor display mode. The Raster address for starting cursor display is set at the lower five bits of this register, and the cursor display mode is specified at its higher two bits.

care)

| D6<br>B | D5<br>P | Cursor Display Modes                                       |            |

|---------|---------|------------------------------------------------------------|------------|

| ×       | 0       | Cursor blinks in 16-field cycles (ON : OFF ratio = $1:1$ ) |            |

| 0       | 1       | Cursor is not displayed                                    |            |

| 1       | 1.      | Cursor blinks in 32-field cycles (ON : OFF ratio $= 1:3$ ) | ) (×:Don't |

## 3-1-13. Cursor End Raster Register (R11)

This register sets the Raster address for ending the cursor display.

#### **Cursor Setting Values and Display Examples**

The Cursor Start Address and Cursor End Address will generally satisfy the following condition:

$0 \leq$  Cursor Start Address  $\leq$  Cursor End Address  $\leq$  Maximum Raster Address

However, in case the relationship between the Cursor Start and End Addresses is the opposite of the above, the cursor will be displayed as split into top and bottom halves. If only the Cursor End Address is larger than the Maximum Raster Address, the cursor will be displayed at all rasters (in character units). Conversely, if only the Cursor Start Address is larger than the Maximum Raster Address, the cursor will not be displayed.

## 3-1-14. Start Address Registers (R12, R13)

These registers set the Memory Address for starting the screen display. (R12 is the high-order portion of the address, and the total address consists of 14 bits). By dynamically rewriting the contents of these registers, paging and scrolling can be easily performed.

## 3-1-15. Cursor Address Registers (R14, R15)

These registers set the Display Address of the cursor. (R14 is the higher-order portion of the address, and the total address consists of 14 bits.)

## 3-1-16. Light Pen Registers (R16, R17)

These registers memorizes the Detection Address for the Light Pen. (R16 is the higher-order portion of the address, and the total address consists of 14 bits.) Since the Memory Address at the rising edge of the Light Pen Strobe signal ( $\overline{LDT}$  pin) is memorized, it is necessary to consider the delay of the Light Pen Detection Circuit and rectify the Memory Address. With LCDs and similar panels, this register is invalid (that is, the register can be read, but its contents will have no meaning).

## 3-1-17. Precautions on Usage

Be sure to write to the Cursor Address Register during the horizontal/vertical retrace timing, and write to the Start Address Register during the displayed timing. For the other registers, avoid writing during display as much as possible (in case writing is performed, a momentary flickering of the screen may occur). Especially in the case of the Horizontal Total Register, Vertical Total Register, Interlace Register, and Maximum Raster Address Register, the scanning cycles are likely to become chaotic.

If Bit 3 (Enable Video) of the Mode Register is set to '0', the display will be switched OFF, eliminating the need to consider the timing for writing to the registers.

The CRT Controller 6845 is available in two types, 6845 and 6845S, which are slightly different. The relationship and differences between these two types and the PCDC are summarized as follows:

| Different Functions                                                  | 6845                                                                           | 6845S                                     | PCDC                                       |  |  |  |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------|--|--|--|

| Interlacing & Video Mode                                             | The method for setting the qu<br>the quantity of rasters per lir<br>different. | No support                                |                                            |  |  |  |

| Vertical Sync signal<br>Pulse width                                  | Fixed to 16-raster width                                                       | Programmable from 1 to 16                 | Similar to 6845 when 45S='0'               |  |  |  |

|                                                                      |                                                                                |                                           | Similar to 6845S when 45S='1'              |  |  |  |

| Skew function                                                        | None                                                                           | DISPTMG and CUDISP have the Skew function | None                                       |  |  |  |

| Start Address                                                        | Reading impossible                                                             | Reading possible                          | Reading possible                           |  |  |  |

| Cursor display (When Start<br>Address is larger than End<br>Address) | Displayed split into top and bottom halves                                     | No display                                | Displayed split into top and bottom halves |  |  |  |

| Cursor Display Mode<br>(When B = P = 0)                              | Cursor does not blink                                                          | Cursor does not blink                     | Cursor blinks every 16 fields              |  |  |  |

| Vertical-direction setting                                           | 7 bits                                                                         | 7 bits                                    | 7 bits when $45S = 0$                      |  |  |  |

| Bit quantity of registers                                            |                                                                                |                                           | 8 bits when 45S='1                         |  |  |  |

#### NOTES:\_\_\_

- 1. The registers for setting the vertical direction indicate the Vertical Total Register (R4), Vertical Displayed Register (R6), and Vertical Sync Position Register (R7). (With PCDC, the bits up to Bit 8 can be set.)

- 2. The Default status after RESET of PCDC is  $45S = 0^{\circ}$ .

- 3. The IBM-PC sets the cursor display mode at B = P = 0 while enabling the 16 field blinking in the external circuit.

### 3-1-18. Sample Setting Values using IBM PC

| Reg. |              |       | CGA   |            | Herc    | ules    |

|------|--------------|-------|-------|------------|---------|---------|

| No.  | Reg. Type    | Те    | ext   | Graphic    | Text    | Graphic |

|      |              | 80×25 | 40×25 |            | 80 × 25 |         |

| R O  | Horiz.Total  | 71    | 38    | 38         | 61      | 35      |

| RI   | Horiz.Disp   | 50    | 28    | 28         | 50      | 2D      |

| R 2  | Hsy.Position | 5A    | 2D    | 2D         | 52      | 2E      |

| R 3  | Sync.Width   | 0A    | 0A    | 0A         | 0F      | 07      |

| R 4  | Vert.Total   | IF    | IF    | <b>7</b> F | 19      | 5B      |

| R 5  | Vert.Adjust  | 06    | 06    | 06         | 06      | 02      |

| R 6  | Vert.Disp    | 19    | 19    | 64         | 19      | 57      |

| R 7  | Vsy.Position | IC    | IC    | 70         | 19      | 57      |

| R 8  | Interlace    | 02    | 02    | 02         | 02      | 02      |

| R 9  | Max.Scan     | 07    | 07    | 01         | 0D      | 03      |

| R 10 | Cur.Start    | 06    | 06    |            | 0B      | —       |

| RII  | Cur.End      | 07    | 07    |            | OC      |         |

(in Hexadecimal)

Generally, the values listed in the preceding table are the setting values for IBM PC. In the following, the horizontal/vertical cycle shall be calculated from the master clock frequency.

1. Since the master clock frequency of CGA is 14.318 MHz, a character unit in Graphics Mode consists of 16 PELs, and R<sub>0</sub> (Horiz. Total) is "56" in decimal, the horizontal cycle will be as follows:

$\frac{14.318/16}{56+1} = 0.01569956 \text{ MHz} \rightarrow 15.7 \text{ KHz}$

R4 (Vert. Total), R5 (Vert. Adjust), and R9 (Max. Scan, which determines the bank number for bank switching) are respectively "127", "6", and "1" in decimal, and the quantity of scan lines becomes  $(127 + 1) \times (1 + 1) + 6 = 262$  lines, so that the vertical cycle will be as follows:

$$\frac{15.69956}{262} = 0.05992 \text{ KHz} \rightarrow 59.9 \text{ Hz}$$

These values are close to the values of Horizontal Cycle = 15.75 KHz and Vertical Cycle = 60 Hz, which are the specifications of the IBM color monitor.

Since the master clock frequency of HGC is 16.257 MHz, the font configuration in Text Mode is 9 by 14 PELs (Max. Scan is determined according to the 14 PELs in the vertical direction), and R0 is "97" in decimal, the horizontal cycle will be as follows:

$$\frac{16.257/9}{97+1} = 0.01843197 \text{ MHz} \rightarrow 18.43 \text{ KHz}$$

R4, R5, and R9 are respectively "25", "6", and "13" in decimal, and the quantity of scan lines becomes  $(25 + 1) \times (13 + 1) + 6 = 370$  lines, so that the vertical cycle will be as follows:

$$\frac{18.43197}{370} = 0.049816 \text{ KHz} \rightarrow 49.8 \text{ Hz}$$

These values are close to the values of Horizontal Cycle = 18.432 KHz and Vertical Cycle = 50 Hz, which are the specifications of the IBM monochrome monitor.

## **3-2. MODE REGISTER (I/O Register 8)**

| (Cle | are | d by RESET)              | (Can be read when RREG = '1')   |  |  |  |  |

|------|-----|--------------------------|---------------------------------|--|--|--|--|

| Bit  | 0   | High Resolution Text     | (Fixed to "1" in Hercules Mode) |  |  |  |  |

|      | 1   | Graphics                 |                                 |  |  |  |  |

|      | 2   | Black/White              | (Fixed to "1" in Hercules Mode) |  |  |  |  |

|      | 3   | Enable Video             |                                 |  |  |  |  |

|      | 4   | High Resolution Graphics | (Fixed to "1" in Hercules Mode) |  |  |  |  |

|      | 5   | Blink                    |                                 |  |  |  |  |

|      | 7   | Page Set                 | (Valid only in Hercules Mode)   |  |  |  |  |

|      |     |                          |                                 |  |  |  |  |

NOTE: \_\_\_\_

In Hercules Mode, Bit 1 (Graphics) can only be written when Bit 0 of the Control/ID Register is 1. Bit 7 (Page Set) can only be written when Bit 1 of the Control/ID Register is 1.

This register sets the Operating Mode. The function of each bit is described as follows:

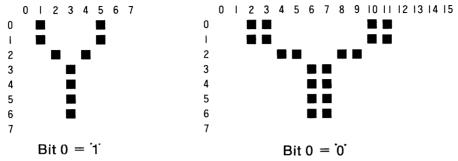

**Bit 0:** Selects the text resolution for Text Mode (Bit 1 (Graphics) =  $^{\circ}0^{\circ}$ ). When Bit 0 = 1 (High Resolution Text Mode), the data from the CG-ROM is sequentially displayed in PEL units; however, when Bit 0 =  $^{\circ}0^{\circ}$  (Low Resolution Text Mode), the data is expanded so that two PELs (a Double PEL) are displayed at a time.

**Bit 1:** Selects either Text Mode or Graphics Mode. Setting Bit 1 = '1' selects the Graphics Mode.

- **Bit 2:** Selects either Color or B/W Mode. This bit is only valid for Composite signals and 2 Bit Graphics Mode, however, and RGB output will result in color display regardless of this bit's set value. When Bit 2= '1', the B/W Mode will be assumed and the Color Burst signals for Composite signals will not be output.

- **Bit 3:** Controls the Display ON/OFF status. When switching modes, be sure to switch the display OFF for a fixed period to avoid the display of disorderly contents on the screen. When Bit 3 = '0', the display will be switched OFF. At this time, the display of the cursor and border will be continued.

- **Bit 4:** Selects the resolution of Graphics Modes. Setting Bit 4=1 selects High Resolution Graphics Mode. With IBM PC, Bit 4=1 will result in a 640 by 200 PEL Graphics Mode and Bit 4=0 will result in a 320 by 200 PEL Graphics Mode.

- **Bit 5:** Controls the blinking of text (valid only in Text Mode). When Bit  $5 = 1^{\circ}$ , the MSB of Attribute assumes blinking control and one out of eight colors can be selected for the text background. When Bit  $5 = 0^{\circ}$ , blinking will be disabled and one out of 16 colors can be selected for the text background. A blink cycle consists of 32 fields.

- **Bit 7:** The Hercules Mode employs 32K bytes for one screen. The 64K-byte FULL Mode has the capacity for two pages, however, and the page is selected by Bit 7. When Bit 7 = 1, the second page will be displayed.

The mode settings for IBM PC are summarized below. (For details on the Operating modes, see CHAPTER 4, "OPERATING MODES.")

| 5 | 4            |   | Reg | <b>]</b> .<br>1 | 0 | MODE                    | IBM-PC<br>Standard Mode |

|---|--------------|---|-----|-----------------|---|-------------------------|-------------------------|

| 1 | ×            | 1 |     | 0               | 0 | Low Resolution Text     | 40 x 25 A/N             |

| 1 | ×            | 1 |     | 0               | 1 | High Resolution Text    | 80 x 25 A/N             |

| × | 0            | 1 |     | 1               | × | Low Resolution Graphic  | 320 x 200 GR            |

| × | 1            | 1 | 1   | 1               | × | High Resolution Graphic | 640 x 200 GR            |

|   | Enable Video |   |     |                 |   |                         | × : Don't care          |

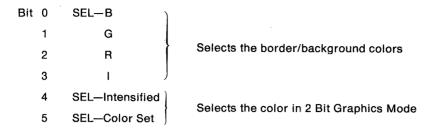

This register performs color specification of the border color in Text Mode or color selection in Graphics Modes.

- **Bits 0-3:** Specify the border color in Text Mode or Graphics Modes (excluding 1 Byte High Resolution Graphics Mode). In 2 Bit (four-color) Graphics Mode, they also specify the background color. In 1 Byte High Resolution Graphics Mode, they also specify the color of the PELs. Bits 0 to 3 respectively specify B, G, R, and Intensity.

- Bit 4: Specifies the intensity of Colors 1-3 in 2 Bit (four-color) Graphics Mode.

- **Bit 5:** Selects one of two color settings (SET1 or SET2) in 2 Bit (four-color) Graphics Mode. Setting Bit 5='1' selects SET2. When Bit 2 of the Mode Register is '1', both SET1 and SET2 will become identical.

The colors in 2 Bit (four-color) Graphics Mode are summarized as follows:

| ſ |    |    | Color      | SET1      |          |          |          | SET2      |          |          |          | B/W = 1   |          |          |          |

|---|----|----|------------|-----------|----------|----------|----------|-----------|----------|----------|----------|-----------|----------|----------|----------|

|   | Cı | C0 | Color      |           | R        | G        | В        | I         | R        | G        | в        | 1         | R        | G        | в        |

|   | 0  | 0  | Background | SEL.      | SEL<br>R | SEL<br>G | SEL<br>B | SEL<br>I  | SEL<br>R | SEL<br>G | SEL<br>B | SEL       | SEL<br>R | SEL<br>G | SEL<br>B |

|   | 0  | 1  | Color 1    | SEL<br>IN | 0        | 1        | 0        | SEL<br>IN | 0        | 1        | 1        | SEL<br>IN | 0        | 1        | 1        |

|   | 1  | 0  | Color 2    | SEL<br>IN | 1        | 0        | 0        | SEL<br>IN | 1        | 0        | 1        | SEL<br>IN | 1        | 0        | 0        |

|   | 1  | 1  | Color 3    | SEL<br>IN | 1        | 1        | 0        | SEL<br>IN | 1        | 1        | 1        | SEL<br>IN | 1        | 1        | 1        |

NOTES:\_\_\_\_

1. The background color is specified by Bits 0 to 3.

2. SEL IN is equivalent to Bit 4, and the SET1/SET2 selection is performed by Bit 5.

## 3-4. STATUS REGISTER (I/O Register A)

| Bit 0 | Hsync             | <b>Display Timing</b> |  |  |

|-------|-------------------|-----------------------|--|--|

| 1     | Light Pen Trigger | Light Pen Trigger     |  |  |

| 2     | Light Pen Switch  | Light Pen Switch      |  |  |

| 3     | Video             | Vsync                 |  |  |

| 7     | Vsync             |                       |  |  |

|       | ſ                 | 1                     |  |  |

|       | Hercules Mode     | CGA Mode              |  |  |

This read-only register is used to know the LSI internal status. For a large number of 6845 registers, including the Cursor Address Register, it is advisable to perform writing during the horizontal/vertical retrace timing; and it is advisable to write to the Start Address Register during the displayed timing. It is thus necessary to know the LSI internal status (retrace timing or displayed timing). At this time, the Status Register shall be used. (If Bit 3 (Enable Video) of the Mode Register is '0', the display will be switched OFF, eliminating the need for considering the timing for writing to the registers.) The functions of each bit are as follows:

- **Bit 0:** Indicates the timing of Horizontal Sync signals in Hercules Mode (when Bit 0 = 1), or indicates the displayed timing in CGA Mode (indicating that displayed timing is in process when Bit 0 = 0).

- **Bit 1:** Indicates the contents of the Light Pen flip-flop which shows whether or not the Light Pen Address has been newly memorized at the rising edge of the Light Pen Strobe signal. (LDT pin) Bit 1 = 1 indicates the memorized status.

- **Bit 2:** Indicates the status of the Light Pen's Switch signal (LSW pin). (For IBM PC, Bit 2= 0 indicates the Switch ON status.) Since chattering prevention circuit is not built-in, chattering must be eliminated by software.

- **Bit 3:** Indicates that Video Dot data is being output in Hercules Mode. This bit is for testing purposes and a '1' setting indicates that the data is being output. It indicates the Vertical Sync signal in CGA Mode (when Bit 3 = 1).

- **Bit 7:** Indicates the Vertical Sync signal only in Hercules Mode (when Bit 7 = '1'). ('0' will be output in CGA Mode.)

## 3-5. CLEAR/PRESET LIGHT PEN

| Preset Light Pen<br>Clear Light Pen | I/O B      | I/O B    |

|-------------------------------------|------------|----------|

|                                     | 1          | Ť        |

| Her                                 | cules Mode | CGA Mode |

The Light Pen flip-flop that indicates whether the Light Pen Address has been newly memorized can be cleared by writing to I/O Register B (any data can be written). Setting of the Light Pen flip-flop can be accomplished by writing to I/O Register 9 in Hercules Mode or to I/O Register C in CGA Mode. (Since this bit is for testing purposes, any data can be written at such time.)

The procedure for reading the Light Pen Address is as follows:

- 1. Clear the Light Pen flip-flop by writing to Register B.

- 2. Read to Status Register to know whether or not the Light Pen flip-flop was set at the rising edge of the Light Pen Strobe signal.

- If it was not set, repeat Step 2 above.

If it was set, read the Light Pen Address (R16 and R17) then return to Step 1.

| Address |          |    |        |        |        | Data                               |                                                   |

|---------|----------|----|--------|--------|--------|------------------------------------|---------------------------------------------------|

| A5      | A4       | Аз | A2     | A1     | Ao     | D7 D6 D5 D4 D3 D2 D1 D0            | The bank address is automatically incremented     |

| 0       | 0        | 0  | 0      | 0      | 0      | × × × × × R2 R1 R0                 | (each time data is written in (I/O register – E). |

| 0       | 0        | 0  | 0      | 0      | 1      | × G2 G1 G0 × B2 B1 B0              | Color Palette #0                                  |

|         |          | (  |        |        |        |                                    |                                                   |

| -       |          |    |        |        | _      |                                    |                                                   |

| 0       | 1        | 1  | 1      | 1      | 0      | × × × × × R2 R1 R0                 | Color Palette #15                                 |

| 0       | 1        | 1  | 1      | 1      | 1      | × G2 G1 G0 × B2 B1 B0              |                                                   |

| 1       | 0        | 0  | 0      | 0      | 0      | Duty                               |                                                   |

| 1       | 0        | 0  | 0      | 0      | 1      | H size                             |                                                   |

| 1       | 0        | 0  | 0      | 1      | 0      | V adj                              |                                                   |

| 1       | 0        | 0  | 0      | 1      | 1      | SCT SCU H adj                      |                                                   |

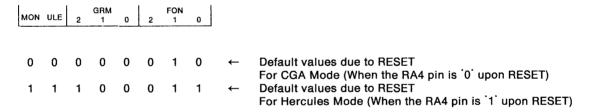

| 1       | 0        | 0  | 1      | 0      | 0      | MON ULE 2 1 0 2 1 0<br>CLK         |                                                   |

| 1       | 0        | 0  | 1      | 0      | 1      | PB PAG                             |                                                   |

| 1       | 0        | 0  | 1      | 1      | 0      |                                    |                                                   |

| 1       | 0        | 0  | 1      | 1      | 1      | 1 0 IEN EXTS INH ACM CPLE PRE      |                                                   |

| 1       | 0        | 1  | 0      | 0      | 0      | SWC VST SSY SSCK H/E R/M 1 0       |                                                   |

| 1       | 0        | 1  | 0      | 0      | 1      | STBY RREG ESIO 4 3 2 1 0<br>TST SS |                                                   |

| 1       | 0        | 1  | 0      | 1      | 0      | 2 1 0 4 3 2 1 0<br>CON             |                                                   |

| 1       | 0        |    | 0      | 1      | 1      |                                    | Der )                                             |

| 1       | 1        | 0  | 0      | 0      | 0      | Horiz. Total                       | Pre                                               |

| 1       | 1        | 0  | 0      | 0<br>1 | 1      | Hsy. Offset                        | os                                                |

| 1       | 1        | 0  | 0      | 1      | 0      | Vsy. Offset                        | OS Dec                                            |

| 1<br>1  | 1        | 0  | 0<br>1 | 1<br>0 | 1<br>0 | Sync. Width<br>Vert. Total         | Pre   6845 Preset Data (For Text) Pre             |

| 1       |          | 0  | 1      | 0      | 1      | × × × Vert. Adjust                 | Pre                                               |

| 1       | '  <br>1 | 0  | 1      | 1      | 0      | × × × Max. Scan                    | Pre                                               |

| 1       |          | 0  | 1      | 1      | 1      | F/O TDS Cur. Offset                |                                                   |

| 1       | 1        | 1  | 0      | 0      | 0      | Horiz. Total                       | Pre )                                             |

| 1       | 1        | 1  | 0      | 0      | 1      | Hsy. Offset                        | os                                                |

| 1       | 1        | 1  | 0      | 1      | 0      | Vsy. Offset                        | os                                                |

| 1       | 1        | 1  | 0      | 1      | 1      | Sync. Width                        | Pre                                               |

| 1       | 1        | 1  | 1      | 0      | 0      | Vert. Total                        | 6845 Preset Data (For Graphics) Pre               |

| 1       | 1        | 1  | 1      | 0      | 1      | GOE HDB LAS Vert. Adjust           | Pre                                               |

| 1       | 1        | 1  | 1      | 1      | 0      | × × × Max. Scan                    | Pre                                               |

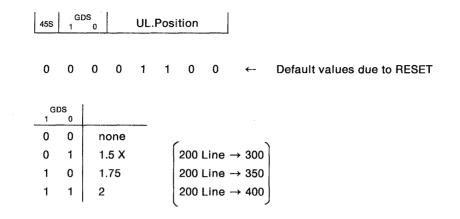

| 1       | 1        | 1  | 1      | 1      | 1      | 458 GDS UL. Position               |                                                   |

The expansion functions from IBM PC are organized within the Register Bank by Registers D and E. Register D serves to specify the address of a register bank, and Register E serves to set the data. (The configuration is similar to that of the 6845 Index/Data Register.) Since the addresses of the register banks are provided with an Auto Increment function, the mere setting of the first address will cause the successive addresses to be automatically incremented by one each time data is written to Register E. In the case of the Color Palette and 6845 Preset Data, this convenient function enables data to be consecutively written.

Due to their relationship to the expansion functions from IBM PC, Registers D and E are provided with software protection by a double-protection feature. Data can be written to the registers only in the case both the IOSEL pin is '0' and Bit 7 (Protect) of the Control/ID Register is '1'. Because the contents written to the register are valid regardless of the IOSEL and Bit 7 (Protect) status, IBM PC software can be run with confidence if the IOSEL = '1' and Bit 7 (Protect) = '0' settings are implemented as soon as initialization is completed.

## 3-6-1. Color Palette (Addresses 00H-1FH)

Regarding the PEL color data IRGB as input, the Color Palette has a 16-address x 9-bit data capacity with respect to the data that is to be converted to the PEL color data which will actually be displayed. Consequently, if three bits each of the nine-bit data are respectively assigned to R, G, and B, then and a linear RGB monitor is connected via a digital-to-analog converter, any 16 out of 512 colors can be simultaneously displayed. If an EGA monitor is connected, six bits can be used as a Color Palette for a simultaneous display of any 16 out of 64 colors. And if an IBM color monitor is connected, four bits can be used as a Color Lookup Table. In any of the above cases, CPLE must be set to '1' (For the linear RGB monitor, the SWC = '1' setting is also required.) When CPLE = '0', the Color Palette will not operate and the PEL color data IRGB will be directly output. The functions of each bit of the Color Palette and their method for use with each monitor is summarized below:

| Bit Name for<br>Color Palette | Linear RGB<br>Monitor | EGA Monitor | IBM Color<br>Monitor | Panel                    |

|-------------------------------|-----------------------|-------------|----------------------|--------------------------|

| R2                            | Red 2 <sup>2</sup>    |             | -                    | Intensity                |

| R1                            | Red 2 <sup>1</sup>    |             |                      | Intensity 2 <sup>3</sup> |

| Ro                            | Red 2 <sup>0</sup>    | Secondary B |                      | Intensity 2 <sup>2</sup> |

| G2                            | Green 2 <sup>2</sup>  | Secondary R |                      | Intensity 2 <sup>1</sup> |

| G1                            | Green 2 <sup>1</sup>  |             |                      | Intensity 2 <sup>0</sup> |

| Go                            | Green 2 <sup>0</sup>  | Secondary G | I                    |                          |

| B2                            | Blue 2 <sup>2</sup>   | Primary R   | R                    |                          |

| Bı                            | Blue 2 <sup>1</sup>   | Primary G   | G                    |                          |

| Bo                            | Blue 2 <sup>0</sup>   | Primary B   | В                    |                          |

#### NOTE: \_

The monochrome monitor can also be used in a manner similar to the Panel. Intensity is used with a monochrome monitor or a plasma display capable of gray scaling.

For the Panel, the Color Palette is also used for converting the PEL color data either to a specified half-tone or to a specified hatching pattern. (With a monochrome monitor, the Color Palette can similarly be used for converting to a half-tone or a hatching pattern.) Since the Panel cannot perform

color display, in the case CGA software has been executed, the color data will be indistinguishable unless the color data is converted to some half-tone or hatching pattern. The Color Palette is used for correspondence of the colors with the half-tone and hatching patterns (and must be used with CPLE = 1).

One datum of the Color Palette consists of two bytes, and writing of the data must be performed in the sequence of an even address byte followed by an odd address byte. The data will actually become valid for the Color Palette upon writing an odd address byte.

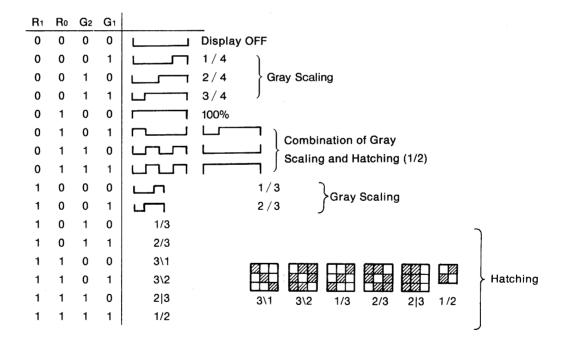

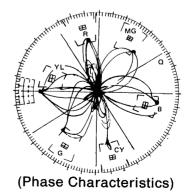

## 3-6-2. Gray Scaling and Hatching

In case of display of the CGA software, the Panel (including Monochrome monitors) will be incapable of color display and gray scaling, so the display pattern cannot be distinguished. In such cases, by synchronizing Fields 3 and 4 and changing the transmission frequency of the display data, a graded display can be achieved and converted to a hatching pattern which deals with the color display problem. Because the response rate of an LCD is slow, this method for applying a graying scale is very effective. But the use of a hatching pattern is recommended because flickering of a graying scale will result when a quick responsive papel (plasma display, EL or monochrome monitor) is used. When R1-G1 is set at the upper four bits of the Color Palette, the display will be converted to gray scaling and Hatching according to the below correspondence. (A combined display of gray scaling and hatching is also possible.)

With CGA graphics software, a four-color display is adequate, so it is recommended that the user sets the gray scaling and hatching of his/her own preference. (Since a maximum 16-color display is possible in Text Mode, it is recommended that MON be set to 1 to convert to a monochrome display, then a clear display be implemented (Set Black as Display OFF and White as 100%.).)

With a monochrome monitor or a Panel capable of Intensity input, if IEN is set to 1 and Intensity is set for output to LD7-LD4, a good gray scaling or hatching display can be achieved. (A double-sequence input can be made to the monitor so high or low intensity can be used even for hatching alone.)

#### 3-6-3. 6845 Preset Data (Addresses 30H-36H, 38H-3EH)

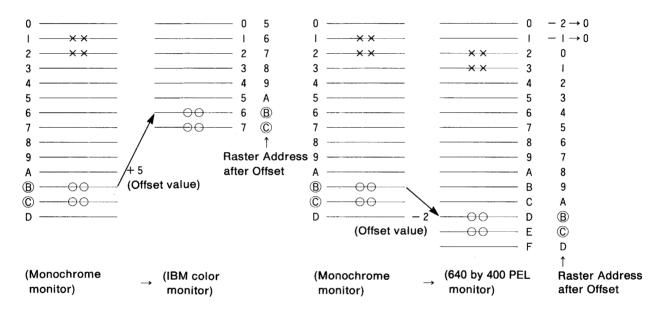

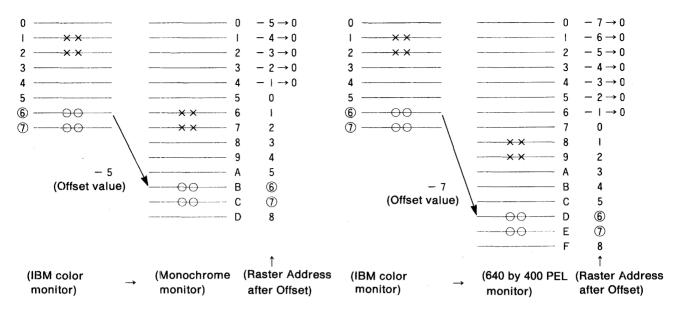

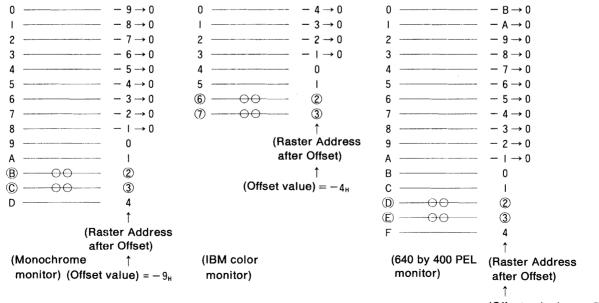

In cases of executing CGA software with an IBM color monitor or executing Hercules software with an IBM monochrome monitor, the software and monitor form a standard combination. In such cases, proper operation can be achieved by setting PRE = 0 (Default status after RESET) and using the 6845 Register as is. In cases of executing CGA software with an IBM monochrome monitor or executing CGA software (for 640 by 200 PEL display) with a display having a 640 by 400 PEL display area, it will become necessary to convert the data for 6845 Register to values suitable for the monitor being used. Since certain software may switch often between Text and Graphics Modes, merely initializing the 6845 Register will not result in proper operation in some cases. (The 6845 is rewritten upon changing modes, resulting in improper operation.) To cope with this problem, the 6845 Preset Data is provided. (There are two types of Preset Data each for the Text and Graphics Modes, so proper operation is ensured even if the mode is switched.) That is, the registers related to the horizontal and vertical cycles, which are fixed values according to the monitor (The values cannot be rewritten by software. With the IBM PC software, however, the values written to 6845 and those suitable for the monitor are different.), are set to Preset values (When PRE = 1 in Preset Mode, the Raster Scan Mode will always be fixed to Non-Interlace Mode.) then used in place of the 6845 Registers (thereby enabling the setting of horizontal and vertical cycles that are suitable for the monitor in use). Moreover, the Offset value is introduced to the registers related to the horizontal/vertical sync position and the Cursor Start/End Raster Addresses, which are values that can be rewritten by software but will not directly match the monitor in use, so that the contents of the 6845 Registers will be shifted by this Offset value for use. Furthermore, the other registers, which have a high possibility of being rewritten by software but can be used directly with no problem, the 6845 Registers shall be used as they are.

The 6845 Preset Data is only valid when PRE = 1 in Preset Mode. The Preset value for the Horizontal Total and the Offset value for the Horizontal Sync Position should be written with values in High Resolution Text Mode. In Low Resolution Text Mode, these values will be automatically halved for use.

#### 3-6-3-1. Horiz. Total (Addresses 30н, 38н)

This is the Preset value for the Horizontal Total Register ( $R_0$ ). In Preset Mode, this value is used in place of the  $R_0$  value. Its setting procedure is identical to that for the 6845 Register  $R_0$ .

#### 3-6-3-2. Sync. Width (Addresses 33н, 3Вн)

This is the Preset value for the Sync Pulse Width Register (R3). In Preset Mode, this value is used in place of the R3 value. Its setting procedure is identical to that for the 6845 Register R3. (In Preset Mode, this function is equivalent to the  $45S = 1^{\circ}$  status, regardless of the 45S setting.)

#### 3-6-3-3. Vert. Total (Addresses 34H, 3CH)

This is the Preset value for the Vertical Total Register (R4). In Preset Mode, this value is used in place of the R4 value. Its setting procedure is identical to that for the 6845 Register R4.

#### 3-6-3-4. Vert. Adjust (Addresses 35H, 3DH)

This is the Preset value for the Total Raster Adjust Register (R5). In Preset Mode, this value is used in place of the R5 value. Its setting procedure is identical to that for the 6845 Register R5.

#### 3-6-3-5. Max. Scan (Addresses 36н, 3Ен)

This is the Preset value for the Maximum Raster Address Register (R9). In Preset Mode, this value is used in place of the R9 value. Its setting procedure is identical to that for the 6845 Register R9.

Even in cases where the monitor and software do not form the standard combination, this register enables the use of a font suitable to the monitor. For example, CGA software that employs a font of an 8 by 8 PEL matrix can be displayed on a monochrome monitor that uses a 9 by 14 PEL matrix (when this register (Address 36H) is set to 0DH.)

#### 3-6-3-6. Hsy. Offset (Addresses 31н, 39н)

This is the Offset value for the Horizontal Sync Position Register (R2). In Preset Mode, this value is added to the 6845 Register R2 value for use. Since the Offset value is expressed in two's complements, it can be set in the range of -128 to +127. In the case an underflow occurs due to the offset, the sync position is regarded as 00H. Attention is required because no countermeasures are provided in case of an overflow. If no offset is desired, write 00H to the Offset value.

#### 3-6-3-7. Vsy. Offset (Addresses 32H, 3AH)

This is the Offset value for the Vertical Sync Position Register (R7). In Preset Mode, this value is added to the 6845 Register R7 value for use. Since the Offset value is expressed in two's complements, it can be set in the range of -128 to +127. (Care is necessary when a negative value will be set, because unless such setting is performed with 45S set to '1', '1' will not be written to its MSB.) In the case an underflow occurs due to the offset, the sync position is regarded as 00H. Attention is required because no countermeasures are provided in case of an overflow. If no offset is desired, write 00H to the Offset value.

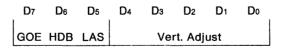

#### 3-6-3-8 Address 3DH

(GOE, HDB, and LAS are cleared by resets.)

#### (1) LAS: Output the preset values for the light pen address

With multitasking software such as MS Windows or Sidekick, it is necessary to know whether display is handled in A/N mode or in graphics mode. In the PCDC when RREG goes to '1', it is possible to read the mode registers, etc. but on CGA boards for the IBM-PC, this function is lacking so the mode is inferred with the light pen address. (When the software operates

through the BIOS, the current mode is written in the BIOS RAM, so there is no need for such inference, but some software (for example, Lotus 1-2-3) changes the mode directly without going through the BIOS, so this type of inference is necessary.) For example, such as MS windows when the start of display is detected from the display timing status, the light pen address is latched by the preset light pen (I/O C) and the address (the value near the start address (R12, R13) of the 6845) at the start of display is read in. In addition, when the rising edge of the Vsy status is detected, the light pen address is latched by the preset light pen address at the end of display is read in. The current display mode is inferred from the difference between the address at the end of display and the address at the start of display.

Sidekick assumes 0000H as the start address for the 6845, latches the light pen address with the preset light pen when the falling edge of the Vsy status is detected to read in the current address, and infers the current display mode from this address. Thus when the progress of addresses differs from that for a CRT, as it does for example for LCDs that are divided into top and bottom halves, then the special software compatibility is lost and misoperation occurs. The way that this problem is handled is that when LAS is set to '1' the preset values are output to the light pen address for each mode and the system operates just as if a CRT were connected. Here are the preset values.

| Display mode | During the vertical retrace | During display |

|--------------|-----------------------------|----------------|

| 40 x 25 A/N  | 04××H                       | 0 0 x x H      |

| 80 x 25 A/N  | 09xxH                       | 0 0 x x H      |

| Graphics     | 11xxH                       | 0 0 x x H      |

Note: Only R16 (uppermost bit of the light pen address) is preset.

#### (2) HDB: Disable Hercules mode

When Ms Word (Version 4) is started up, it checks the status of Bit 7. If this bit is active, the system judges that an HGC is connected and begins writing the data into Page 1. If the PCDC used with a full Hercules circuit, there would be no problem, but with a half-hercules board (which can only display Page 0) such as the PCDC evaluation board and with MDA circuits, there is misoperation. (When WORD/C is entered, there is no problem, but when just WORD is keys in, there are problems. Version 3 asked which board was being used, so this problem did not occur with Version 3.) This problem is handled by setting HDB to 1 so that Status Bit 7, Control/ID Bit 1 and Bit 0, and Mode Bit 7 do not function, providing compatibility with MDA.

#### (3) GOE: Output '1' to GPE

GPE is the OR of the outputs from Bits 0 and 1 of the Control/ID register and is used in space management for the VRAM. (See A15 in 3-6-12.) However, since Bits 0 and 1 of the Control/ID register are only valid in Hercules mode, in CGA mode they could not be used. (Therefore, even though the PCDC evaluation board had 32K bytes of VRAM, only 16K bytes could be used in CGA mode.) A bit, GOE, has been established that can set GPE to 1 to make it easier to manage space in the VRAM.

#### 3-6-4. Address 37н

(Cleared by RESET)

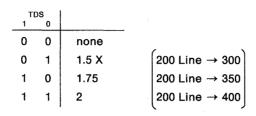

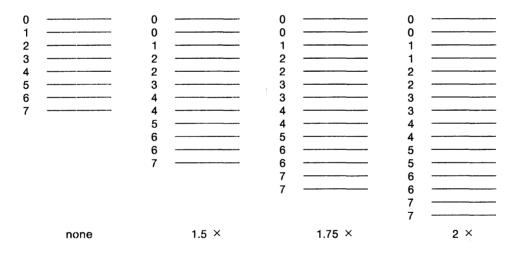

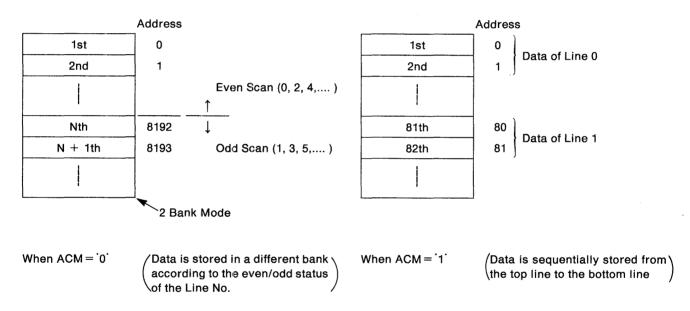

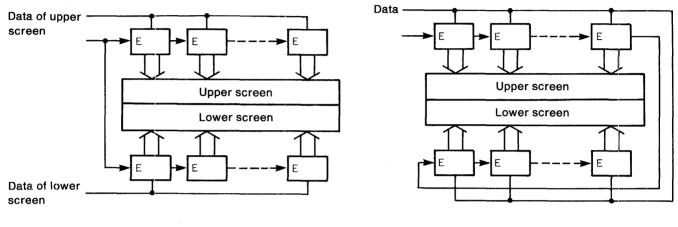

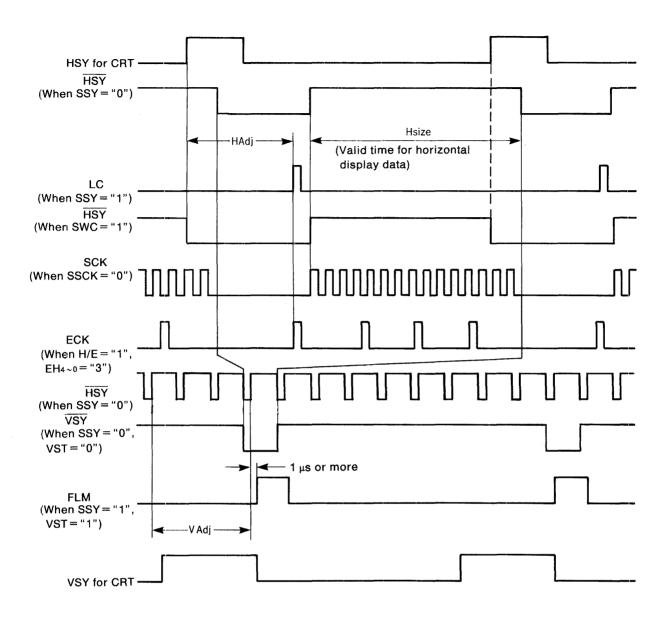

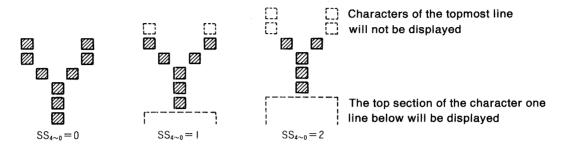

TDS 1,0: Double Scan control (for Text Mode)