Issue 41 Fall/Winter 2001

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

Celiournal

#### Xilinx Introduces Fast, Efficient ISE 4.1i Software

The features and performance will surprise you

#### Xilinx Creates Home Networking Solutions

How to keep up with the emerging standards and protocols

SOFTWARE ISE 4.1i Accelerates Your Time to Market

#### TECHNOLOGY

ProActive Timing Closure Speeds Up Design Process

#### NEW/S

Terabit Networking Forum a Huge Success

XILINX®

### **Cover Story**

Synopsys Senior VP Sanjiv Kaul Leverages ASIC Expertise for FPGA Design

EDITOR IN CHIEF Carlis Collins editor@xilinx com 408-879-4519 MANAGING EDITOR Tom Durkin tom.durkin@xilinx.com 530-271-0899 CREATIVE DIRECTOR Andy Larg **DESIGN & ILLUSTRATION** Scott Blair Dan Teie **BOARD OF ADVISORS** Dave Stieg Mike Seither

Peter Alfke

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3450 Phone: 408-559-7778 FAX: 408-879-4780 ©2001 Xilinx Inc. All rights reserved.

Xcell is published quarterly. XILINX, the Xilinx logo, CoolRunner, Spartan, and Virtex are registered trademarks of Xilinx Inc. Alliance Series, Xilinx Foundation Series, AllianceCore, Foundatian, IRL, LogiCORE, Selectl/O, WebPACK, WebPOWEED, WebFITTER, OPTo, XPERTS, XtremeDSP, CORE Generator, Racket I/O, Fast Zero Power, SelectRAM, IP-Immersion, System ACE, ChipScope, and all XC-prefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilimx makes no warranties, express, implied, statutory, or otherwise, and accepts on liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any claim i might have against Xilinx for any loss, damage, or expense caused thereby.

# A Design Win for Xcell!

Those of you who have been reading *Xcell Journal* for a while have probably noticed a steady improvement in the quality and content of the magazine. This reflects the Xilinx cultural values of ever-escalating standards and the continuing pursuit of excellence.

We are especially proud of the graphic design of *Xcell Journal*, which has risen to the award-winning level. As of press time, *Xcell* had just won a prestigious Ozzie Award for Excellence in Magazine Design. *Xcell's* graphic designers – Scott Blair and Dan Teie of Teie, Gelwicks & Associates – won the Gold Award for Best Use of Digital Imagery. Scott and Dan's striking 3D imagery and imaginative layouts have proved that a diagram, graph, schematic, illustration, or picture really is worth a thousand words. Their blend of art and science help us all better understand the complex technology of programmable logic.

We are justifiably proud that Scott and Dan have brought *Xcell Journal* to the level of world-class quality that genuinely reflects the world-class leadership of Xilinx itself.

*Xcell* is more than just killer graphics, of course. We've also elevated the quality of the editorial content with each issue as well. This summer's Special Edition of *Xcell* was so well received by the industry that the Virtex<sup>TM</sup>-II special section has gone into a second printing.

This issue of *Xcell* is reaching for new levels of excellence – in spite of the hard times our industry is enduring. As a concession to the economy, this issue is a combined fall/winter edition – but as no concession to quality, we are featuring, for the first time, two special sections:

- 1. **ISE 4.1i** The new look and unified feel of the latest release of Xilinx Integrated Software Environment design tools not only present the easiest to use graphical interfaces to date, but the ISE 4.1i configurations are fully compatible with ASIC design and synthesis software from the leading vendors. ISE 4.1i makes it easier than ever to lure ASIC engineers into the superior design environment of programmable logic.

- 2. **Home Networking** Xilinx continues to provide the most up-to-date information and analysis of the competing technologies vying for the lucrative home networking market. Log on to the emerging Standards and Protocols (eSP) Web portal to stay informed of who's who and what's what in home networking.

In addition to the two special sections, we have features on:

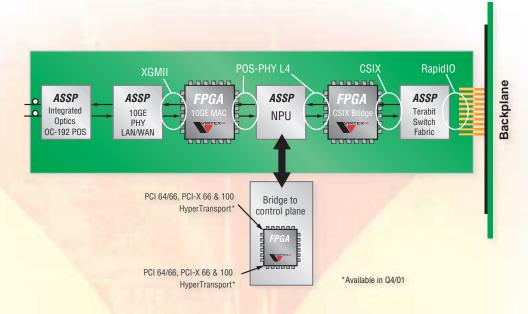

- SystemIO the state-of-the-art solution for interconnecting the various standards and protocols of emerging terabit networking systems

- How Xilinx XPERTS Partner Dillon Engineering developed an ultra high-speed digital imageprocessing system using Virtex-II Platform FPGAs

- The debut of another Xilinx Web portal, Signal Integrity Central.

And that's not all. *Xcell* is now wired. Visit our new website at *www.xilinx.com/publications/xcellonline/*. Please, tell us what you think.

om Durkin

Tom Durkin Managing Editor

#### View from the Top Page 4

### Managing in Difficult Times

It takes more than technology to survive and flourish in this current economic slowdown.

#### Page 8 **Cover Story**

### Leveraging ASIC Expertise for Platform FPGAs

As Platform FPGAs encroach into ASIC territory, complex synthesis tools become essential.

### Page 10

Lead Story – New ISE 4.1i Software

New ISE 4.1i software gives you the fastest time to market, by far.

#### Perspective

Page 40

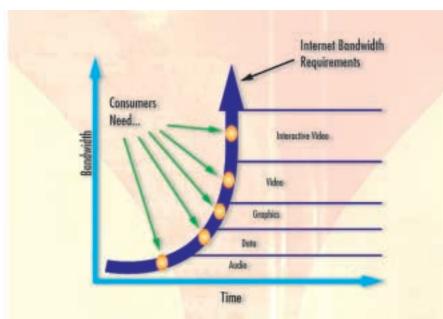

### Lead Story -Networking Comes Home

A silent revolution is happening in home networking.

### Page 56

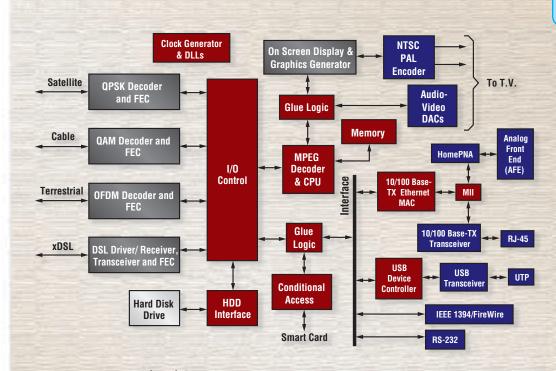

### **Residential Gateways**

A single device connects multiple broadband access and home networking technologies.

#### Page 62 **Technology Focus**

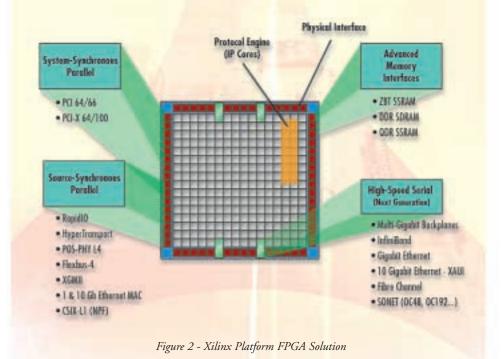

### Platform FPGA SystemIO Solution

Higher I/O performance to meet the growing demand for communications bandwidth.

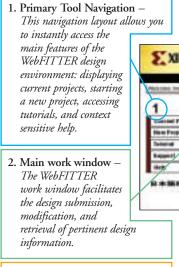

### Contents Fall/Winter 2001 Managing in Difficult Times..... Lead Story – New ISE 4.1i Software......10 New WebFITTER Software .....

| Xilinx Timing Analyzer                                 | 18 |

|--------------------------------------------------------|----|

| HDL Bencher for Fast Verification                      |    |

| Proactive Timing Closure — 133% Better Performance     | 22 |

| Understanding Physical Synthesis and Timing Closure    |    |

| Xpower — New Power Analysis Tool                       | 26 |

| LeonardoSpectrum, Now Supported                        | 28 |

| TOPS — Second Generation Physical Synthesis Technology | 30 |

| Synopsys – Next Generation Flow for Platform FPGAs     | 32 |

| New MicroBlaze Soft Processor Core                     | 34 |

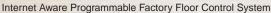

| New Flexbus-4 Core                                     | 36 |

| New Spartan-IIE FPGA Family                            |    |

| Lead Story — Networking Comes Home                     |    |

| Bluetooth Wireless Technology                          | 42 |

| Home Networking — from PCs to Information Appliances   | 46 |

| The Growth in Broadband Access                         | 48 |

| FPGAs Enable Wireless LANs                             | 50 |

| Add Internet Connectivity - New UDP Stack Core         |    |

| Residential Gateways                                   | 56 |

| New Comprehensive Guide to Home Networking             |    |

| iMPACT — New Configuration and Programming Software    | 61 |

| Platform FPGA SystemIO Solution                        | 62 |

| New Signal Integrity Website                           | 65 |

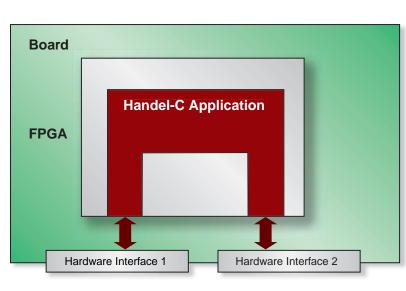

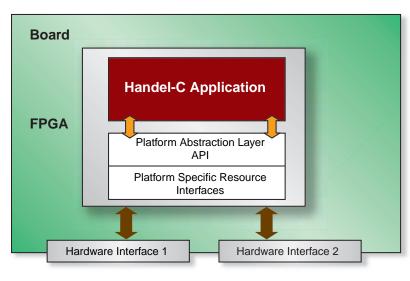

| Co-Processor Acceleration — Celoxica DK1 Design Suite  | 66 |

| Cool Module Design Contest                             | 69 |

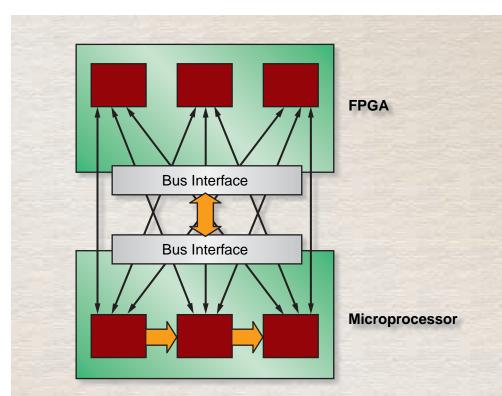

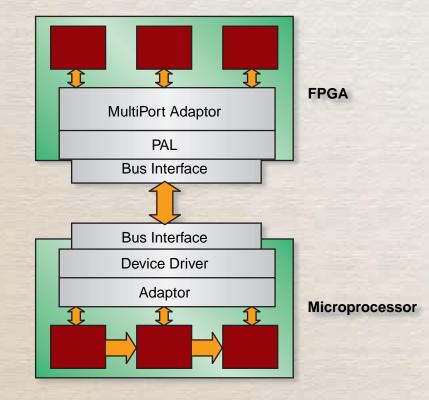

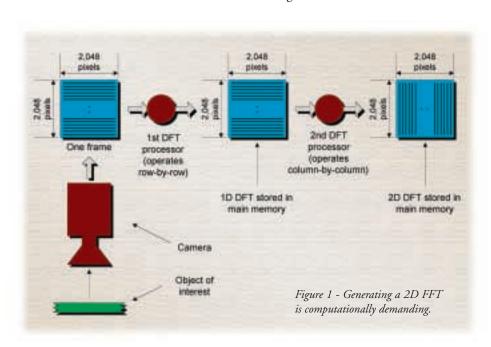

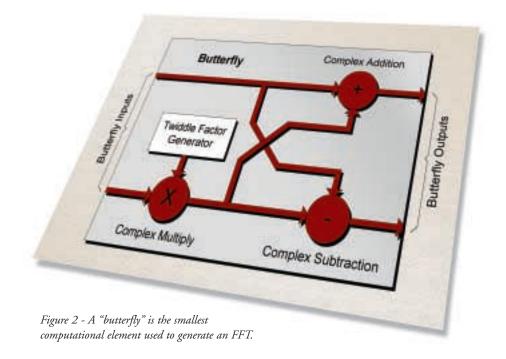

| Virtex-II Image Processing System                      | 70 |

| Reconfigurable Vehicles Are Just Around the Corner     | 74 |

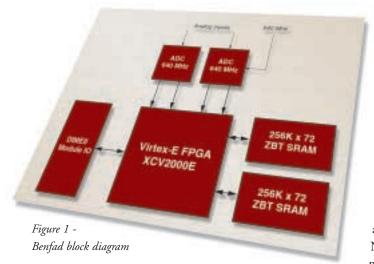

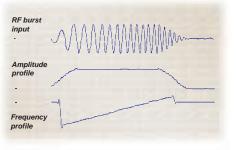

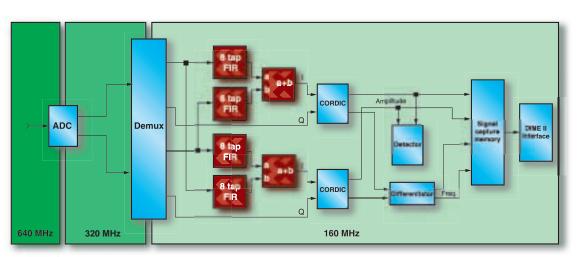

| Virtex-E Giga-Sample DSP Board                         | 78 |

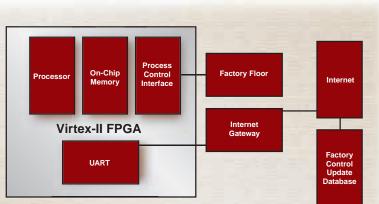

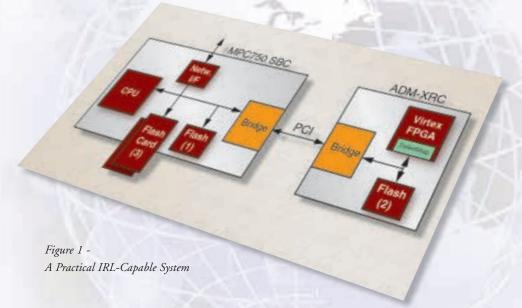

| Internet Reconfigurable Logic with Alpha Data          | 80 |

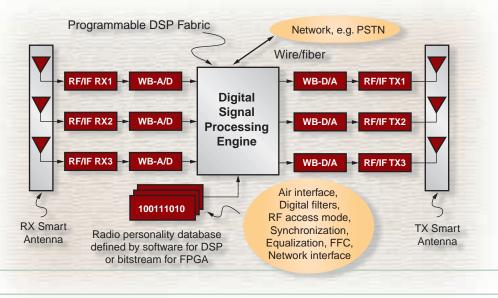

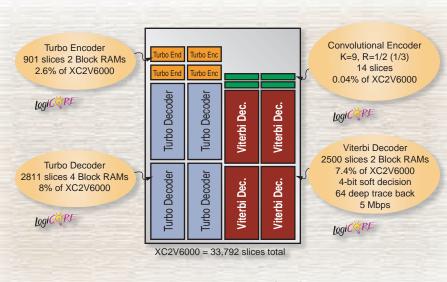

| Virtex-II Enables Software-Defined Radio               | 82 |

| Terabit Networking Forum                               | 84 |

| Learn Smarter, Faster with e-Series I                  | 88 |

| Xilinx Product Reference Guide                         | 90 |

For a Free Subscription to the Xcell Journal enter your request at: www.xilinx.com/forms/literature.htm

Visit Xcell Online at: www.xilinx.com/publications/xcellonline/

ISE 4.1

# Managing in Difficult Times

It takes more than technology to survive and flourish in this current economic slowdown.

Xcell Journal

Fall/Winter 2001

#### by Wim Roelandts CEO, Xilinx

We are facing some of the most difficult challenges our industry

has ever encountered. Yet, in spite of the current economic slowdown, Xilinx remains strong and we are very optimistic about the future. We continue to aggressively develop the next generation of programmable logic technology and to provide the industry's most comprehensive design solutions for both high-performance and low-cost applications. This year we will introduce more new products than ever before – our rate of innovation has not slowed.

In addition to our new products, we continue to develop new ways to help you succeed. For example, our eSP website provides a wealth of current information to help you create designs based on emerging Standards and Protocols - developing products for the home networking market has never been easier. We also hosted the highly successful Terabit Networking Forum, which provided much needed insight into the future of highspeed networking. These innovative marketing efforts, combined with the advantages of our technology, are the reason why the programmable logic sector of the semiconductor market consistently grows faster than other alternatives.

Even in these difficult times, when our revenues have been significantly reduced, Xilinx continues to be a profitable technology leader, as well as a great place to work.

#### The Xilinx Way

Xilinx is able to weather this current economic storm better than most companies, while continuing to bring unprecedented innovation to market, because of four primary factors:

- Our management philosophy

- Our company structure

- Our people

- Our technology.

#### The Xilinx Management Philosophy

I left Hewlett Packard in 1996, after 29 years of service, to become the CEO of Xilinx. I chose Xilinx, because one of my goals is to create a new, enduring style of management that other companies will want to copy. I believe that great companies treat people with respect – and also win in the market – by using creativity, innovation, and the common wisdom of all employees to make all of our jobs enjoyable and rewarding.

In Xilinx, I saw the potential to help create a company that would be a technology leader and a financial success, while also being an excellent place to work. I believed Xilinx could be a company that would one day become great – not just financially successful – and we are well on our way.

I follow four basic management principles that help to make Xilinx a great place to work while also creating an environment in which new technology can flourish:

- People want to be part of a supportive team. We all do our best in a supportive team environment. And, because we spend a large part of our time at work, it is very important that we enjoy our work. At Xilinx, everyone is respected and given plenty of opportunity to succeed. We provide both technical and management career paths so all employees can go as far as they choose.

- People want to do a good job and to contribute. We all want our contributions to be recognized, and we want to be proud of the work we do. Therefore, it's important to provide work that is interesting and exciting, and to let people make their own decisions whenever possible. This requires a lot of communication, so everyone understands our common goals and overall business conditions.

- People want to grow and improve. We all want to be better employees tomorrow than we are today. So, at Xilinx, we encourage all employees to continually learn, and we give them plenty of opportunities to do so.

- People want to have ownership. We all want to share in the responsibilities and rewards of success. As owners of the company, we will do a better job and have a more positive attitude. At Xilinx, everyone gets stock options when they join the company, and they also have an opportunity to participate in further ownership through the company's stock purchase plans.

The end result is that you get better products and services, and you get to work with highly skilled and motivated people who enjoy what they do.

#### The Xilinx Company Structure

We focus on the core business functions that are necessary for our success – design, marketing, and technical support. We leave the two most expensive operations – sales and manufacturing – to our business partners.

Because we outsource these functions, we don't have to worry about keeping a manufacturing facility busy, or worry about financing a large sales force during slow business cycles. Thus, we can focus all of our resources on bringing more innovation to market, while keeping our expenses at a minimum. This is one of the key reasons why we have been able to avoid layoffs at this time, even though our revenues are down by more than 50 percent.

By staying focused on our core functions, and maintaining a full workforce, we are able to keep producing the products and services you need to keep your business running smoothly.

#### **The Xilinx People**

Managing innovation is not difficult – just hire the best people and allow them to rock the boat and make some mistakes as they "push the envelope." What I've done at Xilinx is to create an environment and a management structure where people are encouraged to be creative and take risks; a place where decision making is fast and people feel they can contribute their best. As a result, our company has attracted

the best people, we have consistently created the industry's most advanced products, and we have gained significant market share.

We describe ourselves as "competitors with heart" – that's part of the unique culture that we've created at Xilinx. Our employee attrition rate is a very low 5 percent, while other Silicon Valley companies average about 20 percent or more. In addition, we are among Fortune's "100 Best Companies To Work For" – an honor based largely on the reports from our employees. Our success demonstrates that you can build a company that is very aggressive in technology, and the first to market, while treating employees with respect.

When you choose Xilinx, you are not just buying the best devices, software, and services; you are also choosing a worthy partner. You'll find that Xilinx people are not only capable and friendly, we are also dedicated to your success – because we succeed together or not at all.

#### The Xilinx Technology

Most companies are lucky to be the best at one technology. However, due to the rigorous requirements of programmable logic, we must master both silicon and software – and in our industry, Xilinx is the recognized leader in both. We are producing some of

the most advanced silicon in the world, and our software teams are advancing the state of the art with device programming tools and intellectual property (cores). We are achieving dramatic results on all fronts.

For example, five years ago our biggest device had 50,000 system gates, and was running at a clock rate of 20 MHz. Today, we are delivering devices with more than 6,000,000 system gates, running at a clock rate of over 200 MHz. Devices with 10,000,000 system gates, running faster than 300 MHz are on the horizon, and our technology plan calls for devices with over 50,000,000 system gates in the next few years. This is tremendous progress by anyone's standards.

While many people think of Xilinx as primarily a chip manufacturer, in fact more than half of our technical employees are software engineers. Each time we double the density of our devices, our software must also double in speed to keep your productivity high. A few years ago it took our tools about 60 minutes to compile a 10,000 system gate design. With the latest 4.1i release of our software, it takes only 30 minutes to compile a 1,000,000 system gate design – giving you a huge improvement in your productivity. Our goal is to continue to increase the efficiency of our software

tools by at least 50 percent a year.

We can make this kind of progress because we have developed a tightly coupled product development system where different teams create silicon, software, and intellectual property in coordination. In each discipline alone, we could never have achieved these breakthroughs.

You can be assured that all of our devices, our software, and our intellectual property will give you the best possible performance, because they were all designed, from the beginning, to work together.

#### Conclusion

When I joined Xilinx, programmable logic technology was still in its infancy, but I realized it was going to have a very bright future. Today program-

mable logic is one of the fastest growing segments of the semiconductor business, and it's growing faster than the overall semiconductor market.

I expect Xilinx growth to continue at an average of 30 percent per year for the next several years. And in an odd way, we are actually benefiting from the current economic slowdown because programmable logic provides a cost-effective, flexible alternative to ASICs. As a result, we are gaining many new customers. We previously expected to be a \$5 billion company by the year 2003, and now it will take a little longer. Yet, I'm still confident we will achieve that goal.

Xilinx is truly unique company. Because of our values, our trust, and our confidence in each other, we can get through these tough times and emerge stronger than before.

# ONE PLATFORM. ONE SOFTWARE. TOTAL SOLUTIONS.

Over 300 MHz Design Capability Densities up to 6,000,000 Gates Available Now 10 Gigabit Ethernet Plus Other High-Speed Interfaces

The Virtex<sup>®</sup>-II Platform FPGA family dominates the world of programmable logic system design. Once again Xilinx delivers. Right now we are shipping the fastest FPGA ever produced in a wide range of densities from 40K to 6,000,000 gates.

VIRTEX-II

#### Software with All the Speed You Need

The superior fabric of Virtex-II Platform FPGAs is now

complemented by the industry's fastest software: ISE 4.1i. Offering a single software solution for all Xilinx devices, ISE 4.1i delivers lightning fast clock speeds over 300 MHz. ASIC designers can also take advantage of the first and only formal verification tools for FPGAs. The performance speaks for itself: run times of 100K gates in one minute, or 3,000,000 gates in an hour.

#### The Platform for System Solutions

FORTUNE" 2001 100 BEST COMPANIES TO WORK FOR

Our unique digitally controlled impedance technology—another world's first—has solved signal integrity issues. With on-chip multipliers, Xtreme DSP delivers over 600 billion MACs/s. SystemIO<sup>™</sup> interfaces, including our 10 Gigabit Ethernet MAC core, bridge emerging standards and address all aspects of system connectivity. The Virtex-II IP Immersion<sup>™</sup> architecture gives you the most flexible platform for embedding IP. And our new 70 D-MIPS MicroBlaze<sup>™</sup> soft processor is the fastest on the market today.

The industry leader in speed and density, Virtex-II Platform FPGAs are available now, shipping now, and changing the world of system design . . . *now*.

#### www.xilinx.com

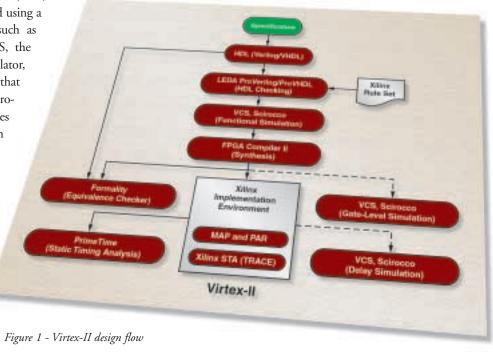

### Leveraging ASIC Expertise for Platform FPGAs encroach into ASIC territory, the need for ever more complex synthesis tools and strategic alliances with industryleading EDA vendors becomes essential.

In a relatively short period of time, programmable logic has evolved from simple glue logic to system-on-a-chip (SoC) prototypes to Platform FPGAs for complex system

applications. These Platform FPGAs, as exemplified by the Xilinx<sup>®</sup> Virtex<sup>TM</sup>-II family, are being targeted for applications that were once solely the domain of ASICs. Now, designers from many different industry segments – communications, medical imaging, graphics processing, and consumer electronics – work with FPGAs.

As devices and applications grow in size and complexity, designers are increasingly applying ASIC-like design and verification techniques to take advantage of the new array of capabilities of Platform FPGAs. The reasons for this vary with the designer's perspective. In some cases, a team verifying an ASIC SoC wants the Platform FPGA prototype to go through the same flow. A designer who used an ASIC on the last project might want to use familiar and proven tools. Many designers who are used to simpler FPGA tools will want to know how ASIC designers have addressed the challenges now faced by Platform FPGA designers. For all these reasons, it's important to ask what has made ASIC and standard cell designers successful in the face of burgeoning complexity and how their EDA tools and flows can apply to Platform FPGA design.

#### **More Sophisticated Synthesis**

For smaller designs, push button synthesis tools have met the needs of FPGA designers. As FPGAs get into the million-gateplus count and support complex clocking schemes, much more sophisticated synthesis technology is required. ASIC designers are accustomed to employing much more sophisticated synthesis methodologies than the current FPGA synthesis tools provide.

More often than not, ASIC designers realize that the fastest path to silicon is to assert a great deal of control over the synthesis process to meet performance goals. Designers of complex ASICs occasionally use a top-down synthesis methodology to handle time budgeting and to give them an overall idea if the design will meet timing goals. This top-down methodology can produce quick results if the design is not pushing the device's performance limits.

Designers at the leading edge of the performance curve, however, also want a bottom-up synthesis capability to focus on the blocks where timing and/or area are tight. During block synthesis, they need precise control of the design hierarchy and a wide

range of design constraints. As designers use FPGAs to implement more challenging designs, they find that only some of the features they need currently exist in today's FPGA synthesis tools. They are demanding more ASIC-like capabilities to get their jobs done.

#### **Combining Synthesis and Placement**

One of the hottest trends in standard cell design is physical synthesis, and this area is heating up for Platform FPGA design as well. True physical synthesis offers more productivity and better performance by integrating synthesis and placement into a single optimization step. By incorporating placement, the optimization algorithms get more accurate timing data for successful timing closure. Currently, FPGA designs are synthesized and placed in two distinct steps. However, even when data is passed back to synthesis after placement, it is difficult to achieve timing closure on the largest designs. A true physical synthesis solution is needed for FPGA designers to reach timing closure and realize fast time to market.

Successful FPGA and ASIC designers also strive to do two things with their HDL code: make their HDL code as technologyindependent as possible, and verify functionality first - because it costs less to fix an error detected early in the design process. The latest in technology independence is power management in SoC designs. Many SoCs use clock-gating schemes in a standard cell implementation. To implement or prototype the same functionality in an FPGA requires clock enables. A complete ASIC tool flow allows the designer to write technology-independent code, which relies on power synthesis tools to insert the clock gating for the standard cell SoC. FPGA synthesis then uses that same code to target the clock enables on the FPGA without the need for any additional technology conversion steps.

#### **Complexity Demands Robust Verification Flow**

Platform FPGAs also need ASIC-like performance in the verification stages of the design. The team that verifies a design often doesn't care whether the final implementation is in standard cell or FPGA technology, they just want to prove it works. That means that the same speed and accuracy that they have come to expect from today's ASIC verification tools must be available, regardless of the final device's implementation. This verification process must also feature test bench generation to handle the soaring gate counts and complex vectors used to verify Platform FPGAs.

Many of the same verification bottlenecks brought on by deep submicron processes also apply to complex FPGAs. Verification engineers need and demand formal verification tools to avoid multiple iterations that can stall a design. Formal verification - in particular the equivalence checking method of formal verification - has recently entered the mainstream of high-capacity, complex designs. This mathematical proof of functional equivalence between two versions of a design can comprehensively verify in a matter of minutes or hours a design that would take weeks to verify using a gate-level simulator. However, to be truly effective as a replacement for gate-level simulation in today's design flows, a formal verification tool must offer more than capacity and speed. It must also provide fast and easy debugging of design errors, it must be usable in a broad array of design types and applications, and it must be easy to integrate into existing design flows.

All verification tools must also provide a feedback loop into implementation, or more valuable design time will be lost. Some of today's formal verification tools meet these requirements, but Platform FPGA designers must be sure that their entire verification environment is suited to verify complex designs.

Another way to reduce the need for gate level simulation is static timing analysis – a technique that both FPGA and ASIC designers have been using for quite some time. Static timing analysis checks the delay on all paths of a chip, providing an exhaustive check of timing to a given set of constraints. What's new for the Platform FPGA world is the need to model the timing of complex IP such as processors and ROMs. FPGA designers also need the application of advanced debugging aids to quickly locate the root cause of timing issues – and feed constraints back to earlier stages of the design process.

#### Conclusion

For designers to meet their goals with Platform FPGAs, EDA, and FPGA vendors must work together closely to ensure that the ASIC design success story can translate into Platform FPGA technology. Synopsys is working closely with Xilinx to ensure that designers who use Platform FPGAs and supporting EDA technology can get the same performance, reliability, and ease of use that the ASIC design community has enjoyed. As a premier EDA company and synthesis pioneer, Synopsys is well poised to apply its extensive knowledge of ASIC design tools and flows to the Platform FPGA arena. Working with Xilinx and its mutual customers, Synopsys will constantly strive to accommodate the myriad changes that will undoubtedly occur as Platform FPGAs take their place alongside ASICs for complex system design.

# Xilinx ISE 4.1i Delivers the Speed You Need

Xilinx ISE 4.1i presents a new set of features and device support to give you the fastest time to market with the most advanced technologies available for FPGA design today.

> by Lee Hansen Software Product Marketing Manager lee.hansen@xilinx.com

Steve Wenande Senior Technical Marketing Engineer steve.wenande@xilinx.com

David Blevins Staff Technical Marketing Engineer david.blevins@xilinx.com

Larry McKeogh CPLD Software Marketing Manager larry.mckeogh@xilinx.com

The new version 4.1i of the Xilinx Integrated Software Environment (ISE) design tool suite has hit the streets running. In this special section of Xcell, we will give vou a detailed look at ISE 4.1i.

Among the improvements we have made are simplified product configurations and software runtimes up to two times faster than ISE 3.1i. We've added ProActive Timing Closure and expanded your choice of verification strategies to deliver the fastest performance possible and the best design flows available despite the push towards everincreasing design complexity and size. ISE 4.1i also includes upgrades of existing tools, such as ModelSim<sup>TM</sup> and ECS (Engineering Capture System) software.

ASIC designers looking to migrate to Platform FPGAs will be happy to find familiar ASIC tools from Synopsys<sup>®</sup>, such as PrimeTimeTM static timing analysis and LEDA<sup>TM</sup> HDL analysis. Moreover, the ISE 4.1i release includes XPower - the industry's first power and thermal analysis tool for FPGAs and CPLDs.

With all this improvement and expanded functionality, ISE 4.1i will allow you to reliably get your product to market faster than your competition.

#### Simplified Configurations -A Single Look and Feel

ISE 4.1i has been simplified to four powerful configurations:

- ISE Alliance Series<sup>TM</sup> configuration for EDA design flow integration

- ISE Foundation<sup>TM</sup> configuration for the most robust single-vendor programmable logic design platform available

- ISE BaseX configuration for a costeffective, full-featured, PC-based programmable logic design environment for the standalone designer, and device size support up to 300K gates

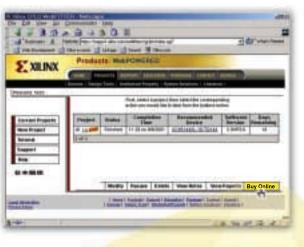

• ISE WebPACK<sup>™</sup> configuration – for a free, Web-delivered design environment for CPLD customers and entry-level FPGA designers, with device size support up to 300K gates.

| the life want being a life to be at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 101       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1918550   |

| Line and the set of th | Comments     Comments | HERE<br>H |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | D ments<br>feet "MENTLY" > 9,4004                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ;         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LIM LOND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -         |

Figure 1 - ISE Project Navigator

#### **Full Device Support in a Single Package**

All Xilinx device families can be designed and programmed from the ISE family of products. This includes existing devices as well as those new FPGA and CPLD families scheduled to be released in the coming year.

ISE 4.1i also delivers a new, unified look and feel in the Alliance and Foundation configurations. By combining ISE Alliance and ISE Foundation configurations into a unified development effort, our customers realize the best performance and features in any of the ISE design configurations, and migration or upgrade between ISE packages is quick and easy.

#### **Project Navigator Up Front**

As shown in Figure 1, both ISE Alliance and ISE Foundation customers will now see Project Navigator for their design management tool. Project Navigator features several new powerful features, including integration with Exemplar's LeonardoSpectrum<sup>TM</sup> synthesis environment, Unix platform support, EDIF source support, and more. For Alliance customers who want to transition over the coming year, Design Manager will still be available in ISE 4.1i.

#### Installs Just Got Easier

ISE 4.1i contains significant improvements to the installation process. Immediately, you will notice ISE 4.1i searches for earlier

> versions of ISE and offers to remove the older versions of software, helping to free up disk space - or ISE 4.1i allows you to save your older ISE versions.

> Adding device support is quick and easy. You can add support for new device families incrementally at a later date simply by re-running the 4.1i install program.

#### 50% Faster Runtimes - Again

The Xilinx Intellectual Property, Services and Software Group operates under a mandate to deliver 2X better software execution with each major release, and

ISE 4.1i is no exception. Benchmarks indicate you will see as much as 50% faster design compilation - that means as many as 100,000 gates compiled per minute. And that translates to millions of gates compiled per hour. This blazing design speed outperforms all other logic vendors.

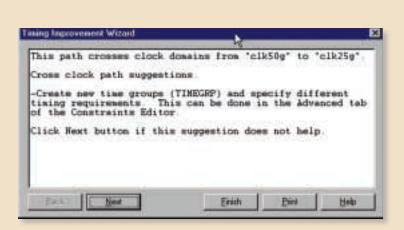

#### **Maximum Performance Through ProActive Timing Closure**

If you take a design compiled in ISE 3.1i and run it on ISE 4.1i, you will see impressive gains in device performance (Fmax) through a new collection of timing technologies known as ProActive Timing Closure. Collectively, the advances in ProActive Timing Closure technology can deliver as much as 133% better Quality of Results (QoR) than our previous major software version:

• As the industry's most advanced timingdriven, place-and-route technology available, ProActive Timing Closure brings a new level of active control to design timing. Placement algorithms scan the design data paths and place critical paths first, helping to reduce timing delays. A new extra-effort routing mode remembers which paths in . - .

4

ш

2

ISE 4.1i

an implementation pass successfully met timing requirements, and then transparently "re-places" and "re-routes" unsuccessful areas to attempt to meet overall timing goals. And our new Directed Routing brings predictable and repeatable placeand-route capabilities to IP cores.

ProActive Timing Closure further expands physical synthesis for programmable logic by using physical timing information to ensure that optimization during synthesis is focused on the critical paths. ISE 4.1i works with Synplicity<sup>®</sup> Inc.'s Amplify<sup>TM</sup> software and new TOPS<sup>TM</sup> (Total Optimization Physical

Synthesis) capability to further source this physical timing information. [See "ProActive Timing Closure Delivers up to 133% Better Device Performance" in this issue of *Xcell* for more information on ISE physical synthesis.]

- Timing and HDL interaction now occur at several levels of implementation, offering design-specific tips that suggest modifications to the design, constraints, or source code, to help meet the design's timing requirements.

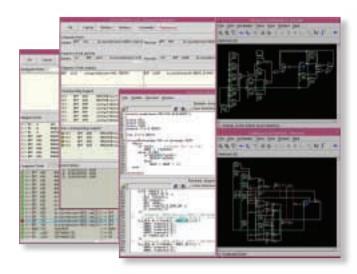

- ISE 4.1i offers timing cross-probing from the timing analysis report to either the Xilinx Floorplanner or to third party synthesis "technology viewers." Cross-probing displays exactly where the problems are in the design in the physical floorplan of the FPGA, the logic gates which were created during synthesis, and even the specific HDL source code itself, significantly reducing debug time.

#### **Expanded Verification Strategies**

As designs grown in complexity and size, verification becomes a greater challenge. ISE 4.1i has been designed to expand the options you have for checkpoint verification. At each stage of the design cycle, you can check your design for accuracy.

#### First Formal Verification Capability for Programmable Logic

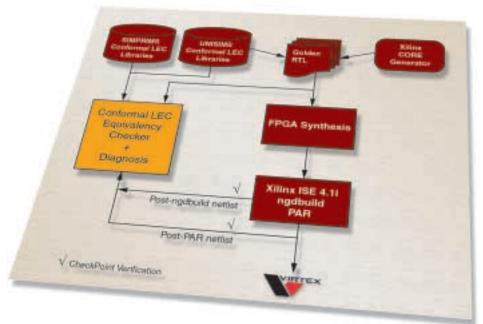

ISE 4.1i offers integration with Synopsys Inc.'s Formality<sup>TM</sup> and Verplex Systems Inc.'s Conformal<sup>TM</sup>-LEC equivalency checkers, leveraging the same technology that was adopted in past years to check highdensity ASICs. In the equivalence method of testing, design passes can be checked in "blocks of logic" against a previous knowngood version. This can occur at any point in the design cycle, particularly in post-synthesis and place-and-route passes. This strategy new versions of ModelSim software add valuable library updates, and they feature support to keep Xilinx ISE 4.1i at the forefront of HDL simulation use with:

- Library importer wizard

- New library view window

- An array of bug fixes.

For convenience, the HDL simulation libraries are now broken out as either CPLD- or FPGA-centric, based on either VHDL or Verilog hardware description languages. This separation of libraries allows the smallest possible download size for the desired design application.

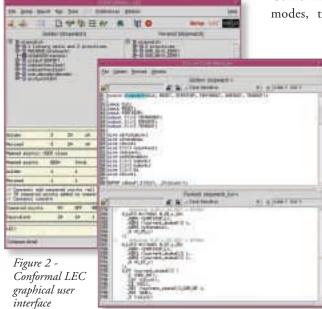

#### **ECS Schematic Capture**

When upgrading to the ISE Foundation 4.1i software from Foundation Series, customers will notice a new change in their schematic capture and block diagram editor. Shown in Figure 2, ECS is now the schematic capture product for all software configurations. The Xilinx ECS application provides the designer with a powerful graphical input tool for creating schematics and block diagrams. Block diagrams can be created and used as the "top level" description of an HDL design. The designer can

describe logic modules in the HDL editor, using VHDL or Verilog, and then use ECS to auto-generate graphical block symbols for each module. Designers can then instantiate and connect the symbols to create a block diagram representation of the design. Prior to synthesis and implementation, the diagram is converted into an HDL netlist that describes the blocks' interconnectivity, which (along with the HDL modules) will be used for subsequent synthesis and implementation in the target Xilinx device.

ECS also supports traditional schematicbased PLD design. Symbol libraries are provided for each Xilinx device architec-

| the set uses during a prove denset many with |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| also a                                       | ESS TH LERIT .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 + + + + P                                  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <u>                                     </u> |

|                                              | dispetitionality, party in 1990001<br>ten 1990000, party interesting to 1, party and 100, party an | - 1                                          |

|                                              | C. mest:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | H <sub>H</sub>                               |

|                                              | New Sector Parts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                              |

| Mittle-10 11 1.000                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| and many transfer                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

Figure 2 - ISE Engineering Capture System (ECS)

offers a rapid checking method that is proving invaluable to high-density design work. For Virtex-II designers moving to 1-million gate designs and above, this new formal verification integration provides a valuable step in the Platform FPGA initiative. [See "High-Performance Platform FPGAs Now Need Formal Verification" in this issue of *Xcell*.]

#### ISE 4.1i Supports ModelSim Version 5.5

ISE 4.1i also includes support for the 5.5 family of ModelSim HDL simulators from Model Technology, a subsidiary of Mentor Graphics Inc. The ModelSim Xilinx Edition (XE) simulator, has been upgraded to version 5.5 as well. These ture, which allows the designer to define a design using flip-flops, counters, gates, and other mechanisms. Symbols come in two varieties – "primitive" components such as a two-input AND gate, and "macro" symbols for more complex functionality, such as counters. ECS now not only provides enhanced functionality and user friendliness, but it will also serve as a framework for future graphics-intensive features in ISE Foundation software.

Some of the new features in ECS include:

- Multi-window interface Multiple schematic and/or symbol windows can be open simultaneously.

- Enhanced object attribute handling system The designer can now arbitrarily and easily create custom attributes for objects (e.g. wires or symbols). Also, attributes for all currently selected objects can be viewed/edited at the same time.

- Right mouse button menu support You can accelerate design tasks by making editing actions immediately available for currently selected object(s).

- Enhanced design rule checking Objects that result in warnings or errors are highlighted on the schematic sheet so they can be easily found.

- Preferences menu Rather than editing a text initialization file, you can now choose application settings and user preferences from a menu.

- Customization Now you can create sheet sizes to your exact specifications.

- Support for Windows® Clipboard For design documentation, you can cutand-paste diagrams and schematics (or portions thereof) into other applications such as Microsoft Word.

- Print Preview Now you can see and adjust – how a printout will look before you print it out.

#### FPGA Tools Powerful Enough for ASIC Users

As the Platform FPGA initiative has reached full steam in the industry, we have seen an influx of ASIC designers converting to FPGAs – both for proto-

typing and for full-production logic. In order to facilitate the migration of ASIC designers to FPGAs, we have provided additional tools that ASIC designers have come to know and love.

#### XPower

This release of ISE 4.1i includes the XPower power analysis product - the industry's first power analysis tool with thermal analysis and reporting capability. XPower lets you see early on in the design cycle how the logic activity will affect the thermal characteristics of Xilinx FPGAs and CPLDs. XPower software is proving invaluable in the high-density design world of Virtex-II devices where multiple FPGAs may be operating at 90% capacity or higher on a single board. Likewise, XPower excels in the low-power world of CoolRunner<sup>™</sup> CPLDs where battery life and low power consumption are critical to product success.

#### Synopsys PrimeTime Support

ASIC designers who are more familiar with the Synopsys PrimeTime<sup>TM</sup> tool for static timing analysis can now use it for their FPGA designs in ISE 4.1i. The Xilinx Timing Analyzer, also delivered in ISE 4.1i, remains the golden signoff for static timing analysis of Xilinx FPGA designs.

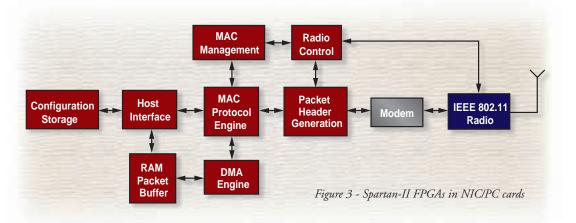

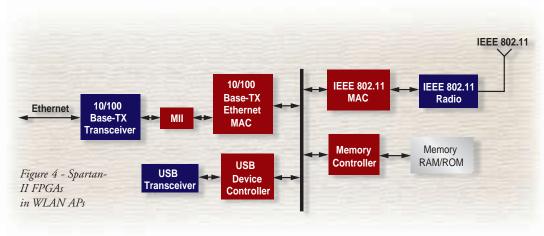

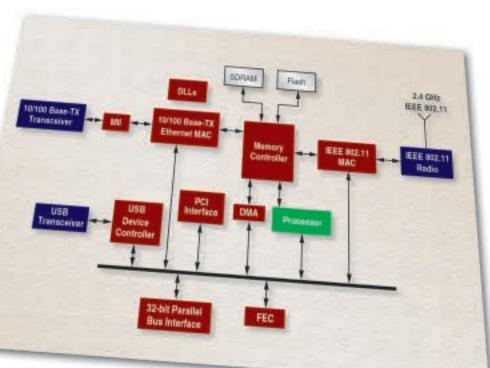

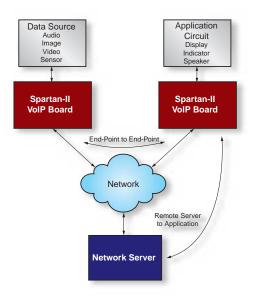

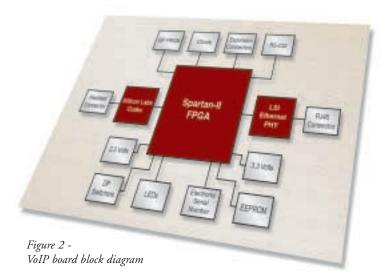

#### Synopsys LEDA-HDL Analysis