# THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

## PRODUCTS

New Virtex Development Board

New HDLC and ADPCM Cores

## **APPLICATIONS**

Using Block-level Incremental Synthesis

## **SOFTWARE**

New WebPack Integrated Synthesis Environment

## NEW/S

IBM and Xilinx Partnership— PowerPC Processors in Virtex-II FPGAs

## **Cover Story**

Synplicity Chief Technology Officer Ken McElvain Talks About the Future of Programmable Logic

## The Partnership Model...

EDITOR

editor@xilinx.com 408-879-4519

Carlis Collins

Andy Larg

Dave Stieg

Mike Seither Peter Alfke

SENIOR DESIGNER

BOARD OF ADVISORS

## XCelljournal

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124-3450 Phone: 408-559-7778 FAX: 408-879-4780 ©1999 Xilinx Inc. All rights reserved.

Xcell is published quarterly. XILINX, the Xilinx logo, and CoolRunner are registered trademarks of Xilinx, Inc. Virtex, LogiCORF, IRI, Spartan, SpartanXL, Alliance Series, Foundation Series, CORE Generator, IP Internet Capture, IP Remote Interface, MultiLinx, OPRO, Selecti //O, Select 1/0+, True Dual-Port, WebFITTER, WebPACK, ChipViewer, Select RAM, Block Ram, Xilinx Online, and all XC-prefix products are trademarks, and The Programmable Logic Company is a service mark of Xilinx, Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided soley for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no liability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any daim it might have against Xilinx for any loss, damage, or expense caused thereby. **P** rogrammable logic technology is advancing at a phenomenal rate; our industry is booming, business has never been better, and Xilinx is growing faster than we ever imagined. Our devices are bigger, faster, easier to use, and less expensive than ever before, and there are many new development tools, support products, and services being offered by a growing number of companies. In addition, as we add new features, increase performance, and lower prices, many new types of applications are opening for our products-and that fuels even more growth and more innovation.

The phenomenal growth of programmable logic technologies is the result of teamwork; we didn't do it alone. As you can read in the article on page 4 from our CEO, Wim Roelandts, Xilinx is based on a partnership model that includes our technology partners, our stock holders, and you, our customers. Clearly, our sustained success is very dependent on the success of those who work with us. That's one reason why we work closely with our technology partners and support their development of new products and services. It's also why we work closely with you, to make sure we are creating the right products for your current and future needs. It's also why we publish this journal.

## **Communication is Key**

Communication is necessary to sustain a healthy partnership, and effective communication requires a two-way process. This journal intends to bring you the latest information about programmable logic technologies and how to use them. It also brings you the insights of industry insiders about the trends and developments that will affect you in the future, so you can make informed decisions today. We are always striving to include articles that make a positive difference for you, and present those articles in a format that is interesting and easy to read.

Your feedback is important because we want to continue bringing you the types of articles that matter most to you. After all, this is your journal; it exists only for your benefit. So, let me know what you think about our new Xcell Journal; your suggestions for improvement are always welcome.

## Write for Xcell

If you have a novel solution to a common design problem or if you have developed a unique design, why not share it with your peers? Writing technical articles for Xcell is easy, it can gain you a modest amount of fame and fortune, and it's a great way to promote your company. Send me an e-mail with your article ideas, and I'll send you more details.

Thanks for your continued support of this journal. I hope you like the new design.

Costa Olars

Carlis Collins Editor

## Page 8

## Design Technology Advances Unleash Powerful New FPGA Capabilities

The Chief Technology Officer at Synplicity talks about the trends that are shaping the FPGA industry.

## Products

**Cover Story**

## New HDLC and ADPCM Cores

A strategic partnership with ISS produces advanced communications products.

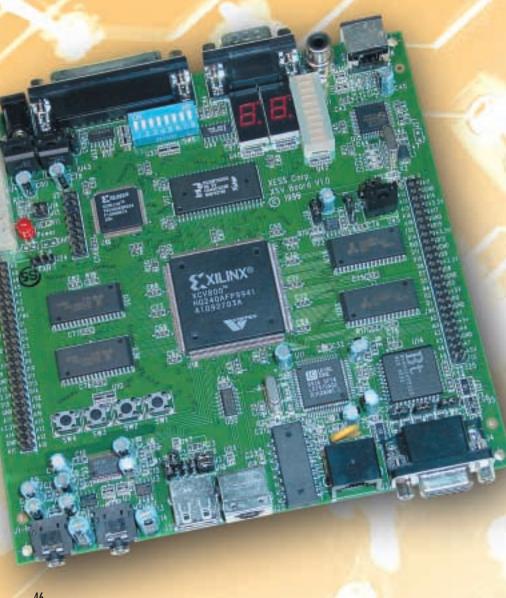

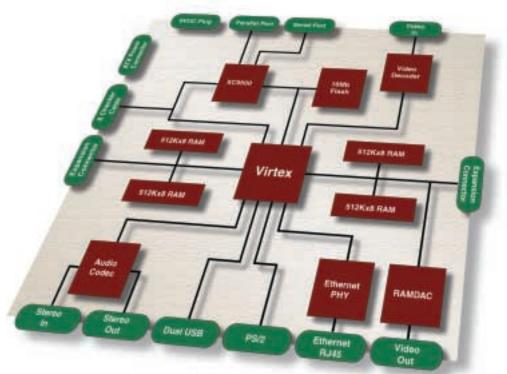

## New Virtex XSV Development Board for Creating Intellectual Property

The XSV Board, designed for the SIP developer community, provides a flexible, low-cost platform that supports a large set of interesting applications.

## Applications Page 24

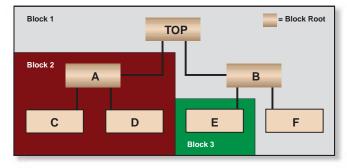

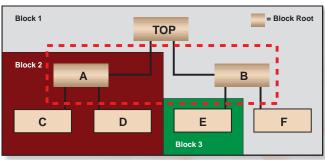

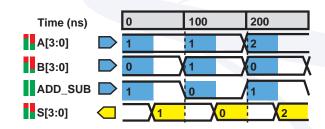

## Using Block-Level Incremental Synthesis in FPGA Compiler II and FPGA ExpressBlock-Level

Incremental Synthesis allows you to modify a subset of a design and then re-synthesize just the modified subset.

News

## Page 34

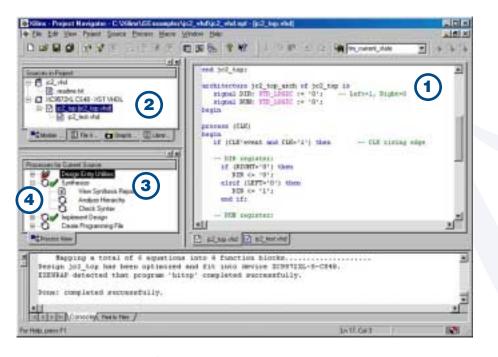

New WebPack Integrated Synthesis Environment

Free, comprehensive design environment for CPLDs available over the Web.

## Page 13

IBM and Xilinx Partnership— PowerPC Processors in Virtex-II FPGAs

IBM and Xilinx combine cutting edge technologies to create a revolutionary new product.

## Contents Fall 2000

| The Xilinx Business "Ecosystem"                                                 | 4   |

|---------------------------------------------------------------------------------|-----|

| Design Technology Advances Unleash Powerful<br>New FPGA Capabilities            | 8   |

| Maximizing FPGA Design Performance Using Amplify from Synplicity                | .11 |

| PowerPC Processors in Virtex-II FPGAs                                           | .13 |

| The MathWorks and Xilinx take FPGAs into Mainstream DSP .                       | .14 |

| Xilinx DSP                                                                      | .16 |

| IRL Makes Console Switching Faster and More Reliable                            | .18 |

| LavaCORE - A Configurable Java Processor                                        | .20 |

| Inferring Read Only Memory in FPGA Compiler II and FPGA Express                 | .22 |

| Using Block-Level Incremental Synthesis in FPGA Compiler II and FPGA Express    | .24 |

| Lucent Technologies Gets a Time-to-market Advantage                             | .27 |

| New HDLC and ADPCM Cores                                                        | .28 |

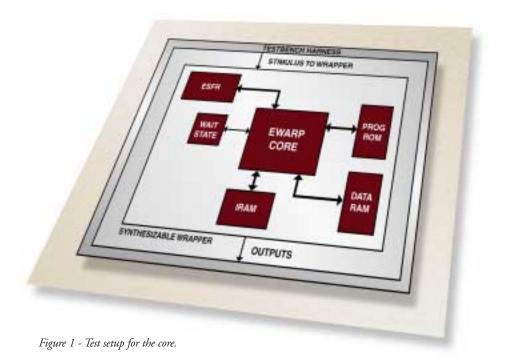

| Moving the M8051Ewarp ASIC Core to a Virtex FPGA $\ldots\ldots$                 | .30 |

| Xilinx WebPACK Software Now Includes ModelSim                                   | .33 |

| New WebPACK Integrated Synthesis Environment (ISE)                              | .34 |

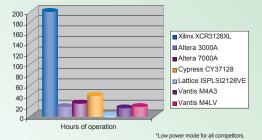

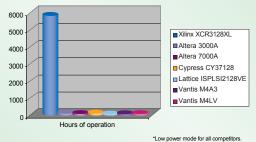

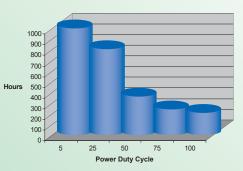

| Low Power CoolRunner CPLDs                                                      | .36 |

| PLDs-Your Competitive Edge for High Volume Production $\ldots$ .                |     |

| Design Reuse Strategy for FPGAs                                                 | .40 |

| Year 2000 Worldwide Xilinx Event Schedules                                      | .42 |

| CoolRunner CPLDs - Your Best Choice for Battery Operation $\ . \ .$             |     |

| Choices, Choices, and Opinions                                                  | .44 |

| New Virtex XSV Development Board for Creating<br>Intellectual Property          | .46 |

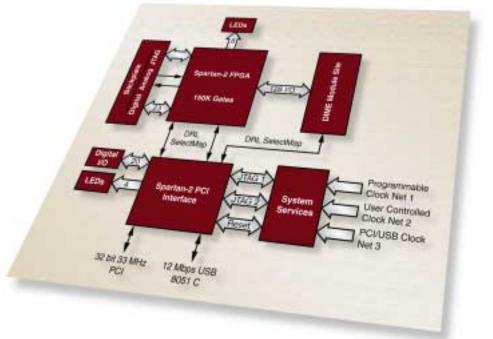

| Strathnuey - The Xilinx Technologies Integrator                                 | .48 |

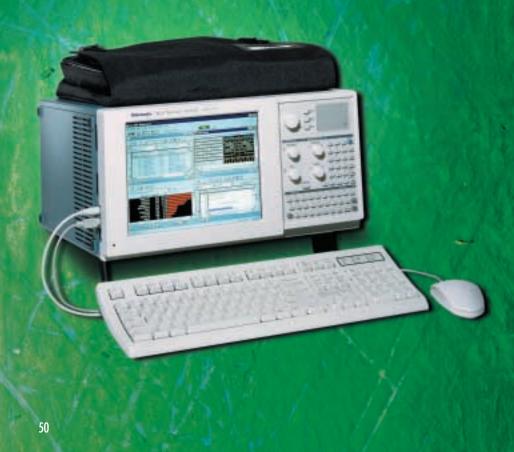

| Tektronix Logic Analyzers - 800 Mbit/sec Using Virtex FPGAs                     | .50 |

| McData Uses Xilinx FPGAs for Fibre-channel Switch                               | .52 |

| The "Flancter"                                                                  | .54 |

| Distribution Adds Value: Intel StrongARM Supported with Xilinx Spartan-II FPGAs |     |

| Product Deference                                                               | го  |

## Xcelljournal

## For a Free Subscription to the Xcell Journal E-mail your request to: literature@xilinx.com.

- Please include:

- 1. Your full name and mailing address.

- 2. Your job title.

- 3. Your e-mail address.

- 4. Your company name.

- 5. Is this a new subscription or a renewal?

## The Xilinx Business "Ecosystem"

## by Wim Roelandts, CEO, Xilinx

In today's fast paced high technology business climate, the keys to success are complex and

they change constantly. It's difficult for any one company to master all of the necessary functions of business management, product design, manufacturing, marketing, sales, and customer support. And, as the breadth of required knowledge and expertise expands, people are becoming much more specialized in their jobs, taking a more narrow focus, because there is so much to master. That's why it has become imperative that high technology companies, such as Xilinx, focus on the key aspects of their business, to become excellent at their core technology and business processes, while partnering with other companies that are also the best in what they do.

Well managed companies must also learn to partner with their customers to develop the insight and the processes that ensure the success of each new generation of technology. And, if the company is successful, its shareholders will profit and will continue to support the company through stock purchases—a key factor in the economic health of the company.

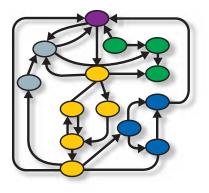

This partnership between companies, specialized partners, customers, and shareholders is like an ecosystem where each part depends on the others, and the boundaries between each are blurred as they work closely together. For each part of this ecosystem to survive and to thrive, all parts must work well together, in balance, and this must become the primary objective of the company management—if any part of the ecosystem fails, all will suffer.

## **The Five Habitats**

The Xilinx business "ecosystem," as I see it, is composed of five main "habitats," or overlapping systems:

- The Company People who focus on the primary business goals; the direct employees and managers of the company.

- Customers People who not only buy products and services but also influence the design of new products.

- Partners People who support the ecosystem through supplying needed services to the company (such as manufacturing and sales, intellectual property and design support).

- Investors People who own the company and support it through their continued investment.

- Government People who have an impact on the overall business environment by making laws and regulations that can affect the company.

Each of these habitats must be healthy and prosperous for the overall ecosystem to be healthy and prosperous.

## The Company Habitat

For a company to prosper and grow, it must create and maintain a balanced ecosystem. Therefore the company must:

- Determine the core competencies required for long term success and become excellent in those key areas.

- Determine which functions can best be handled by other companies (partners), and manage those relationships well.

- Work closely with customers to develop the right products and to provide specialized services.

- Become a learning organization, adapting to the dynamics of the marketplace.

- Be dynamic, adaptive, and free to innovate, with room to make mistakes.

- Take good care of its employees by providing a rewarding, satisfying, and friendly work environment.

• Have a Chief Executive Officer who is a coach, not the "quarterback." Because the business "game" is dynamic, the coach must have competent managers and trust them to fulfill their specific responsibilities.

## The Customer Habitat

For customers to prosper and grow, they need:

- A continuous flow of innovation from the company to help them create leading edge products and remain competitive in their markets.

- Easy access to all of the company's intellectual property.

- Open channels of communication with the company to:

- help it create the right products and services, and become a better company

- receive the latest technical and marketing information

## The Partner Habitat

For partners to prosper and grow, they need:

- Advanced information about new products and new technologies coming from the company so they can be prepared.

- Cooperation from the company for product development and marketing.

- Constant communication with the company to share information about trends, and to maintain overall balance.

- A working relationship that helps them manage their business more effectively and be more successful.

- Training.

When partners are prosperous and growing, customers receive better service and a broader range of support products and services.

## The Investor Habitat

For investors to prosper and grow they need:

- The company to be well managed and provide good return on investment.

- To have a good understanding of the company's strategy and business practices.

- To have timely and unbiased information about the company's results.

In many cases, employees, customers, and partners are also company stockholders, and therefore they are doubly motivated to maintain a healthy environment that supports the long term growth of the company. This is important because the company's ability to borrow money and therefore its flexibility and adaptability are directly affected by the company's worth on the stock market.

## The Government Habitat

To ensure that government supports the company and to ensure that the company is a good corporate citizen, the company must:

- Educate the government about the company and its products.

- · Give feedback on proposed laws and

policies that can an impact on the company and its industry.

• Build a partnership with local government to improve the local community and to reach common goals.

## How the Xilinx Ecosystem Works

Our primary responsibility must be to develop, manage, and balance our business ecosystem if we are to remain the leader in our industry. So, our first task was to decide what key competencies we needed within Xilinx and which we could entrust to outside partners.

We have defined four core competencies

that we must keep within Xilinx:

- Product design and technology development.

- Marketing.

- Customer support.

- Partner relationship management.

By focusing on these core functions, we can put our resources to best use.

## **Product Design**

Product design is our primary focus because innovation is the lifeblood of

any high technology company; we spend more money on research and development than any of our competitors. We continuously strive to create leading edge devices and support tools that meet the specific needs of our customers.

## Marketing

It's not enough to create "dream" products with more and more features. Excellent products must consistently meet the needs of our customers and our customers must be fully aware of what we offer. It is the function of marketing to make sure that we are in full communication with our marketplace, in both directions.

## **Customer Support**

To create superior technology, and make the world aware of it, goes a long way toward the success of any company. However, without effective and consistent customer support, it's not enough. Our technology is complex, and to use it effectively requires an in-depth and constantly evolving expertise. That's why we created our in-house staff of highlytrained support engineers and design services professionals who can quickly help you meet any challenge.

Sometimes the difference between our products and our services blur. For example, our in-house development tools and ners are manufacturing and sales. So, Xilinx has no fabrication facilities or direct sales force. These are two of the most expensive functions in any company, and the costs are not fixed. In a cyclic industry, such as our own, we gain a significant cost advantage by outsourcing these functions to partners who have made it their business to be the best; plus we gain added flexibility that helps us weather the inevitable down turns without having to lay off employees or suffer heavy losses. Therefore, within Xilinx, we have dedicated people to manage these relationships with our 3rd party manufacturing and sales partners. In addition, we also have dedicated marketing people who manage

our relationships with our development tool partners, helping them define and market their products to our customers.

For manufacturing, we have partnered with UMC in Taiwan and Seiko-Epson in Japan. UMC has created one of the world's leading IC fabrication facilities, with the very latest equipment and process technologies. And,

intellectual property are products, but their sole purpose is to assist you in creating the best possible designs with the least time and effort. So, though most of our revenue comes from the sale of FPGAs and CPLDs, we must also make sure the best tools and services are available too.

We also work with many third-party consultants to provide training, design services, IP development, tool development, and so on.

## Partner Relationship Management

Two of the most important competencies that we decided to entrust to outside part-

because it is their business to manufacture semiconductors, they are always on the cutting edge of process technology.

We work very closely with UMC to develop new manufacturing technologies and to ensure that our designs can make best use of the highest performance, and least expensive, process technologies. Through this partnership, we have moved from  $0.5\mu$ technology to  $0.15\mu$  in less than five years; and  $0.13\mu$  technology is soon to be in use. This fast-paced process migration has helped us to quickly reduce costs and significantly increase density, which means you get faster, less expensive devices, sooner. We could not have progressed this

quickly with an in house fabrication facility—the costs would have been far too high. This partnership has benefited both companies, as well as our customers.

For sales, we use our distributors and independent sales representatives. Sales is obviously a critical function in any company, and is very expensive. We chose to partner with our distributors because Xilinx products are a key source of revenue for them, often providing more revenue than any other product line. Therefore our distributors have a lot of incentive to focus on our products and to use their extensive sales force to focus on Xilinx. This is another win-win partnership that helps both companies adapt to the inevitable ups and downs of the business cycles. Our customers also benefit from the broad range of services provided by our distributors.

At Xilinx, average revenue per employee is \$600K; many companies with in-house sales teams are fortunate to have \$200,000/year/employee. By keeping our sales costs low, we can put more resources into research and development which keeps us on the leading edge of technology, and makes our customers and our investors very happy.

For software support, we partner with the industry's leading software and development tool suppliers to make sure that you have access to the broadest range of tools and support. We work very closely with the leading software suppliers to make sure that our tools work well together. Though we have a massive in-house effort for software development we also know how important it is to provide you with the new tools and processes that are constantly being created in the marketplace.

For research, we partner with universities and research centers around the world to access the latest developments. Plus, the Xilinx University Program is helping train engineering students in the use of programmable logic devices by providing donations, discounted products, and services. Today there are over 1200 universities using Xilinx in class labs; about 15% of all of the engineering universities worldwide.

## The Xilinx Value System

Values are what holds any organization together and define the boundaries within which its employees can efficiently function. Too often a company's values are undefined however and this leads to erratic results and confusion.

To help us manage and balance the Xilinx business ecosystem, we developed a clear and consistent set of values that we live by. In part, these values are the boundaries that allow our managers the room to innovate and to take ownership of their functions. Our values also help to make Xilinx a great place to work which inevitably leads to better products, happier customers, and increased profits.

Our values are contained within the acronym "CREATIVE" which stands for:

R

Τ

V

E

**Customer Focused**. We exist only because our customers are satisfied and want to do business with us... and we never forget it!

E Excellence. We strive for "Best in Class" in everything we do.

- Accountability. We do what we say we will do and expect the same from others.

- und oxport mo sumo nom omois.

- Teamwork. We believe that cooperative action produces superior results.

Integrity. We are honest with ourselves, each other, our customers, our partners, and our shareholders.

"Very" Open Communication. We share information, ask for feedback, acknowledge good work, and encourage diverse ideas.

Enjoying Our Work. We work hard, are rewarded for it; and we maintain a good sense of perspective, humor, and enthusiasm.

## Conclusion

Many companies—even successful ones view themselves as adversaries with their customers and with their marketplace, often using military tactics and focusing on winning at all cost. We think there is a better way.

To become successful, and remain competitive, high technology companies must view themselves as part of a synergistic whole that includes customers, strategic partners, employees, investors, and government. At Xilinx, our role is to maintain the dynamic balance of this system, and to keep it growing and expanding in a way that makes everyone more whole and prosperous.

When you work with Xilinx, you'll see what a positive difference our "ecosystem" attitude can bring to your long term success.

## **Cover Story**

Synplicity

55

## Design Technology Advances Unleash Powerful New FPGA Capabilities

The Chief Technology Officer at Synplicity talks about the trends that are shaping the FPGA industry.

by Ken McElvain Chief Technology Officer, Synplicity, Inc.

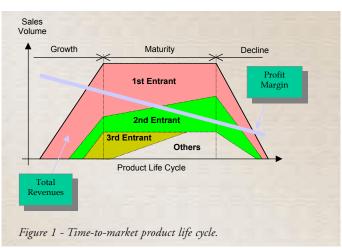

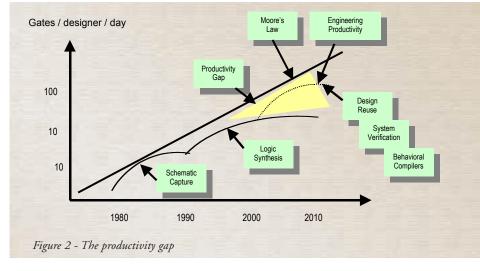

In today's marketplace there is enormous pressure to create increasingly complex systems and get those systems to market as quickly as possible. To challenge these efforts, there is a lack of qualified engineers, industry standards are constantly changing, ASIC development costs are skyrocketing, and new technologies are quickly making yesterday's methods obsolete. These problems are intensified with the fierce competition for lucrative emerging markets. The risks are significant; one equipment vendor estimates the cost of missing a market window to be more than \$1 million a day.

> However, there is also good news. Today's multi-million gate FPGAs offer great promise for designers confounded by the limitations of traditional ASIC implementation. Indeed, the increased

time-to-market demands and lower development cost of FPGAs, combined with today's FPGA capacities well in excess of a million gates, are yielding a profound increase in the number of applications being realized in programmable form. From networking and telecommunications designers grappling with narrow market windows and evolving standards, to a broad scope of designers seeking low-risk rapid prototyping, the number of people turning to FPGA solutions is quickly expanding.

## **Engineers Designing both FPGAs and ASICs**

Only six years ago, engineers were divided into two distinct groups: those that designed ASICs and those that designed with FPGAs. The FPGA designers were primarily schematic based while the ASIC designers had adopted RTL technologies. These two groups didn't work together.

Today, things have changed. Many designers developing FPGAs are also designing ASICs, often at the same time. In addition, designers are now less concerned about the underlying device technology because the gap between ASIC and FPGA performance is narrowing. However, ASICs will remain the technology of choice for certain types of applications. If a design must operate at the low end of power consumption or at the extreme upper end of performance, or if you are designing a very high-volume, cost-sensitive system, an ASIC is likely the most cost-effective solution. If design flexibility or remote design upgradability are needed or if engineering time and risk must be minimized, an FPGA is a logical choice.

## The SoC Opportunity for FPGAs

The advent of systems on chips (SoCs) is more than a simple extension of ASIC technology to higher density. With SoCs, ASIC designers have become system designers, and the event-driven simulation technology traditionally used is no longer sufficient for verifying functionality. Instead, what designers urgently need is a faster, higher-level, hardware-oriented verification path that accepts actual system inputs to yield actual system outputs. Fortunately, just such an approach exists in RTL prototyping, a methodology being adopted widely by both ASIC vendors and system houses.

In contrast to conventional ASIC designers who tend to focus on the functions within their chips, SoC designers must give much more consideration to the system-level nature of the device's inputs and outputs.

TODAY'S MULTI-MILLION GATE FPGAS OFFER GREAT PROMISE FOR DESIGNERS CONFOUNDED BY THE LIMITATIONS OF TRADITIONAL ASIC IMPLEMENTATION.

## -KEN MCELVAIN, SYNPLICITY

Software simulation, which checks circuit functionality against a blast of test vectors, falls short of allowing system I/O to be tested. Other drawbacks of software simulation are well known; it is too slow and can't reproduce electromechanical interactions such as fetching data from a drive. Simulation can take as much as 60 percent of the design cycle time and require too many iterations between RTL and gatelevel implementation. Also, it does not allow for co-verification of hardware and software.

These roadblocks stand in the way of what SoCs require. For example, consumer and communication designs (areas of great promise for SoCs) compete within tight time-to-market windows that suffer when debugging takes many iterations through long cycles of simulation and synthesis. In addition, many chips for these markets must run at high clock rates to verify their correct operation. Inadequate verification of these designs can mean one or more fab re-spins, which can cost over \$1 million per re-spin and take up to six months.

To take fuller advantage of the SoC phenomenon, designers can instead turn to RTL prototyping, a new methodology

## **FPGAs Offer Design Flexibility**

The Internet's explosive popularity, and the resulting surge in demand for bandwidth, has created immense competitive pressure for communications equipment makers. To complicate matters, the communications market is a minefield of specifications evolving unpredictably toward standardization. Schemes for carrying voice and video over the Internet, or the Internet over cable, or any number of variations on the Internet theme bring with them a multitude of implementation details that often must either be ironed out by committees or decided by the market.

Such last minute unpredictability makes bringing complex communications equipment to market quickly even more difficult. Equipment vendors who hope to exploit the high-density and high-volume economics of ASIC technology risk everything should a last minute protocol change force a silicon re-spin. Realizing this, increasing numbers of equipment manufacturers are instead opting for the fast turnaround and flexibility offered by FPGAs.

that is possible through the emergence of fast, dense FPGAs such as the Xilinx Virtex FPGAs and synthesis technologies that can translate ASIC RTL into multiple FPGAs. By building a version of their design in hardware using multiple FPGAs, designers can use RTL prototyping to leapfrog all of the limitations of software simulation.

The quick re-configurability of FPGAs carries other benefits in addition to accommodating shifting specifications. By exploiting the option for in-system programmability, companies can easily and affordably make field upgrades, correct bugs and add features over the Internet, to name just a few possibilities.

## The Impact of FPGA Technology Advances

FPGA technology used to be one or two generations behind ASICs. However, the increase in FPGA density and performance has steadily outpaced that of ASICs for some time. Because of the increasing NRE costs of leading-edge ASICs, typical the ASIC design is falling farther behind the leading edge of process technology, while FPGAs are becoming process drivers.

However, taking full advantage of state-ofthe-art FPGA technology today presents new and difficult challenges. As FPGA process technology progresses well

into the deep submicron realm, interconnect-dominant delay now poses the same difficulties for FPGA designers that previously plagued their ASIC counterparts. Traditional schematic or logic synthesisbased programmable design solutions, similar to the ASIC methodologies of three to four years ago, lack the ability to adequately account for interconnect effects early in the design cycle. With today's highly complex circuits and relentless market pressure, it is more important than ever that accurate interconnect-related performance information be integral to early design processes.

## **Evolution of Software**

Design automation is key to enabling this new era of FPGA design. Unfortunately, simply extending interconnect-aware ASIC design technology to the FPGA domain won't work. The interconnect configurations and options unique to FPGA architectures cannot be comprehended utilizing ASIC physical modeling techniques. Instead, new FPGA-targeted design mented based upon not only traditional timing constraints, but also physical constraints. The nature of FPGA architectures makes it possible to perform physical optimization techniques during synthesis, for example, moving registers across regional boundaries to increase performance.

Physical synthesis offers significant productivity as well as performance advantages to FPGA designers. First, the use of physical

automation technology is needed. Such technology must address the difficult task of bringing accurate information about the physical interconnection of a programmable circuit into the design process without extending design cycles.

Fortunately, FPGA design technology is evolving to accommodate the needs of designers in the deep submicron era. Of particular significance is FPGA-based physical synthesis technology. Physical synthesis factors a design's physical characteristics into the synthesis process. During synthesis, a design is optimized and impleconstraints during synthesis results in more accurate timing estimation, eliminating time-consuming and tedious design iterations common with traditional approaches. Likewise, physical optimization during synthesis makes it possible to physically optimize a circuit for the best possible performance. Combined physical synthesis and optimization techniques can have significant cost benefits, enabling designers in many cases to implement a device in a lower-cost speed grade.

FPGA physical synthesis forms the critical link between state-of-the-art programmable technology and designers seeking to leverage its unique advan-

tages. Such technology opens the door of opportunity for those faced with today's tough market realities.

## Conclusion

Market forces have created a risky environment where the winners and the losers are often separated by only a small gap of innovation. Therefore, it is increasingly important to produce next-generation designs on time and within budget, using limited engineering resources. Today's programmable logic technology and the development tools that support them are your keys to success in this dynamic marketplace.

11

## Maximizing FPGA Design Performance Using Amplify from Synplicity

In very large designs, interconnect delays are becoming more and more predominant. Amplify<sup>™</sup> is the first physical synthesis tool for FPGAs that helps you optimize signal routing delays and achieve timing closure.

## by Philippe Garrault

Technical Marketing Engineer, Xilinx, Inc. philippe.garrault@xilinx.com

Amplify is a new product from Synplicity® that allows you to add physical constraints to your design, using the Synplify® PRO synthesis engine. It links your RTL code to a floorplan of the target device. You can assign your RTL code to physical regions by graphically dropping the logic into these regions. During the synthesis process, Amplify will use a set of rules to optimize the RTL code based on estimated placement and interconnect delays (into and between regions).

Amplify generates an optimized netlist (.edf file) and a Xilinx constraint file (.ncf file) based on the specified physical constraints. These files are then used by the Xilinx Alliance Series 3.1i software tools to implement the design.

## Improving Maximum Frequency

With Amplify you can iterate the implementation twice. In the first pass, you determine the critical paths after place and route. In the second pass, you assign physical constraints on these critical paths to optimize the netlist. By iterating the second pass, the physical constraints can be refined according to the place and route post-layout timing report, until your timing requirements are met.

Another approach is to set several regions prior to implementation. These regions could be a representation of the RTL hierarchy of the design and each could contain one block (or module) of the design.

Finally, you could also mix these techniques to get a floorplan that would not only be a hierarchy representation but you could also add physical constraints on the critical paths regardless of any hierarchy consideration. This is what we did in the following example.

## Design Example

The following example shows how to interface Amplify with the Xilinx place and route tools. The design presented is a network application, which is divided into a top module driving nine similar sub-modules. This code is implementing FIFOs and large busses. We targeted a Virtex-E, XCVE1000-7 device.

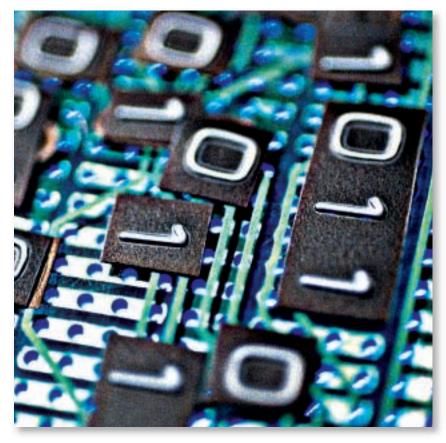

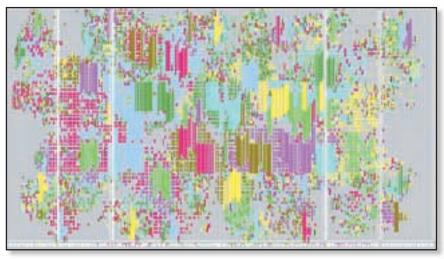

On the first pass, the project is synthesized then implemented with global timing constraints only (without physical constraints). Figure 1 shows a floorplanned view of the design after the first pass. Note that the logic is spread over the chip because, without placement constraints, the place and route algorithm has no information about what logic is crucial for grouping into a region (or there are too many possibilities). The timing constraints were not met, and the best frequency obtained was 104.6MHz.

After this first implementation, we analyzed the post-layout timing report to gather information on the critical path, such as:

- The number of critical paths.

- The start and end points (single or multiple).

- The type of critical path (link with I/O or purely internal, wire or bus).

- The number of logic levels.

- The device resources (flip-flop, combinatorial, block RAM, and so on).

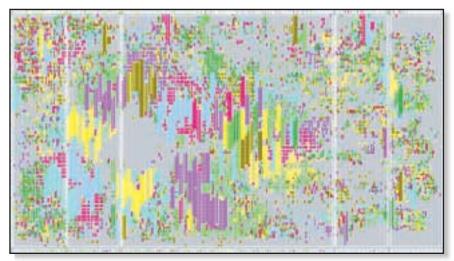

On the second pass, the different critical paths were assigned in separate regions through the Amplify user interface. Figure 2 shows the physical constraints entered in the synthesis environment for our example.

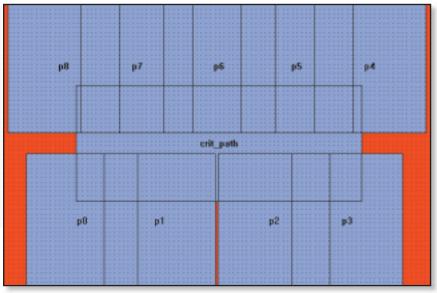

The regions are floorplanned according to the required design resources, such as block RAM and high fanout nets. . By re-synthesizing the design with these physical constraints, a new netlist file along with a constraint file were created. The place and route software uses these optimized files to constrain the logic on these particular areas by placing the critical logic together, shortening net delays to meet the timing requirements.

If the constraints are not met, the Xilinx floorplanner can give useful information about the final layout and determine the precise logic utilization within a region, or view the exact placement of logic on the critical path. This can help to resize regions, remove constraints on non-critical paths, or re-place regions closer together to drive or share common logic or busses.

Figure 3 shows the floorplanned view of the constrained design in our example. Note that the logic is gathered according to the constraint file. The best frequency obtained was 120.1MHz, which is a 12.9% improvement. Using the post-layout timing report and the floorplanner helped us focus on the critical parts of the design, thus saving time by applying more accurate constraints, and reducing the number of iteration needed to meet the timing constraints.

## Interfacing Amplify with Xilinx Tools

Here are some guidelines to help you get the best performance from these tools:

- Put different critical paths into different regions. This usually gives better results.

- If the critical path contains lots of logic, two regions can be overlapped: one small one containing the most critical logic that needs to be placed very close together and a bigger one containing the rest of the critical path.

- Amplify does not currently write constraints for block RAM or black boxes, thus if the critical path includes these objects, use the Constraints Editor and constrain black-boxes and block RAM in the UCF file within or close to the region constraining the rest of the critical path. Use the following command:

## INST p1.qram1 LOC = RAMB4\_R0C1: RAMB4\_R7C1, RAMB4\_R\*C2;

- Applying physical constraints to critical paths is more likely to improve results if the ratio between routing and logic is in favor of routing (this ratio is given by the post-layout timing report).

- Slightly moving a region can affect the maximum frequency of your design.

## Conclusion

Synplicity's Amplify Physical Optimizer in conjunction with the Xilinx Alliance Series 3.1i software can significantly improve your design performance. As a result of the new features and capabilities, you have a more efficient way to visualize and constrain critical paths of your designs, saving time in multiple iterations while getting better speed performance.

Figure 1 - floorplanned view of the design on the first pass.

Figure 2 - Physical constraints entered in the synthesis environment.

Figure 3 - Floorplanned view of the constrained design.

News

### Partnerships

## PowerPC Processors in Virtex-II FPGAs

IBM and Xilinx combine cutting edge technologies to create a revolutionary new product.

by Ann Duft Manager of North American PR, Xilinx annd@xilinx.com

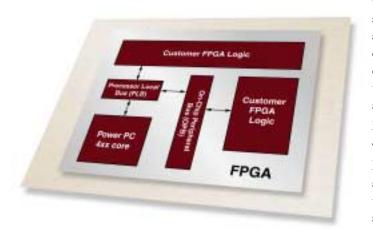

IBM and Xilinx recently announced a partnership to create a new generation of devices for use in communications, storage, and consumer applications. Under the agreement, we are working together to embed IBM PowerPC processor cores in Xilinx VirtexTM-II FPGAs. The pairing of a lowcost, high performance PowerPC processor core with customizable FPGA circuitry allows you to create custom chips for your particular application at reduced cost and

with faster time-to-market. Availability dates for the new chips will be announced later this year by Xilinx.

The new devices will initially be fabricated by IBM for Xilinx using advanced IBM chip manufacturing technologies, including copper interconnects which adds to their performance. This will enable Xilinx to broaden its manufacturing volume and geographic diversity, and leverage common foundry manufacturing processes. "This joint effort will bring about a new design era combining programmable logic time-to-market advantages with the cost benefits of standard cell technology," said Andrew Allison, semiconductor industry analyst. "This is a potent combination."

"IBM and Xilinx are committed to meeting each customer's unique blend of requirements for cost, design time, and individualized function," said John Kelly, general manager, IBM Microelectronics Division. "This requires a variety of chip design options, from standard, off-the-shelf parts

> to FPGAs to ASICs. This agreement creates both a new approach in chip design, as well as a unique collaboration between the world's leading ASIC and programmable logic providers."

> The complementary marketing and technology agreement will enable customers who choose FPGA solutions from Xilinx to more easily migrate to IBM

ASIC and standard product solutions. Customers will factor performance, cost, time-to-market, and volume requirements in making a determination as to the best option for a given application, while using the same industry standard PowerPC and IBM's system-on-a-chip CoreConnect bus technology across all solutions.

"The combination of technologies will lead to a new level of performance and flexibility in the semiconductor market," said Wim Roelandts, president and CEO of Xilinx. "IBM's process technology is the most advanced in the industry and the PowerPC architecture has become the standard in communications, enabling us to deliver the highest performance and highest density products into the market at the leading edge of technology."

Under the multi-year agreement, Xilinx will license IBM's high-performance PowerPC processor cores and CoreConnect bus for integration into Xilinx FPGAs. IBM and Xilinx will map the resulting designs to IBM's advanced chip manufacturing processes, keeping Xilinx FPGAs on the leading edge of technology. IBM will license IP from Xilinx to quickly move leadership process technology to the marketplace. We also plan to explore other areas of cooperation that could benefit customers of both companies.

## About IBM

IBM Microelectronics is the world's leading ASIC supplier and a key contributor to IBM's status as a premier information technology provider. IBM Microelectronics develops, manufactures, and markets state-of-the-art semiconductor and interconnect technologies, products, and services. Its superior integrated solutions can be found in many of the world's best-known electronic brands. More information about IBM Microelectronics can be found at www.chips.ibm.com. DSP

## The MathWorks and Xilinx take FPGAs into Mainstream DSP

Now you can develop high-performance programmable DSP systems with Xilinx FPGAs using system design and verification tools from The MathWorks, Inc.

by Per Holmberg Sr. Product Marketing Manager, Xilinx per.holmberg@xilinx.com

## Anne Mascarin

DSP Market Segment Manager, The MathWorks amascarin@mathworks.com

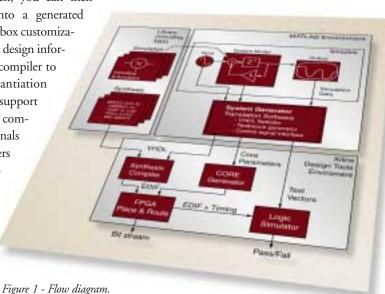

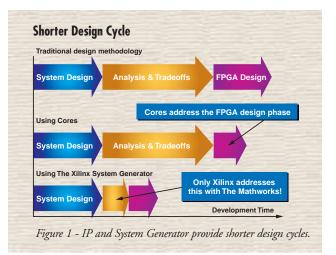

The MathWorks and Xilinx have entered a strategic exclusive alliance and joint development agreement for the system-level creation of FPGA-based DSP designs. The first product will be the Xilinx System Generator for Simulink(tm) software. Used with The MathWorks' popular Simulink system-level design tools, and the Xilinx CORE Generator and LogiCORE DSP algorithms, this software is the first to bridge the gap between system-level DSP design and FPGA implementation, allowing you to easily design high-performance DSP applications in Xilinx FPGAs. The overall system flow is illustrated in Figure 1.

## **System Overview**

The Xilinx System Generator automatically generates hardware description language (HDL) code from a system representation model in Simulink. The HDL design can then be synthesized for implementation in Xilinx FPGAs using standard hardware synthesis software. To maximize predictability, density, and performance, the System Generator automatically maps blocks in the system design into optimized LogiCORE algorithms (cores). With only one representation of the design and no manual intervention when translating the system-level design to HDL, a common source of errors is removed.

You can significantly reduce development time by quickly iterating between the system-level model in Simulink and the hardware implementation. This is especially important for DSP applications, because many system-level design trade-offs are based upon the results of the hardware implementation. Consequently, your development time is significantly reduced, and moreover, even if you are new to FPGAs, you can use the familiar tools from The MathWorks, along with the Xilinx FPGA development tools, to create FPGA-based DSP applications. This combination not only gives you the ease-of-use and time-to-market advantages of FPGAs but also the highest possible performance.

## **The System Generator**

The System Generator consists of two components to help you proceed from a system model to actual hardware. The Xilinx Block Set (XBS) allows you to embed bit-true and cycle-true models of FPGA-specific circuitry into a Simulink design, while the System Generator translation software converts the Simulink model into synthesizable VHDL, with Xilinx FPGA hardware as the target.

The XBS provides these elements:

- Parametric blocks for DSP, arithmetic, and logic functions.

- Gateway blocks to communicate with the Simulink environment, where you have access to the extensive set of Simulink DSP libraries.\*

- Special tokens to support user-defined black boxes and to invoke the System Generator interface to the Xilinx FPGA software.

The XBS provides the functionality of:

- Simulink S-functions the Simulink representation of the XBS.

- Synthesizable VHDL the hardware representation of the XBS, including the use of Xilinx cores where appropriate.

The System Generator software token activates the translation software that converts a Simulink model built from XBS elements into synthesizable VHDL. The VHDL generated may include cores for appropriate functions, as well as corresponding simulation models.

The System Generator graphical user interface (GUI) allows you to customize the Simulink simulation. For example, it can hierarchically override fixed-point values with doubles. This is particularly useful during design and debugging.

## Simulink

You can model a VHDL design using any combination of Simulink blocks. By using the XBS black box token, you can then instantiate the design into a generated VHDL model. The black box customization GUI encapsulates the design information necessary for the compiler to create the correct instantiation interfaces. This black box support allows the abstraction of commonly used control signals and ports, and then infers them within the generated VHDL.

Working in Simulink, you create a model of the hardware system as well as one or more test environments in which to

simulate the model. When the model is first entered, simulation is typically performed using floating-point data to verify its theoretical performance. You then add the appropriate XBS elements, and then convert data types to the bit-true representations used in the hardware implementation. Then the model is re-simulated to verify its performance with quantized coefficient values and limited data bit widths, which can lead to overflow, saturation, and scaling problems. User-defined black boxes can also be incorporated in the modeling and elaboration process. When the model has been converted to a form realizable in the FPGA and its performance meets specification, you can invoke the netlist and the test bench generator.

## The Netlister and Mapper

The netlister extracts a hierarchical representation of the model structure annotated with all the element parameters and signal data types. A mapper then analyzes the elements in the hierarchy and creates a VHDL description of the design. Where possible, the mapper uses the Xilinx CORE Generator to generate optimized LogiCORE implementations for specific design elements.

When an element or its parameter values imply functionality unavailable in the CORE Generator, the mapper instantiates a reference to a parameterized, synthesizable

entity in a synthesis library or your own supplied model. The actual hardware entities used have additional inputs and outputs for control signals that are not evident at the level of abstraction used in Simulink. The mapper inserts the necessary control ports and connects them to control logic blocks.

## About The MathWorks

The MathWorks develops technical computing software for engineers and scientists in industry and education. An extensive family of products, based on MATLAB and Simulink, provides high-productivity tools for

solving challenging mathematical, computational, and simulation

The MATH WORKS

problems. For more information see www.mathworks.com

Multi-rate clocking is supported through time step information provided during simulation. Each control logic block is given a default synthesizable behavior which may require alteration to achieve an efficient implementation.

## The Testbench Generator

The testbench generator is an interactive tool that runs in the MATLAB environment, in

> which you capture the input stimuli and system outputs of selected simulation runs for conversion to test vectors. The generator converts the captured simulation data into VHDL code that will exercise the implemented model and test its outputs against the expected results.

## **Logic Synthesis**

The Xilinx Foundation Series, or any synthesis compiler supported through the Xilinx Alliance Series software tools, can be used to synthesize the control logic and elements for which no hardware macros exist, and combine all the pieces into a fully realized netlist. The outputs of this back-end process are a bit stream

and an EDIF structural netlist of the hardware, annotated with timing information. This netlist can be simulated with the test vectors produced previously from system simulations to verify the performance of the completed FPGA hardware realization.

## Conclusion

With the introduction of the Xilinx System Generator for Simulink, you now have a tool that makes the job of incorporating FPGAs into your DSP designs easier than ever before. Today, Xilinx FPGAs provide you with the world's highest-performance programmable DSP solution, supporting applications equivalent to 160 billion MACs. As FPGA technology continues to advance, it is expected that by the year 2002, you will have access to a ten million gate FPGA offering 0.6 Tera MACS per second.

> See www.xilinx.com for more information.

## The World's Highest-performance Programmable DSP Solution. A New Paradigm in High Performance Digital Signal Processing...

by Rufino Olay Sr. DSP Product Marketing Engineer, Xilinx rufino.olay@xilinx.com

Xilinx DSP consists of the Virtex and Spartan series FPGAs, a wide range of DSP algorithms, and a comprehensive set of software tools and prototyping boards. This is a complete DSP solution giving you the high performance and system integration of ASICs and ASSPs plus the reconfigurability and quick turnaround of standard processors. This ultimate combination provides a comprehensive and robust platform to help you create the highest performing reprogrammable signal processing applications imaginable.

We've created a complete design flow that guides you through the conceptual architectural design, verification, and implementation. Design techniques such as parallel processing and distributed arithmetic, coupled with industry-leading hardware platforms, increases sampling rates by an order of magnitude over that of traditional approach-

es; there is no faster DSP solution, anywhere. Table 1 shows a sample listing of algorithm benchmarks.

## Fast, Flexible, and Easy

With Xilinx DSP you can easily create customized architectures that give you the

best speed and area utilization for your particular needs.

## **Parallel Operations**

Xilinx DSP helps you create the most robust DSP applications by exploiting the parallelism that is inherent in DSP mathematical models. Using the vast logic resources that are present in the Virtex FPGAs, you can create fully parallel structures that give you the utmost in computational power.

## **Customizable Data Structures**

Unlike fixed-width processors or ASICs, Xilinx FPGAs give you the freedom to cre-

## Multiple Data Paths and Channels

Individual arithmetic logic can be linked to separate data paths or mutually coupled to run parallel operations during individual cycles. This approach is ideal for applications consisting of multiple subtasks that need little or no interdependency.

## Logical Operations

You can easily implement a variety of bitand byte-wide operations such as barrel shifting, comparison, rotation, and accumulation by instantiating any of our numerous cores or by writing your own HDL code to cus-

tomize a particular process.

## The MathWorks Simulink Integration

Xilinx and The MathWorks (the leader in DSP algorithm tools) have created a strategic alliance that allows you to build high performance DSP systems in Xilinx FPGAs using the system design and verification tools with which you are already familiar. The result is the Xilinx System Generator<sup>™</sup> tool-set which

bridges the gap between your conceptual architectural design and the actual translation and implementation of your FPGAbased DSP system.

With the Xilinx System Generator you can easily experiment with various DSP functions and quickly see the algorithmic tradeoffs between performance and silicon area.

| Algorithm            | Benchmark       | Unit of Measure |

|----------------------|-----------------|-----------------|

| 16-bit               | 160,000,000,000 | MAC/s           |

| 256 Tap FIR          | 160             | MSPS            |

| 1024 pt FFT          | 41              | USEC            |

| Reed Solomon Decoder | 87              | MHz             |

| JPEG Codec           | 21              | MHz             |

| ADPCM                | 16              | MHz             |

Table 1 - Performance Matrix

ate custom word lengths for your particular situations, including different parameters within the same design. For example some channels in your system might require more bits of precision than others; you can easily change the algorithm and the Xilinx DSP software will easily accommodate the new data configuration.

Then you can easily compare the cost and speed with off-the-shelf DSP devices.

Key Features include:

- Seamless integration; no manual redesign is required.

- No risk of error introduction.

- Only one source code to maintain.

- Floating-point and fixed-point system simulation.

- Automatically generates HDL description for Xilinx FPGAs.

### **Comprehensive IP Offering**

Our extensive selection of IP, including filters, correlators, transforms, FFTs, FECs, integrators, DDS, and math functions, gives you the power to build large, complex designs quickly and effortlessly. Plus, our IP is optimized and parameterized for implementation in our Virtex and Spartan FPGAs so you get the most efficient and fastest implementation.

The intuitive GUI in our CORE Generator guides you through the various options to help you customize the IP for your specific design requirements. The features include:

- Scalable IP to fit your particular application.

- Millions of possible permutations.

- Minimal learning curve.

## **New FIR Filter Generator**

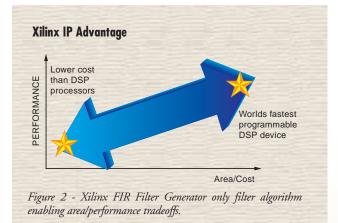

Xilinx recently announced the FIR Filter Generator, a new tool for creating fully optimized and parameterized algorithms for FPGA-based complex single-rate, half-band, Hilbert transform, and interpolated filter designs. Design techniques such as distributed arithmetic are employed to optimize filter structures for high-end DSP applications such as wireless and xDSL modems, medical imaging, and radar signal processing. The operational performance of the FIR filters, in the Virtex family, exceeds 160 billion multiply accumulates (MACs) per second.

The FIR Filter Generator allows you to choose from millions of parameter combinations to match your unique DSP design requirements, from fast, fully parallel systems to cost-effective designs optimized for lower sampling rates, as shown in Figure 2. The available parameters include:

- From 2 to 1024 taps.

- From 1 to 32 bit input data and coefficient precision.

- Signed or unsigned input data.

- Fully serial, parallel, or a combination of serial/parallel filter implementations with the ability for multi-clocking of output data.

- Time multiplexing of data for multiple channel structures.

## Smart-IP Technology

By employing the Xilinx Smart-IP Technology, the CORE Generator maintains constant performance over the entire range of FPGA densities; Smart IP gives you predictable timing and optimal an implementation for area and speed. This predictability, unique to Xilinx, is essential for incorporating entire systems on an FPGA.

## **In-House Expertise**

We've gathered together a highly knowledgeable team of DSP experts to create the best possible DSP tools and to provide you the best possible design expertise. In addition, Xilinx DSP FAEs have extensive design experience which gives them particular insight and knowledge to the challenges and intricacies of high performance DSP applications.

## Third-Party Programs

To help you further reduce your development time, Xilinx has partnered with various DSP development companies to provide a wide range of services, from algorithm development to full turnkey operation, giving you:

- A large and growing selection of system IP from our AllianceCORE partners.

- Access to the leading DSP experts in various application areas.

- Design services and expertise from the Xilinx XPERTS partners.

- A wide range of in-house and third-party design expertise and application experience.

In addition, numerous third-party vendors

such as GV & Associates, Nallatech, and Lyr Signal Processing also offer prototyping hardware.

## Conclusion

With the Xilinx DSP solution, you get faster DSP designs that are customized for your exact needs. Plus, there are no NRE charges or limitations to your creativity. There simply is no better way to create DSP designs.

For more information see www.xilinx.com/dsp

## IRL Makes Console Switching Faster and More Reliable.

by Robert Rowe Product Manager, Apex robert.rowe@apex.com

One of the most pressing concerns facing Information Systems Managers today is managing the volume and diversity of servers under their authority. As corporations increase the number of servers they deploy, the infrastructure needed to support this growth requires more efficient management of physical space, server information, and staff time.

Administrators have recognized the importance of reducing the amount of space occupied by computing and peripheral devices, and as a result, are implementing console switches to manage and operate multiple servers from a single console. This provides more space for servers, routers, hubs, and printers by reducing the quantity of keyboards, monitors, and mice.

Apex, the market leader in console switches, chose Xilinx to provide the FPGAs to create their next generation switch. By using Xilinx FPGAs and the Xilinx Internet Reconfigurable Logic (IRL) technologies, Apex could develop a console switch that can be upgraded with new services or functionality, in the field, without having to supply customers with new boards or EPROM chips. Not only does this provide convenience for their installed base of customers, it also provides flexibility for developing and rapidly deploying new services and for remotely reconfiguring data in the console switch.

## Faster Time-to-Market

By populating the console switch with Xilinx FPGAs, Apex engineers developed 80% of the base solution to get the system up and running. Then, by the time the switches were deployed to customers, the remaining 20% of the code was completed and transmitted to the systems in the field. This gave Apex a lead in deploying the product to the field before the competition-a real time-to-market advantage and a key benefit for their customers.

## **Flexibility and High Throughput**

In most customer environments, the console switch is located in the same facility as the servers, but with the flexibility offered by Xilinx FPGAs, the console can be located anywhere in the world. With the Apex Emerge2000, for remote access server control, you can manage the graphical consoles of your server population from any location.

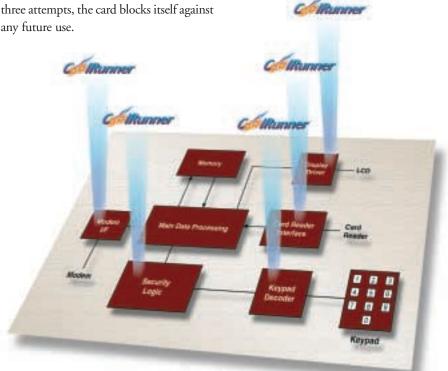

The basic architecture is based on the PCI bus (Figure 1). By using two Xilinx FPGAs in each Emerge2000, one for PCI communications that is loaded at power-up and remains loaded, and the other FPGA loaded dynamically at run time, Apex console switches never have to break the PCI

communication. The Xilinx PCI core provides up to 33 MHz operation, is easy to use, and is easy to migrate to other PCI cores with higher bus widths if the need arises.

Xilinx also provides an easy migration path from low to high density devices allowing Apex to include more robust features in their console switch products as their requirements evolve.

## **Rapid Prototype Development**

By employing Xilinx FPGA technology, the Apex engineers could continue developing

## ...DUE TO THE ABILITY TO REMOTELY UPGRADE THE DESIGN OVER THE INTERNET, THE ENGINEERS WERE ABLE TO SHIP THE PRODUCT EARLY, WITH THE ASSURANCE THAT ANY NEW FEATURES COULD EASILY BE ADDED IN THE FIELD.

the design right up to the time of board delivery. Once the boards became available, the engineers could load the FPGA configuration at the work bench and verify the design. If they had used custom ASICs, it would have required much more time to complete the design. In addition, due to the ability to remotely upgrade the design over the Internet, the engineers were able to ship the product early, with the assurance that any new features could easily be added in the field.

## **Technical Support from Xilinx**

Support from a supplier is a critical path item, often overlooked when designers view supplier technology. Obtaining the most up-to-date information, in a precise format, can become a critical factor when moving at the rapid pace our market demands. The Xilinx support organization is fast and responsive, and delivered the lat-

### Figure 1 - The Emerge2000 board

## Conclusion

Xilinx FPGAs, along with the Xilinx IRL technologies, allows companies like Apex to build flexible, next-generation equipment that can be upgraded over the Internet. The time to market advantages are obvious and the unique design possibilities are limited only by your imagination.

## **About Apex**

Apex designs, manufactures and markets stand-alone electronic switching systems and integrated server cabinet solutions for the client/server computing environment. Apex supplies stand-alone switching systems to some of the largest PC manufacturers in the industry for integration into their product offerings, providing switching systems to OEMs (Compaq, Dell, IBM, and Hewlett-Packard) representing 43 percent of all PC servers and 66 percent of all "super" servers shipped worldwide.Go to http://www.apex.com for more information.

## LavaCORE -A Configurable Java Processor

Create Java-enabled appliances, mobile devices, secure Internet devices, and embedded network computers that can be dynamically configured for application-specific computing.

by Bhaskar Bose, Ph.D. and M. Esen Tuna President, Vice President - R&D, Derivation Systems, Inc. bose@derivation.com, mtuna@derivation.com

LavaCORE<sup>TM</sup> is a 32-bit configurable Java<sup>TM</sup> processor core targeted to the Xilinx Virtex FPGA architecture. The processor executes Java bytecode directly in hardware eliminating the need for software-based interpreters or code translators. LavaCORE is a clean-room implementation of the Java Virtual Machine and is provided as a synthesizable "soft-core" with a suite of tools for parameterized core generation, hardware/software co-design, co-verification, and custom Java application development.

LavaCORE is a revolutionary product that provides unparalleled flexibility for a wide range of prototyping and embedded applications. Direct Java bytecode execution keeps the runtime to a minimum making the processor ideal for embedded applications that require small memory foot-prints and flexible reconfigurable architectures. Both the application and the operating system code can be developed in Java and compiled to native code by standard Java compilers.

LavaCORE is designed to bring embedded Java technology to the reconfigurable marketplace. The customizable core and dynamic reconfiguration take full advantage of the features of programmable hardware.

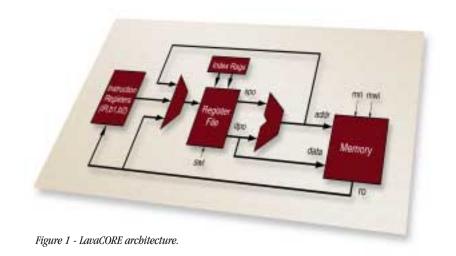

## LavaCORE Features

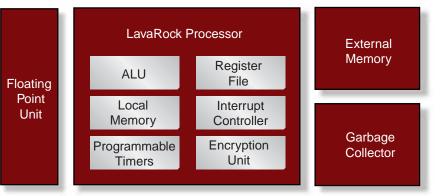

The processor core features a 32-bit architecture with 32-bit address and data paths. Our reference design is implemented in a Virtex XCV300 BG352-4 FPGA. Figure 1 shows a block diagram of the architecture. Some of the features are highlighted below:

- 32-bit direct execution Java processor.

- Executes Java Virtual Machine bytecode in hardware.

- Stand-alone (system on a chip) or core configuration.

A 16x32-bit dual-ported RAM implements the register-file. The instruction register is composed of three 8-bit registers denoting the instruction, byte one, and byte two of the instruction stream. A 32-bit ALU computes arithmetic and logical operations. Additional signals include clock, reset, signal interrupt, memory interface, and a set of observability pins for the state and flags.

- Built-in hardware encryption module.

- Fully synthesizable FPGA core.

- Parameterized Core Generator automatically synthesizes VHDL, Verilog, or EDIF gate-level netlists.

- Software support includes Parameterized Core Generator, LavaOS Runtime Environment, Co-Simulation/Verification Tools, and Hardware Debugger.

Cores

Figure 2 - LavaCORE system architecture.

## **Parameterized Core Generator**

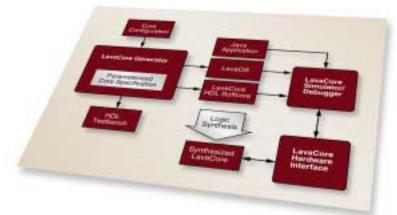

The LavaCORE Parameterized Core Generator operates via an intuitive graphical interface and includes user selectable parameters for a wide range of configurable options. Every implementation of LavaCORE can be application specific, leading to optimal solutions in terms of power, speed, and area.

Typically, specialized embedded applications use only a subset of the full JVM instruction set. By analyzing the application, you can determine which Java bytecode instructions can be omitted or moved from hardware to software, improving various cost criteria.

Additional options allow you to include functional components of the synthesized architecture such as the built-in encryption engine, programmable timers, and interrupt controllers. For larger systems, floating point and external memory interfaces are defined (Figure 2).

Once parameterized options are selected, the LavaCore Generator automatically synthesizes a gate-level implementation in either VHDL, Verilog, or EDIF netlist formats. Along with this softcore, an HDL testbench and a customized runtime called LavaOS<sup>TM</sup> are generated.

The synthesized core can then be directly input to Xilinx Foundation Series or Alliance Series software for place and route. The HDL testbench is used both to test the hardcore and softcore. Figure 1 depicts the dataflow architecture of a LavaCore instance.

## Linker/Application Builder

Standard Java-class files, generated from third party commercial Java development environments, are statically resolved to build executables. In addition, the linker builds the boot tables, class initialization codes, and assigns the interrupt and trap handlers.

The executable image incorporates the runtime environment. It is designed for embedded applications and is small enough to be implemented in the internal block RAM. In a standalone configuration, the LavaCORE system architecture can incorporate the entire runtime environment and a Java application within the Virtex block RAM.

## **Application Debugging Tools**

The LavaCore application debugging tool set consists of a core simulator and a hardware interface (Figure 3). The simulator has a built-in debugger that features single stepping, memory and register file monitors, and conditional break points. The simulator and the debugger share a graphical user interface to display and debug the LavaCore execution both at instruction and micro steps.

The LavaCore simulation environment consists of three separate components that validate all three aspects of the LavaCore:

- The instruction tester.

- The application simulator.

- The hardware testbench for the synthesized core.

The hardware interface provides an implementation debugging bridge for the synthesized hardware. The same debugging environment and user interface are used for the testing of the target hardware.

## Conclusion

The LavaCORE Configurable Java Processor core enables the deployment of Java technology for a new generation of embedded reconfigurable systems. Native execution of Java bytecode provides reliable hardware execution, denser code, and minimum runtime environment. The LavaCORE parameterized core generator allows you to configure the capabilities of the processor core and synthesize an optimal LavaCORE for your application.

LavaCORE provides a fast design solution for embedded Java processors targeted to programmable hardware. With our configurable Java processor core and co-design/verification environment this unique IP product will reduce design time leading to faster time to market.

For more information about Derivation Systems, or the LavaCORE products, see www.derivation.com

LavaCORE and LavaOS are trademarks of Derivation Systems, Inc., JAVA is a registered trademark of Sun Microsystems, Inc.

Figure 3 - LavaCORE design environment.

Software

## Inferring Read Only Memory in FPGA **Compiler II** and **FPGA** Express

## by Alan Ma

Senior Corporate Applications Engineer, Synopsys, Inc. alanma@synopsys.com

Prior to the recent advancements in FPGA technology, you had to rely on external RAM or ROM. Now, with the introduction of million-gate FPGAs such as the Xilinx Virtex devices, you have access to abundant on-chip memory resources. FPGA Compiler II/FPGA Express (FCII/FE) takes advantage of Virtex resources such as Look-Up Tables (LUTs) MUXF5s, MUXF6s, and on-chip block SelectRAM to provide the highest quality of results for ROM functions.

## **Coding Styles**

Version 3.4 of FCII/FE recognizes a ROM description using CASE statements in both

Verilog and VHDL, and by using constant arrays in VHDL.

## **Using CASE Statements**

FCII/FE infers ROM when the inputs to the CASE statement are constant and all the states are specified. Figure 1 shows an example of an 8x4 ROM in Verilog. Figure 2 illustrates its VHDL equivalent.

## **Using Constant Arrays**

You also have the option of using constant arrays in VHDL. Figure 3 describes the coding style for the same 8x4 ROM where CONV\_INTEGER is a built-in function that converts std\_logic\_vector to integer.

## **General Implementations**

FCII/FE generally implements ROM using LUTs, MUXF5s, and MUXF6s when targeting Xilinx Virtex devices. The actual resources used are closely related to the width of the address port. If the address has less than or equal to four bits, then the ROM will be implemented using LUTs. If the address has five bits, then MUXF5s, (which provide multiplexer functions in one half of a Virtex Configurable Logic Block), will be used in addition to the LUTs. If the address has between six to nine bits, the ROM will be implemented using LUTs, MUXF5s, and MUXF6s which provide multiplexer functions in a

| module | e rom_8x4      | (<br>address,<br>rom_out<br>); |

|--------|----------------|--------------------------------|

| input  | [2:0]          | address;                       |

| output | [3:0]          | rom_out;                       |

| reg    | [3:0]          | rom_out;                       |

| always | @(address)     |                                |

|        | case (address) |                                |

|        | 3'b000         | : rom_out <= 4'b0001;          |

|        | 3'b001         | : rom_out <= 4'b0010;          |

|        | 3'b010         | : rom_out <= 4'b0100;          |

|        | 3'b011         | : rom_out <= 4'b1000;          |

|        | 3'b100         | : rom_out <= 4'b1000;          |

|        | 3'b101         | : rom out <= 4'b0100;          |

|        | 3'b110         | : rom_out <= 4'b0010;          |

|        | 3'b111         | : rom_out <= 4'b0001;          |

|        | endcase        |                                |

| endmo  | dule           |                                |

Figure 1 - Using CASE statements for ROM in Verilog.

| library ieee;<br>use ieee.std logic 116 | 34 all:     |                                                           |

|-----------------------------------------|-------------|-----------------------------------------------------------|

| use leee.stu_logie_11e                  | ,           |                                                           |

| entity rom_8x4 is port                  |             | d_logic_vector(2 downto 0);<br>d_logic_vector(3 downto 0) |

| end rom_8x4;                            |             |                                                           |

| architecture rtl of rom_<br>begin       | 8x4 is      |                                                           |

| process (addre<br>begin                 | ss)         |                                                           |

| case a                                  | ddress is   |                                                           |

|                                         | when "000"  | => output <= "0001";                                      |

|                                         | when "001"  | => output <= "0010";                                      |

|                                         | when "010"  | => output <= "0100";                                      |

|                                         | when "011"  | => output <= "1000";                                      |

|                                         | when "100"  | => output <= "1000";                                      |

|                                         | when "101"  | => output <= "0100";                                      |

|                                         | when "110"  | => output <= "0010";                                      |

|                                         | when "111"  | => output <= "0001";                                      |

|                                         | when others | => output <= "0000";                                      |

| end ca                                  | se;         |                                                           |

| end process;                            |             |                                                           |

| end rtl;                                |             |                                                           |

full Virtex CLB. When the address has ten or more bits, FCII/FE implements ROM using on-chip block SelectRAM resources if certain conditions are met.

## Using Block SelectRAM

The Virtex series provides dedicated blocks of on-chip, dual port synchronous RAM, with 4096 memory cells (bits). These resources can also be used for ROM if certain conditions are met. Our research indicates that when the address of the ROM has ten bits and the data has more than or equal to three bits, quality of results can be improved by mapping the ROM to block SelectRAM if the output of the ROM is registered. However, if the data has less than or equal to two bits (when the address has ten bits), using LUTs, MUXF5s, and MUXF6s, as described in the previous section, yields better results. For ROM whose address has more than or equal to eleven bits, block SelectRAM will always be used if the output is registered. Table 1 summarizes the conditions for ROM inference.

To reserve block SelectRAM for user-defined functions, you can use the scripting command "set\_chip\_instantiated\_blockram". For example, the following reserves 4096 bits of block SelectRAM for inferred ROM:

## set\_chip\_instantiated\_blockram 4096

While set\_chip\_instantiated\_blockram applies to the current project, you can use the variable proj\_user\_instantiated\_blockram to reserve block SelectRAM globally for all the subsequent projects. For example, the following reserves 4096 bits of block SelectRAM for all future projects:

### proj\_user\_instantiated\_blockram 4096

### Conclusion

Inferring ROM is easy with FPGA Compiler II and FPGA Express, which take full advantage of the abundant on-chip memory resources of the Xilinx Virtex devices.

Visit the Synopsys FPGA website at www.synopsys.com/fpga for other information on the latest FPGA synthesis technologies.

|                         |                         | LUT | MUXF5 | MUXF6 | SelectRAM |

|-------------------------|-------------------------|-----|-------|-------|-----------|

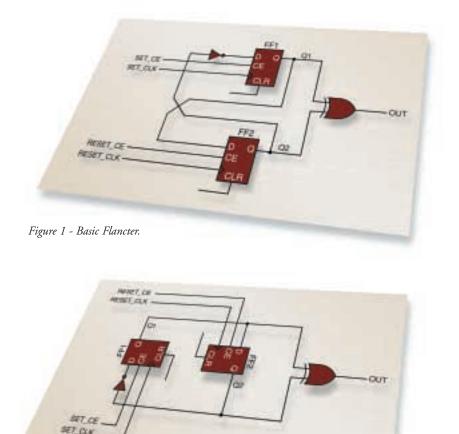

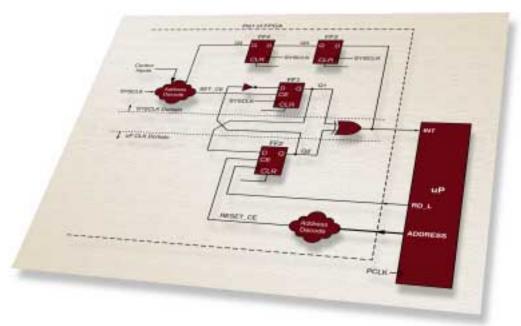

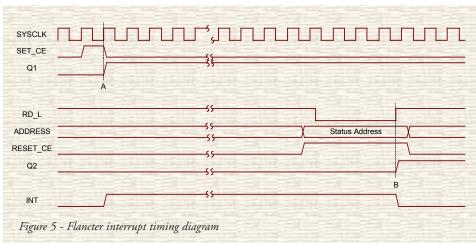

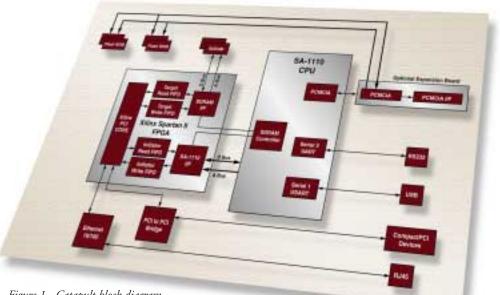

| ADD <= 4 Bits           | Any Data Width          | •   |       |       |           |