#### EDITOR Carlis Collins editor@xilinx.com 108-879-4519

#### SENIOR DESIGNER

ack Farage

#### **3OARD OF ADVISORS**

Dave Stieg Dave Galli Mike Seither Peter Alfke

Pronto Creative vww.prontocreative.com

(ilinx, Inc. !100 Logic Drive ian Jose, CA 95124-3450 'hone: 408-559-7778 iAX: 408-879-4780 2000 Xilinx Inc. All rights reserved.

(cell is published quarterly. XILINX, the (ilinx logo, and CoolRunner are registered rademarks of Xilinx, Inc. Virtex, ogiCORE, Spartan, SpartanXL, Alliance ieries, Foundation Series, CORE Generator, Checkpoint Verification, TimeSpecs, Smart P, OPRO, Selectl /O, Selectl/O+, True Dualort, WebFITTER, WebPACK, Select RAM, BlockRam, Xilinx, Online, and all XC-prefix vroducts are trademarks, and The 'rogrammable Logic Company is a service nark of Xilinx, Inc. Other brand or product iames are trademarks or registered tradenarks of their respective owners.

he articles, information, and other materi-Is included in this issue are provided oley for the convenience of our readers. (ilinx makes no warranties, express, mplied, statutory, or otherwise, and iccepts no liability with respect to any uch articles, information, or other materiils or their use, and any use thereof is olely at the risk of the user. Any person or entity using such information in any vay releases and waives any claim it night have against Xilinx for any loss, lamage, or expense caused thereby.

## **FROM THE EDITOR** A Tale of Two **Giants**...

nce upon a time there were two electronic giants, struggling for dominance in the Valley of Silicon. They were unfriendly rivals; each making similar products, each holding on to an equal share of the marketplace, each "leapfrogging" the other with new designs. When Giant X introduced a new MP3 player, for example, Giant Y would soon introduce one with more features at a lower cost. And, because they used the same basic components, design methods, and manufacturing processes, they each remained "competitive," but their profit margins were atrocious. The competition was fierce; life was uncertain; no one smiled.

Then one bright morning (after reading a particularly insightful editorial in the Xcell Journal), Giant X awoke from a vivid dream in which he saw the future. He thought "What if I could create new products that never had to be replaced? What if I could sell customized features, options, and complete new designs, and download them to my customers, anywhere in the world, over the Internet? That's like manufacturing something once, but selling it many times over!" He knew it was the next "big thing." He grinned a big toothy grin.

Giant X began designing all his new products using the latest programmable logic technology (from Xilinx of course). The new FPGAs and CPLDs were amazing; they were dense, fast, inexpensive, and required little power; they were easy to use because the development tools were fast and efficient, and there was a lot of Intellectual Property (cores) available to make his life easy. Plus, with Xilinx technology, he could provide an Internet interface to all of his products and easily download almost any new design the market demanded. "Simply brilliant!" remarked the press. "Amazing!" remarked his customers. "Highly profitable!" said his shareholders. Everyone grinned big toothy grins, except Giant Y of course.

It wasn't long before Giant Y's market share began to nosedive. In a panic he worked night and day to keep up with the almost daily introduction of new products, features, and options from Giant X; but he could no longer compete using his old technology. Greatly embarrassed, Giant Y quietly packed his bags and left town; he was never heard from again.

The moral of this story is clear. Low-cost, high-performance programmable logic, reprogrammed remotely, is the obvious next step in the evolution of logic design—the advantages are overwhelming.

This issue of Xcell will show you some of our latest, low-cost, remotelyreprogrammable giant killers

#### COLUMN

The year 2000 promises to bring even faster growth, with many new applications, because our technology has passed a key milestone.

#### **COVER STORY**

Spartan<sup>™</sup> FPGAs are experiencing tremendous growth due to their inherent advantages over ASICs.

#### **PRODUCT INFORMATION**

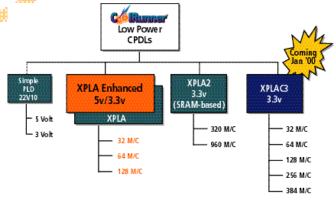

New CoolRunner devices are ideal for low-power, high-performance applications.

#### **APPLICATIONS**

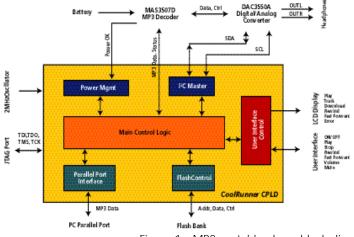

CoolRunner<sup>™</sup> CPLDs are used as the main controller for an MP3 player. (Also see a Spartan-II MP3 design on page 15.)

#### SOFTWARE

52

This HDL design methodology can help you use the largest Virtex<sup>™</sup> FPGAs with a minimum amount of time spent on synthesis, simulation, and verification.

#### www.xilinx.com

E-mail your request to: literature@xilinx.com,

For A FREE **Subscription** To The Xcell Journal

mailing address 2. Your title

1. Your full name and

3. The name of your company

please be sure to include:

- 4. Your e-mail address

- 5. Is this new subscription or a subscription renewal?

#### Inside This Issue:

#### View from the Top

The Programmable Logic Market

**Cover Story**

Δ

5

26

35

The New Spartan-II FPGA Family, Kiss Your ASIC Good-bye

#### **Spartan FPGAs**

New Spartan-II FPGA Family -Ideal for ASSP Replacement . .

The Spartan-II Design Flow Simple Powerful, and Efficient . . . . .

How to Create an MP3 Player, Using a Spartan-II FPGAs ...

Inverse Multiplexing for ATM (IMA) .....

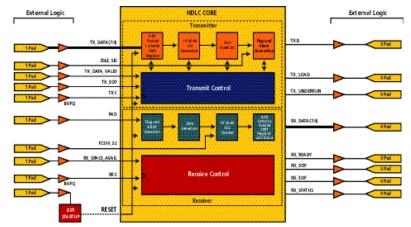

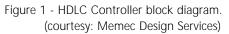

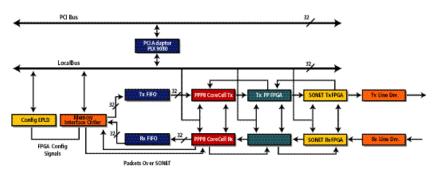

**HDLC Controller Solutions Using** Spartan-II FPGAs

Low Power Benefits of Spartan-XL Family .....

#### **CoolRunner CPLDs**

The New XPLA3 CPLD Family -The Best CoolRunner Family Yet

**CoolRunner Power** Estimator Tool .....

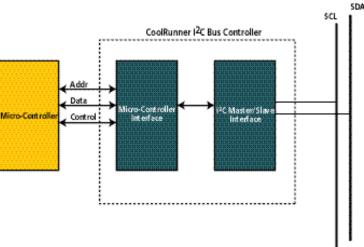

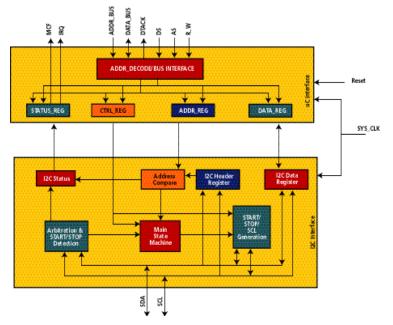

Implementing an I<sup>2</sup>C Bus Controlle in a CoolRunner CPLD .....

How to Create an MP3 Player Using a CoolRunner CPLD . . . .

#### Applications

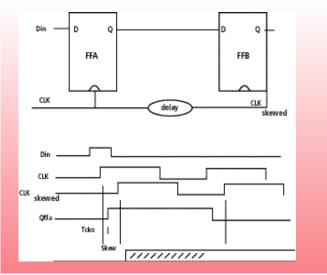

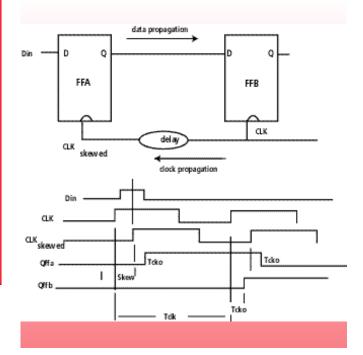

Get the Best Registered I/O Timing with Virtex-E FPGAs ...

**Understanding Setup and** Hold Times

HDL Coding for Pseudo-random Noise Generators . . . . . . .

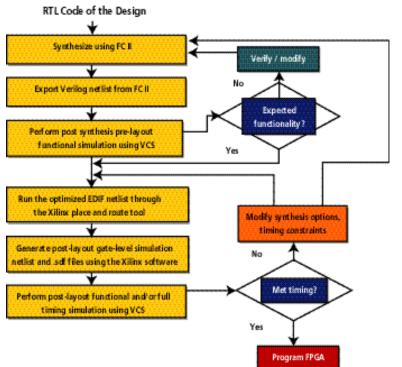

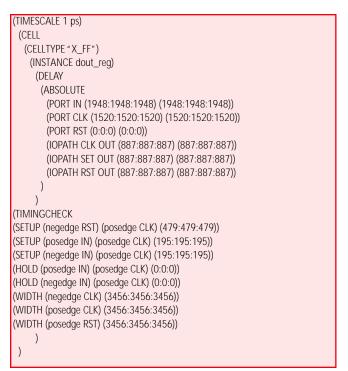

Post Synthesis Verification for Virtex FPGAs

Using the ModelSim FPGA Library Manager . . . . . . . . . . . .

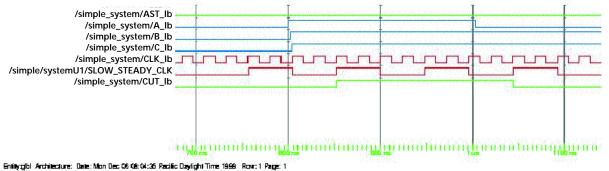

FPGA System Simulation

and Synthesis . . . . .

#### **Columns/Reference**

| Industry Analyst Column    |   |  |  |  |

|----------------------------|---|--|--|--|

| Q&A Column                 |   |  |  |  |

| Trade Show Column          |   |  |  |  |

| Software Availability Guid | e |  |  |  |

## The Programmable Logic Market Grew Significantly in 1999.

...and the year 2000 promises to bring even faster growth, with many new applications, because our technology has passed a key milestone.

by Wim Roelandts, President and CEO, Xilinx

rogrammable logic technology has made many significant advances over the last year, and is well on its way to becoming the development technology of choice for most applications.

Xilinx is growing very quickly as a result. Here are some of the highlights of our phenomenal growth in 1999:

- The Xilinx stock split twice, once in March and once in December. This helped give us a market capitalization of about \$14.5 billion, making us second only to Intel among semiconductor suppliers here in Silicon Valley. This gives us an increased ability to fund new research and bring advanced new technologies to market.

- Xilinx was placed on the Merrill Lynch "Top 10 Tech" list (replacing Intel), indicating their highest confidence in our continued strength, and in the growth potential of the overall programmable logic market.

- Xilinx was added to the S&P 500 index, another indication of the market's confidence in our ongoing strength.

- We built a new 180,000 sq. ft. building on our San Jose campus to handle our recent growth, and began the development of a new 130,000 sq. ft. facility in Longmont Colorado. Groundbreaking is scheduled for March 2000.

- We expect our revenues to approach \$1 billion by the end of our fiscal year (March 2000), 50% higher than last year.

It was a very good year for Xilinx; our investments in new device and software technologies have paid huge dividends, and our products have consistently extended the previous limits of density and performance while significantly reducing prices.

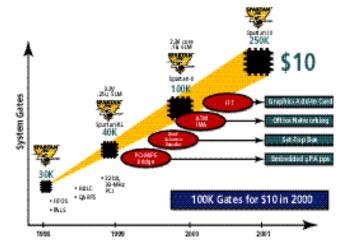

FPGAs were once used primarily in high-end, low-volume equipment which consists of about 25% of the total marketplace. This was due in part to the relatively high cost of FPGAs (as compared to custom devices). To serve the other 75% of the marketplace, our research showed us that we would need to produce high-performance, full-featured FPGAs with at least 100K gates, and sell those devices, in volume, for less than \$10.00. With the introduction of our new Spartan-II family, that's exactly what we've done. This is a significant milestone that will bring many unique new applications.

The growth of the programmable logic marketplace is important to you because these devices allow you to get your products to market six to nine months faster than with ASICs, and they allow you to upgrade your equipment over any network after it's installed at your customers' locations. We here at Xilinx will continue our innovation and this will lead to higher densities, higher performance, more features, a wider selection of intellectual property (cores), and lower prices. We intend to keep making your job easier while adding value to your products.

## THE NEW Spartan-II FPGA Family KISS YOUR GOOD-BYE

Spartan FPGAs are experiencing tremendous growth due to their inherent advantages over ASICs.

by Jay Aggarwal, Product Marketing Manager Spartan Series, Xilinx, jay.aggarwal@xilinx.com

he Spartan Series FPGAs, introduced by Xilinx in January 1998, offer a very attractive alternative to ASICs for your high volume, low cost applications. The Spartan families are designed to penetrate markets that were once dominated by ASICs. These include digital modems, printers, faxes, portable audio players (such as MP3), set-top boxes, and POS terminals. The Spartan Series is the first FPGA family to provide a complete and compelling mix of advanced features, low prices, high performance, and powerful development tools; the key ingredients required by ASIC designers. Now, the new Spartan-II<sup>TM</sup> FPGA family sets a new standard for low cost, and high performance.

#### The Spartan-II Family

Fabricated on a leading 0.18  $\mu$ m, six-layer metal process, the Spartan-II family uses the most advanced process technologies available today. The family's core voltage operation is 2.5V, yet it incorporates unique I/O technology that allows both 3.3V and 5V I/O operation.

| Device        |                 | XC2S15 | XC2S30   | XC2S50 | XC2S100 | XC2S150 |  |

|---------------|-----------------|--------|----------|--------|---------|---------|--|

| System Ga     | ites            | 15K    | 30K      | 50K    | 100K    | 150K    |  |

| Logic Cells   |                 | 432    | 972 1728 |        | 2700    | 3888    |  |

| Block RAMBits |                 | 16,384 | 24,576   | 32,768 | 40,960  | 49,152  |  |

| Block RAM     | <b>//Blocks</b> | 4      | 6        | 8      | 10      | 12      |  |

| DLLs          |                 | 4      | 4        | 4 4 4  |         | 4       |  |

| I/O Standa    | rds Supported   | 17     | 17       | 17     | 17      | 17      |  |

| Max I/O       |                 | 86     | 132      | 176    | 196     | 260     |  |

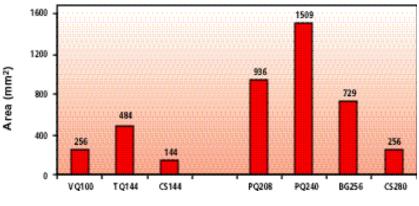

| Packages      | 14x14mm         | VQ100  | VQ100    |        |         |         |  |

|               | 20x20mm         | TQ144  | TQ144    | TQ144  | TQ144   |         |  |

|               | 12x12mm         | CS144  | CS144    |        |         |         |  |

|               | 28x28mm         |        | PQ208    | PQ208  | PQ208   | PQ208   |  |

|               | 17x17mm         |        |          | FG256  | FG256   | FG256   |  |

|               | 23x23mm         |        |          |        | FG456   | FG456   |  |

Table 1 - Integrated features.

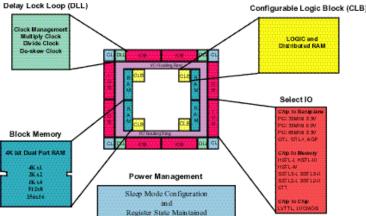

The Spartan-II family includes new systemlevel features such as delay lock loops (DLLs), BlockRAM<sup>™</sup>, distributed RAM, multiple I/O standards, ultra-high performance, and power management. All of the features found in ASICs and ASSP devices are now available in the Spartan-II family at very attractive prices. Spartan-II FPGAs also provide an impressive array of highly complex cores (intellectual property) enabling you to further leverage the time-to-market benefits offered by programmable logic.

#### Memory

On-chip memory is vital to most designs, from buffering data between two dissimilar buses to

Figure 1 - Spartan-II family architecture.

providing storage locations of constants for high performance DSP functions. The Spartan-II family provides you with maximum memory flexibility.

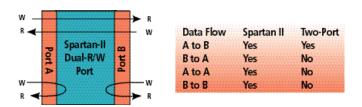

Xilinx pioneered the capability of distributed memory (also found on Spartan and Spartan-XL families), which efficiently implements wide/shallow FIFOs or scratch pads memories. The family also incorporates BlockRAM (in blocks of 4Kbits) which efficiently implement memory for deep FIFOs, single port RAM, and True Dual Port RAMs as shown in Figure 2. Unlike competing two-port architectures, Xilinx provides true dual port RAM operation, for highspeed read and write operation.

#### **Delay Locked Loops**

DLLs perform the same tasks as traditional phase lock loops (PLLs) but are more robust and

Figure 2 - Spartan-II family dual port memory.

are less susceptible to noise interference, a common problem with PLLs. The Spartan-II DLLs allow you to multiply or divide the incoming clock on chip, as well as drive multiple clocks on the board. The DLL feature also allows you to de-skew the clock on chip, ensuring all nodes on the device are synchronized while providing minimum set-up and hold times.

With four DLLs per device, the Spartan-II family provides a sufficient number of DLLs with which you can perform multiple functions. For example, one DLL may be used to deskew the clock on chip, one for multiplying the clock for accelerated performance on chip, two DLLs to drive clocks to various devices on the board—all at the same time. A single crystal oscillator and a Spartan-II device may provide all the clock management you need for your board design.

#### SelectI/O<sup>™</sup>

The Spartan-II family supports most of the popular and demanding I/O standards, including those that are optimized for high-speed memory interfaces. The new input/output standards that are supported, include SSTL, HSTL, AGP, GTL, GTL+, and PCI. The integration of these standards into the Spartan-II family now allow the elimination of costly bus transceivers that take up valuable board space.

The I/Os for the Spartan-II family are 5V and 3.3V tolerant for interfacing with older generation technology on the board. This is a significant advantage for the family because competing architectures are unable to support 5V operation.

Support for high-speed interfaces significantly increases performance over the Spartan (80 MHz) and Spartan-XL (100 MHz) families, to a blazing 200 MHz.

#### **Power Management**

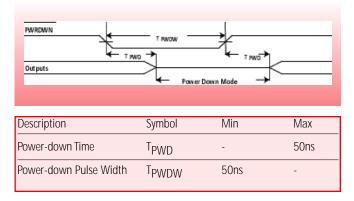

Power consumption is an important issue, especially for portable and hand-held designs. The Spartan-II family extends power management features that were first established with the Spartan-XL family, which provides a power down pin on each device. Once activated, the device goes into a low power sleep mode in which power consumption is significantly reduced. When the pin is deasserted, the device comes back into full power mode and retains its configuration as well as register states.

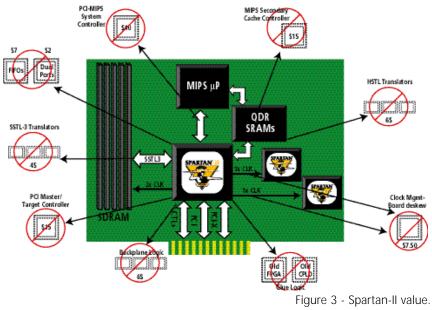

An Example of Spartan-II Value

#### Pricing

The Spartan-II family has been created from the ground-up, in keeping with the Spartan Series philosophy, to provide industry-leading features, density, and performance at price points that match or beat ASICs and ASSP devices. The family has been able to achieve a milestone, long sought after and promised by the programmable logic industry but now only realized by the Spartan-II family: 100,000 gates for \$10.00USD.

Below is a complete listing of high volume prices for the Spartan-II family at introduction.

| Xilinx                                   | Spartan II           |

|------------------------------------------|----------------------|

| Product                                  | High Volume Price*   |

| XC2S15                                   | \$ 3.95              |

| XC2S30                                   | \$ 4.95              |

| XC2S50                                   | \$ 7.95              |

| XC2S100                                  | \$ 9.95              |

| XC2S150                                  | \$ 12.95             |

| * 250K units, a resale price, slowest sp | eed/cheapest package |

Table 2 - Spartan-II family pricing.

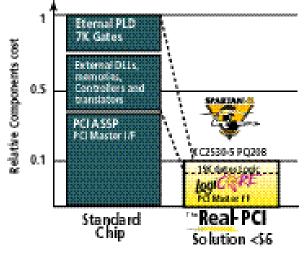

The board diagram in Figure 3 illustrates how you can integrate many different functions into a Spartan-II FPGA to achieve significant cost savings. This example design includes a PCI master/target controller, some HSTL translators, a cache controller, SSTL-3 translators for SDRAM, a backplane interface, some glue logic, and the clock management device. All of these functions can be integrated into the XC2S100 Spartan-II device which costs just \$10.00, almost two-thirds less than the discrete solution, with room to spare for more logic. The Spartan-II solution also uses less board real estate, requires less power, and provides higher reliability.

#### Conclusion

The Spartan-II family offers you the most costeffective and flexible solution, enabling the fastest time-to-market with the lowest possible risk.

For more information regarding how the Spartan-II family addresses traditional ASIC and ASSP designs, please see the article on page 8.

### The Spartan-II family, combined with a vast portfolio of soft IP, is the first programmable logic solution to effectively penetrate the ASSP marketplace.

by Krishna Rangasayee, Manager, Strategic Applications, Xilinx, krishna@xilinx.com

partan-II FPGAs offer more than 100,000 system gates at under \$10.00 and are the most cost-effective PLD solution ever offered. They build on the capabilities of the very successful Virtex<sup>™</sup> FPGA family and include all of the Virtex features, including SelectI/O<sup>™</sup>, BlockRAM<sup>™</sup>, Distributed RAM, and DLLs, with clock speeds up to 200 MHz.

#### PLDs Penetrating the ASSP Market

In the past, programmable logic devices had limited success in penetrating the ASSP market because they could not compete in the key areas of density, features, performance, and cost. However, the Spartan family competes very well due to the use of advanced process technologies. This approach has allowed Xilinx to significantly reduce die sizes, and therefore reduce the cost of the overall solution. This rapid process transition allows the Spartan family to compete

Figure 1 - PLD evolution - addressing the ASSP marketplace.

with ASICs and ASSPs, and has opened up many new markets for PLDs.

#### Advantages of a Programmable ASSP

A programmable ASSP like the Spartan-II family offers significant advantages over a stand-alone ASSP. The advantages are broadly classified under the following areas:

- The value of programmable ASSPs.

- · Accommodating specification changes.

- Testing and verification.

- Xilinx Online<sup>™</sup> field upgradability.

- Problems in creating a stand-alone ASSP.

#### The Value of Programmable ASSPs

ASSPs, designed for a wide array of applications, are rarely able to meet your exact needs. With a programmable ASSP solution, such as Spartan-II FPGAs, you can choose the optimum feature set and optimize your design to achieve best possible results—this gives you a better design and saves money.

The PCI case study shown in Figure 3 is a good example. This Spartan-XL PCI solution was able to effectively cut the total product cost in half and also allow room to accommodate the extra logic that you may want to add to the backend PCI interface, such as a DMA controller, SDRAM controller, or FIFO.

#### Accommodating Specification Changes

ASSP vendors are motivated to quickly create solutions for emerging markets because of the high profit

- Spartan FPGAs migrate to higher densities to handle system features

- -Maintaining low cost

- ASSPs attempt to offer flexibility

- Differentiation need due to market pressures

Available ASSPs require programmable logic

- -Changing system standards

- ASSPs have large role in consumer, networking & data-processing

- –Where Spartan FPGAs are successful

- PCI is the first successful ASSP competition

System Features

Figure 2 - Spartan-II family penetrates ASSP markets.

margins they stand to gain. However, the standards change constantly in these markets, often making ASSPs a risky choice. These conditions create many opportunities for the Spartan-II family, because with a Spartan device, you can upgrade your design to accommodate evolving specifications even after your systems are deployed in the field.

#### **Testing and Verification**

Another problem users encounter with stand-alone ASSPs is that the devices do not always behave as expected. Identifying problems is a lot easier with pro-

Figure 3 - Xilinx PCI solution vs. stand-alone ASSP.

grammable ASSPs, such as the Spartan-II FPGAs, because they are built on the fabric of a proven FPGA technology and the silicon has been pre-verified and guaranteed to perform. Because a programmable ASSP is inherently re-programmable, fixing any problem is simple. This is a tremendous value-added feature that a stand-alone ASSP cannot offer.

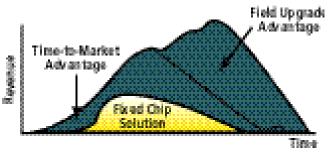

#### Xilinx Online for Field Upgradability

The Xilinx Online capability allows you to add new hardware features and fix bugs, over a network, without sending a technician to the field; this can add up to considerable maintenance and support savings over the entire life of the system. The value of field upgradability is illustrated in Figure 4.

#### Problems in Creating a Stand-alone ASSP

Vendors who create stand-alone ASSP devices must over-design their products to meet the requirements of a wide range of customers. A list of the various hurdles that an ASSP vendor faces today are:

Figure 4 - Field upgradability extends the value of programmable ASSPs.

- **Choosing the Right ASSP** The ASSP vendor must choose the right market segment.

- Product Customization ASSP vendors face the challenge of creating one solution that must successfully meet the demands of a wide range of customers.

- Development Cost and Amortization Standalone ASSPs have high NRE and engineering costs. These costs are increasing with process technology migration.

The Spartan-II family is unaffected by these hurdles and offers a cost-effective programmable ASSP solution.

#### Spartan-II ASSP Replacement Value

The Spartan-II family replaces and or competes against three classes of ASSPs, broadly classified as:

- Feature-Replacement ASSPs

- Logic-Replacement ASSPs

- Value-Added ASSPs

#### Feature-replacement ASSPs

Examples of "Feature-replacement ASSPs" are shown in Table 1. All of these functions are available in a Spartan-II FPGA without using any of the PLD's logic resources. Plus, the price of some of the Spartan-II devices is about the same as that of the ASSP they replace.

| Feature Replacement ASSPs                                          | Price   |

|--------------------------------------------------------------------|---------|

| 32-bit SSTL-3 Transceivers with Tristate Outputs                   | \$ 4.00 |

| 32-bit to 64-bit HSTL-to-LVTTL Memory Address Latch                | \$ 6.00 |

| 32-bit LVTTL to GTL/GTL+ Transceivers with Live Insertion          | \$ 6.00 |

| High Speed CMOS Digital PLLs                                       | \$ 1.00 |

| High Speed Programmable Board Skew Clock Buffer                    | \$ 7.50 |

| 2K x 8 Dual-Port Static RAM                                        | \$ 2.00 |

| 64,256,512,1K,2K,4K x 18 Synchronous FIFOs                         | \$ 7.00 |

| Hot Swap Controller                                                | \$ 2.00 |

| Note:Pricing shown is approximate and for volumes of 100,000 units |         |

Table 1 - A list of potential feature replacement

ASSPs replaced by the Spartan-II Family.

#### Logic-replacement ASSPs

Logic-replacement ASSPs are those that can be replaced by using the logic resources of a Spartan-II chip in combination with various IP cores. Examples of potential logic-replacement ASSPs are shown in Table 2.

#### Value-added ASSPs

Value-Added ASSPs fall into either of two categories:

- ASSPs that take unique advantage of the Xilinx architecture, like the ATM IMA devices from Applied Telecom. The class of field-upgradable ASSPs and network processors also fall into this category.

- ASSPs that serve emerging markets and markets that do not exist today, such as a PCI-X Master/Target Controller.

The Spartan-II family services all three classifications of ASSPs very well. Examples of Value Added ASSPs are shown in Table 3.

#### Conclusion

The new Spartan-II FPGA family, due to its advanced features and low cost, is uniquely capable of replacing many standard ASSP devices. And though it may not

| eplacement ASSPs Price                              | • |

|-----------------------------------------------------|---|

| IHz PCI v2.2 Bus Master \$ 25.00                    | ) |

| IHz CompactPCI(r)                                   |   |

| Hot Swap Friendly PCI interface chip \$ 15.00       | ) |

| IHz Bus Target chip \$12.00                         | ) |

| IHz PCI Master/Slave Controller \$14.00             | ) |

| IHz PCI Target Controller \$ 12.00                  | ) |

| S-3C POS/ATM SONET Mapper \$ 120.00                 | ) |

| Controller for 64-bit MIPS                          |   |

| egrated SDRAM controller \$ 12.00                   | ) |

| CI System Controller for 64-bit MIPS CPUs \$40.00   | ) |

| Cache Controller for the R4600/R4700 \$ 15.00       | ) |

| Port 10/100 Fast Ethernet Switch Controller \$28.00 | ) |

| Microcontrollers are direct                         |   |

| e upgrades for the 8051 \$ 8.00                     | ) |

| el HDLC Controller \$ 60.0                          | 0 |

| nel HDLC Controller with 32-bit,                    |   |

| Controller \$ 120.0                                 | 0 |

| ng Point 16 x 16 Complex                            |   |

| nt Multiplier \$ 300.0                              | 0 |

| ble FIR Filter \$ 310.0                             | 0 |

| FFT Processor \$450.0                               | 0 |

| Digital Switch \$12.0                               | 0 |

| col Controller \$4.5                                | 0 |

| nel ATM AAL1 SAR \$ 90.0                            | 0 |

| A Transcoder \$4.0                                  | 0 |

| PCM Filter CODEC \$ 4.0                             | 0 |

| Reed-Solomon Decoder \$25.0                         | 0 |

| on Forward Error Correction \$20.0                  | 0 |

| Compression \$ 12.0                                 | 0 |

| ression \$ 22.0                                     | 0 |

| al Adapter with HDLC Controller \$10.0              | 0 |

| el Network Interface                                |   |

| or HDLC \$ 60.0                                     | 0 |

| et (100 Mbps) Media Access                          |   |

| (MAC) \$ 20.0                                       | 0 |

| et (100 Mbps) Media Access                          |   |

Table 2 - A List of potential logic-replacement ASSPs supported by the Spartan-II family.

| Value Added ASSPs                                      | Price        |

|--------------------------------------------------------|--------------|

| 64-bit,66-MHz PCI-X System Controller                  | NA           |

| Quad ATM IMA Chip                                      | \$ 30.00     |

| Octal ATM IMA Chip                                     | \$ 50.00     |

| ARC Processor                                          | NA           |

| Note:Pricing shown is approximate and for volumes of 1 | 00,000 units |

Table 3 - A list of potential value added ASSPs supported by the Spartan-II Family.

replace all ASSPs, the Spartan family is now being used in many new high-volume, low-cost applications that were once dominated by stand-alone ASSPs.

The Spartan-II Demon Flow Simple, Powerful, Efficient

A design flow that offers distinct advantages when com pared to an ASIC design methodology

by Craig N. Willert, Software Marketing Manager, Xilinx, cnw@xilinx.com

ith the rapid adoptation of deepsubmicron process technology in the design of FPGAs, Xilinx is now able to provide you with a cost-effective alternative to using an ASIC. But the cost of silicon is only one reason why the use of Spartan devices in high-volume applications is skyrocketing.

Spartan devices are designed using our robust suite of design tools. These tools have become rich in features as a result of the inclusion of a series of patented innovations. This article describes some of the key technologies that are included in the Xilinx development systems, including HDL optimized flows, timing driven layout, core (intellectual property) design and integration, and a comprehensive suite of verification tools.

Xilinx design methodology also offers some distinct advantages when compared to an ASIC design flow. These improvements in the art of logic design deliver benefits that reduce the cost of design development and accelerate time to market.

#### A Robust Suite of Design Tools

The development systems that Xilinx delivers today incorporate the collective innovations of over 15 years of programmable logic design expertise. These improvements to the programmable logic design process have resulted in the creation of a comprehensive, high quality suite of design tools. Xilinx development systems are packaged to deliver the best value for your dollar, enabling you to invest in just what you need to get the job done.

All Xilinx development systems include a comprehensive set of key technologies that enable the efficient design of powerful, high performance products. Other tools useful in the design of programmable logic are delivered as options or as part of the Foundation Series "packaged" solutions, including HDL design, simulation, synthesis, and optimization.

One of the benefits of programmable logic is the ability to program (and reprogram) the device at your desktop. In order to do so, you need a set of tools that take your design from concept to silicon. Processing your design includes design capture (including HDL synthesis and/or schematic entry), implementation, and verification.

#### **Capturing your Design**

The first step in the creation of any logic design is to capture the

intended functionality in electronic format. While Xilinx has a rich history in the support of schematic capture programs, over the last six years Xilinx has been

working with leading vendors in support of HDL design flows (synthesis and optimization). This investment is paying dividends to designers using Xilinx devices in terms of technology specific optimizations that enable the creation of high performance designs from VHDL or Verilog.

The Xilinx Foundation Series<sup>™</sup> software includes synthesis capabilities from industry leader Synopsys<sup>®</sup> (FPGA Express<sup>™</sup>). To ensure

the highest quality of results through the synthesis process, Xilinx works cooperatively with all synthesis partners to develop proprietary optimization technolo-

gy for Xilinx devices. This technology takes advantage of the extensive knowledge that the Xilinx R&D staff have of its silicon and implementation tools. These improvements are developed in a manner which allows them to be shared with third party synthesis vendors to ensure high quality results, through HDL design flows, regardless of your chosen synthesis provider. Xilinx also delivers the industry's best design reuse

methodology, enabling the seamless integration of intellectual property from either third parties (Alliance cores) or Xilinx (LogiCores). The Xilinx CORE Generator<sup>™</sup> enables the customization of the core's parameters at your desktop, creating the exact functionality that your design requires. The use of SmartIP<sup>™</sup> technology in the creation of cores ensures predictable, high-performance, scalable functions. One of the most popular cores is the Xilinx PCI LogiCore, currently offered as both 32-bit/ 33-MHz and 64-bit/66-MHz interfaces.

#### Implementation

Xilinx patented the timing-driven place and route of FPGAs in the early 90s. This technology allows you to specify timing requirements when creating your design, and automatically optimize your design with these requirements in mind. Advanced integration, between the synthesis tools and the Xilinx implementation tools, enable the passing of timing requirements from synthesis to place and route, and circuit delay information from place and route back to the synthesis algorithms.

This closed loop methodology not only saves time, by making sure that the place and route tools are working to create a design that meets all of your system needs, it also provides immediate feedback when timing requirements are unrealistic, given the current design description. In fact, the flexible verification methodology that Xilinx provides ensures that you are given feedback on the feasibility and quality of your design throughout the design flow. This Checkpoint Verification<sup>™</sup> process ensures that you are spending your time most efficiently. The process

|                                                        | Period                                                               | Pad to Setup                             | Clock to Pad |          |

|--------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|--------------|----------|

| К                                                      | 110 MHz HIGH 50 %                                                    | 4 ns                                     | 6 ns         |          |

|                                                        | 55 MHz HIGH 50 %                                                     | 8 ns                                     | 5ns          |          |

| к                                                      | 125 MHz HIGH 50 %                                                    | 5 ns                                     | 9 ns         |          |

| DEC "TS Clock 2 to Clock                               |                                                                      |                                          |              |          |

| PEC "TS_Clock_3_to_Clock_<br>T = IN 4 no BEFORE "MPU_I | DLK";                                                                | a la |              | 4        |

| T = IN 4 no BEFORE "MPU_I                              | IT = FHUM "Clock_3" TU "Clo<br>ILK":<br>arce Constraints (read-only) | J                                        |              | <u>i</u> |

Figure 1: Constraints Editor

continues only with design iterations that will converge on your overall system requirements, and identifies trouble spots in designs that will not.

| 🔓 fpga_express_1.twr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                           |                            |                       |                                                                                                                 |                       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| FPGA Timing Analysis Description     Trining Constraints         TS_Clock_1 = PERIOD TIMEGRI         TS_Clock_2 = PERIOD TIMEGRI         TS_Clock_3 = PERIOD TIMEGRI         TS_Clock_4 = PERIOD TIMEGRI | Data Sheet Report<br>Clock to Setup on de | mation clock RIC           | ακ                    |                                                                                                                 |                       |  |  |  |

| TS_Clock_2_to_Clock_1 - FRDM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock to Setup                            | on destina                 | ion clock             | RIC_CLK                                                                                                         |                       |  |  |  |

| - TS_Clock_3_to_Clock_1 = FRDM     - Constraint Compliance     Data Sheet Report     - Clock to Setup on destination cloc     - Clock to Setup on destination cloc     - Clock to Setup on destination cloc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Source Clock                              | Src/Dest<br>Rise/Rise      | Src/Dest<br>Fall/Rise |                                                                                                                 |                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                           | 16.062<br>13.376<br>12.525 |                       |                                                                                                                 |                       |  |  |  |

| Table of TimeGroups     Timing Summary     End of Benot Elle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Clock to Setup                            |                            |                       |                                                                                                                 |                       |  |  |  |

| - End of hepoti rive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Source Clock                              | Src/Dest<br>Rise/Rise      | Src/Dest<br>Fall/Rise | Src/Dest<br>Rise/Fall                                                                                           | Src/Dest<br>Fall/Fall |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NPU_CLK                                   | 7.633                      |                       |                                                                                                                 |                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Clock to Setup                            | on destina                 | ion clock             | REC_CLK                                                                                                         |                       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Source Clock                              | Src/Dest<br>Rise/Rise      | Src/Dest<br>Fall/Rise | Src/Dest<br>Rise/Fall                                                                                           | Src/Dest<br>Fall/Fall |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RXC CLK                                   | 7.678                      | 10000000000000        | 5 12 17 15 17 16 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 10 17 1 |                       |  |  |  |

Figure 2: Training Analyzer

Xilinx has also made great strides in simplifying the process of timing driven design. The Xilinx "Constraints Editor" (Figure 1) guides you in your selection of signals and nodes to which you will apply timing constraints within your design. The Signal and Node lists are based on the same names you provided during the creation of the schematic or HDL source.

This easy-to-use GUI provides an intuitive interface for using industry's most comprehensive timing specification language—TimeSpecs<sup>™</sup>. Once these timing requirements are specified and the design is implemented, the Xilinx Timing Analyzer (Figure 2) is used to analyze the performance of a design. This intuitive interface streamlines the process of evaluating your designs timing by enabling a hierarchical analysis of all of the design's timing paths through the use of (+) expand and (-) collapse functionality.

The key to many design flows is the ability to rapidly iterate between design capture, implementation, and simulation (or in-system test). Iterative design is one key advantage of using programmable logic in your system, and to best take advantage of this, fast compilation times are important. To this end, Xilinx has dramatically reduced the place and route compilation times for its Spartan-II and Virtex families. Where traditional FPGA design flows implement designs at approximately 10K gates per minute, Xilinx v2.1i tools compile designs at a rate of approximately 100K gates per minute. For Spartan-II devices this translates into place and route times as fast as 1 minute, with average run times less than 10 minutes.

#### Verification

The increased density and performance of programmable logic is resulting in its frequent use as the central component in equipment design. As such, the emphasis on verification of programmable logic designs is becoming paramount to a program's success. Xilinx Check Point Verification methodology provides all of the hooks necessary to verify the operation of your design within the FPGA and within the target system. Elements of the Xilinx checkpoint verification model include:

- Support for functional, gate, and timing simulation.

- LMG SmartModel<sup>™</sup> support for the Xilinx FPGA.

- Chip-level static timing analysis.

- STAMP<sup>™</sup> model generation for board-level static timing analysis.

- In-System debug with Probe<sup>™</sup>.

Through this comprehensive suite of verification tools and data files, Xilinx provides you with the ability to employ the verification methodology of your choice. Our close relationships with our Alliance EDA partners ensure success in the use of partner tools, while Xilinx also offers the Foundation Series solutions as a complete, ready to use package of EDA and place and route tools, automating both design compilation and verification.

#### Improving the Art of Logic Design

The Xilinx design methodology leverages the technological advantages of programmable logic, including the fact that all devices shipped by Xilinx are 100% functionally verified at the factory. This fact alone translates into weeks of savings in design time, as the processes of scan insertion and the re-verification of a design after scan insertion is not required.

Another key benefit in the Xilinx design flow is that the device is "fabricated" (programmed) by you, at your desktop, or in your manufacturing organization. Your retention of control of this process means that there is no Non-Recurring Engineering (NRE) cost associated with the creation of the device. This can dramatically reduce the emphasis frequently placed on running comprehensive (and time consuming) timing simulations after layout, and before device "fabricated".

For programmable logic, a relatively comprehensive verification regimen can consist of functional verification and static timing analysis if good synchronous design practices are followed. The streamlined Xilinx design flow reduces the necessity of timing simulation, which is frequently a time consuming process. If your environment calls for the verification of your chip design within the board (or system), Xilinx also generates the necessary timing information for use with board-level static timing analysis or simulation tools. The ability to program the Xilinx device at your desktop also means that you can quickly iterate your design in a "burn and learn" fashion, reducing the pressure to get it right the first time. Problems discovered during in-system verification can actually be remedied in the chosen logic device. This is particularly useful when industry specifications or marketing requirements haven't stabilized prior to the beginning of your project.

The combination of these factors means that the design methodology that you follow is streamlined when compared to the process required to design with an ASIC. The time saved in the design flow and system verification is frequently dramatic.

#### Conclusion

The advantages of creating your design with programmable logic include more efficient use of your time, faster time to market, and no NRE costs. Our experience has found these benefits frequently result in improved market success of our customers' products. In addition to these benefits, the development systems required to design a Spartan device into your product are configured and priced to comfortably fit within any budget. Visit The Silicon Expresso Cafe (the Xilinx on-line store) or contact your local Xilinx sales representative to learn more.

See page 63 for an overview of our software products.

# How To Create an MP3 Player Using Spartan-II FPGAS.

#### **Spartan-II FPGAs are used to implement complex MP3 system-level glue logic.**

by Jasbinder Bhoot, Manager, Strategic Applications, Xilinx, jasbinder.bhoot@xilinx.com

P3 is rapidly becoming the defacto standard for the delivery of high quality music on the Internet. This technology has been well received as evidenced by the over five million MP3 software plug ins that have been downloaded to date. This is a testament to the future potential of the MP3 technology considering the relatively limited marketing it has received to date.

MP3 is an abbreviation for MPEG 1 layer 3, which is a compressed digital audio format that keeps the file size small without losing the quali-

ty of the original audio. MP3 allows audio files to be compressed to approximately  $1/11^{\text{th}}$  of the original size. For example, a typical music CD consumes 650MB; using MP3 the same audio only takes 55MB! This has allowed music to be stored on the PCs hard drive, allowing users to effortlessly create and customize music play lists.

The compression achieved by MP3 makes it practical to construct a solid state portable audio player based upon FLASH memory as the storage medium. This article explores the development of a portable MP3 player using the Spartan-II FPGA family.

#### **Design Overview**

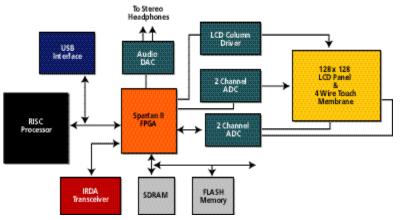

The MP3 player discussed in this application contains advanced user interface features, such as the ability to store contact information, record memos, and other functions typically found in Personal Digital Assistants (PDAs). The design uses an IDT RC32364 RISC processor to decode the MP3 data and implement the graphical user interface. The Xilinx Spartan-II FPGA is used to

implement the complex MP3 system-level glue logic required to interface and manage the memory and I/O devices.

Figure 1 shows a block diagram of the design. The key features are:

- 128 x 128 pixel graphical touch screen.

- USB interface for music downloads and network connectivity.

- IRDA-compliant infrared interface for exchanging data with other units.

- 32 MB of on board FLASH storage.

Figure 1: MP3 system block diagram.

• CompactFlash interface for storage expansion using CompactFlash cards or MicroDrive hard drives.

#### Use of ASSPs

The design uses Application Specific Standard Products (ASSPs) to implement much of the complex logic. Typically, these ASSPs are not designed to communicate with each other. The Xilinx Spartan-II FPGA is used to provide the complex glue logic for the interface between the ASSPs and the RC32364 RISC processor from IDT.

The Digital-to-Analog converter is the Crystal CS4343 from Cirrus Logic. The CS4343 provides the analog stereo headphone interface; a serial port is used to transfer digital audio data streams, while an I<sup>2</sup>C control port is used to configure the device features such as volume, muting, equalization, and power management.

The USB interface is the USBN9602 from National Semiconductor. This device supports full speed USB and includes an integrated USB transceiver. The system interface for the USBN9602 is an 8-bit microprocessor bus that can be configured to operate in a multiplexed or non-multiplexed mode. To reduce the number of pins, the multiplexed mode was used. The FLASH memory is the Samsung KM29U64000T 8M x 8 device based on NAND FLASH technology. This memory is very popular in MP3 players due to its high density and low cost per bit. However, this FLASH memory contains two characteristics that present significant design challenges:

- The KM29U64000T uses a highly multiplexed 8-bit-wide port for both address and data access.

- Error detection and correction is needed to ensure system integrity.

The second and most challenging issue, data integrity, is common with NAND-based FLASH technology. The FLASH memory contains a range of valid memory blocks (NVB). For the KM29U64000T the typical  $N_{VR}$  is 1020, the minimum is 1014, and the maximum is 1024. While the first block is guaranteed to be good, bad blocks can occur at any other location within the memory array. Invalid blocks are marked at the factory by storing a "0" value at location "0" in either the first or second block of the page. The design must keep a record of good blocks resulting in a non-contiguous memory map. A further issue is that the FLASH memory may experience additional block failures during the memories operational life.

#### **Glue Logic Architecture**

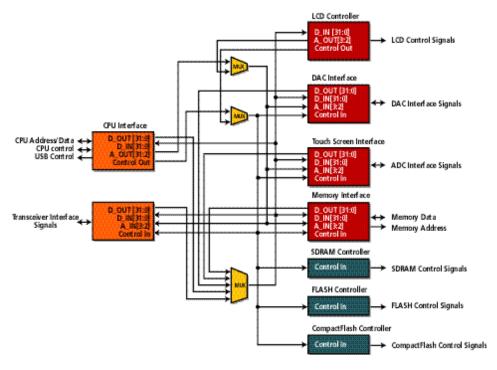

Figure 2 shows an overview of the architecture implemented in the Spartan-II FPGA.

The architecture consists of the following functional blocks:

- IP Bus Controller.

- CPU interface.

- LCD controller.

- Memory Interface.

- SDRAM controller.

Figure 2: Spartan-II block diagram.

- FLASH Controller.

- CompactFlash Controller.

- IRDA Controller.

- Audio DAC Interface.

- Touch Screen Interface.

A simple non-multiplexed, multi-master address data bus called the IP bus, interconnects the blocks. Having the FLASH, SDRAM, and the CompactFlash RAM share a common address and data bus allows a reduction in pin count.

**The IP Bus** has two masters, the CPU interface and the LCD controller. Multiplexers are used for gating data into the internal datapaths, eliminating the need for 3-state drivers.

**The CPU Interface** performs the CPU initialization, the protocol conversion (to and from the CPU bus, USB interface, and the IP bus), and the address de-multiplexing.

**The LCD Controller** is responsible for refreshing the screen with the image stored in the SDRAM. The LCD controller can obtain the data for screen refresh independent of the CPU activities.

**The Memory Interface** block implements the data path required to map the 8- and 16-bit memory devices to the 32-bit IP bus. Although the RC32364 is capable of obtaining instructions and data from devices with varying bus widths, using the Spartan-II to implement this function reduces the CPU bus cycles and hence, increases performance and reduces power consumption.

**The SDRAM controller** is based on the design developed by Xilinx in application note XAPP134: Virtex Synthesizable High Performance SDRAM Controller There are two changes made to this design:

- The host interface is adapted from a multiplexed address data bus to a non-multiplexed data bus.

- A 16-bit wide SDRAM memory configuration is needed in place of the 32-bit wide memory datapath.

**The FLASH Controller** copies the executable image from the FLASH memory to the SDRAM at boot time, to overcome the FLASH random access latency and maximize system performance. This method also allows the NAND FLASH error code correction to be implemented in software, resulting in an efficient use of the FLASH memory.

**The CompactFlash Controller** provides the interface to allow the MP3 music files to be stored in to the CompactFlash memory via the USB serial link. The control signals required to retrieve the MP3 music file for playback are also contained in this block.

**The IRDA Controller** is essentially a specialized, fixed function UART. Separate, 2-word receive and transmit FIFOs are used to reduce the interrupt overhead associated with data transmission. The IR transceiver can support a data rate of 115 Kb/s resulting in a CPU interrupt every 557 ms.

**The Audio DAC Interface** provides the dedicated hardware needed to implement the transfer protocol for delivering an uninterrupted audio stream. This hardware consists of two, 4-word FIFOs, one for each audio channel and a state machine to manage the FIFOs and sequence the interface signals. The audio DAC interface also contains a 2-bit I/O port that uses software to implement the I<sup>2</sup>C protocol used for accessing the control and status registers in the DAC.

**The Touch Screen Interface** is an I/O port that allows the processor to read the data returned by the two-channel analog-to-digital converter. This allows the system software to determine the X and Y touch screen coordinates.

#### **Spartan Device Selection**

Spartan-II devices are available in a wide range of densities and packages. The following criteria were used to select the device:

- I/O Pins. The design requires a total of 137 I/O pins.

- Voltage. The design operates at 3.3V.

- Density. The estimated size of the design is 83,000 gates.

- Performance. The highest clock speed used in this application is 64 MHz; this is used to clock the SDRAM controller. The remaining logic operates at sub multiples of this clock.

- Packaging. The size constraints imposed on most modern designs dictates a high-density surface mount package.

Based on these criteria the device selected for this design is the XC2S100. This device offers 100K gate density, 3.3V operation, 176 user I/Os, and is packaged in a FG256 BGA package. The cost of this device, in 100K quantities, is \$12.95.

#### Conclusion

This design illustrates how Spartan-II FPGAs can be used to provide time-to-market advantages in high volume consumer applications. In this application, the Spartan-II FPGA is used as a cost-effective device to maximize the CPU performance and reduce system power consumption by providing some dedicated functions as well as the glue logic required to interface to the ASSPs. Using a Spartan-II FPGA also allows field upgrade flexibility, in a market where standards and protocols are still evolving.

Inverse Multiplexing for

A Programmable ASSP Solution for transmitting high-bandwidth data over multiple T1 or E1 lines.

by James D. Beatty, President, Applied Telecom, jim@apptel.com, and Krishna Rangasayee, Manager, Strategic Applications, Xilinx, krishna@xilinx.com

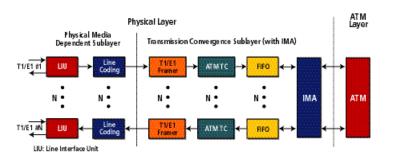

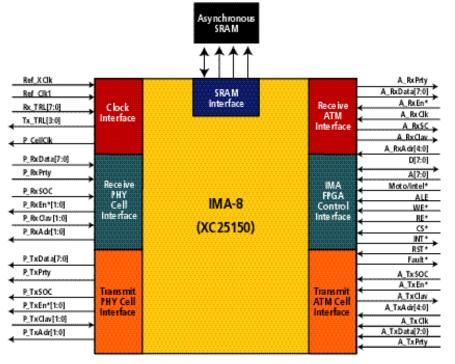

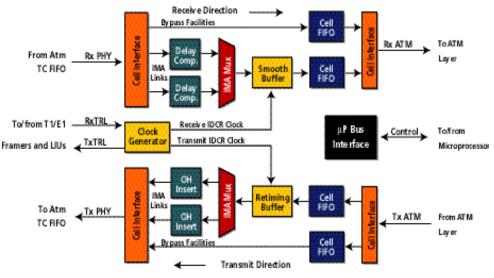

he Spartan-II Family, combined with an extensive soft intellectual property (IP) portfolio is the first programmable logic solution to effectively penetrate the ASSP marketplace. The ATM IMA-8 core from Applied Telecom, ported to the Spartan XC2S150 device, is a good example, highlighting the concept of a programmable ASSP.

Applied Telecom is the newest member of the Xilinx AllianceCORE program and brings a wealth of expertise in ATM, SONET, telecommunications, and networking applications. The IMA-8 core, developed, sold, and supported by Applied Telecom, targets network access systems such as adapters, multiplexers, and switches. Several leading manufacturers, including Alcatel, Ericsson, Nokia, and Nortel, are already using Applied Telecom's Xilinx-based IMA technology in production systems.

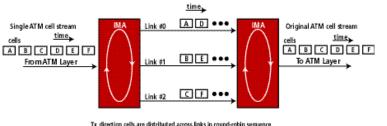

#### What is IMA?

IMA stands for "Inverse Multiplexing for Asynchronous Transfer Mode" (ATM) and it allows the transmission of a high-bandwidth stream of ATM cells over multiple T1 (1.544 Mbps) or E1 (2.048 Mbps) facilities (or circuits). IMA is applicable to both public and private networks and allows end users to enjoy the many benefits of ATM, such as Quality of Service (QoS) provisioning, scalability, and the ability to easily mix data, voice, and video. IMA circumvents the high cost and unavailability of broadband transmission facilities such as T3, E3, and SONET/SDH by using only as many lower cost, lower bandwidth facilities as necessary. With the advent of Digital Subscriber Line (DSL) technology, the case for IMA is even greater.

#### **IMA Applications**