<sup>®</sup> The Programmable Logic Company<sup>SM</sup>

#### Inside This Issue:

#### HARDWARE

| Editorial 2                  |

|------------------------------|

| FPGAs                        |

| New XC4000X Series 3         |

| 3.3V SpartanXL 4-5           |

| FPGAs vs. ASICs              |

| An Effective Alternative 6-7 |

| Rapidly Changing ASIC        |

| Conversion Market 8-9        |

| Replacing ASICs 10-11        |

| CPLDs                        |

| XC9500XL 3.3V                |

| FastFLASH 12                 |

| Chip Scale Packaging13       |

| "ARM" Yourself 14-15         |

| Max Headroom15               |

|                              |

#### SOFTWARE

| Silicon Xpresso 16-17         |

|-------------------------------|

| Alliance Series 1.5           |

| Guaranteeing Designs          |

| Work in All Conditions. 18-19 |

| XC9500 Design Speed 19        |

| Unleash Creativity 20         |

| Column: HDL Advisor 21-23     |

#### **DESIGN HINTS**

| System Emulation 24-25         |

|--------------------------------|

| Reducing CPLD Power            |

| Consumption 26-27              |

| Synplify: Inferring RAM 28-29  |

| MINC Synario: Upgraded         |

| PLSynthesizer                  |

| Viewlogic IntelliFlow:         |

| Design Process 32-33           |

| Q&A From Our Hotline 34-35     |

| Your Best Debug Tools          |

|                                |

| Upcoming Training              |

| Product Selection Matrix 38-39 |

# **PRODUCT INFORMATION**

# **Three New 3.3V Families**

### XC4000X

Industry-leading system performance with double the capacity... SpartanXL Now with faster

Now with faster systems speeds at the same low Spartan price...

### **XC9500XL**

New 3.3V CPLD family offers higher performance and new features...

See page 3

See pages 4-5

See page 12

# **DEVELOPMENT SYSTEMS**

# Alliance Series 1.5 Software

Three articles explore features of the new Alliance software release, from design stability to XC9500 design speed to design creativity...

See pages 18-20

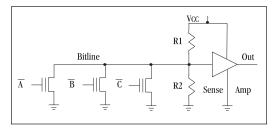

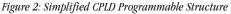

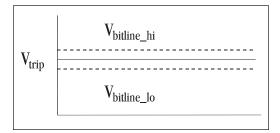

### **DESIGN TIPS & HINTS** Reducing CPLD Power Consumption

Minimizing CPLD power consumption is easy...

See pages 26-27

#### **EDITORIAL**

# Xilinx – The Next Generation

Our mission is to help you explore new

worlds, and new applications; to boldly go where

no programmable logic device has gone before.

And, our next generation of stellar devices are

by Carlis Collins, Managing Editor of Corporate Communications, editor@xilinx.com

here now; no "science fiction." We recently announced more than 20 new devices with densities ranging from 800 to 500,000 system gates, all fully supported by our highly acclaimed Alliance Series 1.5 and Foundation Series 1.5 software. A whole new world of possibility is now available, because these devices not only represent the cutting edge in performance and density, they also set new standards for low cost, high

This unprecedented offering brings you the broadest choice of 3.3V and 2.5V devices available anywhere, in four new families:

reliability, and ease of use.

- The XC9500XL family consists of four 3.3V devices with logic densities ranging from 36 to 288 macrocells (800 to 6,400 gates). These devices are manufactured using advanced 0.35µ Flash technology for the industry's highest reliability in programming and data retention, as well as the lowest device cost and the smallest die size. These are the industry's highest performance CPLDs with pin-to-pin speeds of 4 nanoseconds and system clock frequencies of 200MHz, available in the most popular surface mount technology, including chip-scale packaging. All of our XC9500 products offer the industry's best pin locking and in-system programming capability as well as enhanced JTAG Boundary Scan support.

- The XC4000XLA FPGA family consists of eight 3.3V FPGAs ranging in density from 26,000 to 80,000 system gates. The XC4000XLA devices are manufactured with an advanced 0.25µ process that boosts performance by 30 percent over the

current XC4000XL product line, at half the cost. The XC4000XLA family is the industry's lowest power, highest performance, full line of 3.3V FPGA products.

- The XC4000XV family, first unveiled last October, now consists of five 2.5V FPGAs, with densities from 220,000 to 500,000 system gates, including the newly announced XC40110XV. This second generation of 0.25µ devices offers the industry's highest performance, and includes the largest FPGA devices available today.

- The SpartanXL family consists of five 3.3V FPGAs. These new, very low cost devices follow the introduction earlier this year of the 5V Spartan line that features on-chip RAM and broad support for cores. The new SpartanXL products are available in densities ranging from 5,000 to 40,000 system gates.

All of these devices are supported by the Xilinx Foundation Series 1.5 and Alliance Series 1.5 software, which includes the new Xilinx AKAspeed<sup>™</sup> technology that delivers fast compile times and high clock speeds. These tools also support ASIC-like design features such as the reporting of minimum timing delays, prorated for both voltage and temperature. A wide variety of cores are also available, all managed by the Xilinx CORE Generator.

These new products are driving programmable logic into new applications that include digital cameras, digital television, set-top boxes, arcade games, PCMCIA modem cards, GPS driver information systems, and portable phones – applications that previously did not benefit from the many advantages of programmable logic.

And, even after all this, our million-gate Virtex family arrives next quarter, with system-level features that bring out-of-this-world possibilities — light years ahead of anything you've seen before. It's not science fiction, but it does come from the future. ₣

#### XCell

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3450

Phone:

408-559-7778

FAX:

408-879-4780

©1998 Xilinx Inc.

All rights reserved.

XCell is published quarterly for customers of Xilinx, Inc. XILINX and the Xilinx logo are registered trademarks of Xilinx, Inc. Spartan, Virtex, HardWire, Alliance Series, Foundation Series, AllianceCORE, LogiCORE, WebLINX, SelectRAM, SelectRAM+, Dual Block, FastFLASH, and all XC-prefix products are trademarks, and "The Programmable Logic Company" is a service mark of Xilinx, Inc. Other brand or product names are trademarks or registered trademarks of their respective owners.

The articles, information, and other materials included in this issue are provided solely for the convenience of our readers. Xilinx makes no warranties, express, implied, statutory, or otherwise, and accepts no lability with respect to any such articles, information, or other materials or their use, and any use thereof is solely at the risk of the user. Any person or entity using such information in any way releases and waives any losi, damage, orexpense caused thereby.

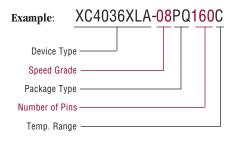

# **New XC4000X Series FPGAS** Doubling Gate Capacities and Delivering Industry-Leading Speed

Optimized for 3.3V designs, the Xilinx XC4000X Series FPGAs double the capacity of FPGAs while delivering industry-leading system performance. Consisting of the new XC4000XLA and XC4000XV families, the XC4000X Series is an enhanced version of the industry standard XC4000 architecture. Consisting of 12 devices with capacities ranging from 30,000 to 500,000 system gates, these FPGAs feature the patented SelectRAM<sup>™</sup> memory; offering a completely flexible logic distribution, as well as single-port or dual-port memory. Designed with advanced CMOS processes, the XC4000X Series delivers industry-leading performance while significantly reducing power consumption.

#### **Unprecedented Performance**

The XC4000X Series uses unique architectural enhancements and aggressive process technology to attain unprecedented speed at full capacity. Additional routing resources and highly buffered clock networks ensure that you get the highest array performance possible. New three-state I/O registers and FastCLK I/O buffers significantly increase system performance.

#### **Double the Capacity**

The XC4000XV Family, offering up to 500,000 system gates, is twice the capacity of competing products. Plus, it offers a high level of performance, with efficient clock buffering and abun-

dant, fast, segmented routing that ensures minimal interconnect delay.

#### **Power Consumption Less Than Half**

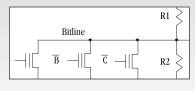

The XC4000XLA consumes half the power of the equivalent XC4000XL device, and the XC4000XV only consumes a third of the power, as shown in **Figure 1**. These savings are derived from efficient design layout, smaller process geometries, and lower operating voltages.

#### Conclusion

The new XC4000X FPGA family represents the next generation of programmable logic technology, with the fastest, highest capacity devices available. Combined with our highly acclaimed Alliance Series 1.5 and Foundation Series 1.5 software, this family is the perfect choice for your next design. **£**

- by Bruce Weyer, Sr. Director, Marketing, weyer@xilinx.com

- Figure 1: Relative Power

- *Consumption*

Table 1: The XC4000X Family

|              |                |                |                         |                         |                         |                         |                         |                         |           | -              |           |                |

|--------------|----------------|----------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-----------|----------------|-----------|----------------|

|              | XC4013XLA      | XC4020XLA      | XC4028XLA               | XC4036XLA               | XC4044XLA               | XC4052XLA               | XC4062XLA               | XC4085XLA               | XC40110XV | XC40150XV      | XC40200XV | XC40250XV      |

| Logic Cells  | 1,368          | 1,862          | 2,432                   | 3,078                   | 3,800                   | 4,598                   | 5,472                   | 7,448                   | 10,982    | 12,312         | 16,758    | 20,102         |

| System Gates | 10-30K         | 13-40K         | 18-50K                  | 22-65K                  | 27-80K                  | 33-100K                 | 40-130K                 | 55-180K                 | 75-200K   | 100-300K       | 130-400K  | 180-500K       |

| Max RAM Bits | 18,432         | 25,088         | 32,768                  | 41,472                  | 51,200                  | 61,952                  | 73,728                  | 100,352                 | 131,072   | 165,888        | 225,792   | 270,848        |

| User I/Os    | 192            | 224            | 256                     | 288                     | 320                     | 352                     | 384                     | 448                     | 448       | 448            | 448       | 448            |

| Packages     | PQ160          | PQ160          | HQ160                   | HQ160                   | HQ160                   | HQ160                   | HQ160                   | HQ160                   |           |                |           |                |

|              | PQ208<br>PQ240 | PQ208<br>PQ240 | HQ208<br>HQ240<br>HQ304 | HQ208<br>HQ240<br>HQ304 | HQ208<br>HQ240<br>HQ304 | HQ208<br>HQ240<br>HQ304 | HQ208<br>HQ240<br>HQ304 | HQ208<br>HQ240<br>HQ304 | HQ240     | HQ240          |           |                |

|              | BG256          | BG256          | BG256<br>BG352          | BG352                   | BG352                   | BG352                   | BG352                   | BG352                   | BG352     | BG352          |           |                |

|              |                |                | 2.0002                  | BG432                   | BG432                   | BG432                   | BG432                   | BG432                   | BG432     | BG432          | BG432     | BG432          |

|              |                |                |                         |                         |                         | BG560                   | BG560                   | BG560                   | BG560     | BG560<br>PG559 | BG560     | BG560<br>PG559 |

# The 3.3V SpartanXL<sup>™</sup> FPGA Series

### Invades New Territory with High Speed and Low Cost

by Marc Baker, Applications Engineer, marc.baker@xilinx.com

> \*84 PLCC, 100K units, -3 speed

FPGA

I he number of different applications supported by the Spartan<sup>TM</sup> Series FPGAs has been dramatically increased with the shipment of the new 3.3V SpartanXL family. For the first time, an FPGA family can provide system speeds beyond 100MHz at prices below \$3.00\*, while supporting all the features needed for complete logic integration. The unique combination of blazing speed and low price eliminates the need for dedicated chips or gate arrays in high-volume applications such as digital imaging and PC peripherals.

Using an advanced 0.35µ process, to achieve smaller die size and higher performance, the SpartanXL family builds on the success of the Spartan Series, the industry's fastest-growing FPGA family. This unique five-layer-metal process, developed by Xilinx, provides the most effective base for a 3.3V logic solution. The five devices in the SpartanXL family offer the same 5,000 to 40,000 gate density range as the 5V Spartan family, introduced in January 1998. Furthermore, they use the same low-cost packages, allowing easy migration between voltage levels.

The SpartanXL architecture features the same synchronous single-port and dual-port SelectRAM

memory capabilities offered in the 5V family. The Spartan series is the only ASIC replacement FPGA that offers this key feature. On-chip RAM is useful for scratch-pad memories, shift registers, and FIFOs such as those used in a PCI interface.

The SpartanXL family (and the 5V Spartan family) are the industry's most cost-effective FPGAs, made possible by total cost management, which includes reduction of the assembly and test costs by using low-cost packaging and new, efficient test methodologies.

#### **New Features**

The SpartanXL architecture adds several key new features to the original 5V Spartan family. The dedicated carry logic has improved performance, providing 16-bit addition in only 8 ns. Clock routing has been simplified with eight identical, global, low-skew buffers to choose from. The new Express Mode decreases configuration time by a factor of eight. Configuration through the dedicated IEEE-compatible Boundary Scan logic has been simplified, and is now supported by the JTAGProgrammer software and cable. Synthesis is simplified as well, by offering level-sensitive latches throughout the device.

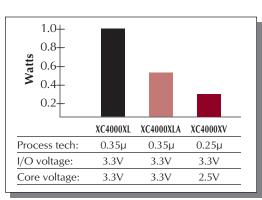

The SpartanXL architecture features the industry's most versatile I/O cell, with features that include:

- 5V input tolerance even before power is applied

- 3.3V or 5V PCI compatibility

- Programmable 12 mA or 24 mA output drive

- Input fast capture latch for shorter setup times

- Output look-up table for the fastest pin-to-pin speeds

#### **High Speed at Low Power**

The SpartanXL series provides system-level speed beyond 100MHz. I/O toggle frequency achieves 100MHz, while functions such as stan-

Figure 1: SpartanXL Family Voltage Compatibility dard 16-bit binary counters run at 120MHz internally. The SpartanXL speed grades were dramatically improved since the initial software release, and the new speed files are available on WebLINX (www.xilinx.com) in the File Download area.

The 3.3V supply reduces power consumption significantly. Xilinx FPGAs benefit from efficient segmented routing that minimizes the amount of power consumed by each net. For the latest power and speed information, see the SpartanXL Series datasheet on WebLINX.

#### Software Support and Core Solutions

The SpartanXL family is fully supported by the Xilinx Alliance Series 1.5 and Foundation Series 1.5 development software. New support includes libraries specifically for the Spartan and SpartanXL families, simplifying design with these products. Dozens of Xilinx Alliance partners provide design entry and verification tools.

Pre-defined system functions are available as core solutions for the SpartanXL family. Xilinx offers PCI and DSP LogiCORE solutions via the CORE Generator software, included in the 1.5 version of the Xilinx development system. Several third-party vendors provide AllianceCORE solutions, which are pre-verified for the SpartanXL family. Implementing these common functions in a SpartanXL FPGA costs less than an ASIC, due to

#### Xilinx Spartan Series

| 5 Volt (0.5/0.35µ)<br>3 Volt (0.35/0.25µ) | XCS05<br>XCS05XL | XCS10<br>XCS10XL | XCS20<br>XCS20XL | XCS30<br>XCS30XL | XCS40<br>XCS40XL |

|-------------------------------------------|------------------|------------------|------------------|------------------|------------------|

| System Gates                              | 2K-5K            | 3K-10K           | 7K-20K           | 10K-30K          | 13K-40K          |

| Logic Cells                               | 238              | 466              | 950              | 1368             | 1862             |

| Max Logic Gates                           | 3,000            | 5,000            | 10,000           | 13,000           | 20,000           |

| Flip-Flops                                | 360              | 616              | 1120             | 1536             | 2016             |

| Max RAM bits                              | 3,200            | 6,272            | 12,800           | 18,432           | 25,088           |

| Max I/O                                   | 77               | 112              | 160              | 192              | 205              |

| Performance                               | >80MHz           | >80MHz           | >80MHz           | >80MHz           | >80MHz           |

#### No Compromises: Performance, RAM, Cores, and Low Price

the dramatically lower prices offered by the SpartanXL family.

#### Conclusion

The SpartanXL series complements the XC4000XLA family, which applies the same process technology to our higher density devices. For applications where less logic is needed, the XC9500XL family provides the fastest CPLDs in the industry. Together, these families provide the broadest choice of 3.3V devices. Rapid application of aggressive new process technologies allows these PLDs to penetrate new applications that were once the stronghold of ASICs, such as arcade games, graphics cards, and automotive cabin controls. **€**:

Figure 2: Availability Chart

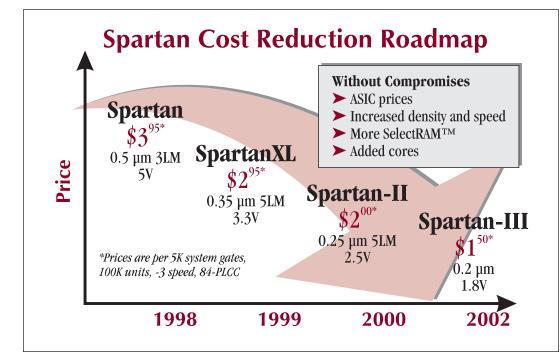

Figure 3: Spartan Cost Reduction Roadmap

#### **FPGAs vs. ASICs**

# FPGAs Can Be an Effective Sharp, sharp@xilinx.com

In this fast-paced electronics industry, gate array engineers are under increasing pressure to produce new ASIC designs ever more quickly. As traditional masked gate arrays decline in usage, a new generation of programmable devices have become a viable alternative for the gate array user.

The new "ASIC Replacement" FPGAs have continued to narrow the price gap with mask ASICs while maintaining the user advantages of quick production and in-system reprogrammability. These FPGAs have begun to replace mask gate arrays in traditional ASIC volume applications, from networking encryption engines to PC adapters to digital camcorders.

In this article we examine recent advances in programmable technology and the advantages of the new ASIC Replacement FPGA.

For a list of Spartan and SpartanXL devices, see the *Xilinx Spartan Series* Table on page 5 in the "3.3V SpartanXL FPGA Series" article.

#### **ASIC Replacement FPGAs**

The Xilinx Spartan Series FPGAs were created to provide a cost effective and flexible replacement for low-end (<40K system gates) ASICs in volume production. These new FPGAs offer the ASIC designer the advantages of in-system reprogrammability at prices that are competitive with masked gate arrays. To become an effective ASIC solution, the Spartan Series had to substantially reduce die-size over the previous generation FPGAs while measurably improving

Figure 1. Spartan FPGAs match die size with mask gate arrays.

| Spartan XCS20XL  | Gate Array        |

|------------------|-------------------|

| 20K system gates | 100K system gates |

| 0.35µ            | 0.35µ             |

| 160 I/O          | 160 I/O           |

|                  |                   |

gate-area density and system performance.

Although FPGAs have historically lagged the ASIC industry by one or two fabprocess generations, current Spartan Series FPGAs were able to surpass most of today's gate arrays by employing a leading-edge, multi-feature size  $0.35\mu/0.25\mu$  technology. In the past, a larger die size was necessary to provide sufficient logic density for typical FPGA designs but caused FPGAs to be priced out of range for higher volume production.

Because the high-end Xilinx FPGAs (such as the Virtex Series) contain more transistors (75 million) than the Pentium II microprocessor, Xilinx wafer foundry partners have chosen these complex devices to debug new fab processes, replacing DRAMs as the technology driver. Becoming a fab process driver means that Xilinx FPGAs will remain on the leading edge of process technology for years to come.

#### **FPGAs Close the Price Gap**

The SpartanXL family (3V version) is currently the lowest cost FPGA family in the industry. The entire Spartan/SpartanXL Series incorporates ASIC-like features such as dual-port synchronous on-chip memory and supports frequencies up to 80+MHz.

The key to the Spartan family's low production pricing is an "I/O pad-limited" die size. "I/O padlimited" means that a die is reduced to the limits imposed by the I/O bonding pads. Pad-limited enables the Spartan Series FPGA die to be cost equivalent to most mask gate arrays of up to 205 I/O pins. With Spartan or SpartanXL prices starting at \$2.95 (84 PLCC, 100K units, -3 speed), the series is able to realistically compete with mask gate arrays for production based upon the same I/O count.

For example, the 160 I/O SpartanXL S20XL, shown in **Figure 1**, has a comparable die size and cost as the 160 I/O 0.35µm gate array, even though the gate array contains a denser architecture (and higher gate count). By sizing the die at the pad-limits, the FPGA cost can be equivalent to most gate arrays.

#### Lower Manufacturing Cost

Because Spartan Series FPGAs were designed for low power consumption, inexpensive plastic packages can be used to help keep manufacturing costs low. Other production savings accrue from a streamlined test methodology, built-in self-test features, and shorter test times. The combination of lower manufacturing overhead and small diesize eliminate cost barriers and enables Spartan Series FPGAs to be effective for both prototyping and for mass production.

#### FPGA Production Parts "Off-the-shelf!"

It is paramount to attain the best development time-to-production because today's product life cycles are often brief (9-18 months). Programmable logic is uniquely able to support both rapid prototyping and a quick ramp to full manufacturing. For many Xilinx customers the immediate availability of production is the most important benefit of programmable logic. After development, early production shipments are critical to market acceptance.

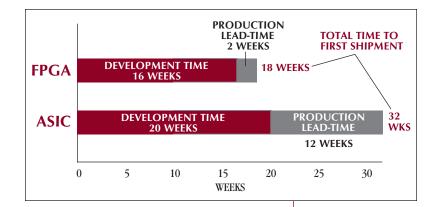

When FPGAs are used in production, marketing channels are quickly stocked for initial sales and new product revenue flow begins. Because the standard ASIC has an 8-16 week production leadtime, a 3-4 month sales delay would substantially decrease revenues and profits throughout the life of the product (see **Figure 2**). By using FPGAs in production; however, your market penetration is immediate.

The well-known McKinsey study found that a six-month delay costs one third of the profits over the lifetime of the product.

#### **FPGA-to-ASIC Conversions**

FPGA-to-ASIC conversions have been a popular approach to reduce unit production costs. However, it has become more difficult to cost justify these conversions in lower-density designs because of the new low price FPGAs along with the flexibility that FPGAs offer in today's quickly changing markets.

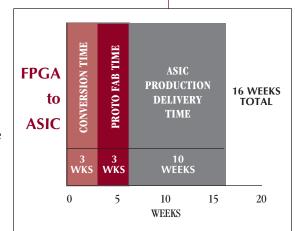

Conversion to a lower density ASIC means losing FPGA advantages of "off-the-shelf" production deliveries and simple field software updates, while incurring re-design risks (see **Figure 3**). Conversion costs such as NRE, silicon re-spins, test vectors, new device characterization, and internal engineering costs, usually outweigh the nominal unit cost difference between FPGAs and ASICs.

In higher density designs, using an ASIC that is crafted to exactly mirror the FPGA features can minimize the costs and the associated re-design risks. For example, the Xilinx HardWire™ family

offers exact ASIC replacements for our higherdensity FPGAs, making conversion very quick, easy, and inexpensive.

However, for most other manufacturers' FPGAs, the conversion time-to-production is frequently under-estimated. The time from start to full production typically exceeds four months. The common milestones are:

- Conversion/internal engineering time three weeks

- Prototype fab time three weeks

- Full production deliveries 10 weeks

In total, 16 weeks are spent before production is fully ramped and the transition to the ASIC is complete. When a short product life or a mid-life product enhancement is likely, conversions become worthless.

#### Conclusion

There are compelling advantages to use programmable logic for both development and production. Today's FPGAs support standard Verilog and VHDL design flows that help ASIC designers transition to programmable logic. Advanced process technology has leveled the playing field, and allowed FPGAs to be very price competitive with low-density gate arrays. When ASIC users now consider pricing, time-to-production, and reprogrammability, the preferred ASIC technology becomes the new Spartan Series FPGAs. **£**  Figure 2: FPGA beats ASIC by more than 3 months to first customer shipment!

Figure 3: FPGA to ASIC conversion to production takes at least four months.

#### **FPGAs vs. ASICs**

by Shelly Davis, HardWire Marketing Manager, sdavis@xilinx.com

# The Rapidly Changing ASIC Conversion Market

As programmable logic devices continue to grow in density, designers are increasingly using FPGAs where they previously used ASICs. The advantages of off-the-shelf availability and rapid prototyping make FPGAs a very attractive solution. However, you must answer a key question: will you use FPGAs for both development *and* production volumes, or will you convert the design to some form of ASIC, such as a gate array or standard cell, for cost reduction?

#### **Third-Party ASIC Conversion Problems**

The FPGA-to-ASIC conversion market has been dynamic over the past few years. Several companies have entered the market, only to find themselves in financial trouble. Microchip Technologies exited after 15 months of business and the D.I.I. group who purchased Orbit Semiconductor took a \$60M

loss last quarter due to the difficulties they continue to experience. It is not due to a lack of conversion business in the marketplace that problems are caused for the small ASIC vendor. The problem is caused instead by the difficulty of accurately converting today's complex PLDs. There are several factors contributing to this.

Most third party FPGA-to-ASIC conversion companies use gate array technology for the translation. The features of today's FPGAs, such as PCI compliance and the ability to implement 50K bits of RAM or more, exceeds the capability of most gate array vendors. In addition, the growing requirement for fast, on-chip RAM is perfectly suited to SRAM-based FPGAs, or fully diffused standard cell embedded RAM, but not for gate array processes. Even the most efficient gate array process

will require 5 to 6 gates per RAM bit to convert FPGA RAM to ASIC RAM. For a design with 15K bits of RAM, this can translate into a minimum of 90K gates on a gate array. Therefore, a design that was slated for cost reduction from an FPGA to a smaller gate array may achieve only a small cost reduction because of the increase in die area required for the RAM.

Gate array price erosion has been fierce in the past few years. While this price reduction has benefited companies using gate arrays, some of the smaller gate array vendors are in poor financial condition, making it difficult for those companies to sustain innovation. This lack of new product development is now causing them to have difficulty converting many of the more complex FPGA designs.

Leaving an FPGA conversion to a third party gate array company is complicated, not well suited technologically, and doesn't offer much cost reduction because a 100K-gate FPGA often becomes a 500K gate array under these circumstances.

#### **Pad Limitation**

True pad limitation is achieved when there is such an abundance of gates available in a device, that the size of the die is determined solely by the number of required pads. The standard cell providers, with their dense core offerings, have been pad limited for some time. At process geometries below 0.5µ, many architectures, including FPGAs and gate arrays, become pad limited. For an FPGAto-ASIC conversion company, who depends on achieving cost reduction through a die area shrink, pad limitation reduces the cost benefit of the gate array. In many cases, because the customer needs all the pads provided on the FPGA, the gate array device will be of equal size, in order to include the same number of pads. Size reduction due to translating programmable SRAM gates to much smaller metal vias is nullified.

#### **Diverging Architectures**

While the features and performance of FPGAs continually increase to include many ASIC-like features, the actual implementation and design methodology are becoming dissimilar; architectur-

"Will you use FPGAs for both development and production volumes, or will you convert the design to some form of ASIC, such as a gate array or standard cell, for cost reduction?" ally, FPGA technology and ASIC technology are diverging. The ability of one architecture to be "converted" to the other will require more than just re-targeting to a specific ASIC vendor's libraries. Gate array processes without embedded RAM structures that are specific to the original FPGA will quickly exceed gate count capability. In addition, indepth knowledge of the FPGA's functionality and detailed specifications of industry standards like PCI will be basic requirements. Furthermore, the ability to provide accurate timing of I/Os and critical system performance will be essential to convert these newer, more complex designs.

FPGA designers who depend on ASIC cost reductions will find their options changing over the next 18 months. Many smaller ASIC vendors will de-emphasize FPGA conversions because they lack the capability to convert them in a cost-efficient and technically effective manner. In the meantime, FPGA price per gate continues to decline to a point that, for 40K system gates and below, FPGAs can be considered for production volume in "formerly ASIC" applications. Companies that continue to provide FPGA-to-ASIC conversions will need to offer increasingly FPGA-specific solutions, because a generic gate array process will not serve the requirements of all PLD features.

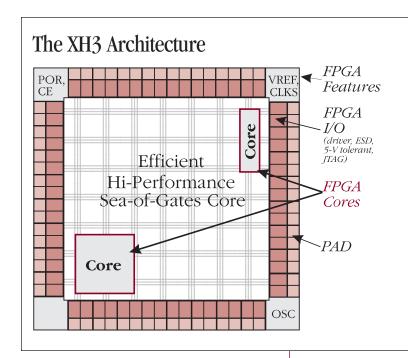

Xilinx is one example of a company that provides a specialized solution for FPGA conversions. The Xilinx HardWire Business Unit continues to develop new ASIC technologies suitable for converting complex, RAM-intensive FPGAs. Xilinx recently introduced the XH3 FpgASIC architecture which provides dense gate array logic surrounded by an I/O ring that replicates the Xilinx FPGA I/O. FPGA features are built into the base arrays, further reducing the risk of conversion problems.

Xilinx HardWire devices are an excellent cost reduction path for FPGA's above 40K system gates and are especially suited for most dense FPGAs.

Another company specializing is Clear Logic Corporation, who offers a solution for Altera FPGAs only. Clear Logic offers their proprietary ClearFire <sup>TM</sup> technique for laser cutting metal fuses in base arrays which closely resemble the logic resources in the Altera Flex8000 family of FPGAs. The advantage to the customer is that by optimizing processes, libraries, and feature sets to convert Altera PLDs exclusively, the risk of con-

verting the design incorrectly is reduced. In the future, this type of focus will be required to provide accurate FPGA cost reductions.

#### Conclusion

In the future, FPGA technology will be increasingly suited for applications previously considered as gate array or standard cell territory. Many logic designers are realizing that they can take advantage of FPGA time-to-market benefits and still achieve a gate array cost point for volume production.

However, options for translating the FPGA to an ASIC are changing. Because of the complexity of the FPGA features and the density of RAM, many smaller gate array conversion vendors are dropping out of the market. Pad limitation for both FPGA's and gate arrays can minimize cost reduction benefits unless creative pad options can be implemented. Architecturally, FPGA's and gate arrays are also diverging. Differing design methodology and RAM implementations can be very inefficient if not specifically accounted for in the conversion process. The new models for success in the conversion market will be companies who specialize in converting a single architecture, such as Clear Logic with Altera devices, Lucent with MACO<sup>™</sup> and Xilinx with HardWire FpgASIC's. These will be the options that provide the closest match and the most expertise for the 200K+ gate FPGA's of today. **£**

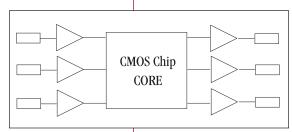

*Figure 1: XH3 Architecture*

# Many ASICs Can Easily be EPELACED with FPGAs by Austin Lesea, Principal Engineer, austin.lesea@xilinx.com

One of the first things you usually notice about a printed circuit board design is the use of the "big chips." It is not hard to find the microcontroller, the memories, the FPGAs, and the ASICs. And, sometimes the unused capacity in one FPGA is enough to replace several ASICs. If you want to reduce your overall development/ manufacturing/test costs it often makes sense to incorporate ASIC functions into your FPGAs.

#### **Telecommunications**

I'll discuss three different common tasks performed in telecommunications: framing, multiplexing, and performance monitoring.

In a typical digital communications application, there may be a T1 or E1 framer ASIC. These devices usually cost about \$20 in quantity, and

**"If you** want to reduce your overall development/ manufacturing/test costs it often makes sense to incorporate ASIC functions into your FPGAs." they may be underutilized by the application. Sometimes, only the transmit section, or just the receive section are used, or sometimes the pattern being generated is fixed, and the device is not being used to its fullest. The descrip-

tion of these functions is available from a number of sources such as ITU G-series documents (G.703 for example), or from ANSI, ATIS T1 documents.

Digital multiplexers/demultiplexers (MULDEM's) are also common ASICs. They take a number of T1 or E1 signals, multiplex and demultiplex them, to and from a higher rate signal. Again, you can refer to the ITU or ANSI standards to get all the information you need to implement the function in an FPGA. Quite frequently, if the application also involves a fiber optic channel, or a radio link, other logic is required, which can easily be implemented on the same FPGA.

Performance monitoring consists of accumulating bit errors, coding violations, out of frame conditions and CRC errors. It must also keep track of these in light of error statistics. In these applications, monitoring bit streams at rates from 1 to 50 megabits per second is not a task that is easily performed by a microcontroller. To detect and keep track of the events, and then present them in a digested fashion to the microcontroller, allows for more features and higher performance. These circuits are all simple counters, shift registers and multiplexers, easily implemented in an FPGA.

#### Signal Processing

Digital finite impulse response filters (FIRs) are common elements of any communications system as well as control systems. Depending on the speed, resolution and number of taps required, an FPGA may be a good choice.

One such application is the root Nyquist transmit filter. In any channel, to provide for zero inter-symbol interference (ISI), you need to filter the transmit symbols. Many designs take the optimal ISI-free filter for a channel and split it into two parts: half at the transmit end, and half at the receive end. This also minimizes transmit bandwidth in the channel. Taking half of a filter is the same as the square root of the response, hence the name root Nyquist filter. **"By designing** ASIC functions into an FPGA, you usually save money, power, and board space. Once designed, the function becomes part of your company's intellectual property, and can be re-used."

A typical FIR structure for the transmit filter is a shift register which is clocked at three times the symbol rate (or more), where the outputs or taps of the flip-flops in the register pass through resistors to a summing junction. The resistor values are chosen to set the gains in the taps of the filter. The sign of the value to be summed is chosen by selecting the normal, or the inverting output of the register. In one example, a 22-tap FIR is easily implemented in the I/O blocks of the FPGA along one side of the device. The output of the summing junction need only pass through a simple low pass filter to remove the sampling clock and the harmonics. Such filters are commonly used in all digital radio systems. Each bit of a modulation format's symbol requires such a filter, so for QAM, two such filters are required, and for 16QAM, four such filters are required.

Resistor/register FIR structures are useful to symbol rates up to a few mega symbols per second, and are easily implemented in an FPGA.

#### **General Purpose Applications**

Another good example of the "no more ASICs" design philosophy is in forward error correcting. Most communication channels have errors that occur (fiber, radio, magnetic, or metallic based channels) and need some amount of error correction to make the channel useful. Rather than buying ASICs to do the job, again it makes sense to perform the functions in an FPGA. Some forward error correction algorithms require a large memory block, but using an external RAM device is still less expensive than the ASIC alternative.

Some error correcting schemes are fairly easy to implement, and require only feedback shift register structures, such as Reed-Solomon codes. The simple schemes have a high overhead; they do not correct many errors per block or byte in relation to the extra bits required. These codes typically require 50% or more bits as check bits.

More powerful error correcting codes are popular where bandwidth or more bits becomes a liability. These are the Bose-Chaudhuri-Hocqueghem (BCH) codes. These codes can correct both random and burst errors, and can recognize when they cannot correct the errors. The more powerful the error correction scheme, the more memory is required. Some BCH codes, 511 bits for a 493-bit block for example, will correct one, two, or three bit errors in any block. The efficiency of this code is that it only adds less than 4% more bits to the channel.

Frequency synthesis is another area where the often expensive and single-sourced parts may be easily replaced by an FPGA. Fractional synthesizers, pulse swallowers, direct digital frequency synthesizers, as well as the phase detectors for phase locked loops, are all easily implemented in FPGAs.

#### Conclusion

By designing ASIC functions into an FPGA, you usually save money, power, and board space. Once designed, the function becomes part of your company's intellectual property, and can be reused. For example, if an application needs to change from being a T1 to and E1 design, often only the FPGA program needs to change, and the board remains the same. In fact, some designs initialize as T1 or E1 depending on configurations stored in memory, once the application is selected.

If at some point the standards change, or the competition adds some highly desirable feature (or you want to add a new feature), the FPGA also gives you a future - it can be easily changed. If an ASIC is part of the design, you will end up with a board re-layout, and probably have to add an FPGA to "band-aid" the design. Why not get the design right the first time? **£**.

#### **PRODUCT INFORMATION - CPLDs**

by David Chiang, Manager, CPLD Technical Marketing, david.chiang@xilinx.com

# **XC9500XL 3.3V FastFLASH CPLDs** *Even More Speed and Features At Lower Costs*

With 10 million 5V XC9500 devices shipped, the world's leading FLASH CPLD family continues to break all records as the fastest growing CPLD family in the industry. Building on that success, we are introducing the new 3.3V XC9500XL. Best

**"The XC9500** architecture is already widely recognized as among the most advanced in the world." of all, the XC9500XL family is already supported by your Alliance Series 1.5 and Foundation Series 1.5 development systems.

The XC9500 architecture is already widely recognized as among the most advanced in the world. The new 3.3V XC9500XL improves on

this success with all-new features:

- High-speed FastCONNECT II switch matrix for up to 200MHz system performance

- New ultra-wide block fan-in of 54 for extrawide functions

- Three global clocks with local clock inversion

- Global and individual output enables (OEs) with local OE inversion

| FEATURE            | XC9536XL  | XC9572XL   | XC95144XL   | XC95288XL   |

|--------------------|-----------|------------|-------------|-------------|

| Macrocells         | 36        | 72         | 144         | 288         |

| Usable Gates       | 800       | 1,600      | 3,200       | 6,400       |

| Registers          | 36        | 72         | 144         | 288         |

| Fastest tPD (ns)   | 4         | 5          | 5           | 6           |

| Fastest fSYS (MHz) | 200       | 178        | 178         | 151         |

| Package Options    | PC44 (34) | PC44 (34)  |             |             |

| (# user I/O pins)  | VQ64 (36) | VQ64 (52)  | TQ100 (81)  |             |

|                    |           | TQ100 (72) | TQ144 (117) | TQ144 (117) |

|                    |           |            |             | PQ208 (168) |

|                    |           |            |             | BG352 (192) |

|                    | CS48 (36) | CS48 (38)  | CS144 (117) |             |

£ XILINX®

Table 1: XC9500XL CPLD Family

- Dedicated clock-enable signal in each register

- Input hysteresis and bus-hold for all user I/O pins

- Inputs compatible with 5V, 3.3V, and 2.5V signals

- Leading-edge 0.35µ feature-size FastFLASH technology

Of course, the XC9500XL architecture also supports the leading-edge features available in the XC9500 family:

- Superior pin-locking characteristics

- Up to 90 product-term functions per macrocell

- Built-in D-type or T-type flip-flop option

- 18-macrocell function blocks for efficient 16-bit look-ahead logic implementations

- Dedicated JTAG/ISP pins for immunity from "ISP Lock-Out"

- Highest programming reliability:10,000 program/erase cycles and 20-year data retention

The XC9500XL devices were developed to operate with leading-edge FPGAs in today's advanced communications and computing systems using a 3.3V power supply. You can optimally partition fast state machines and control functions into XC9500XL devices and partition complex subsystem functions (including cores) into Spartan-XL or XC4000X FPGAs, all using a unified software environment.

#### Conclusion

Now you have the best 3.3V CPLDs available, fully supported by the Xilinx Alliance Series 1.5 and Foundation Series 1.5 software. The XC9500XL family offers the best in speed, flexibility and reliability, along with the high-quality support you expect from Xilinx. **£**

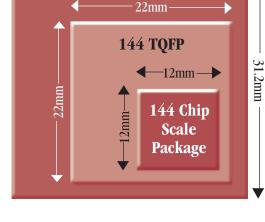

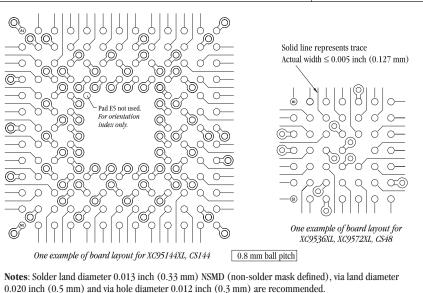

# New Chip Scale Packaging for Small, Lightweight Designs

Xilinx has just introduced two new chip scale packages for the new XC9500XL family: A 48-pin version for the XC9536XL and a 144-pin version for the XC95144XL. The 12x12 millimeter package for the XC95144XL features 117 I/Os and has a seven times smaller footprint than the 160-pin plastic quad flat pack device (see **Figure 1**). In addition, the 48-pin CSP package for the 3.3V XC9536XL gives you access to 36 I/Os while the XC9572XL has 38 I/Os available.

According to Electronic Trend Publications in San Jose, the use of CSP packages is expected to grow by 108% per year over the next few years, reaching more than 6.1 billion units shipped worldwide by 2002. This dramatic growth is occurring because CSP packages bring you the benefits of:

- An extremely small form factor for such applications as PCMCIA cards, portable and wireless designs, and PC add-in cards.

- Lower inductance and lower capacitance

- The absence of the thin, fragile leads found on other packages

- A very thin, very light weight package

- You can take advantage of existing circuit board lithography and assembly equipment. (Board-level assemblers, like Solectron, have already qualified CSPs.)

Xilinx also has a simple board layout solution (see **Figure 2**) for the 48-lead package that uses widely available 5-mil board traces without resorting to more expensive fine line printed circuit board technologies that require features like buried and micro vias. This gives you all the advantages of the smaller CSP foot-

31.2mm

**160 PQFP**

print without the added expense of fine-line lithography boards.

#### Conclusion

Xilinx continues to be an innovator in leadingedge, easy-to-use package technology. These two new chip scale packages are another milestone in our continuing efforts to make programmable logic even more flexible and accessible to you.  $\boldsymbol{\xi}$  by Frank Toth, Marketing Manager for FastFLASH Products, frank.toth@xilinx.com

Figure 1: Package Size Comparison

Figure 2: Two Sample Board Layouts

by Dave Chiang, Manager, CPLD Technical Marketing, david.chiang@ xilinx.com

# Choosing A 3.3V CPLD? "ARM" Yourself...

Leading digital system manufacturers are rapidly adopting 3.3V components for higher performance, lower costs, lower power, and higher system reliability. With many new 3.3V CPLD families being introduced, the choices can seem confusing and overwhelming. To simplify your decision, "ARM" yourself with the three most important criteria when choosing a new 3.3V CPLD family: <u>Architecture, Reliability</u>, and <u>Manufacturing-friendliness</u>.

#### Architecture

CPLDs are commonly used in state machine and control applications, and they are often used to implement the last design fixes before board production. As such, they need the architectural flexibility to adapt to last minute changes without pin assignment changes. For maximum protection

# A RCHITECTURE R ELIABILITY M ANUFACTURING-FRIENDLINESS

against unexpected design iterations, the architecture should have superior pin-locking characteristics and excellent logic resource allocation.

You should look for superior switch matrix routability,

wide block fan-in, an abundance of clocking options, and flexible macrocell capability. This will give you the utmost flexibility to make those last-minute changes without reworking your entire board.

#### **Reliability**

Device reliability is a critical issue, yet many CPLD manufacturers have not kept up with the latest advances. The reliability of CPLDs is a large part of overall system reliability for several reasons:

• CPLDs are being programmed and tested within the system instead of being externally programmed and tested prior to board assembly. Thus, any programming failure involves not only the device cost but also expensive board rework costs as well.

- Leading-edge manufacturers are continuing to increase the operating life of new digital systems. This puts a strain on older CPLD technologies developed for a system life of less than 10 years.

- More systems are incorporating field upgrade capabilities to prolong system life. Because insystem programming is done under variable field conditions, programming reliability is critical.

You should look for a CPLD family that offers the highest level of programming reliability and data retention, to ensure that your designs will continue to work under any conditions. Flash technology currently offers the highest reliability, with an endurance rating of 10,000 program/ erase cycles and 20 years data retention. Most older technologies can offer only 100 cycles and 10 years of data retention. Fortunately, the new Flash CPLD technologies can easily support increased programming reliability levels with no additional cost.

#### Manufacturing-friendliness

Working prototypes do not provide sales dollars until they are produced and sold. CPLDs enable rapid test development and production release, which makes industry-standard, JTAG, insystem programming support invaluable. The IEEE Std 1149.1 (JTAG) interface is the most popular method for in-system programming, because it is supported by the most CPLD and FPGA vendors. Full conformance to the JTAG standard, enables suppliers of in-system programming and test tools to easily support your future designs.

For full compatibility with third party in-system programming suppliers, you should look for full JTAG Boundary-Scan test capability and JTAG insystem programming interface.

#### The FastFLASH XC9500XL Advantage

The XC9500XL 3.3V CPLD family uniquely excels in all three "ARM" criteria, and offers the highest level of programming reliability in a JTAGcompatible, in-system programmable family. The XC9500XL family features:

- The most flexible architecture

- Wide 54-input function blocks\*

- Up to 90 product-terms per output\*

- Three global clocks, with local inversion capability

- Immunity from all power supply sequencing problems

- Compatibility with 5V, 3.3V, and 2.5V signals

- Highest reliability rating

- 20 year data retention\*

- 10,000 endurance cycles\*

*....you can* rest assured that your designs will remain trouble free."

- Full IEEE Std 1149.1 (JTAG) test and programming

- The most complete Boundary-Scan support with eight instructions\*

- JTAG supported in-system programming instructions.

#### Conclusion

Arm yourself with the XC9500XL family for all your 3.3V CPLD needs, and you can rest assured that your designs will remain trouble free. **£**

\*These are the highest available in the 3.3V CPLD industry.

### Get Max Headroom with XC9500 CPLDs

#### Conclusion

Xilinx CPLDs offer 12% more density, with up to 12% less cost – that's something to be excited about.  $\Sigma$  by John Spencer Ahn, CPLD Product Marketing Manager, john.ahn@xilinx.com

The XC9500 CPLDs are not only the mostadvanced in-system programmable CPLDs in the industry, they are also the roomiest. If you are currently using other 128- or 256-macrocell CPLDs, you may be missing out on valuable density "headroom."

Two members of the XC9500 family, the XC95144 and the XC95288 offer 12% more macrocells than competing CPLDs. The XC95144 offers 144 macrocells, 16 more than the competing 128-macrocell devices currently available. The XC95288 has 288 macrocells, 16 more than the competing 256-macrocell CPLDs. This extra headroom that Xilinx offers gives you a significant advantage – you can always use more macrocells.

To top it off, the XC95144 and the XC95288 cost less than the competitor's higher-density offerings.

#### **PRODUCT INFORMATION - SOFTWARE**

Silicon presso Designing with the Web

by Wallace Westfeldt, Frank Toth, Neil Jacobson and Scott Lewis

framework for hardware development called Silicon Xpresso. As its name implies, this framework brings the World Wide Web and Java® into the hardware development system.

Last September, Xilinx announced a new

The Web today is already a powerful tool for the programmable logic designer. The technical nature and time to market pressure of hardware design requires immediate access to up-to-date information. All the semiconductor vendors invest significant resources in creating and maintaining

these informational websites. And with this investment, their customers receive significant returns.

> These websites contain application notes, solutions databases, updates to software releases, and in-depth technical descriptions of the products and their architectures. Some of these sites, such as WebLINX from Xilinx, even provide

a large array of downloadable IP in the form of parameterizable and predefined cores. The usage of pre-existing verified cores as well as the auto-

- matic generation of new cores has become an

- invaluable time saver for programmable logic

- development. Thus, today's Web has become the

- informational infrastructure of choice of the

- hardware designer.

Leveraging the existence of this infrastructure and the acceptance of the powerful Java language as a standard development environment for Webbased tools and applications, Xilinx has initiated a new paradigm where the Web is also used as an interactive component in the development and design of applications. You can now use the Web for development, debug, and deployment as well as making the Web an integral part of your developed end-product. Furthermore, this means that your customer, the end user, can take advantage of this environment for field upgrades, deployment, and real-time usage of your products.

At this time, the first two phases of Silicon Xpresso have been announced. Phase 1, provides new technology in form of two new products: WebFitter and a Java API for Boundary Scan. Phase 2, is a significant enhancement of our existing technologies on the Web and in our existing development tools.

#### WebFitter

WebFitter is a design evaluation tool that allows you to quickly and efficiently evaluate your CPLD designs using the latest revision of our fitter software. You need not learn any software details or use any of your computing power to evaluate your design.

Typically, you need to go through many steps to evaluate a PLD design. Valuable time is spent loading, configuring, and learning design software before the design can be evaluated. You also need to make sure you have the latest software from the PLD vendor and then use your own computer to evaluate the design.

WebFitter makes it much easier to evaluate your design in silicon, and designs run fast over the network. WebFitter eliminates the need for licenses, and software CDs, freeing system time for other tasks. WebFitter is easy to use; you simply register, and submit your design. Then you receive a return email pointing to your data and analysis reports. You can select files that specify the pin-to-pin delays, mapping information, and the resulting pinout. A JEDEC Programming File can also be downloaded for use with the Xilinx

Java is a registered trademark of Sun Microsystems, Inc.

JTAG Programmer Software (and download cable) to program the Xilinx device. If an error occurs, you can gather information from the log files. You can download a zipped version of all the files, and you can choose to save or delete the design once it is completed.

#### Java API For Boundary Scan

The proposed Sun Microsystems Java API for Boundary Scan devices allows complete support of all JTAG and JTAG-based ISP operations for all IEEE 1149.1-compliant (JTAG) devices. Because the API is Java based it also facilitates access to this functionality over the Internet. This enabling technology then provides the framework for you to develop and deploy systems based on any Boundary Scan programmable logic device.

The Java API for Boundary Scan provides you with cross-product, multi-platform support for insystem programming, test, and debug. It takes advantage of the write once/run anywhere feature of Java and provides complete support of Boundary Scan through the entire product life cycle (prototyping, manufacturing, and field upgrade).

Currently each PLD (or other Boundary Scan product) vendor writes a separate format stimulus file for each device which requires separate translators and compilers for each platform. Having more than one type of device on a board means that you must integrate all translators and compilers together in one chain, and call separate routines. Supporting all devices and platforms is an arduous task. Any changes or additions must be painstakingly "edited in" every time a device is added or a change is made.

The Java API for Boundary Scan solution is simple and easy to use across all platforms and can seamlessly incorporate PLDs from different vendors. The write once/run anywhere feature ensures that new parts can easily be integrated into the JTAG environment, simplifying the programming flow and setting the stage for you to easily program and test multiple vendors' devices on the same board. You need not re-write code for separate translators and compilers every time a new device is introduced into the environment. In addition, because of the rich set of existing Java reference materials and development tools, systems incorporating the Java API for Boundary Scan can be quickly developed, debugged, and deployed.

The use of Java's rich set of existing class libraries enables tight integration of hardware subsystems in very powerful ways. This can facilitate the development of systems that interact with one another remotely, to re-program the system PLD's, allowing you to incorporate new functionality on-demand.

#### Web-Enabled Design Software

In the current release of the Foundation Series 1.5 and the upcoming release of the Alliance Se-

ries 1.5i, we have added a direct connection from the Project Manager and Design Manger to our website. This direct connection (PC only for now) means immediate access to the latest Xilinx technical information as well as CoreLINX where valuable and updated IP can be downloaded.

#### The Future of Silicon Xpresso

Silicon Xpresso is designed to provide increased benefits to you

and your customers. By providing enabling technologies that are Web intelligent we are providing not only the environment for design but also the environment for deployment and usage. This will enable you to provide more flexible applications in a broader spectrum of markets.  $\mathbf{x}$

**"Today's Web** has become the informational infrastructure of choice of the bardware designer."

#### FOR MORE INFORMATION, CONTACT:

- Frank Toth (Java API for Boundary-Scan) 408-8796836 frank.toth@xilinx.com

- Neil Jacobson (Java API for Boundary-Scan) 408-879-4885 neil.jacobson@xilinx.com

- Scott Lewis (WebFitter) 408-879-4556 scott.lewis@xilinx.com

- Wallace Westfeldt (Silicon Xpresso) 303-413-3280 wallace.westfeldt@xilinx.com

# **Guaranteeing Designs Work in All Conditions**

Using Minimum and Prorated Delay Information in New Alliance Series 1.5 Software

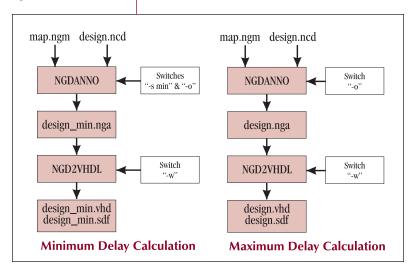

by Julie Callow, Technical Manager, Alliance EDA Program, julie@xilinx.com; and Mahadevan Ramasame, Technical Marketing Engineer,Alliance Series, mahadeva@xilinx.com The new Alliance Series 1.5 software provides two significant new features that support the XC4000XL family. Version 1.5 now provides minimum delay information to help you create racefree asynchronous circuits and it provides prorated delay information that allows you to analyze your circuit under varying voltage and temperature conditions.

#### **Minimum Delays**

FPGA densities now approach one million system gates, making the availability of minimum delay information a significant factor for systemlevel timing analysis. Simulation models generated using minimum delays ensure that race conditions are not generated with a best-case process, and guarantees correct design operation when implemented on devices made from multiple fabrication lines.

Minimum delays for timing simulation are generated using a utility called NGDANNO, which can annotate a minimum or maximum delay value in the design.sdf file. Running NGDANNO with no specific command line option will annotate worstcase delays. To generate minimum delays, run NGDANNO with the "-s min" command line option. By using the "-s min" and "-o" (output)

Figure 1

switches, you can generate both maximum and minimum delay values.

Generate minimum delays using the following command at the DOS prompt:

ngdanno -s min design.ncd map.ngm -o design\_min.nga ngd2vhdl -w design\_min.nga design\_min.vhd

Generate maximum delays using the following command at the DOS prompt:

ngdanno design.ncd map.ngm -o design.nga ngd2vhdl -w design.nga design.vhd

After the design.nga netlist is created, NGD2VER (Verilog Netlister), NGD2VHDL (VHDL Netlister), or NGD2EDIF (EDIF Netlister) is used to create the structural simulation netlist. Using NGD2VER or NGD2VHDL, the minimum delays are output into an SDF file, whereas NGD2EDIF writes minimum delays in the EDIF netlist as pin/instance properties.

Timing Analyzer (TRACE) has the option to view the minimum delays for XC4000XL devices. Minimum delays for the nets can be viewed by setting the speed grade options to "min" and analyzing the design. In the Timing Analyzer window, click on "options," choose "speed grade" and select "min." Selection of other speed grade options generates the maximum delays.

#### Prorated Delays for Voltage and Temperature

Design operating conditions vary, based on your application. Voltage and temperature prorating allows you to test your design under real operating conditions. The delays vary from worst case to best case based on the voltage and temperature, and can be calculated for a voltage range of 3.0V to 3.6V and a temperature range of 0°C to 85°C. The default value is 70°C and 3.3V.

To calculate the prorated delays for timing simulation, specify operating conditions in the Physical Constraints File (.pcf) and run the NGDANNO utility. The syntax for specifying the temperature and voltage is:

```

VOLTAGE = value[units];

value = a real or integer number specifying voltage

Units = unit of measure (volts) [optional]

TEMPERATURE = value[units];

value = a real or integer number specifying

temperature

Units = unit of measure ( F, K, or C ) [optional]

(default unit is C)

```

#### An example design.pcf file:

```

VOLTAGE = 3.15 ;

TEMPERATURE = 70 ;

```

Generate the prorated delays for voltage and temperature using the following command at the DOS prompt:

ngdanno -p design.pcf design.ncd map.ngm -o design\_prorated.nga ngd2vhdl -w design\_prorated.nga design\_prorated.vhd

If the specified voltage and temperature range doesn't fall within bounds, a warning will be issued and the constraint won't apply. NGDANNO will generate a warning when the standard delays (calculated at standard operating conditions) are not used during back annotation.

Timing Analyzer (TRACE) has the option to view the prorated delays for voltage and tempera-

ture for XC4000XL devices. Enter the voltage and terperature in the design.pcf file and invoke the Timing Analyzer. Click on "options," and choose the speed grade to generate the prorated delays for the specified voltage and temperature.

#### Conclusion

As Xilinx continues to provide higher density ASIC replacement devices, minimum delays together with voltage

and temperature prorating analysis becomes an integral part of the FPGA design flow. Minimum delays along with voltage and temperature prorating support will be extended to the XC4000XLA, Spartan, and Virtex families in future Alliance Series software releases.  $\boldsymbol{\xi}$

map.ngm design.ncd design.pcf NGDANNO design\_prorated.nga MGD2VHDL Switch "-p" & "-o" Switches "-p" & "-o" design\_prorated.nga Prorated Delay Calculation

Figure 2

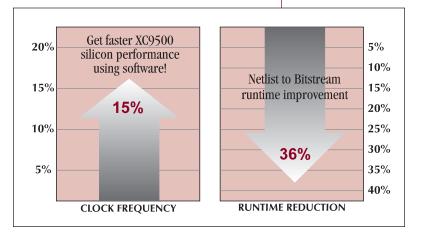

Speed Up Your XC9500 Design With The New v1.5 Software

by Dave Grace, Software Product Manager - CPLD Division, dave.grace@xilinx.com

\*Design Test Suite of 50 HDL (VHDL & Verilog)

Designs. Windows NT 4.0

& Windows 95/98.

#### Our latest advances in CPLD Implementation tools (v1.5) are now included in both the Alliance 1.5 and Foundation 1.5 products. Enhancements to the speed, area, and timing-driven optimization algorithms have resulted in faster runtimes and faster silicon performance.

#### **Faster Runtime**

This new release of the Xilinx implementation technology has improved runtime by 36%\* over the previous V1.4 release. Plus, you will see up to 50% reductions in runtime for designs that use more than 100 macrocells.

#### **Faster Performance**

Using the same device, package, and speed grade, V1.5 delivers a 15%\* improvement in system clock performance. This allows you to choose the best device/package/speed grade combination, based on your cost/performance requirements.

#### Conclusion

If you want to create the most efficient CPLD designs, with the least time and effort, upgrade now to our new v1.5 development tools. For information on upgrading contact your local Xilinx sales representative or authorized distributor. For a complete listing of Xilinx sales contacts, visit WebLINX at www.xilinx.com. **ξ**

# **Unleash Your Creative Potential With The New Alliance Series 1.5 Software**

by Hitesh Patel, Technical Marketing Manager, hiteshp@xilinx.com Our latest Alliance Series 1.5 software not only improves your design performance and reduces runtimes, it also provides support for the industry's first million-gate FPGAs, the new Virtex family from Xilinx. The Alliance Series also works seamlessly with industry-leading synthesis and simulation vendors like Exemplar, Synopsys, Synplicity, and Model Technology, making your job easier than ever before.

"The Alliance Series 1.5 delivers higher frequency of operation and faster runtimes. The intuitive design flow, with its graphical constraints editor and flexible report generation capabilities, offers greater insight to design processing, allowing the engineer to achieve the design goal quickly, and with ease..." said Praveen Shekokar, Director of Engineering at Comit Systems Inc. (www.comit.com).

#### **Productivity Enhancements**

The Alliance Series 1.5 software uses our new AKA*speed*<sup>™</sup> technology to deliver a suite of new

Floorplanner

algorithms and features that give you the industry's fastest timing-driven compile times — up to 30x faster than MAX+plus II — with clock performance improvements up to 30%.

A graphical constraint editor guides you to the best con-

straint methodology, reducing mistakes and eliminating the need to learn cryptic syntax. You enter design constraints through an easy-to-use graphical user interface that allows you to select constraints such as clock rates, input setup delays, and clock-to-out delays. This powerful editor allows you to easily create groups based on net names for multi-cycles path constraints.

AKA*speed* technology brings the power of ASIC development tools to the FPGA world by allowing timing analysis and delay simulation with both

minimum and maximum delays as well as voltage and temperature prorating factors. In high-performance systems, minimum delay analysis is a requirement for creating race-free asynchronous circuits and guaranteeing correct design operation.

#### **Design Planning**

The floorplanner has been rewritten from the ground up to leverage your expertise. Physical design floorplanning allows you to analyze a design's hierarchy, identify structured and unstructured logic, and create an optimal physical hierarchy for your design. Most designs do not need floorplanning to meet the design requirements, however if you need maximum design performance, this tool delivers the power and flexibility of area-based floorplanning. For example, you can precisely place large RAM arrays or relatively place structured logic.

#### **Device Support**

The Alliance Series 1.5 software supports our new Virtex family, which features a synthesisfriendly architecture, fabricated on an advanced 0.25µ process. It is the first FPGA architecture to offer system design capabilities with 160MHz chipto-chip communication, DLLs, 133MHz access to external and internal memory, and true dual-port memory. Virtex offers large on-chip memory for buffering and processing as well as flexible interfaces that connect to existing and emerging I/O standards.

In addition, the Alliance Series software supports the new XC4000XLA, SpartanXL, and the XC9500XL device families.

#### Installation and Security

No license servers or dongles are required. Simply enter the serial number, found on the back of your CD package when you install the Alliance Series software, for instant access.

#### Conclusion

The new Alliance Series 1.5 software enables you to quickly create high performance designs using the most advanced FPGAs and CPLDs in the industry.  $\mathbf{x}$

#### COLUMN

### **Using Nested If Statements**

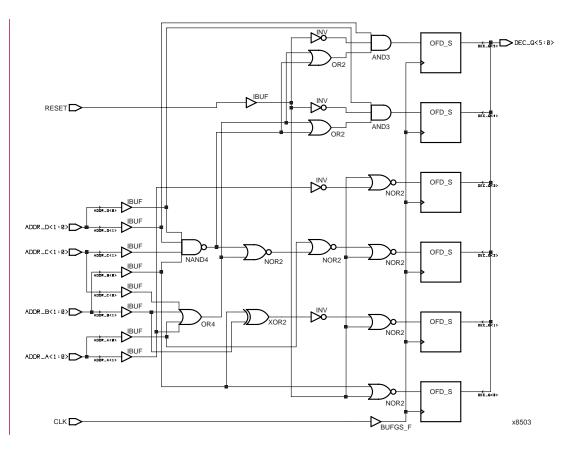

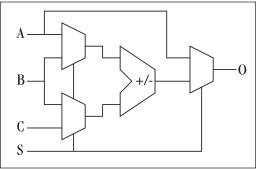

Improper use of the "NESTED IF" statement can result in increased area and longer delays. Each IF keyword specifies priority-encoded logic. To avoid long path delays, do not use extremely long NESTED IF constructs as shown in the following VHDL/Verilog examples. These designs are shown implemented in gates in **Figure 1**. Follow-

**Inefficient Use of Nested If Statement**

#### **VHDL EXAMPLE**

```

- NESTED IF.VHD

- May 1997

Library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.STD_LOGIC_ARITH.all;

entity nested if is

port (ADDR_A: in std_logic_vector (1 downto 0); - ADDRESS Code

ADDR_B: in std_logic_vector (1 downto 0); - ADDRESS Code

ADDR_C: in std_logic_vector (1 downto 0); - ADDRESS Code

ADDR_D: in std_logic_vector (1 downto 0); - ADDRESS Code

RESET: in std logic;

CLK : in std_logic;

DEC_Q: out std_logic_vector (5 downto 0)); - Decode OUTPUT

end nested_if;

architecture xilinx of nested_if is

begin

- NESTED IF PROCESS -

NESTED_IF: process (CLK)

begin

if (CLK'event and CLK = '1') then

if (RESET = 0') then

if (ADDR_A = "00") then

DEC_Q(5 downto 4) <= ADDR_D;</pre>

DEC_Q(3 downto 2) <= "01";</pre>

DEC O(1 downto 0) <= "00";

if (ADDR_B = "01") then

DEC_Q(3 downto 2) <= unsigned(ADDR_A) + `1';</pre>

DEC_Q(1 downto 0) <= unsigned(ADDR_B) + `1';</pre>

if (ADDR_C = "10") then

DEC_Q(5 downto 4) <= unsigned(ADDR_D) + `1';</pre>

if (ADDR_D = "11") then

DEC_Q(5 downto 4) <= "00";</pre>

end if;

else

DEC O(5 downto 4) <= ADDR D;

end if;

end if;

else

DEC_Q(5 downto 4) <= ADDR_D;

DEC_Q(3 downto 2) <= ADDR_A;

DEC_Q(1 downto 0) <= unsigned(ADDR_B) + `1';</pre>

end if;

else

DEC_Q <= "000000";

end if;

end if;

end process

end xilinx;

```

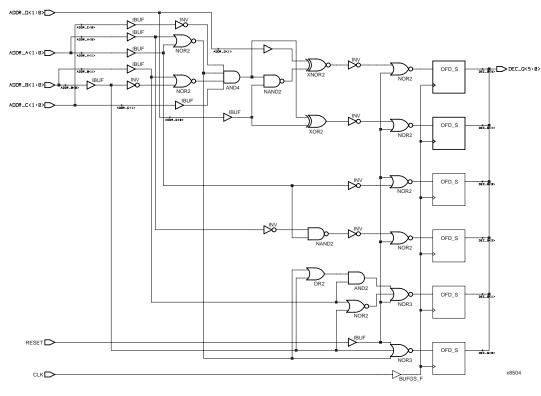

#### ing these examples are VHDL and Verilog designs that use the CASE construct with the NESTED IF to more effectively describe the same function. The CASE construct reduces the delay by approximately 3 ns (using an XC4005E-2 part). The implementation of this design is shown in **Figure 2**.

by Roberta Fulton, Technical Marketing Engineer, Alliance Series, roberta. fulton@xilinx.com

#### **VERILOG EXAMPLE**

endmodule

```

// NESTED_IF.V

11

// Nested If vs. Case Design Example //

// August 1997

11

module nested_if (ADDR_A, ADDR_B, ADDR_C, ADDR_D, RESET, CLK,

DEC_Q);

input [1:0] ADDR A ;

input [1:0] ADDR_B ;

input [1:0] ADDR_C ;

input [1:0] ADDR D ;

input RESET, CLK ;

output [5:0] DEC_Q ;

reg [5:0] DEC 0 ;

// Nested If Process //

always @ (posedge CLK)

begin

if (RESET == 1'b1)

begin

if (ADDR_A == 2'b00)

begin

DEC_Q[5:4] <= ADDR_D;

DEC_Q[3:2] <= 2'b01;

DEC_Q[1:0] <= 2'b00;

if (ADDR_B == 2'b01)

begin

DEC_Q[3:2] <= ADDR_A + 1'b1;</pre>

DEC_Q[1:0] <= ADDR_B + 1'b1;

if (ADDR_C == 2'b10)

begin

DEC_Q[5:4] <= ADDR_D + 1'b1;</pre>

if (ADDR_D == 2'b11)

DEC_Q[5:4] <= 2'b00;

end

else

DEC_Q[5:4] <= ADDR_D;</pre>

end

end

else

DEC_Q[5:4] <= ADDR_D;</pre>

DEC O[3:2] <= ADDR A;

DEC_Q[1:0] <= ADDR_B + 1'b1;</pre>

end

else

DEC O \le 6'b000000;

end

```

```

Continued on the following page

```

#### HDL Advisor

Continued from the previous page

22

Figure 1: The gate implementation for a design with an inefficient use of a nested if statement.

#### Nested If Example Modified to Use If-Case

Note: In the following example, the hyphens ("don't cares") used for bits in the CASE statement may evaluate incorrectly to False for some synthesis tools.

#### **VHDL EXAMPLE**

```

- IF_CASE.VHD

- May 1997

Library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.STD_LOGIC_ARITH.all;

entity if_case is

port (ADDR_A: in std_logic_vector (1 downto 0); - ADDRESS

Code

ADDR_B: in std_logic_vector (1 downto 0); - ADDRESS Code

ADDR_C: in std_logic_vector (1 downto 0); - ADDRESS Code

ADDR_D: in std_logic_vector (1 downto 0); - ADDRESS Code

RESET: in std_logic;

CLK : in std_logic;

DEC_Q: out std_logic_vector (5 downto 0)); - Decode

OUTPUT

end if case;

architecture xilinx of if_case is

signal ADDR_ALL : std_logic_vector (7 downto 0);

begin

-concatenate all address lines -

ADDR_ALL <= (ADDR_A & ADDR_B & ADDR_C & ADDR_D) ;

netlist-

IF_CASE: process (CLK)

begin

if (CLK'event and CLK = `1') then

if (RESET = `0') then

```

```

case ADDR_ALL is

when "00011011" =>

DEC_Q(5 downto 4) <= "00";</pre>

DEC_Q(3 downto 2) <= unsigned(ADDR_A) + `1';</pre>

DEC_Q(1 downto 0) <= unsigned(ADDR_B) + `1';</pre>

when "000110-" =>

DEC_Q(5 downto 4) <= unsigned(ADDR_D) + `1';</pre>

DEC_Q(3 downto 2) <= unsigned(ADDR_A) + `1';</pre>

DEC_Q(1 downto 0) <= unsigned(ADDR_B) + `1';</pre>

when "0001---" =>

DEC_Q(5 downto 4) <= ADDR_D;</pre>

DEC_Q(3 downto 2) <= unsigned(ADDR_A) + `1';</pre>

DEC_Q(1 downto 0) <= unsigned(ADDR_B) + `1';</pre>

when "00----" =>

DEC_Q(5 downto 4) <= ADDR_D;</pre>

DEC_Q(3 downto 2) <= "01";</pre>

DEC_Q(1 downto 0) <= "00";</pre>

when others =>

DEC_Q(5 downto 4) <= ADDR_D;</pre>

DEC_Q(3 downto 2) <= ADDR_A;

DEC_Q(1 downto 0) <= unsigned(ADDR_B) + `1';</pre>

end case;

else

DEC_Q <= "000000";

end if;

end if;

end process;

end xilinx;

```

#### **VERILOG EXAMPLE**

```

// IF_CASE.V

11

// Nested If vs. Case Design Example //

// August 1997

11

module if_case (ADDR_A, ADDR_B, ADDR_C, ADDR_D, RESET, CLK,

DEC_Q);

input [1:0] ADDR_A ;

input [1:0] ADDR_B ;

input [1:0] ADDR_C ;

input [1:0] ADDR_D ;

input RESET, CLK ;

output [5:0] DEC_Q ;

wire [7:0] ADDR_ALL ;

reg [5:0] DEC_Q ;

// Concatenate all address lines //

assign ADDR_ALL = {ADDR_A, ADDR_B, ADDR_C, ADDR_D} ;

// Use `case' instead of `nested_if' for efficient gate netlist

always @ (posedge CLK)

begin

if (RESET == 1'b1)

begin

casex (ADDR_ALL)

8'b00011011: begin

DEC_Q[5:4] <= 2'b00;

DEC_Q[3:2] <= ADDR_A + 1;</pre>

```

```

DEC_Q[1:0] <= ADDR_B + 1'b1;

end

8'b000110xx: begin

DEC_Q[5:4] <= ADDR_D + 1'b1;</pre>

DEC_Q[3:2] <= ADDR_A + 1'b1;</pre>

DEC_Q[1:0] <= ADDR_B + 1'b1;</pre>

end

8'b0001xxxx: begin

DEC_Q[5:4] <= ADDR_D;</pre>

DEC_Q[3:2] <= ADDR_A + 1'b1;</pre>

DEC_Q[1:0] <= ADDR_B + 1'b1;

end

8'b00xxxxxx: begin

DEC_Q[5:4] <= ADDR_D;</pre>

DEC_Q[3:2] <= 2'b01;

DEC_Q[1:0] <= 2'b00;

end

default: begin

DEC_Q[5:4] <= ADDR_D;</pre>

DEC_Q[3:2] <= ADDR_A;</pre>

DEC_Q[1:0] <= ADDR_B + 1'b1;</pre>

end

endcase

end

else

DEC 0 \le 6'b000000;

endmodule

```

end

Figure 2: The gate implementation for a design modified to use if-case.

#### **Comparing the If Statement** and the Case Statement

The IF statement generally produces priorityencoded logic and the CASE statement generally creates balanced logic. An IF statement can contain a set of different expressions while a CASE statement is evaluated against a common controlling expression. In general, use the CASE statement for complex decoding and use the IF statement for speed critical paths. Most current synthesis tools can determine if the IF-ELSEIF conditions are mutually exclusive, and will not create extra logic to build the priority tree. **£**

#### by Roberta Fulton, Alliance EDA Technical Marketing Engineer, roberta@xilinx.com

Several third-party products now use Xilinx FPGAs to provide you with system emulation and rapid-prototyping tools that help you get your