# **NOVRAM\*** Data Sheets

Serial I/O Data Sheets

E<sup>2</sup>PROM Data Sheets

E<sup>2</sup>POT<sup>™</sup> Data Sheets

4

1

2

Applications 5

Reliability 6

**General Information**

### President's Message

Dear Customer:

As the leader of the exciting field of E<sup>2</sup>PROM and NOVRAM memories, Xicor has charted a course to provide an extensive product offering. This catalog contains data sheets for NMOS and CMOS E<sup>2</sup>PROMs and NMOS NOVRAMs. These products are available in a wide variety of speeds, package types and both parallel and serial interface configurations. The majority of the products are offered with extended temperature range, and many are built per Mil-Std-883 for Class B devices.

Xicor has shipped more than 10 million E<sup>2</sup>PROM and NOVRAM memories to its customers. Our research and development budget is very substantial and will enable Xicor to continue to introduce innovative products. Our worldwide sales, marketing and applications organizations are dedicated to the support of your memory requirements. We appreciate your interest and look forward to supplying your present and future requirements.

RIC

Raphael Klein President

Printed in U.S.A. © XICOR, INC., 1985 "All Rights Reserved" **Fact Sheets** contain information on products under development. Xicor reserves the right to change these specifications or modify the product at any time, without notice.

Advanced Data Sheets contain typical product specifications which are subject to change upon device characterization over the full specified temperature range. Xicor reserves the right to change these specifications or modify the product at any time, without notice.

**Preliminary Data Sheets** contain minimum and maximum limits specified over the full temperature range based upon initial production device characterization. Xicor reserves the right to change these specifications or modify the product at any time, without notice.

**Final Data Sheets** contain minimum and maximum limits specified over the full temperature range for production devices.

Contact your local Xicor sales representative to obtain the latest specifications prior to order placement.

E<sup>2</sup>POT<sup>™</sup> is a trademark of Xicor, Inc. NOVRAM is Xicor's nonvolatile static RAM device. COPS<sup>™</sup> is a trademark of National Semiconductor, Corp.

#### LIMITED WARRANTY

#### LIFE RELATED POLICY

In situations where semiconductor component failure may endanger life, system designers using this product should design the system with appropriate error detection and correction, redundancy and back-up features to prevent such an occurrence.

Xicor's products are not authorized for use as critical components in life support devices or systems.

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to

perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

Devices sold by Xicor, Inc. are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. Xicor, Inc. makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Xicor, Inc. makes no warranty of merchantability or fitness for any purpose. Xicor, Inc. reserves the right to discontinue production and change specifications and prices at any time and without notice.

Xicor, Inc. assumes no responsibility for the use of any circuitry other than circuitry embodied in a Xicor, Inc. product. No other circuits, patents, licenses are implied.

## Precautions for the Handling of MOS Devices

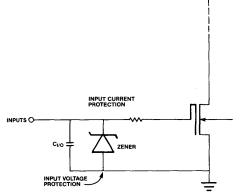

Xicor products are designed with effective input protection to prevent damage to the devices under most conditions. However, any MOS circuit can be catastrophically damaged by excessive electrostatic discharge or transient voltages. The following procedures are recommended to avoid accidental circuit damage.

#### I. Testing MOS Circuits:

- 1. All units should be handled directly from the conductive or antistatic plastic tube in which they were shipped if possible. This action minimizes touching of individual leads.

- 2. If units are to be tested without using the tube carrier, the following precautions should be taken:

- a. Table surfaces which potentially will come in contact with the devices either directly or indirectly (such as through shipping tubes) must be metal or of another conductive material and should be electrically connected to the test equipment and to the test operator (a grounding bracelet is recommended).

- b. The units should be transported in bundled antistatic tubes or metal trays, both of which will assume a common potential when placed on a conductive table top.

- c. Do not band tubes together with adhesive tape or rubber bands without first wrapping them in a conductive layer.

#### II. Test Equipment (Including Environmental Equipment):

- 1. All equipment must be properly returned to the same reference potential (ground) as the devices, the operator, and the container for the devices.

- 2. Devices to be tested should be protected from high voltage surges developed by:

- a. Turning electrical equipment on or off.

- b. Relay switching.

- c. Transients from voltage sources (AC line or power supplies).

#### III. Assembling MOS Devices Onto P.C. Boards:

- 1. The MOS circuits should be mounted on the P.C. board last.

- 2. Similar precautions should be taken as in Item I above, at the assembly work station.

- 3. Soldering irons or solder baths should be at the same reference (ground) potential as the devices.

- 4. Plastic materials which are not antistatic treated should be kept away from devices as they develop and maintain high levels of static charge.

#### IV. Device Handling:

1. Handling of devices should be kept to a minimum. If handling is required, avoid touching the leads directly.

#### V. General:

- 1. The handler should take every precaution that the device will see the same reference potential when moved.

- 2. Anyone handling individual devices should develop a habit of first touching the container in which the units are stored before touching the units.

- 3. Before placing the units into a P.C. board, the handler should touch the P.C. board first.

- 4. Personnel should not wear clothing which will build up static charge. They should wear smocks and clothing made of 100% cotton rather than wool or synthetic fibers.

- 5. Be careful of electrostatic build up through the movement of air over plastic material. This is especially true of acid sinks.

- 6. Personnel or operators should always wear grounded wrist straps when working with MOS devices.

- 7. A 1 meg ohm resistance ground stap is recommended and will protect people up to 5,000 volts AC RMS or DC by limiting current to 5 milliamperes.

- 8. Antistatic ionized air equipment is very effective and useful in preventing electrostatic damage.

- 9. Low humidity maximizes potential static problems. Maintaining humidity levels above 45% is one of the most effective ways to guard against static handling problems.

## **PRODUCT INDEX**

This index includes all devices in Xicor nonvolatile memory product lines.

| Device No.            | Description Pa                                                                 | ge No. |

|-----------------------|--------------------------------------------------------------------------------|--------|

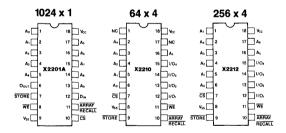

| X2201A                | 1024 x 1 NOVRAM                                                                | . 1-1  |

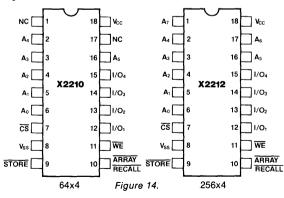

| X2210A                | 64 x 4 NOVRAM                                                                  | . 1-9  |

| X2210, X2210I         | 64 x 4 NOVRAM                                                                  | . 1-17 |

| X2210M                | 64 x 4 NOVRAM Military Temperature Range                                       | . 1-25 |

| X2212A                | 256 x 4 NOVRAM                                                                 | . 1-33 |

| X2212, X2212I         | 256 x 4 NOVRAM                                                                 | . 1-41 |

| X2212M                | 256 x 4 NOVRAM Military Temperature Range                                      | . 1-49 |

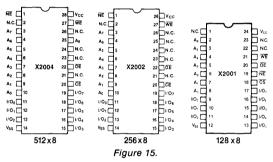

| X2001, X2001I         | 128 x 8 NOVRAM                                                                 | . 1-57 |

| X2002, X2002I         | 256 x 8 NOVRAM                                                                 | . 1-65 |

| X2004, X2004I         | 512 x 8 NOVRAM                                                                 | . 1-73 |

| X2004M                | 512 x 8 NOVRAM Military Temperature Range                                      | . 1-81 |

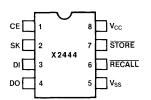

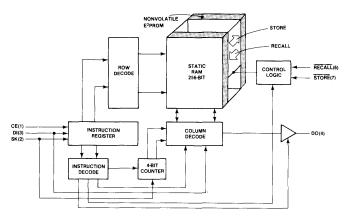

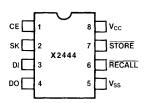

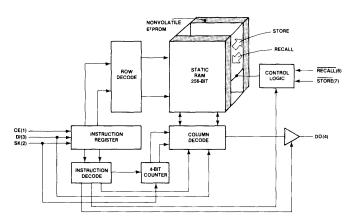

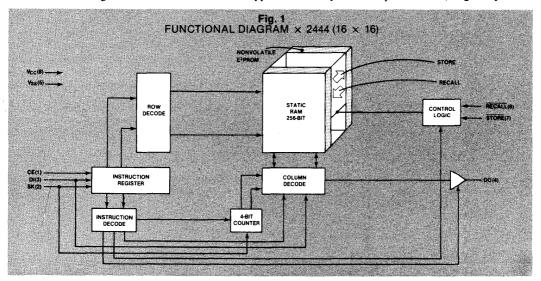

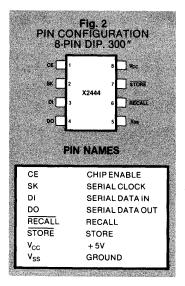

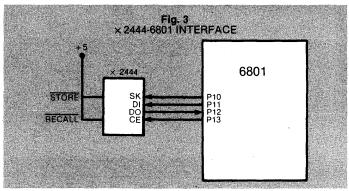

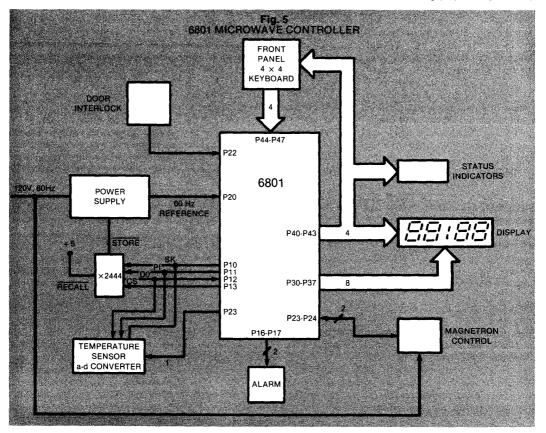

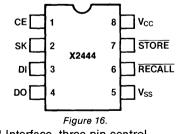

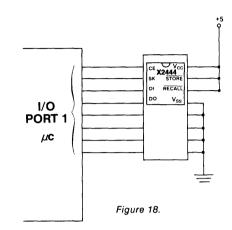

| X2444, X2444I         | 16 x 16 Serial NOVRAM                                                          | . 2-1  |

| X2444M                | 16 x 16 Serial NOVRAM Military Temperature Range                               | . 2-9  |

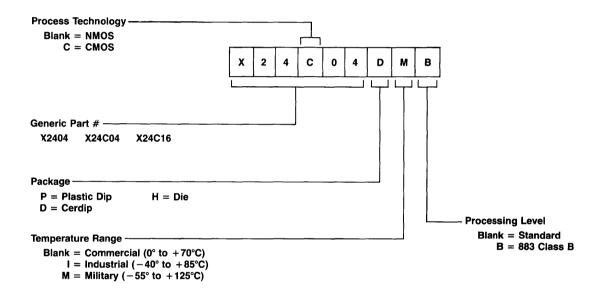

| X2404, X2404I         | 512 x 8 Serial E <sup>2</sup> PROM                                             |        |

| X2404M                | 512 x 8 Serial E <sup>2</sup> PROM Military Temperature Range                  | . 2-27 |

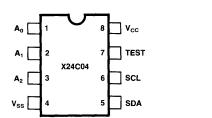

| X24C04                | 512 x 8 CMOS Serial E <sup>2</sup> PROM                                        | . 2-37 |

| X24C16                | 2K x 8 CMOS Serial E <sup>2</sup> PROM                                         | . 2-45 |

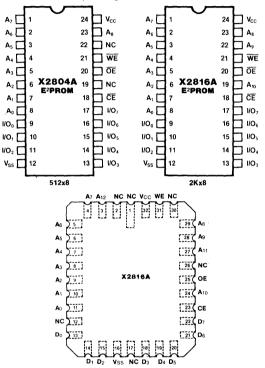

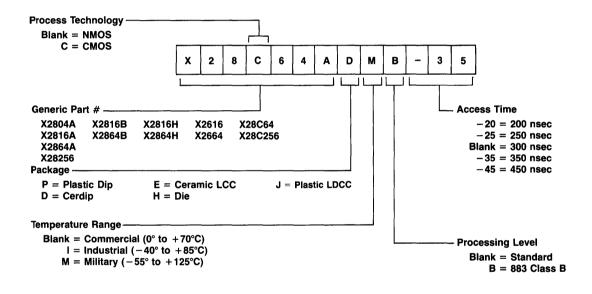

| X2804A, X2804AI       | 512 x 8 E <sup>2</sup> PROM                                                    | . 3-1  |

| X2804AM               | 512 x 8 E <sup>2</sup> PROM Military Temperature Range                         | . 3-7  |

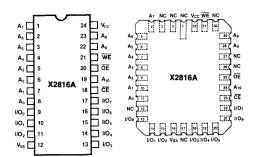

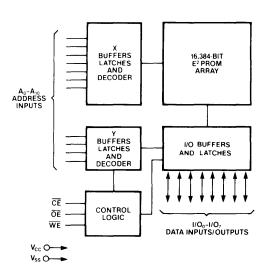

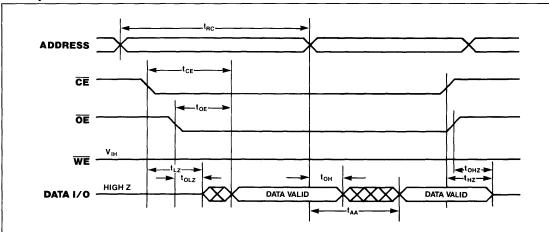

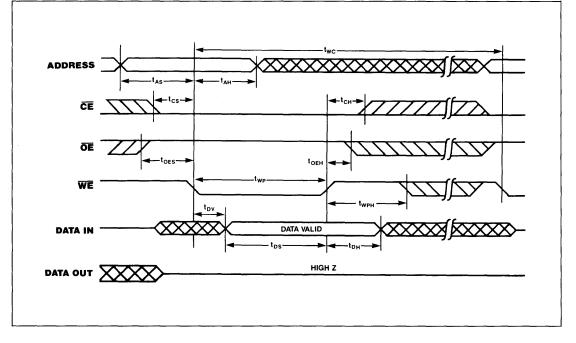

| X2816A, X2816AI       | 2K x 8 E <sup>2</sup> PROM                                                     | . 3-13 |

| X2816AM               | 2K x 8 E <sup>2</sup> PROM Military Temperature Range                          | . 3-19 |

| X2816B                | 2K x 8 E <sup>2</sup> PROM (150ns t <sub>AA</sub> )                            | . 3-25 |

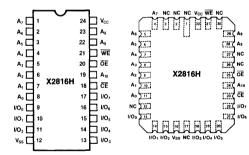

| X2816H                | 2K x 8 E <sup>2</sup> PROM (45ns t <sub>AA</sub> )                             | . 3-31 |

| X2864A-20, X2864AI-20 | 8K x 8 E <sup>2</sup> PROM (200ns t <sub>AA</sub> )                            | . 3-33 |

| X2864A, X2864AI       | 8K x 8 E <sup>2</sup> PROM                                                     | . 3-41 |

| X2864AM-25            | 8K x 8 E <sup>2</sup> PROM Military Temperature Range (250ns t <sub>AA</sub> ) | . 3-49 |

| X2864AM               | 8K x 8 E <sup>2</sup> PROM Military Temperature Range                          | . 3-57 |

| X2864B                | 8K x 8 E <sup>2</sup> PROM (150ns t <sub>AA</sub> )                            | . 3-65 |

| X2864H                | 8K x 8 E <sup>2</sup> PROM (45ns t <sub>AA</sub> )                             | . 3-71 |

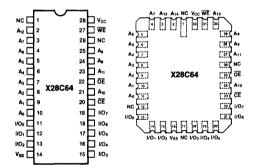

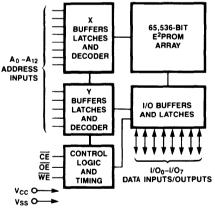

| X28C64                | 8K x 8 CMOS E <sup>2</sup> PROM                                                | . 3-73 |

| X28256                | 32K x 8 E <sup>2</sup> PROM                                                    |        |

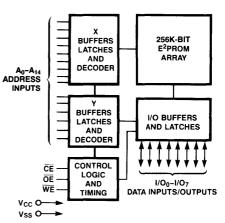

| X28C256               | 32K x 8 CMOS E <sup>2</sup> PROM                                               |        |

| X2616                 | 2K x 8 E <sup>2</sup> PROM Bipolar PROM Pinout                                 |        |

| X2664                 | 8K x 8 E <sup>2</sup> PROM Bipolar PROM Pinout                                 |        |

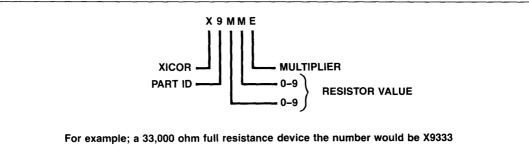

| X9MME                 | E <sup>2</sup> POT <sup>™</sup> Digitally Controlled Potentiometer             | . 4-1  |

. .....

## **Reference Guide to Xicor Nonvolatile Memories**

#### **NOVRAMs**

| Part      |              | Access | Po     | ower    | Store   | No. of | Temp.    | Р | acka | ge | Data<br>Sheet | Order<br>Info. |

|-----------|--------------|--------|--------|---------|---------|--------|----------|---|------|----|---------------|----------------|

| Number    | Organization | Time   | Active | Standby | Cycles  | Pins   | Range(s) | Ρ | D    | E  | Page #        | Page #         |

| X2201A    | 1024 x 1     | 300ns  | 60mA   | N/A     | 10,000  | 18     | A        |   | •    |    | 1-1           | 7-1            |

| X2210A    | 64 x 4       | 250ns  | 50mA   | N/A     | 10,000  | 18     | A        | • | •    |    | 1-9           | 7-1            |

| X2210     | 64 x 4       | 300ns  | 50mA   | N/A     | 10,000  | 18     | A        | • | •    |    | 1-17          | 7-1            |

| X2210/5   | 64 x 4       | 300ns  | 50mA   | N/A     | 50,000  | 18     | A        | • | •    |    | 1-17          | 7-1            |

| X2210/10  | 64 x 4       | 300ns  | 50mA   | N/A     | 100,000 | 18     | A        | • | •    |    | 1-17          | 7-1            |

| X2210I    | 64 x 4       | 300ns  | 55mA   | N/A     | 10,000  | 18     | В        | • | •    |    | 1-17          | 7-1            |

| X2210I/5  | 64 x 4       | 300ns  | 55mA   | N/A     | 50,000  | 18     | В        | • | •    |    | 1-17          | 7-1            |

| X2210I/10 | 64 x 4       | 300ns  | 55mA   | N/A     | 100,000 | 18     | В        | • | •    |    | 1-17          | 7-1            |

| X2210M    | 64 x 4       | 300ns  | 55mA   | N/A     | 10,000  | 18     | С        |   | •    |    | 1-25          | 7-1            |

| X2210M/5  | 64 x 4       | 300ns  | 55mA   | N/A     | 50,000  | 18     | С        |   | •    |    | 1-25          | 7-1            |

| X2210M/10 | 64 x 4       | 300ns  | 55mA   | N/A     | 100,000 | 18     | С        |   | •    |    | 1-25          | 7-1            |

| X2212A    | 256 x 4      | 250ns  | 60mA   | N/A     | 10,000  | 18     | A        | • | •    |    | 1-33          | 7-1            |

| X2212     | 256 x 4      | 300ns  | 60mA   | N/A     | 10,000  | 18     | А        | • | •    |    | 1-41          | 7-1            |

| X2212/5   | 256 x 4      | 300ns  | 60mA   | N/A     | 50,000  | 18     | А        | ٠ | •    |    | 1-41          | 7-1            |

| X2212/10  | 256 x 4      | 300ns  | 60mA   | N/A     | 100,000 | 18     | А        | • | •    |    | 1-41          | 7-1            |

| X2212I    | 256 x 4      | 300ns  | 70mA   | N/A     | 10,000  | 18     | В        | • | •    |    | 1-41          | 7-1            |

| X2212I/5  | 256 x 4      | 300ns  | 70mA   | N/A     | 50,000  | 18     | В        | • | •    |    | 1-41          | 7-1            |

| X2212I/10 | 256 x 4      | 300ns  | 70mA   | N/A     | 100,000 | 18     | В        | ٠ | •    |    | 1-41          | 7-1            |

| X2212M    | 256 x 4      | 300ns  | 70mA   | N/A     | 10,000  | 18     | С        |   | •    |    | 1-49          | 7-1            |

| X2212M/5  | 256 x 4      | 300ns  | 70mA   | N/A     | 50,000  | 18     | С        |   | •    |    | 1-49          | 7-1            |

| X2212M/10 | 256 x 4      | 300ns  | 70mA   | N/A     | 100,000 | 18     | С        |   | •    |    | 1-49          | 7-1            |

N/A = Not Applicable

P = Plastic DIP

D = Cerdip E = Ceramic LCC

#### NOVRAMs (Byte-Wide)

| Part      |              | Access | Po     | wer     | Store   | No. of | Temp.    | Package |   | ge | Data<br>Sheet | Order<br>Info. |

|-----------|--------------|--------|--------|---------|---------|--------|----------|---------|---|----|---------------|----------------|

| Number    | Organization | Time   | Active | Standby | Cycles  | Pins   | Range(s) | Ρ       | D | Е  | Page #        | Page #         |

| X2001-20  | 128 x 8      | 200ns  | 80mA   | 50mA    | 100,000 | 24     | А        | •       | • |    | 1-57          | 7-1            |

| X2001-25  | 128 x 8      | 250ns  | 80mA   | 50mA    | 100,000 | 24     | A        | •       | • |    | 1-57          | 7-1            |

| X2001     | 128 x 8      | 300ns  | 80mA   | 50mA    | 100,000 | 24     | A        | •       | • |    | 1-57          | 7-1            |

| X2001I-20 | 128 x 8      | 200ns  | 100mA  | 65mA    | 100,000 | 24     | В        | •       | • |    | 1-57          | 7-1            |

| X2001I-25 | 128 x 8      | 250ns  | 100mA  | 65mA    | 100,000 | 24     | В        | •       | • |    | 1-57          | 7-1            |

| X2001I    | 128 x 8      | 300ns  | 100mA  | 65mA    | 100,000 | 24     | В        | •       | • |    | 1-57          | 7-1            |

| X2002-20  | 256 x 8      | 200ns  | 90mA   | 55mA    | 100,000 | 28     | A        | •       | • |    | 1-65          | 7-1            |

| X2002-25  | 256 x 8      | 250ns  | 90mA   | 55mA    | 100,000 | 28     | A        | •       | • |    | 1-65          | 7-1            |

| X2002     | 256 x 8      | 300ns  | 90mA   | 55mA    | 100,000 | 28     | A        | •       | • |    | 1-65          | 7-1            |

| X2002I-20 | 256 x 8      | 200ns  | 110mA  | 70mA    | 100,000 | 28     | В        | •       | • |    | 1-65          | 7-1            |

| X2002I-25 | 256 x 8      | 250ns  | 110mA  | 70mA    | 100,000 | 28     | В        | •       | • |    | 1-65          | 7-1            |

| X2002I    | 256 x 8      | 300ns  | 110mA  | 70mA    | 100,000 | 28     | В        | •       | • |    | 1-65          | 7-1            |

| X2004-20  | 512 x 8      | 200ns  | 100mA  | 55mA    | 100,000 | 28     | A        | •       | • | •  | 1-73          | 7-1            |

| X2004-25  | 512 x 8      | 250ns  | 100mA  | 55mA    | 100,000 | 28     | A        | •       | • | •  | 1-73          | 7-1            |

| X2004     | 512 x 8      | 300ns  | 100mA  | 55mA    | 100,000 | 28     | A        | •       | • | •  | 1-73          | 7-1            |

| X2004I-20 | 512 x 8      | 200ns  | 120mA  | 90mA    | 100,000 | 28     | В        | •       | • | •  | 1-73          | 7-1            |

| X2004I-25 | 512 x 8      | 250ns  | 120mA  | 90mA    | 100,000 | 28     | В        | •       | • | •  | 1-73          | 7-1            |

| X2004I    | 512 x 8      | 300ns  | 120mA  | 90mA    | 100,000 | 28     | В        | •       | • | •  | 1-73          | 7-1            |

| X2004M-25 | 512 x 8      | 250ns  | 120mA  | 90mA    | 100,000 | 28     | С        |         | • | •  | 1-81          | 7-1            |

| X2004M    | 512 x 8      | 300ns  | 120mA  | 90mA    | 100,000 | 28     | С        |         | • | •  | 1-81          | 7-1            |

$A = Commercial = 0^{\circ} \text{ to } +70^{\circ}\text{C}. \\ B = Industrial = -40^{\circ} \text{ to } +85^{\circ}\text{C}. \\ C = Military = -55^{\circ} \text{ to } +125^{\circ}\text{C}.$

P = Plastic DIP D = Cerdip E = Ceramic LCC

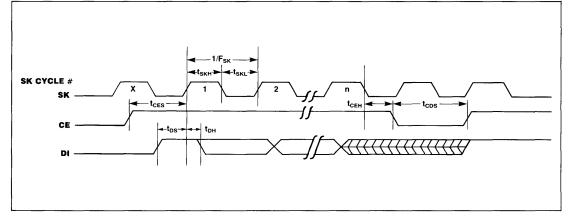

#### SERIAL NOVRAMs

| Part      | Organ-  | Cik.  |        | Power   |       | Store   | No. of | Temp.    | Package |   | ge | Data<br>Sheet | Order<br>Info. |

|-----------|---------|-------|--------|---------|-------|---------|--------|----------|---------|---|----|---------------|----------------|

| Number    | ization | Freq. | Active | Standby | Sleep | Cycles  | Pins   | Range(s) | Ρ       | D | E  | Page #        | Page #         |

| X2444     | 16 x 16 | 1MHz  | 15mA   | 10mA    | 7mA   | 10,000  | 8      | A        | •       | • |    | 2-1           | 7-2            |

| X2444/10  | 16 x 16 | 1MHz  | 15mA   | 10mA    | 7mA   | 100,000 | 8      | A        | •       | • |    | 2-1           | 7-2            |

| X2444I    | 16 x 16 | 1MHz  | 25mA   | 15mA    | 10mA  | 10,000  | 8      | В        | •       | • |    | 2-1           | 7-2            |

| X2444I/10 | 16 x 16 | 1MHz  | 25mA   | 15mA    | 10mA  | 100,000 | 8      | В        | •       | • |    | 2-1           | 7-2            |

| X2444M    | 16 x 16 | 1MHz  | 25mA   | 15mA    | 10mA  | 10,000  | 8      | С        | •       | • |    | 2-9           | 7-2            |

| X2444M/10 | 16 x 16 | 1MHz  | 25mA   | 15mA    | 10mA  | 100,000 | 8      | С        | ٠       | • |    | 2-9           | 7-2            |

#### SERIAL E<sup>2</sup>PROMs

| Part   | Organ-   | Page<br>Size | Cik.   | Po     | wer     | No. of | Temp.    | Pa | acka | ge | Data<br>Sheet | Order<br>Info. |  |

|--------|----------|--------------|--------|--------|---------|--------|----------|----|------|----|---------------|----------------|--|

| Number | ization  | (#Bytes)     | Freq.  | Active | Standby | Pins   | Range(s) | Ρ  | D    | Е  | Page #        | Page #         |  |

| X2404  | 512 x 8  | 8            | 100KHz | 20mA   | 15mA    | 8      | A        | ٠  | •    |    | 2-17          | 7-3            |  |

| X2404I | 512 x 8  | 8            | 100KHz | 20mA   | 15mA    | 8      | В        | ٠  | •    |    | 2-17          | 7-3            |  |

| X2404M | 512 x 8  | 8            | 100KHz | 20mA   | 15mA    | 8      | C        | ٠  | •    |    | 2-27          | 7-3            |  |

| X24C04 | 512 x 8  | 8            | 100KHz | 2mA    | 50µA    | 8      | A, B     | •  | •    |    | 2-37          | 7-3            |  |

| X24C16 | 2048 x 8 | 8            | 100KHz | 2mA    | 50µA    | 8      | А, В     | ٠  | •    |    | 2-45          | 7-3            |  |

$\begin{aligned} \mathsf{A} &= \mathsf{Commercial} = 0^\circ \ \mathsf{to} + 70^\circ \mathsf{C}. \\ \mathsf{B} &= \mathsf{Industrial} = -40^\circ \ \mathsf{to} + 85^\circ \mathsf{C}. \\ \mathsf{C} &= \mathsf{Military} = -55^\circ \ \mathsf{to} + 125^\circ \mathsf{C}. \end{aligned}$

P = Plastic DIP D = Cerdip E = Ceramic LCC

#### 4K E<sup>2</sup>PROMs

| Part       | Organ-  | Page<br>Size | Access | Por    | wer     | No. of | Temp.    | Ра | ncka | ge | Data<br>Sheet | Order<br>Info. |

|------------|---------|--------------|--------|--------|---------|--------|----------|----|------|----|---------------|----------------|

| Number     | ization | (#Bytes)     | Time   | Active | Standby | Pins   | Range(s) | Ρ  | D    | E  | Page #        | Page #         |

| X2804A-25  | 512 x 8 | N/A          | 250ns  | 80mA   | 50mA    | 24     | А        | •  | •    |    | 3-1           | 7-4            |

| X2804A     | 512 x 8 | N/A          | 300ns  | 80mA   | 50mA    | 24     | А        | •  | ٠    |    | 3-1           | 7-4            |

| X2804A-35  | 512 x 8 | N/A          | 350ns  | 80mA   | 50mA    | 24     | А        | •  | ٠    |    | 3-1           | 7-4            |

| X2804A-45  | 512 x 8 | N/A          | 450ns  | 80mA   | 50mA    | 24     | А        | ٠  | ٠    |    | 3-1           | 7-4            |

| X2804AI-25 | 512 x 8 | N/A          | 250ns  | 100mA  | 60mA    | 24     | В        | •  | •    |    | 3-1           | 7-4            |

| X2804AI    | 512 x 8 | N/A          | 300ns  | 100mA  | 60mA    | 24     | В        | •  | •    |    | 3-1           | 7-4            |

| X2804AI-35 | 512 x 8 | N/A          | 350ns  | 100mA  | 60mA    | 24     | В        | ٠  | •    |    | 3-1           | 7-4            |

| X2804AI-45 | 512 x 8 | N/A          | 450ns  | 100mA  | 60mA    | 24     | В        | ٠  | ٠    |    | 3-1           | 7-4            |

| X2804AM    | 512 x 8 | N/A          | 300ns  | 100mA  | 60mA    | 24     | С        |    | •    |    | 3-7           | 7-4            |

| X2804AM-35 | 512 x 8 | N/A          | 350ns  | 100mA  | 60mA    | 24     | С        |    | ٠    |    | 3-7           | 7-4            |

| X2804AM-45 | 512 x 8 | N/A          | 450ns  | 100mA  | 60mA    | 24     | С        |    | ٠    |    | 3-7           | 7-4            |

#### 16K E<sup>2</sup>PROMs

| Part       | Organ-   | Page<br>Size | Access | Power No. of Tem |         | Temp. | Pa       | Package |   | Data<br>Sheet | Order<br>Info. |        |

|------------|----------|--------------|--------|------------------|---------|-------|----------|---------|---|---------------|----------------|--------|

| Number     | ization  | (#Bytes)     | Time   | Active           | Standby | Pins  | Range(s) | Ρ       | D | Ε             | Page #         | Page # |

| X2816A-25  | 2048 x 8 | N/A          | 250ns  | 110mA            | 50mA    | 24    | А        | •       | • | •             | 3-13           | 7-4    |

| X2816A     | 2048 x 8 | N/A          | 300ns  | 110mA            | 50mA    | 24    | А        | •       | • | •             | 3-13           | 7-4    |

| X2816A-35  | 2048 x 8 | N/A          | 350ns  | 110mA            | 50mA    | 24    | А        | ٠       | • | •             | 3-13           | 7-4    |

| X2816A-45  | 2048 x 8 | N/A          | 450ns  | 110mA            | 50mA    | 24    | A        | •       | • | •             | 3-13           | 7-4    |

| X2816AI-25 | 2048 x 8 | N/A          | 250ns  | 140mA            | 60mA    | 24    | В        |         | • | ٠             | 3-13           | 7-4    |

| X2816AI    | 2048 x 8 | N/A          | 300ns  | 140mA            | 60mA    | 24    | В        | •       | • | •             | 3-13           | 7-4    |

| X2816AI-35 | 2048 x 8 | N/A          | 350ns  | 140mA            | 60mA    | 24    | В        | ٠       | • | •             | 3-13           | 7-4    |

| X2816AI-45 | 2048 x 8 | N/A          | 450ns  | 140mA            | 60mA    | 24    | В        | ٠       | • | •             | 3-13           | 7-4    |

| X2816AM    | 2048 x 8 | N/A          | 300ns  | 140mA            | 60mA    | 24    | С        |         | • | •             | 3-19           | 7-4    |

| X2816AM-35 | 2048 x 8 | N/A          | 350ns  | 140mA            | 60mA    | 24    | С        |         | • | •             | 3-19           | 7-4    |

| X2816AM-45 | 2048 x 8 | N/A          | 450ns  | 140mA            | 60mA    | 24    | С        |         | • | •             | 3-19           | 7-4    |

| X2816B     | 2048 x 8 | 32           | 150ns  | 60mA             | 30mA    | 24    | А, В     | •       | • | •             | 3-25           | 7-4    |

| X2816H     | 2048 x 8 | 32           | 45ns   | 80mA             | —       | 24    | А, В     | ٠       | • | •             | 3-31           | 7-4    |

| X2616      | 2048 x 8 | N/A          | 45ns   | 80mA             | _       | 24*   | A, B     | •       | • | •             | 3-83           | 7-4    |

N/A = Not Applicable \*Industry Standard Bipolar PROM Pinout

$A = Commercial = 0^{\circ} \text{ to } +70^{\circ}\text{ C}. \\ B = Industrial = -40^{\circ} \text{ to } +85^{\circ}\text{ C}. \\ C = Military = -55^{\circ} \text{ to } +125^{\circ}\text{ C}.$

P = Plastic DIP

D = Cerdip E = Ceramic LCC

#### 64K E<sup>2</sup>PROMs

| Part       | Organ-   | Page<br>Size | Access | Po     | wer     | No. of | Temp.    | Packag |   | ge | Data<br>Sheet | Order<br>Info. |

|------------|----------|--------------|--------|--------|---------|--------|----------|--------|---|----|---------------|----------------|

| Number     | ization  | (#Bytes)     | Time   | Active | Standby | Pins   | Range(s) | Ρ      | D | E  | Page #        | Page #         |

| X2864A-20  | 8192 x 8 | 16           | 200ns  | 140mA  | 60mA    | 28     | А        | ٠      | • | ٠  | 3-33          | 7-4            |

| X2864A-25  | 8192 x 8 | 16           | 250ns  | 140mA  | 60mA    | 28     | А        | •      | • | •  | 3-41          | 7-4            |

| X2864A     | 8192 x 8 | 16           | 300ns  | 140mA  | 60mA    | 28     | А        | ٠      | • | ٠  | 3-41          | 7-4            |

| X2864A-35  | 8192 x 8 | 16           | 350ns  | 140mA  | 60mA    | 28     | А        | ٠      | ٠ | ٠  | 3-41          | 7-4            |

| X2864A-45  | 8192 x 8 | 16           | 450ns  | 140mA  | 60mA    | 28     | А        | ٠      | • | ٠  | 3-41          | 7-4            |

| X2864AI-20 | 8192 x 8 | 16           | 200ns  | 140mA  | 70mA    | 28     | В        | ٠      | ٠ | ٠  | 3-33          | 7-4            |

| X2864AI-25 | 8192 x 8 | 16           | 250ns  | 140mA  | 70mA    | 28     | В        | •      | • | ٠  | 3-41          | 7-4            |

| X2864AI    | 8192 x 8 | 16           | 300ns  | 140mA  | 70mA    | 28     | В        | ٠      | • | •  | 3-41          | 7-4            |

| X2864AI-35 | 8192 x 8 | 16           | 350ns  | 140mA  | 70mA    | 28     | В        | ٠      | ٠ | ٠  | 3-41          | 7-4            |

| X2864AI-45 | 8192 x 8 | 16           | 450ns  | 140mA  | 70mA    | 28     | В        | ٠      | • | ٠  | 3-41          | 7-4            |

| X2864AM-25 | 8192 x 8 | 16           | 250ns  | 140mA  | 70mA    | 28     | С        |        | • | ٠  | 3-49          | 7-4            |

| X2864AM    | 8192 x 8 | 16           | 300ns  | 140mA  | 70mA    | 28     | С        |        | ٠ | ٠  | 3-57          | 7-4            |

| X2864AM-35 | 8192 x 8 | 16           | 350ns  | 140mA  | 70mA    | 28     | С        |        | • | •  | 3-57          | 7-4            |

| X2864AM-45 | 8192 x 8 | 16           | 450ns  | 140mA  | 70mA    | 28     | С        |        | • | ٠  | 3-57          | 7-4            |

| X2864B     | 8192 x 8 | 32           | 150ns  | 80mA   | 30mA    | 28     | А, В     | •      | • | ٠  | 3-65          | 7-4            |

| X2864H     | 8192 x 8 | 32           | 45ns   | 100mA  | _       | 28     | А, В     | •      | • | ٠  | 3-71          | 7-4            |

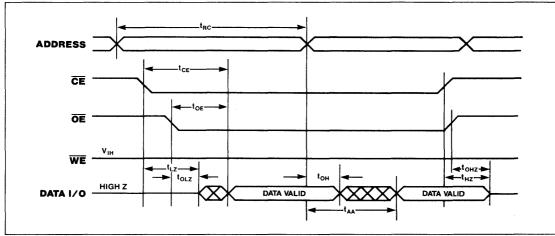

| X28C64     | 8192 x 8 | 32           | 150ns  | 60mA   | 200µA   | 28     | А, В     | ٠      | • | ٠  | 3-73          | 7-4            |

| X2664      | 8192 x 8 | N/A          | 45ns   | 100mA  | —       | 24*    | А, В     | •      | ٠ | •  | 3-85          | 7-4            |

N/A = Not Applicable

\*Industry Standard Bipolar PROM Pinout

#### 256K E<sup>2</sup>PROMs

| Part    | Organ-  | Page<br>Size | Access | Pov    | wer     | No. of | Temp.    | Pa | acka | ge | Data<br>Sheet | Order<br>Info. |

|---------|---------|--------------|--------|--------|---------|--------|----------|----|------|----|---------------|----------------|

| Number  | ization | (#Bytes)     | Time   | Active | Standby | Pins   | Range(s) | Ρ  | D    | Ε  | Page #        | Page #         |

| X28256  | 32K x 8 | 64           | 150ns  | 100mA  | 50mA    | 28     | A, B     | ٠  | •    | •  | 3-75          | 7-4            |

| X28C256 | 32K x 8 | 64           | 150ns  | 80mA   | 200µA   | 28     | A, B     | •  | •    | •  | 3-81          | 7-4            |

$A = Commercial = 0^{\circ} \text{ to } +70^{\circ}\text{ C}. \\ B = Industrial = -40^{\circ} \text{ to } +85^{\circ}\text{ C}. \\ C = Military = -55^{\circ} \text{ to } +125^{\circ}\text{ C}.$

P = Plastic DIP D = Cerdip E = Ceramic LCC

#### E<sup>2</sup>POTENTIOMETERS (E<sup>2</sup>POT<sup>™</sup>)

| Part   | Nominal<br>Wiper | Incremental | Maximum    | No. of | Temp.    | Package |   | e | Data<br>Sheet | Order<br>Info. |

|--------|------------------|-------------|------------|--------|----------|---------|---|---|---------------|----------------|

| Number | Resistance       | Resistance  | Resistance | Pins   | Range(s) | Р       | D | E | Page #        | Page #         |

| X9103  | 40Ω              | 101Ω        | 10KΩ       | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

| X9203  | 40Ω              | 202Ω        | 20ΚΩ       | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

| X9503  | 40Ω              | 505 Ω       | 50KΩ       | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

| X9104  | 40Ω              | 1.01KΩ      | 100KΩ      | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

| X9204  | 40Ω              | 2.02KΩ      | 200KΩ      | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

| X9504  | 40Ω              | 5.05KΩ      | 500KΩ      | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

| X9105  | 40Ω              | 10.1KΩ      | 1MΩ        | 8      | A, B, C  | •       | • |   | 4-1           | 4-2            |

P = Plastic DIP

D = Cerdip E = Ceramic LCC

## TABLE OF CONTENTS

| ection 1 – NOVRAM Data Sheets (See Product Index for sequence)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | v                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ection 2 – Serial I/O Data Sheets<br>(See Product Index for sequence)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | v                                      |

| ection 3 – E <sup>2</sup> PROM Data Sheets<br>(See Product Index for sequence)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | v                                      |

| ection 4 – $E^2POT^{M}$ Data Sheets<br>(See Product Index for sequence)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | v                                      |

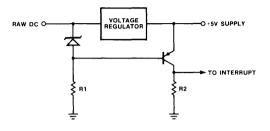

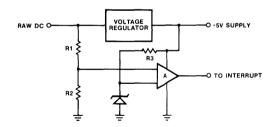

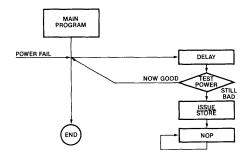

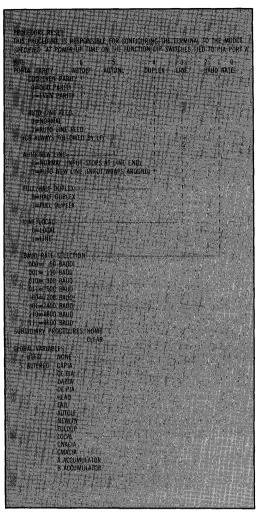

| ection 5 – Applications         Application Notes         AN-101 Xicor NOVRAM Family, Easier Than Ever to Use       5         AN-102 Storing Data in Xicor NOVRAMs During Power Failure       5         AN-103 Xicor Replaces DIP Switches and Trimmers with NOVRAM Memories       5-         AN-104 The World's Easiest-To-Use EEPROMs Are Here       5-2         AN-105 The X2444 Serial NOVRAM Teams Up with the 8051 Microcontroller Family       5-3                                                                                                                                                                                                                                            | -9<br>15<br>23                         |

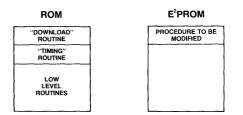

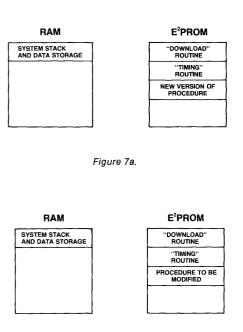

| Application Briefs       Nonvolatile Data Integrity: Inadvertent Write/Store Elimination       5-3         DATA Polling and Page Write Combine to Offer Improved Write       5-4         Timing Characteristics       5-4         X2816A Design Allows Upgrade to X2864A and Beyond       5-4         Replacing DIP Switches with Nonvolatile Technology       5-4         The Nine Most Frequent NOVRAM Questions       5-4         Using DATA Polling in an Interrupt Driven Environment       5-5         E <sup>2</sup> PROM Provides the Solution to Field Alterable Software       5-6         Kicor E <sup>2</sup> PROMs vs. Battery Backed-Up CMOS RAMs Nonvolatile Memory Systems       5-6 | 41<br>44<br>47<br>51<br>55<br>59<br>63 |

| Article Reprints         5-volt-only EE-PROM Mimics static-RAM timing <i>Electronics</i> , June 30, 1982         Understand your application in choosing NOVRAM, EEPROM <i>EDN</i> , May 12, 1983                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                        |

|   | Non-volatile memories keep appliances out of the dark                        | 5-89  |

|---|------------------------------------------------------------------------------|-------|

|   | Uncompromising Features Hi-Lite the 5 Volt E <sup>2</sup> PROM<br>Electro/84 | 5-96  |

|   | The NOVRAM Family: A New Domain of System Possibilities Electro/84           | 5-103 |

|   | Nonvolatile Memory Gives New Life to Old Designs                             | 5-111 |

|   | Save volatile data during power loss                                         | 5-119 |

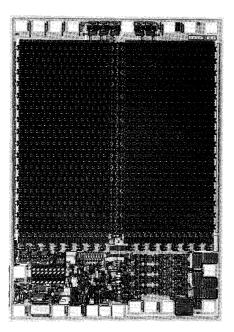

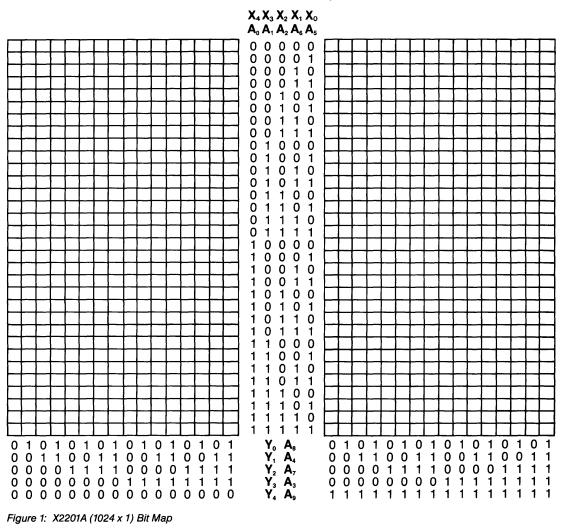

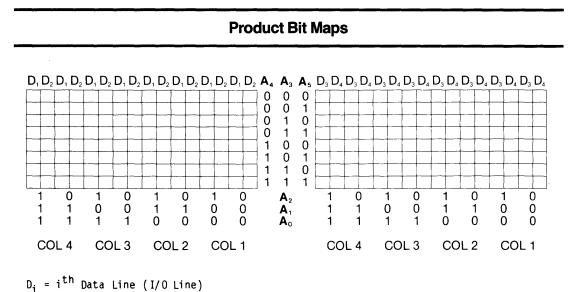

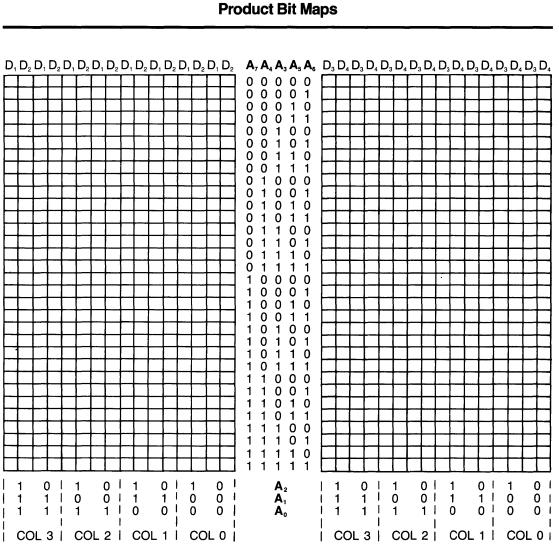

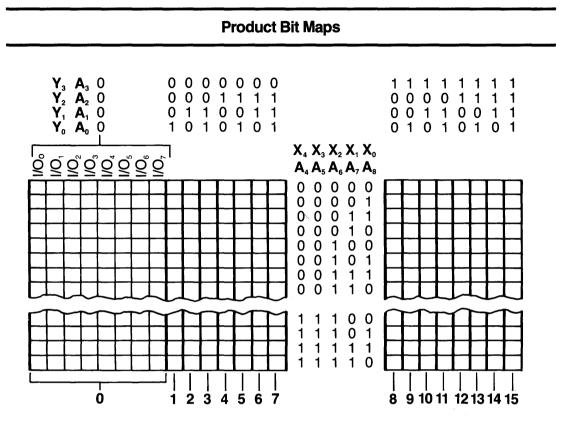

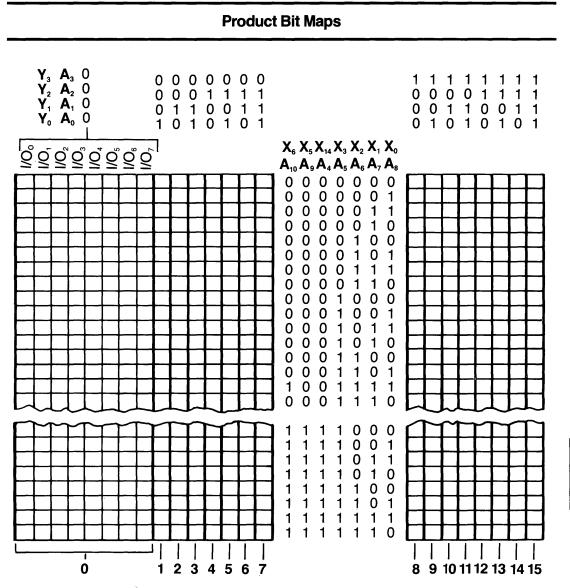

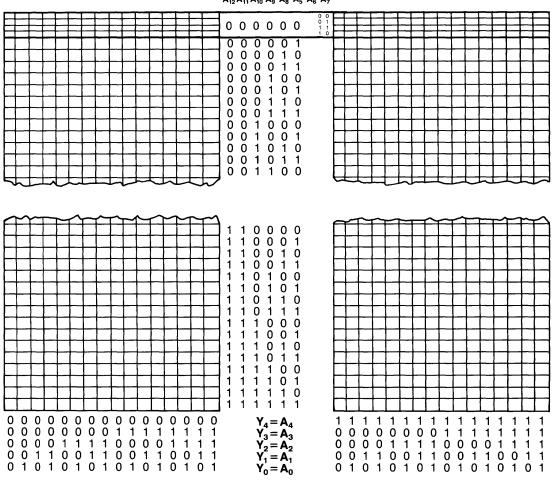

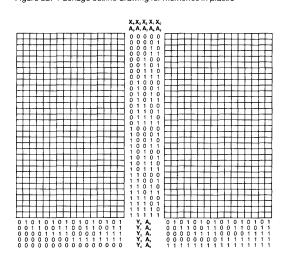

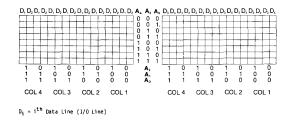

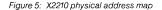

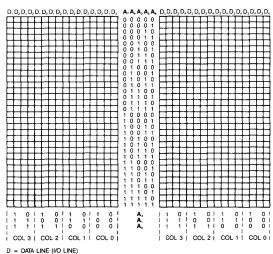

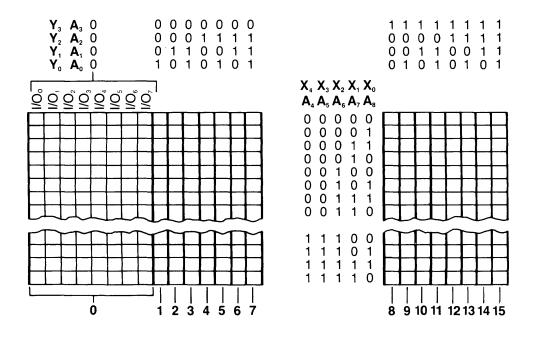

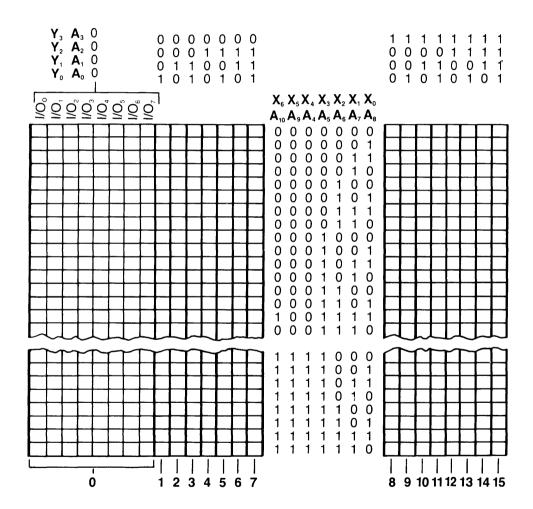

| B | it Maps for Xicor Products                                                   | 5-127 |

## Section 6 - Reliability

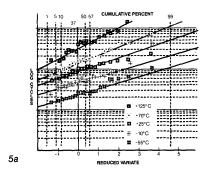

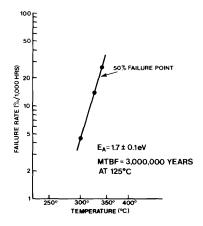

| RR-502A NOVRAM Reliability Report                                      | 6-1  |

|------------------------------------------------------------------------|------|

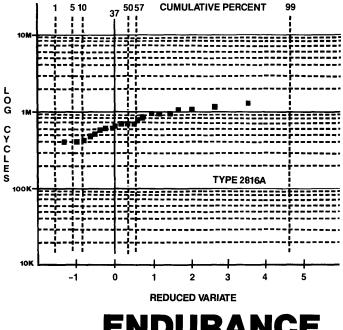

| RR-503 X2816A/04A Preliminary Reliability Summary                      | 6-17 |

| RR-504 Endurance of Xicor E <sup>2</sup> PROMs and NOVRAMs             | 6-31 |

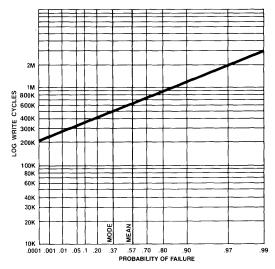

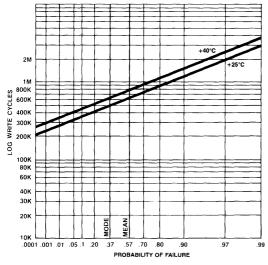

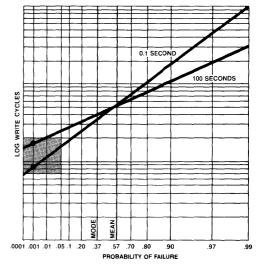

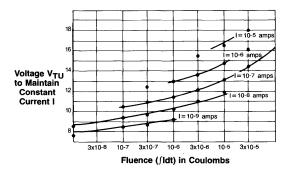

| Determining System Reliability from E <sup>2</sup> PROM Endurance Data | 6-41 |

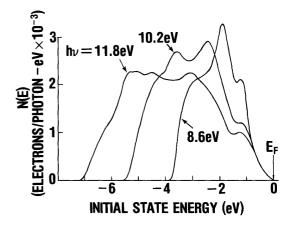

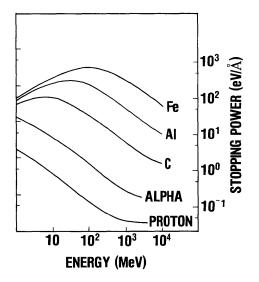

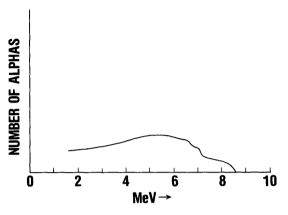

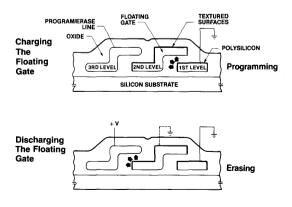

| Radiation-Induced Soft Errors and Floating Gate Memories               | 6-45 |

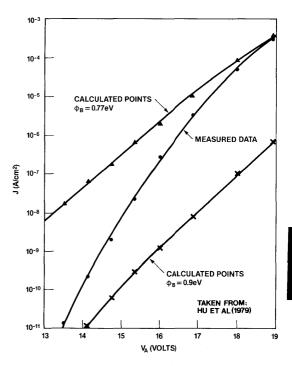

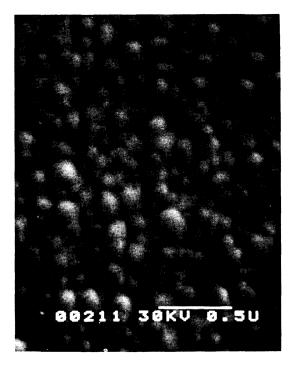

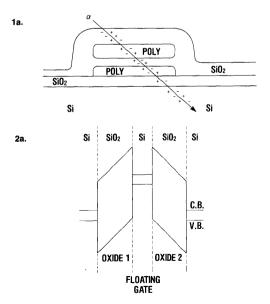

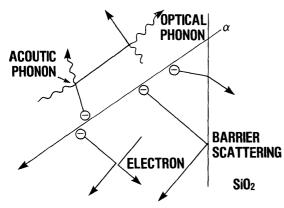

| Endurance Model for Textured-Poly Floating Gate Memories               | 6-51 |

## Section 7 – General Information

| Ordering Information  | 7-1  |

|-----------------------|------|

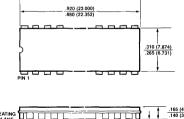

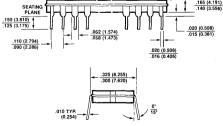

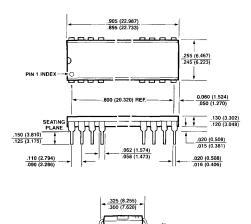

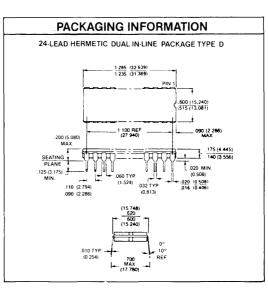

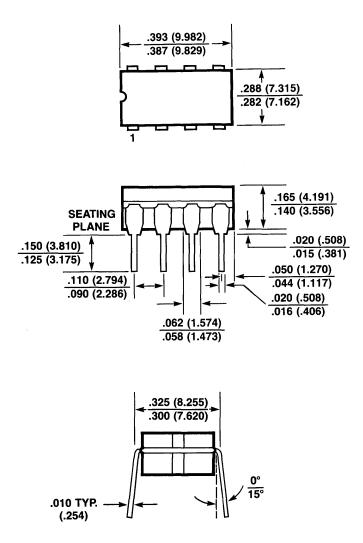

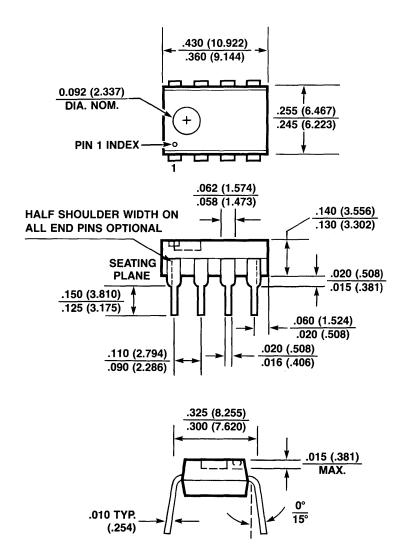

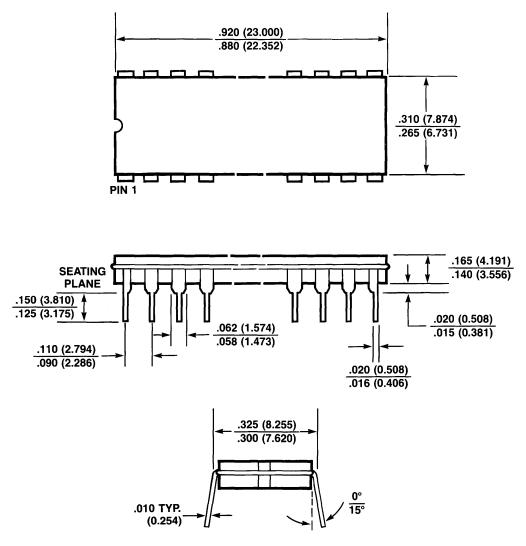

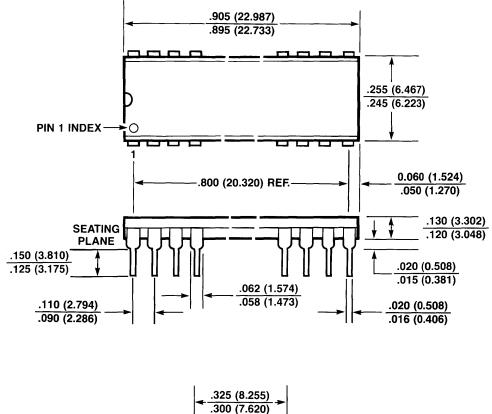

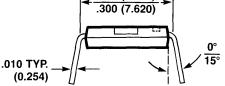

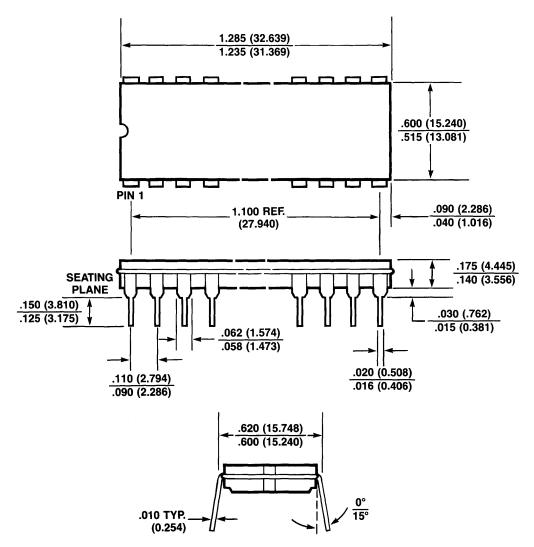

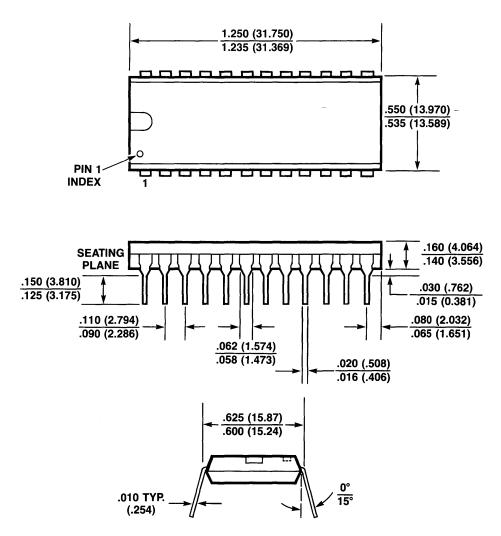

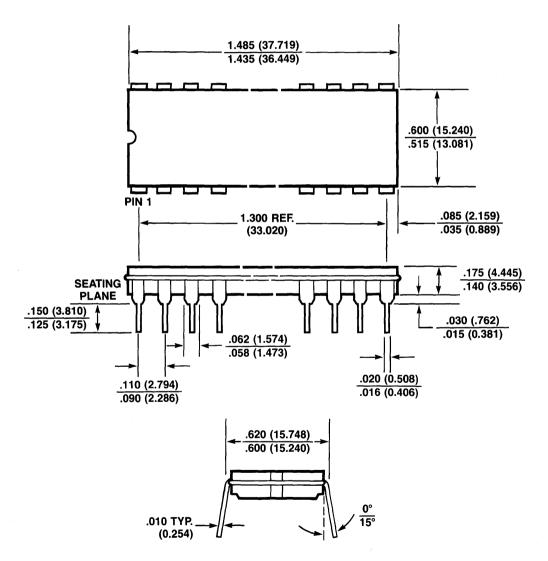

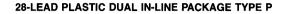

| Packaging Information | 7-6  |

| Sales Offices         | 7-16 |

## **Memory Overview**

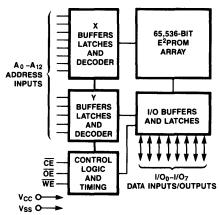

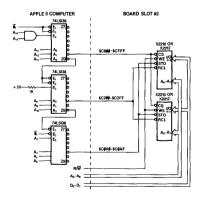

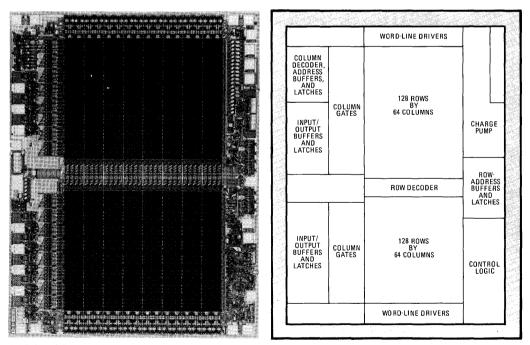

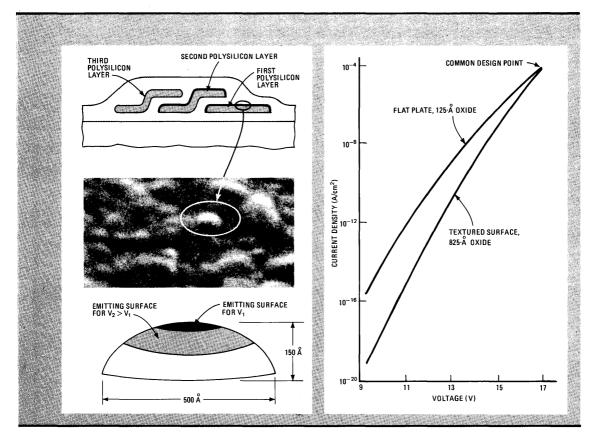

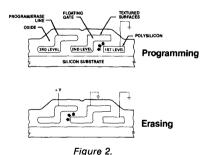

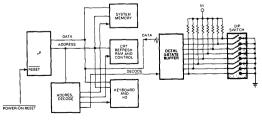

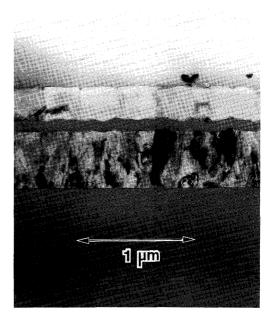

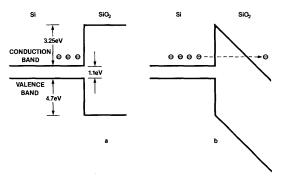

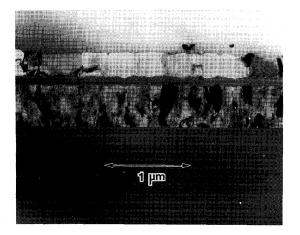

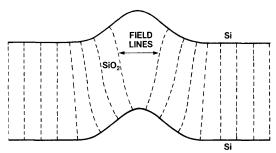

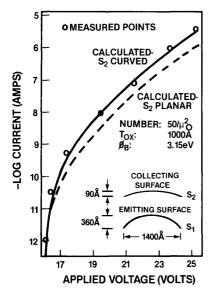

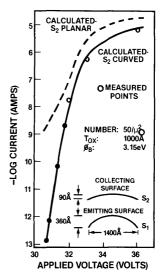

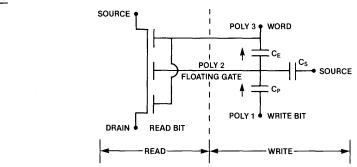

Since its founding, Xicor has developed and placed into production a wide range of system-alterable nonvolatile memory devices. These devices, manufactured with Xicor's proprietary state-of-the-art textured triple-poly floating gate process, are available in a variety of architectures (NOVRAM and E<sup>2</sup>PROM), interfaces (nibble-wide, byte-wide and serial), densities, and speeds. Xicor's success as an innovator and leader in system-alterable nonvolatile memory is affirmed with an *Electronic Product Magazine* Product of the Year award in 1980 and again in 1982 for the first 5-volt only NOVRAM and the first 5-volt only full featured E<sup>2</sup>PROM, respectively.

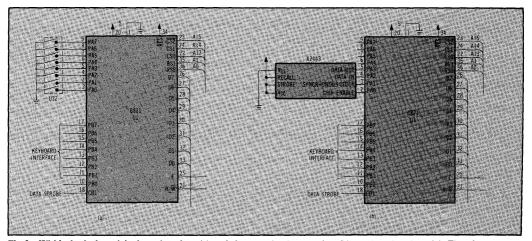

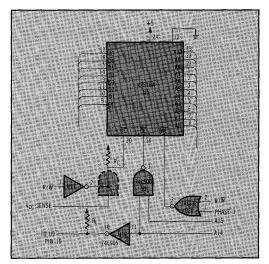

Lower density E<sup>2</sup>PROMs and NOVRAMs have been readily available for a number of years and have provided unique niche applications solutions. Serial devices have replaced DIP switches in a wide range of products that offer user selectable operating parameters. Nibblewide and byte-wide NOVRAMs and E<sup>2</sup>PROMs are being used in instrumentation and industrial control applications to store calibration data and control information. Communications equipment has implemented these same devices to store phone numbers in repertory dialers and antenna positioning equipment. The list of first generation applications goes on at length; however, with the advent of the next generation of higher density E<sup>2</sup>PROM devices, such as the X2864A, the potential applications areas for E<sup>2</sup>PROMs has rapidly expanded.

As designers have gained experience implementing the denser E<sup>2</sup>PROM devices into system memories, they have given Xicor feedback on features they would like. Xicor has listened.

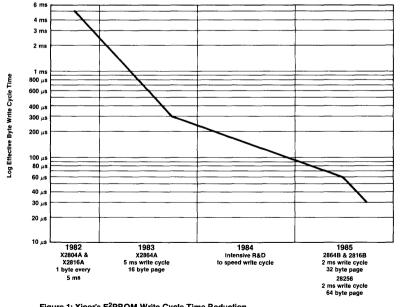

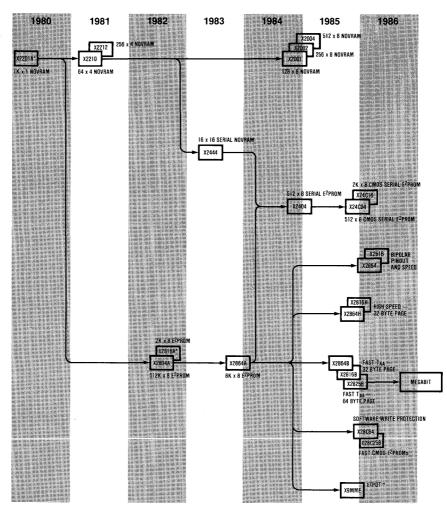

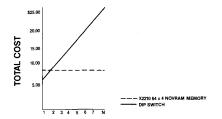

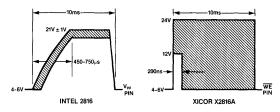

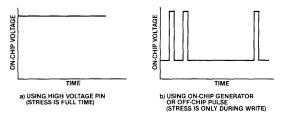

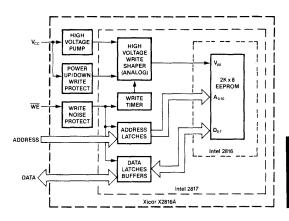

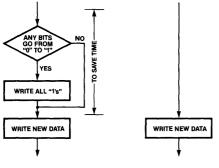

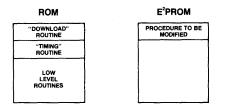

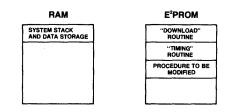

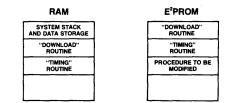

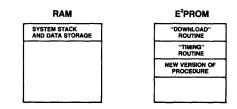

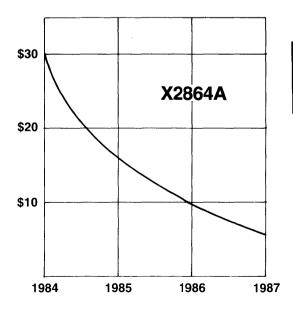

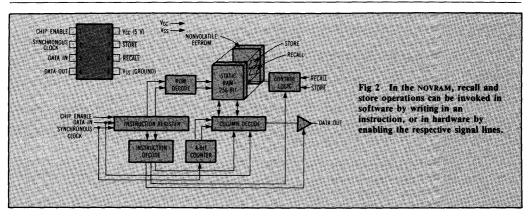

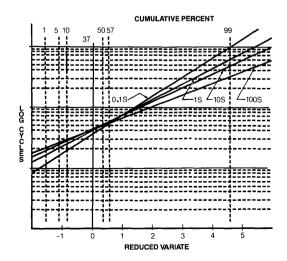

As Figures 1 and 2 illustrate, Xicor's response has been active. The issues addressed by the Xicor design team have been: faster read access time, faster write cycle time (Figure 1), denser memory devices and write protection mechanisms.

Xicor has also implemented added features via software control rather than "dedicated pin" hardware control for optional system use. Xicor is committed to providing solutions that neither hinder nor limit the memory designer's imagination. The products and features shown in Figures 1 and 2 and in the data sheets in this catalog illustrate Xicor's dedication to listening to you, the designer, in providing memory design solutions.

Figure 1: Xicor's E<sup>2</sup>PROM Write Cycle Time Reduction. Effective byte write cycle time is calculated by dividing the device's internal write cycle time by the number of bytes per page.

### Memory Overview

\*Product of the Year Award, *Electronic Product Magazine*.

1980 — First 5 volt only nonvolatile memory, sets new industry standard.

1981 — Expanded 5 volt only NOVRAM family.

- 1982 First 5 volt only E<sup>2</sup>PROM. First E<sup>2</sup>PROM to offer latched address and data setting another industry standard.

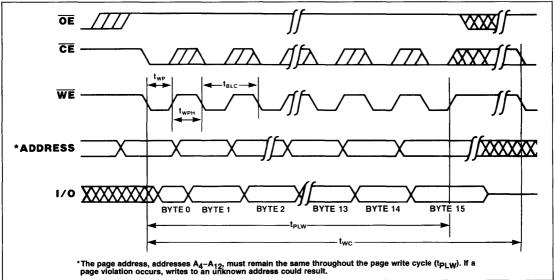

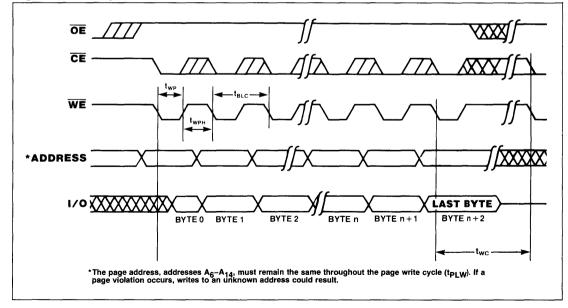

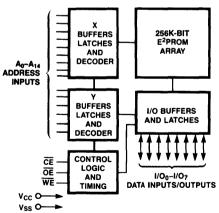

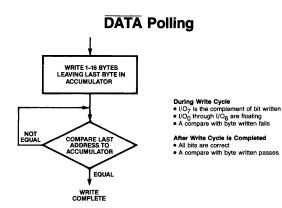

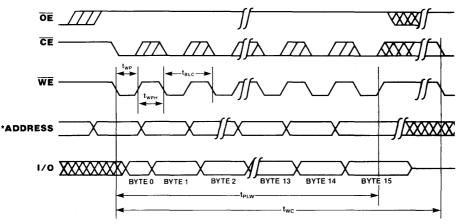

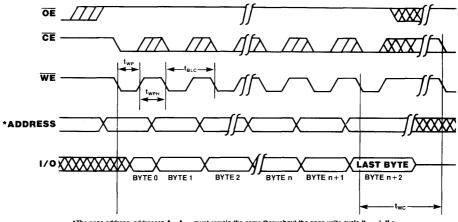

- 1983 First production E<sup>2</sup>PROM to feature page write capability and DATA Polling, becoming de facto industry standard for all E<sup>2</sup>PROMs. First Serial NOVRAM introduced.

- 1984 Expansion of NOVRAM into byte-wide configurations. Introduction of Serial E<sup>2</sup>PROM family.

- 1985 Banner year with introduction of high speed and higher density E<sup>2</sup>PROMs in both NMOS and CMOS technologies.

#### Figure 2: Xicor's Product Evolution.

1

# **NOVRAM\*** Data Sheets

| X2201A        |     | • |       | • | • | • | • | • | • | • • | <br> |   |   |   | • |   |   | • |   | • | • | • |   | • | • |   | • | • | 1-1  |

|---------------|-----|---|-------|---|---|---|---|---|---|-----|------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| X2210A        |     |   |       |   |   |   |   |   | • |     | <br> |   |   |   |   |   |   | • |   |   |   |   |   |   | • |   |   |   | 1-9  |

| X2210, X2210I |     |   | <br>• |   |   | • | • |   |   |     | <br> |   |   |   | • |   |   |   |   |   |   |   | • |   |   |   |   | • | 1-17 |

| X2210M        |     |   |       |   |   |   | • | • |   |     | <br> |   |   |   |   |   | • | • |   | • |   |   |   |   | • |   | • |   | 1-25 |

| X2212A        |     |   |       |   |   |   |   | • | • |     |      | • |   |   |   |   |   | • | • | • | • |   |   | • |   | • | • |   | 1-33 |

| X2212, X2212I | • • |   |       |   | • |   | • | • |   |     |      |   |   |   |   | • |   |   | • |   | • |   |   | • |   | • | • |   | 1-41 |

| X2212M        |     |   |       |   | • |   |   |   |   |     | <br> |   |   |   |   |   |   |   |   |   | • |   |   |   |   |   |   |   | 1-49 |

| X2001, X2001I |     |   |       |   |   |   |   |   | • |     | <br> |   |   | • |   |   |   |   |   | • | • |   |   |   | • | • |   |   | 1-57 |

| X2002, X2002I | •   |   |       |   | • |   | • | • |   |     |      |   | • | • |   |   |   | • | • |   |   |   |   | • |   | • | • |   | 1-65 |

| X2004, X2004I |     | • |       |   | • | • |   | • | • |     |      |   | • | • |   |   |   |   | • |   |   |   |   |   |   | • | • |   | 1-73 |

| X2004M        |     |   |       |   |   |   |   |   |   |     | <br> |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 1-81 |

1K Commercial

X2201A

Nonvolatile Static RAM

## 1024 x 1 Bit

- Single 5 Volt Supply

- Fully TTL Compatible

- Infinite E<sup>2</sup>PROM Array Recall, RAM Read and Write Cycles

- Access Time of 300ns Max.

- Nonvolatile Store Inhibit: V<sub>CC</sub> = 3v Typical

- 100 Year Data Retention

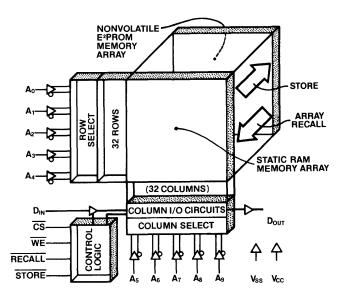

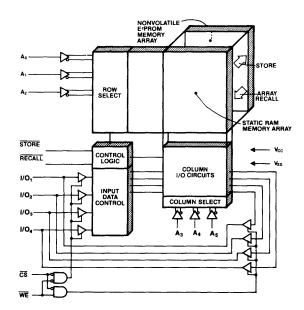

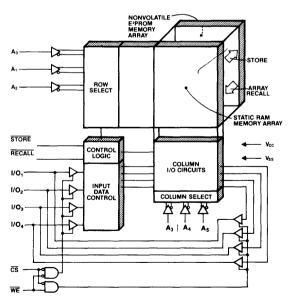

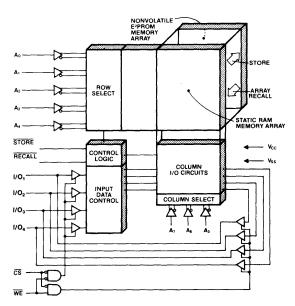

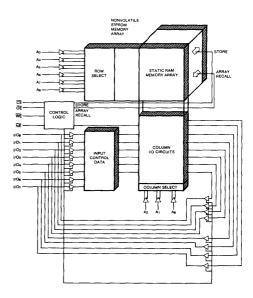

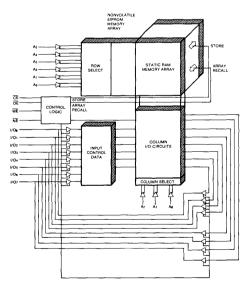

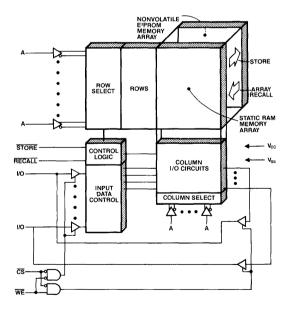

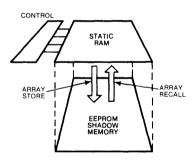

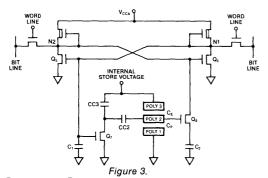

#### DESCRIPTION

FEATURES

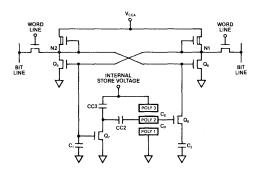

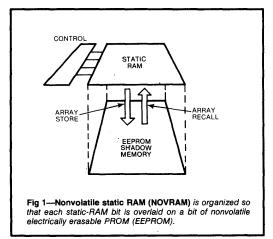

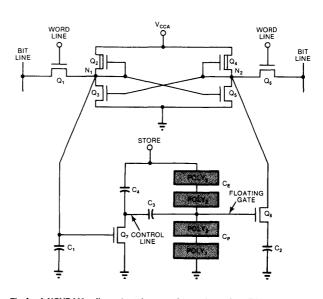

The Xicor X2201A is a 1024 x 1 NOVRAM\* featuring a high-speed static RAM overlaid bit-for-bit with a non-volatile  $E^2$ PROM. The X2201A is fabricated with the same

reliable N-channel floating gate MOS technology used in all Xicor 5 volt nonvolatile memories.

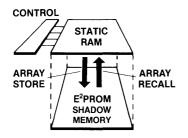

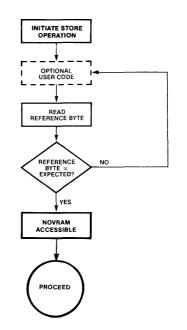

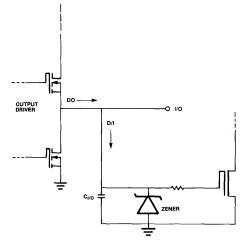

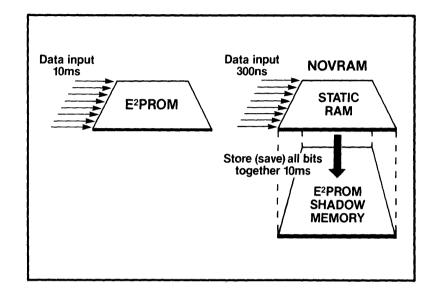

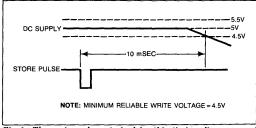

The NOVRAM design allows data to be easily transferred from RAM to E<sup>2</sup>PROM (store) and from E<sup>2</sup>PROM to RAM (recall). The store operation is completed in 10ms or less and the recall is typically completed in 1 $\mu$ s.

Xicor NOVRAMs are designed for unlimited write operations to RAM, either from the host or recalls from  $E^2PROM$ . The  $E^2PROM$  array is designed for a minimum 10,000 store cycles. Data retention is specified to be greater than 100 years.

\*NOVRAM is Xicor's nonvolatile static RAM device.

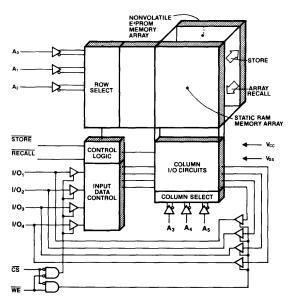

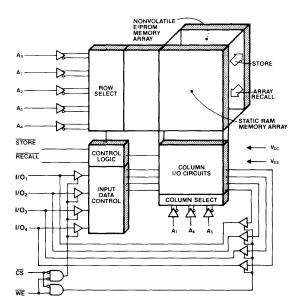

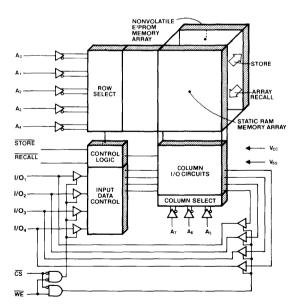

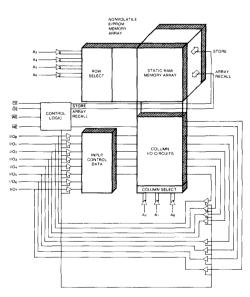

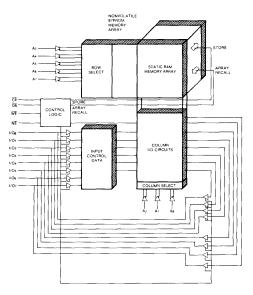

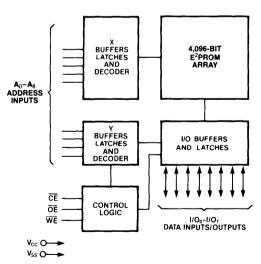

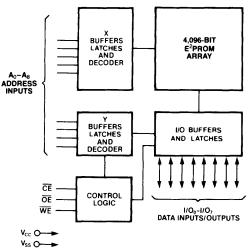

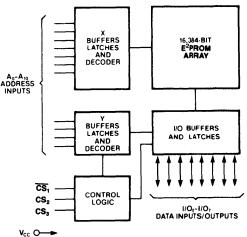

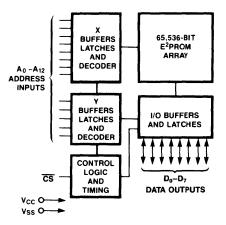

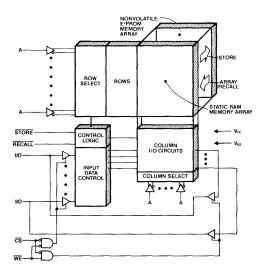

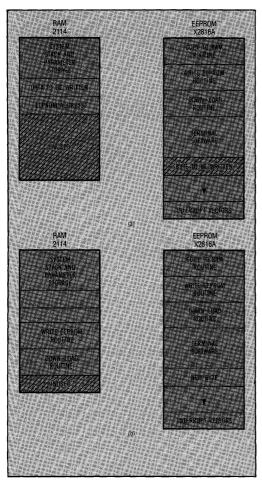

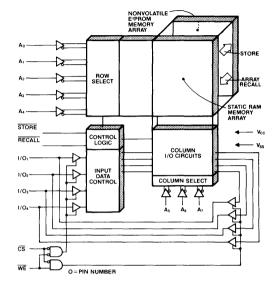

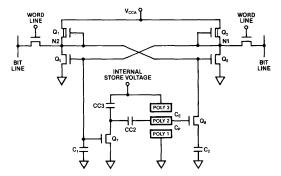

#### FUNCTIONAL DIAGRAM

**PIN CONFIGURATION**

#### PIN NAMES

| A <sub>0</sub> -A <sub>9</sub><br>D <sub>IN</sub><br>D <sub>DUT</sub><br>WE<br>CS<br>ARRAY<br>STORE<br>V <sub>CC</sub> | Address Inputs<br>Data Input<br>Data Out<br>Write Enable<br>Chip Select<br>Array Recall<br>Store<br>+5V |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub>                                                                                                        | +5V                                                                                                     |

| V <sub>ss</sub>                                                                                                        | Ground                                                                                                  |

|                                                                                                                        |                                                                                                         |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias10°C to +85°C |

|-------------------------------------|

| Storage Temperature65°C to +150°C   |

| Voltage on any Pin with             |

| Respect to Ground1.0V to +7V        |

| D.C. Output Current                 |

| Lead Temperature (Soldering,        |

| 10 Seconds)                         |

#### **\*COMMENT**

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### D.C. OPERATING CHARACTERISTICS

$T_A$  = 0°C to +70°C,  $V_{CC}$  = +5V ±10%, unless otherwise specified.

|                 |                        | Li   | mits                 |       |                                                 |  |

|-----------------|------------------------|------|----------------------|-------|-------------------------------------------------|--|

| Symbol          | Parameter              | Min. | Max.                 | Units | Test Conditions                                 |  |

| I <sub>cc</sub> | Power Supply Current   |      | 60                   | mA    | All Inputs = $V_{CC}$<br>I <sub>VO</sub> = 0 mA |  |

| I <sub>LI</sub> | Input Load Current     |      | 10                   | μA    | $V_{IN} = GND$ to $V_{CC}$                      |  |

| ILO             | Output Leakage Current |      | 10                   | μA    | $V_{OUT} = GND$ to $V_{CC}$                     |  |

| VIL             | Input Low Voltage      | -1.0 | 0.8                  | V     |                                                 |  |

| VIH             | Input High Voltage     | 2.0  | V <sub>cc</sub> +1.0 | V     |                                                 |  |

| V <sub>OL</sub> | Output Low Voltage     |      | 0.4                  | V     | $I_{OL} = 4.2 \text{ mA}$                       |  |

| V <sub>он</sub> | Output High Voltage    | 2.4  |                      | v     | I <sub>он</sub> = −2 mA                         |  |

#### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

| Symbol                          | Test                     | Max. | Unit | Conditions     |

|---------------------------------|--------------------------|------|------|----------------|

| C <sub>I/O</sub> <sup>(1)</sup> | Input/Output Capacitance | 8    | pF   | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance        | 6    | рF   | $V_{IN} = 0V$  |

Note: (1) This parameter is periodically sampled and not 100% tested.

#### A.C. CONDITIONS OF TEST

| Input Pulse Levels                | 0 to 3.0 Volts                          |

|-----------------------------------|-----------------------------------------|

| Input Rise and<br>Fall Times      | 10 nsec                                 |

| Input and Output<br>Timing Levels | 1.5 Volts                               |

| Output Load                       | 1 TTL Gate and $C_{L} = 100 \text{ pF}$ |

#### MODE SELECTION

|    |                   | Inputs Input Output |       |                 |                                    |

|----|-------------------|---------------------|-------|-----------------|------------------------------------|

| CS | WE ARRAY RECALL S |                     | STORE | I/O             | Mode                               |

| н  | X                 | н                   | н     | Output High Z   | Not Selected <sup>(2)</sup>        |

| L  | н                 | Н                   | н     | Output Data     | Read RAM                           |

| L  | L                 | н                   | н     | Input Data High | Write "1" RAM                      |

| L  | L                 | Н                   | н     | Input Data Low  | Write "0" RAM                      |

| X  | н                 | L                   | н     | Output High Z   | Array Recall                       |

| н  | X                 | L                   | н     | Output High Z   | Array Recall                       |

| х  | н                 | Н                   | L     | Output High Z   | Nonvolatile Storing <sup>(3)</sup> |

| н  | X                 | Н                   | L     | Output High Z   | Nonvolatile Storing <sup>(3)</sup> |

Notes: (2) Chip is deselected but may be automatically completing a store cycle.

(3) STORE = L is required only to initiate the store cycle, after which the store cycle will be automatically completed (STORE = X).

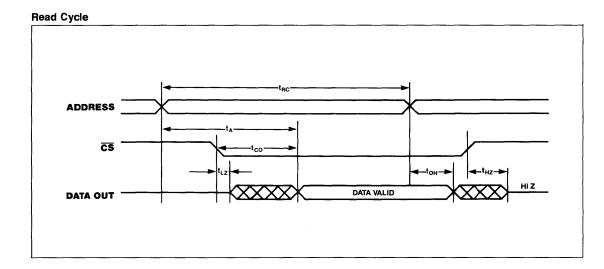

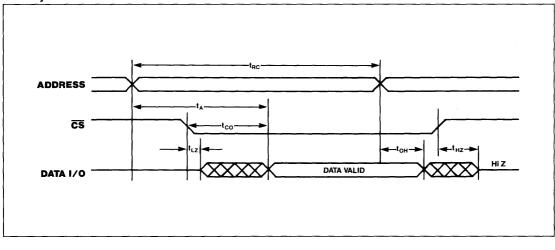

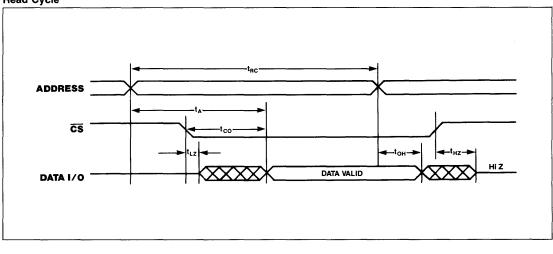

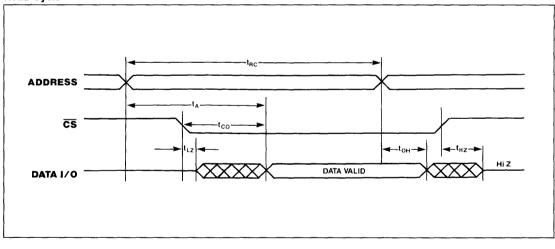

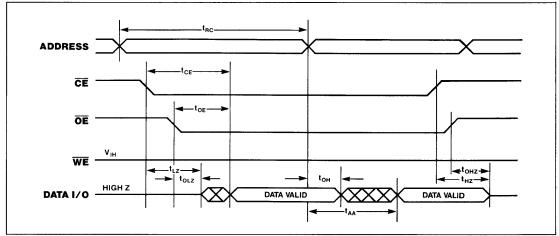

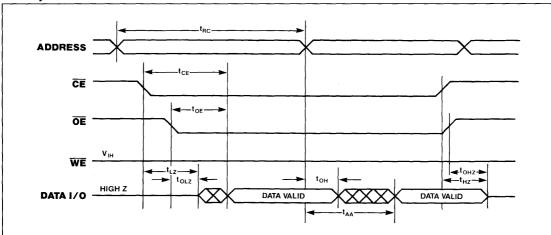

#### A.C. CHARACTERISTICS

$T_{A}$  = 0°C to +70°C,  $V_{CC}$  = +5V ±10%, unless otherwise specified.

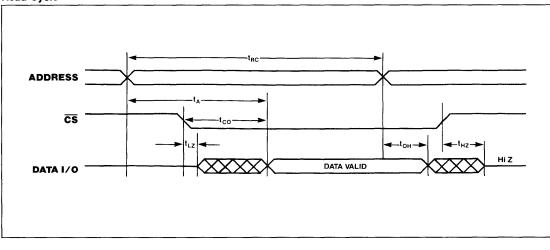

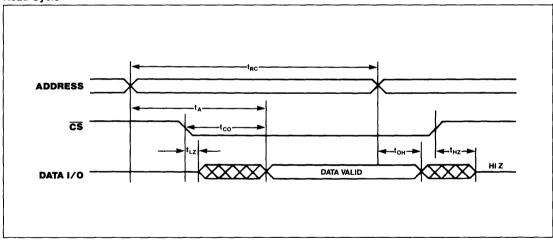

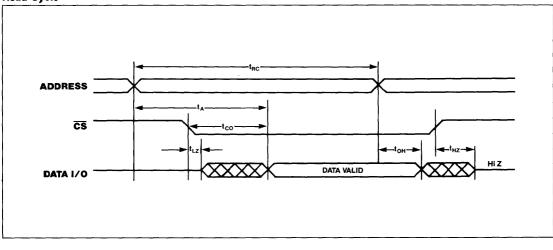

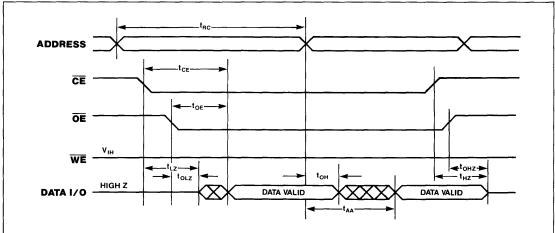

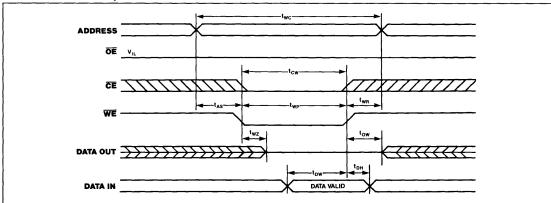

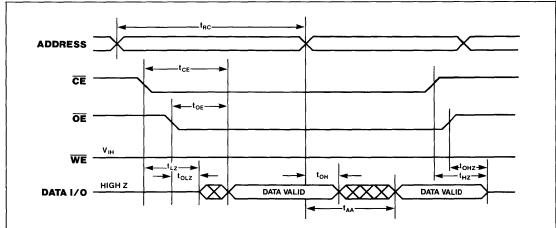

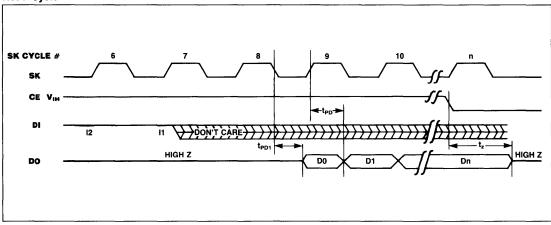

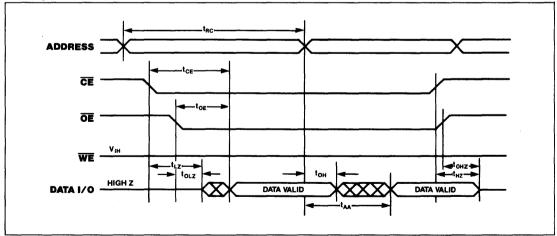

#### **Read Cycle Limits**

| Symbol          | Parameter                         | Min. | Max. | Units |

|-----------------|-----------------------------------|------|------|-------|

| t <sub>RC</sub> | Read Cycle Time                   | 300  |      | ns    |

| t <sub>A</sub>  | Access Time                       |      | 300  | ns    |

| t <sub>co</sub> | Chip Select to Output Valid       |      | 200  | ns    |

| t <sub>он</sub> | Output Hold from Address Change   | 50   |      | ns    |

| t <sub>LZ</sub> | Chip Select to Output in Low Z    | 10   |      | ns    |

| t <sub>HZ</sub> | Chip Deselect to Output in High Z | 10   | 100  | ns    |

## X2201A

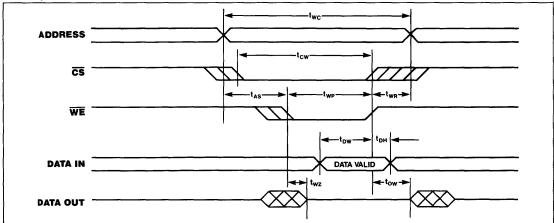

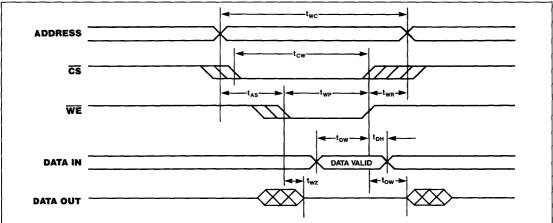

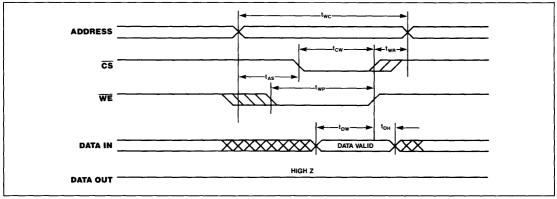

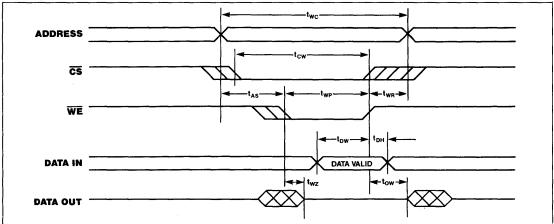

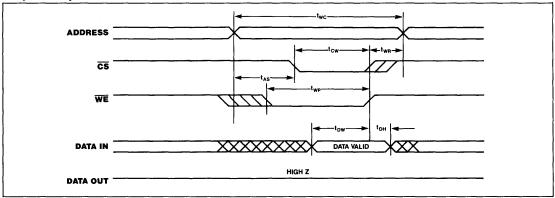

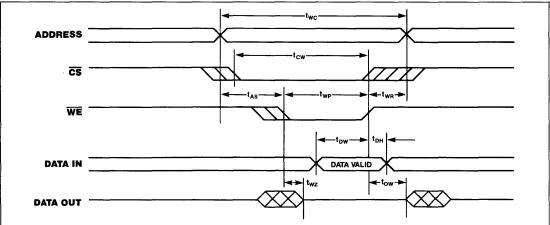

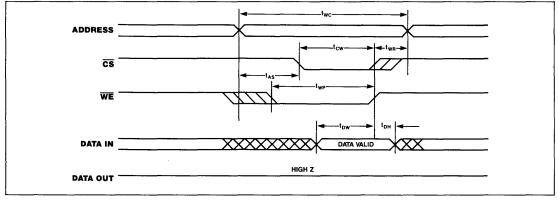

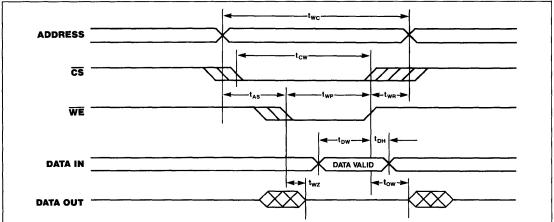

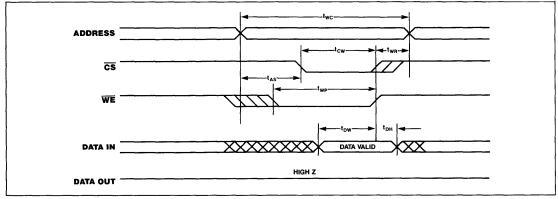

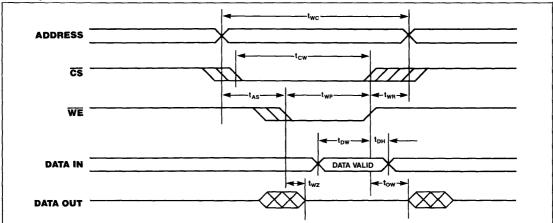

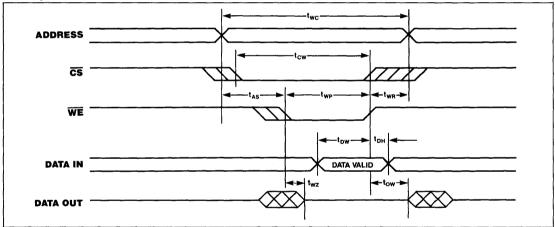

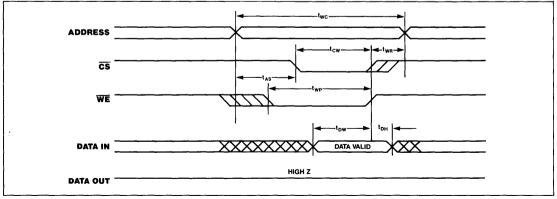

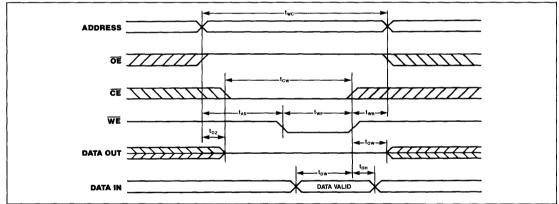

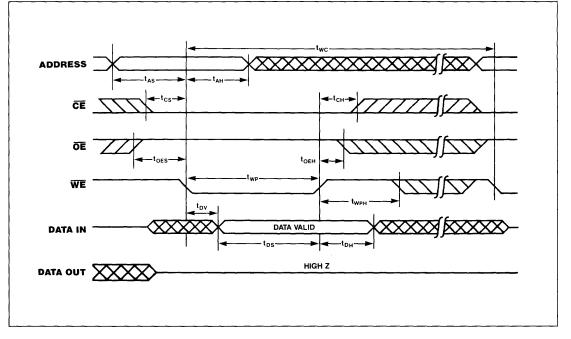

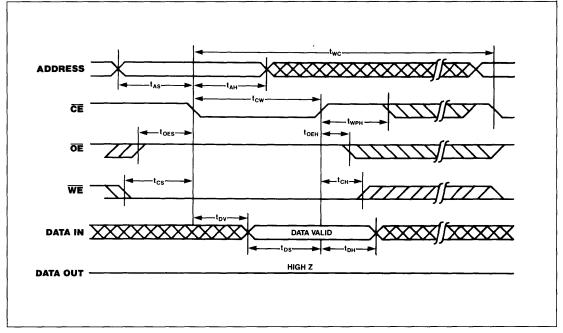

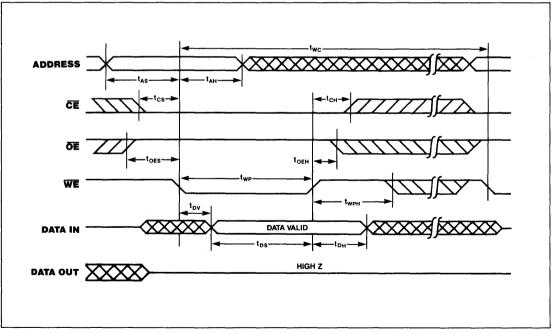

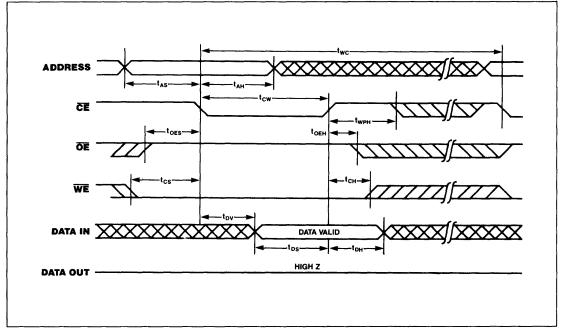

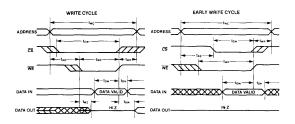

#### Write Cycle Limits

| Symbol          | Parameter                        | Min. | Max. | Units |

|-----------------|----------------------------------|------|------|-------|

| twc             | Write Cycle Time                 | 300  |      | ns    |

| t <sub>cw</sub> | Chip Select to End of Write      | 150  |      | ns    |

| t <sub>AS</sub> | Address Set-up Time              | 50   |      | ns    |

| t <sub>WP</sub> | Write Pulse Width                | 150  |      | ns    |

| t <sub>wR</sub> | Write Recovery Time              | 25   |      | ns    |

| t <sub>DW</sub> | Data Valid to End of Write       | 100  |      | ns    |

| t <sub>DH</sub> | Data Hold Time                   | 0    |      | ns    |

| t <sub>wz</sub> | Write Enable to Output in High Z | 10   | 100  | ns    |

| tow             | Output Active from End of Write  | 10   |      | ns    |

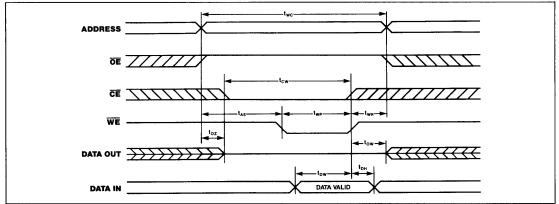

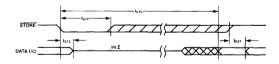

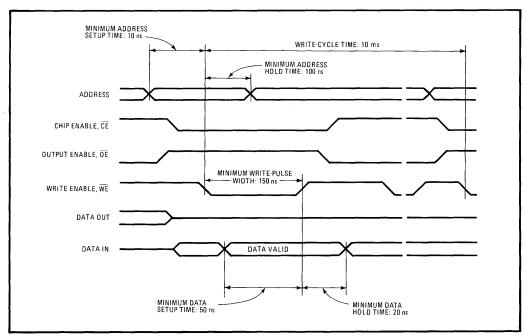

Write Cycle

Contract Sector

in Rates

Same and the second

ë,

ş.

The second

Early Write Cycle

## X2201A

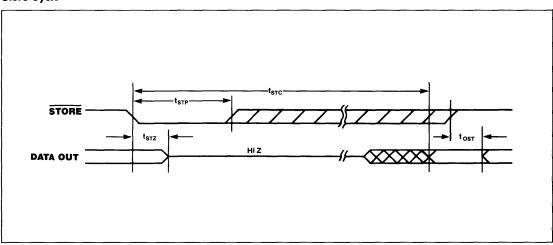

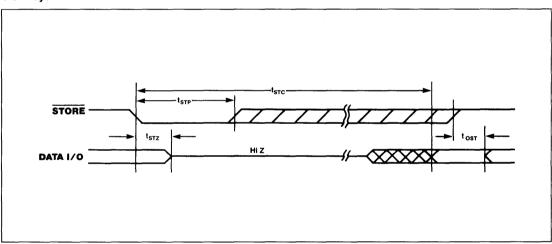

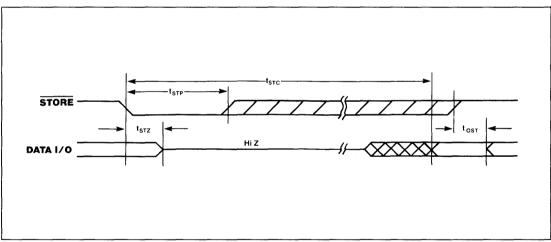

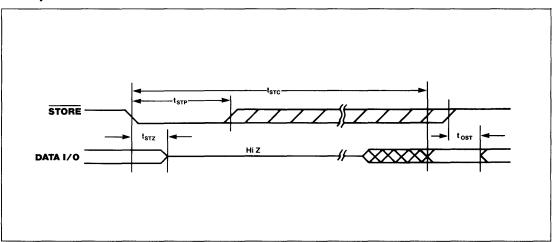

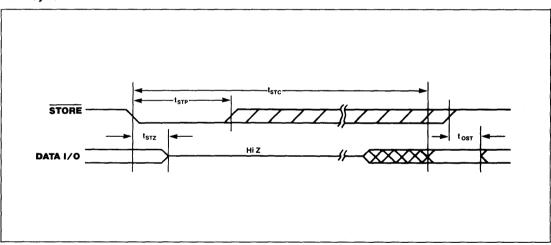

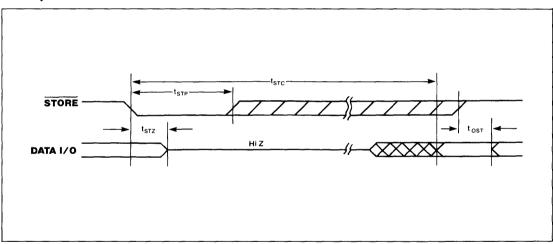

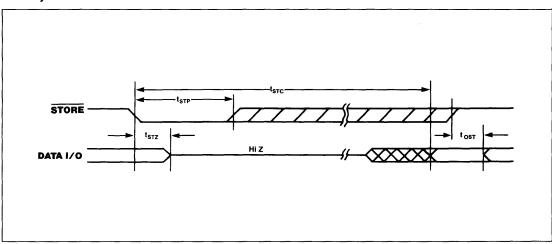

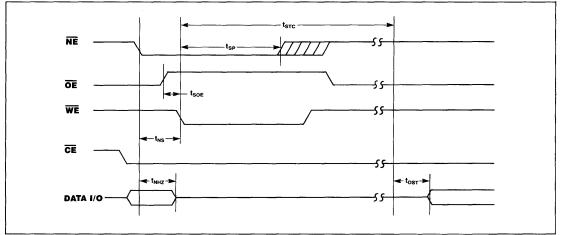

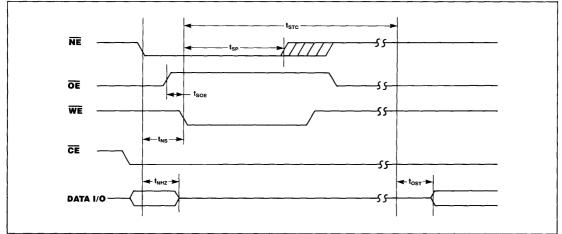

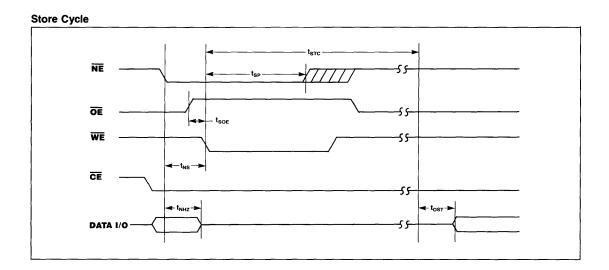

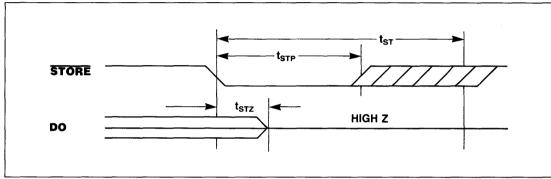

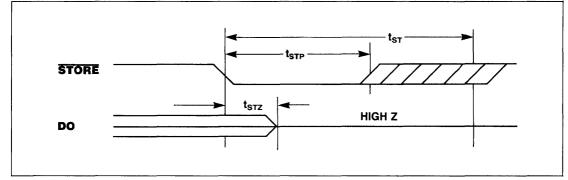

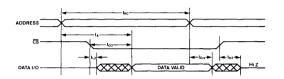

### Store Cycle Limits

| Symbol           | Parameter                       | Min. | Max. | Units |

|------------------|---------------------------------|------|------|-------|

| t <sub>stc</sub> | Store Cycle Time                |      | 10   | ms    |

| t <sub>STP</sub> | Store Pulse Width               | 100  |      | ns    |

| t <sub>stz</sub> | Store to Output in High Z       |      | 500  | ns    |

| t <sub>ost</sub> | Output Active from End of Store | 10   |      | ns    |

Store Cycle

ŝ

ちょう こうしてい あいのないない こうちょうしょう

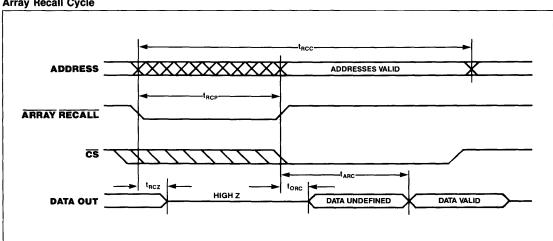

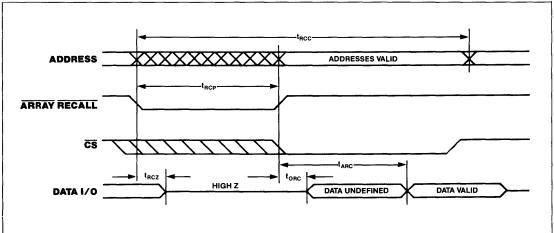

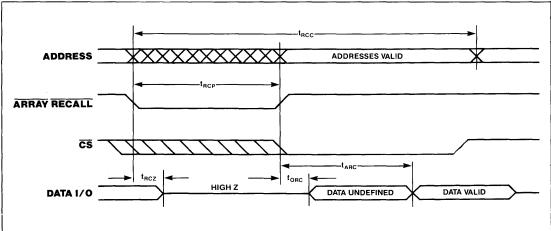

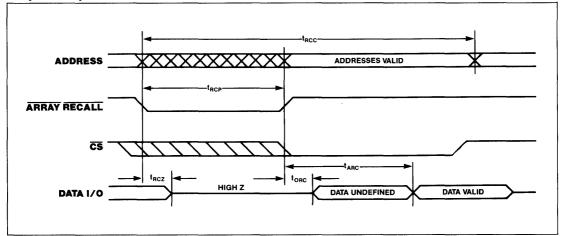

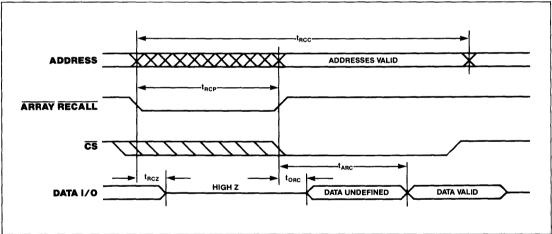

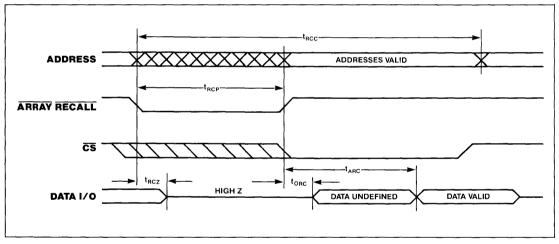

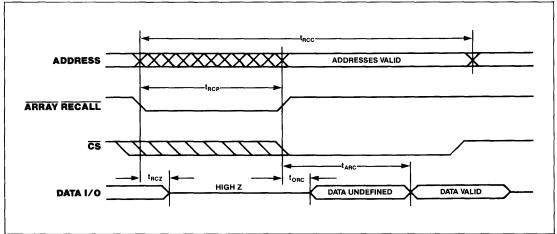

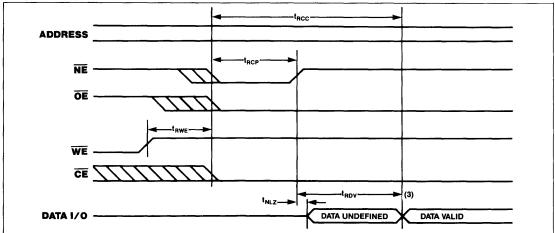

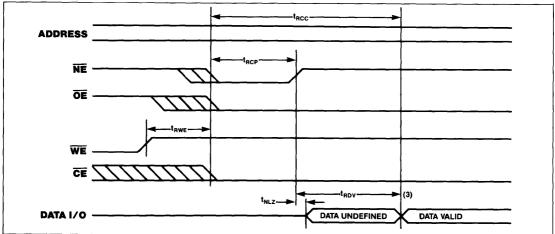

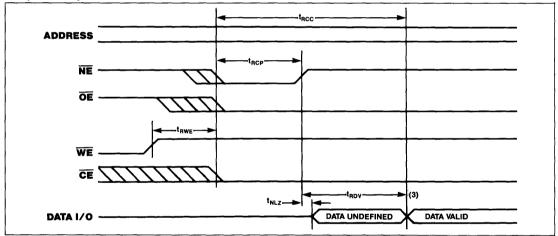

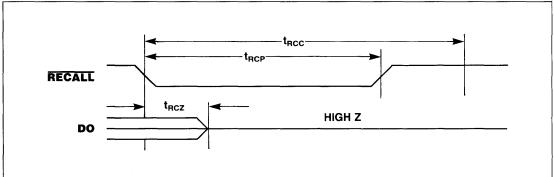

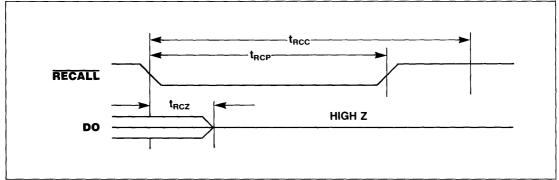

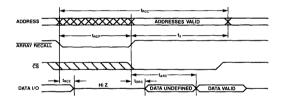

#### Array Recall Cycle Limits

| Symbol           | Parameter                                    | Min. | Max. | Units |

|------------------|----------------------------------------------|------|------|-------|

| t <sub>RCC</sub> | Array Recall Cycle Time                      | 1200 |      | ns    |

| t <sub>RCP</sub> | Recall Pulse Width <sup>(4)</sup>            | 450  |      | ns    |

| t <sub>RCZ</sub> | Recall to Output in High Z                   |      | 150  | ns    |

| t <sub>ORC</sub> | Output Active from End of Recall             | 10   |      | ns    |

| t <sub>ARC</sub> | Recalled Data Access Time from End of Recall |      | 750  | ns    |

Note: (4) Array Recall rise time must be less than 1 µs.

## Array Recall Cycle

#### PIN DESCRIPTIONS AND DEVICE OPERATION

#### Addresses (A<sub>0</sub>-A<sub>9</sub>)

The address inputs select a memory location during a read or write operation.

#### Chip Select (CS)

The Chip Select input must be LOW to enable read/write operations with the RAM array.  $\overline{CS}$  HIGH will place the D<sub>OUT</sub> in the high impedance state.

#### Write Enable (WE)

The Write Enable input controls the  $D_{OUT}$  buffer, determining whether a RAM read or write operation is enabled. WE HIGH enables a read and WE LOW enables a write.

#### Data In (D<sub>IN</sub>)

Data is written into the device via the D<sub>IN</sub> input.

#### Data Out (Dout)

Data from a selected address is output on the  $D_{OUT}$  output. This pin is in the high impedance state when either  $\overline{CS}$  is HIGH or when  $\overline{WE}$  is LOW.

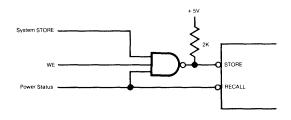

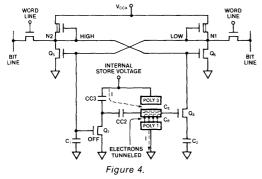

#### STORE

The STORE input, when LOW, will initiate the transfer of the entire contents of the RAM array to the  $E^2$ PROM array. The WE and ARRAY RECALL inputs are inhibited during the store cycle. The store operation will be completed in 10ms or less.

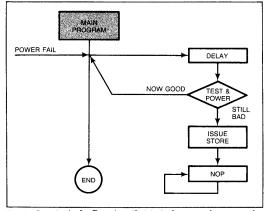

A store operation has priority over RAM read/write operations. If STORE is asserted during a read operation, the read will be discontinued. If STORE is asserted during a RAM write operation, the write will be immediately terminated and the store performed. The data at the RAM address that was being written will be unknown in both the RAM and E<sup>2</sup>PROM.

#### ARRAY RECALL

The ARRAY RECALL input, when LOW, will initiate the transfer of the entire contents of the  $E^2$ PROM array to the RAM array. The transfer of data will typically be completed in 1µs or less.

An array recall has priority over RAM read/write operations and will terminate both operations when ARRAY RECALL is asserted. ARRAY RECALL LOW will also inhibit the STORE input.

#### WRITE PROTECTION

The X2201A has three write protect features that are employed to protect the contents of the nonvolatile memory.

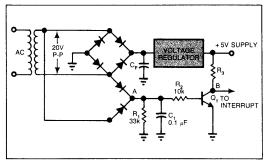

- V<sub>CC</sub> Sense—All functions are inhibited when V<sub>CC</sub> is  $\leq$  3v, typically.

- Write Inhibit—Holding either STORE HIGH or RECALL LOW during power-up or power-down will prevent an inadvertent store operation and E<sup>2</sup>PROM data integrity will be maintained.

- Noise Protection—A STORE pulse of less than 20ns will *not* initiate a store cycle.

#### ENDURANCE

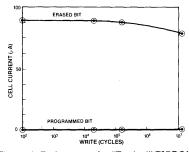

The endurance specification of a device is characterized by the predicted first bit failure to occur in the entire memory (device or system) array rather than the average or typical value for the array. Since endurance is limited by the number of electrons trapped in the oxide during data changes, Xicor NOVRAMs are designed to minimize the number of changes an E<sup>2</sup>PROM bit cell undergoes during store operations. Only those bits in the E<sup>2</sup>PROM that are different from their corresponding location in the RAM will be "cycled" during a nonvolatile store. This characteristic reduces unnecessary cycling of any of the rest of the bits in the array, thereby increasing the potential endurance of each bit and increasing the potential endurance of the entire array. Reliability data documented in RR504, the Xicor Reliability Report on Endurance, and additional reports are available from Xicor.

| Part Number | Store Cycles | Data Changes<br>Per Bit |

|-------------|--------------|-------------------------|

| X2201A      | 10,000       | 1,000                   |

## NOTES

#### 256 Bit Commercial

X2210A

#### 64 x 4 Bit

## Nonvolatile Static RAM

#### FEATURES

- Single 5 Volt Supply

- Fully TTL Compatible

- JEDEC Standard 18-Pin Package

- Infinite E<sup>2</sup>PROM Array Recall, RAM Read and Write Cycles

- Access Time of 250ns Max.

- Nonvolatile Store Inhibit: V<sub>CC</sub> = 3v Typical

- 100 Year Data Retention

#### DESCRIPTION

The Xicor X2210A is a 64 x 4 NOVRAM\* featuring a highspeed static RAM overlaid bit-for-bit with a nonvolatile  $E^2$ PROM. The X2210A is fabricated with the same reliable N-channel floating gate MOS technology used in all Xicor 5 volt nonvolatile memories. The X2210A features the JEDEC approved pinout for 4-bit-wide memories, compatible with industry standard RAMs.

The NOVRAM design allows data to be easily transferred from RAM to E<sup>2</sup>PROM (store) and from E<sup>2</sup>PROM to RAM (recall). The store operation is completed in 10ms or less and the recall is typically completed in 1 $\mu$ s.

Xicor NOVRAMs are designed for unlimited write operations to RAM, either from the host or recalls from  $E^2PROM$ . The  $E^2PROM$  array is designed for a minimum 10,000 store cycles. Data retention is specified to be greater than 100 years.

\*NOVRAM is Xicor's nonvolatile static RAM device.

#### **PIN CONFIGURATION**

#### **PIN NAMES**

| A <sub>0</sub> -A <sub>5</sub> | Address Inputs      |

|--------------------------------|---------------------|

| I/O1-I/O4                      | Data Inputs/Outputs |

| WE                             | Write Enable        |

| CS                             | Chip Select         |

| ARRAY RECALL                   | Array Recali        |

| STORE                          | Store               |

| V <sub>cc</sub>                | +5V                 |

| V <sub>ss</sub>                | Ground              |

| <br>NC                         | No Connect          |

|                                |                     |

#### FUNCTIONAL DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias 10°C to +85°C |

|--------------------------------------|

| Storage Temperature65°C to +150°C    |

| Voltage on any Pin with              |

| Respect to Ground1.0V to +7V         |

| D.C. Output Current                  |

| Lead Temperature (Soldering,         |

| 10 Seconds)                          |

#### D.C. OPERATING CHARACTERISTICS

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = +5V \pm 5\%$ , unless otherwise specified.

#### Limits Symbol Parameter Min. Max. Units **Test Conditions** All Inputs = $V_{CC}$ I<sub>CC</sub> Power Supply Current 50 mΑ $l_{VO} = 0 \text{ mA}$ Input Load Current 10 $V_{IN} = GND$ to $V_{CC}$ IL. μA 10 μA $V_{OUT} = GND$ to $V_{CC}$ **Output Leakage Current** ILO V. v Input Low Voltage -1.00.8 $V_{\text{IH}}$ Input High Voltage 2.0 $V_{CC} + 0.5$ ٧ $V_{\text{OL}}$

0.4

v

v

#### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

**Output Low Voltage**

Output High Voltage

| Symbol                          | Test                     | Max. | Unit | Conditions     |

|---------------------------------|--------------------------|------|------|----------------|

| C <sub>I/O</sub> <sup>(1)</sup> | Input/Output Capacitance | 8    | pF   | $V_{I/O} = 0V$ |

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance        | 6    | pF   | $V_{IN} = 0V$  |

Note: (1) This parameter is periodically sampled and not 100% tested.

#### A.C. CONDITIONS OF TEST

V<sub>OH</sub>

| Input Pulse Levels                | 0 to 3.0 Volts                        |

|-----------------------------------|---------------------------------------|

| Input Rise and<br>Fall Times      | 10 nsec                               |

| Input and Output<br>Timing Levels | 1.5 Volts                             |

| Output Load                       | 1 TTL Gate and $C_L = 100 \text{ pF}$ |

#### MODE SELECTION

2.4

| Inputs |    | Input Output |       |                 |                                    |

|--------|----|--------------|-------|-----------------|------------------------------------|

| cs     | WE | ARRAY RECALL | STORE | I/O             | Mode                               |

| н      | X  | н            | н     | Output High Z   | Not Selected <sup>(2)</sup>        |

| L      | н  | Н            | Н     | Output Data     | Read RAM                           |

| L      | L  | Н            | н     | Input Data High | Write "1" RAM                      |

| L      | L  | Н            | н     | Input Data Low  | Write "0" RAM                      |

| х      | Н  | L            | н     | Output High Z   | Array Recall                       |

| н      | X  | L            | Н     | Output High Z   | Array Recall                       |

| Х      | н  | Н            | L     | Output High Z   | Nonvolatile Storing <sup>(3)</sup> |

| н      | X  | Н            | L     | Output High Z   | Nonvolatile Storing <sup>(3)</sup> |

Notes: (2) Chip is deselected but may be automatically completing a store cycle. (3) STORE = L is required only to initiate the store cycle, after which the store cycle will be automatically completed ( $\overline{STORE} = X$ ).

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$I_{OL} = 4.2 \text{ mA}$

$I_{OH} = -2 \text{ mA}$

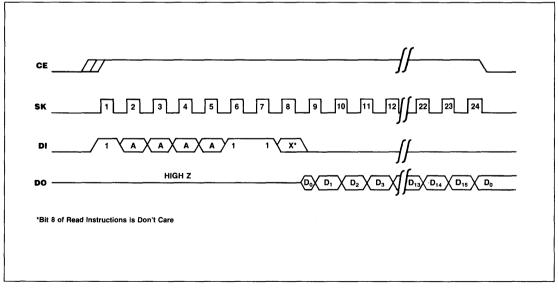

#### A.C. CHARACTERISTICS

$T_{\text{A}}$  = 0°C to +70°C,  $V_{\text{CC}}$  = +5V ±5%, unless otherwise specified.

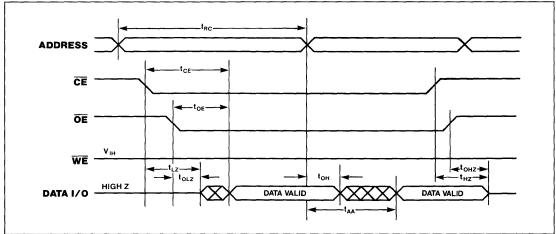

#### **Read Cycle Limits**

| Symbol          | Parameter                         | Min. | Max. | Units |

|-----------------|-----------------------------------|------|------|-------|

| t <sub>RC</sub> | Read Cycle Time                   | 250  |      | ns    |

| t <sub>A</sub>  | Access Time                       |      | 250  | ns    |

| t <sub>co</sub> | Chip Select to Output Valid       |      | 200  | ns    |

| t <sub>он</sub> | Output Hold from Address Change   | 50   |      | ns    |

| t∟z             | Chip Select to Output in Low Z    | 10   |      | ns    |

| t <sub>HZ</sub> | Chip Deselect to Output in High Z | 10   | 100  | ns    |

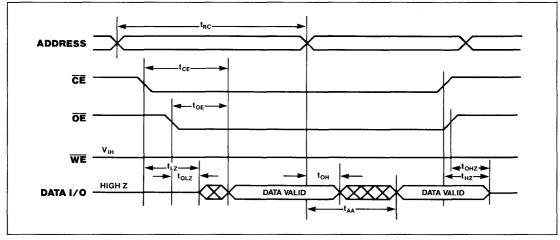

#### **Read Cycle**

## X2210A

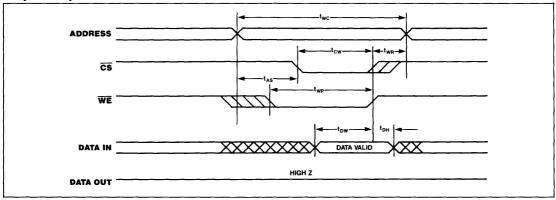

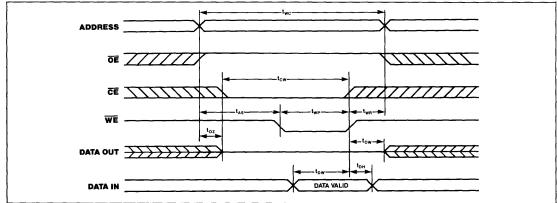

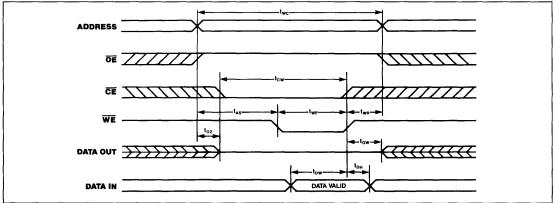

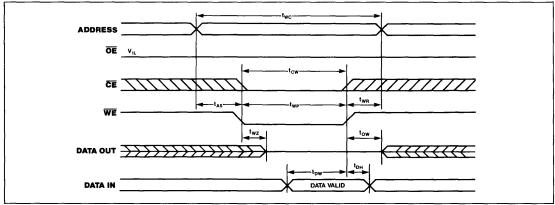

#### Write Cycle Limits

| Symbol          | Parameter                        | Min. | Max. | Units |

|-----------------|----------------------------------|------|------|-------|

| t <sub>wc</sub> | Write Cycle Time                 | 250  |      | ns    |

| t <sub>cw</sub> | Chip Select to End of Write      | 150  |      | ns    |

| t <sub>AS</sub> | Address Set-up Time              | 50   |      | ns    |

| t <sub>WP</sub> | Write Pulse Width                | 150  |      | ns    |

| t <sub>wn</sub> | Write Recovery Time              | 25   |      | ns    |

| t <sub>DW</sub> | Data Valid to End of Write       | 100  |      | ns    |

| t <sub>DH</sub> | Data Hold Time                   | 0    |      | ns    |

| t <sub>wz</sub> | Write Enable to Output in High Z | 10   | 100  | ns    |

| tow             | Output Active from End of Write  | 10   |      | ns    |

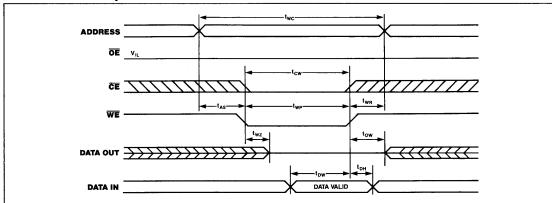

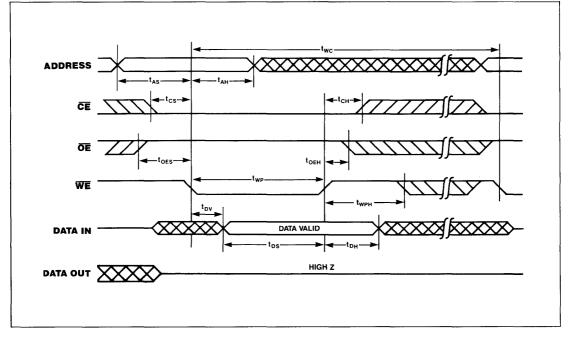

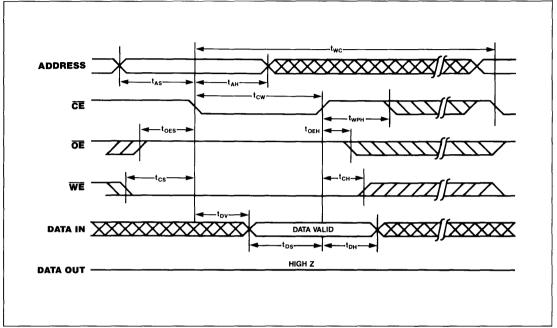

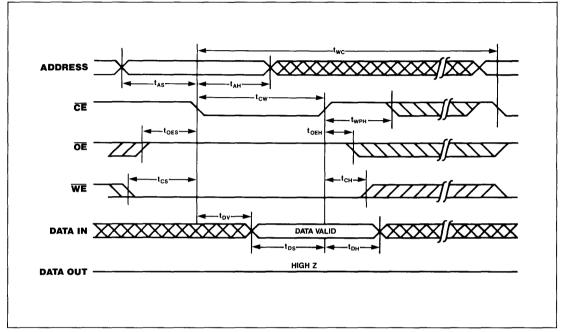

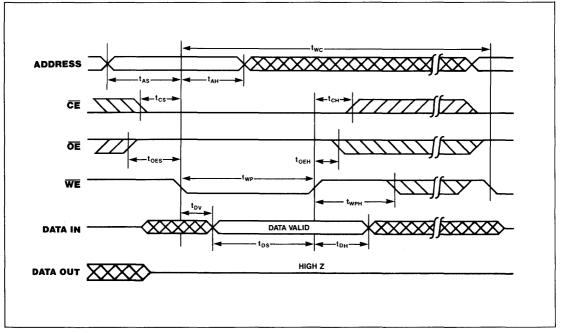

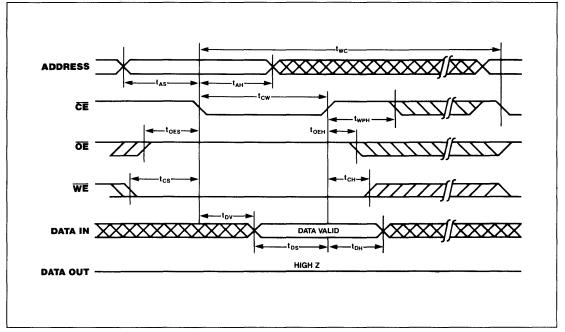

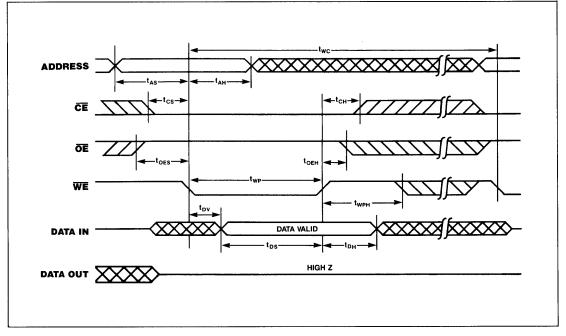

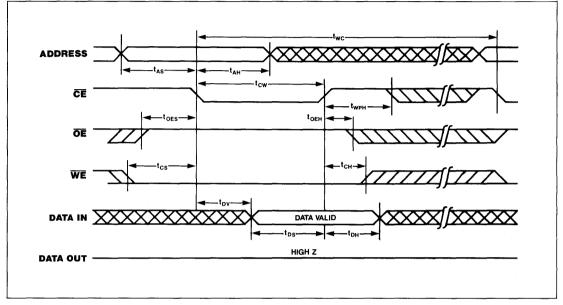

#### Write Cycle

#### Early Write Cycle

## X2210A

### Store Cycle Limits

| Symbol           | Parameter                       | Min. | Max. | Units |

|------------------|---------------------------------|------|------|-------|

| t <sub>stc</sub> | Store Cycle Time                |      | 10   | ms    |

| t <sub>STP</sub> | Store Pulse Width               | 100  |      | ns    |

| t <sub>stz</sub> | Store to Output in High Z       |      | 500  | ns    |

| tost             | Output Active from End of Store | 10   |      | ns    |

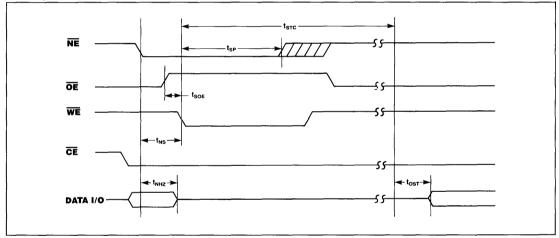

Store Cycle

#### Array Recall Cycle Limits

| Symbol           | Parameter                                    | Min. | Max. | Units |

|------------------|----------------------------------------------|------|------|-------|

| t <sub>RCC</sub> | Array Recall Cycle Time                      | 1200 |      | ns    |

| t <sub>RCP</sub> | Recall Pulse Width <sup>(4)</sup>            | 450  |      | ns    |

| t <sub>RCZ</sub> | Recall to Output in High Z                   |      | 150  | ns    |

| torc             | Output Active from End of Recall             | 10   |      | ns    |

| t <sub>ARC</sub> | Recalled Data Access Time from End of Recall |      | 750  | ns    |

Note: (4) Array Recall rise time must be less than 1  $\mu$ s.

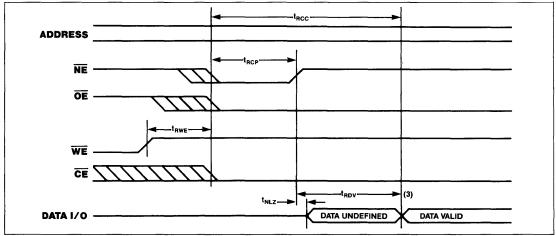

#### Array Recall Cycle

#### PIN DESCRIPTIONS AND DEVICE OPERATION

#### Addresses (A<sub>0</sub>-A<sub>5</sub>)

The address inputs select a 4-bit memory location during a read or write operation.

#### Chip Select (CS)

The Chip Select input must be LOW to enable read/write operations with the RAM array. CS HIGH will place the I/O pins in the high impedance state.

#### Write Enable (WE)

The Write Enable input controls the I/O buffers, determining whether a RAM read or write operation is enabled.  $\overline{WE}$  HIGH enables a read and  $\overline{WE}$  LOW enables a write.

#### Data In/Data Out (I/O1-I/O4)

Data is written to or read from the X2210A through the I/O pins. The I/O pins are placed in the high impedance state when either  $\overline{CS}$  is HIGH or during either a store or recall operation.

#### STORE

The STORE input, when LOW, will initiate the transfer of the entire contents of the RAM array to the  $E^2$ PROM array. The WE and ARRAY RECALL inputs are inhibited during the store cycle. The store operation will be completed in 10ms or less.

A store operation has priority over RAM read/write operations. If STORE is asserted during a read operation, the read will be discontinued. If STORE is asserted during a RAM write operation, the write will be immediately terminated and the store performed. The data at the RAM address that was being written will be unknown in both the RAM and E<sup>2</sup>PROM.

#### ARRAY RECALL

The ARRAY RECALL input, when LOW, will initiate the transfer of the entire contents of the E<sup>2</sup>PROM array to the RAM array. The transfer of data will typically be completed in  $1\mu$ s or less.

An array recall has priority over RAM read/write operations and will terminate both operations when ARRAY RECALL is asserted. ARRAY RECALL LOW will also inhibit the STORE input.

#### WRITE PROTECTION

The X2210A has three write protect features that are employed to protect the contents of the nonvolatile memory.

- $V_{CC}$  Sense—All functions are inhibited when  $V_{CC}$  is  $\leq$  3v, typically.

- Write Inhibit—Holding either STORE HIGH or RECALL LOW during power-up or power-down will prevent an inadvertent store operation and E<sup>2</sup>PROM data integrity will be maintained.

- Noise Protection—A STORE pulse of less than 20ns will *not* initiate a store cycle.

#### ENDURANCE

The endurance specification of a device is characterized by the predicted *first* bit failure to occur in the entire memory (device or system) array rather than the average or typical value for the array. Since endurance is limited by the number of electrons trapped in the oxide during data changes, Xicor NOVRAMs are designed to minimize the number of changes an E<sup>2</sup>PROM bit cell undergoes during store operations. Only those bits in the E<sup>2</sup>PROM that are different from their corresponding location in the RAM will be "cycled" during a nonvolatile store. This characteristic reduces unnecessary cycling of any of the rest of the bits in the array, thereby increasing the potential endurance of each bit and increasing the potential endurance of the entire array. Reliability data documented in RR504, the Xicor Reliability Report on Endurance, and additional reports are available from Xicor.

| Part Number | Store Cycles | Data Changes<br>Per Bit |

|-------------|--------------|-------------------------|

| X2210A      | 10,000       | 1,000                   |

## NOTES

## Nonvolatile Static RAM

#### FEATURES

- Single 5 Volt Supply

- Fully TTL Compatible

- JEDEC Standard 18-Pin Package

- Infinite E<sup>2</sup>PROM Array Recall, RAM Read and Write Cycles

- Access Time of 300ns Max.

- Nonvolatile Store Inhibit: V<sub>CC</sub> = 3v Typical

- 100 Year Data Retention

#### DESCRIPTION

The Xicor X2210 is a 64 x 4 NOVRAM<sup>\*</sup> featuring a highspeed static RAM overlaid bit-for-bit with a nonvolatile  $E^2$ PROM. The X2210 is fabricated with the same reliable N-channel floating gate MOS technology used in all Xicor 5 volt nonvolatile memories. The X2210 features the JEDEC approved pinout for 4-bit-wide memories, compatible with industry standard RAMs.

The NOVRAM design allows data to be easily transferred from RAM to E<sup>2</sup>PROM (store) and from E<sup>2</sup>PROM to RAM (recall). The store operation is completed in 10ms or less and the recall is typically completed in 1 $\mu$ s.

Xicor NOVRAMs are designed for unlimited write operations to RAM, either from the host or recalls from  $E^2PROM$ . The  $E^2PROM$  array is designed for a minimum 10,000 store cycles. Data retention is specified to be greater than 100 years.

\*NOVRAM is Xicor's nonvolatile static RAM device.

#### **PIN CONFIGURATION**

#### **PIN NAMES**

| Analy field         Analy field           STORE         Store           V <sub>cc</sub> +5V           V <sub>ss</sub> Ground           NC         No Connect | A₀-A₅<br>I/O₁-I/O₄<br>WE<br>CS<br>ARRAY RECALL | Address Inputs<br>Data Inputs/Outputs<br>Write Enable<br>Chip Select<br>Array Recall |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------|

| V <sub>ss</sub> Ground                                                                                                                                       |                                                |                                                                                      |

|                                                                                                                                                              | V <sub>cc</sub>                                | +5V                                                                                  |

| NC No Connect                                                                                                                                                | V <sub>ss</sub>                                | Ground                                                                               |

|                                                                                                                                                              | NC                                             | No Connect                                                                           |

#### FUNCTIONAL DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias X2210      |

|-----------------------------------|

| Storage Temperature65°C to +150°C |

| Voltage on any Pin with           |

| Respect to Ground1.0V to +7V      |

| D.C. Output Current               |

| Lead Temperature (Soldering,      |

| 10 Seconds)                       |

\*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **D.C. OPERATING CHARACTERISTICS**

X2210  $T_A$  = 0°C to +70°C,  $V_{CC}$  = +5V ±10%, unless otherwise specified. X2210I  $T_A$  = -40°C to +85°C,  $V_{CC}$  = +5V ±10%, unless otherwise specified.

|                 |                        | X2210 | Limits               | X2210I Limits |                      | X2210I Limits |                                                   |  |  |

|-----------------|------------------------|-------|----------------------|---------------|----------------------|---------------|---------------------------------------------------|--|--|

| Symbol          | Parameter              | Min.  | Max.                 | Min.          | Max.                 | Units         | Test Conditions                                   |  |  |

| Icc             | Power Supply Current   |       | 50                   |               | 55                   | mA            | All Inputs = $V_{CC}$<br>$I_{i/O} = 0 \text{ mA}$ |  |  |

| l <sub>LI</sub> | Input Load Current     |       | 10                   |               | 10                   | μA            | $V_{IN} = GND$ to $V_{CC}$                        |  |  |

| I <sub>LO</sub> | Output Leakage Current |       | 10                   |               | 10                   | μA            | $V_{OUT} = GND$ to $V_{CC}$                       |  |  |

| V <sub>IL</sub> | Input Low Voltage      | -1.0  | 0.8                  | -1.0          | 0.8                  | V             |                                                   |  |  |

| VIH             | Input High Voltage     | 2.0   | V <sub>cc</sub> +1.0 | 2.0           | V <sub>cc</sub> +1.0 | v             |                                                   |  |  |

| V <sub>OL</sub> | Output Low Voltage     |       | 0.4                  |               | 0.4                  | V             | $I_{OL} = 4.2 \text{ mA}$                         |  |  |

| V <sub>он</sub> | Output High Voltage    | 2.4   |                      | 2.4           |                      | ٧             | I <sub>он</sub> = -2 mA                           |  |  |

### **CAPACITANCE** $T_A = 25^{\circ}C$ , f = 1.0 MHz, $V_{CC} = 5V$

| Symbol                          | Test                     | Max. | Unit | Conditions     |  |

|---------------------------------|--------------------------|------|------|----------------|--|

| C <sub>I/O</sub> <sup>(1)</sup> | Input/Output Capacitance | 8    | pF   | $V_{I/O} = 0V$ |  |

| C <sub>IN</sub> <sup>(1)</sup>  | Input Capacitance        | 6    | pF   | $V_{IN} = 0V$  |  |

Note: (1) This parameter is periodically sampled and not 100% tested.

### A.C. CONDITIONS OF TEST

# MODE SELECTION