WD10C01A

Winchester

Disk Controller

# **TABLE OF CONTENTS**

| Section | Title Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.0     | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

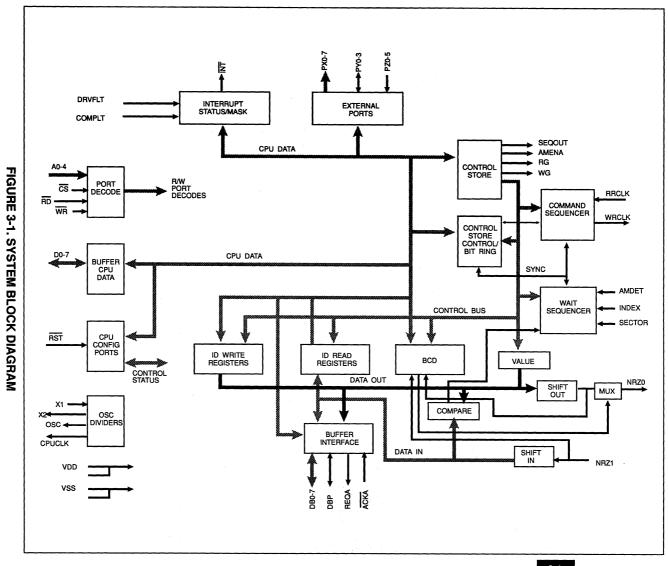

| 3.0     | SYSTEM BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.0     | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.0     | ARCHITECTURE       20-7         5.1 Error Correction And Detection Codes       20-8         5.1.1 CCITT-CRC       20-8         5.1.2 Reed-Solomon ECC       20-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | PROGRAMMING REFERENCE       20-9         6.1 Register Assignments       20-9         6.2 Register Definitions       20-10         6.3 Configuration Group       20-11         6.3.1 SRESET - Set Hardware Reset Register (00)       20-11         6.3.2 SISR - Interrupt Status Register (01)       20-12         6.3.3 SIMR - Interrupt Mask Register (02)       20-13         6.3.4 SEQSTS - Sequencer Status (03)       20-14         6.3.5 PYC - Port Y Configuration (03)       20-15         6.3.6 Control Store Windows       20-16         6.3.6.1 CSERR - Control Store Error Control Byte Window (04)       20-16         6.3.6.2 CSCTL - Control Store Control Store Control Byte Window (05)       20-17         6.3.6.3 CSVAL - Control Store Value Byte Window (06)       20-18         6.3.6.4 CSCNT - Control Store Count Byte Window (07)       20-20         6.3.6.5 Wait Condition Sequences       20-21         6.4 Device Control Group       20-22         6.4.1 PORTX - PORTX Output Bits (08)       20-22 |

|         | 6.4.2 PORTY - PORT Y I/O Bits (09)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Section | Title |           |               |               |              |        |      |     |   |       |       |   | Page    |

|---------|-------|-----------|---------------|---------------|--------------|--------|------|-----|---|-------|-------|---|---------|

|         |       | 6.4.12    | SPORT - S     | Syndrome P    | ort (12)     |        |      |     |   |       |       |   | . 20-31 |

|         |       |           |               | st Register ( |              |        |      |     |   |       |       |   |         |

|         |       | 6.4.14    | SKIP - Ski    | p Address F   | Register (17 | ') .   |      |     |   |       |       |   | . 20-32 |

|         | 6.5   | ID Regist | ter Group     |               |              |        |      |     |   |       |       |   | . 20-33 |

|         | 6.6   | Device P  | rogrammir     | ng            |              |        |      |     |   |       |       |   | . 20-35 |

|         |       |           | Initializatio |               |              |        |      |     |   |       |       |   |         |

|         |       |           |               | Programmi     |              |        |      |     |   |       |       |   |         |

|         |       |           |               | ore Program   |              |        |      |     |   |       |       |   |         |

|         |       |           | Ū             | ing Example   |              |        |      |     |   |       |       |   |         |

|         |       |           | 6.6.4.1       |               | ick Exampl   |        |      |     |   |       |       |   |         |

|         |       |           | 6.6.4.2       |               | or Example   |        |      |     |   |       |       |   |         |

|         |       |           | 6.6.4.3       | Write Sect    |              |        |      |     |   |       |       |   |         |

|         |       |           | 6.6.4.4       | Read And      |              |        |      |     |   |       |       |   |         |

|         |       |           |               | nd Error Co   |              |        |      |     |   |       |       |   |         |

|         |       |           |               | overy         |              |        |      |     |   |       |       |   |         |

|         |       | 6.6.7     | Error Corre   | ection        | • • •        | • • •  |      | •   | • | <br>• | <br>٠ | • | . 20-48 |

| 7.0     | DC E  | LECTRICA  | AL SPECIF     | CATIONS       |              |        |      |     |   |       |       |   | . 20-49 |

|         | 7.1   | Absolute  | Maximum       | Ratings .     |              |        |      |     |   |       |       |   | . 20-49 |

|         | 7.2   | Standard  | Test Cond     | litions       | · · · · ·    |        |      |     |   |       |       |   | . 20-49 |

|         | 7.3   | DC Chara  | acteristics   |               |              |        |      | . • | • |       |       |   | . 20-50 |

| 8.0     | AC O  | PERATING  | 3 CHARAC      | CTERISTIC     | 3            |        |      |     |   |       |       | _ | . 20-51 |

|         | 8.1   |           |               | Timing .      |              |        |      |     |   |       |       |   |         |

|         | 8.2   |           |               | ng            |              |        |      |     |   |       |       |   |         |

|         | 8.3   |           |               | ing           |              |        |      |     |   |       |       |   |         |

|         | 8.4   |           |               |               |              |        |      |     |   |       |       |   |         |

| A.0     | WD1   | CO1A PR   | OGRAMM        | ER'S BENC     | H REFERE     | NCE    | /PRI | 31  |   |       |       |   | 20-63   |

| Α.υ     | A.1   |           | Bit Tables    |               |              |        | •    | ,   |   |       |       |   |         |

|         |       |           |               |               |              |        |      |     |   |       |       |   |         |

| B.0     | RESE  | ET CONDI  | TIONS .       | <i>.</i>      |              | · · ,· |      |     | • |       |       |   | . 20-66 |

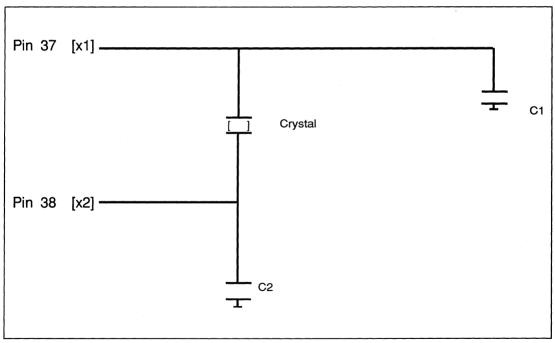

| C.0     | CRYS  | STAL OSC  | ILLATOR A     | APPLICATIO    | ONS          |        |      |     |   |       |       |   | . 20-67 |

| D.0     | PIN/S | SIGNAL SL | JMMARY        |               |              |        |      |     |   |       |       |   | . 20-68 |

| E.0     | DIFF  | ERENCES   | BETWEE        | N WD10C0      | O AND WD     | 10C01  | Α .  |     |   |       |       |   | . 20-69 |

|         | E.1   |           |               | d Detection   |              |        |      |     |   |       |       |   |         |

|         | E.2   |           |               |               |              |        |      |     |   |       |       |   |         |

|         | E.3   |           | -             |               |              |        |      |     |   |       |       |   |         |

|         | E.4   |           | •             | ··            |              |        |      |     |   |       |       |   |         |

|         | E.5   |           |               |               |              |        |      |     |   |       |       |   |         |

|         | E.6   |           |               | g             |              |        |      |     |   |       |       |   |         |

|         | E.7   | SEQCTL    | Register      |               |              |        |      |     |   |       |       |   | . 20-69 |

|         |       |           |               |               |              |        |      |     |   |       |       |   |         |

**//**

# LIST OF ILLUSTRATIONS

| Figure | Title                                           | Page    |

|--------|-------------------------------------------------|---------|

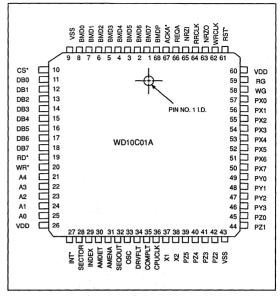

| 1-1    | WD10C01A Pin Diagram                            | . 20-1  |

| 3-1    | System Block Diagram                            | . 20-3  |

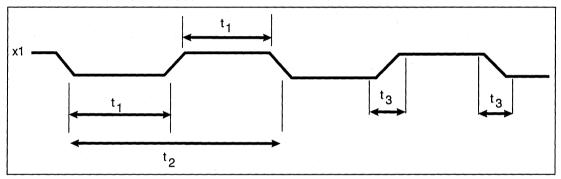

| 8-1    | TTL Source X1 Clock Input                       | . 20-51 |

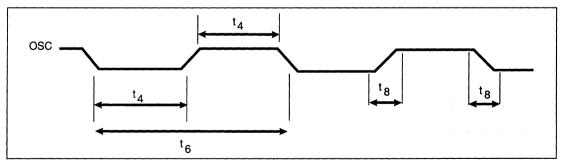

| 8-2    | OSC Output                                      | . 20-51 |

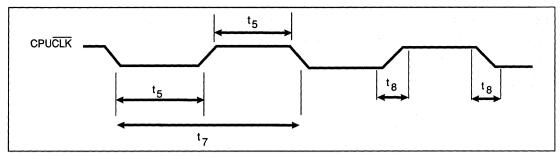

| 8-3    | CPUCLK Output                                   | . 20-52 |

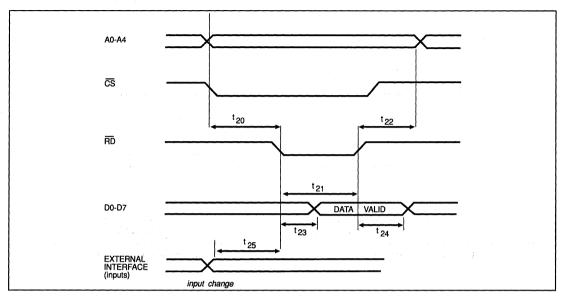

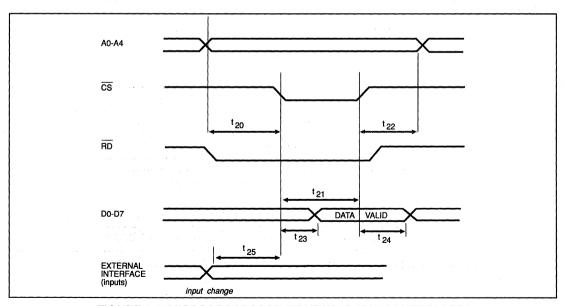

| 8-4    | Microprocessor RD* Timing (RD* Controlled)      | . 20-54 |

| 8-5    | Microprocessor RD* Timing (CS* Controlled)      | . 20-54 |

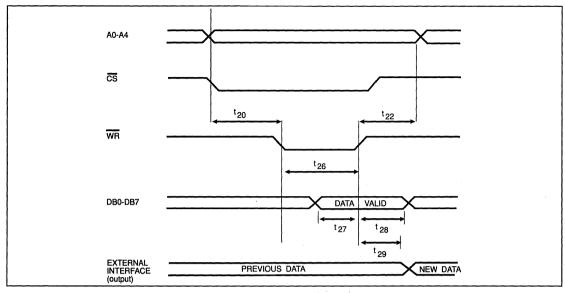

| 8-6    | Microprocessor WR* Timing (WR* Controlled)      | . 20-55 |

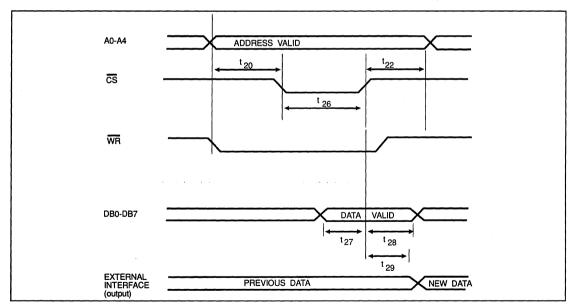

| 8-7    | Microprocessor WR* Timing (CS* Controlled)      | . 20-55 |

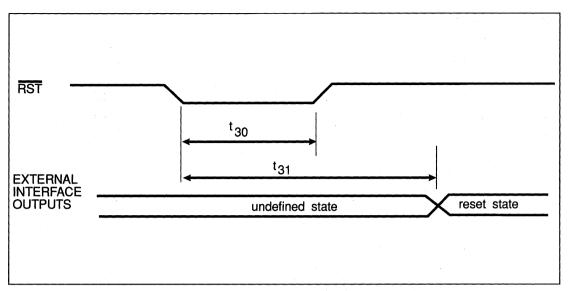

| 8-8    | Reset Timing                                    | . 20-56 |

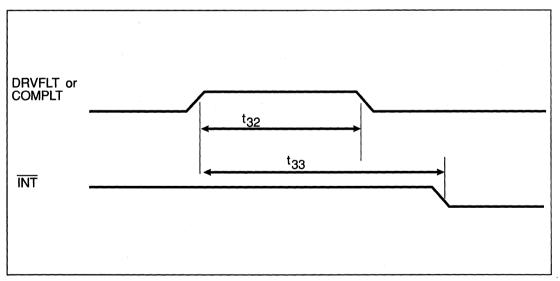

| 8-9    | Externally Generated Interrupt Timing           | . 20-56 |

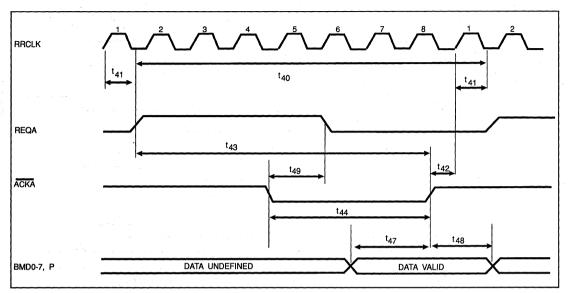

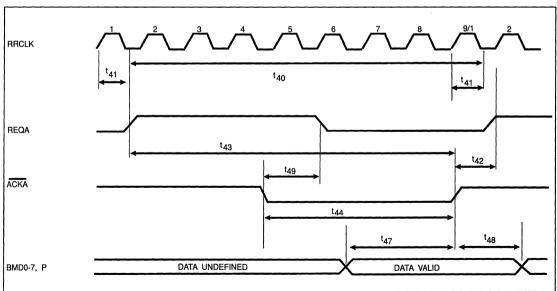

| 8-10   | Asynchronous Mode Data Bus Read Timing (1)      | . 20-58 |

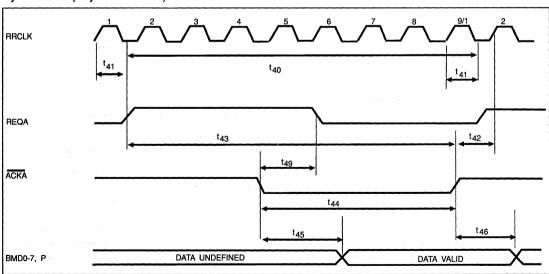

| 8-11   | Asynchronous Mode Data Bus Read Timing (0)      | . 20-58 |

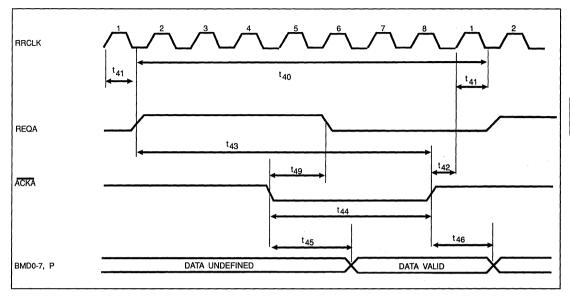

| 8-12   | Asynchronous Mode Data Bus Write Timing (1)     |         |

| 8-13   | Asynchronous Mode Data Bus Write Timing (0)     |         |

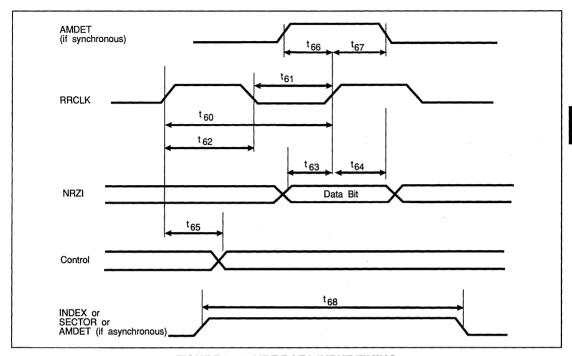

| 8-14   | NRZ Data Input Timing                           | . 20-61 |

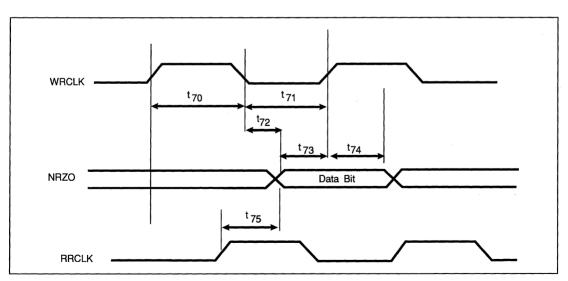

| 8-15   | NRZ Data Output Timing                          | . 20-61 |

| C-1    | Oscillator with Capacitors                      | . 20-67 |

|        | LIST OF TABLES                                  |         |

| Table  |                                                 | Dogo    |

| Table  | Title                                           | Page    |

| 4-1    | CPU Interface                                   | . 20-4  |

| 4-2    | Buffer Interface                                | . 20-5  |

| 4-3    | Disk Data Interface                             | . 20-5  |

| 4-4    | Disk Control Interface                          | . 20-6  |

| 4-5    | Device Power                                    | . 20-6  |

| 6-1    | Register Groups                                 | . 20-9  |

| 6-2    | SRESET- Set Hardware Register (00)              | . 20-11 |

| 6-2A   | ID Register Selection                           |         |

| 6-3    | SISR - Interrupt Status Register                | . 20-12 |

| 6-4    | SIMR - Interrupt Mask Register                  | . 20-13 |

| 6-5    | SEQSTS - Sequencer Status Register              | . 20-14 |

| 6-6    | PYC - Port Y Configuration (03)                 | . 20-15 |

| 6-7    | CSERR - Control Store Error Control Byte Window |         |

| 6-8    | CSCTL - Control Store Byte Window (05)          | . 20-17 |

| 6-9    | SVSEL of Control Byte Zero                      |         |

| 6-10   | SVSEL of Control Byte One                       |         |

| 6-11   | CWSEL of Control Byte Zero                      | . 20-20 |

| 6-12   | CWSEL of Control Byte One                       |         |

|        |                                                 |         |

# WD10C01A

| Table | Title                                       | Page    |

|-------|---------------------------------------------|---------|

| 6-13  | PortX Output Bits (08)                      | . 20-22 |

| 6-14  | PortY I/O Bits (09)                         | . 20-22 |

| 6-15  | PortZ Input Bits (0A)                       | . 20-22 |

| 6-16  | AMC - Address Mark Control (0A)             | . 20-23 |

| 6-17  | SEQCTL - Sequencer Control Register (0B)    | . 20-24 |

| 6-18  | START - Sequencer Start Address (0C)        | . 20-25 |

| 6-19  | LOOP - Sequencer Loop Address (0D)          | . 20-26 |

| 6-20  | ECCCTL - Error Correction Register (1E)     | . 20-27 |

| 6-21  | SECCNT - Sector Count Register (0F)         | . 20-28 |

| 6-22  | ECCP - ECC Parameter Register (10)          | . 20-29 |

| 6-23  | ECCS - RS-ECC Status Register (11)          | . 20-30 |

| 6-24  | SPORT - Syndrome Port (12)                  |         |

| 6-25  | SKIP - Skip Address Register (17)           | . 20-32 |

| 6-26  | Skip Control Store Example                  | . 20-32 |

| 6-27  | ID0 - ID Register 0 (18)                    | . 20-33 |

| 6-28  | ID1 - ID Register 1 (19)                    | . 20-33 |

| 6-29  | ID2 - ID Register 2 (1A)                    | . 20-33 |

| 6-30  | ID3 - ID Register 3 (1B)                    | . 20-33 |

| 6-31  | ID4 - ID Register 4 (1C)                    | . 20-34 |

| 6-32  | ID5 - ID Register 5 (1D)                    |         |

| 6-33  | ID6 - ID Register 6 (1E)                    | . 20-34 |

| 6-34  | ID7 - ID Register 7 (1F)                    | . 20-34 |

| 6-35  | Write Byte Sync Example                     | . 20-36 |

| 6-36  | Data Field Size Example                     | . 20-36 |

| 6-37  | Format Track Example Control Store          | . 20-38 |

| 6-38  | Read Sector Example Control Store           | . 20-40 |

| 6-39  | Write Sector Example Control Store          | . 20-42 |

| 6-40  | Read and Write Sector Example Control Store | . 20-44 |

| 7-1   | DC Characteristics                          |         |

| 8-1   | OSC and CPUCLK Timing Parameters            | . 20-53 |

| 8-2   | CPU Interface Timing Parameters             |         |

| 8-3   | Buffer Interface Timing Parameters          | . 20-60 |

| 8-4   | Serial Data Timing Parameters               | . 20-62 |

20-iv

# 1.0 INTRODUCTION

The WD10C01A is a VLSI Winchester/Optical Disk Controller chip that provides the data handling and control for intelligent disk applications. The WD10C01A interfaces to nearly any serial disk interface, including ST412, ST412HP, ESDI, SMD, and many optical disk interfaces. The WD10C01A provides great flexibility in format design, allowing for multiple ID fields, special synchronization requirements, special information fields, or almost any other special requirement. The WD10C01A can provide all of the data, status, and control signals required by these interfaces.

# 1.1 FEATURES

- Disk interfaces and formats supported include ST412, ST412HP, ESDI, SMD and optical disks

- Full multi-sector operation with four byte ID auto-increment

- Up to 24 mbit/second maximum transfer rate

- Supports 16-bit CRC-CCITT polynomial on ID field

- Degree 5 and 6 Reed-Solomon ECC with 3- or 5-way interleave to protect data field against long error burst

- Provides composite syndromes for error correction

- Up to 1:1 interleave operation

- Writeable control store allows flexible error Recovery, including redundant ID and sync fields

FIGURE 1-1. WD10C01A PIN DIAGRAM

- Support hard or soft sector formats, sector size to 1250 bytes when 5-way interleave is used for degree 5 Reed-Solomon code

- Built in crystal driver for data rate and/or CPU use

- Generic non-multiplexed CPU interface with maskable interrupts

- Separate CPU and disk data busses

- On-the-fly compare against buffer data

- 20 general I/O Lines for disk drive control

- 68-Pin PLCC package

# 2.0 GENERAL DESCRIPTION

The WD10C01A has separate ports for data DMA transfer and for the microprocessor to achieve a maximum performance.

The WD10C01A performs the disk data serialization and de-serialization. It can interface with various magnetic and optical Data Encoder/Decoders (ENDEC). The data format on the disk is controlled by a Writeable Control Store. It is very flexible with the capability to support various formats including optical disk. The device also has the capability to compare data and verify the ECC. The WD10C01A can perform full track operations without CPU intervention using the Writeable Control Store, auto-incrementing ID registers and the sector counter.

The WD10C01A includes logic implementing CCITT-CRC and Reed-Solomon ECC for data protection. The ID field is protected by sixteen bit CRC and the data field is protected by degree five or six RS-ECC. The user can also select the interleave factor of three or five for the data field. The term "interleave" here should not be confused with the term "sector interleave," which defines the relation between the physical and the logical location of sectors within a track. Interleaving the data field means spreading the data across several ECC code words to improve the capability for correcting longer error bursts.

For the error correction, the WD10C01A generates the composite syndromes. From this error information, the correction software can generate individual syndromes to correct up to two error bytes per interleave (for degree 5) or up to three error bytes per interleave (for degree 6). Optionally, the user can use external, more powerful ECC device, such as WD60C80.

The highly programmable nature of the WD10C01A allows the use of redundant ID and data sync fields within a single sector. This feature, along with the programmable degree 5 or 6 RS-ECC, gives the WD10C01A a greater capability for recovering user data in a sector with 'grown' defects.

The WD10C01A interfaces to the buffer manager, such as WD60C40 through an eight bit DMA port. It uses asynchronous protocol through DREQ/DACK signals.

The WD10C01A has a generic microprocessor interface that allows the WD10C01A to be used with all popular 8-bit microprocessors. The WD10C01A has interrupt capability, which frees up the microprocessor from constantly polling the device status. The WD10C01A also has a built-in crystal oscillator driver that can be used to generate data reference, buffer management, or microprocessor clocks. Two separate outputs are provided with internal programmable dividers. Both outputs have the extra drive voltage and current necessary for driving MOS microprocessor clock inputs.

The WD10C01A has 20 lines dedicated to external I/O ports that the microprocessor can use to control the drive and head select lines, seek command and drive status. Eight lines are output only, six lines are input only, and four other lines can be individually programmed for input or output. Two other latch and hold input lines are tied to the interrupt logic and can be used to detect fault and ready conditions without constantly polling the device.

# **%**

# 3.0 SYSTEM BLOCK DIAGRAM

# 4.0 SIGNAL DESCRIPTION

The WD10C01A is a 68-pin PLCC device.

The following section describes the external signals available on the WD10C01A. Conventions are as follows:

- I indicates that a signal is an input to the WD10C01A.

- O indicates that a signal is an output from the WD10C01A.

I/O indicates that a signal is bidirectional.

- I,O indicates that a signal can be input output.

- \* as a suffix indicates an active low signal; however, most drawings and text use an overscore to indicate an active low signal.

| PIN   | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                    |

|-------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25-21 | A0-A4    | ı   | CPU ADDRESS BUS. These signals are used to address internal WD10C01A registers.                                                                                                                                |

| 36    | CPUCLK   | 0   | CPU CLOCK OUTPUT. This is the OSC output (see below) divided by two or three, selected by an internal register. This output has extra drive for use with certain microprocessors.                              |

| 10    | CS       | ı   | CHIP SELECT. This active low signal enables the WD10C01A bus interface logic.                                                                                                                                  |

| 11-18 | DB0-DB7  | I/O | CPU DATA I/O BUS. This data bus is used to transfer data between the CPU and the WD10C01A.                                                                                                                     |

| 27    | INT      | 0   | CPU INTERRUPT. This active low, open drain output is asserted whenever an enabled interrupt condition occurs on the WD10C01A.                                                                                  |

| 33    | OSC      | 0   | OSCILLATOR OUTPUT. The 1x crystal oscillator output, optionally divided by two. This signal has the same drive capability as CPUCLK.                                                                           |

| 19    | RD       | ı   | CPU READ STROBE. This active low signal enables data from the WD10C01A on to the CPU data bus.                                                                                                                 |

| 61    | RST      | 1   | RESET. This active low signal resets all internal circuits that must be reset at power on. A complete list is given later in this document. The reset is latched and the condition must be cleared by the CPU. |

| 20    | WR       | ı   | CPU WRITE STROBE. This active low signal strobes data into the selected WD10C01A register from the CPU data bus.                                                                                               |

| 37    | X1       | 1   | CRYSTAL DRIVER INPUT. X1 can also be driven by an external clock.                                                                                                                                              |

| 38    | X2       | 0   | CRYSTAL DRIVER OUTPUT.                                                                                                                                                                                         |

**TABLE 4-1. CPU INTERFACE**

| PIN | MNEMONIC | I/O | DESCRIPTION                                                                                                                              |

|-----|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 67  | ACKA     | 1   | BUFFER DATA ACKNOWLEDGE. This active low signal indicates to the WD10C01A that data can now be transferred to or from the data buffer.   |

| 8-1 | BMD0-7   | I/O | BUFFER MEMORY DATA BUS. This is an eight bit data bus that interfaces the WD10C01A with the disk data buffer memory.                     |

| 68  | BMDP     | I/O | DATA BUS PARITY. This signal is used to generate and check parity with the disk data buffer memory.                                      |

| 66  | REQA     | 0   | BUFFER DATA REQUEST. This signal is asserted when the WD10C01A has data to write to the data buffer, or needs data from the data buffer. |

**TABLE 4-2. BUFFER INTERFACE**

| PIN | MNEMONIC | I/O | DESCRIPTION                                                                                                                                                                                                                                                              |

|-----|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | AMDET    | ı   | ADDRESS MARK DETECTED. Used only in ST412 type interfaces that use missing clocks or other qualifiers to the sync bytes that mark the start of a field.                                                                                                                  |

| 31  | AMENA    | 0   | ADDRESS MARK ENABLE. Used to write a missing clock sync byte (ST412) or soft sector mark (ESDI, SMD) on the media.                                                                                                                                                       |

| 65  | NRZI     | l   | NRZ READ DATA IN. Serial data input from the disk phase-locked loop. This signal is clocked in by the rising edge of RRCLK.                                                                                                                                              |

| 63  | NRZO     | 0   | NRZ WRITE DATA OUT. Serial data output. NRZO is valid on the rising edge of WRCLK.                                                                                                                                                                                       |

| 59  | RG       | 0   | READ GATE. Active when reading from the disk drive. This signal is turned off for one byte time on an ID search error to reset external data decoders.                                                                                                                   |

| 64  | RRCLK    | l   | READ/REFERENCE CLOCK. This is the reference clock used to set the data rate for write, and is the recovered clock for read. The switching must be glitch free. NRZI is clocked into the WD10C01A by the rising edge of this clock.                                       |

| 32  | SEQOUT   | 0   | SEQUENCER OUTPUT. This signal is a user definable output bit that is set up in the control byte of the sequencer control store (see below). This signal can be used to control an external ECC generator and checker, and is byte aligned with both read and write data. |

| 58  | WG       | 0   | WRITE GATE. Active when writing to the disk drive.                                                                                                                                                                                                                       |

| 62  | WRCLK    | 0   | WRITE CLOCK. This is output during write for drives that require it. NRZO data is valid on the rising edge of this clock.                                                                                                                                                |

**TABLE 4-3. DISK DATA INTERFACE**

| PIN             | MNEMONIC | I/O        | DESCRIPTION                                                                                                                                                                                               |

|-----------------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35              | COMPLT   | 1          | COMPLETE. This signal is used to detect function complete conditions, such as seeks or status requests. The signal only generates a CPU interrupt, and does not interfere with a read or write operation. |

| 34              | DRVFLT   | . <b>1</b> | DRIVE FAULT. This signal is used to detect faults from the drive. The signal only generates a CPU interrupt, and does not interfere with a read or write operation.                                       |

| 29              | INDEX    | I          | INDEX. This signal is used to indicate the start of a track. This signal is latched for CPU status and interrupt.                                                                                         |

| 57-50           | PX0-7    | 0          | PORT X. This general purpose output port is intended for use as drive select and head select signals.                                                                                                     |

| 49-46           | PY0-3    | I,O        | PORT Y. This general purpose port is intended for use as other control outputs or inputs. Each bit is selectable as input or output, but all bits are initialized to input when the WD10C01A is reset.    |

| 45,44,<br>42-39 | PZ0-5    | 1          | PORT Z. This general purpose input port is used to receive drive status signals.                                                                                                                          |

| 28              | SECTOR   | 1          | SECTOR MARK. This signal is used for marking sector start locations on the media. This can either be a hard sector mark, or a soft mark written on the media using AMENA (ESDI or SMD).                   |

**TABLE 4-4. DISK CONTROL INTERFACE**

| PIN   | MNEMONIC | I/O | DESCRIPTION  |    |

|-------|----------|-----|--------------|----|

| 26,60 | VDD      | 1   | +5 VOLTS DC. | 1. |

| 9,43  | VSS      |     | GROUND.      |    |

TABLE 4-5. DEVICE POWER

# 5.0 ARCHITECTURE

The WD10C01A consists of the functional blocks shown in the block diagram in Figure 3-1. VDD and VSS are applied to the device through two separate pins each to improve noise immunity. The top and left hand sides of the diagram show CPU interface features, the right hand side shows disk interface features, and the bottom shows buffer interface features. These blocks are discussed in the following paragraphs.

The PORT DECODE block generates the 28 write strobes and 25 read strobes used by the microprocessor to access the various internal control and status ports. These include the interrupt registers, external disk control ports, control store, control store control, configuration, ECC control, and ID registers.

The BUFFER CPU DATA block controls the transfer of data between the microprocessor and the internal registers. The direction control is qualified by chip select (CS) and read strobe (RD).

The CPU CONFIGURATION PORTS are used to reset the WD10C01A, set the address mark enable timing, set the buffer interface timing, and select the frequency of the clock outputs, OSC and CPUCLK.

The OSCILLATORS AND DIVIDERS block generates the clock outputs, OSC and CPUCLK, using an external crystal (or clock input) and dividers to select the frequency. Frequency selection is glitch free.

The INTERRUPT STATUS AND MASK registers are used to check and mask interrupts. The mask register does not affect the status register inputs. The interrupt sources include index and sector mark, drive fault and operation complete, ECC errors, and internal event status.

The EXTERNAL PORTS are used to generate control signals and read status with the disk drive. Eight bits are output, six are input, and four are individually programmable for either input or output.

The CONTROL STORE consists of 32 words of 28 bits that are used to program the format of the disk sector. The data source, field length, error handling and checksum selection, and control sig-

nals, like Read Gate and Write Gate, are controlled by the data stored here.

The CONTROL STORE CONTROL determines the next address in the control store to use, whether the next sequential address or a jump to another address. This block includes the sector counter used for multi-sector commands. This block also includes the BIT RING COUNTER, which determines the timing of data transfers in the WD10C01A.

The WAIT SEQUENCER handles searches for index, sector mark, address mark, and byte synchronization.

The ID WRITE REGISTERS are 8 eight bit registers that are used to set the ID write field for format, or the search field for read/update write. Four of the registers are counters that auto-increment during multi-sector commands. The other four registers do not increment, and are used for defect and flag information. The first byte of the four counters can be disabled for three byte ID fields.

The ID READ REGISTERS are used to read the last ID read from the media to aid in defect handling.

The ECD block performs the CRC on ID, selects the degree of RS-ECC with 3- or 5-way interleave on data fields, generates the checksum bytes, creates the composite syndromes and ECC error status necessary for the calculation of error location and mask.

The VALUE register holds immediate data from the control store when generating gaps, sync fields, and address mark bytes.

The SHIFT OUT register serializes internal or external (buffer) data for writing on the disk. The output is multiplexed with the output of the checksum register.

The SHIFT IN register de-serializes the read data from the disk, clocked in by RRCLK. The data is also transferred to the checksum register for checking.

The COMPARE block is used to compare incoming read data with an internal or external data

source. These include byte synchronization detection, ID field search, and buffer data compare.

The BUFFER INTERFACE handles the fetching and writing of data with the external data buffer. This includes parity generation and checking, and data handshake with the buffer controller.

# 5.1 ERROR CORRECTION AND DETECTION CODES

# 5.1.1 CCITT-CRC

The WD10C01A protects the ID fields using the CCITT-CRC code. The polynomial is defined as follow:

$$g(x) = x^{16} + x^{12} + x^5 + 1$$

The user can select the initial state of the shift registers to be either all zero's or all one's.

### 5.1.2 Reed-Solomon ECC

The data fields are protected using the interleaved Reed-Solomon code operating on 8 bits symbols. The redundancy bytes are inverted. WD10C01A supports two polynomials of degree five and six. The generator polynomials operate in the finite field GF(256), which are defined as follow:

Let  $\beta^i$  represent elements of a finite field defined by a polynomial over GF(2):

$$q(x) = x^8 + x^5 + x^3 + x^2 + 1$$

.

The elements of the finite field employed by the codes are:

$$a^{i} = (\beta^{i})^{88}$$

.

The generator polynomials are self reciprocal and defined as follows:

1. Degree 5. distance 6:

$$G(x) = (x+a^{253})^*(x+a^{254})^*(x+a^0)^*(x+a^1)^*(x+a^2).$$

The coefficients of the polynomial in decimals are:

2. Degree 6, distance 7:

$$G(x) = (x+a^{125})^*(x+a^{126})^*(x+a^{127})^*(x+a^{128})^*$$

$$(x+a^{129})^*(x+a^{130}).$$

The coefficients of the polynomial in decimals are:

The calculated checkbytes are **inverted** before they are written into the disk. During read operation, the WD10C01A computes the composite syndromes by recalculating the checkbytes for the data field being read and compare them against the checkbytes written on the disk. The individual syndromes can be computed by dividing the composite syndromes with the factors of the generator polynomial:

$$S_i(x) = R(x) MODULO G_i(x)$$

where:

i = 0..ecc degree -1.

$S_i(x) = i'th individual syndrome.$

R(x) = composite syndrome.

$G_i(x)$  = factor of the generator polynomial,  $(x+a^i)$ .

The WD10C01A supports two data interleaving factors. The user can optimize the performance by choosing the right degree and interleave combination.

The following table shows the redundancy overhead and maximum field size.

| Interleave | Degi      | ree 5                     | Degree 6  |                           |  |  |

|------------|-----------|---------------------------|-----------|---------------------------|--|--|

| Factor     | Overhead* | Max. Data*<br>Field Size* | Overhead* | Max. Data*<br>Field Size* |  |  |

| 3          | 15        | 750                       | 18        | 747                       |  |  |

| 5          | 25        | 1250                      | 30        | 1245                      |  |  |

<sup>\*</sup> all units bytes

# 6.0 PROGRAMMING REFERENCE

# 6.1 REGISTER ASSIGNMENTS

The WD10C01A contains 32 output and 23 input ports distributed in a 32 port address space, selected by A0-A4,  $\overline{CS}$ , and  $\overline{RD}$  or  $\overline{WR}$ .

The ports are split into three functional groups:

- · configuration group

- · device control group

- · ID registers.

Address lines A4 and A3 select the group, and A2 through A0 select the register in the group.

|         | CONFIGURATION     | DEVICE CONTROL 1 |              |            |     |  |  |

|---------|-------------------|------------------|--------------|------------|-----|--|--|

| Address | Assignment        | R/W              | Address      | Assignment | R/W |  |  |

| 00000   | SRESET            | W                | 01000        | PORTX      | R/W |  |  |

| 00001   | SISR              | R/W              | 01001        | PORTY      | R/W |  |  |

| 00010   | SIMR              | R/W              | 01010        | PORTZ/AMC  | R/W |  |  |

| 00011   | SEQSTS/PYC        | R/W              | 01011        | SEQCTL     | R/W |  |  |

| 00100   | CSERR             | R/W              | 01100        | START      | R/W |  |  |

| 00101   | CSCTL             | R/W              | 01101        | LOOP       | R/W |  |  |

| 00110   | CSVAL             | R/W              | 01110        | ECCCTL     | R/W |  |  |

| 00111   | CSCNT             | R/W              | 01111        | SECCNT     | R/W |  |  |

| DE      | VICE CONTROL 2    |                  | ID REGISTERS |            |     |  |  |

| Address | Assignment        | R/W              | Address      | Assignment | R/W |  |  |

| 10000   | ECCP              | W                | 11000        | ID0        | R/W |  |  |

| 10001   | ECCS              | R                | 11001        | ID1        | R/W |  |  |

| 10010   | SPORT             | R                | 11010        | ID2        | R/W |  |  |

| 10011   |                   |                  | 11011        | ID3        | R/W |  |  |

| 10100   |                   |                  | 11100        | ID4        | R/W |  |  |

| 10101   |                   |                  | 11101        | ID5        | R/W |  |  |

| 10110   | TEST - do not use |                  | 11110        | ID6        | R/W |  |  |

| 10111   | SKIP              | W                | 11111        | ID7        | R/W |  |  |

**TABLE 6-1. REGISTER GROUPS**

# 6.2 REGISTER DEFINITIONS

The following sections describe each register in detail. The use of the register is described in general and/or each bit is described. The table below defines how bit directions are defined in these sections. Sometimes, a bit encoding is used to select a function that is not obvious from the definition of the bits involved. Refer to the section on Programming Notes for descriptions of these special modes.

The following table contains bit direction definitions.

| Direction | Meaning                                                                           |

|-----------|-----------------------------------------------------------------------------------|

| R         | indicates that the bit is read only                                               |

| W         | indicates that the bit is write only                                              |

| R/W       | indicates that the bit may be written and read                                    |

| R/C       | indicates that the bit may be read<br>and cleared by writing a one to<br>that bit |

| С         | indicates that the bit may be cleared by writing a one to that bit                |

# 6.3 CONFIGURATION GROUP

The configuration group is used to do initial set up of ports and clocks, handle interrupts, and set up the control store memory.

| 6.3.1 | <b>SRESET - Set Hardware Reset</b> | t |

|-------|------------------------------------|---|

|       | Register (00)                      |   |

Bits 7-1 are cleared to zero by reset. Bit 0 is set to one by an external reset. When writing one to SRST, any data on bits 7-1 are lost.

| OSCDIV | CLKDIV | osc    | CPUCLK |

|--------|--------|--------|--------|

| 0      | 0      | XTAL/2 | XTAL/6 |

| 0      | 1      | XTAL/2 | XTAL/4 |

| 1      | 0      | XTAL   | XTAL/3 |

| 1      | 1      | XTAL   | XTAL/2 |

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                                                                                                         |

|----------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00       | 7   | W   | CLKDIV: CPUCLK divisor (see Note 1 below)                                                                                                                                                                                                                                                          |

| 00       | 6   | W   | OSCDIV: OSC divisor (see Note 1 below)                                                                                                                                                                                                                                                             |

| 00       | 5   | W   | Unused.                                                                                                                                                                                                                                                                                            |

| 00       | 4   | W   | Unused.                                                                                                                                                                                                                                                                                            |

| 00       | 3   | W   | Unused.                                                                                                                                                                                                                                                                                            |

| 00       | 2   | W   | REQTIM: buffer request timing. When this bit is one, REQA is set at the same time that the internal buffer data holding register is ready. When this bit is zero, REQA occurs one RRCLK period early. This aids in interfacing to certain buffer circuits that have a lag in their response times. |

| 00       | 1   | W   | ID3\$4: select ID address size (see Note 2)                                                                                                                                                                                                                                                        |

| 00       | 0   | W   | SRST: hardware reset. This bit is set by an external reset on the RST input, or can be set by writing one to this bit. This bit must be set to zero before operating the WD10C01A, or before setting any of the other bits in this register or any other register.                                 |

TABLE 6-2. SRESET - SET HARDWARE REGISTER (00)

**NOTE 1:** The CPUCLK dividers are prescaled by the OSC dividers, as shown in the table below (XTAL is the clock generated by a crystal at X1 and X2):

**NOTE 2:** The eight ID register bytes are split into two fields: the first four are address, and auto-increment for each sector; and the second four are flag bytes which do not increment. The ID3\$4 bit selects whether 3 or 4 bytes of ID address bytes will be used in the ID field. In 3 byte address fields, register ID0 is ignored. See Table 6-2A.

Two other considerations:

- CPUCLK = XTAL/3 will not be a 50% duty cycle unless XTAL is also a 50% duty cycle clock.

- When resetting the WD10C01A under CPU control, and the CPU is clocked by CPUCLK or OSC, set CPUDIV and OSCDIV back to zero before setting SRST. If this is not done, the clocks could glitch and cause the CPU to fail.

| ID3\$4 | Address Counter Size | First Register In Field |

|--------|----------------------|-------------------------|

| 0      | 4 bytes              | ID0                     |

| 1      | 3 bytes              | ID1 (ID0 not used)      |

**TABLE 6-2A. ID REGISTER SELECTION**

# 6.3.2 SISR - Interrupt Status Register (01)

The interrupt status register is designed to be used in interrupt or polled mode. The status is not affected by the interrupt mask register (see below). The interrupting condition has precedence over the CPU clear, which is performed by writing

a one to the selected interrupt bit. If the condition still exists, the clear will not be successful. The COMPLT and FAULT interrupts will stay set until the cause of the interrupt goes away. The ID-FULL, DXFER, SECEND, and SM\$IX interrupts are generated by single bit time pulses that are triggered by the leading edge of the interrupt cause, and can therefore be cleared immediately. SEQSTP is a direct status signal and is cleared when the sequencer is executing a command.

Before checking any bit (except SEQSTP), it should be cleared by writing a one to it. This register is not affected by reset.

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01       | 7   | R   | GINT - group interrupt. This is the state of the $\overline{\text{INT}}$ output, which is the logical OR of all of the enabled (by SIMR, see below) interrupt sources in this register.                                                                                                                                                                                                                                                                                       |

| 01.      | 6   | R/C | IDFULL - ID registers full. This interrupt is set at the end of any ID field access by the transition of the control store ID bit from true to false. This interrupt should be serviced before the next ID field is accessed. This interrupt can be cleared immediately.                                                                                                                                                                                                      |

| 01       | 5   | R/C | DXFER - data transfer started. This interrupt is set at the start of the data field by the transition of the control store BUFF or NOX-FER bit from false to true. This interrupt can be used to determine when it is safe to write to the LOOP, SKIP, SECCNT, or ID registers, if necessary. This interrupt can be cleared immediately.                                                                                                                                      |

| 01       | 4   | R/C | COMPLT - complete. This interrupt is set in response to the COM-<br>PLT input pin going true. This interrupt cannot be cleared until the<br>COMPLT input pin goes false.                                                                                                                                                                                                                                                                                                      |

| 01       | 3   | R   | SEQSTP - sequencer stopped. This interrupt is set when the sequencer has stopped executing a command. This interrupt is cleared when the sequencer starts a new command.                                                                                                                                                                                                                                                                                                      |

| 01       | 2   | R/C | SECEND - sector end interrupt. This interrupt is set by the leading edge of the LAST bit in the control store (see below). This is used to signal the end of a sector for buffer management and other overhead processing. The size of the field in which the LAST bit is set can be adjusted to match the processing overhead to the end of the sector for maximum CPU performance; the minimum size for this field is two bytes. This interrupt can be cleared immediately. |

| 01       | 1   | R/C | SM\$IX - sector mark or index passed. This interrupt is set by the leading edge of the SECTOR or INDEX input going true, as selected by the mask in the sequencer control register (SEQCTL). RRCLK must be present for this interrupt to function. This interrupt can be cleared immediately.                                                                                                                                                                                 |

**TABLE 6-3. SISR - INTERRUPT STATUS REGISTER**

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                         |

|----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01       | 0   | R/C | FAULT - drive fault. This interrupt is set in response to the DRVFLT input pin going true. This interrupt cannot be cleared until the DRVFLT input pin goes false. |

TABLE 6-3. SISR - INTERRUPT STATUS REGISTER (CONTINUED)

# 6.3.3 SIMR - Interrupt Mask Register (02)

The interrupts listed are described in the SISR description. Writing a one to the mask bit enables the interrupt. The state of the mask bits does not

affect the reading of status in SISR in any way. This register is cleared to zero by reset (interrupts disabled). Disabling GINT overrides any other enables set in this register.

| REGISTER | BIT | DIR | DEFINITION                       |

|----------|-----|-----|----------------------------------|

| 02       | 7   | R/W | GINT - enable all interrupts     |

| 02       | 6   | R/W | IDFULL - enable IDFULL interrupt |

| 02       | 5   | R/W | DXFER - enable DXFER interrupt   |

| 02       | 4   | R/W | COMPLT - enable COMPLT interrupt |

| 02       | 3   | R/W | SEQSTP - enable SEQSTP interrupt |

| 02       | 2   | R/W | SECEND - enable SECEND interrupt |

| 02       | 1   | R/W | SM\$IX - enable SM\$IX interrupt |

| 02       | 0   | R/W | FAULT - enable FAULT interrupt   |

**TABLE 6-4. SIMR - INTERRUPT MASK REGISTER**

# 6.3.4 SEQSTS - Sequencer Status (03)

The following status bits are further clarified in later registers and sections. These bits can be

used to check what sequencer operation is taking place.

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                 |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03       | 7   | R   | DATFLD - data field active. This bit means that the either the BUFF or the NOXFER bit is now active from the control store.                                                                                |

| 03       | 6   | R   | ECCEN - checksum calculation active. The WD10C01A is now calculating the checksum. This status line usually encompasses the ID or data field and checksum bytes, and is active during both read and write. |

| 03       | 5   | R   | LAST - The LAST bit is now active from the control store.                                                                                                                                                  |

| 03       | 4   | R   | ID - The ID bit is now active from the control store.                                                                                                                                                      |

| 03       | 3   | R   | CHK - The CHK bit is now active from the control store. The WD10C01 is now processing the checkbytes or syndromes for the CRC or ECC.                                                                      |

| 03       | 2   | R   | WAIT - The wait sequencer is waiting for an event such as index, sector mark, address mark, or byte sync.                                                                                                  |

| 03       | 1   | R   | AMDET - Address mark detect. This is the raw AMDET pin input. This pin can be used as an extra input bit in designs (such as ST506) that do not require this function.                                     |

| 03       | 0   | R   | SEQOUT - The SEQOUT bit is now active from the control store.                                                                                                                                              |

**TABLE 6-5. SEQSTS - SEQUENCER STATUS REGISTER**

# 6.3.5 PYC - PORT Y Configuration (03)

This port is used to configure each port Y bit for input or output. This register is cleared to zero by

reset, which causes all port Y pins to become inputs.

| REGISTER | BIT | DIR | DEFINITION                                |

|----------|-----|-----|-------------------------------------------|

| 03       | 3   | W   | PY3DIR - bit 3 direction: 0 = in; 1 = out |

| 03       | 2   | W   | PY2DIR - bit 2 direction: 0 = in; 1 = out |

| 03       | 1   | W   | PY1DIR - bit 1 direction: 0 = in; 1 = out |

| 03       | 0   | W   | PY0DIR - bit 0 direction: 0 = in; 1 = out |

**TABLE 6-6. PYC - PORT Y CONFIGURATION (03)**

# 6.3.6 Control Store Windows

The heart of the WD10C01A is its control store memory, which is organized as 32 instruction words of 28 bits each. Each 28 bit instruction is divided into three 8 bit parts: the control byte, the value byte, and the count byte; and one 4 bit part: the error control byte. The window registers are used to access these bytes. The control store address is specified by writing to the START register. Any write to a control store window register causes the START register to automatically increment to the next address to facilitate loading.

The contents of the control store are not affected by reset.

# 6.3.6.1 CSERR - Control Store Error Control Byte Window (04)

The transition of DAC from false to true, together with WG (in the control byte of the control store) or RCMP (read compare enable in the SEQCTL register), causes a one byte prefetch from the buffer. If an immediate fill character is used to specify the format data field or read compare byte (see below), and DAC is used to select the ECC for the data field, prefetch REQA signals are generated anyway.

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                                                                                                                                  |

|----------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 04       | 3   | R/W | FAIL - Enable error failure. Setting this bit to one causes a command stop if an error is detected while executing the current control store instruction. The error can be CRC/ECC error, data miscompare error or a parity error during write operation.                                                                   |

| 04       | 2   | R/W | RTY - Enable read error retry. This bit is valid only during read. Setting this bit to one causes a sector retry (see below) if a read error is detected while executing the current control store instruction. An example of the use of this bit is to cause a retry on an ID field miscompare.                            |

| 04       | 1   | R/W | DAC - Data field active. Set this bit to one when the current control store instruction involves a data field operation.  This signal is used to select the data field checksum (RS-ECC) and to control data prefetch. When this bit is zero an ID field operation is assumed, and the ID field checksum (CRC) is selected. |

| 04       | 0   | R/W | SEQOUT - user defined output. This is tied to the SEQOUT output pin through some delays which align the signal to the byte boundary of the read or write serial data. This output can be used to control an external ECC circuit, such as a Reed-Solomon code circuit.                                                      |

TABLE 6-7. CSERR-CONTROL STORE ERROR CONTROL BYTE WINDOW

# 6.3.6.2 CSCTL - Control Store Control Byte Window (05)

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05       | 7   | R/W | SVSEL - value byte select. This bit selects the use of the value byte, which can be either immediate data (SVSEL = 0) or a select for data source or destination (SVSEL = 1).                                                                                                                                                                                                   |

| 05       | 6   | R/W | CWSEL - count byte select. The bit selects the use of the count byte, which can be either an immediate byte count (CWSEL = 0) or to specify an external condition to wait for (CWSEL = 1).                                                                                                                                                                                      |

| 05       | 5   | R/W | WG - write gate output. This is tied directly to the WG output pin.                                                                                                                                                                                                                                                                                                             |

| 05       | 4   | R/W | RG - read gate output. This is tied to the retry logic, which is then tied to the RG output pin.                                                                                                                                                                                                                                                                                |

| 05       | 3   | R/W | AM - address mark enable output. This is tied to the AMC register (see below) which generates the AMENA signal.                                                                                                                                                                                                                                                                 |

| 05       | 2   | R/W | CMPEN - compare enable. This signal is used to indicate that the bytes of the currently selected data source are to be compared with incoming serial data (ID, marker bytes, buffer data).                                                                                                                                                                                      |

| 05       | 1   | R/W | SKPEN - jump to SKIP address at end of the current instruction. This causes an absolute jump to the SKIP register address when the current control store instruction is finished. Typically, this is used to set up a read and write program in the control store with a common ID search routine. (See later examples and SKIP register definition.)                           |

| 05       | 0   | R/W | JMPEN - jump to LOOP address at end of the current instruction. This causes a conditional jump to the LOOP register if the sector count (SECCNT) is not zero. If SECCNT is zero, the next sequential instruction is executed. Typically, this is used to specify the end of a sector, and tells the sequencer to go to the LOOP register address to operate on the next sector. |

TABLE 6-8. CSCTL - CONTROL STORE BYTE WINDOW (05)

# 6.3.6.3 CSVAL - Control Store Value Byte Window (06)

The use of the value byte depends on the state of the SVSEL bit of the control byte. When SVSEL is zero, the value byte specifies actual immediate data, like address mark, gap, and PLL sync bytes. When SVSEL is one, the value byte becomes an encoded bit field that enables the correct data source or destination. Both uses are shown below.

To get large sector sizes, multiple control store instructions are used. For example, for a 1024 byte sector size, use four instructions with 256 byte count fields. With this scheme, the last instruction must be flagged for error correction and write prefetch purposes. The LAST bit must be set with the BUFF or NOXFER bit to ensure proper operation.

| REGISTER | BIT | DIR | DEFINITION                        |

|----------|-----|-----|-----------------------------------|

| 06       | 7-0 | R/W | VALUE7-0 (actual value for field) |

**TABLE 6-9. SYSEL of CONTROL BYTE ZERO**

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06       | 7   | R/W | BUFF - data buffer. This bit causes data to be transferred to (disk read) or from (disk write or read compare) the disk data buffer. The leading edge of BUFF causes a decrement of the SECCNT register, and increments the ID write register counters (see below).                                                                                                                                                                                                                             |

| 06       | 6   | R/W | NOXFER - no data transfer. This bit is used when an ECC/CRC verify on the data field with no buffer data transfer is being performed. This bit is set INSTEAD of the BUFF bit, and affects the SECCNT and ID registers in the same way as the BUFF bit.                                                                                                                                                                                                                                         |

| 06       | 5   | R/W | LAST - last data buffer xfer control store instruction. Long data fields (greater than 256 bytes) are specified by using multiple control store instructions (2 for 512 bytes, 4 for 1024 bytes, etc.). When the control store instruction is the last instruction of the data field specifiers, the LAST bit must be set to flag this. This only applies to data buffer transfers. LAST is set in ADDITION to BUFF or NOXFER. The CSCNT byte must be set to at least 01 when this bit is used. |

| 06       | 4   | R/W | R/W ID - ID registers. On ID read, the incoming ID field from the disk is compared against the ID write registers and written at the same time to the ID read registers. On write (format), the data source is the ID write registers.                                                                                                                                                                                                                                                          |

| 06       | 3   | R/W | CHK - checksum field. On read, this starts the check for a correct checksum. On write, this causes the checksum shift register to be gated into the NRZ0 data. In either case, the calculation is halted at the end of this instruction. The DAC bit in CSERR window selects the appropriate checksum automatically.                                                                                                                                                                            |

**TABLE 6-10. SVEL of CONTROL BYTE ONE**

# 6.3.6.4 CSCNT - Control Store Count Byte Window (07)

The use of the count byte depends on the state of the CWSEL bit of the control byte. When CWSEL is zero, the count byte specifies the actual length of that field in bytes. When CWSEL is one, the count byte becomes an encoded bit field that specifies a condition to wait for before proceding. Both uses are shown below.

The count value is set to the actual number of bytes to do minus one. Therefore, 00 denotes a one byte field, and FF a 256 byte field.

| REGISTER | BIT | DIR | DEFINITION                          |

|----------|-----|-----|-------------------------------------|

| 07       | 7-0 | R/W | COUNT7-0 (actual size of field - 1) |

TABLE 6-11, CWSEL of CONTROL BYTE ZERO

| REGISTER | BIT | DIR | DEFINITION                                                                                                                                                                                                                                                                                                                                                             |

|----------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07       | 7   | R/W | WDAM - Wait for data address mark (ST412 ONLY). This bit causes the WD10C01A to pause until a data address mark is detected at the AMDET input. Bits 6-0 specify a timeout count that is the maximum number of byte times from the end of the ID field to the data address mark. The value field is used to specify the data pattern to compare against for byte sync. |

| 07       | 6   | R/W | WIAM - Wait for ID address mark (ST412 ONLY). This bit causes the WD10C01A to pause until an ID address mark is detected at the AMDET input. The value field is used to specify the data pattern to compare against for byte sync.                                                                                                                                     |

| 07       | 5   | R/W | WIX - Wait for index. Pauses until index is detected at the INDEX input.                                                                                                                                                                                                                                                                                               |

| 07       | 4   | R/W | WSM - Wait for sector mark. Pauses until sector mark is detected at the SECTOR input.                                                                                                                                                                                                                                                                                  |

| 07       | 0   | R/W | STOP - Stop immediate. This bit causes the command sequencer to immediately turn off all control outputs and return to the stopped state.                                                                                                                                                                                                                              |

TABLE 6-12. CWSEL of CONTROL BYTE ONE

# 6.3.6.5 Wait Condition Sequences

The following sequences are performed on the above wait conditions to ensure proper error handling:

# WDAM:

Wait for AMDET. If the byte count is exceeded, a sync error is recorded, and (if the control store FAIL bit is set) the command halts. When AMDET is detected correctly, the sequencer waits sixteen bit times for the sync byte in the value byte to be matched. The bit counter is decremented on each bit while the AMDET signal is active. If this bit count is exceeded, this is also a sync error. When a sync error occurs, the sequencer will stop or retry as defined by the control store FAIL and RTY bits. Checksum calculation starts when the sync byte is detected, and the sync byte is included in the calculation.

### WIAM:

Wait for AMDET. Since ID address marks could be found anywhere, there is no byte count, and the CPU must perform its own timeout. However, after AMDET is detected, the sequencer waits sixteen bit times for the sync byte in the value byte to be matched. The bit counter is decremented on each bit while the AMDET signal is active. If this bit count is exceeded, this is considered a sync error, and (if the control store RTY bit is set) a retry is performed (ID retry is discussed in a later section). Checksum calculation starts when the sync byte is detected, and the sync byte is included in the calculation.

# WIX and WSM: