Making the leading edge work for you WD2511/WD2840 Technical Package April, 1984

# WD2511/WD2840 Technical Package April, 1984

TABLE OF CONTENTS

| WD2511 X.25 Packet Network Interface (LAPB)  | 1  |

|----------------------------------------------|----|

| Application Note Using The WD2511            | 33 |

| WD2840 Local Network Token Access Controller | 53 |

| WD2840 Application Note                      | 89 |

WESTERN DIGITAL

i

#### WESTERN DIGITAL 0 Ρ

Т

Δ

1 0

0

# WD2511 X.25 Packet Network Interface (LAPB)

#### FEATURES

Packet switching controller, complies with CCITT Recommendation X.25, level 2, LAPB.

R

- Programmable primary timer (T1) and retransmission counter (N2).

- Programmable A-field which provides a wider range of applications than defined by X.25. These include: DTE-to-DTE connection, multipoint and loop-back testina.

- · Direct memory access (DMA) transfer: two channels: one for transmit and one for receive. Send/ receive data accessed by indirect addressing method. Sixteen output address lines.

- Zero bit insertion and deletion.

- Automatic appending and testing of FCS field.

- Computer bus interface structure: 8 bit bi-directional data bus. CS, WE, RE and four input address lines.

- DC to 1.1 MBPS data rate.

- TTL compatible. .

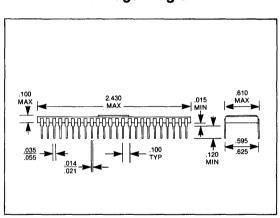

- 48 pin dual in-line packages.

N

A REFININA AV

WD2511

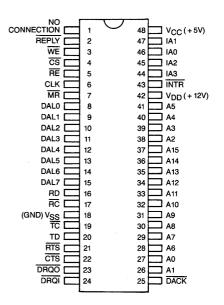

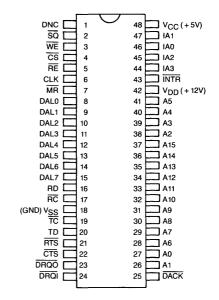

#### **PIN DESIGNATION**

#### DESCRIPTION

The WD2511 is a MOS/LSI device which handles bitoriented, full-duplex serial data communications with DMA, which conforms to CCITT X.25's LAPB with programmable enhancements.

The device is fabricated in N-Channel silicon gate MOS technology and is TTL compatible on all inputs and outputs.

#### APPLICATIONS

X.25 PACKET SWITCHING CONTROLLER PART OF DTE OR DCE PRIVATE PACKET NETWORKS LINK LEVEL CONTROLLER STORE AND FORWARD SYSTEM HIGH REL POINT TO POINT COMMUNICATIONS BIT ORIENTED PROTOCALS WITH BUILT IN DMA

# INTERFACE SIGNALS DESCRIPTION (All signals are TTL compatible.)

| 1       No Connection       Leave pin open.         2       REPLY       Reply       An active low output indicates the WD2511 either a CS•RE or a CS•WE input condition         3       WE       Write Enable       The data on the DAL are written into selected register when CS and WE are low.         4       CS       Chip Select       Active low chip select for CPU control of registers.         5       RE       Read Enable       The contents of the selected register is plat on DAL when CS and RE are low.         6       CLK       Clock       Clock input used for internal timing. Must square wave and should be greater than the KHz.         7       MR       Master Reset       Active low initializes the chip. All registers re to zero, except control bits MDISC and Ll which are set to 1. DACK must be stable hefore MR goes high.         8-15       DAL0-DAL7       Data Access Lines       An 8-bit bi-directional three-state data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ne<br>/O<br>ed<br>De<br>De<br>JK |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3       WE       Write Enable       either a CS•RE or a CS•WE input condition         3       WE       Write Enable       The data on the DAL are written into selected register when CS and WE are low.         4       CS       Chip Select       Active low chip select for CPU control of registers.         5       RE       Read Enable       The contents of the selected register is play on DAL when CS and RE are low.         6       CLK       Clock       Clock input used for internal timing. Must square wave and should be greater than the KHz.         7       MR       Master Reset       Active low initializes the chip. All registers reto zero, except control bits MDISC and LI which are set to 1. DACK must be stable hefore MR goes high.         8-15       DAL0-DAL7       Data Access Lines       An 8-bit bi-directional three-state data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ne<br>/O<br>ed<br>De<br>De<br>JK |

| 4       CS       Chip Select       selected register when CS and WE are low.         5       RE       Read Enable       Active low chip select for CPU control of registers.         6       CLK       Clock       Clock input used for internal timing. Must square wave and should be greater than the KHz.         7       MR       Master Reset       Active low initializes the chip. All registers reto zero, except control bits MDISC and Ll which are set to 1. DACK must be stable here         8-15       DAL0-DAL7       Data Access Lines       An 8-bit bi-directional three-state data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | /O<br>ed<br>De<br>DO<br>et<br>IK |

| 5       RE       Read Enable       registers.         5       RE       Read Enable       The contents of the selected register is plat on DAL when CS and RE are low.         6       CLK       Clock       Clock input used for internal timing. Must square wave and should be greater than the KHz.         7       MR       Master Reset       Active low initializes the chip. All registers reto zero, except control bits MDISC and Liwhich are set to 1. DACK must be stable here of the selected register is plate.         8-15       DAL0-DAL7       Data Access Lines       An 8-bit bi-directional three-state data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ed<br>De<br>DO                   |

| 6       CLK       Clock       Clock input used for internal timing. Must square wave and should be greater than the square wave and should | oe<br>00<br>iet<br>IK            |

| 7       MR       Master Reset       square wave and should be greater than the KHz.         7       MR       Master Reset       Active low initializes the chip. All registers reto zero, except control bits MDISC and Ling which are set to 1. DACK must be stable in before MR goes high.         8-15       DAL0-DAL7       Data Access Lines       An 8-bit bi-directional three-state data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00<br>iet<br>IK                  |

| 8-15       DAL0-DAL7       Data Access Lines       An 8-bit bi-directional three-state data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IK                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

| CPU and DMA controlled transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | or                               |

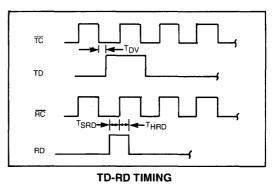

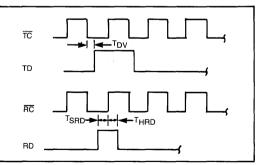

| 16 RD Receive Data Receive serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                  |

| 17         RC         Receive Clock         This is a 1x clock input. RD is sampled on rising edge of RC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ıe                               |

| 18 VSS Ground Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| 19 TC Transmit Clock A 1x clock input. TD changes on the fall edge of TC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ıg                               |

| 20 TD Transmit Data Transmit serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |

| 21 RTS Request-To-Send An open collector (drain) output which g<br>low when the WD2511 is ready to trans<br>either flags or data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

| 22 CTS Clear-To-Send An active low input which signals the WD2 that transmission may begin. If high, the output is forced high. May be hard-wired ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | D                                |

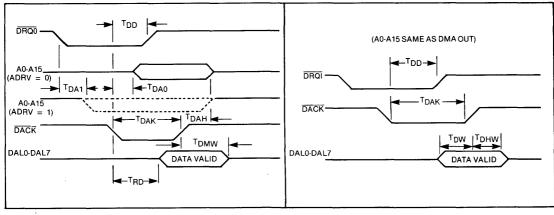

| 23 DRQO DMA Request Out An active low output signal which initiates C bus request so the WD2511 can output d onto the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |

| 24 DRQI DMA Request In An active low output signal which intitia CPU bus request so that data may be input the WD2511.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |

| 25 DACK DMA Acknowledge An active low input from the CPU in response<br>to DRQI or DRQO. DACK must not be low if<br>and RE are low or if CS and WE are low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | se<br>XS                         |

| 27, 26,<br>38-41,<br>28-37A0-A15Address Lines OutSixteen address outputs from the WD2511<br>DMA operation. If the control bit ADRV is 1;<br>outputs are TTL drives at all times. If ADRV is the outputs are three-state, and are HI-Z where the ver DACK is high. (ADRV is in Control Ret<br>ter #1.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | he<br>0,<br>•n-                  |

| 42 VDD Power Supply + 12VDC power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |

WD2511

#### INTERFACE SIGNALS DESCRIPTION CONTINUED (All signals are TTL compatible.)

| PIN<br>NUMBER     | SYMBOL  | PIN NAME          | FUNCTION                                                                                                                                                                               |

|-------------------|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43                | İNTR    | Interrupt Request | An active low interrupt service request output.<br>Returns to high when Status Register #1 is read.                                                                                    |

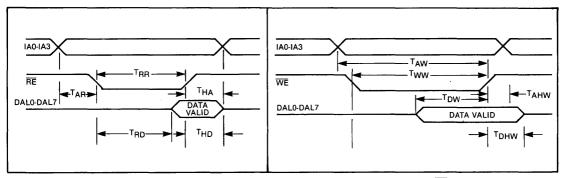

| 46, 47,<br>45, 44 | IA0-IA3 | Address Lines In  | Four address inputs for CPU controlled read/<br>write operation of the I/O registers in the<br>WD2511. If ADRV = 0, these may be tied to A0-<br>A3. (ADRV is in Control Register = 1.) |

| 48                | Vcc     | Power Supply      | + 5VDC power supply input.                                                                                                                                                             |

#### ORGANIZATION

Note: See appendix D for a glossary of terms used throughout this document.

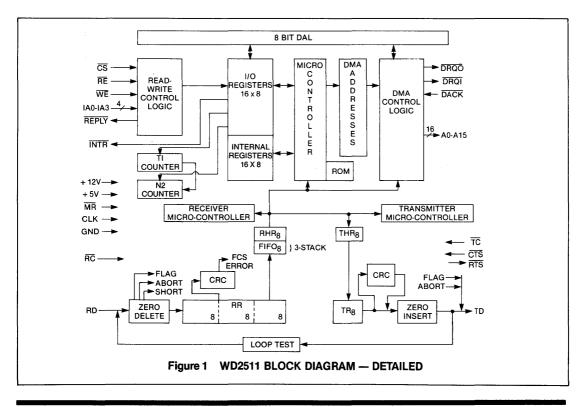

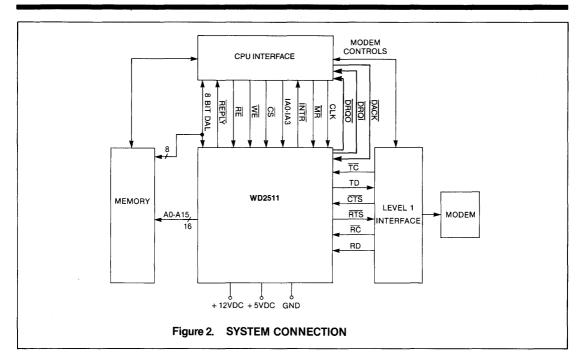

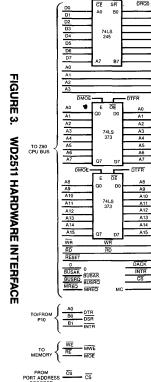

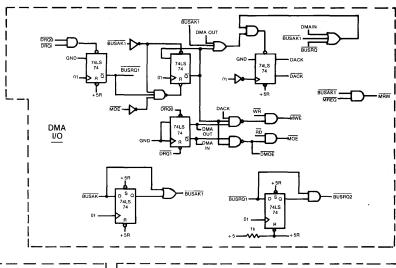

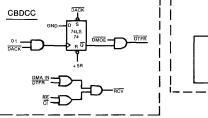

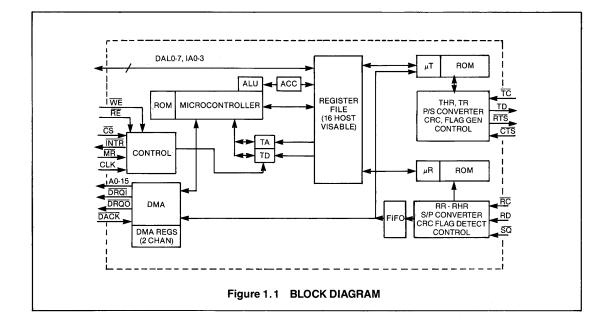

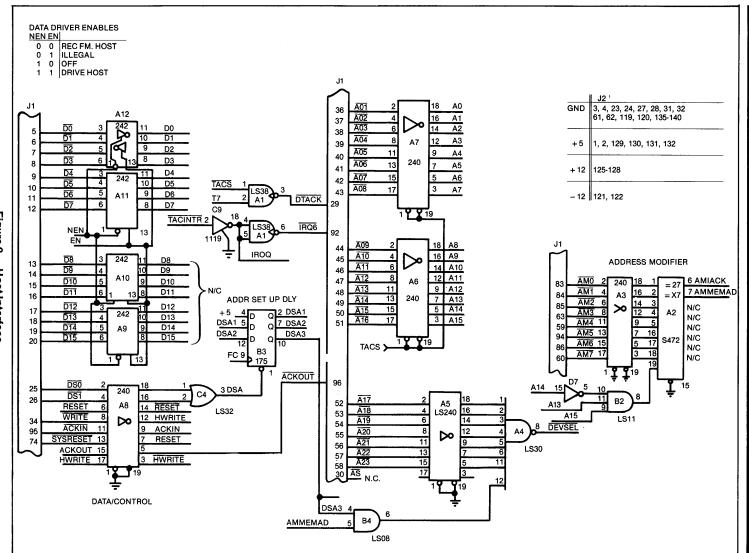

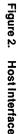

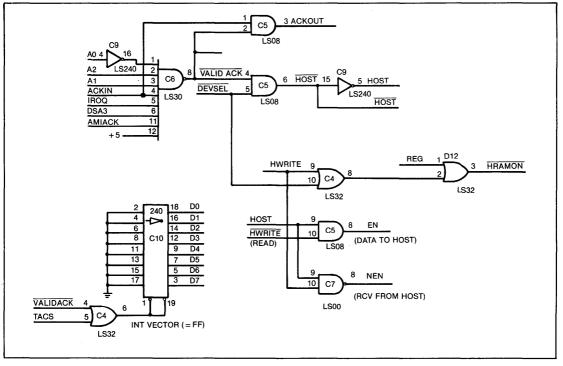

A detailed block diagram of the WD2511 is shown in Figure 1.

Mode control and monitor of status by the user's CPU is performed through the Read/Write Control circuit which reads from or writes into I/O registers addressed by IA0-IA3.

Transmit and receive data are accessed through the DMA control. Serial data is generated and received by the bit-oriented controllers.

Internal Control of the WD2511 is by means of three internal microcontrollers; one for transmit, one for

receive, and one for overall control.

Parallel transmit data are entered into the Transmitter Holding Register (THR), and then presented to the Transmitter Register (TR) which converts the data to a serial bit stream. The Cyclic Redundancy Check (CRC) is computed in the 16-bit CRC register, and the result becomes the transmitted Frame Check Sequence (FCS).

Parallel receive data enters the Receiver Holding Register (RHR) from the 24-bit serial Receiver Register (RR). The 24-bit length of RR permits stripping of the FCS prior to transfer in to the RHR. The receiver CRC register is used to test the validity of the received FCS. A 3-stack FIFO is included in the receiver.

#### FRAME FORMAT

The WD2511 performs "bit-oriented" data communications control. According to the general format for bit-oriented procedures (HDLC, SDLC, ADCCP), each serial block of data is called a frame.

Each frame starts and ends with a Flag (0111110). A single flag may be used both as the closing flag of one frame and the opening flag of the next frame. In between flags, data transparency is provided by the insertion of a 0 bit after all sequences of 5 contiguous 1 bits. The receiver will strip the inserted 0 bits. The last 16-bits before the closing flag is in the Frame Check Sequence (FCS). Each frame also includes address and control fields (A and C fields).

The FCS calculation includes all data between the opening flag and the first bit of the FCS, except for 0's inserted for transparency. The 16-bit FCS has the following characteristics:

After the frame is received, if there were no errors then the remainder in the CRC register (internal in the WD2511) will be:

#### 1111000010111000 FOB8

The WD2511 generates and tests the Flag, FCS, A-Field, C-Field, and performs zero bit insertion and deletion.

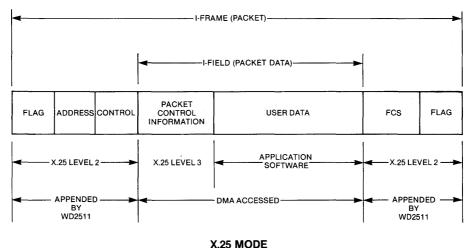

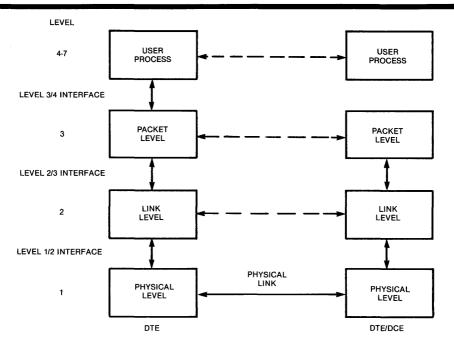

According to the X.25 protocol, there are three types of frames: supervisory (S-frame), un-numbered (U-frame), and information (I-frame). The WD2511 performs frame level (level 2) link access control. All S- and U-frames are automatically generated and tested by the WD2511. The user need only be concerned with the I-frames, which are packets.

The WD2511 will transmit contiguous flags for interframe time fill (full duplex mode).

X.25 MUDI

NOTE: X.25 Level 1, is the Physical Interface

#### **II. PROGRAMMING THROUGH REGISTERS**

The WD2511 is controlled and monitored by sixteen I/O registers.

Control, status, and error bits will be referred to as CR, SR, or ER, respectively, along with two digits. For example, SR16 refers to status register #1 and bit 6, which is "XBA."

#### **REGISTER DEFINITION**

| REG<br># | IA3 | IA2 | IA1 | IA0 | REGISTER                  | REGISTER<br>GROUPING |

|----------|-----|-----|-----|-----|---------------------------|----------------------|

| 0        | 0   | 0   | 0   | 0   | CR0                       |                      |

| 1        | 0   | 0   | 0   | 1   | CR1                       |                      |

| 2        | 0   | 0   | · 1 | 0   | *SR0                      | OVERALL CONTROL      |

| 3        | 0   | 0   | 1   | 1   | *SR1                      | AND<br>MONITOR       |

| 4        | 0   | 1   | 0   | 0   | *SR2                      | MONITOR              |

| 5        | 0   | 1   | 0   | 1   | *ER0                      |                      |

| 6        | 0   | 1   | 1   | 0   | *CHAIN MONITOR            | RECEIVER             |

| 7        | 0   | 1   | 1   | 1   | *RECEIVED C-FIELD         | MONITOR              |

| 8        | 1   | 0   | 0   | 0   | T1                        | ТИГО                 |

| 9        | 1   | 0   | 0   | 1   | N2/T1                     | TIMER                |

| A        | 1   | 0   | 1   | 0   | TLOOK HI                  |                      |

| В        | 1   | 0   | 1   | 1   | TLOOK LO                  |                      |

| С        | 1   | 1   | 0   | 0   | CHAIN/BUFFER SIZE         | DMA SET-UP           |

| D        | 1   | 1   | 0   | 1   | NOT USED                  |                      |

| E        | 1   | 1   | 1   | 0   | XMT COMMAND "E"           | "A" FIELD            |

| F        | 1   | 1   | 1   | 1   | XMT RESPONSE "F" (Note 1) | A FIELD              |

\*CPU READ ONLY. (Write Not Possible)

#### NOTE:

1. Registers E and F should be set-up while MDISC = 1.

# CONTROL, STATUS, ERROR REGISTERS

|          |                  |                  |                    | BIT #              |              |      |      |       |

|----------|------------------|------------------|--------------------|--------------------|--------------|------|------|-------|

| REGISTER | 7                | 6                | 5                  | 4                  | 3            | 2    | 1    | 0     |

| CR0      | ADISC            | 0                | H/F                | ACTIVE/<br>PASSIVE | LOOP<br>TEST | RAMT | RECR | MDISC |

| CR1      | ТХМТ             | TRCV             | XI                 | ADRV               | 0            | 0    | 0    | SEND  |

| SR0      | NA2              | NA1              | NA0                | RNRR               | NB2          | NB1  | NB0  | RNRX  |

| SR1      | <sup>1</sup> PKR | <sup>1</sup> XBA | <sup>1</sup> ERROR | 0                  | NE2          | NE1  | NE0  | 0     |

| SR2      | T1OUT            | IRTS             | REC<br>IDLE        | 0                  | 0            | 0    | 0    | LINK  |

| ER0      | ER07             | ER06             | ER05               | ER04               | ER03         | ER02 | ER01 | ER00  |

1 Causes Interrupt (INTR Goes Low).

# **CONTROL REGISTER 0**

|          |       |                                                                                                                                                                                                                                                |                              | 001111021      | Laistenv     |             |                |            |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|--------------|-------------|----------------|------------|

| REGISTER | CR07  | CR06                                                                                                                                                                                                                                           | CR05                         | CR04           | CR03         | CR02        | CR01           | CR00       |

| CR0      | ADISC | 0 H/F ACTIVE/ LOOP RAMT RECR                                                                                                                                                                                                                   |                              |                |              |             |                |            |

| BIT      |       |                                                                                                                                                                                                                                                |                              | DE             | SCRIPTION    | •           |                |            |

| CR00     |       | MDISC (man<br>link. No DMA<br>Reset, MDIS<br>until MDISC                                                                                                                                                                                       | accessed d<br>C will be set. | ata will be tr | ansferred as | long as MD  | ISC = 1. Af    | ter Master |

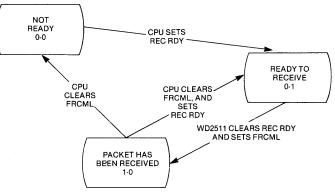

| CR01     |       | RECR (Receiver Ready) indicates the CPU's is receiver buffer is Ready (CR01 = 1). If RECR = 1, the WD2511 may begin receiving I-frames. (See SR00)                                                                                             |                              |                |              |             |                |            |

| CR02     |       | RAMT — Internal Register Test when set. (See Self Tests)                                                                                                                                                                                       |                              |                |              |             |                |            |

| CR03     |       | The LOOP TEST bit will connect the transmit data output to the receive data input. The receiver input pins RD and RC are then logically disconnected from the internal circuitry. The "E" and "F" data registers of the A-field must be equal. |                              |                |              |             |                |            |

| CR04     |       | The Active/Passive bit when set, in conjunction with $MDISC = 0$ , will cause the $WD2511$ to initiate link set-up. When this bit is reset, the $WD2511$ will wait for a link setup from the remote station.                                   |                              |                |              |             |                |            |

| CR05     |       | H/F selects full duplex if CR05 = 0, and half duplex if CR05 = 1. (See Appendix A).                                                                                                                                                            |                              |                |              |             |                |            |

| CR06     |       | Unused conti                                                                                                                                                                                                                                   | rol bits shoul               | d remain at 0  |              |             |                |            |

| CR07     |       | ADISC (disco<br>ates link set-u<br>the SABM if (                                                                                                                                                                                               | up, a ÓISC w                 | ill be transmi | tted and ack | nówledged p | prior to trans |            |

|          |      |                                                                                                                                     |                                                                                                | CONTROL I                                                                                         | REGISTER 1                                                                                     |                                                                            |                                                                                     |                                                                       |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| REGISTER | CR17 | CR16                                                                                                                                | CR15                                                                                           | CR14                                                                                              | CR13                                                                                           | CR12                                                                       | CR11                                                                                | CR10                                                                  |

| CR1      | TXMT | TRCV XI ADRV 0 0 0 SE                                                                                                               |                                                                                                |                                                                                                   |                                                                                                |                                                                            |                                                                                     | SEND                                                                  |

| BIT      |      |                                                                                                                                     |                                                                                                | DE                                                                                                | SCRIPTION                                                                                      |                                                                            |                                                                                     |                                                                       |

| CR10     |      | The SEND bi<br>SEND = 1, t<br>transmission.<br>= 1, the WD2<br>buffer. After tr<br>reads BRDY c<br>is cleared, and<br>should set SE | he WD2511 v<br>If BRDY = 0<br>2511 will then<br>ansmission,<br>of the next se<br>d transmissio | will read fron<br>D, the WD251<br>read TSADF<br>the WD2511 of<br>gment. If 1, th<br>on of packets | n TLOOK the<br>1 will clear S<br>3 and TCNT, t<br>clears BRDY<br>ne next segm<br>is stopped. A | BRDY bit o<br>END and no<br>followed by t<br>of the segme<br>ent is transm | f the next se<br>action occur<br>he transmiss<br>nt just transr<br>itted. If 0, the | egment for<br>s. If BRDY<br>sion of that<br>nitted, and<br>e SEND bit |

| CR11-13  |      | Unused bits,                                                                                                                        | write in 0's.                                                                                  |                                                                                                   |                                                                                                |                                                                            |                                                                                     |                                                                       |

| CR14     |      | The ADRV (A<br>If ADRV = 0,<br>= 1, the outp<br>when DRQO,                                                                          | the outputs a<br>outs are alwa                                                                 | ire tri-state ar<br>ys low imped                                                                  | nd are in HI-Z<br>ance (TTL), a                                                                | , except whe                                                               | n DACK is lo                                                                        | w. If ADRV                                                            |

| CR15     |      |                                                                                                                                     | rame ≥ 3 byte                                                                                  | Used when T<br>es excluding<br>es excluding                                                       | FCS and Flag                                                                                   |                                                                            |                                                                                     |                                                                       |

| CR16     |      | TRCV — Tra                                                                                                                          | nsparent Re                                                                                    | ceive. Rece                                                                                       | ve all frame                                                                                   | s including                                                                | unknown fra                                                                         | ames. See                                                             |

#### STATUS REGISTER 0

|          |      |                                                                                                                               |      | • • • • • • • |      |      |      |      |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------|------|---------------|------|------|------|------|

| REGISTER | SR07 | SR06                                                                                                                          | SR05 | SR04          | SR03 | SR02 | SR01 | SR00 |

| SR0      | NA2  | NA1                                                                                                                           | NA0  | RNRR          | NB2  | NB1  | NBO  | RNRX |

| BIT      | 1    | DESCRIPTION                                                                                                                   |      |               |      |      |      | •    |

| SR00     |      | RNRX. An RNR has been transmitted or will be at next opportunity. The CPU should set RECR when receive buffers are available. |      |               |      |      |      |      |

| SR03-SR0 | 1    | NB2-NB0. Next block to be transmitted.                                                                                        |      |               |      |      |      |      |

| SR04     |      | RNRR. This bit is set when an RNR frame is received. Once set, it is cleared when an RR, REJ, SABM, or UA is received.        |      |               |      |      |      |      |

| SR07-SR0 | 5    | NA2-NA0. Next block of transmitted data to be Acknowledged.                                                                   |      |               |      |      |      |      |

TXMT — Transparent transmit. See Appendix A.

Appendix A.

**CR17**

WD2511

|          |      |                                                                                                                                                                                                                                                                               | STAT                                                | US REGISTI  | ER 1          |               |              |      |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-------------|---------------|---------------|--------------|------|

| REGISTER | SR17 | SR16                                                                                                                                                                                                                                                                          | SR15                                                | SR14        | SR13          | SR12          | SR11         | SR10 |

| SR1      | 1PKR | 1XBA                                                                                                                                                                                                                                                                          | 1ERROR                                              | 0           | NE2           | NE1           | NE0          | 0    |

| BIT      |      |                                                                                                                                                                                                                                                                               |                                                     | DE          | SCRIPTION     |               |              |      |

| SR10     |      | 0 (not used)                                                                                                                                                                                                                                                                  |                                                     |             |               |               |              |      |

| SR13-SR1 | 1    | NE2-NE0. Ne                                                                                                                                                                                                                                                                   | ext Expected                                        | oacket numb | er and next I | RLOOK segn    | nent number. |      |

| SR14     |      | 0 (not used)                                                                                                                                                                                                                                                                  |                                                     |             |               |               |              |      |

| SR151    |      | The ERROR bit indicates: 1) An error has occurred which is not recoverable by the WD2511 or 2) A significant event has occured.                                                                                                                                               |                                                     |             |               |               |              |      |

|          |      | For the specific reason for the ERROR bit being set, see error register (ER0) on next page.                                                                                                                                                                                   |                                                     |             |               |               |              |      |

| SR161    |      | The XBA (transmitted block acknowledgement) bit set, indicates that a previously trans-<br>mitted Block, or Blocks, have been acknowledged by the remote device. Upon acknowl-<br>edgement, the ACK'ED bit is set to "1" for each segment in TLOOK which was<br>acknowledged. |                                                     |             |               |               |              |      |

| SR171    |      | error-free and                                                                                                                                                                                                                                                                | stands for Pac<br>d in correct se<br>ced in the hos | quence acco | ording to the | received N (S |              |      |

#### NOTE 1:

WD2511

The three interrupt-causing bits are SR17, SR16, and <u>SR15</u>. Any of the three will cause an interrupt request (INTR goes low). After SR1 is read, all three bits are reset to 0, and INTR returns to high.

|          |            |                                                                                                                                                      | 3141          | US REGIST                   |                 |              |             |      |  |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|-----------------|--------------|-------------|------|--|

| REGISTER | SR27       | SR26                                                                                                                                                 | SR25          | SR24                        | SR23            | SR22         | SR21        | SR20 |  |

| SR2      | T1OUT IRTS |                                                                                                                                                      | REC<br>IDLE   | 0                           | 0               | 0            | 0           | LINK |  |

| BIT      |            |                                                                                                                                                      | DESCRIPTION   |                             |                 |              |             |      |  |

| SR20     |            | If the link is ea                                                                                                                                    | stablished, L | $\overline{INK} = 0.$ If th | e link is logio | ally disconn | ected, LINK | = 1. |  |

| ST24-21  |            | Unused Bits — 0.                                                                                                                                     |               |                             |                 |              |             |      |  |

| SR25     |            | REC IDLE (Receiver Idle) indicates that the WD2511 has received at least 15 contiguous 1's.                                                          |               |                             |                 |              |             |      |  |

| SR26     |            | IRTS stands for the Internal Request-To-Send bit, and indicates that the transmitter is attempting (successful or not) to send either data or flags. |               |                             |                 |              |             |      |  |

| SR27     | ×          | T1OUT bit me<br>When T1OUT<br>in between in                                                                                                          | = 1, T1 is no | ot running. No              | OTE: This bit   | could be a 1 |             |      |  |

# STATUS REGISTER 2

8

#### ERROR REGISTER (ER0)

| HEX<br>VALUE | ERROR/EVENT                                                                                                                                                                                      |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02           | Receiver overrun. The Receiver Register (RR) had a character to load into the FIFO but the FIFO was full. See note 2.                                                                            |

| 04           | Transmitter underrun. The Transmitter (TR) needed a character from the Transmitter Hold-<br>ing Register (THR) but the THR was not ready. The frame being transmitted is aborted. See<br>note 2. |

| 10           | RLOOK not ready. REC RDY bit of next segment is 0 but RECR = 1. This interrupt will not occur if RECR = 0.                                                                                       |

| 21           | Link is up. Was down.                                                                                                                                                                            |

| 22           | DISC sent. REC IDLE for time T1xN2.                                                                                                                                                              |

| 24           | DISC sent. SABM sent N2 times without receiving UA.                                                                                                                                              |

| 30           | Received DISC or DM while link was up.                                                                                                                                                           |

| 41           | Going to next chain segment.                                                                                                                                                                     |

| 42           | Next chain segment of the Receiver was not ready.                                                                                                                                                |

| 80           | Link reset (SABM) received.                                                                                                                                                                      |

| 88           | S-command sent N2 times without acknowledgement.                                                                                                                                                 |

| CO           | Frame Reject (FRMR) received. See note 1.                                                                                                                                                        |

| C1           | Frame Reject (FRMR) transmitted. See note 3. The received C-field (returned in the first<br>I-field byte of the FRMR frame) was invalid.                                                         |

| C3           | Frame Reject (FRMR) transmitted. See note 3. The received and rejected frame contained<br>an I-field which is not permitted with this frame type.                                                |

| C4           | Frame Reject (FRMR) transmitted. See note 3. Received I-field exceeded the total amount<br>of I-field data bytes established in Register C.                                                      |

| C8           | Frame Reject (FRMR) transmitted. See note 3. The received frame contained an invalid $N(R)$ .                                                                                                    |

#### NOTES:

- Whenever a Frame Reject (FRMR) is received, the I-field will have been placed in the appropriate memory location by the DMA. A link reset (SABM) will be transmitted. The NB is not advanced.

- Receiver overrun and Transmitter underrun are indication that the TC/RC clocks are either too fast for the WD2511, or the DACK response is too slow, or both.

- 3. As a result of FRMR transmitted, a SABM is received, causing link reset. In this case, only the Frame Reject interrupt is indicated.

#### W, X, Y, Z OF FRMR

A frame reject (FRMR) contains a three byte I-field. The first byte is the rejected frame control field. The second byte contains the current N(S) and N(R) counts of the station reporting the reject condition. The third byte contains W-X-Y-Z-0-0-0 where W is the LSB.

W set to 1 indicates that the control field received and returned in the first I-field byte was invalid.

X set to 1 indicates the rejected frame contained an I-field which is not permitted with this command.

W is also set to 1 in this case.

Y set to 1 indicates the received I-field exceeded the maximum I-field data byte count established (CHAIN/ BUFFER SIZE). Y is mutually exclusive with W.

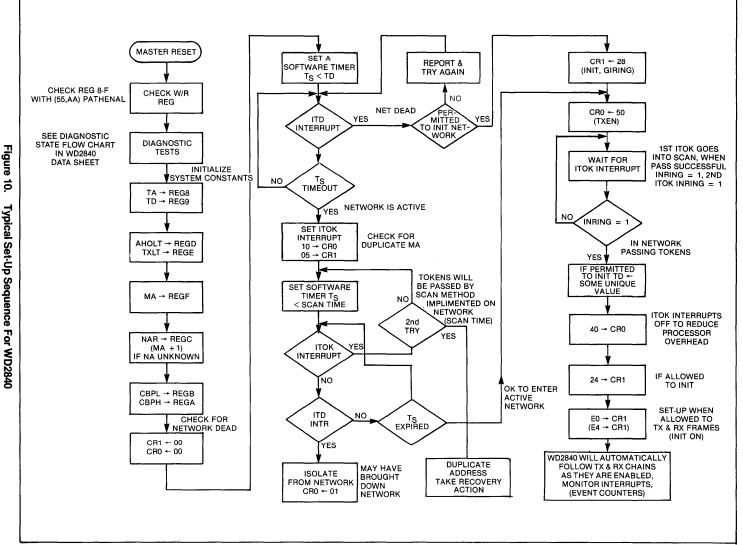

Z set to 1 indicates the received control field contained an invalid N(R). Z is mutually exclusive with W.