## PRELIMINARY DATA October 1988

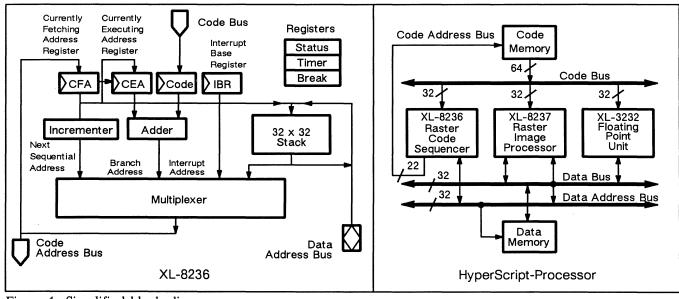

The WEITEK XL-8236 is a fullyintegrated CMOS 22-bit raster code sequencer. It is used with the WEITEK XL-8237 32-bit raster image processor to make the HyperScript-Processor™, a highperformance graphics CPU capable of driving raster printers at up to 60 pages per minute. WEITEK's single-precision floating point unit may also be used to produce a tightly-coupled raster image printing system.

| Contents                  |           |

|---------------------------|-----------|

| Features                  | 1         |

| Description               | 1         |

| Block Diagram             | 2         |

| Signal Description        | 3         |

| Architecture              | 5         |

| Stack                     | 6         |

| Registers                 | 7         |

| Neutralization            | 9         |

| STALL-                    | 10        |

| Interrupts                | 10        |

| RESET-                    | 18        |

| Instruction Set           | 19        |

| Instruction Interaction   | 57        |

| OP Output Bus Operation   | 61        |

| Development Tools         | 63        |

| Design Requirements       | 63        |

| Ratings and DC Specificat | ions 64   |

| AC Specifications         | 65        |

| Timing Description        | 66        |

| I/O Characteristics       | 68        |

| Pin Configuration         | 69        |

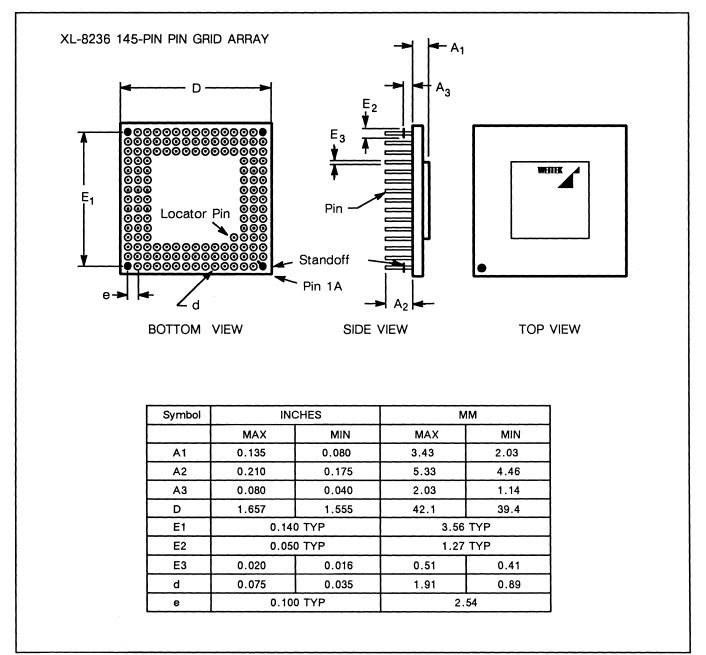

| Physical Dimensions       | 70        |

| Ordering Information      | 71        |

| Revision Summary          | 71        |

| Index                     | 72        |

| Documentation Request Fo  | orm 75    |

| Sales Offices ba          | ack cover |

|                           |           |

The masters for this document were printed on an XL-8200 development system

XL-8236 Raster Code Sequencer Data Sheet October, 1988

Copyright ©WEITEK Corporation 1988 All rights reserved

WEITEK Corporation 1060 East Arques Avenue Sunnyvale, California 94086 Telephone (408) 738-8400

WEITEK is a trademark of WEITEK Corporation

PostScript is a registered trademark of Adobe Systems, Incorporated BITSTREAM and FontWare are trademarks of BITSTREAM Corporation UNIX is a trademark of AT&T Bell Laboratories XENIX and MS-DOS are trademarks of Microsoft Corporation NIMBUS is a registered trademark of URW Corporation

WEITEK reserves the right to make changes to these specifications at any time

Printed in the United States of America 90 89 88 6 5 4 3 2 1

### PRELIMINARY DATA October 1988

### Features

22-BIT SINGLE-CHIP SEQUENCING UNIT

22-bit code address bus 32-bit data address bus  $33 \times 32$ -bit on-chip stack

#### HIGH PERFORMANCE

10 to 60 page per minute with WEITEK's HyperScript interpreter Low-power CMOS with TTL-compatible I/O

POWERFUL DEVELOPMENT TOOLS

PostScript-compatible interpreter C compiler Graphics development system

### Description

The XL-8236 is a high-performance 22-bit raster code sequencer (RCS). The XL-8236 combines with its companion chip, the XL-8237 raster image processor (RIP), to make the XL-8200 HyperScript-Processor, a cost-effective graphics CPU for raster printing applications over a wide performance range. The most typical use of a HyperScript-Processor is in a PostScript-language laser printer.

HyperScript-Processors are graphics RISC processors that combine Harvard architecture, single-cycle instruction execution, and specialized math and bit manipulation functions to make a high-speed grapics processor, capable of interpreting the complex Post-Script language on high-speed printers. The XL-8236 provides instruction sequencing and other control func-

**BUILT-IN REGISTERS AND TIMERS**

TRAP AND INTERRUPT HANDLING

Breakpoint register

Status register

System reset

32-bit programmable timer

Three external interrupt lines

Five internal exceptions

The XL-8236 is a CMOS device offering high performance and low power consumption, with TTL-compatible I/O. It is available in a standard 145-pin ceramic or plastic PGA (Pin Grid Array) package.

tions. The XL-8237 provides data addressing, arithme-

tic, logical, and bit-manipulation fuctions.

Figure 1. Simplified block diagrams

© Copyright WEITEK 1988 All rights reserved

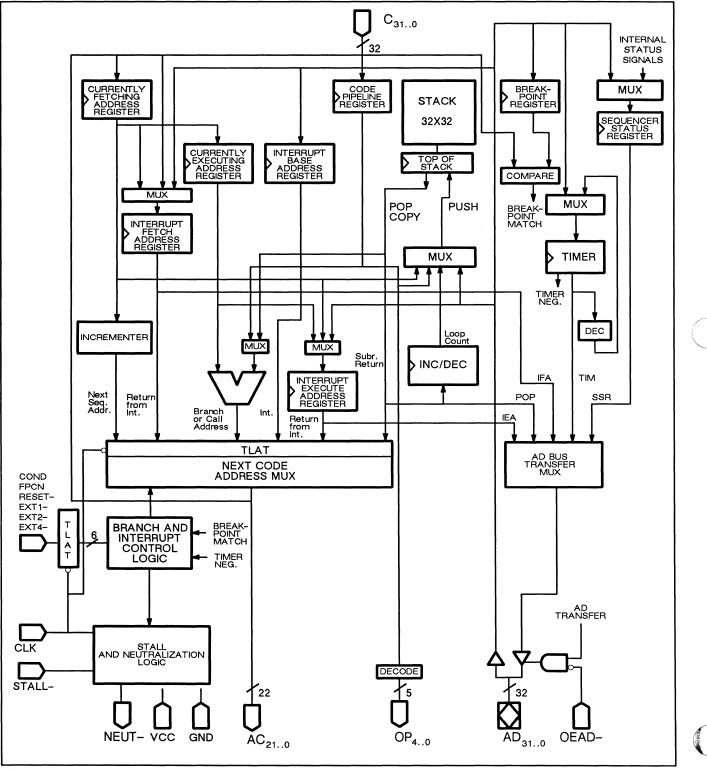

# **Block Diagram**

Figure 2. Block diagram

## **Signal Description**

### C BUS

The  $C_{31..0}$  code input bus is driven by the code memory with the 32-bit instruction word. The code word is latched by the RCS at the rising edge of the clock. Because it contains a built-in pipeline register, it is not necessary to use an external pipeline register between code memory and the XL-8236.

### AC BUS

The  $AC_{21..0}$  code address output bus is driven by the program sequencing unit. It sends a 22-bit instruction address to the code memory. The code address is not latched by the RCS, so an external address latch is needed between the AC bus and code memory.\* Unused high-order bits of the AC bus can be left floating.

The AC bus is driven on every cycle (even when STALL-, or NEUT- are asserted) unless disabled with the OEAC- signal.

The AC bus produces instruction addresses, not byte addresses.

### AD BUS

The  $AD_{31..0}$  data address bus provides addresses for data memory operations (the data is transferred over the D bus to the RIP). It is also used for intra-processor communication. It connects the integer processing unit to the sequencer. The AD bus can also be used as a bidirectional data bus for transfers to and from other hardware.

All 32 bits of the AD bus need to be attached between the RCS and RIP to allow intra-processor data transfer. This traffic may take place during STALL- or NEUT cycles, and it is important that it not be interfered with. If any external device wishes to write to memory asynchronously to the XL-Series devices, it must not write directly to the AD bus.

Addresses on the AD bus are byte addresses.

#### OP BUS

The  $OP_{4..0}$  output bus indicates the type of instruction that is executing, and can be used to control external

hardware. The memory system must decode the OP bus outputs to determine when to read, when to write, and when to latch the data address. In addition, fifteen of the 32 OP combinations are used to signal loads or stores to "external registers" 0-14, which can be any external hardware. These external register transfers take place over the AD bus.

### EXT1-, EXT2-, and EXT4-

Level-sensitive interrupt request inputs. The current instruction is allowed to complete and execution proceeds from one of the interrupt vectors. External interrupts can be enabled and disabled in the sequencer status register. Interrupt signals are examined at the rising edge of the clock.

EXT4- is used as a floating point exception interrupt in systems with the XL-3232 FPU.

There is no EXT3-.

Interrupt signals must be held until acknowledged.

#### RESET-

A level-sensitive input that resets the sequencer and causes a branch to address 0. The sequencer status register is initialized as described on page 18. The other registers in the chip are undefined. Registers that can cause exceptions (such as the timer and breakpoint registers) must be initialized before their exceptions are enabled.

Reset is not useful as a non-maskable interrupt.

#### CLK

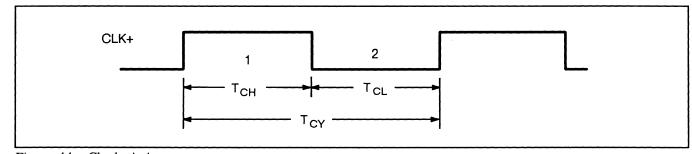

The Clock input, CLK, is a single-phase TTL-level clock signal.

#### NEUT-

2

NEUT- (neutralize) is an output signal that goes from the RCS to the RIP and FPU. It is not normally used by hardware outside the processor chip set. NEUT- is asserted by the sequencer, and instructs all XL devices to cancel their current instructions. This is done on transfer-of-control instructions (including branches, calls, and interrupts) to prevent the instruction in the pipeline from being executed. All XL-Series chips must have their NEUT- lines tied together.

<sup>\*</sup> Note that a latch, not a register, should be used. Future versions of the XL-8236 may contain an on-chip address latch.

## Signal Description, continued

## STALL-

STALL- is a "not-ready" input line that causes the current code fetch to be retried on the next cycle. The instruction that was to be executed on the next cycle is canceled (but the current instruction is allowed to complete). STALL- is typically used by the code memory subsystem when the requested code word cannot be read in the current cycle.

The XL chips each cancel their currently fetching instruction, and fetch the instruction again on the next cycle, and on every cycle that STALL- is asserted. The fetched instruction will be executed when STALL- is de-asserted.

All the XL-Series chips must have their STALL- lines tied together.

## COND

Condition code input. Goes from the RIP to the RCS. Not normally used outside the processor chip set.

### FPCN

Floating point condition code input. This signal goes from the floating point processor to the RCS. In sys-

tems without a floating point processor FPCN is tied to ground.

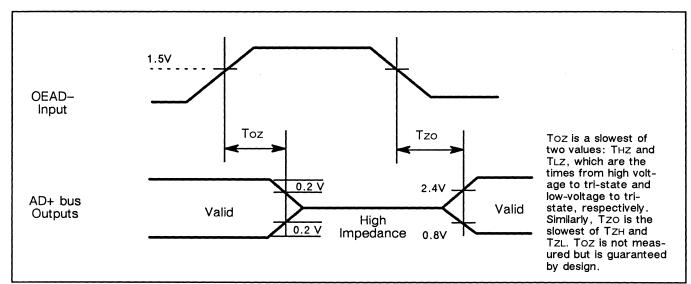

### OEAD-

OEAD- is an asynchronous output enable signal for the AD bus. The bus is at a high-impedance state when disabled.

## VCC AND GND

VCC is a +5.0 volt supply. GND is a system ground. All VCC and GND pins must be connected—floating pins are not allowed.

### NC

No connection (must be left floating). Reserved for future expansion.

## TIE HIGH

This signal line is reserved for future expansion. It should be tied to VCC.

## TIE LOW

This signal line is reserved for future expansion. It should be tied to GND.

#### PRELIMINARY DATA October 1988

### Architecture

### BUSES

The XL-8236 uses three buses: the C bus (32 bits), the AC bus (22 bits), and the AD bus (32 bits). The AC (code address) bus is used to address code memory. The AD (data address) bus can be used to transfer data between the RCS registers and the rest of the system, including the XL-8237 RIP, and to save and restore the stack externally. The XL-8237 RIP also uses this bus as a data address bus. The C (code) bus provides the instructions for both the RCS and the RIP.

#### PIPELINING

The XL-8236 instruction sequence is pipelined. In each clock cycle, the next instruction is fetched while the current instruction is being executed. This parallel fetch/execute architecture allows faster execution than the usual sequential fetch/execute architecture.

#### INSTRUCTION SET

The instruction set contains branch, conditional branch, subroutine call and return, software interrupt and interrupt return, loop control, and coprocessor control instructions.

#### INTERRUPT CONTROL

There are three external interrupt lines, plus reset. Interrupts can be masked individually and collectively, with the individual interrupt enable and master interrupt enable bits in the sequencer status register.

Interrupts are vectored to one of fifteen addresses.

#### MEMORY CONTROL

The RCS's memory interface is controlled by the STALL- input.

STALL- is used to cancel instructions in the event of delayed code memory word. It is typically used with dynamic RAM and memory caches. External hardware detects memory faults and asserts STALL- until the data is available.

In addition to these two input signals, the RCS has a five-bit OP output bus. The OP bus identifies the current state of the memory interface.

### CONTROL FLOW

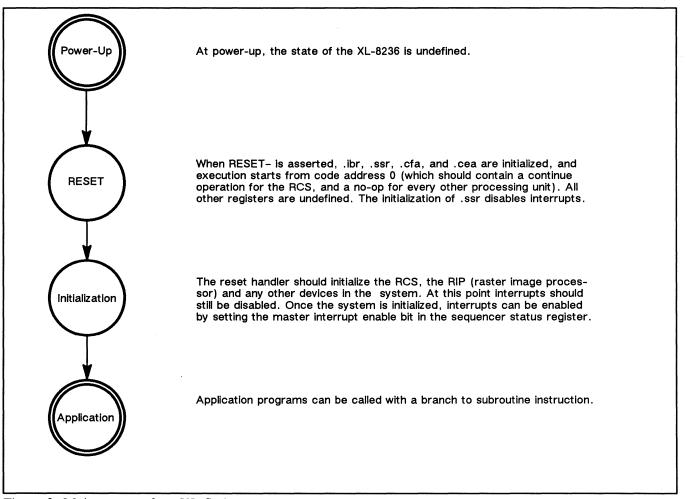

Figure 3 shows the major states of the system: at power-up, at reset, and in applications programs.

## Architecture, continued

Figure 3. Major states of an XL-Series system

## Stack

The RCS has a 33-word-deep by 32-bit-wide register file addressed as a stack. The stack may contain loop counts, branch addresses, and subroutine return addresses. The stack consists of a 32-bit top-of-stack register (.tos), a 32-word by 32-bit register file, and a stack pointer, which is a 5-bit field within the sequencer status register (.ssr).

On reset, the stack pointer is initialized with all 1's (a value of 31), indicating an empty stack. The stack pointer is a modulo-32 counter which increments before each push and decrements after each pop.

Stack underflow and overflow exceptions are provided. An underflow exception occurs when a pop operation nearly empties the stack. An overflow exception is generated when a push operation nearly fills the stack. (For more details, see sections *Stack Overflow* and *Stack Underflow* on page 15.)

A pair of exception routines can implement a larger stack in system memory. When the RCS stack overflows, it is copied to the main memory stack; when it underflows, data in the memory stack is restored to the RCS stack.

PRELIMINARY DATA October 1988

## Registers

## FETCH AND EXECUTION ADDRESS REGISTERS

The sequencer fetches an instruction on every cycle, and executes it on the following cycle. The instruction cancellation mechanism allows the results of an instruction to be discarded after the instruction has completed, effectively turning the instruction into a no-op, but the chip is never idle.

The currently executing address (.cea) register is a 22-bit register containing the address of the instruction currently being executed. This is the instruction that was fetched on the previous cycle.

The currently fetching address (.cfa) register is a 22-bit register containing the address of the instruction being fetched. This instruction will be executed on the next cycle, and the address in the .cfa will be copied into the currently executing register (.cea).

### INTERRUPT ADDRESS REGISTERS

The two interrupt address registers are the interrupt fetch address (.ifa) and the interrupt execute address (.iea). The RCS stores interrupt return addresses in these registers. (For more details see *Interrupt Sequence* on page 10.)

## SEQUENCER STATUS REGISTER

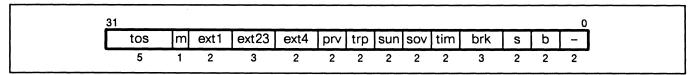

The sequencer status register (.SSr) is a 32-bit register containing state information. The upper five bits contain the stack pointer. The remaining bits include branch bits, nine sets of flag/enable bits which control and identify the state of interrupts and exceptions, and the master interrupt enable bit. If the *master enable bit* (men) is cleared, all interrupts are prevented from executing.

Several instructions implicitly use or alter information in the .ssr. The .ssr is illustrated in Figures 4 and 5.

The b and bi bits are state bits. The b bit indicates that the previous instruction was a taken branch. The bi bit stores the current values of the b bit for interrupt processing.

The nine sets of flag/enable bits selectively control the interrupt mechanism. If the enable bit is set, and if the indicated exception occurs, an interrupt occurs and the associated flag bit is set. Interrupt-handling software reads this word and examines the flag bits to determine which interrupts have occurred. If either the master or individual interrupt enable is false and an interrupt occurs, no interrupt routine will be called, but the associated exception flag will still be set.

The flag bits are "sticky" — they will remain set even if the signal that sets them goes away. The bits can only be cleared by overwriting the .ssr. If a flag bit is set when its interrupt is disabled, it will *not* cause an interrupt when the interrupt is re-enabled. Thus, all pending interrupts must be handled before exiting the interrupt handler. Furthermore, the interrupts that have been serviced must have their flag bits reset before interrupts are re-enabled (or before the interrupt handler is exited) to assure proper operation of the sequencer.

External interrupts (EXT1-, EXT2-, and EXT4-) must be latched externally until acknowledged.

The five-bit top-of-stack (`.tos) pointer is part of the .ssr.

After a reset, the .ssr is initialized with all zeros except for the s bit, which is set; and the .tos field, which is set to all ones to indicate an empty stack.

### MODIFYING THE SSR

The .ssr can be read or written as a 32-bit register using the *Intrasystem Data Transfer Instructions* on pages 46-48. While the .ssr can be examined at any time, special care must be exercised when setting it to avoid losing interrupts.

Figure 4. Sequencer status register (.ssr)

## **Registers**, continued

In order to set or reset a portion of the .ssr, a readmodify-write sequence must be performed, that is, the .ssr is read into the RIP, the desired bit manipulation is performed and the .ssr is written with the new value. In order to avoid losing crucial state information and any interrupts that occurred between reading and writing the .ssr, the following rules must be followed:

- 1. Interrupts should be disabled (that is, the .ssr's men bit should be zero) with a trapi instruction. See pages 16-17.

- 2. Interrupts from external devices should be held until explicitly acknowledged by the interrupt handler software.

- 3. No internal interrupt, except timer interrupts, should occur.

## TIMER REGISTER AND INTERRUPT

The RCS includes a programmable timer based on a 32-bit timer register. The timer register contains a

signed 32-bit number whose value represents the number of clock cycles remaining until a timer interrupt occurs. The timer register is decremented during every clock cycle. Whenever the value is negative, the timer flag is set, allowing a timer interrupt occur.

The timer will continue to decrement even when negative. This allows accurate timing if the service routine is interrupted or delayed.

### BREAKPOINT REGISTER

The XL-8236 also includes a 32-bit breakpoint register (.brk), used to provide a code breakpoint for program development. A code address can be loaded into the .brk register. If the .ssr brkenc bit is set, any attempt to fetch the instruction located at the address loaded in the .brk register sets its breakpoint interrupt flag, generating a code-break interrupt if enabled.

| Symbol | Bit # | Meaning | I                                                                                                 |

|--------|-------|---------|---------------------------------------------------------------------------------------------------|

| -      | 0     | -<br>-  | reserved: must be set to zero<br>reserved: must be set to zero                                    |

| b      | 23    | b<br>bi | last instruction was a taken branch<br>last instruction of interrupted process was a taken branch |

| S      | 4     | s       | reserved: must be set to one                                                                      |

|        | 5     | si      | reserved: must be set to one                                                                      |

| brk    | 6     | brkflg  | flag for breakpoint interrupt                                                                     |

|        | 7     | brkenc  | enable for code breakpoint interrupt                                                              |

|        | 8     | -       | reserved: must be set to zero                                                                     |

| tim    | 9     | timflg  | flag for timer interrupt                                                                          |

|        | 10    | timen   | enable for timer interrupt                                                                        |

| SOV    | 11    | sovflg  | flag for RCS stack overflow interrupt                                                             |

|        | 12    | soven   | enable for RCS stack overflow interrupt                                                           |

| sun    | 13    | sunfig  | flag for RCS stack underflow interrupt                                                            |

|        | 14    | sunen   | enable for RCS stack underflow interrupt                                                          |

| trp    | 15    | trpflg  | flag for trap instruction interrupt                                                               |

|        | 16    | trpen   | enable for trap instruction interrupt                                                             |

| prv    | 17    | prvflg  | reserved: must be set to zero                                                                     |

|        | 18    | -       | reserved: must be set to zero                                                                     |

| ext4   | 19    | ext4flg | flag for external interrupt 4                                                                     |

|        | 20    | ext4en  | enable for external interrupt 4                                                                   |

| ext23  | 21    | ext23en | enable for external interrupt 2                                                                   |

|        | 22    | ext2flg | flag for external interrupt 2                                                                     |

|        | 23    | -       | reserved: must be set to zero                                                                     |

| ext1   | 24    | ext1flg | flag for external interrupt 1                                                                     |

|        | 25    | ext1en  | enable for external interrupt 1                                                                   |

| men    | 26    | men     | master interrupt enable                                                                           |

| .tos   | 31-27 | .tos    | five-bit top-of-stack pointer                                                                     |

Figure 5. Bit fields in the sequencer status register

PRELIMINARY DATA October 1988

## Neutralization

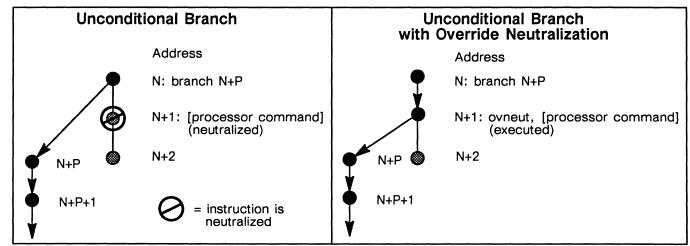

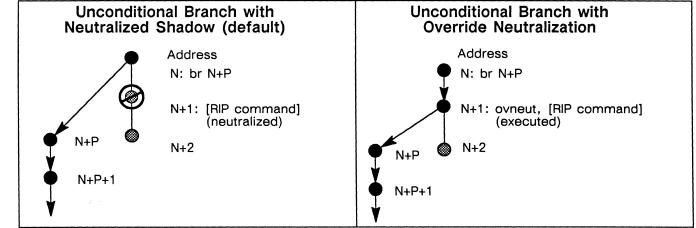

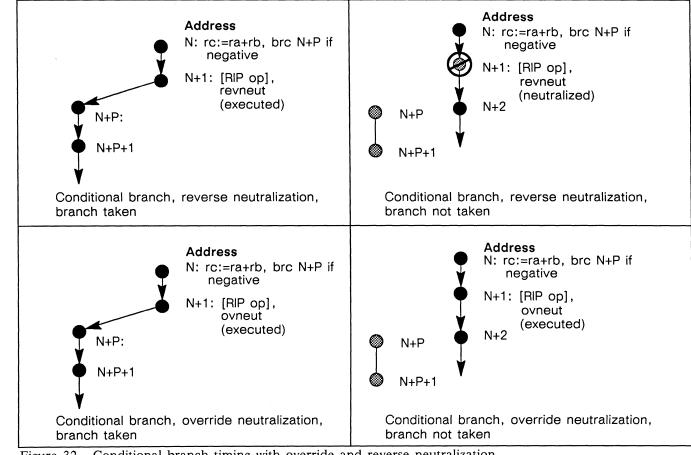

The XL-8236 RCS and its companion, the XL-8237 RIP, achieve high speed by simultaneously fetching the next instruction while executing the current instruction. When a branch is executed, the RCS already has the instruction following the branch in its instruction pipeline. This instruction is called the "shadow instruction." Fetching the instruction at the branch address takes an additional cycle, since it's not yet in the pipeline, so the destination instruction is executed after a one-cycle delay. This is called "delayed branching".

The XL-8236 provides a neutralization output line, NEUT-. It can selectively cancel the effects of the shadow instruction, effectively replacing it with a noop. The XL-8236 instruction set normally sets NEUTactive after branch, call and return instructions (including interrupt calls and returns), thereby canceling the shadow instruction. This allows the programmer to ignore the effects of delayed branching.

Neutralized instructions actually run to completion, but their results are discarded at the end of the cycle. Registers, status flags, and so on are simply not updated, so internal effect is as if the instruction was never executed.

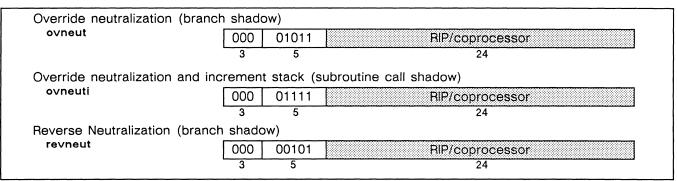

The XL-8236 instruction set also provides three additional instructions which allow the shadow instruction to be executed: override neutralization (ovneut), override and increment stack pointer (ovneuti), and reverse neutralization (revneut). Efficient code makes use of these instructions to selectively execute shadow instructions, saving up to one clock cycle per branch.

Figure 6. Neutralization

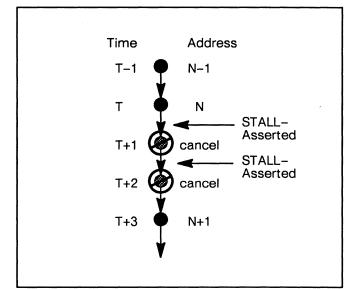

## STALL-

The XL-8236 has a control input, STALL-, which directs the RCS and RIP to cancel the effects of the next instruction. This signal is asserted by external hardware when unable to complete a bus transfer in time, such as during a cache miss or refresh cycle. An active STALL-signal cancels the next instruction. Instructions canceled through this mechanism are refetched and will be re-executed when the STALL- signal is de-asserted.

Cancelled instructions actually run to completion, but their results are discarded at the end of the cycle. Registers, status flags, and so on are simply not updated, so internal effect is as if the instruction was never executed.

STALL- allows the current instruction to complete, but cancels the next instruction. The most common use of STALL- is to re-execute an instruction fetch on a wait state, cache miss, or refresh cycle. The invalid word loaded on the STALL-ed cycle is released, then the instruction is executed and normal execution continues.

Figure 7. Effects of STALL-

## Interrupts

The XL-8236 can receive interrupts from three external sources: EXT1-, EXT2-, and EXT4- (there is no EXT3); and can generate five interrupts internally: BRK, TIM, SOV, SUN, and TRP. When an interrupt control line or internal condition becomes active, the RCS sets the corresponding .ssr interrupt flag. If the master interrupt enable (men) bit of the .ssr is set, and the corresponding .ssr interrupt enable is active, the interrupt will be honored, as described below.

There are fifteen interrupt vector addresses. All external interrupt lines are level-sensitive. They are sampled at the rising edge of the clock.

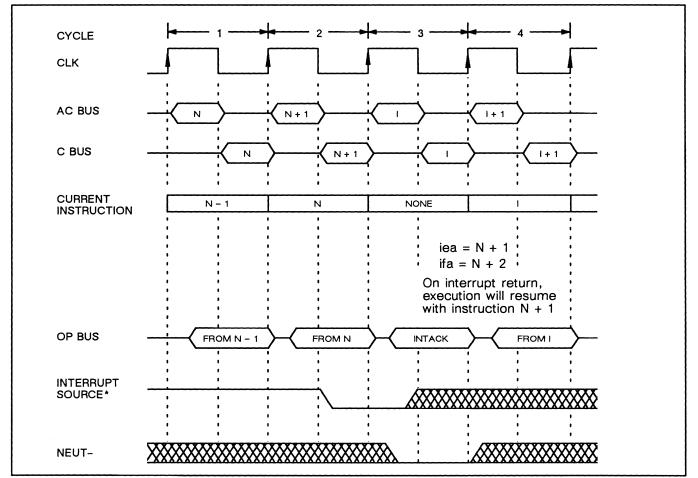

### INTERRUPT SEQUENCE

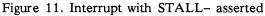

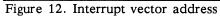

When an interrupt is detected, the .cfa is stored in the iea, and the next fetch address is placed in the .ifa. This sequence allows the system to return to the next instruction (.cfa) on an interrupt return. See figure 8.

The RCS then neutralizes the fetched instruction and branches to the interrupt vector address. The old value of the .ssr b bit is saved in the bi bit.

The interrupt vectoring scheme is based on four classes of interrupts. When an interrupt request is approved, the RCS branches to the address formed by or-ing the 32-bit interrupt base address register (.ibr) with the four interrupt classes as shown in figure 12. This gives the capability of up to 15 different vector addresses (not 16 because at least one class bit must be non-zero for an interrupt to occur).

Note that if multiple interrupts occur simultaneously, they are not prioritized. Rather, the vector address of the interrupt handler is selected to indicate which interrupt classes are pending.

Interrupts can be nested to any depth by saving the contents of the .iea, .ifa and .ssr registers externally.

### **RETURNING FROM INTERRUPTS**

To return from an interrupt, two special interrupt return instructions must be executed, return-from-interrupt-0 (rfi0) and return-from-interrupt-1 (rfi1). Executing rfi0 returns the .iea register to the .cfa register places the contents of the .iea register onto the AC bus and enables the interrupt master enable bit (men). The upadating of the men bit may occur on the cycle in which the rfi0 is executed, or one cycle after that. Executing rfi1 returns the .ifa to the .cfa and places the .ifa register contents onto the AC bus, restoring the RCS state to what it was before the interrupt was requested.

PRELIMINARY DATA October 1988

## Interrupts, continued

Figure 8. Normal interrupt entry sequence

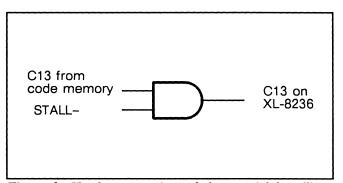

Note that the enabling of the men bit during the rf10 cycle allows an interrupt to be acknowledged before the rfi1 instruction executes, causing the state of the machine to be lost. Rfi0 also ignores the state of STALL-. Two steps must be taken to avoid this from causing trouble:

- 4. Condition C13 by ANDing it with STALL-, as shown in figure 9. This will prevent the RCS from ever seeing an rfi0 instruction during STALL- cycles, and eliminates the problem (that it alters the code word is unimporant, since the STALL- signal will cause it to not be executed). If your design does not use STALL-, you do not need to implement this.

- 5. Use the code in figure 10 at the start of your interrupt routine to test for improper interrupt exit se-

quences and to restore the state correctly. This step must be implemented whether you use STALL- or not.

Figure 9. Hardware portion of the special handling for rfi0/rfi1

### Interrupts, continued

```

/* Beginning of interrupt handler */

/*

This routine works by testing the value of .iea against the address of the interrupt

handler's rfi1 instruction. This implementation assumes that there is only one exit routine;

that is, that there is only one rfi1 instruction in the whole system.

The extra overhead consists only of a few instructions, since the interrupt calls are not

spurious; they simply happened a cycle too soon.

This example is written in a pseudo-code that mixes C and XL assembly code. */

swap register banks

if (.iea == rfi1_addr) {

/* This interrupt came between rfi0 and rfi1. Restore the state of the previous call, with

a few exceptions ... */

saved ssr.bi = .ssr.bi;

} else {

/* This is a normal interrupt call. Save .iea, .ifa, and .ssr specially */

saved lea = .lea;

saved ifa = .ifa;

saved ssr = .ssr;

}

/* Main part of interrupt handler */

/* End of interrupt handler */

.iea = saved iea;

.ifa = saved ifa;

.ssr = saved_ssr;

rfi0;

rfi1_addr:

rfi1; asrtadr

```

Figure 10. Software portion of the special handling of rfi0 and rfi1

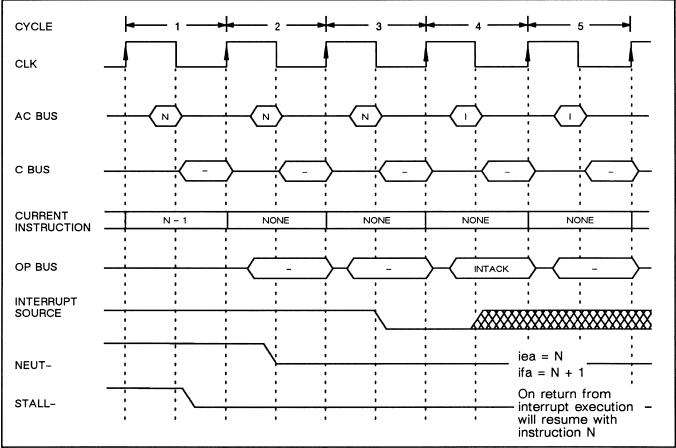

## INTERRUPTS AND STALL-

Interrupt processing takes precedence over stalls: if STALL- is asserted and an enabled interrupt is approved, the RCS will honor the interrupt and perform the interrupt entry sequence. (See figure 11). Because the AC bus address changes (the only situation when it

can change with STALL- asserted), designers using variable-latency code memory subsystems must handle this case. This is described in detail in the *XL-Series* Hardware Designer's Guide.

PRELIMINARY DATA October 1988

## Interrupts, continued

## INTERRUPT FLAG BITS

The interrupt flag bits record the history of the associated interrupt. If the interrupt was asserted at any time in the past, then the flag bit will be set even if the enable is not set (except for the breakpoint register;

breakpoint comparisons are only performed if the associated enable bit is set). Once the flag bit is set it can only be cleared by writing an entire word into the .ssr.

### Interrupts, continued

#### EXTERNAL INTERRUPT SOURCES

The external interrupt sources are: EXT1-, EXT2-, and EXT4-. Each has status and interrupt enable bits in the .ssr.

The EXT1- control line is a dedicated external interrupt. Its interrupt mask bit in the .ssr is ext1en. Its status bit is ext1flg.

The EXT2- interrupt line has an enable bit, ext23en. Its status bit is ext2flg.

EXT4- is typically used to signal exception conditions from floating point processors, but can be used as a general-purpose interrupt. Its enable bit is ext4en, and its status flag is ext4flg.

#### INTERNAL INTERRUPT SOURCES

The five internal interrupt sources (SOV, SUN, TRP, TIM, and BRK) each have a status and interrupt enable bit in the .ssr.

SOV and SUN indicate stack near-overflow and nearunderflow. SOV occurs when data is pushed into the third-to-last available word on the stack (.tos = 29). SUN occurs when the stack is empty or nearly empty (.tos = 1 or .tos = 0, or .tos = 31). The enable and status bits for SOV and SUN are soven, sovflg, sunen, and sunflg, respectively.

Note that the stack underflow exception can occur at more than one stack position. The stack pointer (the .tos field) must be used to determine the stack position in exception handling, rather than using constants showing the stack position at which you expect the exception to occur.

TRP is set by invoking the trap instruction. Its enable and status bits are trpen and trpflg, respectively.

The remaining two exceptions, TIM and BRK, are set on timer interrupts and breakpoints, respectively. Their enable and status bits are timen, timflg, brkenc, and brkflg.

### BREAKPOINT FACILITY

The breakpoint (.brk) register provides a facility to interrupt normal program execution when a specific instruction is executed (breakpoint).

See figure 13 for the timing of a code breakpoint. The system stops *before* executing the instruction referenced by the .brk register. Note that even instructions which are to be neutralized will cause a code breakpoint. This allows simple single-stepping of the system by setting the breakpoint to the .ifa register (the "next" instruction to be executed).

Breakpoints are not reliable if they occur on addresses that are executed *after* shadow instructions, such as branch targets.

Figure 13. Code breakpoint timing

## Interrupts, continued

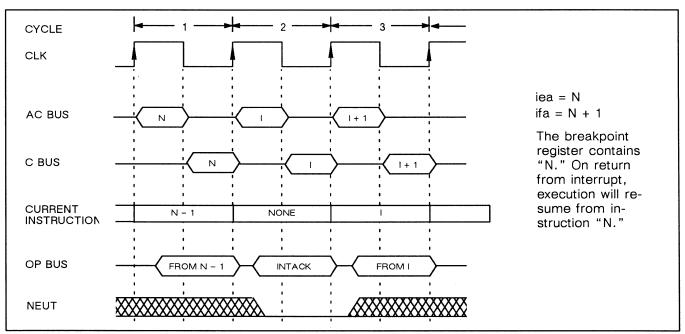

#### STACK OVERFLOW

The sovflg bit of the .ssr is set when the .tos field contains a 29 and a stack push operation is performed. If the stack overflow interrupt is enabled (soven = 1 and men = 1), then it will be detected during the cycle after the completion of the push operation. See figure 14 for details.

### STACK UNDERFLOW

The sunfig bit of the .ssr is set when the .tos field contains a 1, or 0, or 31 and a stack pop operation is performed. If the stack underflow interrupt is enabled (sunen = 1 and men = 1), then it will be detected either one or two cycles after the completion of the pop operation. (The extra cycle of delay doesn't cause problems because the exception is triggered when the next-to-last word is popped off the stack. Even if another pop occurs in the cycle between the first pop and the assertion of the exception, the data popped off will still be valid.) See figure 14 for details.

The stack should be initialized after a reset by pushing two values onto the stack. This will move it past the point where the stack underflow interrupt occurs.

Figure 14. Stack overflow/underflow timing. Note that the underflow may be signaled on one of two cycles.

## Interrupts, continued

### TRAPS

Software interrupts on the XL-8236 are called *traps*. They are invoked with the trapi instruction.

Traps are used primarily for system calls. The programmer would specify a system call by using the immediate field of the trap instructions, as in "trapi 47." This would push the number 47 onto the stack and cause a trap interrupt. The trap handler would use the value on the stack as a parameter.

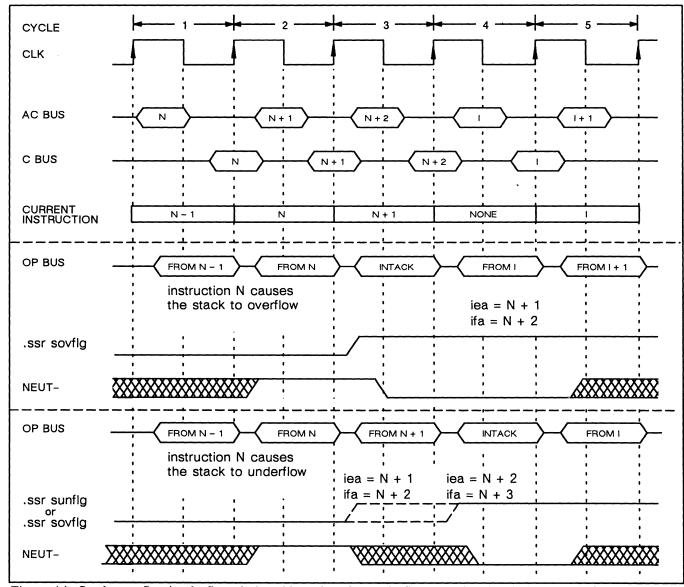

### HANDLING INTERRUPTS

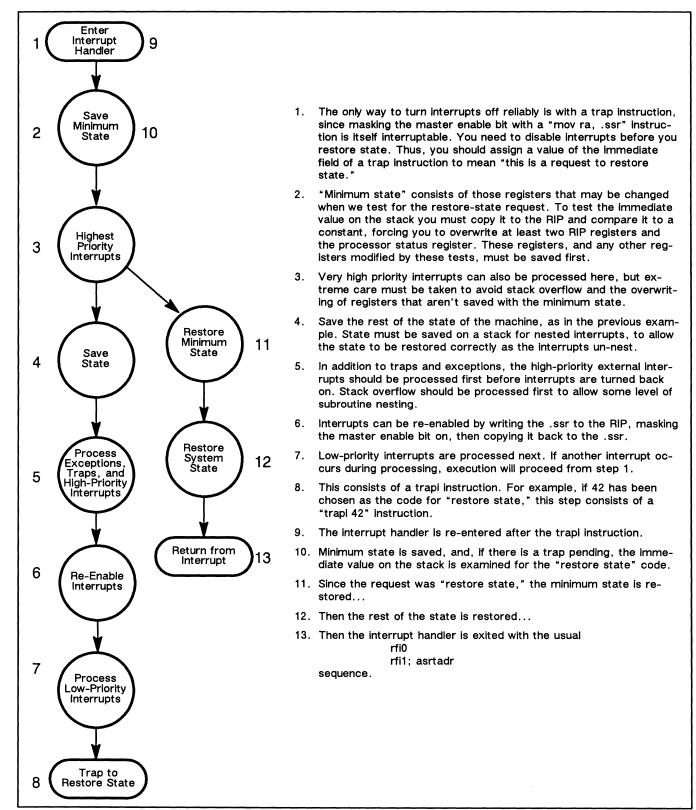

The software that handles interrupts should follow the procedure given in figure 15. The handler for nested interrupts is more complex. This is shown in figure 16 (detail in steps common to both figures is skimpy in figure 16, so be sure to read both).

Each flag bit in the .ssr must be reset after the interrupt or exception is serviced.

Figure 15. Description of interrupt handling

PRELIMINARY DATA October 1988

### Interrupts, continued

Figure 16. Nested interrupts

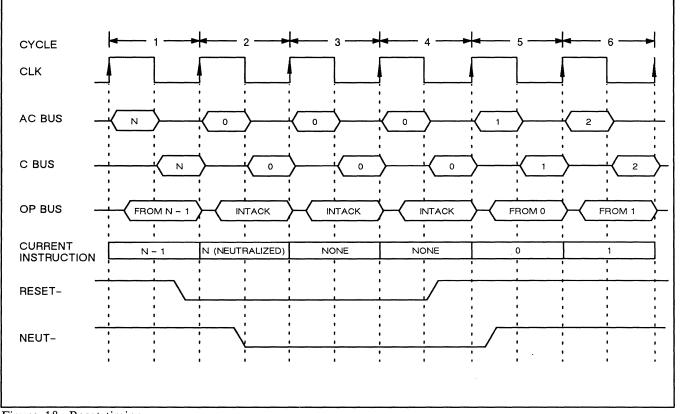

# RESET

Activating the RESET- line at the end of the clock cycle initializes the .ssr according to Figure 17, sets the .cfa register to zeros and sends the value zero out on the AC bus, forcing a branch to address zero. Figure 18 shows detailed reset timing. The user should place a no-op instruction in location zero.

|    |   | .tos | 3 |    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | s |   |   |   |   |

|----|---|------|---|----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1  | 1 | 1    | 1 | 1  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 31 |   |      |   | 27 | 26 |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 5 | 4 | 3 |   |   | 0 |

Figure 17. Sequencer status register, initialized

Figure 18. Reset timing

## Instruction Set

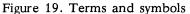

## TERMS AND SYMBOLS

The instructions are listed on pages 20 and 21, then described in detail on the following pages. Each de-

scription includes a pseudo-code definition of the instruction. The following symbols are used:

| 1        | Concatenate fields. abc    def<br>gives abcdef.<br>Indicates that operations sepa-<br>rated by this symbol occur in<br>parallel. | COND { } % ixs [310] | Condition Code<br>Begin and end comment<br>Shift left by ixs bits<br>Specifies the bit field from bit |

|----------|----------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------|

| a dup b  | Duplicate b a times. 3 dup 0 gives 000.                                                                                          |                      | 31 to bit 0, inclusive. For example, reg (ra) [30] gives the lower four bits of register              |

| stack(t) | Location t in the sequencer stack                                                                                                |                      | ra.                                                                                                   |

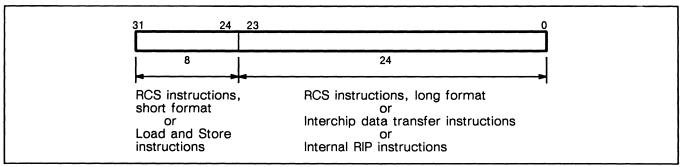

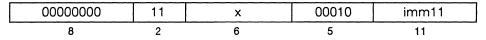

### INSTRUCTION FORMAT

The XL-8236 uses two instruction formats: short and long. Short instructions use the upper 8 bits of a 32-bit instruction; the remaining bits are used as the instruction field for the XL-8237 RIP or a coprocessor. Short instructions include neutralization control, short branches with a 5-bit displacement and branching from a 32-bit displacement on the stack.

tions are used to provide bus transfer and housekeeping control operations, in addition to 24-bit and 28-bit subroutine and branch immediates.

Coprocessor instructions are reserved for future expansion, with the exception of the coprocessor load/store instructions, which are used in the XL-8232 to load and store the graphics floating point unit.

Long instructions are 32 bits long, with a format recognized by the RIP as a RCS operation. These instruc-

| Field               | Meaning                                           |

|---------------------|---------------------------------------------------|

| ra                  | selects ra register (of processor)                |

| imm11, imm24, imm28 | 11, 24, or 28 bit immediate                       |

| c                   | condition polarity select                         |

| imm5                | 5-bit signed or unsigned immediate                |

| ext1, ext2          | operation code extensions                         |

| rd                  | selects rd register (of processor or coprocessor) |

| extn                | external register number n                        |

Figure 20. Instruction fields

Figure 21. Instruction formats

# Instruction Format, continued

| Opertions                                          |             |             |             | Detailed<br>Description<br>Page # |

|----------------------------------------------------|-------------|-------------|-------------|-----------------------------------|

| Continue                                           | 000 00110   | BIP/co      | processor   | 22                                |

| Cont                                               |             |             |             |                                   |

| Branch                                             | 000 00010   |             | nm24        | 7 24                              |

| Branch                                             |             | <u> </u> in | 111124      | 24                                |

| Short branch                                       | 100 imm5    | RIP/co      | processor   | 25                                |

| Branch to stack and pop                            | 000 01110   | RIP/co      | processor   | 26                                |

| Short forward branch on condition                  | 01 c imm5   | RIP/co      | processor   | 27                                |

| Loop Control                                       |             |             |             |                                   |

| Loop enter                                         | 000 00111   | RIP/co      | orocessor   | 29                                |

| Absolute branch to stack or or pop on condition    | 000 01 c 00 | RIP/co      | processor   | 30                                |

| Decrement stack and branch or pop if zero          | 000 00001   | in          | 1m24        | 31                                |

| Decrement stack and backward branch or pop if zero | 001 imm5    | RIP/coj     | processor   | 32                                |

| Branch and pop (loop exit)                         | 000 00011   | irr         | 1m24        | 33                                |

| Subroutine Control                                 |             |             |             | _                                 |

| Subroutine call                                    | 0001        | in          | 1m28        | 35                                |

| Subroutine return                                  | 000 01101   | RIP/co      | processor   | 36                                |

| Interrupt Control                                  |             |             |             |                                   |

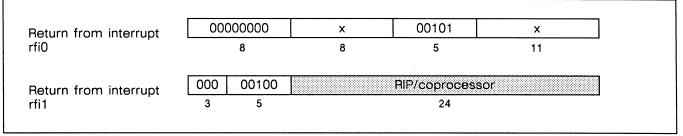

| Return from interrupt 0                            | 00000000    | x           | 00101 x     | 38                                |

| Return from interrupt 1                            | 000 00100   | RIP/cop     | processor   | 39                                |

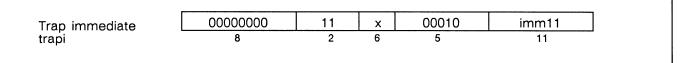

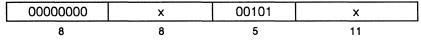

| Тгар                                               |             |             |             | i                                 |

| Trap immediate                                     | 00000000    | 11 x        | 00010 imm11 | 40                                |

| Neutralization                                     |             |             |             |                                   |

| Override neutralization                            | 000 01011   | RIP/coj     | orocessor   | 43                                |

| Override neutralization of subroutine call shadow  | 000 01111   | RIP/cop     | processor   | 44                                |

| Reverse neutralization                             | 000 00101   | RIP/co      | processor   | 45                                |

|                                                    |             |             |             |                                   |

**PRELIMINARY DATA** October 1988

٦

# Instruction Format, continued

| ntrasystem Data Transfer Inst                   | ruction  | s          |             |     |                                       |      | Detaileo<br>Descripti<br>Page # |

|-------------------------------------------------|----------|------------|-------------|-----|---------------------------------------|------|---------------------------------|

| Transfer word from RIP to RCS internal register | 000      | 00000      | 001         | ra  | ext2                                  | ×    | )                               |

| Transfer word from                              | 3        | 5          | 3           | 5   | 5                                     | 11   | } 46                            |

| Coprocessor to RCS internal                     | 000      | 00000      | 11          | ×   | ext2                                  | ×    | )                               |

| register                                        | 3        | 5          | 2           | 6   | 5                                     | 11   | ,                               |

| Transfer word from RCS internal register to RIP | 000      | 00000      | 011         | ra  | ext2                                  | 0    |                                 |

| Transfer word from RCS                          | 3        | 5          | 3           | 5   | 5                                     | 11   | } 48                            |

| internal register to                            | 000      | 00000      | 11          | X   | ext2                                  | ×    | }                               |

| Coprocessor                                     | 3        | 5          | 2           | 6   | 5                                     | 11   | •                               |

| Pop stack to RIP register                       | 000      | 00000      | 010         | ra  | 00000                                 | x    |                                 |

|                                                 | 3        | 5          | 3           | 5   | 5                                     | 11   | } 50                            |

| Pop stack to Coprocessor                        | 000      | 00000      | 101         | x   | 00000                                 | x    | ]                               |

|                                                 | 3        | 5          | 3           | 5   | 5                                     | 11   |                                 |

| Copy stack to RIP register                      | 000      | 00000      | 010         | ra  | 00001                                 | x    |                                 |

|                                                 | 3        | 5          | 3           | 5   | 5                                     | 11   | 51                              |

| Copy stack to Coprocessor                       | 000      | 00000      | 101         | x   | 00001                                 | x    |                                 |

|                                                 | 3        | 5          | 3           | 5   | 5                                     | 11   | ,                               |

| Push RIP register onto stack                    | 000      | 00000      | 000         | ra  | 00000                                 | x    | )                               |

|                                                 | 3        | 5          | 3           | 5   | 5                                     | 11   | 52                              |

| Push Coprocessor register<br>onto stack         | 000      | 00000      | 100         | x   | 00000                                 | x    |                                 |

| Shito Stack                                     | 3        | 5          | 3           | 5   | 5                                     | 11   | ,                               |

| Transfer word from RIP                          | 000      | 00000      | 001         | ra  | 1 extn                                | ×    |                                 |

| register to external register                   | 3        | 5          | 3           | 5   | 4                                     | 11   | 53                              |

| Transfer Coprocessor                            | 000      | 00000      | 11          | ×   | 1 extn                                | x    | $\int 33$                       |

| register to external register                   | 3        | 5          | 2           | 6   | 4                                     | 11   | J                               |

| Transfer word from                              | 000      | 00000      | 011         |     | 1 extn                                |      | ١                               |

| external register to RIP                        |          | 5          | 3           | ra5 | 1 extn 4                              | X    |                                 |

| Transfer external register                      |          |            | · · · · · · |     | · · · · · · · · · · · · · · · · · · · |      | > 54                            |

| to Coprocessor register                         | 000      | 00000      | 11          | ×   | 1 extn                                | X    |                                 |

|                                                 | 3        | 5          | 2           | 0   | 4                                     | 11   | )                               |

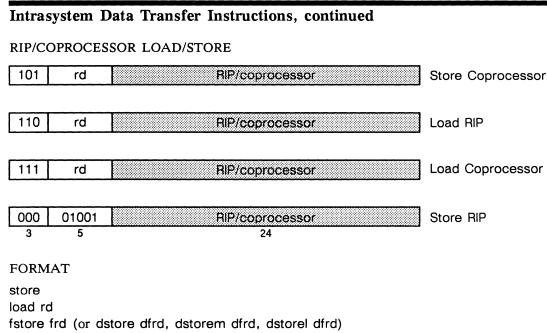

| Store Coprocessor                               | 101      | rd         |             |     | RP/coproces                           | sor  | )                               |

| Load RIP                                        | 110      | rd         |             | ſ   | RIP/coproces                          | SSOF |                                 |

| Load Coprocessor                                | 111      | rd         |             | F   | RIP/coproces                          | ssor | > 55                            |

| Store RIP                                       | 000<br>3 | 01001<br>5 |             | 1   | RIP/coproces<br>24                    | ssor | )                               |

## **Continue Instruction**

## CONTINUE

### FORMAT

cont

## DESCRIPTION

This instruction causes instruction fetching to proceed in normal, sequential fashion. The lower 24 bits are used for either an XL-8237 instruction or a coprocessor instruction. Short instruction format.

## NEUTRALIZATION

This instruction is neutralized if the b field of the .ssr contains a one.

| if b = 1 then   |

|-----------------|

| NEUT := true;   |

| b := 0;         |

| else            |

| NEUT := false;  |

| endif;          |

| cfa := cfa + 1; |

| AC := cfa;      |

|                 |

PRELIMINARY DATA October 1988

## **Branch Instructions Summary**

The following instructions are used for branching:

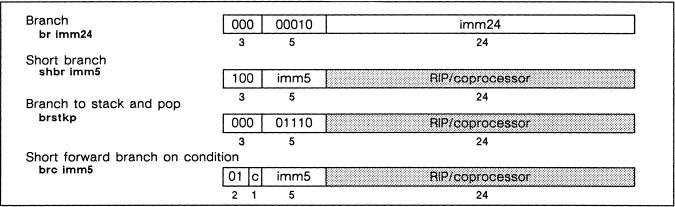

Figure 22. Format of branch instructions

Figure 24. Conditional branch timing-brc imm5 instruction.

## Branch Instructions, continued

## BRANCH

## FORMAT

br imm24

## DESCRIPTION

Causes the RCS to branch to the address specified by adding the sign-extended 24-bit immediate imm24 to the address of the currently executing instruction. Long instruction format.

## NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

## EXCEPTIONS

None

PRELIMINARY DATA October 1988

## Branch Instructions, continued

SHORT BRANCH

100

imm5

RiP/coprocessor

3

5

24

### FORMAT

shbr imm5

### DESCRIPTION

Causes a branch to the address specified by adding the sign-extended 5-bit offset to the currently executing instruction. Short instruction format.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

### EXCEPTIONS

None

```

if b = 1 then

NEUT := true;

cfa := cfa + 1;

b := 0;

else

NEUT := false;

cfa := cea + (28 dup imm[4]) || imm5[3..0];

b := 1;

endif;

AC := cfa;

```

# **Branch Instructions, continued**

### BRANCH TO STACK AND POP

000

01110

RIP/coprocessor

3

5

24

### FORMAT

brstkp

### DESCRIPTION

This instruction takes a branch to the address specified by adding the value on the top of stack to the address of the currently executing instruction. The top of stack value is popped off. Short instruction format.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. The b bit of the .ssr is set to one.

### EXCEPTIONS

Stack underflow

PRELIMINARY DATA October 1988

## Branch Instructions, continued

SHORT FORWARD BRANCH ON CONDITION

01

c

imm5

RiP/coprocessor

2

1

5

24

FORMAT

brc imm5

### DESCRIPTION

If the selected condition is active, causes a branch to the address specified by adding the zero-extended 5-bit offset to the address of the currently executing instruction. If the 24-bit processor/coprocessor field contains a coprocessor instruction, then FPCN is tested; otherwise, COND is tested. See the *XL-8237 Data Sheet* for details of the processor/coprocessor instruction field. Short instruction format.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

### EXCEPTIONS

None

```

if b = 1 then

NEUT := true;

cfa := cfa + 1;

b := 0;

else

NEUT := false;

if {processor operation is coprocessor} then

cond := FPCN;

else

cond := COND;

endif;

if c \cdot cond then

cfa := cfa + 1;

else

cfa := cea + (27 dup 0) || imm5[4..0];

b := 1;

endif;

endif:

AC := cfa;

```

## Loop Control Instructions Summary

The following instructions are used for loop control:

| loop                     | 000 00111                     | RIP/coprocessor |  |

|--------------------------|-------------------------------|-----------------|--|

|                          | 3 5                           | 24              |  |

|                          | or pop on condition (loopa a  | gain or exit)   |  |

| endloop                  | 000 01 c 00                   | RIP/coprocessor |  |

|                          | 3 2 1 2                       | 24              |  |

| Decrement stack and bac  | kward branch or pop if zero   | (for loopi end) |  |

| shsob imm5               | 001 imm5                      | RIP/coprocessor |  |

|                          | 3 5                           | 24              |  |

| Decrement stack and brar | nch or pop if zero (for loopi | end)            |  |

| Decrement stack and brai |                               |                 |  |

| sob imm24                | 000 00001                     | imm24           |  |

|                          | 000 00001<br>3 5              | imm24<br>24     |  |

| sob imm24                | 3 5                           |                 |  |

|                          | 3 5                           |                 |  |

Figure 25. Loop control instruction format

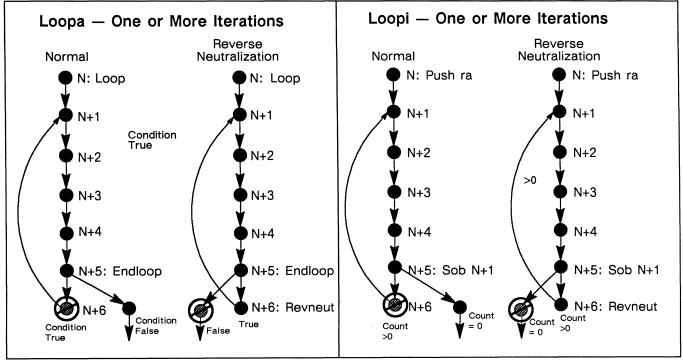

There are two kinds of loops: loops that run for a fixed number of iterations, using a loop count on the stack; and loops that run until a condition is met, with the top-of-loop branch address on the top of stack. The fixed-count loop is called a loopi; the conditional loop is called a loopa.

Figure 26. Loopa and Loopi

PRELIMINARY DATA October 1988

# Loop Control Instructions, continued

LOOP ENTER (PUSH FOLLOWING ADDRESS)

000

00111

RIP/coprocessor

3

5

24

### FORMAT

loop

### DESCRIPTION

This instruction pushes the address of the currently fetching instruction on the stack. Used to start loopa. Short instruction format.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one.

### **EXCEPTIONS**

Stack overflow

## Loop Control Instructions, continued

## ABSOLUTE BRANCH TO STACK OR POP ON CONDITION (LOOP AGAIN OR EXIT)

000

01

c

00

RiP/coprocessor

3

2

1

2

24

## FORMAT

endloop

### DESCRIPTION

If the selected condition is asserted, causes a branch to the contents of the top of stack; otherwise, pops the stack and continues normal sequential execution. If the 24-bit processor/coprocessor field contains a coprocessor instruction, then FPCN is tested, otherwise COND is tested. See the *XL-8237 Data Sheet* for details of the processor/ coprocessor instruction field. Used to conditionally end a loopa. (See the brc instruction on page 27 for details of condition code selection.) Short instruction format.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

## **EXCEPTIONS**

Stack underflow

```

if b = 1 then

NEUT := true:

cfa := cfa + 1;

b := 0;

else

NEUT := false:

if {processor operation is coprocessor} then

cond := FPCN;

else

cond := COND;

endif;

if c · cond then

cfa := cfa + 1;

tos := tos - 1;

b := 0;

else

cfa := stack(tos);

b := 1;

endif;

endif;

AC := cfa;

```

## PRELIMINARY DATA October 1988

## Loop Control Instructions, continued

DECREMENT STACK AND BRANCH OR POP IF ZERO (FOR LOOPI END)

| 000 | 00001 | imm24 |

|-----|-------|-------|

| 3   | 5     | 24    |

### FORMAT

sob imm24

### DESCRIPTION

The acronym sob stands for subtract-one-and-branch. This instruction subtracts one from the top of stack, replacing result back on the top-of-stack. If the result is non-zero, a branch is caused to the address specified by adding the sign-extended 24-bit immediate imm24 to the address of the currently executing instruction. If the result is zero, the value on the top-of-stack is popped off and discarded, and the normal sequential execution resumes. Useful at bottoms of loops designed to continue a set number of iterations (loopi). Long instruction format.

Note that the initial count must be non-negative, (that is, the high bit must be zero) for the instruction to work properly.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

### **EXCEPTIONS**

Stack underflow

### **OPERATION**

```

if b = 1 then

NEUT := true;

cfa := cfa + 1;

b := 0;

else

NEUT := false;

stack(tos) := stack(tos) - 1;

if stack(tos) = 0 then

cfa := cfa + 1;

tos := tos -1;

else

cfa := cea + (9 dup imm24[23]) || imm24[22..0];

b := 1;

endif;

endif;

AC := cfa;

```

© Copyright WEITEK 1988 All rights reserved

## Loop Control Instructions, continued

## DECREMENT STACK AND BACKWARD BRANCH OR POP IF ZERO (FOR LOOPI END)

001

imm5

RIP/coprocessor

3

5

24

FORMAT

shsob imm5

### DESCRIPTION

Same instruction as sob, but performs the branch based on the one-extended field imm5 instead of the 24-bit immediate that sob uses. Used to end a loopi. Short instruction format.

Note that the initial count must be non-negative for the instruction to work properly.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

## EXCEPTIONS

Stack underflow

### **OPERATION**

```

if b = 1 then

NEUT := true;

cfa := cfa + 1;

b := 0;

else

NEUT := false;

stack(tos) := stack(tos) - 1;

if stack(tos) = 0 then

cfa := cfa + 1;

tos := tos - 1;

b := 0;

else

cfa := cea + (27 dup 1) || imm5[4..0];

b := 1;

endif;

endif;

AC := cfa;

```

© Copyright WEITEK 1988 All rights reserved

PRELIMINARY DATA October 1988

## Loop Control Instructions, continued

BRANCH AND POP (LOOPI/LOOPA EXIT)

000

00011

imm24

3

5

24

FORMAT

brp imm24

### DESCRIPTION

Branches to the address specified by adding the sign-extended 24-bit immediate imm24 to the address of the currently executing instruction. The value on the top of stack is popped off and discarded. Used to unconditionally or prematurely exit a loopa or loopi. Long instruction format.

### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. If the branch is taken, the b bit of the .ssr is set to one.

### EXCEPTIONS

Stack underflow

# **Subroutine Control Instructions Summary**

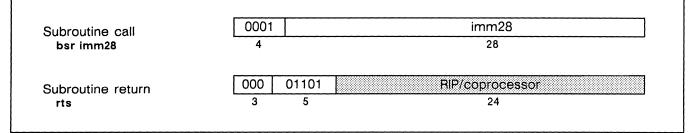

The following instructions are used for subroutine control:

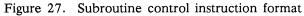

Figure 28. Subroutine call and return

PRELIMINARY DATA October 1988

#### Subroutine Control Instructions, continued

SUBROUTINE CALL

0001 imm28 4 28

FORMAT

bsr imm28

#### DESCRIPTION

Pushes the address of the currently fetching instruction on the stack and branches to the address specified by the sum of the sign-extended 28-bit immediate imm28 and .cea. Long instruction format.

#### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. The b bit of the .ssr is set to one.

#### EXCEPTIONS

Stack overflow

```

if b = 1 then

NEUT := true;

cfa := cfa + 1;

b := 0;

else

NEUT := false;

tos := tos + 1;

stack(tos) := cfa;

cfa := cea + (5 dup imm28[27]) || imm28[26..0];

b := 1;

endif;

AC := cfa;

```

#### Subroutine Control Instructions, continued

#### SUBROUTINE RETURN

000

01101

RiP/coprocessor

3

5

24

#### FORMAT

rts

#### DESCRIPTION

The value on the top of the stack is used as an absolute branch address and discarded. Short instruction format.

#### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one. The b bit of the .ssr is set to one.

#### EXCEPTIONS

Stack underflow

#### PRELIMINARY DATA October 1988

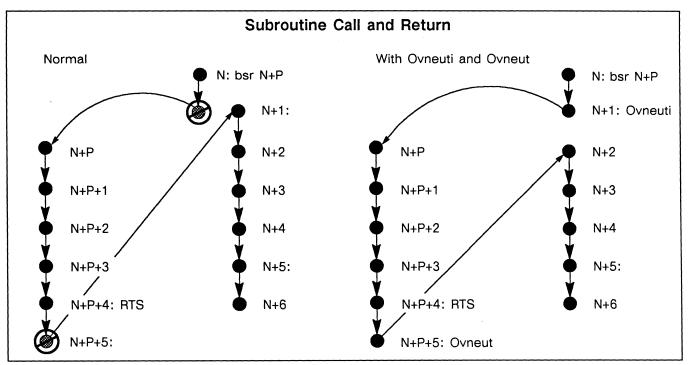

# **Interrupt Control Instructions Summary**

The following instructions are used to return from interrupt:

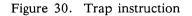

Figure 29. Interrupt control instructions

The following instructions are used to cause software interrupts (traps):

# **Interrupt Control Instructions, continued**

#### **RETURN FROM INTERRUPT (rfi0)**

#### FORMAT

rfi0

#### DESCRIPTION

First of a two-step instruction sequence to restore the RCS state after an interrupt. Restores .cfa from .iea, and enables interrupts by setting the men bit. The rfi0 instruction must be followed by the rfi1 instruction. Long instruction format.

The effect of setting men bit may not take place until one cycle after the rfi0 instruction.

All internal exceptions should be processed before the interrupt handler is exited.

#### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr is a one.

#### EXCEPTIONS

None

#### PRELIMINARY DATA October 1988

### Interrupt Control Instructions, continued

#### **RETURN FROM INTERRUPT (rfi1)**

000

00100

RIP/coprocessor

3

5

24

#### FORMAT

rfi1

#### DESCRIPTION

Second of a two-step instruction sequence to restore the RCS state after an interrupt. Short instruction format. Rfi1 stores the contents of the .ifa to the .cfa and places the contents of the .ifa onto the AC bus. The .ssr bi bit is stored into .ssr b to indicate if the last instruction of the interrupted process was a branch. The rfi1 instruction must always be preceded by the rfi0 instruction. Short instruction format.

#### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a one.

#### **EXCEPTIONS**

None

```

if b = 1 then

cfa := cfa + 1;

b := 0:

NEUT := FALSE;

else

NEUT := FALSE:

if ssr.s = 1 then

cfa := ifa;

ssr.b := ssr.bi;

ssr.s := ssr.si;

OP := 00111;

else

ssr.prvflg := TRUE;

endif;

endif:

AC := cfa;

```

# **Trap Instructions**

#### TRAP IMMEDIATE

#### FORMAT

trapi imm11

#### DESCRIPTION

This instruction sets the trpflg bit of the .ssr. If enabled, the RCS causes an interrupt and pushes an 11-bit zero-extended immediate value onto the stack. The trap flag (trpflg) in .ssr is set when a trap occurs.

#### NEUTRALIZATION

This instruction is neutralized if the b bit of the ssr contains a one.

#### **EXCEPTIONS**

Stack overflow and trap

```

if b = 0 then

ssr.trpflg := 1;

if (ssr.men = 1) and (ssr.trpen = 1) then

stack(tos) := 21 dup 0 || imm11[10..0];

tos := tos + 1;

endif;

endif;

b := 0;

cfa := cfa + 1;

```

PRELIMINARY DATA October 1988

#### **Neutralization Instructions Summary**

The RCS has three short-format instructions that change the neutralization of shadow instructions after branching, subroutine calls and returns.

Figure 31. Neutralization instruction format

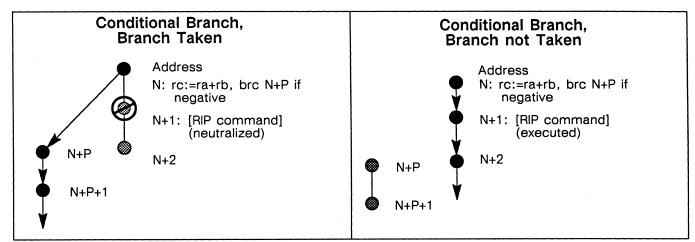

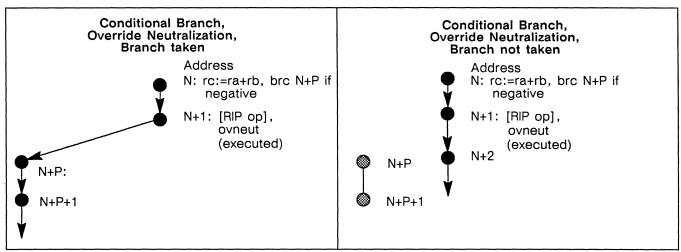

Figure 32. Conditional branch timing with override and reverse neutralization

# Neutralization Instructions, continued

Figure 33. Conditional branch timing with override neutralization

.

PRELIMINARY DATA October 1988

#### Neutralization Instructions, continued

#### OVERRIDE NEUTRALIZATION OF BRANCH SHADOW

000

01011

RIP/coprocessor

3

5

24

#### FORMAT

ovneut

#### DESCRIPTION

Causes the neutralization effect—which normally cancels the execution of an instruction immediately following a branch (or other transfer-of-control operation)—to be overridden. The instruction is unconditionally executed (unless neutralized due to an interrupt). This instruction has a short format and is placed with the shadow instruction to be executed, immediately following the branch.

#### NEUTRALIZATION

This instruction is executed regardless of the value of the b field of the .ssr.

EXCEPTIONS

None

#### OPERATION

NEUT := false; cfa := cfa + 1; b := 0; AC := cfa;

#### Neutralization Instructions, continued

#### OVERRIDE NEUTRALIZATION OF SUBROUTINE CALL SHADOW

000

01111

RIP/coprocessor

3

5

24

#### FORMAT

ovneuti

#### DESCRIPTION

This instruction is the same as ovneut, but after executing the shadow instruction, the stack is incremented. Thus a subroutine return is made *not* to the shadow instruction but to the one following it. This instruction has a short format and is placed with the shadow processor operation to be executed, immediately following the subroutine call.

#### NEUTRALIZATION

This instruction is executed regardless of the b bit of the .ssr.

#### **EXCEPTIONS**

None

```

NEUT := false;

stack(tos) := stack(tos) + 1;

cfa := cfa + 1;

b := 0;

AC := cfa;

```

#### PRELIMINARY DATA October 1988

#### Neutralization Instructions, continued

#### REVERSE NEUTRALIZATION OF BRANCH SHADOW

000

00101

RIP/coprocessor

3

5

24

#### FORMAT

revneut

#### DESCRIPTION

Reverses the neutralization effect that would normally have been applied to an instruction. If it would normally have been neutralized, it is not; if it would normally *not* have been neutralized, it is. Short instruction format.

This instruction is typically used to allow the shadow instruction to be executed as part of a loop, rather than being neutralized. This saves one cycle per iteration.

#### **EXCEPTIONS**

None

#### NEUTRALIZATION

This instruction is neutralized if the b bit of the .ssr contains a zero.

**OPERATION**

####

# Intrasystem Data Transfer Instructions

#### TRANSFER WORD TO RCS INTERNAL REGISTER

| ſ | 000 | 00000 | 001 | ra | ext2 | x  | from RIP         |

|---|-----|-------|-----|----|------|----|------------------|

|   | 3   | 5     | 3   | 5  | 5    | 11 | -                |

| Γ | 000 | 00000 | 11  | x  | ext2 | x  | from coprocessor |

|   | 3   | 5     | 2   | 6  | 5    | 11 |                  |

#### FORMAT

From RIP

| mov | ra, .tim | $\{ext2 = 00110b\}$ |

|-----|----------|---------------------|

| mov | ra, .ssr | $\{ext2 = 01000b\}$ |

| mov | ra, .iea | {ext2 = 01010b}     |

| mov | ra, .ifa | {ext2 = 01100b}     |

| mov | ra, .brk | {ext2 = 01110b}     |

| mov | ra, .ibr | {ext2 = 01111b}     |

From Coprocessor

| mov | .adbus, .tim | {ext2 = 00110b}     |

|-----|--------------|---------------------|

| mov | .adbus, .ssr | $\{ext2 = 01000b\}$ |

| mov | .adbus, .iea | {ext2 = 01010b}     |

| mov | .adbus, .ifa | {ext2 = 01100b}     |

| mov | .adbus, .brk | $\{ext2 = 01110b\}$ |

| mov | .adbus, .ibr | $\{ext2 = 01111b\}$ |

|     |              |                     |

#### DESCRIPTION

These instructions cause the RCS to write the contents of the AD bus into the selected internal register. The two instruction formats differ in their effect on the other components in the system. The first set is recognized by the RIP and causes it to drive the AD bus with one register from its register file. The second set allows a coprocessor to drive the AD bus. Long instruction format.

#### NEUTRALIZATION

These instructions are not neutralized reliably, and therefore must not be put into branch shadows. Furthermore, since interrupts cause an instruction to be neutralized, these instructions must only be used when interrupts are disabled.

PRELIMINARY DATA October 1988

# Intrasystem Data Transfer Instructions, continued

```

{ Note: the cancellation of the instruction by NEUT- does not always work. }

if b = 1 then

NEUT := TRUE;

else

NEUT := FALSE;

if ssr.s = 0 then

ssr.prvflg := TRUE;

else

case ext2 {AD bus is driven by the RIP or a coprocessor} of

00110b :

:= AD;

tim

01000b :

:= AD;

ssr

01110b :

:= AD;

ibr

01010b :

{ no action }

;

01100b :

{ no action }

;

01110b :

{ no action }

;

endcase;

endif;

else

case ext2 of

00110b : tim

:= AD;

01000b : ssr

:= AD;

01110b : ibr

:= AD;

01010b : iea

:= AD;

01100b : ifa

:= AD;

01110b : brk

:= AD;

endcase:

endif;

b := 0;

cfa := cfa + 1;

AC := cfa;

```

# Intrasystem Data Transfer Instructions, continued

TRANSFER WORD FROM RCS INTERNAL REGISTER

| 000                                                          | 00000                 | 011 | ra | ext2 | 0  | to RIP                                                 |  |  |  |  |

|--------------------------------------------------------------|-----------------------|-----|----|------|----|--------------------------------------------------------|--|--|--|--|

| 3                                                            | 5                     | 3   | 5  | 5    | 11 | 1                                                      |  |  |  |  |

| 000                                                          | 00000                 | 11  | x  | ext2 | x  | to coprocessor                                         |  |  |  |  |

| 3                                                            | 5                     | 2   | 6  | 5    | 11 |                                                        |  |  |  |  |

| FORM                                                         | FORMAT                |     |    |      |    |                                                        |  |  |  |  |

| To RIP                                                       | To RIP To Coprocessor |     |    |      |    |                                                        |  |  |  |  |

| mov .tim, ra {ext2 = 00111b}<br>mov .ssr, ra {ext2 = 01001b} |                       |     |    |      |    | n, .adbus {ext2 = 00111b}<br>r, .adbus {ext2 = 01001b} |  |  |  |  |

#### DESCRIPTION

The RCS drives the AD bus with the contents of the designated register. The different formats allow either the RIP or the coprocessor to receive the data. Long instruction format.

mov

mov

.iea, .adbus

.ifa, .adbus

#### NEUTRALIZATION

.iea, ra

.ifa, ra

These instructions are neutralized if the b bit of the .ssr is a one.

$\{ext2 = 01011b\}$

$\{ext2 = 01101b\}$

EXCEPTIONS

None

mov

mov

$\{ext2 = 01011b\}$

$\{ext2 = 01101b\}$

PRELIMINARY DATA October 1988

# Intrasystem Data Transfer Instructions, continued

**OPERATION**

$\mathbf{C}$

```

if b = 1 then

NEUT := TRUE;

else

NEUT := FALSE;

if ssr.s = 0 then

ssr.prvflg := TRUE;

endif;

case ext2 of

00111b : AD

:= tim;

01001b : AD := ssr;

01011b : AD := iea;

01101b : AD

:= ifa;

endcase;

endif;

b := 0;

cfa := cfa + 1;

```

# Intrasystem Data Transfer Instructions, continued

#### POP STACK TO RIP REGISTER OR COPROCESSOR

| 000 | 00000 | 010 | ra | 00000 | x  | Pop to RIP         |

|-----|-------|-----|----|-------|----|--------------------|

| 3   | 5     | 3   | 5  | 5     | 11 |                    |

| 000 | 00000 | 101 | x  | 00000 | x  | Pop to coprocessor |

| 3   | 5     | 3   | 5  | 5     | 11 |                    |

#### FORMAT

| pops | ra     | {pop to RIP}         |

|------|--------|----------------------|

| or   |        |                      |

| pops | .adbus | {pop to coprocessor} |

#### DESCRIPTION

The contents of the top of the stack are driven onto the AD bus. The stack is popped. The RIP recognizes the first format and latches the data from the AD bus. Long instruction format.

#### NEUTRALIZATION

These instructions are neutralized if the b bit of the .ssr is a one.

#### **EXCEPTIONS**

Stack underflow

```

if b = 1 then

NEUT := TRUE;

else

NEUT := FALSE;

AD := stack (tos);

tos := tos - 1;

endif;

b := 0;

cfa := cfa + 1;

AC := cfa;

```

PRELIMINARY DATA October 1988

# Intrasystem Data Transfer Instructions, continued

COPY STACK TO RIP REGISTER OR COPROCESSOR

| 000 | 00000 | 010 | ra | 00001 | ×  | Copy stack to RIP register |

|-----|-------|-----|----|-------|----|----------------------------|

| 3   | 5     | 3   | 5  | 5     | 11 | -                          |

| 000 | 00000 | 101 | x  | 00001 | x  | Copy stack to Coprocessor  |

| 3   | 5     | 3   | 5  | 5     | 11 |                            |

#### FORMAT

| mov | .tos, ra     | {copy to RIP}         |

|-----|--------------|-----------------------|

| mov | .tos, .adbus | {copy to coprocessor} |

#### DESCRIPTION

The contents of the top of the stack are driven onto the AD bus. The stack is *not* popped. The RIP recognizes the first format and latches the data from the AD bus. Long instruction format.

#### NEUTRALIZATION

These instructions are neutralized if the b bit of the .ssr is a one.

**EXCEPTIONS**

None

#### OPERATION

© Copyright WEITEK 1988

### Intrasystem Data Transfer Instructions, continued

# PUSH RIP REGISTER OR COPROCESSOR ONTO STACK

| 000 | 00000 | 000 | ra | 00000 | x  | Push RIP register |

|-----|-------|-----|----|-------|----|-------------------|

| 3   | 5     | 3   | 5  | 5     | 11 |                   |

| 000 | 00000 | 100 | x  | 00000 | x  | Push Coprocessor  |

| 3   | 5     | 3   | 5  | 5     | 11 | -                 |

#### FORMAT

| pushs | ra     | {push RIP register} |

|-------|--------|---------------------|

| pushs | .adbus | {push coprocessor}  |

#### DESCRIPTION

The contents of the AD Bus are pushed onto the RCS stack. The RIP recognizes the first format and drives the AD bus with the selected register. Long instruction format.

#### NEUTRALIZATION

These instructions are neutralized if the b bit of the .ssr is a one.

#### **EXCEPTIONS**

Stack overflow

PRELIMINARY DATA October 1988

#### Intrasystem Data Transfer Instructions, continued

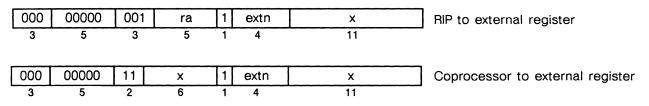

TRANSFER WORD TO EXTERNAL REGISTER

#### FORMAT

mov ra, extn mov .adbus, extn

#### DESCRIPTION

For all formats the OP bus is driven by the external register number (must be in the range 0000b-1110b). Long instruction format. Other than driving the OP bus, the RCS treats the RIP and coprocessor forms of this instruction as a no-op.

Note: the transfer to and transfer from coprocessor to/from external register instructions have the same format. The actual direction of the transfer is a convention between the coprocessor and the external register and is not specified here.

#### NEUTRALIZATION

These instructions are neutralized if the b bit of the .ssr is a one.

**EXCEPTIONS**

Stack underflow

# Intrasystem Data Transfer Instructions, continued

#### TRANSFER WORD FROM EXTERNAL REGISTER

| 000 | 00000 | 011         | ra | 1 | extn | x  | External register to RIP         |

|-----|-------|-------------|----|---|------|----|----------------------------------|

| 3   | 5     | 3           | 5  | 1 | 4    | 11 | _                                |

|     |       | <del></del> |    |   |      |    | -                                |

| 000 | 00000 | 11          | x  | 1 | extn | X  | External register to Coprocessor |

| 3   | 5     | 2           | 6  | 1 | 4    | 11 | -                                |

#### FORMAT

mov extn, ra mov extn, .adbus

#### DESCRIPTION

Takes a word from the AD bus and copies it to a register in the RIP or coprocessor.

For all formats the OP bus is driven by the external register number (must be in the range 0000b-1110b). Other than driving the OP bus, the RCS treats the RIP and coprocessor forms of this instruction as a no-op. Long instruction format.

Note: the transfer to and transfer from coprocessor to/from external register instructions have the same format. The actual direction of the transfer is a convention between the coprocessor and the external register and is not specified here.

#### NEUTRALIZATION

These instructions are neutralized if the b bit of the .ssr is a one.

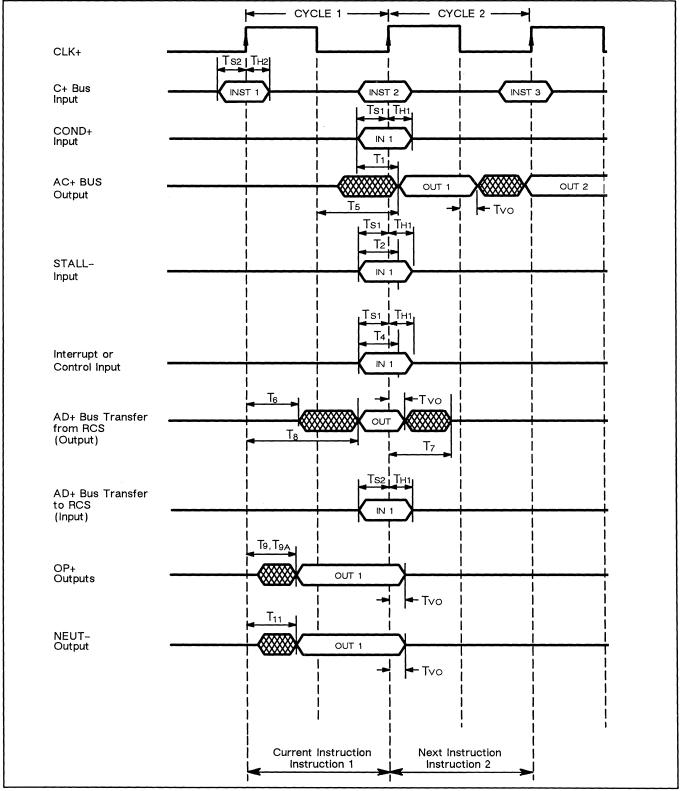

#### **EXCEPTIONS**