|  | VGT USERS     |

|--|---------------|

|  | GUIDE         |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  |               |

|  | ASIC Division |

|  |               |

|  |               |

|  | \$15.00       |

|  |               |

| VGT USERS<br>GUIDE                         |

|--------------------------------------------|

|                                            |

|                                            |

|                                            |

|                                            |

|                                            |

|                                            |

| •<br>• • • • • • • • • • • • • • • • • • • |

| •                                          |

**ASIC** Division

©1988 VLSI Technology, Inc. All rights reserved. This document and the software that it describes are the proprietary and confidential property of VLSI Technology, Inc. ("VLSI") and Xidak Inc., for distribution and use only under license from VLSI and may not be copied without VLSI's written consent.

VLSI Technology reserves the right to make changes in the contents of this document without notice. VLSI Technology assumes no responsibility for any errors that appear in this document.

Mainsail is a trademark of Xidak, Inc. Bitpad is a trademark of Summagraphics, Inc. VAX and Vax/VMS are trademarks of Digital Equipment Corporation. Unix is a trademark of AT&T Bell Laboratories. EMBOS is a trademark of Elxsi, Inc. ROS is a trademark of Ridge Computers. Aegis is a trademark of Apollo Computer, Inc.

#### RESTRICTED RIGHTS LEGEND

Use, duplication or disclosure by the U.S. Government is subject to restrictions as set forth in subdivision (b) (3) (ii) of the Rights In Technical Data and Computer Software clause at 52.227-7013 (48 CFR 252).

# CONTENTS

| Overview  |                            | T  |

|-----------|----------------------------|----|

|           | Introduction               | 1  |

|           | VGT Series Description     | 1  |

|           | Process                    | 1  |

|           | Array Core                 | 3  |

|           | Features                   | 3  |

|           | Package Availability       | 4  |

|           | I/O Buffers                | 4  |

|           | I/O Locations              | 4  |

|           | Output                     | 5  |

|           | Input                      | 5  |

|           | Power                      | 5  |

|           | Guide Description          | 6  |

|           | Terms And Definitions      | 7  |

|           |                            |    |

| Design Cy | ycle                       | 9  |

|           | Introduction               | 9  |

|           | Planning Your Design       | 9  |

|           | Preliminary Specifications | 11 |

|           | Design/ Schematic Capture  | 11 |

$\mathbf{2}$

1

|           | Schematic Capture                                       | 11 |

|-----------|---------------------------------------------------------|----|

|           | Netlist Screening                                       | 12 |

|           | Timing Verification                                     | 13 |

|           | Logic Verification And Pre-Route Design<br>Verification | 13 |

|           | Logic Verification                                      | 13 |

|           | Pre-Route Design Verification                           | 13 |

|           | Test Vector Check                                       | 14 |

|           | Fault Simulation                                        | 16 |

|           | Initial Signoff Review                                  | 16 |

|           | Place and Route                                         | 17 |

|           | Post Route Performance Verification                     | 17 |

|           | Physical Design Verification                            | 17 |

|           | Final Signoff Review                                    | 18 |

|           | Test Generation and Prototype Build<br>and Test         | 18 |

|           | Test Generation                                         | 18 |

|           | Prototype Build and Test                                | 18 |

|           | Prototype Approval                                      | 18 |

|           | Design Assistance                                       | 19 |

|           |                                                         |    |

| Specifyin | g Your Design                                           | 21 |

|           | Introduction                                            | 21 |

|           | Design Specifications                                   | 21 |

|           | Initial Specifications                                  | 22 |

|           |                                                         |    |

User Design Information Form 22

3

| AC/DC Specification Form                                   | 22 |

|------------------------------------------------------------|----|

| Optional Files                                             | 23 |

| Completing The User Design Information<br>Form             | 24 |

| Selecting Package Type                                     | 24 |

| Determining the Number of<br>Package Pins                  | 24 |

| Estimating Gate Count                                      | 25 |

| Selecting Array Size                                       | 25 |

| Power Calculations                                         | 26 |

| Background Information                                     | 26 |

| Completing the Power<br>Calculations Worksheet             | 28 |

| Complete the Circuit Data Section                          | 30 |

| Calculate the Internal Power<br>Dissipation (Pint)         | 30 |

| Calculate the External Power<br>Dissipation (Pext)         | 31 |

| Calculate the Total Power<br>Dissipation (Ptot)            | 31 |

| Write In The Package Type                                  | 31 |

| Write The Thermal Impedance                                | 31 |

| Calculate the Junction<br>Temperature (Tj)                 | 32 |

| Specifying Power Pads                                      | 32 |

| Background Information                                     | 32 |

| To Split or Not to Split                                   | 34 |

| How to Determine the Number and<br>Placement of Power Pads | 37 |

|          | Example I - Separate Power<br>Sources/Buses Structure      | 47 |

|----------|------------------------------------------------------------|----|

|          | Example II - Non-Separate Power<br>Sources/Buses Structure | 52 |

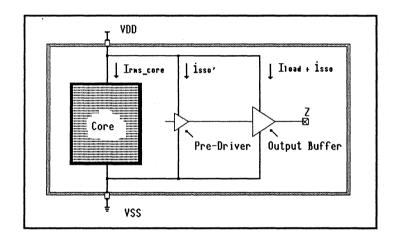

|          | Preferred Power Pad Locations                              | 54 |

|          | Preferred Power Pad Locations                              | 55 |

|          | Preparing a Bonding Diagram                                | 57 |

|          | Preparation                                                | 57 |

|          | Completing the Bonding Diagram                             | 57 |

|          | Observe these basic guidelines:                            | 59 |

| Implemen | nting Your Design                                          | 61 |

|          | Introduction                                               | 61 |

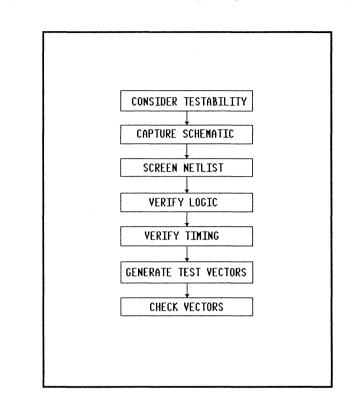

|          | Design Implementation Flow                                 | 61 |

|          | Consider Testability                                       | 62 |

|          | Capture Schematic                                          | 64 |

|          | Partitioning Considerations                                | 64 |

|          | Top Level Schematic<br>Considerations                      | 64 |

|          | Provide Adequate Signal Drive                              | 66 |

|          | Parallel Logic                                             | 67 |

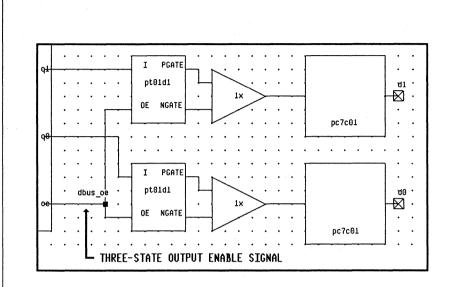

|          | Bus Repeater Cells For<br>Three-State Nodes                | 68 |

|          | Clock Buffers                                              | 68 |

|          | Weights on Clock Buffers                                   | 69 |

|          | VLSI Reserved Signal Names                                 | 69 |

|          | Place and Route Information in Your<br>Schematic           | 70 |

4

| 70 |

|----|

| 72 |

| 72 |

| 73 |

| 75 |

| 77 |

| 77 |

| 78 |

| 78 |

| 78 |

| 79 |

| 79 |

| 79 |

| 79 |

| 80 |

| 80 |

| 80 |

| 81 |

| 81 |

| 82 |

|    |

5

6

Α

| Pre-Rou | ite Design Review                   | 83   |

|---------|-------------------------------------|------|

|         | Design Preparation                  | 83   |

|         | Preparing the Netlist               | 84   |

|         | HNS Format                          | 84   |

|         | Netlist Screening                   | 84   |

|         | Preparing Test Patterns             | 84   |

|         | Creating a Critical Placement File  | 86   |

|         | Introduction                        | 86   |

|         | CPF File Format                     | 86   |

|         | Sample Critical Placement File      | 91   |

|         | Your Final Bonding Diagram          | 91   |

|         | Creating a Pad Placement File       | 92   |

|         | Determine Pinouts                   | 92   |

|         | Filling Out the Pad Placement File  | e 92 |

|         | Enter Package Pin Numbers           | 92   |

|         | Identify Pin Function               | 93   |

|         | Enter Signal And Macro Names        | 93   |

|         | Customer Marking Form               | 94   |

|         | Pre-Route Design Review and Signoff | 94   |

| Post-Ro | ute Simulation/Signoff              | 95   |

|         | Introduction                        | 95   |

|         | How to Simulate After Layout        | 95   |

|         | Final Timing Signoff Review         | 96   |

| VGT Pa  | ackage Availability                 | 97   |

Contents vii

| В            | Screen Reports And Errors | 101 |

|--------------|---------------------------|-----|

|              | Screen Report             | 101 |

|              | Cell Utilization Summary  | 101 |

|              | Design Statistics         | 102 |

|              | Design Complexity Summary | 103 |

|              | Screen Errors             | 103 |

|              | Macro Usage Table         | 107 |

| $\mathbf{C}$ | Output Buffers            | 109 |

| Index        | Index                     | 111 |

|              |                           |     |

|              |                           |     |

# CHAPTER 1

# **OVERVIEW**

Introduction This User's Guide describes the methodology for designing with VGT10 and VGT100 series gate arrays, using VLSI Technology's software tools and portable library.

For further information on using the software tools described in this guide, refer to the corresponding VLSI tool manual.

VGT Series Description Process

The VGT10 VGT100 series and advanced, are CMOS families in VLSI high-performance gate array  $Gate^{TM}$  technology. Technology's proprietary Continuous These series, fabricated using a dual metal, N-well, implanted CMOS process, have high layout efficiency. Effective channel lengths are typically  $1.5\mu$  for VGT10 and  $1.1\mu$  for VGT100. The base arrays for the current VGT10 and VGT100 series are listed in Tables 1 and 2, respectively, together with pertinent information; other bases may be added in the future.

| Marketing<br>Part # | Nominal<br>Array<br>Size | Actual<br># Raw<br>Gates <sup>1</sup> | Estimated<br>Usable<br>Gates <sup>2</sup> | # Sites | # 1/0<br>Pads <sup>3</sup> |

|---------------------|--------------------------|---------------------------------------|-------------------------------------------|---------|----------------------------|

| VGT10-016           | 1600                     | 1590                                  | 1200                                      | 3179    | 56                         |

| VGT10-024           | 2400                     | 2425                                  | 1800                                      | 4850    | 68                         |

| VGT10-037           | 3700                     | 3718                                  | 2800                                      | 7436    | 84                         |

| VGT10-064           | 6400                     | 6358                                  | 4800                                      | 12716   | 108                        |

| VGT10-084           | 8400                     | 8365                                  | 6300                                      | 16731   | 124                        |

| VGT10-106           | 10600                    | 10648                                 | 8000                                      | 21296   | 140                        |

Table 1. Standard VGT10 Series Arrays

Table 2. Standard VGT100 Series Arrays

| Marketing<br>Part # | Nominal<br>Array<br>Size | Actual<br># Raw<br>Gates <sup>1</sup> | Estimated<br>Usable<br>Gates <sup>2</sup> | # Sites | # I/O<br>Pads <sup>3</sup> |

|---------------------|--------------------------|---------------------------------------|-------------------------------------------|---------|----------------------------|

| VGT100122           | 12000                    | 12149                                 | 9000                                      | 24299   | 152                        |

| VGT100160           | 16000                    | 16038                                 | 12000                                     | 32076   | 172                        |

| VGT100205           | 20000                    | 20465                                 | 15000                                     | 40931   | 196                        |

| VGT100270           | 27000                    | 26950                                 | 20000                                     | 53900   | 224                        |

| VGT100397           | 40000                    | 39700                                 | 30000                                     | 79475   | 272                        |

| VGT100528           | 53000                    | 52800                                 | 40000                                     | 105644  | 312                        |

| VGT100665           | 66500                    | 66550                                 | 50000                                     | 133100  | 348                        |

### Notes:

1. A gate is defined as one 2-input NAND equivalent. Raw refers to total gates available before routing.

- 2. The Estimated Usable Gates value represents approximately 75% of the raw gate count. Maximum usage varies depending upon design.

- 3. Every array has eight additional dedicated VSS pads available to the user: four for internal VSS and four for output buffer VSS.

#### Array Core

The VGT10 and VGT100 cores consist of rows of uncommitted P and N transistors laid out at regular intervals. Key features are high gate density arising from a gate isolation technique and a unique global routing scheme.

Gate isolation turns off P and N transistors to isolate diffusion nodes from one another. This technique allows array area normally consumed by oxide isolation to be used as raw transistors.

The VGT gate array architecture eliminates open areas for routing channels; instead, the routing channels run over active cells.

#### Features

The VGT10 and VGT100 Series Gate Arrays provide these features:

- An advanced high-density architecture with typical 75% gate utilization.

- A flexible I/O structure, including:

- TTL, CMOS, and Schmitt trigger inputs

- pullup, pulldown, and hold circuits

4 Overview

- output drive programmable from 2 to 12 mA

- VLSI's extensive Portable Library, which allows future migration of your design to other gate array and cell-based technologies.

- Full support by VLSI Technology's comprehensive integrated IC design tools.

- An advanced dual metal, N-well, implanted CMOS process, with  $2.0\mu$  drawn channel lengths for VGT10 and  $1.5\mu$  for VGT100.

- High immunity to noise, latchup and electrostatic discharge (ESD).

#### Package Availability

The packages available for the VGT10 and VGT100 series gate array bases, as of the date of this publication, are listed in Appendix A.

### I/O Buffers | I/O Locations

Any I/O location can be programmed as input, output, bidirectional, VSS or VDD.

### Output

The output buffers have been designed to sink and source up to 12mA across the industrial temperature range. In addition, the VGT10 and VGT100 I/O buffers have minimal susceptibility to latchup and electrostatic discharge (ESD). Appendix E discusses output buffer AC characterization for the VGT family.

#### Input

By selecting appropriate library I/O cells, you can program each input location as TTL, CMOS, or Schmitt Trigger. In addition, pullup and pulldown resistors and hold circuits are available in combination with inputs, to prevent floating signals.

#### Power

A dual power bus structure isolates the output buffer power supply from that of the array core, to achieve high noise immunity. A complete set of rules for power pads is given in Chapter 3, SPECIFYING YOUR DESIGN.

There are no dedicated pads in the padring other than the eight VSS pads in the corners: four for internal VSS and four for output buffer VSS.

# Guide Description

This User's Guide contains six chapters:

- This Chapter, OVERVIEW, gives a brief overview of the VGT gate array series and its primary features.

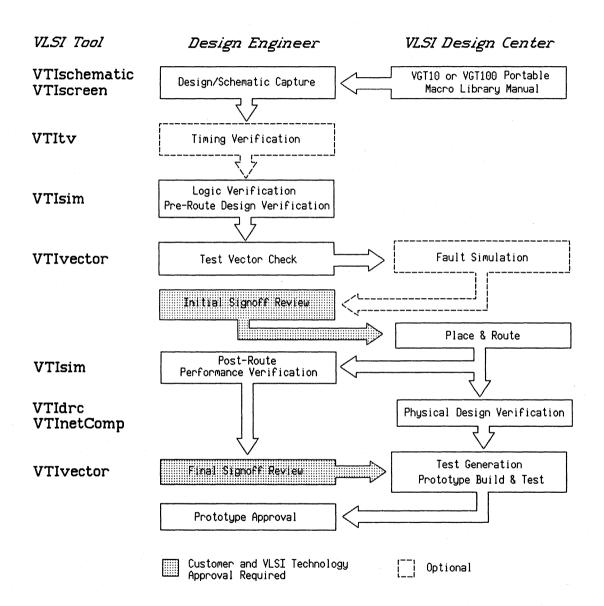

- Chapter 2, DESIGN CYCLE, lists what you, and the VLSI Technology Design Center, need to do to complete your chip, and the VLSI software design tools needed to perform these tasks.

- Chapter 3, SPECIFYING YOUR DESIGN, describes how to specify the physical characteristics of your chip, such as array size, power pads, packaging, and bonding diagrams.

- Chapter 4, IMPLEMENTING YOUR DESIGN, discusses the considerations that are unique to VGT gate array design.

- Chapter 5, PRE-ROUTE DESIGN REVIEW, describes the design tasks that must be completed before VLSI can place and route your chip.

- Chapter 6, POST-ROUTE SIMULATION/SIGNOFF, describes the design tasks that must be completed before VLSI can build prototypes of your chip.

## Terms And Definitions

This section defines the specialized terms used in this guide.

**Base Array** - A fixed-size gate array, consisting of the non-custom mask layers.

**Base Count** - The number of transistor pairs necessary to implement a particular macro function. The base count includes one end isolation transistor pair.

Cell Count - The total number of transistors in an array base divided by two.

**Gate Utilization** - The number of active gates used in a design as a percentage of total available gates. Gate utilization with the VGT series is typically 75%.

**Option** - A design implemented on a gate array base, including the custom mask layers.

**Portable Library** - VLSI's cell library, which is supported in several design and process technologies, including VGT10 and VGT100 arrays, and VSC10 and VSC100 standard cells.

**Raw Gates** - The total number of available gates in the core of a particular base array. A gate is defined as four transistors.

Sites - Refers to the core transistor pairs in which macro functions may be implemented. The number of sites is approximately equal to one half the number of raw gates. Also referred to as Cell Sites.

Site Utilization - The number of transistor pairs that are used in a design, including isolation transistors, as a percentage of total available sites. Transistor pairs are called "placement sites" or "sites." The typical maximum upper limit for site utilization with the VGT series is 90%. VTIscreen reports this value as SITE UTILIZATION PERCENTAGE. The number of sites in each base array is given in Tables 1 and 2.

Usable Gates - The number of gates that is estimated to be routable. In the VGT Series, the maximum number of usable gates is approximately 75% of the raw gates, but is dependent on the particular design and may be even higher. The difference between raw and usable gates is due to isolation transistors and routing inefficiency.

**VDDI** - VDD pad for the internal core, input logic, and pad drivers.

**VDDO** - VDD pad for the external output and I/O buffers.

VGT - Refers to two series of gate array bases first introduced by VLSI Technology, Inc. These bases use Continuous Gate TM technology to achieve dense arrays and high cell utilization.

**VGT10** - The  $2\mu$  (drawn) VGT gate array series.

**VGT100** - The 1.5 $\mu$  (drawn) VGT gate array series.

**VSSI** - VSS pad for the internal core, input logic, and pad drivers.

VSSO - VSS pad for the external output and I/O buffers.

# CHAPTER 2

# DESIGN CYCLE

### Introduction

This chapter gives a top-level look at how to plan, implement, and check your gate array design. It also describes the VLSI software tools that are used during the VGT design process. It assumes that you already have a working knowledge of the applicable tools. Detailed information concerning the use of a particular tool can be found in the appropriate user's manual; for example, details on using the VTIsim logic/timing simulator can be found in the VTIsim Users Manual.

## Planning Your Design

Figure 1 shows the standard design flow using the VGT Portable Library. The steps are described in more detail in the text following the figure. Figure 1. Standard VGT Design Flow

Preliminary Specifications Before you begin your design, you need to:

- Determine the gate array base to be used in the design.

- Define the I/O ring and pinouts.

- Select the device package.

- Describe performance specifications.

You can then fill out the Initial Design Specification Form and begin a draft of the AC/DC Specification Form.

If necessary, an Initial Specification Acceptance review can be held at a VLSI Design Center to determine design feasibility, review the specifications, and answer and resolve any technical questions.

## Design/ Schematic Capture

#### Schematic Capture

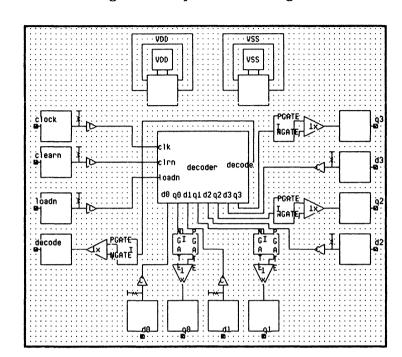

After the base and package are selected, enter your schematic using VTIschematic on your workstation. Either the VGT10 or VGT100 macro library is used, depending upon which gate array family you choose to implement your design. Wire up the appropriate macros, in a hierarchical fashion, to create the desired circuit.

For detailed instructions on schematic capture, refer to your VTIschematic manual.

## **Netlist Screening**

Next, run VTIscreen to identify simple errors and other potential problems in the logic design. It also provides a utilization summary of the particular array you have chosen. Refer to the VTIscreen manual for more details.

When you run VTIscreen to read the [hns] netlist created by VTIschematic, it:

- Calculates the internal site and I/O pad utilization and produces a summary report.

- Provides a Design Statistics report listing information on the number of nets and FromTos - connections between two pins - in your design.

- Provides a Design Complexity report listing gate equivalents per macro.

- Checks for certain design and connectivity errors and other potential problems in your design.

- Prints a short form of the report to your terminal as well as producing a disk file, [scr], containing the entire report.

- Includes in the [scr] disk file a summary listing of the number of each type of macro used as well as the instance names of each placement.

- Optionally writes an [lds] file to be used by VTIvector. This file is required for test program generation; be sure to specify this file by using the SAVE command in VTIscreen.

A summary of the reports, warnings, and errors provided by VTIscreen can be found in Appendix B of this document, SCREEN REPORTS AND ERRORS.

Timing Verification After the schematic is entered and checked, it is useful to check critical paths for timing verification. Timing verification with VTItv allows you to detemine if your design functions properly at your clock speed and that all critical speed paths meet their specified timing. This step is optional.

Logic Verification And Pre-Route Design Verification

### Logic Verification

Prepare an evaluation logic driver file and run a detailed logic simulation of your circuit with VTIsim to verify the functionality of your design. VTIsim creates waveform plots and a trace file, [trc].

### **Pre-Route Design Verification**

The customer design engineer prescribes a set of timing and test program engineering simulations, where the pre-route performance of the chip is predicted by simulating with predicted wire capacitances. These simulations are run and documented by the customer engineer, or at the VLSI Design Center. Test Vector Check Once the initial logic is verified, use VTIvector and its CHECK command to assure that the simulation vectors you have chosen adhere to the test vector guidelines described in the application note called **Test Generation Guidelines**. When there are no errors in the resulting **[ver]** error report file, VLSI can use your simulation vectors to produce Sentry test vectors.

To create the simulation vectors, prepare a standard 1MHz test program driver file and run a simulation to generate a [trc] trace output file. This file is used to create the test program for the specified tester.

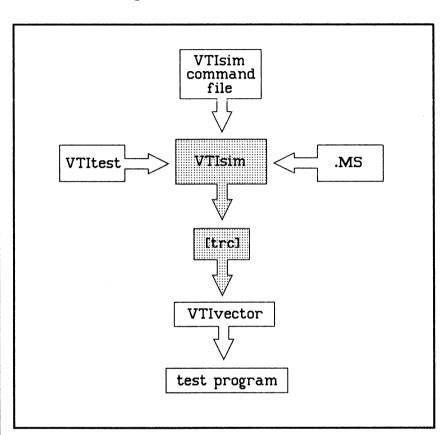

There are three ways to create the required [trc] file, as shown in Figure 2:

- Use VTItest to drive VTIsim as described in the VTItest manual.

- Use VTIsim commands entered manually or from a command file.

- Write a Mainsail .MS file to drive VTIsim as described in the VTIsim manual.

In all cases, the resulting output [trc] file is used by VTIvector, run by a VLSI Design Center, to create the test program.

Figure 2. Trace File Generation

VLSI uses your simulation trace file, [trc], and the [lds] file produced by VTIscreen, to produce the correct test vectors. These vectors are mapped from the simulation vectors that were used in your VTIsim simulation.

You also create an Input Timing Generator [1tg] file and, if you want a critical path check, an optional Critical Path Check [cpc] file. See the application note entitled **Test Generation Guidelines** for more information on creating these files.

# Fault Simulation

Fault simulation provides an automated algorithmic measure of a test program's ability to exercise nodes in your circuit. VLSI Technology Design Centers, as a service, offers assistance in performing fault simulation.

Using your design netlist and simulation vectors, VLSI Technology runs the GenRad HILO3 fault simulator, and provides you with a detailed report of the results. The report includes fault coverage, percentage of faults dropped, and potential coverage. Additionally, VLSI provides a file of undetected, undetectable and potentially detected faults, a cross-reference file, a netlist screen file, and documents to help evaluate and interpret the results.

Assistance in analyzing the results is also provided to help you determine if the fault coverage is acceptable. If not, then additional vectors are needed. VLSI can also assist you to enhance your fault coverage.

Fault simulation is an optional step.

Initial Signoff Review When simulation is complete, you can fill out the initial VLSI forms detailing the pinouts and pad selections. A completed User Design Information Form, AC/DC Specification Form, and Customer Package Marking Form are required. In addition, the Pad Placement File, on floppy disk or magnetic tape, is required. A joint customer-and-VLSI pre-route design review is then held at which the Initial Signoff Review Checklist is filled out and signed off.

Place and The VLSI Technology Design Center automatically places and routes your design in accordance with your Pad Placement Route File and the optional Critical Placement File. The Design Center checks the resulting CIF data base file with VTIdrc verifies the and it against original schematics with VTInetComp. A post-route [pst] file containing the actual routing interconnect wire capacitance is returned to you for use in post-route timing analysis.

Post Route After routing, the VLSI Design Center provides you with a Perfor-[pst] file containing the metal interconnect routing capacitances. Use this file to rerun the simulation, with mance Verifica-VTIsim in the timing mode, to get accurate timing tion information about your circuit. You can then document the prescribed set of design timing and test program performance simulations, to be included in the final signoff review package. Based upon this information, you decide whether or not to proceed with prototyping the array.

Physical Design Verification After the circuit is routed, VLSI does a final verification on your circuit by:

- Comparing the [hns] netlist from VTIschematic to the extracted netlist from the physical routed array and

- Performing a design rule check of the physical array.

These are the final checks performed before prototype build can begin.

Final Signoff Review

Test.

A joint customer-and-VLSI post-route design review is held, during which the **Final Timing Signoff Review Checklist** is filled out and signed off.

**Test Generation**

During the Test Generation phase, the VLSI Technology Design Center uses VTIvector to convert your simulation trace file, [trc], to a test program for wafer sort and final device test of your prototypes.

#### Prototype Build and Test

The VLSI Technology Design Center submits the fully checked and verified mask data base to the foundry for design code mask generation. VLSI fabricates the wafers, assembles the prototype parts, tests them, and delivers them to the customer.

## Prototype Approval

When you approve the tested prototypes by signing the **Prototype Approval Report**, the device is transferred to manufacturing and is ready for volume production.

Generation and Prototype Build and Test Design Assistance VLSI Technology Design Centers, as a service, offer assistance in performing any step in the design flow. Design Center services include test vector generation, functional/timing simulation, fault simulation and special testing services.

# CHAPTER 3

# SPECIFYING YOUR DESIGN

Introduction This chapter introduces the recommended methodology for beginning a VLSI Technology gate array design.

Design Specifications Preparing your design specifications requires you to make several decisions and calculations about your circuit. These specifications are listed on the User Design Information Form: the array size, the package type, and other physical design specifications.

Prepare the initial specifications based on planning done at your site, and submit them to VLSI Technology. The initial specifications include:

- User Design Information Form

- AC/DC Specification Form

- Customer Package Marking Form

- Special requirements (optional)

These are your first performance goal statements for the circuit. The initial specifications identify key requirements and estimates such as gate count, I/O buffer count, AC characteristics, power, and packaging.

Submit the initial specifications before implementing the actual design so that VLSI Technology can advise you of the feasibility of your design plan. Because this phase occurs early in the design process, and because estimates are used, initial specifications should be considered only as guidelines.

Initial Specifications

#### User Design Information Form

Use this form to provide the VLSI Design Center with information and general specifications for your design, such as:

- The array size

- Prototype and production packages for your design

- Maximum operating frequency

- Engineering contact

- Estimated design schedule

### AC/DC Specification Form

Use this form to specify the operating conditions for your chip:

- Ambient operating temperature

- Supply voltage

- Power dissipation

- Output load capacitance

- Input capacitance

- Output three-state leakage current

- Input leakage current

- VIL, VIH, VOL, VOH, IOL, IOH

- Critical path information

#### **Optional Files**

Performance requirements can affect many of your design decisions. VLSI Technology's VGT series of gate arrays is specified for high performance design and offers some very high drive output buffers. Even so, your design may have one or more critical paths requiring special design consideration.

VLSI Technology addresses this problem in two ways. For placement and routing, VLSI allows you to specify critical placements in a **critical placement file**, CPF (Chapter 5). To test a critical path, you can submit a **critical path check file**, CPC. Refer to the application note called **Test Generation Guidelines** for information on creating the CPC file.

Both of these files are optional, and need only be submitted in the case of some critical timing that even the VGT series' overall high performance specifications cannot guarantee without special attention.

While you do not submit these files until the end of the design process, the critical path should be identified and analysed at the **beginning** of the design specification.

### Completing The User Design Information Form

This section describes the information required to complete the User Design Information Form.

#### Selecting Package Type

You need to specify the package type for both the prototype and production versions of your chip on the User Design Information Form. You can choose from a variety of plastic and ceramic packages for your device, including:

- Plastic dual in-line packages, PDIP

- Side-brazed ceramic packages, S/B

- Leaded ceramic chip carriers, LDCCC

- Leadless ceramic chip carriers, LLCCC

- Plastic leaded chip carriers, PLCC

- Ceramic pin-grid arrays, CPGA

- Plastic pin-grid arrays, PPGA

Decide the package type and size you want, using the charts in Appendix A. Contact your VLSI Technology Design Center for information on availability of packages not listed in these charts.

#### Determining the Number of Package Pins

One package pin is required for each input, output, bidirectional, power and ground signal. The number of package pins is the number of pins needed for the design plus power and ground pins. The section entitled How To Determine the Number and Placement of Power Pads, later in this chapter, tells how to determine the number of power pins. Write the number of input, output, bidirectional, power, and ground pins on the User Design Information Form as part of your initial specifications.

This information is also required for preparing a bonding diagram, which is covered in the section entitled **Preparing a Bonding Diagram**, later in this chapter.

#### Estimating Gate Count

Estimate the number of gates your design will contain. If this number exceeds 75% of the raw gate count of the base array you selected, please contact your VLSI Design Center for approval.

#### Selecting Array Size

Each array size has a specific number of gates, I/O pads, and fixed VSS pads, as shown in Tables 1 and 2 in Chapter 1. To choose the device which best suits your needs, you must determine the following factors about your circuit:

- Percentage of array used (gate utilization)

- Number of I/O signals

- Number of power pads (VSSI, VSSO, VDDI, VDDO)

Determining these factors will aid you in properly filling out the User Design Information Form. More importantly, accurately determining these factors helps you choose the package type most appropriate for your gate array design.

## **Background Information**

When you complete the **Power Calculations Worksheet** according to the instructions at the end of this section, you will be using typical power dissipation figures supplied by VLSI for each array series. These figures are based on the following considerations:

- Causes of Power Dissipation: The amount of heat generated within the silicon chip, known as power dissipation, is low in CMOS technology, compared to other technologies. Power dissipation causes temperature to rise, increasing a circuit's propagation delay. The three causes of power dissipation in CMOS technology are:

- 1. The charging and discharging of the internal capacitance of a circuit. Known as AC power dissipation, the charging and discharging -- switching -- of circuit capacitance is responsible for more than 90% of a circuit's total power dissipation. The power dissipation in a CMOS circuit is essentially a function of the frequency of the logic switching. The charging of a capacitor (C) to a voltage (V) through a P-channel device builds up a charge (CV) and stores energy (CV\*V). This energy is later discharged through the N-channel device which is paired with the P-channel device. When such switching takes place at a frequency (F), the resulting power dissipation can be expressed as  $P = FCV^2$ , where P is power dissipation.

- 2. DC current. There are two types of DC power consumption: static DC current, which flows through ON transistors; and leakage DC current, which

Power Calculations continues to flow when transistors are OFF. Because DC leakage in a properly functioning CMOS circuit is very low, you need to set up a test condition in which all static DC current can be turned off, so DC leakage (static Idd) can be measured easily.

The total power dissipation of a gate array option can be accurately estimated by adding the estimated power dissipation for the macros you have used in your design, and multiplying by a correction factor to account for the percentage of gates which switch simultaneously. Statistically, 0.20 (20%) has been found to be a useful correction factor, reflecting the percentage of simultaneously switching gates commonly found in VGT designs. Your own estimate may be somewhat higher or lower, depending on the characteristics of your design.

The power dissipation for each VGT macro is given in the library manual. Unused I/O macro locations dissipate no power. Maximum allowable power dissipation, of course, depends on the package and cooling system used.

3. Transient currents. Transient currents occur when the P- and N- transistors switch from the High to Low state, or vice-versa, in the period when:

### VTH(N) > VIN < VDD-VTH(P)

where VTH = input threshold loads, N = N-transistor, VIN = input, VDD = supply voltage, and P = P-transistor. Transient currents are responsible for less than 10% of the total power dissipation.

### Completing the Power Calculations Worksheet

The Power Calculations Worksheet, illustrated in Figure 3, helps you calculate your circuit's junction temperature, which is the temperature of the die inside the package. It is also used to arrive at certain values required on the AC/DC Specifications Form. VLSI encourages you to include a copy of the worksheet as part of the initial signoff review package, although it is not required.

Completing the **Power Calculations Worksheet** requires the following steps, described in detail in the text that follows:

- Complete the circuit data section.

- Calculate the Register Percentage (R).

- Calculate the Internal Power Dissipation (Pint).

- Calculate the External Power Dissipation (Pext).

- Calculate the Total Power Dissipation (Ptot).

- Calculate the Junction Temperature (Tj).

| Figure 3. Power Calculations Worksheet |                                                                  |      |         |           |       |

|----------------------------------------|------------------------------------------------------------------|------|---------|-----------|-------|

|                                        | POWER CALCULATIONS                                               | WORK | SHEET   |           |       |

| DES                                    | IGN NAME                                                         |      |         |           |       |

| VLS                                    | I TECHNOLOGY PART NUMBER                                         |      |         |           |       |

|                                        | ARRAY SERIES MILLIWATTS/GATE                                     | Р    | = 0.020 | mW/MHZ/G/ | TE    |

|                                        | AVG. OPERATING FREQUENCY (F)                                     | F    | =       | Mł        | łZ    |

|                                        | EST. FRACTION OF GATES SWITCHI<br>SIMULTANEOUSLY (TYPICALLY 0.20 |      | =       |           |       |

|                                        | AMBIENT OPERATING TEMPERATURE                                    | TA   | =       | C         |       |

|                                        | NUMBER OF GATES                                                  | G    | =       |           |       |

|                                        | NUMBER OF OUTPUT PINS                                            | В    | =       |           |       |

|                                        | AVG. OUTPUT LOAD CAPACITANCE                                     | С    | =       | PF        | 7     |

|                                        | NTERNAL POWER DISSIPATION<br>INT = P * F * S * G                 | PINT | =       | mV        | I     |

| E<br>P                                 | XTERNAL POWER DISSIPATION<br>EXT = 0.035 * F * B * .2 * C        | PEXT | =       | mV        | I     |

| -                                      | OTAL POWER DISSIPATION<br>TOT = 0.001 * (PINT + PEXT)            | PTOT | =       | W         |       |

| Р                                      | ACKAGE TYPE (INCL. # PINS)                                       |      |         |           |       |

| Т                                      | HETA JA OF PACKAGE                                               |      |         | de        | eg. ( |

| -                                      | UNCTION TEMPERATURE<br>J = (PTOT * THETA JA) + TA                | TJ   | =       | C         |       |

|                                        |                                                                  |      |         |           |       |

REPORT GENERATED BY:

### Complete the Circuit Data Section

Complete each part of the circuit data section as follows:

- ARRAY SERIES MILLIWATTS/GATE (P). Typical power dissipation in milliwatts/MHz/gate. The typical power dissipation for VLSI's VGT arrays is provided in the datasheets in the VGT10 and VGT100 Macro Library Manuals.

- AVERAGE OPERATING FREQUENCY (F). Write the circuit's operating frequency in megahertz in the blank.

- AMBIENT OPERATING TEMPERATURE (Ta). Write the circuit's maximum ambient operating temperature in degrees centigrade in the blank.

- NUMBER OF GATES (G). Write the number of gates required by the circuit in the blank.

- NUMBER OF OUTPUT PINS (B). Write the number of outputs the circuit contains in the blank.

- AVERAGE OUTPUT LOAD CAPACITANCE (C). Estimate the output load capacitance using the input capacitance specifications for the interfacing chips and the interconnect capacitance. Write your estimate of the average, in picofarads, in the blank.

### Calculate the Internal Power Dissipation (Pint)

Using the values you noted in the circuit data section, and the Register Percentage you calculated, solve the equation shown and write the result in the blank.

## Calculate the External Power Dissipation (Pext)

Using the values you noted in the circuit data section, solve the equation shown, and write the result in the blank.

### Calculate the Total Power Dissipation (Ptot)

Add the Internal Power Dissipation to the External Power Dissipation and multiply the sum by .001. The result is the circuit's Total Power Dissipation in watts. Write the results in the blank.

## Write In The Package Type

Write the type of package you have chosen, including the number of pins, in the blank provided.

### Write The Thermal Impedance

Write the thermal impedance (Theta JA) of the package you have chosen in the blank provided. This value is given in the Semiconductor Package Selection Guide which you obtain from the Design Center.

The junction-to-ambient (JA) thermal resistance data is based on a 10,000 square mil die, with the board mounted in still air. The thermal resistance varies with the materials used, die size, process technology, air circulation, and heat dissipation characteristics of the device. Values listed in the Package Selection Guide are meant to serve as guidelines and are believed to be on the high side. For larger die, the values are typically lower.

## Calculate the Junction Temperature (Tj)

Multiply the Total Power Dissipation by the thermal impedance  $(\Theta_{ja})$  of the package you have chosen. When the thermal impedance is given as a range, use the highest value in the range. Add the result to the Ambient Operating Temperature  $(T_a)$  you noted in the circuit data section. Write the sum in the blank. This is the estimated junction temperature in your circuit.

## Specifying Power Pads

The rules, tables, and procedures in this section must be closely followed to ensure reliability of your VGT design. Various design examples are presented at the end to help you determine the right number of power pins for your design.

### **Background Information**

The VGT family I/O buffers are designed for high output drive capability. The switching current of an output buffer with this drive level can be as high as 95 mA. When a number of output buffers switch simultaneously, within a window of 100ns (worst case), the peak switching current at a VSS or VDD pin is high enough to cause a voltage spike on the internal VSS and VDD buses. This spike might result in erroneous switching of the input level shifters. TTL input level shifters are exceptionally sensitive to these spikes since they are designed to operate within narrow VIL and VIH levels.

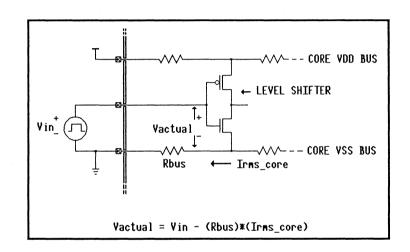

Power pin spikes are caused mainly by two factors. One source is the inductive voltage drop/surge caused by the lead inductance of the package pin bonded to the power pad. The other factor affecting the switching performance of input level shifters is the ohmic voltage drop across the VSS power bus between the virtual VSS of the level shifter and the VSS pin of the device. This voltage drop causes the input of the level shifter to see an actual voltage of VIN reduced by the voltage drop across the VSS bus (Figure 4).

#### Figure 4. Level Shifter Model

Additionally, enough power must be applied to handle the DC requirements of the output buffers and the average operating current of the array core.

### To Split or Not to Split

The VGT family power structure is designed for maximum flexibility of power pad arrangement. Power macros can be selected to:

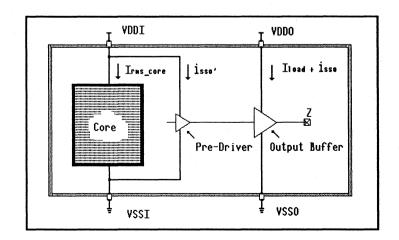

• Have a separate VSS and VDD bus structure for the output buffers and the input buffers/array core (Figure 5). This arrangement requires a minimum of two VSS pins and two VDD pins, and is by far the best avoiding input level arrangement for sensitivity problems. Although using two separate power supplies is the ultimate in performance optimization, running two separate power traces from a single external power supply is the next best thing. This requires bonding out internal and external power pairs separately. However, the noise immunity performance obtained from such a split is much better than using a non-split power configuration. For the purpose of the next sections, treat the case of internally split power pairs powered from two separate traces of a single supply as a case of two separate supplies.

#### Figure 5. Split Power Supplies

VLSI Technology Inc - 6 April 1988

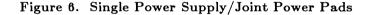

• Have no separate VSS and VDD power buses (Figure 6). The internal and external VSS and VDD buses are shorted at the power pad level. This is a less favorable arrangement than the separate power buses described above, but it is maintained since some applications cannot manage to have two separate power traces on the board housing the part.

Regardless of the choice of a joint or separate power bus arrangement, noise problems are minimized by choosing the proper package pins for power. This is due to the fact that different pins of the same package have a wide range of lead inductance, ranging from less than 5 nH to over 20 nH. For the same current level, a 20 nH pin produces a spike four times greater than the voltage spike caused by a 5 nH pin. Thus, choosing the appropriate power pin assignment for a selected package can by itself reduce the number of power pins required, and the associated noise, by a large factor. Output buffers' DC currents, IOL and IOH, establish high current demand on the supplies. Thus, the output buffers are designed with four levels of drive capability: 2 mA, 4 mA, 8 mA, and 12 mA. The buffer with the lowest drive capability should be used, unless higher speed or drive capability is required.

As seen in Figures 5 and 6, there are four primary current paths in your design:

- Irms\_core is the RMS current required by the internal core of the array. This current is primarily a function of operating frequency and array utilization.

- **1***sso* is the instantaneous current associated with the simultaneously switching output buffers.

- **1sso'** is the instantaneous current caused by the simultaneously switching outputs. This current is associated with the internal core since the power for the pre-drivers is tapped from the internal power bus.

- Iload is the DC current that the output buffers sink when they output a low state.

With split supplies, shown in Figure 5, 1550 is steered away from the input level shifters, which greatly improves noise margins. Designs using a single supply must effectively handle all current components through one VSS bus. This deteriorates the input noise margins, and usually requires more power pairs. How to Determine the Number and Placement of Power Pads Use the steps given in this section to determine the number and placement of power pairs in your design. Determining power pairs and placement can be an iterative process if your design operates at a very high frequency and has many simultaneously switching outputs.

### • Step One: Determine the power pin locations.

If the pin assignment is predetermined, then the pin numbers used for power are known and their inductances can be looked up in the package inductance table, Table 3. If the bonding is not preassigned, consult the package inductance table for the package pins with the least inductance. If only partial bonding flexibility is available, try to assign the pin with the lowest inductance to VSS.

| S/B                      | Pi                           | in Inductance                      | - S/B Packag                | es                      |

|--------------------------|------------------------------|------------------------------------|-----------------------------|-------------------------|

| PKG.                     | Low<br>(0 - 5 nH)            | Medium Low<br>(5 - 10 nH)          | Medium<br>(10 - 15 nH)      | High<br>(15 - 20 nH)    |

| 22-pin<br>S/B            | 2, 3, 7-10,<br>13, 14, 18-21 | 1, 4, 5, 11,<br>12, 15, 16,<br>22  | 6, 17                       |                         |

| 24-pin<br>S/B            | 2-11,<br>14-23               |                                    | 1, 12, 13, 24               |                         |

| 28-pin<br>S/B<br>250x250 | 4-11,<br>18-25               | 2, 3, 12, 13,<br>16, 17, 26,<br>27 | 1, 14, 15,<br>28            |                         |

| 28-pin<br>S/B<br>310x310 | 6-9,<br>20-23                | 1-5, 10-19,<br>24-28               |                             |                         |

| 28-pin<br>S/B<br>350x350 | 4-11,<br>18-25               | 1-3, 12-17,<br>26-28               |                             |                         |

| 40-pin<br>S/B            | 8-13, 28-33                  | 2-7,14-19,<br>22-27,<br>34-39      | 1, 20, 21, 40               |                         |

| 48-pin<br>S/B            | 10-15,<br>34-39              | 4-9, 16-21,<br>28-33,<br>40-45     | 1-3, 22-27,<br>46-48        |                         |

| 64-pin<br>S/B            |                              | 10-23,<br>42-55                    | 2-9, 24-31,<br>34-41, 56-63 | 1,32,33,64<br>(23.4 nH) |

Table 3. Package Pin Inductance

| CPGA            | Pin Inductance - CPGA Packages |                                                                                                                                                                    |                                                                                                                                                                                                                                                                |                      |  |  |  |

|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| PKG.            | Low<br>(0 - 5 nH)              | Medium Low<br>(5 - 10 nH)                                                                                                                                          | Medium<br>(10 - 15 nH)                                                                                                                                                                                                                                         | High<br>(15 - 20 nH) |  |  |  |

| 68-pin<br>CPGA  | 9, 26, 43, 60                  | All pins<br>except 9,26,<br>43 and 60                                                                                                                              |                                                                                                                                                                                                                                                                |                      |  |  |  |

| 84-pin<br>CPGA  | 1, 22, 43, 64                  | All pins<br>except 1,22,<br>43 and 64                                                                                                                              |                                                                                                                                                                                                                                                                |                      |  |  |  |

| 120-pin<br>CPGA |                                | 1, 2, 4, 5,<br>7-26, 28, 29,<br>31, 32, 34, 35,<br>37-56, 58, 59,<br>61, 62, 64, 65,<br>67-86, 88, 89,<br>91, 92, 94, 95,<br>97-116, 118,<br>119                   | 87, 90, 93,<br>96, 117, 120                                                                                                                                                                                                                                    |                      |  |  |  |

| 180-pin<br>CPGA | 23,68,113,<br>158              | 1, 10, 11,<br>16-18, 22,<br>24, 28, 31,<br>46, 63, 64,<br>66, 70, 71,<br>91, 100, 101,<br>106-108,<br>112, 114,<br>118, 121,<br>136, 153,<br>154, 156,<br>160, 161 | $\begin{array}{c} 2-9, 12-15, \\ 19-21, 23, \\ 25-27, 29, \\ 30, 32-45, \\ 47-62, 65, \\ 67, 69, 72- \\ 82, 84-90, \\ 92-99, \\ 102-105, \\ 109-111, \\ 115-117, \\ 119, 120, \\ 122-135, \\ 137-152, \\ 155, 157, \\ 159, \\ 162-172, \\ 174-180 \end{array}$ | 83, 173              |  |  |  |

## Table 3. Package Pin Inductance (Cont'd)

VLSI Technology Inc - 6 April 1988

| PDIP                      | Pin 1             | [nductance - F                    | DIP Packages           |                      |

|---------------------------|-------------------|-----------------------------------|------------------------|----------------------|

| PUIP<br>PKG.              | Low<br>(0 - 5 nH) | Medium Low<br>(5 - 10 nH)         | Medium<br>(10 - 15 nH) | High<br>(15 - 20 nH) |

| 20-pin<br>PDIP            | 2-9, 12-19        | 1,10,11,<br>20                    |                        |                      |

| 40-pin<br>PDIP<br>180x180 | 8-13,<br>28-33    | 2-7, 14-19,<br>22-27,<br>34-39    | 1,20,21,<br>40         |                      |

| 40-pin<br>PDIP<br>200x200 | 6-15,<br>26-35    | 2-5,<br>16-19,<br>22-25,<br>36-39 | 1,20,21,<br>40         |                      |

| 40-pin<br>PDIP<br>260x266 | 2-19,<br>22-39    | 1,20,21,<br>40                    |                        |                      |

Table 3. Package Pin Inductance (Cont'd)

|                | Pii                                     | n Inductance ·                 | - PLCC Packag          | es                   |

|----------------|-----------------------------------------|--------------------------------|------------------------|----------------------|

| PLCC<br>PKG.   | Low<br>(0 - 5 nH)                       | Medium Low<br>(5 - 10 nH)      | Medium<br>(10 - 15 nH) | High<br>(15 - 20 nH) |

| 28-pin<br>PLCC | All pins                                |                                |                        |                      |

| 44-pin<br>PLCC | 1-4, 9-15,<br>20-26,<br>31-37,<br>42-44 | 5-8, 16-19,<br>27-30,<br>38-41 |                        |                      |

| 68-pin<br>PLCC |                                         | All pins                       |                        |                      |

| 84-pin<br>PLCC |                                         | All pins                       |                        |                      |

|                 | Pin Indu                          | uctance - LLCC                                                      | C and LDCCC Pa                       | ackages              |

|-----------------|-----------------------------------|---------------------------------------------------------------------|--------------------------------------|----------------------|

| PKG.            | Low<br>(0 - 5 nH)                 | Medium Low<br>(5 - 10 nH)                                           | i iiouraii                           | High<br>(15 - 20 nH) |

| 44-pin<br>LDCCC | 1-5,8-16<br>19-27,30-38,<br>41-44 | 6, 7, 17, 18,<br>28, 29, 39,<br>40                                  |                                      |                      |

| 68-pin<br>LLCCC |                                   | All pins                                                            |                                      |                      |

| 84-pin<br>LLCCC | 1, 21, 22, 43,<br>44, 64, 65, 84  | 2-10, 13-20,<br>23-31, 34-<br>42, 45-52,<br>55-63, 66-<br>73, 76-83 | 11, 12, 32,<br>33, 53, 54,<br>74, 75 |                      |

#### Table 3. Package Pin Inductance (Cont'd)

In general, arrange the power pairs for maximum current distribution. However, in arrays larger than 16,000 with high utilization and operating at frequencies greater than 10 MHz, internal power requirements can be in the hundreds of milliamperes.

The power pads must be arranged so that those located on the sides adjacent to the internal buses, the two opposite sides from which internal VSS/VDD buses are tapped, can fully handle all the internal power needs of the array plus that of the output buffers located on those sides as well. The power pads should alternate (VSS, VDD) and should be evenly distributed. Refer to the section on **Preferred Power Pad Locations**, in this chapter.

# • Step Two: Determine the power pairs required for core, Irms core.

Table 4 gives the total current, Irms\_core, for various array internals at 100% utilization as a function of f-clock, the highest clocking frequency of the circuit. Irms\_core is in mA and f (f-clock) is in MHz. For lower utilization:

Irms core = Irms core(table) \* %utilization

This table also gives the maximum Irms\_core at which an array can be operated before the maximum current handling capability of internal buses is reached.

| DEVICE<br>SIZE | TOTAL Irms_core (IN MA)<br>AS A FUNCTION OF F(IN MHZ)<br>AND AT 100% UTILIZATION | MAXIMUM Irms_core (IN MA)<br>FOR INTERNAL BUS SAFETY |

|----------------|----------------------------------------------------------------------------------|------------------------------------------------------|

| 1590           | 1.0 mA ¥ f-clock (MHz)                                                           | ·                                                    |

| 2425           | 1.4 <b>*</b> f                                                                   |                                                      |

| 3718           | 2.2 <b>#</b> f                                                                   |                                                      |

| 6358           | 3.4 ¥f                                                                           |                                                      |

| 8365           | 4.45 <b>*</b> f                                                                  |                                                      |

| 10648          | 6.45 ¥ f                                                                         |                                                      |

| 12149          | 7.75 <b>#</b> f                                                                  | 435                                                  |

| 16038          | 8.8 <b>*</b> f                                                                   | 435                                                  |

| 20465          | 10.0 <b>x</b> f                                                                  | 500                                                  |

| 26930          | 13.1 <b>#</b> f                                                                  | 550                                                  |

| 39700          | 18.8 <b>#</b> f                                                                  | 600                                                  |

| 52800          | 23.9 <b>#</b> f                                                                  | 700                                                  |

| 66550          | 29.4 ¥ f                                                                         | 700                                                  |

#### Table 4. Current Requirements

At the upper limit of Irms\_core, the maximum current handling capability of an internal bus might be approached, and the proper operation of the circuit is no longer guaranteed.

Using the Irms\_core current derived from Table 4, the number of power pads needed for the VGT10 internal array is:

| Number of VSSI pads needed (VGT10) = | Irms_core (in mA)<br><br>40 (Ma/Power Pad) |

|--------------------------------------|--------------------------------------------|

| Number of VDDI pads needed (VGT10) = | Irms_core (in mA)<br><br>50 (Ma/Power Pad) |

For VGT10, 40 mA is the maximum current rating of the internal VSSI pad, and 50 mA is the maximum current rating of the internal VDDI pad.

Using the Irms\_core current derived from Table 4, the number of power pads needed for the VGT100 internal array is:

| Number of VSSI pads needed (VGT100) = | Irms_core (in mA)<br>100 (Ma/Power Pad)     |

|---------------------------------------|---------------------------------------------|

| Number of VDDI pads needed (VGT100) = | Irms_core (in mA)<br><br>110 (Ma/Power Pad) |

For VGT100, 100 mA is the maximum current rating of the internal VSSI pad, and 110 mA is the maximum current rating of the internal VDDI pad.

• Step Three: Determine the power pairs required for SSO noise, 1550'.

Based on the lead inductances to be used for power pins, calculate an average inductance for all of the VSS pins.

Now calculate the average SSO drive capability of your design. Use the rated drive capability, even if your application does not use the full current handling capability of the driver.

If you have split power supplies, use Table 5 to calculate the number of SSO's per power pair.

| Power<br>Drive<br>(mA)<br>L (nH) | 2 mA | 4 mA | 8 mA | 12 mA |

|----------------------------------|------|------|------|-------|

| 2 nH                             | 17   | 16   | 15   | 15    |

| 3 nH                             | 15   | 14   | 14   | 13    |

| 4 nH                             | 12   | 12   | 12   | 11    |

| 5 nH                             | 10   | 10   | 10   | 9     |

| 7 nH                             | 8    | 8    | 7    | 7     |

| 10 nH                            | 6    | 5    | 5    | 5     |

| 15 nH                            | 5    | 4    | 4    | 4     |

| 20 nH                            | 3    | 3    | 3    | 3     |

#### Table 5. Maximum SSO's For Split Supplies

NOTE: With separate power buses, the number of SSO's per power pair for a certain inductance does not diminish with increased drive requirements. If you have a single power supply, use Table 6 to calculate the number of SSO's per power pair.

| Power<br>Drive<br>(mA)<br>L (nH) | 2 mA | 4 mA | 8 mA | 12 mA |

|----------------------------------|------|------|------|-------|

| 2 nH                             | 11   | 9    | 7    | 5     |

| 3 nH                             | 9    | 7    | 4    | 4     |

| 4 nH                             | 8    | 6    | 3    | 3     |

| 5 nH                             | 7    | 4    | 3    | 3     |

| 7 nH                             | 5    | 3    | 2    | 2     |

| 10 nH                            | 3    | 2    | 1    | 1     |

| 15 nH                            | 2    | 2    | 1    | 1     |

| 20 nH                            | 1    | 1    | 1    | 1     |

Table 6. Maximum SSO's For Single Power Supply

The total number of internal power pairs required for SSO noise margins can be calculated as follows:

[Number of SSO's] / [SSO's per power pair]

• Step Four: Determine the number of external power pairs for DC loads, Iload.

Calculate your total DC load requirement, Iload, by summing the individual drive capability of each output buffer. Divide this number by the current rating per pad to obtain total power pairs required for the external power bus. The calculation is:

Iload (in Ma) Number of external power pairs needed (VGT10): -------85 (Ma/Power Pad)

Iload (in Ma) Number of external power pairs needed (VGT100): ------130 (Ma/Power Pad)

Where 85 mA is the maximum current rating of the VGT10 power pad and 130 mA is the maximum current rating of the VGT100 power pads.

# • Step Five: Determine the total number of power pairs.

Add the total number of power pairs calculated in Steps Two and Four, and compare this number to the number obtained in Step Three. The total number of required pairs is the larger of these numbers.

### • Step Six: Determine the distribution.

FOR SPLIT SUPPLIES -- If the sum of the values obtained in Steps Two and Four is greater than the value obtained in Step Three, then the total number of power pairs needed is the sum of Steps Two and Four. Otherwise, use the Step Three value for the total number needed.

Bias the distribution of the internal power pairs to have the majority on the vertical sides of the array, where pad 1 is in the lower left corner and the VLSI logo is in the upper left corner.

If the Step Three value is greater than the Steps Two and Four value, place all the required internal and external power pairs first; you can then add any extra power pairs in the ratio of 3 to 1, favoring external pairs.

FOR NON-SPLIT SUPPLIES -- There is no need to treat internal pairs differently, but be sure that at least the number of internal pairs calculated in Step Two is located on the vertical sides of the array.

### Example I - Separate Power Sources/Buses Structure

This example will demonstrate the steps used to calculate the number of required power pairs for an 8K VGT10 design. The design has a total of 80 outputs:

- 40 I/Os have 2 mA drive capability

- 20 I/Os have 4 mA drive capability

- 20 I/Os have 12 mA drive capability

- Three power pairs are available on pins 20, 40, 69, 80, 100, and 119

The clock frequency going into the array is 15 MHz, and the package used is a 120-pin CPGA. Utilization of the array is 55%. 24 I/O's switch simultaneously within a window of 100 ns and are utilized as follows:

- 10 with 12 mA drive capability

- 14 with 2 mA drive capability

The chip will have separate power supplies. These are the steps used to determine the number of power pairs required for this example:

#### • Step One: Determine the power pin locations.

Using Table 3, we find that power pins 20, 40, 69, 80, 100 and 119 in the CPGA package all have lead inductance of 5 - 10 nH. Since the pinout is fixed, all we can do is alternate the VDD and VSS pins around the array. Also, the power pins we did choose have the lowest range of inductances for the 120-pin CPGA package.

# • Step Two: Determine the power pairs required for core, Irms core.

For a VGT10 8K array, the internal core requirement from Table 4 is 4.45 (mA/MHz)\*f (MHz) at 100% utilization. The value from the table is corrected for 55% utilitzation, and this results in an Irms core of 36 mA.

Irms core = 4.45 (mA/Mhz) \* 15 (Mhz) \* .55 = 36 mA.

Since the number of pads needed for the internal array is the Irms\_core value in mA divided by either 40 mA for VSSI or 50 mA for VDDI, the total number of power pairs required for the core current can then be calculated as follows:

Number of VSSI pads needed (VGT10) = 36/40 = 0.9Number of VDDI pads needed (VGT10) = 36/50 = 0.72

This design example requires one internal power pair.

# • Step Three: Determine the power pairs required for SSO noise, 1550'.

Since all of the power pins are located in the Medium Low inductance range (5 to 10 nH), we can assume that the average VSS pin inductance is 7 nH.

Of the 24 IOs that switch simultaneously, 10 have 12 mA drive and 14 have 2 mA drive. Now calculate the average drive capability of the SSO's:

The closest drive value to 6.17 mA in Table 5 is 8 mA. Using 7 nH for the inductance of the VSS pins, we can consult Table 5 for the number of power pairs per SSO, which is seven. The total number of power pairs required for SSO noise can then be calculated by dividing the number of SSO's by the number of SSO's per power pair:

The result of this last calculation can be rounded to the nearest integer; In this case we would round 3.4 down to 3. Therefore the number of internal power pairs required for SSO noise is 3.

• Step Four: Determine the number of external power pairs for DC loads, Iload.

Worst case output buffer current load requirements are calculated by summing the individual drive capability of each output buffer:

1load = (40)\*(2mA) + (20)\*(4mA) + (20)\*(12ma) = 400 mA

The number of power pairs required can be calculated by dividing the load requirement, Iload, by the current rating per pad for VGT10, 85:

400Ma External Power Pairs Required (VGT10) = ------ = 5 power pairs 85 (mA/Power Pair)

# • Step Five: Determine the total number of power pairs.

Since the sum of the numbers found in Steps Two and Four (1 + 5 = 6) is greater than the number found in Step Three (3 pairs), the total number of power pairs needed is 6.

### • Step Six: Determine the distribution.

The total number of power pairs is determined by adding the internal and external requirements. Therefore, the total number of power pairs for this design is (1 + 5) = 6. At first this requirement of 6 power pairs may seem large, but careful analysis of the design gives a smaller figure, as seen below.

Analysis. Although current requirements for the array core required only one power pair, noise requirements dictate using three power pairs for the internal VSSI/VDDI bus. The reason for the requirement of three power pairs is the 7 nH lead inductance on the VSS pins. If there were, for example, a package with 4 nH lead inductance for the same power pins, the number of power pairs for internal switching would be reduced to two.

Adding the external power requirement for the output buffer, five pairs, to the internal requirement of one pair produces a total of six power pairs. This is because it is assumed that all 80 outputs are either in the High or the Low state at the same time. All that is needed, however, is to determine the maximum number of outputs that could be in one state at one time.

For this example, a maximum number of 30 outputs are active in any one cycle, and, of those 30, 16 are Low and 14 are High.

Then, assuming that the average drive is 8 mA, all that is needed is:

```

16 (Outputs in LOW state) * 8 (mA)

----- = 2 power pairs

85 (mA/Power Pair)

```

This lowers the total power pair requirement to a reasonable value of three, one internal and two external.

## Example II - Non-Separate Power Sources/Buses Structure

This is the same example, only with non-separate power supplies:

#### • Step One: Determine the power pin locations.

The analysis is the same as for split supplies, but it is included here for convenience.

Using Table 3, we find that the power pins have lead inductance of 5 - 10 nH. Since the pinout is fixed, all we can do is alternate the VDD and VSS pins around the array. Also, the power pins we did choose have the lowest range of inductances for the 120-pin CPGA package.

# • Step Two: Determine the power pairs required for core, Irms core.

The internal power requirement has not changed, so we can use the value calculated in Step Two of the split supply example. The number of power pairs required for handling Irms core is one.

## • Step Three: Determine the power pairs required for SSO noise, 1550'.

Since all of the power pins are located in the Medium Low inductance range (5 to 10nH), we can assume that the average VSS pin inductance is 7 nH.

Now determine the average drive capability of the SSO's. This can be calculated as follows:

$$(10)*(12mA) + (14)*(2mA)$$

----- = 6.17 mA

10 + 14

The closest value to 6.17 mA in Table 6 is 8 mA. Using 7 nH for the inductance of the VSS pins, we can consult Table 6 for the number of power pairs per SSO, which is two. The number of power pairs required for SSO noise can then be calculated by dividing the number of SSO's by the number of SSO's per power pair:

24 (SSO) ----- = 12 2 (Power Pairs/SSO)

This step is where the split versus non-split power pair requirements differ greatly. Calculating the number of SSO's per power pair for split supplies requires using Table 6. If you compare the numbers in Table 5 with the numbers in Table 6, you'll notice a significant decrease in the ability of a single supply to handle SSO's.

# • Step Four: Determine the number of external power pairs for DC loads: Iload.

Assuming that only 16 of the outputs are in the Low state during a cycle, and that the average drive is 8 mA, the number of external power pairs can be calculated as follows:

```

16 (Outputs in LOW state) * 8 (mA)

----- = 2 power pairs

85 (mA/Power Pair)

```

• Step Five: Determine the total number of power pairs.

Since the number found in Step Three (12 pairs) is greater than the sum of the numbers found in Steps Two and Four (1 + 2 = 3), the total number of power pairs needed is 12.

## • Step Six: Determine the distribution.

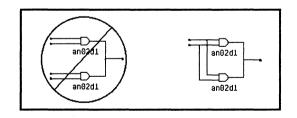

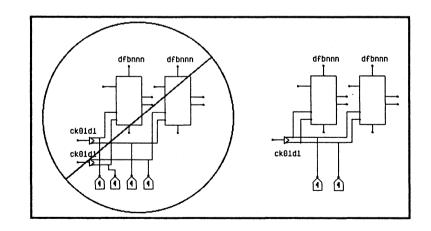

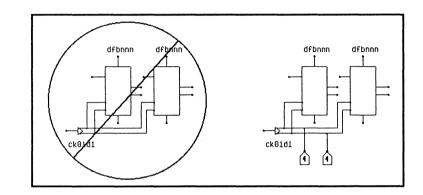

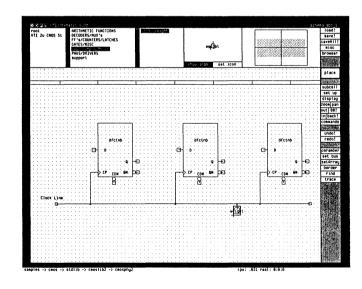

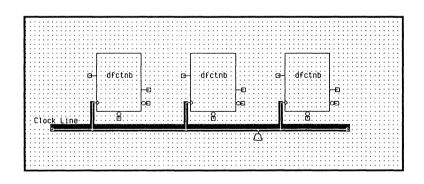

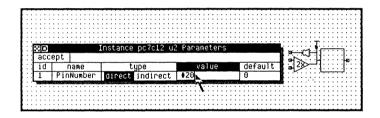

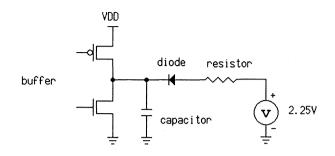

The total number of power pairs is determined by adding the internal and external requirements. Therefore the total number of power pairs for this design is (1 + 2) = 3. However, the requirement for SSO's is 12 pairs, so you need a total of 12 pairs. Start with one internal pair and two external pairs. Then split the remaining nine pairs into six external pairs and three internal pairs.