# VT6508

# 8 RMII PORTS OF 10/100BASE-T/TX ETHERNET SWITCH CONTROLLER

REVISION D DATASHEET (Preliminary)

**ISSUE 1: Nov 23, 1999**

VIA Technologies, Inc.

#### PRELIMINARY RELEASE

Please contact VIA Technologies for the latest documentation.

# **Copyright Notice:**

Copyright © 1995, VIA Technologies Incorporated. Printed in Taiwan. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies Incorporated.

The VT86C100P may only be used to identify products of VIA Technologies. All trademarks are the properties of their respective owners.

#### **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

# **Offices:**

1045 Mission Court 8<sup>th</sup> Floor, No. 533

Fremont, CA 94539 Chung-Cheng Rd., Hsin-Tien

USA Taipei, Taiwan ROC

Tel: (510) 683-3300 Tel: (886-2) 2218-5452 Fax: (510) 683-3301 Fax: (886-2) 2218-5453

# **Online Services:**

BBS: 886-2-2186408 FTP: <u>FTP.VIA.COM.TW</u>

HTTP: WWW.VIA.COM.TW -or- WWW.VIATECH.COM

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                                   | 3          |

|---------------------------------------------------------------------|------------|

| FIGURES AND TABLES                                                  |            |

| REVERSION HISTORY                                                   | 5          |

| Features                                                            |            |

| Block Diagram                                                       | 9          |

| FIGURE 1: FUNCTION BLOCK DIAGRAM OF VT6508. (NOTE THAT SOME INTERFA | <b>\CE</b> |

| SIGNALS ARE ONLY AVAILABLE IN VT6509 OF 208-PIN PQFP PACKAGE.)      |            |

| Pinout Diagram                                                      | 10         |

| FIGURE 2: PINOUT DIAGRAM OF VT6508                                  | 10         |

| PIN DESCRIPTIONS                                                    | 11         |

| DEFINITION OF VT6508B STRAPPING PINS                                |            |

| Pin                                                                 |            |

| SRAM TYPE:                                                          | 12         |

| SECTION I FUNCTIONAL DESCRIPTIONS                                   | 15         |

| 1 General Description                                               | 15         |

| 2 THE VIA ETHER SWITCH ARCHITECTURE.                                |            |

| 2.1 Switch initialization procedures                                |            |

| 2.2 Packet Switching Flow                                           |            |

| 2.3 PACKET BUFFERS AND FORWARDING TABLE                             | 16         |

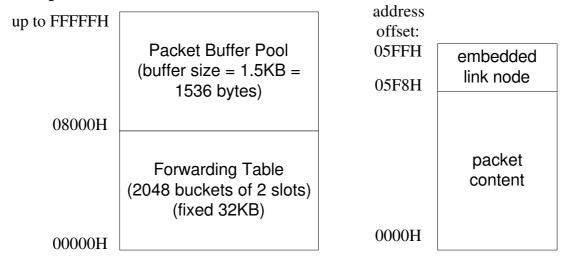

| FIGURE 3. SRAM MEMORY LAYOUT                                        | 17         |

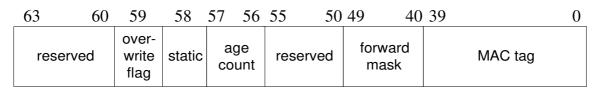

| FIGURE 4. DATA STRUCTURE OF FORWARDING TABLE SLOT                   | 17         |

| TIGORE II DITTI STRUCTURE OF TORWINDING TIBLE SECTION               |            |

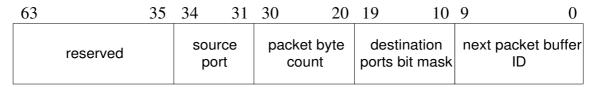

| FIGURE 5. DATA STRUCTURE OF EMBEDDED LINK NODE                      | 17         |

| 2.3 RMII INTERFACE                                                  | 19         |

| 2.3 MANAGEMENT INTERFACE AND AUTO NEGOTIATION                       |            |

| 2.4 FLOW CONTROL                                                    | 21         |

| FIGURE 6. XON/XOFF WINDOW CONCEPT                                   | 23         |

| 2.5 Broadcast Storm Filtering                                       | 27         |

| 2.6 SERIAL EEPROM INTERFACE AND CONFIGURATION COMMANDS              |            |

| 2.7 Trunking                                                        |            |

| 3 THE VT6508 SRAM ADDRESS MAPPING TABLE                             | 30         |

| SECTION II REGISTER MAP                                             | 31         |

| 1. Registers Table                                                  | 31         |

| SECTION III ELECTRICAL SPECIFICATIONS                               | 45         |

| ABSOLUTE MAXIMUM RATINGS                                            | 45         |

| DC CHARACTERISTICS                                                  |            |

| AC CHARACTERISTICS.                                                 | 46         |

| DACKAGE MEGHANICAL CRECIEICATIONS                                   | 10         |

# FIGURES AND TABLES

| Figure 1: Function Block Diagram of VT6508. (Note that some interface sign | als are only |

|----------------------------------------------------------------------------|--------------|

| available in VT6509 of 208-pin PQFP package.)                              | 9            |

| Figure 2: Pinout Diagram of VT6508.                                        |              |

| Figure 3. SRAM memory layout.                                              | 17           |

| Figure 4. Data structure of forwarding table slot.                         | 17           |

| Figure 5. Data structure of embedded link node.                            |              |

| Figure 6. XON/XOFF Window Concept                                          | 23           |

# **REVERSION HISTORY**

| Reversion | Date       | Reason for change     | Ву          |

|-----------|------------|-----------------------|-------------|

| V0.01     | 11/23/1999 | First release version | Murphy Chen |

#### **FEATURES**

- Single chip 8 ports 10/100Mbps Ethernet switch controller

- Highly integrated single chip shared memory switch engine

- Supports 8 RMII (Reduced Media Independent Interface) ports

- Non-blocking layer 2 switch, 148,810 packets/sec on each 100Mbps Ethernet port

- Media Access Control (MAC)

- Dual 64-byte FIFO's per port for receiving and transmitting

- Auto-sensing 10/100Mbps media speed, full/half -duplex mode, and flow-control capability

- Two switching mechanisms

- Supports 'store and forward' switching with filtering CRC-bad packets

- Supports 'cut through' switching subject to long packets of length over 64 bytes

- Packet buffering

- Glueless 32-bit interface to SSRAM as a packet buffer pool

- 64 packet buffers for 32Kx32 SSRAM, 149 packet buffers for 64Kx32 SSRAM

- 1536 bytes for each packet buffer

- Storing control data (forwarding table and packet link entries) in external SSRAM

- Buffer status is stored in the internal free-buffer bit map registers

- Shared forwarding table of 2K entries (or 4K slots) to support multiple (up to 4K) Mac addresses per port

- Efficient address recognition, self learning, and auto-aging mechanism

- Two-slot hashing algorithm to prevent hash collision

- Two optional hashing algorithms, CRC-map and direct-map

- Advanced congestion control mechanism

- IEEE 802.3X compliant flow control for full duplex ports

- Backpressure for half duplex ports

- Drop control for full duplex ports without flow control capability

- Incorporating with the output private buffering scheme to prevent HOL (head of line) blocking

- Supports port mirroring (Sniffer feature)

- By-pass VLAN packets

- Support port-based trunking

- Support two individual trunk groups, each of 2 member ports

- Load balance according to DMAC address and source port number

- Support chip initialization through EEPROM or by strapping only

- Supports I<sup>2</sup>C EEPROM interface for customized configuration

- Supports LED serial-out in the strapping-only initialization mode

- 50MHz internal reference clock rate

- 83~100MHz SSRAM clock rate, typically 83MHz

- Single +3.3V supply, 0.3µm TSMC CMOS technology

- 128-pin PQFP package

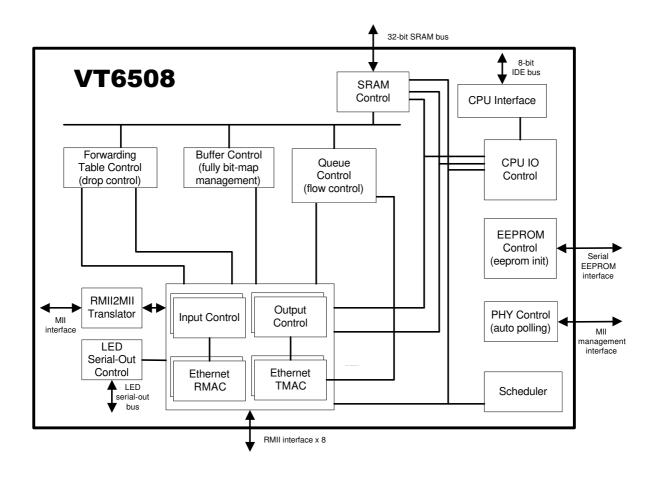

#### **BLOCK DIAGRAM**

Figure 1: Function Block Diagram of VT6508. (Note that some interface signals are only available in VT6509 of 208-pin PQFP package.)

99/12/09

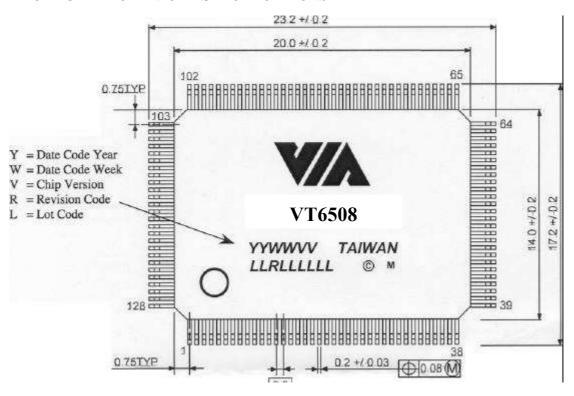

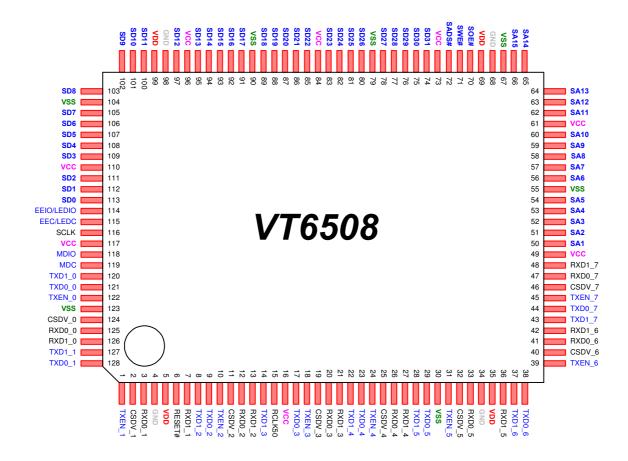

#### **PINOUT DIAGRAM**

Figure 2: Pinout Diagram of VT6508.

99/12/09

# PIN DESCRIPTIONS

| No.        | Name                    | Type | Description                                                                                             |  |  |

|------------|-------------------------|------|---------------------------------------------------------------------------------------------------------|--|--|

|            | RMII interface          |      |                                                                                                         |  |  |

| See Fig. 2 | CSDV[7:0]               | I    | Carries sense and data valid from port 7 to port 0:                                                     |  |  |

| See Fig. 2 | RXD0[7:0]               | I    | Receive data zero from port 7 to port 0:                                                                |  |  |

| See Fig. 2 | RXD1[7:0]               | I    | Receive data one from port 7 to port 0:                                                                 |  |  |

| See Fig. 2 | TXEN[7:0]               | O    | Transmit enable from port 7 to port 0:                                                                  |  |  |

| See Fig. 2 | TXD0[7:0]               | О    | Transmit data zero from port 7 to port 0:                                                               |  |  |

| See Fig. 2 | TXD1[7:0]               | 0    | Transmit data one from port 7 to port 0:                                                                |  |  |

|            | T                       | 1    | SRAM Interface                                                                                          |  |  |

| See Fig. 2 | SA[15:1]                | О    | SRAM Address Bus:                                                                                       |  |  |

|            |                         |      | 15-bit SDRAM data bus. These signals connect directly to the address                                    |  |  |

|            |                         |      | input of the SDRAM devices.                                                                             |  |  |

| See Fig. 2 | SOE                     | О    | Output Enable                                                                                           |  |  |

| See Fig. 2 | SWE                     | О    | SRAM Write Enable                                                                                       |  |  |

| See Fig. 2 | SADS                    | О    | Synchronous Processor Address Status                                                                    |  |  |

| See Fig. 2 | SD[31:0]                | I/O  | SRAM Data:                                                                                              |  |  |

|            |                         |      | 32-bit SRAM data bus. These signals connect directly to the data input/output pins of the SRAM devices. |  |  |

|            | Miscellaneous Interface |      |                                                                                                         |  |  |

| See Fig. 2 | EEC/LEDC                | О    | Serial EEPROM Interface Clock (if strapping SD25 is default high)                                       |  |  |

|            |                         |      | The on-board EEPROM device address must be 1010 001 XXXXXXXX.                                           |  |  |

|            |                         |      | Serial LED Serial-Out Clock (if strapping SD25 is low)                                                  |  |  |

|            |                         |      | , 11 0                                                                                                  |  |  |

| See Fig. 2 |                         | 7/0  | The LEDC is 1MHz and has a burst per 50ms.                                                              |  |  |

| See Fig. 2 | EEIO/LEDIO              | I/O  | Serial EEPROM Interface Data (if strapping SD25 is default high)                                        |  |  |

| a: :       |                         |      | Serial LED Serial-Out Data Output (if strapping SD25 is low)                                            |  |  |

| See Fig. 2 | MDC                     | О    | Management Interface (MI) Clock Output                                                                  |  |  |

| See Fig. 2 | MDIO                    | I/O  | Management Interface (MI) Data I/O                                                                      |  |  |

| See Fig. 2 | RCLK50                  | I    | 50MHz Main Reference Clock                                                                              |  |  |

| See Fig. 2 | SCLK                    | I    | SRAM Reference Clock                                                                                    |  |  |

|            |                         |      | The suggested clock rate is 83MHz or more high for non-blocking requirement.                            |  |  |

| See Fig. 2 | RESET                   | I    | SYSTEM RESET                                                                                            |  |  |

| Power Sup  | ply & Ground |   |                                                 |

|------------|--------------|---|-------------------------------------------------|

| See Fig. 2 | VDD          | P | Positive 3.3V supply to the core digital logic. |

| See Fig. 2 | VCC          | P | Positive 3.3V supply to all I/O pads.           |

| See Fig. 2 | GND | G | Ground supply to the core digital logic. |

|------------|-----|---|------------------------------------------|

| See Fig. 2 | VSS | G | Ground supply to all I/O pads.           |

### **DEFINITION OF VT6508B STRAPPING PINS**

SD[31:0]: \*Note that the default strapping bit value is 1

| SD[31:0]: | *Note that the default strapping bit value is $1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SD[0]     | Broadcast or Drop BPDU Packets:  BCAST_BPDU == 1' b1 => broadcast BPDU packet if CPU_FWD_CFG[1] == 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SD[1]     | without regard to the value of BCAST_BPDU.  LED Display Combination of Link Activity Status with RX/TX Event:  LED_COMB [0] == 1' b1 => combined (default)                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | LED_COMB [0] == 1' b0 => not combined  Note that the LED bit sequence [10:1] is used originally to display link activity status. By setting combination with RX/TX event, it will indicate both the link activity status and RX/TX events so that required LED number can be reduced.                                                                                                                                                                                                                                                                                    |

| SD[2]     | Enable Drop Control for Private Buffer Reservation:  DROP_CONTROL_EN [0] == 1' b1 => enabled (default)  DROP_CONTROL_EN [1] == 1' b0 => disabled  Note that drop control has a lower priority than flow control and backpressure.  If it is disabled, all TMACs will not make the drop window signals to Forwarding Control. If it is enabled and the flow control/backpressure mechanism is not enabled, all TMACs will make the drop window signals to Forwarding Control.  If it is enabled and the flow control mechanism is also enabled, but the full-duplex party |

| SD[3]     | has no flow control capability, TMAC will make the drop window signal to Forwarding Control.  SRAM TYPE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | SRAM_TYPE == 1' b1 => 64Kx32 (default) SRAM_TYPE == 1' b0 => 32Kx32  size=128KB: FREEMCNT=64, XON_THRED=43, PRIVATE_BUF_SIZE=1                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SD[5:4]   | CHIP_INIT[1:0] == 2' b11 => Chip Initialization via strapping only (default) CHIP_INIT[1:0] == 2' b10 => Chip Initialization via EEPROM CHIP_INIT[1:0] == 2' b01 => Chip Initialization via CPU CHIP_INIT[1:0] == 2' b00 => Chip Initialization via EEPROM in speedup mode In none speedup mode, EEC = 78.125K Hz, LED period = 50ms. In speedup mode for testing, EEC = 2.778MHz, LED period = 1ms without one-second flash.                                                                                                                                            |

| SD[7:6]   | Number of Tries of Excessive Collisions Before Dropping:                                        |

|-----------|-------------------------------------------------------------------------------------------------|

|           | RETRY_EXCE_COLL [1:0] == 2' b11 => 3 tries (default)                                            |

|           | RETRY_EXCE_COLL [1:0] == 2' b10 => 2 tries                                                      |

|           | RETRY_EXCE_COLL [1:0] == 2' b01 => retry forever                                                |

| 1         | RETRY EXCE COLL [1:0] == 2' b00 => 1 try                                                        |

|           |                                                                                                 |

|           | Internally, retry_no = RETRY_EXCE_COLL, or infinite if it is zero.                              |

|           | By default, after 3 tries (i.e. 3 turns of (excessive) 16 collisions), the outgoing packet will |

|           | be dropped.                                                                                     |

| SD[15:8]  | (reserved with default value pull-high )                                                        |

| 30[13.0]  | (reserved with default value pull-night)                                                        |

| SD[17 16] | Trunking Mode:                                                                                  |

| 30[17,10] |                                                                                                 |

|           | SD16 == 1, port (0,1) no trunking (default)                                                     |

|           | 0, port (0,1) in trunking mode,                                                                 |

|           | SD17 == 1, port (6,7) no trunking (default)                                                     |

|           | 0, port (6,7) in trunking mode.                                                                 |

|           | To simplify layout, trunk group (6,7) can connect with neighboring (right-side)                 |

|           | VT6508's trunk group (0,1) in on-board manner.                                                  |

|           | Note that on-board trunk ports do not need auto-polling and they must be full-duplex &          |

|           | 100Mbps ports & forced flow control enable mode.                                                |

| SD[18]    | Enable Backpressure:                                                                            |

|           | BACKPRESSURE_EN [0] == 1' b1 => enabled (default)                                               |

|           | BACKPRESSURE_EN [1] == 1' b0 => disabled                                                        |

|           |                                                                                                 |

|           | Note that if it is disabled, all TMAC of half-duplex ports will ignore the flow control         |

|           | XON/XOFF signals from Queue Control.                                                            |

| SD[20:19] | Enable RMII Port Flow Control:                                                                  |

| 30[20.19] |                                                                                                 |

|           | RMII_PORT_FC_EN[1:0] == 2' b11 => for RMII ports, set self flow control ability                 |

|           | register bit and detect party's flow control ability (default)                                  |

|           | RMII_PORT_FC_EN[1:0] == 2' b10 => for RMII ports, disable self flow control ability             |

|           | register bit and assume (ignore auto-polling) party has no flow control capability              |

|           | RMII_PORT_FC_EN[1:0] == 2' b01 => for RMII ports, enable self flow control ability              |

|           | register bit and assume (ignore auto-polling) party has flow control capability                 |

|           | RMII_PORT_FC_EN[1:0] == 2' b00 => same as 2' b11.                                               |

|           | While enabled (RMII_PORT_FC_EN[1:0] == 2' b11 or 2' b00), set self each PHY                     |

|           | device's flow control ability register bit PHY ANAR 4.10 as 1, and auto polling                 |

|           | PHY_ANLPAR_5.10 to check whether the party has the flow control capability.                     |

|           | While forced disabling (RMII_PORT_FC_EN[1:0] == 2' b10), set self PHY devices'                  |

|           | flow control ability register bit PHY_ANAR_4.10 as 0 (no such capability), and does not         |

|           | need auto polling PHY ANLPAR 5.10.                                                              |

|           | While forced disabling (RMII_PORT_FC_EN[1:0] == 2' b01), set self PHY devices'                  |

|           | flow control ability register bit PHY_ANAR_4.10 as 1 (with flow control capability), and        |

|           |                                                                                                 |

|           | does not need auto polling PHY_ANLPAR_5.10.                                                     |

|           | For forced disabling, turn off flow control enable bits of all RMII ports.                      |

| 0         | For (forced) enabling, turn on flow control enable bits of all RMII ports.                      |

| SD[23:21] | LED Serial-Out Mask for Groups 0,1,2,3 [3:0]:                                                   |

|           | LED_MASK[0] == 1' b1 => enable group 0 data out (default)                                       |

|           | LED_MASK[1] == 1' b1 => enable group 1 data out (default)                                       |

|           | LED_MASK[2] == 1' b1 => enable group 2 data out (default)                                       |

|           |                                                                                                 |

|           | LED Groups 3,4,5 serial out is always enabled. The time period of LED sequence is               |

|           | 50ms.                                                                                           |

|           |                                                                                                 |

| SD[24]  | Hash Algorithm Selection:                                                                    |

|---------|----------------------------------------------------------------------------------------------|

| 55[= .] | HASH ALG SEL == 1 => CRC-map with scramble (default)                                         |

|         | HASH ALG SEL == 0 => Direct-map without scramble                                             |

|         | TINOTI_NEG_OLE == 0 => Birott map without solution                                           |

|         | HASH ALG SEL == 1 will make the register HASH ALG[1:0]=0 that is helpful to the              |

|         | X-Stream test.                                                                               |

|         | HASH ALG SEL == 0 will make the register HASH ALG[1:0]=3 that can get a good                 |

|         | result of 4094 MAC addresses in Address Handling test.                                       |

| SD[25]  | No Swap EEPROM and LED output pins:                                                          |

| 05[20]  | NO SWAP EEPROM LED == 1 => The pins 192/193 are used as                                      |

|         | EEIO/EEC. (default)                                                                          |

|         | NO_SWAP_EEPROM_LED == 0 => The pins 192/193 are used as                                      |

|         | LEDIO/LEDC.                                                                                  |

|         | In 128-pin package, we can bond this pin to VSS to select LED output from the original       |

|         | EEPROM output pins.                                                                          |

| SD[26]  | Enable Aging:                                                                                |

|         | EN_AGING == 1 => enable aging function (default)                                             |

|         | EN_AGING == 0 => disable aging function                                                      |

|         | _                                                                                            |

| SD[27]  | Disable Cut Through Enable:                                                                  |

|         | DIS CUT THRU == 1 => disable cut-through feature                                             |

|         | (default, i.e. store & forward)                                                              |

|         | DIS_CUT_THRU == 0 => enable cut-through feature                                              |

| SD[28]  | Disable Aggressive Backoff Algorithm:                                                        |

|         | DIS_AGGRES_BACKOFF == 1'b1 => disabled (default)                                             |

|         | DIS_AGGRES_BACKOFF == 1' b0 => enabled                                                       |

|         | quadratics.                                                                                  |

|         | Note that if this feature is enabled, the backoff algorithm for all Ethernet ports is in MBA |

|         | mode. By default, the backoff algorithm bits MBA=0 and OFSET=1.                              |

| SD[29]  | Backpreasure Collision Point Configuration:                                                  |

|         | COLL_POINT_CFG == 1 => 32th byte (default)                                                   |

|         | COLL_POINT_CFG == 0 => 2nd byte                                                              |

| SD[30]  | Disable TEST mode:                                                                           |

|         | DIS_TEST_MODE == 1 => disabled (default)                                                     |

|         | DIS_TEST_MODE == 1 => enabled                                                                |

| SD[31]  | Disable Latchup Mode:                                                                        |

|         | DIS_LATCH_UP_MODE == 1' b1 => disable Latchup mode (default)                                 |

|         | DIS_LATCH_UP_MODE == 1' b0 => enable Latchup mode, all output only IO PADs                   |

|         | are in tri-state after reset.                                                                |

#### SECTION I FUNCTIONAL DESCRIPTIONS

#### 1 GENERAL DESCRIPTION

The VT6508 is a low-cost switch engine chip implementation of an 8 ports 10/100Mbps Ethernet switch system for IEEE 802.3 and IEEE 802.3u networks. Each port can be either auto-sensing or manually selected via EEPROM configuration to run at 10Mbps or 100Mbps speed rate, full or half duplex mode.

The VT6508 supports RMII (reduce MII) port interface. There are eight independent MACs within the VT6508 chip. The MAC controller controls the receiving, transmitting, and deferring of each individual port, and the MAC controller also provides framing, FCS checking, error handling, status indication and flow control function. It has wire-speed performance with forwarding rate of 148,810 packets/sec on each 100Mbps Ethernet port. The VT6508 can be configured via EEPROM or strapping only.

#### 2 THE VIA ETHER SWITCH ARCHITECTURE

The VT6508 switch engine uses the shared memory architecture. In order to improve the packet latency, VT6508 provides two methods for packet switching, cut-through and store-and-forwarding.

#### 2.1 Switch initialization procedures

- Step\_1. Read strapping signal.

- Step\_2 Write Reg 0619H with WR\_DATA = 8'h01 to trigger SRAM\_Ctrl module autotest.

- Step\_3. If initialization by Strapping, then go to Step\_4.

If initialization by EEPROM, eeprom\_ctrl module will download register data from EEPROM (by internal register bus IOW, CS\_\*, IO\_ADDR, and IO\_WR\_DATA).

If EEPROM data download error, then go to step6.

- Step\_4 After SRAM auto-test completed, write Reg 0304H with WR\_DATA = 8'h01 to trigger Forward Ctrl module auto aging.

- Step\_5 Write Reg 0404H with WR\_DATA = 8'h08 to trigger PHY\_Ctrl module phy\_auto-polling.

- Step\_6 Write Reg 000aH with WR\_DATA = 8'h01 to trigger LED\_Ctrl module to display LED.

- Step\_7 Chip initialization done.

#### 2.2 Packet Switching Flow

- 1. After initialization, the input control of each enabled port will pre-allocate one packet buffer from the free buffer pool.

- 2. When the Receive MAC (RMAC) receives a packet data from the PHY device via the RMII network interface, it packs the data into 16-bit words then passes it to input control. If RMAC detects any error, it also notifies input control to stop forwarding process.

- 3. Input control extracts the destination MAC address from incoming data, passes it to forwarding table control for forwarding decision. In the mean while, it packs 16-bit words into 64-bit quad-words, and saves it to an input FIFO before storing the packet data to packet buffers in SRAM.

- 4. If the switch is configured to "store and forward" mode, input control queues the packet to the output queue of the destination port after input control is informed by RMAC that this is a good packet and it stores all packet data to SRAM. If the switch is configured to "cut-through" mode, the input control queues the packet to the output queue of the destination port after the first 64-byte packet data is stored in SRAM to prevent output FIFO underrun.

- 5. After the whole packet is received and FCS is correct, input control pass the source MAC address of the packet to forwarding table control for address learning.

- 6. Output control of the outbound port dequeues the packet from itself output queue, and fetches packet data from SRAM and saves it into output FIFO. Then it notifies the Transmit MAC (TMAC) to transmit the read-to-outgoing packet.

- 7. TMAC grabs 16-bit word at a time from output control, adds preamble and SFD to the beginning of the packet, then send them out. Proper deferring is done for collision to conform to 802.3 standard.

- 8. After the packet is successfully transmitted, TMAC notifies output control of the successful transmission. Output control then returns the packet to the free buffer pool.

#### 2.3 PACKET BUFFERS AND FORWARDING TABLE

VT6508 provides a 32-bit SRAM interface for packet buffering and maintaining address table and per-port output link lists. Each packet buffer is a 1536-byte contiguous memory block in SRAM, and it also contains to a 8-byte link node data structure in every buffer's tail. A link node corresponds uniquely to a packet buffer that could belong an output queue, the free buffer pool, incoming packet buffers of an input control, or outgoing packet buffers of an output control.

Initially, each input port control will request one packet buffer from its private buffer pool. Each time when a packet buffer is consumed by an incoming packet, the input port control will request another packet buffer to prepare for next packet.

There are two data structures in SRAM memory layout, shown in Figure 3. One is the forwarding table that locates at the lowest 32K-byte address space and contains 2048 entries (buckets), each of 2 slots. The structure of an 64-bit forwarding table slot is shown in Figure 4, composed of:

(1) bits 39..0: MAC Tag

The MAC Tag is used to record the partial content of MAC address for lookup identification. The mapping of Tag and MAC address is as follows:

Tag[39:32] = MAC[15:8]

Tag[31:24] = MAC[23:16]

Figure 3. SRAM memory layout.

Figure 4. Data structure of forwarding table slot.

Figure 5. Data structure of embedded link node.

Tag[23:16] = MAC[31:24]

Tag[15:8] = MAC[39:32]

Tag[7:0] = MAC[47:40]

(2) bits 49..40: Forwarding Port Mask

- (3) This is the bit mask of the destination ports corresponding to the forwarding table slot. The bits 49 and 48, corresponding to CPU port and MII port respectively, should be zero in VT6508.

- (4) bits 57..56: Age Count

- (5) If this field is equal to zero, it means this slot is an empty one; otherwise, it is valid. When the auto-aging is enabled (by default), every valid slot' age count will be decreased by one per 100 seconds.

- (6) bits 58: Static Flag

- (7) This flag is used to program a static MAC slot, that will not be overwritten by dynamic learning mechanism, with specified forwarding port mask for special purpose.

- (8) bits 59: Over-Write Flag

During learning, if both slots are used, the 3rd address will replace one of the slots according to current value of the concatenated over-write order pointer and their static bits regardless of ages of the two slots.

Let the concatenated over-write pointer ow[1:0] = (over-write pointer of slot 1, over-write pointer of slot 0).

Let  $static[1:0] = \{static bit of slot 1, static bit of slot 0\}.$

The possible mapping of ow[1:0] and static[1:0] are as follows:

|         | static[1:0] |       |       |       |

|---------|-------------|-------|-------|-------|

| ow[1:0] | (0,0)       | (0,1) | (1,1) | (1,0) |

| (0,0)   | 0           | 1     | X     | 0     |

| (0,1)   | 1           | 1     | X     | 0     |

| (1,1)   | 0           | 1     | X     | 0     |

| (1,0)   | 1           | 1     | X     | 0     |

The internal operation rules for the over-write pointer are as follows:

- (1) When a slot is over-written, its over-write pointer is toggled.

- (2) When one of the slots is a static entry, the static entry must always be placed in slot 0, and slot 1 is always the entry over-written. Over-write pointer has no effect what so ever here.

- (3) When both slots are static, no entry can be written to either slot by the learning process.

- (4) When update an entry, value of the over-write pointer must not be changed unless indicated otherwise, i.e. over-writing an existing slot.

Another data structures in SRAM memory layout is the packet buffer pool, located at the upper address space. Every packet buffer is 1.5K bytes with a corresponding embedded link node in the tailing 8 bytes. The embedded link nodes are used to construct output queues, one queue for each output port. Its structure is shown in Figure 5, composed of:

- (1) bits 9..0: Next Packet Buffer ID

- (2) bits 19..10: Destination Ports Bit Mask

(3) bits 30..20: Packet Byte Count

(4) bits 34..31: Source Port ID

The number of packet buffers is determined by the configured SRAM size, listed as follows:

| SRAM Size                   | 128KB      | 256KB       | 512KB       | 1MB         |

|-----------------------------|------------|-------------|-------------|-------------|

| maximum # of packet buffers | 64 buffers | 149 buffers | 320 buffers | 661 buffers |

#### 2.3 RMII INTERFACE

The VT6508 can directly connect to an 8 port RMII PHY device through the reduced MII (RMII) interface to construct a small-sized system board. The signals of RMII interface are described as follows:

| Name     | Type | Description              |

|----------|------|--------------------------|

| CRSDV    | I    | Carrier sense and Data   |

|          |      | valid                    |

| RXD[0-1] | I    | Receive data bit 0 to 1, |

|          |      | data rate with 50MHz     |

| TXEN     | O    | Transmit Enable          |

| TXD[0-1] | O    | Transmit Data bit 0 to   |

|          |      | 1                        |

#### 2.3 MANAGEMENT INTERFACE AND AUTO NEGOTIATION

The VT6508 communicates with the external 10/100M PHY and access the PHY register through MDC, MDIO. The signals of management interface are described as follows:

| Name | Type | Description                      |

|------|------|----------------------------------|

| MDC  | О    | management interface             |

|      |      | clock                            |

| MDIO | Ю    | management interface data signal |

|      |      | autu bigiitii                    |

#### **Auto-polling state machine:**

step1. Auto-polling idle

- if auto-polling\_command="on" then go to step2

- step2. Check the chip internal register, phyint\_setup\_reg, to setup the pause capability (Reg4.10) and phy auto-negotiation enable (Reg0.12)

- if (this port do not need phy setup) and (phyint\_setup\_reg == done), then go to step 10(done)

- else if (this port do not need phy setup) and (phyint\_setup\_reg != done), then config ioctl, set phyint\_setup\_reg == done, go to step10(done)

- else if (phyint\_setup\_reg != done),

then go to step3(phy fc setup)

- else if (this port do not need auto-poll, then go to step 10(done)

- else go to step 5(read phy link status)

#### step3. Phy flow\_control ability setup

- if the phy\_pause\_ability(reg4.10) != port\_phy\_fc\_set, then write reg4.10 = port\_phy\_fc\_set and go to step4 (phy auto-negotiation ability setup)

- else go to step4 (phy auto-negotiation ability setup)

#### step4. PHY auto-negotiation ability setup

- if (Reg0.12)="1"(on), then modify chip internal register for phyint\_setup\_reg = done; go to step5

- else if (Reg0.12)="0"(off) or phy\_pause\_ability have been modified ( in step3 ), then write PHY auto-negotiation\_enable bit (Reg0.12) ="1" (on), restart\_auto-negotiation bit (Reg0.9) = "1" and modify chip internal register for phyint\_setup\_reg = done; go to step5

#### step5. Read PHY link status bit (Reg1.2) 1st time

- if link is down (Reg1.2)="0", then go to step6

- else if link is up (Reg1.2)="1" and chip\_internal\_reg for link status is "down", then go to step7

- else if link is up (Reg1.2)="1" and chip\_internal\_reg for link status is "up", then go to step10.

#### step6. Read PHY link status bit (Reg1.2) 2st time

- if link is up (Reg1.2)="1", then go to step7

- else if link is down (Reg1.2)="0", then go to step10

\*if chip\_internal\_reg for link status is "down"=> generate link\_change interrupt and disable io\_port

#### step7. Read PHY Auto-negotiation Complete bit (Reg1.5)

- if auto-negotiation is completed (Reg1.5)="1", then go to step8.

- else if auto-negotiation is not completed (Reg1.5)="0", then go to step10.

\*if chip\_internal\_reg for link status is "down"=> generate link\_change interrupt and disable io\_port

#### Step8. Read PHY ANAR(Reg4) and ANLPAR(Reg5)

- if speed\_arbit\_bit ="0"(speed from PHY proprietary reg), then go to step9

- if speed\_arbit\_bit ="1"(speed from ANLPAR), then go to step10

- \* generate link\_change interrupt and enable io\_port

#### Step9. Read PHY proprietary Reg for RMII speed, then go to step10

\* generate link\_change interrupt and enable io\_port

#### Step10. Done

- if auto-polling\_command = "off", then go to step1, and stay idle

- else go to step2, for next port.

#### **Duplex mode decision rule:**

```

RMII_DUPLEX_MODE = ~( ( ANAR.8 = 1 and ANLPAR.8 =1:100BASE-TX Full ) or ( ( ANAR.7 =0 or ANLPAR.7 =0) and ANAR.6 =1 and ANLPAR.6=1))

```

Note that value 1 denotes half duplex, 0 denotes full duplex.

#### **Speed decision rule:**

```

According to ANLPAR,

- if ~((ANLPAR.9=1 or ANLPAR.8=1 or ANLPAR.7=1)

then speed = 10MHz

```

#### 2.4 FLOW CONTROL

In VT6508, there are three policies of resource management for different objectives:

- (1) flow control for full-duplex ports

- Objective: slow down the input traffic without incurring any drops.

- (2) backpressure for half-duplex ports

- Objective: slow down the input traffic with intended collision and the Ethernet backoff mechanism.

- (3) drop control for private buffer reservation

- Objective: shape the input traffic to be compliant to the buffer reservation discipline. In the following, we call "congestion control" as aggregation of the above three policies.

The application conditions of resource management policies are as follows:

(1) flow control for full-duplex ports

Enabled only when the flow control feature is enabled and the full-duplex port's party has flow control capability.

Note that as both the flow control feature and the drop control feature are enabled, the drop control feature is not turned on if the full-duplex port's party has flow control capability.

(2) backpressure for half-duplex ports

Enabled only when the flow control feature is enabled and the port is in half-duplex mode. Note that as both the flow control feature and the drop control feature are enabled, the drop control feature is not turned on if the port is in half-duplex mode.

(3) drop control for private buffer reservation

Enabled when the flow control feature and the drop control feature are enabled, but the full-duplex port's party has not flow control capability.

Also enabled when the flow control feature is disabled and the drop control feature is enabled.

#### **XON/XOFF Window and Drop Window**

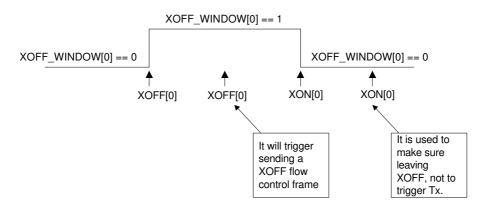

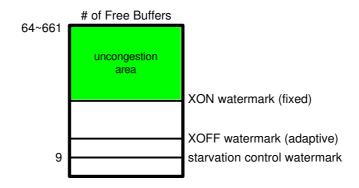

The flow control and backpressure are based on XON/XOFF window. Within XON window, the source port is in non-congestion status so that any incoming packets are forwarded normally. If an incoming packet violates the constraint of congestion control, the source port will leave the XON window and enter the XOFF window after this enqueue operation is served. Within XOFF window, the source port is in congestion status so that any incoming packet will trigger a congestion-control operation that depends on the used policy. The drop control mechanism, residing in Forwarding Control and enabled by DROP\_EN = 1, is based on every ports' congestion windows that are defined as (1) any one is in XOFF window, (2) a destination port is in congestion status if its reservation buffer count == 0.

The XON/XOFF windows and the DROP ON/OFF windows are maintained by TMAC, according to port status and input signals from Queue Control. Figure 6 shows an example XOFF window status (named as XOFF\_WINDOW[0]) of port 0, where XOFF[0] and XON[0] is an event generated by queue control to notify this source port should enter XOFF state, and XON[0] are events generated by queue control to notify this source port should enter or leave XOFF state, respectively. If the source port is within XOFF window as an XOFF event arrives, an flow control frame with pause time = 0xffff will be sent out. If the source port is within XON window, the arriving XON event will be ignored.

Figure 6. XON/XOFF Window Concept.

#### **Congestion-Control Operations**

The starvation control threshold is 9 in VT6508. Let  $\Phi$  be the Free Memory Count. Let  $\Omega$  be the Virtual Free Buffer Count, where  $\Omega = \Phi$  - 9. In congestion control, decisions are based on  $\Omega$ . Within XOFF window, the corresponding congestion-control operations are as follows:

#### (1) flow control operation

As a unicast or broadcast packet, enqueued by Input Control, violates the congestion control constraints, Queue Control will assert a trigger to its source port's TMAC to send out a flow control frame with pause time = FFFFH. There are two congestion conditions: (1)  $\Phi \le \max\{\Psi,28\}$  and  $R_k = 0$ , (2) any port is in XOFF window and  $R_k = 0$ .

Note that even a source port is within XOFF window, an XOFF triggering signal from Queue Control will also make the TMAC to send out a flow control frame of pause time = FFFFH. Although it costs more bandwidth to perform the flow control operation, this duplicated transmission can guarantee the XOFF flow control frame could be received by the party successfully.

#### (2) backpressure for half-duplex ports

As a non-local incoming packet is received, Input Control will assert a signal of "Non\_Local" to notify its TMAC sub-module about the status. TMAC will collide this packet if it is a half-duplex port and it is within XOFF window.

#### (3) drop control for private buffer reservation

As an incoming packet, coming from a port within DROP\_ON window and destining to a port within CONGESTION window, is detected by Forwarding Control in lookup operation, Forwarding Control will unmask its port mask to make it to be dropped by Input Control. Note that the DROP\_ON window indicates the time duration in which the drop feature to the specific port is enabled, that is determined by TMAC. Note that the CONGESTION window of port k is turned on when any port is in XOFF window and  $R_k = 0$ , that is determined by Queue Control.

#### **XON/XOFF Thresholds Selection**

In VT6508, the XON threshold is fixed and programmable. Basically, the XON threshold is equal to half of total number of buffers -10.

The XOFF threshold is adaptive and has two objectives:

- (1) Prevent buffers are exhausted by some hungry port for unbalanced traffic condition. So, XOFF threshold >= total # of buffers necessary to be reserved.

- (2) Prevent packet drop because of too late response to buffer insufficience condition for balanced traffic condition. In VT6508, we assume the flow control response time to each port is 2 buffers.

Q[k]: queue length of output port k

$R_{\text{max}}$ : maximum reserved buffer number for each port

R[k]: reserved buffer number of port k,  $R[k] = (Q[k] \ge R_{\text{max}} ? 0 : Q[k] - R_{\text{max}})$

$\Psi$ : # of buffers necessary to be reserved,  $\Psi = \sum_{k=0}^{9} R[k]$

$\Phi$ : free memory count

C: reserved memory count for virtual free space, C = 10 (default)

$\Omega$ : virtual free buffer count,  $\Omega = (\Phi \le C ? 0 : \Phi - C)$

Θ: XON threshold

When to enter XOFF window  $\Rightarrow$  ( $\Omega = 0$ )

or  $(\Omega \le \max{\{\Psi,28\}} \text{ and } R[k] = 0)$

or (any port is XOFF and R[k] = 0)

When to leave XOFF window for any input ports  $\Rightarrow \Omega > \Theta$

C: number of reserved buffers to prevent touching buffer starvation threshold (Virtual Free Space)

9 < C < D, default C = 10

D: offset of # buffers to tolerate incoming packets before source parties stop (Minimum XOFF Constant Threshold)

Default D = 2x9 + 9 + 1 = 28 for SRAM size of 256KB

£ XFree memory count

£ Z# of buffers necessary to be reserved for private policy.

**XOFF** condition:

$((\pounds X) (\max{\pounds ZD}+C))$  and  $(R_k = 0))$  or  $(\pounds X C)$

XON condition:

( (£  $\times XON_Thred$ ) XON\_Thred = (1/2) x (MaxBufferNo + MaxXOFF - 20)

| SRAM size | # of buffers | Max XOFF   | Min XOFF | XON | Rmax |

|-----------|--------------|------------|----------|-----|------|

| 128KB     | 64           | D+C = 29   | D+C = 29 | 43  | 1    |

|           |              | D = 19     | D = 15   |     |      |

|           |              | C = 10     | C = 10   |     |      |

| 256KB     | 149          | 4x9+C = 46 | D+C = 38 | 98  | 4    |

|           |              |            | D = 28   |     |      |

|           |              | C = 10     | C = 10   |     |      |

| 512KB     | 320          | 6x9+C = 76 | D+C = 57 | 198 | 6    |

|           |              | C = 20     | D = 37   |     |      |

|           |              |            | C = 20   |     |      |

| 1MB       | 661          | 8x9+C=102  | D+C = 67 | 381 | 8    |

|           |              | C = 30     | D = 37   |     |      |

|           |              |            | C = 30   |     |      |

#### 2.5 Broadcast Storm Filtering

In VT6508, the feature of broadcast storm filtering is based on the above congestion control, and subjects to incoming broadcast packets. When an incoming broadcast packet is first enqueued by the Input Control of the source port, Queue Control will check if any one of its destination output ports is in XOFF window. If yes, it will trigger flow control to source port. For example, if a broadcast packet comes in from port 0, it will be forwarded to port1, port2, port3, port4, ... port8 in turn. If any one of ports 1~8 is congested, it will trigger flow control to source port 0, right on it is received and enqueued by Input Control of port 0.

If any port's drop window is turned on, Forwarding Control will drop the incoming broadcast packets to restrict the resource allocation.

#### 2.6 SERIAL EEPROM INTERFACE AND CONFIGURATION COMMANDS

If the chip initialization mode is "EEPROM-init" (by strapping), VT6508 will read the external EEPROM device through EEC, EEIO during the system initialization. The signals of EEPROM interface are described as follows:

| Name | Type | Description           |

|------|------|-----------------------|

| EEC  | O    | serial EEPROM         |

|      |      | interface clock       |

| EEIO | IO   | serial EEPROM         |

|      |      | interface data signal |

There are two types of EEPROM commands with the following format:

1. EOF Command: this must be the last command in EEPROM.

$EE_DATA[7:0] = 8'b0000\_0000$

- 2. Download Command:

- EE\_DATA[7:6] = 2'b01 → eeprom download data for a specific address

- EE\_DATA[5:0] → sequentially download data length from the following address

- The next 2 EE\_DATA will be Register base and offset address

Note that there must be an 8-bit check sum following the EOF command to make the sum of all commands and this check-sum byte is equal to zero bits 0000-0000.

#### **EEPROM** memory layout:

| EEPROM Address                        | Data[7:0]                                                             |

|---------------------------------------|-----------------------------------------------------------------------|

| 00H                                   | - 1st Command[1:0](2 b01) + $1^{st}$ _Data_Length[5:0] (1 <= n <= 63) |

| 00H+1                                 | - CS_Module[7:0]                                                      |

| 00H+2                                 | - IO_Write Start Address                                              |

| <i>00H</i> +3 ∼                       | - IO_Write_DATA[7:0] *n                                               |

| 00H+2+1 <sup>st</sup> _Data_Length(n) |                                                                       |

| 00H+3+1 <sup>st</sup> _Data_Length(n) | - 2 <sup>nd</sup> Command                                             |

|                                       |                                                                       |

|                                       |                                                                       |

|                                       |                                                                       |

|                                       | - Ending Command[7:0]=8'b0000_0000 → End_of_file                      |

|                                       | Check_Sum                                                             |

Note that EEPROM device id and address must be 7'b1010\_001.

#### 2.7 TRUNKING

There are two trunk groups in VT6508, one is port (0,1), another is port (6,7). Each one can be enabled individually. The trunking load balance algorithm is as follows:

Assume DMAC=12'h000000000002, source\_port\_id = 4'b000<u>1</u>.

Assume the above value is 12'b000000011010 after lookup for DMAC = 12'h000000000002.

Let dest\_bit = DMAC\_forwarding\_entry\_address[4] xor source\_port\_id[0]. If the DMAC refers to a trunk port of the trunk group (0,1), the selected outgoing trunk port is port 0 + dest\_bit.

If the DMAC refers to a trunk port of the trunk group (6,7), the selected outgoing trunk port is port 6 + dest\_bit.

# 3 THE VT6508 SRAM ADDRESS MAPPING TABLE

128-pin 32bit mode (1 Bank of 32Kx32, 64Kx32):

|          | ZDIL Mode ( 1 D      |                             |                     | an 115 11           |

|----------|----------------------|-----------------------------|---------------------|---------------------|

| Internal | 6508 Pad(64bit mode) | 6508 Package<br>Address Pin | SRAM Address Pin    | SRAM chip<br>select |

| 64bit    |                      | 7 Iddiess I III             |                     | Select              |

| linear   |                      |                             |                     |                     |

| Address  |                      |                             |                     |                     |

| IA15     | SA15 = IA14          | SA15 =                      | A15 = IA14          |                     |

|          |                      | IA14                        | N/A for 32kx32      |                     |

| IA14     | SA14 = IA13          | SA14 =                      | A14 = IA13          |                     |

|          |                      | IA13                        |                     |                     |

| IA13     | SA13 = IA12          | SA13 =                      | A13 = IA12          |                     |

|          |                      | IA12                        |                     |                     |

| IA12     | SA12 = IA11          | SA12 =                      | A12 = IA11          |                     |

|          |                      | IA11                        |                     |                     |

| IA11     | SA11 = IA10          | SA11 =                      | A11 = IA10          |                     |

|          |                      | IA10                        |                     |                     |

| IA10     | SA10 = IA9           | SA10 = IA9                  | A10 = IA9           |                     |

| IA9      | SA9 = IA8            | SA9 = IA8                   | A9 = IA8            |                     |

| IA8      | SA8 = IA7            | SA8 = IA7                   | A8 = IA7            |                     |

| IA7      | SA7 = IA6            | SA7 = IA6                   | A7 = IA6            |                     |

| IA6      | SA6 = IA5            | SA6 = IA5                   | A6 = IA5            |                     |

| IA5      | SA5 = IA4            | SA5 = IA4                   | A5 = IA4            |                     |

| IA4      | SA4 = IA3            | SA4 = IA3                   | A4 = IA3            |                     |

| IA3      | SA3 = IA2            | SA3 = IA2                   | A3 = IA2            |                     |

| IA2      | SA2 = IA1            | SA2 = IA1                   | A2 = IA1            |                     |

| IA1      | SA1 = IA0            | SA1 = IA0                   | A1 = IA0            |                     |

| IA0      | SA0 = 0              | N/A                         | A0 = 0(directly tie |                     |

|          | (internally)         |                             | to ground)          |                     |

# **SECTION II REGISTER MAP**

# 1. REGISTERS TABLE

By using EEPROM initialization mode, all internal registers can be accessed.

|          | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Name     | Bits   | Default         | R/W  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-----------------|------|

| (base/of |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |        | Value           |      |

| fset)    | Ohio Opationastica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |        |                 |      |

|          | i ü                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OLUB OFO | [00.0] |                 | D/\/ |

| 0000H    | Chip Configuration by strapping: CHIP_CFG[0]: BCAST_BPDU CHIP_CFG[1]: LED_COMB [0] CHIP_CFG[2]: DROP_CONTROL_EN CHIP_CFG[3]: SRAM_TYPE[1] CHIP_CFG[3]: SRAM_TYPE[1] CHIP_CFG[5:4]: CHIP_INIT_MODE[1:0] CHIP_CFG[16] RETRY_EXCE_COLL [1:0] CHIP_CFG[16] TRUNK_MODE[0] CHIP_CFG[17] TRUNK_MODE[2] CHIP_CFG[18]: EN_BACKPRESSURE [0] CHIP_CFG[20:19]:RMII_PORT_FC_EN CHIP_CFG[23:21]:LED_CFG[2:0] CHIP_CFG[24]: HASH_ALG_SEL CHIP_CFG[25]: NO_SWAP_EEPROM_LED CHIP_CFG[26]: EN_AGING CHIP_CFG[27]: DIS_CUT_THRU CHIP_CFG[28]: DIS_AGGRES_BACKOFF CHIP_CFG[29]: COLL_POINT CHIP_CFG[29]: COLL_POINT CHIP_CFG[30]: DIS_TEST_MODE CHIP_CFG[31]: DIS_LATCH_UP_MODE CHIP_CFG[41:40]: SNIFFER_PORT[7:0] CHIP_CFG[43]: TRUNK_MODE[1] CHIP_CFG[45]: TRUNK_MODE[3] CHIP_CFG[46]: SRAM_NUM CHIP_CFG[47]: SRAM_TYPE[0] CHIP_CFG[47]: SRAM_TYPE[0] CHIP_CFG[48]: DIS_DROP_STARV CHIP_CFG[48]: DIS_DROP_STARV CHIP_CFG[55]: SRAM_32BIT_MODE CHIP_CFG[56]: DIS_BORT_PREAM CHIP_CFG[55]: RMII_SPEED_ARB CHIP_CFG[56]: DIS_9_PORT_LED_MODE CHIP_CFG[56]: DIS_9_PORT_LED_MODE CHIP_CFG[56]: DIS_9_PORT_LED_MODE CHIP_CFG[56]: DIS_9_PORT_LED_MODE CHIP_CFG[56]: DIS_9_PORT_LED_MODE CHIP_CFG[56]: DIS_9_PORT_LED_MODE | CHIP_CFG | [63:0] | by<br>strapping | R/W  |

|          | CHIP_CFG[63]: DIS_INIT_DBG_MODE (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |        |                 |      |

| 0AH    | Enable Normal Operation of LED Serial-Out                                                                                                                                                                 | EN LED OUT               | [0]   | 0               | R/W |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------|-----------------|-----|

|        | The normal operation (periodic data sending) of LED Serial-Out can be triggered by (1)                                                                                                                    |                          |       |                 |     |

|        | EEPROM-init complete signal from EEPROM-init module, or (2) software writes value 1 to this                                                                                                               |                          |       |                 |     |

| 10H    | register. CPU Soft Reset for the whole switch chip reset                                                                                                                                                  | CPU SOFT RESET           | [0]   | 1               | R/W |

|        | For Read, 0: soft reset in progress 1: soft reset done                                                                                                                                                    | 5. 5_53. 1_1.55.         | [0]   |                 |     |

|        | For Write, any value will trigger the whole chip reset. The soft reset is similar to power-on reset for the switch chip, except that it is asserted by                                                    |                          |       |                 |     |

|        | writing any value to this register. The CPU soft reset has to take 16 RCLK50 cycles, i.e. 320ns.                                                                                                          |                          |       |                 |     |

| 0100H  | Queue control                                                                                                                                                                                             |                          |       |                 |     |

|        | Congestion Control Xon Threshold register                                                                                                                                                                 | XON_THRED                | [9:0] | by<br>strapping | R/W |

| 02H    | Output Private Buffer Size                                                                                                                                                                                | PRIVATE_BUF_SIZE         | [4:0] | by<br>strapping | R/W |

| 03H    | Selected Output Queue ID                                                                                                                                                                                  | QUEUE_ID                 | [3:0] | 0               | R/W |

|        | Selected Output Queue Length                                                                                                                                                                              | OUEUE_LENGTH             | [9:0] | 0               | R/W |

|        | Selected Output Queue Head Pointer                                                                                                                                                                        | OUEUE_HEAD               | [9:0] | 3FF<br>(null)   | R/O |

|        | Virtual Free Space                                                                                                                                                                                        | V_FREE_SPACE             | [9:0] | by SRAM<br>size |     |

| 0A-0BH | Minimum XOFF Constant Threshold                                                                                                                                                                           | MIN_XOFF_CONST<br>_THRED | [9:0] | by SRAM<br>size | R/W |

|        | Buffer control                                                                                                                                                                                            |                          |       |                 |     |

| 00-01H | Free Memory Block Count                                                                                                                                                                                   | FREEMCNT                 | [9:0] | by SRAM<br>size | R/W |

| 02H    | Memory Allocation Bit Mask Byte ID                                                                                                                                                                        | MASK_ID                  | [6:0] | 0               | R/W |

| 03H    | Memory Allocation Bit Mask                                                                                                                                                                                | BUFFER_MASK              | [7:0] | 0               | R/O |

|        | Forwarding table control                                                                                                                                                                                  |                          |       |                 |     |

| 00H    | sniffer port id                                                                                                                                                                                           | SNIFFER_PID              | [3:0] | by<br>strapping | R/W |

|        | monitor ports bit mask                                                                                                                                                                                    | MONITOR_PM               | [8:0] |                 | R/W |

| 03H    | monitor ports bit mask  0 => to monitor input&output traffic (default)  1 => to monitor input traffic only  2 => to monitor output traffic only                                                           | MONITOR_MODE             | [1:0] | 0               | R/W |

| 04H    | auto-aging configuration 0: disable auto-aging (default) 1: enable auto-aging Note: Initialization Control should enable auto-aging for strapping-only initialization.                                    | EN_AUTO_AGE              | [0]   | 0               | R/W |

| 05H    | inter-aging time (in millisecond)                                                                                                                                                                         | INTER_AGE_TIME           | [7:0] | 50              | R/W |

|        | The valid value is 1255. The default inter-aging time value is 50ms for an entry by default strapping so that the forwarding table of 4K 2K entries (4K slots) can be aged completely in about 5 minutes. |                          |       |                 |     |

| 06-07H | aging index                                                                                       | AGING INDEX   | [10:0] | 0         | R/W |

|--------|---------------------------------------------------------------------------------------------------|---------------|--------|-----------|-----|

|        | 06H: AGING_INDEX[7:0]                                                                             | _             |        |           |     |

|        | 07H: AGING_INDEX[10:8]                                                                            |               |        |           |     |

|        | for CPU to trigger aging on specific entry                                                        |               |        |           |     |

| H80    | aging status                                                                                      | AGING_STATUS  | [0]    | 0         | R/W |

|        | 0: idle or complete                                                                               |               |        |           |     |

|        | 1: in progress (no matter how the process is                                                      |               |        |           |     |

|        | triggered by auto-init or by CPU)                                                                 |               |        |           |     |

|        | for CPU to detect status of aging process                                                         |               |        | - 14      |     |

| 09H    | hash algorithm                                                                                    | HASH_ALG      | [1:0]  | 0 if      | R/W |

|        | HASH_ALG[0]: 0, crc11, 1, direct map                                                              |               |        | strapping |     |

|        | HASH_ALG[1]: 0, scramble, 1, no scramble                                                          |               |        | SD[24]=1  |     |