# System Specification for MBus SPARC Compatible

Rev 1.0

VIA Technologies, Inc. (408) 746-2200 860 East Arques Avenue Sunnyvale, CA 94086

<sup>1</sup>anuary, 1991 1.012591

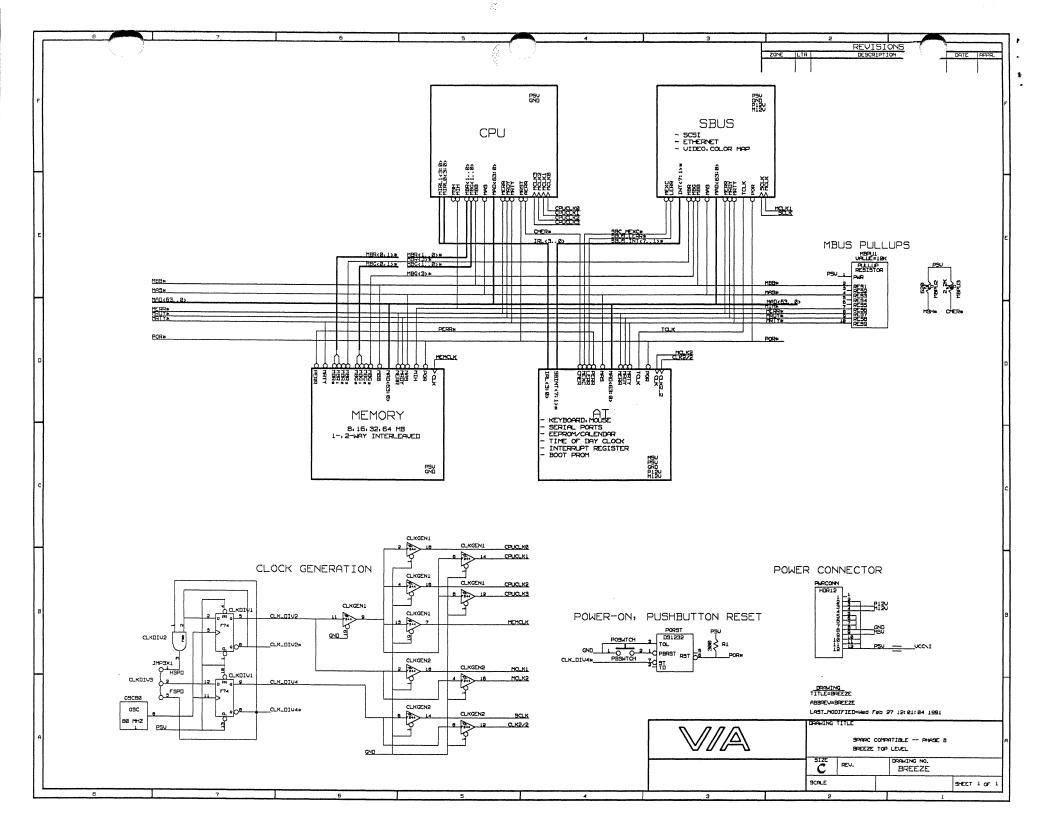

## **OVERVIEW OF PROCESSOR SECTION**

The processor section of the compatible is based around the Cypress CY7C600 Uni-Module Board. It is a complete SPARC chip set consisting of the CY7C601 (Integer Unit), the CY7C602 (Floating-Point Unit), the CY7C604 (Cache Controller and Memory Management Unit), and two CY7C157s (Cache RAMs). The processor section communicates with the rest of the system through the Mbus.

# MEMORY MANAGEMENT UNIT

The memory management unit resides in the CY7C604. It provides translation from a 32 bit virtual address range (4 gigabytes) to a 36 bit physical address (64 gigabytes), as provided in the SPARC reference MMU specification. Virtual address translation is further extended with the use of a context register, which is used to identify upto 4096 contexts or tasks. The cache tag entries and TLB entries contain context numbers to identify tasks or processes. This minimizes unnecessary cache tag and TLB entry replacement during task swithching.

The MMU features a 64 entry Translation Lookaside Buffer (TLB). The TLB acts as a cache for address mapping entries used by the MMU to map a virtual address to a physical address. These mapping entries, referred to as page table entries or PTE's, allow one of four levels of address mapping. A PTE can be defined as the address mapping for a single 4-Kbyte page, a 256 Kbyte region, a 16 Mbyte region, or a 4 Gbyte region. The TLB entries are lockable, allowing the user to exclude important TLB entries from replacement.

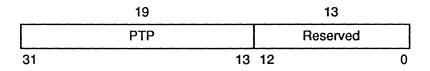

As specified by the SPARC reference MMU, the MMU provides translation for bits 31 through 12 of the virtual address to an expanded physical address mapping using bits 35 through 12. Bits 11 through 0 of the virtual address are not translated, and are defined as the page offset for the 4-Kbyte memory page.

# CACHE

The cache on the compatible is a 64 Kbyte direct mapped write through virtual cache. The cache controller and the cache tag RAMs reside in the CY7C604 and is designed to use two CY7C157 Cache RAMs for the cache memory. The cache is organized as 2048 cache lines of 32 bytes each. The CY7C604 has 2048 cache tag entries on-chip, one tag entry for each cache line. The virtual address field VA<15:5> selects one of the 2048 lines of the cache. Cache data replacement is always performed by replacing cache lines.

For the write through cache used in the compatible, write access cache hits cause both the cache and the main memory to updated simultaneously. A write access cache miss causes only the main memory to be updated (no write allocate). The selected cache line is invalidated for a write access cache miss.

During read access cache hits, the cached data is read out and supplied to the IU. In case of a read access cache miss, a cache line is fetched from main memory and loaded into the cache before the required data is supplied to the IU.

Each entry in the cache tag consists of the 16 bits of virtual address (VA(31:16)), a 12 bit context number (CXN(11:0)), one valid bit (V) and one modified bit (M). A supervisor bit (S) is included in the cache tag entry. For cache tag entries which are accesible by the supervisor only (access level 6 or 7), the S bit is set.

# MAIN MEMORY SPECIFICATIONS

The main memory of the compatible consists of three sections:

- 1. Mbus Interface

- 2. Memory Array

- 3. DRAM Controller

The Main Memory supports a Level 2 Mbus Interface as per the SPARC Mbus Interface Specifications. Read and write transactions of byte, halfword, word, doubleword, and bursts of 16, 32, 64, and 128 bytes are supported. Coherent Invalidate transactions for the Level 2 Mbus Interface are also supported.

The Memory Array is organized as 2 banks of memory with each bank consisting of 8 1M  $\times$  9 DRAM modules (SIMMs) forming a data path 64 bits wide. Parity on a per byte basis is generated when memory is written and checked when it is read. The memory can be upgraded to use 4M  $\times$  9 DRAM modules without changing the design. The design of the memory allows for the following 6 configurations by setting up a configuration register in the Mbus Interface:

- 1. 8MB 1M x 9 SIMMs, non-interleaved, half populated (1bank)

- 2. 16MB 1M x 9 SIMMs, non-interleaved, fully populated

- 3. 16MB 1M x 9 SIMMs, interleaved, fully populated

- 4. 32MB 4M x 9 SIMMs, non-interleaved, half populated (1 bank)

- 5. 64MB 4M x 9 SIMMs, non-interleaved, fully populated

- 6. 64MB 4M x 9 SIMMs, interleaved, fully populated

The DRAM Controller have two sets of DRAM address and control logic so that it can control each bank of memory independently of the other. Interleaving the two banks of memory is done on a doubleword basis.

Transactions to Main Memory are initiated by an Mbus master. The transaction is sent across MAD<63:0>, which is a multiplexed address and data bus, and received by the Mbus Interface. The address, transaction type and size are latched on the other side of the Mbus Interface. For reads, the data is parallel loaded from each of the memory banks into the Mbus Interface and transmitted back to the Mbus master who initiated the transaction. For writes, the Mbus master holds the data on MAD<63:0> until the DRAM Controller acknowledges that it has written the data to the Memory Array. Burst transactions cause the DRAM Controller to do multiple DRAM page mode cycles. The DRAM Controller has programmable wait states based on DRAM speed and system clock frequency to provide maximum memory bandwidth given various memory configurations.

and all

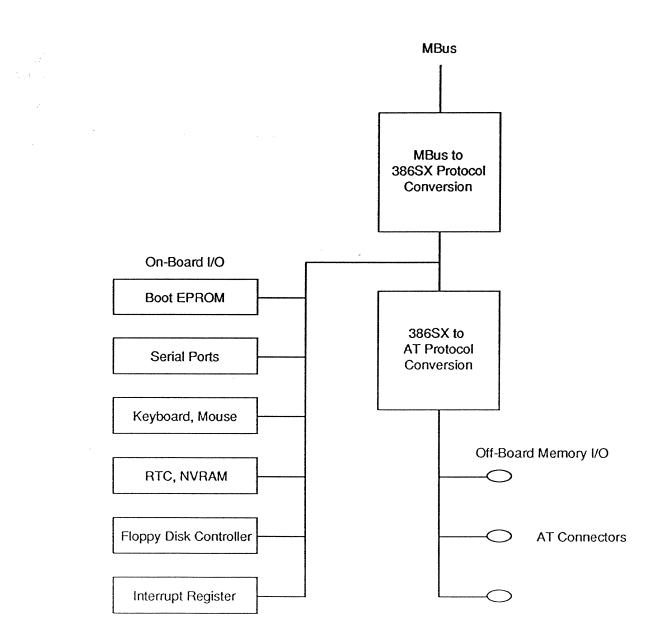

# ON-BOARD AND AT BUS I/O

#### **OVERALL ARCHITECTURE**

(4)

•

#### GENERAL DESCRIPTION

Devices can be interfaced in one of two ways. The first is for standard on-board devices, which can be connected to a specialized byte-wide bus. The second is an AT interface.

### AT INTERFACE

There are two levels of bus conversion in the AT interface. The first translates Mbus cycles into the the bus protocol of the Intel 386sx. There is no actual 386 processor involved, just logic which executes the bus cycle sequences of the 386sx, with a data path to adapt the 64- bit wide MAD data bus to a 16 bit width. The 386sx protocol is used as an intermediate format which can easily interface to other system busses, in this case the AT.

In the second level of bus conversion, 386sx bus cycles are translated into AT cycles.Data transfer sizes supported are: 64, 32, 16 and 8 bits. The AT bus has 24 bits of address and 16 bits of data. Devices on the AT can be connected to either the full 16-bit data bus, or just to the lower 8 bits. In the case of a 16-bit access to an 8-bit AT data path device, the AT logic executes a bus sizing sequence, performing two 8-bit transfers on the AT bus. In the case of a byte access to either an 8-bit or 16-bit data path AT device, the AT logic copies data from/to the low 8 bits of the bus to/from the high 8 bits, when the byte address that it sees is odd (A[0] = 1).

The AT divides its address space into memory and I/O spaces, and accesses to both spaces are supported. Memory and I/O spaces are distinguished by Mbus address bit 24. To address AT memory space, accesses are made within AT address space with bit 24= 1. To address AT I/O space, accesses are made with bit 24= 0.

In addition to the set of I/O devices on board, there is the capability of expanding, by means of plugging standard AT daughtercards into the connectors provided.

#### **ON-BOARD DEVICES**

Any transfer size permitted by the MBUS is allowed(byte,halfword,word,double,16,32,64, and 128 byte burst).

#### EPROM

The size of the boot prom is 256K bytes. It consists physically of a 256K by 8, CMOS EPROM, part number AM27C020, speed 100ns.

The boot prom is always selected when Mbus bit MBL (MAD<45>) = 1.Data accesses in Bypass Mode (ASI = 20-2f) will access the boot prom using PA<17:0>.The physical base address is 0xFF0000000. Alternatively, the PROM can be accessed at address F00000000. The only difference is that a write operation to 0xFF0000000 will result in a null cycle, while a write to 0xF0000000 will proceed as a write operation.

#### Serial Ports

There are two identical serial ports, referred to as A and B. They are contained in one Z85C30 SCC chip from Zilog or AMD. The external connection is RS-232. Both ports interrupt on Mbus level 12. Port A has higher priority than Port B. The registers are located as follows:

| Address     | · · · · · · · · · · · · · · · · · · · |      | -          |

|-------------|---------------------------------------|------|------------|

| 0xf01000000 | Port B control                        | byte | read/write |

| 0xf01000001 | Port B data                           | byte | read/write |

| 0xf01000002 | Port A control                        | byte | read/write |

| 0xf01000003 | Port A data                           | byte | read/write |

The clock oscillator input frequency is 4.9152 Mhz.A device recovery time of 800 ns must be observed between accesses.

#### Keyboard/Mouse

This is also a Z85C30 SCC chip, with Port A corresponding to the keyboard, and Port B the mouse. The interrupt is on level 12, with lower priority than the 2 serial ports. The register address locations are as follows:

| [ | Byte Address |                  |      |            |

|---|--------------|------------------|------|------------|

|   | 0xf02000000  | mouse control    | byte | read/write |

|   | 0xf02000001  | mouse data       | byte | read/write |

|   | 0xf02000002  | keyboard control | byte | read/write |

|   | 0xf02000003  | keyboard data    | byte | read/write |

The clock oscillator input frequency is 4.9152 Mhz.A device recovery time of 800 ns must be observed between accesses.

#### **Real-Time Clock/ NVRAM**

This is a Mostek MK48T02B, size 2K bytes. The base address is 0xF04000000.

## Floppy Disk Controller

This is an Intel 82077 floppy disk controller. Register locations are as follows:

| 0xF03000000 | Status Register A               | byte | read       |

|-------------|---------------------------------|------|------------|

| 0xF03000001 | Status Register B               | byte | read       |

| 0xF03000002 | Digital Output Register         | byte | read/write |

| 0xF03000004 | Main Status Register            | byte | read       |

| 0xF03000004 | Data Rate Select Register       | byte | write      |

| 0xF03000005 | Data (FIFO)                     | byte | read/wr    |

| 0xF03000007 | Digital Input Reg/Configuration | byte | read/wr    |

ISDN

This is an AMD AM79C30A (Digital Subscriber Controller). Its Base address is 0xF05000000.

. -

٩,

.

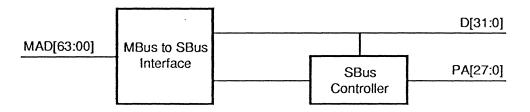

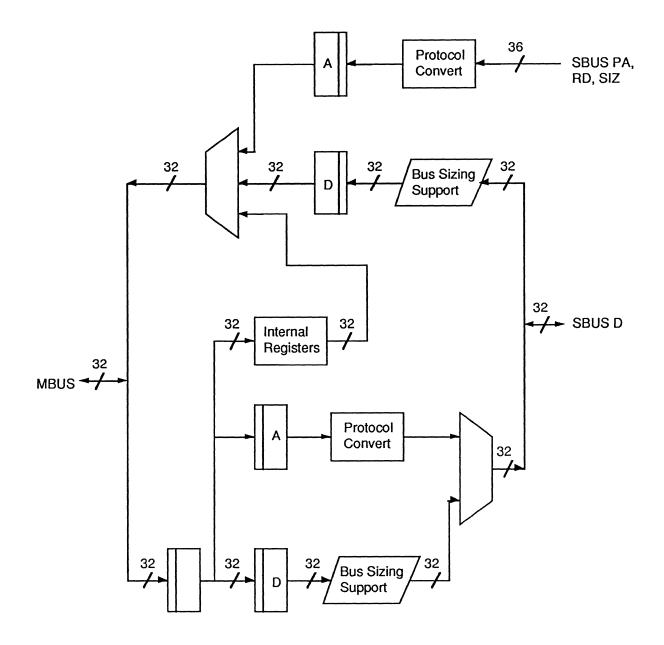

# SPARC MBUS TO SBUS INTERFACE

The compatible has a SBus interface to attach the frame buffer and other SBus peripherals. The SBus interface is attached to Mbus, the main system bus through which the CPU communicates with the Memory subsystem as well as all other sections of the machine. The Mbus to SBus (M2S) interface can be a master or a slave on either bus. The Mbus interface is designed to operate at clock frequencies up to 40 Mhz while the SBus interface is designed to operate within the range of 16.67 to 25 MHz. For Mbus clock frequencies above 33.33 Mhz, the SBus interface will operate at half of the Mbus clock frequency. In addition to the bus interface logic, this section of the machine also contains an SBus Controller.

#### MBUS TO SBUS INTERFACE

This section contains the logic for connecting the 64-bit Mbus to the 32-bit SBus. This interface can behave as both a master and a slave on either the Mbus or the SBus. For transactions going from Mbus to SBus, the M2S interface is an Mbus slave for an Mbus master like the CPU. After receiving the transaction, the M2S interface then becomes an SBus master and initiates a transfer to the targeted SBus slave. For transfers going from SBus to Mbus, the M2S interface is an SBus slave for an SBus slave for an SBus master. After receiving the transfer, the M2S interface then becomes an Mbus slave for an SBus slave for an SBus slave for an SBus master. After receiving the transfer, the M2S interface then becomes an Mbus master and initiates a transaction to the targeted Mbus slave.

There is single set of control logic to control the interfaces on both busses. Only one Mbus to SBus transaction or one SBus to Mbus transfer can be processed by the M2S interface at any one time.

The M2S Interface supports Mbus Read and Write transactions of the following sizes: byte, halfword, word, doubleword. A doubleword Mbus transaction becomes two single word transfers on the SBus.

The M2S Interface supports SBus Read and Write transfers of the following sizes: byte, halfword, word.

The M2S interface supports bus sizing as a master on the SBus. Bus sizing allows a master to initiate a word or halfword transfer to a slave device without regard to whether or not the slave supports a transfer that large. The intent is to allow a master to treat the slave as though it were a word or halfword device, even though the slave may implement only halfword or byte transfers. Bus sizing can occur only during word or halfword transfers. Bus sizing reduces software complexity. For example, an 8-bit frame buffer that is otherwise functionally identical to 32-bit frame buffer can use the 32-bit software unmodified.

#### Mbus as a Master

If the M2S interface is not busy, then the Mbus transaction is accepted. A protocol conversion is performed and a bus request is made to the SBus Controller. The transfer proceeds on SBus after ownership is acquired. The M2S interface then waits for an acknowledgment from the targeted SBus slave. When the acknowledgment is received, it is converted to an Mbus acknowledgment and the transaction is com-

pleted. For a read transaction the read data is driven onto Mbus during the cycle in which the acknowledgment is given. If the M2S interface is busy, then a Relinquish and Retry (R&R) acknowledgment is given, indicating that the Mbus master should relinquish ownership of Mbus and retry the transaction after the Mbus is rearbitrated.

Also, if the Mbus transaction is a doubleword transaction or if the acknowledgment from the SBus slave results in bus sizing taking place on SBus, then a R&R acknowledgment is given back to the Mbus master. The R&R acknowledgment frees up the Mbus for other transactions while the multiple SBus cycles are taking place. When the SBus transfers have completed, the M2S interface waits for the Mbus master to reissue the transaction before giving the Mbus acknowledgment.

### SBUS AS A MASTER

If the M2S interface is not busy, then the SBus transfer is accepted. A protocol conversion is performed and a bus request is made to the Mbus Arbiter. The transaction proceeds on Mbus after ownership is acquired. The M2S interface then waits for an acknowledgment from the targeted Mbus slave. When the acknowledgment is received, it is converted to an SBus acknowledgment and the transfer is completed. For a read transfer the read data is driven onto SBus on the cycle following the one in which the acknowledgment was given. If the M2S interface is busy, then a Rerun acknowledgment is given, indicating that the SBus master should retry the transfer.

### SBUS CONTROLLER

The SBus Controller contains the logic for controlling the SBus. It supports transfers of the following sizes:

| Byte               |            |

|--------------------|------------|

| Halfword           | (2 bytes)  |

| Word               | ( 4 bytes) |

| Two Word Burst     | (8 bytes)  |

| Four Word Burst    | (16 bytes) |

| Eight Word Burst   | (32 bytes) |

| Sixteen Word Burst | (64 bytes) |

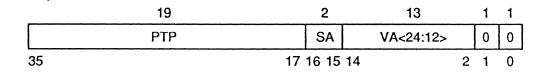

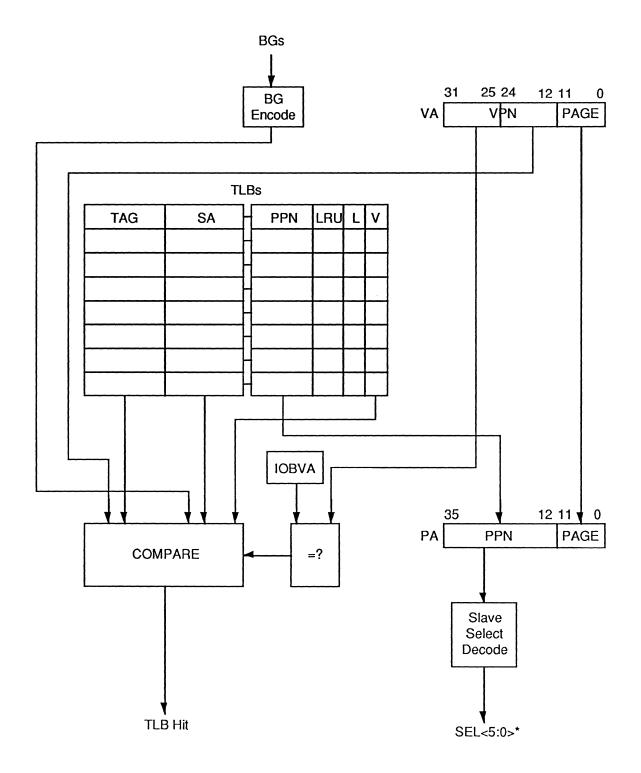

The SBus Controller supports up to 4 SBus masters of which one is the M2S interface. It employs a fair arbitration scheme so that all pending bus requests are granted before a master is allowed to acquire the bus again. It supports geographically selecting six SBus slaves, one being the M2S interface. Virtual to physical address translation is done through an eight-entry fully associative TLB with LRU as replacement policy. The TLBs provide translation for a 32 Mbyte address space for each SBus slot. Translation can also be disabled on a per SBus slot basis.

The SBus Controller also has an 8-bit counter to generate a bus timeout acknowledgment if an SBus slave does not give any acknowledgment by the 256th slave cycle.

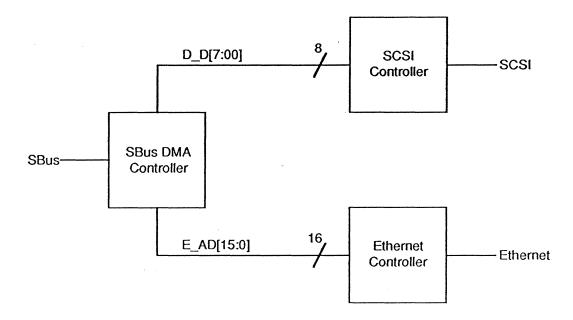

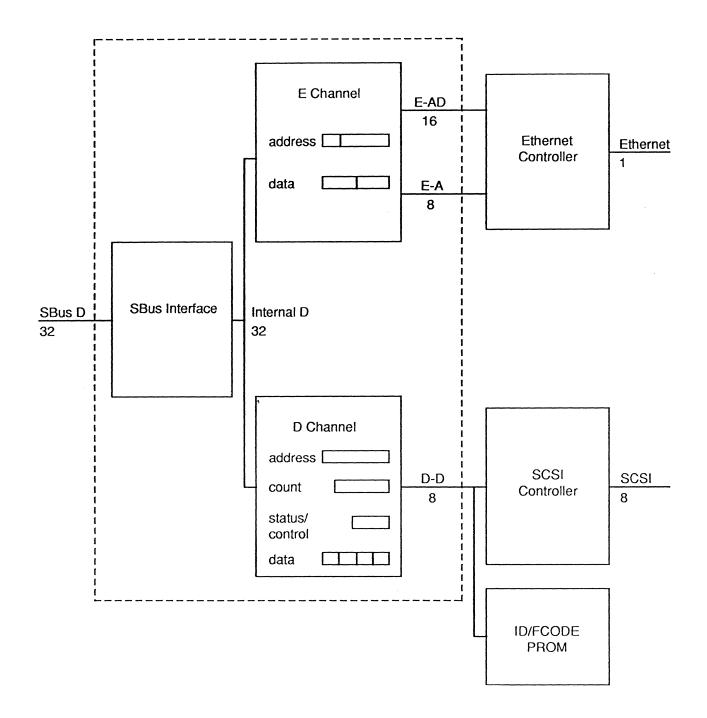

## **DMA I/O STRUCTURE**

The DMA section of the Sparc processor consists of 3 main sections:

- 1. Sbus DMA controller

- 2. SCSI controller

- 3. Ethernet controller

Numbers 2 and 3 consist of the following ICs: NCR 53C90, and AMD7990, respectively. The Sbus DMA controller is made from discrete logic which will be integrated into a gate array.

#### SCSI CONTROLLER (NCR 53C90)

Data is transferred over the 8 - bit SCSI cable at 3 Mbytes/sec worst case. The chip is controlled via a set of 13 byte - wide registers, memory mapped into M bus physical addresses. SCSI commands are given using one of these registers. For data transfers, there is a 16 deep byte-wide FIFO. Data in the FIFO appears to the CPU as another of the 13 registers. Block transfers of data can be done either by the CPU using this register for programmed I/O, or by means of the DMA controller. In the latter case, the SCSI controller communicates its need to send or receive another 8 bits by means of an signal called DREQ, which is connected to one of the DMA controller's channels. That is, the SCSI chip is "implicitly addressed" during DMA.

In DMA mode, an interrupt will be generated when the transfer counter decrements to zero. In non-DMA mode, an interrupt can be generated after each byte transferred, if interrupts are enabled. The interrupt bit appears in a register visible to the CPU.

### ETHERNET CONTROLLER (AMD7990)

The Ethernet controller (LANCE) functions primarily as a bus master. Its master bus cycles are converted into Sbus master cycles by the DMA controller. The CPU initializes the LANCE with a pointer to a control block in main memory, from which the LANCE reads its initialization information. The CPU and the LANCE communicate by means of shared main memory and semaphores, using circular buffer descriptor data structures for the transmit and recieve buffers.

## GRAPHICS

The graphics on the SUN compatible would be supported by a Frame Buffer on the Sbus. All offset addresses need to be added to the slot base address to get the effective address.

#### FRAME BUFFER

The data organization for Frame buffer is as follows. Each byte of video data corresponds to a display pixel. A color map described translates the byte of Video data into the display pixel. The high order byte in Color Video RAM maps to the first visible pixel in the upper left corner of the display monitor. Consecutive bytes are displayed as consecutive pixels along the horizontal scan line, left to right. After 1152 pixels are displayed on one scan line the next pixel is displayed on the next scan line. A total of 900 such lines are displayed per frame at 66 such frames per second.

#### COLOR VIDEO RAM

The Color Video RAM is located in a dedicated area of system memory space and is dual ported; one for video refresh, and the second for processor access. The size of the Color Video RAM is 1 MByte, and is organized as an array of 256K x 32. The Color Video RAM is updated by reading and writing it directly, like memory.

Address Mapping:

| Device offset | Device          | Size   | Туре       | Sbus Transaction Size |

|---------------|-----------------|--------|------------|-----------------------|

| 0 0030 0000   | Color Video RAM | 32-bit | Read-Write | Byte, halfword,word   |

#### COLOR MAP

The Color Map maps bytes in Color Video RAM into pixels. It contains three 256 Byte sections :one each, for red, green and blue. Besides the Color Map, several registers exist in this section. The sub-space address of the internal registers and RAM space has to be loaded into the address register before any meaningful transaction can be done in this section.

To read color data, the SPARC loads the address register with the address of the color palette RAM location to be read. The SPARC then performs three successive read cycles (red, green, and blue) to access the data from the color palette. Following the blue read cycle the address register increments to the next location which the SPARC may read by simply reading another sequence of red, green and blue data from the Color palette. A write to the color palette is done exactly the way a read is done, except that the data bytes of red, green, and blue are written. When accessing the color palette RAM, the address register resets to \$00 after the blue, read or write cycle to location \$FF.

|               |                | <u> </u>  | <u></u> | - <b>-</b> |

|---------------|----------------|-----------|---------|------------|

| Device Offset | Device         | Sub-Space | Size    | Туре       |

| 0 0010 0000   | Address reg    | \$xx      | byte    | Read-Write |

| 0 0010 0001   | Color palette  | \$00-\$FF | byte    | Read_Write |

| 0 0010 0002   | Read Mask reg  | \$04      | byte    | Read-Write |

| 0 0010 0002   | Blink Mask reg | \$05      | byte    | Read-Write |

| 0 0010 0002   | Command reg    | \$06      | byte    | Read-Write |

| 0 0010 0002   | Cntrl/Tst reg  | \$07      | byte    | Read-Write |

Refer to Brooktree part Bt458 data sheet for details on the internal registers and also about programming the Color Map. It is required that bit CR6 in command register be set to a 1. Bit CR7 should be set to 0 to reflect a 4:1 multiplexing of pixels in hardware.Set bits 0 and 1,viz CR0 and CR1 to 0. The rest of the command register bits is left to the discretion of the software programmer.

The Color Map is generally written during vertical retrace. Following the assertion of Level 5 interrupt for the Color Map, the map update must complete in 600 microSeconds (the vertical retrace time) to avoid being visible in the display. Longer updates will complete but the display appearance may be affected.

References: Brooktree Bt458 data sheet.

#### INTERRUPT REGISTER

At the beginning of a vertical retrace the video interrupt is set. This is a level 5 interrupt on theSbus. The interrupt is kept pending until the software clears it. The only relevant bits are as shown below. At the time of power-up interrupt is disabled and need to be explicitly enabled by software by writing a '1' to the ENB bit. Note that the INT pending bit is writable by software and this can aid in diagnostics as well.

| Devic | e Offset | Device | Size      | Туре       |

|-------|----------|--------|-----------|------------|

| 0 002 | 0 0000   | IntReg | Byte      | Read-Write |

|       |          |        |           |            |

| 1     | 1        |        | 6         |            |

| INT   | ENB      |        | not relev | vent       |

| 7     | 6        | 5      |           | 0          |

, <del>-</del>'

## D Prom

As per the SBus specification an IDPROM is located at the base address of this slot. It is a 8Kx8 device and carries the relevant FCode.

| Address     | Device | Size | Туре |

|-------------|--------|------|------|

| 0 0000 0000 | IDProm | Byte | Read |

#### Reserved

$\mathcal{M}^{(i)}$

0 0040 0000 to 0 00F0 0000 reserved

# MBUS ARBITRATION FOR SPARC CLONE

The Mbus arbiter is a separate unit from both the Mbus slaves and masters. It can arbitrate among 4 Mbus masters and incorportates both a linear and a rotating priority algorithm. One bus request will have the highest priority. This can be used to minimize latency for an Ethernet Controller device. The other three bus requests have a rotating priority. Arbitration is overlapped with the current bus cycle. Bus parking is employed which means that the current master retains ownership of the bus until it is taken away by a request from another master. Back-to-back transactions by different masters are not allowed. There must be at least one dead cycle in between each transaction during which the bus busy signal is deasserted.

Each Mbus master has dedicated bus request and bus grant signals. The master requests the Mbus by asserting its bus request signal. Upon receiving a bus grant from the bus arbiter, the requesting Master can start using the bus by asserting the bus busy signal as soon as the previous masters deasserts it.

The Mbus arbiter looks at the bus requests from the 4 Mbus masters and the bus busy signal and generates the bus grants for each master. Only one bus grant is asserted at any time. and the second secon

# PHYSICAL ADDRESS MAP

The physical address map is allocated to minimize hardware decoding for the different devices in the compatible system.

### PHYSICAL ADDRESS ASSIGNMENTS

Mbus

198

| Physical Base Address | Device             | Physical Address Space |

|-----------------------|--------------------|------------------------|

| 0x 0 0000 0000        | Main Memory        | A[p:0]                 |

| 0x C 0000 0000        | reserved           |                        |

| 0x D 0000 0000        | reserved           |                        |

| 0x E 0000 0000        | SBus               |                        |

| 0x F 0000 0000        | AT                 |                        |

|                       | Mbus Configuration | n Address Map          |

| 0x F F000 0000        | (Mbus ID =0x0)     | Boot PROM              |

| 0x F F100 0000        | (Mbus ID =0x1)     |                        |

| 0x F F200 0000        | (Mbus ID =0x2)     |                        |

| 0x F F300 0000        | (Mbus ID =0x3)     |                        |

| 0x F F400 0000        | (Mbus ID =0x4)     |                        |

| 0x F F500 0000        | (Mbus ID =0x5)     |                        |

| 0x F F600 0000        | (Mbus ID =0x6)     |                        |

| 0x F F700 0000        | (Mbus ID =0x7)     |                        |

| 0x F F800 0000        | (Mbus ID =0x8)     |                        |

| 0x F F900 0000        | (Mbus ID =0x9)     |                        |

| 0x F FA00 0000        | (Mbus ID =0xA)     |                        |

| 0x F FB00 0000        | (Mbus ID =0xB)     |                        |

| 0x F FC00 0000        | (Mbus ID =0xC)     |                        |

| 0x F FD00 0000        | (Mbus ID =0xD)     |                        |

| 0x F FE00 0000        | (Mbus ID =0xE)     |                        |

| 0x F FF00 0000        | (Mbus ID =0xF)     |                        |

Memory - upto 64 Mbytes

0x 0 0000 0000 to 0x 0 03FF FFFF

### SBus

| Physical Base Address    | Device                        |

|--------------------------|-------------------------------|

| 0x E 0000 0000           | M2S SBus Slave Interface      |

| 0x E 1000 0000           | SBus Slot1 - SBus Connector 1 |

| 0x E 2000 0000           | SBus Slot2 - SBus Connector 2 |

| 0x E 3000 0000           | SBus DMA Controller           |

| 0x E 4000 0000 to 0x E F | 000 0000 reserved             |

# BOOT\_PROM

| Physical Base Address | Physical Address Space |

|-----------------------|------------------------|

| 0x F F000 0000        | A[17:0]                |

## ON\_- BOARD IO AND AT

| Physical Base Address                     | Device                     | Physical Address Space |  |  |  |  |  |

|-------------------------------------------|----------------------------|------------------------|--|--|--|--|--|

| 0x F 0000 0000                            | Boot Prom                  | A[17:0]                |  |  |  |  |  |

| 0x F 0100 0000                            | Serial Ports               | A[1:0]                 |  |  |  |  |  |

| 0x F 0200 0000                            | Keyboard, Mouse            | A[1:0]                 |  |  |  |  |  |

| 0x F 0300 0000                            | Floppy Disk Controller     | A[2:0]                 |  |  |  |  |  |

| 0x F 0400 0000                            | Real Time Clock/EEPROM     | A[10:0]                |  |  |  |  |  |

| 0x F 0500 0000                            | ISDN                       | A[2:0]                 |  |  |  |  |  |

| 0x F 0600 0000                            | Interrupt Register, Timers | A[4:0]                 |  |  |  |  |  |

| 0x F 0700 0000                            | reserved                   |                        |  |  |  |  |  |

| 0x F 110A 0000                            | AT Memory                  | A[23:0]                |  |  |  |  |  |

| 0x F 1000 0000                            | AT IO                      | A[9:0]                 |  |  |  |  |  |

| 0x F 2000 0000 to 0x F F000 0000 reserved |                            |                        |  |  |  |  |  |

#### **INTERRUPT ASSIGNMENTS**

The Mbus allows for 16 levels of interrupts. The interrupt sources are the following, with 15=highest priority, 0= lowest.

- 15 Non-Maskable Interrupts (NMI)

- 14 Clock (Monitor, Profiler)

- 13 Audio, AT Bus level 3

- 12 Keyboard, mouse, serial ports, AT Bus level 4

- 11 Floppy Disk, AT Bus level 6

- 10 Clock (Timer), AT Bus level 7

- 9 SBus level 7, AT Bus level 9

- 8 SBus level 6, AT Bus level 10

- 7 Video, SBus level 5

- 6 Software Interrupt Level 6

- 5 Ethernet, SBus level 4, AT Bus level 11

- 4 Software Interrupt Level 4

- 3 SCSI, SBus level 3, AT Bus level 12

- 2 SBus level 2, AT Bus level 14

- 1 Software Interrupt Level 1, AT-Bus-level 15

- 0 No Interrupt

32.

Non-Maskable Interrupts include:

- 1. Push-Button Switch

- 2. Memory Parity Error

- 3. CPU Memory Error (Asynchronous Error on Memory Access)

- 4. SBus Controller Memory Exception

- 5. SBus Late Error

Interrupts are auto-vectored. That is, the address of the interrupt service routine is formed from a trap base register plus an index formed from the level of the interrupt.

status of m2m chip:

DESIGN: Partially done. MIH signal is not being handled correctly. Parity error checking on memory reads is not being done.

SIMULATION: Functionally about 90% simulated. The arbiter circuitry not simulated. Diagnostics : Not Done.

BUGS: Several relating to IO. For example, the perr signal should be open-collector, the mrty pin should be tristate etc. Initial values of registers.

SYNOPSYS: Mapped to Fujitsu library (0.8um). The arbiter circuitry not compiled yet.

LOCATION OF FILES:

verilog hdl desc. : ~biyani/pc/m2m/v10.0/vlg verilog library : /tools/lib/model/hdl, Fujitsu libraries synopsys environment : ~biyani/pc/m2m/v3.0 simulation environment : /s/users/sparc/breeze/memory

## ADVANCE

# **General Description**

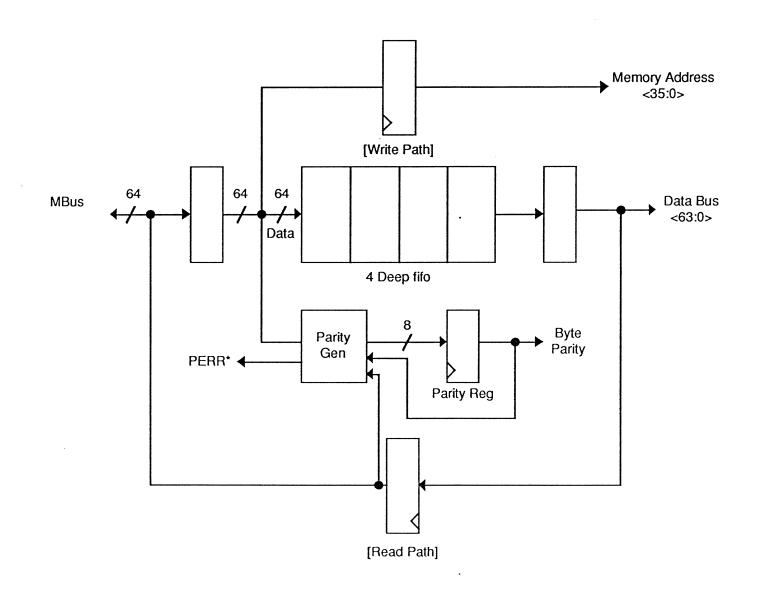

This ASIC connects the MBus to the memory controller. Ideally, the interface logic and the memory controller should be in the same ASIC, but it results in a very high pin count ASIC. Also, the combined ASIC would need external drivers to drive the address, RAS and CAS lines. Thus, the need to have two ASIC's, the memory interface ASIC and the memory controller ASIC.

The function of the Memory Interface logic is fairly straightforward and is shown below.

What makes the chip complicated is that the Memory Interface Logic has to be sliced into two chips. The slicing becomes a little tricky as the address is available on only the lower 36 bits. Another complication is the design of the dual-ported FIFO, simultaneous Read and Write should be done on the 4-deep fifo. This would significantly improve the performance of the memory system.

# **Objectives for ASIC**

This ASIC designed for memory interface must achieve the following objectives:

- Only one load on MBus

- Fit in a 128 PQFP

- Run up 40MHz

- The filling and emptying of the on board buffers can take place simultaneously.

- The ASIC should support all burst modes.

# **Slicing Methodology**

Byte Defintion

|          | 1     |       |       | SL    | AVE    |       |      | I   |

|----------|-------|-------|-------|-------|--------|-------|------|-----|

| Bits     | 63:56 | 55:48 | 47:40 | 39:32 | .31:24 | 23:16 | 15:8 | 7:0 |

| Byte No. | 0     | 1     | L2    | 3     | 4      | 5     | 6    | 7   |

|          |       |       |       | MA    | STER   |       |      |     |

Even though the two slices are identical, I define them as the MASTER and SLAVE. This would become clear later in the SPEC. The slicing is done as follows:

MASTER Slice would receive bytes 2,3,4,5 from MBus

SLAVE Slice would receive bytes 0,1,6,7 from MBus.

The advantage of this scheme is that the 36 bits of physical MBus address is split 16 bit in SLAVE and 20 bits in MASTER. Further, the Type (MBus <39:36>) and Size (MBus <42:40>) will originate for the memory controller from the 'MASTER SLICE'.

# **Internal Registers**

## **Configuration/Parity Error Register**

Address 0XFFnXXXXX8

(This is a Read/Write Register)

| 31 | 28   | 27 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 9        | 8 0         | ) |

|----|------|-------|----|----|----|----|----|----|-------------|-------------|---|

| ſ  | PERR | PI    | PE | Ι  | MS | CS | S  | R  | Upper_Bound | Lower_Bound |   |

This register would be read from the 'MASTER Slice', using double word read.

Upper-bound = highest address supported by DRAM controller.

Lower-bound = lowest address supported by DRAM controller.

The Memory Interface would respond if Lower-bound < Target Address (MBus < 31:23>) < Upper-bound and MBus <35:32> is OX) in the address phase of MBus operation.

| R | RAM | Size |

|---|-----|------|

|---|-----|------|

- S Spare

- CS Clock Speed

- MS Memory Speed

- I Interleave

- PE Parity Enable (4 bytes)

- PI Parity Invert <br/>bytes 2,3,4,5> (per byte)

PERR Parity Error <bytes 2,3,4,5> (per byte)

## **MBus Port Register**

#### Address OXFFnXXXXXC

This is a Read/Write register. This would be read from the SLAVE slice using the double word READ. The double word Read/Write at address OXFFnXXXX8 would access this register from the SLAVE. This register is accessed from SLAVE.

| 31 28 | 27 | 24 | 23 | 22 16 | 515  | 87   | 43 | 0     |

|-------|----|----|----|-------|------|------|----|-------|

| PERR  | PI |    | PE | SPACE | MDEV | MREV |    | MVEND |

MVEND Vendor ID

MREV Rev # of device

MDEV Device #

PE Parity Enable

PI Parity Invert <br/>bytes 0,1,6,7> (per byte)

PERR Parity Error <bytes 0,1,6,7> (per byte)

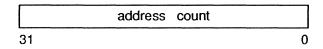

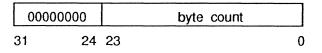

## **Bus Error Register I**

Address OXFFnXXXXX0

This again is a 32 Read/Write register. This can be accessed by double word Read or Write. This register contains a copy of the address from MAS cycle for operation. This is accessed from MASTER.

.

| 31 | 0 |

|----|---|

|    |   |

## **Bus Error Register II**

Address OXFFnXXXX4

This register is identical to Bus Error Register I except its address. This is accessed from the SLAVE. The Read/Write access to this register is done by doing a double word access on address OXFFnXXXXX0.

# **Pinouts of Memory Interface**

| <u>Count</u> | Pin Name              | Type  | Description                                                                                                                                                                                   |

|--------------|-----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32           | MAD <31:0>            | I/O   | MBus multiplexed 32 bit address data                                                                                                                                                          |

| 32           | MD <31:0>             | I/O . | Memory Data Bus                                                                                                                                                                               |

| 16           | MA <15:0>             | 0     | Memory Address Bus                                                                                                                                                                            |

| 4            | PARITY <3:0>          | I/O   | Byte Parity                                                                                                                                                                                   |

| 1            | MASTER/SLAVE          | Ι     | Defines physical location of chip                                                                                                                                                             |

| 1            | C-Mrdy*               |       | I Handshare signal from memory controller. Tells interface controller done.                                                                                                                   |

| 1            | ТҮРЕ                  | I/O   | This is a Multifunction pin. In the MASTER it is an<br>output pin describing the type of operation as<br>Read/Write. If SLAVE it has the same meaning as<br>above, but is an input.           |

| 3            | SIZE <2:0>            | I/O   | this is a multifunction pin. In the MASTER it<br>drives the size information to the memory control-<br>ler. In SLAVE it is an input pin and receives the<br>size information.                 |

| 1            | MAS*                  | I     | Memory Address Strobe on MBUS                                                                                                                                                                 |

| 4            | ID <3:0>              | I     | For MASTER these 4 pins define the MBus slot ID through some internal jumper setting. These pins have no meaning for SLAVE.                                                                   |

| 1            | REGIN/REGOUT          | I/O   | This is a multifunction pin. For the MASTER slice<br>this pin is an output indicating a register operation<br>was decoded. For SLAVE this is an input pin<br>indicating a register operation. |

| 1            | REGADDRO<br>/REGADDRI | I/O   | This is a multifunction pin. For the MASTER slice<br>this is an input pin with the dw address of the<br>register set.                                                                         |

| 1            | MRDY*                 | 0     | In the MASTER slice it drives the MBus MRDY*                                                                                                                                                  |

|              |                       |       |                                                                                                                                                                                               |

|     |              |     | signal. In slave slice is unconnected.                                                                                                            |

|-----|--------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | MERR*        | 0   | This is a multifunction pin. For the MASTER slice<br>this is the MERR* signal for the MBus*. For the<br>slave this is nc.                         |

| 1   | AERR*        | 0   | This is an open collector signal and is the PERR*<br>from each slice.                                                                             |

| 1   | MREQ*/MOP*   | I/O | This is a multifunction bit. In MASTER it drives<br>'MREQ' signal to memory controller. In SLAVE it<br>is an input indicating a memory operation. |

| 1   | MEMBSY*      | I   | This is an input indicating that the memory is busy.<br>This signal comes from the memory controller.                                             |

| 1   | CLK          | Ι   | Clock Line                                                                                                                                        |

| 1   | RESET*       | I   | Reset input                                                                                                                                       |

| 4   | CONFIG <3:0> | 0   | In the MASTER this feeds the configuration information to the memory controller. In SLAVE it is NC.                                               |

| 109 |              |     |                                                                                                                                                   |

|     |              |     |                                                                                                                                                   |

# Software Format of Configuration Registers

To have a thorough idea of qhat a double word register access would give to the processor it is better to see it pictorially. this is because the bytes sent to each of the slices and not contiguous.

DW access on location address OXFFnXXXXX0

| _63        |          | 48 47 |     |     |     |       | 16 15 | 0      |

|------------|----------|-------|-----|-----|-----|-------|-------|--------|

| BUS ER     | R REG II |       | BUS | ER  | R I | REG I | BUS   | ERR II |

| <31        | :16>     |       |     | <31 | :0> |       | <1    | 15:0>  |

| Byte No. 0 | 1        | 2     | 3   | 4   | 5   | 6     | 7     |        |

DW access on location on register address OXFFnXXXX8

| e | 60 60     | 59 56     | 56        | 54 48 | 47 44     | 43 40     | 39        | 38 37 | 36   | 35    | 34 3 | 33 25 | 24 16 | 15 8 | 74   | 3 0   |

|---|-----------|-----------|-----------|-------|-----------|-----------|-----------|-------|------|-------|------|-------|-------|------|------|-------|

|   | PERR      | PI        | PE        | SPARE | PERR      | PI        | PE        | IM    | sics | SPARE | R    | UPPER | LOWER | MDEV | MREV | MVEND |

| l | <0,1,6,7> | <0,1,6,7> | <0,1,6,7> |       | [2,3,4,5] | [2,3,4,5] | [2,3,4,5] |       |      |       |      | BND   | BND   |      |      |       |

PERR <0,1,6,7>Indicates Parity error for bytes 0,1,6,7PERR <2,3,4,5>Indicates Parity error for bytes 2,3,4,5PI <0,1,6,7>Indicates Parity Invert for bytes 0,1,6,7PI <2,3,4,5>For enabling parity for bytes 0,1,6,7PE <2,3,4,5>For enabling parity for bytes 2,3,4,5

1

/s/users/sparc/breeze/sim/v

status of DRMC chip:

DESIGN : complete

SIMULATION :test suite in /s/users/sparc/breeze/sim/v/{debug.v,mem.diag6,rgrs} testing of rgrs is not complete and could yield unknown problems.

BUGS: none outstanding.

SYNOPSYS: mapped to att.

LOCATION of files: verilog hdl description of chip: /s/users/sparc/breeze/memory/v/tst/{memctrl.v,rascas.v,rowcol.v, coladr.v,maddr.v,maxadr.v,refcntr.v,enable.v} simualtion environment: /s/users/sparc/breeze/sim/v

# MBus DRAM Controller Specification

'ecember, 1990 ∠.011691 VIA Technologies, Inc. (408) 746-2200 860 East Arques Avenue Sunnyvale, CA 94086

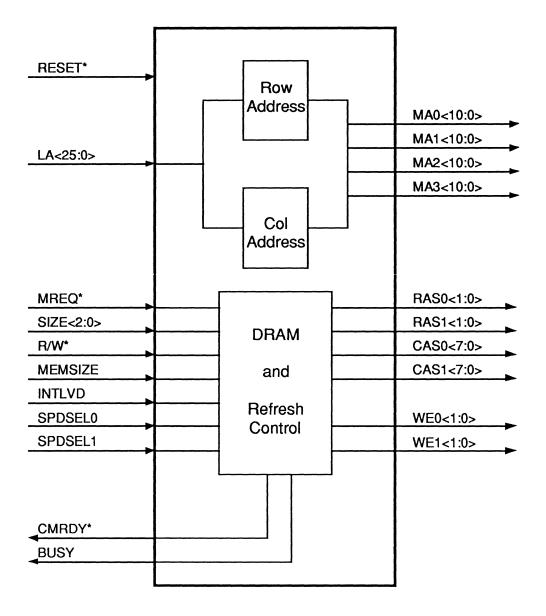

# BLOCK DIAGRAM

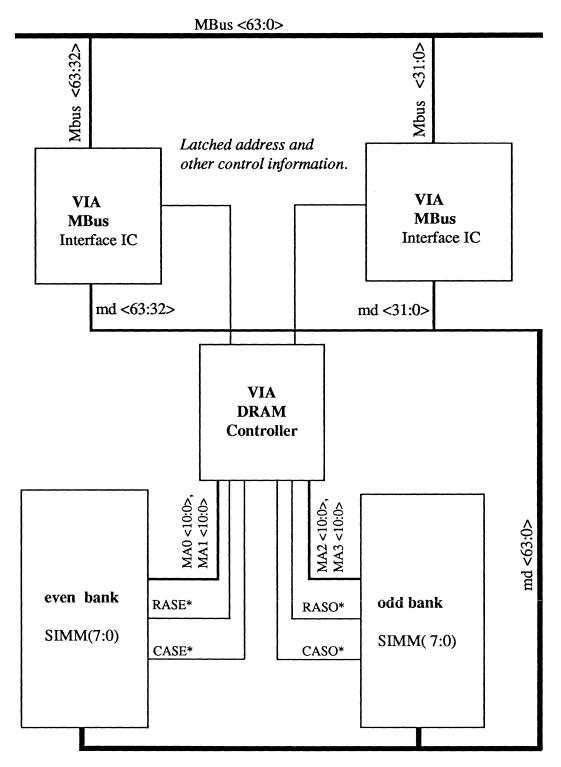

## **DRAM Controller Block Diagram**

# Overview

The DRAM controller is a high-performance CMOS integrated circuit that provides all the necessary control signals between the DRAM array and a pair of MBUS interface ICs in a SPARC based workstation. The rest of the document describes the functions supported in this IC.

# **FEATURES:**

- 2-way Interleaving for High Performance.

- 1 to 128 byte DRAM Read, Write Transaction Using Fast Page Mode.

- Byte Wide Parity.

- CAS Before RAS Refresh Scheme.

- Supports 1 Megabyte and 4 Megabyte RAM Modules.

- Memory Configurations Supported:

- 8 Mbytes 1M x 9 SIMM DRAM's even bank non-interleved.

- 16 Mbytes 1M x 9 SIMM DRAM's both banks and interleaved.

- 32 Mbytes 4M x 9 SIMM DRAM's even bank non-interleaved.

- 64 Mbytes 4M x 9 SIMM DRAM's both banks and interleaved.

- Clock Speed 25 Mhz, 33 MHz and 40 MHz.

- No External Buffers Needed for RAS\*, CAS\*, WE\* and Memory Address For 64 Mbytes of DRAM.

- Needs a Pair of VIA MBus Interface IC's or Equivalent For Optimum Performance on MBus.

- Built in Scan Chain for 100% Fault Grading.

# Pinout

| Signal Name | Signal Name No. of Pins |                | Signal Description            |

|-------------|-------------------------|----------------|-------------------------------|

| LA<25:0>    | 26                      | Input          | Latched 26 bit memory address |

| SIZE<2:0>   | 3                       | Input          | Transaction size              |

| RD/WR⁺      | 1                       | Input          | Rd if =1 else wr              |

| MREQ*       | 1                       | Input          | Request for memory operation  |

| MEMSIZE     | 1                       | Input          | 1=4M Byte ,0=1M Byte sel      |

| SPDSEL0     | 1                       | Input          | Wait state generator bit 0    |

| SPDSEL1     | 1                       | Input          | Wait state generator bit 1    |

| INTLVD      | 1                       | Input          | Turns on 2-way interleaving   |

| CMRDY*      | 1                       | Output         | Operation done                |

| BUSY        | 1                       | Output         | Controller Busy               |

| MA0<10:0>   | 11                      | Output (12 ma) | DRAM address copy 0           |

| MA1<10:0>   | 11                      | Output (12 ma) | DRAM address copy 1           |

| MA2<10:0>   | 11                      | Output (12 ma) | DRAM address copy 2           |

| MA3<10:0>   | 11                      | Output (12 ma) | DRAM address copy 3           |

| RAS0<1:0>*  | 2                       | Output (12 ma) | Even DRAM RAS                 |

| RAS1<1:0>*  | 2                       | Output (12 ma) | Odd DRAM RAS                  |

| CAS0<7:0>*  | 8                       | Output (12 ma) | Even DRAM CAS                 |

| CAS1<7:0>*  | 8                       | Output (12 ma) | Odd DRAM CAS                  |

| WE0<1:0>*   | 2                       | Output (12 ma) | Even DRAM WE                  |

| WE1<1:0>*   | 2                       | Output (12 ma) | Odd DRAM WE                   |

| RESET*      | 1                       | Input          | System Reset                  |

| VDD         | 4                       |                | Power                         |

| VSS         | 4                       |                | Ground                        |

| SCAN_OUT    | 1                       | Output(4ma)    | Scan Data Out                 |

| SCAN_IN     | 1                       | Input          | Scan Data In                  |

| TM_OE⁺      | 1                       | Input          | Test Mode/Output Enable       |

| Pinout Summary: | 107 | Signal I/O        |

|-----------------|-----|-------------------|

|                 | 4   | VDD               |

|                 | 4   | VSS               |

|                 |     |                   |

|                 | 115 | <b>Total Pins</b> |

# FUNCTIONAL DESCRIPTION

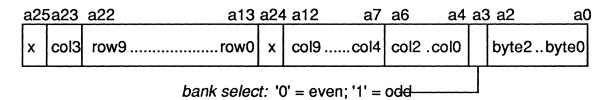

The DRAMC is initiated by MREQ\* signal being active for a cycle. At which time if the DRAMC is not busy doing either a memory operation or refreshing the DRAMs a new memory operation is started on the DRAMs. Depending on the information on the MEM\_SIZE and INTLVD pins, the address on the LA<25:0> are muxed onto MAn<10:0> as row and column addresses at the appropriate time intervals. Again one address bit is used to select the bank. The address muxing is as shown below

# Interleaved memory mapping:

1 MegaByte SIMM

# 4 MegaByte SIMM

| a25  | a23                                 | a13   | 3a24  | a12  | a7   | a6   | a4 a | a3 a | a2     | a0    |

|------|-------------------------------------|-------|-------|------|------|------|------|------|--------|-------|

| col3 | row10                               | .row0 | col10 | col9 | col4 | col2 | col0 | 1    | oyte2. | byte0 |

|      | hank select: '0' - over: '1' - odd- |       |       |      |      |      |      |      |        |       |

bank select: '0' = even; '1' = odd-

# Non-Interleaved memory mapping:

# 1 MegaByte SIMM

| a25 | a23 | 3a22 | a13  | a24 | l a12 | a3    | a2     | a0     |

|-----|-----|------|------|-----|-------|-------|--------|--------|

| x   |     | row9 | row0 | x   | col9  | .col0 | byte2. | .byte0 |

|     | Τ   |      |      |     |       |       |        |        |

*bank select:* '0' = lower; '1' = upper

## 4 MegaByte SIMM

| <u>a2</u> | 5a23                                         | a13  | a24   | a12  | a3   | a2       | a0  |  |

|-----------|----------------------------------------------|------|-------|------|------|----------|-----|--|

|           | row10                                        | row0 | col10 | col9 | col0 | byte2byt | te0 |  |

|           | <i>bank select:</i> '0' = lower: '1' = upper |      |       |      |      |          |     |  |

#### CAS WIDTH SELECT:

The DRAMC is optimized for system clock speeds of 25Mhz to 40 MHz and DRAM access times of 100 ns or better for the fast page mode operation. The deafult count for RAS\_to\_CAS delay,*viz* RCD is 2 cycles and the default CAS\* cycle time is 1 cycle. However additional cycles can be added by setting the SPDSEL0 and SPDSEL1 pins to appropriate levels as shown below.

| spdsel1 | spdsel0 | CAS* | RCD |

|---------|---------|------|-----|

| 0       | 0       |      |     |

| 0       | 1       |      | +1  |

| 1       | 0       |      | +1  |

| 1       | 1       | +1   | +1  |

### TRANSACTION SIZE:

The SIZE<2:0> lines carry the encoded version of the transaction size as shown in the table below.

| SIZE<2:0> | Transaction |

|-----------|-------------|

| 000       | Byte        |

| 001       | 2 Bytes     |

| 010       | 4 Bytes     |

| 011       | 8 Bytes     |

| 100       | 16 Bytes    |

| 101       | 32 Bytes    |

| 110       | 64 Bytes    |

| 111       | 128 Bytes   |

**MBus DRAM Controller Specs**

# TYPICAL MEMORY ORGANIZATION

#### CLK : MAS\* ADDRO ADDRI MAO : D0 D1 : LMA OLD MEM ADDR MEM ADDRO VALID MEM ADDR1 VALID : MREQ\* : : : MRDY\* • : : RAS\* : CAS\* CMRDY\* CBUSY ; ÷ ; : MD<63.0> STALE DATA ; ÷ DO D1

#### Typical M2M and DRAMC Interface Timing

| /tmp/STATUS                                                                                                                   | Tue Feb 26 19:18:15 1991       | 1                            |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------|--|--|--|--|

| /s/users/sparc/breeze/at/STATUS                                                                                               |                                |                              |  |  |  |  |

| status of M2SX chip:                                                                                                          |                                |                              |  |  |  |  |

| DESIGN: comple                                                                                                                | ete                            |                              |  |  |  |  |

| SIMULATION: test suite in /s/users/sparc/breeze/at/{main.v,test.v}<br>additional testing which could be done: half speed mode |                                |                              |  |  |  |  |

| BUGS: none out                                                                                                                | tstanding                      |                              |  |  |  |  |

| SYNOPSYS: map                                                                                                                 | ped to att (13571 cells, minim | num cycle time 16.48 ns),vti |  |  |  |  |

LOCATIONS of files:

verilog hdl description of chip: /s/users/sparc/breeze/at/synopsys/pure\_hdl verilog library: /tools/lib/model/hdl synopsys environment : /s/users/sparc/breeze/at/synopsys simulation environment : /s/users/sparc/breeze/at

status of AT subsection:

DESIGN: complete

SIMULATION: test suite in /s/users/sparc/breeze/at/test.v additional testing which could be done: refresh,dma, off-board master

BUGS: none outstanding

LOCATIONS of files:

```

drawings:/s/users/sparc/breeze/at/at

simulation environment:/s/users/sparc/breeze/at

verilog libraries: /tools/lib/model

/tools/lib/lai_vlog

/tools/lib/v

/tools/lib/v

/tools/lib/oki

/s/users/sparc/breeze/v/breezeCustom.v

/s/users/sparc/breeze/v/breezeLaiInt.v

/s/users/sparc/breeze/at/synopsys/pure hdl

```

.

# M2SX Chip Specification

# Rev 1.0

ebruary, 1991 1.020591 VIA Technologies, Inc. (408) 746-2200 860 East Arques Avenue Sunnyvale, CA 94086

#### INTRODUCTION

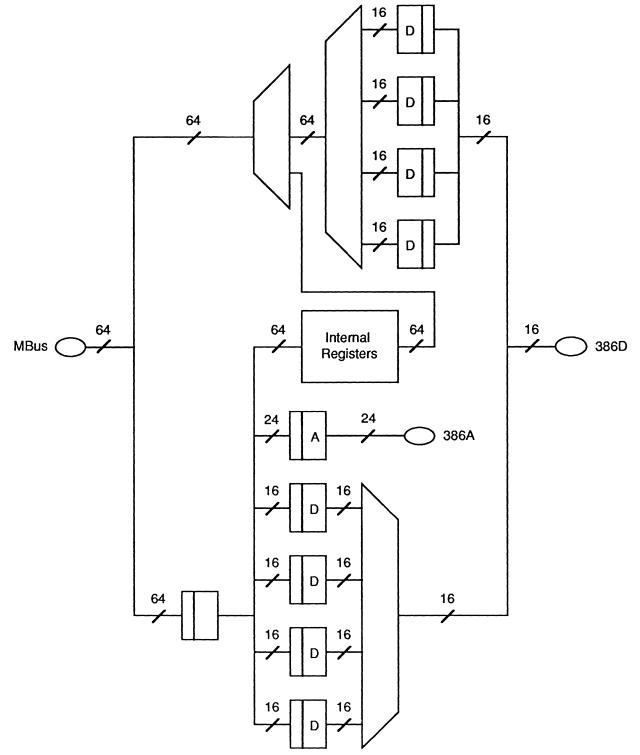

The M2SX chip provides a means by which Mbus slave accesses are transformed into accesses in 386SX protocol. That is, the Mbus interface of the chip acts as an Mbus slave, while the 386SX side acts as a master. Then, other logic can translate the 386 master cycles into bus cycles of a standard system bus, such as the AT.

Another function of the M2SX chip is to handle accesses to basic on-board devices, such as the boot prom and serial ports. These do not proceed as 386SX cycles, but do use the 386 address and data busses. No additional "glue" logic is necessary to connect these to the M2SX.

#### **MBUS SLAVE INTERFACE**

Mbus is a multiplexed address and data bus. During the address phase the Mbus master drives the physical address (PA), transaction type (TYPE) and size (SIZE), and other control signals. The M2SX chip compares PA<35:32> with its Mbus Slot Address, MSLOT, to determine if whether it is the target of the transaction. MSLOT is a field in its internal Status/Control Register. The internal registers themselves are addressed when PA<35:28>=FF hex and PA<27:24> equals the value on the ID<3:0> inputs. Finally, physical addresses of FF0xxxxx will result in boot PROM accesses. This address comparison is summarized below:

| if $PA<35:0> = FFnxxxx00$ , where $n = ID<3:0>$ | -> Internal Registers        |

|-------------------------------------------------|------------------------------|

| else if PA<35:0> = FF0xxxxx                     | -> Boot Prom space           |

| else if PA<35:32> = MSLOT<3:0>                  | -> on-board I/O and AT space |

| offset(bytes) | description             | access type | size(bits) |

|---------------|-------------------------|-------------|------------|

| 0             | Bus Error Register      | Read        | 64         |

| 8             | Status/Control Register | read/write  | 32         |

| C             | Mbus Port Register      | read        | 32         |

| 10            | Latency Register        | read/write  | 64         |

| 18            | Recovery Register       | read/write  | 64         |

## **INTERNAL REGISTERS**

|    |    | Mbus | addres | s bit p | attern |    |    |                                       |

|----|----|------|--------|---------|--------|----|----|---------------------------------------|

| 31 | 30 | 29   | 28     | 27      | 26     | 25 | 24 |                                       |

| 0  | 0  | 0    | 1      | х       | х      | х  | 1  | -> AT memory space                    |

| 0  | 0  | 0    | 1      | х       | Х      | Х  | 0  | -> AT I/O space                       |

| 0  | 0  | 0    | 0      | x       | 0      | 0  | 0  | -> on-board I/O device #0 (boot prom) |

| 0  | 0  | 0    | 0      | х       | 0      | 0  | 1  | -> on-board I/O device #1             |

| 0  | 0  | 0    | 0      | х       | 0      | 1  | 0  | -> on-board I/O device #2             |

| 0  | 0  | 0    | 0      | х       | 0      | 1  | 1  | -> on-board I/O device #3             |

| 0  | 0  | 0    | 0      | х       | 1      | 0  | 0  | -> on-board I/O device #4             |

| 0  | 0  | 0    | 0      | х       | 1      | 0  | 1  | -> on-board I/O device #5             |

| 0  | 0  | 0    | 0      | x       | 1      | 1  | 0  | -> on-board I/O device #6             |

| 0  | 0  | 0    | 0      | x       | 1      | 1  | 1  | -> on-board I/O device #7             |

#### AT/ ON BOARD IO ADDRESS MAPPING

The M2SX chip will accept two transaction types: Read (TYPE<3:0>=0001) and Write (TYPE<3:0>=0000). All other transaction types are not supported.

| TYPE<3:0> | Transaction Type |

|-----------|------------------|

| 0000      | Write            |

| 0001      | Read             |

| 001x      | Illegal          |

| 01xx      | Illegal          |

| 1xxx      | Illegal          |

#### **Transaction Sizes Supported**

For on-board I/O and AT accesses, all Mbus size transactions are supported, that is byte, halfword, word, doubleword, and bursts of 16,32,64 and 128 bytes.

For the internal registers, byte, halfword, word and doubleword reads are supported. For writes, only word and doubleword sizes are allowed. Unsupported size transactions will result in a bus error acknowledgement being given. This is summarized in the following table:

#### Allowed internal register accesses

| size   | typ     | e       |

|--------|---------|---------|

|        | read    | write   |

| byte   | ОК      | illegal |

| short  | OK      | illegal |

| word   | OK      | OK      |

| double | OK      | OK      |

| burst  | illegal | illegal |

There are three transaction status bits, MERR\*, MRDY\*, and MRTY\*, that the M2SX chip uses to send an acknowledgment back to the Mbus master for a transaction it receives. The transaction status is shown as follows:

| MERR* | MRDY* | MRTY* | Acknowledgment       |

|-------|-------|-------|----------------------|

| 1     | 1     | 1     | Idle Cycle           |

| 1     | 1     | 0     | Relinquish and Retry |

| 1     | 0     | 1     | Valid Data Transfer  |

| 0     | 1     | 1     | Error1 => Bus Error  |

Valid Data Transfer. On Mbus Write transactions, the M2SX chip will assert MRDY\* when it senses the 386 READY\* signal becoming active, which signals that the 386 peripheral has accepted the write data. For Mbus Read transactions, MRDY\* is asserted when the read data is driven by the M2SX onto Mbus.

Bus Error Acknowledgment. The M2SX will assert MERR\* when it detects an unsupported operation for an Mbus transaction which has targetted it. An unsupported operation is defined as one for which the TYPE and/or SIZE is not supported, as defined above.

Relinquish and Retry Acknowledgment. The M2SX chip will give a Relinquish and Retry acknowledgment (R&R) if it is the target of an Mbus transaction, but the 386 bus is not immediately available because another master is controlling from the 386 side.

#### MBUS PORT REGISTER

The Mbus Port Register (MPR) is a read only register which contains the Implementation Number and Version Number of the M2SX Chip. It is addressed when PA<35:0>=FFnxxxxC where n=ID<3:0>. The format of the MPR is shown below:

| 16       | 8    | 4    | 4     |

|----------|------|------|-------|

| Reserved | MDEV | MREV | MVEND |

| 31 16    | 15 8 | 7 4  | 3 0   |

MDEV: Mbus Device Number. This field contains a unique number which identifies the device as a VIA M2SX Chip.

MREV: Mbus Revision Number. This field contains the revision number for the VIA M2SX Chip.

MVEND: Mbus Vendor Number. This field contains the vendor number for VIA.

#### STATUS/CONTROL REGISTER

The Status/Control Register (SCR) is addressed when PA<35:0>=FFnxxxx8 where n=ID<3:0>. The format of the SCR is shown below:

| 27       | 1   | 4     |

|----------|-----|-------|

| Reserved | ALT | MSLOT |

| 31       | 54  | 3 0   |

MSLOT: Mbus Slot Address (read/write, bits 3:0). This field contains a unique number among all Mbus modules which reside on Mbus. MSLOT is compared with PA<35:32> to determine whether this chip is the target of the transaction. This register should be configured by the Operating System after it has read all of the MPRs for the modules which reside on Mbus. The Mslot value is set to value 0 upon reset.

ALT\_MASTER (read only, bit 4). This status bit being high indicates that another bus master has control of the 386SX bus.

#### **BUS ERROR REGISTER**

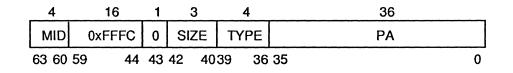

The Bus Error Register is a read only register which contains information about the circumstances that caused the M2SX Chip to assert MERR\*. It is addressed when PA<35:0>= FFnxxxx0 where n=MID<3:0>. MERR\* is asserted when the Mbus Slave interface face receives a transaction which it does not support. The physical address, size, type, and acknowledgment for the transaction is saved in the Bus Error Register. The format of the Bus Error Register is shown below:

MID: Module Identifier. This field contains a copy of the Mbus Module Identifier of the Mbus master which was the source of the transaction which led to the bus error.

OCC: Error Occurred. This bit = 1 if a bus error has occurred since the Bus Error register was last read. It is cleared upon reading this register. OCC is initially = 0 upon system reset. If a bus error occurs, the bit is set and the register's contents are updated. The Bus Error Register's contents are then held until it is read by the CPU, at which point it is re-armed again.

| 4     | 20       | 1     | 3     | 4     | 36   |

|-------|----------|-------|-------|-------|------|

| MID   | Reserved | 000   | SIZE  | TYPE  | PA   |

| 63 60 | 59       | 44 43 | 42 40 | 39 36 | 35 0 |

SIZE: Mbus Transaction Size. This field contains a copy of the Mbus transaction size.

TYPE: Mbus Transaction Type. This field contains a copy of the Mbus transaction type.

PA: Physical Address. This field contains a copy of the physical address for the Mbus transaction.

#### LATENCY REGISTER

This 64-bit register is used with on-board I/O (OBIO) accesses. There is an eight-bit value for each of the eight possible OBIO devices. This value is programmable by the CPU and has a default value of 0xA. The ordering is such that the value for OBIO device 0 (boot prom) comes from register bits [63:56], while the value for device 7 comes from register bits [7:0]. The latency value set for a device determines the number of additional clock cycles that the read or write strobe is active for an I/O access to that device. The total number can vary between 1 and 256 clock cycles. For example, consider a system with a 25ns Mbus cycle time, and a read of the boot prom in which the latency register bits[63:56] = 0x8. The read strobe will be active for (1+8)x25ns=225ns.

| <br>LAT0 | LAT1 | LAT2 | LAT3 | LAT4 | LAT5 | LAT6 | LAT7 |

|----------|------|------|------|------|------|------|------|

| 63       |      |      |      |      |      |      | 0    |

#### **RECOVERY REGISTER**

This 64-bit register is also used with on-board I/O (OBIO) accesses. There is an eight-bit value for each of the eight possible OBIO devices. This value is programmable by the CPU and has a default value of 0x1. The ordering is such that the value for OBIO device 0 (boot prom) comes from register bits [63:56], while the value for device 7 comes from register bits [7:0]. The recovery value set for a device determines the number of additional clock cycles between the time that the chip select becomes active for that device and the time that the read or write strobe becomes active. This serves two functions: 1) to ensure enough address set-up time before the read or write strobe becomes active and 2) to provide enough recovery time (time between successive read or write strobes to the same device.) The total number can vary between 1 and 256 clock cycles. For example, consider a system with a 25ns Mbus cycle time, and a write of the serial port in which the latency register bits = 0x1f. The recovery register will provide (1+ 31)x25ns=800ns between when the chip select for the serial port becomes active.

| [ | REC0 | REC1 | REC2 | REC3 | REC4 | REC5 | REC6 | REC7 |

|---|------|------|------|------|------|------|------|------|

| ( | 63   |      |      |      |      |      |      | 0    |

#### 386 memory and I/O spaces

The 386 processor has a concept of memory and I/O address spaces. The cycles are the same except for the state of the MEMIO bit, which is high for memory cycles and low for I/O cycles. This function is simulated by the M2SX chip by making the state of PA<24> during each 386 access determine whether a memory or I/O cycle is performed. Setting PA<24> = 1 causes a memory access, PA<24> = 0 causes an I/O access.

## "BIG-ENDIAN" VS. "LITTLE-ENDIAN" CONVERSION

The Mbus and the 386 are opposites with respect to the "big-endian" vs. "little-endian" convention. Because of this, for byte accesses, the least significant bit of the Mbus address is complemented before being put out as a 386 address.

| Low-order addresses formed by 386sx sequencer |                                |                       |  |  |  |

|-----------------------------------------------|--------------------------------|-----------------------|--|--|--|

| Mbus cycle size                               | initial byte address from Mbus | byte address sequence |  |  |  |

| doubleword                                    | 0                              | 0,2,4,6               |  |  |  |

| word                                          | 0                              | 0,2                   |  |  |  |

| word                                          | 4                              | 4,6                   |  |  |  |

| halfword                                      | 0                              | 0                     |  |  |  |

| halfword                                      | 2                              | 2                     |  |  |  |

| halfword                                      | 4                              | 4                     |  |  |  |

| halfword                                      | 6                              | 6                     |  |  |  |

| byte                                          | 0                              | 1                     |  |  |  |

| byte                                          | 1                              | 0                     |  |  |  |

| byte                                          | 2                              | 3                     |  |  |  |

| byte                                          | 3                              | 2                     |  |  |  |

| byte                                          | 4                              | 5                     |  |  |  |

| byte                                          | 5                              | 4                     |  |  |  |

| byte                                          | 6                              | 7                     |  |  |  |

| byte                                          | 7                              | 6                     |  |  |  |

## M2SX PINOUT

| Signal Name   | # Pins | I/O          | Signal Description        |

|---------------|--------|--------------|---------------------------|

| MAD<63:0>     | 64     | I/O (4ma)    | Mbus Address/Control/Data |

| MAS*          | 1      | Input        | Mbus Address Strobe       |

| MERR*         | 1      | Output (4ma) | Mbus Error Indicator      |

| MRDY*         | 1      | Output (4ma) | Mbus Data Ready Indicator |

| MRTY*         | 1      | Output (4ma) | Mbus Retry Indicator      |

| ID<3:0>       | 4      | Input        | Mbus Module Identifier    |

| MCLK          | 1      | Input        | Mbus Clock                |

| RSTIN*        | 1      | Input        | Mbus Reset                |

| A<23:0>       | 24     | Output (4ma) | 386SX address             |

| D<15:0>       | 16     | I/O (4ma)    | 386SX Data                |

| ADS*          | 1      | Output (4ma) | 386SX Address Strobe      |

| READY*        | 1      | Input        | 386SX Bus Ready           |

| WR            | 1      | Output (4ma) | 386SX Write               |

| MIO           | 1      | Output (4ma) | 386SX Memory Cycle        |

| BHE*          | 1      | Output (4ma) | 386SX Byte High Enable    |

| CPUCLK        | 1      | Input        | 386SX Processor Clock     |

| CLK2/2        | 1      | Input        | Slow mode clock           |

| HOLD          | 1      | Input        | 386SX Hold Request        |

| HLDA*         | 1      | Output (4ma) | 386SX Hold Acknowledge    |

| IOR*          | 1      | Input        | AT I/O Read Strobe        |

| MEMR*         | 1      | Input        | AT Memory Read Strobe     |

| SCAN_OUT      | 1      | Output (4ma) | Scan Data Out             |

| SCAN_IN       | 1      | Input        | Scan Data In              |

| TM_OE*        | 1      | Input        | Test Mode/Output Enable   |

| OBIO_WR*      | 1      | Output (4ma) | On-board I/O write strobe |

| OBIO_RD*      | 1      | Output (4ma) | On-board I/O read strobe  |

| OBIO_CS<7:0>* | 8      | Output (4ma) | On-board I/O chip selects |

Total 138 Signal pins.

#### **CLOCKING CONSIDERATIONS**

The Mbus may operate at clock rates of as high as 40Mhz, while most 386 system logic, such as an AT chipset, has a maximum of from 25 to 33 Mhz. If the Mbus is running at a clock rate higher than a particular set of 386 system logic can accomodate, there is provision for running the 386 system logic at half the Mbus clock rate, and having the M2SX chip automatically synchronize to the slower speed by means of the CLK2/2 synchronizing input.

## ALTERNATE BUS MASTERS

The M2SX has provision for allowing alternate bus masters on the 386sx bus. If the 386SX bus request signal (HOLD) is asserted, the M2SX will assert the bus acknowledge (HLDA) and go into a state in which it tristates its address data and control lines, until HOLD is negated. During that time, internal accesses to the M2SX can proceed, but onboard I/O accesses by the CPU will generally result in a retry acknowledgement on the Mbus. The exception is the case of a boot prom access to space 0xFF0XXXXX, in which the M2SX will wait until the alternate bus master cycle is over, then proceed with the cycle normally.

#### SIGNAL DESCRIPTIONS

MAD<63:0>: Mbus Multiplexed Address and Data.

MAS\*: Mbus Address Strobe. This signal goes active low to indicate the portion of the address cycle when the MAD bus contains address information.

MERR\*. This signal is asserted when the M2SX detects an error condition, such as an unsupported operation.

MRDY\*. This signal is asserted by the M2SX to indicate the successful completion of a transfer.

MRTY\*. This signal is asserted by the M2SX to indicate that the requested operation cannot be completed now, and should be retried later.

ID<3:0>. These pins define a unique ID for each Mbus module in the system. In the case of the M2SX they determine the Mbus space in which its configuration registers lie.

MCLK: Mbus System Clock.

RSTIN\*: Mbus System Reset.

A[23:0]: Address Bus for the 386SX.

D[15:0]: Data Bus for the 386SX.

ADS\*. This signal from the M2SX, when active low, is used by 386SX system logic to store the 386 address A[23:0], and signals 386 system logic that a bus cycle is beginning.

READY\*. This signal from 386 system logic, when active low, indicates to the M2SX chip that a 386 cycle is complete.

WR. 386 bus control signal which when high indicates a write transfer.

MIO. 386 bus control signal which when high indicates a memory cycle.

BHE\*. 386 bus control signal which when active low, indicates that valid data is on bits 15:8 of D(15:0).

CPUCLK: 386 Processor Clock. Normally = MCLK/2, except if chip is configured for slow mode, in which case it = MCLK/4.

CLK2/2: Slow Mode Clock. Normally =MCLK. It could be the case MCLK is running at a sufficiently high clock rate such that the 386 system support logic external to theM2SX cannot use MCLK directly as its clock input, and must divide MCLK down by 2. In that case, connecting this pin to MCLK/2 will make the M2SX automatically synchronize the signals it sends to the 386 support logic, running at the slower speed.

HOLD. This signal is asserted by the 386 system support logic when it desires to take control of the 386SX bus.

HLDA. This signal is asserted by the M2SX to indicate to the 386 system support logic that it has granted the 386 bus to it.

IOR\*. This signal 's positive-going edge clocks data into the M2SX on AT I/O reads.

MEMR\*. This signal 's positive-going edge clocks data into the M2SX on AT Memory reads.

OBIO\_WR\*. Write strobe for on-board I/O accesses.

OBIO\_RD\*. Read strobe for on-board I/O accesses.

OBIO\_CS<7:0>\*. Chip selects for on-board I/O accesses.

SCAN\_OUT

SCAN\_IN

SCAN\_MODE

## M2SX DATA PATH

/s/users/sparc/breeze/sbus/STATUS

status of SBus subsection:

DESIGN: complete

SIMULATION: test suite in /s/users/sparc/breeze/v

m2s.diag contains a concatenation of m2s.diagX individual

diagnostics for the Mbus to SBus interface logic.

tlb.diag contains a concatenation of tlb.diagX individual

diagnostics for the SBus Controller and its I/O MMU.

all.diag contains a concatenation of m2s.diag and tlb.diag.

Simulation environment includes the DMA subsection.

See /s/users/sparc/breeze/v/verilog.cmd for verilog

simulation files.

BUGS: none outstanding

LOCATIONS of files: drawings: /s/users/sparc/breeze/sbus/sbus simulation environment : see above verilog libraries: see /s/users/sparc/breeze/v/verilog.cmd

status of M2SCHIP chip:

DESIGN: complete

SIMULATION: test suite in /s/users/sparc/breeze/v

m2s.diag contains a concatenation of m2s.diagX individual

diagnostics for the Mbus to SBus interface logic.

tlb.diag contains a concatenation of tlb.diagX individual

diagnostics for the SBus Controller and its I/O MMU.

all.diag contains a concatenation of m2s.diag and tlb.diag.

Simulation environment includes the SBus subsection

with the DMA subsection mapped to an SBus Driver.

See /s/users/sparc/breeze/v/verilog.cmd for verilog

simulation files.

BUGS: none outstanding

SYNOPSYS: not mapped at all

LOCATIONS of files:

verilog hdl description of chip: /s/users/sparc/breeze/sbus/v/m2sChip.v /s/users/sparc/breeze/sbus/v/m2s.v /s/users/sparc/breeze/sbus/v/sbusController.v /s/users/sparc/breeze/sbus/v/tlbs.v verilog library: /tools/lib/model/hdl synopsys environment : none simulation environment : /s/users/sparc/breeze/v

# M2S Chip Specification

## Rev 1.0

nuary, 1991 3.020891 VIA Technologies, Inc. (408) 746-2200 860 East Arques Avenue Sunnyvale, CA 94086

## M2S PINOUT

| Signal Name     | # Pins | Input/Output       | Signal Description                  |

|-----------------|--------|--------------------|-------------------------------------|

| MAD<31:0>       | 32     | Input/Output (4ma) | Mbus Address/Control/Data           |

| MAS*            | 1      | Input/Output (8ma) | Mbus Address Strobe                 |

| MERR*           | 1      | Input/Output (8ma) | Mbus Error Indicator                |

| MRDY*           | 1      | Input/Output (8ma) | Mbus Data Ready Indicator           |

| MRTY*           | 1      | Input/Output (8ma) | Mbus Retry Indicator                |

| MBR*            | 1      | Output (4ma)       | Mbus Request                        |

| MBG*            | 1      | Input              | Mbus Grant                          |

| MBB*            | 1      | Input/Output (8ma) | Mbus Busy Indicator                 |

| MID<3:0>        | 4      | Input              | Mbus Module Identifier              |

| MCLK            | 1      | Input              | Mbus Clock                          |

| SBR<3:1>*       | 3      | Input              | SBus Request                        |

| SBG<3:1>*       | 3      | Output (4ma)       | SBus Grant                          |

| D<31:0>         | 32     | Input/Output (4ma) | SBus Data                           |

| RD              | 1      | Input/Output (4ma) | SBus Transfer Direction             |

| SIZ<2:0>        | 3      | Input/Output (4ma) | SBus Transfer Size                  |

| PA<27:0>        | 28     | Output (4ma)       | SBus Physical Address               |

| AS*             | 1      | Output (4ma)       | SBus Address Strobe                 |