# TOSHIBA AMERICA, INC.

# MICROPROCESSORS VOL. 2-PERIPHERALS

# MICROPROCESSORS VOL. 2-PERIPHERALS

May 1987

# **TABLE OF CONTENTS**

# **Micro-Computer Peripheral LSI**

| TC8250P/AP Real Time Clock                       | 33  |

|--------------------------------------------------|-----|

| TC8505AP/F CRT Display Controller                | 53  |

| TMPZ80C47P Hard Disk Controller                  |     |

| TC8565P/F Floppy Disk Controller                 | 113 |

| TC8576AF Centronics Compatible Parallel I/O      | 159 |

| TC8577AP Centronics Compatible Parallel Output   | 159 |

| TC8578AP Centronics Compatible Parallel Input    | 159 |

| TC8600F Floppy Disk Mechanism Controller (5¼")   | 197 |

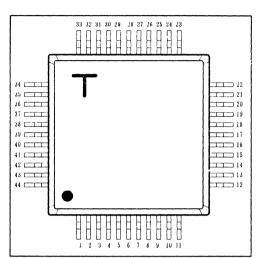

| TC8602F Floppy Disk Mechanism Controller (31/2") | 226 |

| T7779 CRT/LCD Controller                         | 251 |

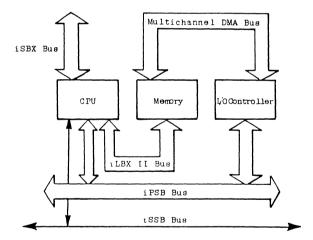

# **Multibus II Interface Devices**

| Multibus II                                        | 301 |

|----------------------------------------------------|-----|

| BAC 84110 Multibus II Bus Arbiter/Controller       | 449 |

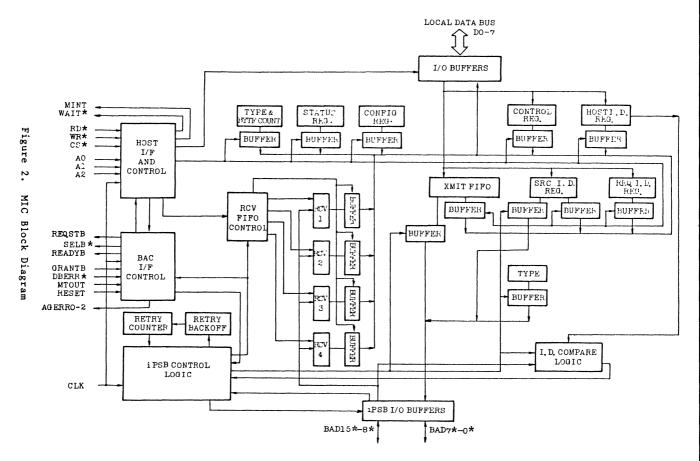

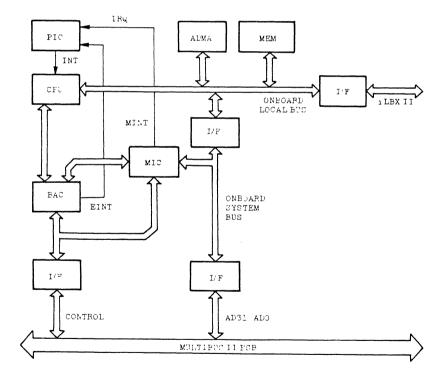

| MIC 84120 Multibus II Message Interrupt Controller |     |

# **Speech Device**

| 65 |

|----|

| -  |

| 55 |

| 65 |

| 3  |

| 5  |

| 33 |

| 39 |

| 27 |

|    |

— ii —

1

# Micro-Computer Peripheral LSI

χų,

# TOSHIBA MICROCOMPUTER PERIPHERAL LSI

|                                       |                  |         |                                           |                        |               | N· 1986                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------|------------------|---------|-------------------------------------------|------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре                                  | Parts name       | Package | Function.                                 | TD                     | ES            | MP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RTC :                                 |                  | i .     | Real Time Clock                           |                        | 1             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                                     |                  | 1       | 4bit MPX data bus                         |                        | 1             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                                     |                  |         | Counts second,minute,hour,day,            |                        | 1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                                     |                  | ł       | month,year,day of the week.               |                        | 1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L                                     |                  | L       | Low power consumption.                    |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

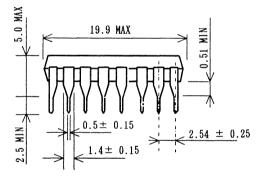

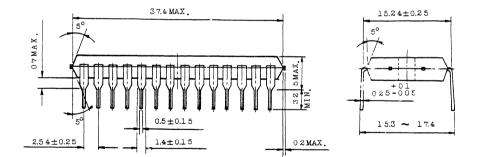

| 1                                     | TC8250P          | DIP16   | Battery charge control                    | OK                     | - <u>OK</u> - | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| · · · · · · · · · · · · · · · · · · · | TC8250AP         | DIP16   |                                           | OK                     | OK            | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

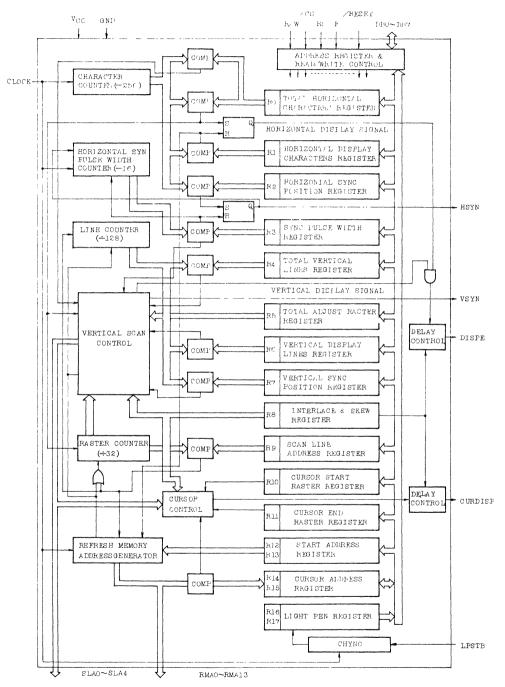

| CRTC                                  |                  |         | CRT Controller LSI                        |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ~                                     |                  | A       | MC68B45 function compatible CMOS          |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

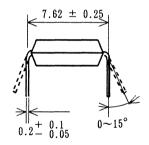

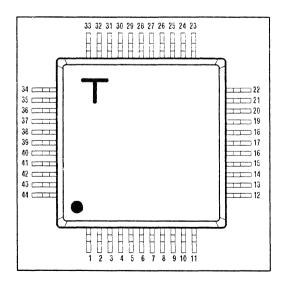

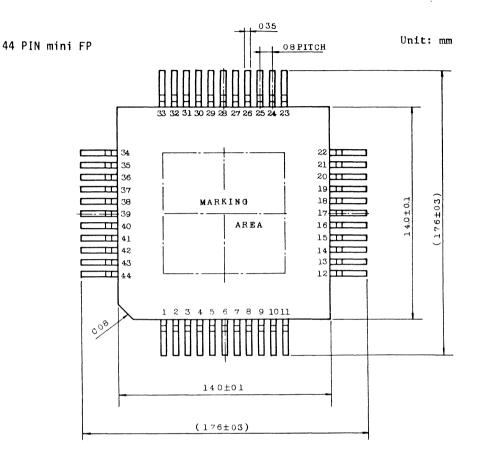

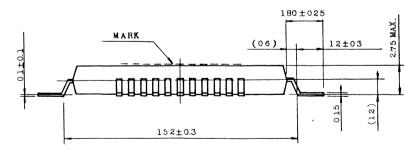

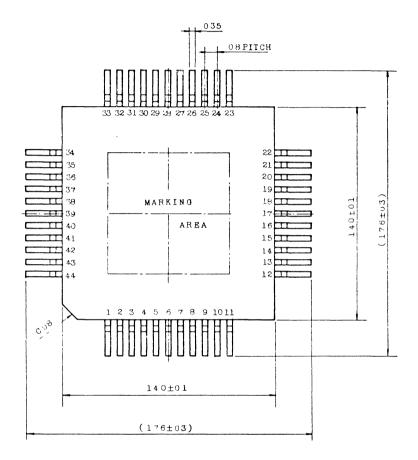

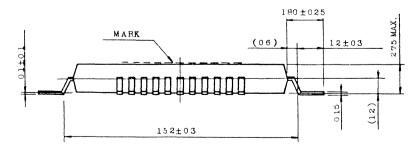

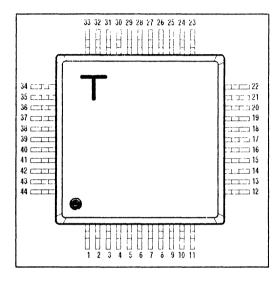

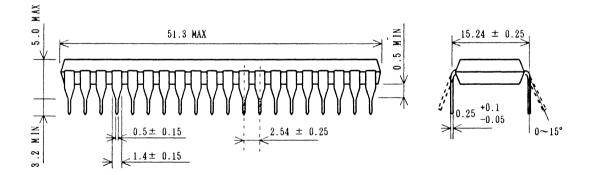

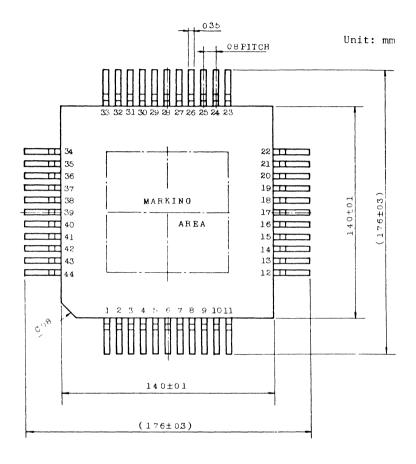

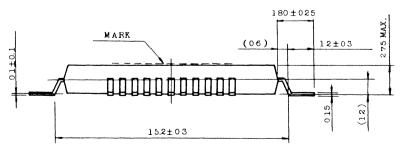

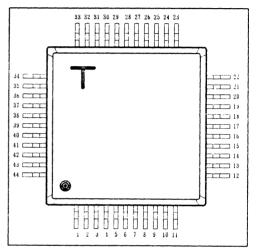

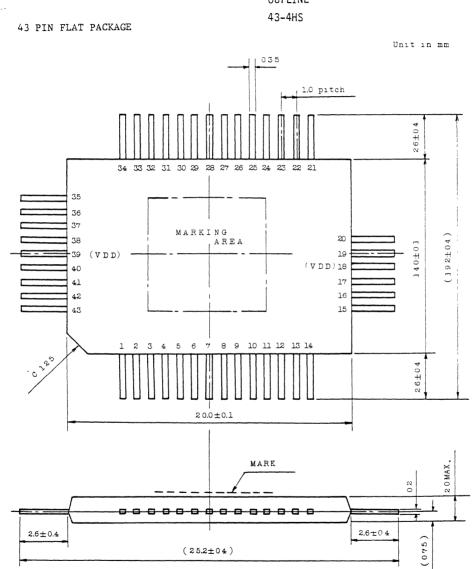

| L                                     | TC8505AF         | MFP44   | yersion. fmax 6MHz.                       | OK                     | OK            | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

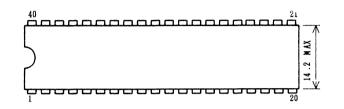

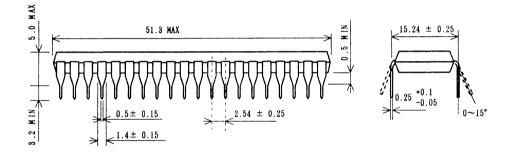

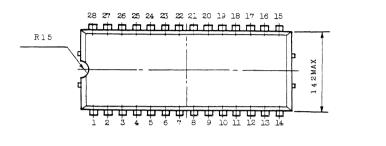

| i                                     | TC8505AP         | DIP40   |                                           | OK                     | OK            | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

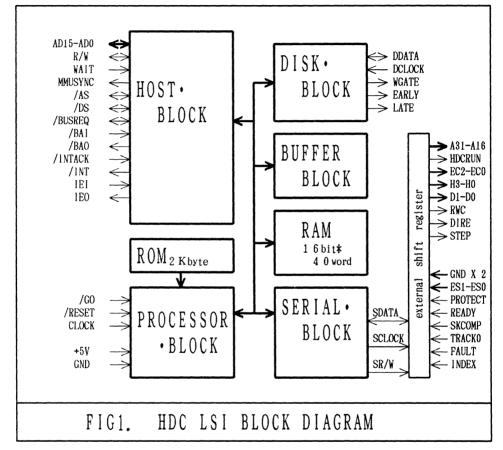

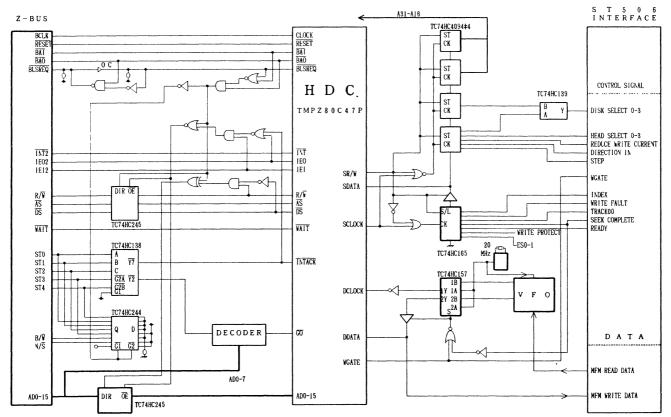

| HDC                                   |                  | ŀ       | Hard Disk Controller                      |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| i                                     |                  | i       | Z8000 CPU bus compatible                  |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                                     |                  | ł       | ST506 type disk interface                 |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

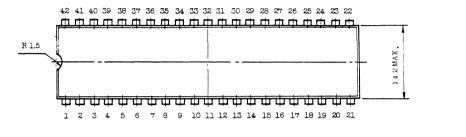

| 1                                     | TMPZ80C47P       | DIP48   | 10Mbps disk I/0 transfer                  | OK                     | OK            | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| i                                     | <u>(T6647)</u>   | L       |                                           |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

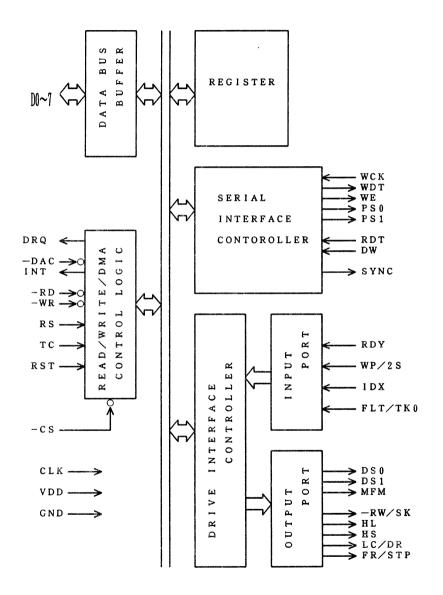

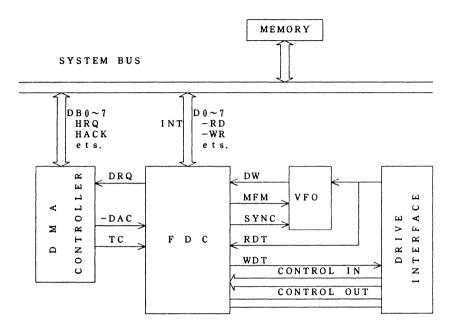

| FDC                                   |                  |         | Floppy Disk Controller                    |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| l<br>L                                |                  |         | uPD765AC function compatible CMOS         |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

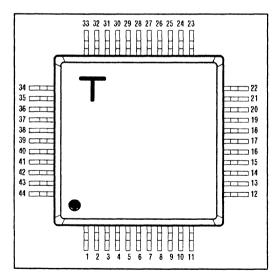

|                                       | TC8565F          | MFP44   | version                                   | warm needs warming and | OK            | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| l                                     | TC8565P          | DIP40   |                                           | OK                     | , OK          | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

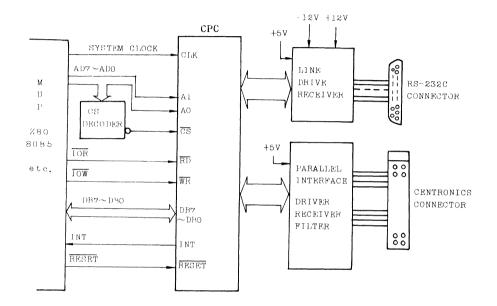

| CPC                                   |                  | i       | Combination Peripheral Controller         |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

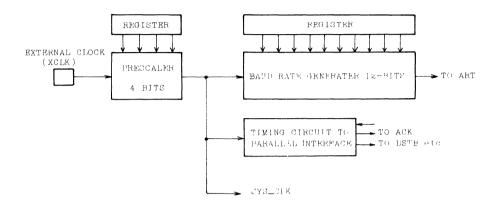

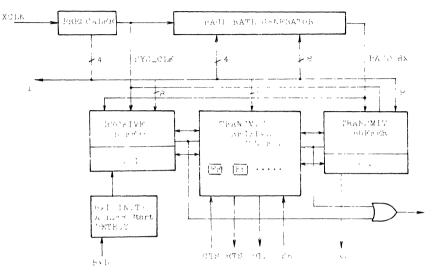

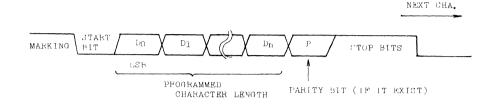

| 1                                     |                  |         | UART 1ch + Baud Generator +               |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ĺ                                     | 191 <sup>9</sup> | +       | Parallel Interface (8bit).                |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

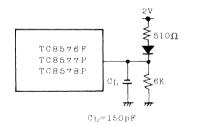

| 6<br>1                                | TC8576AF         | MFP44   | <u> UART + Parallel I/O Programmable.</u> | OK                     | ) OK          | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| l                                     | TC8577AP         | DIP40   | UART + Parallel Output.                   |                        | <u>I OK</u>   | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                       | TC8578AP         | DIP40   | UART + Parallel Input.                    | OK                     | OK            | <u>OK</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

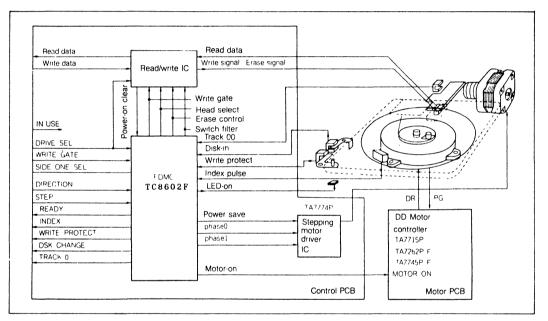

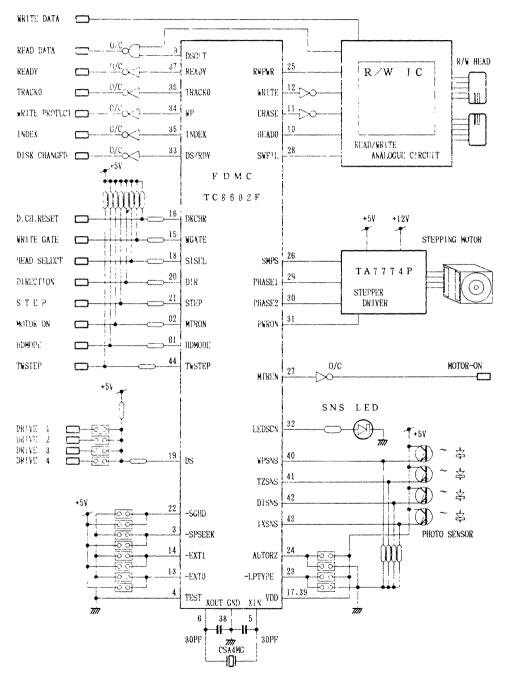

| FDMC                                  |                  |         | Floppy Disk Mechanism Controller          |                        |               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                       |                  | 4       | Customized 4bit CPU for floppy            |                        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| l                                     |                  | L       | disk drive control.                       |                        |               | . 1986-1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 1991 - 19 |

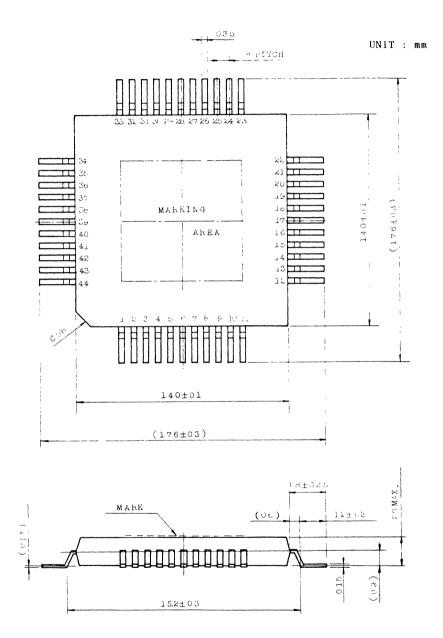

| i                                     | TC8600F          | MFP44   | <u>5.25 inch FDD</u> .                    | OK                     | <u>OK</u>     | OK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ĺ                                     | TC8601F          | MFP60   | 3.5 inch FDD with CMOS interface          | -                      | OK            | <u>86/1Q</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                       | TC8602F          | MFP44   | 3.5 inch FDD .                            | <u> </u>               | OK            | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |