INTEGRATED CIRCUIT TECHNICAL DATA

# MICROCOMPUTER DATA BOOK

2nd Edition

Mar., 1982

#### PREFACE

Since LSIs for the microcomputer manufactured first in Japan by Toshiba was put on the market in 1973, Toshiba has devoted efforts in strengthening its semiconductor devices for microcomputer. Toshiba has been developing various highly efficient and low power consumption type LSIs for microcomputers to more and more diversifying application fields, and supplying numerous kinds of new products to users.

This manual covers the technical description of LSIs for microcomputers supplied by Toshiba, including TLCS-43 Series (NMOS), TLCS-46A Series (CMOS) and TLCS-47 Series (NMOS and CMOS) 4-bit single chip microcomputer, TLCS-84 Series (NMOS and CMOS) 8-bit single chip microcomputer and TLCS-85A Family (NMOS) 8-bit microcomputer.

In addition to this manual, the technical description of the microcomputer development system is also available.

Further, examples of application circuits listed in this manual are only for reference in using the LSIs. Toshiba will not assume any responsibility for problem relative to patent rights which may be generated from use of the said application circuits.

## CONTENTS

**4BIT SINGLE CHIP MICROCOMPUTER**

## Page

| TLCS-43 (NMOS)                                                    |

|-------------------------------------------------------------------|

| • TMP4310AP/TMP4315BP/TMP4320AP/TMP4300C                          |

| • TMP4310APL/TMP4310APLL 82                                       |

| • TMP4321AP                                                       |

| • TMP4399C 93                                                     |

| 4BIT SINGLE CHIP MICROCOMPUTER                                    |

| TLCS-46A (CMOS)                                                   |

| • TCP4620AP/TCP4630AP                                             |

| • TCP4620AF/TCP4630AF                                             |

| • TCP4620BP                                                       |

| • TCP4621AP                                                       |

| • TCP4632BF                                                       |

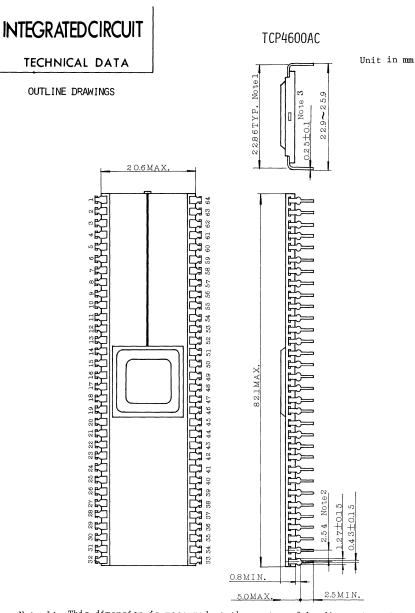

| • TCP4600AC                                                       |

| 4BIT SINGLE CHIP MICROCOMPUTER<br>TLCS-47 (NMOS/CMOS) PRELIMINARY |

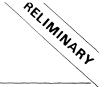

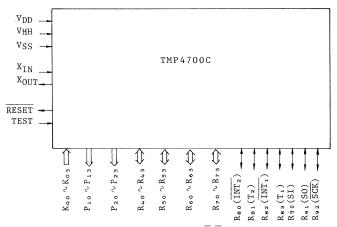

| • TMP4700C/TMP4720P/TMP4740P/ TMP499C (NMOS)                      |

| • TMP47C20P/TMP47C40P/TMP47C22F (CMOS)                            |

| / TMP47C41P/ TMP47C21P                                            |

| 8BIT SINGLE CHIP MICROCOMPUTER                                    |

| TLCS-84 (NMOS/CMOS)                                               |

| • TMP8048P/TMP8035P/TMP8048PI/TMP8035PI                           |

| • TMP8049P/TMP8049P-6/TMP8039P/TMP8039P-6                         |

| /TMP8049PI-6/TMP8039PI-6                                          |

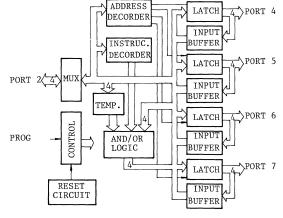

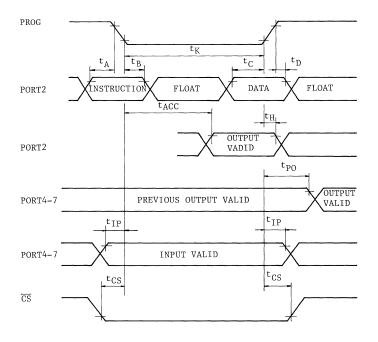

| • TMP8243P/TMP8243PI                                              |

| • TMP8022P                                                        |

| • TMP80C49-6/TMP80C39P-6 PRELIMINARY                              |

|                                                                   |

|                                                                   |

|                                                                   |

|                                                                   |

##

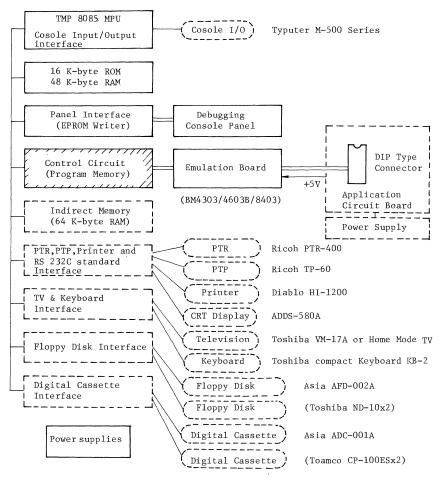

#### MICROCOMPUTER APPLICATION DEVELOPMENT TOOL .... 701

#### TLCS-43 (4 BIT SINGLE CHIP NMOS MICROCOMPUTER) TLCS-43 SERIES (NMOS)

| Device<br>Number | RAM     | ROM             | I/0              | Instruction<br>Cycle Time<br>(Min.) | Power Supply<br>Current<br>(Typ.) | Power<br>Supply | Operating<br>Temperature | Package<br>Type   | Alternate<br>Source |

|------------------|---------|-----------------|------------------|-------------------------------------|-----------------------------------|-----------------|--------------------------|-------------------|---------------------|

| TMP4300C         | 128 × 4 | Without<br>ROM  | 35 Lines         | 4 µs                                | 70 mA                             | 5V±10%          | -10°C ∿ 70°C             | Ceramic<br>64 pin |                     |

| TMP4399C         | 128 × 4 | Without<br>ROM  | 35 Lines         | 4 µs                                | 70 mA                             | 5V±10%          | -10°C∿70°C               | Ceramic<br>42 pin |                     |

| TMP4310AP        | 48 × 4  | 1024 × 8        | 22 Lines         | 4 µs                                | 40 mA                             | 5V±10%          | -10°C ∿ 70°C             | Plastic<br>28 pin |                     |

| TMP4315BP        | 64 × 4  | 1536 × 8        | 35 Lines         | 4 µs                                | 40 mA                             | 5V±10%          | -10°C∿70°C               | Plastic<br>42 pin | Toshiba<br>Original |

| TMP4320AP        | 128 × 4 | 2048 × 8        | 35 Lines         | . 4 µs                              | 40 mA                             | 5V±10%          | -10°C∿70°C               | Plastic<br>42 pin | Ū                   |

| TMP4321AP        | 128 × 4 | 2048 × 8        | 35 Lines         | 4 µs                                | 40 mA                             | 5V±10%          | -10°C ∿ 70°C             | Plastic<br>42 pin |                     |

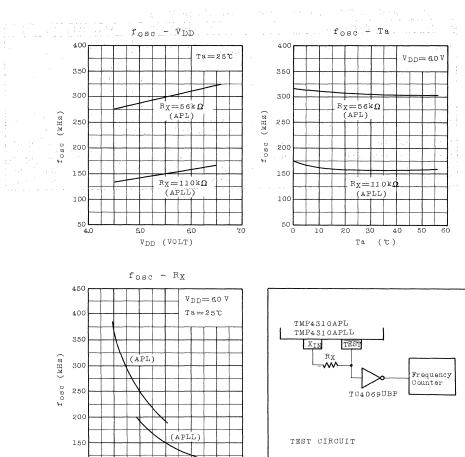

| TMP4310APL       | 1.9 1   | 10249           | 22 14            | 5 µs                                | 30 mA                             | 5.5V±10%        | 0°C∿55°C                 | Plastic           |                     |

| TMP4310APLL      |         | 48 × 4 1024 × 8 | 024 × 8 22 Lines | 10 µs                               | 15 mA                             | 5.5V±10%        | 0.04.55.0                | 28 pin            |                     |

# TLCS-46A (4 BIT SINGLE CHIP CMOS MICROCOMPUTER)

| Device<br>Number | RAM     | ROM            | I/0      | Instruction<br>Cycle Time<br>(Min.) | Power Supply<br>Current<br>(Typ.) | Power<br>Supply | Operating<br>Temperature | Package<br>Type             | Alternate<br>Source |

|------------------|---------|----------------|----------|-------------------------------------|-----------------------------------|-----------------|--------------------------|-----------------------------|---------------------|

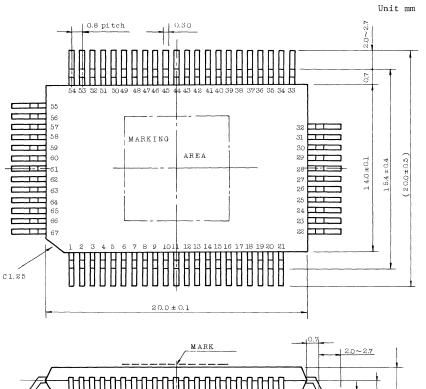

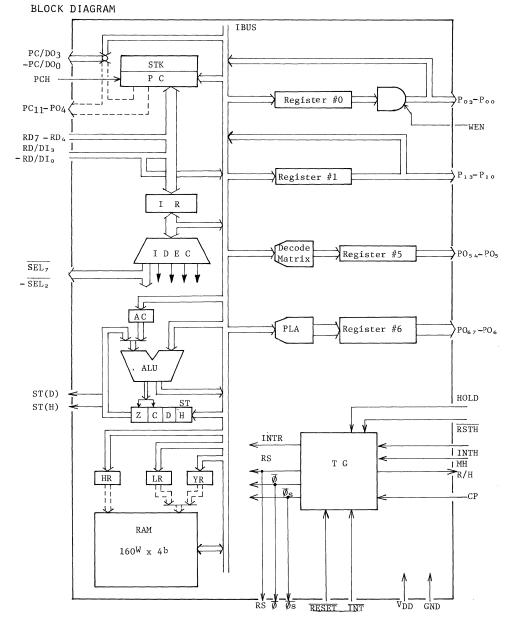

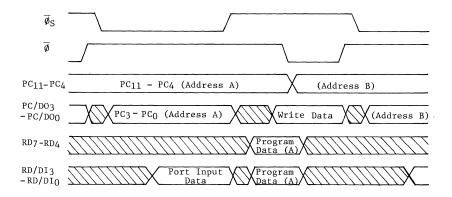

| TCP4600AC        | 160 × 4 | Without<br>ROM |          |                                     | 0.15 mA<br>at 100kHz              | $4 \sim 6V$     | -10°C∿70°C               | Ceramic<br>64 pin           |                     |

| TCP4620AP        | 96 × 4  | 2048 × 8       |          | 10 µs                               |                                   |                 |                          | Plastic                     |                     |

| TCP4620BP        | 7 96×4  | 2040 x 0       |          |                                     | 0.4 mA<br>at 400kHz               |                 | -30°C∿85°C               |                             |                     |

| TCP4630AP        | 160 × 4 | 3072 × 8       | 34 Lines |                                     |                                   | $4 \sim 6V$     |                          | 42 pin                      | Original            |

| TCP4620AF        | 06.1    | 2010 0         | 54 Lines |                                     |                                   |                 |                          | Plastic                     |                     |

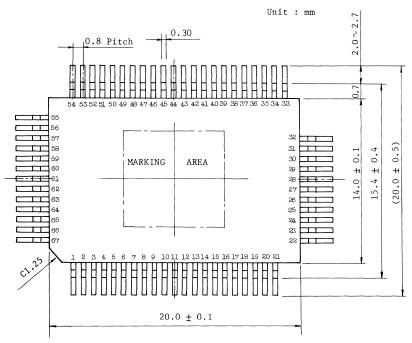

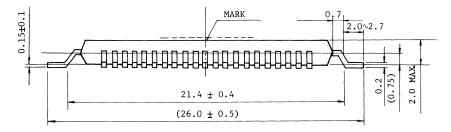

| TCP4620BF        | 96 × 4  | 2048 × 8       |          |                                     |                                   |                 |                          | 43 pin                      |                     |

| TCP4630AF        | 160 × 4 | 3072 × 8       |          | 1                                   |                                   |                 |                          | (Flat)                      |                     |

| TCP4621AP        | 96 × 4  | 2048 × 8       |          |                                     |                                   |                 | -20°C∿70°C               | Plastic<br>42 pin           |                     |

| TCP4632BF        | 160 × 4 | 3072 × 8       | 57 Lines |                                     |                                   |                 |                          | Plastic<br>67 pin<br>(Flat) |                     |

## TLCS-47 (4 BIT SINGLE CHIP NMOS/CMOS MICROCOMPUTER)

TLCS-47 SERIES (NMOS/CMOS)

|      | Device<br>Number | RAM       | ROM            | -  | 1/0     | Instruction<br>Cycle Time<br>(Min.) | i F | ower Supply<br>Current<br>(Typ.) | Power<br>Supply | Operating<br>Temperature | Package<br>Type             | Alternate<br>Source |

|------|------------------|-----------|----------------|----|---------|-------------------------------------|-----|----------------------------------|-----------------|--------------------------|-----------------------------|---------------------|

|      | TMP4720P         | 128 × 4   | 2048 × 8       |    |         |                                     |     |                                  | :               | Plastic :                |                             |                     |

|      | TMP4740P         | 256 × 4 i | 4096 × 8       |    |         |                                     |     |                                  | -               | 42 Pin i                 |                             |                     |

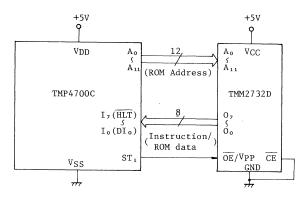

| NMOS | TMP4700C         | 256 × 4   | without<br>ROM |    |         | 2 us                                | l   | 50 mA                            |                 | 4                        | QIC<br>80 Pin               | •                   |

|      | TMP4799C         | 256 × 4   | without<br>ROM |    | 5 Lines | 5 1                                 |     | 5V±10%                           | _30°C ∿ 70°C    | DIC<br>42 Pin            | Toshiba                     |                     |

|      | TMP47C20P        | 128 × 4   | 2048 × 8       | l. |         |                                     | :   |                                  | . JV-10% .      | 50 C -70 C               |                             | Original            |

|      | TMP47C40P        | 256 × 4   | 4096 × 8       | ,  |         |                                     |     |                                  |                 | Plastic                  |                             |                     |

| CMOS | TMP47C21P        | 128 × 4   | 2048 × 8       | 1  |         | 4 us                                |     | 5 mA                             |                 |                          | 42 Pin :                    | 1                   |

| ð    | TMP47C41P        | 256 × 4   | 4096 × 8       |    |         |                                     |     |                                  |                 |                          |                             |                     |

|      | TMP47C22F        | 192 × 4   | 2048 × 8       | 55 | Line    | si                                  | :   |                                  |                 | 1                        | Plastic<br>67 Pin<br>(Flat) |                     |

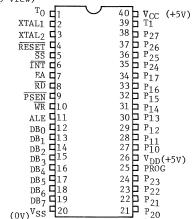

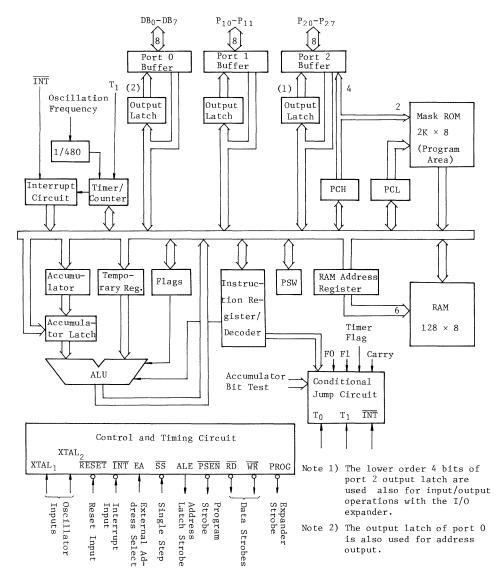

#### TLCS-84 (8 BIT SINGLE CHIP NMOS/CMOS MICROCOMPUTER) TLCS-84 SERIES (NMOS/CMOS)

|      | Device<br>Number | RAM            | ROM             | I/0        | Instruction<br>Cycle Time<br>(Min.) | Power Supply<br>Current<br>(Max.) | Power<br>Supply        | Operating<br>Temperature | Package<br>Type   | Alternate<br>Source |

|------|------------------|----------------|-----------------|------------|-------------------------------------|-----------------------------------|------------------------|--------------------------|-------------------|---------------------|

|      | TMP8048P         | 64 × 8         | $1024 \times 8$ |            | 2.5 µs                              | 135 mA                            |                        |                          |                   | <b>i</b> 8048       |

|      | TMP8035P         | 64 × 8         | -               |            | 2.5 µs                              | 135 mA                            | _                      |                          |                   | 18035L              |

|      | TMP8049P-6       | $128 \times 8$ | 2048 × 8        |            | 2.5 µs                              | 170 mA                            |                        |                          | Plastic<br>40 pin |                     |

|      | TMP8039P-6       | $128 \times 8$ | -               |            | 2.5 µs                              | 170 mA                            |                        | 0°C ∿ 70°C               |                   | i8039-6             |

| 10   | TMP8049P         | $128 \times 8$ | 2048 × 8        |            | 1.36 µs                             | 170 mA                            | 5v±10%<br>-40°C ∿ 85°C |                          |                   | i8049               |

| VMOS | TMP8039P         | 128 × 8        | -               | 27 Lines   | 1.36 µs                             | 170 mA                            |                        |                          |                   | 18039               |

| 1    | TMP8048PI        | 64 × 8         | 1024 × 8        |            | 2.5 µs                              | 145 mA                            |                        |                          | iD8048            |                     |

|      | TMP8035P1        | 64 × 8         | -               |            | 2.5 µs                              | 145 mA                            |                        | -40°C∿85°C               |                   | iD8035              |

|      | TMP8049PI-6      | $128 \times 8$ | 2048 × 8        |            | 2.5 µs                              | 170 mA                            |                        |                          |                   | iD8049              |

|      | TMP8039PI-6      | $128 \times 8$ | -               |            | 2.5 µs                              | 170 mA                            |                        |                          |                   | iD8039              |

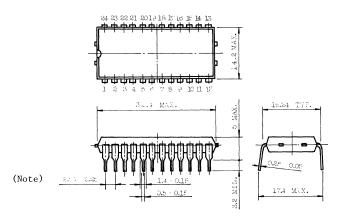

|      | TMP8243P         | I/O Exp        | pander fo       | r TMP80481 | P/TMP8049P                          | 20 mA                             | 5V±10%                 |                          | Plastic<br>24 pin | i8243               |

|      | TMP8243PI        | I/O Exp        | pander fo       | r TMP8048] | PI-6/8049PI-6                       | 20 mA                             | 5V±10%                 | -40°C∿85°C               | Plastic<br>24 pin | iD8243              |

| CMOS | TMP80C49P-6      | 128 × 8        | 2048 × 8        | 27 Lines   | 2.5 µs                              | 10 mA                             | 5v±10%                 | -40°C∿85°C               | Plastic           |                     |

| S    | TMP80C39P-6      | 128 × 8        | -               | 2/ Lines   | 2.5 µs                              | 10 mA                             | - JV ±10%              | -40 0.085 0              | 40 pin.           |                     |

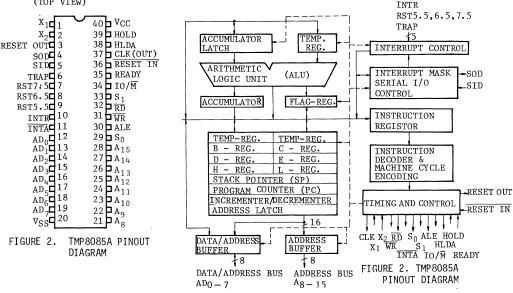

#### TLCS-85A

• 8 BIT MICROPROCESSOR

| Device<br>Number | Description          | Instruction<br>Cycle Time<br>(Min.) | Power Supply<br>Current<br>(Max.) | Power<br>Supply | Operating<br>Temperature | Package<br>Type   | Alternate<br>Source |

|------------------|----------------------|-------------------------------------|-----------------------------------|-----------------|--------------------------|-------------------|---------------------|

| TMP8085AP        | 8 Bit Micrøprocessor | 1.3 µs                              | 170 mA                            | 5V±10%          | 0°C ∿ 70°C               | Plastic<br>40 pin | 18085A              |

#### PERIPHERALS (NMOS)

| Device<br>Number | Description                                                | Power Supply<br>Current<br>(Max.) | Power<br>Supply | Operating<br>Temperature | Package<br>Type   | Alternate<br>Source |

|------------------|------------------------------------------------------------|-----------------------------------|-----------------|--------------------------|-------------------|---------------------|

| TMP8155P         | 256 Byte RAM with I/O Ports and Timer<br>(CE: Active Low)  | 180 mA                            | 5V±5%           |                          | Plastic<br>40 pin | 18155               |

| TMP8156.P        | 256 Byte RAM with I/O Ports and Timer<br>(CE: Active High) | 180 mA                            | 5V±5%           | 0°C∿70°C                 | Plastic<br>40 pin | 18156               |

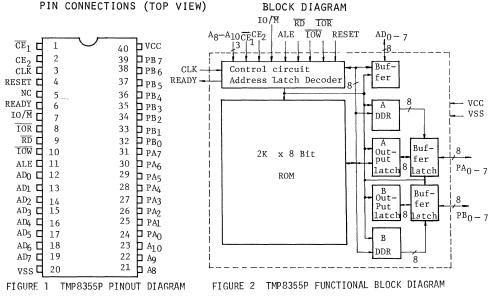

| TMP8355P         | 2K Byte Mask ROM with I/O Ports                            | 180 mA                            | 5V±5%           | 0.0.0.0.0                | Plastic<br>40 pin | i8355               |

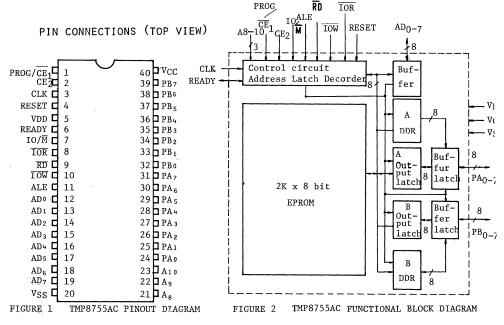

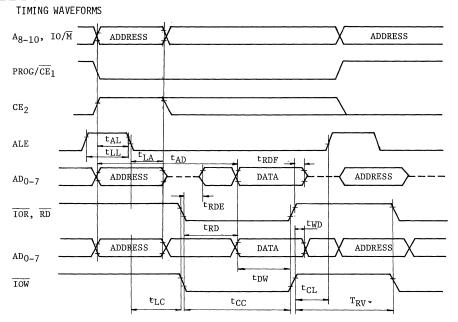

| TMP8755AC        | 2K Byte EPROM with I/O Ports                               | · 180 mA                          | 5V±5%           |                          | Ceramic<br>40 pin | i8755A              |

# **4BIT SINGLE CHIP MICROCOMPUTER**

TLCS-43(NMOS)

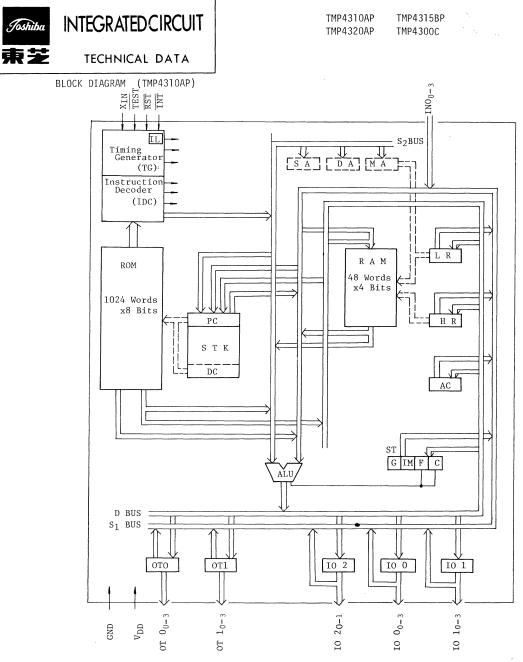

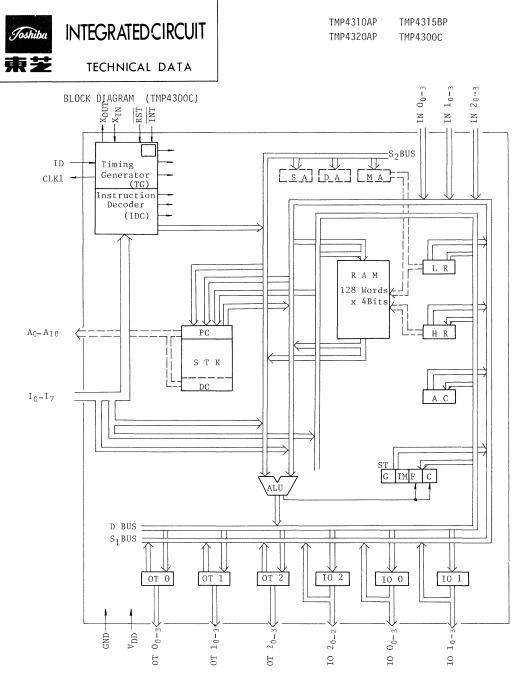

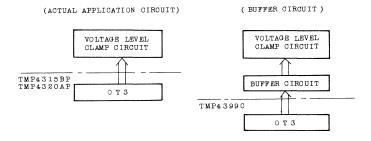

TOSHIBA MOS TYPE DIGITAL INTEGRATED CIRCUIT TMP4310AP TMP4315BP TMP4320AP TMP4300C Silicon Monolithic N-Channel Silicon Gate Depression Load

#### GENERAL DESCRIPTION

TLCS-43 is a complete single chip micro computer series having an internal 4 bit parallel processing function which is suitable for controller applications.

It contains ROM (read only memory) which stores the control programs and the fixed data, RAM (read/write memory) which temporarily stores various data nd a plural number of input/output ports.

In order to provide for a variety of applications the TLCS-43 provides short instruction execution time, multiple subroutine nesting, and flexible input/output ports.

By combining index instructions with processing instructions, the same instruction can be executed for all the registers and all the input/output ports enabling highly efficient programes to be written.

In TLCS-43, there are three versions, TMP4310AP, TMP4315BP and TMP4320AP each of which has different memory capacity and different number of input/ output lines, so that the optimum version for a specific application can be selected. Furthermore, TMP4300C is available as the evaluator chip.

TECHNICAL DATA

#### FEATURES

- o TMP4310AP 1024 x 8 ROM 48 x 4 RAM 22 I/O Lines

- o TMP4315BP 1536 x 8 ROM 64 x 8 RAM 35 I/O Lines

- o TMP4320AP 2048 x 8 ROM 128 x 4 RAM 35 I/O Lines

- o TMP4300C Evaluator Chip for TLCS-43

TMP4310AP

TMP4315BP

TMP4320AP

TMP4300C

- o 35 Basic instructions

- 31 Processing Instructions

- 4 Index Instructions

- o 4 Level Subroutine Nesting

- o Single Level External Interrupt

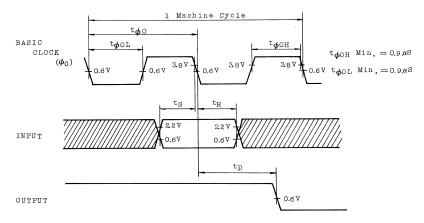

- o 4 µs Instruction Executuion Time

- o Single 5V Supply

- o ROM Data Readout Instructions

- o LED Direct Drive Capability

(Except TMP4315BP)

TMP4310AP

TMP4315BP

TMP4320AP

TMP4300C

Toshiba 束 芝

TECHNICAL DATA

#### TABLE OF FEATURES

| Feature                                | TMP4310AP               | TMP4315BP                      | TMP4320AP               | TMP4300C                                       |  |  |  |

|----------------------------------------|-------------------------|--------------------------------|-------------------------|------------------------------------------------|--|--|--|

| ROM Capacity                           | 1,024 Words<br>x 8 Bits | l,536 Words<br>x 8 Bits        | 2,048 Words<br>x 8 Bits | External connection<br>2,048 Words<br>x 8 Bits |  |  |  |

| RAM Capacity                           | 48 Words                | 64 Words                       | 128 Words               | 128 Words                                      |  |  |  |

| KAN Capacity                           | x 4 Bits                | x 4 Bits                       | x 4 Bits                | x 4 Bits                                       |  |  |  |

|                                        | 1 Port                  | 3 Port                         | 3 Port                  | 3 Ports                                        |  |  |  |

| Input Port                             | (4 Bits)                | (12 Bits)                      | (12 Bits)               | (12 Bits)                                      |  |  |  |

|                                        | 2 Port                  | 4 Port                         | 4 Port                  | 3 Port                                         |  |  |  |

| Output Port                            | (8 Bits)                | (15 Bits)                      | (15 Bits)               | (12 Bits)                                      |  |  |  |

|                                        | 3 Port                  | 2 Port                         | 2 Port                  | 3 Port                                         |  |  |  |

| Input/Output<br>Port                   | (10 Bits)               | (8 Bits)                       | (8 Bits)                | (ll Bits)                                      |  |  |  |

| Subroutine<br>Nesting Level            |                         | 4 Levels (including interrupt) |                         |                                                |  |  |  |

| Interrupt Level                        |                         | l Level                        |                         |                                                |  |  |  |

| Nunber of<br>Instructions              | 3.                      | 5 Basic Instruct               | ions                    |                                                |  |  |  |

| Execution Time of<br>Basic Instruction |                         | 4 μS (l Cycle Ir               | struction), 8           | μS (2 Cycle Instruction)                       |  |  |  |

| Input/Output<br>Level                  |                         | TTL Compatible                 |                         |                                                |  |  |  |

| Power Supply                           |                         | 5V ± 10 %                      |                         |                                                |  |  |  |

| Power Dissipation                      | 200mW (TYP.)            | 200mW (TYP.)                   | 200mW (TYP.)            | 350mW (TYP.)                                   |  |  |  |

| Operating<br>Ambient Temp.             | -                       | 10°C to 70°C                   | I                       | L                                              |  |  |  |

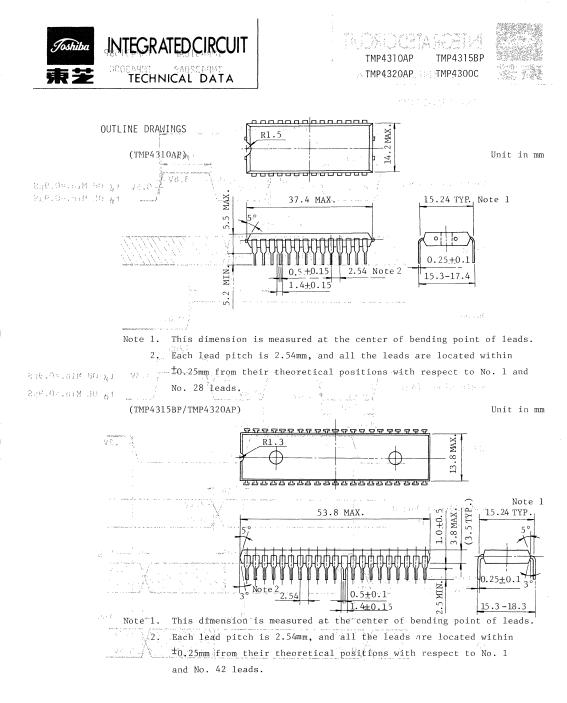

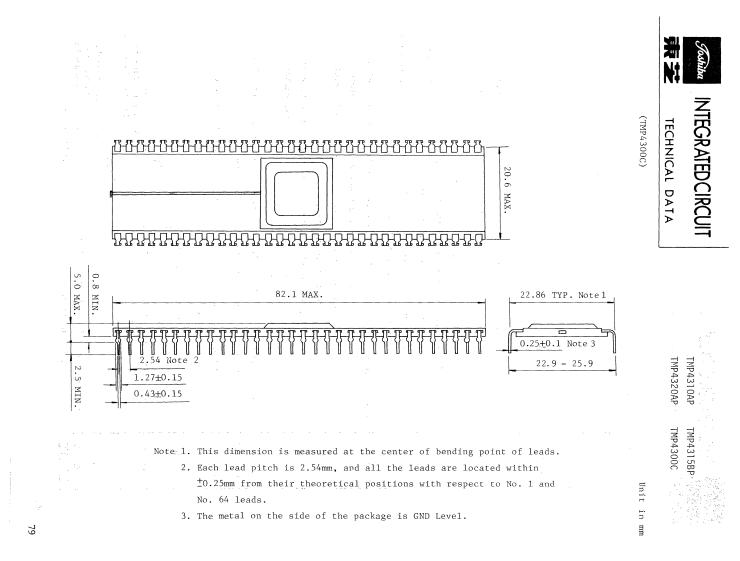

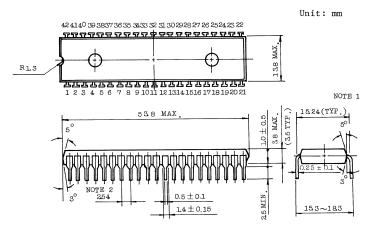

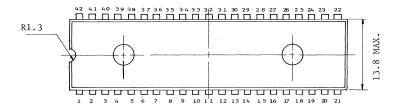

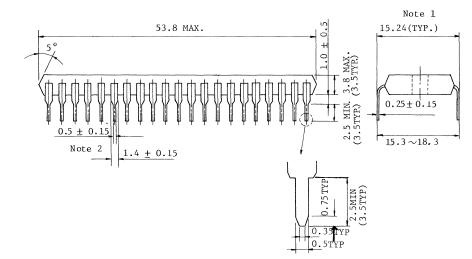

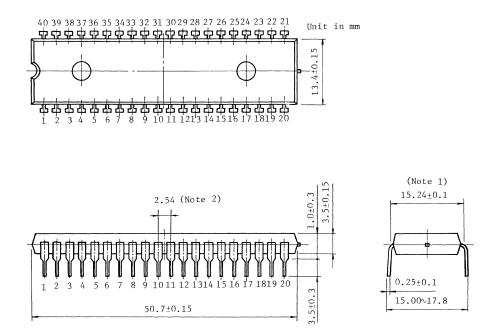

| Package                                | 28 Pin<br>Plastic DIP   | 42 Pin<br>Plastic DIP          | 42 Pin<br>Plastic DIP   | 64 Pin<br>Ceramic DIP                          |  |  |  |

| Process                                |                         | N-Channel E/D MC               | )S                      | 1                                              |  |  |  |

TECHNICAL DATA

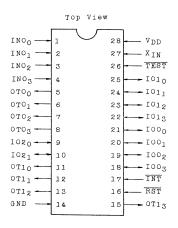

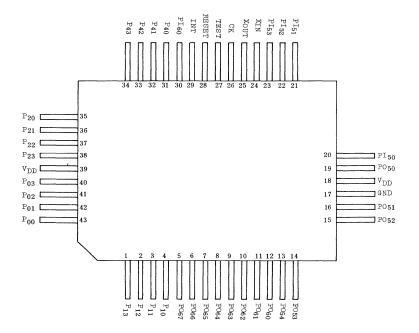

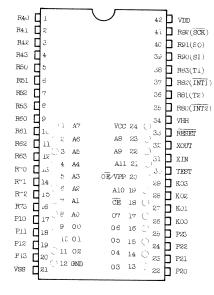

PIN CONNECTIONS Top View (TMP4310AP) 2.8 IN O<sub>0</sub> 1 □ v<sub>DD</sub> 27 h XIN IN 01 2 IN 02 TEST 3 26  $10 1_0$ IN 03 4 25 1 IO 11 OT 00 [ 5 24 IO 12 от 0₁ □ 6 23

| OT $0_2 \square$    | 7  | 22 | IO 1 <sub>3</sub> |

|---------------------|----|----|-------------------|

| от 0 <sub>3</sub> □ | 8  | 21 | 10 0 <sub>0</sub> |

| IO 20               | 9  | 20 | IO $0_1$          |

| IO 21               | 10 | 19 | IO 0 <sub>2</sub> |

| OT 10               | 11 | 18 | IO $0_3$          |

| от 11               | 12 | 17 | INT               |

| OT 12               | 13 | 16 | RST               |

| GND                 | 14 | 15 | OT 1 <sub>3</sub> |

TMP4310AP TMP4320AP TMP4315BP TMP4300C

(TMP4300C) 1 64 NC GND RST INT 2 63 XIN 3 62 ID  $\square$ IO 22 X<sub>OUT</sub> 61 4 5 60 IO 21  $10 \ 0_3 \square$ IO 20 IO  $0_2$ 59 6 IO 01 7 58 NC IO 00 57 D OT 03 8 IO 130 9 0T 02 56 IO  $1_2 \square_{10}$ OT 01 55 OT 00  $I_7$ **H**11 54 OT 23 I<sub>6</sub>  $\Box_{12}$ 53 OT 22 L5 113 52 51 D OT 2, I<sub>L</sub> I3 [15 50 🗖 OT 20 49 🗖 OT 13 I2 16 1, d OT 12 17 48 I0 018 47 OT 1, 10 11 19 46 OT 10  $10 \quad 1_0^1 \quad 20$ 45 🗖 IN 03 44 IN 23221 IN 02 43 IN  $0_1$ IN 2222 IN 2123 42 🗖 IN O<sub>0</sub> IN 20024 41 CLK 1 IN 130 25 An 40 IN 12 26 39 Al 38 A<sub>2</sub> IN 1 27 IN 10<sup>28</sup> 37 A<sub>3</sub> A10 29 36  $\Box$ Aμ A9 30 35 A 5 A<sub>8</sub>  $\square$  <sup>31</sup> 34 A6 32 331 VDD A7

TMP4310AP

TMP4315BP

TMP4320AP

TMP4300C

TECHNICAL DATA

#### PIN NAMES & PIN DESCRIPTION

| Pin Name         | Input/<br>output | Function                                                                                                                                                                                                                                                                       | 4310           | 4315/<br>4320 | 4300       |

|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|------------|

| INOo-INO3        | Input            | 4-bit Input Port INO                                                                                                                                                                                                                                                           | 0              | 0             | $\bigcirc$ |

| IN10-IN13        | Input            | 4-bit Input Port [N1                                                                                                                                                                                                                                                           |                | 0             | $\bigcirc$ |

| IN20-IN23        | Input            | 4-bit Input Port IN2                                                                                                                                                                                                                                                           |                | 0             | $\bigcirc$ |

| 0ТОо-ОТОЗ        | Output           | 4-bit Output Port OTO                                                                                                                                                                                                                                                          | $\overline{O}$ | 0             | 0          |

| OT10-OT13        | Output           | 4-bit Output Port OT1                                                                                                                                                                                                                                                          |                |               |            |

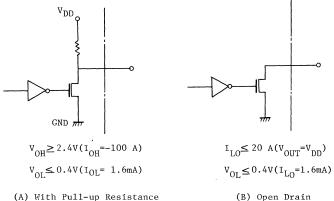

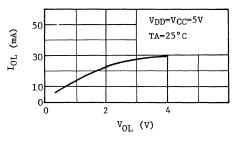

|                  |                  | Large sink current(IOL TYP=20mA,VOL=2V)<br>is possible in<br>TMP4310AP/20AP/00C.                                                                                                                                                                                               | 0              | 0             | 0          |

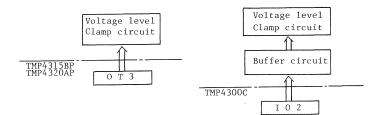

| OT20-OT23        | Output           | 4-bit Output Port OT2                                                                                                                                                                                                                                                          |                |               |            |

|                  |                  | Large sink current(IOL TYP=20mA,VOL=2V)<br>is possible in<br>TMP4320AP/00C.                                                                                                                                                                                                    |                | 0             | 0          |

| OT30-OT32        | Output           | 3-bit Output Port OT3                                                                                                                                                                                                                                                          |                |               |            |

|                  |                  | IO2o-IO22 of TMP4300C are available in evaluation.                                                                                                                                                                                                                             |                |               |            |

| 1000-1003        | Input/<br>Output | 4-bit Input/Output Port IOO                                                                                                                                                                                                                                                    | 0              | 0             | 0          |

| 1010-1013        | Input/<br>Output | 4-bit Input/Output Port IO1                                                                                                                                                                                                                                                    | 0              | 0             | 0          |

| 1020-1022        | Input/           | 3-bit Input/Output Port IO2                                                                                                                                                                                                                                                    | $\cap$         |               | $\bigcirc$ |

|                  | Output           | 2-bit Port (IO2o-IO21) in TMP4310AP                                                                                                                                                                                                                                            | 0              |               | 0          |

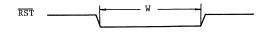

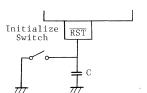

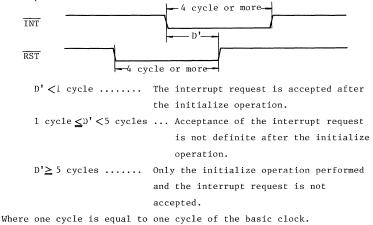

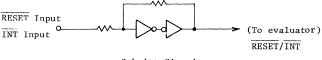

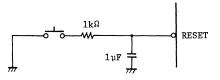

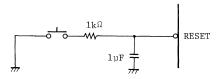

| RST              | Input            | Initialize Signal Input                                                                                                                                                                                                                                                        |                |               |            |

|                  |                  | The initialize operation is performed<br>by placing RST terminal at low level<br>for more than four clock cycles.                                                                                                                                                              | 0              | 0             | 0          |

| INT              | Input            | Interrupt Request Signal Input<br>The interrut request is accepted<br>by placing INT terminal at low<br>level for more than our clock<br>cycles. The repetetive interrupt<br>should be requested, after keeping<br>INT terminal at high level for two<br>clock cycles or more. | 0              | 0             | 0          |

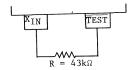

| TEST<br>(Note 1) | Input            | LSI Test Signal Input<br>TEST should be always kept at high level<br>(open or connect an oscillation resistance<br>in TMP4310AP) except in LSI test mode.                                                                                                                      | 0              | 0             |            |

Toshiba

TECHNICAL DATA

TMP4315BP TMP4300C

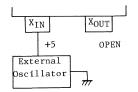

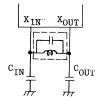

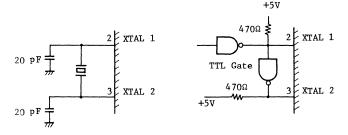

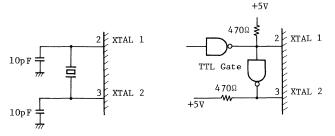

| XIN                | Input  | Basic Clock Terminal                                                                                                                                      |   |   |            |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|------------|

| (Note 1)           |        | XIN is used as an external clock<br>input pin, or a oscillator<br>connection pin.                                                                         | 0 | 0 | 0          |

| XOUT               | Output | Basic Clock Terminal<br>XOUT is used as a oscillator<br>connection pin.                                                                                   |   | 0 | 0          |

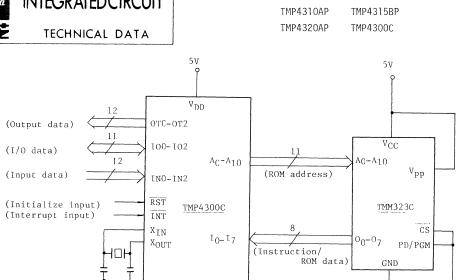

| Ao-A <sub>10</sub> | Output | ROM Address Output (MSB:A <sub>10</sub> ,LSB:Ao)                                                                                                          |   |   | $\bigcirc$ |

| Io-17              | Input  | ROM Data Input (MSB:I7,LSB:I0)                                                                                                                            |   |   | $\bigcirc$ |

| CLK1               | Output | Internal Clock Output                                                                                                                                     |   |   | 0          |

| ID                 | Input  | Interrupt Operation Inhobit Input<br>ID is a dedicated terminal only for<br>TDS400/43, and should be always<br>kept at low level except in TDS400/<br>43. |   |   | 0          |

| v <sub>DD</sub>    |        | +5V (Power Supply)                                                                                                                                        | 0 | 0 | 0          |

| GND                |        | OV (Power Supply)                                                                                                                                         | 0 | 0 | 0          |

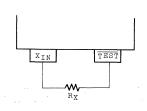

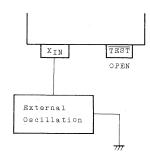

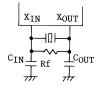

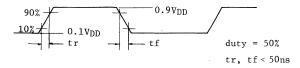

- Note 1 The basic clock of TMP4310AP

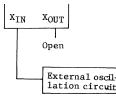

- o Internal oscillation (with resistance externally installed between  $X_{\rm TN}$  and  $\overline{\rm TEST}$ ) and external clock supply can be available.

- o TEST terminal should be kept open when the basic clock is supplied by an external oscillator circuit.

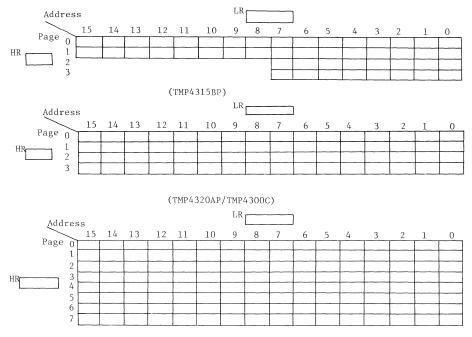

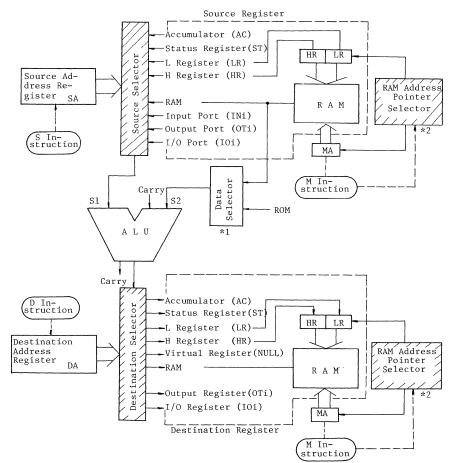

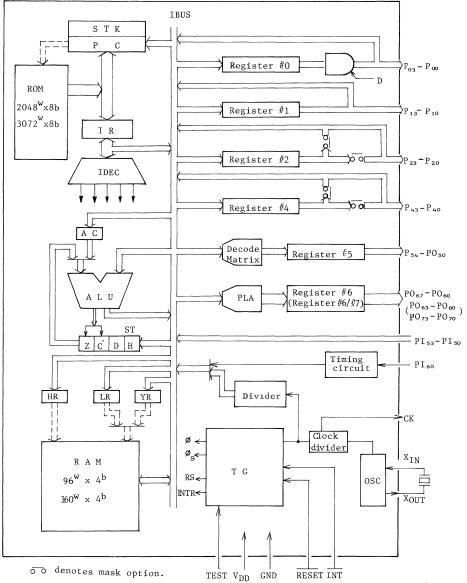

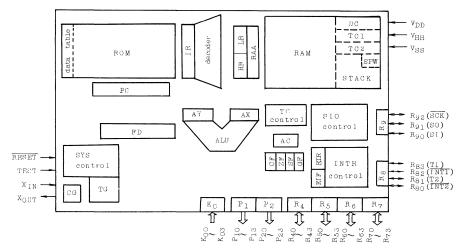

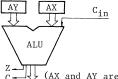

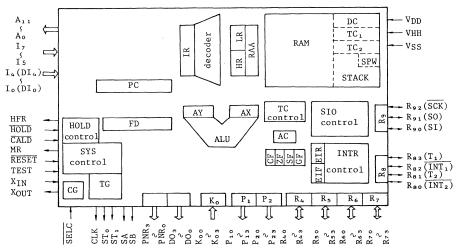

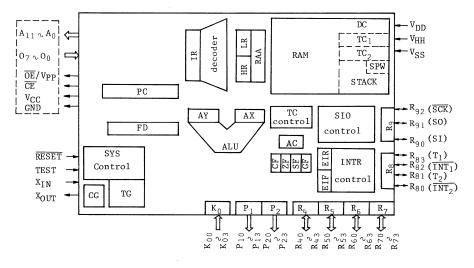

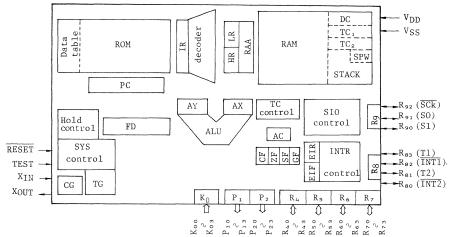

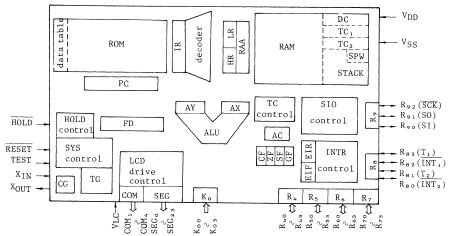

IN  $0_{0-3}$ IN 10-3 IN 20-3 BLOCK DIAGRAM (TMP4315BP/TMP4320AP) X<sub>IN</sub> EST RST INT XoU IL S2BUS Timing Π 11 U Generator S A D A M A (TG) Instruction Decoder (IDC) J 10 LR RAM ROM 64/128 Words 1536/2048 x4 Bits Words x8 Bits PC ΗR S T K ⇒ DC 1 r A C ST GIMF С AĽM D BUS T TI Π Π Π S<sub>1</sub>BUS OT 0 OT 1 OT 2 OT 3 IO 0 IO 1 30-2 IO  $1_{0-3_1}^{<}$ IO 0 0-3< ř 2 6-34 10-GND OT 00 $v_{\mathrm{DD}}$ OT τo Ъ

TECHNICAL DATA

FUNCTIONAL DESCRIPTION

[Block Description]

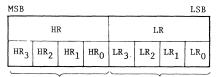

For all registers and I/O ports, MSB is the High order bit and LSB is the Low order bit.

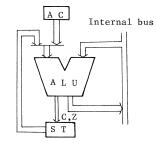

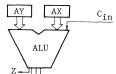

1. Arithmetic and Logical Unit (ALU)

The ALU is the central 4 bit parallel processing function of the TLCS-43.  $S_1$  and  $S_2$  are the two 4 bit input words and C is the carry input from some previous calculation. The ALU processed these and outputs one 4 bit result (D) and a carry bit.

2. Accumulator (AC)

The accumulator is a four bit register, which stores the data for arithmetic and logical operations. In addition the accumulator is also used to store the results of arithmetic and logical calculations.

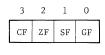

3. Status Register (ST)

The status register is a four bit register which contains fields to represent the carry flag (C), branch condidtion flag (F), interrupt flag (IM) and general purpose flag (G).

1) C

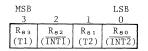

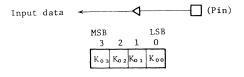

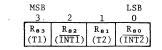

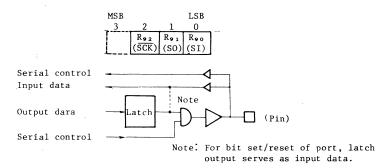

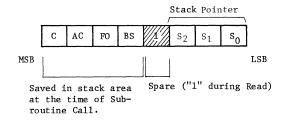

ST MSB 3 2 1 0 LSB G IM F C

Bit O of the status register is called C flag and used to indicate Carry (or Borrow) during arithmetic operation with multiple number of digits.

2) F

Bit 1 of the status register is called F flag and set or reset according to the result of logical operation or arithmetic operation just executed. And this bit is referred to during execution of conditional branch instruction in a program.

3) IM

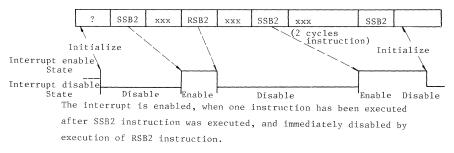

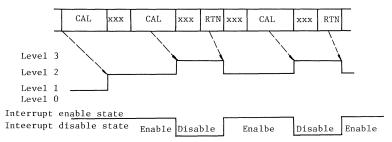

Bit 2 of the status register is the interrupt flag called IM flag which is set or reset by program. IM flag being "1" indicates the interrupt enabled condition and IM flag is cleared to "0" as soon as an interrupt routine is initiated. This is also cleared to "0" by the initialize operation.

4) G

Bit 3 of the status register is called G flag and this one bit flag is used generally by programs.

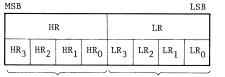

4. L Register (LR)

L Register (lower address register) is a four bit register which indicates the lower order 4 bits of RAM address and is used in conjunction with H Register for addressing RAM.

5. H Register (HR)

H Register (Higher address register) is a two bit or three bit register which indicates the higher order two or three bits of RAM address, and used in conjunction with L Register for addressing RAM.

When a program reads, the undefined higher order two bits (bit 3 and bit 2) or one bit (bit 3) are always processed to be zero.

| (Tì | MP4310# | AP/TMP4315B | P) |

|-----|---------|-------------|----|

| M   | SB 1    | O LSB       |    |

| HR  |         |             |    |

| (TMP4320AP/TMP4300C) |   |   |   |     |  |  |  |  |

|----------------------|---|---|---|-----|--|--|--|--|

| MSB                  | 2 | 1 | 0 | LSB |  |  |  |  |

| HR                   |   |   |   |     |  |  |  |  |

|                      |   |   |   |     |  |  |  |  |

,

6. Input Port (INO, IN1, 1N2)

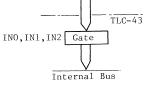

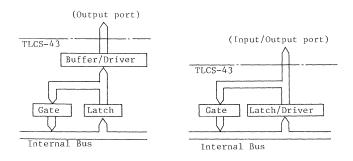

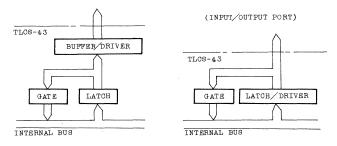

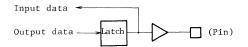

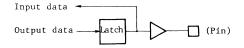

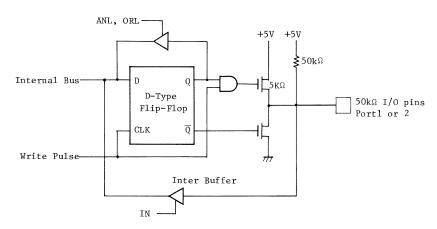

All of INO, IN1 and IN2 ports are the dedicated input ports having four bit configuration and read the data sent from outside. The input ports are non-latch type ports. Toshiba INTEGRATEDCIRCUIT

TMP4310APTMP4315BPTMP4320APTMP4300C

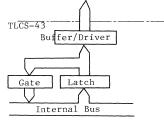

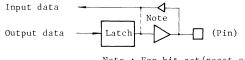

7. Output Port (OTO, OT1, OT2, OT3) OTO,OT1 and OT2 have four bit configuration and OT3 has three bit configuration, all of which are the dedicated output ports. The content of each port is output to outside and retained until replaced with new data. And the content of a port can read by program. In this case the undefined bit 3 of OT3 port is always processed,tobe zero. All the bits of all the output ports are set to "1" by the initialize operation.

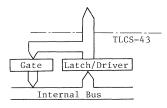

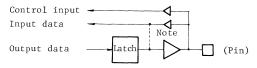

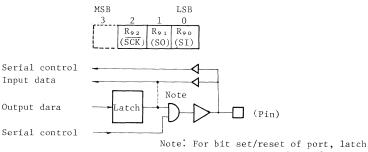

8. Input/Output Port (I00, I01, I02)

100 and 101 have four bit configuration and 102 has two or three bit configuration, all of which are the input/output ports.

The content of each port is output to outside and retained until replaced with new data. It can also input data from outside. However, the output data must be set to "1" whenever the input operation is performed.

Whenver no data is input from outside, the output data to outside can be read by program. When the output data is read, undefined bit 3 and bit 2 of IO2 port are always processed to be zero.

All bits of the output data are set to "1" by the initialize operation.

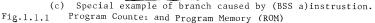

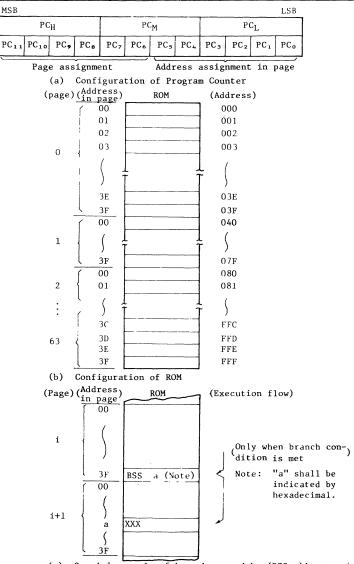

9. Program Counter (PC)

The program counter is 11 bit counter which addresses the program stored in ROM (refer to (Note) in the ROM paragraph.)

While the normal instructions are executed, the program counter is incremented by word length of instruction just excuted. However, for branch instructions, subroutine call and interrupt operation, the counter is set to the values designated by the instructions. The counter is reset to "0" by the initialize operation.

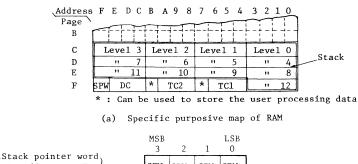

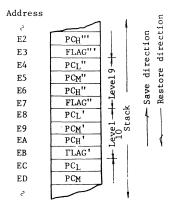

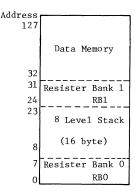

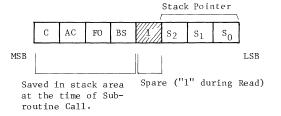

10. Stack

The stack is a group of 4 words x ll bits registers including the data counter.

The stack is used as the save area of the program counter during subroutine call and interrupt operation. If it is already occupied up to level 2, the data counter becomes to be the stack area of level 3.

11. Data Counter (DC)

The data counter is an 11 bit counter which addresses fixed data stored in ROM (refer to (Note) in the ROM paragraph.)

The content of the data counter can be set by program. The data counter is also used as the deepest stack level (level 3) and when nesting has been done up to level 2, if further nesting is performed, the content as the data counter is destroyed.

TMP4310AP TMP4320AP TMP4315BP TMP4300C

TECHNICAL DATA

And when the data counter is being used as stack level 3, if setting operation is performed to the data counter, the content as stack level 3 is destroyed.

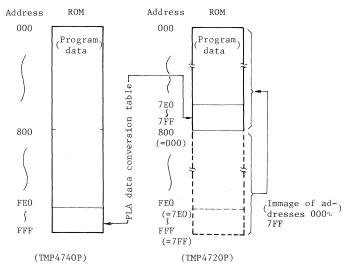

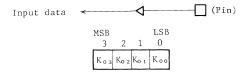

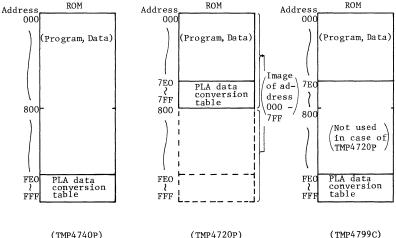

12. Read Only Memory (ROM)

The read only memory (ROM) can also store fixed data as well as programs which are required by users.

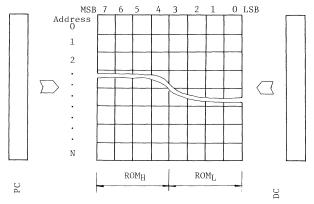

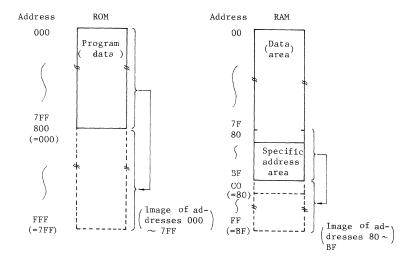

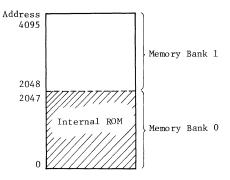

ROM has a maximum capacity of 2,048 words x 8 bits and is independently addressed by the program counter which addresses the storage area for programs and by the data counter which addresses the storage area for fixed data.

For storing programs the ROM is processed as 8 bit words but for fixed data, 8 bit word is divided into the higher order 4 bits and the lower order 4 bits, namely divided to two 4 bit words of ROM<sub>H</sub> and ROM<sub>L</sub>.

(TMP4310AP).... N=1,023 (TMP4315BP).... N=1,535 (TMP4320AP)... N=2,047

(Note) In the case of TMP4310AP, both of the program counter (PC) and the data counter (DC) are 11 bit counters, and if bit 10 is "1", any contents of ROM are not accessed.

TMP4315BP. TMP4300C

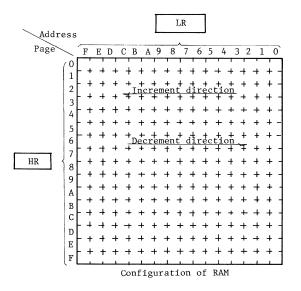

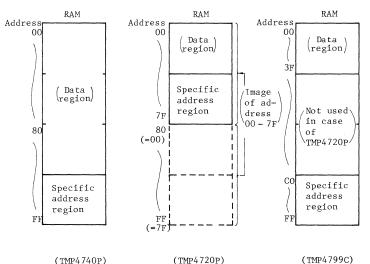

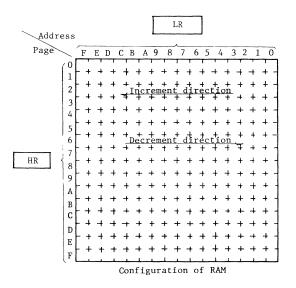

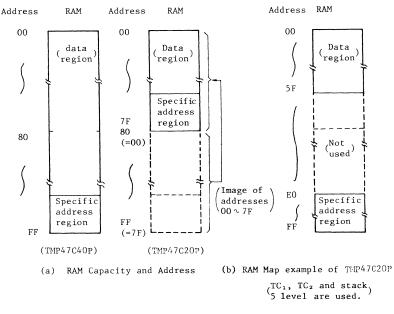

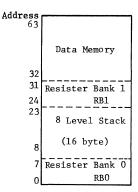

13. Read/Write Memory (RAM)

The read/write memory (RAM) can be used as the working area for data processing.

RAM has the maximum configuration of 128 words x 4 bits and is addressed by H Register which designates a page and L Register which designates an address in a page.

In addition to the above, another addressing method of RAM is to access an address in page 0 using the index instructions (M instructions) which will be explained later. This method is effective to save the contents of registers on the interrupt operation. The configuration of each version is as follows.

(TMP4310AP)

TMP4310AP

TMP4315BP

TMP4320AP

TMP4300C

TECHNICAL DATA

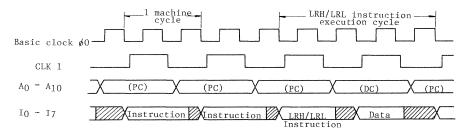

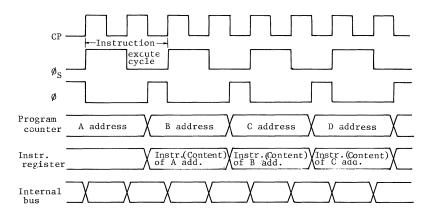

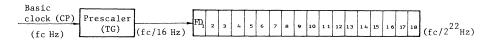

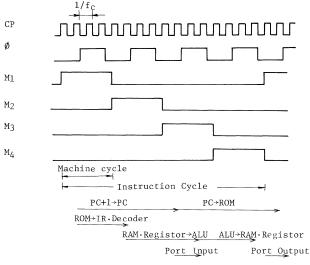

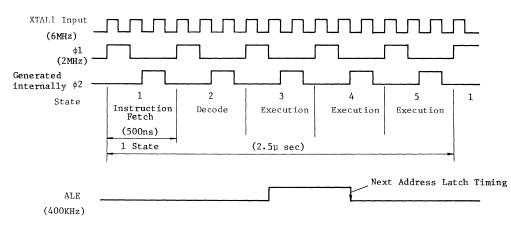

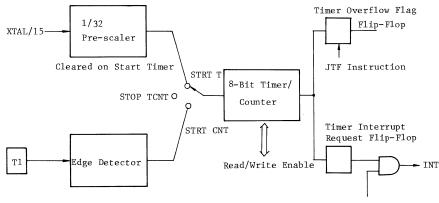

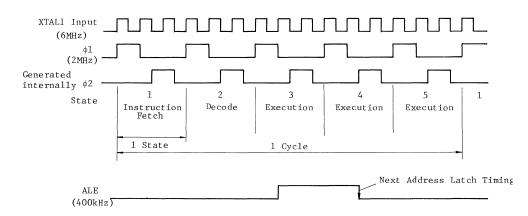

14. Timing Generator (TG) and Instruction Decoder (IDC) The timing generator produces a clock frequency that is dependant on the oscillator connected externally. Based on this timing the instruction decoder reads and decodes the fields unique to each instruction.

Timing of interrupts, initialize requests etc. are also synchronized by the Timing Generator.

Registers Dedicated to Index Instructions (SA, DA and MA)

..... Refer to the paragraph of Index Instructions.

These are 4 bit registers used by the index instructions which are explained later, and there are three kinds, namely SA (Source Address Register), DA (Destination Address Register) and MA (Memory Address Register). Source register code, destination register code and RAM address which are activated by the index instructions are input to SA, DA and MA respectively, and these are temporarily retained until the following one operation instruction is completely executed.

The registers dedicated to the index instructions can not be used by program as additional data registers.

1. Features of TLCS-43 Machine Instructions

One of the features of the TLCS-43 Machine Instruction set is the existance of index instructions. In the case of processing instructions, usually the source and destination of data have been inherently defined. The index instructions modify the processing instructions to change the source of data to be processed or/and the destination of the processing results. Therefore, it is much simpler to write programs which require sequential operations through an area of memory. The extensive use of index instructions produces efficient programs in terms of the number of program steps.

Another great feature is that the machine instructions with Data Counter (DC) maintaing ROM address in addition to PC have the instructions which can read out the content of ROM directly, which allows a greater amount of fixed data to be efficiently read.

Furthermore, with the addition of four level subroutine nesting ability, the subroutine call instructions of 1 byte length are available. This is effective in reducing overall program size.

2. Format of Machine Instructions

The explanation of each instructions is described according to the following format.

n) x x x ( ) Name of Instruction Mnemonic Code Series Number of Instruction

Symbol

Instruction Mnemonic Operation Code Operand

#### [Machine Instructions]

TLCS-43 series microcomputer is provided with 35 kinds of machine instructions. Unless otherwise mentioned the machine instructions are described as just instructions.

Among the machine instructions of TLCS-43, 30 instructions are of 1-byte length and 5 instructions are of 2-byte length. As regards the execution time of machine instructions, 28 instructions are of 1machine cycle and 7 instructions are of 2-machine cycle.

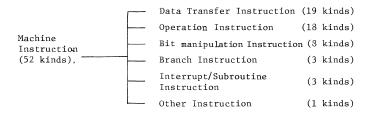

Machine Instructions are classified by their functions as follows:

Number of Instructions -Index Instructions..... 4 TLCS-43 -Data Processing Instructions Machine \_ Instruc-Processing Data Transfer tions Instructions Instructions .....7 Logical Operating Instructions ..... 10 Bit Processing Instructions ..... 3 -ROM Readout Instructions ..... 3 -Branch Instructions ..... 5 Total 35

TECHNICAL DATA

| $<\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

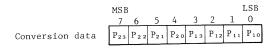

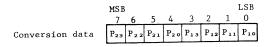

| No.l Byte                                                                   | MSB LSB<br>7 6 5 4 3 2 1 0<br>x x x x x x x x x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| No.2 Byte<br>( <sup>Address next to</sup> )<br>(+1) No.1 Byte               | $\begin{array}{c} \text{MSB} \\ 7 \\ \hline 7 $ |

|                                                                             | (The correspondence of the operand of<br>symbol instruction and the machine code<br>is recorded, if necessary.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| < Function >                                                                | The logical peration performed by this instruction is explained with symbols.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <status flag=""></status>                                                   | <ul> <li>(F): The status after the execution</li> <li>(C): Of status flag is described.</li> <li>(Dependent on the data when designated to store data in status register.)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <pre>Execution Cycle</pre>                                                  | The number of machine cycles necessary for executing instructions is described.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <pre>Function Explanation</pre>                                             | The function of instructions is explained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |