TMS320C14/TMS320E14

1988

1988

# User's Guide

TMS320C14/TMS320E14

**Digital Signal Processor Products**

# TMS320C14/TMS320E14 User's Guide

## **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. TI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

TI warrants performance of its semiconductor products to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

TI assumes no liability for TI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1988, Texas Instruments Incorporated

# **Manual Update Sheet**

DATE: November 16, 1989

Document Title: TMS320C14/E14 User's Guide

ECN: 550007 (10-12-89)

Document Numbers: SPRU032

New Rev. Level: A

2558514-9701

New Rev. Level: -9702

The following are changes to the TMS320C14/E14 User's Guide.

| -                | CHANGE OF APP                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>PAGE</u>      | CHANGE OR ADD                                                                                                                                                                                                                                                                                                                                                                     |

| iv               | Change page numbers of Sections 5.8 and 5.3.1 to 5-40 and 5-41 respectively.                                                                                                                                                                                                                                                                                                      |

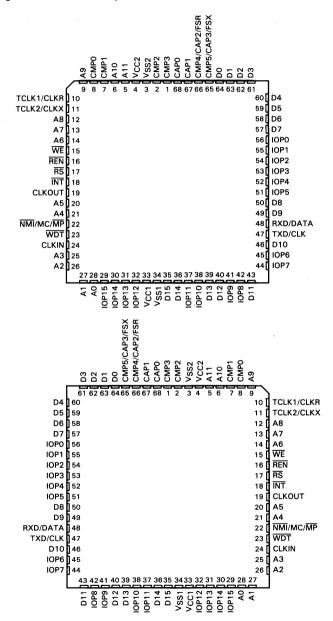

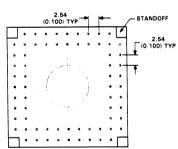

| 2–2              | Note that the top figure is the top view and the bottom figure is the bottom view.                                                                                                                                                                                                                                                                                                |

| 3–6              | In Section 3.1.2, note that $\overline{\text{REN}}$ and $\overline{\text{WE}}$ are active for program fetch/write regardless of the state of MC/ $\overline{\text{MP}}$ . If the device is in MC mode, a dummy read is performed for program fetch or an external write is performed for the case of TBLW.                                                                        |

|                  | Also note that the data bus is driven during all write operations, including writes to internal peripherals.                                                                                                                                                                                                                                                                      |

| 3–14             | It should not be inferred from the second paragraph in Section 3.2.2 that the address lines are driven only during accesses to external peripherals. <b>Address lines are always driven.</b> For instruction fetch, it is the instruction address, and for a peripheral, it is the peripheral port address. It does not matter whether or not the access is internal or external. |

| 3–18             | In Figure 3–6, delete the two OR gates and flip-flop that compose the $MC/\overline{MP}$ function in the top of the figure.                                                                                                                                                                                                                                                       |

| 3–46             | In Table 3–12, rewrite the zero setting for Bit 10 to read:  0 = Holds the output pins at zero and prevents interrupts from being generated by the compare subsystem.                                                                                                                                                                                                             |

|                  | (Bit 10 does not hold registers CMPR0—CMPR5 to zero when the bit is zero.)                                                                                                                                                                                                                                                                                                        |

| 3-48/49          | In subsection 3.7.1.5 (High Precision PWM Mode), note that the value that decides when the output pin drops is written to the Action Register and not to the Compare Register directly.                                                                                                                                                                                           |

|                  | Also, 2 is the minimum valid value that can be loaded into the Period Register of the timer specified to drive the compare system.                                                                                                                                                                                                                                                |

| 3–50             | Change item 2 in the summary at the bottom of the page to read:  2) TMRx counts until its 14 LSBs match the 14 MSBs of the Compare Register.                                                                                                                                                                                                                                      |

| 3–54             | It should not be inferred from subsection 3.7.2.3 (Capture Control Register) that writing to CCLR affects all the bits of Register CCON. It does not; the effect is only on the overrun error bits (bits 3, 7, 11, and 15 of Register CCON).                                                                                                                                      |

| 3–61             | In the data for bit 10 in Table 3–19, change the last line to read:  Set to 1 on reset.                                                                                                                                                                                                                                                                                           |

| 3-69 to 3-79     | Parity is not supported in synchronous and codec modes on the serial port. Delete all references to parity generation and detection in Sections 3.8.4 and 3.8.5.                                                                                                                                                                                                                  |

| 3-70, 3-76, A-19 | The maximum transmission/reception rate is CLKOUT/6 for external serial clock sources asynchronous to CLKOUT, and CLKOUT/4 for external sources synchronous to CLKOUT.                                                                                                                                                                                                            |

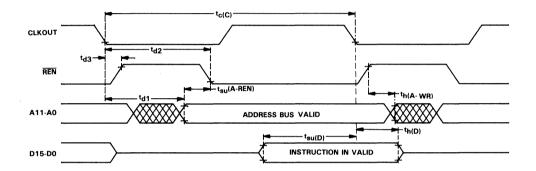

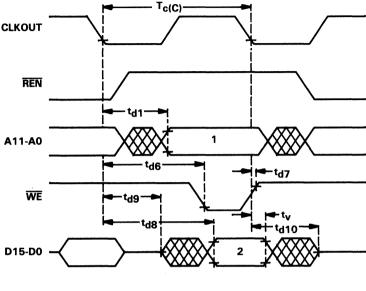

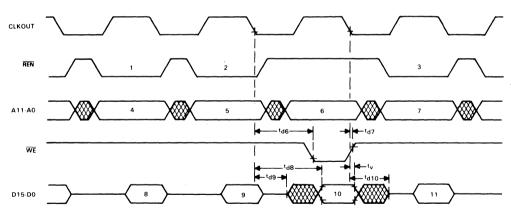

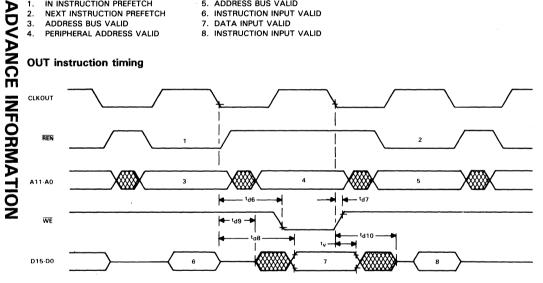

6-10

in the third equation, middle of the page, change 2.4 to 24 in the second line so that it reads:

The write enable access time is:

$$t_{c(C)}$$

-  $t_{d6}$  -  $t_{d7}$  = 156.25 - 1/2  $t_{c(C)}$  - 12 - 12

= 78.1 - 24

= 54.1 ns

A-19

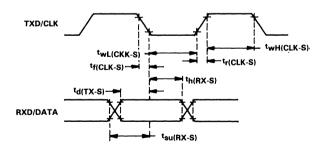

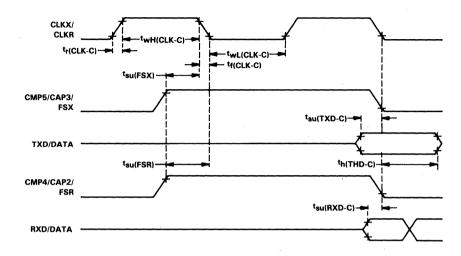

The timing for  $t_{h(TXD-C)}$  is for unsynchronized operation of the port.  $t_{h(TXD-C)}$  is the duration of the interval where TXD is valid. This is  $t_{wL} + t_{wH} - 0.25 \times t_{c(C)} - 20$  ns.

The values for  $t_{wL(CLK-C)}$  and  $t_{wH(CLK-C)}$  assume synchronized operation of the serial port. CLKX should be synchronized to CLKOUT to within 5 ns to achieve proper operation of the port at full speed.

A-24

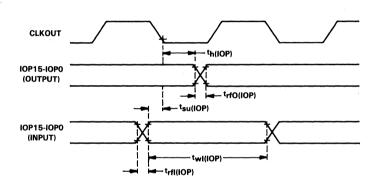

In the **bit I/O timing** diagram,  $t_{h(IOP)}$  should read  $t_{d(IOP)}$ .

A-26

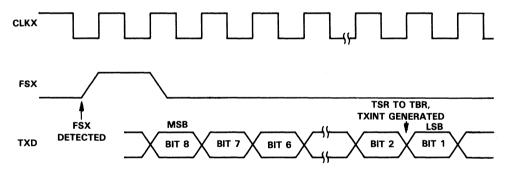

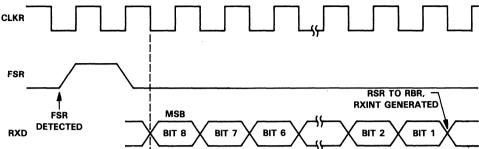

Note that the externally generated FSX and FSR signal durations must be less than the duration of the data word. If this is violated, another transmission occurs. Also, FSX and FSR must be low-to-high transistions in order to mimic their internally generated counterparts.

E-72

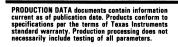

The device has no input for adding a crystal. It does have internal circuitry for this purpose, but no pin is brought out to simply add a crystal and provide CLKIN. Section 6.1.2 on page 6-5 describes typical circuits for CLKIN generation.

F-12

Note that once the RBIT is programmed, the device functions only in the microcomputer mode.

## Contents

| Seci  | tion                                         | Page |

|-------|----------------------------------------------|------|

| 1     | Introduction                                 | 1-1  |

| 1.1   | Control System Design Considerations         | 1-3  |

| 1.2   | TMS320C14/E14 Description                    |      |

| 1.3   | Key Features                                 | 1-6  |

| 2     | Pinout and Signal Descriptions               | 2-1  |

| 2.1   | Pinouts                                      | 2-2  |

| 2.2   | Signal Descriptions                          | 2-3  |

| 3     | Architecture                                 | 3-1  |

| 3.1   | Architectural Overview                       | 3-2  |

| 3.1.1 | Processing Hardware                          |      |

| 3.1.2 | I/O Structure                                |      |

| 3.1.3 | I/O Peripherals                              |      |

| 3.1.4 | On-Chip Peripheral Register Mapping          | 3-8  |

| 3.1.5 | On-Chip/Off-Chip Peripheral Selection        | 3-8  |

| 3.2   | System Control                               |      |

| 3.2.1 | Program Counter and Stack                    | 3-12 |

| 3.2.2 | Microprocessor/Microcomputer Modes           | 3-14 |

| 3.2.3 | Reset                                        | 3-15 |

| 3.2.4 | Status Register                              |      |

| 3.2.5 | Interrupts                                   |      |

| 3.3   | Central Arithmetic Logic Unit (CALU)         |      |

| 3.3.1 | Shifters                                     | 3-23 |

| 3.3.2 | ALU and Accumulator                          | 3-24 |

| 3.3.3 | Multiplier, T and P Registers                |      |

| 3.4   | Memory Organization                          |      |

| 3.4.1 | Data Memory                                  |      |

| 3.4.2 | Program Memory                               |      |

| 3.4.3 | Auxiliary Registers                          |      |

| 3.4.4 | Memory Addressing Modes                      |      |

| 3.5   | Bit Selectable I/O Port                      |      |

| 3.5.1 | Configuring Data Direction                   | 3-32 |

| 3.5.2 | L/O Port Status and Control                  | 3-34 |

| 3.5.2 | I/O Port Status and Control                  | 3-34 |

| 3.6   | Timers                                       | 3-35 |

| 3.6.1 |                                              |      |

| 3.6.2 | Watchdog Timer                               |      |

| 3.6.3 | General Purpose Timers                       |      |

| _     | Serial Port Baud Rate Generator (as a timer) | 3-42 |

| 3.7   | Event Manager                                | 3-43 |

| 3.7.1 | Compare Subsystem                            |      |

| 3.7.2 | Capture Subsystem                            |      |

| 3.8   | Serial Port                                  |      |

| 3.8.1 | Serial Control Register                      | 3-59 |

| 3.8.2 | Serial Port Baud Rate Generator              |      |

| 3.8.3 | Asynchronous Mode                            |      |

| 3.8.4 | Synchronous Mode                             | 3-69 |

| 3.8.5<br>3.8.6           | Codec Mode                                                                   |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 3-74<br>3-79             |

|--------------------------|------------------------------------------------------------------------------|-------|---|----|---|-------|----|---|---|----|---|---|-----|---|---|--------------------------|

| <b>4</b><br>4.1<br>4.1.1 | Assembly Language Instruction Memory Addressing Modes Direct Addressing Mode |       |   |    |   |       |    |   |   |    |   |   |     |   |   | <b>4-1</b><br>4-2<br>4-2 |

| 4.1.2                    | Indirect Addressing Mode                                                     |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 4-4                      |

| 4.1.3                    | Immediate Addressing Mode                                                    |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 4-5                      |

| 4.2                      | Instruction Set                                                              |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 4-7                      |

| 4.2.1                    | Symbols and Abbreviations                                                    |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 4-7                      |

| 4.2.2                    | Instruction Set Summary                                                      |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 4-8                      |

| 4.3                      | Individual Instruction Descriptions                                          |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 4-11                     |

| 5                        | Software Applications                                                        |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-1                      |

| 5.1                      | Processor Initialization                                                     |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-2                      |

| 5.1.1                    | Header File Defining Constants                                               |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-3                      |

| 5.2                      | Interrupt Management                                                         |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-14                     |

| 5.3                      | Memory Management                                                            |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-17                     |

| 5.4                      | Logical and Arithmetic Operations                                            |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-19                     |

| 5.4.1                    | Bit Manipulation                                                             |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-19                     |

| 5.4.2                    | Overflow Management                                                          |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-20                     |

| 5.4.3                    | Scaling                                                                      |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-21                     |

| 5.4.4                    | Convolution Operations                                                       |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-22                     |

| 5.4.5                    | Multiplication                                                               |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-23                     |

| 5.4.6                    | Division                                                                     |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-26                     |

| 5.4.7                    | Addition                                                                     |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-29                     |

| 5.4.8                    | Floating-Point Arithmetic                                                    |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-30                     |

| 5.5                      | PID Control                                                                  |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-32                     |

| 5.6                      | PWM Generation                                                               |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-34                     |

| 5.7                      | Speed/Position Measurement                                                   |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 5-36<br>3-40             |

| 5.8<br>5.8.1             | Using the Serial Port                                                        |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 3-40                     |

| 5.6.1                    | Asynchronous Configuration .                                                 | <br>• | • | ٠. | • | <br>• |    | • | • |    | • | • | • • | • | • | 3-41                     |

| 6                        | Hardware Applications                                                        |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-1                      |

| 6.1                      | System Control Circuitry                                                     | <br>• | ٠ |    | ٠ | <br>• | ٠. | ٠ | • |    | ٠ | • |     | ٠ | • | 6-3                      |

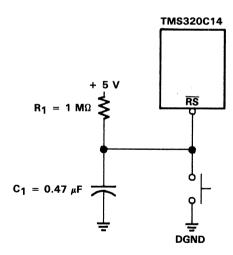

| 6.1.1                    | Powerup Reset Circuit                                                        |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-3<br>6-5               |

| 6.1.3                    | Crystal Oscillator Circuit                                                   |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-5<br>6-7               |

| 6.2                      | MC/MP Mode Configurations External Memory Interfacing                        |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-8                      |

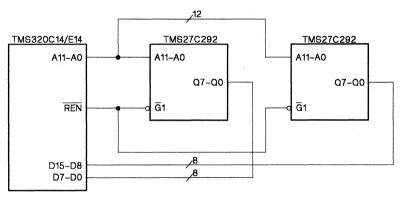

| 6.2.1                    | Program ROM Expansion                                                        | <br>• |   |    | • | <br>• | ٠. | • | • | ٠. | • | • |     | • | • | 6-11                     |

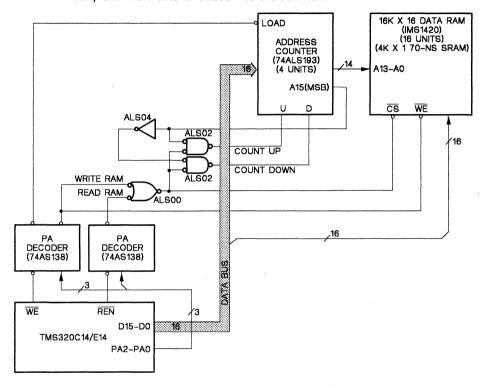

| 6.2.2                    | Data RAM Expansion                                                           |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-12                     |

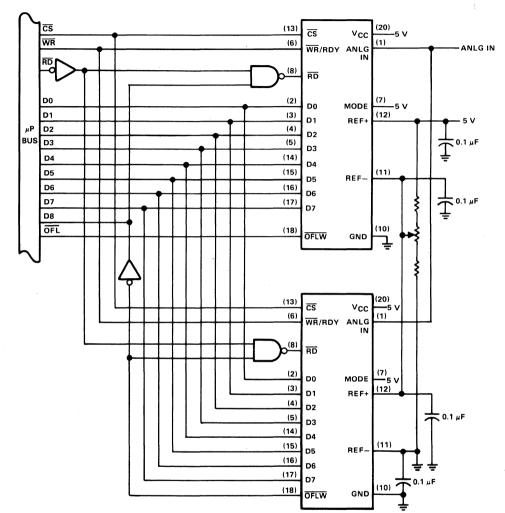

| 6.3                      | External Peripheral Interfacing                                              |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-14                     |

| 6.3.1                    | A/D Interface                                                                |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-14                     |

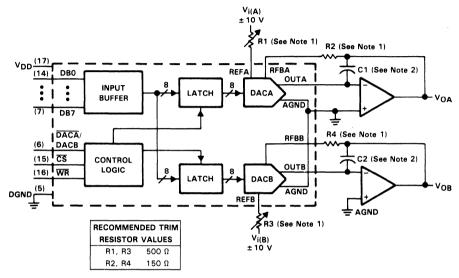

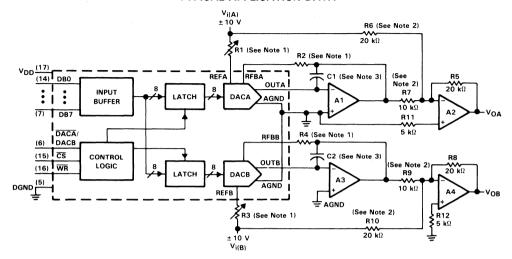

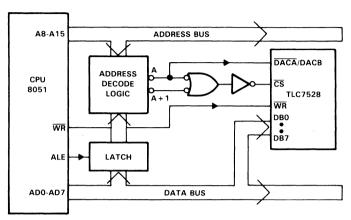

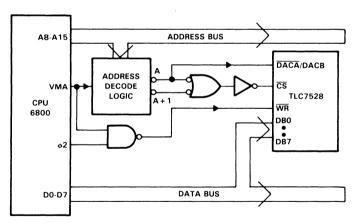

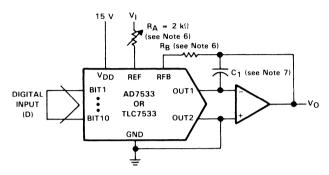

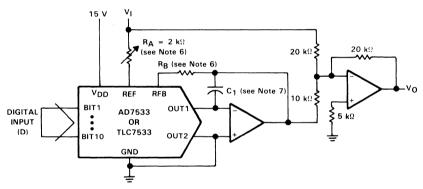

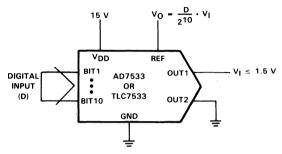

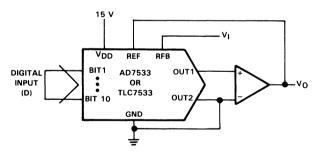

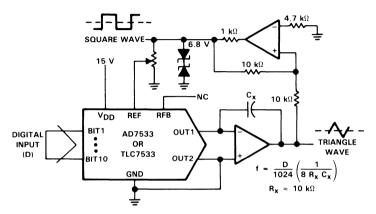

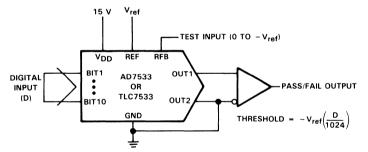

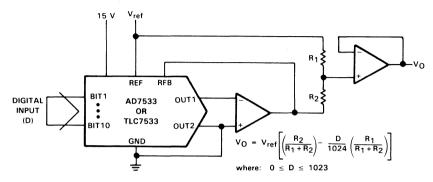

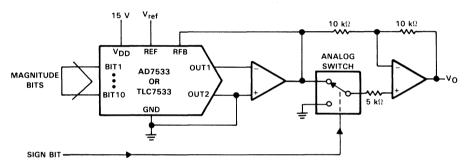

| 6.3.2                    | D/A Interface                                                                |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-16                     |

| 6.3.3                    | Codec Interface                                                              |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-16                     |

| 6.3.4                    | RS-232 Interface                                                             |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-19                     |

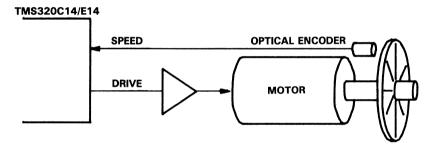

| 6.3.5                    | Optical Encoder Interface                                                    |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-20                     |

| 6.3.6                    | XDS Design Considerations .                                                  |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-21                     |

| 6.4                      | XDS Design Considerations . System Applications                              |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-24                     |

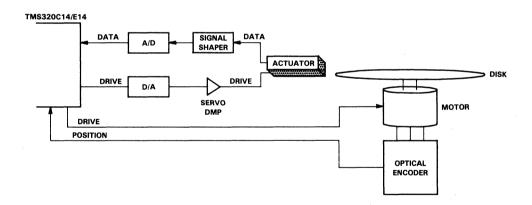

| 6.4.1                    | Disk Drive Control                                                           |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-24                     |

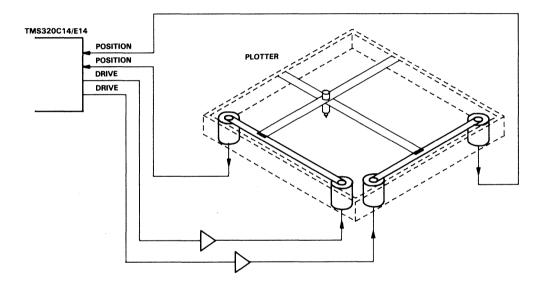

| 6.4.2                    | Plotter Control                                                              |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-25                     |

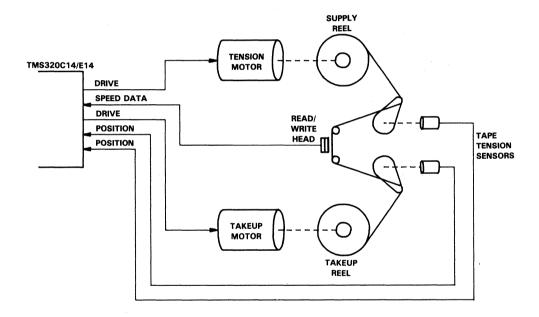

| 6.4.3                    | Tape Drive Control                                                           |       |   |    |   |       |    |   |   |    |   |   |     |   |   | 6-26                     |

| 6.4.4                    | AC Motor Control                                                             | <br>  |   |    |   | <br>  |    |   |   |    |   |   | ٠.  |   |   | 6-27                     |

| Α | First-Generation TMS320C14/E14 Data Sheet  | A-1 |

|---|--------------------------------------------|-----|

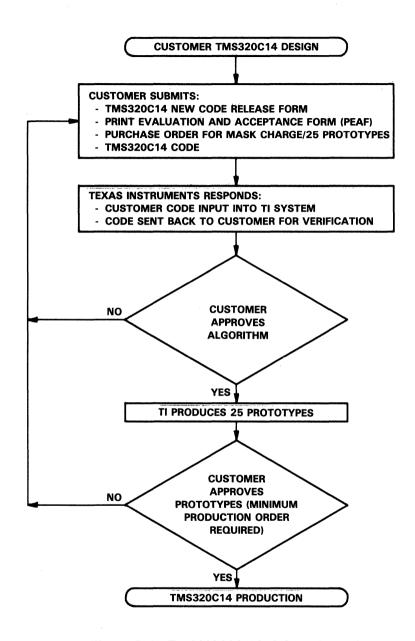

| В | ROM Codes                                  | B-1 |

| С | Quality and Reliability                    | C-1 |

| Ď | Development Support/Part Order Information | D-1 |

| E | External Peripherals, Sockets and Crystals | E-1 |

| F | Programming the TMS320E14 EPROM Cell       | F-1 |

## Illustrations

| Figui        | re                                                                      | Page   |

|--------------|-------------------------------------------------------------------------|--------|

| 1-1          | TMS320 Family Evolution                                                 | 1-2    |

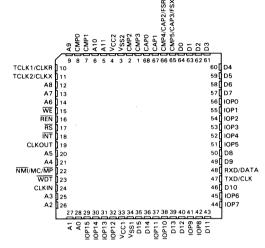

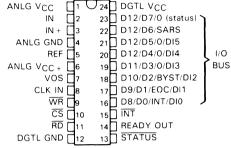

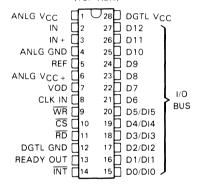

| 2-1          | TMS320C14/E14 Pin Assignments                                           | 2-2    |

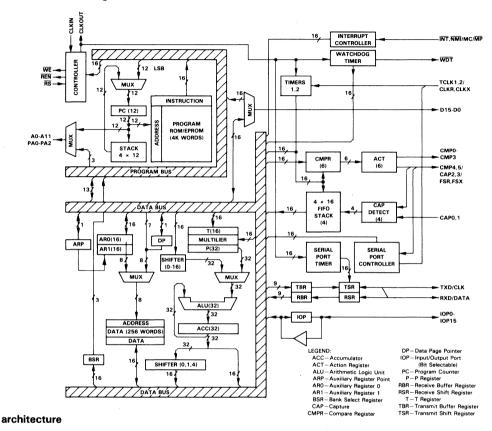

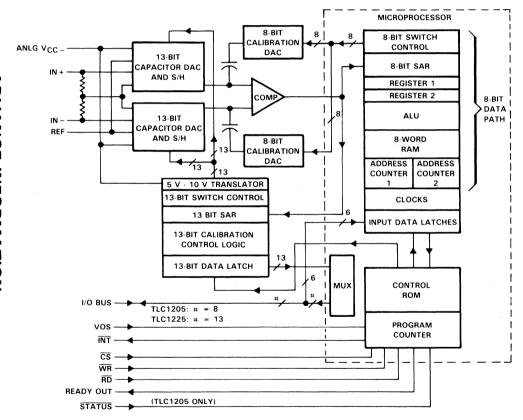

| 3-1          | TMS320C14/E14 Functional Block Diagram                                  | 3-3    |

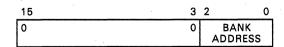

| 3-2          | Bank Select Register                                                    |        |

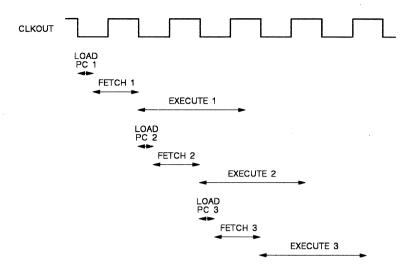

| 3-3          | Instruction Pipeline Operation                                          | 3-13   |

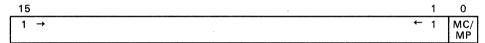

| 3-4          | Syscon Register                                                         | 3-13   |

| 3-5          | Status Register Organization                                            | 3-17   |

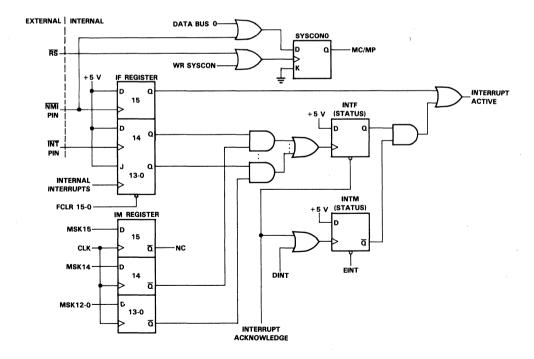

| 3-6          | Interrupt Subsystem                                                     | 3-12   |

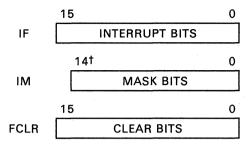

| 3-7          | IF/IM/FCLR Register Relationship                                        | 3-10   |

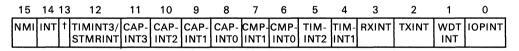

| 3-8          | IF/IM/FCLR Register Relationship IF Register                            | 3-20   |

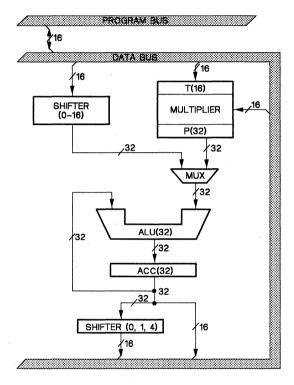

| 3-9          | Central Arithmetic Logic Unit (CALII)                                   | 3-20   |

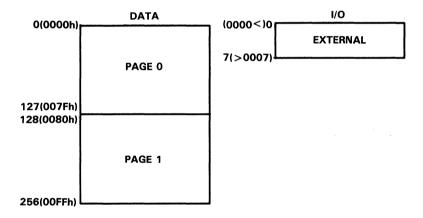

| 3-10         | Central Arithmetic Logic Unit (CALU)  Data Memory Map                   | 3.27   |

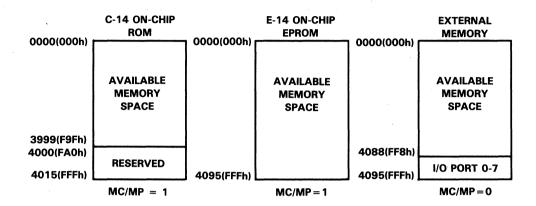

| 3-10         | Program Memory Map                                                      | 3-22   |

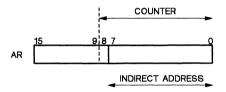

| 3-12         | Auxiliary Register Counter                                              |        |

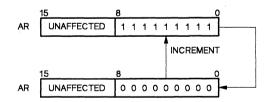

| 3-12         | Indirect Addressing Autoincrement                                       | 3 20   |

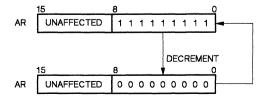

| 3-14         | Indirect Addressing Autodecrement                                       | 2 20   |

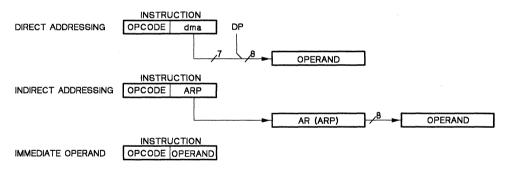

| 3-15         | Methods of Instruction Operand Addressing                               |        |

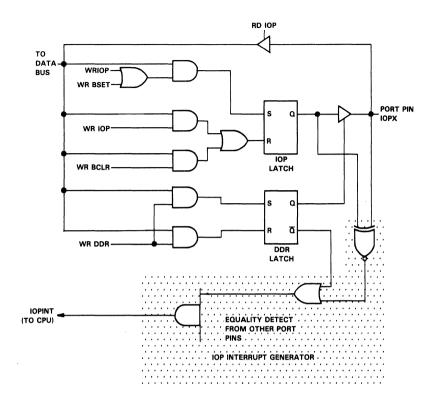

| 3-16         | Bit Selectable I/O Port                                                 | 2 22   |

| 3-10         | Configuring the IOP Register                                            | 2 24   |

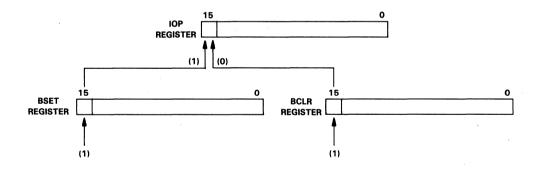

| 3-17         | Watchdog Timer Module                                                   | 2 20   |

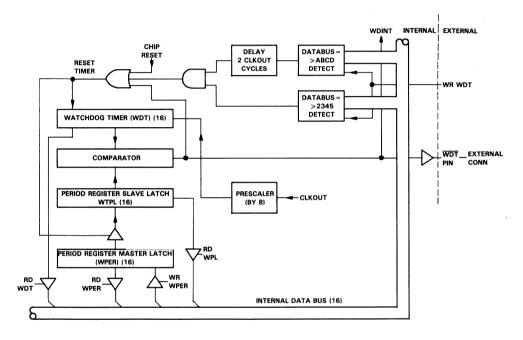

| 3-10         | Timer1 and Timer2 Block Diagram                                         | 3-40   |

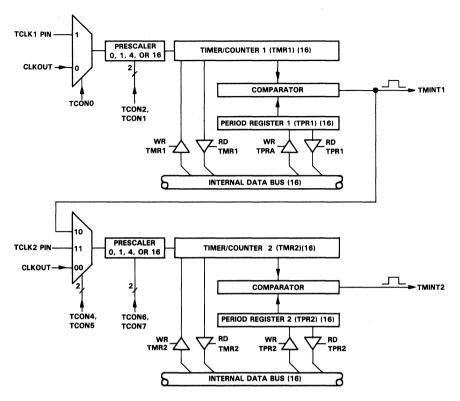

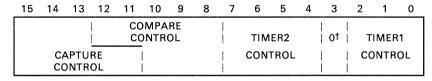

| 3-19         | TCON Parieter Timer Bit Configuration                                   | 2 41   |

| 3-20         | TCON Register Timer Bit Configuration                                   | 3-41   |

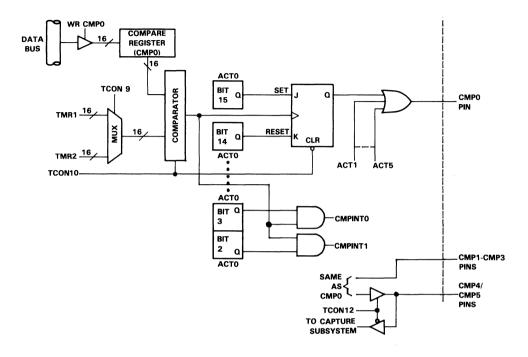

| 3-21         | Compare Module                                                          | 3-45   |

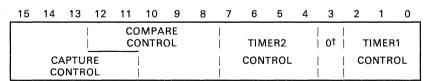

| 3-22         | TCON Register Compare Bit Configuration                                 | 3-40   |

| 3-23<br>3-24 | ACTx Register Configuration                                             | 3-40   |

|              | CMPs. Big Lavel                                                         | 3-49   |

| 3-25         | CMPx Pin Level                                                          | 3-50   |

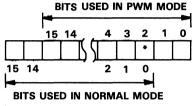

| 3-26         | TMR Bit Configuration                                                   | 3-51   |

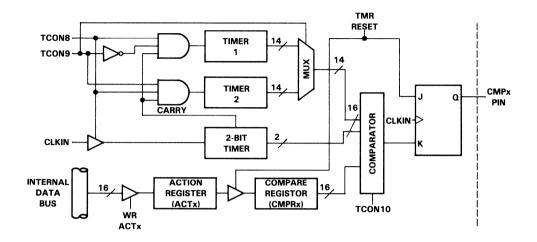

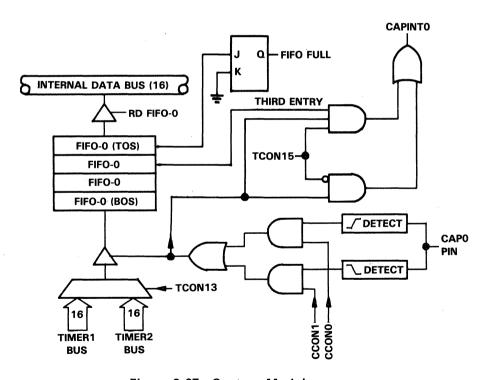

| 3-27         | Capture Module                                                          | 3-52   |

| 3-28         | TCON Register Capture Bit Configuration                                 |        |

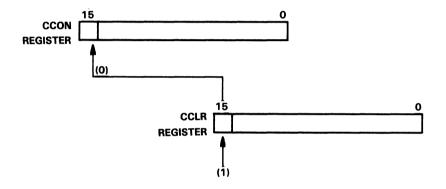

| 3-29         | CCON and CCLR Registers                                                 | 3-55   |

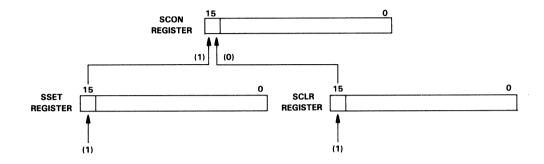

| 3-30         | SCON Register Control                                                   |        |

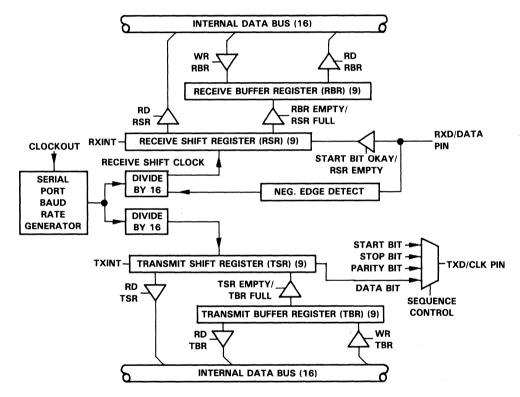

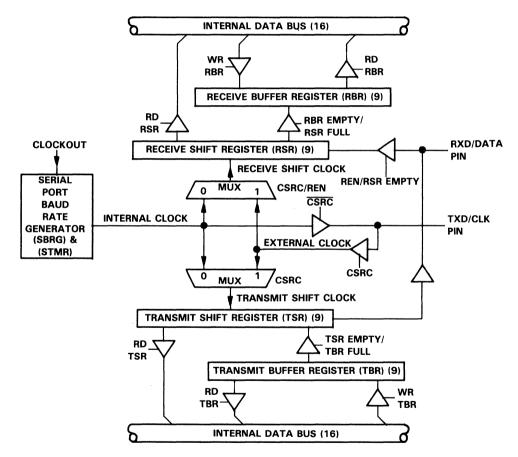

| 3-31         | Serial Port in Asynchronous Operation                                   | 3-65   |

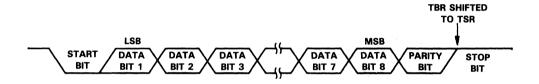

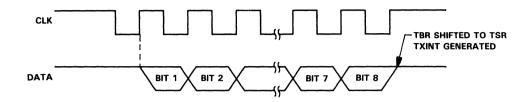

| 3-32         | Asynchronous Transmission of Eight Bits Plus Parity                     | 3-66   |

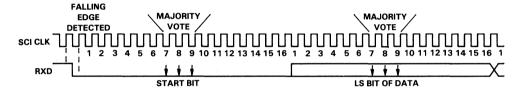

| 3-33         | Start Bit Detection                                                     | 3-67   |

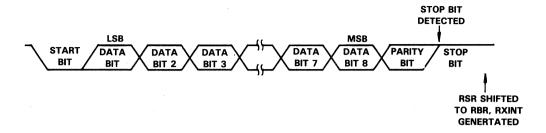

| 3-34         | Asychronous Reception of Eight Bits Plus Parity                         | 3-68   |

| 3-35         | Serial Port in Synchronous Operation                                    |        |

| 3-36         | Master Mode Single Synchronous Transmission with 8 Data Bits, No Parity |        |

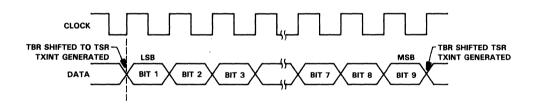

| 3-37         | Synchronous Continuous Transmission with 9 Data Bits, No Parity         |        |

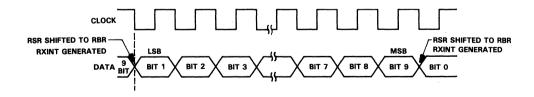

| 3-38         | Synchronous Reception with 9 Data Bits, No Parity                       | 3-72   |

| 3-39         | Master Mode Single Synchronous Reception with 8 Data Bits, No Parity    | 3-73   |

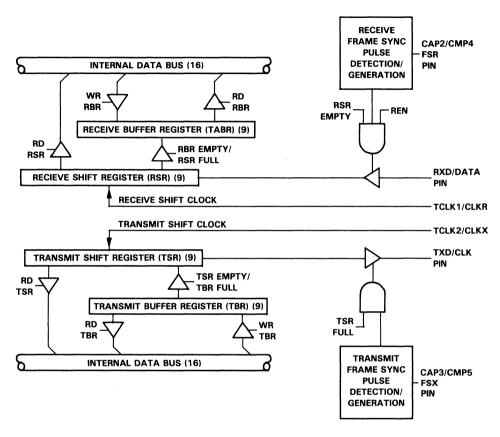

| 3-40         | Serial Port in Codec Operation                                          | 3-75   |

| 3-41         | Codec Transmit Timing for External Framing                              | 3-76   |

| 3-42         | Codec Receive Timing for External Framing                               | . 3-78 |

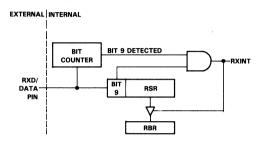

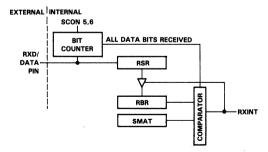

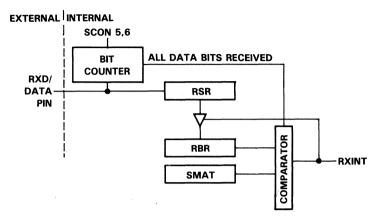

| 3-43         | Serial Port Using Address Detect Protocol                               | 3-80   |

| 3-44         | Address Detect Reception                                                | . 3-80 |

| 3-45         | Serial Port Using Address Match Protocol                                | 3-82   |

| 3-46         | Address Match Reception                                                 | 3-82   |

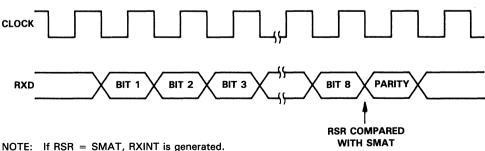

| 4-1          | Direct Addressing Block Diagram                                         | 4-3    |

| 5-1  | Long Division and SUBC Division                     | 5-27 |

|------|-----------------------------------------------------|------|

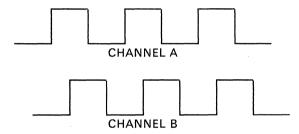

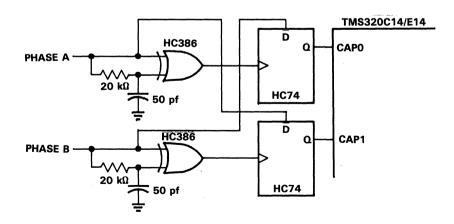

| 5-2  | Dual Channel Optical Encoder Outputs                |      |

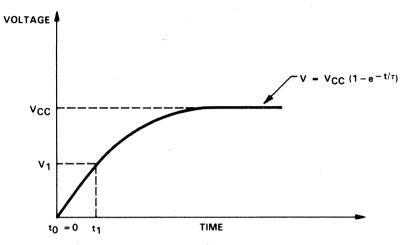

| 6-1  | Powerup Reset Circuit                               |      |

| 6-2  | Voltage on TMS320C14/E14 Reset Pin                  |      |

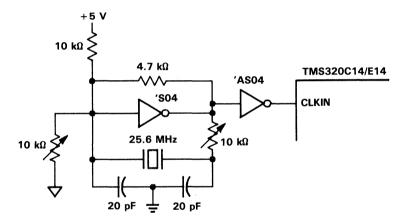

| 6-3  | Parallel Resonant Crystal Oscillator Circuit        | 6-5  |

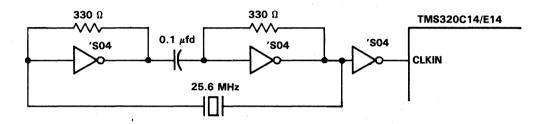

| 6-4  | Series Resonant Crystal Oscillator Circuit          | 6-6  |

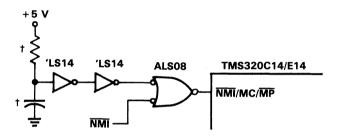

| 6-5  | Mode Control Circuit                                |      |

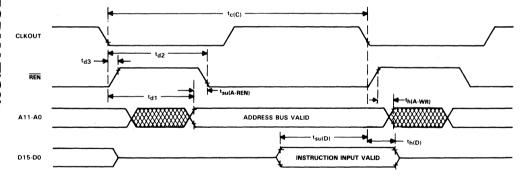

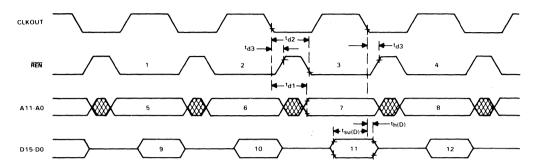

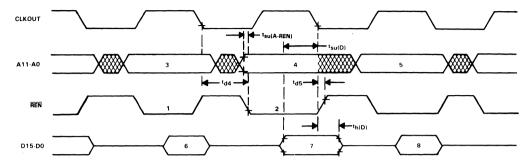

| 6-6  | Memory Read Timing                                  |      |

| 6-7  | Memory Write Timing (TBLW Instruction)              | 6-11 |

| 6-8  | Minimum Program ROM Expansion                       | 6-12 |

| 6-9  | Data RAM Expansion                                  | 6-13 |

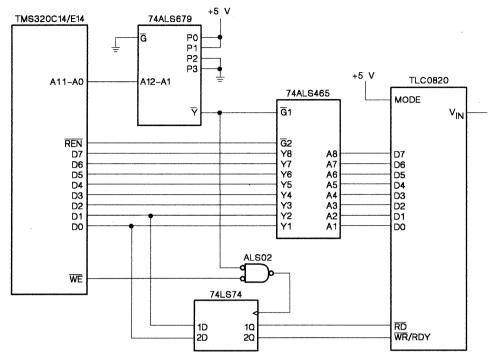

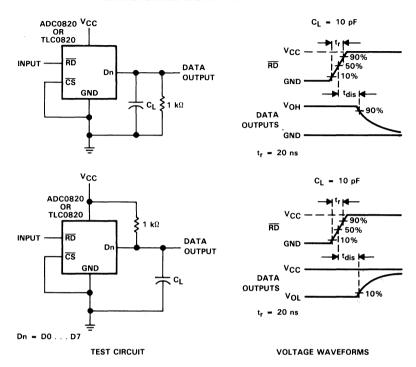

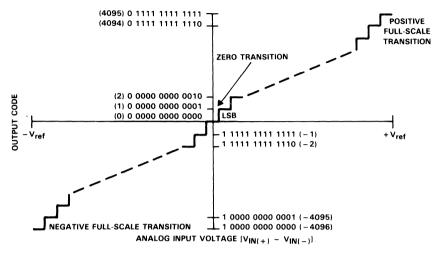

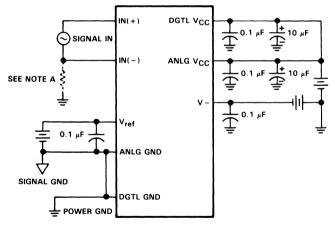

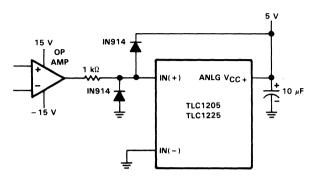

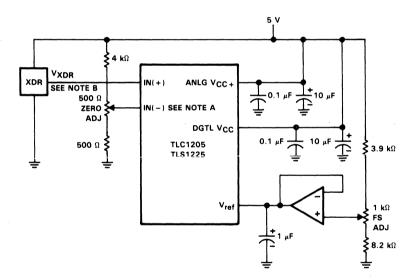

| 6-10 | A/D Converter to TMS320C14/E14 Interface            | 6-15 |

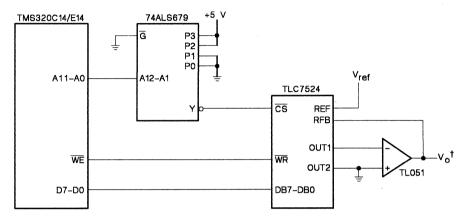

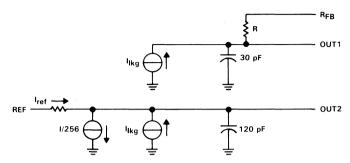

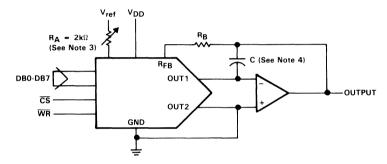

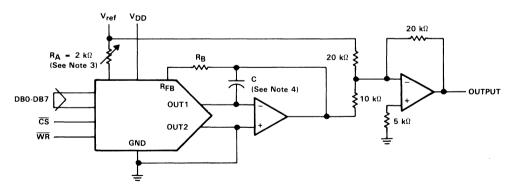

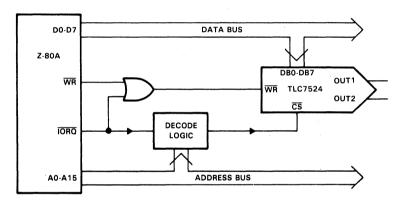

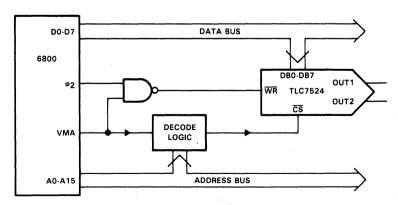

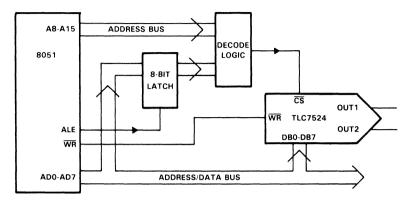

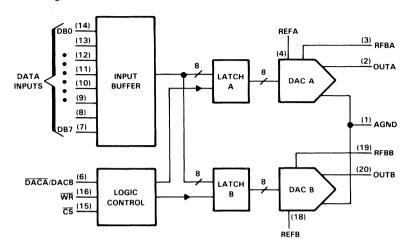

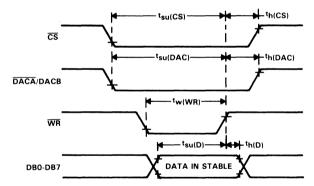

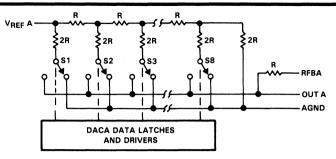

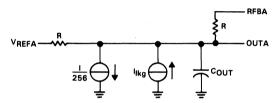

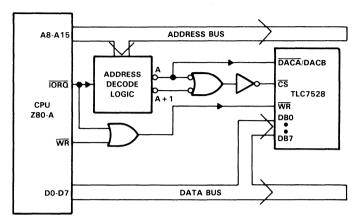

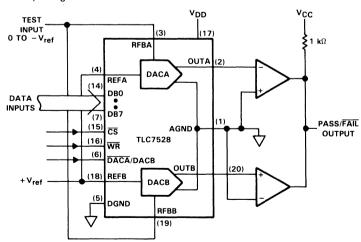

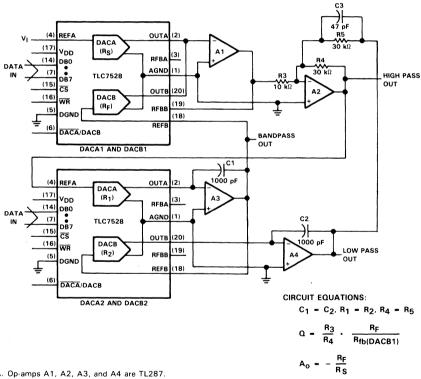

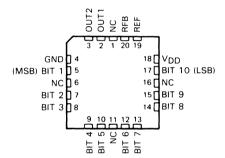

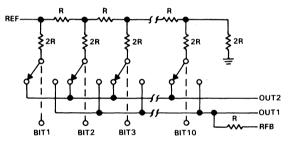

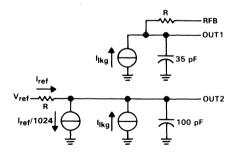

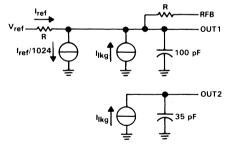

| 6-11 | D/A Converter to TMS320C14/E14 Interface            | 6-16 |

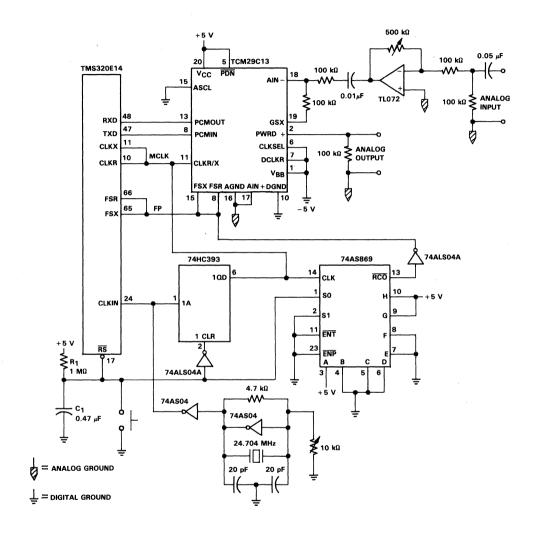

| 6-12 | Interface of TMS320C14/E14 to TCM29C13 Codec        | 6-18 |

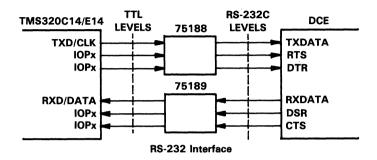

| 6-13 | RS-232 Interface                                    | 6-20 |

| 6-14 | Optical Encoder Interface                           |      |

| 6-15 | Disk Drive Control                                  |      |

| 6-16 | Plotter Control                                     |      |

| 6-17 | Tape Drive Control                                  |      |

| 6-18 | AC Motor Control                                    |      |

| B-1  | TMS320C14 ROM Code Flowchart                        |      |

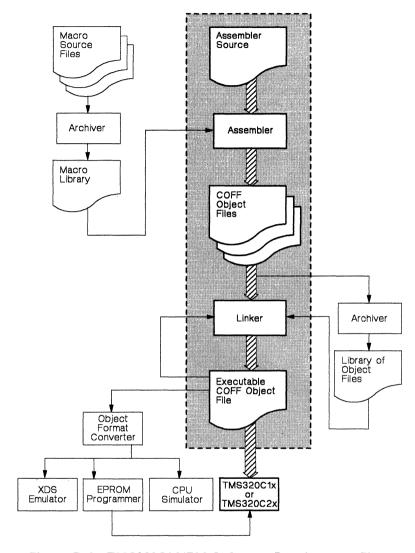

| D-1  | TMS320C14/E14 Software Development Flow             |      |

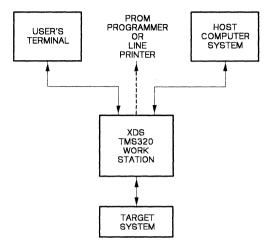

| D-2  | TMS320C14/E14 XDS/22 System Configuration           |      |

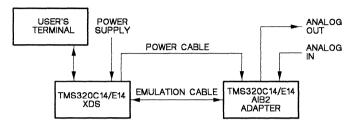

| D-3  | TMS320C14/E14 AIB2 System Configuration             |      |

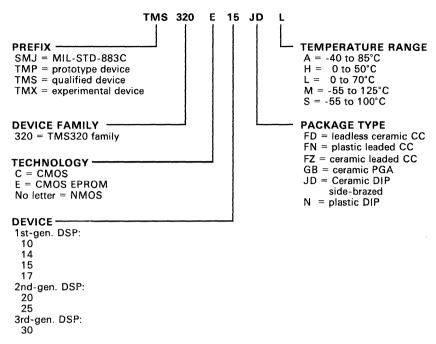

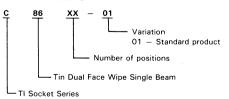

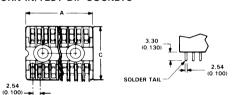

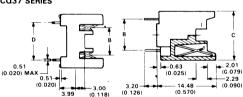

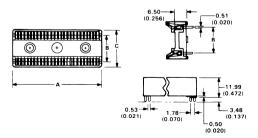

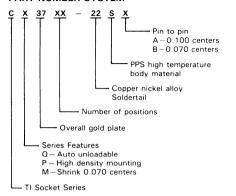

| D-4  | TMS320 Device Nomenclature                          |      |

| E-1  | Crystal Connection                                  |      |

| F-1  | EPROM Adaptor Socket                                |      |

| F-2  | EPROM Programming Data Format                       |      |

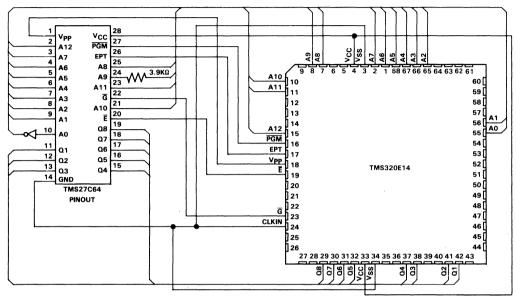

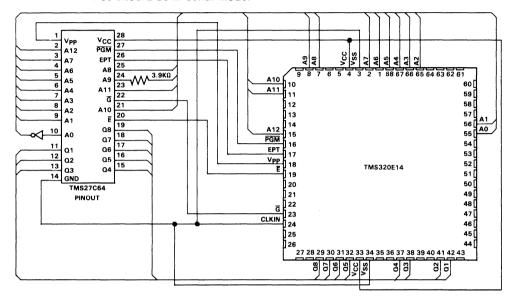

| F-3  | TMS320E14 EPROM Conversion to TMS27C64 EPROM Pinout |      |

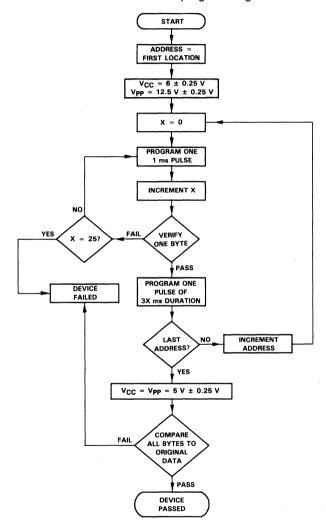

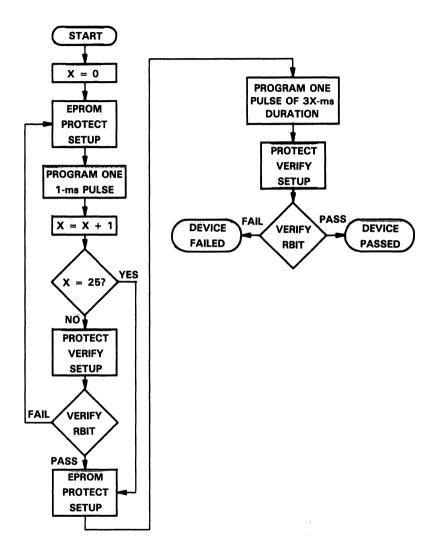

| F-4  | Fast Programming Flowchart                          |      |

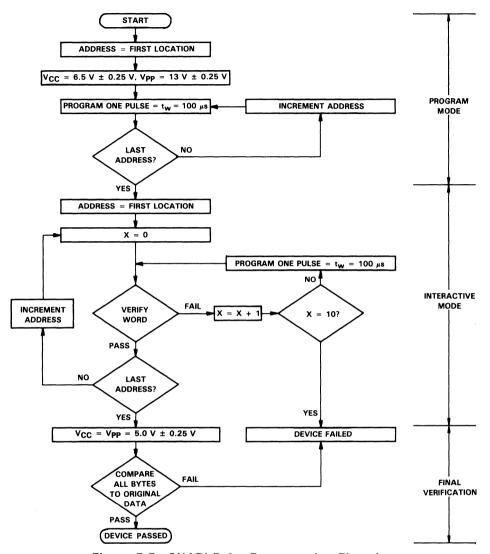

| F-5  | SNAP! Pulse Programming Flowchart                   |      |

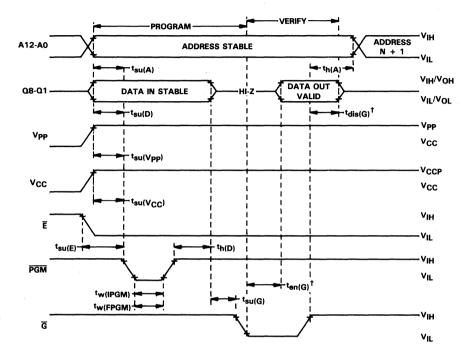

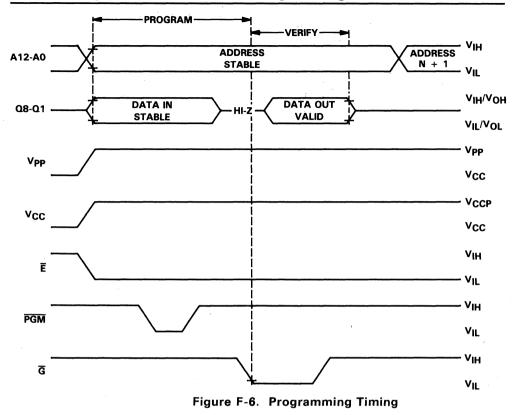

| F-6  | Programming Timing                                  |      |

| F-7  | EPROM Protection Flowchart                          |      |

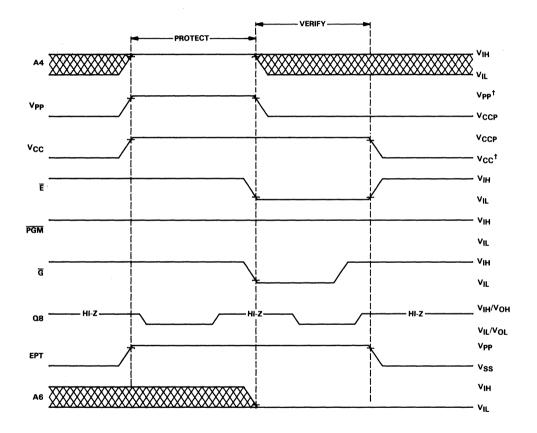

| F-8  | EPROM Protection Timing                             | F-15 |

|      |                                                     |      |

|      | Tables                                              |      |

| Table | ,                                          | Page   |

|-------|--------------------------------------------|--------|

| 2-1   | TMS320C14/E14 Signal Descriptions          | . 2-3  |

| 3-1   | TMS320C14/E14 Processing Hardware Summary  | . 3-5  |

| 3-2   | I/O Register Map                           | . 3-8  |

| 3-3   | Peripheral Registers                       | . 3-10 |

| 3-4   | Registers Configuration on Reset           | . 3-16 |

| 3-5   | Status Register Field Definitions          |        |

| 3-6   | IF Register Description                    | . 3-21 |

| 3-7   | Accumulator Results of a Logical Operation | . 3-25 |

| 3-8   | I/O Port Register Summary                  |        |

| 3-9   | Timer Module Register Summary              | . 3-37 |

| 3-10  | TCON Register Timer Description            | . 3-41 |

| 3-11  | Compare Subsystem Register Summary         |        |

| 3-12  | TCON Compare Register Description          | . 3-46 |

| 3-13  | Action Register Description                | . 3-47 |

| 3-14 | PWM Resolution Bits Comparison                         | 3-49 |

|------|--------------------------------------------------------|------|

| 3-15 | Capture Subsystem Register Summary                     | 3-52 |

| 3-16 | TCON Capture Register Description                      | 3-54 |

| 3-17 | CCON Register Description                              | 3-56 |

| 3-18 | Serial Port Register Summary                           | 3-59 |

| 3-19 | SCON Register Description                              | 3-60 |

| 3-20 | Serial Port Key Default Settings                       | 3-63 |

| 3-21 | SBRG Value For Standard Baud Rates                     | 3-64 |

| 4-1  | Instruction Symbols                                    | 4-7  |

| 4-2  | Instruction Set Summary                                | 4-8  |

| 5-1  | I/O Register Map                                       | 5-2  |

| 6-1  | XDS/Target Device Timing Delays                        | 6-21 |

| 6-2  | XDS/Device DC Loading                                  | 6-22 |

| C-1  | Microprocessor and Microcontroller Tests               | C-5  |

| C-2  | Transistor Complement                                  | C-5  |

| D-1  | TMS320C14/E14 Digital Signal Processor Part Numbers    | D-11 |

| D-2  | TMS320C14/E14 Support Tool Part Numbers                | D-11 |

| E-1  | Commonly Used Crystal Frequencies                      | E-72 |

| F-1  | TMS320E14 Programming Mode Levels                      | F-6  |

| F-2  | TMS320E14 EPROM Protect and Protect Verify Mode Levels | F-12 |

## Section 1

# Introduction

The TMS320C14 and TMS320E14 are members of Texas Intruments first-generation TMS320 digital signal processor (DSP) family. The TMS320C14/E14 has been specifically designed for control system applications and are the first devices that combine the high performance of a DSP with the on-chip peripherals of a microcontroller. The TMS320C14/E14, at 25.6 MHz, offer 10 to 20 times the speed of traditional 16-bit microcontrollers and microprocessors.

The DSP engine of the TMS320C14/E14 provides analog designers, for the first time, a digital solution without sacrificing the precision and performance of their systems. In fact, system performance can be enhanced through the use of advanced control algorithms. These include adaptive control, Kalman filtering, and state controllers. The TMS320C14/E14 offer the reliability and programmability of a digital solution. Analog control systems, on the other hand are hard-wired solutions, and can experience performance degradation due to aging and other environmental factors.

The high speed central processing unit (CPU) of the TMS320C14/E14 allows the digital designer to process algorithms in real time as opposed to approximation results via look-up tables. System performance is thus dramatically increased. The general purpose instruction set of the TMS320C14/E14 coupled with the extensive development support for the TMS320 DSP family reduces development time, and provides the same ease of use as traditional 8-and 16-bit microcontrollers.

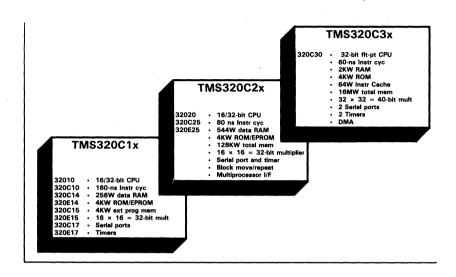

The TMS320 family architecture has been available for more than six years providing users with the security of a standard architecture. The TMS320 family has now expanded into three generations of processors: TMS320C1x, TMS320C2x, and TMS320C3x (see Figure 1-1). Many features are common among these generations. Some specific features are added in each processor to provide different cost/performance tradeoffs. Software compatibility is maintained throughout the family to protect the user's investment in architecture. Each processor has software and hardware tools to facilitate rapid design.

This section includes the following information listed below:

- Control System Design Considerations (Section 1.1 page 1-3)

- TMS320C14/E14 Description (Section 1.2 on page 1-5)

- Key Features (Section 1.3 on page 1-6)

Figure 1-1. TMS320 Family Evolution

## 1.1 Control System Design Considerations

Traditional control systems have been implemented with analog components, and designers have had to learn to live with these systems. Analog components exhibit the disadvantages of temperature drift and component aging. An analog solution for an application requires that hardware be designed to perform a specific function. Modifications and upgrades for such hardware mean labor-intensive projects. These problems have prompted a growing trend toward implementing control systems in digital form.

In a digital control system, the actual processing of the intput signal is done in digital form by a microprocessor. However, the input signal has to be converted into digital form by an analog-to-digital (A/D) converter. The output of the microprocessor has to be converted again (D/A) to analog form to provide a control function.

Although 8/16-bit microcontrollers have the necessary peripherals that would seem to provide a single chip solution for a digital controller, they lack both the performance and the architecture needed to process control signals. For years control designers have worked around this problem by using look-up tables. In this method, the processing of control signals is done in non-real-time on large computers and the results are programmed in the microcontroller's memory. When an input signal is received, the corresponding result is looked up from memory and routed from the processor. The algorithms that can be used with this kind of approach are usually simpler and limited to single input, single output systems.

In some cases realtime processing of control signals is implemented with traditional microcontrollers/microprocessors. These controllers are restricted to low bandwidth systems. In spite of these limitations, most digital control systems implemented today use 8/16-bit general purpose microprocessors/microcontrollers. Designers of high precision and high bandwidth systems find solutions provided by these CPUs far from optimum. They still have to rely upon analog solutions to provide the performance needed for their systems.

To provide an optimum solution for a digital controller, a processor must have the architecture, performance, and peripherals necessary for digital control systems. The input signal is not processed continuously in digital control systems, but rather sampled at discrete intervals. The discrete samples are then processed by the controller. Selection of a sampling interval is critical and is usually chosen to be six to ten times the bandwidth of the system. For realtime performance the processor should be able to process the sample before the arrival of the next sample. Most digital control and DSP algorithms are made up of many multiply and accumulate terms and the processor should be able to perform these operations very rapidly. For this reason, the TMS320 family of processors incorporate a hardware multiplier to perform a multiply in only one clock cycle.

In addition to having realtime capability, the controller should have the appropriate architecture. Conversion of a continuous signal into discrete form results in loss of resolution. This is often referred to as quantization error. Therefore, the controller should have a large wordlength to reduce quantization error. Additional errors are also introduced due to processing of signals. As an example, if a 16 x 16 multiply is done, the result is 32 bits. However,

if only 16 bits are stored, an error is induced because of lack of precision. This is referred to as truncation error. The TMS320 family minimizes the effects of truncation by employing 32-bit precision for storing intermediate results.

Additional truncation and quantization errors can be introduced if the numbers are not scaled properly (i.e., all significant bits are not maintained, and there are too many leading or trailing zeros). To maintain the correct precision, shifters should be available that do not require CPU overhead. Finally, numeric processing of control signals can create overflows, causing the accumulator to wrap-around and suddenly go from the most positive value to the most negative with disastrous consequences for the control system. In the TMS320 family, the accumulator can be prevented from wrapping around, and the value is kept at the most positive or most negative value. This simulates the saturation of an analog system.

The final requirement for an optimum controller is to provide all the necessary peripherals on a single chip. Different members of the TMS320 family have been optimized for specific signal processing applications. The TMS320C14/E14 integrates peripherals on-chip that have been optimized for implementing digital controllers.

## 1.2 TMS320C14/E14 Description

The TMS320C14/E14 is a DSP that meets the requirements for an optimum digital controller. Using a 25.6 MHz clock input, the TMS320C14/E14 can execute 6.4 million instructions per second. Almost all instructions are executed in a single cycle, including multiplication. This high performance allows execution of very complex control algorithms such as adaptive control and Kalman filters in realtime. Very high sampling rates can also be implemented to minimize loop delays.

The TMS320C14/E14 has been optimized for digital control system applications and has all the architectural features necessary for high-speed signal processing. The device possesses all the peripherals needed to provide a sinale-chip solution in control system applications. Based on the TMS320 family's first-generation CPU (the industry standard TMS320C10), the device includes 256 words of RAM and 4K words of ROM or EPROM. Also integrated on-chip are additional peripheral functions for control systems and other applications requiring a single-chip stand-alone DSP controller. These peripherals include bit-selectable I/O ports, a serial port with USART and codec-compatible modes. six high-precision pulse width modulation (PWM) four capture inputs, and four independent timers. TMS320C14/E14 devices are manufactured using CMOS technology, achieving a power dissipation of less than one sixth that of a comparable NMOS device.

The instruction set of the TMS320C14/E14 is source and object code compatible with the other members of the TMS320C1x family, allowing users to protect their investment in TMS320C1x software.

The TMS320C14/E14 architecture is also optimized for processing control signals. A 16-bit wordlength is used along with 32-bit registers for storing intermediate results, and two hardware shifters are available to scale numbers independent of the CPU. This combination minimizes quantization and truncation errors, and increases processing power for additional functions. Such functions might include: A notch filter that could cancel mechanical resonances in the system, or an estimation technique that could eliminate state sensors in a system.

The VLSI of the TMS320C14/E14 allows extra on-chip peripherals that provide additional functions. An event manager, with its own capture inputs/PWM compare outputs, simplifies system design. Up to four timers are available for sequencing of control signal processing. The on-chip peripherals of the TMS320C14/E14 make it the ideal solution for digital control.

## 1.3 Key Features

Some of the key features of the TMS320C14/E14 devices are listed below:

- 160-ns instruction cycle

- 256-word on-chip data RAM

- 4K-word on-chip program ROM (TMS320C14)

- 4K-word on-chip program EPROM (TM\$320E14)

- EPROM code protection for copyright security

- 4K-word total external memory at full speed (microprocessor mode)

- 32-bit ALU/accumulator

- 16 x 16-bit multiplier with a 32-bit product

- 0 to 16-bit barrel shifter

- Seven input and seven output channels

- 16-bit bidirectional data bus with 50-Mbps transfer rate

- Bit-selectable I/O port (16pins)

- Serial port with programmable protocols

- Event manager with capture inputs and compare outputs

- Four independent timers (watchdog, general purpose (2), serial port)

- 15 external/internal interrupts

## Section 2

# **Pinout and Signal Descriptions**

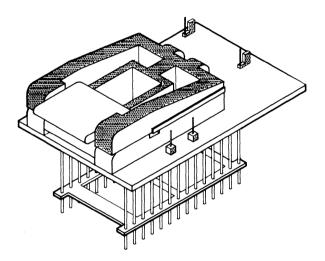

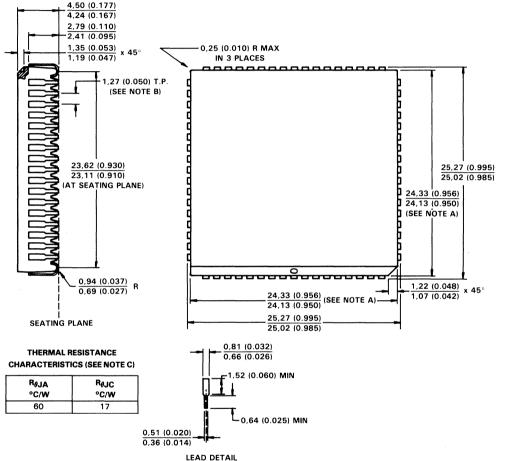

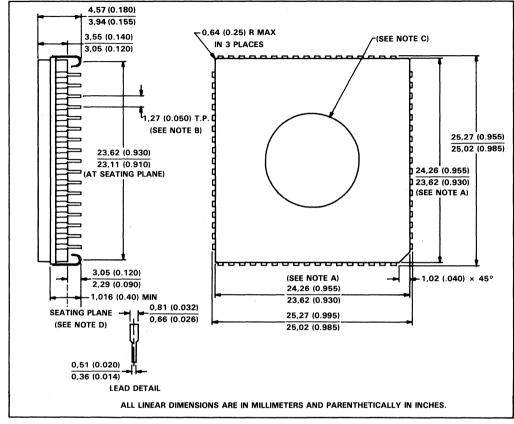

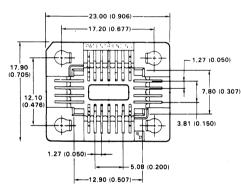

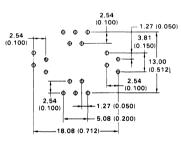

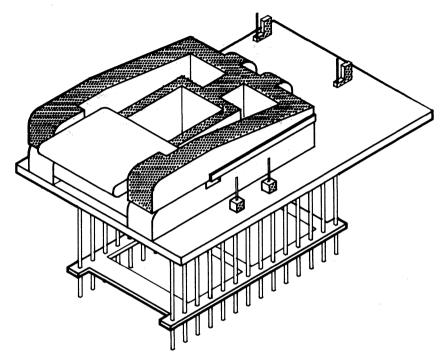

The TMS320C14/E14 digital signal processor devices are available in plastic-leaded chip carrier (PLCC) and ceramic-leaded chip carrier (CLCC) packages.

This section provides the pinouts and signal descriptions in the following sections:

- Pinouts (Section 2.1 on page 2-2)

- Pin Descriptions (Section 2.2 on page 2-3)

Electrical specifications and mechanical data are given in the data sheet in Appendix A. Refer to Appendix F for the pinouts used for EPROM programming.

## 2.1 Pinouts

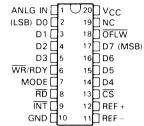

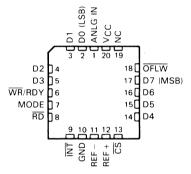

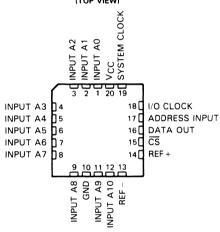

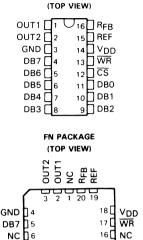

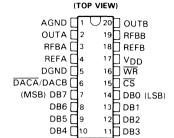

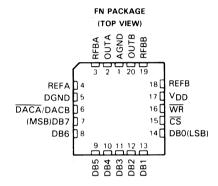

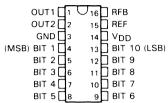

Figure 2-1 shows the pinouts of the TMS320C14/E14 devices.

Figure 2-1. TMS320C14/E14 Pin Assignments

## 2.2 Signal Descriptions

This section provides the signal descriptions for the TMS320C14/E14 devices. Table 2-1 lists each signal, its pin location, operating mode (i.e., input, output, high impedance state), and description. The signals are grouped according to function and alphabetized within that grouping.

Table 2-1. TMS320C14/E14 Signal Descriptions

| SIGNAL                                                                             | PIN                                                                                          | I/O/Z† | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADDRESS/DATA BUSES                                                                 |                                                                                              |        |                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2/PA2<br>A1/PA1<br>A0/PA0 | 5<br>6<br>9<br>12<br>13<br>14<br>20<br>21<br>25<br>26<br>27<br>28                            | O/Z    | Program memory address bus A11 (MSB) through A0 (LSB) and port addresses PA2 (MSB) through PA0 (LSB). Addresses A11 through A0 are always active and never go to high impedance except during reset. During execution of the IN and OUT instructions, pins 26, 27, and 28 carry the port addresses. Pins A3 through A11 are held high when port accesses are made on pins PA0 through PA2. |  |  |  |

| D15 MSB D14 D13 D12 D11 D10 D9 D8 D7 D5 D5 D4 D3 D2 D1 D0 LSB                      | 35<br>36<br>39<br>40<br>43<br>46<br>49<br>50<br>57<br>58<br>59<br>60<br>61<br>62<br>63<br>64 | I/O/Z  | Parallel data bus D15 (MSB) through D0 (LSB). The data bus is always in the high-impedance state except when WE is active (low). The data bus is also active when internal peripherals are written to.                                                                                                                                                                                     |  |  |  |

<sup>†</sup> Input/Output/High-impedance state

Table 2-1. TMS320C14/E14 Signal Descriptions (Continued)

| SIGNAL            | PIN                       | I/O    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | AND MISCELLANEOUS SIGNALS |        |                                                                                                                                                                                                                                                                                                                                                  |

| ĪNT               | 18                        | 1      | External interrupt input. The interrupt signal is generated by a low signal on this pin.                                                                                                                                                                                                                                                         |

| <u>ПМІ</u> /МС/МР | 22                        | 1      | Non-maskable interrupt. When this pin is brought low, device is interrupted irrespective of the state of INTM (status register ST) bit.  Microcomputer/Microprocessor select. This pin is also sampled when RS is low. If high during reset, internal program memory is selected. If low during reset, external program memory will be selected. |

| WE                | 15                        | 0      | Write enable. When active low, $\overline{\text{WE}}$ indicates that device will output data on the bus.                                                                                                                                                                                                                                         |

| REN               | 16                        | 0      | Read enable. When active low, $\overline{\text{REN}}$ indicates that device will accept data from the bus.                                                                                                                                                                                                                                       |

| RS                | . 17                      | I      | Reset. When this Schmidt trigger input is low, the device is reset and PC is set to zero.                                                                                                                                                                                                                                                        |

|                   |                           | SUPP   | LY/OSCILLATOR SIGNALS                                                                                                                                                                                                                                                                                                                            |

| CLKOUT            | 19                        | 0      | System clock output (one fourth CLKIN frequency).                                                                                                                                                                                                                                                                                                |

| V <sub>CC</sub>   | 4,33                      | ı      | 5-V supply pins.                                                                                                                                                                                                                                                                                                                                 |

| V <sub>SS</sub>   | 3,34                      | 1      | Ground pins.                                                                                                                                                                                                                                                                                                                                     |

| CLKIN             | 24                        | ı      | Master clock input (from external clock source).                                                                                                                                                                                                                                                                                                 |

|                   |                           | SERIAL | PORT AND TIMER SIGNALS                                                                                                                                                                                                                                                                                                                           |

| RXD/DATA          | 48                        | 1/0    | In the asynchronous and codec modes, this pin is the receive input. In the synchronous mode, this pin is data in while receiving data, and data out while transmitting data.                                                                                                                                                                     |

| TXD/CLK           | 47                        | I/O    | In the asynchronous and codec modes, this pin is the trans-<br>mit output. In the synchronous mode, this pin is clock input<br>with external clock, and clock output with internal clock.                                                                                                                                                        |

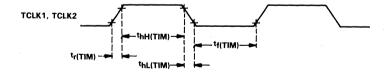

| TCLK1/CLKR        | 10                        | I      | Timer 1 clock. If external clock selected, it serves as clock input to Timer 1. Can also be configured as serial port receive clock in codec mode.                                                                                                                                                                                               |

| TCLK2/CLKX        | 11                        | I      | Timer 2 clock. If external clock selected, it serves as clock input to Timer 2. Can also be configured as serial port transmit clock in codec mode.                                                                                                                                                                                              |

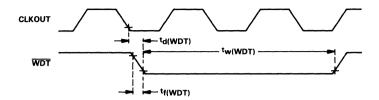

| WDT               | 23                        | 0      | Watchdog timer output. An active low is generated on this pin when the watchdog timer times out.                                                                                                                                                                                                                                                 |

Table 2-1. TMS320C14/E14 Signal Descriptions (Concluded)

| SIGNAL                                                                                        | PIN                                                                                          | I/O   | DESCRIPTION                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                               |                                                                                              |       | BIT I/O PINS                                                                                                                                                                                                        |

| IOP15 MSB IOP14 IOP13 IOP12 IOP11 IOP10 IOP9 IOP8 IOP7 IOP6 IOP5 IOP4 IOP3 IOP2 IOP1 IOP0 LSB | 29<br>30<br>31<br>32<br>37<br>38<br>41<br>42<br>44<br>45<br>51<br>52<br>53<br>54<br>55<br>56 | 1/0   | 16 bit I/O lines that can be individually configured as inputs or outputs and also be individually set or reset when configured as outputs.                                                                         |

|                                                                                               |                                                                                              | COMPA | RE AND CAPTURE SIGNALS                                                                                                                                                                                              |

| CMP0<br>CMP1<br>CMP2<br>CMP3                                                                  | 8<br>7<br>2<br>1                                                                             | 0     | Compare outputs. The states of these pins are determined by the combination of compare and action registers.                                                                                                        |

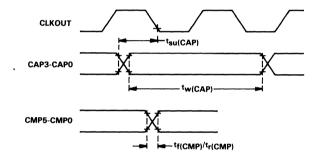

| CAP0<br>CAP1                                                                                  | 68<br>67                                                                                     | l     | Capture inputs. A transition on these Schmidt trigger inputs causes the timer register value to be loaded into the corresponding FIFO.                                                                              |

| CMP4/CAP2/<br>FSR                                                                             | 66                                                                                           | 1/0   | This pin can be configured as a compare output, capture input, or as an external framing input/output for the receiver of the serial port in codec mode.                                                            |

| CMP5/CAP3/<br>FSX                                                                             | 65                                                                                           | 1/0   | This pin can be configured as a Schmidt trigger input or as an output. That is, as a compare output, capture input, or as external framing input/output for transmit sectionof the serial port while in codec mode. |

## **Section 3**

## **Architecture**

This section describes the architecture of the TMS320C14/E14, which is based on the TMS320C1x architecture. The term TMS320C1x architecture is used to describe the features that are generic to all members of the TMS320C1x family, e.g., TMS320C10, TMS320C14/E14, TMS320C15/E15, TMS320C17/E17, and others. For more information regarding the TMS320C1x family, refer to the TMS320C1x User's Guide. Major topics discussed in this section are listed below.

- Architectural Overview (Section 3.1 on page 3-2)

- System Control (Section 3.2 on page 3-12)

- Central Arithmetic logic Unit (Section 3.3 on page 3-22)

- Memory Organization (Section 3.4 on page 3-27)

- Bit Selectable I/O Port (Section 3.5 on page 3-32)

- Timers (Section 3.6 on page 3-36)

- Event Manager (Section 3.7 on page 3-43)

- Serial Port (Section 3.8 on page 3-58)

## 3.1 Architectural Overview

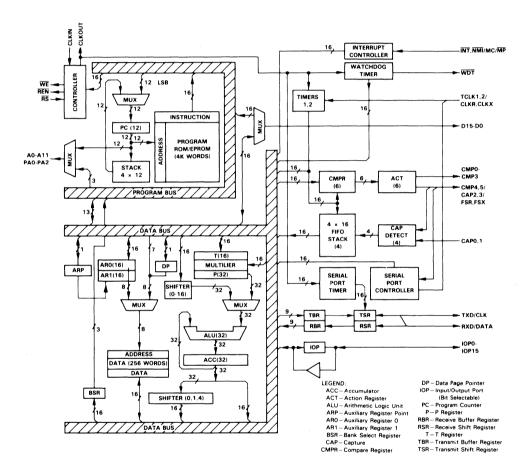

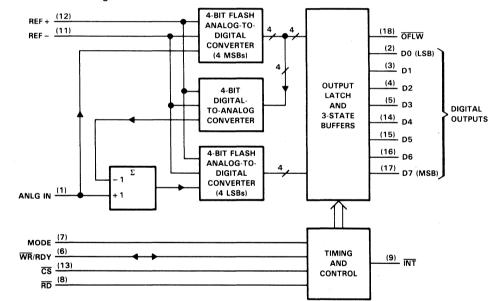

The TMS320C14/E14 architecture is based on the TMS320C1x, which utilizes a modified Harvard architecture for speed and flexibility. In a strict Harvard architecture, program and data memory lie in two separate spaces, permitting a full overlap of instruction fetch and execution. The TMS320C1x modification of the Harvard architecture allows transfers between program and data spaces, thereby increasing the flexibility of the device. This permits gain constants (or coefficients) stored in program memory to be read into RAM, allowing expansion beyond the 256 word data memory space. This also makes available immediate instructions and subroutines based on computed values. The functional block diagram shown in Figure 3-1 outlines the principal hardware structure of the TMS320C14/E14 devices. Both devices are the same except for the respective ROM/EPROM difference in program memory.

Figure 3-1. TMS320C14/E14 Functional Block Diagram

## 3.1.1 Processing Hardware

The TMS320C14/E14 devices contain a 32-bit ALU and accumulator for support of double-precision, two's complement arithmetic. The ALU is a general-purpose arithmetic unit that uses 16-bit words taken from data RAM or derived from immediate instructions, or uses the 32-bit result of the multiplier's product register. In addition to the usual arithmetic instructions, the ALU can perform Boolean operations, providing the bit manipulation ability required of a high-speed controller. The accumulator stores the output from the ALU and is often an input to the ALU. The accumulator is 32-bits in length and is divided into a high-order word (bits 16 through 31) and a low-order word (bits 0 through 15). Instructions are provided for storing the high-and low-order accumulator words in memory.

The multiplier performs a 16 x 16-bit two's complement multiplication with a 32-bit result in a single instruction cycle. The multiplier consists of three elements: the T register, P register, and multiplier array. The 16-bit T register temporarily stores the multiplicand; the P Register stores the 32-bit product. Multiplier values either come from the data memory, or are derived immediately from the MPYK (multiply immediate) instruction word. The fast on-chip multiplier allows the device to efficiently perform mathematically intensive algorithms such as Kalman filtering, PID loops, and lead/lag compensation.

Two shifters are available for manipulating data. The ALU barrel shifter performs a left-shift of 0 to 16 places on data memory words loaded into the ALU. This shifter extends the high-order bit of the data word and zero-fills the low-order bits for two's complement arithmetic. The accumulator parallel shifter performs a left-shift of 0, 1, or 4 places on the entire accumulator, and stores the resulting high-order accumulator bits into data RAM. Both shifters are useful for scaling and bit extraction.

The TMS320C1x devices contain a four-level hardware stack for saving the contents of the program counter during interrupts and subroutine calls. Instructions are available for saving the device's complete context. PUSH and POP instructions permit a level of nesting restricted only by the amount of available RAM.

Table 3-1 provides a summary of the processing hardware contained in the TMS320C14/E14.

Table 3-1. TMS320C14/E14 Processing Hardware Summary

| UNIT                             | SYMBOL              | FUNCTION                                                                                                                                                                                                                                                                                         |

|----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accumulator                      | ACC                 | A 32-bit accumulator divided into a high-order word (bits 31 through 16) and a low-order word (bits 15 through 0). Used for storage of ALU output.                                                                                                                                               |

| Arithmetic Logic Unit            | ALU                 | A 32-bit two's-complement arithmetic logic unit having two 32-bit input ports and one 32-bit output port feeding the accumulator.                                                                                                                                                                |

| Auxiliary Registers              | AR0,AR1             | Two 16-bit registers used for data memory addressing and loop count control. Nine LSBs of each register are configured as up/down counters.                                                                                                                                                      |

| Auxiliary Register Pointer       | ARP                 | A status bit that indicates the currently active auxiliary register.                                                                                                                                                                                                                             |

| Central Arithmetic Logic<br>Unit | CALU                | The grouping of the ALU, multiplier, accumulator, and shifters.                                                                                                                                                                                                                                  |

| Data Bus                         | D(15-0)             | A 16-bit bus used to route data to and from RAM.                                                                                                                                                                                                                                                 |

| Data Memory Page<br>Pointer      | DP                  | A status bit that points to the data RAM address of the current page. A data page contains 128 words.                                                                                                                                                                                            |

| Data RAM                         | -                   | 256 words of on-chip random access memory containing data.                                                                                                                                                                                                                                       |

| External Address Bus             | A(11-0)/<br>PA(2-0) | A 12-bit bus used to address external program memory. The three LSBs are port addresses in the I/O mode.                                                                                                                                                                                         |

| Interrupt Flag                   | INTF                | A single-bit flag that indicates an interrupt request has occurred (is pending).                                                                                                                                                                                                                 |

| Interrupt Mode                   | INTM                | A status bit that masks the interrupt flag.                                                                                                                                                                                                                                                      |

| Multiplier                       | MULT                | A 16 x 16-bit parallel hardware multiplier.                                                                                                                                                                                                                                                      |

| Overflow Flag                    | OV                  | A status bit flag that indicates an overflow in arithmetic operations.                                                                                                                                                                                                                           |

| Overflow Mode                    | OVM                 | A status bit that defines a saturated or unsaturated mode in arithmetic operations.                                                                                                                                                                                                              |

| P Register                       | Р                   | A 32-bit register containing the product of multiply operations.                                                                                                                                                                                                                                 |

| Program Bus                      | P(15-0)             | A 16-bit bus used to route instructions from program memory.                                                                                                                                                                                                                                     |

| Program Counter                  | PC (11-0)           | A 12-bit register used to address program memory. The PC always contains the address of the next instruction to be executed. The PC contents are updated following each instruction decode operation.                                                                                            |

| Program ROM/EPROM                | -                   | 4K words of on-chip read only memory (ROM or EPROM) containing the program code.                                                                                                                                                                                                                 |

| Shifters                         | -                   | Two shifters: the ALU barrel shifter that performs a left-shift of 0 to 16 bits on data memory words loaded into the ALU, and the accumulator parallel shifter that performs a left-shift of 0, 1, or 4 places on the entire accumulator and places the resulting high-order bits into data RAM. |

| Stack                            | -                   | A 4 x 12-bit hardware stack used to store the PC during interrupts or calls.                                                                                                                                                                                                                     |

Table 3-1. TMS320C14/E14 Processing Hardware Summary (Concluded)

| UNIT            | SYMBOL | FUNCTION                                                                  |  |  |

|-----------------|--------|---------------------------------------------------------------------------|--|--|

| Status Register | ST     | A 16-bit status register that contains status and control bits.           |  |  |

| T Register      | Т      | A 16-bit register containing the multiplicand during multiply operations. |  |  |

## 3.1.2 I/O Structure

The TMS320C1x architecture implements a variety of I/O functions that can be used for communicating with internal/external peripherals. The 16-bit parallel data bus can be utilized to perform I/O functions in two cycles using IN and OUT instructions. The I/O ports are addressed by A0 through A2 of the address bus, with A0 as the LSB of the I/O port address. The upper address bits of A3 through A11 are driven high during I/O port accesses. In the TMS320C14/E14, the I/O ports addressed can be on-chip or off-chip.

I/O design is simplified by having I/O treated the same way as memory. I/O peripherals, whether on-chip or off-chip, are mapped into the I/O space using the processor's internal/external address and data buses in the same manner as memory mapped devices.

Input/output of data, to/from an on-chip or off-chip peripheral, is accomplished by IN and OUT instructions. If external peripherals are addressed, data is transferred over the external 16-bit data bus to and from data memory by two independent strobes: read enable ( $\overline{\text{REN}}$ ) and write enable ( $\overline{\text{WE}}$ ). If on-chip peripherals are addressed, data is transferred over the internal data bus and the  $\overline{\text{REN}}$  and  $\overline{\text{WE}}$  strobes are not active.

## Note:

Unlike other TMS320C1x devices, strobe REN is active for ALL external accesses, whether for an I/O port or program memory.

The bidirectional external data bus (D15 - D0) is always in the high-impedance state, except when  $\overline{WE}$  is active (low).  $\overline{WE}$  goes low during the first cycle of the OUT instruction, if external peripherals are addressed.  $\overline{WE}$  also goes low during the second cycle of the TBLW instruction if external program memory is addressed. If internal peripherals are addressed, then  $\overline{WE}$  remains inactive (high).

## 3.1.3 I/O Peripherals

The TMS320C14/E14 includes all the features of the TMS320C1x achitecture as well as some additional I/O functions. The 16-bit parallel data bus can be utilized to access external program memory and I/O functions. These external bus cycles are controlled by the write enable ( $\overline{\text{WE}}$ ) and read enable ( $\overline{\text{REN}}$ ) pins.

The TMS320C14/E14 has 16-pins of bit I/O that can be individually selected as inputs or outputs. There are provisions to allow setting and clearing of each pin without affecting the others. The capability to detect and match patterns on the input pins is also included. Refer to section 3.5 for more information on the bit I/O pins.

Also included in the TMS320C14/E14 are two 16-bit timers that can be used as event counters with internal or external clocks, and a Watchdog timer that is available for time-out functions. A fourth timer, the serial port baud rate generator, is intended for serial port operation, but may also be used as a general-purpose timer if sychronous/asychronous communication is not used. Associated with each timer is a 16-bit period register. Refer to Section 3.6 for more information on the timers.

The TMS320C14/E14 has an event manager that consists of a compare subsystem and a capture subsystem. The compare subsystem has six compare registers that constantly compare their outputs with one of the timers. Associated with each compare register is an action register that controls the compare output pins. The action registers determine actions that take place on output pins in case of a match between the timer and a compare register. In addition, the compare subsystem can be configured to generate six channels of high-precision PWM. The event manager also contains four capture inputs. This subsystem captures the value of a timer in a corresponding four-deep FIFO stack when a certain transition is detected on a capture input pin. Section 3.8 contains more information on the event manager.

The serial port of the TMS320C14/E14 provides three modes of operation: synchronous, asynchronous, and codec-compatible. Two protocols for interprocessor communication are supported, and a dedicated timer generates the baud rates. Refer to Section 3.8 for more information on the serial port.

The TMS320C14/E14 has a total of 15 internal/external interrupts that can be individually masked. An external non-maskable interrupt (\overline{NMI}/MC/\overline{MP}) is also available. Each of the interrupts triggers a master interrupt. The master interrupt is controlled by the INTM bit in the status register. For more information, refer to Section 3.2.5 regarding interrupts.

A maximum of eight I/O addresses are available on the TMS320C1x and TMS320C14/E14 for interfacing to peripheral devices: eight 16-bit multiplexed input ports and eight 16-bit multiplexed output ports. To maintain compatibility with the TMS320C1x architecture, all peripherals on the TMS320C14/E14 are implemented in the I/O address space. However, the number of on-chip peripheral devices that can be accessed is greater than 16. To implement the peripherals within the address space of eight I/O ports, a dual address scheme has been adopted that includes a bank address, and a port address within that bank. This allows a user to preserve his investment in TMS320C1x software and development tools.

## 3.1.4 On-Chip Peripheral Register Mapping