# STARTECH SEMICONDUCTOR, INC.

DATA BOOK 1993

# STARTECH Component Data Catalog 1993

STARTECH semiconductor Inc. 1219 BORDEAUX Dr. SUNNYVALE, CA 94089 TEL (408) 745-0801 FAX (408) 745-1269 No part of this document may be copied or reproduced in any form or by means without the prior written consent of STARTECH Semiconductor Inc. The information in this document is subject to change without notice. STARTECH Semiconductor Inc. assumes no responsibility for any errors that may appear in this document and makes no commitment to update or to keep current the information contained in this document. STARTECH Semiconductor Inc. makes no warranty (express, statutory, implied, or by description) regarding the information set forth herein or regarding the freedom of the described device from patent infringement. STARTECH Semiconductor Inc. makes no warranty of merchantability or fitness for any purpose.

STARTECH Semiconductor Inc.'s products are not authorized for use as critical components in the life support devices or systems without the express written approval of the president of STARTECH Semiconductor Inc..

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform

can be reasonably expected to cause the failure of the life support device or system, or to effect its

safety or effectiveness.

286/386/486 is a trademark of Intel Corporation.

IBM PC/XT/AT, PS/2 is a trademark of International Business Machines Corporation.

WD is a trademark of Western Digital Corporation.

NS, INS, DS is a trademark of National Semiconductor Corporation.

VL is a trademark of VLSI Technologies Corporation.

CENTRONICS is a trademark of Centronics Data Computer Corporation.

XR is a trademark of Exar Corporation.

TL is trademark of Texas Instrument, Inc.

MC is a trademark of Motorola Semiconductor.

ICS is a trademark of Integrated Circuit Systems, Inc.

AV is a trademark of Averse Corporation.

SSI is a trademark of Silicon Systems Inc.

#### To our valued customer:

Startech Semiconductor was founded in 1990, with the charter to design, manufacture and market high performance data communication peripheral products in both the commercial and industrial semiconductor markets. Since then, Startech continues to follow that charter and enjoys a rapid growth.

Startech's products are marketed and distributed through a world-class network of representatives and distributors.

At Startech, we are dedicated to keeping your designs competitive with leading edge solutions. All our products are low power, high performance, CMOS ICs. Our commitment to you is to provide you with high quality and reliable ICs.

Unner

Ram K. Reddy President

### Introduction

#### Dear customer,

Startech Semiconductor is proud to present you with our updated 1993 Data Book. Startech's technical staff have worked together to provide you with the most accurate, up-to-date information.

We believe that when you design our products in your systems, you have started a partnership with a company that is committed to work with the customers and deliver quality products. Startech offers to customize any of these standard products to meet your special requirements.

If you have any questions or comments, please call us directly.

Startech Semiconductor Technical Staff

achal.

Art Khachaturian Vice President

# FREQUENCY SYNTHESIZERS

# LINE DRIVERS / RECEIVERS

### UARTS

# COMMUNICATIONS

# **APPLICATION NOTES**

# QUALITY/RELIABILITY

# **ORDERING INFORMATION**

# PACKAGING INFORMATION

# REPRESENTATIVES

# Contents

| FREQUENCY SYNTHESIZERS                |   |

|---------------------------------------|---|

| ST49C061                              | 3 |

| ST49C063                              | 1 |

| ST49C064                              | 1 |

| ST49C103                              | 9 |

| ST49C104                              | 9 |

| ST49C106                              | 9 |

| ST49C155                              | 5 |

| ST49C214                              | 5 |

| ST49C394                              | 7 |

| ST49C694                              | 5 |

|                                       |   |

| DIFFERENTIAL LINE DRIVERS             |   |

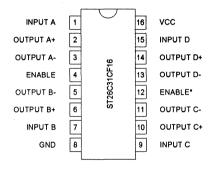

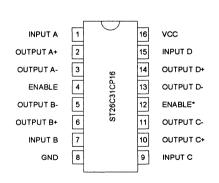

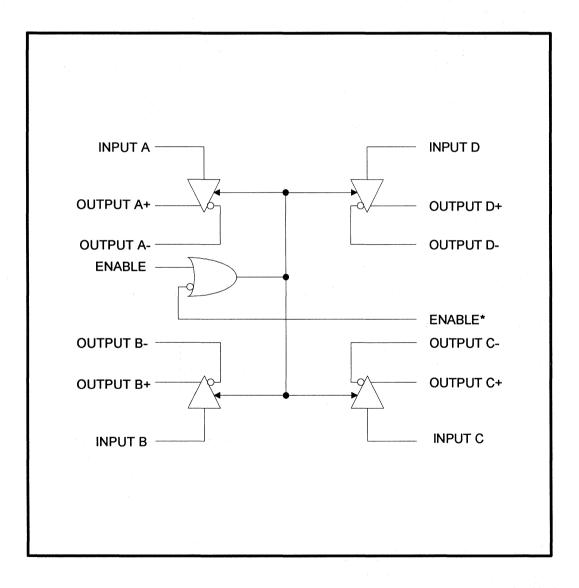

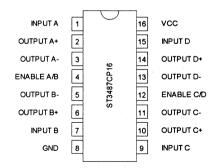

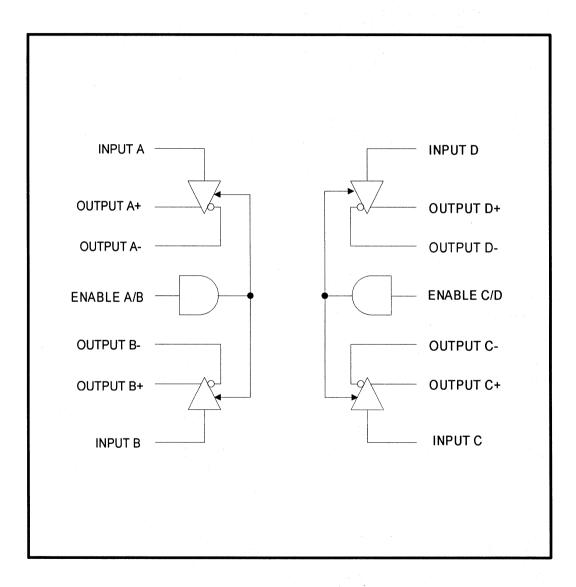

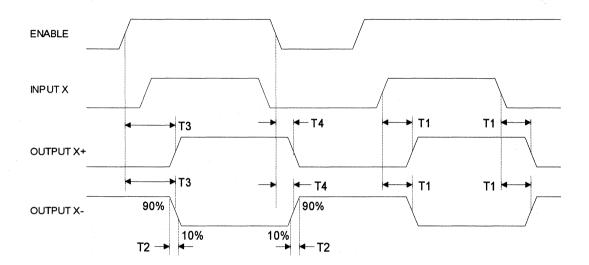

| ST26C31                               | 3 |

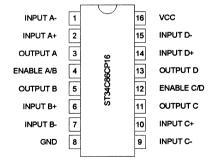

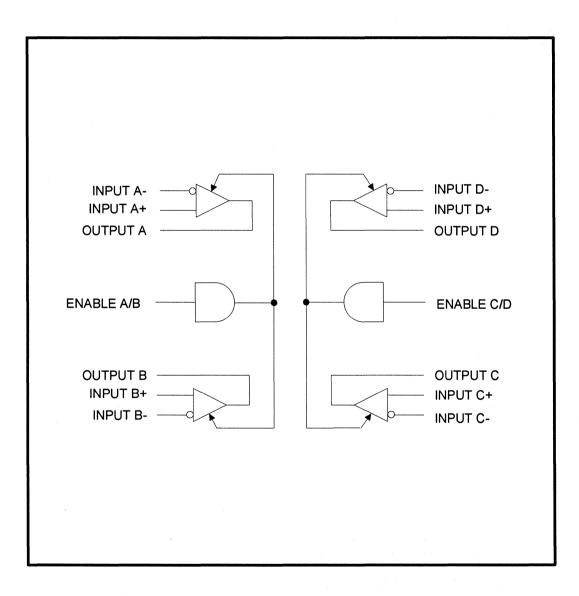

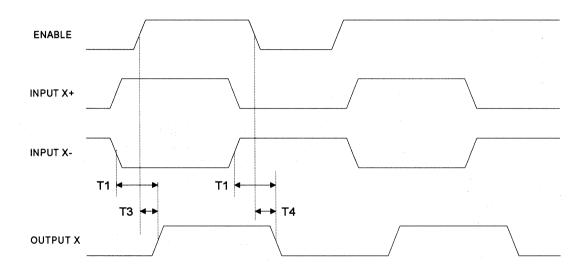

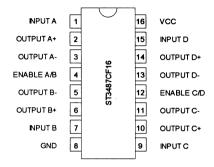

| ST34C87                               | 9 |

|                                       |   |

| DIFFERENTIAL LINE RECEIVERS           |   |

| ST26C32                               | 9 |

| ST34C86                               | 3 |

|                                       |   |

| DIFFERENTIAL LINE DRIVERS / RECEIVERS |   |

| ST34C50                               | 5 |

| ST34C51                               | 5 |

|                                       |   |

| UARTS                                 |   |

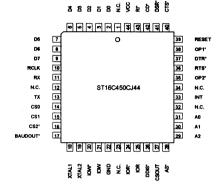

| ST16C1450                             | 3 |

| ST16C1451                             | 3 |

| ST16C2450                             | 5 |

| ST16C450                              | 3 |

| ST16C454                              | 1 |

|                                       |   |

| UARTS WITH FIFO                       |   |

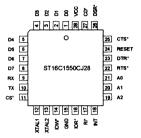

| ST16C1550                             | 3 |

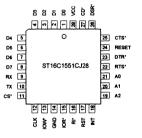

| ST16C1551                             | 3 |

| ST16C1552                             | 3 |

| ST16C2550                             | 5 |

| ST16C2552                             | 7 |

| ST16C550                              | 3 |

| ST16C554                              | 3 |

| ST68C454                              | 1 |

|                                       |   |

| ST68C554                              | 7 |

#### **UARTS WITH PRINTER**

| ST16C452AT | 3-229 |

|------------|-------|

| ST16C452PS |       |

| ST16C552   |       |

| ST16C553   |       |

#### PARALLEL I/O WITH FIFO

| ST78C35 | <br> |

|---------|------|

|         |      |

|         |      |

|         |      |

|         |      |

###

| ST84C72 |                                         | A.1  | 5 |

|---------|-----------------------------------------|------|---|

| 0104072 | *************************************** | <br> | 5 |

|         |                                         |      |   |

### **CROSS REFERENCE LIST**

#### DIFFERENTIAL LINE DRIVERS

National Semiconductor DS26C31 DS34C86

DIFFERENTIAL LINE RECEIVERS

National Semiconductor DS26C32 DS34C37

#### DIFFERENTIAL LINE RECEIVERS / DRIVERS Motorola Semiconductor MC34050 MC34051

#### UARTS

National Semiconductor INS8250A INS82C50A NS16450 NS16C450 NS16550AF NS16C552

Silicon Systems SSI73M550 SSI73M1550 SSI73M2550

VLSI Technology, Inc. VL82C50A VL16C450 VL16C550

Western Digital Inc. WD16C450 WD16C550

Texas Instruments TL16C450 TL16C550A

Exar Corporation XR16C450 XR16C550 Startech Semiconductor ST26C31 ST34C86

Startech Semiconductor ST26C32 ST34C87

Startech Semiconductor ST34C50 ST34C51

Startech Semiconductor ST16C450 ST16C450 ST16C450 ST16C450 ST16C550 ST16C2552

Startech Semiconductor ST16C550 ST16C1450 / ST16C1550 ST16C1451 / ST16C1551

Startech Semiconductor ST16C450 ST16C450 ST16C550

Startech Semiconductor ST16C450 ST16C550

Startech Semiconductor ST16C450 ST16C550

Startech Semiconductor ST16C450 ST16C550

### **CROSS REFERENCE LIST**

#### **UARTS WITH PRINTER**

VLSI Technology, Inc. VL16C452 VL16C552

Western Digital Inc. WD16C452 WD16C552

Texas Instruments TL16C452 TL16C552

Exar Corporation XR16C452 XR16C552

#### VIDEO DOT CLOCK GENERATOR

Integrated Circuit Systems, Inc. ICS1394XXX ICS2494XXX ICS9061AXXX ICS9063 ICS9064 ICS2694

Avasem Corporation AV9103-XX AV9104-XX AV9106 AV9155 Startech Semiconductor ST16C452 ST16C552 / ST16C553

Startech Semiconductor ST16C452 ST16C552 / ST16C553

Startech Semiconductor ST16C452 ST16C552

Startech Semiconductor ST16C452 ST16C552

Startech Semiconductor ST49C394-XX ST49C214-XX ST49C061-XX ST49C063 ST49C064 ST49C664

Startech Semiconductor ST49C103-XX ST49C104-XX ST49C106 ST49C155

# FREQUENCY SYNTHESIZERS

# Index

| ST49C061 | <br>1-3 |

|----------|---------|

| ST49C063 | <br>-11 |

| ST49C064 | <br>-11 |

|          |         |

| ST49C104 | <br>-19 |

| ST49C106 | <br>-29 |

| ST49C155 | <br>-35 |

| ST49C214 | <br>-45 |

|          |         |

| ST49C694 | <br>-65 |

Printed May 17, 1993

### PREPROGRAMMED DUAL VIDEO/MEMORY FREQUENCY GENERATOR

#### **GENERAL DESCRIPTION**

The ST49C061 is a monolithic analog CMOS device designed to generate dual frequency outputs from seven possible combinations for video Dot clock frequencies and four memory clock frequencies for high performance video display systems. The ST49C061 is a mask option programmable device to provide different output frequencies for custom applications. It is designed with  $1.2\mu$  process to achieve 130 MHz speed for high end frequencies.

The ST49C061 is designed to replace existing video clocks generated from individual oscillators, to reduce board space and number of oscillators. To provide high speed and low jitter clock, The ST49C061 utilizes high speed analog CMOS phase locked loop using 14.318 MHz system clock as reference clock (reference clock can be changed to generate optional frequencies from standard programmed device).

The ST49C061 can provide optional clock frequencies, utilizing single layer metal mask option. The programmed clock outputs are selectable via four address lines and address latch enable pin for video Dot clock selection and two address lines for memory clock selection.

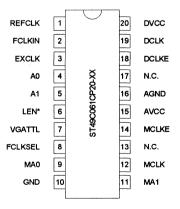

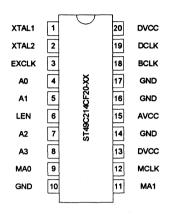

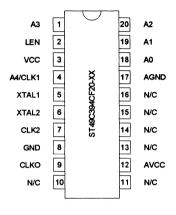

#### REFCLK 20 DVCC 1 2 FCLKIN 19 DCLK 3 EXCLK 18 DOLKE 17 AO 4 5T49C061CF20-XX N.C. 5 16 A1 15 LEN\* 6 AVCC 14 7 VGATTL MCLKE 13 FCLKSEL 8 N.C. 12 9 MCLK MAO GND 10 11 MA1

SOIC Package

# 1

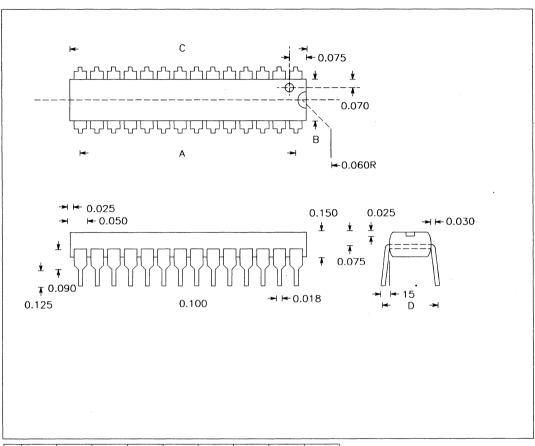

### Plastic-DIP Package

#### FEATURES

- Can replace multiple oscillators/crystals

- Pin -to-pin compatible to ICS90C61A

- Programmable analog phase locked loop

- High speed (up to 130 MHz output)

- Low power single 5V CMOS technology

- 20 pin dip or SOIC package

- Compatible with Western Digital Imaging Video Graphics Array clock requirements.

#### **ORDERING INFORMATION**

| Part number     | Package     | Oper | atin | g te | mperat | ure |

|-----------------|-------------|------|------|------|--------|-----|

| ST49C061CP20-xx | Plastic-DIP | 0°   | С    | to   | +70°   | С   |

| ST49C061CF20-xx | SOIC        | 0°   | С    | to   | +70°   | С   |

| ST49C061CJ20-xx | PLCC        | 0°   | С    | to   | +70°   | С   |

ST49C061

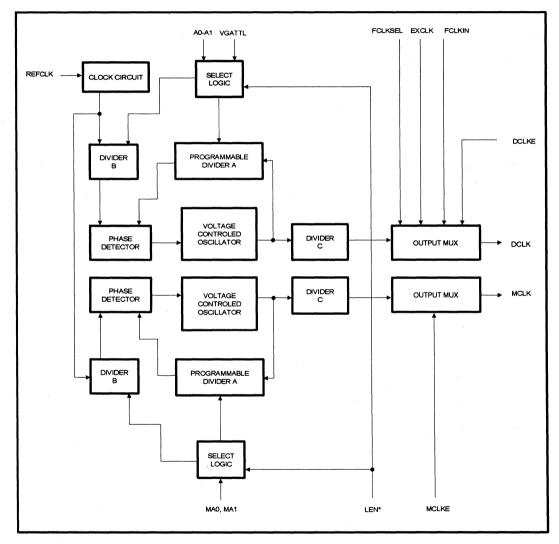

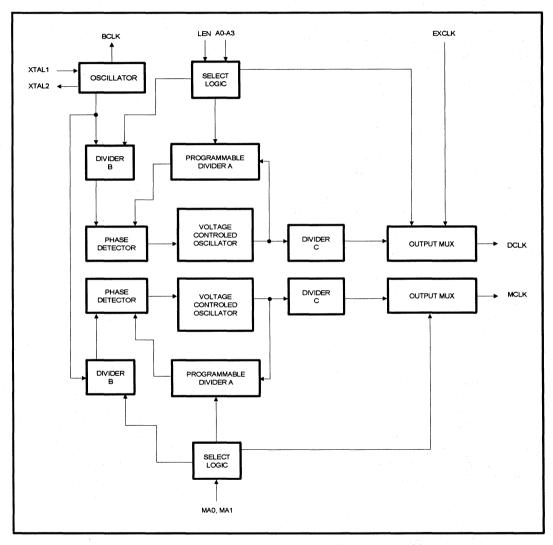

### BLOCK DIAGRAM

### SYMBOL DESCRIPTION

| Symbol  | Pin | Signal Type | Pin Description                                                                     |

|---------|-----|-------------|-------------------------------------------------------------------------------------|

| REFCLK  | 1   | I           | External 14.318 MHz system reference clock input.                                   |

| FCLKIN  | 2*  | I           | Feature clock input.                                                                |

| EXCLK   | 3*  | I           | External clock input. For additional clock frequency.                               |

| A0      | 4*  | I           | Dot clock Frequency select address 1.                                               |

| A1      | 5*  | I           | Dot clock Frequency select address 2.                                               |

| LEN*    | 6*  | I           | Address latch enable input (active low). To latch selected programmed clock output. |

| VGATTL  | 7*  | ł           | Control input for DCLK selection.                                                   |

| FCLKSEL | 8*  | , I         | Control input for FCLK selection.                                                   |

| MA0     | 9*  | 1           | Memory clock Frequency select address 1.                                            |

| DGND    | 10  | 0           | Digital ground.                                                                     |

| MA1     | 11* | ł           | Memory clock Frequency select address 2.                                            |

| MCLK    | 12  | о           | Programmed memory clock output frequency.                                           |

| N.C.    | 13  |             | No connect.                                                                         |

| MCLKE   | 14* | I           | MCLK output enable.                                                                 |

| AVCC    | 15  | I           | Analog supply voltage. Single +5 volts.                                             |

| AGND    | 16  | 0           | Analog ground.                                                                      |

| N.C.    | 17  |             | No connect.                                                                         |

| DCLKE   | 18* | Į.          | DCLK output enable.                                                                 |

| DCLK    | 19  | 0           | Programmed video clock output frequency.                                            |

| DVCC    | 20  | I.          | Digital supply voltage. Single +5 volts.                                            |

\* Have internal pull-up resistors on inputs.

#### **GENERAL INFORMATION**

The Western Digital Imaging VGA controllers normally have a status bit that indicates to the VGA controller that it is working with a clock chip. The VGA controller has capability to change two of its clock inputs VCLK1 and VCLK2 to outputs when working with a clock chip. These outputs are used to select the required video frequency.

The ST49C061 is programmed to generate different video clock frequencies using the inputs of A0 and A1. The VGATTL selects one of the two preprogrammed registers to provide four of eight clock frequencies.

The EXCLK and FCLKIN are additional inputs that may be internally connected to the DCLK output. The additional inputs are useful for supporting modes that require frequencies not provided by the ST49C061.

#### FREQUENCY SELECT CALCULATION

The ST49C061 contains an analog phase locked loop circuit with a digital closed loop divider and a final series divider to achieve desired dividing ratios for clock output.

The accuracy of the frequencies produced by the ST49C061 depends on the input frequency and final output frequency. The formula for calculating the exact output frequency is as follows:

DCLK = (Reference clock) X (A/B.C) MCLK = (Reference clock) X (A/B.C)

where A=1,2,3,......127, B=1,2,3,.....127, and C=1,2,4

For proper output frequency, the ST49C061 can accept reference frequency from 5 - 40 MHz and divider ratio up to 15.

#### MASK OPTIONS

The following mask options are provided for custom applications.

\* Any frequency can be in any decoding position.

\* DCLK, can control selection of the internal frequencies.

### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

#### DC ELECTRICAL CHARACTERISTICS

$T_{A}$ =25° C,  $V_{cc}$ =5.0 V ± 5% unless otherwise specified.

| Symbol                                                                               | Parameter                                                                                                                                    | Min        | Limits<br>Typ | Max                           | Units                   | Conditions                                                                                 |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-------------------------------|-------------------------|--------------------------------------------------------------------------------------------|

| V <sub>IL</sub><br>V <sub>IL</sub><br>V <sub>O</sub> H<br>IL<br>I <sub>H</sub><br>CC | Input low level<br>Input high level<br>Output low level<br>Output high level<br>Input low current<br>Input high current<br>Operating current | 2.0<br>2.4 | 20            | 0.8<br>0.4<br>-350<br>1<br>30 | V<br>V<br>V<br>µA<br>mA | I <sub>oL</sub> = 8.0 mA<br>I <sub>OH</sub> = 8.0 mA<br>VIN=Vcc<br>No load.<br>DCLK=80MHz, |

| R <sub>IN</sub>                                                                      | Input pull-up resistance                                                                                                                     | 15         | 20            | 25                            | KΩ                      | MCLK=40MHz                                                                                 |

# ST49C061

### AC ELECTRICAL CHARACTERISTICS

$\rm T_{A}=25^{\circ}$  C,  $\rm ~V_{cc}=5.0~V\pm5\%$  unless otherwise specified.

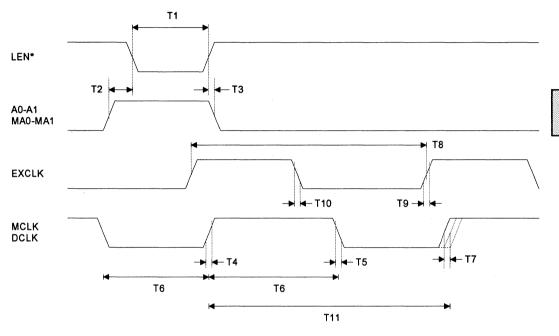

| Symbol                                                   | Parameter                 | Min    | Limits | Мах  | Units | Conditions         |

|----------------------------------------------------------|---------------------------|--------|--------|------|-------|--------------------|

|                                                          |                           |        | Тур    | wax  |       |                    |

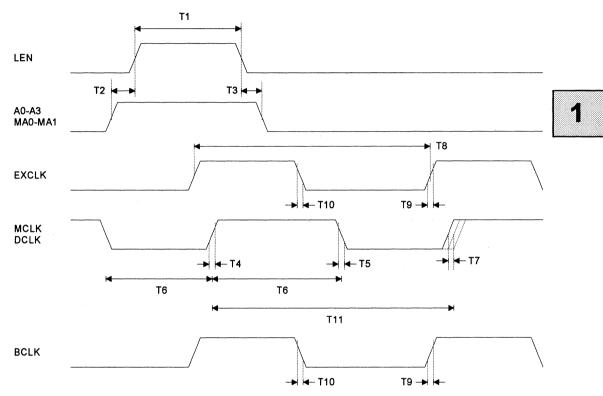

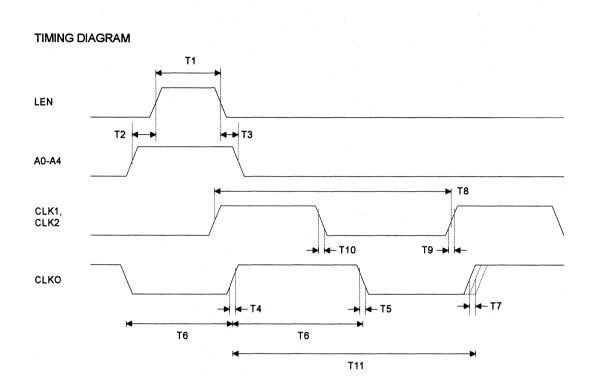

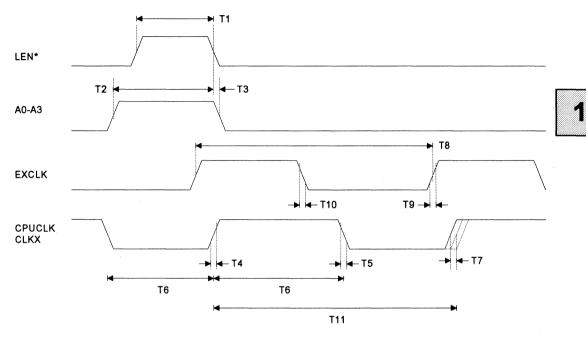

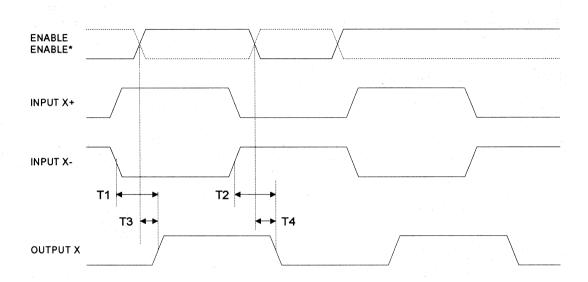

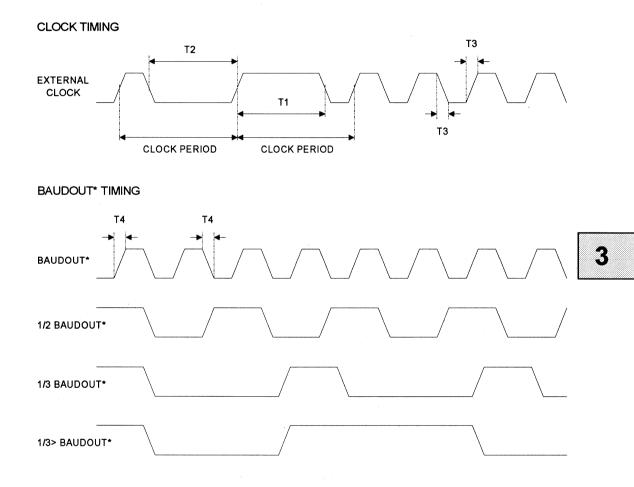

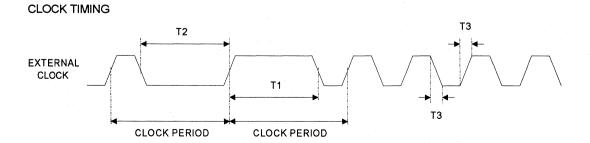

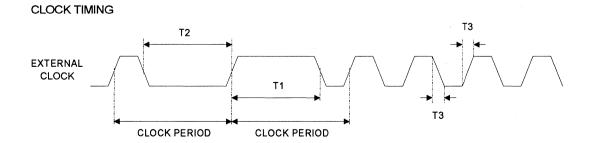

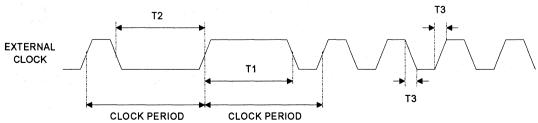

| Т,                                                       | Enable pulse width        | 20     |        |      | ns    |                    |

| T,                                                       | Setup time data to enable | 20     |        |      | ns    |                    |

| T,                                                       | Hold time to data enable  | 10     |        |      | ns    |                    |

| T₄                                                       | Rise time                 |        | 1      | 1.5  | ns    | 0.8V - 2.0V        |

| T,                                                       | Fall time                 |        | 1      | 1.5  | ns    | 2.0V - 0.8V        |

| Ť                                                        | Duty cycle                | 40     | 48/52  | 60   | %     | 1.4V switch point  |

| Т <sub>е</sub> ́                                         | Duty cycle                | 45     | 48/52  | 55   | %     | Vcc/2 switch point |

| T,                                                       | Jitter                    |        | ±85    | ±100 | ps    |                    |

| T,                                                       | Input frequency           | 14.318 |        | 32   | MHz   |                    |

| Т                                                        | Input clock rise time     |        |        | 20   | ns    |                    |

| T₁<br>T₂<br>T₄<br>T₅<br>T₀<br>T₀<br>T₀<br>T₃<br>T₃<br>T₃ | Input clock fall time     |        |        | 20   | ns    |                    |

| T <sub>11</sub>                                          | Output frequency change   |        | 0.005  |      | %     |                    |

ST49C061

1

### TIMING DIAGRAM

1-9

|                                           |                                      |                                      |                                           |                                 | ST49C061-01                                                                              | ST49C061-02                                                                              |

|-------------------------------------------|--------------------------------------|--------------------------------------|-------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Video<br>clock<br>address<br>(Hex)        | FCLKSEL                              | VGATTL                               | A1                                        | A0                              | Frequency<br>(MHz)                                                                       | Frequency<br>(MHz)                                                                       |

| 0<br>1<br>2<br>3<br>0<br>1<br>2<br>3<br>X | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>0 | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>X | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>X | 0<br>1<br>1<br>0<br>1<br>1<br>X | REFCLK<br>16.256<br>32.000<br>44.900<br>25.175<br>28.322<br>65.000<br>36.000<br>FCLKIN** | REFCLK<br>16.108<br>32.216<br>44.744<br>25.057<br>28.089<br>EXTCLK<br>36.242<br>FCLKIN** |

| Memory<br>clock<br>address<br>(Hex)       |                                      |                                      | MA1                                       | MA0                             | Frequency<br>(MHz)                                                                       | Frequency<br>(MHz)                                                                       |

| 0<br>1<br>2<br>3                          |                                      |                                      | 0<br>0<br>1<br>1                          | 0<br>1<br>0<br>1                | 40.000<br>37.500<br>36.000<br>44.900                                                     | 41.612<br>37.585<br>36.242<br>44.744                                                     |

Compatible with Video Controller

ICS-PR1

ICS-PR2 WD90C30

\*\* Note: FCLKIN and EXCLK may be programmed to output custom frequencies.

## ST49C063 ST49C064

Printed May 17, 1993

### PREPROGRAMMED DUAL VIDEO/MEMORY FREQUENCY GENERATOR

#### **GENERAL DESCRIPTION**

The ST49C063/64 is a monolithic analog CMOS device designed to generate dual frequency outputs from fifteen possible combinations for video Dot clock frequencies and eight memory clock frequencies for high performance video display systems. The ST49C063/64 is a mask option programmable device to provide different output frequencies for custom applications. It is designed with  $1.2\mu$  process to achieve 130 MHz speed for high end frequencies.

The ST49C063/64 is designed to replace existing video clocks generated from individual oscillators, to reduce board space and number of oscillators. To provide high speed and low jitter clock, The ST49C063/64 utilizes high speed analog CMOS phase locked loop using 14.318 MHz system clock as reference clock (reference clock can be changed to generate optional frequencies from standard programmed device).

The ST49C063/64 can provide optional clock frequencies, utilizing single layer metal mask option. The programmed clock outputs are selectable via four address lines and address latch enable pin for video Dot clock selection and three address lines for memory clock selection.

### **FEATURES**

- Can replace multiple oscillators/crystals

- Pin -to-pin compatible to ICS90C63/64

- Programmable analog phase locked loop

- High speed (up to 130 MHz output)

- Low power single 5V CMOS technology

- 20 pin dip / SOIC / PLCC packages

- Compatible with Western Digital Imaging Video Graphics Array clock requirements.

### **ORDERING INFORMATION**

| Part number     | Package     | Operating temperature |

|-----------------|-------------|-----------------------|

| ST49C063CP20-xx | Plastic-DIP | 0°C to +70°C          |

| ST49C063CF20-xx | SOIC        | 0°C to +70°C          |

| ST49C063CJ20-xx | PLCC        | 0°C to +70°C          |

| ST49C064CP20-xx | Plastic-DIP | 0°C to +70°C          |

| ST49C064CF20-xx | SOIC        | 0°C to +70°C          |

| ST49C064CJ20-xx | PLCC        | 0° C to +70° C        |

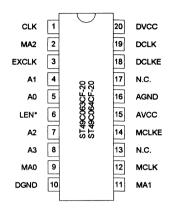

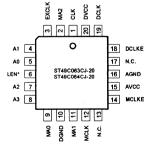

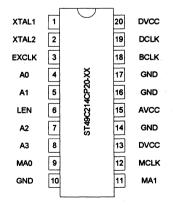

#### **SOIC Package**

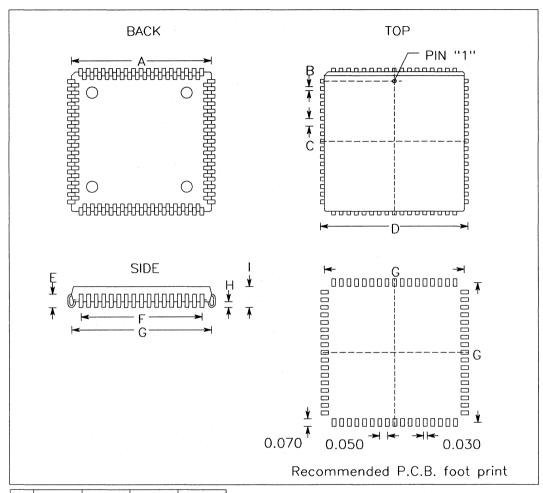

### PLCC Package

# ST49C063/64

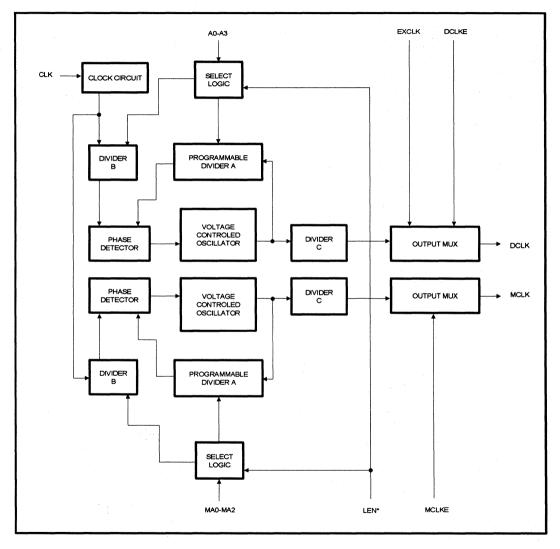

#### BLOCK DIAGRAM

1

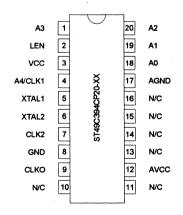

### SYMBOL DESCRIPTION

| Symbol | Pin | Signal Type | Pin Description                                                                     |

|--------|-----|-------------|-------------------------------------------------------------------------------------|

| CLK    | 1   | 1           | External 14.318 MHz system reference clock input.                                   |

| MA2    | 2*  | I           | Memory clock Frequency select address 3.                                            |

| EXCLK  | 3*  | 1           | External clock input. For additional clock frequency.                               |

| A1     | 4*  | I           | Dot clock Frequency select address 2.                                               |

| A0     | 5*  | I           | Dot clock Frequency select address 1.                                               |

| LEN*   | 6*  | I           | Address latch enable input (active low). To latch selected programmed clock output. |

| A2     | 7*  | I           | Dot clock Frequency select address 3.                                               |

| A3     | 8*  | <u>,</u> 1  | Dot clock Frequency select address 4.                                               |

| MA0    | 9*  | I           | Memory clock Frequency select address 1.                                            |

| DGND   | 10  | 0           | Digital ground.                                                                     |

| MA1    | 11* | I           | Memory clock Frequency select address 2.                                            |

| MCLK   | 12  | 0           | Programmed memory clock output frequency.                                           |

| N.C.   | 13  |             | No connect.                                                                         |

| MCLKE  | 14* | 1           | MCLK output enable.                                                                 |

| AVCC   | 15  | I           | Analog supply voltage. Single +5 volts.                                             |

| AGND   | 16  | 0           | Analog ground.                                                                      |

| N.C.   | 17  |             | No connect.                                                                         |

| DCLKE  | 18* | I           | DCLK output enable.                                                                 |

| DCLK   | 19  | 0           | Programmed video clock output frequency.                                            |

| DVCC   | 20  | I           | Digital supply voltage. Single +5 volts.                                            |

\* Have internal pull-up resistors on inputs

#### **GENERAL INFORMATION**

The ST49C063/64 is programmed to generate 15 different video clock frequencies using the A0-A3 inputs and 8 different memory frequencies using M0-M2 inputs. The address lines A2-A3 can be connected to video controller like Western Digital Imaging VGA controllers. Address lines A0 and A1 are latched with LEN\* pin which is generated from video controllers to select proper Dot clock output. All inputs to the ST49C063/64 contain internal pull-up resistors including CLK and EXCLK inputs.

The EXCLK is additional input that may be internally connected to the DCLK output. The additional input is useful for supporting modes that require frequencies not provided by the ST49C063/64.

#### FREQUENCY SELECT CALCULATION

The ST49C063/64 contains an analog phase locked loop circuit with a digital closed loop divider and a final series divider to achieve desired dividing ratios for clock output.

The accuracy of the frequencies produced by the ST49C063/64 depends on the input frequency and final output frequency. The formula for calculating the exact output frequency is as follows:

DCLK = (Reference clock) X (A/B.C) MCLK = (Reference clock) X (A/B.C)

where A=1,2,3,.....127, B=1,2,3,.....127, and C=1,2,4

For proper output frequency, the ST49C063/64 can accept reference frequency from 5 - 40 MHz and divider ratio up to 15.

#### MASK OPTIONS

The following mask options are provided for custom applications.

\* Any frequency can be in any decoding position.

\* DCLK, can control selection of the internal frequencies.

#### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

#### DC ELECTRICAL CHARACTERISTICS

$T_{A}$ =25° C,  $V_{cc}$ =5.0 V ± 5% unless otherwise specified.

| Symbol                                                                                                                            | Parameter                                                                                                                                    | Min        | Limits<br>Typ | Max                           | Units                   | Conditions                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-------------------------------|-------------------------|--------------------------------------------------------------------------------------------|

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>OL</sub><br>V <sub>OH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub><br>I <sub>CC</sub> | Input low level<br>Input high level<br>Output low level<br>Output high level<br>Input low current<br>Input high current<br>Operating current | 2.0<br>2.4 | 20            | 0.8<br>0.4<br>-350<br>1<br>30 | V<br>V<br>V<br>µA<br>mA | I <sub>ol</sub> = 8.0 mA<br>I <sub>OH</sub> = 8.0 mA<br>VIN=Vcc<br>No load.<br>DCLK=80MHz, |

| $R_{in}$                                                                                                                          | Internal pull-up resistance                                                                                                                  | 15         | 20            | 25                            | kΩ                      | MCLK=40MHz                                                                                 |

ST49C063/64

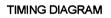

### AC ELECTRICAL CHARACTERISTICS

| Symbol                                                                                                                  | Parameter                                                                                                                                                                                                                                   | Min                                  | Limits<br>Typ                   | Max                                              | Units                                                  | Conditions                                                            |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------|--------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------|

| $T_{1}$<br>$T_{2}$<br>$T_{3}$<br>$T_{5}$<br>$T_{6}$<br>$T_{6}$<br>$T_{7}$<br>$T_{8}$<br>$T_{9}$<br>$T_{10}$<br>$T_{11}$ | Enable pulse width<br>Setup time data to enable<br>Hold time to data enable<br>Rise time<br>Fall time<br>Duty cycle<br>Duty cycle<br>Jitter<br>Input frequency<br>Input clock rise time<br>Input clock fall time<br>Output frequency change | 20<br>20<br>10<br>40<br>45<br>14.318 | 1<br>1<br>48/52<br>48/52<br>±85 | 1.5<br>1.5<br>60<br>55<br>±100<br>32<br>20<br>20 | ns<br>ns<br>ns<br>ns<br>%<br>ps<br>z<br>MHz<br>ns<br>% | 0.8V - 2.0V<br>2.0V - 0.8V<br>1.4V switch point<br>Vcc/2 switch point |

ST49C063/64

|                                                                              |                                                                    |                                                               |                                                                    |                                                                  | ST49C063                                                                                                                                                    | ST49C064                                                                                                                                                    |

|------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Video<br>clock<br>address<br>(Hex)                                           | A3                                                                 | A2                                                            | A1                                                                 | A0                                                               | Frequency<br>(MHz)                                                                                                                                          | Frequency<br>(MHz)                                                                                                                                          |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>E<br>F | 0<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>1<br>1<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>1 | 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0<br>1 0 | 30.000<br>77.250<br>EXCLK<br>80.000<br>31.500<br>36.000<br>75.000<br>50.000<br>40.000<br>50.000<br>32.000<br>44.900<br>25.175<br>28.322<br>65.000<br>36.000 | 30.000<br>77.250<br>EXCLK<br>80.000<br>31.500<br>36.000<br>75.000<br>50.000<br>40.000<br>50.000<br>32.000<br>44.900<br>25.175<br>28.322<br>65.000<br>36.000 |

| Memory<br>clock<br>address<br>(Hex)                                          |                                                                    | MA2                                                           | MA1                                                                | MAO                                                              | Frequency<br>(MHz)                                                                                                                                          | Frequency<br>(MHz)                                                                                                                                          |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7                                         |                                                                    | 0<br>0<br>0<br>1<br>1<br>1<br>1                               | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1                               | 0<br>1<br>0<br>1<br>0<br>1<br>0                                  | 33.000<br>50.000<br>60.000<br>30.500<br>40.000<br>37.500<br>36.000<br>44.900                                                                                | 33.000<br>49.218<br>60.000<br>30.500<br>41.612<br>37.500<br>36.000<br>44.296                                                                                |

Compatible with Video Controller

ICS-90C63 WD90C30 ICS-90C64 WD90C30

# ST49C103 ST49C104

Printed May 17, 1993

### PREPROGRAMMED FREQUENCY GENERATOR $\angle$

#### DESCRIPTION

The ST49C103 and ST49C104 are mask programmable monolithic analog CMOS devices designed to generate up to 8 single frequency outputs from a single input clock. The ST49C104 will provide eight different output frequencies and the ST49C103 will provide four different output frequencies. They are designed in a  $1.2\mu$  process to achieve 130 MHz speed for high end frequencies.

The ST49C103 and ST49C104 are designed to replace existing video clocks generated from individual oscillators in order to reduce board space and number of oscillators. To provide high speed and low jitter clock, the parts utilize a high speed analog CMOS phase locked loop using 14.318 MHz system clock as the reference clock (note that reference clock can be changed to generate optional frequencies from a standard programmed device). The programmed clock outputs are selectable via three address lines and address latch enable pin. The ST49C104 also includes a power on reset circuit which will cause the select logic to select the frequency at address "000" upon power up. The latch enable pin is also mask programmable to be active high, active low or rising or falling edge sensitive.

### **FEATURES**

- Can replace up to 8 oscillators/crystals and a multiplexer

- Pin-to-pin compatible to Avasem AV9103/104

- Programmable analog phase locked loop

- Low power single 5V CMOS technology

- 8 or 14 pin DIP or SOIC package.

#### ORDERING INFORMATION

| Part number  | Package     | Operating tempe | rature |

|--------------|-------------|-----------------|--------|

| ST49C103CP8  | Plastic-DIP | 0°C to +7       | '0° C  |

| ST49C103CF8  | SOIC        | 0°C to +7       | '0° C  |

| ST49C104CP8  | Plastic-DIP | 0°C to +7       | '0° C  |

| ST49C104CF8  | SOIC        | 0°C to +7       | '0° C  |

| ST49C104CP14 | Plastic-DIP | 0°C to +7       | '0° C  |

| ST49C104CF14 | SOIC        | 0°C to +7       | '0° C  |

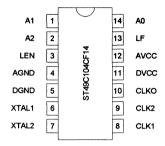

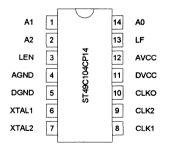

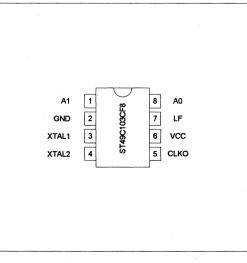

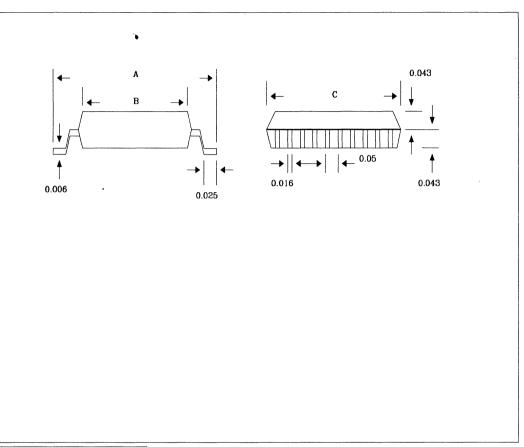

#### SOIC Package

EVALUATION KIT AVAILABLE

#### Plastic-DIP package

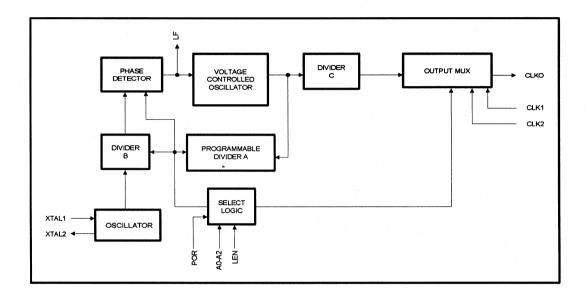

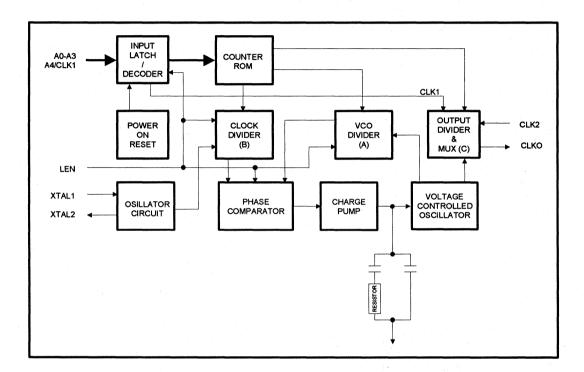

#### **BLOCK DIAGRAM**

1

### SYMBOL DESCRIPTION (ST49C104 14 pin package)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                     |  |

|--------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1     | 1   | I           | Frequency select address input 2.                                                                                                                                                                                                   |  |

| A2     | 2*  | 1           | Frequency select address input 3.                                                                                                                                                                                                   |  |

| LEN    | 3*  | I           | Address latch enable input. To latch selected programmed<br>clock output.                                                                                                                                                           |  |

| AGND   | 4   | 0           | Analog ground.                                                                                                                                                                                                                      |  |

| DGND   | 5   | 0           | Digital ground.                                                                                                                                                                                                                     |  |

| XTAL1  | 6   | I           | Crystal or external clock input. A crystal can be connect<br>to this pin and XTAL2 pin to generate internal phase lock<br>loop reference clock. For external 14.318 MHz clo<br>XTAL2 is left open or used as buffered clock output. |  |

| XTAL2  | 7   | 0           | Crystal output.                                                                                                                                                                                                                     |  |

| CLK1   | 8   | 1           | External clock 1 input.                                                                                                                                                                                                             |  |

| CLK2   | 9   | 1           | External clock 2 input / output select.                                                                                                                                                                                             |  |

| сіко   | 10  | 0           | Programmed output clock.                                                                                                                                                                                                            |  |

| DVCC   | 11  | I           | Digital supply voltage. Single +5 volts.                                                                                                                                                                                            |  |

| AVCC   | 12  | 1           | Analog supply voltage. Single +5 volts.                                                                                                                                                                                             |  |

| LF     | 13  | 0           | Loop filter.                                                                                                                                                                                                                        |  |

| A0     | 14  | 1           | Frequency select address input 1.                                                                                                                                                                                                   |  |

\* Have internal pull-up resistors on inputs.

1-21

ST49C103/104

### SYMBOL DESCRIPTION (ST49C104 8 pin package)

| Symbol | Pin                                     | Signal Type  | Pin Description                                                    |

|--------|-----------------------------------------|--------------|--------------------------------------------------------------------|

| A1     | 1                                       |              | Frequency select address input 2.                                  |

| A2     | 2*                                      | l I          | Frequency select address input 3.                                  |

| GND    | 3                                       | 0            | Digital ground.                                                    |

| EXCLK  | 4                                       | I            | External clock input. Internal phase locked loop reference clock . |

| сіко   | 5                                       | 0            | Programmed output clock.                                           |

| vcc    | 6 · · · · · · · · · · · · · · · · · · · | a an Italian | Digital supply voltage. Single +5 volts.                           |

| LF     |                                         | Ο            | Loop filter.                                                       |

| A0     | 8                                       | l i          | Frequency select address input 1.                                  |

\* Has internal pull-up resistor on input

### SYMBOL DESCRIPTION (ST49C103 8pin package)

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1   | I           | Frequency select address input 2.                                                                                                                                                                                                          |

| GND    | 2   | 0           | Digital ground.                                                                                                                                                                                                                            |

| XTAL1  | 3   | 1           | Crystal or external clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 4   | 0           | Crystal output.                                                                                                                                                                                                                            |

| СГКО   | 5   | 0           | Programmed output clock.                                                                                                                                                                                                                   |

| vcc    | 6   | I           | Digital supply voltage. Single +5 volts.                                                                                                                                                                                                   |

| LF     | 7   | 0           | Loop filter.                                                                                                                                                                                                                               |

| A0     | 8   | I           | Frequency select address input 1.                                                                                                                                                                                                          |

ST49C103/104

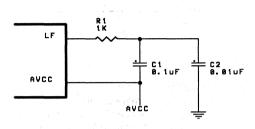

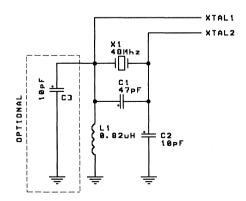

#### LOOP FILTER

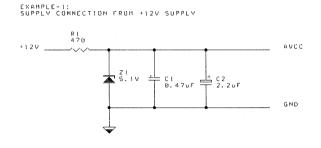

The loop filter must be connected as follows for proper operation.

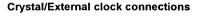

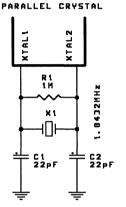

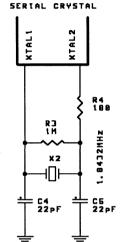

#### **EXTERNAL CLOCK CONNECTION**

To minimize the noise pickup, it is recommended to connect  $0.047\mu$ F capacitor to XTAL1, and keep the lead length of the capacitor to XTAL1 to a minimum to reduce noise susceptibility.

#### FREQUENCY SELECT CALCULATION

The ST49C104 contains an analog phase locked loop circuit with digital closed loop dividers and a final output multiplexer to achieve the desired dividing ratios for the clock output.

The accuracy of the frequencies produced by the ST49C104 depends on the input frequency and divider ratios. The formula for calculating the exact output frequency is as follows:

CLKO = (Reference clock) X A/(B.C)

where

A=1,2,3,.....127 B=8, 16, 32 ,64 C=1,2,4,8

For proper output frequency, the ST49C104 can accept a reference frequency from 5 - 40 MHz and divider ratio up to 15.

#### MASK OPTIONS

The following mask options are provided for custom applications.

\* Latch Enable can be edge triggered or level sensitive.

- \* Latch Enable can be active high or active low.

- \* Any frequency can be in any decoding position.

- \* CLK 1 and CLK 2 can be included in decoding table.

- \* CLK2 can control selection of either CLK 1 or the internal frequencies.

| FEATURE                             | ST49C104<br>14-pin | ST49C104<br>8-pin | ST49C103<br>8-pin |

|-------------------------------------|--------------------|-------------------|-------------------|

| 8 output frequencies                | x                  | x                 |                   |

| 4 output frequencies                |                    |                   | X                 |

| Programmable LEN pin                | X                  | X                 | X                 |

| Clock input only                    | e*                 |                   |                   |

| Crystal or clock input              | X                  |                   | X                 |

| CLK1, CLK2 available for output mux | X                  |                   |                   |

| Address latch (LEN) | State                    |

|---------------------|--------------------------|

| ST49C104-1          | Transparent for LEN high |

| ST49C104-2          | Transparent for LEN low  |

| ST49C104-3          | Transparent for LEN low  |

# 1

### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

### DC ELECTRICAL CHARACTERISTICS

$T_{A}$ =25° C,  $V_{cc}$ =5.0 V ± 5% unless otherwise specified.

| Symbol                                                                   | Parameter                | Min | Limits<br>Typ | Max  | Units | Conditions               |

|--------------------------------------------------------------------------|--------------------------|-----|---------------|------|-------|--------------------------|

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>OL</sub><br>V <sub>OH</sub> | Input low level          |     |               | 0.8  | V     |                          |

| . V <sup>IH</sup>                                                        | Input high level         | 2.0 |               |      | V     |                          |

| V <sub>OL</sub>                                                          | Output low level         |     |               | 0.4  | V     | l <sub>oL</sub> = 8.0 mA |

| V <sub>oH</sub>                                                          | Output high level        | 2.4 |               |      | V     | I <sub>он</sub> = 8.0 mA |

| l <sub>iL</sub>                                                          | Input low current        |     |               | -350 | μA    | Except crystal<br>input  |

| l <sub>in</sub>                                                          | Input high current       |     |               | 1    | μA    | V <sub>IN</sub> =Vcc     |

| I <sub>cc</sub>                                                          | Operating current        |     | 20            | 30   | mA    | No load.<br>DCLK=80MHz   |

| R <sub>IN</sub>                                                          | Input pull-up resistance | 15  | 20            | 25   | KΩ    |                          |

# ST49C103/104

ST49C103/104

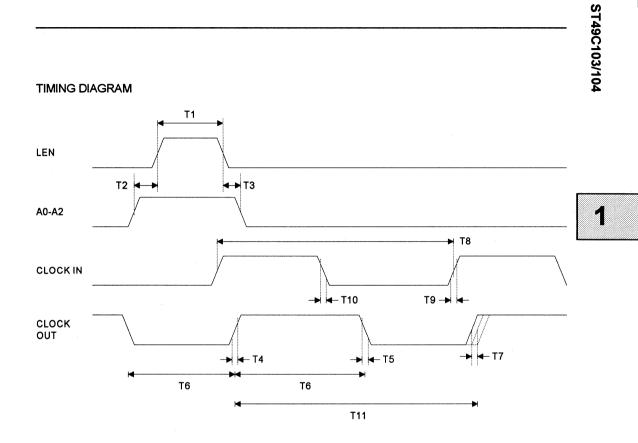

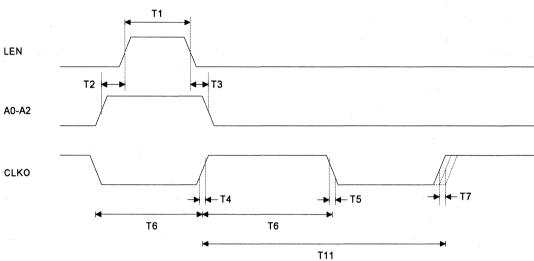

### AC ELECTRICAL CHARACTERISTICS

| $T_{A}=25^{\circ}$ C, $V_{cc}=5.0$ V ± 5% unless other | wise specified. |

|--------------------------------------------------------|-----------------|

|--------------------------------------------------------|-----------------|

| Symbol                                                                                                  | Parameter                                                                                                                                                                                                                                   | Min                                  | Limits<br>Typ                            | Max                                              | Units                                                       | Conditions                                                            |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|

| $T_{1}^{1}$<br>$T_{2}^{2}$<br>$T_{3}^{4}$<br>$T_{5}^{6}$<br>$T_{6}^{7}$<br>$T_{8}^{9}$<br>$T_{11}^{10}$ | Enable pulse width<br>Setup time data to enable<br>Hold time to data enable<br>Rise time<br>Fall time<br>Duty cycle<br>Duty cycle<br>Jitter<br>Input frequency<br>Input clock rise time<br>Input clock fall time<br>Output frequency change | 20<br>20<br>10<br>40<br>45<br>14.318 | 1<br>1<br>48/52<br>48/52<br>±85<br>0.005 | 1.5<br>1.5<br>60<br>55<br>±100<br>32<br>20<br>20 | ns<br>ns<br>ns<br>ns<br>%<br>%<br>ps<br>MHz<br>ns<br>s<br>% | 0.8V - 2.0V<br>2.0V - 0.8V<br>1.4V switch point<br>Vcc/2 switch point |

# ST49C103/104

# ST49C103/104

ST49C103/104

| A2 A             | 11          |                                      | ST49C                                                                    | 104-1<br>ACTUAL                                                          | ST490<br>NOMINAL                                                             | 104-2<br>ACTUAL                                                              | ST49C                                                                        | 104-3<br>ACTUAL                                                               | ST49C<br>NOMINAL                                                             |                                                                               | ST490<br>NORMAL                                              | C103**<br>ACTUAL                |

|------------------|-------------|--------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------|

| 0<br>0<br>1<br>1 | 0<br>1<br>1 | 0<br>1<br>0<br>1<br>0<br>1<br>0<br>1 | Xtal<br>16.257<br>Clk2<br>32.514<br>25.175<br>28.322<br>24.000<br>40.000 | Xtal<br>16.331<br>Clk2<br>32.663<br>25.056<br>28.412<br>23.938<br>39.822 | 25.175<br>28.322<br>32.514<br>36.000<br>40.000<br>44.900<br>50.000<br>65.000 | 25.280<br>28.412<br>32.663<br>35.795<br>39.822<br>44.744<br>50.113<br>65.326 | 50.350<br>56.664<br>65.028<br>72.000<br>80.000<br>89.800<br>75.000<br>108.00 | 50.560<br>56.824<br>65.326<br>71.590<br>79.640<br>89.488<br>75.169<br>108.280 | 39.000<br>25.000<br>30.750<br>26.250<br>32.000<br>25.250<br>31.250<br>37.500 | 39.0000<br>25.000<br>30.750<br>26.250<br>32.000<br>25.250<br>31.250<br>37.500 | 32.000<br>40.00<br>50.00<br>1.00<br>N/A<br>N/A<br>N/A<br>N/A | 32.00<br>40.00<br>50.00<br>1.00 |

| A2 A1 A0                                                                                                                                  | ST49C104-6**<br>Nominal Actual                                                                   |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| $\begin{array}{ccccccc} 0 & 0 & 0 \\ 0 & 0 & 1 \\ 0 & 1 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 0 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \\ 1 & 1 & 1 \end{array}$ | 25.50025.50016.50016.50020.75020.75022.50022.50024.50024.50019.50019.50015.00015.00014.00014.000 |  |  |

Input clock frequency = 14.318 MHz \* Input clock frequency = 16.0 MHz \*\* Input clock frequency = 8.0 MHz

Printed May 17, 1993

### EVALUATION KIT PREPROGRAMMED FREQUENCY GENERATOR

### DESCRIPTION

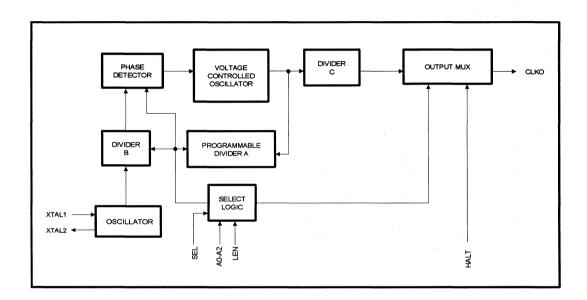

The ST49C106 is a mask programmable monolithic analog CMOS device designed to generate up to 8 single frequency outputs from a single input clock. The ST49C106 is designed in a 1.2µ process to achieve 130 MHz speed for high end frequencies.

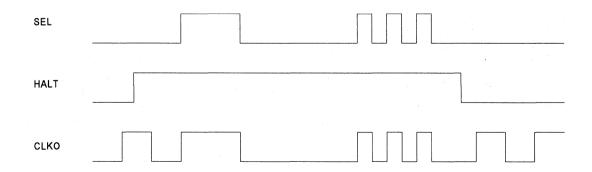

The ST49C106 is designed to replace existing video clocks generated from individual oscillators in order to reduce board space and number of oscillators. To provide high speed and low jitter clock, the parts utilize a high speed analog CMOS phase locked loop using 14.318 MHz system clock as the reference clock (note that reference clock can be changed to generate optional frequencies from a standard programmed device). The programmed clock outputs are selectable via three address lines and address latch enable pin. The ST49C106 also includes a power on reset circuit which will cause the select logic to select the frequency at address "000" upon power up. The ST49C106 contains de-glitch circuit so that full clock cycles are provided whenever the HALT pin stops or starts the output clock.

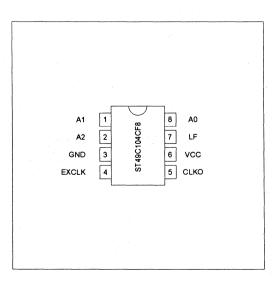

#### **SOIC Package**

AVAILABLE

#### Plastic-DIP package

### **FEATURES**

- . Can replace up to 8 oscillators/crystals and a multiplexer

- Pin-to-pin compatible to Avasem AV9106-14

- Programmable analog phase locked loop

- Low power single 5V CMOS technology

- 14 pin DIP or SOIC package.

### ORDERING INFORMATION

| Part number  | Package     | Operating temperature |

|--------------|-------------|-----------------------|

| ST49C106CP14 | Plastic-DIP | 0°C to +70°C          |

| ST49C106CF14 | SOIC        | 0° C to +70° C        |

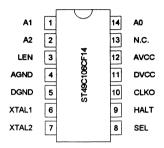

### **BLOCK DIAGRAM**

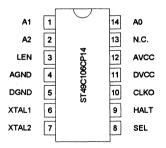

### SYMBOL DESCRIPTION

| Symbol | Pin | Signal Type | Pin Description                                                                                                                                                                                                                            |

|--------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | 1   | l 1         | Frequency select address input 2.                                                                                                                                                                                                          |

| A2     | 2*  | 1           | Frequency select address input 3.                                                                                                                                                                                                          |

| LEN    | 3*  | 1           | Address latch enable input. To latch selected programmed<br>clock output.                                                                                                                                                                  |

| AGND   | 4   | 0           | Analog ground.                                                                                                                                                                                                                             |

| DGND   | 5   | 0           | Digital ground.                                                                                                                                                                                                                            |

| XTAL1  | 6   | I           | Crystal or external clock input. A crystal can be connected<br>to this pin and XTAL2 pin to generate internal phase locked<br>loop reference clock. For external 14.318 MHz clock,<br>XTAL2 is left open or used as buffered clock output. |

| XTAL2  | 7   | 0           | Crystal output.                                                                                                                                                                                                                            |

| SEL    | 8   | I           | Clock level select / CLK1. When HALT is asserted, SEL selects whether the clock is high or low. This level must be selected before the clock is halted. SEL pin can be used as an xternal clock input when HALT is active.                 |

| HALT   | 9   | 1           | Start / Stop output clock.                                                                                                                                                                                                                 |

| CLKO   | 10  | 0           | Programmed output clock.                                                                                                                                                                                                                   |

| DVCC   | 11  | 1           | Digital supply voltage. Single +5 volts.                                                                                                                                                                                                   |

| AVCC   | 12  | 1           | Analog supply voltage. Single +5 volts.                                                                                                                                                                                                    |

| A0     | 14  | 1           | Frequency select address input 1.                                                                                                                                                                                                          |

\* Have internal pull-up resistors on inputs.

#### EXTERNAL CLOCK CONNECTION

To minimize the noise pickup, it is recommended to connect  $0.047\mu$ F capacitor to XTAL1, and keep the lead length of the capacitor to XTAL1 to a minimum to reduce noise susceptibility.

#### FREQUENCY SELECT CALCULATION

The ST49C106 contains an analog phase locked loop circuit with digital closed loop dividers and a final output multiplexer to achieve the desired dividing ratios for the clock output.

The accuracy of the frequencies produced by the ST49C106 depends on the input frequency and divider ratios. The formula for calculating the exact output frequency is as follows:

CLKO = (Reference clock) X A/(B.C)

where

A=1,2,3,.....127 B=8, 16, 32 ,64 C=1,2,4,8

For proper output frequency, the ST49C106 can accept a reference frequency from 5 - 40 MHz and divider ratio up to 15.

#### **ABSOLUTE MAXIMUM RATINGS**

Supply range Voltage at any pin Operating temperature Storage temperature Package dissipation 7 Volts GND-0.3 V to VCC+0.3 V 0° C to +70° C -40° C to +150° C 500 mW

### DC ELECTRICAL CHARACTERISTICS

$T_a=25^{\circ}$  C,  $V_{cc}=5.0$  V ± 5% unless otherwise specified.

| Symbol                                                                   | Parameter                                                                    | Min        | Limits<br>Typ | Max             | Units          | Conditions                                                  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------|------------|---------------|-----------------|----------------|-------------------------------------------------------------|

| V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>OL</sub><br>V <sub>OH</sub> | Input low level<br>Input high level<br>Output low level<br>Output high level | 2.0<br>2.4 |               | 0.8<br>0.4      | V<br>V<br>V    | I <sub>оL</sub> = 8.0 mA<br>I <sub>он</sub> = 8.0 mA        |

| I <sub>⊫</sub><br>I <sub>⊮</sub><br>I <sub>cc</sub>                      | Input low current<br>Input high current<br>Operating current                 | -          | 20            | -350<br>1<br>30 | μA<br>μA<br>mA | Except crystal<br>input<br>V <sub>IN</sub> =Vcc<br>No load. |

| R <sub>IN</sub>                                                          | Input pull-up resistance                                                     | 15         | 20            | 25              | KΩ             | DCLK=80MHz                                                  |

### AC ELECTRICAL CHARACTERISTICS

$\rm T_{A}=25^{\circ}$  C,  $\rm ~V_{cc}=5.0~V\pm5\%$  unless otherwise specified.

| Symbol                                                                                                                  | Parameter                                                                                                                                                                                                                                   | Min                                  | Limits<br>Typ                   | Max                                              | Units                                                      | Conditions                                                            |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------|--------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------|

| $T_{1}$<br>$T_{2}$<br>$T_{3}$<br>$T_{4}$<br>$T_{5}$<br>$T_{6}$<br>$T_{7}$<br>$T_{8}$<br>$T_{9}$<br>$T_{10}$<br>$T_{11}$ | Enable pulse width<br>Setup time data to enable<br>Hold time to data enable<br>Rise time<br>Fall time<br>Duty cycle<br>Duty cycle<br>Jitter<br>Input frequency<br>Input clock rise time<br>Input clock fall time<br>Output frequency change | 20<br>20<br>10<br>40<br>45<br>14.318 | 1<br>1<br>48/52<br>48/52<br>±85 | 1.5<br>1.5<br>60<br>55<br>±100<br>32<br>20<br>20 | ns<br>ns<br>ns<br>ns<br>%<br>%<br>%<br>MHz<br>ns<br>s<br>% | 0.8V - 2.0V<br>2.0V - 0.8V<br>1.4V switch point<br>Vcc/2 switch point |

| A2 | A1 | AO | ST49C   | 106-5* |

|----|----|----|---------|--------|

|    |    |    | NOMINAL | ACTUAL |

| 0  | 0  | 0  | 39.000  | 39.000 |

| 0  | 0  | 1  | 25.000  | 25.000 |

| 0  | 1  | 0  | 30.750  | 30.750 |

| 0  | 1  | 1  | 26.250  | 26.250 |

| 1  | 0  | 0  | 32.000  | 32.000 |

| 1  | 0  | 1  | 25.250  | 25.250 |

| 1  | 1  | 0  | 31.250  | 31.250 |

| 1  | 1  | 1  | 37.500  | 37.500 |

Printed May, 1993

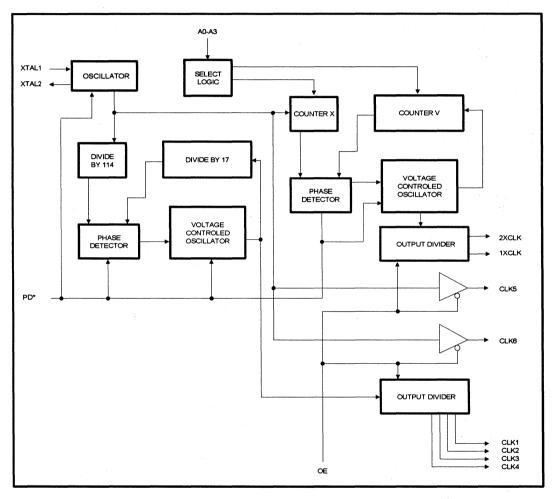

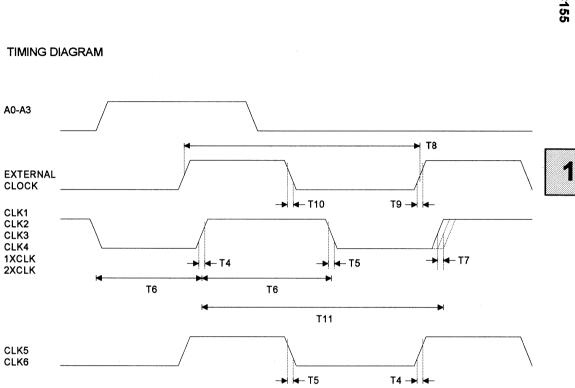

### PREPROGRAMMED CPU MOTHERBOARD FREQUENCY GENERATOR

#### **GENERAL DESCRIPTION**

The ST49C155 is a monolithic analog CMOS device designed to generate eight simultaneous clock outputs for mother board applications. It is designed in a 1.2m process to achieve 130 MHz operation with low clock jitter.

The ST49C155 may be used to replace existing BUS and I/O clocks generated from individual oscillators so that board space and number of oscillators are reduced. The high speed analog CMOS phase locked loops use the 14.318 MHz system clock or external crystal connected between XTAL1 and XTAL2 as the reference clock (reference clock can be changed to generate non-standard frequencies from the standard programmed device).

The ST49C155 is metal mask programmable to provide any custom set of CPUCLK frequencies. The programmed clock outputs are selectable via four address lines for 1XCLK / 2XCLK outputs.

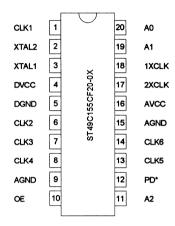

#### **SOIC Package**

# 1

#### **FEATURES**

- Can replace multiple oscillators/crystals

- Pin -to-pin compatible to AV9155

- Compatible with 286, 386, and 486 CPUs

- Supports Turbo modes

- Generates communications clock, keyboard clock, floppy disk clock, system reference clock, bus clock and CPU clock

- Skew controlled 2X and 1X clocks

- · Programmable analog phase locked loop

- High speed (up to 130 MHz output)

- Low power single 5V CMOS technology

- 20 pin dip or SOIC package

#### ORDERING INFORMATION

| Part number     | Package     | Opera | atin | g tei | mperati | ure |

|-----------------|-------------|-------|------|-------|---------|-----|

| ST49C155CP20-xx | Plastic-DIP | 0°    | С    | to    | +70°    | С   |

| ST49C155CF20-xx | SOIC        | 0°    | С    | to    | +70°    | С   |

| ST49C155CJ20-xx | PLCC        | 0°    | С    | to    | +70°    | С   |

### **BLOCK DIAGRAM**

### SYMBOL DESCRIPTION (ST49C155-01/-02)

| Symbol | Pin | Signal Type | Pin Description                                                                        |

|--------|-----|-------------|----------------------------------------------------------------------------------------|

| CLK1   | 1   | 0           | 1.8432 MHz clock output.                                                               |

| XTAL2  | 2   | 0           | Crystal output.                                                                        |

| XTAL1  | 3   | 1           | Crystal or External clock input.                                                       |

| DVCC   | 4   | I           | Digital supply voltage. Single +5 volts.                                               |

| DGND   | 5   | o           | Digital signal ground.                                                                 |

| CLK2   | 6   | 0           | 16 MHz ( ST49C155-01 ) or 32 MHz ( ST49C155-02 ) clock<br>output.                      |

| СLКЗ   | 7   | 0           | 24 MHz floppy disk clock output.                                                       |

| CLK4   | 8   | 0           | 12 MHz keyboard clock output.                                                          |

| AGND   | 9   | 0           | Analog ground.                                                                         |

| OE     | 10* | ο           | Output Enable (active high). Low on this pin sets all the outputs to three state mode. |

| A2     | 11  | ł           | CPU clock frequency select address 2.                                                  |

| PD*    | 12* | 1           | Power down ( active low ). Shuts off entire chip when low.                             |

| CLK5   | 13  | 0           | 14.318 MHz reference clock output.                                                     |

| CLK6   | 14  | 0           | 14.318 MHz reference clock output.                                                     |

| AGND   | 15  | 0           | Analog ground.                                                                         |

| AVCC   | 16  | l ·         | Analog supply voltage. Single +5 volts.                                                |

| 2XCLK  | 17  | 1           | 2X CPU clock output.                                                                   |

| 1XCLK  | 18  | I           | 1X CPU clock output.                                                                   |

| A1     | 19  | I           | CPU clock frequency select address 1.                                                  |

| A0     | 20  | . 1         | CPU clock frequency select address 0.                                                  |

\*Have internal pull-up resistor on inputs

# ST49C155

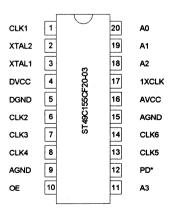

### SYMBOL DESCRIPTION (ST49C155-03)

| Symbol | Pin | Signal Type                                                                                                                                                                                                                        | Pin Description                                                                        |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| CLK1   | 1   | ο                                                                                                                                                                                                                                  | 6 MHz clock output.                                                                    |

| XTAL2  | 2   | 0                                                                                                                                                                                                                                  | Crystal output.                                                                        |

| XTAL1  | 3   | I                                                                                                                                                                                                                                  | Crystal or External clock input.                                                       |

| DVCC   | 4   | 1                                                                                                                                                                                                                                  | Digital supply voltage. Single +5 volts.                                               |

| DGND   | 5   | ο                                                                                                                                                                                                                                  | Digital signal ground.                                                                 |

| CLK2   | 6   | 0 · ·                                                                                                                                                                                                                              | 24 MHz floppy disk clock output.                                                       |

| CLK3   | 7   | ο                                                                                                                                                                                                                                  | 16 MHz bus clock output.                                                               |

| CLK4   | 8   | 0                                                                                                                                                                                                                                  | 8 MHz keyboard clock output.                                                           |

| AGND   | 9   | 0                                                                                                                                                                                                                                  | Analog ground.                                                                         |

| OE     | 10* | 0                                                                                                                                                                                                                                  | Output Enable (active high). Low on this pin sets all the outputs to three state mode. |

| A3     | 11  | I                                                                                                                                                                                                                                  | CPU clock frequency select address 3.                                                  |

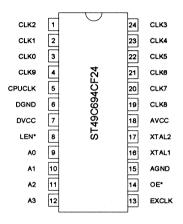

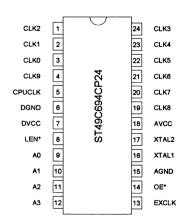

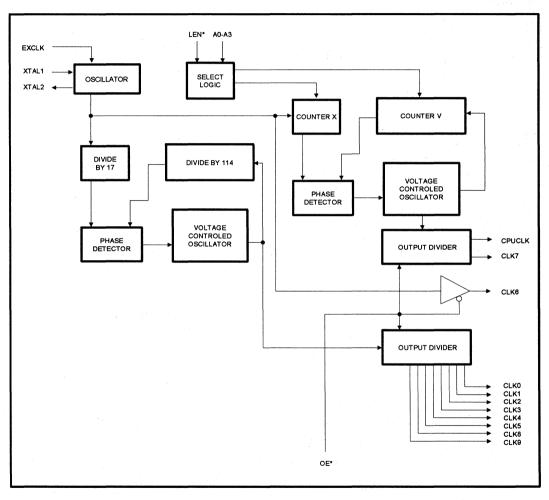

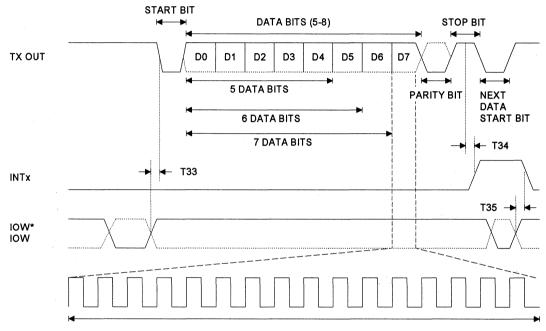

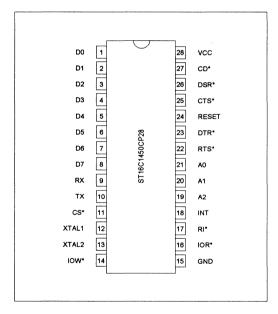

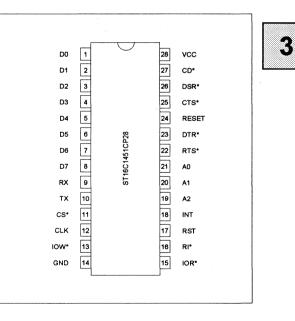

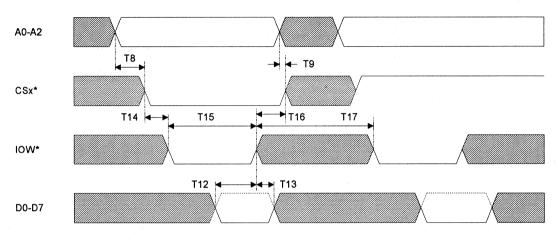

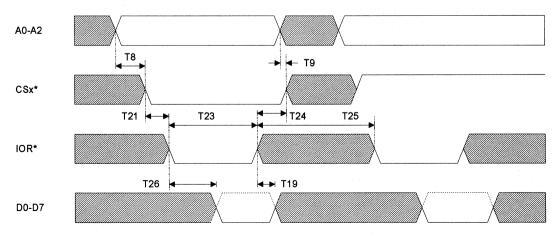

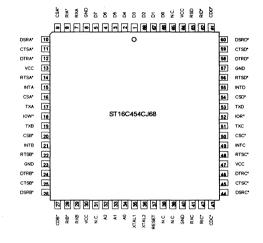

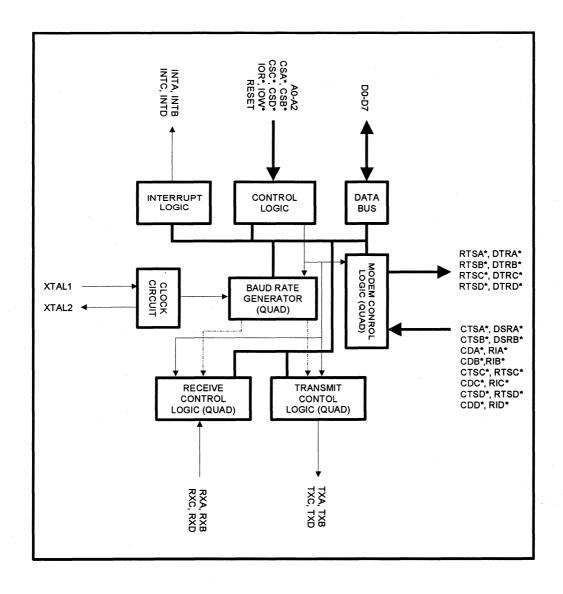

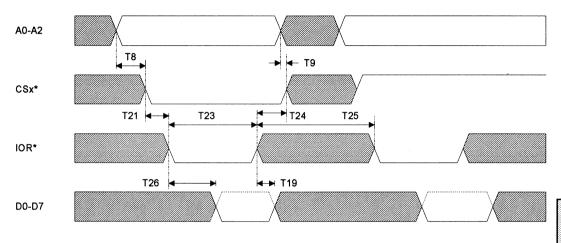

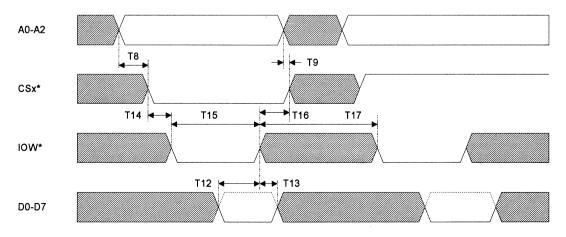

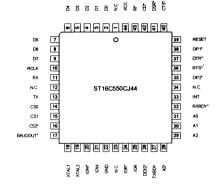

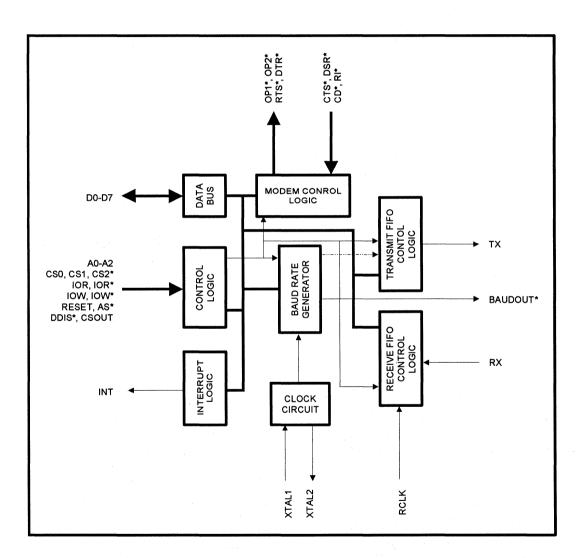

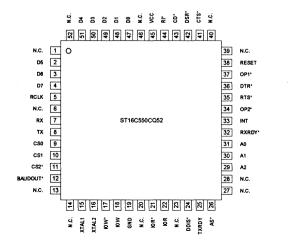

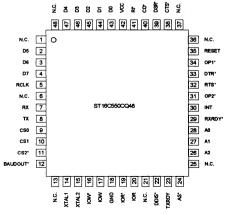

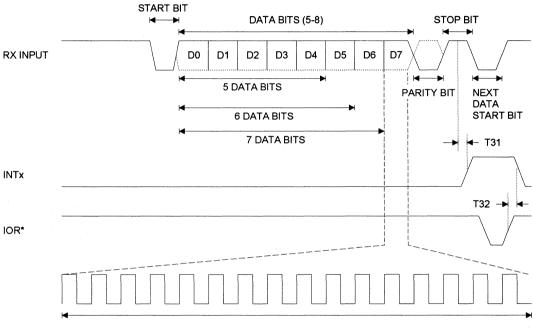

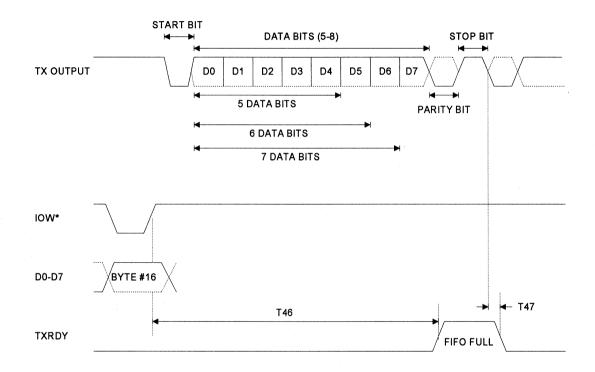

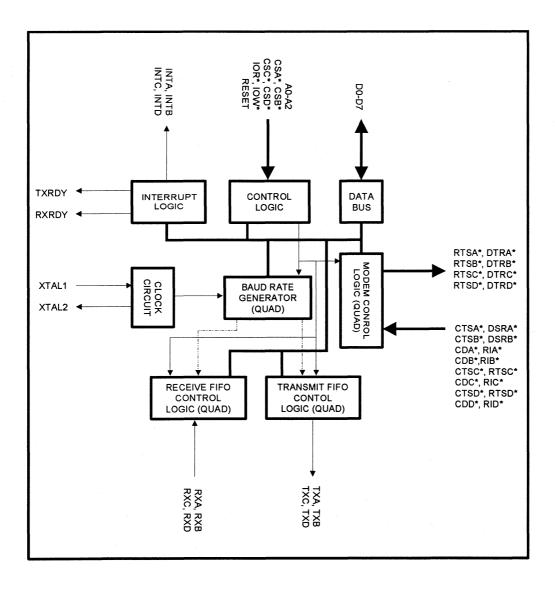

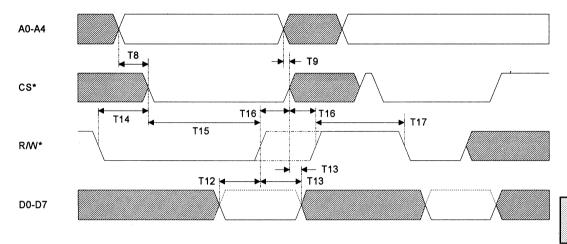

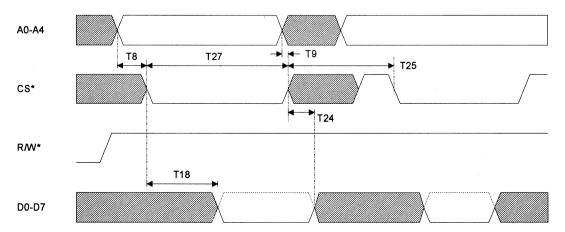

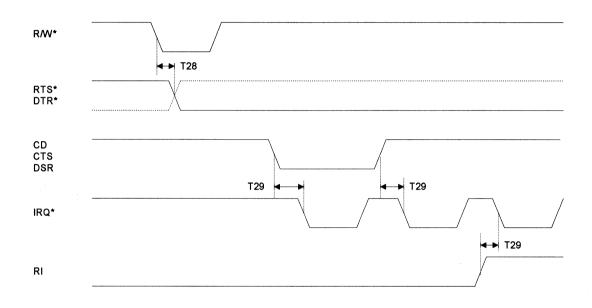

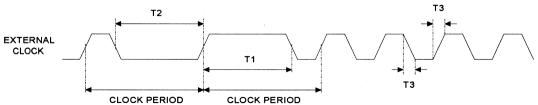

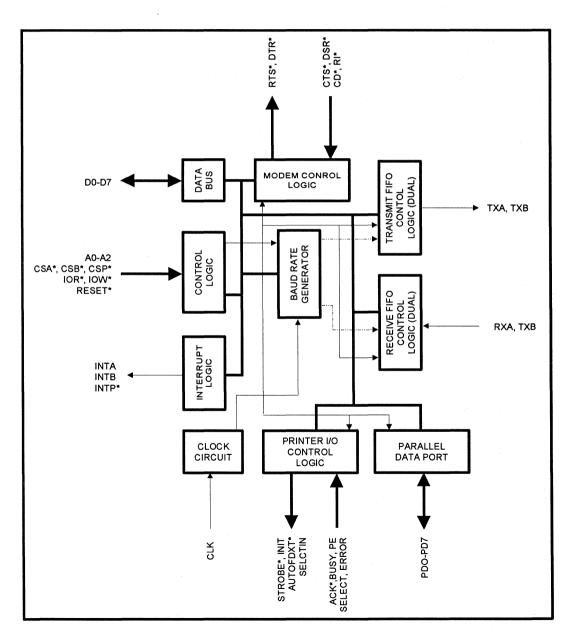

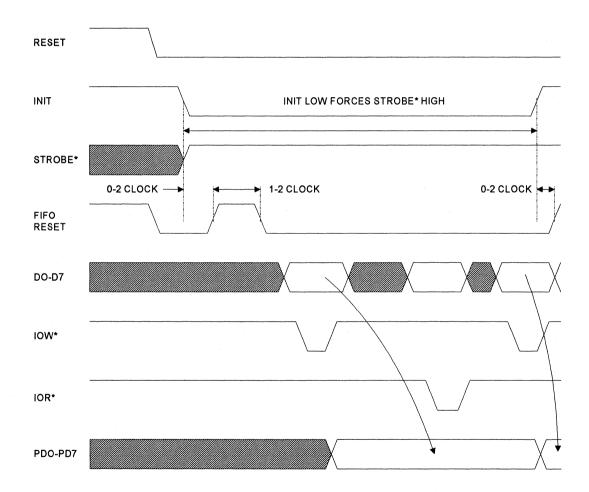

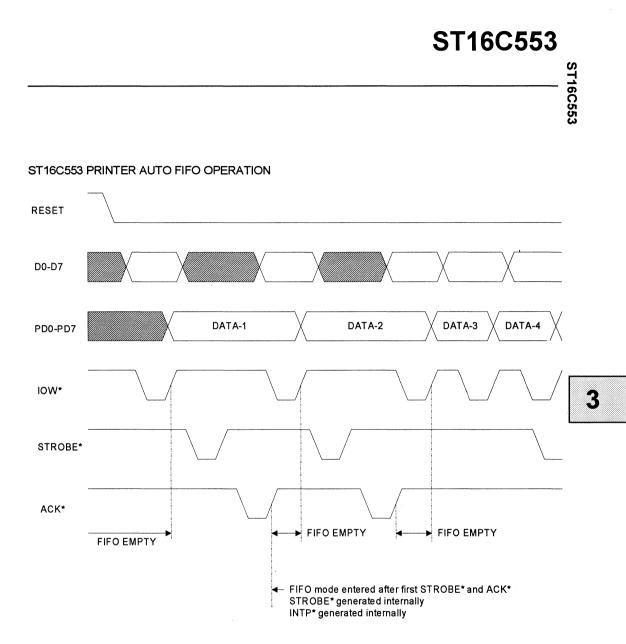

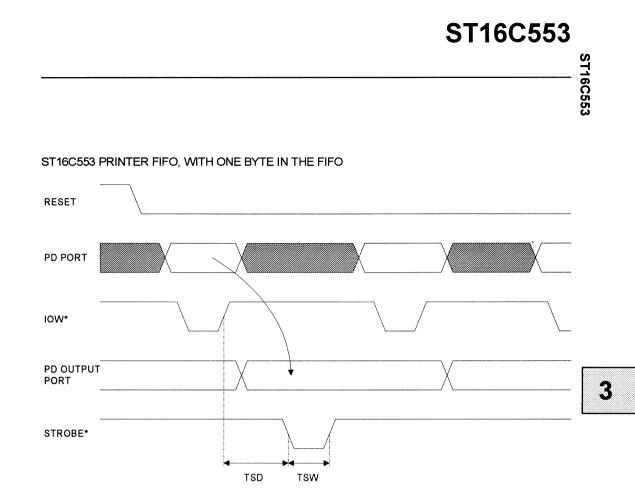

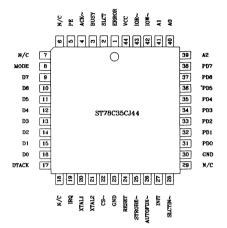

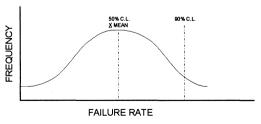

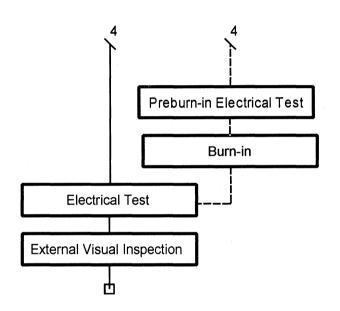

| PD*    | 12* | I .                                                                                                                                                                                                                                | Power down ( active low ). Shuts off entire chip when low.                             |