DATA BOOK 1989

UARTICOMBO

VIDEO

MENORY

MASS STORAGE

COMMUNICATIONS

UART

$\bigcirc$

$\bigcirc$

PRODUCT DATA BOOK 1989

SILICON LOGIC, INC. 550 EAST BROKAW RD. P.O. BOX 49048 SAN JOSE, CA 95161-9048 TEL. (408) 441-1615 FAX (408) 954-0727

# UART

# UART/COMBO

VIDEO

**MEMORY**

**MASS STORAGE**

COMMUNICATION

**APPLICATION NOTES**

QUALITY/RELIABILITY

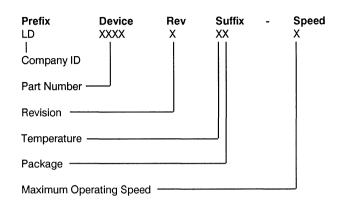

# **ORDERING INFORMATION**

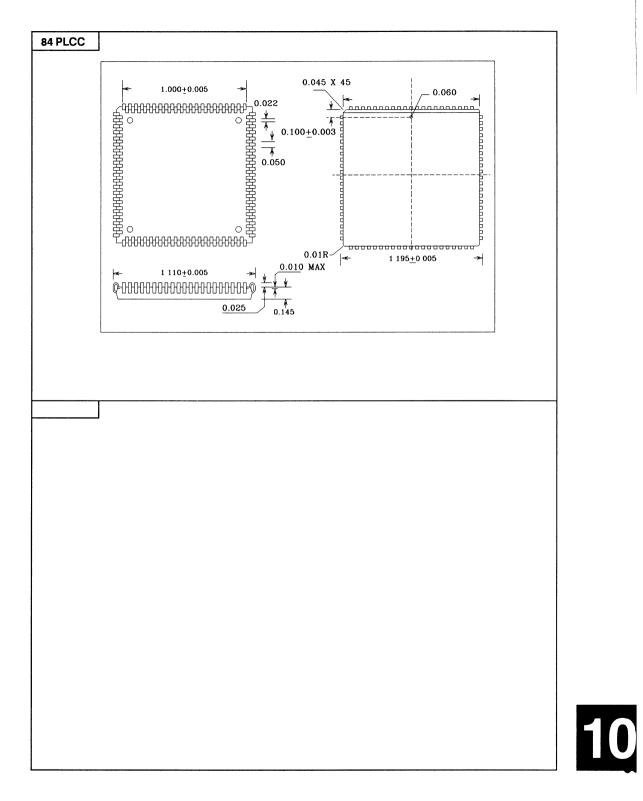

# PACKAGING INFORMATION

١V

.

# CONTENTS

| LD805  | 6-3  |

|--------|------|

| LD806  | 6-15 |

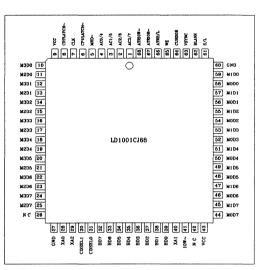

| LD1001 | 3-15 |

| LD1002 | 3-15 |

| LD1101 | 1-3  |

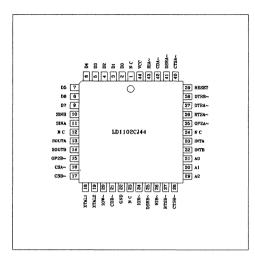

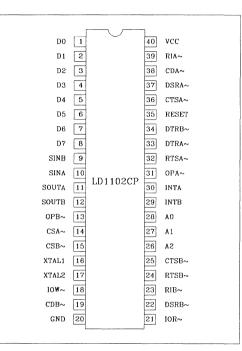

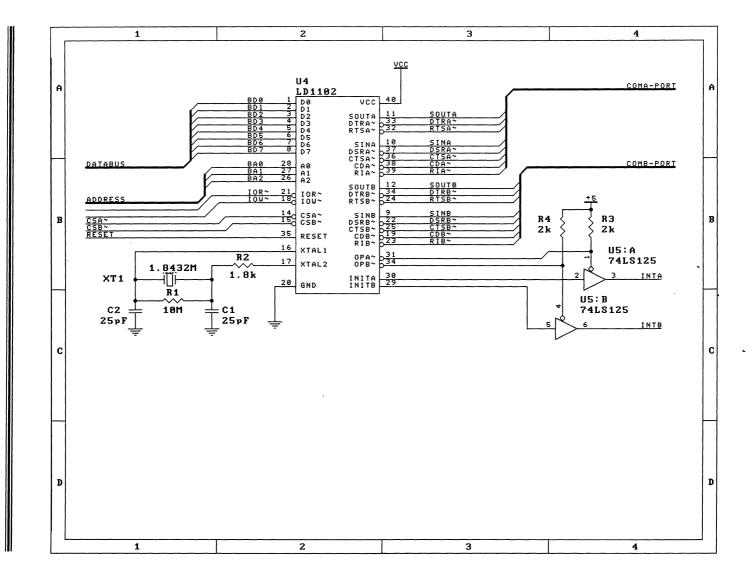

| LD1102 | 1-37 |

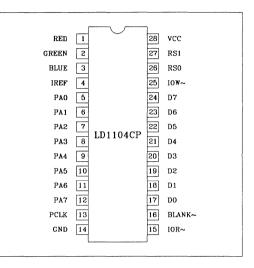

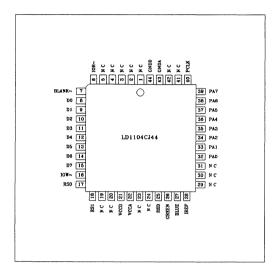

| LD1104 | 3-3  |

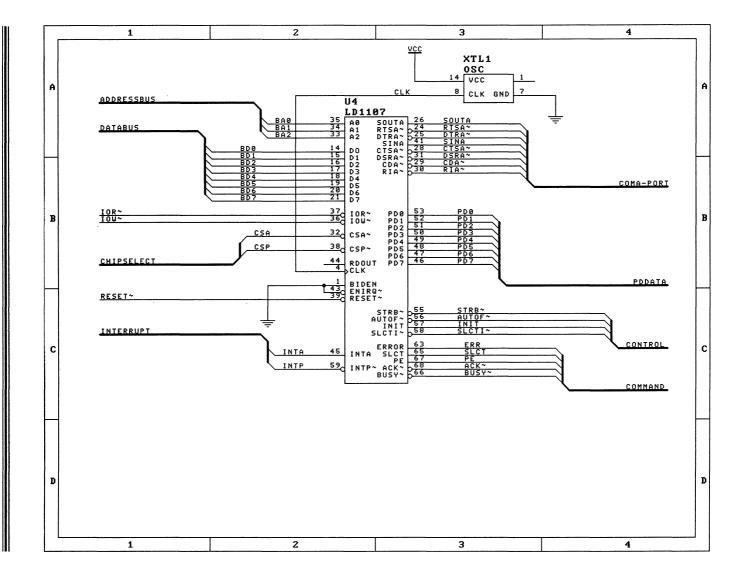

| LD1107 | 2-3  |

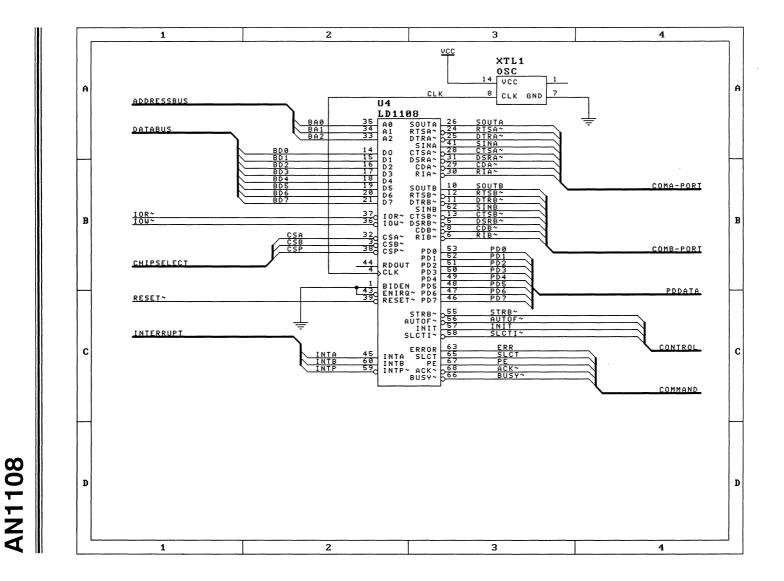

| LD1108 | 2-21 |

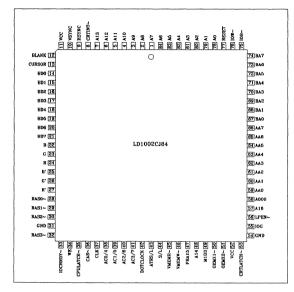

| LD1111 | 5-3  |

| LD1201 | 1-19 |

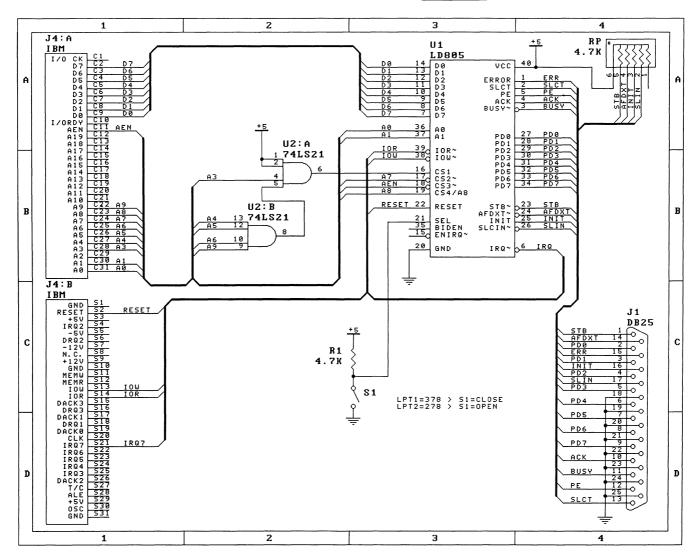

| AN805  | 7-3  |

| AN806  | 7-5  |

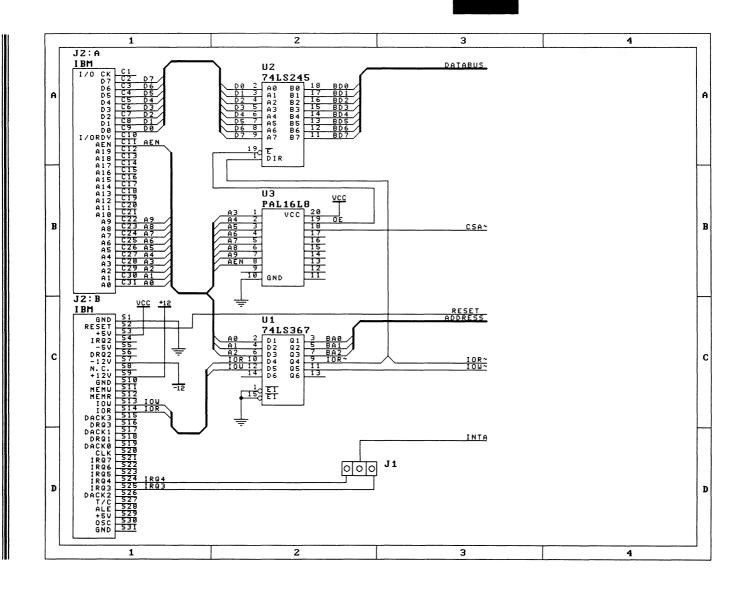

| AN1101 | 7-7  |

| AN1102 | 7-11 |

| AN1107 | 7-15 |

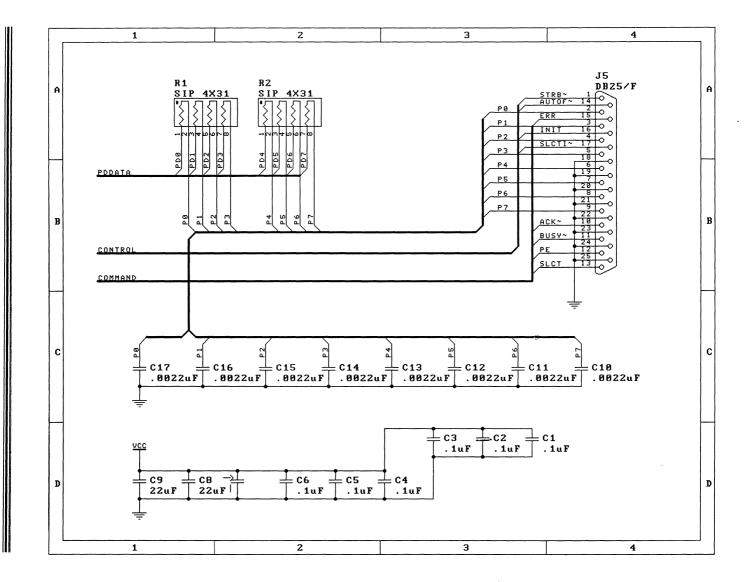

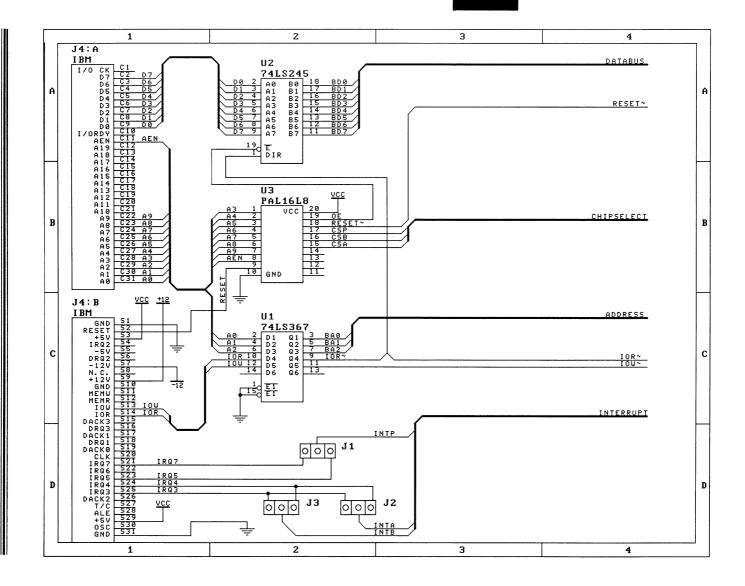

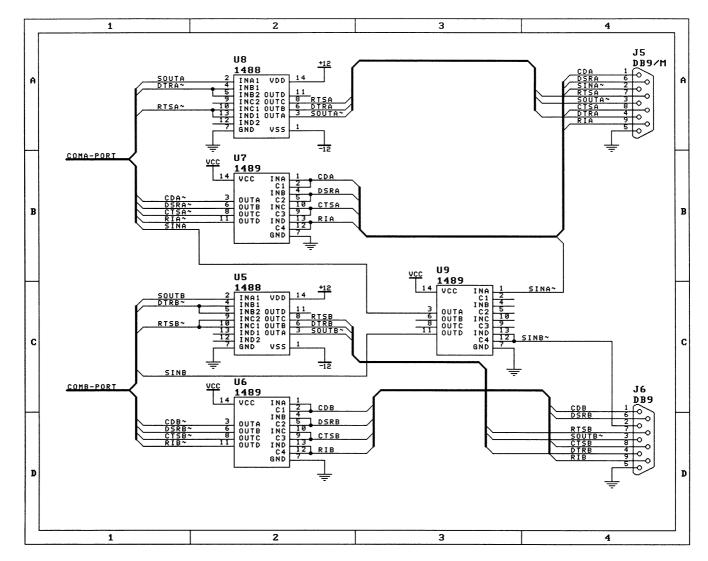

| AN1108 | 7-19 |

# SELECTION GUIDE/CROSS REFERENCE

| Part Number      | Short Description                                  | Second Source<br>Information                                      | Packaging<br>Information                 |

|------------------|----------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|

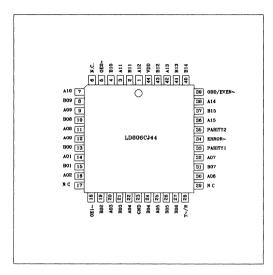

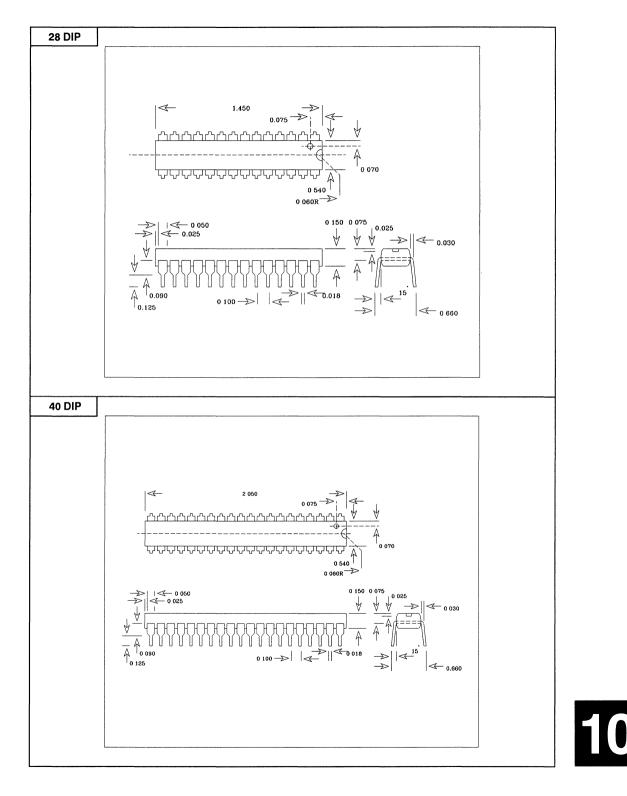

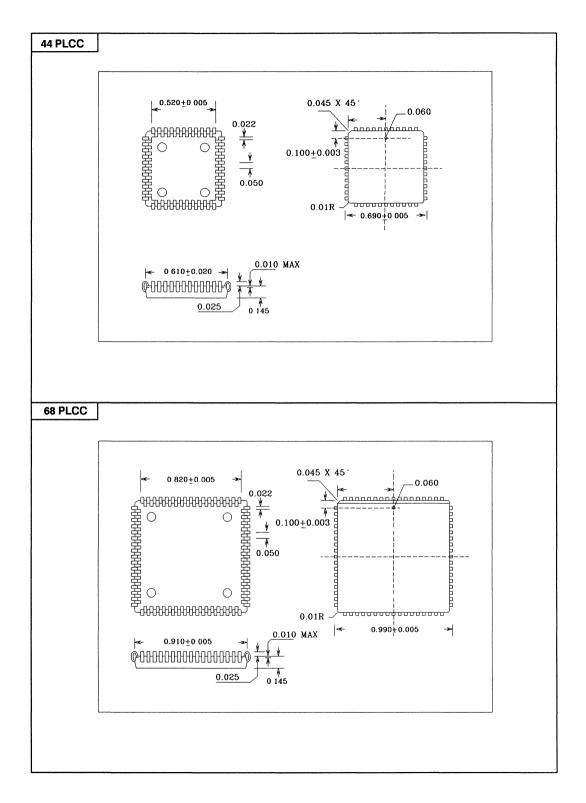

| LD805            | Bidirectional Parallel (printer) Port              | N/A                                                               | 40 pin DIP<br>44 pin PLCC                |

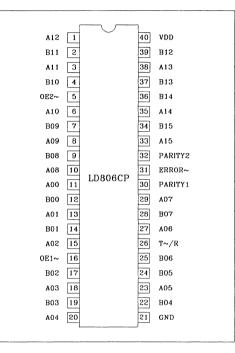

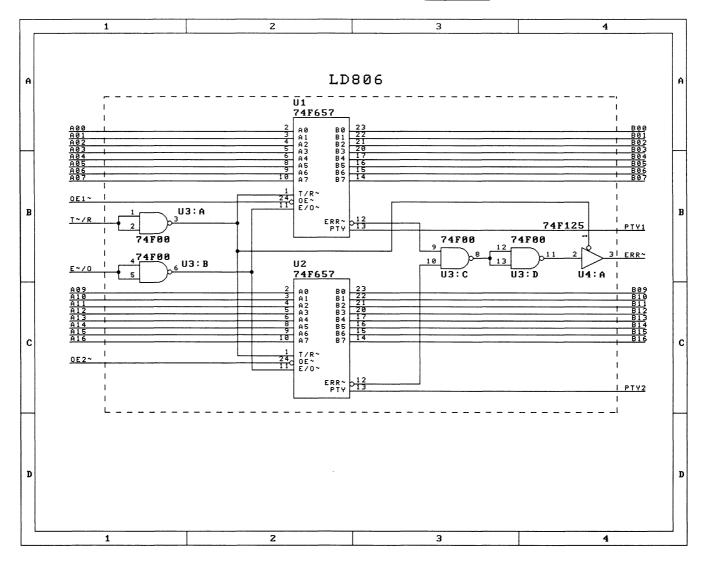

| LD806            | Dual 74LS657 Transceiver                           | N/A                                                               | 40 pin DIP<br>44 pin PLCC                |

| LD1001<br>LD1002 | EGA Chip Set                                       | N/A<br>N/A                                                        | 68 pin PLCC<br>84 pin PLCC               |

| LD1101           | Universal Asynchronous Receiver<br>and Transmitter | INS8250, INS8250B<br>NS16C450<br>VL16C450<br>XR16C450<br>WD16C450 | 40 pin DIP<br>44 pin PLCC                |

| LD1102           | Dual LD1101                                        | N/A                                                               | 40 pin DIP<br>44 pin PLCC                |

| LD1104           | Video DAC with look Up Table                       | IMS G171<br>IMS G176<br>TRIAD 171<br>Bt 476                       | 28 pin DIP<br>32 pin PLCC<br>44 pin PLCC |

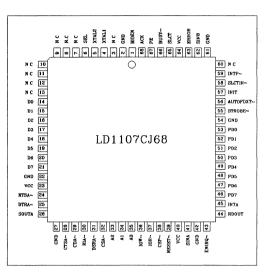

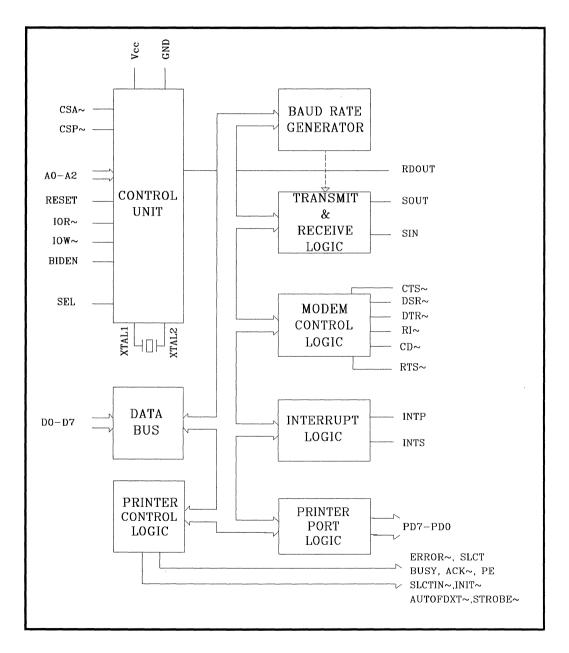

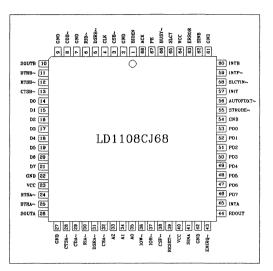

| LD1107           | Uart with Printer Port                             | VL16C451<br>WD 16C451                                             | 68 pin PLCC                              |

| LD1108           | Duart with Printer Port                            | VI16C452<br>WD 16C452                                             | 68 pin PLCC                              |

| LD1201           | Uart with FIFO                                     | NS16C550<br>VL16C550                                              | 40 pin DIP<br>44 pin PLCC                |

| LD1111           | Hard Disk Controller                               | N/A                                                               | 128 pin QFP                              |

VIII

# SILICON LOGIC HISTORY

Silicon Logic was founded in late 1982 primarily to design custom circuits. During the first four years of operation, CMOS and NMOS circuits were successfully designed and manufactured for Compaq, Microsoft, Western Digital, and Renaissance GRX Inc. In late 1987, Silicon logic was acquired by medium size US computer manufacturer. Silicon Logic operates as an independent subsidiary offering its products to the merchant IC market while having the financial stability of a major corporation.

Silicon Logic will work with independent consultants and circuit designers as well as OEMs to define common requirements so that VLSI circuit implementations can be realized in the shortest time.

Silicon Logic subcontracts its wafer fabrication to one of several US foundries depending on the volume of the specific circuit. Most of the circuits are designed using a 2 - 1½ micron, double-metal, CMOS that can be fabricated by multiple sources. Assembly is subcontracted to both on-shore and off shore sources depending on the specific situation.

Silicon Logic offers:

- \* Circuits having a combination of greater performance, lower power and more features into an existing footprint at a competitive price.

- \* Combine existing and next generation functions into new VLSI circuits.

- \* Develop new circuits rapidly by using advanced CAD tools and fast-turn wafer fabrication.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of SILICON LOGIC, INC. The information in this document is subject to change without notice. SILICON LOGIC, INC. makes no warranty (express, statutory, implied, or by description) regarding the information set forth herein or regarding the freedom of the described device from patent infringement.SILICON LOGIC, INC. makes no warranty of merchantability or fitness for any purpose. SILICON LOGIC, INC. assumes no responsibility for any errors that may appear in this document and makes no commitment to update or to keep current the information contained in this document.

C 1989 SILICON LOGIC, INC.

Х

# UART

1-2

# **ASYNCHRONOUS RECEIVER AND TRANSMITTER**

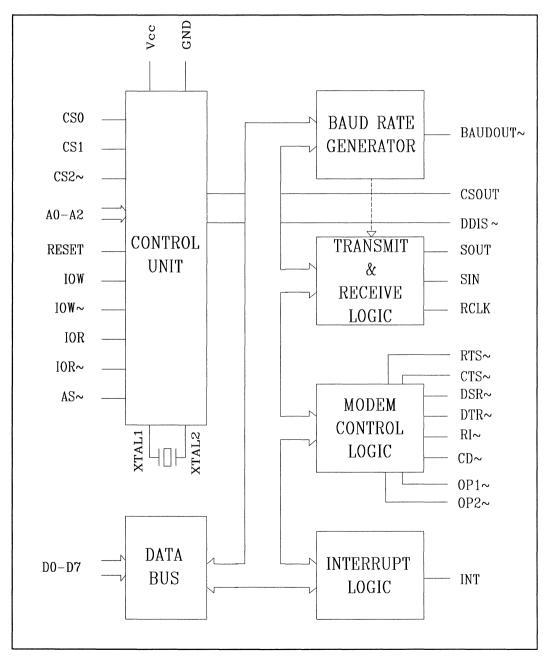

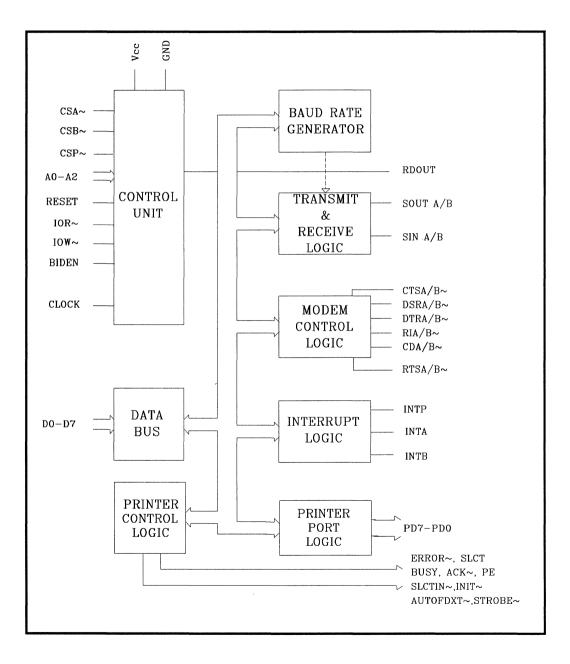

#### DESCRIPTION

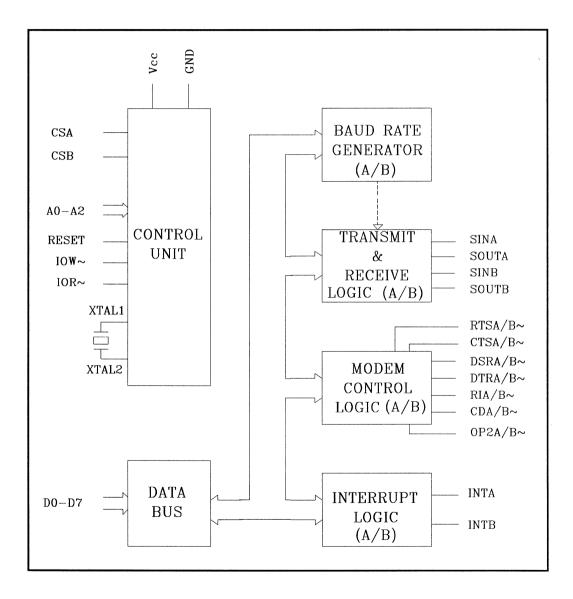

The LD1101 is a universal asynchronous receiver and transmitter with modem control signals. An internal programmable baud rate generator is provided to select transmit and receive clock rates from 50Hz to 56kHz. The LD1101 is fabricated in an advanced 2 u CMOS process to achieve low drain power and high speed requirements.

#### FEATURES

- \* Pin-to-pin and functionally compatible toINS8250, NS16C450

- \* Modem control signals (CTS~, RTS~, DSR~, DTR~, RI~, CD~)

- \* Programmable character lengths (5, 6, 7, 8)

- \* Even, odd, or no parity bit generation and detection

- \* Status report register

- \* Independent transmit and receive control

- \* TTL compatible inputs, outputs

#### **GENERAL DESCRIPTION**

The LD1101 is an improved version of the INS8250/ NS16C450 UART with higher speed operating access time. The LD1101 performs the parallel to serial/serial to parallel conversion on the data characters received from the CPU or the MODEM. The on board status register will provide the error conditions, type and status of the transfer operations being performed. Complete MODEM control capability, and a processor interrupt system that may be software tailored to the user's requirements to minimize the computing required to handle the communications link. The LD1101 can interface easily to the most popular microprocessors and communications link faults can be detected with internal loopback capability.

## APPLICATIONS

- \* RS232 receiver or transmitter

- \* Serial to parallel/parallel to serial converter

- \* Modem handshaking

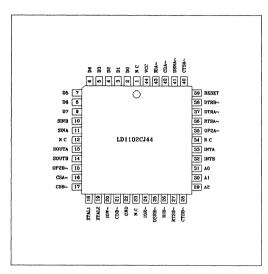

#### **ORDERING INFORMATION**

| Part number              | Package         | Operating temperature            |

|--------------------------|-----------------|----------------------------------|

| LD1101CP40<br>LD1101CJ44 | Plastic<br>PLCC | 0° C to +70° C<br>0° C to +70° C |

|                          | 00              |                                  |

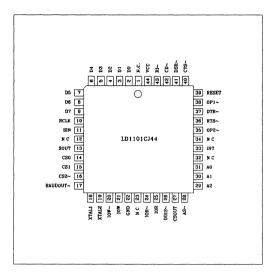

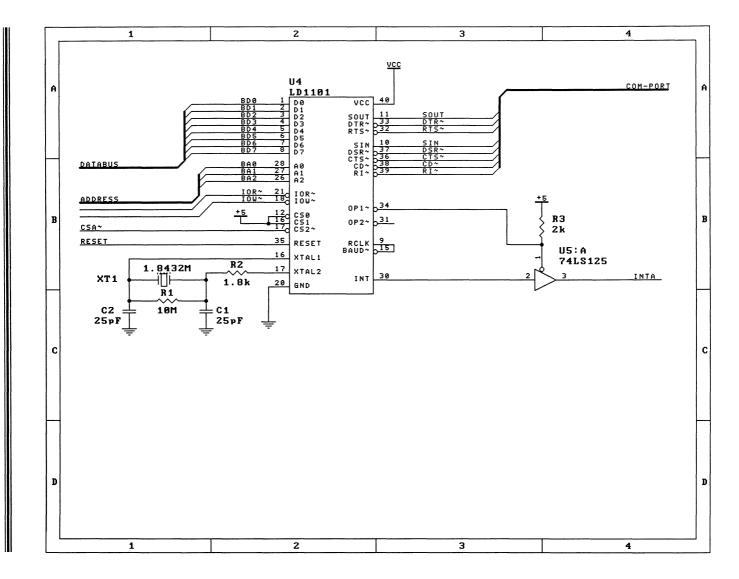

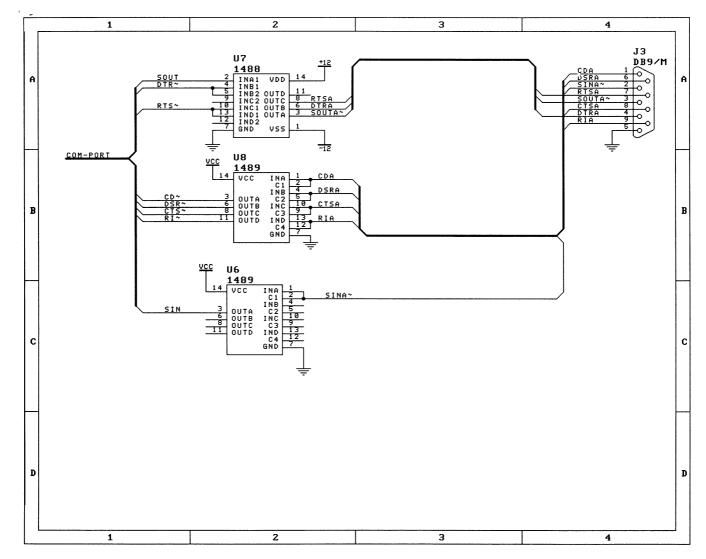

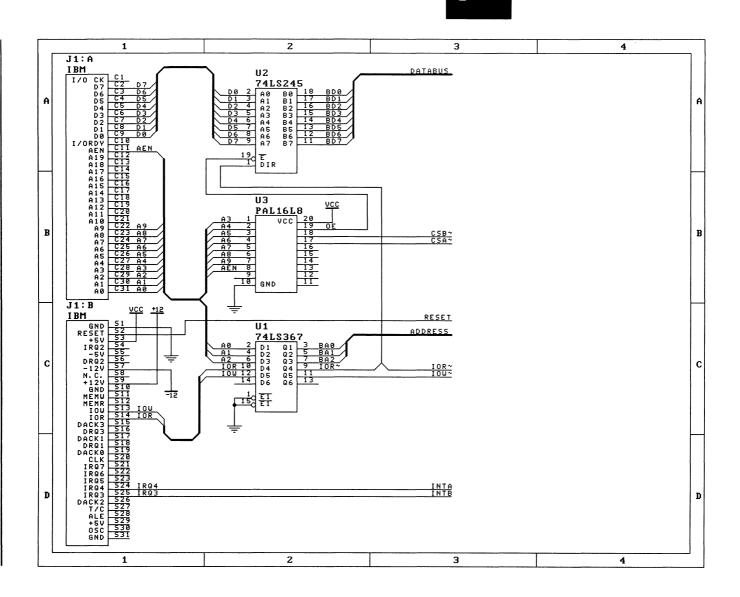

# LD1101

## **BLOCK DIAGRAM**

# SYMBOL DESCRIPTION

| Symbol   | Pin | Signal type | Pin description                                                                                                                                                                                                                                                                                                           |

|----------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7    | 1-8 | 1/0         | Bidirectional data I/O. Eight bit, three state data bus to transfer infor-<br>mation to or from the CPU. D0 is the least significant bit (Isb) of the<br>data bus and the first serial data bit to be received or transmitted.                                                                                            |

| RCLK     | 9   | I           | Receive clock input. The external clock input to the LD1101 receiver section.                                                                                                                                                                                                                                             |

| SIN      | 10  | I           | Serial data input. The serial information (data) received from MODEM<br>or RS232 to LD1101 receive circuit. A mark (high) is logic one and a<br>space (low) is logic zero. During the local loopback mode the SIN input<br>is disabled from external connection and connected to the SOUT<br>output internally.           |

| SOUT     | 11  | 0           | Serial data output. The serial data is transmitted via this pin with<br>additional start, stop and parity bits. The SOUT will be held in mark<br>(high) stateduring reset, local loopback mode or when the transmitter<br>is disabled.                                                                                    |

| CS0      | 12  | I           | Chip select 1. (active high) A high at this pin (while CS1=h and CS2=I) will enable the UART/CPU data transfer operation.                                                                                                                                                                                                 |

| CS1      | 13  | I           | Chip select 2. (active high) A high at this pin (while CS0=h and CS2=I) will enable the UART/CPU data transfer operation.                                                                                                                                                                                                 |

| CS2~     | 14  | I           | Chip select 3. (active low) A low at this pin (while $CS0=h$ and $CS1=h$ ) will enable the UART / CPU data transfer operation.                                                                                                                                                                                            |

| BAUDOUT~ | 15  | I           | Baud rate generator clock output. This output provides the 16x clock of the internal selected baud rate.                                                                                                                                                                                                                  |

| XTAL1    | 16  | 1           | Crystal input 1 or external clock input. A crystal can be connected to<br>this pin and XTAL2 pin to utilize the internal oscillator circuit. An exter-<br>nal clock can be used to clock internal circuit and baud rate generator<br>for custom transmission rates.                                                       |

| XTAL2    | 17  | 1           | Crystal input 2. See XTAL1.                                                                                                                                                                                                                                                                                               |

| IOW~     | 18  | I           | I/O write strobe. (active low) A low on this pin will transfer the contents of the CPU data bus to the addressed register.                                                                                                                                                                                                |

| IOW      | 19  | I           | I/O write strobe. (active high) Same as IOW~, but uses active high input. Note that only an active IOW~ or IOW input is required to transfer data from CPU to LD1101 during write operation (while CS0=h, CS1=h and CS2~=I). The unused pin should be tied to V <sub>CC</sub> or GND(IOW=GND or IOW~ = V <sub>CC</sub> ). |

| GND      | 20  | 0           | Signal and power ground.                                                                                                                                                                                                                                                                                                  |

| Symbol | Pin | Signal type | Pin description                                                                                                                                                                                                                                                                                                               |

|--------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOR~   | 21  | I           | I/O read strobe. (active low) A low level on this pin (while CS0=h, CS1=h and CS2~=I) will transfer the contents of the LD1101 data bus to the CPU.                                                                                                                                                                           |

| IOR    | 22  |             | I/O read strobe. (active high) Same as IOR ~, but uses active high input. Note that only an active IOR ~ or IOR input is required to transfer data from LD1101 to CPU during read operation (while CS0=h, CS1=h and CS2 ~ =I). The unused pin should be tied to V <sub>cc</sub> or GND (IOR=GND or IOR ~ = V <sub>cc</sub> ). |

| DDIS~  | 23  | 0           | Drivedisable. (active low) This pin goes low when CPU is reading data from LD1101 to disable the external transceiver or logics.                                                                                                                                                                                              |

| CSOUT  | 24  | 0           | Chip select out. A high on this pin indicates that the chip has been selected by the chip select input pins.                                                                                                                                                                                                                  |

| AS~    | 25  | 1           | Address strobe. (active low) A low on this pin will latch the state of the chip selects and addressed register.                                                                                                                                                                                                               |

| A2     | 26  | 1           | Address line 2. To select internal registers.                                                                                                                                                                                                                                                                                 |

| A1     | 27  | 1           | Address line 1. To select internal registers.                                                                                                                                                                                                                                                                                 |

| AO     | 28  | ,<br>I      | Address line 0. To select internal registers.                                                                                                                                                                                                                                                                                 |

| INT    | 30  | 0           | Interrupt output. (active high) This pin goes high (when enabled by the interrupt enable register) whenever a receiver error, receiver data available, transmitter empty or modem status condition flag is detected.                                                                                                          |

| OP2~   | 31  | 0           | General purpose output. (active low) User defined output. See bit-3 modem control register.                                                                                                                                                                                                                                   |

| RTS~   | 32  | 0           | Request to send. (active low) To indicate the transmitter has data ready to send. Writing a "1" in the modem control register (MCR bit-1) will set this pin to low state. After the reset this pin will be set to high.                                                                                                       |

| DTR~   | 33  | 0           | Data terminal ready. (active low) To indicate that LD1101 is ready to receive data. This pin can be controlled via the modem control register (MCR bit-0). Writing a "1" at the MCR bit-0 will set the DTR~ output to low. This pin will be set to high state after writing a "0" to that register or after the reset.        |

| OP1~   | 34  | o           | General purpose output. (active low) User defined output. See bit-2 of modem control register.                                                                                                                                                                                                                                |

|        |     |             |                                                                                                                                                                                                                                                                                                                               |

-

| Symbol          | Pin | Signal type | Pin description                                                                                                                                                                           |

|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET           | 35  | 1           | Master reset. (active high) A high on this pin will reset all the outputs<br>and internal registers. The transmitter output and the receiver input<br>will be disabled during reset time. |

| CTS~            | 36  | I           | Clear to send. (active low) The CTS~ signal is a MODEM control function input whose conditions can be tested by reading the MSR BIT-4. CTS~ has no effect on the transmitter output.      |

| DSR~            | 37  | I           | Data set ready. (active low) A low on this pin indicates that MODEM is ready to exchange data with UART.                                                                                  |

| CD~             | 38  | I           | Carrier detect. (active low) A low on this pin indicates that a carrier has been detected by the modem.                                                                                   |

| RI~             | 39  | I           | Ring detect indicator. (active low) A low on this pin indicates that modem has received a ringing signal from telephone line.                                                             |

| V <sub>cc</sub> | 40  | I           | Power supply input.                                                                                                                                                                       |

### **PROGRAMMING TABLE**

| DLAB | A2 | A1 | A0     | READ MODE                 | WRITE MODE                |

|------|----|----|--------|---------------------------|---------------------------|

| 0    | 0  | 0  | 0      | Receive Holding Register  | Transmit Holding Register |

| 0    | 0  | 0  | 1      | Receive Holding Register  | Interrupt Enable Register |

| x    | 0  | 1  | 0<br>0 | Interrupt Status Register | interrupt Enable negister |

| x    | 0  | 1  | 1      |                           | Line Control Register     |

| x    | 1  | 0  | 0      |                           | Modem Control Register    |

| x    | 1  | 0  | 1      | Line Status Register      | -                         |

| x    | 1  | 1  | 0      | Modem Status Register     |                           |

| x    | 1  | 1  | 1      | Scratchpad Register       | Scratchpad Register       |

| 1    | 0  | 0  | 0      | -                         | LSB of Divisor Latch      |

| 1    | 0  | 0  | 1      |                           | MSB of Divisor Latch      |

# **REGISTER FUNCTIONAL DESCRIPTION**

#### TRANSMIT AND RECEIVE HOLDING REGISTER

The serial transmitter section consists of a Transmit Hold Register and Transmit Shift Register. The status of the transmit hold register is provided in the Line Status Register. Writing to this register will transfer the contents of data bus (D7-D0) to the transmit holding register whenever the transmitter holding register or transmitter shift register is empty. The transmit holding register empty flag will be set to "1" when the transmitter is empty or data is transfered to the transmit shift register. Note that a write operation should be per-

formed when the transmit holding register empty flag is set. On the falling edge of the start bit, the receiver internal counter will start to count 7 1/2 clocks (16x clock) which is the center of the start bit. The start bit is valid if the SIN is still low at the mid-bit sample of the start bit. Verifying the start bit prevents the receiver from assembling a false data character due to a low going noise spike on the SIN input. Receiver status codes will be posted in the Line Status Register.

# LD1101 ACCESSIBLE REGISTERS

| Register | BIT-7                      | BIT-6           | BIT-5                      | BIT-4              | BIT-3                        | BIT-2                                  | BIT-1                           | BIT-0                          |

|----------|----------------------------|-----------------|----------------------------|--------------------|------------------------------|----------------------------------------|---------------------------------|--------------------------------|

| RHR      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                                  | bit-1                           | bit-0                          |

| THR      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                                  | bit-1                           | bit-0                          |

| IER      | 0                          | 0               | 0                          | 0                  | modem<br>status<br>interrupt | receive<br>line<br>status<br>interrupt | transmit<br>holding<br>register | receive<br>holding<br>register |

| ISR      | 0                          | 0               | 0                          | 0                  | 0                            | int<br>priority<br>bit-1               | int<br>priority<br>bit-0        | int<br>status                  |

| LCR      | divisor<br>latch<br>enable | set<br>break    | set<br>parity              | even<br>parity     | parity<br>enable             | stop<br>bits                           | word<br>length<br>bit-1         | word<br>length<br>bit-0        |

| MCR      | 0                          | 0               | 0                          | loop<br>back       | OP2~                         | OP1~                                   | RTS~                            | DTR~                           |

| LSR      | 0                          | trans.<br>empty | trans.<br>holding<br>empty | break<br>interrupt | framing<br>error             | parity<br>error                        | overrun<br>error                | receive<br>data<br>ready       |

| MSR      | CD~                        | RI~             | DSR~                       | CTS~               | delta<br>CD~                 | delta<br>RI~                           | delta<br>DSR~                   | delta<br>CTS~                  |

| SPR      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                                  | bit-1                           | bit-0                          |

| DLL      | bit-7                      | bit-6           | bit-5                      | bit-4              | bit-3                        | bit-2                                  | bit-1                           | bit-0                          |

| DLM      | bit-15                     | bit-14          | bit-13                     | bit-12             | bit-11                       | bit-10                                 | bit-9                           | bit-8                          |

#### **INTERRUPT ENABLE REGISTER (IER)**

The Interrupt Enable Register (IER) masks the incoming interrupts from receiver ready, transmitter empty, line status and modem status registers to the INT output pin.

#### IER BIT-0:

0 = disable the receiver ready interrupt 1 = enable receiver ready interrupt

#### IER BIT-1:

0 = disable transmitter empty interrupt 1 = enable transmitter empty interrupt

#### IER BIT-2:

0 = disable receiver line status interrupt 1 = enable receiver line status interrupt

#### IER BIT-3:

0 = disable the modem status register interrupt 1 = enable the modem status register interrupt

#### IER BIT 7-4:

All these bits are set to logic zero.

#### **INTERRUPT STATUS REGISTER (ISR)**

The LD1101 provides four level prioritized interrupt conditions to minimize software overhead during data character transfers. The Interrupt Status Register (ISR) provides the source of the interrupt in prioritized matter. During the read cycle the LD1101 provides the highest interrupt level to be serviced by CPU, no other interrupts are acknowledged until the particular interrupt is serviced. The following are the prioritized interrupt levels:

| Priority level | Source of the interrupts                      |

|----------------|-----------------------------------------------|

| 1              | ISR (Receiver Line Status<br>Register)        |

| 2              | RXRDY (Received Data Ready)                   |

| 3              | TXRDY (Transmitter Holding<br>Register Empty) |

| 4              | MSR (Modem Status Register)                   |

#### ISR BIT-0:

0 = an interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt service routine.

1 = no interrupt pending

#### ISR BIT 1-2:

Logical combination of these bits, provides the highest priority interrupt pending.

#### ISR BIT 3-7:

These bits are not used and are set to zero.

#### LINE CONTROL REGISTER (LCR)

The Line Control Register is used to specify the asynchronous data communication format. The number of the word length, stop bits, and parity can be selected by writing appropriate bits in this register.

#### LCR BIT1-0:

These two bits specify the word length to be transmitted or received. 00=5 bits word length 01=6 bits word length 10=7 bits word length 11=8 bits word length

#### LCR BIT-2:

The number of stop bits can be specified by this bit. 0=1 stop bit , when word length=5, 6, 7, 8 bits 1=1 and 1/2 stop bit , when word length=5 bits 1=2 stop bits, word length=6, 7, 8 bits

#### LCR BIT-3:

Parity or no parity can be selected via this bit. 0=no parity

1 = a parity bit is generated during the transmission, receiver also checks for received parity.

#### LCR BIT-4:

If the parity bit is enabled, LCR BIT-4 selects the even or odd parity format.

0 = odd parity is generated by calculating odd number of 1's in the transmitted data, receiver also checks for same format.

1 = an even parity bit is generated by calculating the number of even 1's in the transmitted data, receiver also checks for same format.

#### LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5=1 and LCR bit-4=0, parity bit is forced to "1" in the transmitted and received data.

LCR BIT-5=1 and LCR bit-4=1, parity bit is forced to "0" in the transmitted and received data.

#### LCR BIT-6:

Break control bit.

1 = forces the transmitter output (SOUT) to go low to

alert the communication terminal 0 = normal operating condition

#### LCR BIT-7:

The internal baud rate counter latch enable (DLAB) 0 = normal operation1 = select divisor latch register

#### MODEM CONTROL REGISTER (MCR)

This register controls the interface with the MODEM or a peripheral device (RS232).

#### MCR BIT-0:

0 =force DTR  $\sim$  output to high 1 =force DTR  $\sim$  output to low

#### MCR BIT-1:

0 =force RTS~ output to high 1 =force RTS~ output to low

#### MCR BIT-2:

0 = set OP1 output to high 1 = set OP1 output to low

#### MCR BIT -3:

$0 = set OP2 \sim output to high 1 = set OP2 \sim output to low$

#### MCR BIT -4:

0 = normal operating mode

1=enable local loop-back mode (diagnostics). The transmitter output (SOUT) is set high (mark condition), the receiver input (SIN), CTS~, DSR~, DCD~, and RI~ are disabled. Internally transmitter output is connected to the receiver input and DTR~, RTS~, OP1~, and OP2~ are connected to modem control inputs. In this mode, the receiver and transmitter interrupts are fully operational. The Modem Control Interrupts are also operational, but the interrupts sources are now the lower four bits of the Modem Control Register instead of the four Modem Control inputs. The interrupts are still controlled by the IER.

#### MCR BIT 5-7:

Not used. Are set to zero permanently.

#### LINE STATUS REGISTER (LSR)

This register provides the status of data transfer to CPU.

#### LSR BIT-0:

0=no data in receive holding register 1 = data has been received and saved in the receive holding register

#### LSR BIT-1:

0=no overrun error (normal) 1=overrun error, next character arrived before receive holding register was empty

#### LSR BIT-2:

0=no parity error (normal) 1=parity error, received data does not have correct parity information

#### LSR BIT-3:

0 = no framing error (normal) 1 = framing error received, received data did not have a valid stop bit

#### LSR BIT-4:

0=no break condition (normal) 1=receiver received a break signal (SIN was low for one character time frame)

#### LSR BIT-5:

$0\!=\!transmit$  holding register is full. LD1101 will not accept any data for transmission

$1\!=\!$  transmit holding register is empty. CPU can load the next character

#### LSR BIT-6:

0=transmitter holding and shift registers are full 1=transmitter holding and shift registers are empty

#### LSR BIT-7:

Not used. Set to zero permanently.

#### MODEM STATUS REGISTER (MSR)

This register provides the current state of the control lines from the modem or peripheral to the CPU. Four bits of this register are used to indicate the changed information. These bits are set to "1" whenever a control input from the MODEM changes state. They are set to "0" whenever the CPU reads this register.

#### MSR BIT-0:

Indicates that the CTS $\sim$  input to the LD1101 has changed state since the last time it was read.

#### MSR BIT-1:

Indicates that the DSR  $\sim$  input to the LD1101 has changed state since the last time it was read.

#### MSR BIT-2:

Indicates that the RI  $\sim$  input to the LD1101 has changed from a low to a high state.

#### MSR BIT-3:

Indicates that the CD $\sim$  input to the LD1101 has changed state since the last time it was read.

#### MSR BIT-4:

This bit is equivalent to RTS in the MCR. It is the compliment of the CTS  $\sim$  input.

#### MSR BIT-5:

This bit is equivalent to DTR  $\,$  in the MCR. It is the compliment of the DSR  $\sim$  input.

#### MSR BIT-6:

This bit is equivalent to OP1 in the MCR. It is the compliment of the RI  $\sim$  input.

#### MSR BIT-7:

This bit is equivalent to OP2 in the MCR. It is the compliment to the CD $\sim$  input.

#### SCRATCHPAD REGISTER (SR)

LD1101 provides a temporary data register to store 8 bits of information for variable use.

#### BAUD RATE GENERATOR PROGRAMMING TABLE

| BAUD RATE | 16 x CLOCK DIVISOR | % ERROR |

|-----------|--------------------|---------|

| 50        | 2304               |         |

| 75        | 1536               |         |

| 110       | 1047               | 0.026   |

| 150       | 768                |         |

| 300       | 384                |         |

| 600       | 192                |         |

| 1200      | 96                 |         |

| 3600      | 32                 |         |

| 4800      | 24                 |         |

| 7200      | 16                 |         |

| 9600      | 12                 |         |

| 19.2K     | 6                  |         |

| 38.4K     | 3                  |         |

| 56K       | 2                  | 2.86    |

|           |                    | 1       |

#### LD1101 EXTERNAL RESET CONDITION TABLE

| RESET STATE                                                                                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R BITS 0-7=0<br>R BIT-0=1, ISR BITS 1-7=0<br>CR BITS 0-7=0<br>FR BITS 0-7=0<br>FR BITS 0-4=0, LSR BITS 5-<br>I LSR, BIT 7=0<br>SR BITS 0-3=0, MSR BITS 4-<br>input signals |

|                                                                                                                                                                            |

| SIGNALS | RESET STATE  |

|---------|--------------|

| SOUT    | High         |

| OP1~    | High         |

| OP2~    | High         |

| RTS~    | High         |

| DTR~    | High         |

| INT     | BITS 0-3=low |

|         |              |

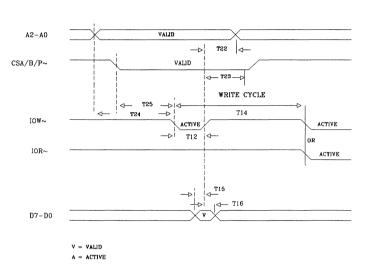

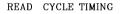

# AC ELECTRICAL CHARACTERISTICS

$\rm T_{A}{=}\,25^{o}$  C,  $\rm ~V_{CC}{=}\,5.0$  V  $\pm$  5% unless otherwise specified.

| Symbol               | Parameter                                  | Limits      |  | Units | Conditions |                |

|----------------------|--------------------------------------------|-------------|--|-------|------------|----------------|

|                      | · · · · · · · · · · · · · · · · · · ·      | min typ max |  |       |            |                |

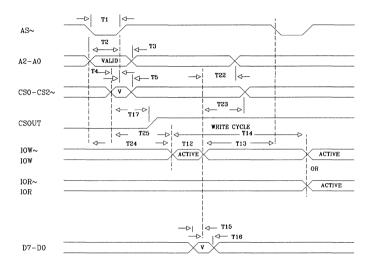

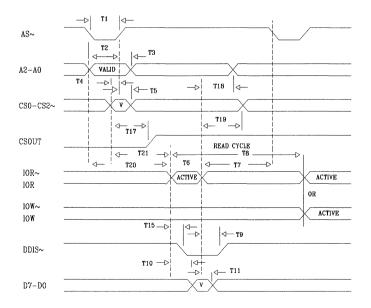

| -                    | Address stroks width                       |             |  |       |            |                |

| T,<br>T <sub>2</sub> | Address strobe width<br>Address setup time | 30          |  | ns    |            |                |

| $T^2$                | Address hold time                          | 30<br>5     |  |       | ns         |                |

| T <sub>3</sub><br>T  | Chip select setup time                     | 25          |  |       | ns<br>ns   |                |

| T₄<br>T₅             | Chip select hold time                      | 0           |  |       | ns         |                |

| T <sub>6</sub>       | IOR~/IOR strobe width                      | 75          |  |       | ns         |                |

| $T_{7}^{6}$          | Read cycle delay                           | 50          |  |       | ns         |                |

| $T_{8}^{7}$          | Read cycle = $T_{20} + T_6 + T_7$          | 135         |  |       | ns         |                |

| T <sub>g</sub>       | $IOR \sim /IOR$ to drive                   | 100         |  | 35    | ns         | 100 pF load    |

| .9                   | disable delay                              |             |  | 00    |            | loo pi loud    |

| T <sub>10</sub>      | Delay from IOR~/IOR                        |             |  | 75    | ns         | 100 pF load    |

| 10                   | to data                                    |             |  |       |            |                |

| T <sub>11</sub>      | IOR~/IOR to floating                       | 0           |  | 50    | ns         | 100 pF load    |

|                      | data delay                                 | -           |  |       |            |                |

| T <sub>12</sub>      | IOW~/IOW strobe width                      | 50          |  |       | ns         |                |

| T <sub>13</sub>      | Write cycle delay                          | 55          |  |       | ns         |                |

| T <sub>14</sub>      | Write cycle = $T_1 + T_{12} + T_{13}$      | 135         |  |       | ns         |                |

| T <sub>15</sub>      | Data setup time                            | 10          |  |       | ns         |                |

| T <sub>16</sub>      | Data hold time                             | 25          |  |       | ns         |                |

| T <sub>17</sub>      | Chip select output delay                   |             |  | 50    | ns         | 100 pF load    |

|                      | from select                                |             |  |       |            |                |

| Т <sub>18</sub>      | Address hold time from<br>IOR~/IOR         | 0           |  |       | ns         | Note: 1        |

| Т <sub>19</sub>      | Chip select hold time from<br>IOR~/IOR     | 0           |  |       | ns         | Note: 1        |

| T <sub>20</sub>      | IOR~/IOR delay from<br>address             | 10          |  |       | ns         | Note: 1        |

| T <sub>21</sub>      | IOR~/IOR delay from<br>chip select         | 10          |  |       | ns         | Note: 1        |

| T <sub>22</sub>      | Address hold time from<br>IOW~/IOW         | 5           |  |       | ns         | Note: 1        |

| Т <sub>23</sub>      | Chip select hold time<br>from IOW~/IOW     | 5           |  |       | ns         | Note: 1        |

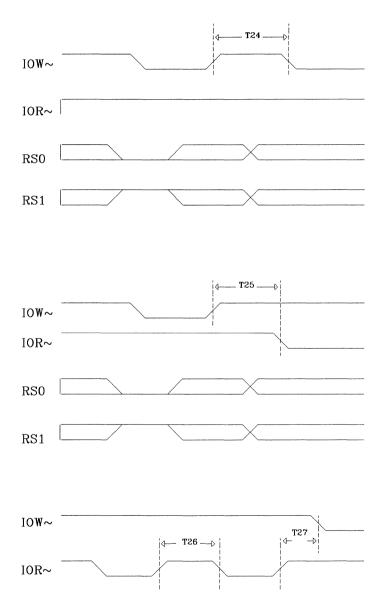

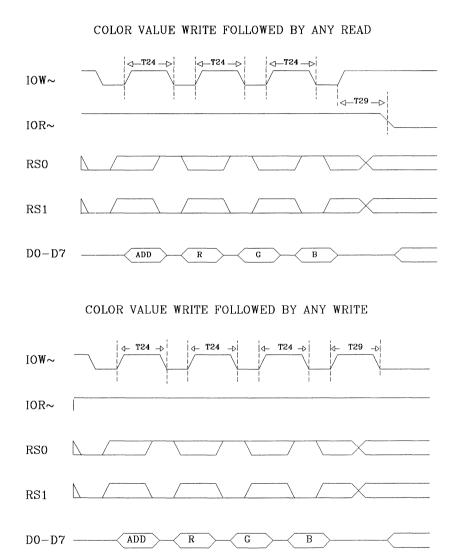

| T <sub>24</sub>      | IOW~/IOW delay from<br>address             | 25          |  |       | ns         | Note: 1        |

| Т <sub>25</sub>      | IOW~/IOW delay from<br>select              | 10          |  |       | ns         | Note: 1        |

| T <sub>26</sub>      | Reset pulse width                          | 5           |  |       | ns         |                |

| T <sub>27</sub>      | Clock high pulse duration                  | 140         |  |       |            |                |

| Т <sub>28</sub>      | Clock low pulse duration                   | 140         |  |       |            | External clock |

|                      |                                            |             |  |       |            |                |

|                      |                                            |             |  |       |            |                |

# AC ELECTRICAL CHARACTERISTICS

$T_{A}{=}25^{\circ}\,C,~V_{CC}{=}5.0$  V  $\pm$  5% unless otherwise specified.

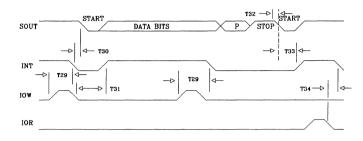

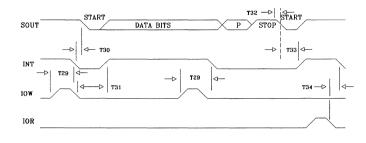

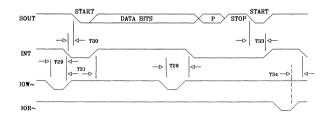

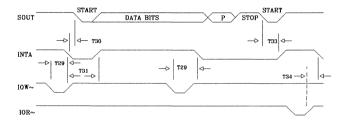

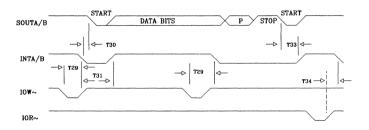

| TRANS                | MITTER                                                              |            |      |                           |          |                                                |

|----------------------|---------------------------------------------------------------------|------------|------|---------------------------|----------|------------------------------------------------|

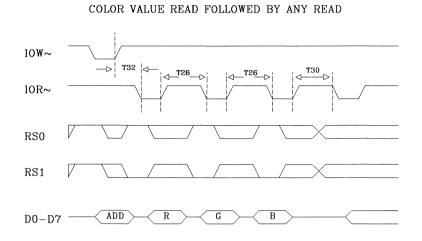

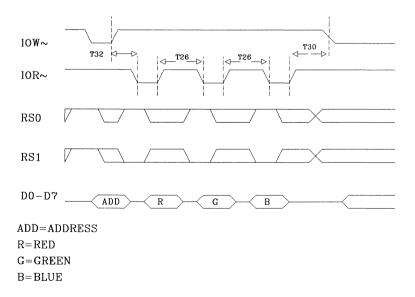

| T <sub>29</sub>      | Delay from rising edge of IOW~/IOW to reset                         |            |      | 75                        | ns       | 100 pF load                                    |

| T <sub>30</sub>      | interrupt<br>Delay from initial INT                                 | 24         |      | 40                        | *        |                                                |

| Т <sub>31</sub>      | reset to transmit start<br>Delay from initial Write<br>to interrupt | 16         |      | 24                        | *        |                                                |

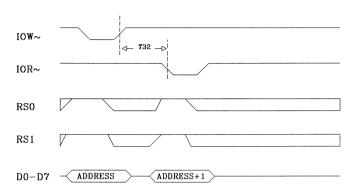

| T <sub>32</sub>      | Delay from stop to<br>next start                                    |            |      | 100                       | ns       |                                                |

| Т <sub>33</sub>      | Delay from start bit low to<br>interrupt high                       |            |      | 8                         | *        |                                                |

| T <sub>34</sub>      | Delay from IOR~/IOR<br>to reset interrupt                           |            |      | 75                        | ns       | 100 pF load                                    |

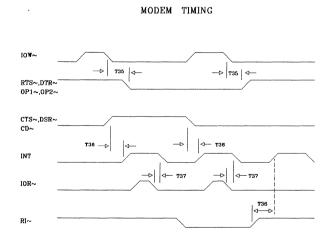

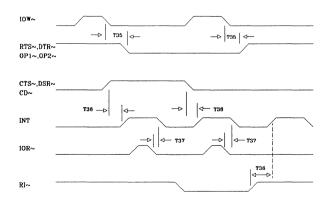

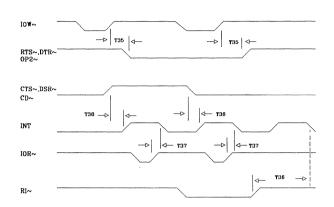

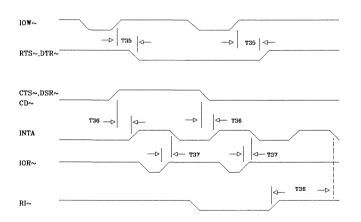

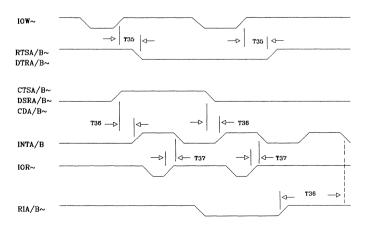

| MODEN                | CONTROL                                                             |            | .L., |                           | L        | L                                              |

| Т <sub>35</sub>      | Delay from IOW~/IOW to output                                       |            |      | 50                        | ns       | 100 pF load                                    |

| T <sub>36</sub>      | Delay to set interrupt<br>from MODEM input                          |            |      | 70                        | ns       | 100 pF load                                    |

| Т <sub>37</sub>      | Delay to reset interrupt<br>from IOR~/IOR                           |            |      | 70                        | ns       | 100 pF load                                    |

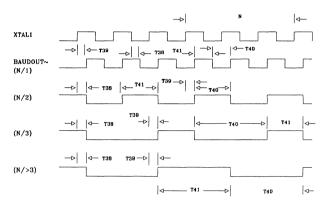

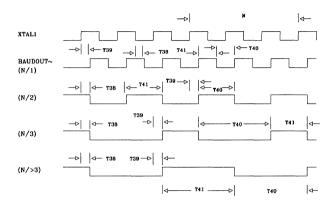

| BAUD R               | ATE GENERATOR                                                       | 1          |      |                           | I        | I                                              |

| N<br>T <sub>38</sub> | Baud rate devisor<br>Baud out negative<br>edge delay                | 1          |      | 2 <sup>16</sup> -1<br>100 | ns       | 100 pF load                                    |

| Т <sub>з9</sub>      | Baud out positive<br>edge delay                                     |            |      | 100                       | ns       | 100 pF load                                    |

| T₄₀<br>T₄1           | Baud out down time<br>Baud out up time                              | 425<br>250 |      |                           | ns<br>ns | 100 pF load , Note: 2<br>100 pF load , Note: 2 |

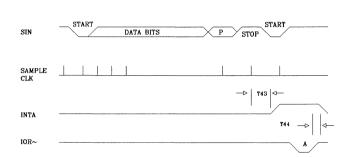

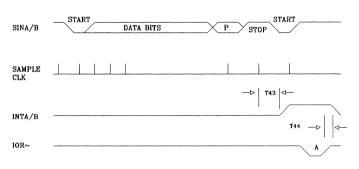

| RECEIV               | ER                                                                  |            |      |                           |          | • · · · · · · · · · · · · · · · · · · ·        |

| T <sub>42</sub>      | Delay from RCLK to sample time                                      |            |      | 500                       | ns       |                                                |

| T <sub>43</sub>      | Delay from stop to set<br>interrupt                                 |            |      | 1 <sub>Rcik</sub>         | ns       | 100 pF load                                    |

| T <sub>44</sub>      | Delay from IOR~/IOR to<br>reset interrupt                           |            |      | 200                       | ns       | 100 pF load                                    |

Note 1: Applicable only when AS is tied low

Note 2: Fx=3.1 MHz clock

\* Baudout~ cycle

# **ABSOLUTE MAXIMUM RATINGS**

Operating supply range Voltage at any pin Operating temperature Storage temperature Package dissipation  $\begin{array}{c} 5 \mbox{ Volts } \pm 5\% \\ \mbox{GND-0.3 V to } V_{\rm CC} + 0.3 V \\ 0^{\circ} \mbox{C to } + 70^{\circ} \mbox{C} \\ -40^{\circ} \mbox{C to } + 150^{\circ} \mbox{C} \\ 500 \mbox{ mW} \end{array}$

## **DC ELECTRICAL CHARACTERISTICS**

$T_{\rm A}\!=\!25^{\circ}$  C,  $\,V_{\rm CC}\!=\!5.0$  V  $\pm$  5% unless otherwise specified.

| Symbol                                                 | Parameter                                                                                                                                                                                        |                                   | Limits |                                                                        | Units                              | Conditions                                                       |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------|------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------|

|                                                        |                                                                                                                                                                                                  | min                               | typ    | max                                                                    |                                    |                                                                  |

| VILOK<br>VIHCK<br>VIL<br>VOL<br>VOH<br>I <sub>CC</sub> | Clock input low level<br>Clock input high level<br>Input low level<br>Input high level<br>Output low level<br>Output high level<br>Avg power supply<br>current<br>Input leakage<br>Clock leakage | -0.5<br>3.0<br>-0.5<br>2.2<br>2.4 |        | 0.6<br>$V_{cc}$<br>0.8<br>$V_{cc}$<br>0.4<br>6<br>$\pm 10$<br>$\pm 10$ | V<br>V<br>V<br>V<br>MA<br>uA<br>uA | I <sub>oL</sub> = 6 mA on all outputs<br>I <sub>oH</sub> = -6 mA |

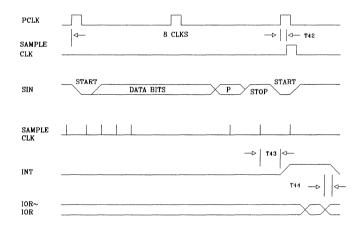

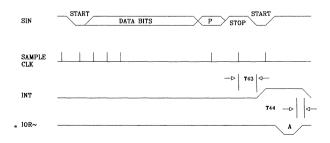

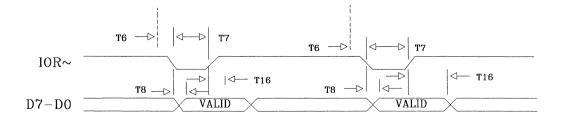

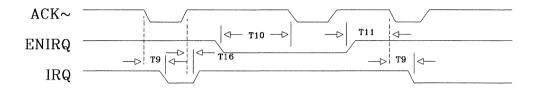

# TIMING DIAGRAM

#### TRANSMITTER TIMING

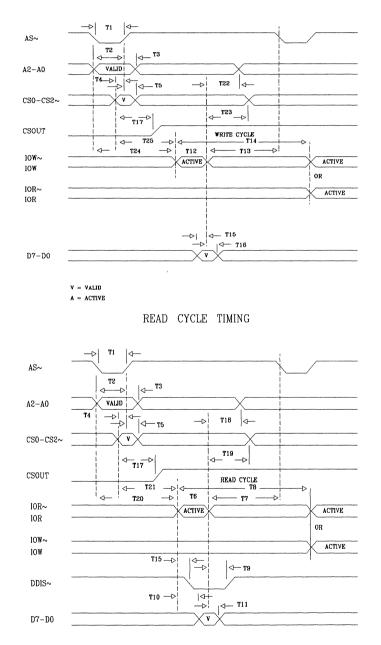

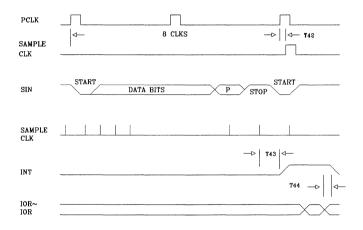

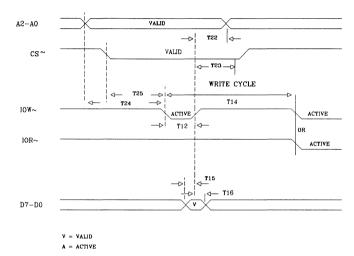

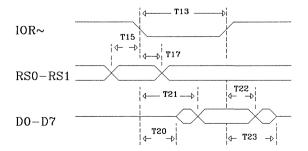

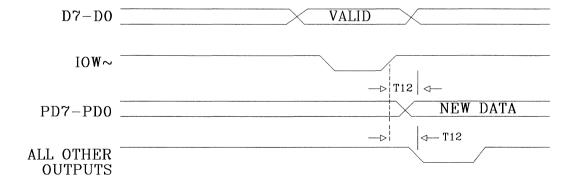

# **TIMING DIAGRAM**

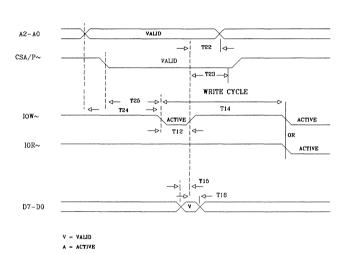

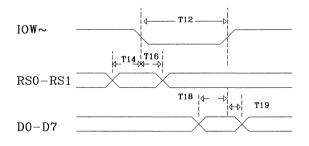

WRITE CYCLE TIMING

# LD1101

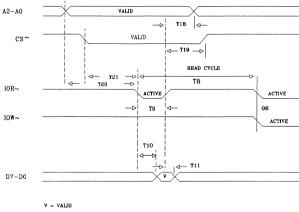

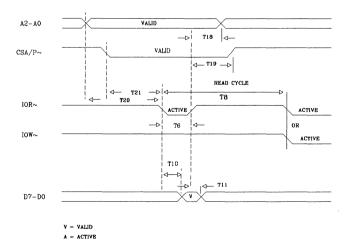

### **TIMING DIAGRAM**

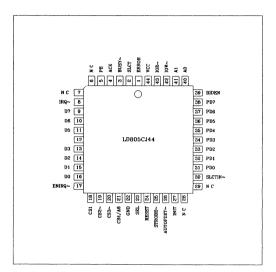

#### 44-PIN PLCC INPUT

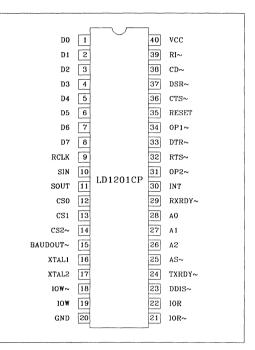

# UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER WITH FIFOs

#### DESCRIPTION

The LD1201 is a universal asynchronous receiver and transmitter with FIFO and modem control signals. An internal programmable baud rate generator is provided to select transmit and receive clock rates from 50Hz to 256KHz. The LD1201 is fabricated in an advanced 2 u CMOS process to achieve low drain power and high speed requirements.

#### FEATURES

- \*Pin to pin and functional compatible to NS16C550

- \*Modem control signals (CTS~, RTS~, DSR~, DTR~, RI~, CD~)

- \*16 byte programmable FIFO for transmit and receive section

- \*Programmable character lengths (5, 6, 7, 8)

- \*Even, odd, or no parity bit generation and detection

- \*Status report register

- \*Independent transmit and receive control

- \*TTL compatible inputs, outputs

- \*Software compatible with INS8250, NS16C450, LD1101

#### APPLICATIONS

- \* RS232 receiver or transmitter

- \* Serial to parallel/parallel to serial converter

- \* Modem handshaking

- \* IBM PS/2 serial port

#### **ORDERING INFORMATION**

| Part number | Package | Operating temperature |

|-------------|---------|-----------------------|

| LD1201CP40  | Plastic | 0° C to + 70° C       |

| LD1201CJ44  | PLCC    | 0° C to + 70° C       |

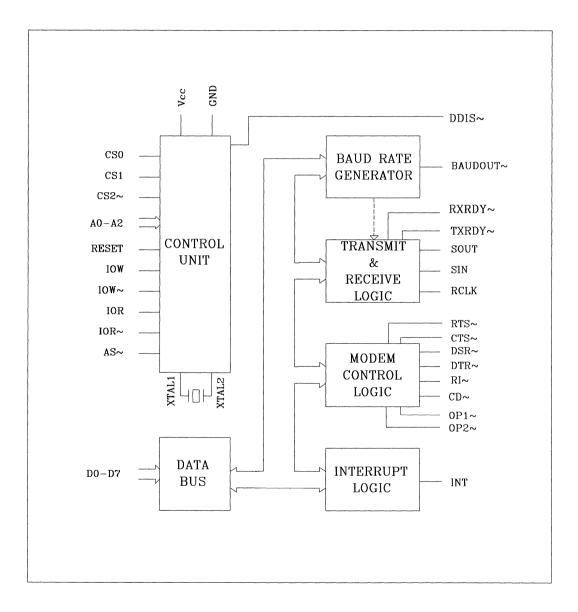

#### **GENERAL DESCRIPTION**

The LD1201 is an improved version of the NS16C550 UART with higher operating speed and lower access time. The LD1201 performs the parallel to serial/serial to parallel conversion on the data characters received from the CPU or the MODEM. The on board status registers will provide the error conditions, type and status of the transfer operations being performed. Included is complete MODEM control capability, and a processor interrupt system that may be software tailored to the user's requirements to minimize the computing required to handle the communications link. On board 16 byte (plus 3 bits of error data per byte in the RX-FIFO) FIFO and two DMA signaling functions are designed to minimize system overhead and maximize system efficiency. The LD1201 provides internal loop-back capability for on board diagnostic testing.

# **BLOCK DIAGRAM**

| Symbol   | Pin | Signal type | Pin description                                                                                                                                                                                                                                                                                                    |

|----------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7    | 1-8 | 1/0         | Bidirectional data I/O. Eight bit, three state data bus to transfer information to or from the CPU. D0 is the least significant bit (Isb) of the data bus and the first serial data bit to be received or transmitted.                                                                                             |

| RCLK     | 9   | I           | Receive clock input. The external clock input to the LD1201 receiver section.                                                                                                                                                                                                                                      |

| SIN      | 10  | I           | Serial data input. The serial information (data) received from MODEM<br>or RS232 to LD1201 receive circuit. A mark (high) is logic one and a<br>space (low) is logic zero. During the local loopback mode the SIN<br>input is disabled from external connection and connected to the SOUT<br>output internally.    |

| SOUT     | 11  | 0           | Serial data output. The serial data is transmitted via this pin with additional start, stop and parity bits. The SOUT will be held in mark (high) state during reset, local loopback mode or when the transmitter is disabled.                                                                                     |

| CS0      | 12  | I           | Chip select 1. (active high) A high at this pin (while $CS1 = h$ and $CS2 = I$ ) will enable the UART / CPU data transfer operation.                                                                                                                                                                               |

| CS1      | 13  | I           | Chip select 2. (active high) A high at this pin (while CS0=h and CS2=I) will enable the UART / CPU data transfer operation.                                                                                                                                                                                        |

| CS2~     | 14  | I           | Chip select 3. (active low) A low at this pin (while $CS0 = h$ and $CS1 = h$ ) will enable the UART / CPU data transfer operation.                                                                                                                                                                                 |

| BAUDOUT~ | 15  | I           | Baud rate generator clock output. This output provides the 16x clock of the internal selected baud rate.                                                                                                                                                                                                           |

| XTAL1    | 16  | I           | Crystal input 1 or external clock input. A crystal can be connected to<br>this pin and XTAL2 pin to utilize the internal oscillator circuit. An<br>external clock can be used to clock internal circuit and baud rate<br>generator for custom transmission rates.                                                  |

| XTAL2    | 17  | I           | Crystal input 2. See XTAL1.                                                                                                                                                                                                                                                                                        |

| IOW~     | 18  | I           | I/O write strobe. (active low) A low on this pin will transfer the contents of the CPU data bus to the addressed register.                                                                                                                                                                                         |

| IOW      | 19  | I           | I/O write strobe. (active high) Same as IOW~, but uses active high input. Note that only an active IOW~ or IOW input is required to transfer data from CPU to LD1201 during write operation (while CS0=h, CS1=h and CS2~=I). The unused pin should be tied to $V_{\rm CC}$ or GND(IOW=GND or IOW~= $V_{\rm CC}$ ). |

| Symbol | Pin | Signal type | Pin description                                                                                                                                                                                                                                                                                          |

|--------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND    | 20  | 0           | Signal and power ground.                                                                                                                                                                                                                                                                                 |

| IOR~   | 21  | · 1         | I/O read strobe. (active low) A low level on this pin (while CS0=h, CS1=h and CS2~=I) will transfer the contents of the LD1201 data bus to the CPU.                                                                                                                                                      |

| IOR    | 22  |             | I/O read strobe. (active high) Same as IOR~, but uses active high input. Note that only an active IOR~ or IOR input is required to transfer data from LD1201 to CPU during read operation (while CS0=h, CS1=h and CS2~=I). The unused pin should be tied to $V_{cc}$ or GND(IOR=GND or IOR~= $V_{cc}$ ). |

| DDIS~  | 23  | ο           | Drive disable. (active low) This pin goes low when the CPU is reading data from the LD1201 to disable the external transceiver or logics.                                                                                                                                                                |

| TXRDY~ | 24  | ο           | Transmit ready. (active low) This pin goes low when the transmit FIFO of the LD1201 is full. It can be used as a single or multi-transfer DMA.                                                                                                                                                           |

| AS~    | 25  | I           | Address strobe. (active low) A low on this pin will latch the state of the chip selects and addressed register (A2-A0). This input is used when signals are not stable for the duration of a read or write operation. If not required, tie the AS $\sim$ input permanently low.                          |

| A2     | 26  | 1           | Address line 2. To select internal registers.                                                                                                                                                                                                                                                            |

| A1     | 27  | I           | Address line 1. To select internal registers.                                                                                                                                                                                                                                                            |

| AO     | 28  | 1           | Address line 0. To select internal registers.                                                                                                                                                                                                                                                            |

| RXRDY~ | 29  | 0           | Receive ready. (active low) This pin goes low when the receive FIFO is full. It can be used as a single or multi-transfer DMA.                                                                                                                                                                           |

| INT    | 30  | 0           | Interrupt output. (active high) This pin goes high (when enabled by the interrupt enable register) whenever a receiver error, receiver data available, transmitter empty, or modem status condition flag is detected.                                                                                    |

| OP2~   | 31  | о           | General purpose output. (active low) User defined output. See bit-3 modem control register.                                                                                                                                                                                                              |

| RTS~   | 32  | ο           | Request to send. (active low) To indicate that the transmitter has data<br>ready to send. Writing a "1" in the modem control register (MCR bit-<br>1) will set this pin to a low state. After the reset this pin will be set to<br>high.                                                                 |

| Symbol          | Pin | Signal type | Pin description                                                                                                                                                                                                                                                                                                              |

|-----------------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTR~            | 33  | 0           | Data terminal ready. (active low) To indicate that LD1201 is ready to receive data. This pin can be controlled via the modem control register (MCR bit-0). Writing a "1" at the MCR bit-0 will set the DTR $\sim$ output to low. This pin will be set to high state after writing a "0" to that register or after the reset. |

| OP1~            | 34  | 0           | General purpose output. (active low) User defined output. See bit-2 of modem control register.                                                                                                                                                                                                                               |

| RESET           | 35  | I           | Master reset. (active high) A high on this pin will reset all the outputs<br>and internal registers. The transmitter output and the receiver input<br>will be disabled during reset time.                                                                                                                                    |

| CTS~            | 36  | I           | Clear to send. (active low) The CTS $\sim$ signal is a MODEM control function input whose conditions can be tested by reading the MSR BIT-4. CTS $\sim$ has no effect on the transmitter output.                                                                                                                             |

| DSR~            | 37  | I           | Data set ready. (active low) A low on this pin indicates the MODEM is ready to exchange data with UART.                                                                                                                                                                                                                      |

| CD~             | 38  | I           | Carrier detect. (active low) A low on this pin indicates the carrier has been detected by the modem.                                                                                                                                                                                                                         |

| RI~             | 39  | I           | Ring detect indicator. (active low) A low on this pin indicates the modem has received a ringing signal from telephone line.                                                                                                                                                                                                 |

| V <sub>cc</sub> | 40  | 1           | Power supply input.                                                                                                                                                                                                                                                                                                          |

# **PROGRAMMING TABLE**

| DLAB | A2 | A1 | A0 | READ MODE                 | WRITE MODE                |

|------|----|----|----|---------------------------|---------------------------|

| 0    | 0  | 0  | 0  | Receive Holding Register  | Transmit Holding Register |

| 0    | Ō  | Ō  | 1  |                           | Interrupt Enable Register |

| x    | 0  | 1  | 0  | Interrupt Status Register | FIFO Control Register     |

| x    | 0  | 1  | 1  |                           | Line Control Register     |

| x    | 1  | 0  | 0  |                           | Modem Control Register    |

| x    | 1  | 0  | 1  | Line Status Register      |                           |

| x    | 1  | 1  | 0  | Modem Status Register     |                           |

| x    | 1  | 1  | 1  | Scratchpad Register       | Scratchpad Register       |

| 1    | 0  | 0  | 0  |                           | LSB of Divisor Latch      |

| 1    | 0  | 0  | 1  |                           | MSB of Divisor Latch      |

#### **REGISTER FUNCTIONAL DESCRIPTIONS**

#### TRANSMIT AND RECEIVE HOLDING REGISTER

The serial transmitter section consists of a Transmit Hold Register (THR) and Transmit Shift Register (TSR). The status of the transmit hold register is provided in the Line Status Register (LSR). Writing to this register will transfer the contents of data bus (D7-D0) to the Transmit holding register whenever the transmitter holding register or transmitter shift register is empty. The transmit holding register empty flag will be set to "1" when the transmitter is empty or data is transfered to the transmit shift register. Note that a write operation should be performed when the transmit holding register empty flag is set.

On the falling edge of the start bit, the receiver internal counter will start to count 7 1/2 clocks (16x clock) which is the center of the start bit. The start bit is valid if the SIN is still low at the mid-bit sample of the start bit. Verifying the start bit prevents the receiver from assembling a false data character due to a low going noise spike on the SIN input. Receiver status codes will be posted in the Line Status Register.

#### FIFO INTERRUPT MODE OPERATION

When the receive FIFO (FCR BIT-0=1) and receive interrupts (IER BIT-0=1) are enabled, receiver interrupt will occur as follows:

A) The receive data available interrupts will be issued to the CPU when the FIFO has reached its programmed trigger level; it will be cleared as soon as the FIFO drops below its programmed trigger level.

B) The ISR receive data available indication also occurs when the FIFO trigger level is reached, and like the interrupt it is cleared when the FIFO drops below the trigger level.

C) The data ready bit (LSR BIT-0) is set as soon as a character is transferred from the shift register to the receiver FIFO. It is reset when the FIFO is empty.

#### FIFO POLLED MODE OPERATION

When FCR BIT-0=1; resetting IER BIT 3-0 to zero puts the LD1201 in the FIFO polled mode of operation. Since the receiver and transmitter are controlled separately either one or both can be in the polled mode operation by utilizing the Line Status Register.

A) LSR BIT-0 will be set as long as there is one byte in the receive FIFO.

B) LSR BIT4-1 will specify which error(s) has occurred.

C) LSR BIT-5 will indicate when the transmit FIFO is

empty.

D) LSR BIT-6 will indicate when both transmit FIFO and transmit shift register are empty.

E) LSR BIT-7 will indicate when there are any errors in the receive FIFO.

#### **PROGRAMMABLE BAUD RATE GENERATOR**

The LD1201 contains a programmable Baud Rate Generator that is capable of taking any clock input from DC-16 MHz and dividing it by any divisor from 2 to  $2^{16}$ -1. The output frequency of the Baudout~ is equal to 16X of transmission baud rate (Baudout~ =16 x Baud Rate). Customize Baud Rates can be achieved by selecting proper divisor values for MSB and LSB of baud rate generator.

divisor value (decimal) =  $\frac{\text{input frequency}}{\text{baud rate x 16}}$

| EXAMPLE:     | <u>1.8432 x 10</u><br>1200 (baud) | (,               |

|--------------|-----------------------------------|------------------|

| 96 decimal = | 0060 HEX                          | Divisor MSB = 00 |

Divisor LSR = 60

#### **INTERRUPT ENABLE REGISTER (IER)**

The Interrupt Enable Register (IER) masks the incoming interrupts from receiver ready, transmitter empty, line status and modem status registers to the INT output pin.

#### IER BIT-0:

0 = disable the receiver ready interrupt. 1 = enable the receiver ready interrupt.

#### IER BIT-1:

0 = disable the transmitter empty interrupt. 1 = enable the transmitter empty interrupt.

#### IER BIT-2:

0 = disable the receiver line status interrupt. 1 = enable the receiver line status interrupt.

#### IER BIT-3:

0 = disable the modem status register interrupt. 1 = enable the modem status register interrupt. IER BIT 7-4: All these bits are set to logic zero.

# **INTERRUPT STATUS REGISTER (ISR)**

The LD1201 provides four level prioritized interrupt conditions to minimize software overhead during data character transfers. The Interrupt Status Register (ISR) provides the source of the interrupt in prioritized matter. During the read cycle the LD1201 provides the highest interrupt level to be serviced by CPU. No other interrupts are acknowledged until the particular interrupt is serviced. The following are the prioritized interrupt levels:

| Priority level | Source of the interrupts                                                      |

|----------------|-------------------------------------------------------------------------------|

| 1              | ISR (Receiver Line Status Regis-<br>ter)                                      |

| 2              | RXRDY (Received Data Ready)                                                   |

| 3              | RXRDY (Received Data Ready)<br>TXRDY(Transmitter Holding Reg-<br>ister Empty) |

| 4              | MSR (Modem Status Register)                                                   |

#### ISR BIT-0:

0 = an interrupt is pending and the ISR contents may be used as a pointer to the appropriate interrupt service routine.

1 = no interrupt pending.

#### ISR BIT 1-2:

Logical combination of these bits, provides the highest priority interrupt pending.

#### ISR BIT 3-7:

These bits are not used and are set to zero.

# FIFO CONTROL REGISTER (FCR)

This register is used to enable the FIFOs, clear the FIFOs, set the receiver FIFO trigger level, and select the type of DMA signalling.

#### FCR BIT-0:

0 = Disable the transmit and receive FIFO.

1 = Enable the transmit and receive FIFO.

### FCR BIT-1:

#### 0=No change.

1 = Clears the contents of the receive FIFO and resets its counter logic to 0 (the receive shift register is not cleared or altered). This bit will return to zero after clearing the FIFOs.

### FCR BIT-2:

0=No change.

1 = Clears the contents of the transmit FIFO and resets its counter logic to 0 (the transmit shift register is not cleared or altered). This bit will return to zero after clearing the FIFOs.

#### FCR BIT-3:

#### 0=No change.

1 = Changes RXRDY and TXRDY pins from mode "0" to mode "1".

#### FCR BIT 4-5:

Not used.

#### FCR BIT 6-7:

These bits are used to set the trigger level for the receiver FIFO interrupt.

| BIT-7 | BIT-6 | FIFO trigger level |

|-------|-------|--------------------|

| 0     | 0     | 01                 |

| 0     | 1     | 04                 |

| 1     | 0     | 08                 |

| 1     | 1     | 14                 |

|       |       |                    |

#### LINE CONTROL REGISTER (LCR)

The Line Control Register is used to specify the asynchronous data communication format. The number of the word length, stop bits, and parity can be selected by writing appropriate bits in this register.

#### LCR BIT1-0:

These two bits specify the word length to be transmitted or received.

| BIT-1 | BIT-0 | Word length |

|-------|-------|-------------|

| 0     | 0     | 5           |

| 0     | 1     | 6           |

| 1     | 0     | 7           |

| 1     | 1     | 8           |

#### LCR BIT-2:

The number of stop bits can be specified by this bit.

| BIT-2 | World length | Stop bit(s) |

|-------|--------------|-------------|

| 0     | 5,6,7,8      | 1           |

| 1     | 5            | 1-1/2       |

| 1     | 6,7,8        | 2           |

#### LCR BIT-3:

Parity or no parity can be selected via this bit. 0 = no parity

1 = a parity bit is generated during the transmission, receiver also checks for received parity.

#### LCR BIT-4:

If the parity bit is enabled, LCR BIT-4 selects the even or odd parity format.

0 = ODD parity is generated by forcing an odd number of 1's in the transmitted data, receiver also checks for same format.

1 = EVEN parity bit is generated by forcing an even the number of 1's in the transmitted data, receiver also checks for same format.

#### LCR BIT-5:

If the parity bit is enabled, LCR BIT-5 selects the forced parity format.

LCR BIT-5=1 and LCR BIT-4=0, parity bit is forced to "1" in the transmitted and received data.

LCR BIT-5 = 1 and LCR BIT-4 = 1, parity bit is forced to "0" in the transmitted and received data.

#### LCR BIT-6:

Break control bit. It causes a break condition to be transmitted (the SOUT is forced to low state).

0 = normal operating condition.

$1 = \mbox{forces}\xspace$  the transmitter output (SOUT) to go low to alert the communication terminal.

#### LCR BIT-7:

The internal baud rate counter latch enable(DLAB). 0 = normal operation.

1 = select divisor latch register.

#### MODEM CONTROL REGISTER (MCR)

This register controls the interface with the MODEM or a peripheral device (RS232).

#### MCR BIT-0:

0 =force DTR $\sim$  output to high. 1 = force DTR $\sim$  output to low.

#### MCR BIT-1:

0 =force RTS~ output to high. 1 = force RTS~ output to low.

#### MCR BIT-2:

$0 = set OP1 \sim output to high.$  $1 = set OP1 \sim output to low.$

#### MCR BIT-3:

$0 = set OP2 \sim output to high.$  $1 = set OP2 \sim output to low.$

#### MCR BIT-4:

0 = normal operating mode.

1 = enable local loop-back mode (diagnostics). The transmitter output (SOUT) is set high (Mark condition), the receiver input (SIN), CTS~, DSR~, DCD~, and RI~ are disabled. Internally the transmitter output is connected to the receiver input and DTR~, RTS~, OP1~ and OP2~ are connected to modem control inputs. In this mode , the receiver and transmitter interrupts are fully operational. The Modem Control Interrupts are also operational, but the interrupts sources are now the lower four bits of the Modem Control inputs. The interrupts are still controlled by the IER.

#### MCR BIT 5-7:

Not used. Are set to zero permanently.

# LINE STATUS REGISTER (LSR)

This register provides the status of data transfer to  $\ensuremath{\mathsf{CPU}}$  .

# LSR BIT-0:

0 = no data in receive holding register or FIFO. 1 = data has been received and saved in the receive holding register or FIFO.

# LSR BIT-1:

0 = no overrun error (normal).

1 = overrun error, next character arrived before receive holding register was emptied or if FIFOs are enabled, an overrun error will occur only after the FIFO is full and the next character has been completely received in the shift register. Note that character in the shift register is overwritten, but it is not transferred to the FIFO.

#### LSR BIT-2:

0 = no parity error (normal).

1 = parity error, received data does not have correct parity information. In the FIFO mode this error is associated with the character at the top of the FIFO.

#### LSR BIT-3:

0 = no framing error (normal).

1 = framing error received, received data did not have a valid stop bit. In the FIFO mode this error is associated with the character at the top of the FIFO.

#### LSR BIT-4:

0=no break condition (normal).

1 = receiver received a break signal (SIN was low for one character time frame). In FIFO mode, only one zero character is loaded into the FIFO.

#### LSR BIT-5:

$0\!=\!transmit$  holding register is full. LD1201 will not accept any data for transmission.

$1 = \mbox{transmit}$  holding register (or FIFO ) is empty. CPU can load the next character.

#### LSR BIT-6:

0=transmitter holding and shift registers are full. 1=transmitter holding and shift registers are empty. In FIFO mode this bit is set to one whenever the transmitter FIFO and transmit shift register are empty.

# LSR BIT-7:

0 = Normal.

$1\!=\!at$  least one parity error, framing error or break indication in the FIFO. This bit is cleared when LSR is read.

#### **MODEM STATUS REGISTER (MSR)**

This register provides the current state of the control lines from the modem or peripheral to the CPU. Four bits of this register are used to indicate the changed information. These bits are set to "1" whenever a control input from the MODEM changes state. They are set to "0" whenever the CPU reads this register.

#### MSR BIT-0:

Indicates that the CTS  $\sim$  input to the LD1201 has changed state since the last time it was read.

#### MSR BIT-1:

Indicates that the DSR~ input to the LD1201 has changed state since the last time it was read.

#### MSR BIT-2:

Indicates that the RI $\sim$  input to the LD1201 has changed from a low to a high state.

#### MSR BIT-3:

Indicates that the CD~ input to the LD1201 has changed state since the last time it was read.

#### MSR BIT-4:

This bit is equivalent to RTS in the MCR during local loop-back mode. It is the compliment of the CTS  $\sim$  input.

#### MSR BIT-5:

This bit is equivalent to DTR in the MCR during local loop-back mode. It is the compliment of the DSR  $\sim$  input.

#### MSR BIT-6:

This bit is equivalent to OP1 in the MCR during local loop-back mode. It is the compliment of the  $RI \sim$  input.

#### MSR BIT-7:

This bit is equivalent to OP2 in the MCR during local loop-back mode. It is the compliment to the  $CD \sim$  input.

Note: Whenever MSR BIT3-0: is set to logic "1", a MODEM Status Interrupt is generated.

#### SCRATCHPAD REGISTER (SR)

LD1201 provides a temporary data register to store 8 bits of information for variable use.

### LD1201 EXTERNAL RESET CONDITION TABLE:

| REGISTERS | RESET STATE                 |

|-----------|-----------------------------|

| IER       | IER BITS 0-7=0              |

| ISR       | ISR BIT-0=1, ISR BITS 1-7=0 |

| LCR       | LCR BITS 0-7=0              |

| MCR       | MCR BITS 0-7=0              |

| LSR       | LSR BITS 0-4=0,             |

|           | LSR BITS 5-6=1 LSR, BIT 7=0 |

| MSR       | MSR BITS 0-3=0,             |

|           | MSR BITS 4-7=input signals  |

| FCR       | FCR BITS 0-7=0              |

| SIGNALS                                                         | S RESET STATE                                                |

|-----------------------------------------------------------------|--------------------------------------------------------------|

| SOUT<br>OP1~<br>OP2~<br>RTS~<br>DTR~<br>INT<br>RXRDY~<br>TXRDY~ | High<br>High<br>High<br>High<br>BITS 0-3=Iow<br>High<br>High |

| BAUD  | RATE    | GENERATOR   | PROGRAMMING |

|-------|---------|-------------|-------------|

| TABLE | (1.8432 | MHz CLOCK): |             |