# Microprod anual ARROW ELECTRONICS, INC. ELECTRONICS DISTRIBUTION DIVISION ELECTRONICS DISTRIBUTION DIVISION ELECTRONICS DIVISION E

317/243/9353

WDW

**Microprocessor Products**

Data Manual 1986

# Microprocessor Products

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1986 Signetics Corp.

# **Contents**

# **Microprocessor Products**

| Ordering Information                                     |                                                                | ii    |

|----------------------------------------------------------|----------------------------------------------------------------|-------|

| Product Status                                           |                                                                | iv    |

| Section 1 – QUALITY & RELIABI<br>Quality and Reliability | ILITY                                                          | . 1-3 |

| Section 2 - MICROPROCESSOR                               | PRODUCTS                                                       |       |

| SCN2641                                                  | Asynchronous Communications Interface                          | 2-3   |

| SCN2651                                                  | Programmable Communications Interface (PCI)                    |       |

| SCN2652                                                  | Multi-Protocol Communications Controller (MPCC)                |       |

| SCN2653                                                  | Polynomial Generator Checker (PGC).                            |       |

| SCN2661                                                  | Enhanced Programmable Communications Interface (EPCI)          |       |

| SCN2672                                                  | Programmable Video Timing Controller (PVTC)                    |       |

| SCB2673                                                  | Video Attributes Controller (VAC)                              |       |

| SCN2674                                                  | Advanced Video Display Controller (AVDC)                       |       |

| SCB2675                                                  | Color/Monochrome Attributes Controller (CMAC)                  |       |

|                                                          |                                                                |       |

| SCB2675T                                                 | Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)      |       |

| SCB2677                                                  | Video Attributes Controller (VAC)                              |       |

| SCN2681                                                  | Dual Asynchronous Receiver/Transmitter (DUART)                 |       |

| SCC2691                                                  | Universal Asynchronous Receiver/Transmitter (UART)             |       |

| SCC2698                                                  | Octal Universal Asynchronous Receiver/Transmitter (Octal UART) |       |

| SCN68000                                                 | 16-/32-Bit Microprocessor                                      |       |

| SCN68010                                                 | 16-Bit Virtual Memory Microprocessor                           |       |

| SCB68154                                                 | Interrupt Generator                                            |       |

| SCB68155                                                 | Interrupt Handler                                              |       |

| SCB68171                                                 | Very Little Serial Interface Chip (VLSIC)                      |       |

| SCB68172                                                 | VMEbus Controller (BUSCON)                                     |       |

| SCC68173                                                 | VMSbus Controller (VMSCON)                                     | 2-416 |

| SCB68175                                                 | Bus Controller                                                 |       |

| SCB68430                                                 | Direct Memory Access Interface (DMAI)                          |       |

| SCN68454                                                 | Intelligent Multiple Disk Controller (IMDC)                    |       |

| SCB68459                                                 | Disk Phase-Locked Loop (DPLL)                                  | 2-489 |

| SCN68562                                                 | Dual Universal Serial Communications Controller (DUSCC)        | 2-500 |

| SCN68681                                                 | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-547 |

| SCC68905                                                 | Basic Memory Access Controller (BMAC)                          | 2-568 |

| SCC68906                                                 | Basic Memory Access Controller (BMAC)                          | 2-599 |

| Section 3 - MICROCONTROLLER                              | PRODUCTS                                                       |       |

| SCN80 Series                                             | Single-Chip 8-Bit Microcontroller                              | 3-3   |

| SCC80 Series                                             | CMOS Single-Chip 8-Bit Microcontroller                         | 3-18  |

| SCC80C31/SCC80C51                                        | CMOS Single-Chip 8-Bit Microcontroller                         | 3-30  |

| SCN8031AH/SCN8051AH                                      | Single-Chip 8-Bit Microcontroller                              | 3-43  |

| SCN8032AH/SCN8052AH                                      | Single-Chip 8-Bit Microcontroller                              | 3-56  |

| SCN8400 Series                                           | Single-Chip 8-Bit Microcontroller                              | 3-69  |

| Section 4 - MICROSYSTEMS PRO                             | ODUCTS                                                         |       |

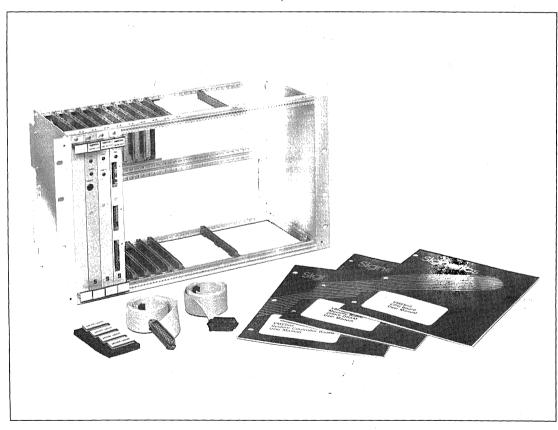

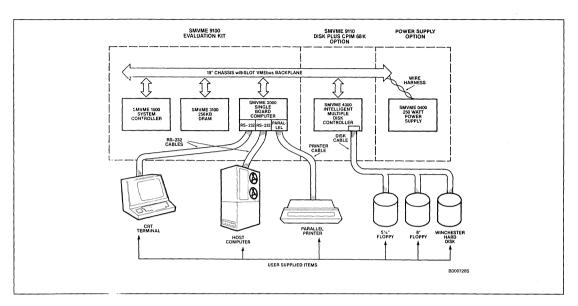

| SMVME0400                                                | VMEbus Power Supply                                            | 4-3   |

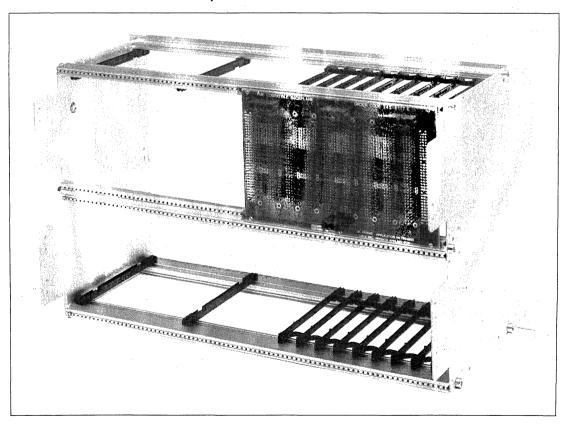

| SMVME0500/0510                                           | Card Cage Assembly                                             |       |

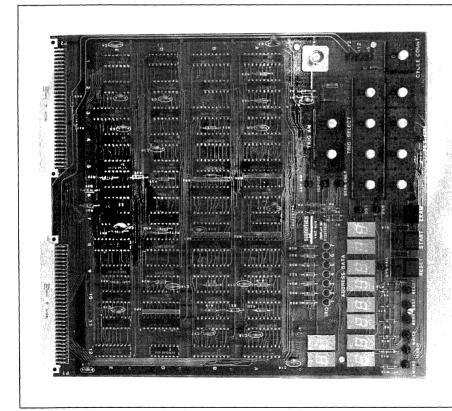

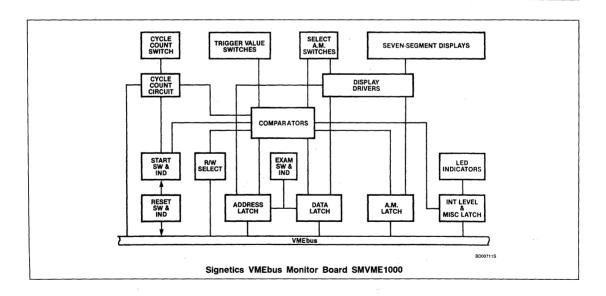

| SMVME1000                                                | VMEbus Monitor Board                                           | 4-7   |

| SMVME1200/1201                                           | VMEbus Prototype Board                                         |       |

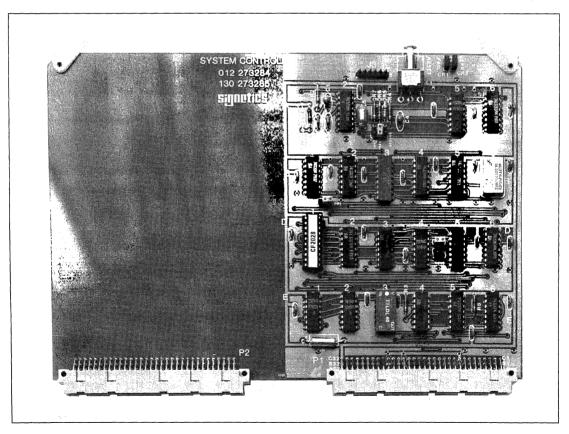

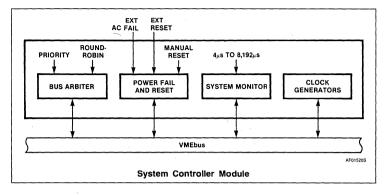

| SMVME1500                                                | VMEbus System Controller                                       |       |

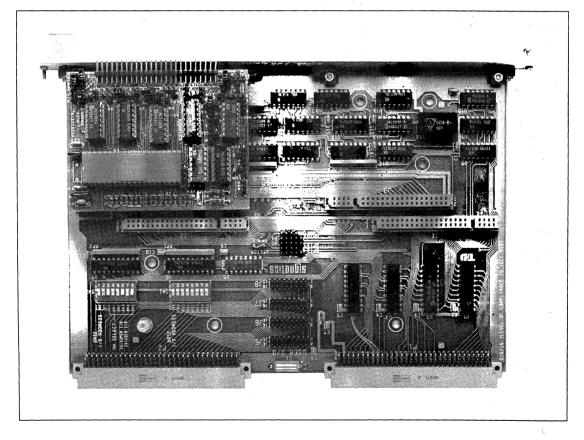

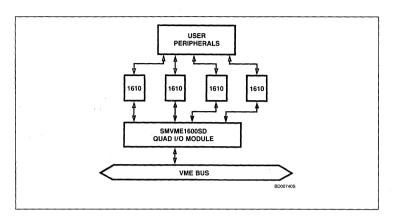

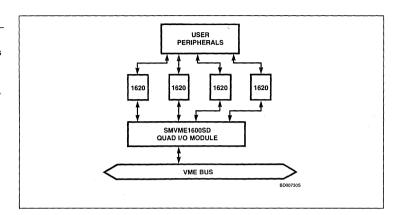

| SMVME1600                                                | VMEbus Quad I/O Module                                         |       |

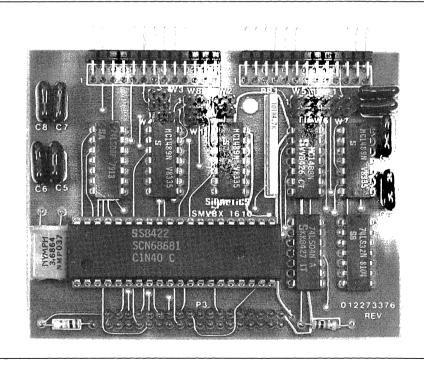

| SMVME1610                                                | VMEbus Serial Module                                           |       |

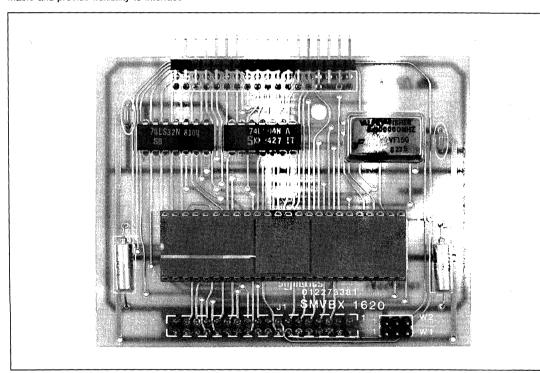

| SMVME1620                                                | VMEbus Parallel Module                                         |       |

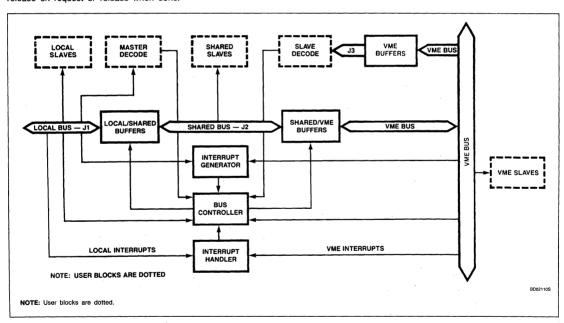

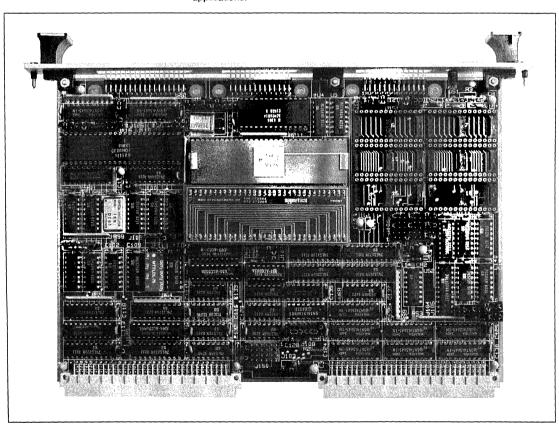

| SMVME2000                                                | VMEbus CPU Module                                              | 4-20  |

| SMVME21XX Series                                         | VMEbus Distributed Multiprocessing Engine                      |       |

| SMVME31XX                                                | VMEbus 256KB/1MB Memory Module                                 | 4-24  |

| SMVME3300                                                | VMEbus RAM, ROM and EPROM Module                               | 4-26  |

|                                                          | :                                                              |       |

# Contents

| 4-28<br>4-30<br>4-32 |

|----------------------|

| 4-30                 |

| 4.00                 |

| 4-3,                 |

| 4-34                 |

| 4-3                  |

| 4-39                 |

| 4-4                  |

| 4-44                 |

| 4-47                 |

|                      |

| 5-0                  |

|                      |

| 6-3                  |

|                      |

| 7-3                  |

|                      |

ii

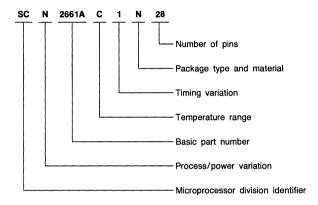

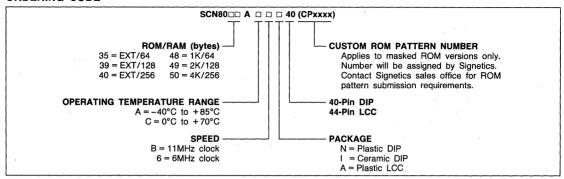

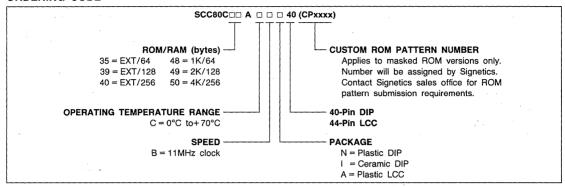

# Ordering Information

## **Microprocessor Products**

## **Microprocessor Part Numbers:**

# Microsystems Part Number Template:

#### Pos. Description 1-2 SM to signify Signetics Microsystems 3-5 Indicates Product Family --VME - Modular Board Products DEV - Development Support SFT - Software Support MAN - Manuals KIT - Development Kits 6-9(10) Individual Product Identifier - number to be defined by Product Marketing Manager 0xxx — Accessories 5xxx - Communication 1xxx - Other Modules Modules 6xxx - Industrial I/O Modules 2xxx — CPU Modules 3xxx — Memory Modules 7xxx --- Video Modules 4xxx — Mass Storage 8xxx - Target Software Modules 9xxx -- Evaluation Kits 11 - 12IC Package Type Identifier - we will use SD as our standard

13 - 14 Revision Identifier

package identifier

# Product Status

**Microprocessor Products**

| DEFINITIONS                  |                        |                                                                                                                                                                                                                                              |  |  |  |  |  |

|------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Sheet<br>Identification | Product Status         | Definition                                                                                                                                                                                                                                   |  |  |  |  |  |

| Objective Specification      | Formative or In Design | This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice.                                                                                           |  |  |  |  |  |

| Preliminary Specification    | Preproduction Product  | This data sheet contains preliminary data and supplementary data will be published at a later date. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. |  |  |  |  |  |

| Product Specification        | Full Production        | This data sheet contains Final Specifications. Signetics reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |  |  |  |  |  |

# Section 1 Quality and Reliability

**Microprocessor Products**

# Quality and Reliability

### **Microprocessor Products**

## INTRODUCTION

The Microprocessor Division was formed in 1979 when it became apparent that microprocessor circuits and their peripheral devices would become increasingly important system components to the OEM customer base. Because of performance to cost ratios, reduced power requirements and inherent reliability, these components provide the solution to designers' complex system requirements.

NMOS became the dominant technology because of the simplicity of its design and processing and its large historical reliability data base. To date, NMOS has serviced 95% of the division's device requirements. Bipolar devices are used to a limited extent as interface drivers between the NMOS system components and CRT displays.

The Microprocessor Division serves a broad base of customers with its product lines of eight and sixteen bit microprocessors, microcontrollers, and data communication and CRT peripheral circuits. The division's customers range from large mainframe computer manufacturers to small systems users, and the division can generally satisfy all the microprocessor requirements of any customer.

Our goal is to establish ourselves as the preferred alternate source in both the 68000 microprocessor and the 80XX microcontroller product areas and at the same time become the prime supplier of the interface and peripheral circuits required to integrate the parts within a system. Our design philosophy is to give superior performance while minimizing the overall number of parts required for the overall system.

The terms quality and reliability are often misinterpreted. In general, quality refers to the condition of a device when received; reliability covers extent of useful life. Quality is readily measurable; reliability is predictable and verifiable based on historical evidence.

# MICROPROCESSOR DIVISION RELIABILITY

No amount of stress testing can improve a product's reliability. Stress tests are used to measure and define an end of life which can be expected from a family of products. Reliability as well as quality must be built in through proper design, processing, assembly, testing and handling. For Signetics' Microprocessor Division parts, accelerated life test data show an extremely reliable product line and serve as one input for continuous product reliability improvement.

#### DESIGN

Product quality and reliability begin in design. Strategic questions directly affecting reliability must be answered. How much static protection is required on input leads? Do formal design rules exist? Can they ever be violated? What method is used to anticipate future processes or "shrinks"?

Within Signetics' Microprocessor Division, rigid guidelines are in effect to ensure compliance with our design rules. Design rules, once established, are inviolate.

#### QUALIFICATION TESTING

Signetics' Microprocessor Division verifies device reliability through a series of qualification tests and a continuous reliability monitor program, Sure III (Systematic Uniform Reliability Evaluation).

All new fab processes at Signetics are qualified by stress testing parts from a variety of production lots. This accelerated stress testing is shown in the table.

#### SURE III

Continuous reliability monitoring is performed via our SURE III program. Devices are ran-

domly selected from production lots and subjected to the same environmental stresses noted in the table. The program is administered by the Corporate Reliability Engineering Group, which publishes a summary of results on a guarterly basis.

The SURE III program covers two functions: Monitoring short term and long term reliability performance.

#### LONG-TERM AUDIT

One hundred devices from each generic family are subjected to each of the following stresses every other four weeks:

- High Temperature Operating Life T<sub>J</sub> = 150°C, 1000 hours — (Static Biased or Dynamic Operation, as appropriate);

- Temperature-Humidity Biased Life 85°C, 85% RH, 1000 hours, static biased;

- Temperature Cycling (Air-Air) -65°C to +150°C, 1000 cycles.

#### SHORT-TERM MONITOR

Every week 20-piece samples from each generic family are run to 96 hours of pressure pot (15 psig, 121°C, 100% saturated steam), 300 cycles of thermal shock ( $-65^{\circ}$ C to  $+150^{\circ}$ C) and 168 hours of high temperature operating life ( $T_J = 150^{\circ}$ C, static or dynamic operation).

In addition, each Signetics assembly plant performs SURE product monitor stresses weekly on each generic family and molded package, by pin count and frame type. Fifty pieces are subjected to 300 cycles of thermal shock (Cond. C) and 100 devices are subjected to pressure pot stress at 20 psig for 72 hours (168 hour equivalent at 15 psig).

# Quality and Reliability

#### **Accelerated Life Stress Tests**

|      | TEST                             | TEST CONDITION                     | NUMBER OF<br>DEVICES | DURATION   |

|------|----------------------------------|------------------------------------|----------------------|------------|

| DHTL | Dynamic high temperature life    | T <sub>A</sub> @125°C (operating)  | 52                   | 1000 hrs   |

| SHTL | Static high temperature life     | T <sub>A</sub> @125°C (operating)  | 52                   | 1000 hrs   |

| THBS | Biased temperature humidity life | 85°C/85% RH (operating)            | 52                   | 1000 hrs   |

| PPOT | Pressure pot (autoclave)         | 121°C/15 psig (storage)            | 52                   | 96 hrs     |

| TMSK | Thermal shock                    | -55°C/125°C liq. to liq. (storage) | 77                   | 300 cycles |

| TMCL | Temperature cycle (air-to-air)   | -65°C/150°C (storage)              | 77                   | 300 cycles |

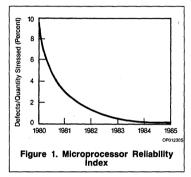

Figure 1 shows the relative improvement in Sure III performance for the Microprocessor Division for the past five years. This curve combines all the stress tests and plots the overall percentage defective by year. Clearly, the reliability of our product line is improving, and more importantly, it is consistent and predictable.

# SIGNETICS' QUALITY IMPROVEMENT PROGRAM

Signetics began its Quality Improvement Program in 1980, and developed it around the concepts outlined in the book, "Quality is Free," by Phil Crosby.

This program, which is actively supported by top management, defines Quality as "Conformance to the Specification." With this definition in mind, our performance standard is "Zero Defects." Tracking charts measuring

quality improvement targets are used and displayed throughout the Division.

Microprocessor Division personnel are all actively involved in this program. Our people have taken formal training in Quality College and have pledged to "Do It Right the First Time, On Time." Administrative personnel promise to "Make Certain" of their own work.

The program improves quality through education, commitment and feedback.

Internally, there are many signs of the program's success. The SURE III Reliability Assurance Monitor shows improved results in each of the past three years. In-line quality improvements are impressive. All new products are placed on QRA Hold until completion of environmental stress testing; all significant process changes go through qualification prior to release to production; test programs are controlled and released only after extensive engineering correlation; wafers with less than the required minimum number of good die are scrapped to avoid jeopardizing product quality.

These are examples of how the Quality Improvement Program functions internally. However, the real measure of the program is customer belief in and acceptance of our improvement.

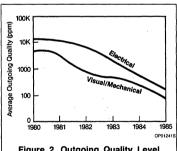

Over the past few years, customers have verified a continuous improvement in the quality and reliability of Microprocessor Division parts. Figure 2 shows the improvement in visual mechanical and electrical outgoing quality levels over the past several years.

In addition to the marked improvement in our AOQ (Average Outgoing Quality), we have become a qualified source for the 80XX and the 68000 families, as well as our own proprietary peripheral circuits, for more than 200 customers. We have developed Ship-to-Stock programs for several key accounts, eliminating the need for costly incoming inspection by our customers.

The improved reliability of our parts has allowed several customers to drop their requirements for burn-in for high reliability programs. This, of course, has lowered their costs significantly and has allowed them to improve their over-all system reliability.

Reliability testing is an important monitor of our manufacturing process. Signetics' microprocessor parts not only meet specifications when shipped but continue to operate satisfactorily throughout their lifetime.

Figure 2. Outgoing Quality Level Microprocessor Division

# Section 2 Microprocessor Products

**Microprocessor Products**

# **INDEX**

| SCN2641  | Asynchronous Commmunications Interface                         | . 2-3 |

|----------|----------------------------------------------------------------|-------|

| SCN2651  | Programmable Communications Interface (PCI)                    | 2-16  |

| SCN2652  | Multi-Protocol Communications Controller (MPCC)                | 2-32  |

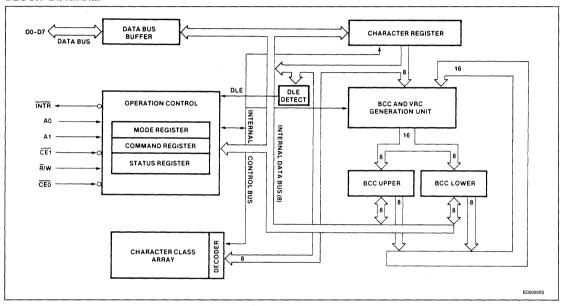

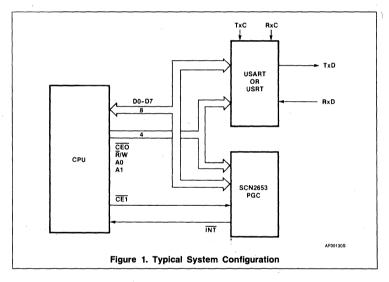

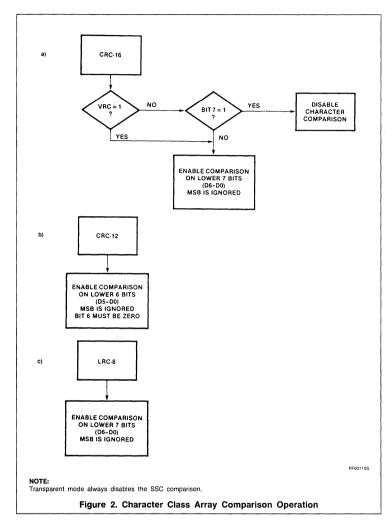

| SCN2653  | Polynomial Generator Checker (PGC)                             | 2-52  |

| SCN2661  | Enhanced Programmable Communications Interface (EPCI)          | 2-70  |

| SCN2672  | Programmable Video Timing Controller (PVTC)                    | 2-87  |

| SCB2673  | Video Attributes Controller (VAC)                              | 2-110 |

| SCN2674  | Advanced Video Display                                         | 2-123 |

| SCB2675  | Color/Monochrome Attributes Controller (CMAC)                  | 2-155 |

| SCB2675T | Turbo Color/Monochrome Attributes Controller (Turbo-CMAC)      | 2-166 |

| SCB2677  | Video Attributes Controller (VAC)                              | 2-177 |

| SCN2681  | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-189 |

| SCC2691  | Universal Asynchronous Receiver/Transmitter (UART)             | 2-208 |

| SCC2698  | Octal Universal Asynchronous Receiver/Transmitter (Octal UART) | 2-225 |

| SCN68000 | 16-/32-Bit Microprocessor                                      | 2-227 |

| SCN68010 | 16-Bit Virtual Memory Microprocessor                           | 2-289 |

| SCB68154 | Interrupt Generator                                            | 2-358 |

| SCB68155 | Interrupt Handler                                              | 2-369 |

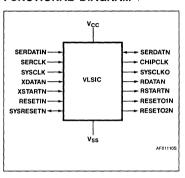

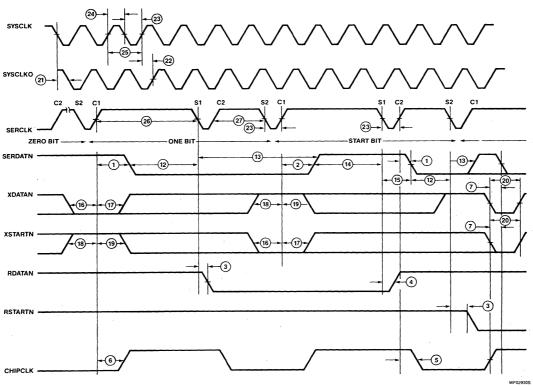

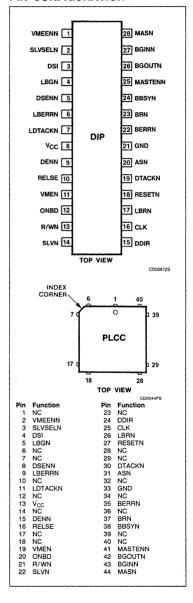

| SCB68171 | Very Little Serial Interface Chip (VLSIC)                      | 2-386 |

| SCB68172 | VMEbus Controller (BUSCON)                                     | 2-391 |

| SCC68173 | VMSbus Controller (VMSCON)                                     | 2-416 |

| SCB68175 | Bus Controller                                                 | 2-426 |

| SCB68430 | Direct Memory Access Interface (DMAI)                          | 2-438 |

| SCN68454 | Intelligent Multiple Disk Controller (IMDC)                    | 2-459 |

| SCB68459 | Disk Phase Locked Loop (DPLL)                                  | 2-489 |

| SCN68562 | Dual Universal Serial Communications Controller (DUSCC)        | 2-500 |

| SCN68681 | Dual Asynchronous Receiver/Transmitter (DUART)                 | 2-547 |

| SCC68905 | Basic Memory Access Controller (BMAC)                          | 2-568 |

| SCC68906 | Basic Memory Access Controller (BMAC)                          | 2-599 |

# SCN2641 Asynchronous Communications Interface

Product Specification

# Microprocessor Products

#### DESCRIPTION

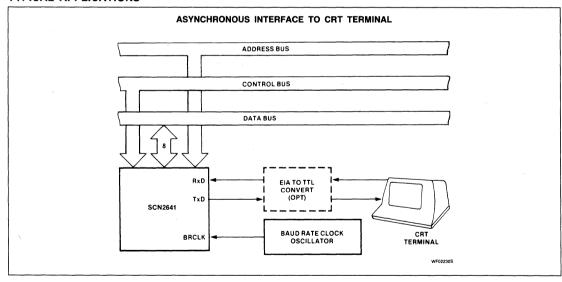

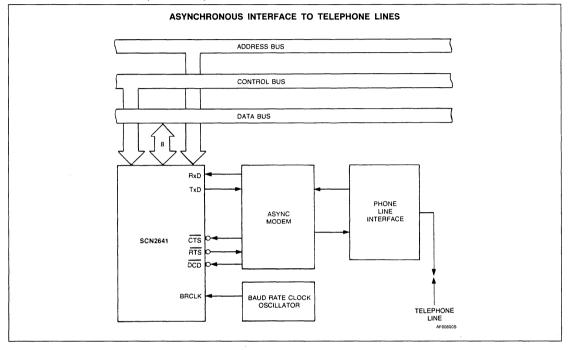

The Signetics SCN2641 is a universal asynchronous data communications controller chip that interfaces directly to most 8-bit microprocessors and may be used in a polled or interrupt-driven system environment. The SCN2641 accepts programmed instructions from the microprocessor while supporting asynchronous serial data communications in full- or half-duplex mode.

The SCN2641 serializes parallel data characters received from the microprocessor for transmission. Simultaneously, it can receive serial data and convert it into parallel data characters for input to the microcomputer.

The SCN2641 contains a baud rate generator which can be programmed to either accept an external clock or to generate internal transmit or receive clocks. Sixteen different baud rates can be selected under program control when operating in the internal clock mode.

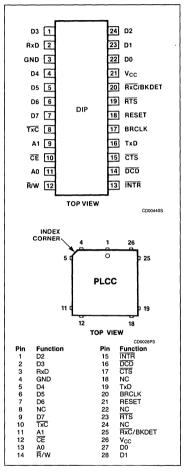

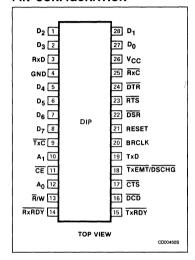

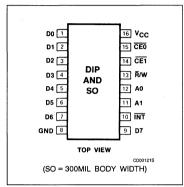

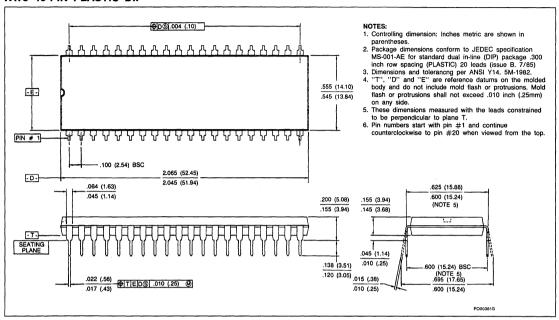

The SCN2641 is constructed using Signetics n-channel silicon gate depletion load technology and is packaged in a 24-pin DIP.

#### **FEATURES**

- 5- to 8-bit characters plus parity

- 1. 1½ or 2 stop bits transmitted

- Odd, even or no parity

- Parity, overrun and framing error detection

- Line break detection and generation

- False start bit detection

- Automatic serial echo mode (echoplex)

- Local or remote maintenance loopback mode

- Baud rate:

- DC to 1M bps (1X clock)

- DC to 62.5K bps (16X clock)

- DC to 15.625K bps (64X clock)

- Internal or external baud rate clock

- 16 internal rates

- Double-buffered transmitter and receiver

- Single +5V power supply

- 400 mil package width

#### **APPLICATIONS**

- Intelligent terminals

- Network processors

- Front-end processors

- Remote data concentrators

- Serial peripherals

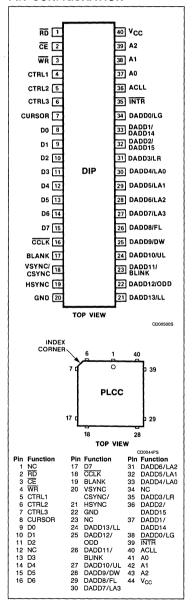

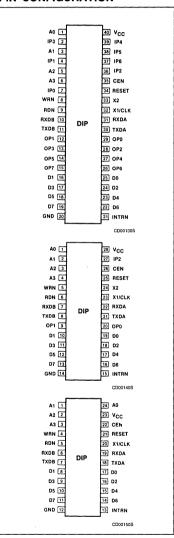

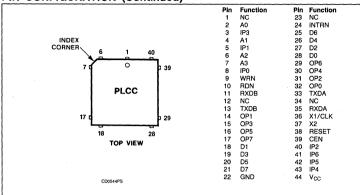

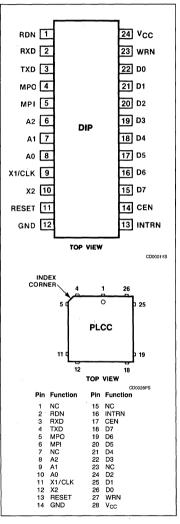

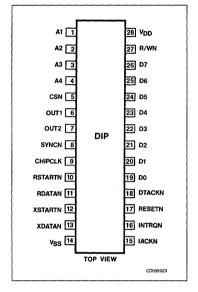

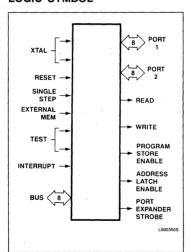

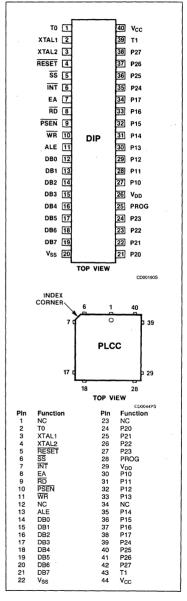

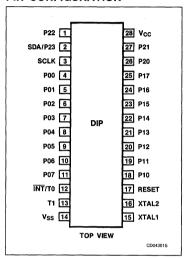

# PIN CONFIGURATION

SCN2641

#### **ORDERING CODE**

| PACKAGES    | V <sub>CC</sub> = 5V± 5%, T <sub>A</sub> = 0°C to 70°C |

|-------------|--------------------------------------------------------|

| Plastic DIP | SCN2641CC1N24                                          |

| Plastic LCC | SCN2641CC1A28                                          |

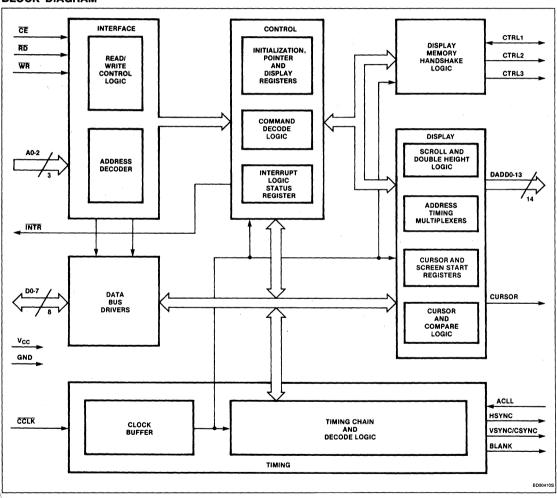

## **BLOCK DIAGRAM**

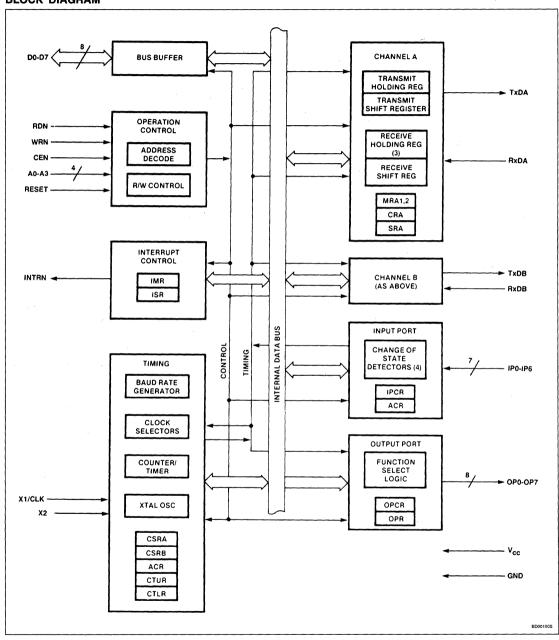

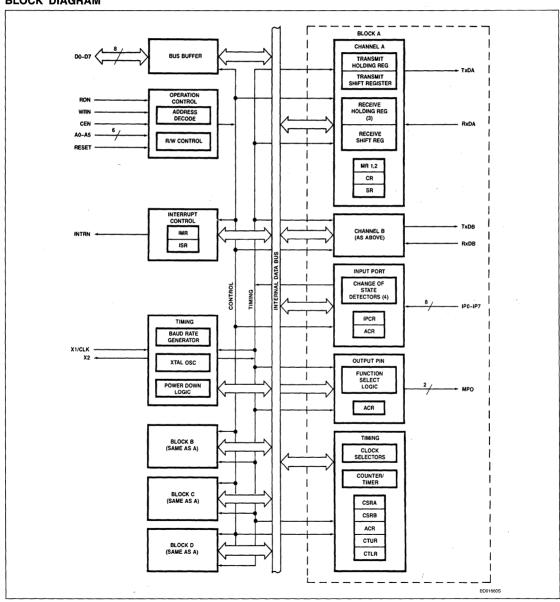

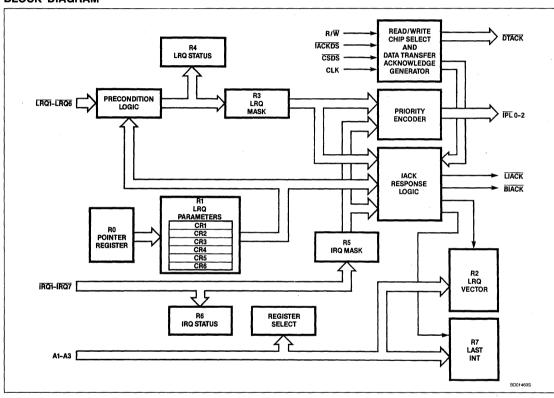

# **BLOCK DIAGRAM**

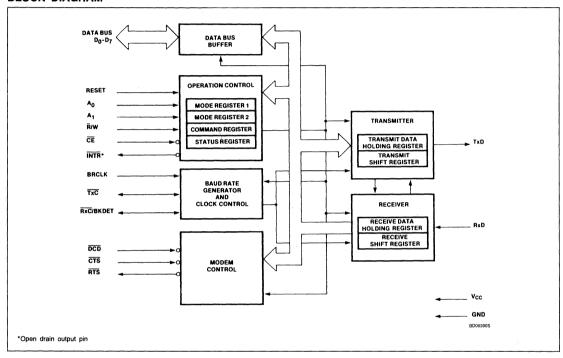

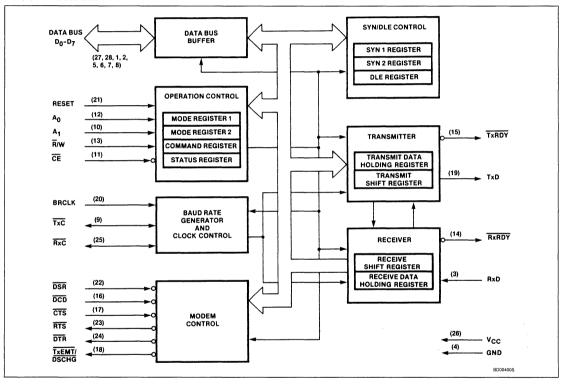

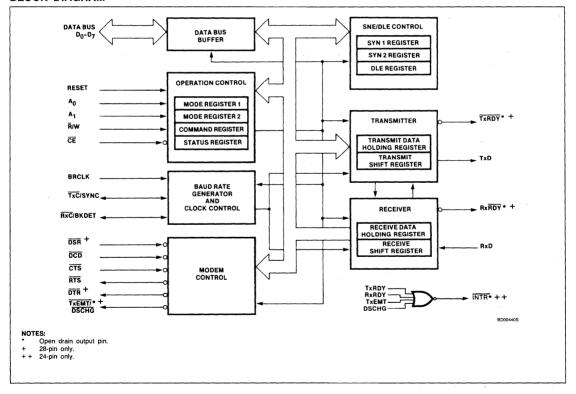

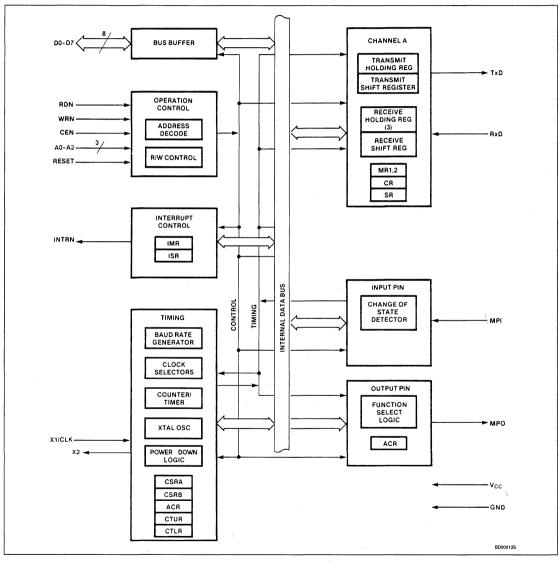

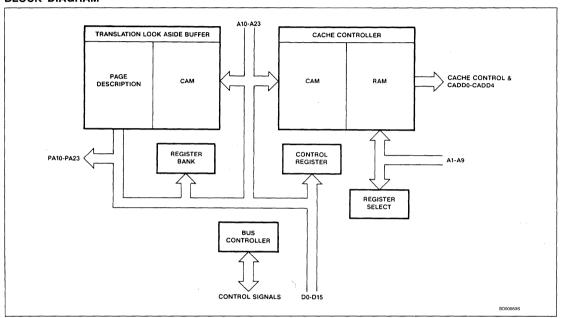

The SCN2641 consists of five major sections. These are the transmitter, receiver, timing, operation control and modem control. These sections communicate with each other via an internal data bus and an internal control bus. The internal data bus interfaces to the microprocessor data bus via a data bus buffer.

### **Operation Control**

This functional block stores configuration and operation commands from the CPU and generates appropriate signals to various internal sections to control the overall device operation. It contains read and write circuits to permit communications with the microprocessor via the data bus and contains mode registers 1 and 2, the command register, and the status register. Details of register addressing are presented in the SCN2641 programming section of this data sheet.

## **Timing**

The SCN2641 contains a baud rate generator (BRG) which is programmable to accept external transmit or receive clocks or to divide an external clock to perform data communications. The unit can generate 16 commonly used baud rates, any one of which can be selected for full-duplex operation. See table 1.

#### Receiver

The receiver accepts serial data on the RxD pin, converts this serial input to parallel format, checks for certain errors and sends an "assembled" character to the CPU.

# **Transmitter**

The transmitter accepts parallel data from the CPU, appends start and stop bits, and, optionally, a parity bit, and outputs a composite serial stream of data on the TxD output pin.

# **Modem Control**

The modem control section provides interfacing for two input signals and one output signal used for "handshaking" and status indication between the CPU and a modem.

## **INTERFACE SIGNALS**

The SCN2641 interface signals can be grouped into two types: the CPU-related signals (shown in table 2), which interface the SCN2641 to the microprocessor system and the device-related signals (shown in table 3), which are used to interface to the communications device or system.

# **OPERATION**

The functional operation of the SCN2641 is programmed by a set of control words supplied by the CPU. These control words speci-

SCN2641

Table 1. BAUD RATE GENERATOR CHARACTERISTICS (BRCLK = 3.6864MHz)

| MR23 - 20 | BAUD<br>RATE | ACTUAL FREQUENCY<br>16X CLOCK | PERCENT<br>ERROR | DIVISOR |

|-----------|--------------|-------------------------------|------------------|---------|

| 0000      | 50           | 0.8kHz                        | _                | 4608    |

| 0001      | 75           | 1.2                           | _                | 3072    |

| 0010      | 110          | 1.7596                        | -0.022           | 2095    |

| 0011      | 134.5        | 2.152                         | ] _ ]            | 1713    |

| 0100      | 150          | 2.4                           | -                | 1536    |

| 0101      | 300          | 4.8                           | _                | 768     |

| 0110      | 600          | 9.6                           | 9.6              |         |

| 0111      | 1200         | 19.2                          | _                | 192     |

| 1000      | 1800         | 28.8                          | _                | 128     |

| 1001      | 2000         | 32.055                        | 0.174            | 115     |

| 1010      | 2400         | 38.4                          | . – [            | 96      |

| 1011      | 3600         | 57.6                          |                  | 64      |

| 1100      | 4800         | 76.8                          | _                | 48      |

| 1101      | 7200         | 115.2                         | _ [              | 32      |

| 1110      | 9600         | 153.6                         | -                | 24      |

| 1111      | 19200        | 307.2                         | _                | 12      |

fy items such as baud rate, number of bits per character, etc. The programming procedure is described in the SCN2641 programming section of this data sheet.

After programming, the SCN2641 is ready to perform the desired communications functions. The receiver performs serial to parallel conversion of data received from a modem or equivalent device. The transmitter converts parallel data received from the CPU to a serial bit stream. These actions are accomplished within the framework specified by the control words.

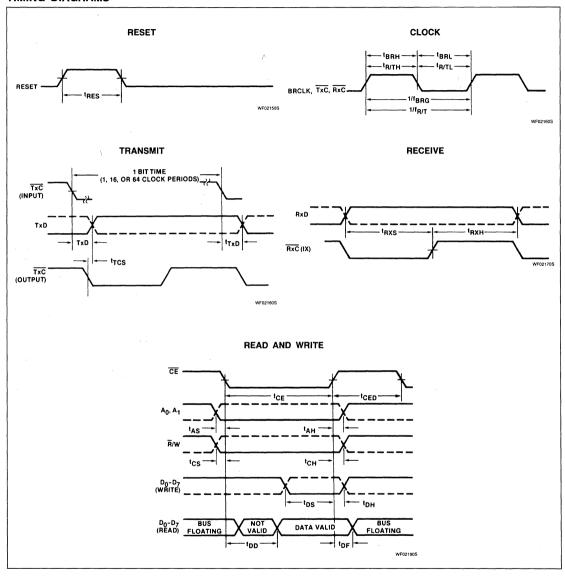

## Receiver

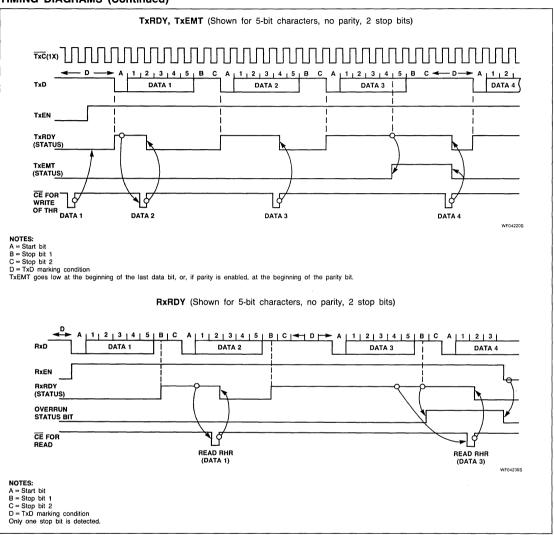

The SCN2641 is conditioned to receive data when the  $\overline{\text{DCD}}$  input is low and the RxEN bit in the command register is true. The receiver looks for a high-to-low transition of the start bit on the RxD input line. If a transition is detected, the state of the RxD line is sampled again after a delay of one-half of a bit time. If RxD is now high, the search for a valid start bit is begun again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input line at one bit time intervals until the proper number of data bits, the parity bit, and one stop bit have been assembled. The data is then transferred to the receive data holding register, the RxRDY

bit in the status register is set, and the INTR output is asserted. If the character length is less than 8 bits, the high-order unused bits in the holding register are set to zero. The parity error, framing error, and overrun error status bits are strobed into the status register on the positive-going edge of RxC corresponding to the received character boundary. If the stop bit is present, the receiver will immediately begin its search for the next start bit. If the stop bit is absent (framing error), the receiver will interpret a space as a start bit if it persists into the next bit time interval. If a break condition is detected (RxD is low for the entire character as well as the stop bit), only one character consisting of all zeros (with the FE status bit set) will be transferred to the holding register. The RxD input must return to a high condition before a search for the next start bit begins.

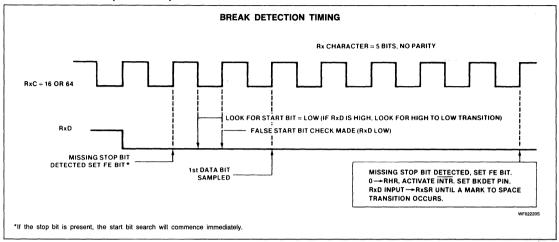

Pin 20 can be programmed to be a break detect output by appropriate setting of MR27 – MR24. If so, a detected break will cause that pin to go high. When RxD returns to mark for one RxC time, pin 20 will go low. Refer to the break detection timing diagram.

## **Transmitter**

The SCN2641 is conditioned to transmit data when the  $\overline{\text{CTS}}$  input is low and the TxEN

command register bit is set. The SCN2641 indicates to the CPU that it can accept a character for transmission by setting the TxRDY status bit and asserting the INTR output. When the CPU writes a character into the transmit data holding register, these conditions are negated. Data is transferred from the holding register to the transmit shift register when it is idle or has completed transmission of the previous character. The TxRDY conditions are then asserted again. Thus, one full character time of buffering is provided.

The transmitter automatically sends a start bit followed by the programmed number of data bits, the least significant bit being sent first. It then appends an optional odd or even parity bit and the programmed number of stop bits. If, following transmission of the data bits, a new character is not available in the transmit holding register, the TxD output remains in the marking (high) condition and the TxEMT/DSCHG status bit and the INTR output are asserted. Transmission resumes when the CPU loads a new character into the holding register. The transmitter can be forced to output a continuous low (BREAK) condition by setting the send break command bit (CR3) high.

SCN2641

Table 2. CPU-RELATED SIGNALS

| PIN                             | PIN             | NO.    | INPUT/ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|---------------------------------|-----------------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                            | DIP             | PLCC   | OUTPUT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| V <sub>CC</sub>                 | 21              | 26     | ı      | +5V supply input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| GND                             | 3               | 4      | 1      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

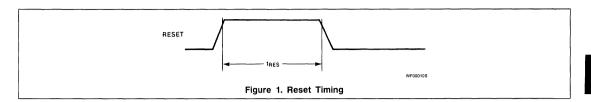

| RESET                           | 18              | 21     | 1      | A high on this input performs a master reset on the SCN2641. This signal asynchronously terminates any device activity and clears the mode, command and status registers. The device assumes the idle state and remains there until initialized with appropriate control words.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| A <sub>1</sub> - A <sub>0</sub> | 9, 11           | 11, 13 | 1.     | Address lines used to select internal SCN2641 registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| R∕W                             | 12              | 14     | 1      | Read command when low, write command when high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

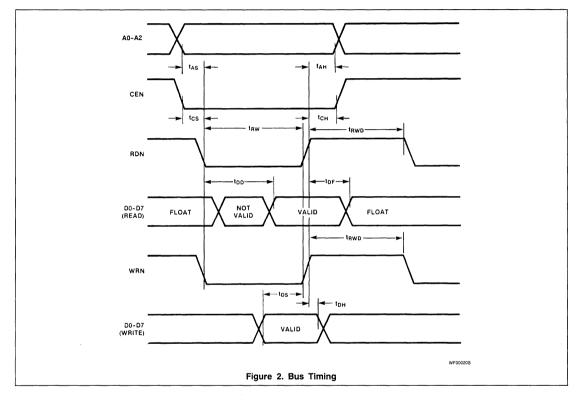

| CE                              | 10              | 12     | 1      | Chip enable command. When low, indicates that control and data lines to the SCN2641 are valid and that the operation specified by the $\overline{R}/W$ , $A_1$ and $A_0$ inputs should be performed. When high, places the $D_0-D_7$ lines in the three-state condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| D <sub>7</sub> – D <sub>0</sub> | 7-4,1,<br>24-22 |        | 1/0    | 8-bit, three-state data bus used to transfer commands, data and status between the SCN2641 and the CPU. $D_0$ is the least significant bit; $D_7$ the most significant bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

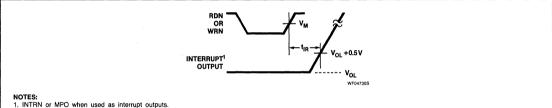

| INTR                            | 13              | 15     | 0      | Interrupt request output (open drain). This output is asserted (low) under the following conditions.  1. When the transmitter holding register (THR) is ready to accept a data character from the CPU. This corresponds to assertion of status bit SR0. If this is the only condition asserting the output, the output will be negated (high) when the THR is loaded by the CPU, or if the transmitter is disabled via command register bit CR0.  2. When the receiver holding register (RHR) has a character ready to be read by the CPU. This corresponds to assertion of status bit SR1. If this is the only condition asserting the output, the output will be negated (high) when the RHR is read by the CPU, or if the receiver is disabled via command register bit CR2.  3. When the transmitter has completed serialization of the last character loaded by the CPU. This corresponds to asserting the output, the output will be negated (high) when the THR is loaded by the CPU.  4. When a change of state has occurred at the DCD input while either the receiver or the transmitter are enabled. This corresponds to assertion of status bit SR2. If this is the only condition asserting the output, the output, the output will be negated (high) when the THR receiver or the transmitter are enabled. This corresponds to assertion of status bit SR2. If this is the only condition asserting the output, the output will be negated (high) when the status register is read by the CPU. |  |  |

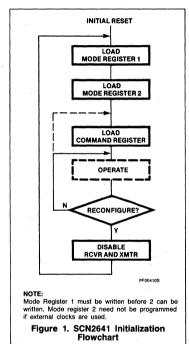

#### **PROGRAMMING**

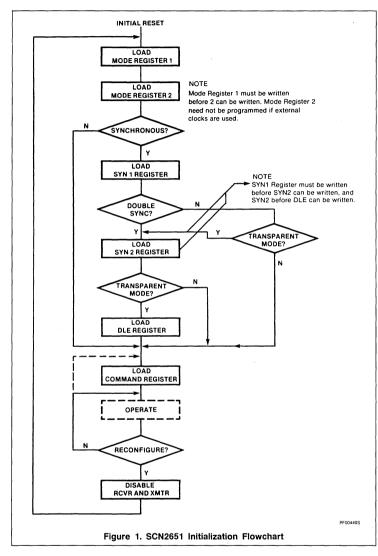

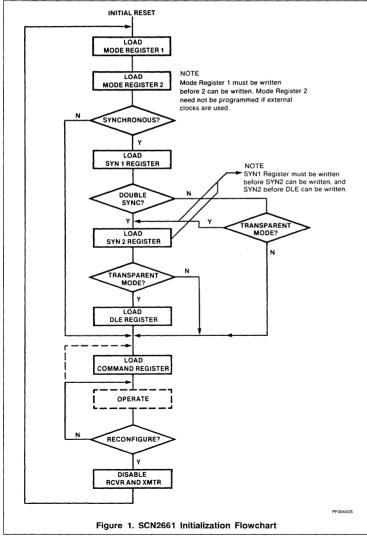

Prior to initiating data communications, the SCN2641 operational mode must be programmed by performing write operations to the mode and command registers. The SCN2641 can be reconfigured at any time during program execution. A flowchart of the initialization process appears in figure 1.

The internal registers of the SCN2641 are accessed by applying specific signals to the  $\overline{\text{CE}}$ ,  $\overline{\text{R}}/\text{W}$ ,  $\text{A}_1$  and  $\text{A}_0$  inputs. The conditions

necessary to address each register are shown in table 4.

Reading or loading the mode registers is done as follows: the first write (or read) operation addresses mode register 1 and a subsequent operation addresses mode register 2. If more than the required number of accesses are made, the internal sequencer recycles to point at the first register. The pointer is reset to mode register 1 by a RESET input or by performing a read com-

mand register operation, but is unaffected by any other read or write operation.

The SCN2641 register formats are summarized in tables 5, 6, 7 and 8. Mode registers 1 and 2 define the general operational characteristics of the SCN2641, while the command register controls the operation within this basic framework. The SCN2641 indicates its status in the status register. These registers are cleared when a RESET input is applied.

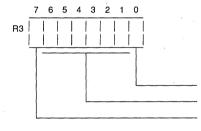

## Mode Register 1 (MR1)

Table 5 illustrates mode register 1. Bits MR11 and MR10 select the baud rate multiplier. 1X, 16X and 64X multipliers are programmable if the external clock input option is selected by MR24 or MR25.

MR13 and MR12 select a character length of 5, 6, 7 or 8 bits. The character length does not include the parity bit, if programmed, and does not include the start and stop bits.

MR14 controls parity generation. If enabled, a parity bit is added to the transmitted character and the receiver performs a parity check on incoming data. MR15 selects odd or even parity when parity is enabled by MR14.

MR17 and MR16 select character framing of 1, 1.5 or 2 stop bits. (If 1X baud rate is

SCN2641

programmed, 1.5 stop bits default to 1 stop bit on transmit.)

The bits in the mode register affecting character assembly and disassembly (MR12 – MR16) can be changed dynamically (during active receive/transmit operation). The character mode register affects both the transmitter and receiver; therefore, character changes should be made when RxEN and TxEN = 0 or when TxEN = 1 and the transmitter is marking in half-duplex mode (RxEN = 0).

To effect assembly/disassembly of the next received/transmitted character, MR12 – MR15 must be changed within n-bit times of the assertion of RxRDY/TxRDY. (n = smaller of the new and old character lengths.)

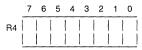

## Mode Register 2 (MR2)

Table 6 illustrates mode register 2. MR23, MR22, MR21 and MR20 control the frequency of the internal baud rate generator (BRG). Sixteen rates are selectable as per table 1. MR23 – MR20 are don't cares if external clocks are selected (MR25 – MR24 = 0). The individual rates are given in table 1.

MR24 – MR27 select the receive and transmit clock source (either the BRG or an external input) and the function at pins 8 and 20. Refer to table 6.

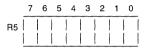

## Command Register (CR)

Table 7 illustrates the command register. Bits CR0 (TxEN) and CR2 (RxEN) enable or disable the transmitter and receiver respectively. If the transmitter is disabled, it will complete the transmission of the character in the transmit shift register (if any) prior to terminating operation. The TxD output will then remain in the marking state (high), while the TxRDY and TxEMT status bits go low. Disabling the receiver causes the RxRDY status bit to go low. If the receiver is disabled, it will terminate operation immediately. Any character being assembled will be negated. A 0-to-1 transition of CR2 will initiate start bit search on the second RxC rising edge following the transition.

Bit CR5 (RTS) controls the RTS output. Data at the output is the logical complement of the register data.

Setting CR3 will force and hold the TxD output low (spacing condition) at the end of the current transmitted character. Normal operation resumes when CR3 is cleared. The user should wait at least one bit time after terminating the break before loading the THR with the next character to be transmitted.

Setting CR4 causes the error flags in the status register (SR3, SR4 and SR5) to be cleared. This is a one-time command. There is no internal latch for this bit.

Table 3. DEVICE-RELATED SIGNALS

| Table 3.      |     |      | IELATED          | SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|-----|------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN<br>NAME   | DIP | PLCC | INPUT/<br>OUTPUT | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                     |

| BRCLK         | 17  | 20   | i                | Clock input to the internal baud rate generator (see table 1). Not required if external receiver and transmitter clocks are used.                                                                                                                                                                                                                                                                            |

| RxC/<br>BKDET | 20  | 25   | 1/0              | Receiver clock. If external receiver clock is programmed, this input controls the rate at which the character is to be received. Its frequency is 1X, 16X or 64X the baud rate, as programmed by mode register 1. Data are sampled on the rising edge of the clock. If internal receiver clock is programmed, this pin can be a 1X/16X clock or a break detect output pin.                                   |

| RxD           | 2   | 3    | į                | Serial data input to the receiver. "Mark" is high, "space" is low.                                                                                                                                                                                                                                                                                                                                           |

| TxC           | 8   | 10   | 1/0              | Transmitter clock. If external transmitter clock is programmed, this input controls the rate at which the character is transmitted. Its frequency is 1X, 16X or 64X the baud rate, as programmed by mode register 1. The transmitted data changes on the falling edge of the clock. If internal transmitter clock is programmed, this pin can be a 1X/16X clock output.                                      |

| TxD           | 16  | 19   | 0                | Serial data output from the transmitter. "Mark" is high, "space" is low. Held in mark condition when the transmitter is disabled.                                                                                                                                                                                                                                                                            |

| DCD           | 14  | 16   |                  | Data carrier detect input. Must be low in order for the receiver to operate. Its complement appears as status register bit SR6. Causes a low output on $\overline{\text{INTR}}$ when its state changes if CR2 or CR0 = 1. If DCD goes high while receiving, the RxC is internally inhibited. Operation of the receiver resumes on the second $\overline{\text{RxC}}$ rising edge following assertion of DCD. |

| CTS           | 15  | 17   | I                | Clear to send input. Must be low in order for the transmitter to operate. If it goes high during transmission, the character in the transmit shift register will be transmitted before termination.                                                                                                                                                                                                          |

| RTS           | 19  | 23   | 0                | General-purpose output which is the complement of command register bit CR5. Normally used to indicate request to send. See Command Register (CR5) for details.                                                                                                                                                                                                                                               |

Table 4. REGISTER ADDRESSING

| abic 4. | I I L                            | ILII AL | DITECOM                           | <b>.</b>                 |  |  |  |  |

|---------|----------------------------------|---------|-----------------------------------|--------------------------|--|--|--|--|

| CE      | CE A <sub>1</sub> A <sub>0</sub> |         |                                   | FUNCTION                 |  |  |  |  |

| 1       | Х                                | X       | Х                                 | Three-state data bus     |  |  |  |  |

| 0       | 0                                | 0       | 0 Read receive holding register   |                          |  |  |  |  |

| 0       | 0                                | 0       | 1 Write transmit holding register |                          |  |  |  |  |

| 0       | 0                                | 1       | 0 Read status register            |                          |  |  |  |  |

| 0       | 0                                | 1       | 1                                 | Invalid                  |  |  |  |  |

| 0       | 1                                | 0       | 0                                 | Read mode registers 1/2  |  |  |  |  |

| 0       | 1                                | 0       | 1 1                               | Write mode registers 1/2 |  |  |  |  |

| 0       | 1                                | 1       | 0 Read command register           |                          |  |  |  |  |

| 0       | 1                                | 1       | 1                                 | Write command register   |  |  |  |  |

|         |                                  |         |                                   |                          |  |  |  |  |

NOTE:

See AC characteristics section for timing requirements.

SCN2641

When CR5 (RTS) is set, the RTS pin is forced low. A 1-to-0 transition of CR5 will cause RTS to go high (inactive) one TxC time after the last serial bit has been transmitted. If a 1-to-0 transition of CR5 occurs while data is being transmitted, RTS will remain low (active) until both the THR and the transmit shift register are empty and then go high one TxC time later.

The SCN2641 can operate in one of four submodes. The operational submode is determined by CR7 and CR6. CR7 – CR6 = 00 is the normal mode, with the transmitter and receiver operating independently in accordance with the mode and status register instructions.

CR7 - CR6 = 01 places the SCN2641 in the automatic echo mode. Clocked, regenerated received data are automatically directed to the TxD line while normal receiver operation continues. The receiver must be enabled (CR2 = 1), but the transmitter need not be enabled. CPU-to-receiver communications continue normally, but the CPU-to-transmitter link is disabled. Only the first character of a break condition is echoed. The TxD output will go high until the next valid start is detected. The following conditions are true while in automatic echo mode:

Data assembled by the receiver are automatically placed in the transmit holding register and retransmitted by the transmitter on the TxD output.

- The transmitter is clocked by the receive clock.

- The INTR pin will reflect only the data set change condition.

- 4. The TxEN command (CR0) is ignored.

Two diagnostic submodes can also be configured. In local loopback mode (CR7 – CR6 = 10), the following loops are connected internally:

- The transmitter output is connected to the receiver input.

- 2. RTS is connected to CTS.

- The receiver is clocked by the transmitter clock.

- 4. The RTS and TxD outputs are held high.

- The CTS, DCD and RxD inputs are ignored.

Additional requirements to operate in the local loopback mode are that CR0 (TXEN), CR1 and CR5 (RTS) must be set to 1. CR2 (RXEN) is ignored by the SCN2641.

The second diagnostic mode is the remote loopback mode (CR7 – CR6 = 11). In this mode:

- Data assembled by the receiver are automatically placed in the transmit holding register and retransmitted by the transmitter on the TxD output.

- The transmitter is clocked by the receive clock.

- No data is sent to the local CPU, but the error status conditions (PE, OE, FE) are set.

- The INTR output is held high.

- 5. CR0 (TxEN) is ignored.

- 6. All other signals operate normally.

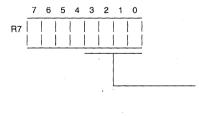

# Status Register

The data contained in the status register (as shown in table 8) indicate receiver and transmitter conditions and modem/data set status.

SR0 is the transmitter ready (TxRDY) status bit. It is valid only when the transmitter is enabled. If equal to 0, it indicates that the transmit holding register has been loaded by the CPU and the data has not been transferred to the transmit shift register. If set equal to 1, it indicates that the holding register is ready to accept data from the CPU. This bit is initially set when the transmitter is enabled by CR0, unless a character has previously been loaded into the holding register. It is not set when the automatic echo or remote loopback modes are programmed. When this bit is set, the INTR output pin is low, except in the automatic echo and remote loopback modes.

SR1, the receiver ready (RxRDY) status bit, indicates the condition of the receive data holding register. If set, it indicates that a character has been loaded into the holding register from the receive shift register and is ready to be read by the CPU. If equal to 0, there is no new character in the holding register. This bit is cleared when the CPU reads the receive data holding register or when the receiver is disabled by CR2. When set, the INTR output is low.

Table 5. MODE REGISTER 1 (MR1)

| MR17                                                  | MR16                               | MR15                | MR14                        | MR13                                 | MR12             | MR11         | MR10                                       |

|-------------------------------------------------------|------------------------------------|---------------------|-----------------------------|--------------------------------------|------------------|--------------|--------------------------------------------|

| Stop Bit                                              | Stop Bit Length Parity Type Parity |                     |                             |                                      | acter<br>igth    |              | nd Baud<br>Factor                          |

| 00 = Invalid<br>01 = 1 sto<br>10 = 1½ s<br>11 = 2 sto | p bit<br>top bits                  | 0 = Odd<br>1 = Even | 0 = Disabled<br>1 = Enabled | 00 = 8<br>01 = 6<br>10 = 1<br>11 = 8 | 6 bits<br>7 bits | 01 =<br>10 = | Invalid<br>1X rate<br>16X rate<br>64X rate |

#### NOTE

Baud rate factor applies only if external clock is selected. Factor is 16X if internal clock is selected.

Table 6. MODE REGISTER 2 (MR2)

|      |     | MR23 - MR20 |       |        |      |     |     |       |         |                           |

|------|-----|-------------|-------|--------|------|-----|-----|-------|---------|---------------------------|

|      | TxC | RxC         | Pin 8 | Pin 20 |      | TxC | RxC | Pin 8 | Pin 20  | Baud Rate Selection       |

| 0000 | Е   | Е           | TxC   | RxC    | 1000 | E   | E   | NF    | RxC/TxC |                           |

| 0001 | Ε   | 1           | TxC   | 1X     | 1001 | Ε   | 1   | TxC   | BKDET   |                           |

| 0010 | 1   | Ε           | 1X    | RxC    | 1010 | 1   | Ε   | NF    | RxC     |                           |

| 0011 | 1   | 1.          | 1X    | 1X     | 1011 | 1   | 1   | 1X    | BKDET   | See baud rates in table 1 |

| 0100 | · E | Ε           | TxC   | RxC    | 1100 | Ε   | Ε   | NF    | RxC/TxC |                           |

| 0101 | E   | 1           | TxC   | 16X    | 1101 | E   | l   | TxC   | BKDET   |                           |

| 0110 | 1   | E           | 16X   | RxC    | 1110 | 1   | Ε   | NF    | RxC     |                           |

| 0111 | 1   | 1           | 16X   | 16X    | 1111 | 1   | 1 ' | 16X   | BKDET   |                           |

## NOTES:

E = External clock

NF = No function; output not valid 1X and 16X are clock outputs

i = Internal clock (BRG) 1X and 16

SCN2641

Table 7. COMMAND REGISTER (CR)

| CR7                                                                                                                                              | CR6 | CR5                                                                    | CR4                           | CR3                          | CR2                                 | CR1                           | CR0 |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------|-------------------------------|------------------------------|-------------------------------------|-------------------------------|-----|

| Operating Mode Request To Send                                                                                                                   |     | Reset Error                                                            | Force Break                   | Receive<br>Control<br>(RxEN) |                                     | Transmit<br>Control<br>(TxEN) |     |

| 00 = Normal operation   01 = Automatic echo mode   11 = Remote loopback   11 = Remote loopback   12   13   14   15   15   15   15   15   15   15 |     | 0 = Normal<br>1 = Reset error<br>flags in status<br>register<br>(FE, O | 0 = Normal<br>1 = Force break | 0 = Disable<br>1 = Enable    | Not used. Must be programmed to '1' |                               |     |

Table 8. STATUS REGISTER (SR)

| SR7      | SR6                                                 | SR5                                | SR4                                | SR3                               | SR2                                                                              | SR1                                                                      | SR0                                                                                        |

|----------|-----------------------------------------------------|------------------------------------|------------------------------------|-----------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|          | Data Carrier<br>Detect                              | Framing Error                      | Overrun Error                      | Parity Error                      | TxEMT/DSCHG                                                                      | RxRDY                                                                    | TxRDY                                                                                      |

| Not used | 0 = DCD input<br>is high<br>1 = DCD input<br>is low | 0 = Normal<br>1 = Framing<br>Error | 0 = Normal<br>1 = Overrun<br>Error | 0 = Normal<br>1 = Parity<br>error | 0 =Normal<br>1 =Change in<br>DCD or<br>transmit<br>shift<br>register<br>is empty | 0 = Receive holding register empty 1 = Receive holding register has data | 0 = Transmit<br>holding<br>register<br>busy<br>1 = Transmit<br>holding<br>register<br>busy |

The TxEMT/DSCHG bit, SR2, when set, indicates either a change of state of the  $\overline{\text{DCD}}$  input (when CR2 or CR0 = 1) or that the transmit shift register has completed transmission of a character and no new character has been loaded into the transmit data holding register. TxEMT will not go active until at least one character has been transmitted. It is cleared by loading the transmit data holding register. The DSCHG condition is enabled when the TxEN = 1 or RxEN = 1. It is cleared when the status register is read by the CPU. If the status register is read twice and SR2 = 1

while SR6 remains unchanged, then a TxEMT condition exists. When SR2 is set, the  $\overline{\text{INTR}}$  output is low.

SR3, when set, indicates a received parity error when parity is enabled by MR14. This bit is cleared when the receiver is disabled and by a reset error command, CR4.

The overrun error status bit, SR4, indicates that the previous character loaded into the receive holding register was not read by the CPU at the time a new received character was transferred into it. This bit is cleared

when the receiver is disabled and by the reset error command, CR4.

Bit SR5 signifies that the received character was not framed by a stop bit; i.e., only the first stop bit is checked. If RHR = 0 when SR5 = 1, a break condition is present. The bit is reset when the receiver is disabled and when the reset error command is given.

SR6 reflects the condition of the DCD input. A low input sets the status bit and a high input clears it.

SCN2641

# **ABSOLUTE MAXIMUM RATINGS**1

| PARAMETER                                        | RATING       | UNIT |

|--------------------------------------------------|--------------|------|

| Operating ambient temperature <sup>2</sup>       | 0 to +70     | °C   |

| Storage temperature                              | -65 to +150  | °C   |

| All voltages with respect to ground <sup>3</sup> | -0.5 to +6.0 | V    |

# DC ELECTRICAL CHARACTERISTICS<sup>4,5,6</sup>

|                                                 |                       |                                        |     | LIMITS |     |      |  |

|-------------------------------------------------|-----------------------|----------------------------------------|-----|--------|-----|------|--|

|                                                 | PARAMETER             | TEST CONDITIONS                        | Min | Тур    | Max | UNIT |  |

| Input voli                                      | tage                  |                                        |     |        |     | V    |  |

| V <sub>IL</sub>                                 | Low                   |                                        | 1   |        | 0.8 |      |  |

| V <sub>IH</sub>                                 | High                  |                                        | 2.0 |        | }   |      |  |

| Output vo                                       | oltage                |                                        |     |        |     | V    |  |

| V <sub>OL</sub>                                 | Low                   | $I_{OL} = 2.2 \text{mA}$               |     |        | 0.4 | 1    |  |

| V <sub>OL</sub><br>V <sub>OH</sub> <sup>7</sup> | High                  | $I_{OH} = -400 \mu A$                  | 2.4 |        |     |      |  |

| կլ                                              | Input leakage current | V <sub>IN</sub> = 0 to V <sub>CC</sub> |     |        | 10  | μΑ   |  |

| 3-state or                                      | utput leakage current |                                        |     |        |     | μΑ   |  |

| ILH                                             | Data bus high         | $V_{O} = 4.0V$                         |     | }      | 10  |      |  |

| الد                                             | Data bus low          | $V_{O} = 0.45V$                        |     |        | 10  |      |  |

| lcc                                             | Power supply current  |                                        |     |        | 150 | mA   |  |

# **CAPACITANCE** $T_A = 25$ °C, $V_{CC} = 0$ V

| DADAMETED                                                                               | TECT COMPLETIONS                            |     |     |                |      |

|-----------------------------------------------------------------------------------------|---------------------------------------------|-----|-----|----------------|------|

| PARAMETER                                                                               | TEST CONDITIONS                             | Min | Тур | Max            | UNIT |

| Capacitance C <sub>IN</sub> Input C <sub>OUT</sub> Output C <sub>I/O</sub> Input/Output | fc = 1MHz<br>Unmeasured pins tied to ground |     |     | 20<br>20<br>20 | pF   |

SCN2641

# AC ELECTRICAL CHARACTERISTICS $T_A = 0^{\circ}C$ to $+70^{\circ}C$ , $V_{CC} = 5.0V \pm 5\%^{4,5,6}$