# 8X300 DESIGN GUIDE

# 8X300 DESIGN GUIDE

December 1980

Bipolar LSI Division SIGNETICS Corporation

SIGNETICS<sup>®</sup> reserves the right to make changes in the products contained in this book in order to improve design or performance and to supply the best possible products. Signetics also assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and Signetics makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of Signetics is prohibited.

©Copyrighted by Signetics Corporation November 1980

.

DSPG Document No. 80-102

#### Preface

The Signetics  $8\times300$  Design Guide is intended to supply the design engineer with a concentration of valuable and, in some cases, previously unpublished information relative to the implementation of systems using the Signetics  $8\times300$  Microcontroller and its compatible devices.

The material contained within this handbook is arranged in such a manner as to provide the user with the following:

- 1. An overview of the 8X300 family as a state-of-the-art design tool.

- 2. Tutorial information relative to the operation and use of the Signetics 8×300 Microcontroller and its compatible devices.

Additional information necessary for the design of systems utilizing the Signetics 8X300 Microcontroller may be obtained from the following Signetics documents:

- Signetics 8X300 Programming Manual

- . Signetics Microcontroller Cross Assembly Program Manual

- . Signetics Data Sheets for specific devices to be used

# CONTENTS

| Chapter |         |         |                                   | Page |

|---------|---------|---------|-----------------------------------|------|

|         | Preface | ••••    |                                   | • i  |

| 1.0     | 8×300 F | AMILY   | AS STATE-OF-THE-ART DESIGN TOOLS  | .1-1 |

|         | 1.1     | INTRO   | DUCTION                           | 1-2  |

|         | 1.2     | DESIGN  | ADVANTAGES OF THE SIGNETICS 8X300 |      |

|         |         | MICRO   | CONTROLLER                        | 1-4  |

|         | 1.3     | DESIGN  | CONSIDERATIONS                    | 1-5  |

| 2.0     | THEOR   | y of op | ERATION                           | 2-1  |

|         | 2.1     | CPU AI  | RCHITECTURE                       | 2-3  |

|         |         | 2.1.1   | Decode and Control Logic          | 2-3  |

|         |         | 2.1.2   | Arithmetic Logic Unit             | 2-4  |

|         |         | 2.1.3   | Program Address Logic             | 2-5  |

|         |         | 2.1.4   | Bus Structure and Control         | 2-7  |

|         |         | 2.1.5   | Internal Working Storage          | 2-9  |

|         |         | 2.1.6   | Bit Manipulation Logic            | 2-10 |

|         |         | 2.1.7   | Oscillator                        | 2-13 |

|         | 2.2     | SIGNET  |                                   | 2-16 |

|         |         | 2.2.1   | Instruction Cycle                 | 2-16 |

|         |         | 2.2.2   | Timing Calculations               | 2-22 |

|         | 2.3     | THE 8×  | (300 INSTRUCTION SET              | 2-31 |

|         | 2.4     | INTERF  | ACE PRINCIPLES                    | 2-33 |

|         |         | 2.4.1   | Memory Interface                  | 2-34 |

|         |         | 2.4.2   | I/O Interface                     | 2-40 |

|         |         | 2.4.3   | Data Conversion                   | 2-42 |

# CONTENTS

| Chapter  |     |       | Page                                             |

|----------|-----|-------|--------------------------------------------------|

|          | 2.5 | 8×300 | INTERRUPT STRUCTURE2-47                          |

|          |     | 2.5.1 | Execute and Return Decoding                      |

|          |     | 2.5.2 | Interrupt Control (Handshake)                    |

|          |     | 2.5.3 | Interrupt Control (Edge and Strobe)              |

|          |     | 2.5.4 | Return Address Register and Interrupt Vector2-54 |

|          |     | 2.5.5 | IVL, IVR Storing Logic2-55                       |

|          |     | 2.5.6 | Priority Interrupt Levels                        |

|          |     |       |                                                  |

|          |     |       |                                                  |

| Annendix | Δ   | 8×300 |                                                  |

| Appendix A | 8X300 FAMILY DATA SHEETSA-1 |

|------------|-----------------------------|

| Appendix B | PROGRAMMING FORMATSB-1      |

# LIST OF TABLES

# TABLE

# PAGE

11111

| 2-2 Crystal Specifications2-14                |

|-----------------------------------------------|

| 2-3 8×300 A.C. Electrical Characteristics2-19 |

| 2-4 Bit Manipulation Functions                |

| 2-5 8X300 Compatible Devices                  |

## LIST OF ILLUSTRATIONS

# FIGURE

| 1-1  | 8×300 Family1-3                                                    |

|------|--------------------------------------------------------------------|

| 1-2  | Typical System Block Design1-5                                     |

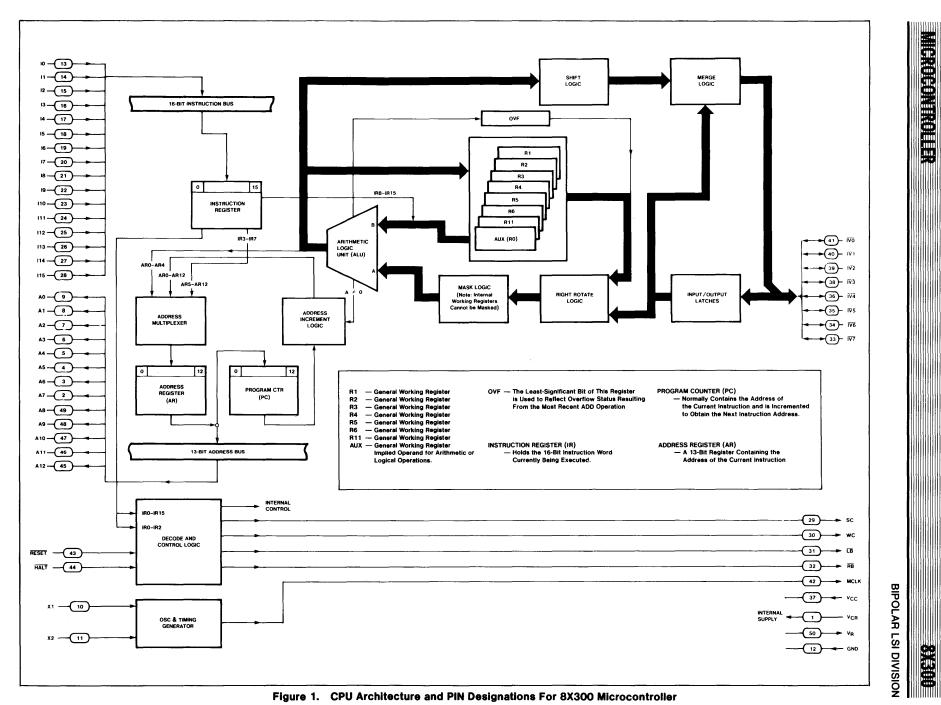

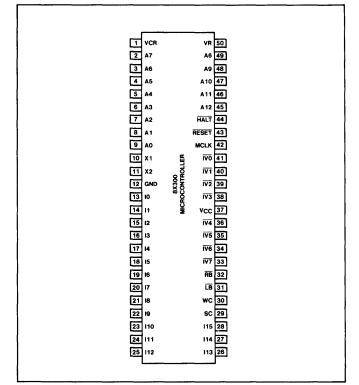

| 2-1  | CPU Architecture and Pin Designations for<br>8X300 Microcontroller |

| 2-2  | Decode and Control Inputs and Outputs                              |

| 2-3  | ALU Data Inputs and Outputs                                        |

| 2-4  | Program Address Logic Data Flow                                    |

| 2-5  | Simple Control System2-9                                           |

| 2-6  | Instruction Cycle2-10                                              |

| 2-7  | Mask Function2-11                                                  |

| 2-8  | Shift and Merge Functions                                          |

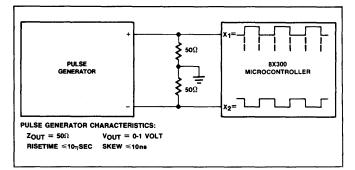

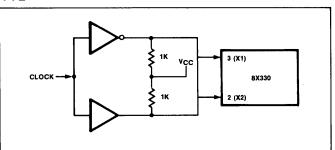

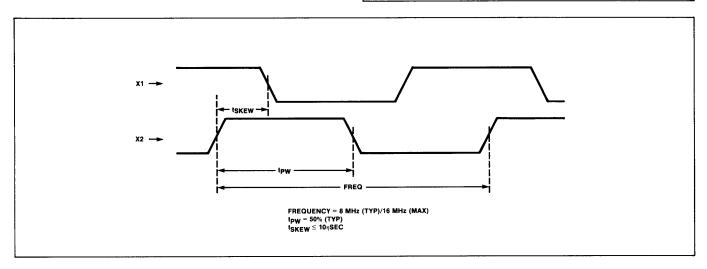

| 2-9  | Pulse Generator Clocking2-15                                       |

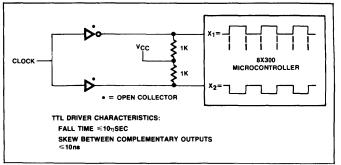

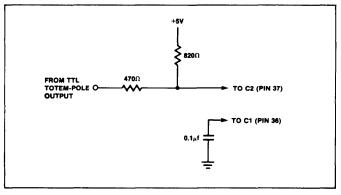

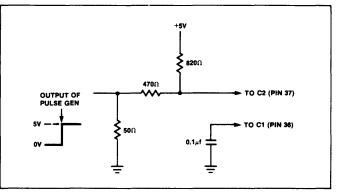

| 2-10 | TTL Clocking2-15                                                   |

| 2-11 | 8X300 Detailed Block Diagram2-17                                   |

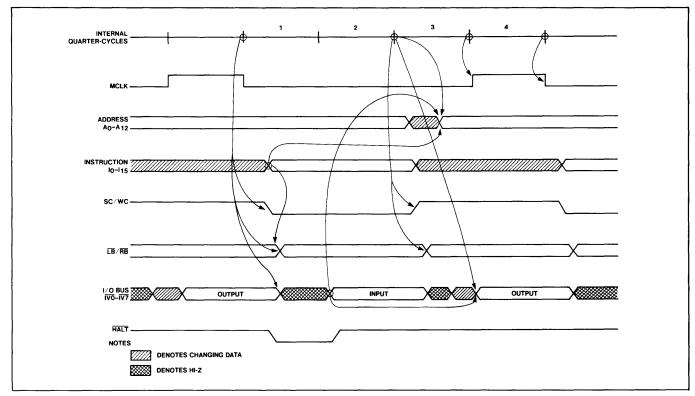

| 2-12 | 8X300 Instruction Cycle Timing2-18                                 |

| 2-13 | Internal Timing Generator                                          |

| 2-14 | Internal Timing for 250 nS Instruction Cycle2-21                   |

| 2-15 | 8X300 Timing Relationships2-22                                     |

| 2-16 | LB/RB Enable Paths2-24                                             |

| 2-17 | HALT Timing2-25                                                    |

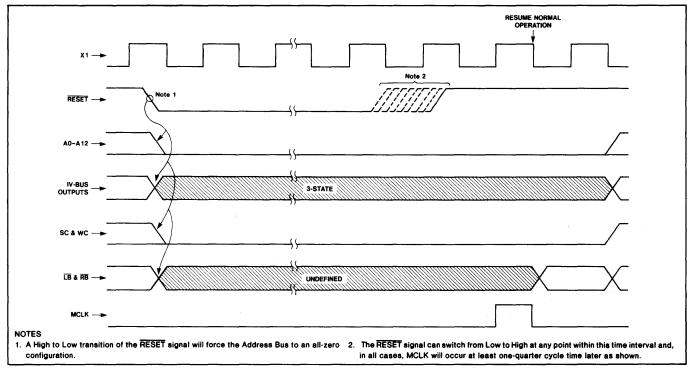

| 2-18 | RESET Timing2-26                                                   |

| 2-19 | Constraints of 8X300 Instruction Cycle Time2-29                    |

| 2-20 | Elongated Positive Cycle Clock                                     |

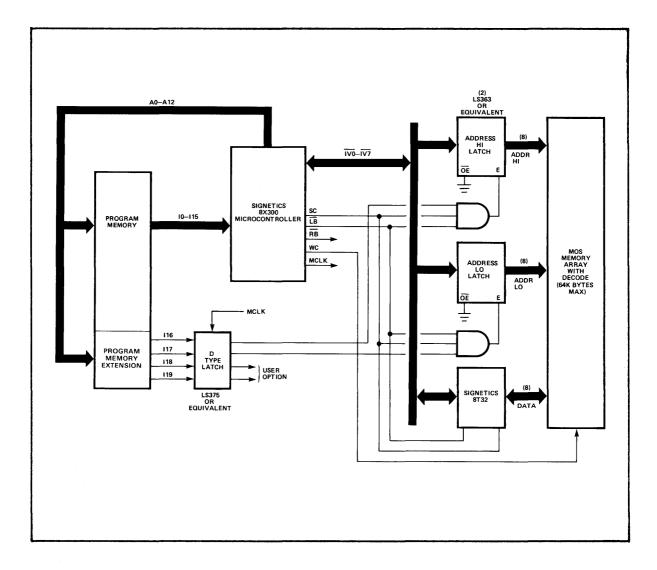

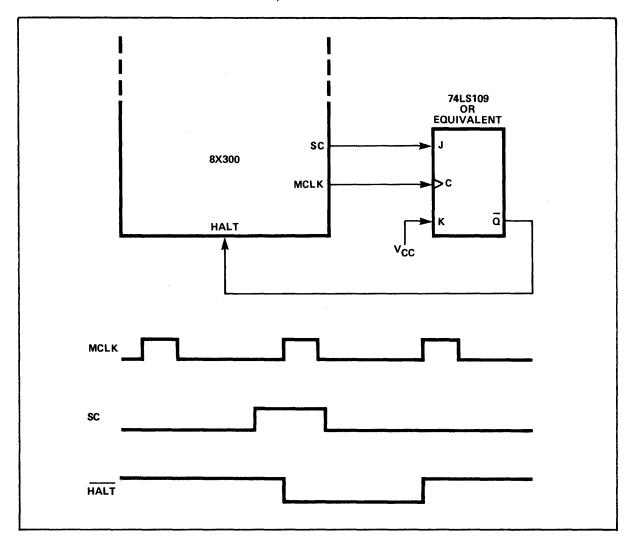

| 2-21 | Extended Microcode Select2-37                                      |

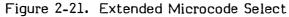

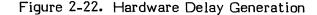

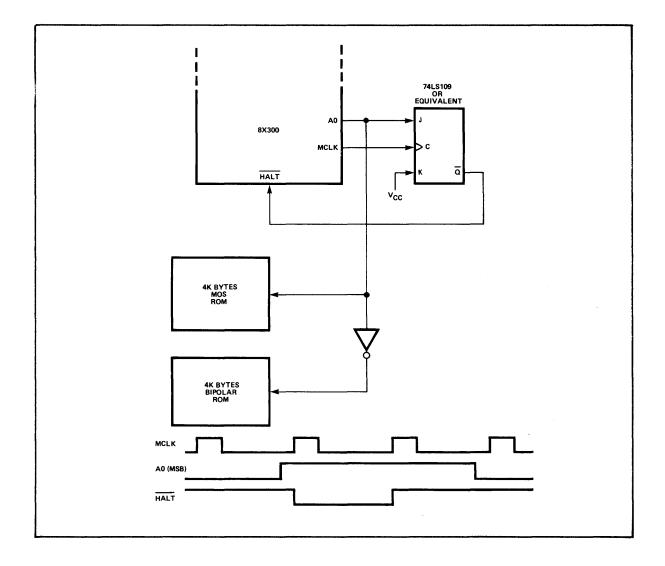

| 2-22 | Hardware Delay Generation                                          |

| 2-23 | Hardware Delay Generation With Program                             |

|      | Storage Partitioning2-39                                           |

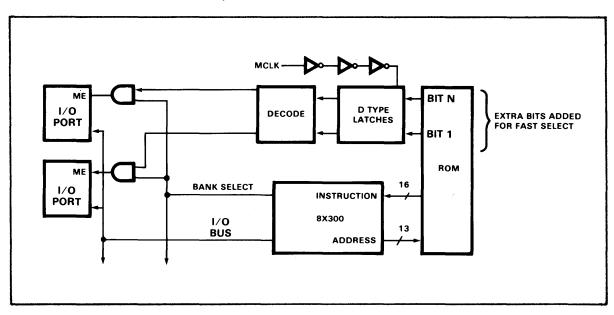

| 2-24 | Fast I/O Select For Small Systems                                  |

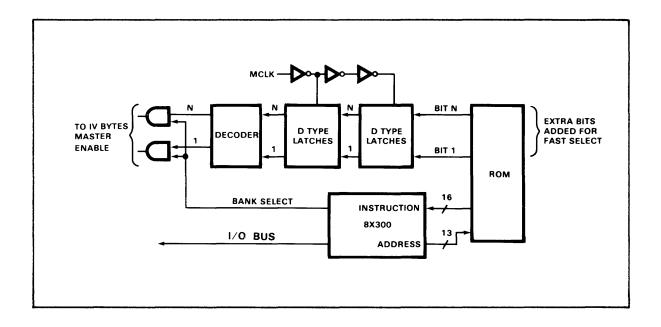

| 2-25 | Fast I/O Select For Large Systems                                  |

|      |                                                                    |

| ,      | LIST OF ILLUSTRATIONS (Cont.)                                |

|--------|--------------------------------------------------------------|

| FIGURE | PAGE                                                         |

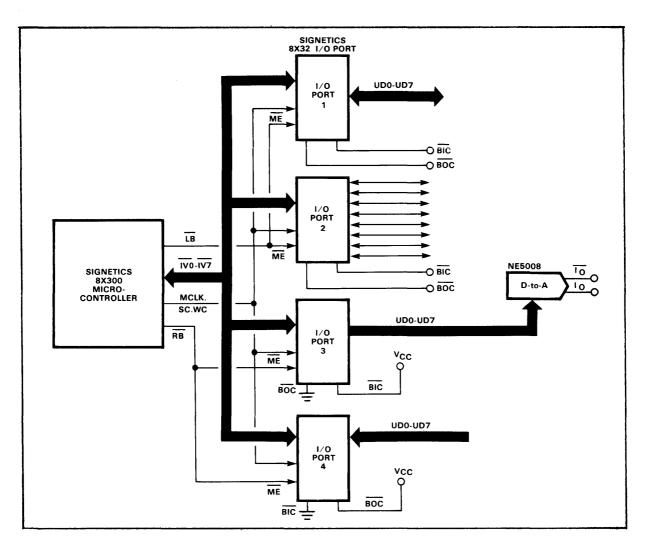

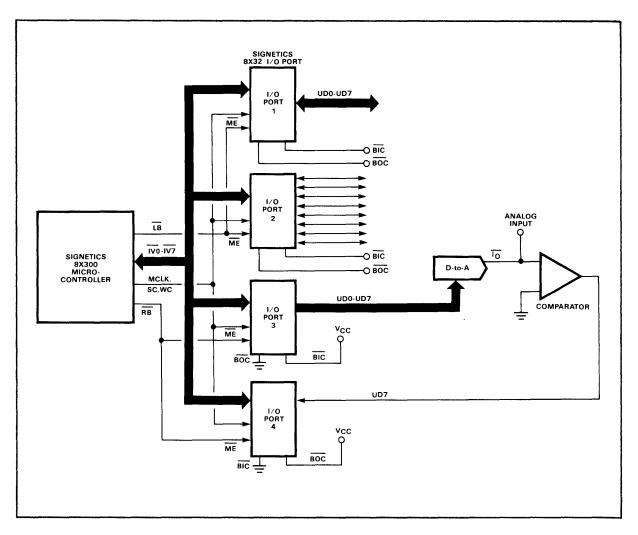

| 2-26   | Digital-To-Analog Converter Configuration 2-44               |

| 2-27   | Successive-Approximation Analog-to-Digital                   |

|        | Converter Configuration                                      |

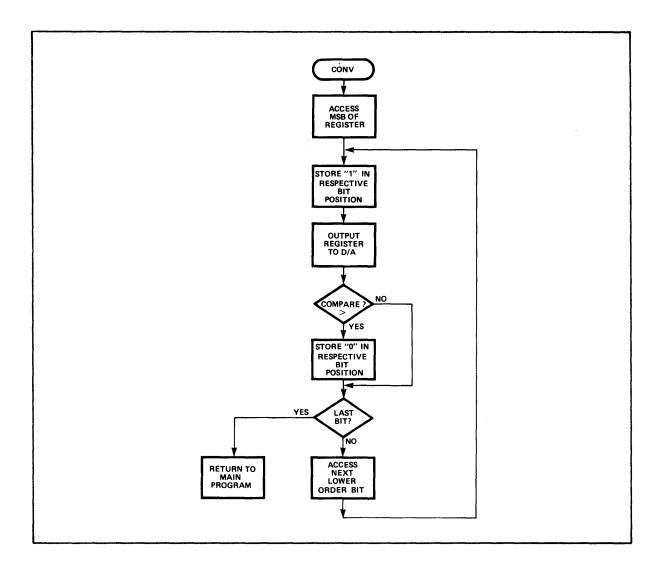

| 2-28   | Sucessive-Approximation Flowchart                            |

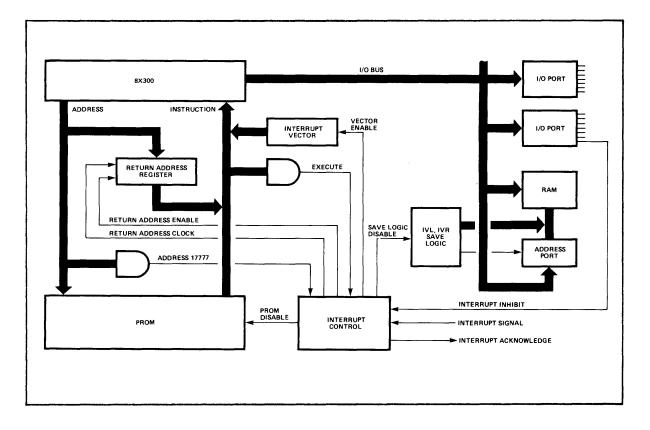

| 2-29   | Typical Interrupt Block Diagram                              |

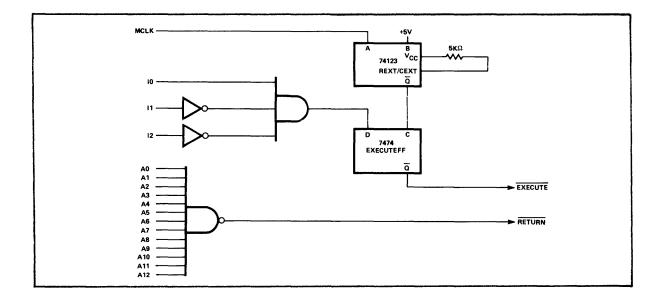

| 2-30   | Execute and Return Decoding                                  |

| 2-31   | Interrupt Control (Handshake)                                |

| 2-32   | Interrupt Control (Edge and Strobe)                          |

| 2-33   | Handshake Timing                                             |

| 2-34   | Edge and Strobe Timing                                       |

| 2-35   | Return Address Register                                      |

| 2-36   | Interrupt Vector Logic • • • • • • • • • • • • • • • • • • • |

| 2-37   | IVL, IVR Storage Logic                                       |

| 2-38   | Priority Interrupt Level Logic                               |

|        |                                                              |

,

1.0 8X300 FAMILY AS STATE-OF-THE-ART DESIGN TOOLS

#### 1.1 INTRODUCTION

The Signetics 8×300 Microcontroller is a high-speed 8-bit bipolar microprocessor, fabricated using Schottky technology. The device is capable of executing (fetch, decode and execute) a 16-bit instruction in one machine cycle (a minimum of 250 nanoseconds), with a maximum power consumption of less than 2.5 watts. The 8×300 architecture and instruction set are designed to provide a high data throughput with bit-oriented, rather than word-oriented operations. This allows the designer a considerable degree of flexibility in control applications. Under program control, the microprocessor is able to select and test individual bits or groups of bits, make calculations and decisions based upon the selected data, and issue appropriate commands to the system.

Because of its high speed, the 8X300 is able to perform, through software, many operations that would otherwise have to be performed by additional hardware. The resultant lower parts count means less handling and inventory, reduced assembly and testing, lower power consumption and improved reliability.

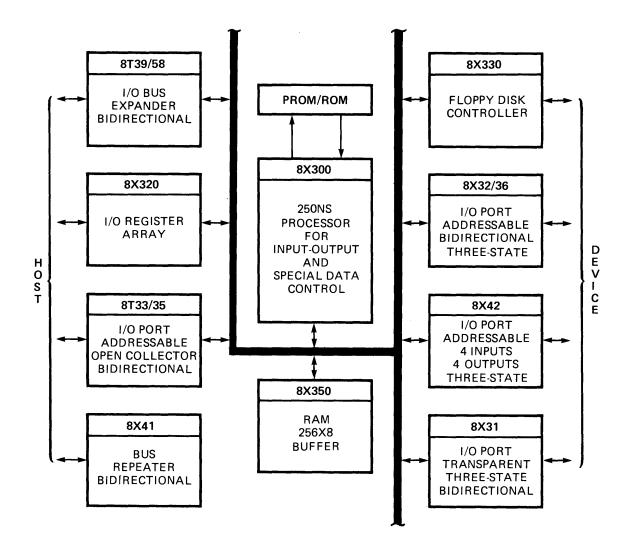

For more complex applications, Signetics offers a broad range of  $8\times300$  family and compatible devices. These devices are illustrated in Figure 1-1, and further information relative to them may be obtained through the offices listed in the back of this manual.

Figure 1-1. 8X300 Family and Compatible Devices

#### 1.2 DESIGN ADVANTAGES OF THE SIGNETICS 8X300 MICROCONTROLLER

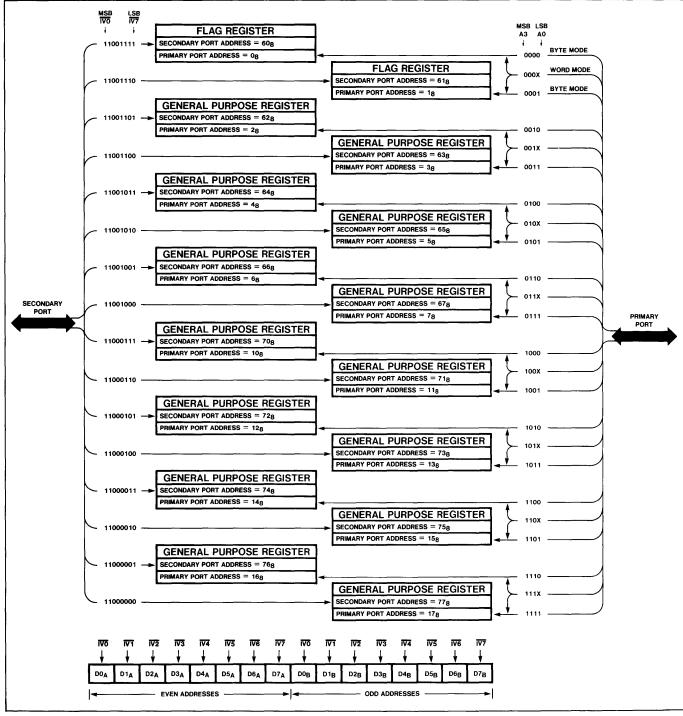

The Signetics 8×300 Microcontroller comprises three separate buses: a non-multiplexed 13-bit Instruction Address bus, a non-multiplexed 16-bit Instruction Data bus, and a multiplexed 3-state, 8-bit I/O bus. This dedicated bus structure contributes to the speed and flexibility of the device by allowing more actions to overlap. In brief, the 8×300 offers the designer a degree of speed and versatility previously available only with bit-slice architecture.

The  $8\times300$  may select as its data source either the user I/O bus or one of eight internal read/write registers. Previous to performing the instructed function, the designer can manipulate source data using both rotate and mask functions. The results of the instructed function may then be shifted, masked and merged with the original source data prior to output. All of the above-mentioned operations can be totally executed in 250 nanoseconds, accounting for the designers ability to process 1- to 8-bit variables as easily as MOS microprocessors handle byte-oriented data.

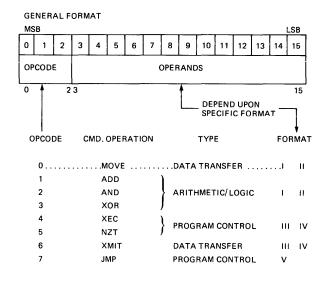

Although the instruction set of the Signetics 8X300 Microcontroller contains only eight major catagories of instructions, a variable operand field within these instructions provides the designer with an extensive set of unique instructions. The inherent simplicity of the instruction set allows several hundred lines of machine code to be written by hand. Where more complex programs are required, a cross assembly program, MCCAP, is available. MCCAP allows the system designer to construct well-documented firmware readily employing all the powerful features of the 8X300 architecture.

The on-chip oscillator and timing generators of the device require only a crystal or single capacitor for reliable operation. If the Signetics  $8\times300$  is to be operated from an external TTL clock, all that is required is an inverting buffer, a non-inverting buffer and two resistors. The device requires only a single plus five-volt power supply for its operation, and its inputs and outputs are TTL.

1

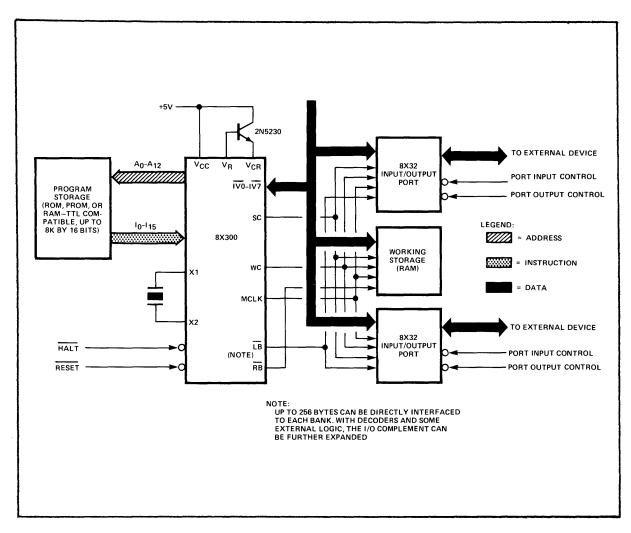

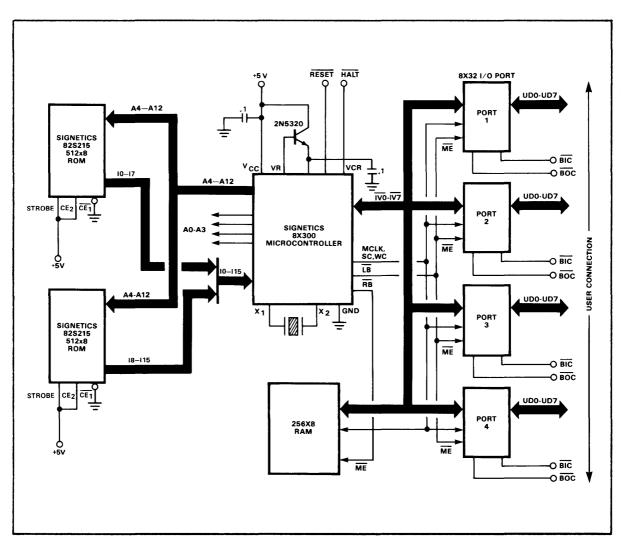

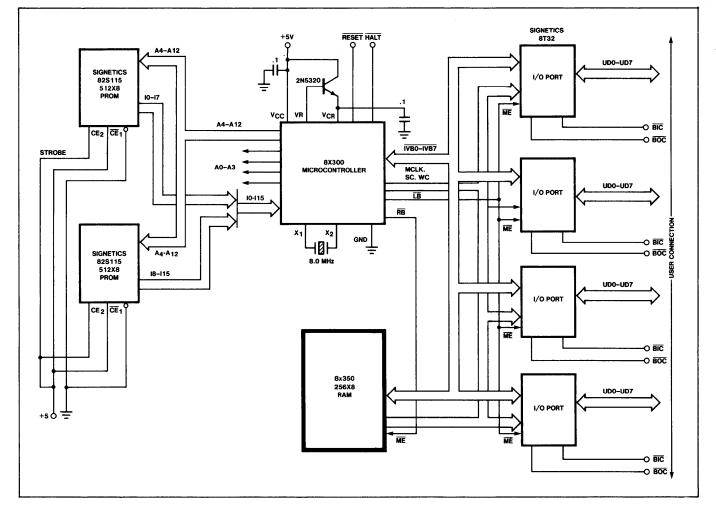

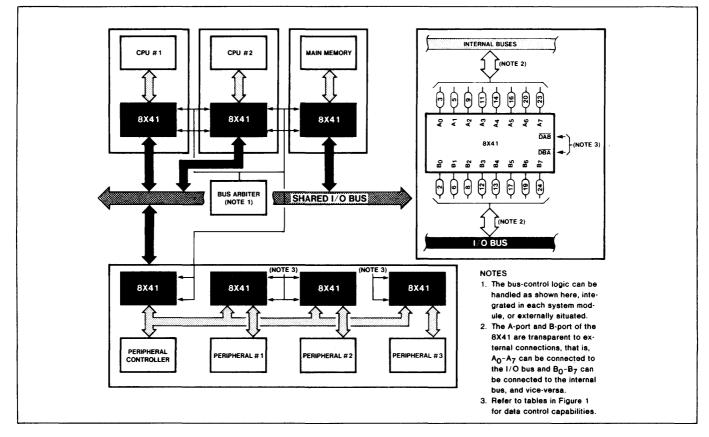

Figure 1-2 illustrates a typical system configuration.

Figure 1-2. Typical System Block Diagram

#### **1.3 DESIGN CONSIDERATIONS**

The Signetics  $8\times300$  Microcontroller moves data at 4 million operations per second, while requiring only minimal support and peripheral circuitry. Where speed is of prime importance, the  $8\times300$ offers an economic alternative to random logic or the bit-slice approach. The device reduces both the complexity and cost usually associated with the above mentioned approaches. Anywhere rapid intelligent control is important -- disk drive controllers, CRT displays, data communications, industrial control -- the  $8\times300$  is an excellent choice.

Signetics offers extensive support for the development of systems employing the  $8\times300$ . The designer will find aids available in the forms of:

- Development Systems

- Training

- Documentation

- . Applications Support

In the area of development systems, Signetics offers an  $8\times300$  Evaluation Kit and an  $8\times300$  Microcontroller Cross Assembly Program (MCCAP).

Training aids include a general introductory movie on the  $8 \times 300$  and the  $8 \times 300$  Training Course, a self-paced audio-visual course.

A wide range of 8×300 Family documentation is available. In addition to application notes and data sheets for specific devices, Signetics offers the following manuals:

- The 8X300 Design Guide

- The 8X300 Programming Manual

- The 8X330 Floppy Disk Controller Manual

- The Microcontroller Cross Assembler Program Manual

During the design phase of a project, the Field Applications Engineer is an invaluable source of advice. They are available to offer on-site technical assistance, and are equipped technically to help analyze your application and transform it into a viable hardware/software system. The Field Applications Engineers are supported by the factory-based Product Applications Engineers, who are also available to answer specific technical questions regarding the use of the Signetics  $8 \times 300$  and its support components.

Additional design tools which are under development and will be released in the near future include -

8X300 In-Circuit Emulator - A hardware development system that converts other development systems and computers into 8X300 development systems.

MDS MCCAP - A version of the  $8\times300$  assembler tailored to execute on the MDS development system.

PDP-11 MCCAP - A version of the 8X300 assembler that executes on PDP-11 and LSI-11 computers.

8X300 Designers Kit - A new version of the current Evaluation Kit which includes writable program storage, an RS232 port, and an key/display panel.

2.0 THEORY OF OPERATION

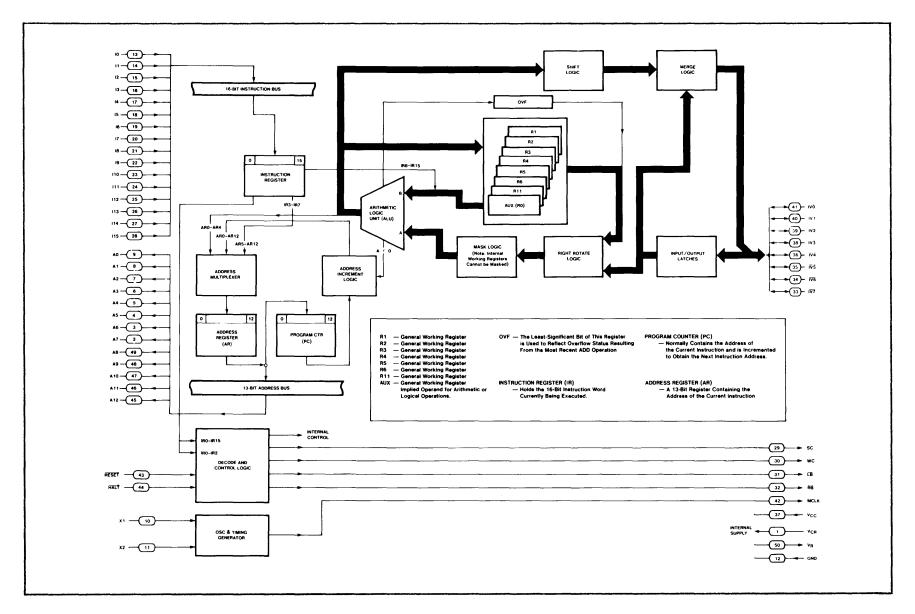

Figure 2-1. Architecture and Pin Designations for 8X300 Microcontroller

2-2

$\sim \ldots \simeq i^{2-m}$

#### 2.1 CPU ARCHITECTURE

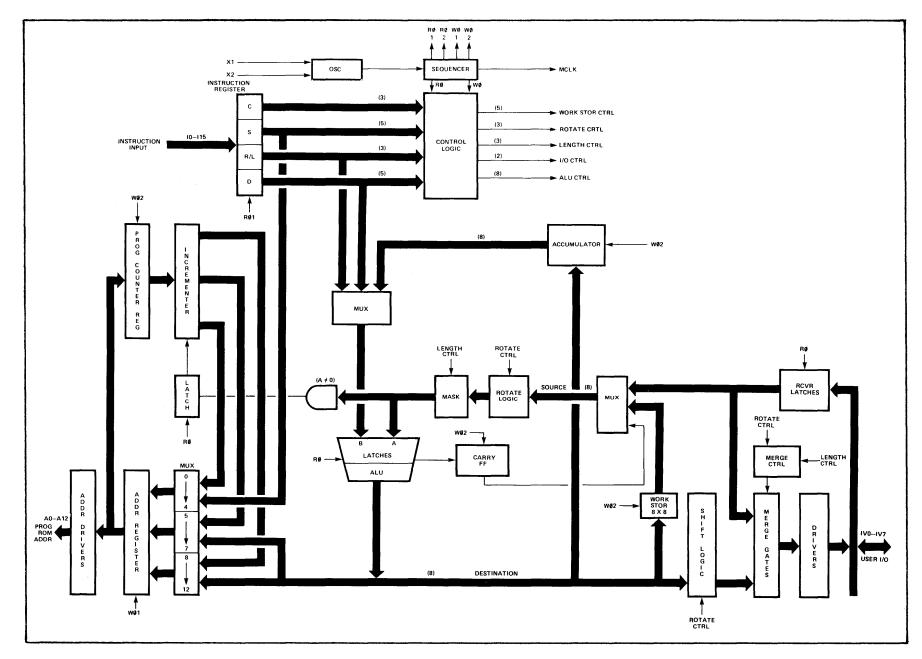

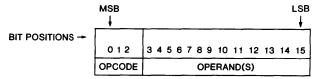

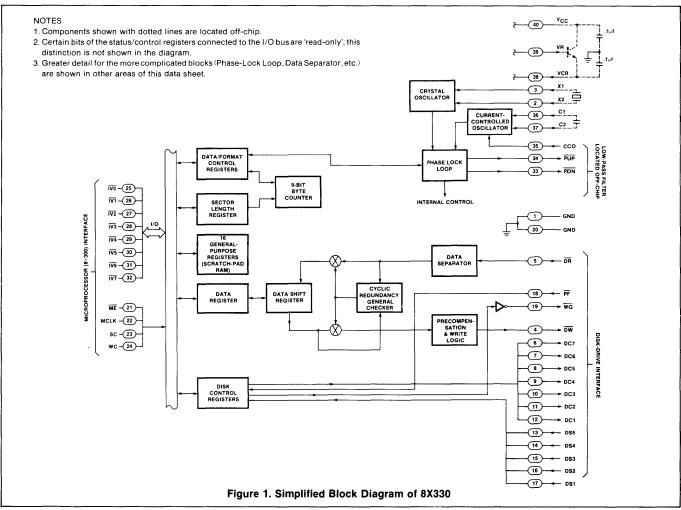

Figure 2-1 is a simplified block diagram of the Signetics 8X300 illustrating the major internal functional blocks and data paths of the device. As is shown in the illustration, the device includes an Arithmetic Logic Unit (ALU), eight 8-bit working registers, logic for rotate and mask of data, logic for shifting and merging of data, decode and control logic, an address register, a program counter and an instruction register.

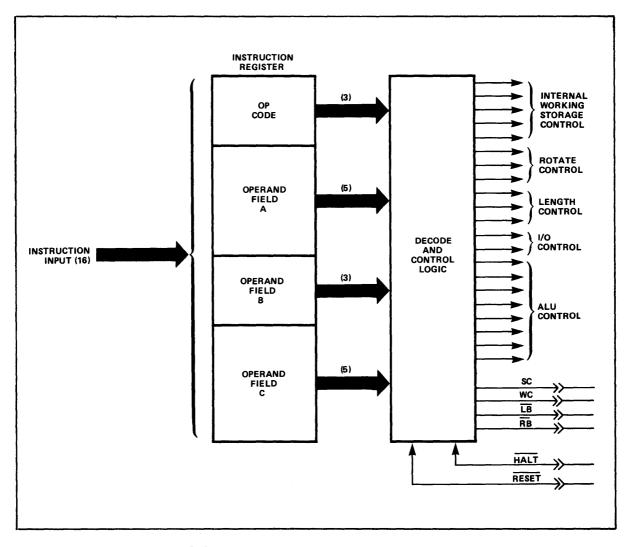

#### 2.1.1 Decode and Control Logic

The decode and control logic contained in the Signetics 8X300 interprets the instruction according to its op code and operand fields, and directs the device to perform the specified operation. Additionally, the decode and control logic provides signals (Select Command, Write Command, Left Bank/Right Bank) to control logic external to the device. Such logic includes RAM and I/O interface to user equipment. As shown in Figure 2-2, the decode and control logic also receives control commands (RESET and HALT) from logic external to the device.

Figure 2-2. Decode and Control Inputs and Outputs

The function of the operand fields vary according to the instruction to be performed. Table 2-1 provides a summary of operand field functions in order of instruction called for. More detailed information on this subject is available in the Signetics  $8\times300$  Programming Manual.

|                                 |                                                | OPERAND FIELD FUNCTION |                   |                     |  |  |

|---------------------------------|------------------------------------------------|------------------------|-------------------|---------------------|--|--|

|                                 | INSTRUCTIONS                                   | A B                    |                   | С                   |  |  |

|                                 |                                                | BITS 3–7               | BITS 8-10         | BITS 11–15          |  |  |

| MOVE<br>ADD<br>AND              | REGISTER TO REGISTER                           | SOURCE ROTATI          |                   | DESTINATION         |  |  |

| XOR                             | REGISTER TO IV BUS ADDRESS                     |                        |                   |                     |  |  |

| MOVE<br>ADD<br>AND<br>XOR       | ADD IV BUS TO REGISTER<br>AND IV BUS TO IV BUS |                        | SOURCE LENGTH DES |                     |  |  |

| XEC<br>NZT                      | REGISTER                                       | SOURCE                 | LOCAL ADDRESS     |                     |  |  |

| XEC<br>NZT                      | IV BUS                                         | SOURCE                 | LENGTH            | LOCAL ADDRESS       |  |  |

| XMIT REGISTER<br>IV BUS ADDRESS |                                                | DESTINATION            | LITERA            | L CONSTANT          |  |  |

|                                 |                                                | DESTINATION            | LENGTH            | LITERAL<br>CONSTANT |  |  |

| JMP                             |                                                | ADDRESS                |                   |                     |  |  |

#### Table 2-1. Operand Field Functions

#### 2.1.2 Arithmetic Logic Unit

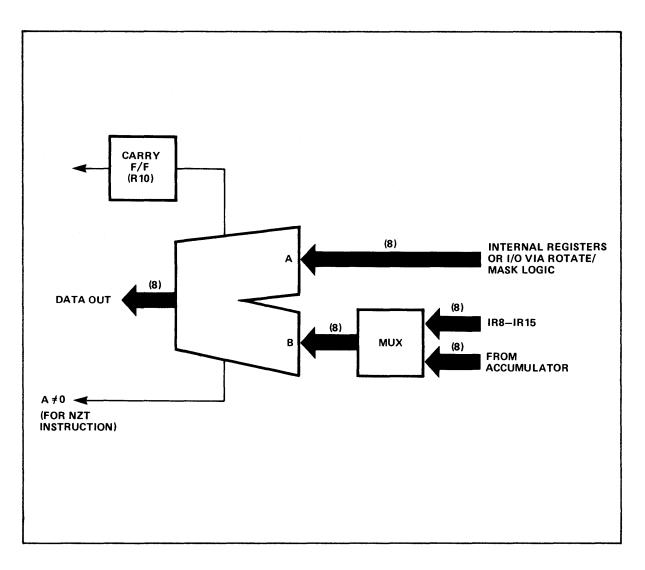

Referring to Figure 2-3, the Arithmetic Logic Unit (ALU) receives its A-bus inputs from internal registers or I/O (through Rotate/Mask logic) and its B-bus inputs from either the Instruction Register (IR8-IR15) or from the Accumulator (a register containing an exact duplicate of the information contained in the Auxiliary Register, RO) via a multiplexer. The ALU performs one of four functions on the data. It may ADD, AND or XOR the A and B input data, or it may pass either input data straight through with no modification (MOVE, XMIT). The output data is then transferred to either the Internal Working Storage registers, the I/O Bus through Shift and Merge logic, or the Program Address logic. The ALU also indicates a carry-out condition during eight bit ADD functions by means of a discrete output to the LSB of the Overflow Register, R10. During NZT instructions the ALU tests for all bits "0" (A $\neq$ 0).

Figure 2-3. ALU Data Inputs and Outputs

2.1.3 Program Address Logic

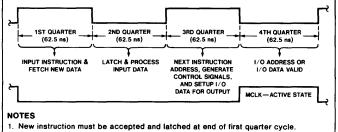

The data flow within the Program address logic is controlled by the transitions of the internal system clock of the 8X300. Each instruction cycle comprises four of these clock transitions, referred to as quarter-cycles.

The Program Address logic data flow is shown in Figure 2-4. When operating with instructions other than Program Control instructions, the Program Counter data is incremented by the Increment logic during the third quarter-cycle. The incremented data then passes through the lower ports of Multiplexers A, B and C, and is loaded into the address Register. During the fourth quarter-cycle this new address is looped back and loaded into the Program Counter.

The above described data flow becomes altered when operating with Program Control instructions (XEC, NZT, JMP). In these cases, the lower five or eight bits of the address are received from the ALU via the upper ports of Multiplexers A and B. In the case of the JMP instruction, the upper five bits of the address are received from the instruction register through the upper ports of Multiplexer C. The JMP instruction is unconditional and is immediately loaded. In the case of the NZT instruction, the source is first tested for non-zero contents. If the non-zero condition  $(A\neq 0)$  exists the new address is loaded, otherwise normal program sequencing continues. The XEC instruction differs in that the new address in the Address Register is not looped back to the Program Counter. The result is that unless a JMP is encountered at the executed instruction, the program sequencing resumes operation at the address following the XEC instruction. That is, the program counter, which still contains the address of the XEC instruction, is incremented as normal.

Figure 2-4. Program Address Logic Data Flow

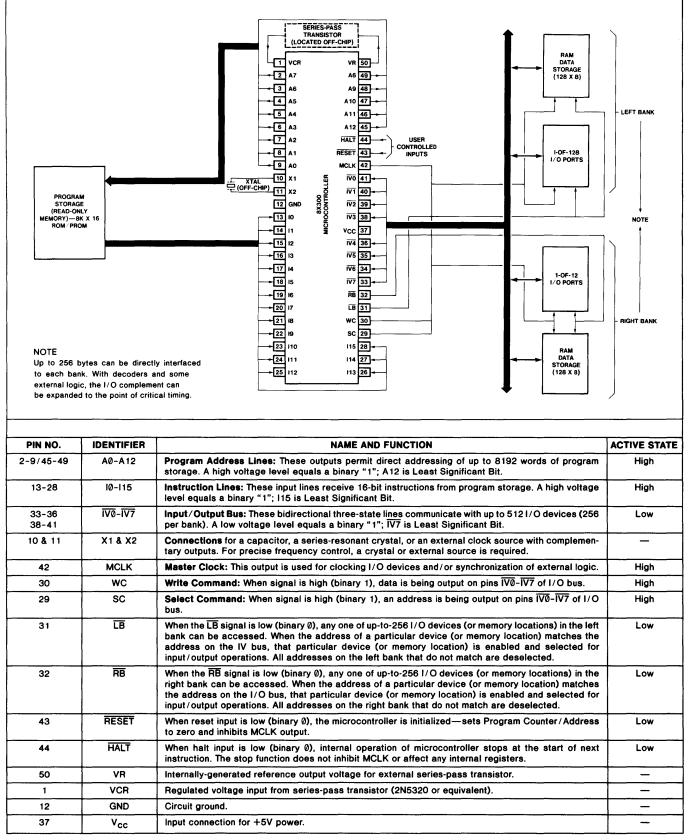

2.1.4 Bus Structure and Control

The 8X300 bus structure, depicted in Figure 2-1, consists of dedicated Instruction and Instruction Address buses. and а multiplexed I/O bus. This bus structure allows direct implementation of a totally independent read only Program Memory of up to 8192 words by 16-bits. The 13-bit Program Control logic allows the order of program execution to be altered by instructions, either unconditionally or under conditions determined from selected data.

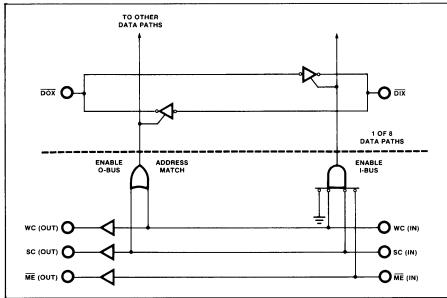

Interface with external working storage (RAM) and user equipment is through the I/O bus. This bus carries either address information or data, and is accompanied by two Data-I/O control lines (WC and SC) which indicate to external circuitry which of the two types of information is on the bus. Ordinarily the 8-bit I/O bus would only be capable of addressing a maximum of 156 bytes of memory and/orI/O registers, but through the use of two additional complementary control lines (LB and RB) this capability has been expanded to a maximum of 512. This is accomplished by grouping the memory-I/O into two banks of 256 bytes and/or devices, and using one control line to select each. It should be noted that only one device per bank may be enabled at any given time. Timing for the external memory and I/O is by means of the MCLK signal from the Signetics 8X300. The five control lines function as follows:

- 1. <u>Select Command (SC)</u> a high (binary 1) on this line indicates that an address is being output on the I/O bus.

- 2. Write Command (WC) a high (binary 1) on this line indicates that data is being output on the I/O bus, to be stored in the previously enabled register/port.

NOTE: When both SC and WC are low (binary 0) the Microcontroller expects data from the selected device. Both SC and WC high (binary 1) is a condition not generated by the Microcontroller.

- 3. Left Bank Select (LB) a low (binary 0) on this line enables one of two groups of I/O devices (or memory locations). In all following text, this group of Memory-I/O devices is referred to as the Left Bank.

- 4. <u>Right Bank Select (RB) a low (binary 0) on this line enables</u> the second of the previously mentioned two groups of I/O devices (or memory locations). In all following text, this group of Memory-I/O devices is referred to as the Right Bank.

NOTE: LB and RB are complementary outputs of a single control line which can be considered as a ninth address bit. Each I/O device (port, memory, etc.) is connected to either the LB or RB control line.

5. Master Clock (MCLK) - an output signal of the Microcontroller used for clocking of I/O devices and/or synchronization of external logic. The I/O bus data must be stable during the period the MCLK is high.

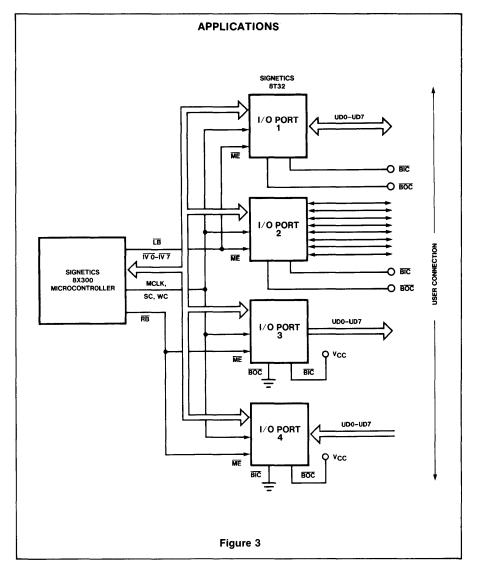

Figure 2-5 illustrates a simple control system composed of the Signetics 8×300 and its compatible devices. The illustration depicts the wiring configuration of the Program Address, Instruction and I/O buses, and the control lines. In this particular application the Left Bank of devices is composed of I/O ports used for interface with user equipment. The Right Bank of devices comprise the system's external Working Storage. Through program control, the Microcontroller is able to input data from one bank of devices, manipulate this data and output it to the opposite bank of devices, all in one instruction cycle (see Figure 2-6). It should be noted thatthe I/O and Memory devices must have been addressed prior to this instruction cycle, and that an operation from one device to another of the same bank is not normally done during a single instruction cycle. It is a simple matter to input data from a specific device, operate on it and output it again to the same device during one instruction cycle.

#### 2.1.5 Internal Working Storage

Internally, the Signetics 8X300 stores data in eight 8-bit read/write registers. These registers include registers R1 through R6, R11 and the Auxiliary register, R0. The Auxiliary register holds one of the operands used in two-operand instructions. As previously mentioned, an exact duplicate of the Auxiliary register data is also maintained in the Accumulator. This allows the Microcontroller to perform operations which use the Auxiliary register data as both operands. Register 10 stores the carry bit from addition operations in its LSB position. Because the LSB is the only bit used, R10 can only have one of two possible values - binary "1" or binary "0".

Figure 2-5. Simple Control System

Figure 2-6. Instruction Cycle

2.1.6 Bit Manipulation Logic

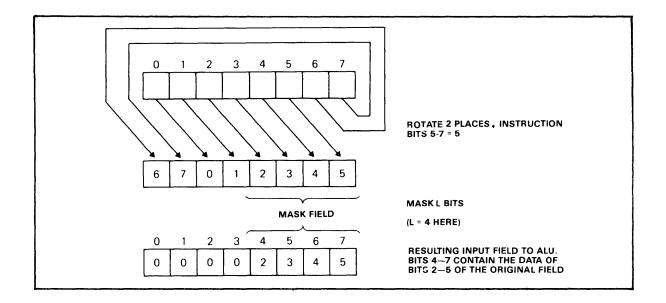

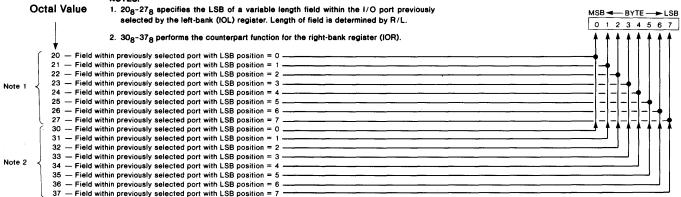

The A input of the ALU is preceded by data-rotate and data-mask logic. The combination of right-rotate and mask functions allows selection of one or more bits from a source data field. For instructions where both the source and destination are internal registers, only the rotate function is available, the data being a fixed length of eight bits.

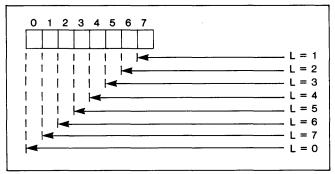

The right-rotate function provides an end-around-shift of one to seven places of the 8-bit source field. In this manner, the least significant bit of the bit string required can be positioned in the least significant position of the data byte, ready for further processing. See Figure 2-7.

Figure 2-7. Mask Function

The number of places that the data is to be rotated is specified by the R operand field, when present, and by instruction bits 5, 6, and 7 when the source is the I/O bus. These bits specify the bit of the source data field which will be rotated to bit position seven before masking.

The mask function allows selection of the least significant L contiguous bits of the rotated I/O bus source data for subsequent processing. The value L is specified by the L operand field of the instruction. After masking, the least significant bits are output to the ALU, with the remaining bits of the byte set to zero.

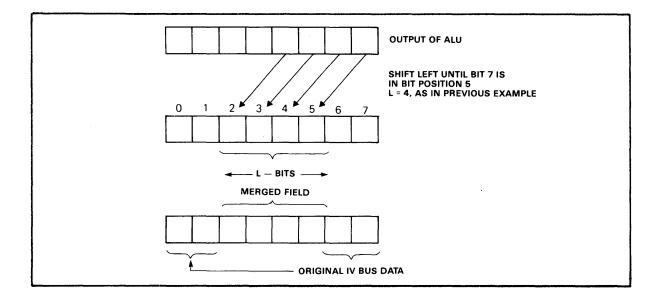

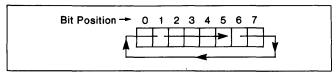

The ALU output is followed by the shift and merge logic. These functions allow alteration of the state of a bit string within the I/O bus data byte. The action of the rotate and mask functions ensures that the required processed data is in the least significant bits of the ALU output; the left shift function then aligns the data in the required bit positions prior to merging. See Figure 2-8.

Figure 2-8. Shift and Merge Functions

Because the process is not an end-around-shift, data shifted from position 0, the MSB, is lost. The number of positions to be shifted is determined by instruction bits 13-15: the data is left shifted until the LSB has reached the bit position specified by instruction bits 13-15.

The merge function allows the user to update part of the existing I/O bus data without affecting the remaining parts of the data byte. The length of the bit string to be merged with the existing data is specified by the L operand field, the LSB of the bit string (after shifting) being specified by instruction bits 13-15.

It must be kept in mind that the I/O bus is "read from" and "written to" only in 8-bit bytes. The eight bits of information is read from the I/O bus and latched into the internal I/O latches of the  $8\times300$ . Some number of bits may then be rotated, masked and shifted as desired. Prior to output to the I/O bus, the desired bits are then merged with the original information still being retained in the internal I/O latches. For this reason, a single bit cannot be read from one device and written to replace just one bit of another device in one instruction cycle.

#### 2.1.7 Oscillator

The  $8 \times 300$  contains an on-chip oscillator which generates all necessary clock signals. The oscillator output frequency may be controlled by any one of four methods:

- 1. External capacitor

- 2. External crystal

- 3. Pulse generator

- 4. TTL clock

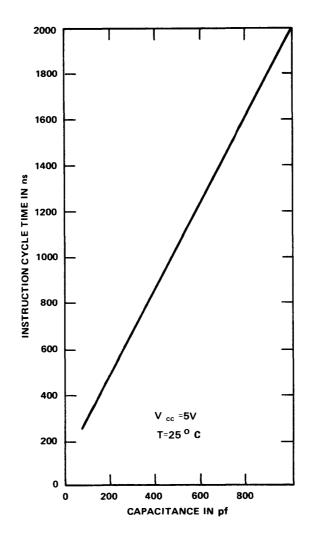

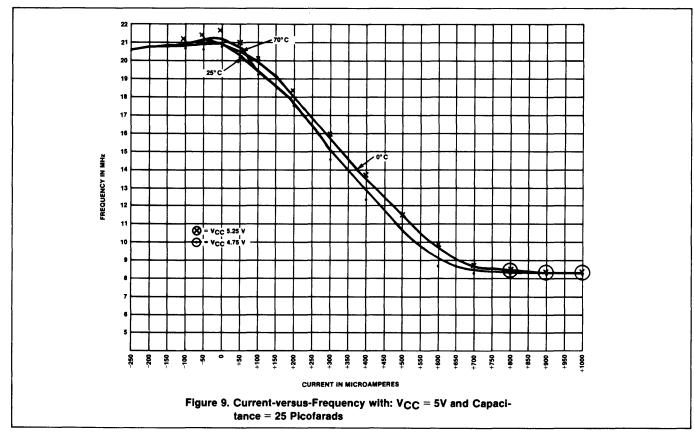

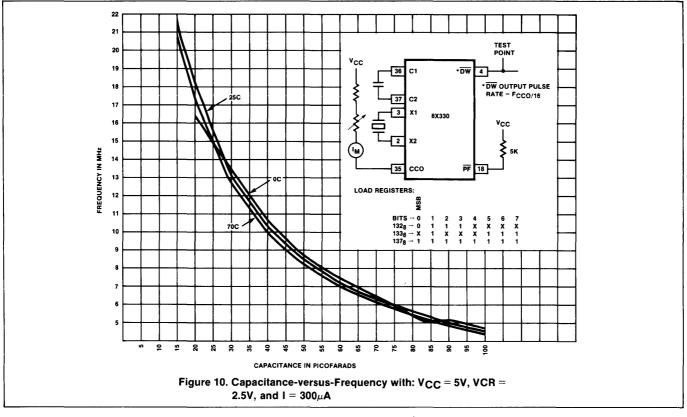

The first control method, an external capacitor, is an imprecise way of controlling the speed of the 8X300, and its use should be restricted to low speed applications. In actual operation, the value of the capacitor may be affected by its environmental conditions. Approximate capacitor values are shown in Graph 2-1.

Graph 2-1. Typical Cycle Time Versus Capacitance

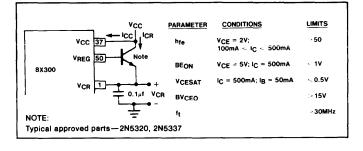

The second, and most desirable, method of oscillator control is implemented through the use of a frequency determining crystal. The oscillator is designed such that its gain decreases as its operating frequency increases. When used with a crystal of the proper characteristics, the oscillator has little or no tendency to operate in a harmonic mode. Because of this, no external components other than the crystal are required for frequency control. Table 2-2 lists the specifications of crystals to be used with the 8X300, and their resonant frequency f in Hertz is related to the desired instruction cycle time T in seconds, by the relationship f =2/T.

For example:

The desired instruction cycle time is 250 nanoseconds, or  $250 \times 10^{-9}$  seconds.

Therefore:

$$\frac{2}{250\times10^{9}} = 8\times10^{6}$$

HZ = 8 MHz.

Table 2-2. Crystal Specifications

| ТҮРЕ              | IMPEDANCE<br>AT FUNDAMENTAL | IMPEDANCE AT<br>HARMONICS AND<br>SPURS |  |  |

|-------------------|-----------------------------|----------------------------------------|--|--|

| FUNDAMENTAL MODE, | 35 OHMS                     | 50 OHMS                                |  |  |

| SERIES RESONANT   | MAXIMUM                     | MINIMUM                                |  |  |

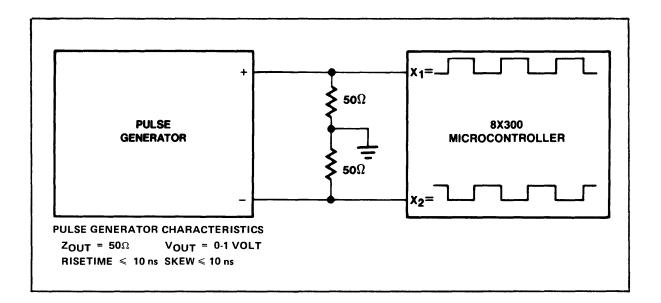

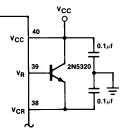

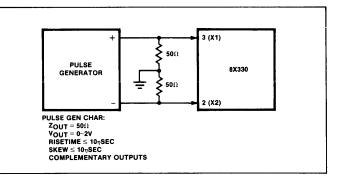

The third method of frequency control is accomplished by driving the oscillator with an external pulse generator. This method is especially useful in applications that require the ability to vary the instruction cycle time. The X1 and X2 inputs of the  $8\times300$  must be connected to the complementary outputs of the pulse generator as shown in Figure 2-9.

Figure 2-9. Pulse Generator Clocking

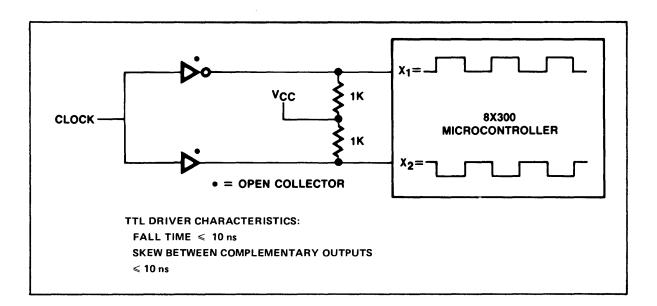

The final method of oscillator control involves driving the oscillator with an external TTL clock. The interfacing of a master TTL clock to the  $8\times300$  is illustrated in Figure 2-10.

Figure 2-10. TTL Clocking

#### 2.2 8X300 TIMING

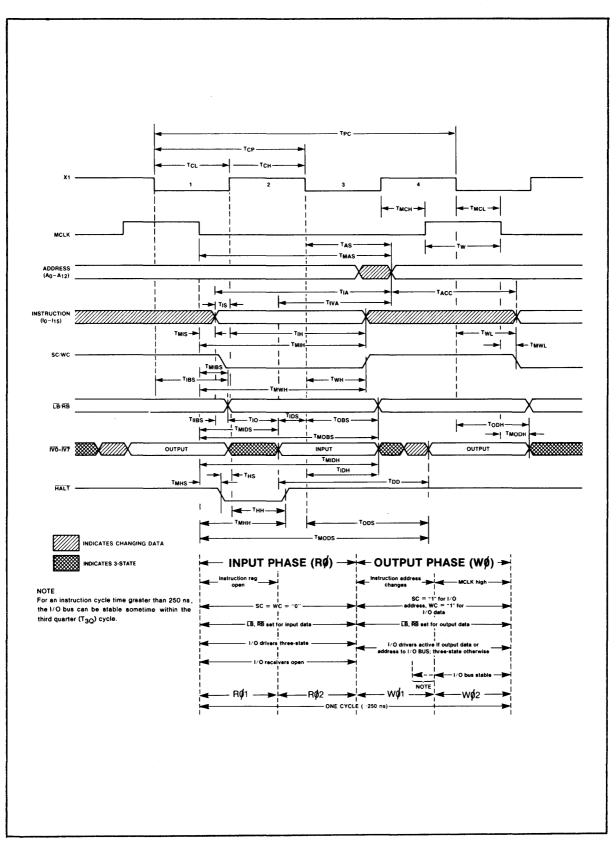

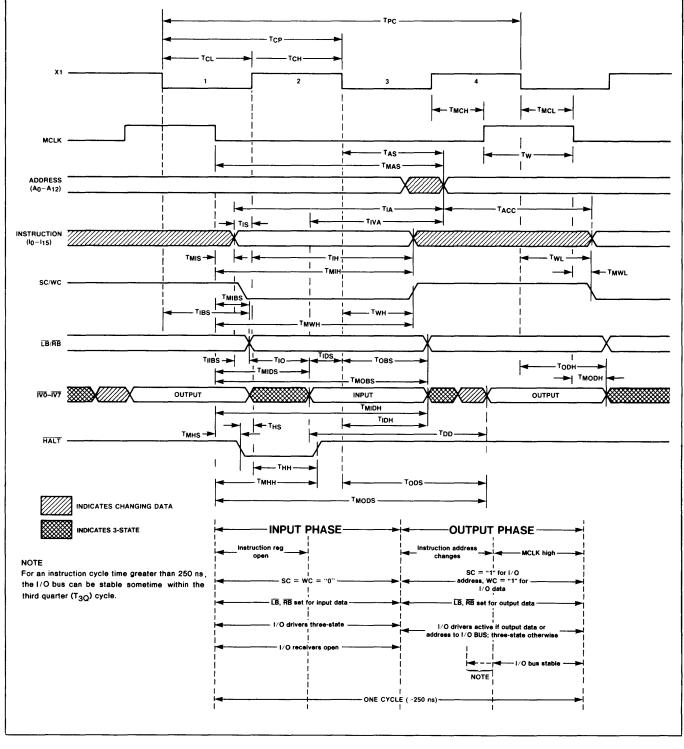

To understand the  $8\times300$  timing, it is necessary to know when the internal latches of the device are open and when they are not. Figure 2-11 is a detailed internal block diagram of the  $8\times300$ , depicting the latches and registers referred to in the discussions that follow in this section of the manual. Figure 2-12 is a timing chart illustrating the actions of these latches and registers throughout an instruction cycle. Table 2-3 describes the timing specifications of the device. It should be noted that all  $8\times300$  internal latches are level triggered.

#### 2.2.1 Instruction Cycle

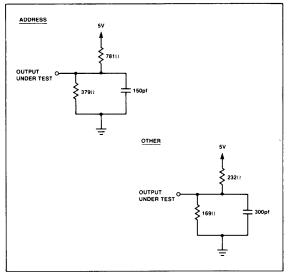

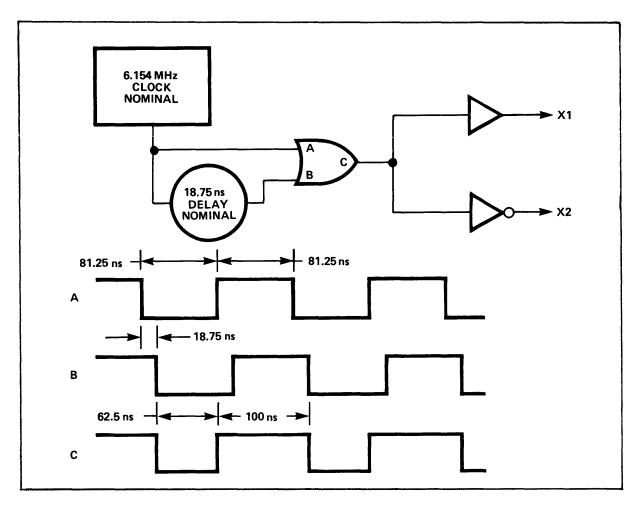

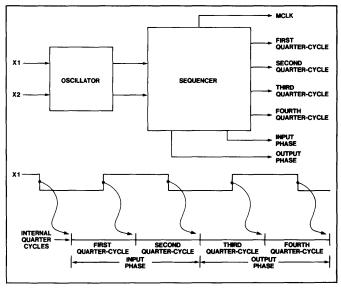

The Internal Timing Generator of the  $8\times300$  is depicted in Figure 2-13. Either an external TTL clock or a crystal may be connected to X1 and X2, the inputs to the device's internal oscillator. In conjunction with the sequencer, the output of this oscillator generates all internal timing-control signals. Figure 2-14 shows the relationship of the internal timing signals to the X1 input.

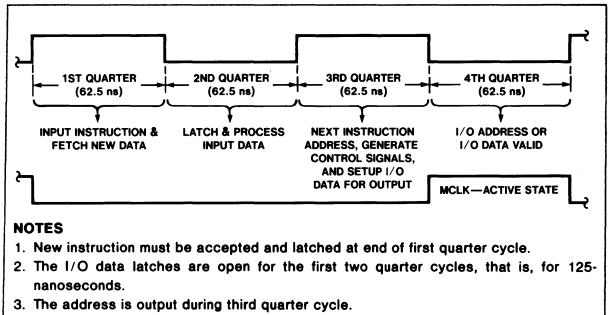

The 8×300 instruction cycle comprises four transitions of the internal system clock. The internal latches are controlled by these transisions, commonly referred to as quarter-cycles. Keep in mind that "quarter-cycles" refer to transitions of the internal system clock, not transitions of X1.

Figure 2-11. 8X300 Detailed Block Diagram

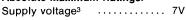

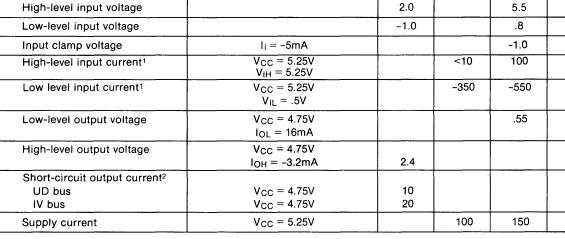

#### Table 2-3. 8X300 AC Electrical Characteristics

#### AC CHARACTERISTICS (Commercial Part) CONDITIONS: $V_{CC} = 5V (\pm 5\%)$ , $V_{IN} = 0V \text{ or } 3V$ , $0^{\circ}C \le T_A \le 70^{\circ}C$ LOADING: (See test circuits)

|       | PARAMETER                                     | LIMITS (INSTRUCTION<br>CYCLE TIME = 250 ns) |     |     | LIMITS (INSTRUCTION<br>CYCLE TIME > 250 ns) |                                         |                                         | UNITS    | COMMENTS                 |

|-------|-----------------------------------------------|---------------------------------------------|-----|-----|---------------------------------------------|-----------------------------------------|-----------------------------------------|----------|--------------------------|

|       | (NOTE 1)                                      | Min                                         | Тур | Max | Min                                         | Тур                                     | Max                                     |          | COMMENIS                 |

| TPC   | Processor cycle time                          | 250                                         |     |     | 250                                         |                                         |                                         | ns       |                          |

| ТСР   | X1 clock period                               | 125                                         |     |     | 125                                         |                                         |                                         | ns       |                          |

| тсн   | X1 clock high time                            | 62                                          |     | L   | 62                                          |                                         |                                         | ns       |                          |

| TCL   | X1 clock low time                             | 62                                          |     | ļ   | 62                                          |                                         |                                         | ns       |                          |

| Тмсн  | MCLK high delay                               | 31                                          | 42  | 52  | 31                                          | 42                                      | 52                                      | ns       |                          |

| TMCL  | MCLK low delay                                | 31                                          | 42  | 52  | 31                                          | 42                                      | 52                                      | ns       |                          |

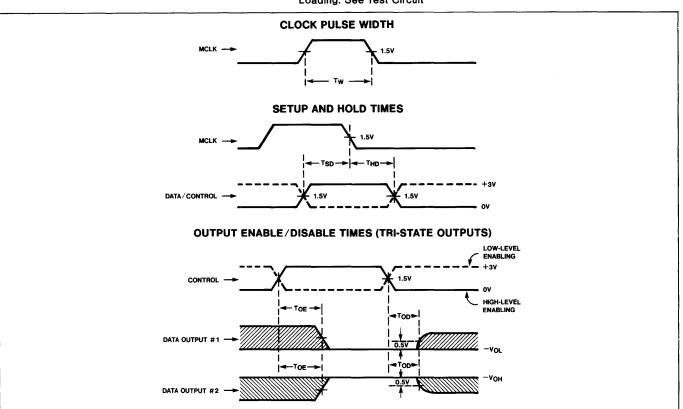

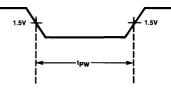

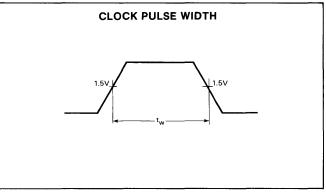

| Tw    | MCLK pulse width                              | 55                                          | 62  | 69  | T <sub>4Q</sub> -7                          | T <sub>4Q</sub>                         |                                         | ns       | Note 2                   |

| TAS   | X1 falling edge to<br>address stable          | 50                                          | 63  | 80  | 50                                          | 63                                      | 80                                      | ns       | Note 7                   |

| TMAS  | MCLK falling edge to<br>address stable        | 130                                         | 143 | 160 | T <sub>1Q</sub> +T <sub>2Q</sub><br>+5      | T <sub>1Q</sub> +T <sub>2Q</sub><br>+18 | T <sub>1Q</sub> +T <sub>2Q</sub><br>+35 | ns       | Notes 2, 3, & 7          |

| TIA   | Instruction to address                        |                                             |     | 170 |                                             |                                         | T <sub>2Q</sub> +108                    | ns       | Notes 2, 3, & 8          |

| TIVA  | input data to address                         |                                             |     | 105 |                                             |                                         | 105                                     | ns       | Notes 3 & 9              |

| TIS   | Instruction set-up time<br>(X1 rising edge)   | -7                                          |     |     | -7                                          |                                         |                                         | ns       | Note 10                  |

| TMIS  | MCLK falling edge to<br>instruction stable    |                                             |     | 20  |                                             |                                         | T <sub>1Q</sub> -42                     | ns       | Notes 2, 4, & 10         |

| TIH   | Instruction hold time (X1 rising edge)        | 45                                          |     |     | 45                                          |                                         |                                         | ns       | Note 11                  |

| тмін  | Instruction hold time)<br>(MCLK falling edge) | 60                                          |     |     | T <sub>1Q</sub> -2                          |                                         |                                         | ns       | Notes 2 & 11             |

| тwн   | X1 falling edge to<br>SC/WC rising edge       | 40                                          | 49  | 58  | 40                                          | 49                                      | 58                                      | ns       |                          |

| тмwн  | MCLK falling edge to<br>SC/WC rising edge     | 125                                         | 130 | 135 | T <sub>1Q</sub> +T <sub>2Q</sub>            | T <sub>1Q</sub> +T <sub>2Q</sub><br>+5  | T <sub>1Q</sub> +T <sub>2Q</sub><br>+10 | ns<br>ns | Note 2                   |

| TWL   | X1 falling edge to<br>SC/WC falling edge      | 40                                          | 49  | 58  | 40                                          | 49                                      | 58                                      | ns       |                          |

| TMWL  | MCLK falling edge to<br>SC/WC falling edge    | 5                                           | 7   | 15  | 5                                           | 7                                       | 15                                      | ns       |                          |

| TIBS  | X1 falling edge to<br>LB/RB (Input phase)     | 48                                          | 60  | 70  | 48                                          | 60                                      | 70                                      | ns       |                          |

| TMIBS | MCLK falling edge to<br>LB/RB (Input phase)   | 7                                           | 17  | 25  | 7                                           | 17                                      | 25                                      | ns       |                          |

| TIIBS | Instruction to LB/RB<br>(Input phase)         |                                             | 27  | 35  |                                             | 27                                      | 35                                      | ns       |                          |

| TOBS  | X1 falling edge to<br>LB/RB (Output phase)    | 48                                          | 60  | 70  | 48                                          | 60                                      | 70                                      | ns       |                          |

| TMOBS | MCLK falling edge to<br>LB/RB (Output phase)  | 132                                         | 137 | 147 | T <sub>1Q</sub> +T <sub>2Q</sub><br>+7      | T1Q+T2Q<br>+12                          | T <sub>1Q</sub> +T <sub>2Q</sub><br>+22 | ns       | Note 2                   |

| TIDS  | Input data set-up time<br>(X1 falling edge)   | 25                                          | 16  |     | 25                                          | 16                                      |                                         | ns       |                          |

| TMIDS | MCLK falling edge to<br>input data stable     |                                             | 65  | 55  |                                             | T1Q <sup>+T</sup> 2Q<br>−60             | <sup>T</sup> 1Q <sup>+T</sup> 2Q<br>-70 | ns       | Notes 2 & 5              |

| TIDH  | Input data hold time<br>(X1 falling edge)     | 40                                          | 30  |     | 40                                          | 30                                      |                                         | ns       |                          |

| TMDIH | Input data hold time<br>(MCLK falling edge)   | 125                                         | 112 |     | <sup>T</sup> 1Q <sup>+T</sup> 2Q            | T <sub>1Q</sub> +T <sub>2Q</sub><br>-13 |                                         | ns       | Note 2                   |

| TODH  | Output data hold time<br>(X1 falling edge)    | 55                                          | 65  | 75  | 55                                          | 65                                      | 75                                      | ns       |                          |

| тморн | Output data hold time<br>(MCLK falling edge)  | 11                                          | 20  | 25  | 11                                          | 20                                      | 25                                      | ns       |                          |

| TODS  | Output data stable<br>(X1 falling edge)       | 74                                          | 84  | 94  | ,74                                         | 84                                      | 94                                      | ns       | Notes 12, 14, & 15       |

| TMODS | Output data stable<br>(MCLK falling edge)     | 150                                         | 160 | 170 | T <sub>1Q</sub> +T <sub>2Q</sub><br>+25     | T <sub>1Q</sub> +T <sub>2Q</sub><br>+35 | T <sub>1Q</sub> +T <sub>2Q</sub><br>+45 | ns       | Notes 2, 12,<br>14, & 15 |

### Table 2-3. 8X300 AC Electrical Characteristics (Cont'd)

AC CHARACTERISTICS (Commercial Part) (Continued)

CONDITIONS: V\_{CC} = 5V (±5%), V\_IN = 0V or 3V, 0°C  $\leq$  T\_A  $\leq$  70°C LOADING: (See test circuits)

| PARAMETER       |                                                                  | LIMITS (INSTRUCTION<br>CYCLE TIME = 250 ns) |     | LIMITS (INSTRUCTION<br>CYCLE TIME > 250 ns) |                     |     |                     | COMMENTS |               |

|-----------------|------------------------------------------------------------------|---------------------------------------------|-----|---------------------------------------------|---------------------|-----|---------------------|----------|---------------|

|                 | (NOTE 1)                                                         | Min                                         | Тур | Typ Max                                     | Min                 | Тур | Max                 |          | COMMENTS      |

| T <sub>DD</sub> | Input data to output<br>data                                     | 104                                         | 120 | 136                                         | 104                 | 120 | 136                 | ns       | Notes 13 & 15 |

| THS             | HALT set-up time<br>(X1 rising edge)                             | 0                                           |     |                                             | 0                   |     |                     | ns       |               |

| TMHS            | MCLK failing edge to<br>HALT failing edge                        |                                             |     | 18                                          |                     |     | T <sub>1Q</sub> -44 | ns       | Notes 2 & 6   |

| тнн             | HALT hold time<br>(X1 rising edge)                               | 32                                          |     |                                             | 32                  |     |                     | ns       |               |

| тмнн            | HALT hold time<br>(MCLK falling edge)                            | 50                                          |     |                                             | T <sub>1Q</sub> -12 |     |                     | ns       | Note 2        |

| TACC            | Program storage<br>access time                                   |                                             |     | 80                                          |                     |     |                     | ns       |               |

| тю              | I/O port output enable<br>time (LB/RB to valid<br>IV data input) |                                             |     | 30                                          |                     |     |                     | ns       |               |

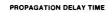

NOTES:

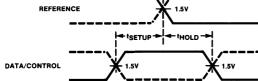

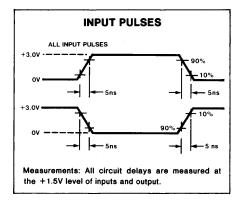

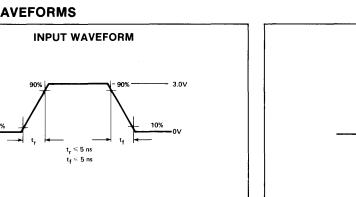

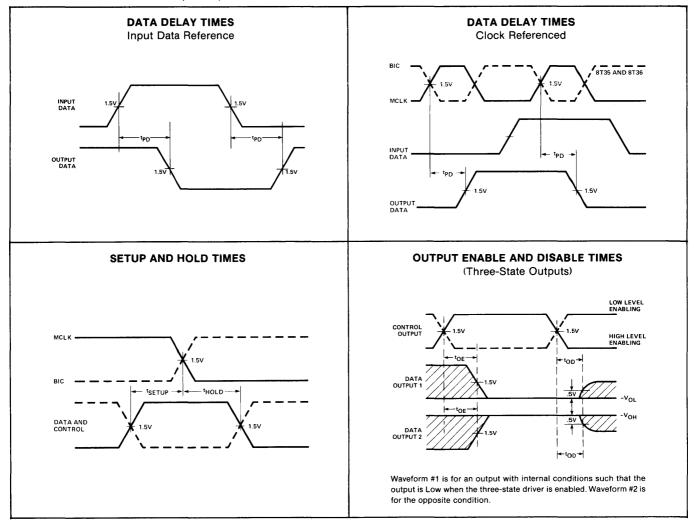

- 1. X1 and X2 inputs are driven by an external pulse generator with an amplitude of 1.5 volts; all timing parameters are measured at this voltage level.

- Respectively, T<sub>1Q</sub>, T<sub>2Q</sub>, T<sub>3Q</sub>, and T<sub>4Q</sub> represent time intervals for the first, second, third, and fourth quarter cycles.

- Capacitive loading for the address bus is 150 picofarads.

Same as TIS but referenced to falling edge of MCLK.

- Same as TIDS but referenced to failing edge of MCLK.

Same as THS but referenced to failing edge of MCLK.

- 7. TAS is obtained by forcing a valid instruction and an I/O bus input to occur earlier than the specified minimum set-up time; the TAS parameter then represents the earliest time that the address bus is valid.

- 8. TIA is obtained by forcing a valid instruction input to occur earlier than the minimum set-up time. 9. TIVA is obtained by forcing a valid I/O bus input to just meet the minimum set-up time.

- 10. TMIS represents the set-up time required by internal latches of the 8X300. In system applications, the instruction input may have to be valid before the worst-case set-up time in order for the system to respond with a valid 1/0 bus input that meets the 1/0bus input set-up time (TIDS and TMIDS).

- 11. TIH represents the hold time required by internal latches of the 8X300. To generate proper LB/RB signals, the instruction must be held valid until the address bus changes.

- 12. TODS is obtained by forcing a valid I/O bus input to occur earlier than the I/O bus input set-up time (TIDS); this timing parameter represents the earliest time that the I/O output data can be valid.

- 13. TDD is obtained by forcing a valid I/O bus input to just meet the minimum I/O bus input set-up time; thus timing parameter represents the latest time that the I/O output data can be valid.

- 14. The minimum figure for these parameters represents the earliest time that I/O bus output drivers of the 8X300 will turn on.

- 15. For TIDS  $\geq$  35 ns, TODS or TMODS should be used to determine when the output data is stable.

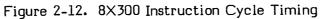

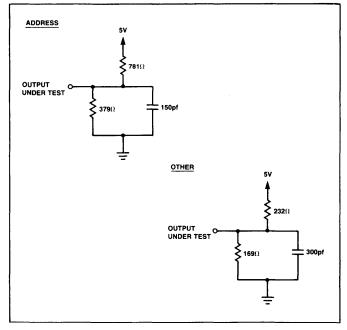

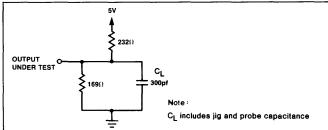

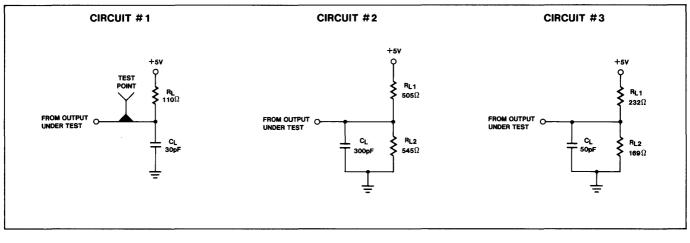

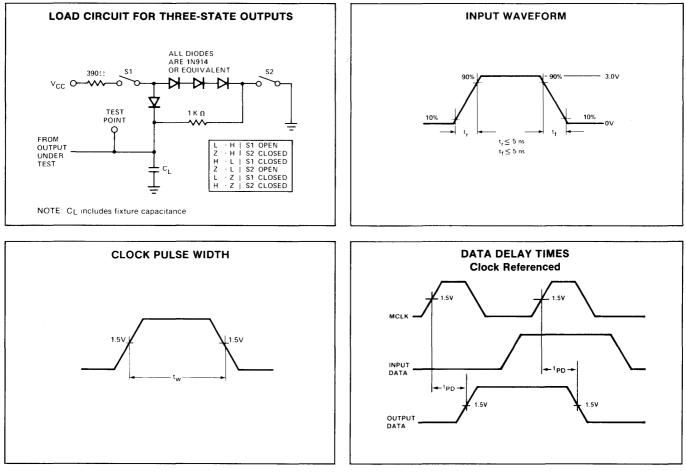

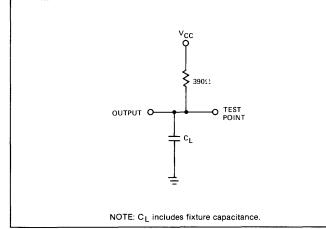

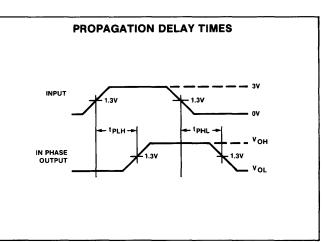

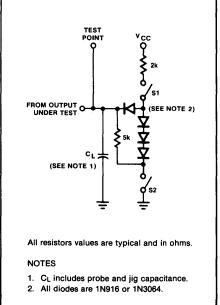

#### **TEST CIRCUITS**

Figure 2-13. Internal Timing Generator

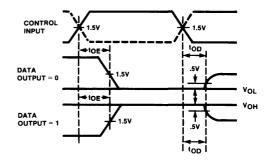

4. I/O bus drivers are active (turned on) during third and fourth quarter cycles.

Figure 2-14. Internal Timing for 250 Nanosecond Instruction Cycle

## 2.2.2 Timing Calculations

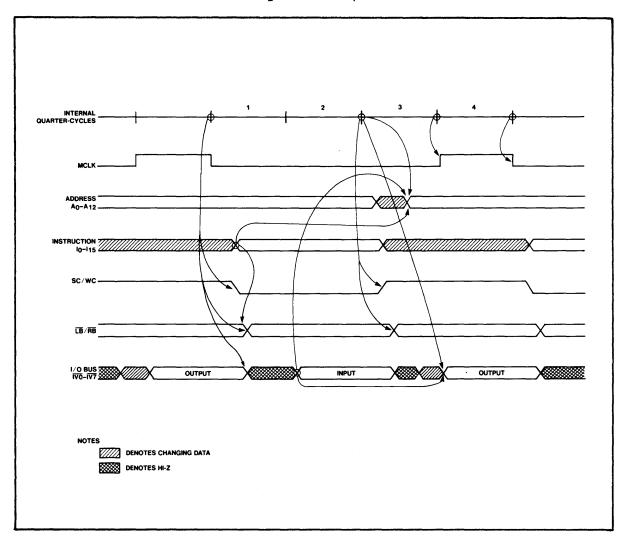

It is an operational requirement of the  $8\times300$  that certain timing events must occur in specific quarter-cycles. In  $8\times300$  systems operating with fast instruction cycle times, most Microcontroller delays are strictly determined by internal gate propagation delays. When operating with slower instruction cycle times, the delays appear to increase due to gating by internal clocks. Figure 2-15 illustrates the timing relationships within the  $8\times300$ .

Figure 2-15. 8X300 Timing Relationships

The switching points of the signals illustrated in Figure 2-15 are defined in the following paragraphs:

MCLK: Master clock. MCLK occurs during, and is equal in length to, the fourth quarter-cycle. The leading and trailing edges of MCLK are, respectively, concurrent with the leading and trailing edges of the fourth quarter-cycle.

ADDRESS: Instruction address output signals. The opening and closing of the internal address latches (register) occur, respectively, with the leading and trailing edges of the third quarter-cycle. Therefore, these latches are open only during the third The address of the previous instruction cycle quarter-cycle. remains stable until the trailing edge of the second quarter-cycle, after which time a new address becomes available on the bus. The point at which the new address becomes valid and stable is dependent on the condition of the following worst case considerations: .

- 1. The propagation delay from the address latch input to the address latch output, when the address latch starts to open during the third quarter-cycle (TAS).

- 2. The propagation delay from the time an instruction becomes stable to the address output (for example, a JMP instruction) (TIA).

- 3. The propagation delay from the beginning a valid I/O bus input to the address output (TIVA). As an example, an instruction in which bit seven of the selected right bank device is examined and the next instruction is executed if the bit is zero, or the instruction at the current location plus five is executed if the bit is one (NZT RB7,\*+5).

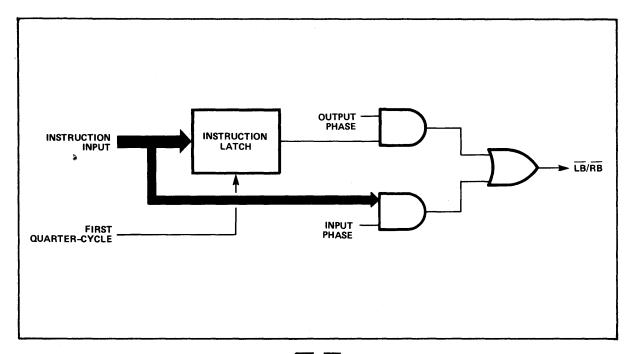

INSTRUCTION: Input signals to the instruction latches (register). These latches are open for the duration of the first quarter-cycle only. When considered at the chip level, there is a minimum set-up and hold time requirement with respect to the trailing edge of the first quarter-cycle. At a system level, there are further requirements as to when and how long the instruction inputs must be valid. As is shown in Figure 2-16, the LB/RB signals are derived directly from the instruction input during the input phase.

To insure the correct LB/RB signals, the instruction input must be stable until the end of the input phase. Since the address bus is stable for the entire input phase, the instruction output of the program storage should be stable for the entire input phase, thus satisfying the requirements for stability of the  $\overline{LB}/\overline{RB}$  signals.

Another factor determining the latest point at which the instruction must become valid is the worst case I/O input set-up time, as shown below:

I/O - data stability depends on the setting of the LB/RB control lines which, in turn, depend on the stability of the instruction bus. See section on "Timing Considerations" for detailed explanation.

# Figure 2-16. LB/RB Enable Paths

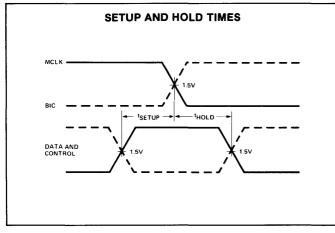

SC/WC: Select command and Write command signals. These signals change state at the leading edges of the first and third quarter-cycles. Keep in mind that SC and WC are never concurrently in a high state.

LB/RB: The complementary left bank and right bank enable signals. When required to change during the input phase, LB/RB becomes valid after the latest occurance of either the leading edge of the first quarter-cycle (TIBS) or the beginning of a valid instruction (TIIBS). If a change is required during the output phase, LB/RB is valid after the leading edge of the third quarter-cycle. Refer to Figure 2-16.

I/O Bus: Input/Output Bus. The I/O bus input latches and the ALU input latches are open during the first two quarter-cycles. Allowing some delay after the leading edge of the third quarter-cycle, the I/O bus drivers are turned on, and remain on throughout the fourth quarter-cycle. When operating at 250 nanosecond instruction cycle times, the I/O data may not be valid until the fourth quarter-cycle.

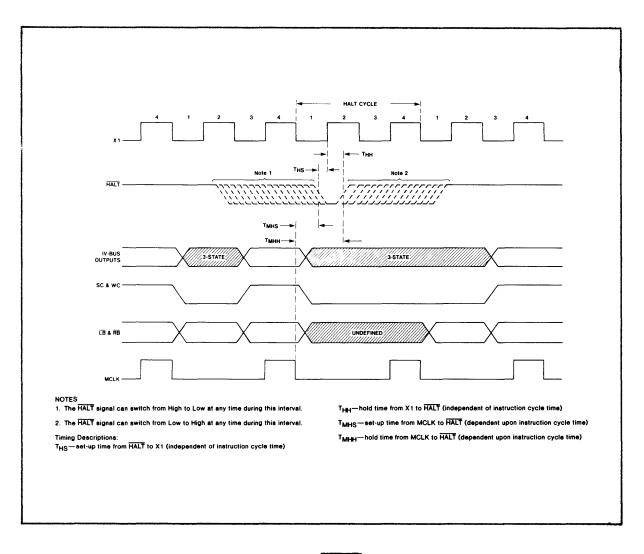

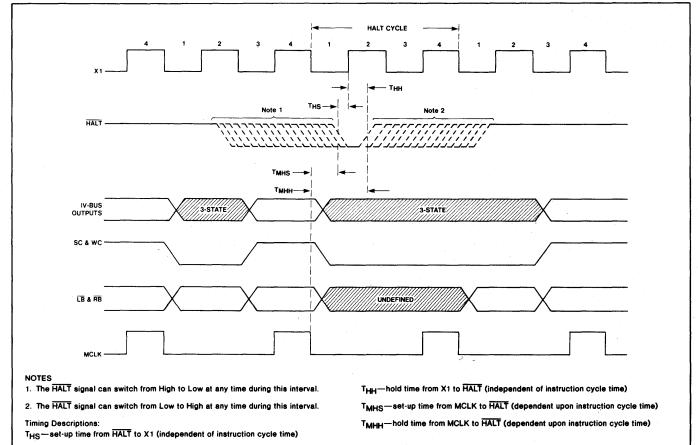

HALT: Halt Signal. The HALT signal is sampled by the  $8\times300$  internal logic during the first quarter-cycle. If the HALT signal

goes low (and remains low) during the first quarter-cycle, the current instruction cycle becomes a HALT cycle. A HALT cycle ceases the internal operation of the 8×300, but does not inhibit MCLK or affect any internal registers. During the HALT cycle the I/O bus is in a high-impedance mode, SC and WC are low, and the address bus, A0-A12, retains the address latched in it at the time the HALT was applied. Normal operation resumes with the cycle in which the HALT signal is high when sampled. Refer to Figure 2-17.

Figure 2-17. HALT Timing

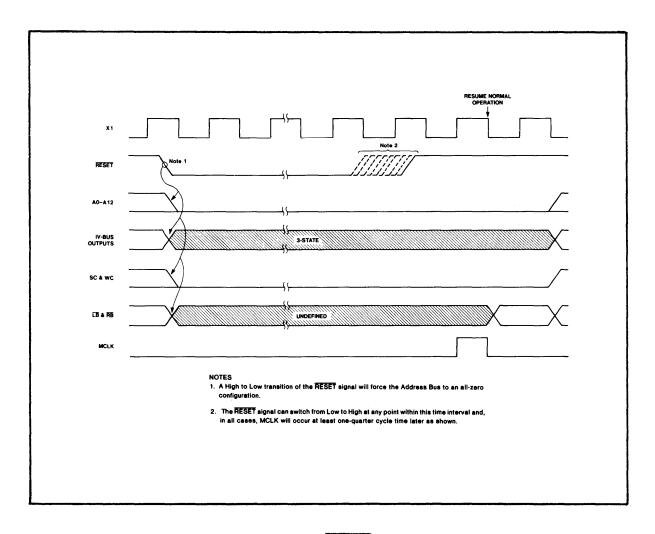

Although RESET timing is not shown in Figure 2-12, it is appropriate that it be described in this portion of text. Figure 2-18 depicts the relationship of RESET to other signals of the 8X300.

When power is first applied to the  $8\times300$ , the RESET input of the device must be forced low as part of the initialization process. This

Figure 2-18. RESET Timing

must be done by some external means, such as an R-C network. To ensure proper operation during normal program flow, the RESET input <u>must</u> be forced low for at least one full instruction cycle. When RESET goes low, the following takes place:

- 1. The Program Counter and Address Register set to zeros asynchronously, with a delay equal to the propagation delay. Their contents remain zeros as long as the RESET input remains low.

- 2. The I/O bus goes to the high-impedance mode asynchronously, and remains in this state as long as RESET is held low.

- 3. The SC and WC outputs go low asynchronously, and remain low as long as RESET remains low.

- 4. The LB/RB outputs are undefined as long as RESET remains low.

- 5. <u>The MCLK</u> output is inhibited as long as RESET is held low. If RESET is forced low during the last two quarter-cycles, the MCLK that occurs during that instruction cycle may be shortened.

The RESET signal has no affect on any internal registers other than those listed above. When the RESET input is allowed to again go high, at least one quarter-cycle later an MCKL (approximately one quarter-cycle long) occurs prior to the resumption of normal operation.

TIMING CONSIDERATIONS (Commercial Part) - As shown in the "AC CHARACTERISTICS" table for this part, Table 2-3, the minimum instruction cycle time is 250 nanoseconds, whereas, the maximum is determined by the on-chip oscillator frequency and can be any value the user chooses. With an instruction cycle time of 250 nanoseconds, the part can be characterized in terms of absolute values; these are shown in the first "LIMITS" column of the table. When the instruction cycle time is greater than 250 nanoseconds, certain parameters are cycle-time dependent; thus, these parameters are specified in terms of the four quarter-cycles  $(T_{1Q}, T_{2Q}, and T_{4Q})$  that make up one instruction cycle -see the timing diagram Figure 2-12. As the time interval for each instruction cycle increases (becomes greater than 250 nanoseconds), the delay for all parameters that are cycle-time dependent is likewise increased. In some cases, these delays have a significant impact on timing relationships and other areas of systems design; subsequent paragraphs describe these timing parameters and reliable methods of calculation.

Timing parameters for the 8X300 are normally measured with reference to X1 and MCLK; those referenced to MCLK are prefaced with an "M" in the mnemonic-- TMAS, TMIH, and so on. To determine the timing relationship between a particular signal, say "A", and MCLK, the user should, at all times, use the value specified in the table-- DO NOT calculate the value by adding or subtracting two or more parameters that are referenced to X1. When deriving timing relationships between two signals (A to B, etc.) by adding or subtracting the parameter values, the user must consistently use the same parameter reference-- MCLK or X1.

System determinants for the instruction cycle time are:

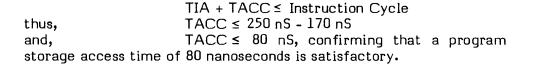

Propagation delays within the 8×300 Access time of Program Storage Enable time of Output Port Normally, the instruction cycle time is constrained by one or more of the following conditions:

- Condition 1 -- Instruction or MCLK to LB/RB (input phase) plus I/O port output enable (TIO)  $\leq$  IV data set-up time (Figure 2-19a)

- Condition 2 -- Program storage access time (TACC) plus instruction to LB/RB (input phase) plus I/O port output enable (TIO) plus IV data (input phase) to address ≤ instruction cycle time (Figure 2-19b).

- Condition 3 -- Program Storage access time plus instruction to address  $\leq$  instruction cycle time (Figure 2-19c).

From condition #1 and with an instruction cycle time of 250 nanoseconds, the I/O port output enable time (TIO) can be calculated as follows:

|               | TMIBS + TIO ≤ TMIDS  |

|---------------|----------------------|

| transposing,  | TIO ≤ TMIDS - TMIBS  |

| substituting, | TIO ≤ 55nS - 25 nS   |

| result,       | TIO ≤ 30 nanoseconds |

Using 30 nanoseconds for TIO, the constraint imposed by Condition #1 can also be used to calculate the minimum cycle time:

|       | TMIBS + TIO ≤ TMIDS                                    |

|-------|--------------------------------------------------------|

| thus, | 25 nS + 30 nS ≤ T <sub>1Q</sub> + T <sub>2Q</sub> - 70 |

|       | 25 nS + 30 nS $\leq \frac{1}{2}$ cycle - 70 therefore  |

the worst-case instruction cycle time is 250 nanoseconds. With subject parameters referenced to X1, the same calculations are valid:

TIBS + TIO + TIDS  $\leq \frac{1}{2}$  cyclethus,70 nS + 30 nS + 25 nS  $\leq \frac{1}{2}$  cycle therefore,the worst-case instruction cycle time is again 250 nanoseconds.From Condition #2 and with an instruction cycle time of 250nanoseconds, the program storage access time can be calculated:

|                         | TACC + TIIBS + TIO + TIVA ≤ 250 nS                |

|-------------------------|---------------------------------------------------|

| transposing,            | $TACC \le 250 \text{ nS} - TIIBS - TIO - TIVA$    |

| substituting,           | TACC ≤ 250 nS - 35 nS - 30 nS - 105 nS            |

| thus,                   | TACC $\leq$ 80 nS hence, for an instruction cycle |

| time of 250 nanosec     | onds, a program storage access time of 80         |

|                         | I. The constraint imposed by Condition #3 can     |

| be used to verify the n | naximum program storage access time:              |

Figure 2-19. Constraints of 8X300 Instruction Cycle Time

For an instruction cycle time of 250 nanoseconds and a program storage access time of 80 nanoseconds (Condition #2), the instruction should be valid 10 nanoseconds before the falling edge of MCLK. This relationship can be derived by the following equation:

250 nS - TMAS - TACC = 250 nS - 160 nS - 80 nS = 10 nS

It is important to note that, during the input phase, the beginning of a valid LB/RB signal is determined by either the instruction to

LB/RB delay (TIIBS) or the delay time from the falling edge of MCLK to LB/RB (TMIBS). Assuming the instruction is valid 10 nanoseconds before the falling edge of MCLK and adding the instruction-to-LB/RB delay (TIIBS = 35 nS), the LB/RB signal will be valid 25 nanoseconds after the falling edge of MCLK. With a fast program-storage memory and with a valid instruction more than 10 nanoseconds before the falling edge of MCLK -- the LB/RB signal will, due to the TMIBS delay, still be valid 25 nanoseconds after the falling edge of MCLK -- the LB/RB signal will, due to the TMIBS delay, still be valid 25 nanoseconds after the falling edge of MCLK. Using a worst-case instruction cycle time of 250 nanoseconds, the user cannot gain a speed advantage by selecting a memory with faster access time. Under the same conditions, a speed advantage cannot be obtained by using an I/O port with fast output enable time (TIO) because the address bus will be stable 80 nanoseconds (TAS) after the beginning of the third quarter-cycle -- no matter how early the IV data input is valid.

When operating at slower instruction cycle times (TPC > 250 nS), there are two more timing conditions which must be satisfied in addition to those already mentioned. First, the I/O input data must be stable by the set-up time required by the input latches. The program storage access time (TACC) must be such that

TAS + TACC + TIIBS + TIC + TIDS

$$\leq$$

TPC

Second, the instruction must be stable by the set-up time required by the instruction latches. The program storage access time must also be such that

TAS + TACC + TIS

$$\leq$$

TPC - T<sub>2Q</sub>

where  $T_{2Q}$  is the length of the second quarter-cycle (pulse width of X1 high); for symetric clock signals

$$T_{2Q} = \frac{1}{4}$$

TPC, or

TAS + TACC + TIS  $\leq .75$  TPC

Program storage access time must satisfy the worst case of all of the timing conditions mentioned.

### 2.3 THE 8X300 INSTRUCTION SET

The  $8\times300$  instruction set comprises eight categories of instruction, each identified by a different OP code value. A variable operand field within these instructions provide the equivalent of 32 instructions. During the process of an instruction, the data may undergo some combinations of rotate, mask, and shift and merge manipulations. Table 2-4 describes the functions that can be performed on the data during the instruction operations. Certain instruction operations perform no function on the data, therefore, they do not appear in this Table (example: XMIT, Register).

The following paragraphs, in conjunction with Table 2.4, provide a brief description of the operations that may be performed by each of the instruction categories. It is suggested that when reading these descriptions, the reader should also refer back to the internal block diagram, Figure 2-11.

- Op Code 0 (MOVE): Data from the source register or I/O bus is moved to the destination register or I/O bus. Bit manipulations may be performed as specified in Table 2-4. The source data field remains unchanged after the operation.

- Op Code 1 (ADD): Data from the source register or I/O bus is added to the contents of the AUX reaister (Accumulator). The result is then placed in the destination register or I/O bus. Bit manipulations may be performed as specified in Table 2-4. The source data field and AUX register remain unchanged unless one of those is also the destination. Only during the ADD instruction is the value of Register 10 set. (RIO cannot be specified as a destination.) The high order seven bits always remain zero. The LSB is set to indicate the carry-out of the MSB of the ALU.

NOTE: This does not indicate an overflow condition resulting from excessive magnitude of a two's complement sum.

Op Code 2 (AND): Data from the source register or I/O bus is ANDed with the contents of the AUX register (Accumulator). The result is then placed in the destination register or I/O bus. Bit manipulations may be performed as specified in Table 2-4. The source data field and AUX register remain unchanged unless one of those is also the destination.

|                         | FUNCTION |      |       |       |  |  |

|-------------------------|----------|------|-------|-------|--|--|

| OPERATION               | ROTATE   | MASK | SHIFT | MERGE |  |  |

| MOVE, ADD, AND, XOR     | ОК       | x    | x     | х     |  |  |

| REGISTER – REGISTER     |          |      |       |       |  |  |

| MOVE, ADD, AND, XOR     | ок       | x    | x     | x     |  |  |

| REGISTER IV BUS ADDRESS |          | ^    | ^     | ^     |  |  |

| MOVE, ADD, AND, XOR     | x        | v    | ОК    | ок    |  |  |

| REGISTER – IV BUS       | ^        | X    |       | UK    |  |  |

| MOVE, ADD, AND, XOR     | ок       | ок   | x     | x     |  |  |

| IV BUS – REGISTER       |          |      | ~     |       |  |  |

| MOVE, ADD, AND, XOR     | ОК       | ок   | ок    | ок    |  |  |

| IV BUS – IV BUS         | OK       | ÖK   | ÖK    | UK    |  |  |

| MOVE, ADD, AND, XOR     | ок       | ОК   | x     | x     |  |  |

| IV BUS – IV BUS ADDRESS |          |      | ^     |       |  |  |

| XEC, NZT<br>IV BUS      | ок       | ок   | x     | х     |  |  |

| XMIT<br>IV BUS          | ×        | ×    | ок    | ок    |  |  |

Table 2-4. Bit Manipulation Functions

NOTES: 1. X REPRESENTS A NON-USABLE FUNCTION.

2. XEC, NZT AND XMIT REGISTER, AND XMIT IV BUS ADDRESS HAVE NO BIT MANIPULATIONS PERFORMED DURING THEIR OPERATION.

- Op Code 3 (XOR): Data from the source register or I/O bus undergoes an EXCLUSIVE OR operation with the contents of the AUX register (Accumulator). The result is then placed in the destination register or I/O bus. Bit manipulations may be performed as specified in Table 2-4. The source data field and AUX register remain unchanged unless one of those is also the destination.

- Op Code 4 (XEC): Executes the instruction at the address formed by replacing the least significant bits of the current address with the sum of the J field and the data in the source register or I/O port.\* Bit manipulations may be performed on I/O source data only as specified in Table 2-4. After execution of the instruction at the specified address, instruction execution continues at the address following the XEC instruction, unless the instruction at the specified address caused a jump.

- Op Code 5 (NZT): The least significant bits of the program counter are replaced by the J field data if the register or I/O bus specified by the source field has non-zero contents.\* Bit manipulations may be performed on I/O destination data only as specified in Table 2-4. The tested data field remains unchanged.

- Op Code 6 (XMIT): The data in the J field is placed in the register or I/O port specified as the destination field.\* Bit manipulations may be performed as specified in Table 2-4.

- Op Code 7 (JMP): The address of the next instruction to be executed is changed to that specified by the 13-bit A field of the instruction.

#### \*NOTE:

If the source field specified a register, the J field contains an eight-bit value. If the source field specifies an I/O port (or memory), the J field contains a five-bit value.

A compendium of information on instruction formats is contained in Appendix B.

# 2.4 INTERFACE PRINCIPLES

Designing hardware to interface with the 8X300 Microcontroller is primarily a task of selecting external devices that suit the job to be done. Careful consideration must be given to the minimum requirements necessary to accomplish the job. Such requirements might include instruction cycle time, memory size and memory access time. Must the system operate with a 250 nS instruction cycle time, or is 500 nS sufficient? At longer instruction cycle times, slower and less expensive memory may be used. How much External Working Storage is necessary? As External Working Storage increases, the methods of manipulating it become more complex. Which is the most economical method of manipulating larger and/or slower memory - hardware or software?

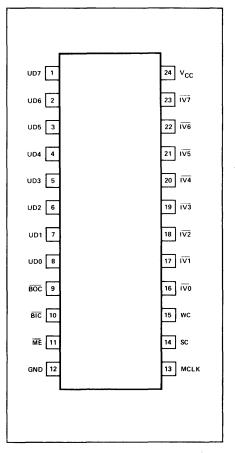

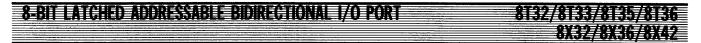

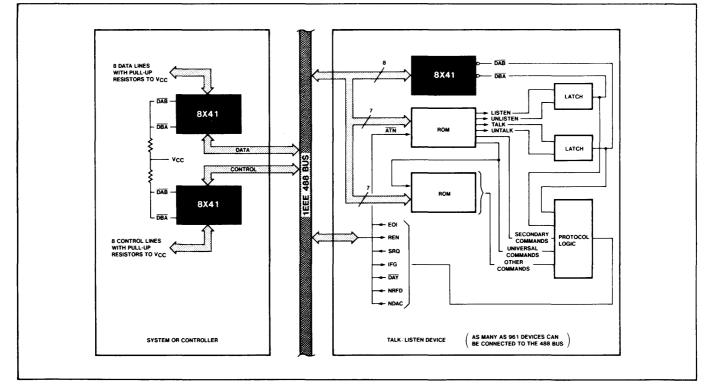

Signetics offers a broad line of devices that are either specifically designed for use with or are compatible with the  $8\times300$ . Table 2-5 provides a listing of these devices, by function. Selection of devices from this list can greatly reduce the time and tasks necessary in  $8\times300$  system design.

The following sections provide general information which will aid designers seeking solutions to specific interface problems.

### 2.4.1 Memory Interface

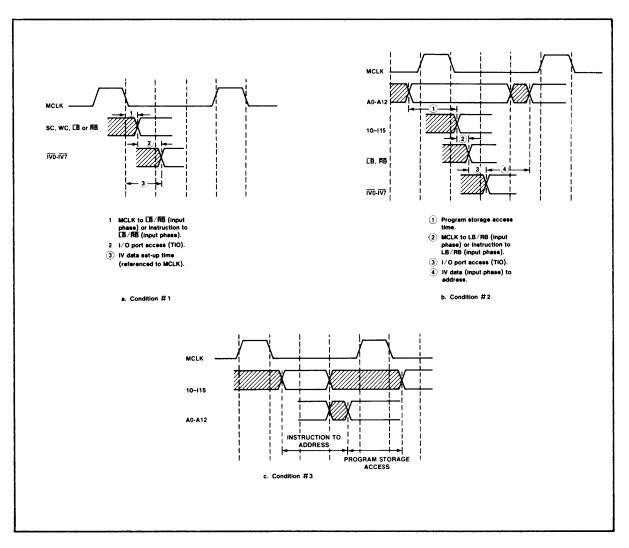

It should be pointed out that the program storage and working storage devices listed in Table 2-5 are all bipolar devices. Furthermore, as is shown in Table 2-5, the access times of the majority of devices are within the 80 nanosecond maximum required for an  $8\times300$  operating with an instruction cycle time of 250 nanoseconds. This is not to say that all systems must have bipolar memory devices, or that all systems must operate with a maximum memory access time of 80 nanoseconds. If the system under design is of a nature that allows instruction cycle times greater than 250 nanoseconds, the designer might desire to stretch the instruction cycle time in order to select memory devices. It is suggested that the designer review Section 2-2 of this manual prior to attempting calculations of instruction cycle times versus memory access times.

As an alternative to stretching the entire instruction cycle, the designer might consider an oscillator configuration which selectively stretches the instruction quarter-cycles. A suggested configuration is shown in Figure 2-20. This design stretches all positive phases of clock input X1. The system is self-synchronizing, and elongates the memory fetch cycles. An arbitrary oscillator frequency of 6.154  $MH_z$  and delay time of 18.75 nanoseconds was chosen for purposes of illustration. Other oscillator frequencies and delay times will yield different quarter-cycle time periods.

| Program Storage (ROM, F                                                                                       | PROM)                                                                                                                                                                                                               |                                                                         |                                                              |                                                                                |  |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------|--|

| Туре                                                                                                          | Description                                                                                                                                                                                                         |                                                                         |                                                              | Access Time                                                                    |  |

| 82S23/123<br>82S126/129<br>82S131<br>82S115<br>82S137<br>82S181<br>82S185<br>82S190/191<br>82S2708(Mil. only) | OC/TS<br>OC/TS<br>TS<br>TS<br>TS<br>TS<br>TS<br>OC/TS<br>TS                                                                                                                                                         | 32×8<br>256×4<br>512×4<br>512×8<br>1K×4<br>1K×8<br>2K×4<br>2K×8<br>1K×8 | Prom<br>Prom<br>Prom<br>Prom<br>Prom<br>Prom<br>Prom<br>Prom | 50 ns<br>50 ns<br>50 ns<br>60 ns<br>60 ns<br>70 ns<br>100 ns<br>80 ns<br>60 ns |  |

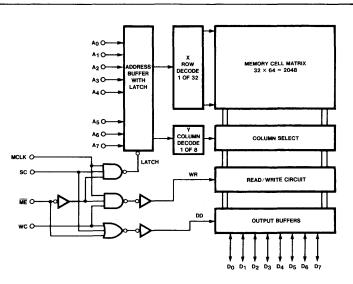

| Working Storage (RAM)<br>82S09<br>82S16<br>82S116<br>8X350                                                    | OC<br>TS<br>TS<br>TS                                                                                                                                                                                                | 64×9<br>256×1<br>256×1<br>256×8                                         | RAM<br>RAM<br>RAM<br>RAM                                     | 50 ns<br>50 ns<br>40 ns<br>35 ns                                               |  |

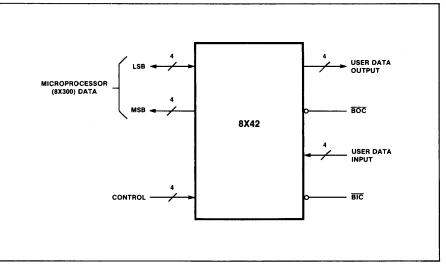

| I/O Devices                                                                                                   |                                                                                                                                                                                                                     |                                                                         |                                                              |                                                                                |  |

| 8T26A/28<br>8T31<br>8T32/33/35/36<br>8T39<br>8T58<br>8×41<br>8×320                                            | Quad Bus Transceiver<br>8-Bit Bidirectional I/O Port<br>8-Bit Addressable Bidirectional I/O Port<br>Bus Extender<br>Transparent Bus Expander<br>Bidirectional Bus Extender/Repeater<br>Bus Interface Register Array |                                                                         |                                                              |                                                                                |  |

| Communications Devices                                                                                        |                                                                                                                                                                                                                     |                                                                         |                                                              |                                                                                |  |

| 2652<br>8×01<br>8×330<br>9403                                                                                 | Synchronous Data Link Controller<br>Cyclic Redundancy Checker<br>Floppy Disk Formatter/Controller<br>64-Bit FIFO Buffer Memory                                                                                      |                                                                         |                                                              |                                                                                |  |

| Integrated Fuse Logic                                                                                         |                                                                                                                                                                                                                     |                                                                         |                                                              |                                                                                |  |

| 825100/101<br>825102/103                                                                                      | TS/OC I<br>OC/TS F                                                                                                                                                                                                  | l6X8X48 F<br>FPGA                                                       | PLA                                                          |                                                                                |  |

Figure 2-20. Elongated Positive Cycle Clock

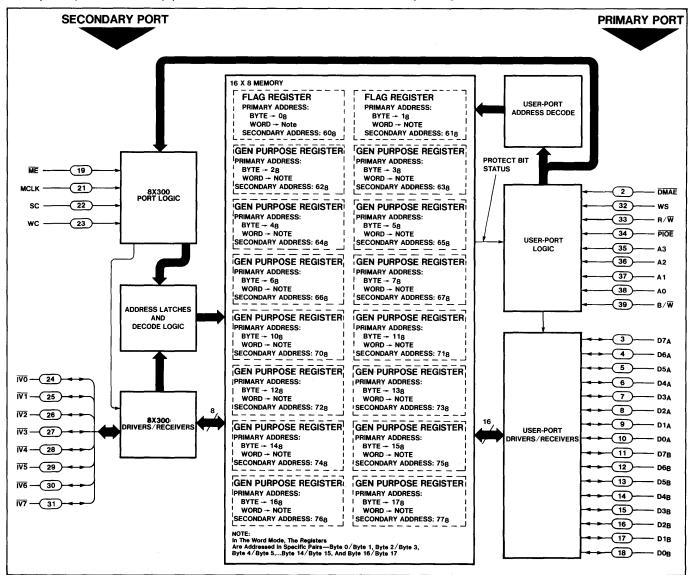

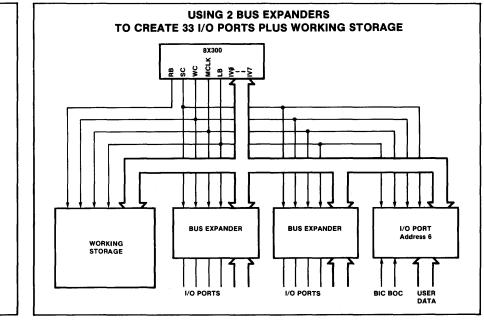

Figure 2-21 illustrates a system which operates with up to 64K bytes of industry standard, TTL compatible MOS working storage. The system is implemented through the use of some additional hardware. It should be noted that the program memory should consist of devices with an access time of 80 nanoseconds or less and that the instruction word has been extended from 16 bits to 20 bits. Two of these bits are used as enables for the RAM address latches. The remaining two bits may be used for other control or display drive functions. Although this method requires additional ROMs for the extension, it eliminates the latch select instruction cycle that would be necessary if addressable latches, such as the  $8\times32$ , were used as RAM address latches. This saves both in program storage and in total processing time for working storage. It requires that a specific program structure be followed within program storage. The RAM address latches must be sequentially loaded, the data latch selected, then the data itself loaded into the data latch. If the RAM array is composed of devices with an access time of 250 nanoseconds or less, the RAM address will be stable by the time data is to be written to or read from the RAM array.

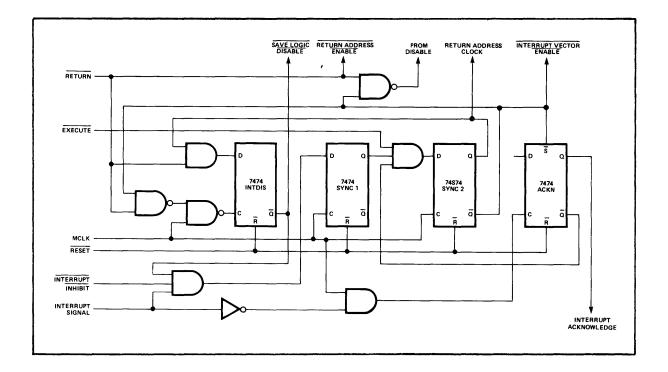

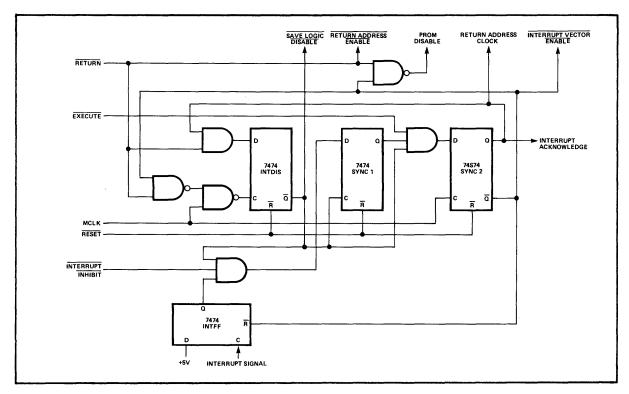

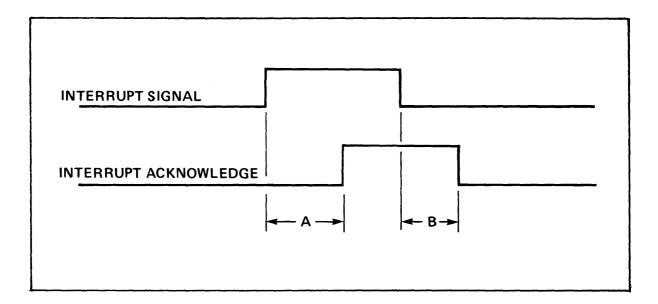

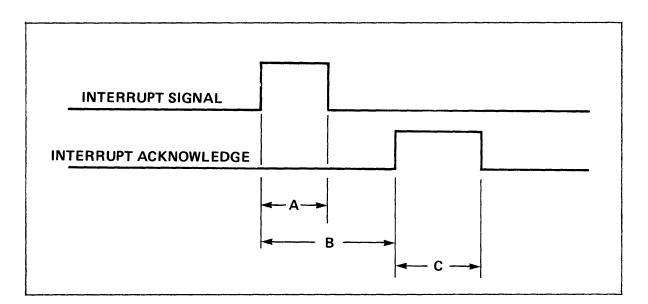

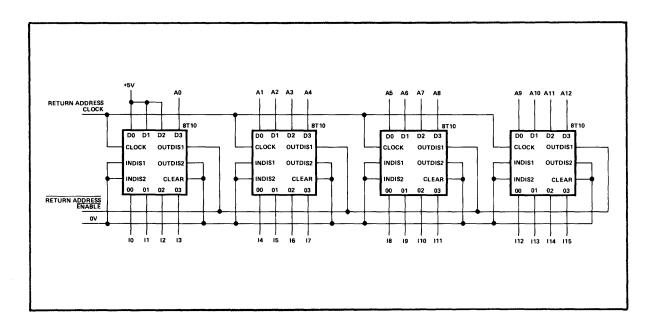

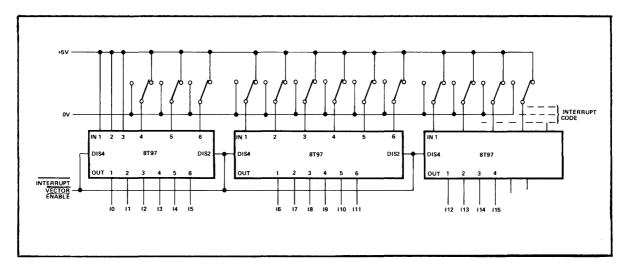

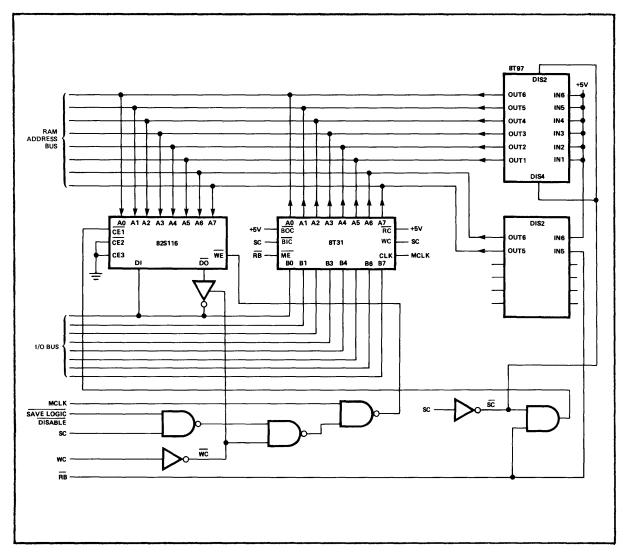

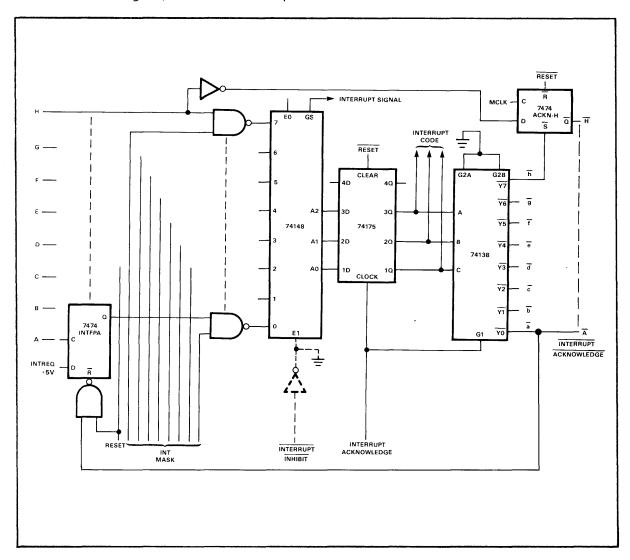

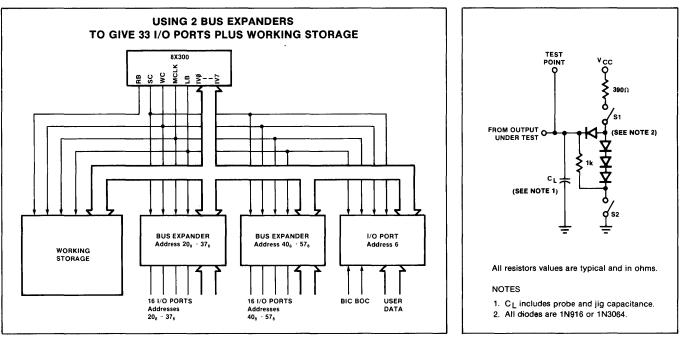

The system designer must ensure that the program instruction becomes valid early enough relative to MCLK in order for the RAM address latch enable bits (II6 and II7) to be latched into the D-latches. In cases where the instruction is not yet valid at the trailing edge of MCKL, the MCLK signal to the D-latches can be slightly delayed by adding two or three buffer stages to the MCKL signal line, just prior to the D-latches