# $\textbf{TriCore}\; \boldsymbol{\mu}\textbf{C}\textbf{-}\textbf{DSP}$

Ŷ

Architecture Manual

# TriCore Architecture Manual

Erin Farquhar Elaine Hadad

Version 1.1 09/17/97

♦ PRELIMINARY EDITION ♦

#### Copyright © 1997 Siemens AG.

#### All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes, and circuits implemented within components or assemblies.

This information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery, and prices, please contact the Semiconductor Group offices in Germany or the Siemens Companies and Representatives worldwide.

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact your nearest Siemens Semiconductor Group.

Siemens, AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you get in touch with your nearest sales office. By agreement, we will take packing material back, if it is sorted. You must bear the cost of transport.

For packing material that is returned to us unsorted or which we are not obligated to accept, we shall have the right to invoice you for any costs incurred.

# Components used in the life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- A critical component is a component used in a life-support device whose failure can reasonably be expected to cause the failure of that lifesupport device or system, and/or to affect the safety or effectiveness of that device or system.

- Life-support devices or systems are intended: (a) to be implemented in the human body, or (b) to support and/or maintain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| Front Matter                 | Front Matter                    |   |

|------------------------------|---------------------------------|---|

| Preface                      | Preface                         |   |

| Architecture Overview        | Architecture<br>Overview        | 1 |

| Programming Model            | Programming<br>Model            | 2 |

| Core Registers               | Core Registers                  | 3 |

| Managing Tasks and Functions | Managing Tasks<br>and Functions | 4 |

| Interrupt System             | Interrupt System                | 5 |

| Traps                        | Traps                           | 6 |

| Protection System            | Protection System               | 7 |

| Instruction Set Overview     | Instruction Set<br>Overview     | 8 |

| TriCore Instruction Set      | TriCore Instruction<br>Set      | 9 |

### Front Matter

Front Matter

# SIEMENS Variet

# **Front Matter**

# **1.1 Revision History**

| Release Version | Release Date | Contents of Revision |

|-----------------|--------------|----------------------|

| 1.0             | 06/01/97     | Beta Release.        |

| 1.1             | 09/17/97     | Preliminary Release. |

TriCore Architecture Manual

iv

# SIEMENS UTION

| 1 | ARC  | HITECTURE OVERVIEW                    |

|---|------|---------------------------------------|

|   | 1.1  | TriCore Architecture Feature Overview |

|   | 1.2  | Program State Registers               |

|   | 1.3  | Data Types                            |

|   | 1.4  | Addressing Modes                      |

|   | 1.5  | Instruction Formats                   |

|   | 1.6  | Tasks and Contexts                    |

|   | 1.0  | 1.6.1 Upper and Lower Contexts        |

|   |      |                                       |

|   |      |                                       |

|   |      | 1.6.3 Fast Context Switching          |

|   | 1.7  | Interrupt System                      |

|   | 1.8  | Trap System                           |

|   | 1.9  | Protection System                     |

|   |      | 1.9.1 Permission Levels               |

|   |      | 1.9.2 Protection Model                |

|   | 1.10 | Reset System 10                       |

|   | 1.11 | Debug System 10                       |

| ~ | Dec  |                                       |

| 2 |      | GRAMMING MODEL                        |

|   | 2.1  | Data Types                            |

|   | 2.2  | Data Formats 14                       |

|   | 2.3  | Memory Model                          |

|   | 2.4  | Addressing Model 19                   |

|   |      | 2.4.1 TriCore Addressing Modes        |

|   |      | 2.4.1.1 Absolute Addressing 20        |

|   |      | 2.4.1.2 Base+Offset Addressing 20     |

|   |      | 2.4.1.3 Pre-Increment Addressing 2    |

|   |      | 2.4.1.4 Post-Increment Addressing 2   |

|   |      | 2.4.1.5 Circular Addressing2          |

|   |      | 2.4.1.6 Bit-Reverse Addressing 22     |

|   |      | 2.4.2 Synthesized Addressing Modes    |

|   |      | 2.4.2.1 Indexed Addressing            |

|   |      | 2.4.2.2 PC-Relative Addressing        |

|   |      |                                       |

|   |      | 2.4.2.3 Extended Absolute Addressing               | 24 |

|---|------|----------------------------------------------------|----|

| 3 | COR  | e Registers                                        | 27 |

|   | 3.1  | Access to the Core Registers                       | 28 |

|   | 3.2  | General-Purpose Registers (GPRs)                   | 29 |

|   | 3.3  | Program State Information (PC, PSW, and PCXI)      | 30 |

|   |      | 3.3.1 Program Counter                              | 30 |

|   |      | 3.3.2 Program Status Word (PSW)                    | 30 |

|   |      | 3.3.3 Previous Context Information Register (PCXI) | 32 |

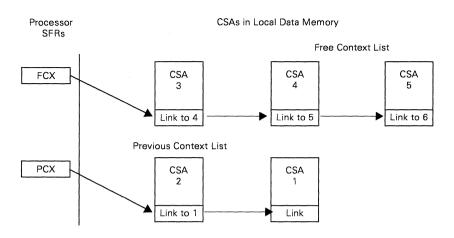

|   | 3.4  | Context Management Registers                       | 33 |

|   |      | 3.4.1 Free CSA List Head Pointer (FCX)             | 34 |

|   |      | 3.4.2 Previous Context Pointer (PCX)               | 34 |

|   |      | 3.4.3 Free CSA List Limit Pointer (LCX)            | 35 |

|   | 3.5  | Stack Management                                   | 35 |

|   | 3.6  | Interrupt and Trap Control                         | 36 |

|   |      | 3.6.1 Interrupt Control Register (ICR)             | 36 |

|   |      | 3.6.2 Interrupt Vector Table Pointer (BIV)         | 37 |

|   |      | 3.6.3 Trap Vector Table Pointer (BTV)              | 37 |

|   | 3.7  | System Control Registers                           | 38 |

|   |      | 3.7.1 SYSCON Register                              | 38 |

|   |      | 3.7.2 PMUCON Register                              | 38 |

|   |      | 3.7.3 DMUCON Register                              | 38 |

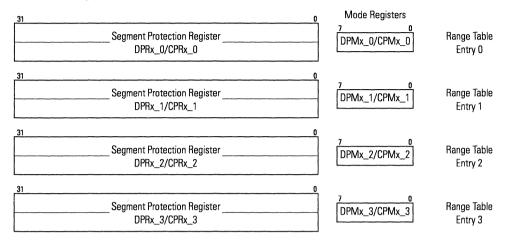

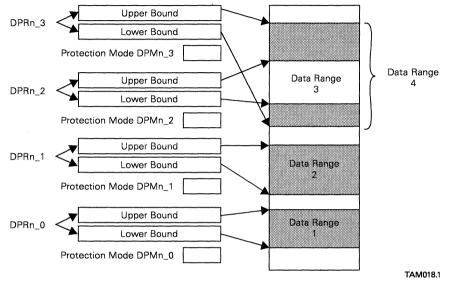

|   | 3.8  | Memory Protection Registers                        | 39 |

|   |      | 3.8.1 Data and Code Segment Protection Registers   | 40 |

|   |      | 3.8.2 Data Protection Mode Registers               | 41 |

|   |      | 3.8.3 Code Protection Mode Registers               | 42 |

|   | 3.9  | Debug Registers                                    | 44 |

| 4 | Mar  | VAGING TASKS AND FUNCTIONS                         | 47 |

|   | 4.1  | Upper and Lower Contexts                           | 47 |

|   | 4.2  | Task Switching Operation                           | 48 |

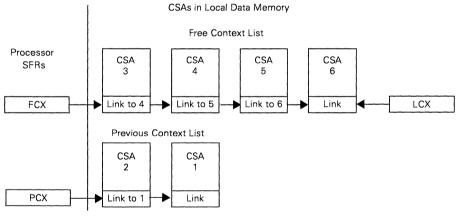

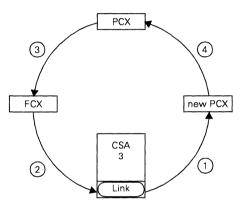

|   | 4.3  | CSAs and Context Lists                             | 49 |

|   | 4.4  | Context Switching with Interrupts                  | 50 |

|   | 4.5  | Context Switching with Function Calls              | 51 |

|   | 4.6  | Context Save/Restore Examples                      | 52 |

|   |      | 4.6.1 Context Save                                 | 52 |

|   |      | 4.6.2 Context Restore                              | 54 |

| 5 | INTE | RRUPT SYSTEM                                       | 59 |

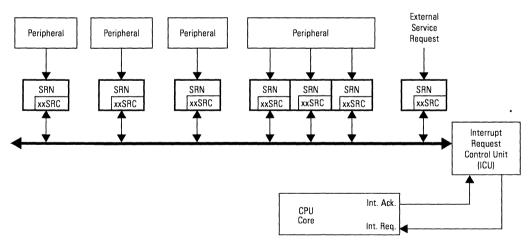

|   | 5.1  | System Overview                                    | 59 |

|   | 5.2  | The Service Request Priority Number (SRPN)         | 60 |

|   | 5.3  | The Interrupt Control Unit (ICU)                   | 61 |

|   | 5.4  | Interrupt Arbitration                              | 61 |

|   | 5.5  | Entry into an Interrupt Service Routine (ISR)      | 62 |

|   |      | 5.5.1 Default State of the PSW upon an Interrupt   | 63 |

|   |      | 5.5.2 The Interrupt Vector Table                   | 63 |

TriCore Architecture Manual

|   | 5.6 | Interri | upt Priorit | y Levels                              | 64       |

|---|-----|---------|-------------|---------------------------------------|----------|

|   | 5.7 |         |             | ling the Interrupt System             | 64       |

|   | 5.8 |         |             | g of Interrupt Requests               | 65       |

|   |     | 5.8.1   | Softwar     | e-Posted Interrupts                   | 65       |

|   |     |         |             | t One                                 | 65       |

| 6 | TDA | DC      |             |                                       | 69       |

| 0 | 6.1 |         |             |                                       | 69       |

|   | 0.1 |         |             | nous Traps                            | 71       |

|   |     |         |             | onous Traps                           | 71       |

|   |     |         |             | re Traps                              | 71       |

|   |     | 614     | Softwar     | e Traps                               | 72       |

|   | 6.2 |         |             |                                       | 72       |

|   | 0.2 |         |             | ctor Format                           | 72       |

|   |     |         |             | ng the Trap Vector Table              | 72       |

|   |     |         |             | State upon a Trap                     | 72       |

| _ | _   |         |             |                                       |          |

| 7 |     |         |             | Μ                                     | 77       |

|   | 7.1 |         |             | tem Registers                         | 77       |

|   |     | 7.1.1   |             | otection Fields                       | 77       |

|   |     |         | 7.1.1.1     | PRS                                   | 78       |

|   |     |         |             | 10                                    | 78       |

|   |     |         |             | IS                                    | 78       |

|   |     |         | 7.1.1.4     | GW                                    | 78<br>79 |

|   |     |         |             | CDE                                   | 79<br>79 |

|   |     | 710     |             | CDC<br>Protection Registers           | 79       |

|   |     | 7.1.2   | 7.1.2.1     | Modes of Use for Range Table Entries  | 80       |

|   |     |         | 7.1.2.1     | Using Protection Register Sets        | 81       |

|   | 7.2 | Samn    |             | tion Register Set                     | 81       |

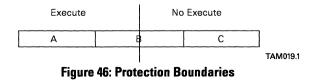

|   | 7.3 |         |             | s Checking                            | 82       |

|   | 7.0 |         |             | ed vs. Valid Accesses                 | 83       |

|   |     |         |             | Protection Boundaries                 | 83       |

|   |     |         |             | ·                                     |          |

| 8 |     |         |             | VERVIEW                               | 87       |

|   | 8.1 |         |             | ructions                              | 87       |

|   |     | 8.1.1   | 0           | Arithmetic                            | 88       |

|   |     |         | 8.1.1.1     |                                       | 88       |

|   |     |         | 8.1.1.2     | Addition and Subtraction              | 89       |

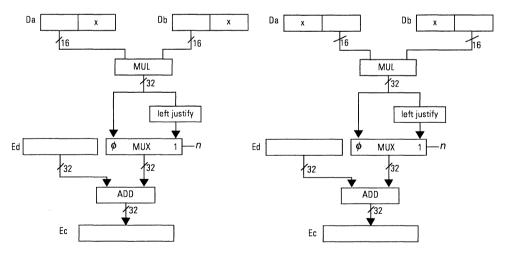

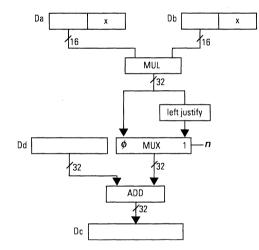

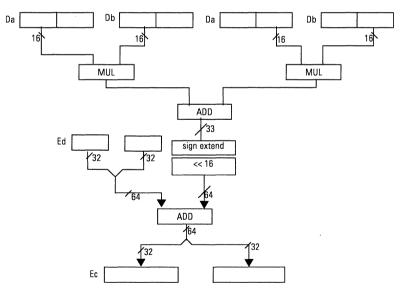

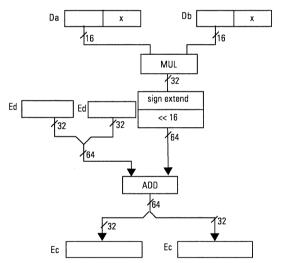

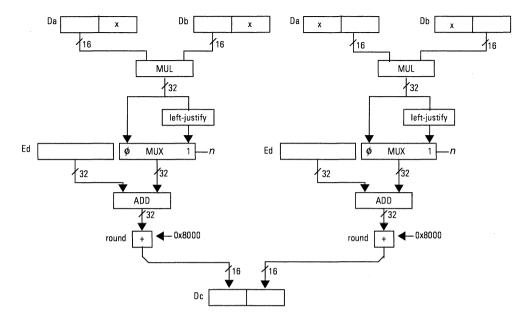

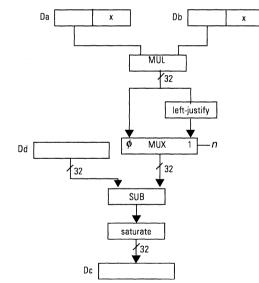

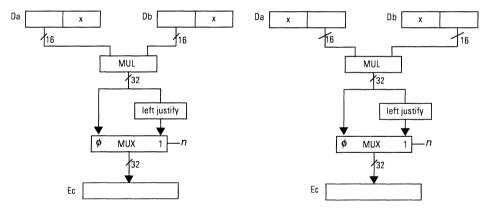

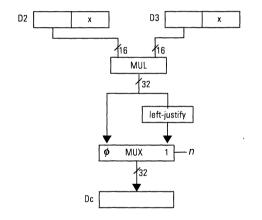

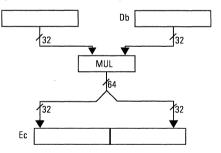

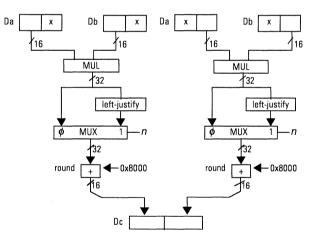

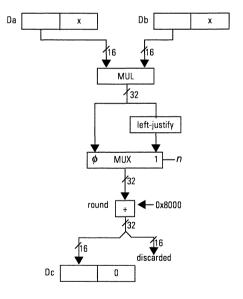

|   |     |         | 8.1.1.3     | Multiply and Multiply-Add             | 89       |

|   |     |         | 8.1.1.4     | Division                              | 90       |

|   |     |         | 8.1.1.5     | Absolute Value, Absolute Difference   | 90       |

|   |     |         | 8.1.1.6     | Min, Max, Saturate                    | 90       |

|   |     |         | 8.1.1.7     | Conditional Arithmetic Instructions   | 90       |

|   |     |         | 8.1.1.8     | Logical                               | 91<br>91 |

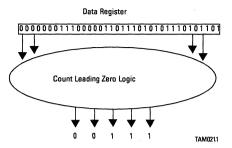

|   |     |         | 8.1.1.9     | Count Leading Zeroes, Ones, and Signs | 91       |

Front Matter

|            |                                                           | ~ ~ |

|------------|-----------------------------------------------------------|-----|

|            |                                                           | 92  |

|            |                                                           | 92  |

|            |                                                           | 94  |

|            |                                                           | 94  |

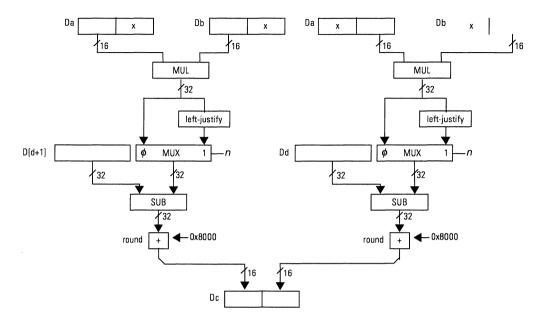

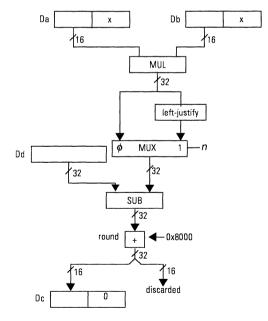

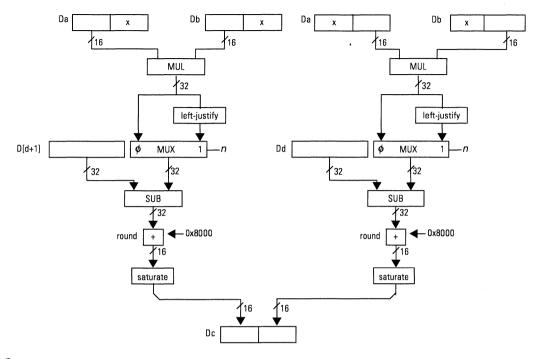

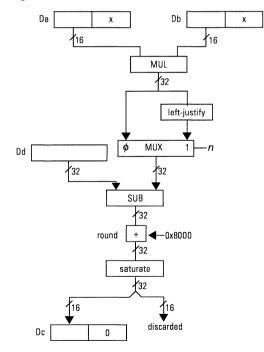

|            | 8.1.2.2 Special case = -1 * -1 => +1                      | 94  |

|            | 8.1.2.3 Guard bits                                        | 95  |

|            | 8.1.2.4 Rounding                                          | 95  |

|            | 8.1.2.5 Overflow and Saturation                           | 95  |

|            | 8.1.2.6 Sticky Advanced Overflow and Block Scaling in FFT | 95  |

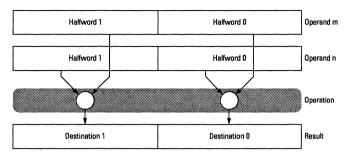

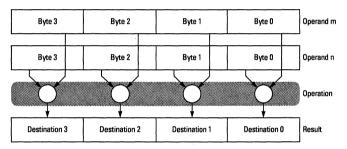

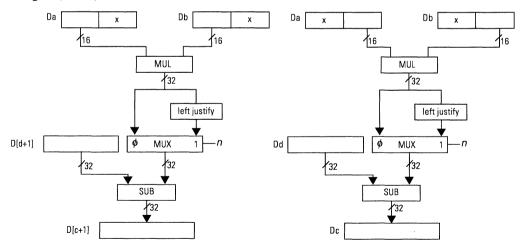

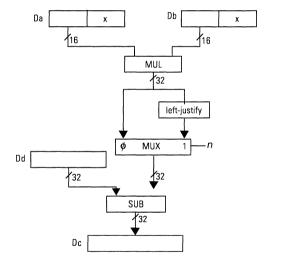

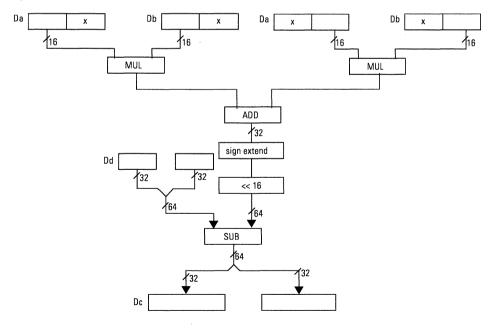

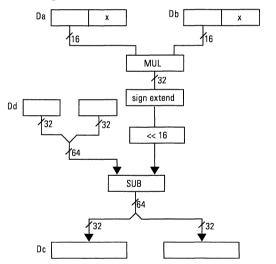

|            | 8.1.3 Packed Arithmetic                                   | 95  |

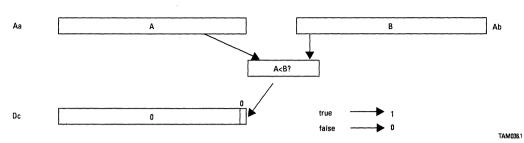

| 8.2        | Compare Instructions                                      | 97  |

| 8.3        | Bit Operations                                            | 00  |

| 8.4        |                                                           | 02  |

| 8.5        |                                                           | 02  |

| 8.6        |                                                           | 03  |

|            |                                                           | 03  |

|            |                                                           | 04  |

|            |                                                           | 04  |

|            | · •                                                       | 05  |

|            |                                                           | 05  |

|            |                                                           | 05  |

| 8.7        |                                                           | 00  |

| 0.7        |                                                           | 06  |

|            |                                                           | 00  |

|            |                                                           | 07  |

| 8.8        |                                                           |     |

| 0.0        |                                                           | 09  |

|            | · · · · · · · · · · · · · · · · · · ·                     | 09  |

| 0.0        | 5 5                                                       | 09  |

| 8.9        | ,                                                         | 10  |

|            |                                                           | 10  |

|            |                                                           | 10  |

|            |                                                           | 10  |

|            |                                                           | 10  |

|            |                                                           | 11  |

|            |                                                           | 11  |

|            |                                                           | 11  |

|            |                                                           | 11  |

|            |                                                           | 12  |

| 8.10       | 16-bit Instructions 1                                     | 12  |

| TRIC       | CORE INSTRUCTION SET                                      | 15  |

| 9.1        |                                                           | 15  |

| 9.2        | •                                                         | 18  |

| 9.3        |                                                           | 20  |

| 9.3<br>9.4 |                                                           | 20  |

| 9.4<br>9.5 |                                                           | 20  |

| 5.5        |                                                           | ۷۷  |

TriCore Architecture Manual

9

| 10 | INDEX                                     | 403 |

|----|-------------------------------------------|-----|

| 11 | GLOBAL PARTNERCHIP FOR SYSTEMS ON SILICON | 407 |

| 1  | TOTAL QUALITY MANAGEMENT                  | 410 |

TriCore Architecture Manual

♦ PRELIMINARY EDITION ♦

х

# SIEMENS HIT

# **List of Figures**

| TriCore: A Modular Instruction Set Architecture                       | 3                                                   |

|-----------------------------------------------------------------------|-----------------------------------------------------|

| Program State Registers                                               | 5                                                   |

| Upper and Lower Contexts                                              | 7                                                   |

| TriCore Data Formats                                                  | 15                                                  |

| Byte Ordering                                                         | 16                                                  |

| Address Map and Memory Model                                          | 18                                                  |

| Translation of Absolute Address to Full Effective Address             | 20                                                  |

| Circular Addressing Mode                                              | 21                                                  |

| Bit-Reverse Addressing                                                | 22                                                  |

| Register Pair for Bit-Reverse Addressing                              | 23                                                  |

| General-Purpose Registers (GPRs)                                      | 29                                                  |

| Program Counter (PC)                                                  | 30                                                  |

| Program Status Word (PSW)                                             | 31                                                  |

| Previous Context Information Register (PCXI)                          | 32                                                  |

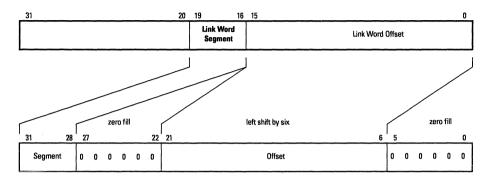

| Generation of the Effective Address for the Context Save Areas (CSAs) | 34                                                  |

| A10/SP                                                                | 35                                                  |

| Interrupt Stack Pointer (ISP)                                         | 35                                                  |

| Interrupt Control Register (ICR)                                      | 36                                                  |

| Interrupt Vector Table Pointer (BIV)                                  | 37                                                  |

| Trap Vector Table Pointer (BTV)                                       | 37                                                  |

| SYSCON Register                                                       | 38                                                  |

| PMUCON Register                                                       | 38                                                  |

| DMUCON Register                                                       | 39                                                  |

| Memory Protection Register Sets                                       | 39                                                  |

| Range Table Entries in a Protection Register Set                      | 40                                                  |

| Data Segment Protection Registers (DPRx_n)                            | 41                                                  |

|                                                                       | Program State Registers<br>Upper and Lower Contexts |

TriCore Architecture Manual

### List of Figures

## SIEMENS

| Figure 27 | Code Segment Protection Registers (CPRx_n)                       | 41  |

|-----------|------------------------------------------------------------------|-----|

| Figure 28 | Data Protection Mode Register (DPMx_n)                           | 41  |

| Figure 29 | Code Protection Mode Register (CPMx_n)                           | 43  |

| Figure 30 | Generation of the Effective Address of a Context Save Area (CSA) | 48  |

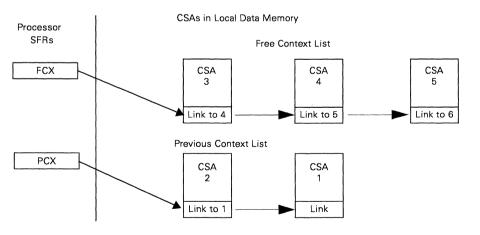

| Figure 31 | CSAs in Context Lists                                            | 49  |

| Figure 32 | CSAs and Processor State Prior to Context Save                   | 52  |

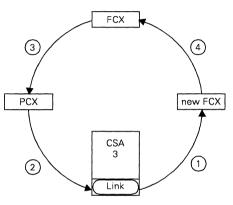

| Figure 33 | CSA and Processor SFR Updates on a Context Save Process          | 53  |

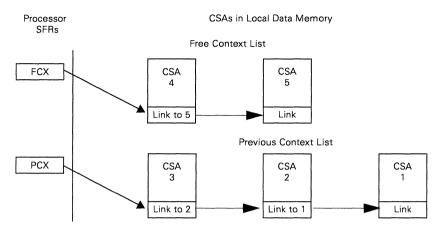

| Figure 34 | CSAs and Processor State After Context Save                      | 54  |

| Figure 35 | CSAs and Processor State Prior to Context Restore                | 54  |

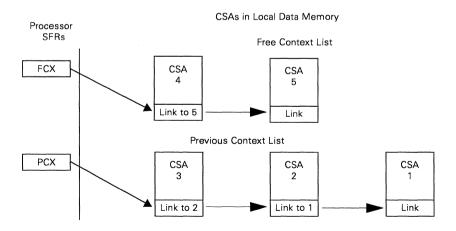

| Figure 36 | CSA and Processor SFR Updates on a Context Restore Process       | 55  |

| Figure 37 | CSAs and Processor State After Context Restore                   | 56  |

| Figure 38 | Block Diagram of Interrupt System                                | 59  |

| Figure 39 | Service Request Control Register (xxSRC)                         | 60  |

| Figure 40 | ICR Register                                                     | 61  |

| Figure 41 | Data Segment Protection Register                                 | 79  |

| Figure 42 | Code Segment Protection Register Pair                            | 80  |

| Figure 43 | Data Protection Mode Register                                    | 80  |

| Figure 44 | Code Protection Mode Register                                    | 80  |

| Figure 45 | Example Configuration of a Data Protection Register Set          | 82  |

| Figure 46 | Protection Boundaries                                            | 83  |

| Figure 47 | Operation of CLZ Instruction                                     | 92  |

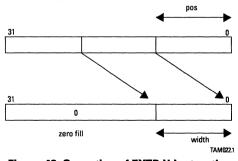

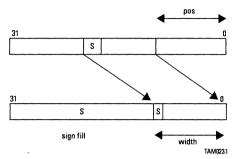

| Figure 48 | Operation of EXTR.U Instruction                                  | 92  |

| Figure 49 | Operation of EXTR Instruction                                    | 93  |

| Figure 50 | Operation of DEXTR Instruction                                   | 93  |

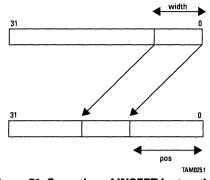

| Figure 51 | Operation of INSERT Instruction                                  | 94  |

| Figure 52 | Packed Halfword Data Format                                      | 96  |

| Figure 53 | Packed Byte Data Format                                          | 96  |

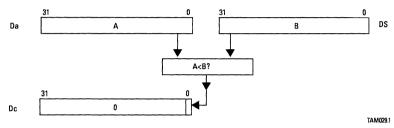

| Figure 54 | LT Comparison                                                    | 97  |

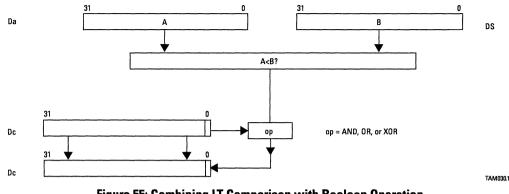

| Figure 55 | Combining LT Comparison with Boolean Operation                   | 98  |

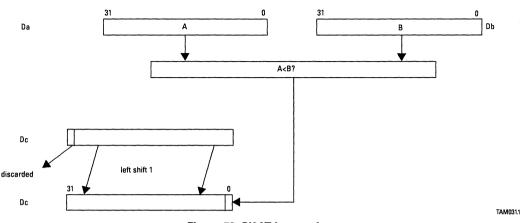

| Figure 56 | SH.LT Instruction                                                | 99  |

| Figure 57 | EQ.B Instruction Operation                                       | 100 |

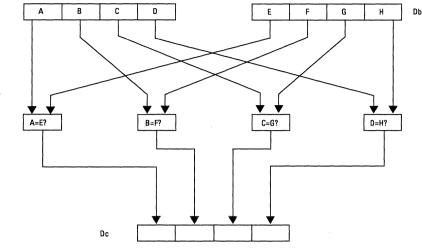

| Figure 58 | Boolean Operations                                               | 100 |

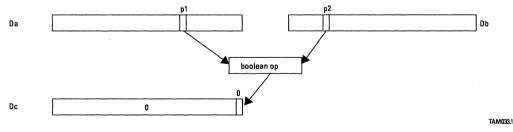

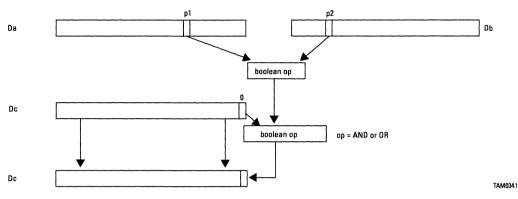

| Figure 59 | 3-Input Boolean Operation                                        | 101 |

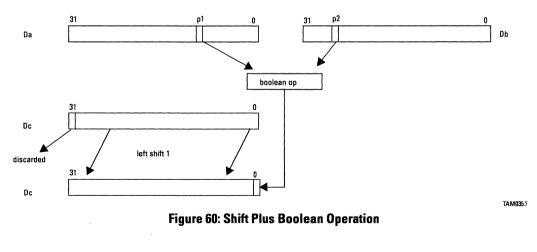

| Figure 60 | Shift Plus Boolean Operation                                     | 101 |

| Figure 61 | LT.A Comparison Operation                                        | 103 |

| Figure 62 | Jump Target Address with Displacement                            | 104 |

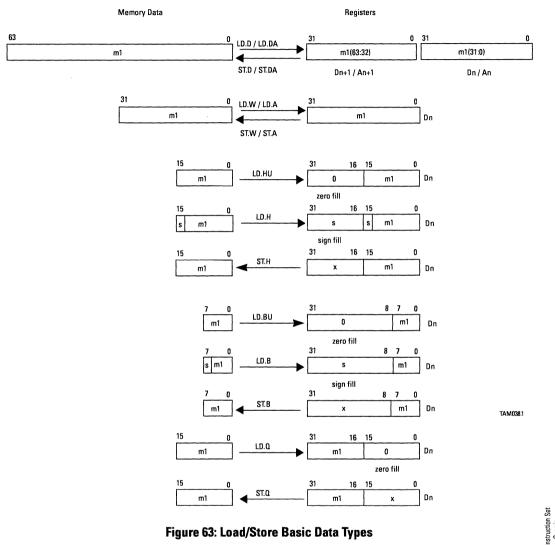

| Figure 63 | Load/Store Basic Data Types                                      | 107 |

| Figure 64 | 32-Bit Instruction Formats                                       | 121 |

| Figure 65 | 16-Bit Instruction Formats                                       | 122 |

TriCore Architecture Manual

# SIEMENS MET

# **List of Tables**

| Table 1  | Addressing Modes of the TriCore Architecture | 20  |

|----------|----------------------------------------------|-----|

| Table 2  | Core Register Map                            | 28  |

| Table 3  | Context Management Registers                 | 33  |

| Table 4  | Memory Protection Registers                  | 40  |

| Table 5  | Debug Registers                              | 44  |

| Table 6  | Context-Related Events and Instructions      | 49  |

| Table 7  | Supported Traps                              | 70  |

| Table 8  | PSW Status Flags                             | 87  |

| Table 9  | Addressing Modes                             | 106 |

| Table 10 | Instruction Syntax Definitions               | 116 |

| Table 11 | Operation Modifiers                          | 117 |

| Table 12 | Data Type Modifiers                          | 118 |

| Table 13 | RTL Syntax Description                       | 119 |

| Table 14 | PSW Status Flags                             | 120 |

|          |                                              |     |

TriCore Architecture Manual

♦ PRELIMINARY EDITION ♦

xiv

## Preface

# Preface

This document contains the following parts:

- Chapter 1, "Architecture Overview," provides a general description of the TriCore architecture and its features.

- Chapter 2, "Programming Model," describes the data formats, data types, addressing modes, and memory model of the TriCore architecture.

- Chapter 3, "Core Registers," describes the core registers, which are categorized according to function.

- Chapter 4, "Managing Tasks and Functions," describes the TriCore's task management operation.

- Chapter 5, "Interrupt System," describes the elements of the TriCore interrupt system including arbitration, the priority level scheme, and interrupt handling.

- Chapter 6, "Traps," lists the eight classes of traps and describes how the TriCore architecture handles traps.

- Chapter 7, "Protection System," describes the components of the TriCore protection system including access permissions and the connection to the debug system.

- Chapter 8, "Instruction Set Overview," describes the instructions by type.

- Chapter 9, "TriCore Instruction Set," describes the individual TriCore instructions.

### Where to Look for More Information

Additional information about the TriCore product line can be found in the following publications. Please call your regional sales office to request these publications.

- TriCore Instruction Set Simulator User's Guide

- TriCore Architectural Overview Handbook

- Introducing TriCore (Brochure)

- TriCore Development Tools (Brochure)

### **Acknowledgments**

We would like to acknowledge the extraordinary effort of all of the individuals who participated in the development and production of this manual, particularly the TriCore Architecture group for providing expertise, input, and technical reviews; and, the Marcom group for the coordination of collateral materials and graphic production of this manual.

TriCore Architecture Manual

## **Architecture Overview**

# **Architecture Overview**

TriCore is the first single-core 32-bit microcontroller-DSP architecture optimized for real-time embedded systems. TriCore unifies the best of three worlds—real-time capabilities of microcontrollers, the computational prowess of DSPs, and the highest performance/price implementations of RISC loadstore architectures.

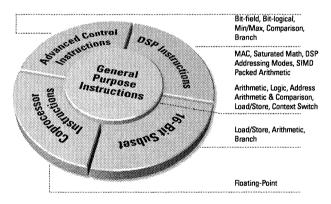

Figure 1 shows a high-level view of the TriCore architecture.

Figure 1: TriCore: A Modular Instruction Set Architecture

The architecture supports a uniform, 32-bit address space, with memory-mapped I/O. It allows for a wide range of implementations, ranging from simple scalar to superscalar. Furthermore, the ISA is capable of interacting with different system architectures, including those with multiprocessing. This flexibility at the implementation and system levels allows for different trade-offs between performance and cost at any point in time.

To support TriCore implementations with 32-bit instructions and simplified instruction fetching, the entire TriCore architecture is represented in 32-bit instruction formats. In addition, the architecture includes 16-bit instruction formats for the most frequently occurring instructions. These instructions

### **Architecture Overview**

significantly reduce code space, lowering memory requirements, system cost, and power consumption.

Real-time responsiveness is largely determined by interrupt latency and context-switch time. The high-performance architecture minimizes interrupt latency by avoiding long multicycle instructions and by providing a flexible hardware-supported interrupt scheme. Furthermore, the architecture supports fast context switching.

## **1.1 TriCore Architecture Feature Overview**

The following list summarizes the basic features of the TriCore architecture.

- 32-bit architecture

- 4-GByte unified data, program, and input/output address space

- 16-/32-bit instructions for reduced code size

- Low interrupt latency

- Fast automatic context switching

- Multiply-accumulate unit

- Saturating integer arithmetic

- Bit handling

- Packed data operations

- Zero-overhead loop

- Flexible power management

- Byte and bit addressing

- Little-endian byte ordering

- Support for big- and little-endian byte ordering at bus interface

- Precise exceptions

- Flexible interrupt prioritization scheme

## **1.2 Program State Registers**

The TriCore program state registers consist of 32 general-purpose registers (GPRs), two 32-bit registers with program status information (PCXI and PSW), and a program counter (PC). PCXI, PSW, and PC are core special function registers (CSFRs).

| 31                     | 0  | 31              | 0 :  | 31     | 0 |

|------------------------|----|-----------------|------|--------|---|

| A15 (Implicit Base Add | r) | D15 (Implicit D | ata) | PCXI   |   |

| A14                    |    | D14             |      | PSW    |   |

| A13                    |    | D13             |      | PC     |   |

| A12                    |    | D12             |      |        |   |

| A11 (Return Address)   |    | D11             |      |        |   |

| A10 (Stack Pointer)    |    | D10             |      |        |   |

| A9                     |    | D9              |      |        |   |

| A8                     |    | D8              |      |        |   |

| A7                     |    | D7              |      |        |   |

| A6                     |    | D6              |      |        |   |

| A5                     |    | D5              |      |        |   |

| A4                     |    | D4              |      |        |   |

| A3                     |    | D3              |      |        |   |

| A2                     |    | D2              |      |        |   |

| A1                     |    | D1              |      |        |   |

| A0                     |    | DO              |      |        |   |

| Address                |    | Data            |      | System |   |

#### **Figure 2: Program State Registers**

The 32 general-purpose registers are divided into 16, 32-bit data registers (D0 through D15) and 16, 32-bit address registers (A0 through A15). Four GPRs have special functions: D15 is used as an implicit data register, A10 is the stack pointer (SP), A11 is the return address register, and A15 is the implicit base address register.

Registers A0 and A1 in the lower address registers and A8 and A9 in the upper address registers are defined as **SYSTEM GLOBAL REGISTERS**. These registers are not included in either context partition, and are not saved and restored across calls or interrupts. The operating system normally uses them to reduce system overhead.

The PCXI and PSW registers contain status flags, previous execution information, and protection information.

Refer to Chapter 3, "Core Registers," for complete information on each register.

## 1.3 Data Types

The TriCore instruction set supports operations on booleans, bit strings, characters, signed fractions, addresses, signed and unsigned integers, and single-precision floating-point numbers. Most instructions work on a specific data type, while others are useful for manipulating several data types.

Refer to Section 2.1, "Data Types," and Section 2.2, "Data Formats," for more specifics on the data types and formats, respectively.

## **1.4 Addressing Modes**

Addressing modes allow load and store instructions to efficiently access simple data elements within data structures like records, randomly and sequentially accessed arrays, stacks, and circular buffers. Simple data elements are 1, 8, 16, 32, or 64 bits wide.

The addressing modes provide efficient compilation of C, easy access to peripheral registers, and efficient implementation of typical DSP data structures (circular buffers for filters and bit-reversed indexing for FFTs). The following seven addressing modes are supported in the Trillium architecture.

- Absolute

- Base + Short Offset

- Base + Long Offset

- Pre-increment or decrement

- Post-increment or decrement

- Circular

- Bit Reverse

Refer to Section 2.4, "Addressing Model," for more details on each addressing mode.

## **1.5 Instruction Formats**

The TriCore architecture supports both 16- and 32-bit instruction formats. All instructions have a 32bit format; the 16-bit instructions are a subset of the 32-bit instructions, chosen because of their frequency of use and are included to reduce code space.

Refer to Chapter 8, "Instruction Set Overview," and Chapter 9, "TriCore Instruction Set," for more detailed information on the 16-bit and 32-bit instruction formats.

## **1.6 Tasks and Contexts**

Throughout this book, the term **TASK** refers to an independent thread of control. There are two types of tasks: **SOFTWARE-MANAGED TASKS (SMTS)** and **INTERRUPT SERVICE ROUTINES (ISRS)**. Software-managed tasks are created through the services of a real-time kernel or OS, and dispatched under the control of scheduling software. ISRs are dispatched by hardware in response to an interrupt. In this architecture, ISR refers only to the code that is invoked by the hardware directly. Software-managed tasks are sometimes referred to as **USER TASKS**, assuming that they will execute in user mode.

Each task is allocated its own permission level. The individual permissions are enabled/disabled primarily by IO mode bits in the Program Status Word (PSW).

Associated with any task is a set of state elements known collectively as the task's **CONTEXT**. The context is everything the processor needs in order to define the state of the associated task and enable its continued execution. It includes the CPU general-purpose registers that the task uses, the

6

task's program counter (PC), and its Program Status Information (PCXI and PSW). The TriCore architecture efficiently manages and maintains the tasks' contexts through hardware.

Chapter 4, "Managing Tasks and Functions," provides more details on task management. The registers associated with task management are described in Section 3.4, "Context Management Registers."

## **1.6.1 Upper and Lower Contexts**

The context is subdivided into the **UPPER CONTEXT** and the **LOWER CONTEXT**, as illustrated in Figure 3. The upper context consists of the upper address registers, A10 - A15, and the upper data registers, D8 - D15. These registers are designated as non-volatile, for purposes of function calling. The upper context also includes the PCXI and PSW registers.

The lower context consists of the lower address registers, A2 through A7, the lower data registers, D0 through D7, and the PC.

Both upper and lower contexts include a LINK WORD. Contexts are saved in fixed- size areas (see next section); they are linked together via the link word.

The upper context is saved automatically on interrupts and is restored on returns. The lower context is saved and restored explicitly by the interrupt service routine (ISR) if the ISR needs to use more registers than provided by the upper context.

Refer to Chapter 4, "Managing Tasks and Functions," for more information.

| Lower Context    |   |

|------------------|---|

| D7               |   |

| D6               |   |

| D5               |   |

| D4               |   |

| D3               |   |

| D2               |   |

| D1               |   |

| DO               |   |

| A7               |   |

| A6               |   |

| A5               |   |

| A4               |   |

| A3               |   |

| A2               |   |

| Saved PC         |   |

| PCXI (Link Word) | i |

| Upper Context    |   |

|------------------|---|

| D15              |   |

| D14              |   |

| D13              |   |

| D12              |   |

| D11              |   |

| D10              |   |

| D9               |   |

| D8               |   |

| A15              |   |

| A14              |   |

| A13              |   |

| A12              | - |

| A11 (RA)         |   |

| A10 (SP)         |   |

| PSW              |   |

| PCXI (Link Word) |   |

|                  | - |

#### Figure 3: Upper and Lower Contexts

### 1.6.2 Context Save Areas

The Trillium architecture uses linked lists of fixed-size **CONTEXT SAVE AREAS** (CSAs), which accommodate systems with multiple interacting threads of control. A CSA is 16 words of on-chip memory storage, aligned on a 16-word boundary. A single CSA can hold exactly one upper or one lower context. Unused CSAs are linked together on a free list. They are allocated from the free list as needed, and returned to it when no longer needed. The processor hardware handles the allocation and freeing. They are transparent to the applications code. Only the system start-up code and certain OS exception handling routines need to access the CSA lists and memory storage explicitly.

## 1.6.3 Fast Context Switching

To increase performance, the TriCore architecture implements a uniform context-switch mechanism for function calls, interrupts, and traps. In all cases, the task's upper context is automatically saved and restored by hardware; saving (and restoring) the lower context is left as an option for the new task.

Fast context switching is further enhanced by the TriCore's unique memory subsystem design, which allows transfers of up to 16 data words between processor registers and memory, thus permitting the entire context to be saved in one operation.

## 1.7 Interrupt System

In this manual, a **SERVICE REQUEST** is defined as an interrupt request from a peripheral, a DMA request, or an external interrupt. For simplicity, a service request may also be referred to as an interrupt.

The entry code for the ISR is a block within a vector of code blocks. Each code block provides an entry for one interrupt source. Each source is assigned a priority number. All priority numbers are programmable. The service routine uses the priority number to determine the location of the entry code block.

The prioritization of service routines enables nested interrupts. A service request can interrupt the servicing of a lower priority interrupt. Interrupt sources with the same priority cannot interrupt each other.

Refer to Chapter 5, "Interrupt System," for more information on service requests and the interrupt system.

## 1.8 Trap System

A trap occurs as a result of an exception within one of the following eight classes:

- Reset

- Internal Protection

- Instruction Errors

TriCore Architecture Manual

♦ PRELIMINARY EDITION ♦

8

Architecture Overview

- Context Management

- Internal Bus and Peripheral Errors

- Assertion

- System Call

- Non-Maskable Interrupt

The entry code for the trap handler is comprised of a vector of code blocks. Each code block provides an entry for one trap. When a trap is taken, the trap's Trap Identification Number (TIN) is placed in data register D15. The trap handler uses the TIN to identify precisely the cause of the trap. The trap with the lowest TIN wins during arbitration.

Refer to Chapter 6, "Traps," for more information.

## **1.9 Protection System**

The protection system allows the programmer to assign access permissions to memory regions for both data and code. This capability is useful for protecting core system functionality from bugs that may have slipped through testing and from transient hardware errors.

The TriCore's protection system also provides the essential features needed to isolate errors, and thus facilitates debugging.

The registers associated with the protection system are defined in Section 3.8, "Memory Protection Registers." Chapter 7, "Protection System," describes the Memory Protection System in more detail. A list of Debug registers is located in Section 3.9, "Debug Registers."

### **1.9.1 Permission Levels**

The TriCore's embedded architecture allows each task to be allocated the specific permission level it needs to perform its function. Individual permissions are enabled through the IO mode bits in the Program Status Word (PSW). The three permission levels are User-0, User-1, and Supervisor:

- **User-0 MODE** is used for tasks that do not access peripheral devices. Tasks at this level do not have permission to enable or disable interrupts.

- USER-1 MODE is used for tasks that access common, unprotected peripherals. Accesses typically include read/write accesses to SIO ports and read accesses to timers and most I/O status registers. Tasks at this level may disable interrupts.

- SUPERVISOR MODE permits read/write access to system registers and protected peripheral devices.

### **1.9.2 Protection Model**

The memory protection model for the TriCore architecture is based on address ranges, where each address range has an associated permission setting. Address ranges and their associated permis-

#### **Architecture Overview**

sions are specified in two to four identical sets of tables residing in core SFR (CSFR) space. Each set is referred to as a **PROTECTION REGISTER SET (PRS)**.

When the protection system is enabled, the TriCore checks every load/store or instruction fetch address for legality before performing the access. To be legal, the address must fall within one of the ranges specified in the currently selected PRS, and permission for that type of access must be present in the matching range.

## 1.10 Reset System

Most of the reset functions and options are located external to the core and are not described in this architecture manual. Several events can force a reset of the TriCore device:

- Power-On Reset: activated through an external pin when the power to the device is turned on (cold reset).

- Hard Reset: activated through an external pin during run time (warm reset).

- Soft Reset: activated through a software write to a reset request register. This register has a special protection mechanism to prevent accidental accesses. Implementation-specific controls in this register facilitate either a partial or a full reset of the device.

- Watchdog Timer Reset: activated through an error condition detected by a watchdog timer.

- Wake-up Reset: activated through an external pin to wake the device from a power saving mode.

A reset status register allows the core to check which one of the different triggers caused the reset.

## 1.11 Debug System

The TriCore contains mechanisms and resources to support on-chip debugging. These are used by the Debug Control Unit, which is an off-core module. Most functions and details of the Debug Control Unit are implementation specific. Thus, this document does not provide further descriptions of the debug control unit and its associated registers. Please contact your local Siemens sales office for literature information.

TriCore Architecture Manual

♦ PRELIMINARY EDITION ♦

Programming Model

**Programming Model**

# **Programming Model**

This chapter discusses the following aspects of the TriCore architecture that are visible to software: the supported data types, the formats of the data types in registers and memory, the various addressing modes that the architecture provides, and the memory model.

## 2.1 Data Types

The TriCore instruction set supports operations on booleans, bit strings, characters, signed fractions, addresses, signed and unsigned integers, and single-precision floating-point numbers. Most instructions operate on a specific data type, while others are useful for manipulating several data types.

| Boolean         | A boolean is either TRUE or FALSE. TRUE is the value one (1) when generated and non-zero when tested; FALSE is the value zero (0). Booleans are produced as the result in comparison and logic instructions, and are used as source operands in logical and conditional jump instructions.                                                                                                                            |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit String      | A bit string is a packed field of bits. Bit strings are produced and used by logical, shift, and bit field instructions.                                                                                                                                                                                                                                                                                              |

| Character       | A character is an eight-bit value that is a very short unsigned integer. No specific coding is assumed.                                                                                                                                                                                                                                                                                                               |

| Signed Fraction | The TriCore architecture supports 16-bit signed fractional data for DSP arithmetic. Data values in this format have a single, high-order sign bit, with a value of 0 or -1, followed by an implied binary point and fraction. Thus their values are in the range [-1,1). When stored in registers, fractional data occupies the register's most-significant 16 bits, with the least-significant 16 bits set to zeros. |

| Address         | An address is a 32-bit unsigned value.                                                                                                                                                                                                                                                                                                                                                                                |

#### Signed/Unsigned Integers

Signed and unsigned integers are normally 32 bits. Shorter signed or unsigned integers are sign-extended or zero-extended to 32 bits when loaded from memory

into a register. Multi-precision integers are supported with addition and subtract using carry. Integers are considered to be bit strings for shifting and masking operations. Multi-precision shifts can be done using a combination of single-precision shifts and bit field extracts.

### IEEE-754 single-precision floating-point number

Depending on the particular implementation of the core architecture, IEEE-754 floating-point numbers are supported by direct hardware instructions or by software emulation.

### 2.2 Data Formats

All the general-purpose registers are 32 bits wide, and most instructions operate on word (32-bit) values. Thus when data with fewer bits than a word is loaded from memory, it must be sign or zero-extended before operations can be applied to the full word.

Alignment requirements differ for addresses and data. Addresses (32 bits) must be aligned on a word boundary to permit transfers between address registers and memory. For transfers between data registers and memory, data may be aligned on any halfword boundary, regardless of size; bytes may be accessed on any valid byte address.

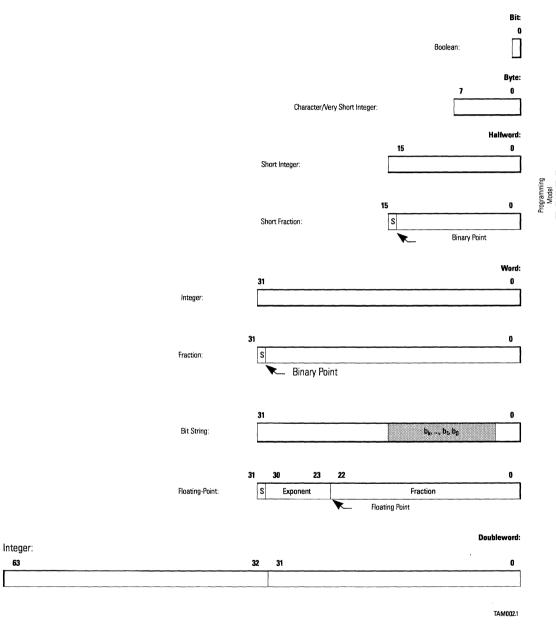

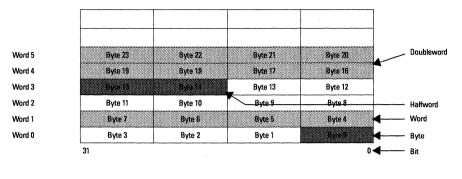

Figure 4 on page 15 illustrates the supported data formats.

TriCore Architecture Manual

### **Programming Model**

2

### Figure 4: TriCore Data Formats

### TriCore Architecture Manual

The data memory and CPU registers store data in little-endian byte order (the least-significant bytes are at lower addresses). Figure 5 illustrates the byte ordering. Little-endian memory referencing is used consistently for data and instructions.

TAM003.1

### **Figure 5: Byte Ordering**

When the TriCore system is connected to an external big-endian device, translation between big- and little-endian format is performed by the bus interface.

As stated previously, bytes must be stored on byte boundaries; halfwords, words, and doublewords must be stored on halfword boundaries.

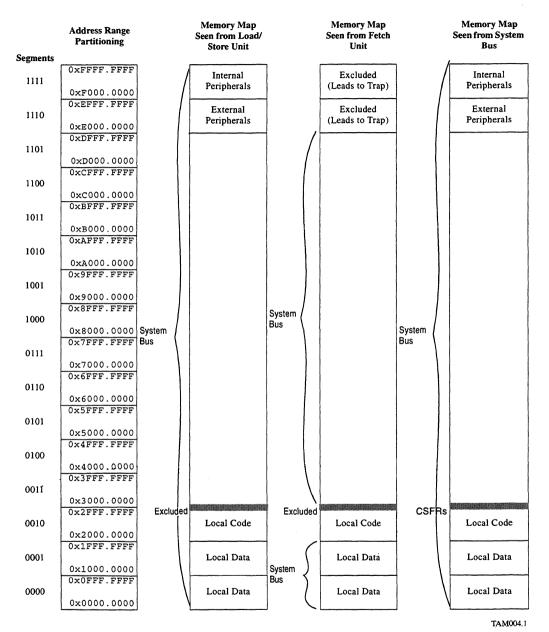

### 2.3 Memory Model

The TriCore architecture can access up to 4 Gbytes of memory. The address width is 32 bits. The address space is divided into 16 regions or segments (0 through 15). Each segment is 256 Mbytes. The upper four bits of an address select the specific segment. The first 16-Kbytes of each segment can be accessed using either absolute addressing or absolute bit addressing.

Segment 0 is the local static data memory space for the core. Segment 1 is the local dynamic data memory space for the core. Segment 2 is the local code memory space for the core. The upper 16-Kbytes of the local code space in Segment 2 are reserved for the core special function registers (CS-FRs).

Segments 14 and 15 are excluded from speculative read accesses. Accesses to this space are initiated only when the core knows that the access will be completed successfully. Segment 14 can be used for external peripherals. FIFOs, peripherals with status registers, and other devices should be located in this address segment so that they will receive no speculative reads that could destroy information. Segment 15 is reserved for the peripheral SFRs (PSFRs) of the internal, on-chip peripherals.

Addresses in Segments 3 through 15 are routed to the System bus. Addresses within Segments 3 through 14 may be either on-chip or off-chip. Devices in the Segment 14 are usually off-chip.

TriCore Architecture Manual

♦ PRELIMINARY EDITION ♦

16

### **Programming Model**

Many data accesses use addresses computed by adding a displacement to the value of a base address register. Using a displacement to cross one of the segment boundaries is not allowed, and, if done, will cause a trap. This restriction allows direct determination of the accessed segment.

Figure 6 shows the TriCore architecture's address space mapping. The figure also shows how the Load/Store Unit, the Instruction Fetch Unit, and other devices on the System bus view the address space.

Figure 6. Address Map and Memory Model

TriCore Architecture Manual

♦ PRELIMINARY EDITION ♦

### **Programming Model**

The Load/Store Unit regards Segments 0 and 1 as the local data memory and the local code Segment 2 as a "data memory" on the System Bus. This means a data access to the local code memory (for example, access to data constants in code memory) by the Load/Store Unit is routed to the code memory via the System Bus. The Load/Store Unit views Segments 2 through 15 to be on the System Bus. No System Bus access is initiated when the unit accesses its local data space in Segments 0 or 1. Accesses to the core SFR space (CSFR) are not allowed and will cause a trap.

The Instruction Fetch Unit regards Segment 2 as the local code memory and the data Segments 0 and 1 as a "code memory" on the System Bus. This means a code access to the local data memory (for example, execute code out of data memory) by the Instruction Fetch Unit is routed to the data memory via the System Bus. Instruction fetches from Segments 14 and 15 are not allowed and will cause a trap. Instruction fetches from the core SFR space (CSFR) are not allowed and will cause a trap.

The System bus views the entire address space. Devices on the System bus can access all resources, including the local code and data memories and the core SFRs.

### 2.4 Addressing Model

The first subsection in this section describes the addressing modes that the TriCore architecture supports. The second subsection describes how extended addressing modes can be synthesized through short instruction sequences.

### 2.4.1 TriCore Addressing Modes

Addressing modes allow load and store instructions to efficiently access simple data elements within data structures such as records, randomly and sequentially accessed arrays, stacks, and circular buffers. Simple data elements are 1, 8, 16, 32, or 64 bits wide.

The TriCore architecture supports seven addressing modes, as listed in Table 1. These addressing modes support efficient compilation of C, easy access to peripheral registers, and efficient implementation of typical DSP data structures (circular buffers for filters and bit-reversed indexing for FFTs). Each addressing mode is described in detail in the following subsections.

| Addressing Mode     | Address Register Use  | Offset Size<br>(bits) |

|---------------------|-----------------------|-----------------------|

| Absolute            | None                  | 18                    |

| Base + Short Offset | Address Register      | 10                    |

| Base + Long Offset  | Address Register      | 16                    |

| Pre-increment       | Address Register      | 10                    |

| Post-increment      | Address Register      | 10                    |

| Circular            | Address Register Pair | 10                    |

| Bit-reverse         | Address Register Pair | -                     |

**Table 1: Addressing Modes of the TriCore Architecture**

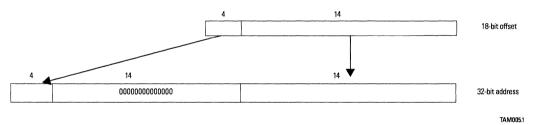

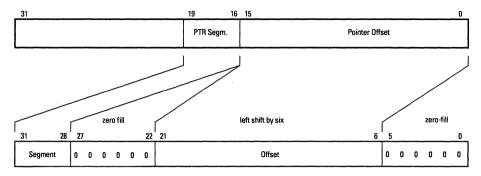

### 2.4.1.1 Absolute Addressing

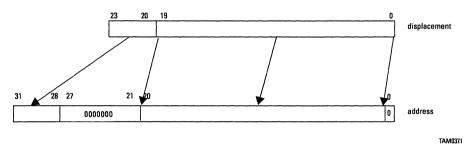

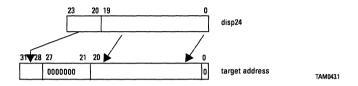

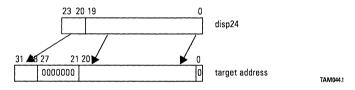

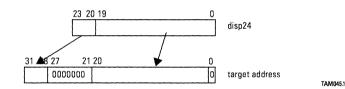

Absolute addressing is useful for referencing I/O peripheral registers and global data. The instruction specifies an 18-bit constant as the memory address. As shown in Figure 7, the full 32-bit address results from moving the four most-significant bits of the 18-bit constant to the four most-significant bits of the 32-bit address. The other bits are zero filled.

### Figure 7: Translation of Absolute Address to Full Effective Address

The special treatment of the four high-order address bits allows absolute addressing to be used in the first 16 KBytes of each address segment.

### 2.4.1.2 Base+Offset Addressing

Base+offset addressing is used for referencing record elements, local variables (using the stack pointer SP as the base), and static data (using an address register pointing to the static data area).

The effective address is the sum of an address register and the sign-extended offset. The size of the offset depends on the specific instruction. A few of the most common load/store instructions that would be generated by a compiler are allocated 16-bit offsets. Less common instructions are allocated 10 bit offsets.

20

### 2.4.1.3 Pre-Increment Addressing

Pre-incrementing and pre-decrementing are used to push data onto an upward or downward growing stack, respectively. The pre-increment addressing mode uses the sum of the address register and the sign-extended 10-bit offset both as the effective address and as the value written back into the address register.

### 2.4.1.4 Post-Increment Addressing

Post-incrementing and post-decrementing allow forward and backward sequential access of arrays, respectively. Post-decrementing uses a negative offset. This mode also can be used to pop down (post-increment) or up (post-decrement) a growing stack.

The post-increment addressing mode uses the value of the address register as the effective address, and then updates this register by adding the sign-extended 10-bit offset to its previous value.

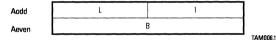

### 2.4.1.5 Circular Addressing

Circular addressing is used primarily for accessing data values in circular buffers while performing filter calculations.

### Figure 8: Circular Addressing Mode

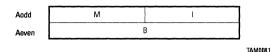

The circular addressing mode uses an address register pair to hold the state it requires. The even register is always a base address (B). The most-significant half of the odd register is the buffer size (L). The least significant half holds the index into the buffer (I). The effective address is (B+I). The buffer occupies memory from addresses B to B + L - 1.

The index is post-incremented using the following algorithm:

```

tmp = I + sign_ext(offset10);

if (tmp < 0)

I = tmp + L;

else if (tmp >= L)

I = tmp - L;

else

I = tmp;

```

The 10-bit offset is specified in the instruction word and is a byte-offset that can be either positive or negative. Note that correct "wraparound" behavior is guaranteed as long as the magnitude of the offset is smaller than size of the buffer.

For example, consider a circular buffer consisting of 25, 16-bit values (50 bytes). If the current index is 48, then the next item is obtained using an offset of 2 (two bytes per value). The new value of the index wraps around to 0. If instead the index is 48 and the offset is 4 (two entries per step), the new value of the index would be 2 ((48 + 4) - 50). If the current index is 4 and the offset is -8, then the new index would be 46 ((4 - 8) + 50).

### **Programming Model**

Note that in the end case where a memory access runs off the end of the circular buffer, the data access also wraps around to the start of the buffer. For example, consider a circular buffer containing n elements, where each element is a 16-bit value. If a load word is performed using the circular addressing mode and the effective address of the operation points to element n-1, the 32-bit result will contain element n-1 in the bottom 16 bits and element 0 in the top 16 bits.

The size and length of a circular buffer have the following restrictions placed on them:

- The start of the buffer start must be aligned to a multiple of the data size, where the data size is determined from the instruction being used to access the buffer. For example, a buffer accessed using a load word instruction must be aligned to a word boundary and a buffer being accessed using a load doubleword must be aligned to a doubleword boundary.

- 2. The length of the buffer must be a multiple of the data size, where the data size is determined from the instruction being used to access the buffer. For example, a buffer accessed using a load word instruction must be a multiple of four in length and a buffer accessed using a load double-word instruction must be a multiple of eight in length.

If the two restrictions are not met, then an alignment trap is taken.

### 2.4.1.6 Bit-Reverse Addressing

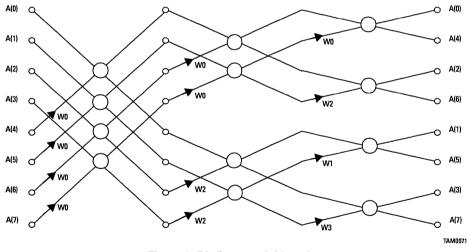

Figure 9 shows bit-reverse addressing, which is used to access arrays used in FFT algorithms. The most common implementation of the FFT ends with results stored in bit-reversed order.

Figure 9: Bit-Reverse Addressing

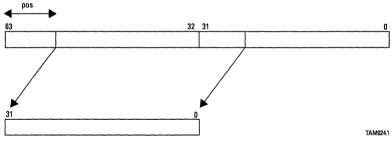

Bit-reverse addressing uses an address register pair to hold the required state (see Figure 10).

TriCore Architecture Manual

### Figure 10: Register Pair for Bit-Reverse Addressing

The even register is the base address of the array (B). The least-significant half of the odd register is the index into the array (I); the most-significant half is the modifier (M), which is added to I after every access.

The effective address is B+I. The index I is post-incremented; its new value is reverse (reverse (I) + reverse (M)), where M is the most-significant half of the odd register. The reverse() function exchanges bit n with bit (15 - n) for n = 0, ..., 7.

### 2.4.2 Synthesized Addressing Modes

This section describes how addressing not supported directly in the hardware addressing modes can be synthesized through short instruction sequences.

### 2.4.2.1 Indexed Addressing

Indexed addressing can be synthesized using the ADDSC.A instruction, which adds a scaled data register to an address register. The scale factor can be one, two, four, or eight for addressing indexed arrays of bytes, halfwords, words, or doublewords.

For support of addressing of indexed bit arrays, the ADDSC.AT instruction scales the index value by one eighth (shifts right three bits) and adds it to the address register. The two low-order bits of the resulting byte address are cleared to give the address of the word containing the indexed bit. To extract the bit, the word containing it is loaded, and the bit index is used in an EXTRACT instruction. A bit field, beginning at the indexed bit position, can be extracted also. To store a bit or bit field at an indexed bit position, ADDSC.AT is used in conjunction with the LDMST (Load/Modify/Store) instruction.

### 2.4.2.2 PC-Relative Addressing

PC-relative addressing is the normal mode for branches and calls. However, the TriCore architecture does not support direct PC-relative addressing of data. The main reason is that the separate on-chip instruction and data memories make data access to the program memory expensive. It typically adds two cycles of added access time.

When PC-relative addressing of data is required, the address of a nearby code label is placed into an address register and used as a base register in base + 16-bit offset mode to access the data. Once the base register is loaded, it can be used to address other PC-relative data items nearby.

A code address can be loaded into an address register in various ways. If the code is statically linked—as it almost always is for embedded systems—then the absolute address of the code label is known, and can be loaded using the LEA instruction (load effective address), or with a sequence to load an extended absolute address (see next subsection below). The absolute address of the PC relative data is also known, and there is no need to synthesize PC-relative addressing.

### **Programming Model**

For code that is dynamically loaded, or assembled into a binary image from position-independent pieces without the benefit of a relocating linker, the appropriate way to load a code address for use in PC-relative data addressing is to use the JL (jump and link) instruction. A jump and link to the next instruction is executed, placing the address of that instruction into the return address register (A11). Before doing so, it is necessary to copy the actual return address of the current function to another register.

### 2.4.2.3 Extended Absolute Addressing

Extended absolute addressing is synthesized using two instructions: the MOVH.A (Move Highword) instruction and the LEA (load effective address). The LEA instruction loads a 32-bit address into an address register. After execution of the MOVH.A instruction, a base + 16-bit offset is used to address data in order to establish a base register.

TriCore Architecture Manual

Core Registers

# **Core Registers**

# **Core Registers**

The TriCore architecture defines a set of Core Special Function Registers (CSFRs). These CSFRs control the operation of the core and provide status information about the core's operation. The CSFRs are split into the following groups:

- Program State Information

- Stack Management

- Context Management

- Interrupt and Trap Control

- System Control

- Memory Protection

- Debug Control

The following sections describe these registers in detail. The CSFRs are complemented by a set of general purpose registers (GPRs). Table 2 shows all CSFRs and GPRs.

Note that most of the memory protection system and debug control unit is implementation specific, therefore, this architecture manual only summarizes these topics. Note also that the reset functions and options are located in a block outside of the core; their functionality is briefly described in this manual. Please contact your local Siemens Sales office for more information on literature availability.

| Table 2: Co | re Regi | ister Ma | p |

|-------------|---------|----------|---|

|-------------|---------|----------|---|

| Register<br>Name | Description                                         | Page # |

|------------------|-----------------------------------------------------|--------|

| D0 - D15         | Data Registers                                      | 29     |

| A0 - A15         | Address Registers                                   | 29     |

| PSW              | Program Status Word                                 | 30     |

| PCXI             | Previous Context Information                        | 32     |

| PC               | Program Counter (read only)                         | 30     |

| FCX              | Free Context List Head Pointer                      | 34     |

| LCX              | Free Context List Limit Pointer                     | 35     |

| ISP              | Interrupt Stack Pointer                             | 35     |

| ICR              | Interrupt Control Register                          | 36     |

| BIV              | Base Address of Interrupt Vector Table              | 37     |

| BTV              | Base Address of Trap Vector Table                   | 37     |

| SYSCON           | System Configuration Register                       | 38     |

| PMUCON           | Program Memory Control Register                     | 38     |

| DMUCON           | Data Memory Control Register                        | 38     |

| DPRx_0 DPRx_3    | Data Segment Protection Register Sets $(x = 0 - 3)$ | 39     |

| CPRx_0 - CPRx_3  | Code Segment Protection Register Sets $(x = 0 - 3)$ | 39     |

| DPMx_0 - DPMx_3  | Data Protection Mode Register Sets (x = 0 - 3)      | 39     |

| CPMx_0 - CPMx_3  | Code Protection Mode Register Sets (x = 0 - 3)      | 39     |

| DBGSR            | Debug Status Register                               | 44     |

| GPRWB            | GPR Write Back Trigger                              | 44     |

| EXEVT            | External Break Input Event Specifier                | 44     |

| SWEVT            | Software Break Event Specifier                      | 44     |

| CREVT            | Core SFR Access Event Specifier                     | 44     |

| TRnEVT           | Trigger Event n Specifier (n = 0, 1)                | 44     |

### 3.1 Access to the Core Registers

The core accesses the CSFRs through two instructions: MFCR and MTCR. The MFCR instruction (Move From Core Register) moves the contents of the addressed CSFR into a data register. MFCR can be executed on any privilege level. The MTCR instruction (Move To Core Register) moves the contents of a data register to the addressed CSFR. To prevent unauthorized writes to the CSFRs, the MTCR instruction can only be executed on the supervisor privilege level.

The CSFRs are also mapped into the top of the local code segment in the memory address space. This mapping makes the complete architectural state of the core visible in the address map. This feature allows efficient debug and emulator support. Note it is not permitted for the core to access the CSFRs through this mechanism— it must use MFCR and MTCR.

There are no instructions allowing bit, bit field or load-modify store accesses to the CSFRs. The RSTV instruction (Reset Overflow Flags) resets only the overflow flags in the PSW, without modifying any of the other PSW bits. This instruction can be executed at any privilege level.

### 3.2 General-Purpose Registers (GPRs)

Figure 11 shows the general-purpose registers. The 32-bit wide general-purpose registers are split evenly into 16 data registers, or DGPRs, (D0 to D15) and 16 address registers, or AGPRs, (A0 to A15). Separation of data and address registers facilitates efficient implementations in which arithmetic and memory operations are performed in parallel. Several instructions allow the interchange of information between data and address registers in order to create or derive table indexes, etc. Two consecutive even-odd data registers can be concatenated to form eight extended-size registers (E0, E2, E4, E6, E8, E10, E12, and E14), in order to support 64-bit values.

| Address GPRs (AGPRs)            | Data GPRs (DGPRs)            |      |

|---------------------------------|------------------------------|------|

| 31 0                            | 31 0                         |      |

| A15 (implicit address register) | D15 (implicit data register) |      |

| A14                             | D14                          | }E14 |

| A13                             | D13                          |      |

| A12                             | D12                          | }E12 |

| A11 (Return Address / RA)       | D11                          |      |

| A10 (Stack Pointer / SP)        | D10                          | }E10 |

| A9 (global address register)    | D9                           |      |

| A8 (global address register)    | D8                           | }E8  |

| A7                              | D7                           |      |

| A6                              | D6                           | }E6  |

| A5                              | D5                           |      |

| A4                              | D4                           | }E4  |

| A3                              | D3                           | )    |

| A2                              | D2                           | }E2  |

| A1 (global address register)    | D1                           |      |

| A0 (global address register)    | D0                           | }E0  |

### Figure 11: General-Purpose Registers (GPRs)

### **Core Registers**

Registers A0, A1, A8, and A9 are defined as **SYSTEM GLOBAL REGISTERS**. Their contents are not saved and restored across calls, traps, or interrupts. Register A10 is used as the stack pointer (SP); register A11 is used to store the return address (RA) for calls and linked jumps and to store the return program counter (PC) value for interrupts and traps. Refer to Chapter 4, "Managing Tasks and Functions," for more information.

While the 32-bit instructions have unlimited used of the GPRs, many 16-bit instructions implicitly use A15 as their address register and D15 as their data register. This implicit use eases the encoding of these instructions into 16 bits.

In order to support 64-bit data values, an even/odd register pair holds these values. In the assembler syntax, these register pairs are either referred to as a pair of 32-bit registers (for example, D9/D8) or as an extended 64-bit register (for example, E8 is the concatenation of D9 and D8, where D8 is the least significant word of E8).

Note that there are no separate floating-point registers—the data registers are used to perform floating-point operations. The floating-point data is saved/restored automatically using the fast context switch support.

The GPRs are an essential part of a task's context. When saving or restoring a task's context to and from memory, the context is split into the upper and lower contexts. Registers A2 through A7 and D0 through D7 are part of the lower context. Registers A10 through A15 and D8 through D15 are part of the upper context. Refer to Section 1.6.1, "Upper and Lower Contexts," on page 7 and Chapter 4, "Managing Tasks and Functions," for more information.

### 3.3 Program State Information (PC, PSW, and PCXI)

The PC, PSW, and PCXI registers hold and reflect program state information. When storing and restoring a task's context, the contents of these registers are an important part of this procedure and are stored/restored or modified during this process.

### 3.3.1 Program Counter

Figure 12 shows the 32-bit program counter (PC). The PC contains the address of the instruction that is currently executing. The PC is part of a task's state information.

31

Program Counter

### Figure 12: Program Counter (PC)

### 3.3.2 Program Status Word (PSW)

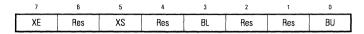

Figure 13 shows the Program Status Word (PSW). The five most-significant bits of PSW contain ALU status flags that are set and cleared by arithmetic instructions. The remaining bits of PSW control the permission levels, protection register sets, and the call depth counter. The PSW is part of a task's state information.

♦ PRELIMINARY EDITION ♦

30

A single instruction, RSTV, resets all overflow status bits (V, SV, AV, SAV). RSTV can be executed at any privilege level.

| 31 | 30 | 29 | 28 | 27  | 26 14 | 13 | 12  | 11 | 10 | 9  | 8  | 7   | 6 0 |

|----|----|----|----|-----|-------|----|-----|----|----|----|----|-----|-----|

| С  | ۷  | S٧ | AV | SAV | Res   | F  | PRS |    | 0  | IS | GW | CDE | CDC |

### Figure 13: Program Status Word (PSW)

C — Carry (Bit 31) This flag is set when a carry occurs.

V --- Overflow (Bit 30) This flag is set when an overflow occurs.

#### SV — Sticky Overflow (Bit 29)

This flag is set when an overflow occurs. This flag remains set until it is explicitly reset by an RSTV (Reset Overflow bits) instruction.

#### AV — Advanced Overflow (Bit 28)

This flag is set when an arithmetic instruction "almost" caused an overflow. This flag is updated after every arithmetic instruction.

#### SAV — Sticky Advanced Overflow (Bit 27)

This flag is set when an arithmetic instruction "almost" caused an overflow. This flag remains set until it is explicitly reset by an RSTV (Reset Overflow bits) instruction.

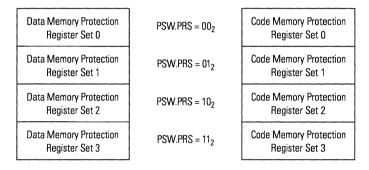

### PRS — Protection Register Set (Bits 13:12)

This two-bit field selects one of up to four sets of memory protection registers.

| 00 | Protection Register Set 0 |

|----|---------------------------|

| 01 | Protection Register Set 1 |

| 10 | Protection Register Set 2 |

| 11 | Protection Register Set 3 |

IO — I/O Privilege (Bits 11:10) This field selects the I/O privilege mode.

| 00 | User-0     |

|----|------------|

| 01 | User-1     |

| 10 | Supervisor |

| 11 | Reserved   |

#### IS — Interrupt Stack (Bit 9)

This bit reflects the status of the current task.

| Γ | 0   | Current task uses a user stack               |

|---|-----|----------------------------------------------|

| ſ | 1 . | Current task uses the global interrupt stack |

#### GW — Global Register Write Permission (Bit 8)

This bit enables write permission to the global registers.

| 0 | Write permission to global registers A0, A1, A8, A9 is disabled |

|---|-----------------------------------------------------------------|

| 1 | Write permission to global registers A0, A1, A8, A9 is enabled  |

### CDE — Call Depth Count Enable (Bit 7)

This bit is the enable for call depth counting.

| 0 | Call depth counting is temporarily disabled. It is automatically re-en-<br>abled following execution of the next Call instruction. |

|---|------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Call depth counting is enabled. If $CDC = 111.1111_2$ , call depth counting is disabled regardless of the setting on this bit.     |

#### CDC — Call Depth Counter (Bits 6:0)

The CDC field consists of two variable-width subfields. The first subfield is a mask field, consisting of a string of zero or more initial "1" bits, terminated by the first "0" bit. The remaining bits comprise the subfield, which constitutes the Call Depth Counter. Refer to Section 7.1.1.6, "CDC," on page 79 for more information on the call depth counter.

Refer to Section 8.1, "Arithmetic Instructions," for more information on the ALU status flags C, V, SV, AV, and SAV. Refer to Chapter 7, "Protection System," for more information on the PRS, IO, GW, CDE, and CDC fields. Refer to Section 4.4, "Context Switching with Interrupts," for more information on the IS bit.

### 3.3.3 Previous Context Information Register (PCXI)

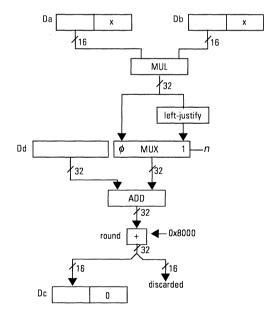

PCXI contains linkage information to the previous execution context, supporting fast interrupts and automatic context switching. The PCXI is part of a task's state information.