8-Bit Single-Chip Microcontroller Handbook

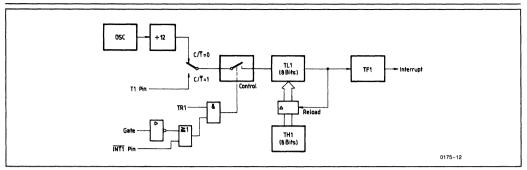

1989/90

## SIEMENS

# 8-Bit Single-Chip Microcontroller Handbook

# SIEMENS

## 8-Bit Single-Chip Microcontroller Handbook

1989/90

#### Published by Siemens Components Inc. 2191 Laurelwood Rd., Santa Clara, CA 95054

For the circuits, descriptions, and tables indicated no responsibility is assumed as far as patents or other rights of third parties are concerned.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery, and prices please contact the Offices of Siemens Components.

#### **Table of Contents** 1 Summary of Types 2 **General Information SAB-51 Architectural Overview** 3 **Microcontroller Components** 4 **Data Sheets** 5 **Instruction Set** SAB 80512/80532 **Single-Chip Microcontroller** 6 User's Manual SAB 80515/80535 7 **Single-Chip Microcontroller** User's Manual Microcontroller Application Notes/Article Reprints 8 Software Support/Development Tools for the SAB-51 Family 9 of Microcontrollers 10 **Summary of Package Outlines Siemens Sales Offices**

# Table of ContentsSummary of Types

### **Table of Contents**

| Page                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 Summary of Types                                                                                                                                                   |

| 2.0 General Information                                                                                                                                                |

| 3.0 SAB-51 Architectural Overview                                                                                                                                      |

| 4.0 8-Bit Single-Chip Microcontroller Components Data Sheets                                                                                                           |

| 4.1 SAB 8051A/8031A, SAB 8051A-16/8031A-16 8-Bit Single Chip Microcontroller Data Sheet4-1                                                                             |

| 4.2 SAB 8051A/8031A Extended Temperature 8-Bit Single-Chip Microcontroller Data Sheet4-14                                                                              |

| 4.3 SAB 8052B/8032B, SAB 8052B-16/8032B-16 8-Bit Single Chip Microcontroller Data Sheet4-19                                                                            |

| 4.4 SAB 8052B/8032B Extended Temperature 8-Bit Single-Chip Microcontroller Data Sheet4-26                                                                              |

| 4.5 SAB 80513-16/80533-16 8-Bit Single-Chip Microcontroller Data Sheet                                                                                                 |

| 4.6 SAB 80512/80532 8-Bit Single-Chip Microcontroller Data Sheet                                                                                                       |

| 4.7 SAB 80515/80535, SAB 80515-16/SAB 80535-16 8-Bit Single Chip Microcontroller Data Sheet 4-47                                                                       |

| 4.8 SAB 80515/80535 Extended Temperature 8-Bit Single-Chip Microcontroller Data Sheet4-70                                                                              |

| 4.9 SAB 80C51/80C31 8-Bit CMOS Microcontroller Data Sheet                                                                                                              |

| 4.10 SAB 80C51/80C31 Extended Temperature 8-Bit CMOS Microcontroller Data Sheet                                                                                        |

| 4.11 SAB 80C52/80C32 8-Bit CMOS Microcontroller Data Sheet                                                                                                             |

| 4.12 SAB 80C515/80C535 8-Bit CMOS Microcontroller Data Sheet                                                                                                           |

| 4.13 SAB 80C517/80C537 High Performance 8-Bit Single-Chip CMOS Microcontroller Data Sheet 4-118                                                                        |

| 5.0 Microcontroller Instruction Set                                                                                                                                    |

| 5.1 Addressing Modes                                                                                                                                                   |

| 5.2 Introduction to the Instruction Set5-2                                                                                                                             |

| 5.3 Instruction Definitions                                                                                                                                            |

| 5.4 Instruction Set Summary                                                                                                                                            |

| 6.0 SAB 80512/80532 Single-Chip Microcontroller User's Manual6-1                                                                                                       |

| 7.0 SAB 80515/80535 Single-Chip Microcontroller User's Manual                                                                                                          |

| 8.0 Microcontrollers Application Notes/Article Reprints8-1                                                                                                             |

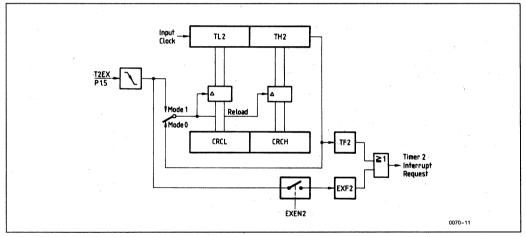

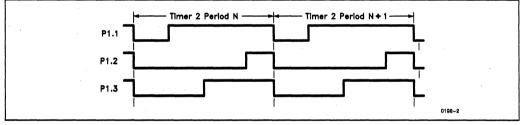

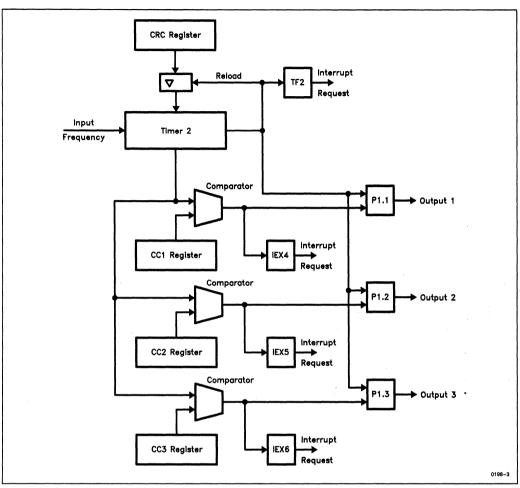

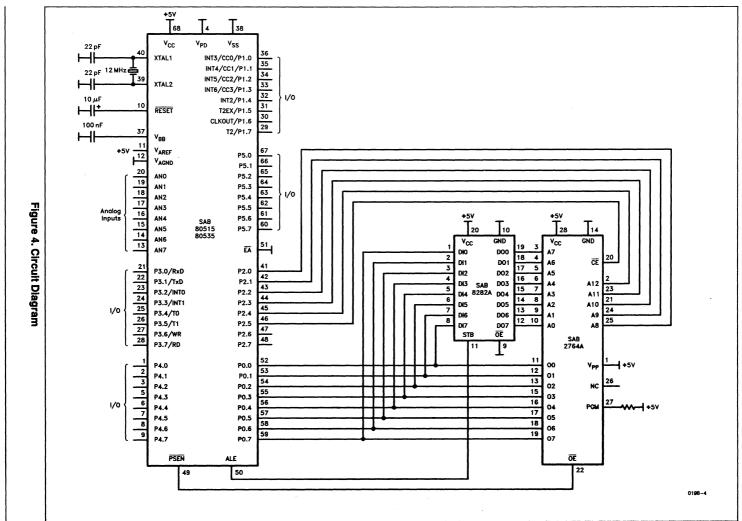

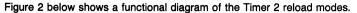

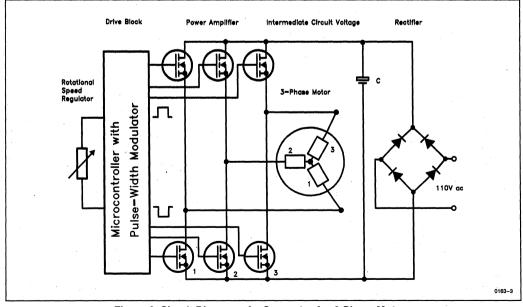

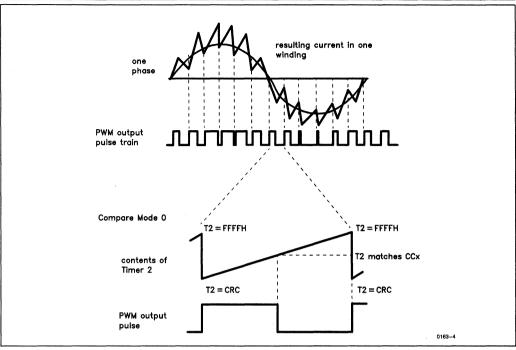

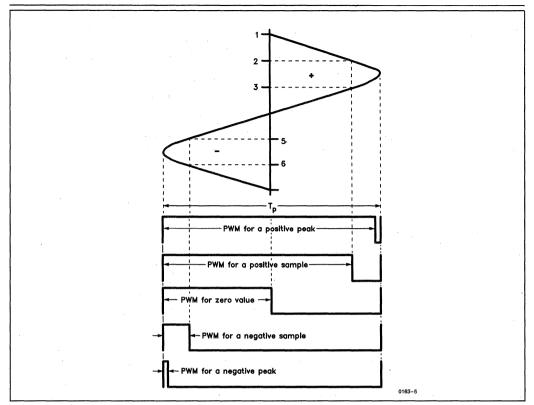

| 8.1 SAB 80515/80535 Application Note: Applications Using Operation of Timer 2<br>in the SAB 80515/80535—Generating Pulse Width Modulated Signals                       |

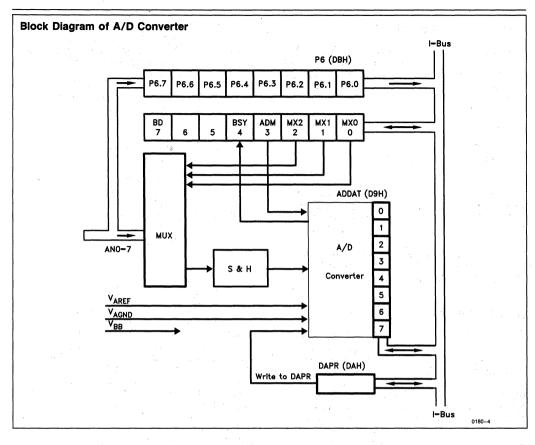

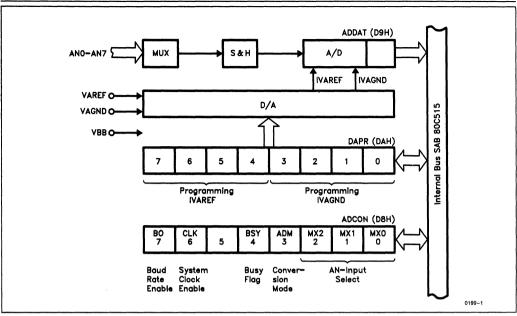

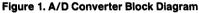

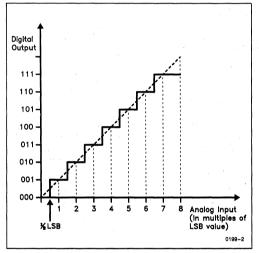

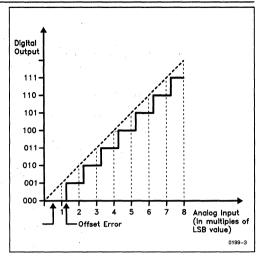

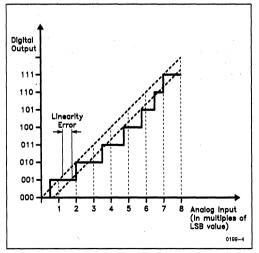

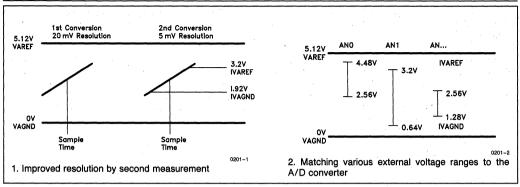

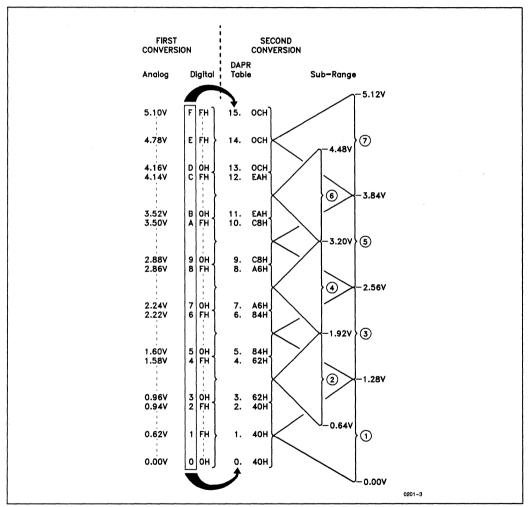

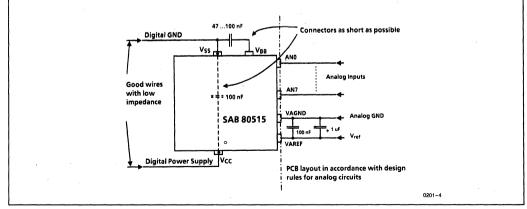

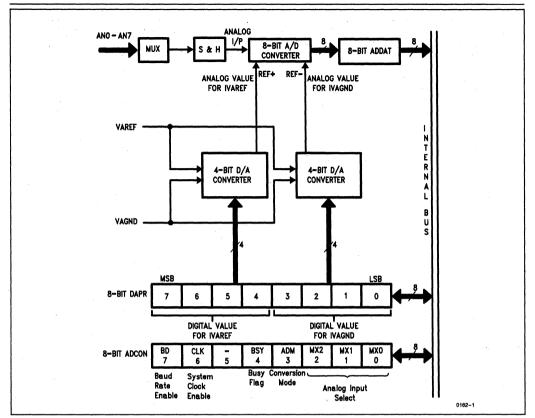

| 8.2 SAB 80515/80535 Application Note: Operation of the A/D Converter in the SAB 80515/805358-11                                                                        |

| 8.3 SAB-51 Family of Microcontrollers Application Note: On-Chip A/D Converters<br>in Siemen's SAB 8051-Based Microcontrollers                                          |

| 8.4 SAB 80515/80535 Application Note: Ten Bits of Resolution with the<br>Eight-Bit On-Chip A/D Converter of the SAB 80515/80535                                        |

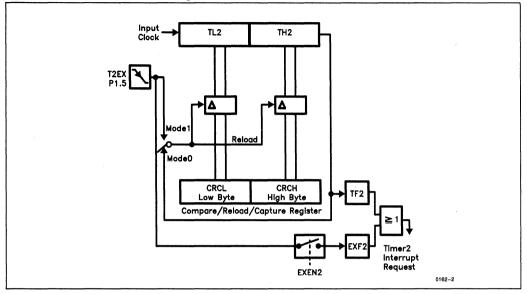

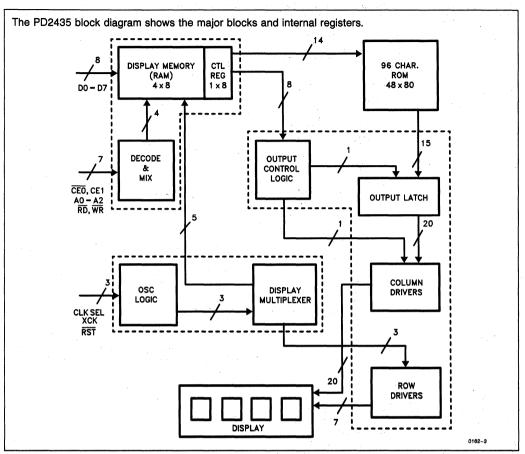

| 8.5 SAB 80515/80535 Application Note: Bidirectional, Speed Regulated Moving<br>Message Display by Using the Timer 2 and 8-Bit A/D Converter of the SAB 80515/805358-42 |

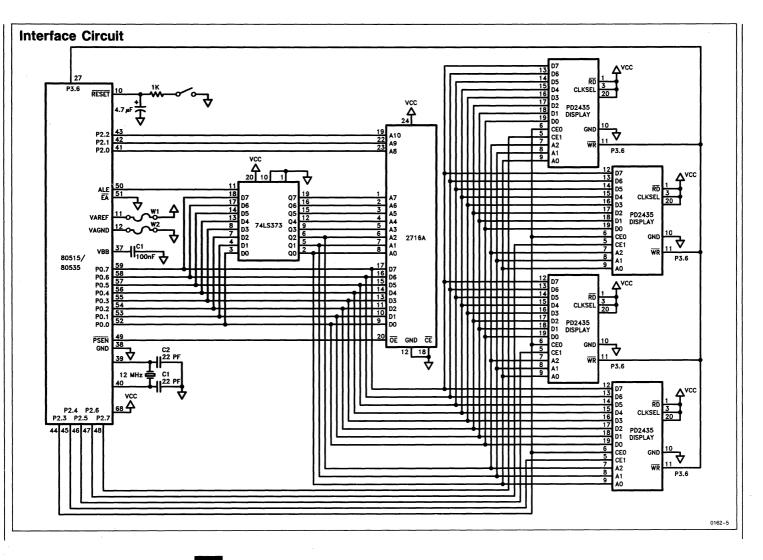

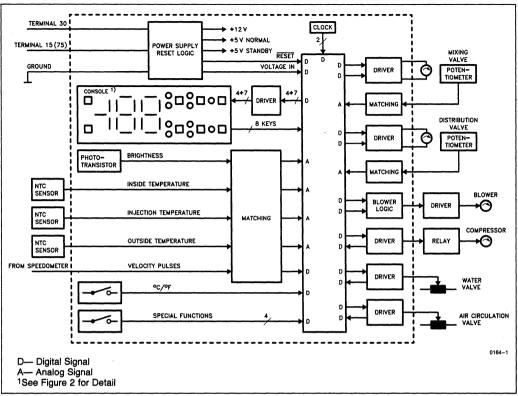

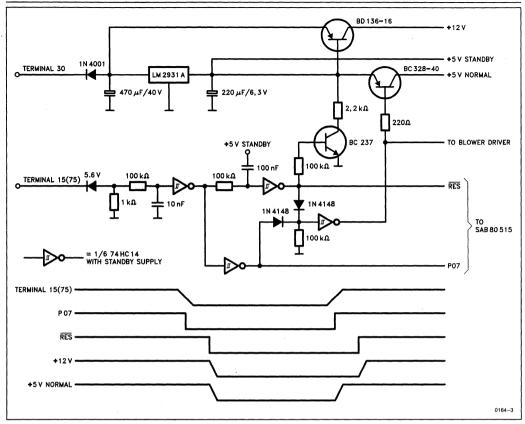

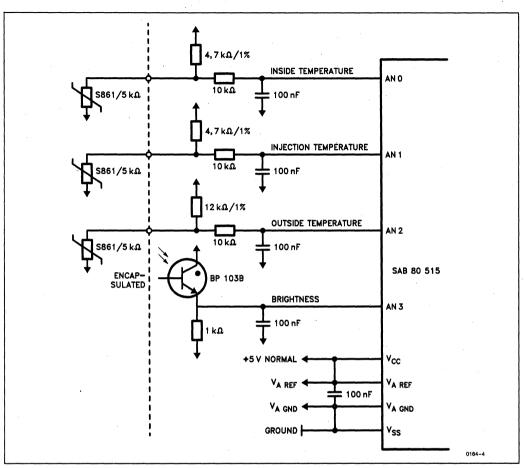

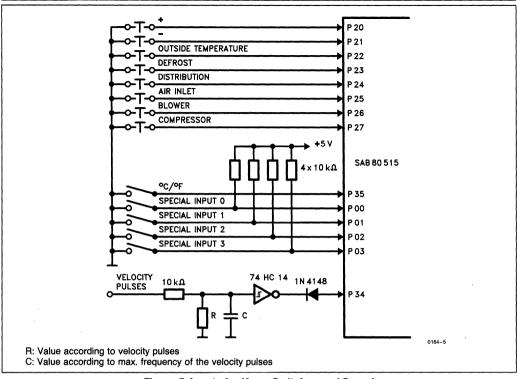

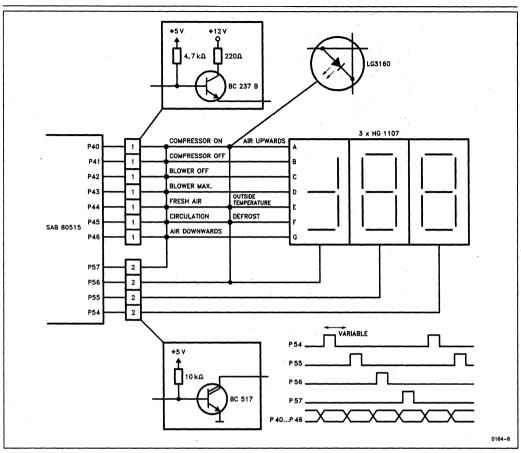

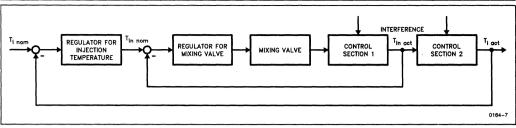

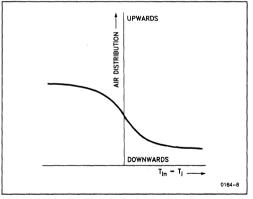

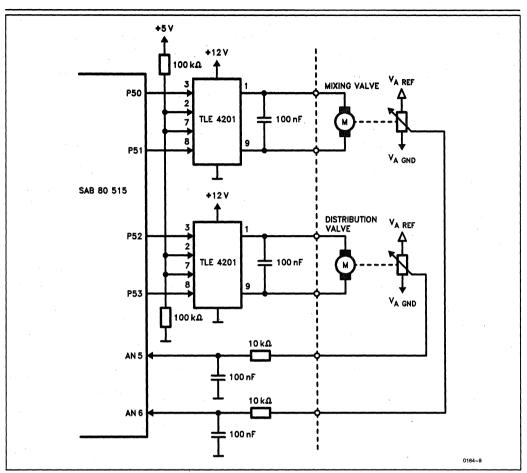

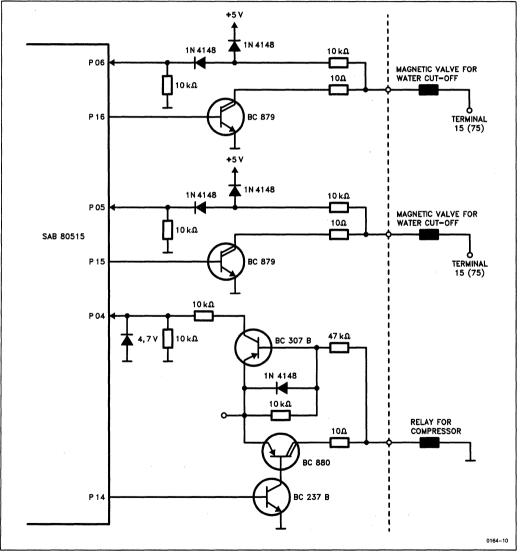

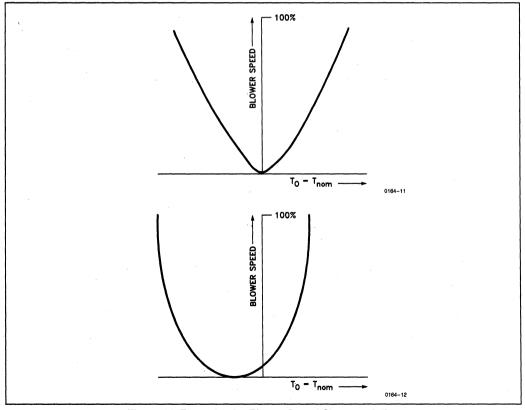

| 8.6 SAB 80515/80535 Application Note: Heating and Air Conditioning in Cars<br>with the Microcontroller SAB 80515/805358-53                                             |

| 8.7 SAB-51 Family Application Note: E <sup>2</sup> PROM Interface with a Siemens 8031 Based Microcontroller .8-67                                                      |

| 8.8 SAB 80515/80535 Article Reprint: Programmable Timer/Counter<br>Register Array in Microcontrollers                                                                  |

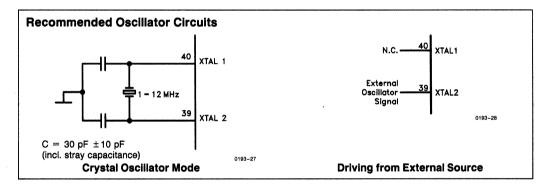

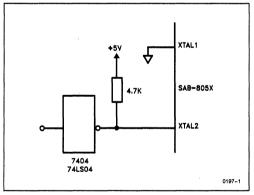

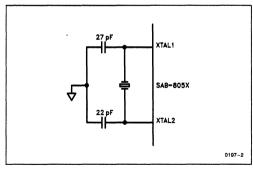

| 8.9 SAB-51 Family Application Brief: Oscillator Design Considerations for<br>SAB-51 Family of Microcontrollers Operating at Frequencies Higher than 16 MHz8-82         |

| 9.0 Software Support/Development Tools for the SAB-51 Family of Microcontrollers                                                                                       |

| 10.0 Summary of Package Outlines                                                                                                                                       |

| 11.0 Siemens Sales Offices                                                                                                                                             |

#### Summary of Types

| Туре                    | Package      | Description/Speed             |

|-------------------------|--------------|-------------------------------|

| 8-Bit Single-Chip Micro | ocontrollers |                               |

| SAB 8031A-N             | PLCC 44      | without ROM, 12 MHz           |

| SAB 8031A-P             | P-DIP 40     | without ROM, 12 MHz           |

| SAB 8031A-16-N          | PLCC 44      | without ROM, 16 MHz           |

| SAB 8031A-16-P          | P-DIP 40     | without ROM, 16 MHz           |

| SAB 80C31-N             | PLCC 44      | without ROM, CMOS, 12 MHz     |

| SAB 80C31-P             | P-DIP 40     | without ROM, CMOS, 12 MHz     |

| SAB 8032B-N             | PLCC 44      | without ROM, 12 MHz           |

| SAB 8032B-P             | P-DIP 40     | without ROM, 12 MHz           |

| SAB 8032B-16-N          | PLCC 44      | without ROM                   |

| SAB 8032B-16-P          | P-DIP 40     | without ROM, 16 MHz           |

| SAB 80C32-N             | PLCC 44      | without ROM, CMOS, 12 MHz     |

| SAB 80C32-P             | P-DIP 40     | without ROM, CMOS, 12 MHz     |

| SAB 8051A-N             | PLCC 44      | 4K x 8-bit, ROM, 12 MHz       |

| SAB 8051A-P             | P-DIP 40     | 4K x 8-bit, ROM, 12 MHz       |

| SAB 8051A-16-N          | PLCC 44      | 4K x 8-bit, ROM, 16 MHz       |

| SAB 8051A-16-P          | P-DIP 40     | 4K x 8-bit, ROM, 16 MHz       |

| SAB 80C51-N             | PLCC 44      | 4K x 8-bit, ROM, CMOS, 12 MHz |

| SAB 80C51-P             | P-DIP 40     | 4K x 8-bit, ROM, CMOS, 12 MHz |

| SAB 8052B-N             | PLCC 44      | 4K x 8-bit, ROM, 12 MHz       |

| SAB 8052B-P             | P-DIP 40     | 8K x 8-bit, ROM, 12 MHz       |

| SAB 8052B-16-N          | PLCC 44      | 8K x 8-bit, ROM, 16 MHz       |

| SAB 8052B-16-P          | P-DIP 40     | 8K x 8-bit, ROM, 16 MHz       |

| SAB 80C52-N             | PLCC 44      | 8K x 8-bit, ROM, CMOS, 12 MHz |

| SAB 80C52-P             | P-DIP 40     | 8K x 8-bit, ROM, CMOS, 12 MHz |

| SAB 80512-N             | PLCC 68      | 4K x 8-bit, ROM, 12 MHz       |

| SAB 80513-N             | PLCC 44      | 16K x 8-bit, ROM, 12 MHz      |

| SAB 80513-P             | P-DIP 40     | 16K x 8-bit, ROM, 12 MHz      |

| SAB 80513-16-N          | PLCC 44      | 16K x 8-bit, ROM, 16 MHz      |

| SAB 80513-16-P          | P-DIP 40     | 16K x 8-bit, ROM, 16 MHz      |

| SAB 80515-N             | PLCC 68      | 8K x 8-bit, ROM, 12 MHz       |

| SAB 80515-16-N          | PLCC 68      | 8K x 8-bit, ROM, 16 MHz       |

| SAB 80C515-N            | PLCC 68      | 8K x 8-bit, ROM, CMOS, 12 MHz |

| SAB 80C517-N            | PLCC 84      | 8K x 8-bit, ROM, CMOS, 12 MHz |

| SAB 80532-N             | PLCC 68      | without ROM, 12 MHz           |

| SAB 80533-N             | PLCC 44      | without ROM, 12 MHz           |

| SAB 80533-P             | P-DIP 40     | without ROM, 12 MHz           |

| SAB 80535-N             | PLCC 68      | without ROM, 12 MHz           |

| SAB 80535-16-N          | PLCC 68      | without ROM, 16 MHz           |

| SAB 80C535-N            | PLCC 68      | without ROM, CMOS, 12 MHz     |

| SAB 80C537-N            | PLCC 84      | without ROM, CMOS, 12 MHz     |

#### Summary of Types (Continued)

| Туре                             | Package                | Description/Speed                        |

|----------------------------------|------------------------|------------------------------------------|

| 8-Bit Single-Chip Microcontrolle | rs Extended Temperatur | e Range                                  |

| SAB 8031A-10-P-T40/110           | P-DIP 40               | -40°C to +110°C                          |

| SAB 8031A-12-P-T40/85            | P-DIP 40               | −40°C to +85°C                           |

| SAB 8031-N-T40/85                | PLCC 44                | -40°C to +85°C, CMOS                     |

| SAB 80C31-P-T40/85               | P-DIP 40               | $-40^{\circ}$ C to $+85^{\circ}$ C, CMOS |

| SAB 8032B-N-T40/85               | PLCC 44                | −40°C to +85°C                           |

| SAB 8032B-P-T40/85               | P-DIP 40               | -40°C to +85°C                           |

| SAB 8032B-P-T40/100              | P-DIP 40               | -40°C to +100°C                          |

| SAB 8051A-10-P-T40/110           | P-DIP 40               | -40°C to +110°C                          |

| SAB 8051A-12-P-T40/85            | P-DIP 40               | -40°C to +85°C                           |

| SAB 80C51-N-T40/85               | PLCC 44                | -40°C to +85°C, CMOS                     |

| SAB 80C51-P-T40/85               | P-DIP 40               | -40°C to +85°C, CMOS                     |

| SAB 8052B-N-T40/85               | PLCC 44                | -40°C to +85°C                           |

| SAB 8052B-P-T40/85               | P-DIP 40               | -40°C to +85°C                           |

| SAB 8052B-P-T40/100              | P-DIP 40               | -40°C to +100°C                          |

| SAB 80512-N-T40/85               | PLCC 68                | -40°C to +85°C                           |

| SAB 80515-N-T40/85               | PLCC 68                | -40°C to +85°C                           |

| SAB 80515-N-T40/110              | PLCC 68                | -40°C to +110°C                          |

| SAB 80C515-N-T40/85              | PLCC 68                | -40°C to +85°C, CMOS                     |

| SAB 80C517-N-T40/85              | PLCC 84                | -40°C to +85°C, CMOS                     |

| SAB 80532-N-T40/85               | PLCC 68                | -40°C to +85°C                           |

| SAB 80535-N-T40/85               | PLCC 68                | -40°C to +85°C                           |

| SAB 80535-N-T40/110              | PLCC 68                | -40°C to +110°C                          |

| SAB 80C535-N-T40/85              | PLCC 68                | $-40^{\circ}$ C to $+85^{\circ}$ C, CMOS |

| SAB 80C537-N-T40/85              | PLCC 84                | -40°C to +85°C, CMOS                     |

#### **General Information**

# SIEMENS

### **General Information**

#### Type Designation Code of ICs

IC type designations are based on the Eurpoean Pro Electron System. The code system is explained in the Pro Electron brochure D 15, edition 1985, available at:

Pro Electron, Avenue Louise, 430 (B.12) B-1060 Brussels, Belgium

#### **Mounting Instructions**

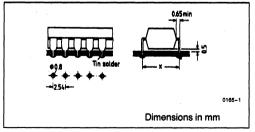

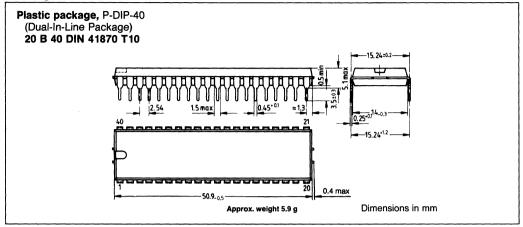

#### Plastic Package (Dual In-Line)

The 90° pins fit into holes with a diameter of 0.7mm to 0.9mm, spaced 2.54mm apart. See spacing x in Figure 1.

The bottom of the package will not touch the PC board after insertion because the pins have shoulders just below the package (see Figure 1).

After insertion of the package into the PC board it is advisable to bend the ends of two pins at an angle of approx. 30° to the board so that the package does not have to be pressed down during soldering. Plastic packages are soldered on that side of the PCB facing away from the package.

The maximum permissible soldering temperature is 350°C (max. 3s) for hand soldering and 260°C (max. 10s) for dip soldering and wave soldering.

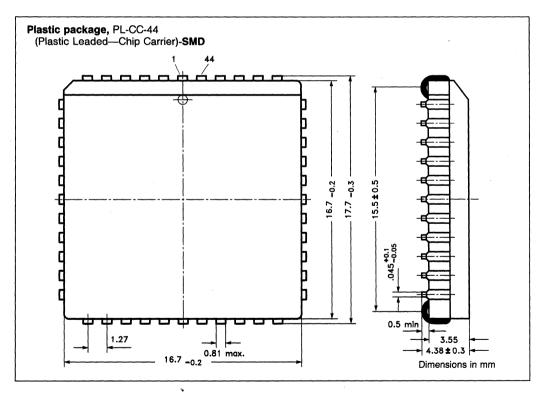

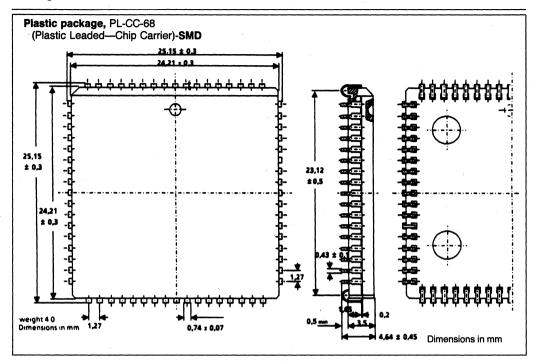

### Plastic Packages (SO and PLCC) for Surface Mounting (SMD)

| Iron Soldering:                                                          | Soldering temperature<br>350°C for max. 3s; minimum<br>distance between package<br>and soldering point 1.5mm<br>package temperature max.<br>150°C; no mechanical<br>stress on the pins |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vapor phase soldering:                                                   | Soldering temperature 215°C, max. soldering time 40s                                                                                                                                   |

| Wave soldering:<br>(pins and package<br>are dipped into<br>the tin bath) | Soldering temperature 260°C, max. soldering time 8s                                                                                                                                    |

### Storage, Pretreatment before Processing

The components are to be stored in a dry environment. When solder methods causing solder heat shock stresses are used (reflow soldering where the component is dipped into the solder bath, vaporphase soldering) it is recommendable to subject IC's in plastic packages to a 24-hour drying phase at 125°C.

#### **Other Points to Note**

Ensure that no current is able to flow between the solder bath or soldering iron and the PCB. It is advisable to ground the pins that are to be soldered as well as the solder bath or soldering iron.

When the pins are being prepared and inserted in a PCB, circuits should be protected against static charge. Under no circumstances should the components be removed or inserted while the operating voltage is switched on.

The increase in chip temperature during the soldering process results in a temporary increase in electrostatic sensitivity of integrated circuits. Special precautions should therefore be taken against line transients, e.g. through the switching of inductances on magnetic chutes, etc.

#### Processing Guidelines for ICs

Integrated circuits (ICs) are electrostatic-sensitive (ESS) devices. The requirement for greater packing density has led to increasingly small structures on semiconductor chips with the result that today every IC, whether bipolar, MOS, or CMOS, has to be protected against electrostatics.

MOS and CMOS devices generally have integrated protective circuits and it is hardly possible any more for them to be destroyed by purely static electricity. On the other hand, there is acute danger from electrostatic discharge (ESD).

Of the multiple of possible sources of discharge, charged devices should be mentioned in additon to charged persons. With low-resistive discharges it is possible for peak power amounting to kilowatts to be produced.

For the protection of devices the following principles should be observed:

- a. Reduction of charging voltage, below 200V if possible. Means which are effective here are an increase in relative humidity to  $\geq$  60% and the replacement of highly charging plastics by antistatic materials.

- b. With every kind of contact with the device pins a charge equalization is to be expected. This should always be highly resistive (ideally  $R = 10^6 \Omega$  to  $10^8 \Omega$ ).

All in all this means that ICs call for special handling, because uncontrolled charges, voltages from ungrounded equipment or persons, surge voltage spikes and similar influences can destroy a device. Even if devices have protective circuits (e.g. protective diodes) on their inputs, the following guidelines for their handling should nevertheless be observed.

#### Identification

The packing of ESS devices is provided with the following label by the manufacturer:

#### Scope

The guidelines apply to the storage, transport, testing, and processing of all kinds of ICs, as well as the soldered circuit boards equipped with such components.

#### Handling of Devices

- 1. ICs must be left in their containers until they are processed.

- 2. ICs may only be handled at specially equipped work stations. These stations must have work surfaces covered with a conductive material of the order of  $10^6 \Omega/cm$ . to  $10^9 \Omega/cm$ .

- 3. With humidity of >50% a coat of pure cotton is sufficient. In the case of chargeable synthetic fibers the clothing should be worn close-fitting. The wrist strap must be worn snugly on the skin and be grounded through a resistor of 50 k $\Omega$  to 100 k $\Omega$ .

- 4. If conductive floors,  $R = 5 \times 10^4 \Omega$  to  $10^7 \Omega$  are provided, further protection can be achieved by using so-called MOS chairs and shoes with a conductive sole ( $R \approx 10^5 \Omega$  to  $10^7 \Omega$ ).

- 5. All transport containers for ESS devices and assembled circuit boards must first be brought to the same potential by being placed on the work surface or touched by the operator before the individual devices may be handled. The potential equalization should be through a resistor of  $10^6\Omega$ to  $10^8\Omega$ .

- 6. When loading machines and production devices it should be noted that the devices come out of the transport magazine charged and can be damaged if they touch metal, e.g. machine parts.

Example 1. Conductive (black) tubes.

The devices may be destroyed in the tube by charged persons or come out of the tube charged if this is emptied by a charged person. Conductive tubes may only be handled at ESS work stations (high-resistance work-station and person grounding).

Example 2. Anti-static (transparent) tubes.

The devices cannot be destroyed by charged persons in the tube (there may be a rare exception in the case of custom ICs with unprotected gate pins). The devices can be endangered as in 1) when the tube is emptied if the latter, especially at low humidity, is no longer sufficiently antistatic after a long period of storage (> 1 year). In both cases damage can be avoided by discharging the devices through a grounded adapter of high-resistance material ( $\approx 10^6 \Omega/\text{cm}$  to  $10^8 \Omega/\text{cm}$ ) between the tube and the machine.

The use of metal tubes—especially of anodized aluminum—is not advisable because of the danger of low-resistance device discharge.

#### Storage

ESS devices should only be stored in identified locations provided for the purpose. During storage the devices should remain in the package in which they are supplied. The storage temperature should not exceed 60°C.

#### Transport

ESS devices in approved packing tubes should only be transported in suitable containers of conductive or longterm anti-static-treated plastic or possible unvarnished wood. Containers of high-charging plastic or very low-resistance materials are likewise unsuitable.

Transfer cars and their rollers should exhibit adequate electrical conductivity ( $R < 10^6 \Omega$ ). Sliding contacts and grounding chains will not reliably eliminate charges.

#### **Incoming Inspection**

In incoming inspection the above guidelines should be observed. Otherwise any right for refund or replacement if devices fail inspection may be lost.

#### **Material and Mounting**

- The drive belts of machines used for the processing of the devices, in as much as they come into contact with them (e.g. bending and cutting machines, conveyor belts), should be treated with anti-static spray (e.g. anti-static spray 100 from Kontaktchemie). It is better, however, to avoid the contact completely.

- If ESS devices have to be soldered or desoldered manually, soldering irons with thyristor control cannot be used. Siemens EMI-suppression capacitors of the type B 81711-B31-B36 have proven very effective against line transients.

- 3. Circuit boards fitted and soldered with ESS devices are always to be considered as endangered.

#### **Electrical Tests**

- The devices should be processed with observation of these guidelines. Before assembled and soldered circuit boards are tested, remove any shorting ring.

- 2. Test sockets must not be conducting any voltage when individual devices or assembled circuit boards are inserted or withdrawn, unless works' specifications state otherwise. Ensure that the test devices do not produce any voltage spikes, either when being turned on and off in normal operation or if the power fuse blows or other fuses respond.

- Signal voltages may only be applied to the inputs of ICs when or after the supply voltage is turned on. They must be disconnected before or when the supply voltage is turned off.

- 4. Observe any notes and instructions in the respective data books/sheets.

#### Packing of Assembled PC Boards or Flatpack Units

The packing material should exhibit low volume conductivity:

$10^5 \,\Omega/cm < \rho < 10^{10} \,\Omega/cm$ .

In most cases—especially with humidity of > 40% this requirement is fulfilled using simple corrugated board. Better protection is obtained with bags of conductive polyethylene foam (e.g. RCAS 1200 from Richmond of Redlands, California).

It must always be ensured that boards do not touch.

In special cases it may be necessary to provide protection against strong electric fields, such as can be generated by conveyor belts for example. For this purpose a sheath of aluminum foil is recommended, although direct contact between the film and the PCB must be avoided. Cardboard boxes with an aluminum-foil lining, such as those used for shipping of our devices, are available from Laber of Munich.

#### **Ultrasonic Cleaning of ICs**

The following recommendation applies to plastic packages. For cavity packages (metal and also ceramic) separate regulations have to be observed.

Freon and isopropyl alcohol (trade name: propanol) can be used as solvents. These solvents can also be used for plastic packages because they do not eat into the plastic material. An ultrasonic bath in double halfwave operation is advisable because of the low component stress.

The ultrasonic limits are as follows:

| sound frequency            | f > 40 kHz             |

|----------------------------|------------------------|

| exposure                   | t < 2 min              |

| alternating sound pressure | p < 0.29 bar           |

| sound power                | $N < 0.5 W/cm^2/liter$ |

#### **Data Classification**

#### **Maximum Ratings**

Maximum ratings are absolute ratings; exceeding only one of these values may cause irreversible damage to the integrated circuit.

#### **Characteristics**

The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics will apply at  $T_A = 25^{\circ}$ C and for the given supply voltage.

#### **Operating Range**

In the operating range the functions given in the circuit description wil be fulfilled.

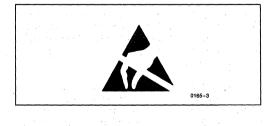

#### **Quality Assurance System**

The high quality and reliability of integrated circuits from Siemens is the result of a carefully arranged production which is systematically checked and controlled at each production stage.

The procedures are subject to a quality assurance system; full details are given in the brochure "Siemens Quality Assurance—Integrated Circuits' (SQS-IC).

Figure 2 shows the most important stages of the "SQS-IC". A quality assurance (QA) department which is independent of production and development, is responsible for the selected control measures, acceptance procedures, and information feedback loops. This department has state-of-theart test and measuring equipment at its disposal, works according to approved methods of statistical quality control, and is provided with facilities for accelerated life and environmental tests used for both qualification and routine monitoring test.

Figure 2. Quality Assurance System

© Siemens Components, Inc.

The latest methods and equipment for preparation and analysis are employed to achieve continuity of quality and reliability.

#### Conformance

Each integrated circuit is subjected to a final test at the end of the production process. These tests are carried out by computer-controlled, automatic test systems because hundreds of thousands of operating conditions as well as a large number of static and dynamic parameters have to be considered. Moreover, the test systems are extremely reliable and reproducible. The quality assurance department carries out a final check in the form of a lot-by-lot sampling inspection to additionally ensure this minimum percent defectives as well as the acceptable quality level (AQL). Sampling inspection is performed in accordance with the inspection plans of DIN 40080, as well as of the identical MIL-STD-105 or IEC 410.

#### Reliability

#### **Measures Taken during Development**

The reliability of ICs is already considerably influenced at the development stage. Siemens has, therefore, fixed certain design standards for the development of circuit and layout, specifying e.g. minimum width and spacing of conductive layers on a chip, dimensions and electrical parameters of protective circuits for electrostatic charge, etc. An examination with the aid of carefully arranged programs operated on large-scale computers, guarantees the immediate identification and elimination of unintentional violations of these design standards.

#### **In-Process Control during Production**

The manufacturing of integrated circuits comprises several hundred production steps. As each step is to be executed with utmost accuracy, the in-process control is of outstanding importance. Some processes require more than a hundred different test measures. The tests have been arranged such that the individual process steps can be reproduced continuously.

The decreasing failure rates reflect the never ending effort in this direction; they have been reduced considerably despite an immense rise in the IC's complexity.

#### **Reliability Monitoring**

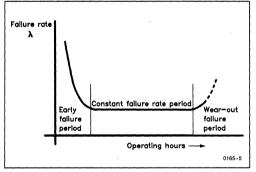

The general course of the IC's failure rate versus time is shown by a so-called "bathtub" curve (Figure 3). The failure rate has its peak during the first few operating hours (early failure period). After the early failure period has decayed, the "constant" failure rate period starts during which the failures may occur at an approximately uniform rate. This period ends with a repeated rise of the curve during the wear-out failure period. For ICs, however, the latter period usually lies far beyond the service life specified for the individual equipment.

Reliability tests for ICs are usually destructive examinations. They are, therefore, carried out with samples. Most failure mechanisms can be accelerated by means of higher temperatures. Due to the temperature dependence of the failure mechanisms, it is possible to simulate future operational behavior within a short time by applying high temperatures; this is called accelerated life testing.

Figure 3. Reliability "Bath-Tub" Curve

#### **General Information**

The accerleration factor B for the life test can be obtained from the Arrhenius equation

$$B = \exp \qquad \frac{\mathsf{E}_{\mathsf{A}}}{k} \left[ \frac{1}{T_1} - \frac{1}{T_2} \right]$$

where  $T_2$  is the temperature at which the life test is performed,  $T_1$  is the assumed operating temperature, and k is the Boltzmann constant.

Important for factor B is the activation energy  $E_A$ . It lies between 0.3V and 1.3 eV and differs considerably for individual failure mechanisms.

For all Siemens ICs, the reliability data from life tests is converted to an operating temperature of  $T_A =$ 55°C, assuming an average activation energy of 0.5 eV. The acceleration factor for life tests at 125°C is thus 22.3, compared with operational behavior. This method considers also failure mechanisms with low activation energy, i.e. which are only slightly accelerated by the temperature effect.

Various reliability tests are periodically performed with IC types that are representative of a certain production line—this is described in the brochure "SQS-IC". Such tests are e.g. humidity test at 85°C and 85% relative humidity, pressure cooker test, as well as life tests up to 1000 hours and more. Test results are available in the form of summary reports.

#### SAB-51 Architectural Overview

# SIEMENS

### **SAB-51 Architectural Overview**

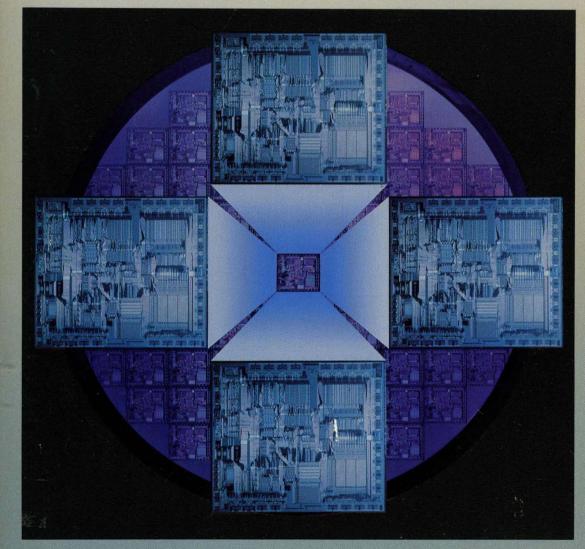

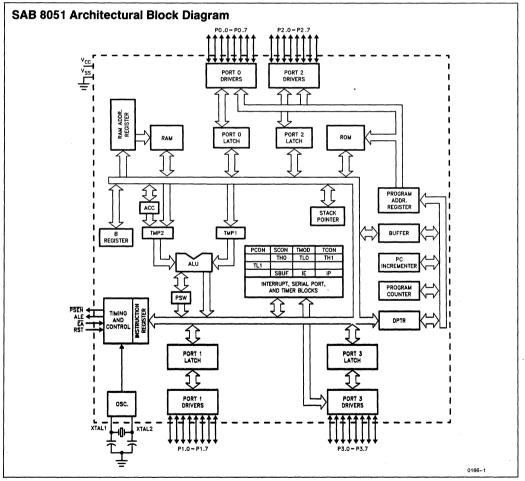

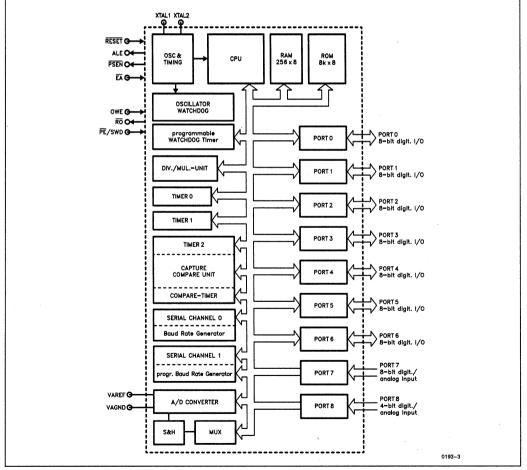

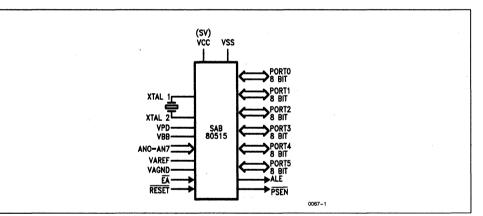

Siemens SAB-51 family of 8-bit microcontrollers consists of the devices listed in Table 1, all of which are based on the SAB-8051 architecture shown in Figure 1. The original 8051 was built in N-channel, silicon gate, Siemens MYMOS II technology and packaged in a 40-pin DIP. The 8051A which is in the advanced N-channel, silicon gate Siemens MYMOS III process, is the device currently in production.

All other microcontrollers listed in this book are backward compatible with the SAB-8051A.

Figure 1. SAB 8051 Architectural Block Diagram

3-1

#### **SAB-51 Architectural Overview**

| · · · · · · · · · · · · · · · · · · · |                        |     |               |                       |                                    |                               |                       |                                      |                    |       |                      |                              |                    |

|---------------------------------------|------------------------|-----|---------------|-----------------------|------------------------------------|-------------------------------|-----------------------|--------------------------------------|--------------------|-------|----------------------|------------------------------|--------------------|

| Device<br>* = ROMless<br>Version      | Clock<br>Rate<br>(MHz) | ROM | RAM<br>(Byte) | I/O-Ports<br>(8-Bit)  | ADC<br>Inputs<br>(8-Bit<br>Resol.) | Timer/<br>Counter<br>(16-Bit) | Watch<br>Dog<br>Timer | Inter-<br>rupt<br>Sources/<br>Levels | Seriai<br>I/O      | PWM   | Div/<br>Mult<br>Unit | Data<br>Pointers<br>(16-Bit) | Package            |

| SAB 8051<br>SAB 8031*                 | 12, 16                 | 4   | 128           | 4                     | · · · · · · · ·                    | 2                             | -                     | 5/2                                  | USART              | _     | -                    | 1                            | PDIP 40<br>PLCC 44 |

| SAB 8052<br>SAB 8032*                 | 12, 16                 | 8   | 256           | 4                     | _                                  | 3                             |                       | 6/2                                  | USART              | -     | _                    | .1                           | PDIP 40<br>PLCC 44 |

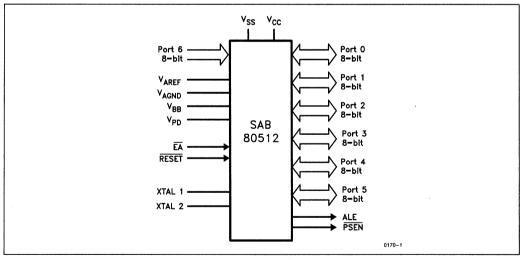

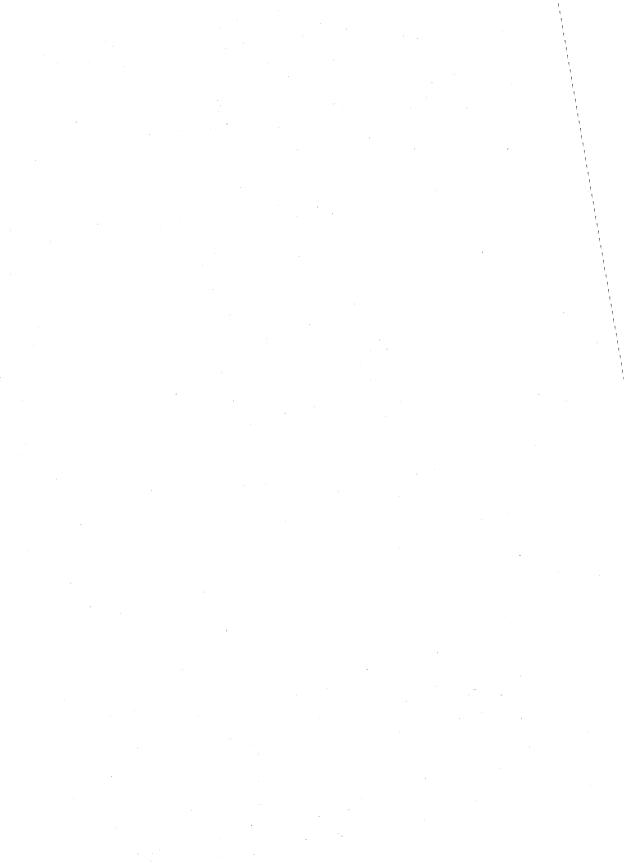

| SAB 80512<br>SAB 80532*               | 12                     | 4   | 128           | 6(I/O)<br>+<br>1(I)   | 8                                  | 2                             |                       | 6/2                                  | USART              |       | _                    | 1                            | PLCC 68            |

| SAB 80513                             | 12<br>16               | 16  | 256           | 4                     |                                    | 3                             |                       | 6/2                                  | USART              | -     | _                    | 1                            | PDIP 40<br>PLCC 44 |

| SAB 80515<br>SAB 80535*               | 12, 16                 | 8   | 256           | 6                     | 8                                  | 3                             | .1                    | 12/4                                 | USART              | 4-ch  |                      | 1                            | PLCC 68            |

| SAB 80C515<br>SAB 80C535*             | 12                     | 8   | 256           | 6(I/O)<br>+<br>1(I)   | 8                                  | 3                             |                       | 12/4                                 | USART              | 4-ch  | _                    | 1                            | PLCC 68            |

| SAB 80C517<br>SAB 80C537*             | 12                     | 8   | 256           | 7(I/O)<br>+<br>1½ (I) | 12                                 | 4                             | 2                     | 14/4                                 | USART<br>+<br>UART | 21-ch | Yes                  | 8                            | PLCC 84            |

Table 1. The SAB-51 Family of Microcontrollers

3-2

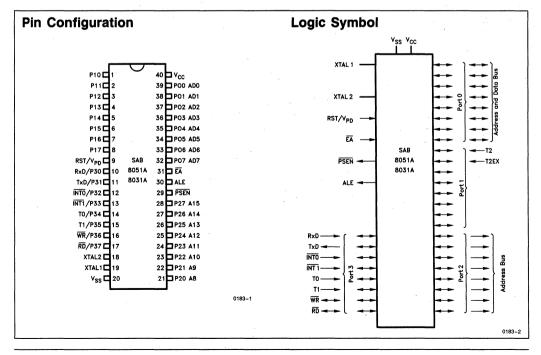

#### SAB 8051A/8031A, SAB 8051A-16/8031A-16

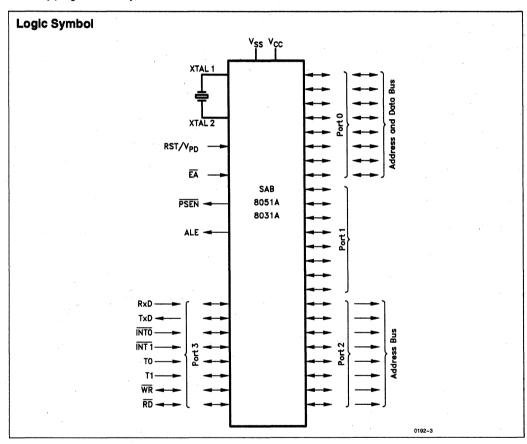

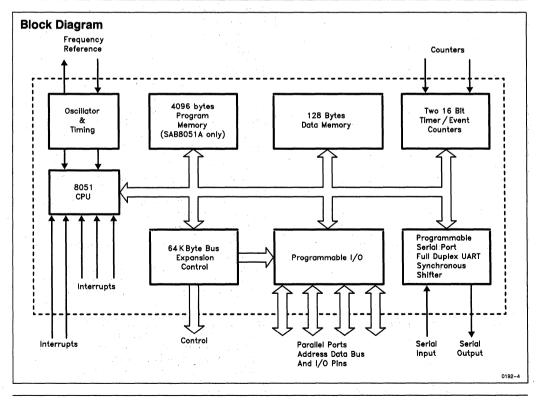

The SAB8051A is the original member of the SAB-51 family. Among the features of the SAB 8051A are:

- 8-Bit CPU Optimized for Control Applications

- Extensive Boolean Processing (Single-Bit Logic) Capabilities

- 32 Bidirectional and Individually Addressable I/O Lines

- 128 Bytes of On-Chip Data RAM

- RAM Power-Down Supply

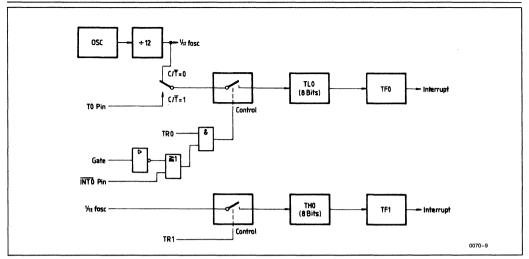

- Two 16-Bit Timer/Counters

- Full Duplex UART

- 5-Source Interrupt Structure with 2 Priority Levels

- On-Chip Clock Oscillator

- 4 Kbytes of On-Chip Program Memory

- 64K Program Memory Address Space

- 64K Data Memory Address Space

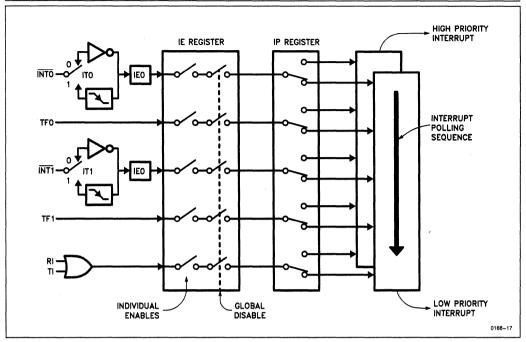

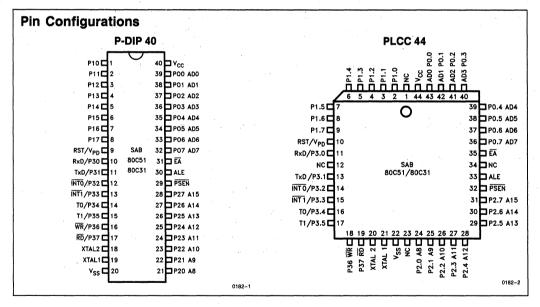

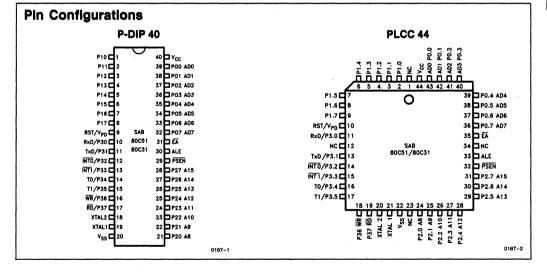

The SAB 8051A/8031A is a standalone, high-performance single-chip microcontroller fabricated in +5V advanced Siemens MYMOS (III) technology and supplied in a 40-pin plastic P-DIP or 44-pin plastic leaded chip carrier (PL-CC-44) package.

The SAB8031A differs from the SAB8051A, in not having the on-chip program ROM. Instead, the SAB 8031A fetches all instructions from external memory.

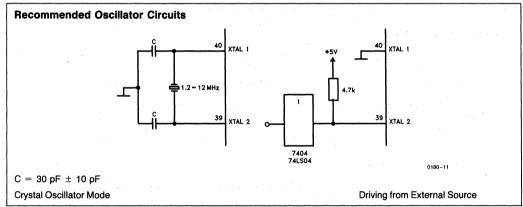

The SAB8051A-16 differs from the SAB8051A only in the speed of operation. The SAB8051A can run with a clock oscillator frequency from 1.2 MHz to 12 MHz whereas the SAB 8051A-16 can run upto a clock oscillator frequency of 16 MHz.

The extended temperature versions of these parts are also available.

#### SAB 80C51/80C31

The SAB 80C51/80C31 is a standalone, high-performance CMOS single-chip microcontroller, designed in Siemens ACMOS technology. It is functionally compatible with the SAB 8051A/8031A devices in MYMOS technology.

The low-power properties of ACMOS technology allow applications where power consumption and dissipation are critical. In addition, the SAB 80C51/80C31 has two software-selectable modes of power reduction—idle and power-down.

The SAB 80C51/80C31 is supplied in a 40-pin P-DIP package or a 44-pin plastic leaded chip carrier (PLCC 44) package.

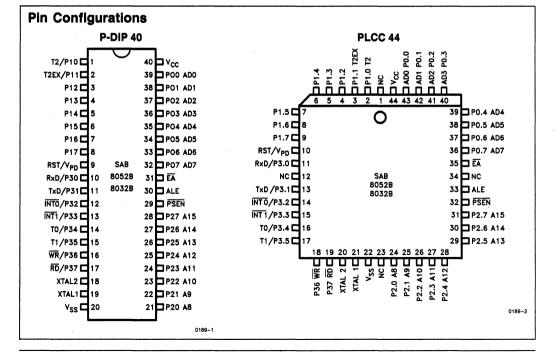

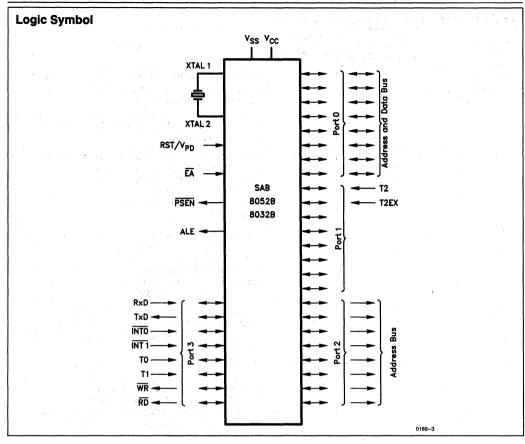

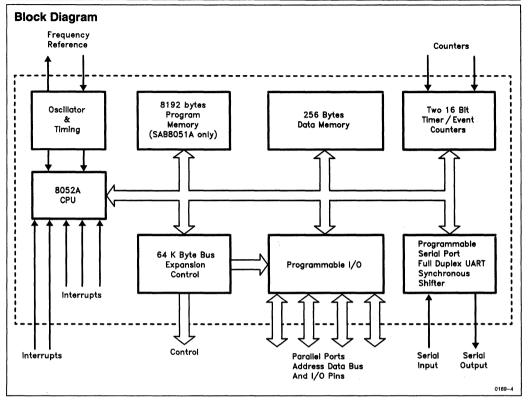

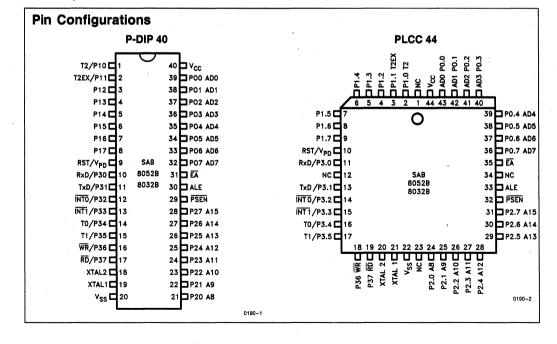

#### SAB 8052B/8032B, SAB8052B-16/SAB8032B-16

The SAB 8052B/8032B is identical to the SAB 8051A/8031A and is also fabricated in advanced N-channel, Silicon gate Siemens MYMOS III technology. It is pin for pin compatible with the SAB8051A. Its enhancements over the SAB8051A are as follows:

- 256 Bytes of On-Chip Data RAM

- Three Timer/Counters

- 6-Source Interrupt Structure

- 8 Kbytes of On-Chip Program ROM

The ROMless version of the 8052B is the 8032B. The 16 MHz version is the SAB 8052B-16/8032B-16. The extended temperature versions of these parts are also available. The earlier version of the SAB 8052B/8032B was fabricated in N-channel, silicon gate Siemens MYMOS II technology and was called the SAB 8052A/8032A. Whatever applies to the SAB 8052A/8032A also applies to the SAB 8052B/8032B except that the SAB 8052B/8032B is in the advanced N-channel, silicon gate Siemens MYMOS III technology.

#### SAB 80C52/80C32

The SAB 80C52/80C32 is a standalone, high-performance CMOS single-chip microcontroller, designed in Siemens ACMOS technology. It is functionally compatible with the SAB 8052A/8032A or the SAB 8052B/8032B devices in MYMOS technology.

Furthermore, it is backwardly compatible with the SAB 80C51/80C31. The low-power consumption properties of ACMOS technology allow applications where power consumption and dissipation are critical. In addition, the SAB 80C52/80C32 has two software-selectable modes of reduced activity for further power reduction—idle and power-down.

#### SAB-51 Architectural Overview

The SAB 80C52/80C32 is supplied in a 40-pin P-DIP package, or a 44-pin plastic leaded chip carrier (PLCC 44) package.

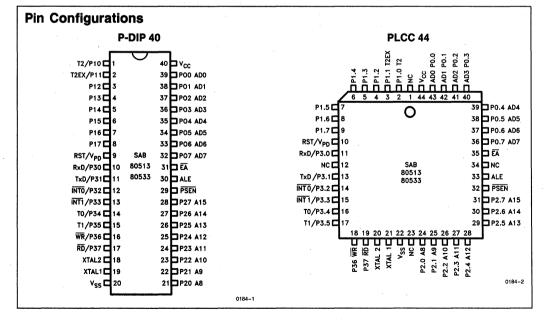

#### SAB 80513 SAB 80513-16

The SAB 80513/80533 is a new member of the Siemens SAB 8051 family of 8-bit microcontrollers. It is fabricated in N-channel silicon-gate Siemens MYMOS technology.

The SAB 80513 is a stand-alone, high-performance, single-chip microcontroller based on the SAB 8051 architecture. It maintains all features of the SAB 8051A and SAB 8052B (including Timer 2 of the SAB 8052B) and is thus fully compatible to both the SAB 8051A and SAB 8052B.

In addition, the SAB 80513 contains 16 Kbyte of onchip ROM, which makes it a powerful and cost-effective controller for applications requiring more ROM space.

The SAB 80513 operates up to 12 MHz crystal oscillator frequency. The SAB 80513-16 operates up to 16 MHz crystal oscillator frequency.

The SAB 80513 is supplied in a 40-pin dual-in-line package or a 44-pin plastic leaded chip carrier (PLCC 44) package.

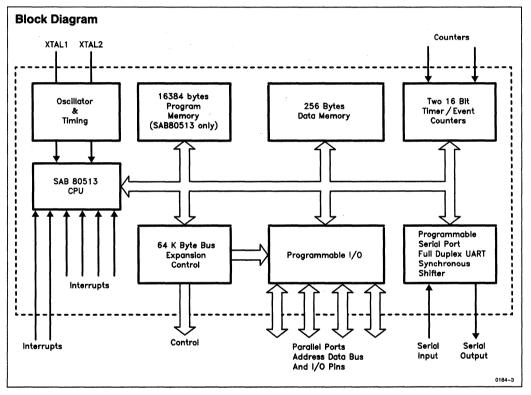

#### SAB 80512/80532

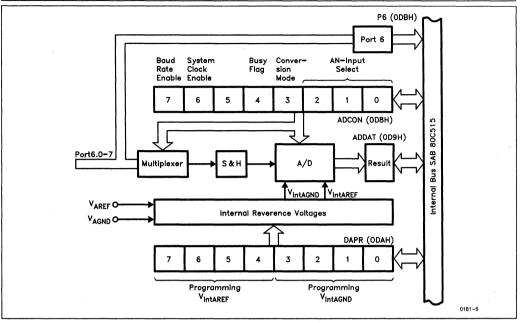

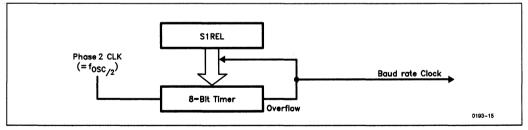

The SAB 80512/80532 is a new member of the Siemens SAB 8051 family of 8-bit microcontrollers. Maintaining all features of the SAB 8051A/8031A, it is backwardly compatible with the SAB 8051A/ 8031A. Furthermore the SAB 80512/80532 incorporates several enhancements, that significantly increase design flexibility and cost effectiveness. In addition to the SAB 8051A/8031A the SAB 80512/ 80532 contains an 8-bit A/D converter with 8 multiplexed inputs (these inputs can also be used as digital inputs), an own baud rate generator for the serial interface and two more I/O ports. The SAB 80532 is identical with the SAB 80512, except that it lacks the on-chip ROM.

The SAB 80512/80532 is fabricated in +5V advanced N-channel, silicon gate MYMOS technology of Siemens and supplied in a PLCC 68 package. For the industrial temperature range  $-40^{\circ}$ C to  $+85^{\circ}$ C, the SAB 80512/80532-T40/85 is available.

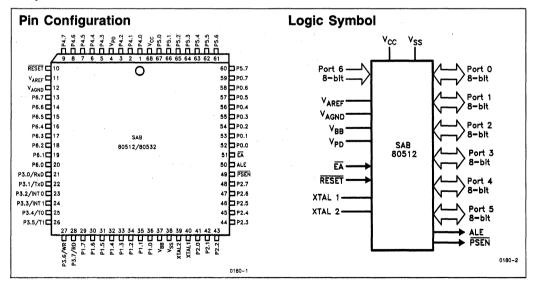

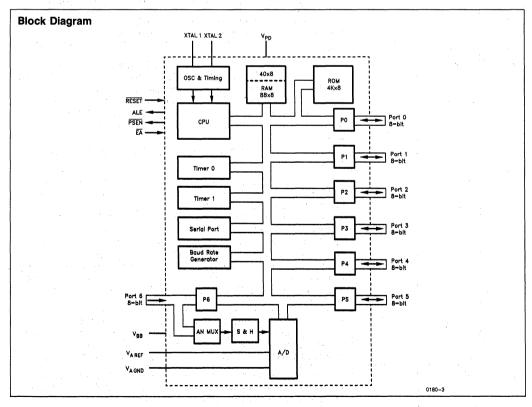

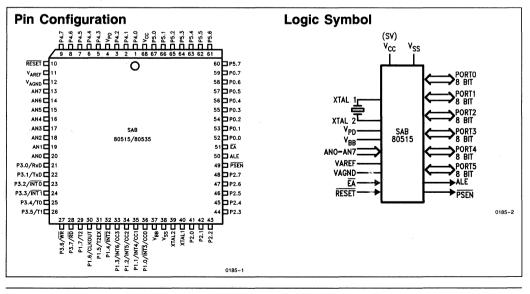

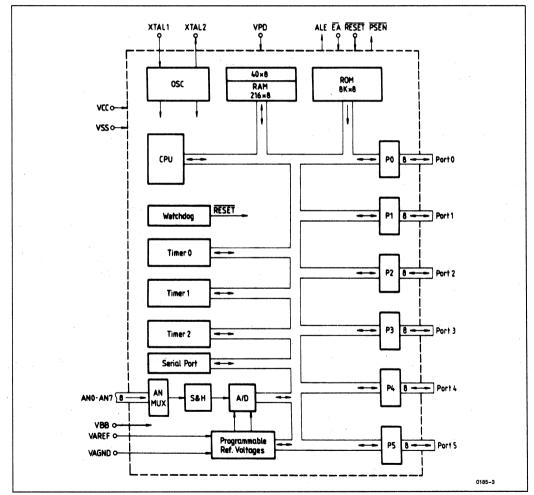

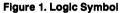

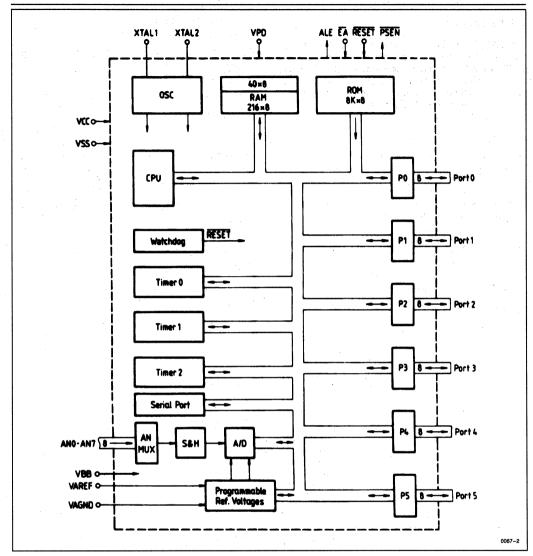

#### SAB 80515/80535, SAB 80515-16, 80535-16

The SAB 80515/80535 is a powerful member of the Siemens SAB 8051 family of 8-bit microcontrollers. It is fabricated in +5V N-channel, silicon-gate Siemens MYMOS technology.

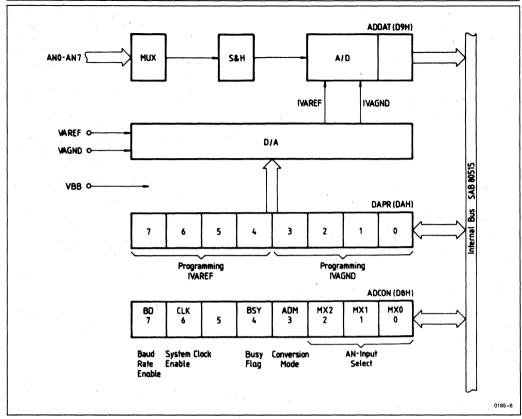

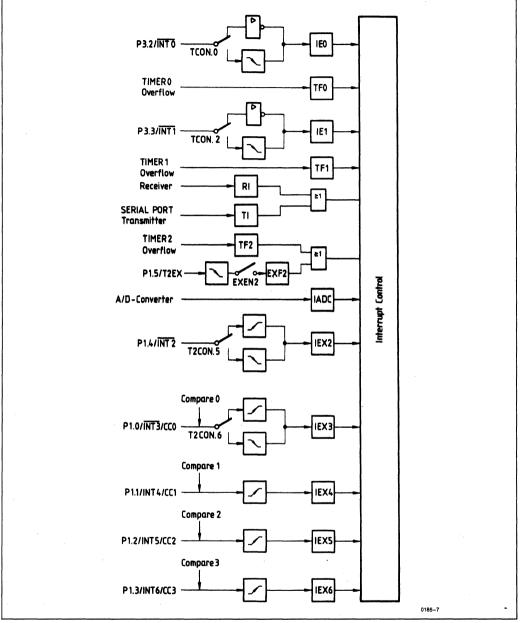

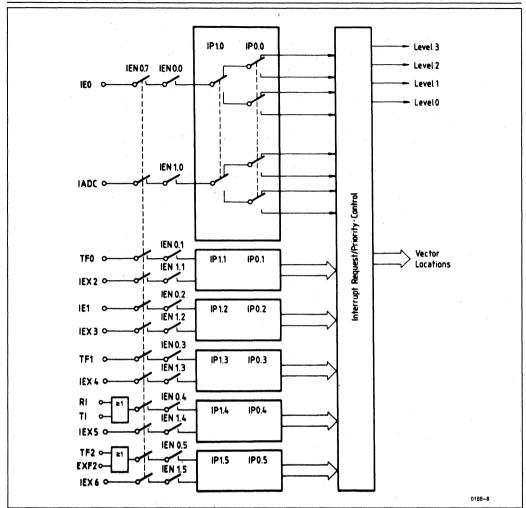

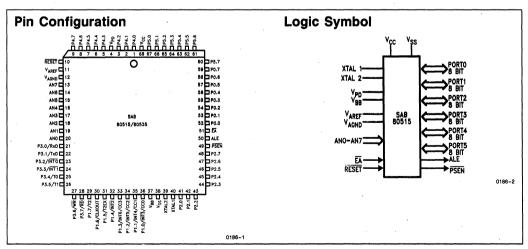

The SAB 80515/80535 is a stand-alone, high-performance single-chip microcontroller based on the SAB 8051 architecture. While maintaining all the SAB 8051 operating characteristics, the SAB 80515/80535 incorporates several enhancements which significantly increase design flexibility and overall system performance. These features are:

- 8K × 8 ROM (SAB 80515 Only)

- 256 imes 8 RAM

- Six 8-Bit I/O Ports, One 8-Bit Input Port for Analog Signals

- Three 16-Bit Timer/Counters

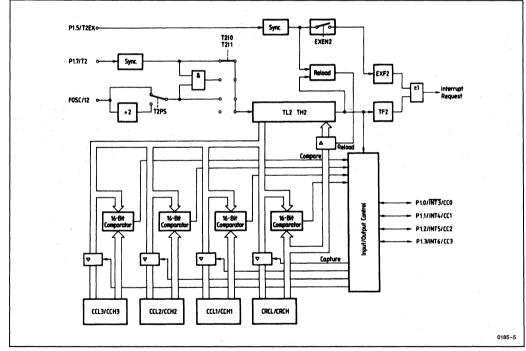

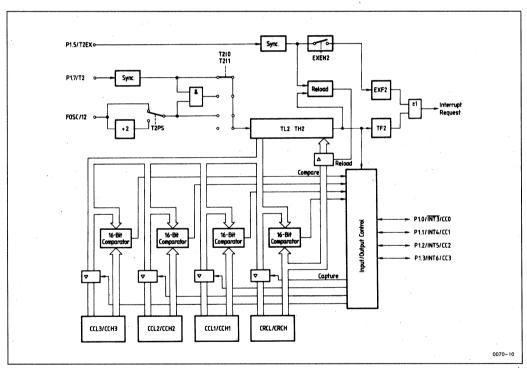

- Programmable Timer/Counter Register-Array with Compare/Capture Auto Reload Pulse Width Modulator Capabilities

- Full-Duplex Serial Channel

- Twelve Interrupt Vectors, Four Priority Levels

- 8-Bit A/D Converter with Eight Multiplexed Inputs and Programmable Internal Reference Voltages

- 16-Bit Watchdog Timer

- V<sub>PD</sub> Provides Standby Current for 40 Bytes of RAM

- Boolean Processor

- 256 Bit-Addressable Locations

- Most Instructions Executed in: 1 μs (SAB 80515/80535) 750 ns (SAB 80515-16/80535-16)

- 4 µs (3 µs) Multiply and Divide

- Backwardly Compatible with SAB 8051

- 68-Pin Plastic Leaded Chip Carrier Package (PLCC 68)

The SAB 80535 is identical with the SAB 80515 except that it lacks the on-chip program memory. The SAB 80515/80535 is supplied in a 68-pin plastic leaded chip carrier package (PLCC 68). The SAB 80515/80535 operates up to 12 MHz crystal oscillator frequency. The SAB 80515-16/80535-16 operates up to 16 MHz crystal oscillator frequency. The SAB 80515/80535 is also available in industrial temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C) and in the automotive temperature range ( $-40^{\circ}$ C to  $+110^{\circ}$ C).

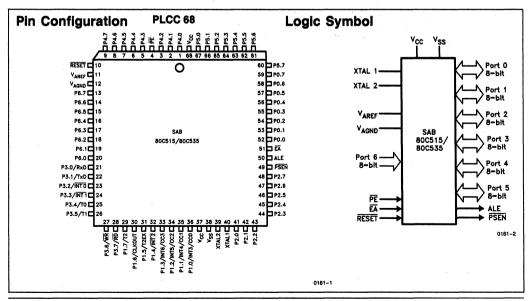

#### SAB 80C515/80C535

The SAB 80C515/80C535 is a new, powerful member of the Siemens SAB 8051 family of 8-bit microcontrollers. It is designed in Siemens ACMOS technology and is functionally compatible with the SAB 80515/80535 devices designed in MYMOS technology.

In addition, the SAB 80C515 has two software-selectable power saving modes: idle mode and the power-down mode. These modes replace the power-down supply mode via pin  $V_{PD}$  of the SAB 80515 (NMOS).

In case of the SAB 80C515 the analog port can also be used as a digital input port.

The SAB 80C535 is identical with the SAB 80C515 except that it lacks the on-chip program memory. The SAB 80C515/80C535 is supplied in a 68-pin plastic leaded chip carrier package (PLCC 68). For the industrial temperature range  $-40^{\circ}$ C to  $+85^{\circ}$ C, the SAB 80C515/80C535-T40/85 is available.

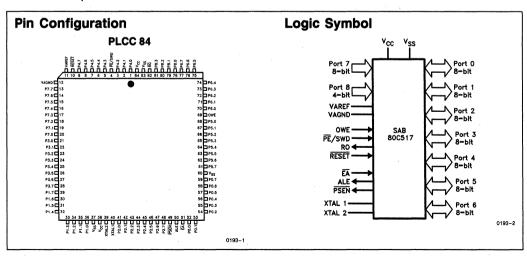

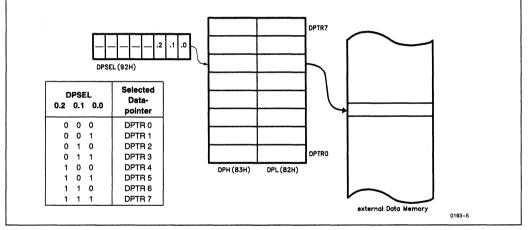

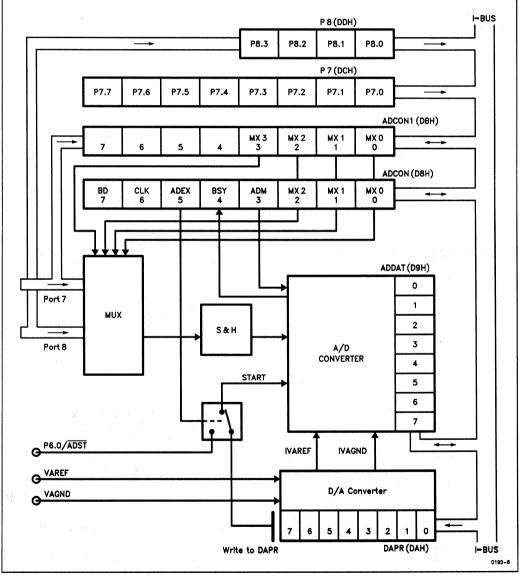

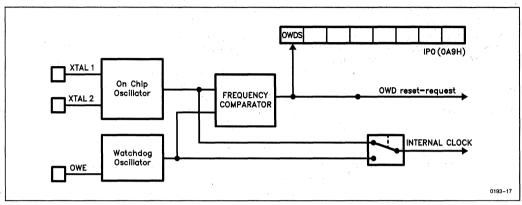

#### SAB 80C517/80C537

The SAB80C517/80C537 is a new and the most powerful member of the Siemens SAB 8051 family of 8-bit microcontrollers. It is designed in Siemens ACMOS technology and is functionally compatible with the SAB 80C515/80C535 devices. While maintaining all the SAB 80C51 operating characteristics, the SAB 80C517/80C537 incorporates several enhancements which significantly increase design flexibility and overall system performance. These features are:

- 8 Kbyte On-Chip Program Memory

- 256 Byte On-Chip RAM

- 256 Directly Addressable Bits

- 1 µs Instruction Cycle at 12 MHz

- 64 of 111 Instructions Executed in One Cycle

- External Program and Data Memory Expandable to 64 Kbyte Each

- 8-Bit A/D Converter

- 12 Multiplexed Inputs

- Programmable Reference Voltages

- External/Internal Start of Conversion

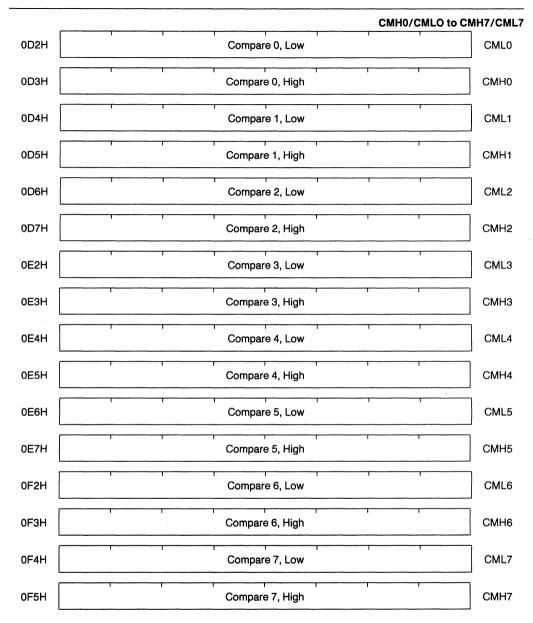

- Two General Purpose 16-Bit Timers/Counters (Timer 0, Timer 1)

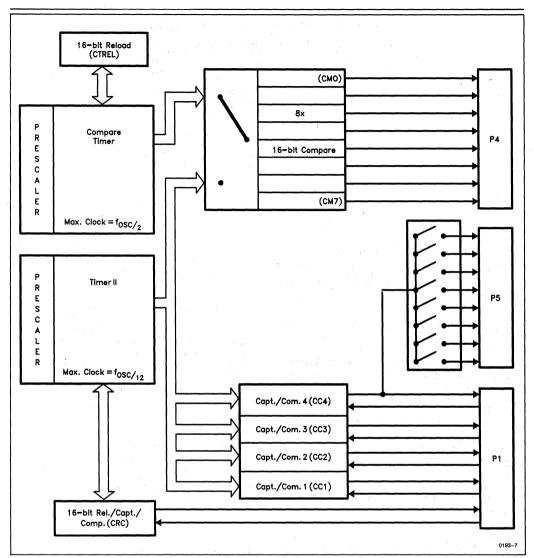

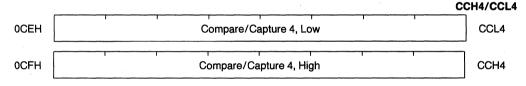

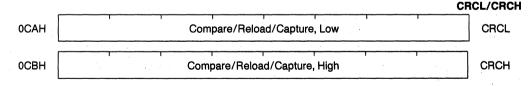

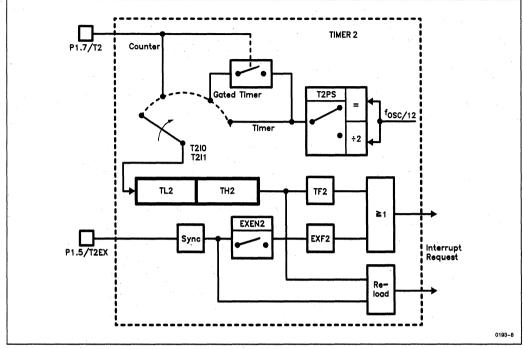

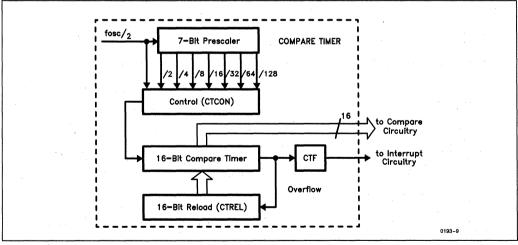

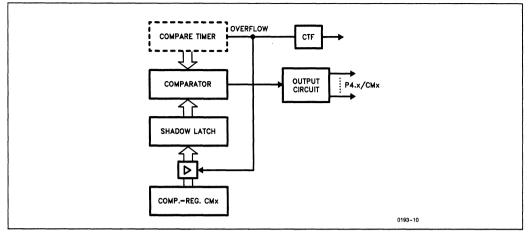

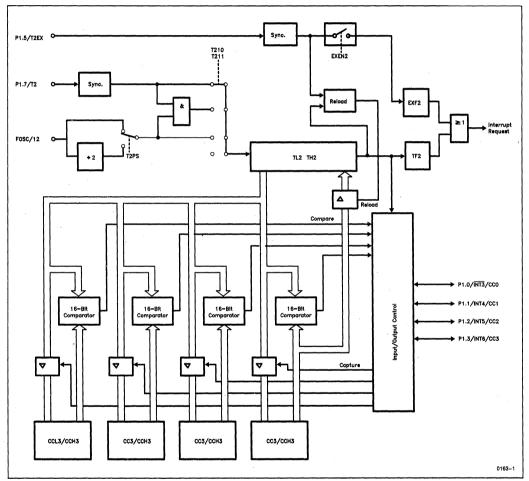

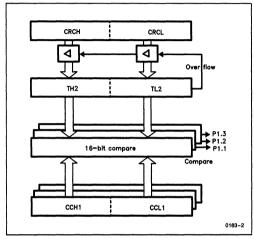

- Compare Capture Unit (CCU)

- One 16-Bit Timer/Counter, 1 MHz Clock

- One 16-Bit Compare-Timer, 6 MHz Clock with Dedicated Reload Register

- One 16-Bit Reload/Capture/Compare Register

- Four 16-Bit Capture/Compare Registers

- Eight 16-Bit Compare Registers

- Concurrent Compare

- Pulse Width Modulation or High Speed Output Possible on up to 21 Channels

- Fine Capture Input Channels

- Two Full Duplex Serial Interfaces with Own Baud Rate Generator

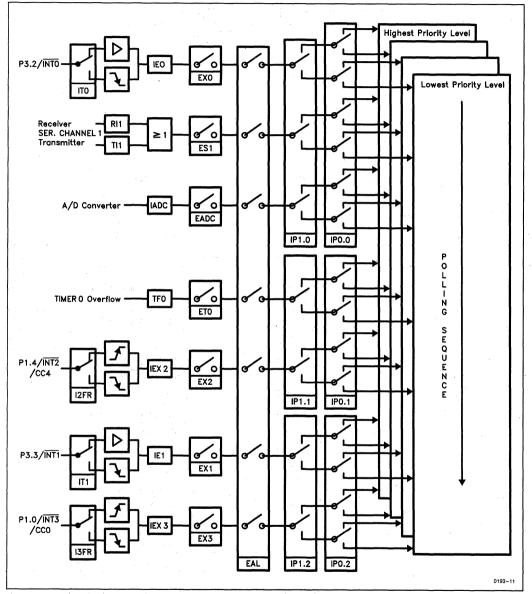

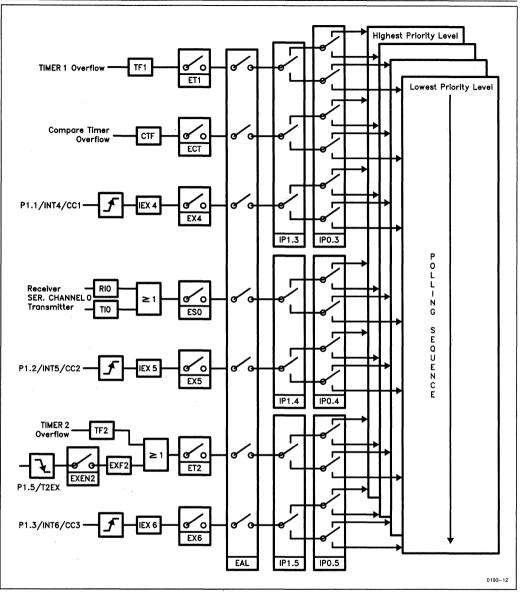

- Four Priority Level Interrupt System, 14 Interrupt Sources

- Extended Arithmetic Capabilities for Division and Multiplication (Mul./Div. Unit Operations to Fast 16/32-Bit)

- Eight Datapointers for Indirect Addressing

- Extended Fail Safe Mechanisms

- 16-Bit Programmable Watchdog Timer

- Oscillator Watchdog

- Hardware Disable for Power Saving Modes

- Extended Power Saving Modes (Slow Down, Idle, Power-Down)

- Nine Ports

- Seven Bidirectional 8-Bit Ports

- One 8-Bit, One 4-Bit Input Port

- 84 Pin PLCC Package

#### **SAB-51 Architectural Overview**

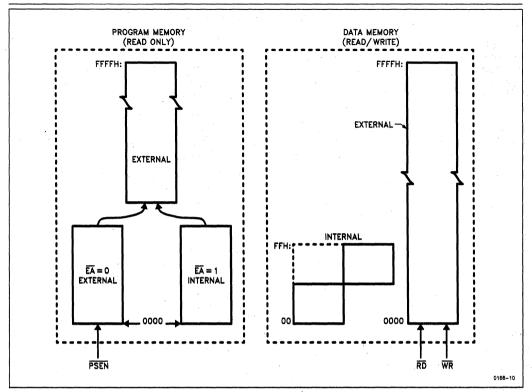

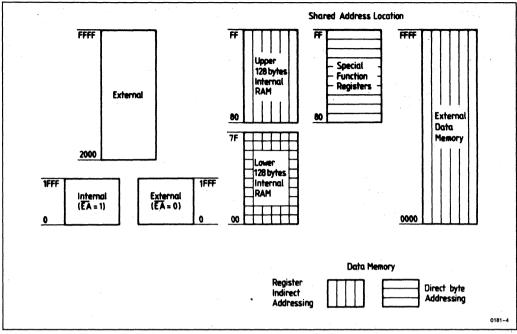

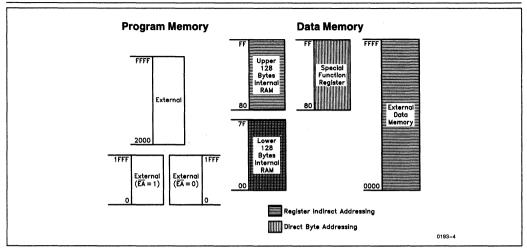

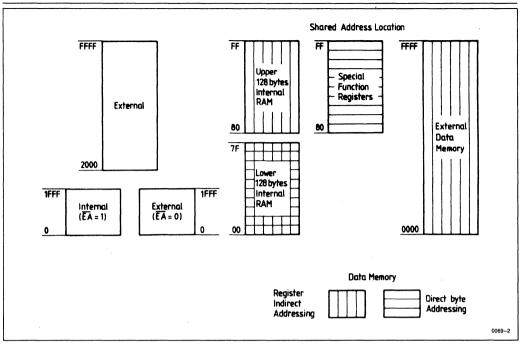

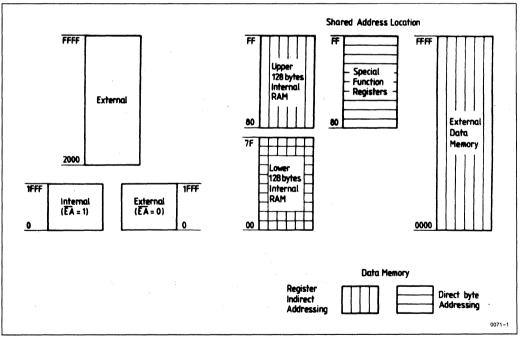

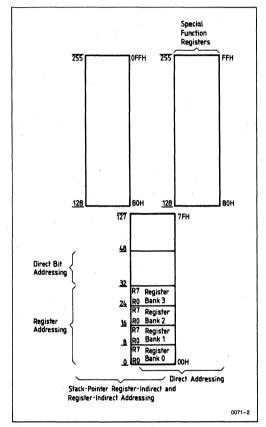

Figure 2. SAB-51 Memory Structure

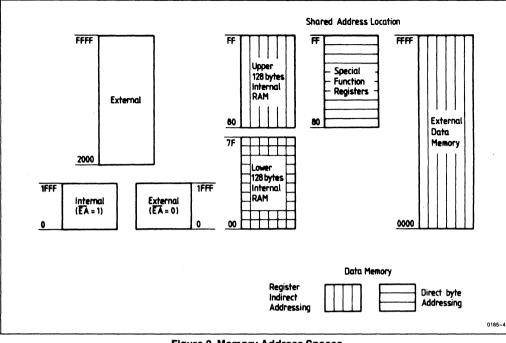

#### Memory Organization in SAB-51 Devices

#### Logical Separation of Program and Data Memory

All SAB-51 devices have separate address spaces for Program and Data Memory, as shown in Figure 2. The logical separation of Program and Data Memory allows the Data Memory to be accessed by 8-bit addresses, which can be more quickly stored and manipulated by an 8-bit CPU. Nevertheless, 16-bit Data Memory addresses can also be generated through the DPTR register.

Program Memory can only be read, not written to. There can be up to 64 Kbytes of Program Memory. In the 8051A, 80C51 and 80512 the lowest 4 Kbytes of Program Memory are on-chip. The 8052B, 80515, 80C515 and 80C517 provide 8 Kbytes of on-chip Program Memory storage. The SAB 80513 has 16K of on-chip program memory. In the ROMIess versions all Program Memory is external. The read strobe for external Program Memory is the signal PSEN (Program Store Enable).

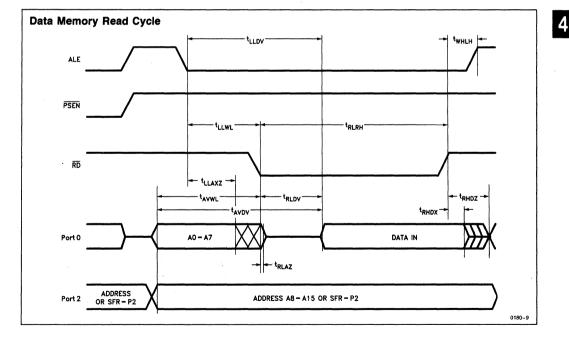

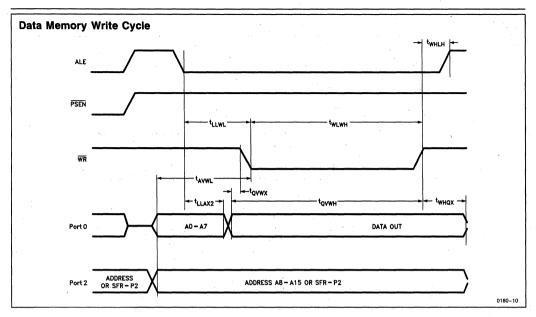

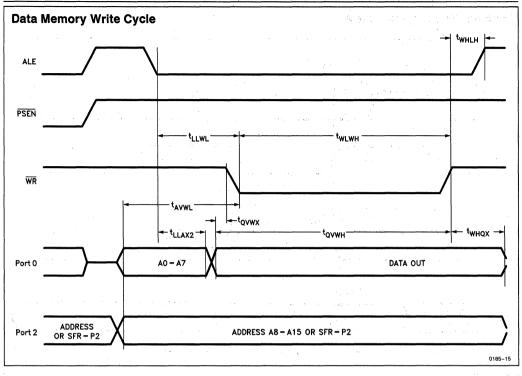

Data Memory occupies a separate address space from Program Memory. Up to 64 Kbytes of external RAM can be addressed in the external Data Memory space. The CPU generates read and write signals, RD and WR, as needed during external Data Memory accesses.

External Program Memory and external Data Memory may be combined if desired by applying the RD and PSEN signals to the inputs of an AND gate and using the output of the gate as the read strobe to the external Program/Data memory.

#### **Program Memory**

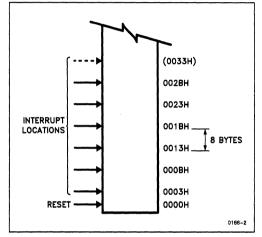

Figure 3 shows a map of the lower part of the Program Memory. After reset, the CPU begins execution from location 0000H.

As shown in Figure 3, each interrupt is assigned a fixed location in Program Memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External Interrupt 0, for example, is assigned to location 0003H. If External Interrupt 0 is going to be used, its service routine must begin at location 0003H. If the interrupt is not going to be used, its service location is available as general purpose Program Memory.

Figure 3. SAB-51 Program Memory

The interrupt service locations are spaced at 8-byte intervals: 0003H for External Interrupt 0, 000BH for Timer 0, 0013H for External Interrupt 1, 001BH for Timer 1, etc. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within that 8-byte interval. Longer service routines can use a jump instruction to skip over subsequent interrupt locations, if other interrupts are in use.

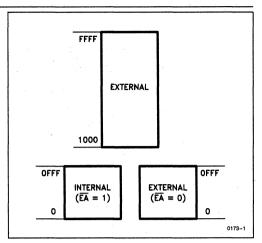

The lowest 4K (or 8K, in the 8052B, 80515 and 80C517) bytes of Program Memory can be either in the on-chip ROM or in an external ROM. This selection is made by strapping the  $\overline{\text{EA}}$  (External Access) pin to either V<sub>CC</sub> or V<sub>SS</sub>.

In 8051A, 80C51 and 80512, if the  $\overline{EA}$  pin is strapped to V<sub>CC</sub>, then program fetches to addresses 0000H through 0FFFH are directed to the internal ROM. Program fetches to addresses 1000H through FFFFH are directed to external ROM.

In the 8052B and the other 8K ROM parts,  $\overline{EA} = V_{CC}$  selects addresses 0000H through 1FFFH to be internal, and addresses 2000H through FFFFH to be external.

In the 80513,  $\overline{\text{EA}} = \text{V}_{\text{CC}}$  selects addresses 0000H through 3FFFH to be internal and addresses 4000H through FFFH to be external.

If the  $\overline{\text{EA}}$  pin is strapped to V<sub>SS</sub>, then all program fetches are directed to external ROM. The ROMless parts 8031A, 8032B, 80532 etc. must have this pin externally strapped to V<sub>SS</sub> to enable them to execute from external Program Memory.

The read strobe to external ROM, PSEN, is used for all external program fetches. PSEN is not activated for internal program fetches.

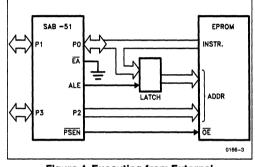

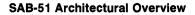

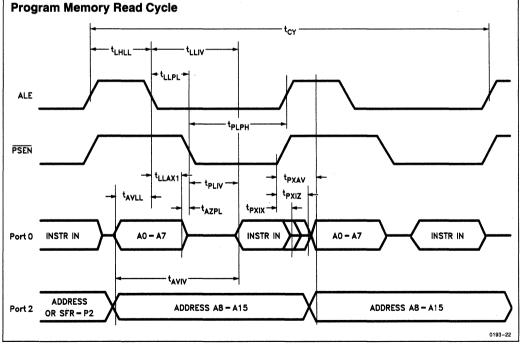

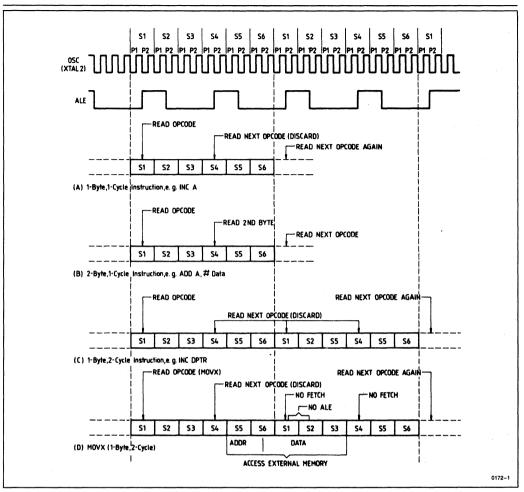

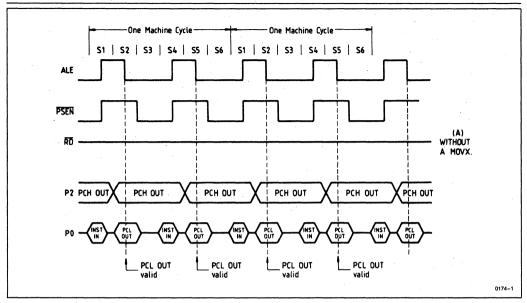

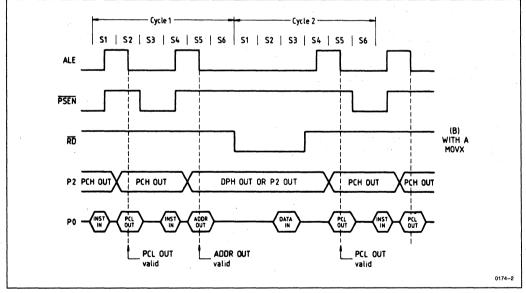

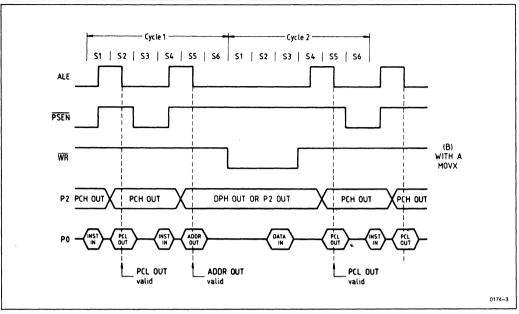

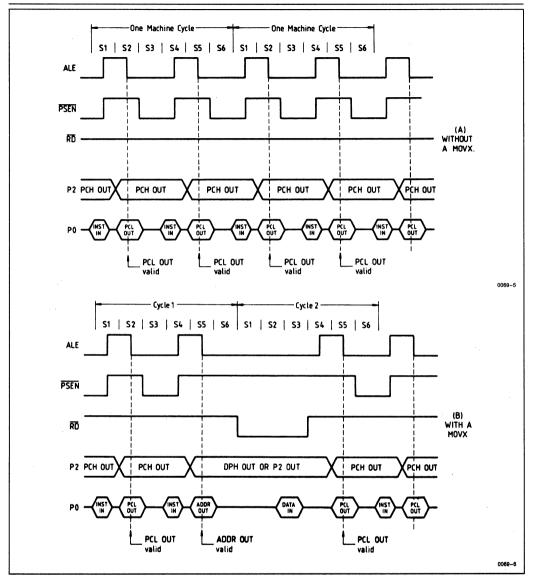

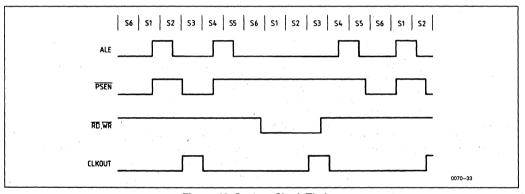

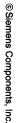

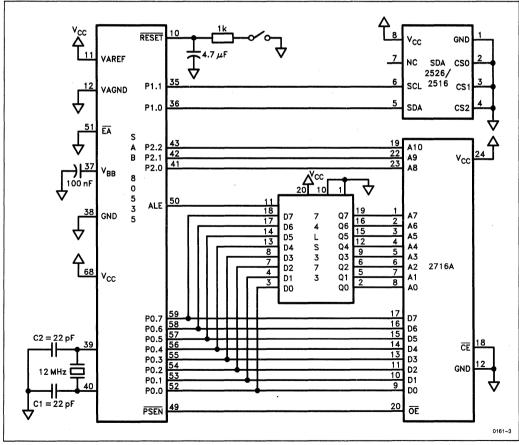

#### Figure 4. Executing from External Program Memory

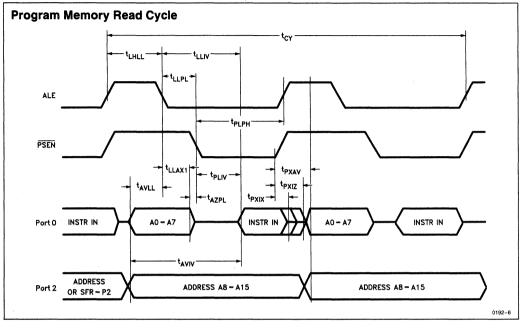

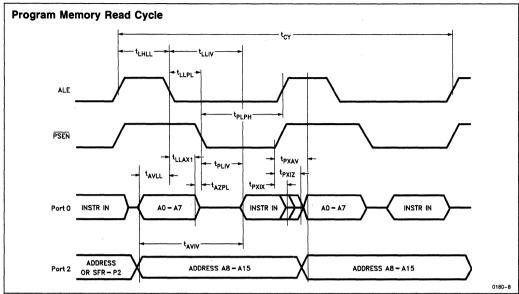

The hardware configuration for external program execution is shown in Figure 4. Note that 16 I/O lines (Ports 0 and 2) are dedicated to bus functions during external Program Memory fetches. Port 0 (P0 in Figure 4) serves as a multiplexed address/data bus. It emits the low byte of the Program Counter (PCL) as an address, and then goes into a float state awaiting the arrival of the code byte from the Program Memory. During the time that the low byte of the Program Counter is valid on P0, the signal ALE (Address Latch Enable) clocks this byte into an address latch. Meanwhile, Port 2 (P2 in Figure 4) emits the high byte of the Program Counter (PCH). The PSEN strobes the EPROM and the code byte is read into the microcontroller.

Program Memory addresses are always 16 bits wide, even though the actual amount of Program Memory used may be less than 64 Kbytes. External program execution sacrifices two of the 8-bit ports, P0 and P2, to the function of addressing the Program Memory.

#### **Data Memory**

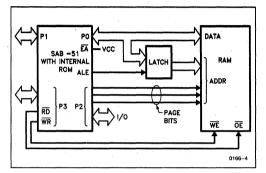

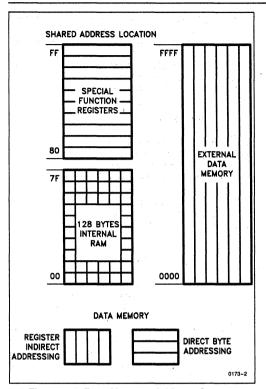

The right half of Figure 2 shows the internal and external Data Memory spaces available to the SAB-51 user.

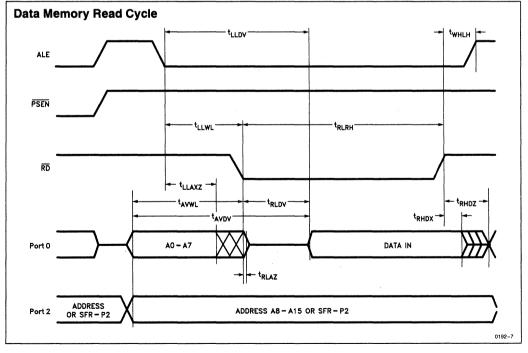

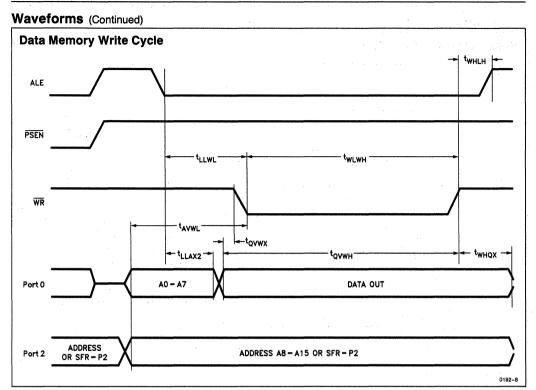

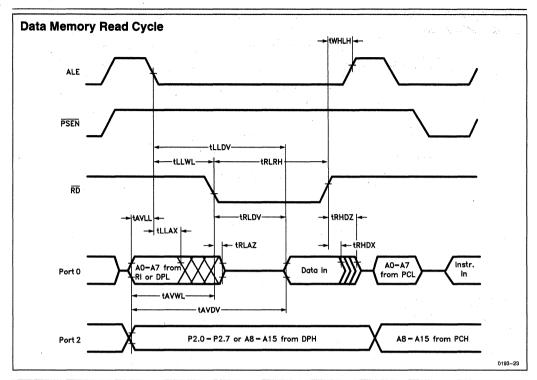

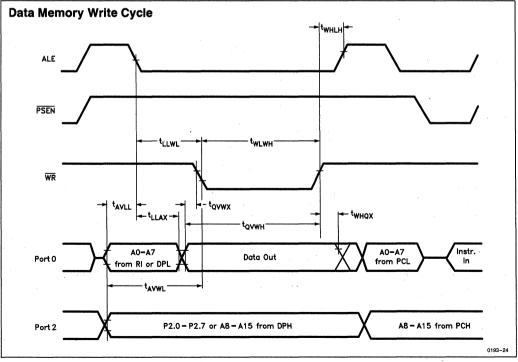

Figure 5 shows a hardware configuration for accessing up to 2 Kbytes of external RAM. The CPU in this case is executing from internal ROM. Port 0 serves as a multiplexed address/data bus to the RAM and 3 lines of Port 2 are being used to page the RAM. The CPU generates  $\overline{RD}$  and  $\overline{WR}$  signals as needed during external RAM accesses.

Figure 5. Accessing External Data Memory If the Program Memory is Internal, the Other Bits of P2 are Available as I/O.

There can be up to 64 Kbytes of external Data Memory. External Data Memory addresses can be either 1 or 2 bytes wide. One-byte addresses are often used in conjunction with one or more other I/O lines to page the RAM, as shown in Figure 5. Two-byte addresses can also be used, in which case the high address byte is emitted at Port 2.

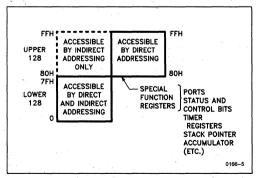

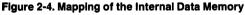

Figure 6. Internal Data Memory

Internal Data Memory is mapped in Figure 6. The memory space is shown divided into three blocks, which are generally referred to as the Lower 128, the Upper 128 and SFR space.

Internal Data Memory addresses are always one byte wide, which implies an address space of only 256 bytes. However, the addressing modes for internal RAM can in fact accommodate 384 bytes, using a simple trick. Direct addresses higher than 7FH access one memory space, and indirect addresses higher than 7FH access a different memory space. Thus Figure 6 shows the Upper 128 and SFR space occupying the same block of addresses, 80H through FFH, although they are physically separate entities.

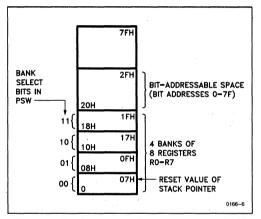

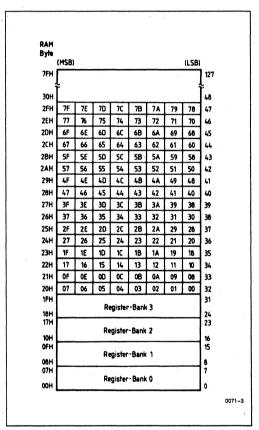

Figure 7. The Lower 128 Bytes of Internal RAM

The Lower 128 bytes of RAM are present in all SAB-51 devices as mapped in Figure 7. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call out these registers as R0 through R7. Two bits in the Program Status Word (PSW) select which register bank is in use. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing.

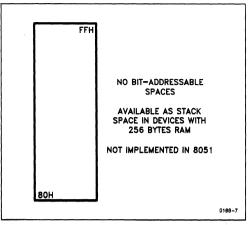

Figure 8. The Upper 128 Bytes of Internal RAM

The next 16 bytes above the register banks form a block of bit-addressable memory space. The SAB-51 instruction set includes a wide selection of singlebit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00H through 7FH.

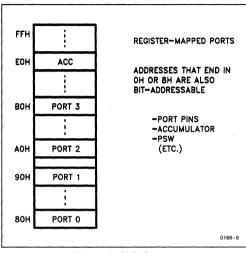

All of the bytes in the Lower 128 can be accessed by either direct or indirect addressing. The Upper 128 (Figure 8) can only be accessed by indirect addressing. The Upper 128 bytes of RAM are not implemented in the 8051A, but are in the 8052B, 80515 and 80C517. Figure 9 gives a brief look at the Special Function Register (SFR) space. SFR include the Port latches, timers, peripheral controls, etc. These registers can only be accessed by direct addressing. In general, all SAB-51 microcontrollers have the same SFRs as the 8051. However, enhancements to the 8051 have additional SFRs that are not present in the 8051, nor perhaps in other proliferations of the family.

Figure 9. SFR Space

The bit addresses in this area are 80H through FFH.

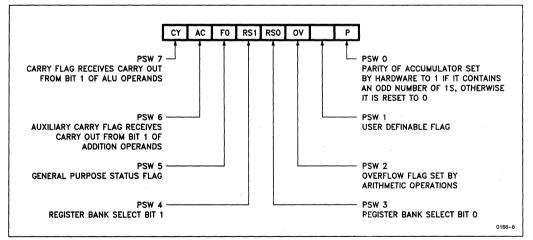

Figure 10. PSW (Program Status Word) Register SAB-51 Devices

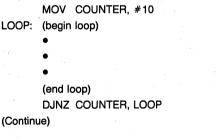

#### The SAB-51 Instruction Set

All members of the SAB-51 family execute the same instruction set. SAB-51 instruction set is optimized for 8-bit control applications. It provides a variety of fast addressing modes for accessing the internal RAM to facilitate byte operations on small data structures. The instruction set provides extensive support for one-bit variables as a separate data type, allowing direct bit manipulation in control and logic systems that require Boolean processing.

An overview of the SAB-51 instruction set is presented below, with a brief description of how certain instructions might be used. Refer to the chapter on instruction set in this book for detailed information on the instructions.

#### **Program Status Word**

The Program Status Word (PSW) contains several status bits that reflect the current state of the CPU. The PSW, shown in Figure 10, resides in SFR space. It contains the Carry bit, the Auxiliary Carry (for BCD operations), the two register bank select bits, the Overflow flag, a Parity bit, and two user-definable status flags.

The Carry bit, other than serving the functions of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

The bits RS0 and RS1 are used to select one of the four register banks shown in Figure 7. A number of instructions refer to these RAM locations as R0 through R7. The selection of which of the four banks is being referred to is made on the basis of the bits RS0 and RS1 at execution time.

The Parity bit reflects the number of 1s in the Accumulator: P = 1 if the Accumulator contains an odd number of 1s, and P = 0 if the Accumulator contains an even number of 1s. Thus the number of 1s in the Accumulator plus P is always even.

Two bits in the PSW are uncommitted and may be used as general purpose status flags.

#### Addressing Modes

The addressing modes in the SAB-51 instruction set are as follows:

#### Direct Addressing

In direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal Data RAM and SFRs can be directly addressed.

#### **Indirect Addressing**

In indirect addressing the instruction specifies a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be R0 or R1 of the selected register bank or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit "data pointer" register, DPTR.

#### **Register Instructions**

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3-bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of the eight registers in the selected bank is accessed. One of four banks is selected at execution time by the two bank select bits in the PSW.

#### **Register-Specific Instructions**

Some instructions are specific to a certain register. For example, some instructions always operate on the Accumulator, or Data Pointer, etc., so no address byte is needed to point to it. The opcode itself does that. Instructions that refer to the Accumulator as A assemble as accumulator-specific opcodes.

#### **immediate Constants**

The value of a constant can follow the opcode in Program Memory. For example,

#### MOV A, #100

loads the Accumulator with the decimal number 100. The same number could be specified in hex digits as 64H.

#### Indexed Addressing

Only Program Memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in Program Memory. A 16-bit base register (either DPTR or the Program Counter) points to the base of the table, and the Accumulator is set up with the table entry number. The address of the table entry in Program Memory is formed by adding the Accumulator data to the base pointer. Another type of indexed addressing is used in the "case jump" instruction. In this case the destination address of a jump instruction is computed as the sum of the base pointer and the Accumulator data.

#### Arithmetic Instructions

With the on-chip arithmetic unit the SAB 80C517 has a special provision for fast multiplication and division. Refer to the SAB 80C517 User's Manual for detailed information on this logic. However, the following information applies to all the members of the SAB-51 family.

The menu of arithmetic instructions is listed in Table 2. The table indicates the addressing modes that can be used with each instruction to access the <byte> operand. For example, the ADD A, <byte> instruction can be written as:

ADD A.7FH (direct addressing)

ADD A.@R0 (indirect addressing)

- ADD A,R7 (register addressing)

- ADD A.#127 (immediate constant)

The execution times listed in Table 2 assume a 12 MHz clock frequency. All of the arithmetic instructions execute in 1 us except the INC DPTR instruction, which takes 2 us, and the Multiply and Divide instructions, which take 4 µs.

Note that any byte in the internal Data Memory space can be incremented or decremented without going through the Accumulator.

One of the INC instructions operates on the 16-bit Data Pointer. The Data Pointer is used to generate 16-bit addresses for external memory, so being able to increment it in one 16-bit operation is a useful feature.

The MUL AB instruction multiplies the Accumulator by the data in the B register and puts the 16-bit product into the concatenated B and Accumulator registers.

| Mnemonic |                  | Operation                                         |                   | Address          | Execution  |     |           |

|----------|------------------|---------------------------------------------------|-------------------|------------------|------------|-----|-----------|

|          |                  |                                                   | Dir               | Ind              | Reg        | Imm | Time (μs) |

| ADD      | A, <byte></byte> | $A = A + \langle byte \rangle$                    | X                 | Х                | X          | X   | 1         |

| ADDC     | A, <byte></byte> | $A = A + \langle byte \rangle + C$                | X                 | Х                | X          | X   | 1         |

| SUBB     | A, <byte></byte> | $A = A - \langle byte \rangle - C$                | Х                 | Х                | x          | X   | 1         |

| INC      | Α                | A = A + 1                                         |                   | Accumulator Only |            | 1   |           |

| INC      | <byte></byte>    | $\langle byte \rangle = \langle byte \rangle + 1$ | X                 | X                | X          |     | 1         |

| INC      | DPTR             | DPTR = DPTR + 1                                   | Data Pointer Only |                  |            |     | 2         |

| DEC      | A                | A = A - 1                                         |                   | Accum            | ulator Onl | у   | 1         |

| DEC      | <byte></byte>    | $\langle byte \rangle = \langle byte \rangle - 1$ | X                 | X                | X          |     | 1         |

| MUL      | AB               | $B:A = B \times A$                                | ACC and B Only    |                  |            |     | 4         |

| DIV      | AB               | A = Int [A/B] $B = Mod [A/B]$                     | ACC and B Only    |                  |            | r   | 4         |

| DA       | Α                | Decimal Adjust                                    |                   | Accumulator Only |            | 1   |           |

Table 2. A List of the SAB-51 Arithmetic Instructions

#### SAB-51 Architectural Overview

The DIV AB instruction divides the Accumulator by the data in the B register and leaves the 8-bit quotient in the Accumulator, and the 8-bit remainder in the B register.

Oddly enough, DIV AB finds less use in arithmetic "divide" routines than in radix conversions and programmable shift operations. An example of the use of DIV AB in a radix conversion will be given later. In shift operations, dividing a number by 2<sup>n</sup> shifts its n bits to the right. Using DIV AB to perform the division completes the shift in 4  $\mu$ s and leaves the B register holding the bits that were shifted out.

The DA A instruction is for BCD arithmetic operations. In BCD arithmetic, ADD and ADDC instructions should always be followed by a DA A operation, to ensure that the result is also in BCD. Note that DA A will not convert a binary number to BCD. The DA A operation produces a meaningful result only as the second step in the addition of two BCD bytes.

#### Logical Instructions

Table 3 shows the list of SAB-51 logical instructions. The instructions that perform Boolean operations (AND, OR, Exclusive OR, NOT) on bytes perform the operation on a bit-by-bit basis. That is, if the Accumulator contains 00110101B and <br/>byte> contains 01010011B, then

ANL A, <byte>

will leave the Accumulator holding 00010001B.

The addressing modes that can be used to access the <byte> operand are listed in Table 3. Thus, the ANL A, <byte> instruction may take any of the forms:

| ANL | A,7FH  | (direct addressing)   |

|-----|--------|-----------------------|

| ANL | A,@R1  | (indirect addressing) |

| ANL | A,R6   | (register addressing) |

| ANL | A,#53H | (immediate constant)  |

| Mnemonic |                      | Operation                                | A                | ddress           | Execution |     |           |

|----------|----------------------|------------------------------------------|------------------|------------------|-----------|-----|-----------|

|          |                      | Operation                                | Dir              | Ind              | Reg       | Imm | Time (μs) |

| ANL      | A, <byte></byte>     | A = A.AND. <byte></byte>                 | X                | Х                | X         | X   | 1         |

| ANL      | <byte>, A</byte>     | <byte> = <byte> .AND.A</byte></byte>     | X                |                  |           |     | 1         |

| ANL      | <byte>, #data</byte> | <byte> = <byte> .AND.#data</byte></byte> | X                |                  |           |     | 2         |

| ORL      | A, <byte></byte>     | A = A.OR. <byte></byte>                  | X                | X                | X         | X   | 1         |

| ORL      | <byte>,A</byte>      | <byte> = <byte> .OR.A</byte></byte>      |                  |                  |           |     | 1         |

| ORL      | <byte>,#data</byte>  | <byte> = <byte>.OR.#data</byte></byte>   |                  |                  |           |     | 2         |

| XRL      | A, <byte></byte>     | A = A.XOR. <byte></byte>                 |                  | X                | X         | X   | 1         |

| XRL      | <byte>, A</byte>     | <byte> = <byte> .XOR.A</byte></byte>     | X                |                  |           |     | 1         |

| XRL      | <byte>, #data</byte> | <byte> = <byte> .XOR.#data</byte></byte> | X                |                  |           |     | 2         |

| CRL      | Α                    | A = 00H                                  |                  | Accum            | 1         |     |           |

| CPL      | Α                    | A = .NOT.A                               |                  | Accum            | ulator O  | nly | 1         |

| RL       | A                    | Rotate ACC Left 1 Bit                    |                  | Accum            | ulator O  | nly | 1         |

| RLC      | Α                    | Rotate Left through Carry                | Accumulator Only |                  |           | nly | 1         |

| RR       | Α                    | Rotate ACC Right 1 Bit                   |                  | Accumulator Only |           | 1   |           |

| RRC      | Α                    | Rotate Right through Carry               |                  | Accumulator Only |           | 1   |           |

| SWAP     | Α                    | Swap Nibbles in A                        |                  | Accum            | ulator O  | nly | 1         |

#### Table 3. A List of the SAB-51 Logical Instructions

All of the logical instructions that are Accumulator-specific execute in 1  $\mu s$  (using a 12 MHz clock). The others take 2  $\mu s.$

Note that Boolean operations can be performed on any byte in the internal Data Memory space without going through the Accumulator. The XRL <br/>byte>,<br/>#data instruction, for example, offers a quick and<br/>easy way to invert port bits, as in:

XRL R1,#0FFH

If the operation is in response to an interrupt, not using the Accumulator saves the time and effort to stack it in the service routine.

The Rotate instructions (RL A, RLC A, etc.) shift the Accumulator 1 bit to the left or right. For a left rotation, the MSB rolls into the LSB position. For a right rotation, the LSB rolls into the MSB position.

The SWAP A instruction interchanges the high and low nibbles within the Accumulator. This is a useful operation in BCD manipulations. For example, if the Accumulator contains a binary number which is known to be less than 100, it can be quickly converted to BCD by the following code.

MOV B, #10 DIV AB SWAP A ADD A, B

Dividing the number by 10 leaves the tens digit in the low nibble of the Accumulator, and the ones digit in

the B register. The SWAP and ADD instructions move the tens digit to the high nibble of the Accumulator and the ones digit to the low nibble.

#### Data Transfers

#### Internal RAM

Table 4 shows the menu of instructions that are available for moving data around within the internal memory spaces, and the addressing modes that can be used with each one. With a 12 MHz clock, all of these instructions execute in either 1  $\mu$ s or 2  $\mu$ s.

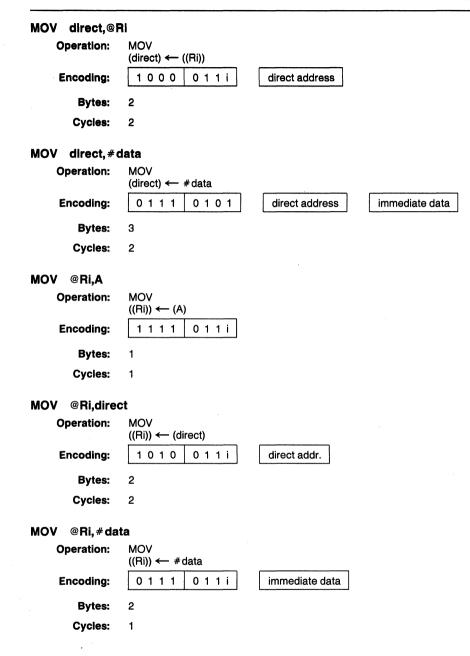

The MOV <dest>, <src> instruction allows data to be transferred between any two internal RAM or SFR locations without going through the Accumulator. Remember the Upper 128 bytes of data RAM can be accessed only by indirect addressing and SFR space only by direct addressing.

Note that in all SAB-51 devices, the stack resides in on-chip RAM, and grows upwards. The PUSH instruction first increments the Stack Pointer (SP), then copies the byte into the stack. PUSH and POP use only direct addressing to identify the byte being saved or restored, but the stack itself is accessed by indirect addressing using the SP register. This means the stack can go into the Upper 128, if they are implemented, but not into SFR space.

| Mnemonic |                            | Operation                           | Ac  | ddress | Execution |     |           |

|----------|----------------------------|-------------------------------------|-----|--------|-----------|-----|-----------|

|          |                            |                                     | Dir | Ind    | Reg       | Imm | Time (µs) |

| MOV      | A, <src></src>             | $A = \langle src \rangle$           | Х   | X      | X         | X   | 1         |

| MOV      | <dest>, A</dest>           | <dest> = A</dest>                   | X   | X      | X         |     | 1         |

| MOV      | <dest>, <src></src></dest> | <dest> = <src></src></dest>         | x   | X      | X         | Х   | 2         |

| MOV      | DPTR, #data16              | DPTR = 16-Bit Immediate Constant    |     |        |           | Х   | 2         |

| PUSH     | <src></src>                | INC SP: MOV "@SP", <src></src>      | х   |        |           |     | 2         |

| POP      | <dest></dest>              | MOV <dest>, "@SP": DEC SP</dest>    | X   |        |           |     | 2         |

| ХСН      | A, <byte></byte>           | ACC and <byte> Exchange Data</byte> | х   | X      | X         |     | 1         |

| XCHD     | A, @Ri                     | ACC and @Ri Exchange Low Nibbles    |     | X      |           |     | 1         |

#### Table 4. A List of the SAB-51 Data Transfer Instructions that Access Internal Data Memory Space

#### SAB-51 Architectural Overview

The Upper 128 Bytes are not implemented in the 8051A, 80C51 and 80512, nor in their ROMless counterparts. With these devices, if the SP points to the Upper 128, PUSHed bytes are lost, and POPped bytes are indeterminate.

The Data Transfer instructions include a 16-bit MOV that can be used to initialize the Data Pointer (DPTR) for look-up tables in Program Memory, or for 16-bit external Data Memory accesses. Refer to the SAB 80C517 Data Sheet for extended Data Pointer Capabilities.

The XCH A, <br/>byte> instruction causes the Accumulator and addressed byte to exchange data. The XCHD A,@Ri instruction is similar, but only the low nibbles are involved in the exchange.

To see how XCH and XCHD can be used to facilitate data manipulations, consider first the problem of shifting an 8-digit BCD number two digits to the right. Figure 11 shows how this can be done using direct MOVs, and for comparison how it can be done using XCH instructions. To aid in understanding how the code works, the contents of the registers that are holding the BCD number and the content of the Accumulator are shown alongside each instruction to indicate their status after the instruction has been executed.

| · · · · |          | 2A | 2B  | 2C | 2D | 2E | ACC |

|---------|----------|----|-----|----|----|----|-----|

| MOV     | A, 2EH   | 00 | 12  | 34 | 56 | 78 | 78  |

| MOV     | 2EH, 2DH | 00 | 12  | 34 | 56 | 56 | 78  |

| MOV     | 2DH, 2CH | 00 | 12  | 34 | 34 | 56 | 78  |

| MOV     | 2CH, 2BH | 00 | 12  | 12 | 34 | 56 | 78  |

| MOV     | 2BH, #0  | 00 | .00 | 12 | 34 | 56 | 78  |

(a) Using Direct MOVs: 14 Bytes, 9 µs

|     |        | 2A | 2B | 2C | 2D | 2E | ACC  |

|-----|--------|----|----|----|----|----|------|

| CLR | Α      | 00 | 12 | 34 | 56 | 78 | 00   |

| XCH | A, 2BH | 00 | 00 | 34 | 56 | 78 | 12   |

| XCH | A, 2CH | 00 | 00 | 12 | 56 | 78 | . 34 |

| XCH | A, 2DH | 00 | 00 | 12 | 34 | 78 | 56   |

| XCH | A, 2EH | 00 | 00 | 12 | 34 | 56 | 78   |

|     |        |    |    |    |    |    |      |

(b) Using XCH<sub>S1</sub> 9 Bytes, 5 μs

#### Figure 11. Shifting a BCD Number Two Digits to the Right

After the routine has been executed, the Accumulator contains the two digits that were shifted out on the right. Doing the routine with direct MOVs uses 14 code bytes and 9  $\mu$ s of execution time (assuming a 12 MHz clock). The same operation with XCHs uses less code and executes almost twice as fast. To right-shift by an odd number of digits, a one-digit shift must be executed. Figure 12 shows a sample of code that will right-shift a BCD number one digit, using the XCHD instruction. Again, the contents of the registers holding the number and of the Accumulator are shown alongside each instruction.

|       |            |                                       | 214 - X    |    | 1   |    |    |       |          |

|-------|------------|---------------------------------------|------------|----|-----|----|----|-------|----------|

|       |            | ien di di                             | 2          | A  | 2B  | 2C | 2D | 2E    | ACC      |

|       | MOV        | R1, #2EH                              |            |    |     |    | 56 |       |          |

|       | MOV        | R0, #2DH                              | 0          | ol | 12  | 34 | 56 | 78    | XX       |

|       | Loop f     | or R1 = 2EH                           | <b>ł</b> : |    |     |    |    |       |          |

| LOOP: | MOV        | A, @R1                                | 0          | o  | 12  | 34 | 56 | 78    | 76       |

| 1     | XCHD       | A, @R0                                | 0          | 0  | 12  | 34 | 58 | 78    | 76       |

|       | SWAP       | A                                     | 0          | 0  | 12  | 34 | 58 | 78    | .67      |

|       | MOV        | @R1, A                                | 0          | 0  | 12  | 34 | 58 | 67    | 67       |

|       | DEC        | R1                                    | 0          | 0  | 12  | 34 | 58 | 67    | 67       |

|       | DEC        | R0                                    | 0          | 0  | 12  | 34 | 58 | 67    | 67       |

|       | CJNE       | R1, #2AH,                             | LOO        | Ρ  |     |    |    | e e k |          |

|       |            | · · · · · · · · · · · · · · · · · · · | 11         | .  |     | ·  |    |       |          |

|       |            | or R1 = 2D                            |            |    |     |    |    |       |          |

|       |            | or $R1 = 2CH$                         |            |    |     |    |    |       |          |

|       | Loop f     | or $R1 = 2BH$                         | H: 10      | 8  | 101 | 23 | 45 | 67    | 01       |

|       |            | ٨                                     | ما         | 。  | 04  | 00 | AF | 67    |          |

|       | CLR<br>XCH |                                       | 0          | 0  |     | 23 | 40 | 67    | 00<br>08 |

|       | лоп        | A, 2AH                                | 10         | U  |     | 23 | 40 | 0/    |          |

|       |            |                                       |            |    |     |    |    |       |          |

#### Figure 12. Shifting a BCD Number One Digit to the Right

First, pointers R1 and R0 are set up to point to the two bytes containing the last four BCD digits. Then a loop is executed which leaves the last byte, location 2EH, holding the last two digits of the shifted number. The pointers are decremented, and the loop is repeated for location 2DH. The CJNE instruction (Compare and Jump if Not Equal) is a loop control that will be described later.

The loop is executed from LOOP to CJNE for R1 2EH, 2DH, 2CH and 2BH. At that point the digit that was originally shifted out on the right has propagated to location 2AH. Since that location should be left with 0s, the lost digit is moved to the Accumulator.

#### **External RAM**

Table 5 shows a list of the Data Transfer instructions that access external Data Memory. Only indirect addressing can be used. The choice is whether to use a one-byte address, @Ri, where Ri can be either R0 or R1 of the selected register bank, or a two-byte address, @DPTR. The disadvantage to using 16-bit addresses if only a few Kbytes of external RAM are involved is that 16-bit addresses use all 8 bits of Port 2 as address bus. On the other hand, 8-bit addresses allow one to address a few Kbytes of RAM, as shown in Figure 5, without having to sacrifice all of Port 2.

All of thes instructions execute in 2  $\mu s,$  with a  $^\circ$  12 MHz clock.

#### Table 5. A List of the SAB-51 Data Transfer Instructions that Access External Data Memory Space

| Address<br>Width | Mnemonic      | Operation                   | Execution<br>Time (µs) |

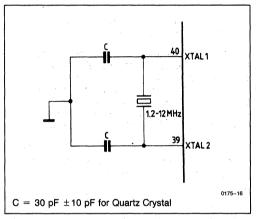

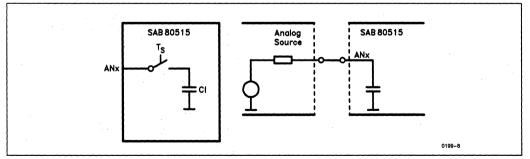

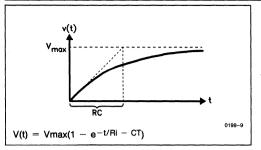

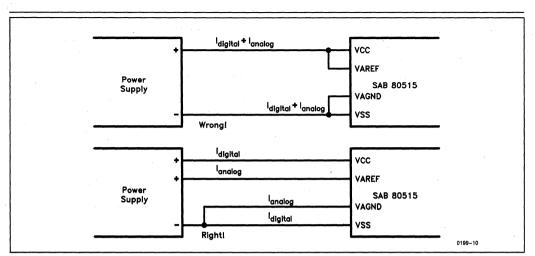

|------------------|---------------|-----------------------------|------------------------|